# Development of CMOS pixel sensors for a vertex detector suited to the ILC

Yunan Fu

### ▶ To cite this version:

Yunan Fu. Development of CMOS pixel sensors for a vertex detector suited to the ILC. Other. Université de Strasbourg, 2012. English. NNT: 2012STRAE032. tel-00869940

### HAL Id: tel-00869940 https://theses.hal.science/tel-00869940v1

Submitted on 4 Oct 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

No d'ordre: 77434

### Ecole Doctorale de Physique, Chimie-Physique - ED 182

UDS - IPHC - CNRS/IN2P3

# **THÈSE**

### Présentée pour obtenir le grade de

### Docteur de l'Université de Strasbourg

Discipline: Électronique, Électrotechnique et Automatique

Spécialité : Instrumentation et Microélectronique

par

### Yunan FU

### Développement de Capteurs à Pixel CMOS pour un Détecteur de Vertex Adapté au Collisionneur ILC

Soutenue publiquement le 09 May 2012 devant le jury:

Directeur de thèse : Marc WINTER Directeur de Recherches - IPHC-UDS-IN2P3, France

Rapporteur : Norbert WERMES Professeur - Université de Bonn, Allemagne Rapporteur : Valerio RE Professeur - Université de Bergamo, Italie

Examinateur : Christophe DE LA TAILLE Directeur technique de l'IN2P3-CNRS, France

Examinateur : Yann HU Professeur - Université de Strasbourg, France

No d'ordre: 77434

### Doctoral School of Physics, Chemistry-Physics - ED 182

UDS - IPHC - CNRS/IN2P3

### **THESIS**

### Presented to obtain the degree of

### Doctor of Philosophy in University of Strasbourg

Discipline: Electronics, Electrotechnique and Automation Specialty: Instrumentation and Microelectronics

by

### Yunan FU

# Development of CMOS Pixel Sensors for a Vertex Detector Suited to the ILC

Submitted publicly on  $09^{th}$  May 2012 to the jury:

Director of thesis: Marc WINTER Director of research - IPHC-UDS-IN2P3, France

Reporter: Norbert WERMES Professor - University of Bonn, Germany

Reporter: Valerio RE Professor - University of Bergamo, Italy

Examiner: Christophe DE LA TAILLE Technique director of IN2P3-CNRS, France

Examiner: Yann HU Professor - University of Strasbourg, France

# Contents

| $\mathbf{A}$ | ckno                   | wledgn  | nents                                                                 | 7  |

|--------------|------------------------|---------|-----------------------------------------------------------------------|----|

| In           | trod                   | uction  |                                                                       | 14 |

| 1            | $\mathbf{C}\mathbf{M}$ | OS pi   | xel sensors for the ILC vertex detector                               | 1  |

|              | 1.1                    | Scient  | ific motivation for the ILC                                           | 1  |

|              | 1.2                    | Requi   | rements for CMOS pixel sensors                                        | 4  |

|              |                        | 1.2.1   | Requirements from the physics goals                                   | 4  |

|              |                        | 1.2.2   | Requirements from the running conditions                              | 5  |

|              |                        |         | 1.2.2.1 Readout speed                                                 | 5  |

|              |                        |         | 1.2.2.2 Radiation tolerance                                           | 6  |

|              |                        | 1.2.3   | Power consumption considerations                                      | 6  |

|              | 1.3                    | R&D     | on CMOS pixel sensors adapted to the ILC vertex detector              | 7  |

|              |                        | 1.3.1   | Principle of standard CMOS pixel sensors                              | 7  |

|              |                        | 1.3.2   | Why considering CMOS pixel sensors for the ILC?                       | 8  |

|              |                        | 1.3.3   | Potential of CMOS pixel sensors                                       | 10 |

|              |                        |         | 1.3.3.1 $$ Full charge collection by drift in a depleted EPI layer $$ | 10 |

|              |                        |         | 1.3.3.2 Full CMOS electronics in the active area                      | 11 |

|              |                        |         | 1.3.3.3 3D Integrated CMOS pixel sensors                              | 14 |

|              | 1.4                    | Concl   | usion                                                                 | 15 |

| 2            | Offs                   | set con | npensated in-pixel amplifiers for CMOS pixel sensors                  | 17 |

|              | 2.1                    | Ultra-  | light pixelated ladders for an ILC vertex detector                    | 18 |

|              |                        | 2.1.1   | Full-scale sensor with binary readout architecture                    | 19 |

|              |                        | 2.1.2   | PLUME ladder concept                                                  | 21 |

|              | 2.2                    | Topolo  | ogy and analysis of MIMOSA-26 pixels                                  | 23 |

|              |                        | 2.2.1   | MIMOSA-26 pixel architecture                                          | 23 |

4 Contents

|   |      |         | 2.2.1.1 In-pixel amplifier used in MIMOSA-26                   |

|---|------|---------|----------------------------------------------------------------|

|   |      |         | 2.2.1.2 Calibration procedure                                  |

|   |      |         | 2.2.1.3 Characterization of MIMOSA-26 sensors                  |

|   | 2.3  | Noise : | sources in CMOS pixel sensors                                  |

|   |      | 2.3.1   | Leakage current related shot noise                             |

|   |      | 2.3.2   | Thermal noise                                                  |

|   |      | 2.3.3   | Flicker noise                                                  |

|   |      | 2.3.4   | Board-level noise                                              |

|   |      | 2.3.5   | Fixed pattern noise                                            |

|   |      | 2.3.6   | Correlated double sampling technique                           |

|   | 2.4  | Multi-  | stage in-pixel amplifiers with the CDS circuitry               |

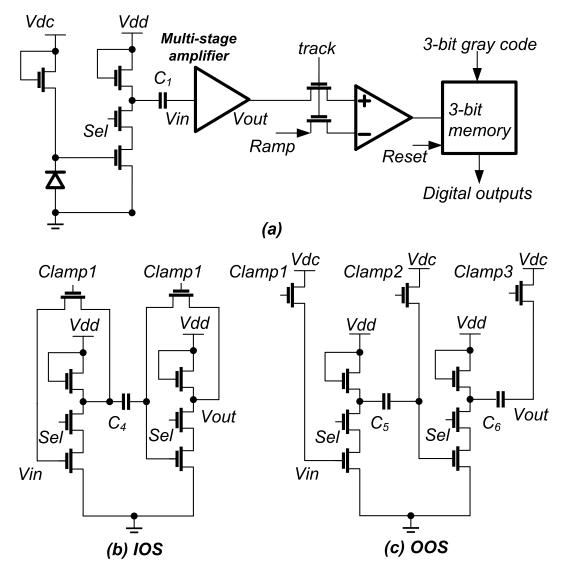

|   |      | 2.4.1   | Multi-stage amplifiers with input offset cancellation          |

|   |      | 2.4.2   | Multi-stage amplifiers with output offset cancellation         |

|   |      | 2.4.3   | Multi-stage amplifiers with hybrid offset cancellations        |

|   | 2.5  | Sensor  | implementation                                                 |

|   |      | 2.5.1   | Simulated characteristics of the pixel architecture            |

|   |      |         | 2.5.1.1 DC characteristics of the pixel-level amplifier        |

|   |      |         | 2.5.1.2 Noise analysis                                         |

|   |      | 2.5.2   | Measurement results                                            |

|   |      |         | 2.5.2.1 Noise calculation algorithm                            |

|   |      |         | 2.5.2.2 Measurement of CVF                                     |

|   |      |         | 2.5.2.3 Noise performance                                      |

|   |      |         | 2.5.2.4 Lessons learned and future plans                       |

|   | 2.6  | Conclu  | sion                                                           |

| 3 | 3D i | integra | ated CMOS pixel sensors with a delayed readout architecture 47 |

|   | 3.1  | Ü       | tages of 3D integrated CMOS pixel sensors                      |

|   | 3.2  |         | on 3D vertical integration technique                           |

|   | 3.3  |         | yping strategy of delayed readout architecture                 |

|   | 3.4  |         | ogy and circuit analysis                                       |

|   |      | 3.4.1   | Pixel design on the analog tier                                |

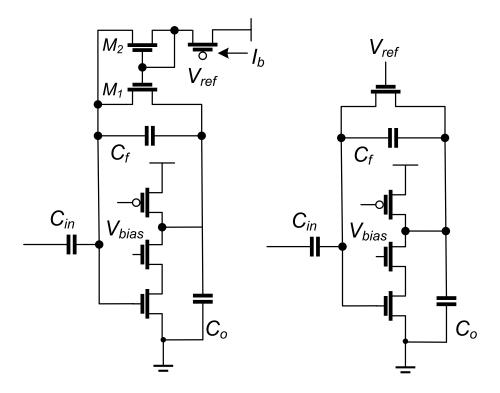

|   |      |         | 3.4.1.1 Feedback with a constant current                       |

|   |      |         | 3.4.1.2 Feedback with MOS in saturation                        |

|   |      |         | 3.4.1.3 Zero crossing pixel-level discriminator                |

|   |      |         |                                                                |

|   |      |          | 3.4.1.4 Noise in the analog front-end                     | 59 |

|---|------|----------|-----------------------------------------------------------|----|

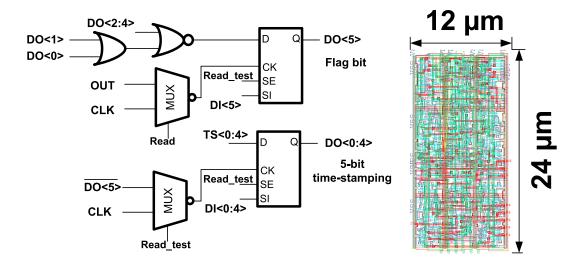

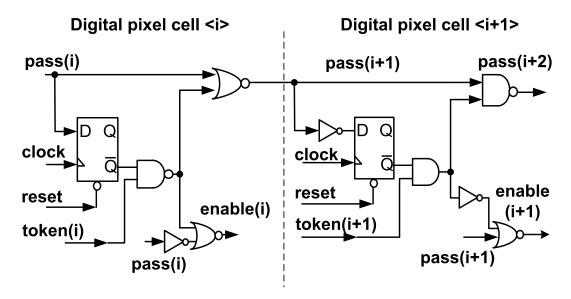

|   |      | 3.4.2    | Pixel design on the digital tier                          | 33 |

|   |      | 3.4.3    | Delayed readout                                           | 34 |

|   | 3.5  | Exper    | imental results and discussion                            | 66 |

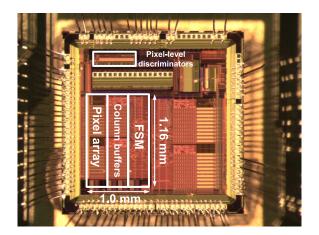

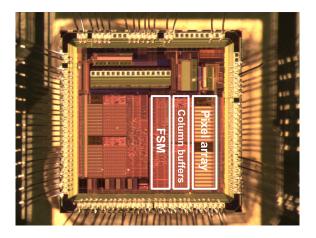

|   |      | 3.5.1    | Description of the chip                                   | 66 |

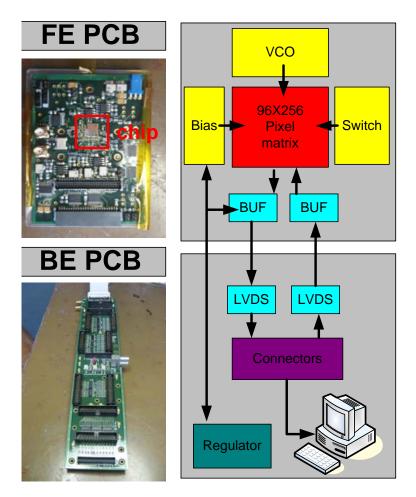

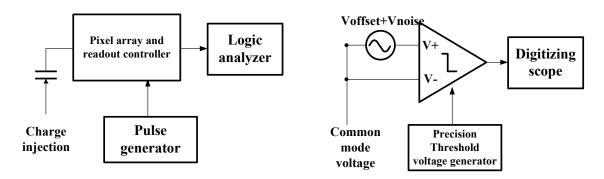

|   |      | 3.5.2    | Test setup                                                | 67 |

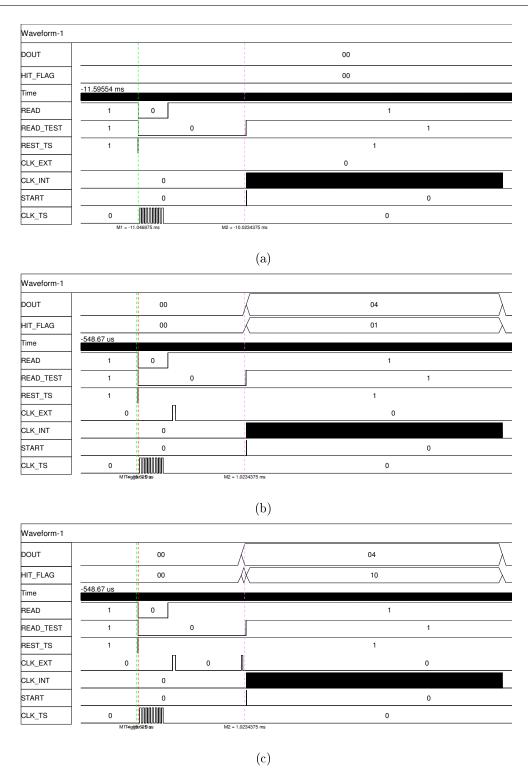

|   |      | 3.5.3    | Measurement of misaligned 2D chips                        | 38 |

|   |      | 3.5.4    | Discussion                                                | 70 |

|   | 3.6  | Concl    | asion                                                     | 70 |

| 4 | 3D   | integr   | ated CMOS pixel sensors with a continuous rolling shutter |    |

|   | reac | dout     | 7                                                         | 73 |

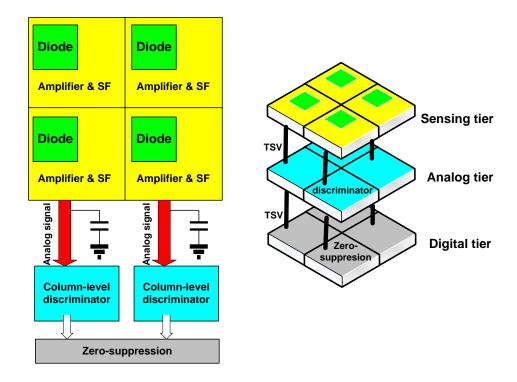

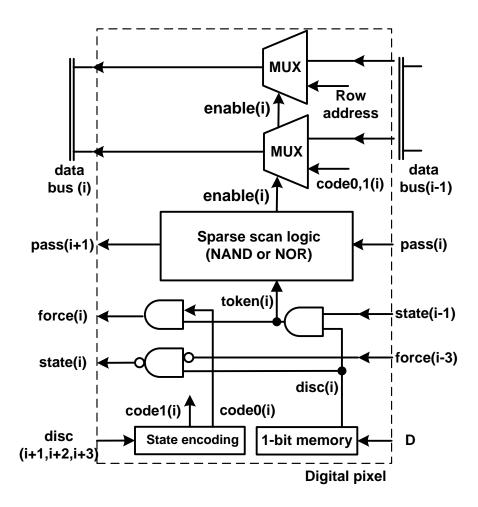

|   | 4.1  | 3D int   | egrated CMOS pixel sensors based on a continuous readout  | 74 |

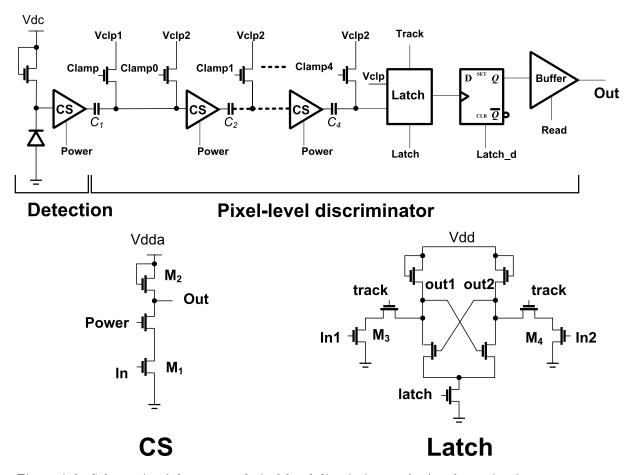

|   | 4.2  | High s   | peed pixel-level discriminator                            | 76 |

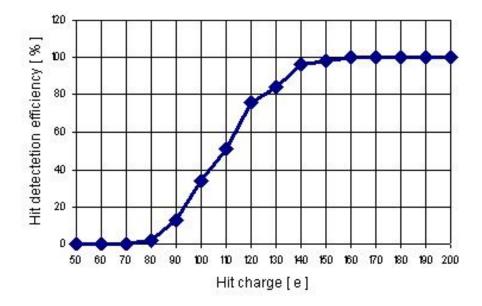

|   | 4.3  | Pixel-l  | evel zero suppressed readout                              | 30 |

|   | 4.4  | Reado    | ut controller design                                      | 34 |

|   | 4.5  | Circui   | t implementation                                          | 34 |

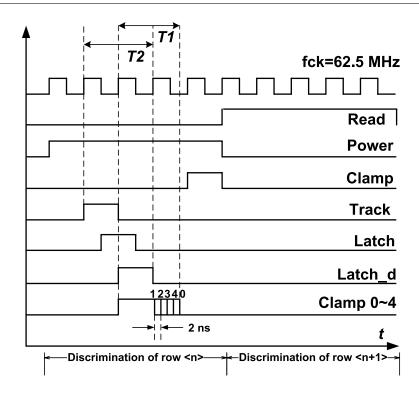

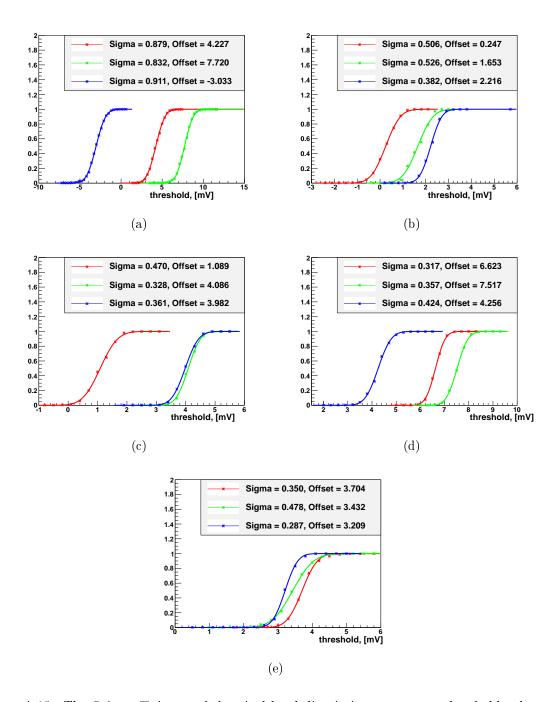

|   |      | 4.5.1    | Experimental results of the pixel-level discriminators    | 37 |

|   |      | 4.5.2    | Lessons learned and future plans                          | 90 |

|   | 4.6  | Concl    | ısion                                                     | 91 |

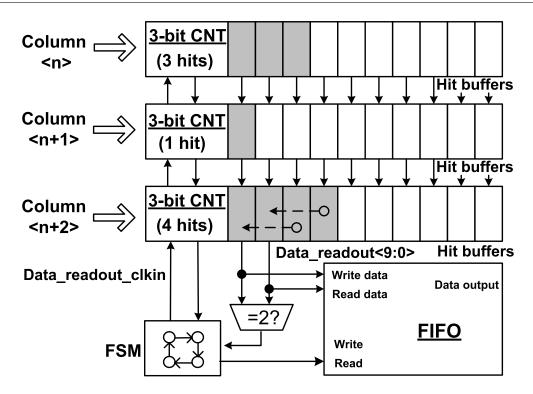

| 5 | 3-bi | it pixel | -level ADCs designed for 3D integrated CMOS pixel sensors | 93 |

|   | 5.1  | Motiva   | ation of integrating ADCs in CMOS pixel sensors           | 93 |

|   |      | 5.1.1    | ADC integration approaches                                | 93 |

|   |      | 5.1.2    | Which kind of pixel-level ADC?                            | 95 |

|   | 5.2  | Specif   | ications of the ADC                                       | 96 |

|   | 5.3  | A 3-bi   | t pixel-level single-slope ramp ADC                       | 98 |

|   |      | 5.3.1    | Principle of the single-slope ramp ADC                    | 98 |

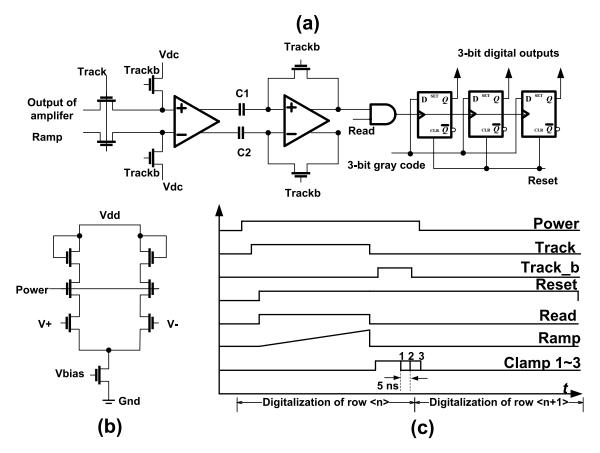

|   |      | 5.3.2    | Pixel-level ADC architecture                              | 99 |

|   | 5.4  | Exper    | imental measurements                                      | )2 |

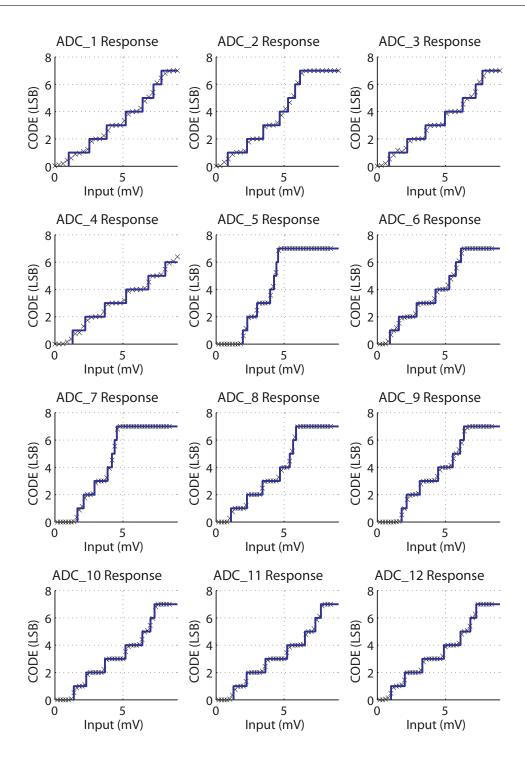

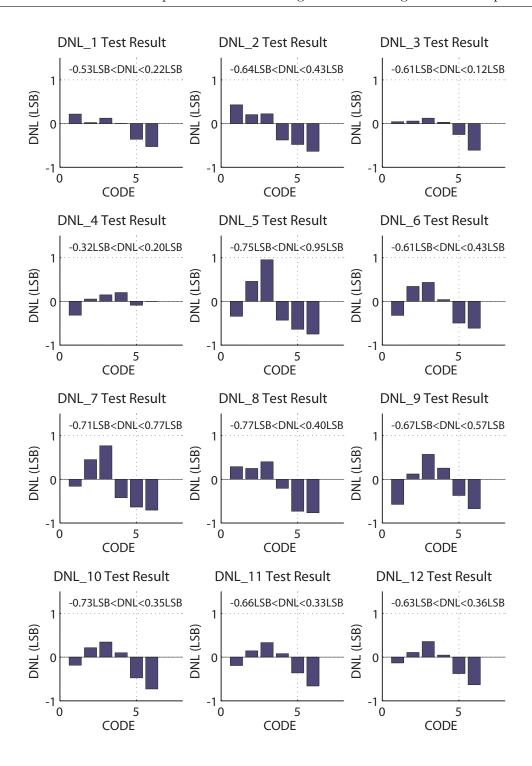

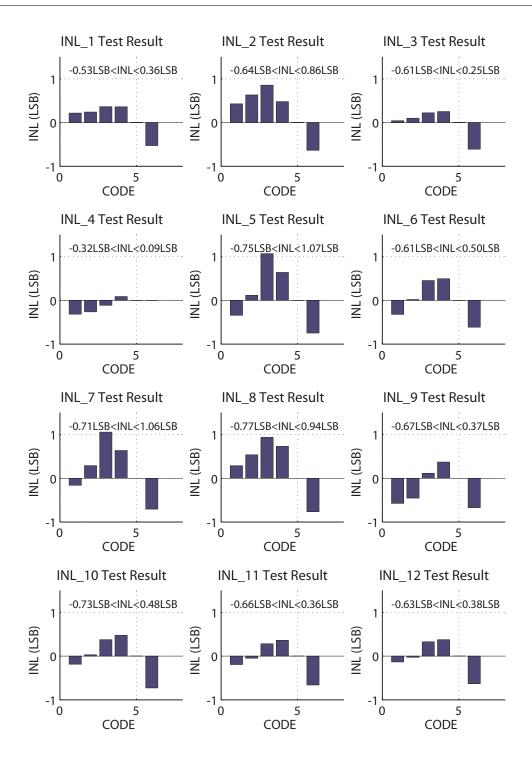

|   |      | 5.4.1    | Chip description and test setup                           | )2 |

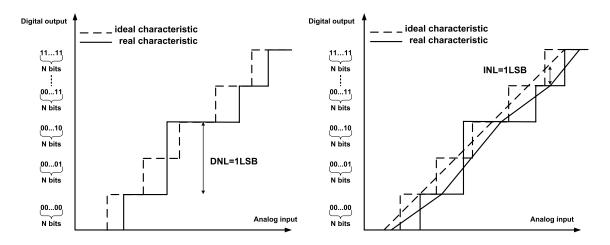

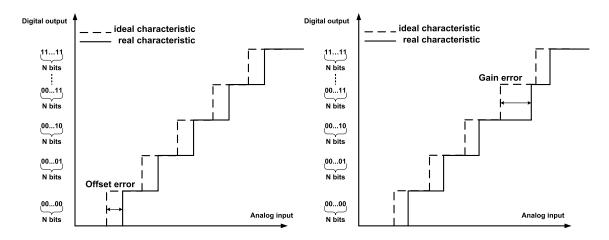

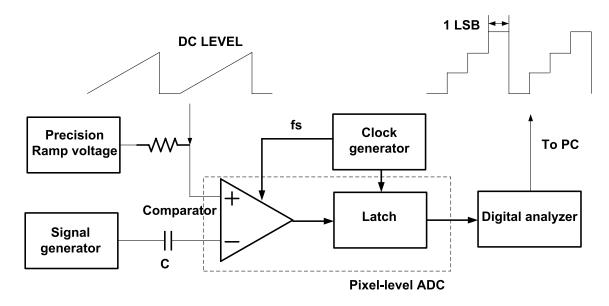

|   |      | 5.4.2    | Test methods of the pixel-level ADCs                      | )2 |

|   |      | 5.4.3    | Test results of the pixel-level ADCs                      | )3 |

|   |      | 5.4.4    | Lessons learned and future plans                          | )8 |

| 6 | Contents |

|---|----------|

|---|----------|

|         | 5.5 Conclusion                                            | 109 |

|---------|-----------------------------------------------------------|-----|

| 6       | Summary and outlook                                       | 111 |

|         | 6.1 Achievements of this thesis                           | 111 |

|         | 6.2 Future plans                                          | 114 |

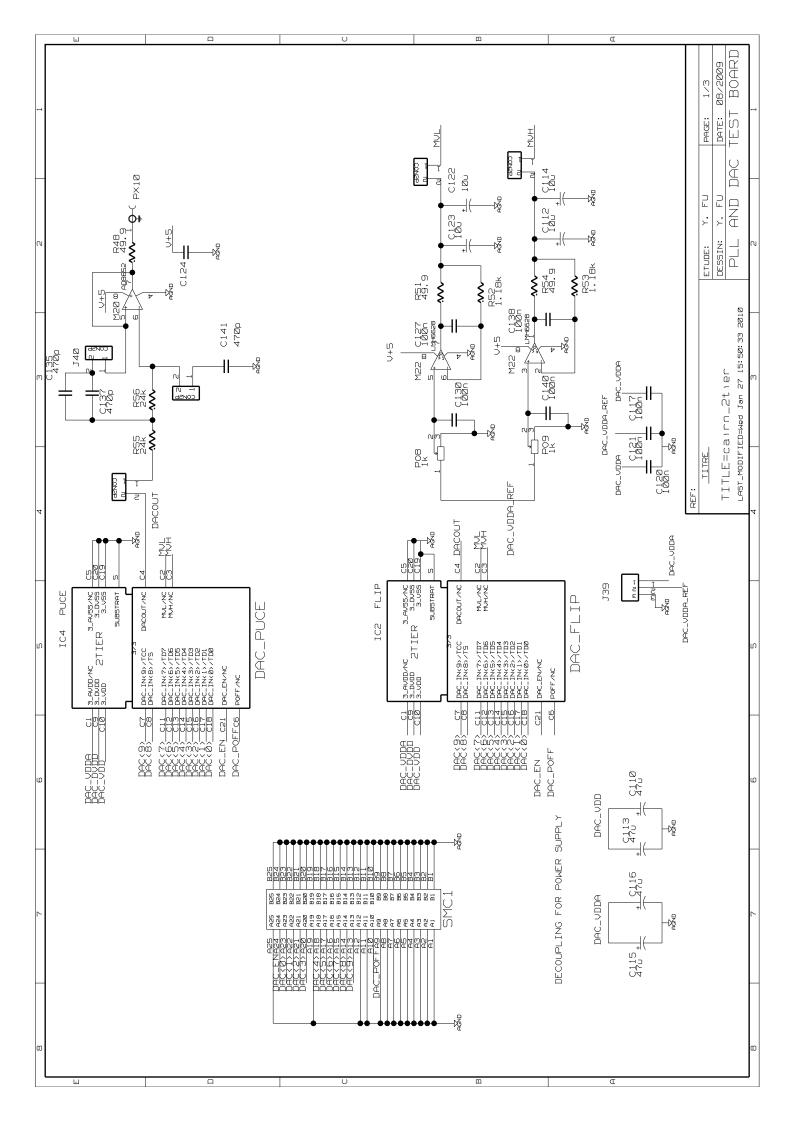

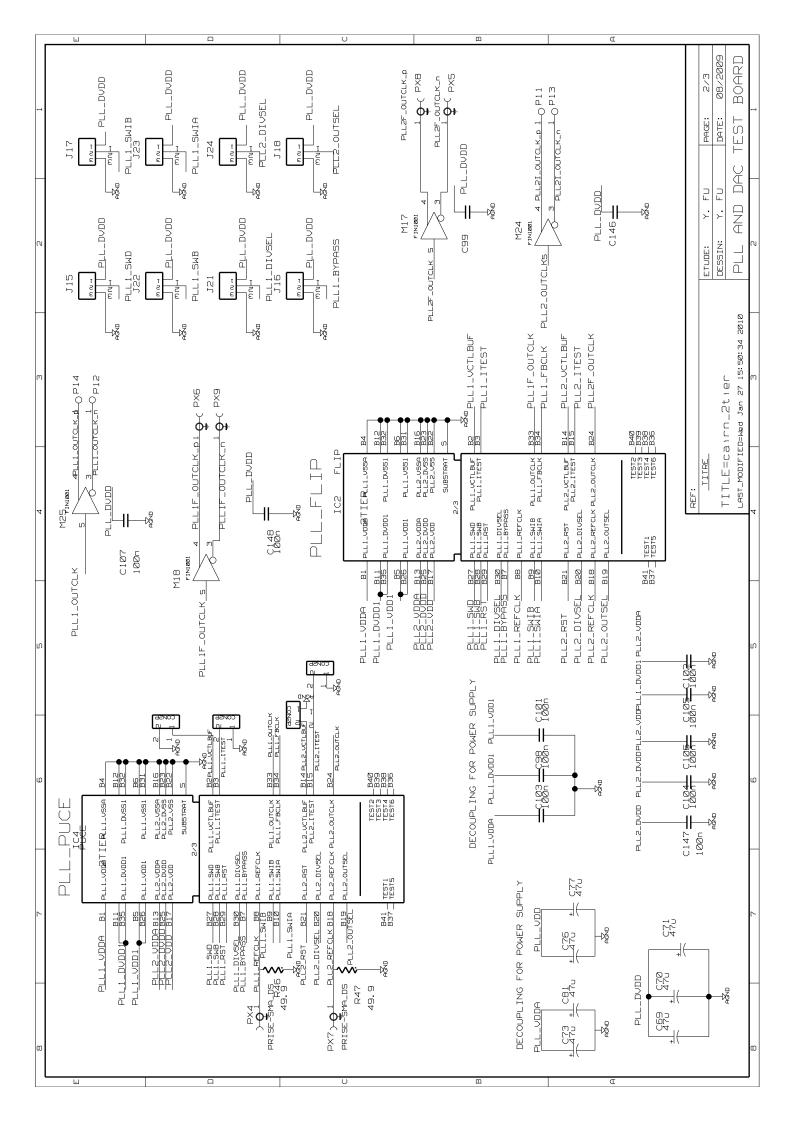

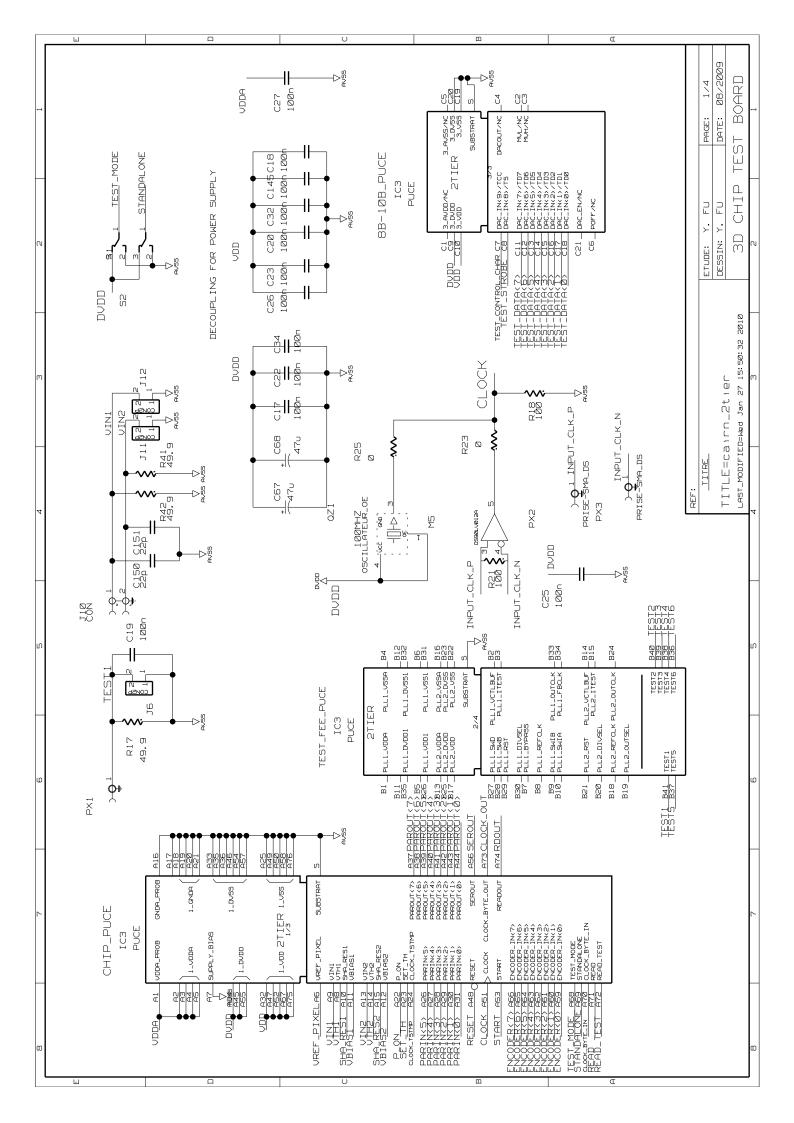

| ${f A}$ | Schematic of the test boards for the CAIRN-1 and CAIRN-2D | 117 |

## Acknowledgments

This work has been accomplished in the group of PICSEL (Physics with Integrated Cmos Sensors and ELectron machines) at IPHC. I would like to thank my thesis supervisor Marc Winter for combination of support and freedom he gave me, as well as for invaluable stimulating discussions.

Prof. Yann Hu as a professional specialist and Christine Guo-Hu as a micro-electronic group head have enabled and supported this thesis, which would have been impossible without them. Additional thanks for detailed partial proofreading of this thesis and, more importantly, for many interesting technical as well as non-technical discussions are owed to Jerome Baudot, Michal Szelezniak, Andrei Dorokhov and Olave Torheim.

Gilles Claus, Kimmo Jaaskelainen, Matthieu Specht and Mathieu Goffe gave me support for anything related to hardware and software aspects of the test bench and provided me with very useful suggestions of designing the test boards.

Wojciech Dulinski, Claude Colledani, Isabelle Valin and Hung Pham have always shared their tremendous knowledge on CMOS pixel sensors and have helped me getting familiar with the topic in my early days. Later on, technical discussions with Guy Doziere, Frederic Morel, Gregory Bertolone and Xiaochao Fang have also been very interesting and helpful, due to complementary aspects of our work.

It goes without saying that I am indebted to all the people whose contributions, small and large, made my work and my life easier during the period that I spent working for this thesis. The list of their names would be too long to write down.

Strasbourg, 2012

### Introduction

A large fraction of the world wide particle physics community elaborates its future on an e+ e- collider called International Linear Collider (ILC), which is expected to start providing beams for physics beyond 2020. The ILC offers experimental conditions which allow for very high precision measurements, provided the experiments installed around the beam interaction regions exhibit a sensitivity allowing to take advantage of these favorable conditions.

Existing detection technologies, such as those used at the Large Hardon Collider (LHC), are often inadequate for this purpose. The case is particularly striking for the vertex detector, which requires developing a new generation of sensors, which would be much more granular and thin than those in use, while allowing to cope with the intense beam related background particles which swamp the inner layer of the detector.

Several pixel technologies are being developed since many years to comply with the required specifications. CMOS pixel sensors (CPS)<sup>1</sup> are well suited for this type of application, where the running conditions are still not as demanding as those imposed at hadron colliders such as the LHC. The fact that the running conditions are milder allows privileging the specifications imposed by the physics goals, and fosters developing a sensor design allowing for the fastest readout speed and highest radiation tolerance not affecting the physics driven performances.

CPS are being developed at IPHC since more than a decade for this purpose, motivated by the necessary readout speed and power consumption improvements, the radiation tolerance being a lesser issue despite the ambition to run at room temperature.

The readout speed achieved up to now complies with the requirements expressed in the Letter of Intent (LoI) of the International Large Detector (ILD) detector concept, adapted to the first phase of the ILC project (characterized by a collision energy of up to 500 GeV). It is not suited to the higher particle rate expected at the energies foreseen

<sup>&</sup>lt;sup>1</sup>CMOS pixel sensors are also called CMOS Monolithic Active Pixel Sensors (MAPS).

10 Contents

for the second phase of the collider running (up to about 1 TeV). A higher readout speed than the one achieved today would also allow feeling more comfortable in case the beam background turns out to be much higher than expected.

The goal for this second phase is to reach a readout time below 10  $\mu$ s while keeping the spatial resolution below 3  $\mu$ m. Speed and resolution are strongly correlated parameters: in the column parallel readout architecture on which present sensors are based, a small pixel pitch, as required by the ambitioned resolution, translates into a large number of pixels to be read out (serially) in each column, at the expense of the readout speed and, possibly, of the power consumption.

3D integration technologies (3DIT) provide a way to mitigate this hampering correlation between speed and resolution, since they allow to staple layers of readout circuitry on top of the sensing layer, which results in a drastic increase of the functionalities located in (the shadow of) each pixel. A multi-layer structure allows for a higher spatial resolution because more and more transistors may be integrated vertically in a relatively small pixel. Moreover, bringing the components of the sensor closer to each other translates in a faster readout, owing to the reduction in the average length of the inner-connecting wires. Vertical integration also opens up the possibility of combining different technologies best suited to each of the sensor main functionalities (signal sensing, analog and digital signal processing and transmission). 3D-CPS are thus expected to overcome most of the limitations of 2D-CPS, and are therefore suspected to offer new perspectives for the innermost layer of the ILC vertex detector. This thesis was motivated by these perspectives.

Besides emerging 3D integration techniques, a double-sided ladder<sup>2</sup> concept based on 2D-CPS is another way to alleviate, though in a lesser extent, the conflict between speed and resolution. This approach consists in equipping each side of the ladders composing the detector with sensors optimized for different, but complementary, functionalities: spatial resolution on one side and time resolution on the other. The two functionalities are combined for traversing particles by correlating their impacts reconstructed on each ladder side.

While the concept is based on the position resolution delivered by state-of-the-art sensors (based on square pixels), the time resolution requires steps ahead. A part of this thesis is devoted to the design of 2D-CPS with novel in-pixel amplifiers and pixel-level discriminators for this purpose, relying on elongated pixels. Sensors made of both types

<sup>&</sup>lt;sup>2</sup>Called PLUME ladder (Pixelated Ladder with Ultra-low Material Embedding).

of pixels were fabricated in a multi-well CMOS technology, which allows for in-pixel full CMOS capability without degradation of the detection efficiency. These 2D-CPS with significant in-pixel processing capability are important forerunners of those fully complying with the targeted requirements.

### Micro-circuit designs developed within the thesis

Several micro-circuits were designed within the framework of the thesis, adapted to the evolution of the sensors developed by the PICSEL group of IPHC. Some main features of these sensors are summarized below. The development of CPS for charged particle tracking was started at IPHC in the late nineties. In these devices, the sensor volume and electronics share the same substrate, and in-pixel signal processing can be performed. The charge is generated in the sensing layer and reaches the electrodes by thermal diffusion in the CMOS technologies with a low-resistivity epitaxial layer. This scheme allows for a high granularity with resolution down to  $\sim 1-2~\mu m$  at very low noise. The question was raised on how the other driving parameters of the innermost layer of the ILC vertex detector, i.e. the sensor readout speed and power consumption, can be accommodated.

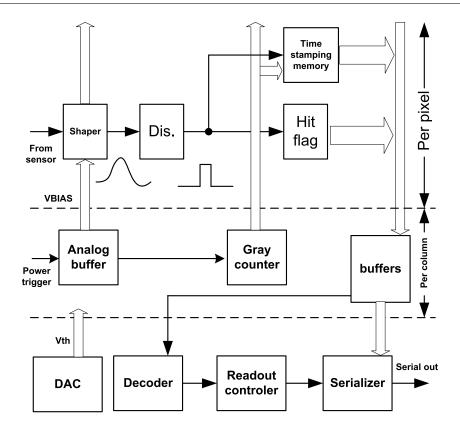

In order to obtain a high readout speed, the pixel columns of a pixel array are read out in parallel by sweeping the array with a row-wise rolling shutter (e.g. MIMOSA-26 sensors). A singularity of CPS is that their integration time corresponds to the readout time of the whole pixel array. Although MIMOSA-26 sensors have made a big progress in terms of integration time reduction (it amounts to  $\sim 100~\mu s$ ), the column parallel architecture becomes a bottleneck to improve the readout speed for a large-scale pixel array. The global frame readout time is actually limited by the sizable number of rows (typically several hundreds to about one thousand) and the row processing time (typically 200 ns). A pixelated double-sided ladder equipped with two types of 2D-CPS is a first step against this bottleneck. This approach is also advantageous in terms of power consumption.

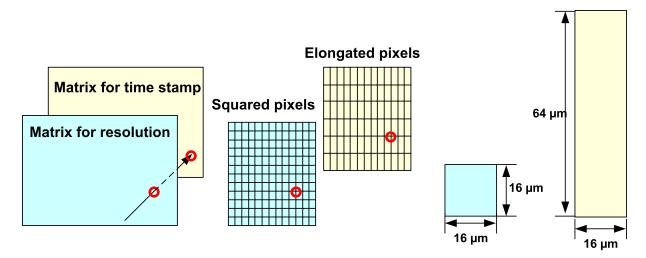

The required spatial resolution can be achieved with square pixels of  $\sim$  16  $\mu$ m pitch. A shortening of the readout time may be obtained with an elongated pixel pitch in the column readout direction. By correlating the two hits on both faces of the ladder generated by a traversing particle, the latter gets assigned a spatial resolution of  $\sim$  3  $\mu$ m together with a time resolution of below 10  $\mu$ s.

12 Contents

To obtain the ambitioned single point resolution, a  $\lesssim 16 \ \mu m$  pitch pixel with a novel in-pixel amplifier was designed. Theory, circuit simulation and measurement of implemented structure indicate that this advantageous **multi-stage in-pixel amplifier** can potentially provide a better signal-to-noise ratio (SNR) performance than a single-stage amplifier, currently used in present 2D-CPS.

To reach the targeted time resolution, a 16  $\mu$ m  $\times$  80  $\mu$ m pitch pixel with a pixel-level discriminator was developed. This **digital pixel sensor architecture** allows digitizing the signal charge within each pixel. Moreover, the readout gets substantially accelerated, as compared to the conventional methodology in which the signal is accumulated on a large parasitic capacitor at each column end. In addition, a relatively large current is required to drive the parasitic capacitor and to maintain a satisfactory signal-to-noise ratio of the analog outputs used in the conventional designs, which translates into extra power consumption. The in-pixel digital outputs make the new approach amenable to development of low-power 2D-CPS, for it eliminates the analog readout bottlenecks. This approach was addressed extensively in this thesis. Its fast readout speed, integration capabilities and low power operation represent a substantial progress w.r.t. existing 2D-CPS approaches.

The next important topic of the thesis concerns 3D-CPS. An important part of the work was devoted to the achievement of low noise, fast, sensors as required for the ILC vertex detector, while keeping the power consumption at an affordable level. Two alternative readout approaches are being investigated: one, called delayed readout, where the signals are stored in the sensors during the bunch train interval and read out during the beam-less period (adapted to the beam time structure of the ILC), and another, called continuous readout, where the sensors continuously transfer the measured signals for readout. In this thesis, these two complementary readout strategies were explored in parallel in order to evaluate and compare their potential and benefits.

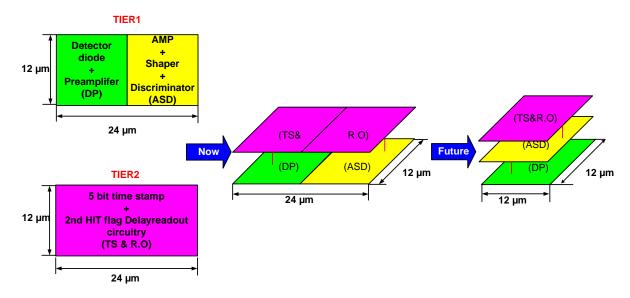

The delayed readout approach is motivated by power savings. It consists in implementing a circuitry which accumulates the hits from each pixel during the complete collider train, and to read it out in between consecutive trains using a very low-frequency clock. **3D-CPS with delayed readout**: A 2-tier sensor featuring a 12  $\mu$ m pitch pixel array, which incorporates in-pixel signal discrimination and time-stamping, was developed in the framework of the thesis. The pixel cell of the bottom (analog) layer includes an n-well/p-substrate diode, a shaper and a threshold discriminator, whose output is

vertically interconnected to the digital pixel on the top tier. Each digital pixel has the capability for storing double hits and the 5-bit time stamps of the relevant first hit.

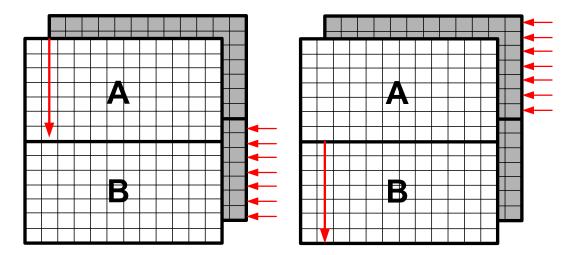

Another 3D-CPS with continuous readout (i.e. parallel rolling shutter readout) was designed, developed and tested in this thesis. By taking advantages of 3DIT, the parallel continuous readout architecture overcomes many limitations imposed by conventional rolling shutter readout. The entire pixel array could be split into several sub-arrays. Each sub-array is organized independently in a rolling shutter mode and all sub-arrays are read out in parallel. The global frame readout time is therefore reduced to the time of rolling the shutter across the exposable sensitive area of each sub-array. Moreover, with the reduced parasitic capacitors between analog and digital sections, it is possible to place a considerable amount of small pixels with a power saving feature. The power consumption estimation also shows that this readout architecture has the potential to comply with the power dissipation constraints set for the ILD vertex detector, despite the consumption increase consecutive to the parallelized readout.

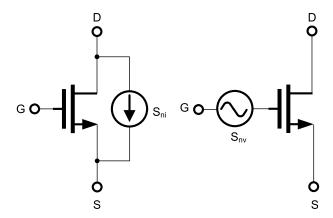

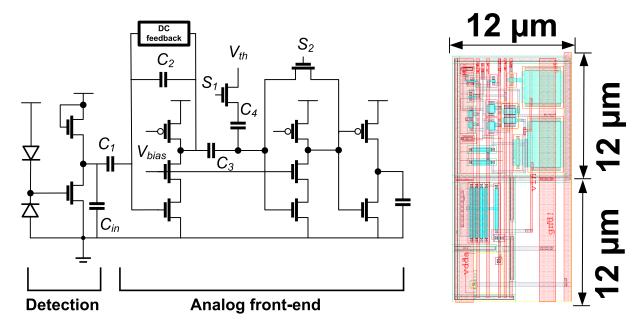

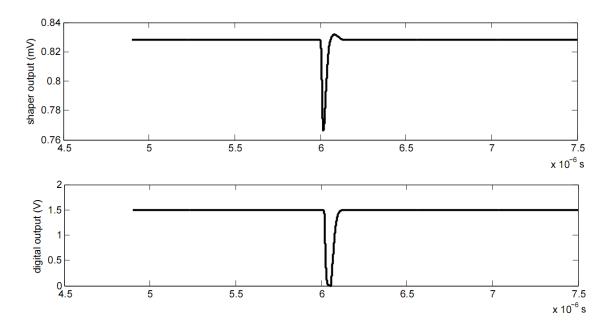

In this 3D-CPS, the pixel of the analog tier consists of a diode, a first amplification stage, a first double sampling circuitry and a discriminator. The discriminator output is vertically connected to the digital pixel for performing zero suppression. As a first step towards verifying the functionalities of the pixels, the in-pixel discriminator and zero-suppressing readout circuit have been realized<sup>3</sup> in a 0.13  $\mu$ m CMOS technology. An alternative approach is also proposed, where a 3-bit pixel-level Analog-to Digital Converter (ADC) is integrated in each pixel for improving the spatial resolution provided by a 20  $\mu$ m pitch pixel initially equipped with a 1-bit discriminator. Power dissipation concern leads to the investigation of a single-slope ADC, those design includes a diode, a comparator and 3-bit memory in each pixel. The pixel-level ADCs operating in the parallel rolling shutter mode could maintain high frame rate and required spatial resolution.

### Thesis layout

This thesis is organized in two parts. The first part, spanning from chapter 1 to 2, is dedicated to the topic of 2D-CPS. Chapter 1 gives a description of the requirements of the innermost layer of an ILC vertex detector, and of different types of CPS. Chapter 2 introduces a light double-sided ladder equipped with 2D-CPS. It is considered as a possible solution to meet the specified requirements. In order to obtain a high signal-

$<sup>^3</sup>$ The pixel pitch is 20  $\mu m$  pitch.

to-noise ratio of the pixel, a novel pixel structure based on multi-stage amplification is presented. We discuss the results of the characterization of an implemented pixel employing this novel offset compensated amplifier.

The second part of this thesis, which consists of chapter 3, 4 and 5, covers the topic of 3D-CPS. A design of 3D-CPS with delayed readout is presented in chapter 3. Chapter 4 introduces novel pixel topologies of 3D-CPS featuring parallel continuous readout. The analysis of the pixel circuits, test results of the proposed pixel-level discriminator and zero-suppressing readout are presented. Chapter 5 describes an alternative pixel architecture (using a 3-bit pixel-level ADC) for a high spatial resolution. The characterization of the pixel-level ADC is also discussed in the same chapter.

The main outcome of the PhD are summarized and discussed at the end of the document, complemented with an outlook providing proposals on the most promising ways to pursue the development of the different approaches addressed in the thesis.

# Chapter 1

# CMOS pixel sensors for the ILC vertex detector

### 1.1 Scientific motivation for the ILC

The Large Hadron Collider (LHC), the world's most powerful particle accelerator, started its physics programme with first collisions at CERN. The LHC is a proton-proton collider and has provided 3.5 TeV per beam up to now, i.e. the collision energy amounts to 7 TeV. By 2014, it will reach 14 TeV. The International Linear Collider (ILC) will collide electrons and positrons at energies of initially 500 GeV, upgradeable to 1 TeV at least. Together with the LHC, it will offer mutually supporting views of the new physics world at the TeV-scale.

The ILC has an ambitious physics program, which will extend and complement that of the LHC. It can provide a wealth of information on Standard Model physics and on yet unresolved questions it triggers [1]. Based on experiments and discoveries over the last decades, physicists believe that the TeV-scale will yield evidence for new forms of matter and possibly even extra dimensions of space. The new matter is expected to rely on a Higgs boson and may, for instance, include an extended family of elementary super particles. These discoveries will continue telling us about the nature of the Universe and how the laws of physics came to be.

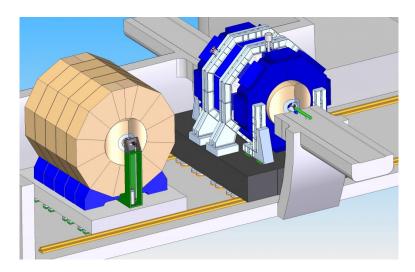

The ILC scheme calls for two detectors, called International Large Detector (ILD) and Silicon Detector (SiD) [2]. The two detector designs for the ILC are now being elaborated by the ILD and SiD groups towards the Detailed Baseline Design Report (DBD), their layouts are shown in Figure 1.1. These two detector concepts take different approaches for the cost-performance optimization.

Figure 1.1: Two detectors in the detector hall. ILD (left) is offline, and SiD (right) is shown in the beamline.

While the SiD apparatus relies on a central tracker composed of silicon strips, the ILD design is based on a Time Projection Chambre (TPC). Material budget considerations impose the SiD main tracker to be composed of 5 layers only, which imposes the vertex detector to provide track seeding. With its gaseous detection medium, the ILD main tracker is much less constrained in terms of material budget and provides more than 200 impacts for fully traversing particles. This improved situation alleviates the requirements on the vertex detector readout time, which is not supposed to play a central role in track seeding. The SiD, on the other hand, is more compact than ILD, a difference which benefits to the overall cost, driven by the dimensions of the calorimetres, as well as to the achievable experimental field (5 T against 3.5 T for ILD).

Two alternative vertex detector (VTX) geometries are being considered within the ILD concept [3]. Both geometries are purely cylindrical. The first geometry (called VTX-DL) features 3 double-sided layers, where each layer is equipped with two,  $\lesssim 2$  mm apart, arrays of sensors. The second geometry (called VTX-SL) features 5 single-sided layers equipped with one layer of sensors only. Both geometries are shown in Figure 1.2. The double-sided layer option allows spatial correlations between hits generated by the same particle in the two sensor layers equipping a ladder. It is expected to provide better rejection of beamstrahlung background (low momentum < 300 MeV/c) [3] and to provide additional pointing accuracy. The VTX-DL presents however a more challenging goal because of the limited experience in double-sided ladders compared to in single-sided ones. Selected main geometrical parameters of the two VTXs are listed in Table 1.1.

Figure 1.2: Vertex detector geometries of the two design options: (left) 5 single-sided layers (VTX-SL), (right) 3 double-sided layers (VTX-DL).

All vertexing system designs under consideration include a pixelated vertex detector, which surrounds as close as possible the Interaction Point (IP) for accurate measurements of charged particle impact parameters. This creates a major technical challenge because of the rapidly increasing beam-related background when approaching the IP. The sensor technology best adapted to the high background environment is not yet defined. It would be difficult for well established technologies to meet simultaneously all requirements, defined by the physics goals (granularity, material budget) and those imposed by the running conditions (readout speed and radiation dose). Several alternative pixel technologies are therefore being considered and developed [4, 5, 6], among which CPS are one of the most promising candidates. This thesis focuses on developing innovative CPS

Table 1.1: Radius and ladder length for each layer of the two vertex detector geometries.

|          | radius[mm] |        | ladder length [mm] |        |

|----------|------------|--------|--------------------|--------|

| geometry | VTX-SL     | VTX-DL | VTX-SL             | VTX-DL |

| layer1   | 15         | 16/18  | 125                | 125    |

| layer2   | 26         | 37/39  | 250                | 250    |

| layer3   | 37         | 58/60  | 250                | 250    |

| layer4   | 48         |        | 250                |        |

| layer5   | 60         |        | 250                |        |

to satisfy the requirements of the innermost layer of an ILC vertex detector, taking the ILD concept as a reference.

### 1.2 Requirements for CMOS pixel sensors

The small pixel pitch desired for a high spatial resolution requires a large number of pixels per surface unit, which translates into a high power consumption and/or a slow readout speed. The granularity and readout speed drive the power dissipation, which also impacts more or less severely the material budget, depending on the type of cooling system required. It is therefore unavoidable that the sensor R&D concentrates on a balance between those conflicting requirements. The latter is summarized in the coming sub-section.

### 1.2.1 Requirements from the physics goals

The ILC vertex detectors will provide the central tool for flavour identification based on the displaced vertex of weakly decaying particles. Beauty- and charm-tagging, or even more sophisticated methods such as separated identification of quark and anti-quark jets will be addressed [3]. One of the key detector parameters is the track impact parameter resolution  $(\sigma_{ip})$ , which can be parametrized for a set of cylindrical detector layers as [3]:

$$\sigma_{ip} = a \oplus b/p \cdot \sin^{3/2}\theta \tag{1.1}$$

Where the constant a reflects the single point resolution and the geometrical stability of the detectors, the parameter b represents the resolution degradation due to multiple scattering, which varies with the incident particle momentum p and the track polar angle  $\theta$  measured with respect to the beam direction. a and b are required to be below 5  $\mu$ m and 10  $\mu$ m· GeV/c, respectively. The innermost layer has a radius of 15/16 mm and intercepts all particles produced with a polar angle such that  $|\cos\theta| \leq 0.97$ . Monte-Carlo studies show that to achieve these specifications:

- The spatial resolution should be  $\lesssim 3 \ \mu \text{m}$ .

- The distance between the first measured point of tracks and the IP should be less than  $\sim 20$  mm.

- The material budget should be limited to only a few per mill of radiation length.

Figure 1.3: The schematic of the bunch timing of the ILC.

• The length of the sensor ladder should typically be about  $\sim 125$  mm.

### 1.2.2 Requirements from the running conditions

### 1.2.2.1 Readout speed

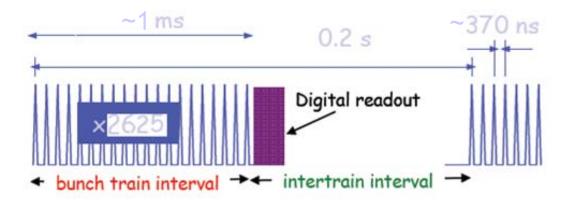

The time structure of the ILC bunch train has been described in the Reference Design Report (RDR) [7]. As shown in Figure 1.3, the beam is divided into bunch trains of  $\sim$  1 ms length, containing 2625 bunches with a period of 200 ms. In order to establish a better and more cost-effective baseline, the 2009 Strawman Basline option (SB2009) [8] was proposed, with some major modifications to the design of the ILC. It benefits from a lower beam-power parameter set, obtained with a twice smaller number of bunches per pulse ( $\sim$  1312), as compared to the nominal RDR parameter set.

The hit rate is highest in the innermost layer and is governed by beam-related background. The latter is essentially due to incoherent  $e^+$   $e^-$  pairs produced through beamstrahlung processes. Their rate was estimated with Monte-Carlo simulations, which predict  $5.3/4.4 \pm 0.5$  hits/ $cm^2$  per bunch crossing at 15/16 mm radius [9]. Extensive background simulations have also been performed with the latest beam geometry. They lead to similar rate values. The latter translate in demanding readout speed requirements in order to keep the occupancy at an affordable level ( $\lesssim$  few %) [9].

The acceptable time resolution indicated in the LoI of the ILD is 25-50  $\mu$ s, for the foreseen running conditions at a collision energy of up to  $\sim 500$  GeV. This time is shorter for the SiD vertex detector, where it is more alike a few  $\mu$ s in order to be able to achieve standalone tracking in the vertex detector. In this thesis, a time resolution well below 10  $\mu$ s is a target value for both ILD and SiD vertex detectors. In the case of ILD, the

Table 1.2: The requirements of the sensors for the innermost layer of the ILD vertex detector. The values address a collision energy  $\lesssim 500$  GeV, except for the time resolution, which is also provided for 1 TeV.

| Radiation tolerance to non-ionizing particles              | $O(10^{11})n_{eq}/cm^2$                                                           |

|------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Radiation tolerance to ionizing particles                  | $\sim 150 \; \mathrm{kRad/per \; year}$                                           |

| Spatial resolution                                         | $2-3 \ \mu \mathrm{m}$                                                            |

| Material budget per ladder                                 | $\begin{bmatrix} 2\text{-}3 \ \mu\text{m} \\ 0.2\text{-}0.3\% \ Xo \end{bmatrix}$ |

| Time resolution (center-of-mass energy of $500~{\rm GeV})$ | $\lesssim 25\text{-}50~\mu\mathrm{s}$                                             |

| Time resolution (center-of-mass energy of 1 TeV)           | $ $ $<$ $10~\mu \mathrm{s}$                                                       |

targeted readout time is intended for the running condition at a collision energy near 1 TeV or above, where the beam related background is expected to be a couple of times higher than at 500 GeV as a consequence of the higher luminosity.

#### 1.2.2.2 Radiation tolerance

From the simulations, the annual ionising dose was calculated to be in the order of 50 kRad per year at 15 mm radius. To account for the limited accuracy of the simulated beamstrahlung rate, it is multiplied by a safety factor of 3 to derive the sensor specification. At least 2 years of operation were assumed before replacing the sensors. Overall, an ionising radiation tolerance of 300 kRad is required for a 2 year life time [10]. The corresponding non-ionising radiation tolerance amounts to  $\lesssim 1 \times 10^{11} \ n_{eq}/cm^2$ . Table 1.2 summarizes the requirements of the sensors equipping the innermost layer of the ILD vertex detector.

### 1.2.3 Power consumption considerations

In order to address the challenging issue of power consumption, two alternative readout strategies are being investigated based on the ILC time structure: continuous readout and delayed readout. In the former readout approach, the sensors are read out continuously and the hits are allocated to the time slot which coincides with the time needed to read all pixels (called frame readout time). The other strategy is the delayed readout, where the hits are stored in the sensors during the whole train duration and read out during the beam-less period separating two consecutive trains.

For the continuous readout approach, power consumption estimates were performed

at IPHC, based on fabricated sensors and accounting for power cycling. It was assumed that the beam time structure can be used to reduce the sensor power consumption during a large fraction of the inter-train time by about two orders of magnitude. It is also estimated that a transient time ( $\lesssim 4$  ms) is needed before and after the train to switch on and off all sensors in a well controlled way. With a rather conservative duty cycle of 2% (while the machine duty cycle is  $\sim 0.5\%$ ), the average power consumption would amount to a few tens of watts only (e.g. about 10 W for CPS) [3]. Such values are compatible with modest cooling by air flow, which does not require introducing additional material in the VTX fiducial volume.

Power consumption may in principle even be more mitigated with the delayed readout approach, because it allows for a very low readout clock frequency. This approach has as an important consequence to avoid the effect of the Lorentz forces on the ladders generated by power cycling in the experimental magnetic filed. If the electronic signal is read out only after the end of the train, immunity against EMI may also be reinforced [3]. In order to compare and evaluate the potential and benefits of those two different readout architectures, they will be both developed in this thesis.

# 1.3 R&D on CMOS pixel sensors adapted to the ILC vertex detector

### 1.3.1 Principle of standard CMOS pixel sensors

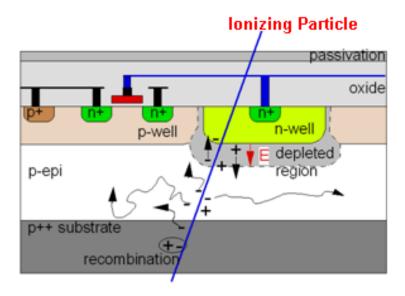

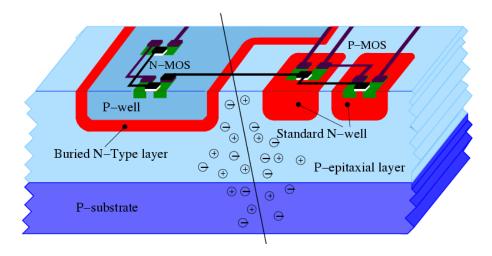

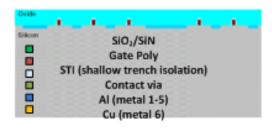

The cross-section of a typical CPS device is illustrated in Figure 1.4. The active volume of the sensor is a lightly doped and undepleted epitaxial (EPI) layer. This layer is common in many modern CMOS processes featuring twin wells, where it is grown on a highly doped substrate. The doping level of the p-well is typically three orders of magnitude higher than the EPI layer, translating into potential barriers at the region boundaries. The substrate is also made of highly doped, crystalline silicon with a typical thickness of several hundreds of microns. Minimum ionizing particles (MIP) produce excess carriers in the EPI layer at a rate of  $\sim 80$  electron-hole pairs per micron. The thickness of the detecting volume is limited to  $\sim 10\text{--}20~\mu\text{m}$ . Most of the signal charge electrons are reflected back to the EPI layer by the p-EPI/p++substrate and the p-well/p-EPI interface, while the electrons created in the substrate are quickly recombined.

The total signal charge of CPS amounts therefore to several hundred electron-hole

Figure 1.4: Schematic cross-section of a typical CMOS sensor.

pairs. Since the charge is shared between several neighboring pixels, the number of charge carriers collected in the seed pixel<sup>1</sup> is typically 20-50% of the total deposited charge, depending on the EPI layer resistivity, on its thickness and on the pixel pitch and sensing node dimensions.

CPS are a fully monolithic device, where the readout electronics is fully integrated with the sensors on a single chip. Each pixel in such a sensor contains a sensing diode accompanied by electronics needed for reading out the signal. This feature allows for a high chip integration, which alleviates the overall detector cost and allows for very compact systems.

### 1.3.2 Why considering CMOS pixel sensors for the ILC?

In the last years, several new sensors have been developed for the ILC, CPS for particle detectors being one of them. This technology has many advantages and potential for an application at the ILC as compared to Hybrid Pixel Sensors (HPS), today's most advanced technology [11]. The HPS are mainly built from two different chips: a sensor chip and a readout electronics chip bonded by a bulky metal bump [12], as shown in Figure 1.5. This metal bump is a source of complication, of multiple scattering and of granularity limitations.

<sup>&</sup>lt;sup>1</sup>The seed pixel of a signal cluster is defined as the one collecting the largest fraction of the total cluster charge.

Figure 1.5: Sketch of the composition of a complete ATLAS module, including sensor and FE-chip connected by bump bonds, a hybrid kapton foil and the module control chip.

The ATLAS² pixel detector made of HPS is the innermost tracking system of the ATLAS experiment at the LHC. The spatial resolution measured with ATLAS modules (a pixel dimension of 50  $\mu$ m × 400  $\mu$ m ) before irradiation is  $\lesssim$  10  $\mu$ m along the 50  $\mu$ m pixel pitch. The charge sharing is less effective in the orthogonal z-coordinate (400  $\mu$ m pitch), where the spatial resolution is about 115  $\mu$ m [13]. A full ATLAS module featuring a relatively large thickness consists of two bump-bonded slices of silicon and a module controller chip on the top. It translates into a material budget of about 1.5%  $Xo^3$  [13]. As a consequence, HPS have been limited so far by the achievable material budget and poor granularity for the ILC vertex detector. On the other hand, CPS show a significant advantage over these two parameters, at the expense however of the readout speed and radiation tolerance, which are much less demanding at the ILC than at the LHC.

$<sup>^2</sup>$ The ATLAS acronym stands for A Toroidal Lhc ApparatuS, but it is also a reminder of the unprecedented size of this detector.

$<sup>^{3}</sup>Xo$  stands for the radiation length.

Figure 1.6: CPS based on a high resistivity EPI layer: potential [V] calculated using the ISE-TCAD package [14]. Reverse biasing of n-well/p-EPI junction at 5.5 V results in a depleted zone extending over several  $\mu m$  inside the sensitive volume.

### 1.3.3 Potential of CMOS pixel sensors

CMOS sensor technology has long been desired in many fields and being became mature. Their industrial manufacturing relies on procedures optimized for commercial items, which may be far from those needed for charged particle detection. With the rapid development of commercial processes, some remarkable progresses have been made in the right direction and the real potential of CPS has being approached.

### 1.3.3.1 Full charge collection by drift in a depleted EPI layer

Modern CMOS technologies are often built over very thin EPI layers (a few microns) to minimize noise coupling or crosstalk. The number of excess carriers produced by a MIP is proportional to the thickness of the EPI layer, and thus this thin EPI layer results in a very limited signal. This point is one of serious concern in traditional CPS.

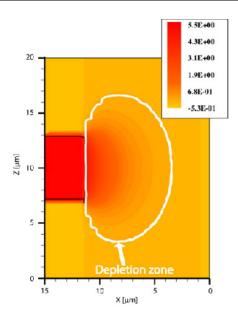

The charge collection mechanism in the EPI layer can be another limiting aspect of the standard CMOS technologies, because the latter suffer from small and incomplete signal charge collected by thermal diffusion rather than by a drift. A promising way of improving this mechanism is to manufacture CPS with a high resistivity EPI layer, featuring an EPI layer which is at least partially depleted.

Due to the electric field existing in the depleted region, the charge collection is

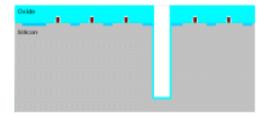

Figure 1.7: Schematic cross-section of a typical CMOS wafer with the deep n-well.

expected to be faster. The features of this kind of technology have been simulated by using ISE-TCAD [14]. The simulation results showed that the depleted zone inside an EPI layer had a significant extension, as shown in Figure 1.6. It therefore enhances the pixel SNR value and the sensor radiation tolerance with respect to the performance achieved with a low resistivity EPI layer.

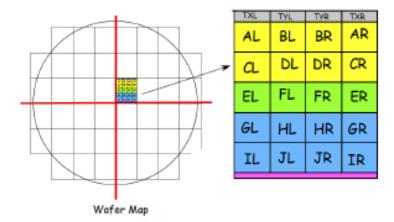

In order to explore this kind of CMOS process, one of the prototype chips (called MIMOSA-25)<sup>4</sup> was fabricated in a commercially available XFAB-0.6 CMOS process, featuring a high resistivity EPI layer of  $\sim 1 \text{k} \ \Omega \cdot \text{cm}$  [15]. The test results of MIMOSA-25 showed that the charge collected in seed pixels is at least twice larger than that of the sensors with a low resistivity EPI layer, resulting into a high SNR of up to  $\sim 50$ . A SNR of  $\sim 35$  has been achieved with chips exposed to a fluence of  $\sim 3 \times 10^{13} \ n_{eq}/cm^2$ . This is to be compared with the measurements performed with the MIMOSA-15 prototype, fabricated with a low resistivity EPI layer, which exhibited a SNR value as low as  $\sim 15$  after an exposure to a substantially smaller fluence of  $\sim 0.2 \times 10^{13} \ n_{eq}/cm^2$  [15].

#### 1.3.3.2 Full CMOS electronics in the active area

**Deep n-well CMOS pixel sensors** The implementation of CMOS circuitry in the active area is impractical for traditional CPS. In order to overcome this limitation, a deep n-well of a triple-well commercial CMOS process may be used as charge collecting

<sup>&</sup>lt;sup>4</sup>MIMOSA stands for Minimum Ionizing particle MOS Active pixel sensors. More than a decade has past since MIMOSA-1 was designed as the first CMOS pixel sensor dedicated to charged particle tracking. Thirty-two different MIMOSA prototype chips have been designed and fabricated at IPHC since 1999.

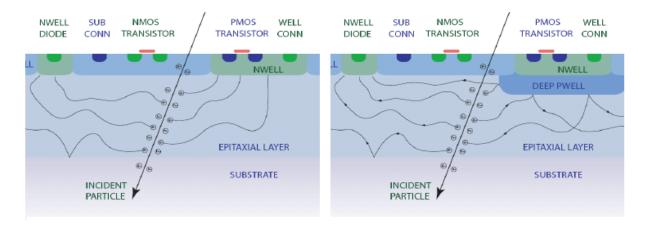

Figure 1.8: A CPS without a deep p-well implant (left) and with a deep p-well implant (right).

electrode, while the PMOS transistors are implemented in an n-well which is geometrically smaller and less deep than the charge collecting deep n-well. Figure 1.7 shows a concept of using a buried n-type layer as the charge collection diode. This approach may take full advantage of the properties of a CMOS technology, taking into account the limited area of PMOS transistors.

This approach was followed in [16]. Several prototype chips (called the APSEL series) have been designed and fabricated in the STMicroelectronics 130 nm CMOS technology. For the first "ILC-class" prototype (named SDR0 chip), a design of CMOS deep n-well sensors with a 25  $\mu$ m pixel pitch provides a 5-bit time stamping<sup>5</sup>, corresponding to a time resolution of  $\sim 30~\mu$ s. Each pixel dissipates  $\sim 5~\mu$ W static power. The limited charge collection efficiency is a main drawback of this deep n-well device, due to parasitic charge collection in the additional n-wells containing PMOS transistors. One of the prototype chips called APSEL4D has been characterized as an example. Beam test results of APSEL4D show that the hit detection efficiency could not be sufficient (up to 92% taking into account a reasonable  $\sim 450~e^-$  threshold settings [16]). Therefore, this kind of the sensor still needs to demonstrate its ability to build a working detector, in particular when considering the performance of charge collection efficiency [17].

Deep p-well CMOS pixel sensors A new Jazz-Tower 0.18  $\mu$ m CMOS technology with a quadruple-well (deep p-well) offers another opportunity of using PMOS transistors in the active area [18]. A deep p-well is introduced underneath the n-wells containing

<sup>&</sup>lt;sup>5</sup>A time stamping is a sequence of characters, denoting the time at which a certain hit occurred. This data is usually presented in a consistent format, allowing for easy comparison of two different records and tracking progress over time.

the PMOS transistors, which isolates the n-wells from the EPI layer and prevents them from acting as the sensing diodes. This then ensures that all charge is being collected by the sensing diode and maximizes charge collection efficiency (nearly 100%) [19]. This is illustrated in Figure 1.8.

A prototyping sensor (called TPAC1.0 chip) designed by the CMOS sensor design group in Rutherford Appleton Laboratory has demonstrated its feasibility for nearly 100% collection efficiency [20]. The pixel of TPAC1.0 sensors has a pitch of 50  $\mu$ m, it comprises a preamplifier, a shaper and a comparator. The static power consumption for each pixel is  $\sim 12~\mu W$ .

Another design called "Chronopixel" is also expected to implement a deep p-well over most of the pixel area in the near future. An important feature of this design is the possibility of putting a time stamping on each hit (up to two hits) with sufficient precision (i.e. a 14-bit time stamping) in a relatively small pixel. The second prototype will be designed for a 25  $\mu$ m pixel with binary readout in TSMC 90 nm technology. This small pixel with 14-bit time stamping capability will be developed as a good candidate of the ILC vertex detectors, but this has to be demonstrated [21].

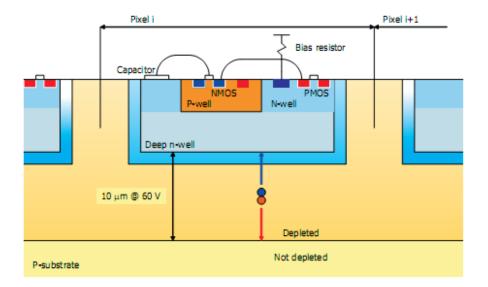

High voltage CMOS pixel sensors Still another approach was followed, using as a high voltage triple-well CMOS technology. The main motivation of this approach is to avoid relying on the limited number of CMOS processes featuring an adequate (thick, resistive) EPI layer. As a consequence, very deep sub-micron processes ( $<0.18~\mu m$ ) can be used, which do almost never provide an EPI layer. This opens up the possibility of integrating a substantial amount of transistors in small pixels. A drawback is however that one needs using a high voltage option of the process used, and more power may be consumed. The novel sensor is based on two main ideas: the first idea is to use the deep n-well as the signal collection electrode. The second idea is to implement both types of transistors inside the deep n-well, which is also the substrate of PMOS transistors [22], as shown in Figure 1.9.

In order to verify the performance of high voltage CPS, one of the pixel sensors with a 21  $\mu$ m pixel pitch was designed in a 0.35  $\mu$ m high voltage CMOS technology. Test beam measurements have been performed. The measured MIP cluster signals are  $\sim$  2200  $e^-$ , spatial resolution  $\sim 7\mu$ m, SNR of 12.3 and detection efficiency more than 85% [23]. To test the radiation tolerance, several chips have been irradiated with neutrons up to  $\sim 10^{14}$

<sup>&</sup>lt;sup>6</sup>The design was developed by Sarnoff company, the detailed pixel circuits are not open to the public.

Figure 1.9: Schematic cross-section of a typical CMOS wafer in the high voltage technology.

$n_{eq}/cm^2$ . Before irradiation the equivalent noise charge (ENC) was 70  $e^-$ , immediately after irradiation 300  $e^-$  and after three days of annealing at room temperature it went to 130  $e^-$ . More R&D is still required to validate this technological approach, aiming in particular at better SNR and spatial resolution performance.

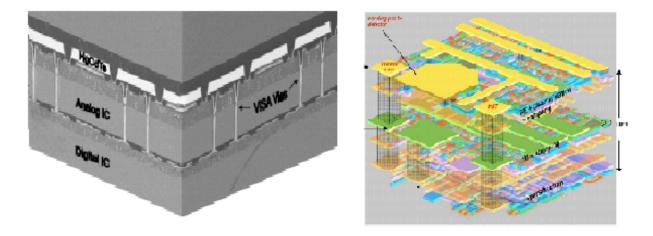

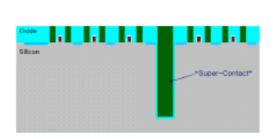

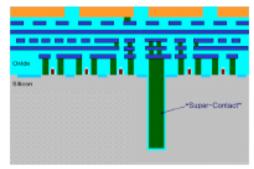

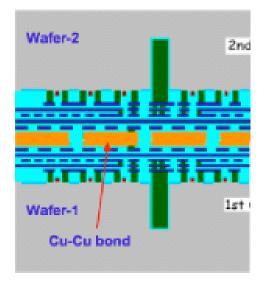

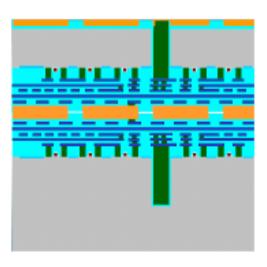

### 1.3.3.3 3D Integrated CMOS pixel sensors

3D integration is defined as the integration of thinned and bonded silicon integrated micro-circuits with vertical interconnects between the different layers. It is particularly suited to CPS, for it could integrate different CMOS manufacturing processes, each optimized for a given sequence of the charge generation and signal processing chain. In this case, vertical integration of two (or more) CMOS layers makes it possible to separate the analog front-end section from the digital readout section, with the widest advantages. The designs in this thesis therefore focus on the development of 3D integrated CPS. Their advantages will be discussed in more detail in chapter 3.

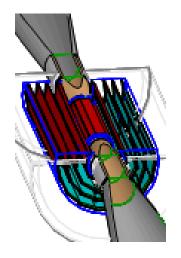

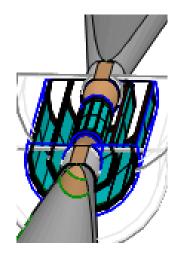

In order to demonstrate the feasibility of 3D-CPS for the ILC vertex detector, a 3D-chip named VIP1 has been designed by the Fermi Laboratory using the MIT Lincoln Laboratory 0.18  $\mu$ m process [24]. The analog pixel including an analog front-end and the digital pixel including a 5-bit time stamping latch are vertically integrated within a 20  $\mu$ m pitch. The test results showed that the VIP1 chip works with full functionality. However, the fabrication yield was very poor and it was concluded that such a 3D process is not optimal for mixed-mode signal circuitry that includes high precision and low noise

Conclusion 15

Figure 1.10: Sketch of the 3D-integration technique, integrating several electronic layers (left) and Fermi-Lab 3D design with 3 tiers for different electronic tasks (right).

parts [25].

After VIP1, the focus at Fermi Lab shifted to a commercial CMOS process (i.e. Chartered-3D Tezzaron technology, to be introduced in chapter 3) for possible higher yield. A 24  $\mu$ m pitch 3D-CPS (called VIP2) has been developed with a 8-bit time stamping, corresponding to a time resolution of  $\sim 4~\mu s$ . Each pixel dissipates  $\sim 10~\mu W$  static operation power [26].

### 1.4 Conclusion

In order to fully exploit the advantageous running conditions of the ILC and achieve the high precision physics program it allows for, a vertex detector of unprecedented performance is mandatory.

Its specifications are governed by the spatial resolution (i.e.  $< 3 \mu m$ ) and the material budget (50  $\mu m$  thin sensors, low power consumption), and compromise the readout speed and the radiation tolerance to a certain extent. Hybrid Pixel Sensors, which are well established and widely used at the LHC, are thus not suited to this application. CPS are intrinsically significantly better adapted to it.

Several variants of CPS using 2D technologies have been developed so far for charged particle tracking. Despite the appealing results obtained, it is clear that their ultimate performance do not allow exploiting fully the real potential of the technology, mainly because the fabrication parameters are dictated by industrial interests featuring modest overlap with those of subatomic physics experiments. This reality hampers the possibility

of using 2D-CPS for the most demanding running conditions at the ILC such as those foreseen at its highest collision energy.

3D integration technologies seem to be the most promising way to turn around the limitations of 2D-CPS, since they allow combining different CMOS technologies in a single, stapled, multi-tier chip. Each tier can then be optimized for its dedicated functionalities. It is the main purpose of this thesis to explore this possibility using two different readout approaches.

Before exposing the work performed for this purpose, the thesis addresses the question of improving the 2D approach, which exploits the concept of double-sided ladder. The next chapter summarizes design developments realized to improve the signal-to-noise ratio of 2D-CPS.

## Chapter 2

# Offset compensated in-pixel amplifiers for CMOS pixel sensors

In the previous chapter, different types of CPS were presented, their essential advantages have been explained. The state of the art technology is an optimized 2D-CPS, based on a continuous readout (or called rolling shutter readout) [27]. It makes use of rolling shutter operation, in-pixel amplification, correlated double sampling (CDS) and column-level discrimination. MIMOSA-26 is the first full scale sensor based on this architecture. It was designed and fabricated in 2008. Based on its first performance assessment, a pixelated double-sided ladder equipped with MIMOSA-26 sensors has next been proposed to study the system integration aspects relevant for the ILD vertex detector (see section 2.1).

MIMOSA-26 was manufactured in a 0.35  $\mu$ m technology, which was not supposed to be used for final sensors. This technology limits CPS to read out in a short integration time of  $\sim$  a few  $\mu$ s. However, it is particularly needed to cope with the beam related a high beamstrahlung background, when the ILC will be running around 1 TeV collision energy. In order to realize this goal, many R & D on CPS are being exploited. Many advanced CMOS technologies with smaller feature sizes (e.g. 0.18  $\mu$ m Jazz-Tower CMOS process) are expected to provide several improvements with respect to the aforementioned 0.35  $\mu$ m CMOS technology, e.g.:

- Due to smaller parasitic capacitors of metal lines, the readout speed can be increased

- An enlarged number of metal layers is provided (e.g. 6-7 metal layers are available in a 0.18  $\mu$ m Jazz-Tower CMOS technology)

- The total power consumption usually decreases with lower power supply voltage used in these processes

- Because of the thinner gate oxide, transistors will be less perturated by intense ionising radiation

- The higher degree of integration allows for increased in-pixel functionality implementation

In addition, the shrinking of the feature size of CMOS transistors is an obvious outcome of the evolution of microelectronics. This is exploited in the design of new pixel systems, where advanced functionalities can be implemented in each pixel to provide a higher SNR and to handle a higher hit rate. Therefore, this chapter is motivated by investigating a novel pixel structure, which was designed as a promising solution to the integration of high density circuitry in a small pixel. The proposed CPS were designed and fabricated in a 0.13  $\mu$ m CMOS process. As compared to MIMOSA-26 pixel structure, a two-stage amplifier instead of a single-stage amplifier was designed for achieving a higher SNR. Even so, a 12  $\mu$ m pixel pitch is  $\sim$  1.5 times smaller than that of MIMOSA-26 sensors, the proposed CPS may be considered for very small pixel pitch in the inner layers of future vertex detectors.

This chapter is organized as follows: section 2.1 provides an introduction to a pixelated double-sided ladder based on MIMOSA-26 sensors. Section 2.2 introduces the pixel design of MIMOSA-26. In section 2.3, we discuss the main noise sources in CPS. In order to improve the SNR, we proposed a new pixel structure with noise reduction and multi-stage amplification techniques. Section 2.5 covers the aspects of designing and characterizing such a novel CPS.

# 2.1 Ultra-light pixelated ladders for an ILC vertex detector

The large energy of beam bunches causes a large background of e+ e- pairs produced by beamstrahlung radiation. It forces to build a light weight, high precision inner detector system in order to accurately measure prosperities. A reduction of the detector thickness is highly desirable because it minimizes the amount of multiple scattering experienced by traversing particles. A mechanical support structure of the sensor and electrical cables will add extra material, the system integration is therefore a crucial issue. Although MIMOSA-26 has already shown very promising performance as a single sensor, the con-

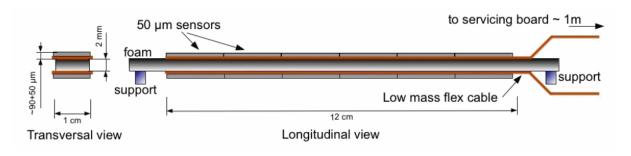

Figure 2.1: Design of the exploratory ladder of the PLUME project.

struction of a functional full vertex detector equipped with a large number of sensors is another challenge.

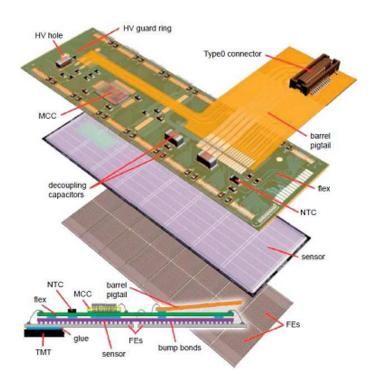

The PLUME <sup>1</sup> collaboration aims to prototype an ultra-light detector for matching the geometry required by the inner layer of the ILD vertex detector, as described in chapter 1. This collaboration gathers four laboratories <sup>2</sup> to design, fabricate and evaluate the prototypes of the double-sided pixellated ladder. It features a sensitive length of 12.5 cm, a thickness of 2 mm and a material budget around 0.3% of  $X_o$ , as a proof of principle for the ILC Detector Baseline Document [28]. The ladder design follows an approach: two flex cables are glued on each side of a support, made of low density silicon carbide foam, as shown in Figure 2.1.

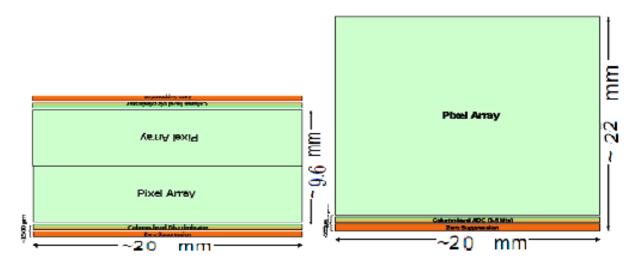

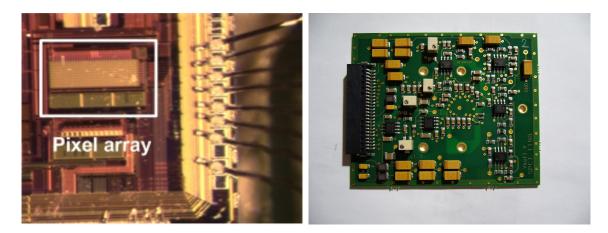

According to the initial assumption of the ladder architecture, the requirements of the ILD vertex detector should be reached. As a first step, the goal of the PLUME project is to construct the double-sided ladder equipped with 6 MIMOSA-26 sensors on each side and to assess their performance. Six MIMOSA-26 sensors with total area of  $\sim 12 \times 1$   $cm^2$  are butted together and glued on the kapton-metal flex cable, on which they are wire bonded. The latter is connected to a servicing board located  $\sim 1$  m away. Before describing the double-sided pixelated ladder, the overall performance of MIMOSA-26 is presented in the following subsection.

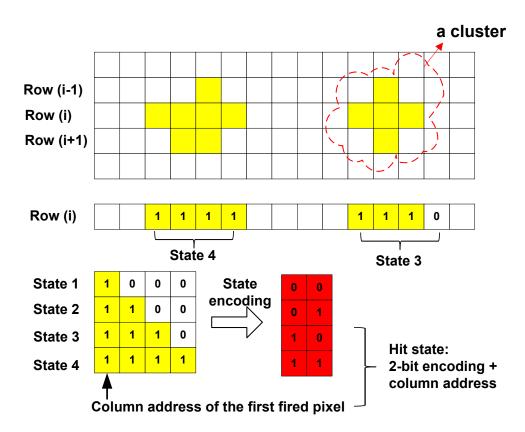

## 2.1.1 Full-scale sensor with binary readout architecture

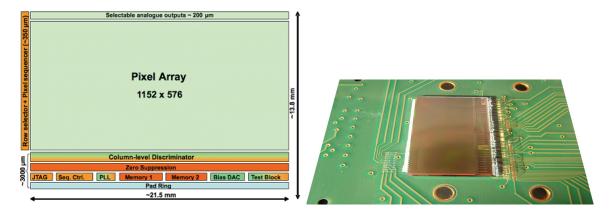

MIMOSA-26 (see Figure 2.2) is the first full-scale sensor with binary output architecture realized for charged particle tracking. The pixel matrix consists of 1152 columns and 576 rows. Each pixel, featuring a pitch of 18.4  $\mu$ m, incorporates a diode, an amplifier with CDS and a source follower (SF). The rolling shutter mode, used to read it out, is

<sup>&</sup>lt;sup>1</sup>Standing for Pixelated Ladder with Ultra-Low Material Embedding

<sup>&</sup>lt;sup>2</sup>DESY-Hamburg, IPHC-Strasbourg, Universities of Bristol and Oxford

Figure 2.2: Schematic view of MIMOSA-26 displaying the different functional blocks (left) and photograph of the MIMOSA-26 sensor mounted on its interface board (right).

steered through a row selector located on the left side of the pixel matrix. All 576 rows in a column are multiplexed onto a discriminator at end of the column, all 1152 discriminators are read out in parallel. The total active area of the chip is  $\sim 224 \ mm^2$ , the whole pixel matrix is read out in  $\sim 100 \ \mu s$ , and the average power dissipation is  $\sim 280 \ mW/cm^2$  [27].

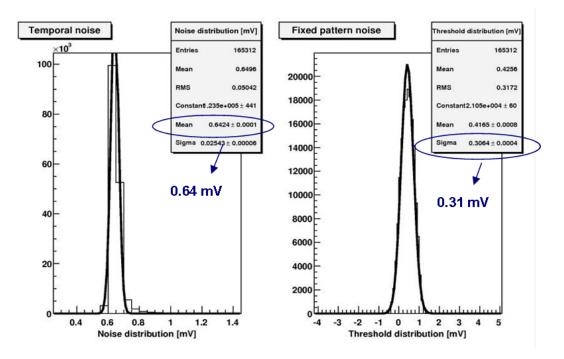

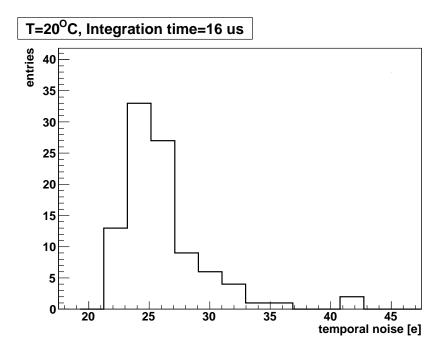

The discriminated signals are processed by a zero-suppressing<sup>3</sup> readout circuit at the periphery of the matrix. In order to reduce the discriminator offset dispersion, the sensor was subdivided into 4 groups of 288 columns. The distribution of noise over a quarter of the pixel array (288 columns) with its associated discriminators is shown in Figure 2.3.

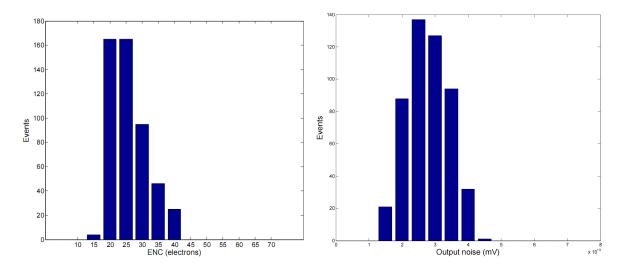

The total temporal noise<sup>4</sup> of the pixel array associated with discriminators is in the range 0.6-0.7 mV, corresponding to about the equivalent noise charge (ENC)<sup>5</sup> of 12  $e^-$ . The total fixed pattern noise (FPN), caused mainly by the dispersion of discriminator thresholds, is about 0.3-0.4 mV, corresponding to about the ENC of 6  $e^-$ .

Six MIMOSA-26 sensors have been assembled as a beam telescope and characterized with 120 GeV/c pion beams at the CERN-SPS. The detection efficiency in case of a low resistivity EPI layer is  $\sim 99.5\pm0.1\%$  up to a threshold value of discriminators  $\sim 4$  mV,

<sup>&</sup>lt;sup>3</sup>Zero suppression is the removal of zeros from all outputs of discriminators. This can be done for data compression.

<sup>&</sup>lt;sup>4</sup>The predominant components of electronic noise are divided into two categories: temporal noise and FPN. The latter, also called non-uniformity noise, is due to the spatial variation of output values consecutive to the mismatches of devices. The temporal noise refers to the time-dependent fluctuations; it is primarily due to the diode shot noise, and to the amplifier thermal and flicker noise. The specific impact of these noise sources of pixels will be analyzed in subsection 2.3.

$<sup>^5</sup>$ The total temporal noise is usually equivalent to noise charge of pixels; the ENC of 12  $e^-$  includes the pixel temporal noise and that of column-level discriminators.

Figure 2.3: MIMOSA-26 noise distributions over a quarter of the sensitive surface (group of 288 columns) as measured at a 80 MHz clock frequency: temporal noise (left) and FPN (right).

corresponding to  $\sim 6$  times the noise standard deviation, with a fake rate<sup>6</sup> below  $10^{-4}$ . A spatial resolution close to 3.5  $\mu$ m was observed with a low resistivity EPI layer [29].

The MIMOSA-26 sensor is a starting point for the development of future micro-vertex detectors. It has reached the necessary prototyping maturity for real scale applications, including the innermost layer of the ILD vertex detector.

# 2.1.2 PLUME ladder concept

As mentioned above, the main feature of the PLUME ladder concept is a double-sided layout, which consists of two sensor layers separated by a support structure [30]. In this double-sided ladder, the same traversing particle generates a hit information on both sides of the ladder. As illustrated on Figure 2.4, the concept may be used to equip the ladder with different sensors on each side, one providing a high spatial resolution and one optimized for a high readout speed:

• One side can be equipped with squared pixels of 16-17  $\mu$ m pitch providing a high spatial resolution of  $< 3 \mu$ m. The minimum integration time of MIMOSA-26 sensors

<sup>&</sup>lt;sup>6</sup>The fake hit rate is defined as the probability for one pixel in one event to deliver a noise fluctuation above the discriminator threshold.

Figure 2.4: The placement of squared and elongated pixels equipped on a double-sided layer (left), and the pitches required for both squared and elongated pixels (right).

Figure 2.5: The double-sided readout architecture derived from MIMOSA-26 is to equip in the innermost layer (left), and the extension of MIMOSA-26 prepared for the outer layer (right).

is  $\sim 100~\mu s$ . Based on the double-sided readout (i.e. the columns of MIMOSA-26 are split in halves and are read out in parallel on each side, as shown in Figure 2.5), the frame readout time would be reduced by a factor of  $\sim 2$ . Further improvements down to  $\lesssim 40~\mu s$  are expected by moving to a new CMOS technology with smaller feature size 0.18  $\mu m$ .

• On the other side, the pixels will be elongated in the column direction. The pitch will be increased by a factor of 4-5 with respect to the square pixel<sup>7</sup>. With the same sensitive area as the former side, the integration time can be improved to  $\lesssim$

<sup>&</sup>lt;sup>7</sup>The elongated pixel pitch is 16  $\mu$ m  $\times$  64  $\mu$ m or 16  $\mu$ m  $\times$  80  $\mu$ m.

10  $\mu$ s due to the reduction of the number of rows in the readout direction. As a consequence of the increased sensing diode spacing, the spatial resolution will be 6-7  $\mu$ m in both directions with staggered diodes.

# 2.2 Topology and analysis of MIMOSA-26 pixels

#### 2.2.1 MIMOSA-26 pixel architecture

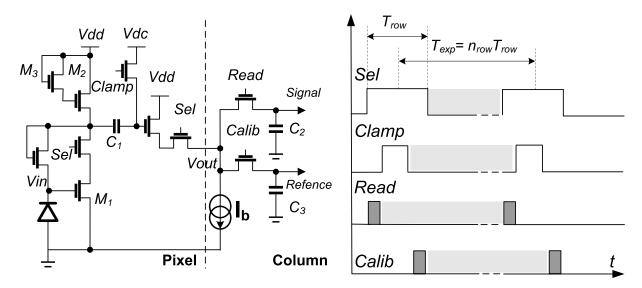

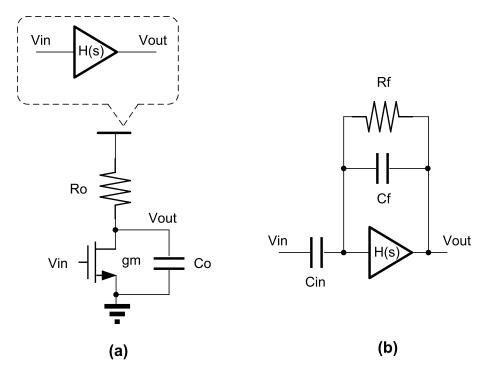

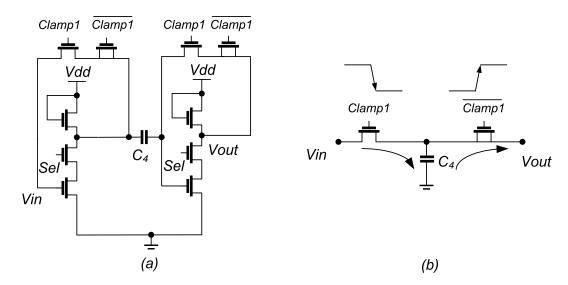

#### 2.2.1.1 In-pixel amplifier used in MIMOSA-26

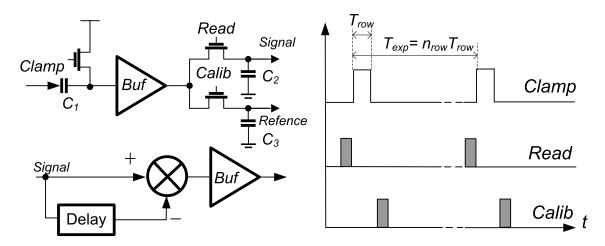

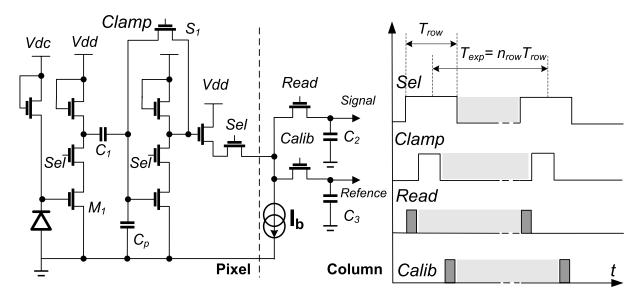

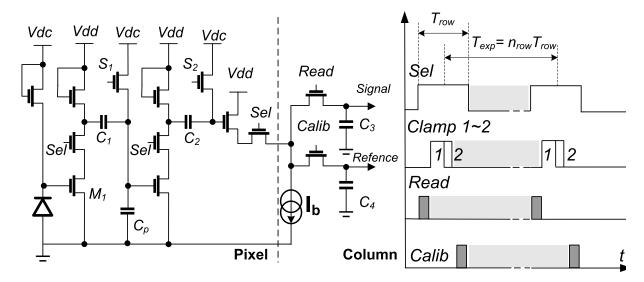

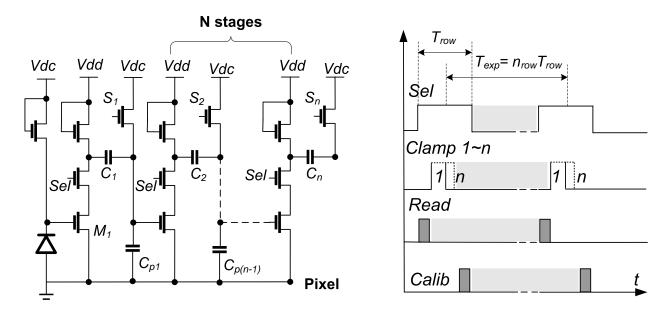

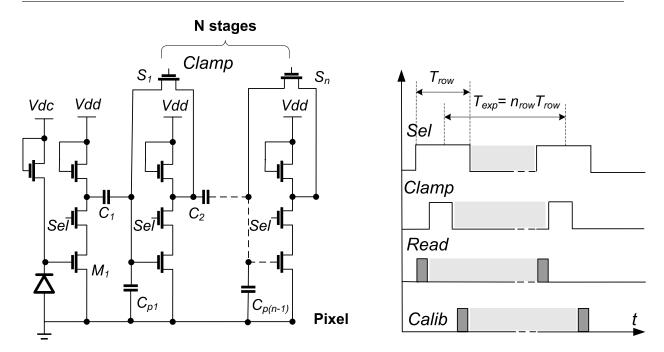

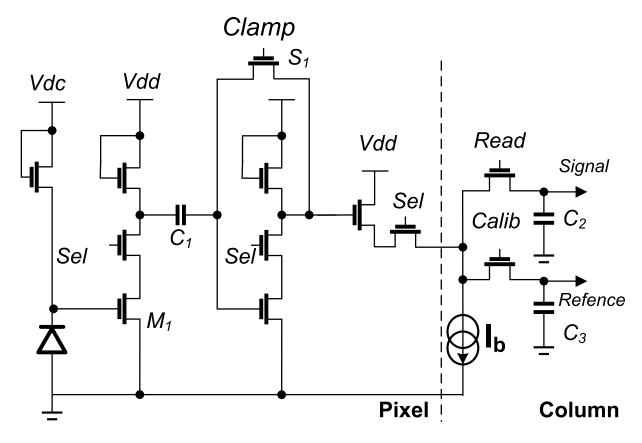

An all-NMOS in-pixel amplifier was implemented in MIMOSA-26. Its schematic and the operation timing waveform are shown in Figure 2.6. Each pixel contains a diode, an in-pixel amplifier with CDS and a source follower (SF) with a select switch Sel. The SF transistor in conjunction with the column bias current source acts as a buffer, which reproduces the sense node voltage on the column line. This SF buffer is only active, when the Sel signal is the logical one. The signal from two successive frames is extracted by the clamping technique. A second double sampling is implemented to remove the pixel-to-pixel offsets in each discriminator stage [31]. Operation of this double sampling is controlled by clock phases Read and Calib, which memorize the pixel output signal and the reference level, respectively.

All pixels of a row receive the common signals Sel and Clamp, which are generated by the row decoder. Since the column-level buffer and discriminator are shared among all pixels of a column, the pixels of only one row can be active at a time. A solution respecting this criterion is the rolling shutter timing scheme, in which the control signals are row-wise staggered. The described row operation sequence is repeated row by row,

Table 2.1: The explanation of main control signals for the MIMOSA-26 pixel.

| Sel         | pixel power control signal                                       |

|-------------|------------------------------------------------------------------|

| Clamp       | clamping control signal                                          |

| $I_b$       | biasing current for driving a parasitic capacitor at each column |

| Read, Calib | control signals for storing the pixel outputs                    |

| Vdc         | analog biasing voltage                                           |

| Vdd         | analog power supply voltage                                      |

Figure 2.6: Schematic of the pixel amplifier in MIMOSA-26, followed by the parasitic capacitors at the end of each column (left) and the timing diagram of the rolling shutter operation (right). The main control signals are listed in Table 2.1.

the integration time  $(T_{row})$  is the time of selecting sequentially the whole pixel array from top to bottom.

The performance of in-pixel amplifiers plus column-level discriminators was first validated in a prototype, called MIMOSA-22. A special biasing with a transistor  $M_3$  for the load transistor  $M_2$  has been introduced to increase the gain of this amplifier. The AC gain of improved amplifier is increased by about a factor of 2, and the DC operation points and its gain are almost not changed. Negative feedback makes the circuits more resistant to CMOS process variation, it can also be used to stabilize the operation point of the amplifier [32].

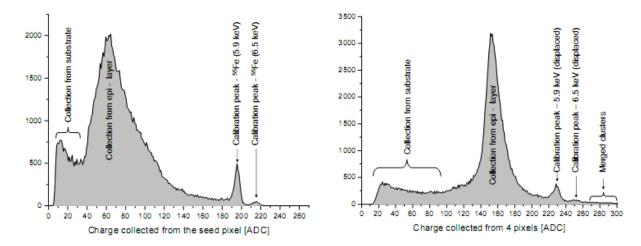

#### 2.2.1.2 Calibration procedure

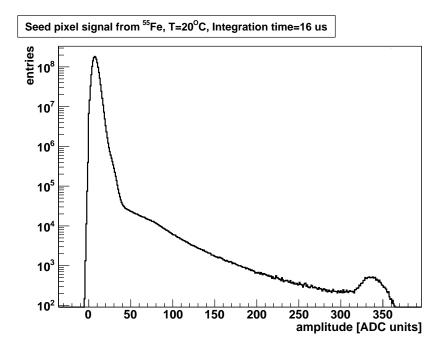

In order to study the electronics properties of CPS, e.g. charge-to-voltage conversion factor (CVF), charge collection efficiency (CCE) and noise performance, a calibration procedure needs to be done by using a X-Ray  $Fe^{55}$  source. This source delivers photons with two emission energies:  $K_{\alpha}=5.9$  keV (24.4 % emission probability) and  $K_{\beta}=6.5$  keV (2.8 % emission probability). The calibration procedure is accomplished by comparing the ADC units translated into the associated electrons. An example of such a distribution of signals from single pixels is shown in Figure 2.7. Three peaks are visible in the typical  $Fe^{55}$  spectrum.

The first peak at low values is usually interpreted as a result of the hits outside the

Figure 2.7: Response to a  $Fe^{55}$  5.9-keV X-ray source, the peaks correspond to photons interacting in the thin depleted region under n-well (left) and the corresponding spectrum for signals summed in a  $2\times2$  cluster (right).

EPI layer. This interpretation is probably incomplete, as the hits in the EPI layer close to a sensing diode also contribute to its low high energy part. The second peak is called "charge collection peak", which corresponds to the charge collected from hits occurring inside the EPI layer but outside of depleted zone of the sensing diode, due to a thermal diffusion. The distribution exhibits a small peak, the charge liberated in silicon by a 5.9 keV photon, which amounts to  $\sim 1640~e^-$  (an electron-hole pair needs a deposited energy of  $\sim 3.6$  eV). This peak is called "calibration peak", it corresponds to a hit into the depleted zone of the sensing diode. A measurement with a high statistics shows a smaller second peak at a signal level above the calibration peak. This peak corresponds to the interaction of photons of the less intensive 6.5 keV  $K_{\beta}$  radiation. These calibration peaks are usually used as an absolute reference for estimation of CVF and ENC, they can be given by:

$$CVF = \frac{U_{calib} \cdot G}{1640e^{-}} \tag{2.1}$$

$$ENC = \frac{U_{noise} \cdot 1640e^{-}}{U_{calib}} \tag{2.2}$$

where  $U_{calib}$  and  $U_{noise}$  represent the position of the calibration peak and noise peak in ADC units, respectively. G represents the conversion gain<sup>8</sup>.

<sup>&</sup>lt;sup>8</sup>The output signals are usually given in ADC counts of a 12-bit ADC mounted on the test board, where analog output signals of pixels can be translated into 12 digital outputs.

| EPI layer                         | EPI thickness       | seed | $2\times2$ | 3×3 |

|-----------------------------------|---------------------|------|------------|-----|

| standard( $10\Omega.cm$ )         | $14 \mu \mathrm{m}$ | 21%  | 54%        | 71% |

|                                   | $10 \mu \mathrm{m}$ | 36%  | 85%        | 95% |

| high resistivity $(400\Omega.cm)$ | $15 \mu \mathrm{m}$ | 31%  | 78%        | 91% |

|                                   |                     |      |            |     |

|                                   | $20 \mu \mathrm{m}$ | 22%  | 57%        | 76% |

Table 2.2: Charge collection efficiency for the seed pixel, and for 2x2 and 3x3 pixel clusters using a  $Fe^{55}$  source (analog output at the clock frequency of 20 MHz).

The CCE is defined as the ratio of the total charge collection peak to the calibration peak.

$$CCE = \frac{U_{charge}}{U_{calib}} \tag{2.3}$$

where  $U_{charge}$  represents the position of the charge collection peak in ADC units.

#### 2.2.1.3 Characterization of MIMOSA-26 sensors

In the laboratory, the measured ENC of MIMOSA-26 sensors with a low resistivity EPI layer is 12-13  $e^-$  and the CVF is  $\sim 74~\mu\text{V}/e^-$  at a clock frequency of 80 MHz (the integration time of the sensor is  $\sim 115~\mu\text{s}$ ) and at an operation temperature of about 20 °C. The charge collection efficiency was also measured. It reached a value of  $\sim 21\%$  for the seed pixel and of  $\sim 71\%$  for a small matrix of 3×3 pixels [32].

In order to study the performance of MIMOSA-26 sensors with a high resistivity EPI layer, MIMOSA-26 sensors have been refabricated in 0.35  $\mu$ m technology with a high resistivity ( $\sim 400~\Omega.cm$ )<sup>9</sup> EPI layer. They were fabricated on three different wafers featuring the EPI layer thickness of 10, 15 and 20  $\mu$ m respectively. A comparison of CCE between them has also been listed in Table 2.2 [33]. One observation is that the CCE decreases with increasing thickness of the active volume. Since the average diffusion path of the signal electrons increases, the probability of losing charge carriers also increases by recombination. From the beam tests, the maximum SNR is found for the sensors with the EPI layer thickness of 15  $\mu$ m. It proves that an optimum SNR needs to not only

$<sup>^9400~\</sup>Omega.cm$  is a lower limit, meanwhile, we learned that the most likely value is  $\sim 1~\mathrm{k}\Omega.cm$

keep a good CCE but also generate a sizable signal charge in a sufficiently thick EPI layer [34].

# 2.3 Noise sources in CMOS pixel sensors

CPS suffer from noise of various natures that affect the system at different stages. The most important noise sources to be controlled in CPS are the leakage current shot noise of the sensing element [35], electronic noise of circuits used for the chip-level and board-level signal processing, and possibly also quantization noise (if the system has a digitized output).