# Simulation Native des Systèmes Multiprocesseurs sur Puce à l'aide de la Virtualisation Assistée par le Matériel

M.M. Hamayun

### ▶ To cite this version:

M.M. Hamayun. Simulation Native des Systèmes Multiprocesseurs sur Puce à l'aide de la Virtualisation Assistée par le Matériel. Micro et nanotechnologies/Microélectronique. Université de Grenoble, 2013. Français. NNT: . tel-00877962v1

# HAL Id: tel-00877962 https://theses.hal.science/tel-00877962v1

Submitted on 29 Oct 2013 (v1), last revised 11 Mar 2014 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### UNIVERSITÉ DE GRENOBLE

ISBN: 978-2-11-129179-9

## **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique

Arrêté ministériel : 7 août 2006

Présentée par

### **Mian Muhammad HAMAYUN**

Thèse dirigée par Frédéric PÉTROT

préparée au sein du Laboratoire TIMA et de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique (MSTII)

# Simulation Native des Systèmes Multiprocesseurs sur Puce à l'aide de la Virtualisation Assistée par le Matériel

« Native Simulation of Multi-Processor System-on-Chip using Hardware-Assisted Virtualization »

Thèse soutenue publiquement le **04 juillet, 2013**, devant le jury composé de :

#### **Mme. Florence MARANINCHI**

Professeur, Institut Polytechnique de Grenoble, Présidente

#### M. Jean-luc DEKEYSER

Professeur, Université des Sciences et Technologies de Lille, Rapporteur

### M. Guy BOIS

Professeur Titulaire, École Polytechnique de Montréal, Rapporteur

#### M. Alain GREINER

Professeur, Université Pierre et Marie Curie (Paris VI), Examinateur

### M. Benoit DUPONT DE DINECHIN

Directeur du Développement Logiciel, KALRAY, Examinateur

#### M. Frédéric PÉTROT

Professeur, Institut Polytechnique de Grenoble, Directeur de Thèse

# **Abstract**

Integration of multiple heterogeneous processors into a single System-on-Chip (SoC) is a clear trend in embedded systems. Designing and verifying these systems require high-speed and easy-to-build simulation platforms. Among the software simulation approaches, native simulation is a good candidate since the embedded software is executed natively on the host machine, resulting in high speed simulations and without requiring instruction set simulator development effort. However, existing native simulation techniques execute the simulated software in memory space shared between the modeled hardware and the host operating system. This results in many problems, including address space conflicts and overlaps as well as the use of host machine addresses instead of the target hardware platform ones. This makes it practically impossible to natively simulate legacy code running on the target platform. To overcome these issues, we propose the addition of a transparent address space translation layer to separate the target address space from that of the host simulator. We exploit the Hardware-Assisted Virtualization (HAV) technology for this purpose, which is now readily available on almost all general purpose processors. Experiments show that this solution does not degrade the native simulation speed, while keeping the ability to accomplish software performance evaluation. The proposed solution is scalable as well as flexible and we provide necessary evidence to support our claims with multiprocessor and hybrid simulation solutions. We also address the simulation of cross-compiled Very Long Instruction Word (VLIW) executables, using a Static Binary Translation (SBT) technique to generate native code that does not require run-time translation or interpretation support. This approach is interesting in situations where either the source code is not available or the target platform is not supported by any retargetable compilation framework, which is usually the case for VLIW processors. The generated simulators execute on top of our HAV based platform and model the Texas Instruments (TI) C6x series processors. Simulation results for VLIW binaries show a speed-up of around two orders of magnitude compared to the cycle accurate simulators.

### **Key Words**

Design Automation, Simulation, System Level Design, Hardware-Assisted Virtualization (HAV), System-on-Chip (SoC), Very Long Instruction Word (VLIW), Static Binary Translation (SBT).

# Résumé

L'intégration de plusieurs processeurs hétérogènes en un seul système sur puce (SoC) est une tendance claire dans les systèmes embarqués. La conception et la vérification de ces systèmes nécessitent des plateformes rapides de simulation, et faciles à construire. Parmi les approches de simulation de logiciels, la simulation native est un bon candidat grâce à l'exécution native de logiciel embarqué sur la machine hôte, ce qui permet des simulations à haute vitesse, sans nécessiter le développement de simulateurs d'instructions. Toutefois, les techniques de simulation natives existantes exécutent le logiciel de simulation dans l'espace de mémoire partagée entre le matériel modélisé et le système d'exploitation hôte. Il en résulte de nombreux problèmes, par exemple les conflits l'espace d'adressage et les chevauchements de mémoire ainsi que l'utilisation des adresses de la machine hôte plutôt des celles des plates-formes matérielles cibles. Cela rend pratiquement impossible la simulation native du code existant fonctionnant sur la plate-forme cible. Pour surmonter ces problèmes, nous proposons l'ajout d'une couche transparente de traduction de l'espace adressage pour séparer l'espace d'adresse cible de celui du simulateur de hôte. Nous exploitons la technologie de virtualisation assistée par matériel (HAV pour Hardware-Assisted Virtualization) à cet effet. Cette technologie est maintenant disponibles sur plupart de processeurs grande public à usage général. Les expériences montrent que cette solution ne dégrade pas la vitesse de simulation native, tout en gardant la possibilité de réaliser l'évaluation des performances du logiciel simulé. La solution proposée est évolutive et flexible et nous fournit les preuves nécessaires pour appuyer nos revendications avec des solutions de simulation multiprocesseurs et hybrides. Nous abordons également la simulation d'exécutables crosscompilés pour les processeurs VLIW (Very Long Instruction Word) en utilisant une technique de traduction binaire statique (SBT) pour généré le code natif. Ainsi il n'est pas nécessaire de faire de traduction à la volée ou d'interprétation des instructions. Cette approche est intéressante dans les situations où le code source n'est pas disponible ou que la plate-forme cible n'est pas supportée par les compilateurs reciblable, ce qui est généralement le cas pour les processeurs VLIW. Les simulateurs générés s'exécutent au-dessus de notre plate-forme basée sur le HAV et modélisent les processeurs de la série C6x de Texas Instruments (TI). Les résultats de simulation des binaires pour VLIW montrent une accélération de deux ordres de grandeur par rapport aux simulateurs précis au cycle près.

#### Mots Clès

Conception Assistée par Ordinateur (CAO), Simulation, Conception Niveau Système, Virtualisation Assistée par le Matériel (HAV), Système sur Puce (SoC), Mot d'Instruction Très Long (VLIW), Traduction Binaire Statique (SBT).

# Acknowledgments

First and foremost, I would like to thank my advisor Prof. Frédéric Pétrot for giving me the opportunity to work in his research group and for his continuous support during the last four years. I am also thankful to him for his guidance, kindness, patience and his technical support during research and writing of this dissertation. Without his help and guidance, it would have been impossible for me to finish this thesis.

I would like to thank Prof. Florence Maraninchi for presiding over my thesis defense committee. My special thanks to Prof. Jean-luc Dekeyser and Prof. Guy Bois for taking the time to review my thesis manuscript and their constructive remarks. I am very thankful to the examiners, Prof. Alain Greiner and Dr. Benoit Dupont De Dinechin for their pertinent questions and valuable remarks.

I would like to thank the French Ministry of Higher Education and Research for providing the financial support during my PhD studies. I am also thankful to Higher Education Commission (HEC) Pakistan, for awarding me the scholarship for Master program in France, which lead to my PhD studies.

I would like to thank my colleagues, Patrice Gerin, Hao Shen and Marius Gligor<sup>1</sup> for their indispensable support during my thesis. I must also thank the permanent SLS team members for their warm welcome and wonderful company, including Prof. Frédéric Rousseau, Hamed Sheibanyrad, Stephane Mancini, Paul Amblard (Late), Nicolas Fournel and Olivier Muller<sup>2</sup>. I should not forget Xavier Guerin, Luc Michel<sup>1</sup>, Ashraf Elantably<sup>1</sup>, Maryam Bahmani<sup>1</sup>, Sahar Foroutan, Clément Deschamps, Etienne Ripert, Gilles Bizot, Wassim Mansour<sup>1</sup>, Yi Gang<sup>1</sup> and Saif-ur-Rehman<sup>1</sup> for their support. I would like to convey my best wishes to Guillaume Sarrazin, who has accepted to continue working on native simulation technique for his thesis.

In my social circles, I would like to thank my dear friend Dr. Anis-ur-Rehman Khan, who provided me the best possible fellowship one could expect from anyone. His presence of mind, witty humor and sporting activities provided me with the necessary fresh air, during stressful times. I must not forget Asif Iqbal Baba for his religious expressions and cricketing enthusiasm, which brought the necessary physical activity to our lives. I am also very grateful to the Grenoblois Pakistanais community, which organized many gatherings that gave us the means to celebrate our cultural events, with friends and families.

In the end, I must thank my parents, my brothers Usman & Umar, my sister Ayesha, my wife Fouzia and my children Shehryar & Mahnoor for their prayers and encouragement during my studies. Without their moral support, things would have been much more difficult. I will remain in their debt for the rest of my life!

Mian Muhammad Hamayun 25 September, 2013

<sup>&</sup>lt;sup>1</sup>An additional thanks for their help in the preparations of my "Pot-de-Thèse".

<sup>&</sup>lt;sup>2</sup>An additional thanks for his kind support in my teaching assignments as well as in general discussions.

# List of Figures

|      |                                                                           | Page     |

|------|---------------------------------------------------------------------------|----------|

| 1.1  | Les tendances de marché SoC et complexité de conception                   | 4        |

| 1.2  | MPSoC de future avec plusieurs processeurs GPP et DSP                     |          |

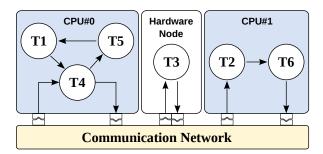

| 1.3  | Encapsulation du logiciel pour la simulation native                       |          |

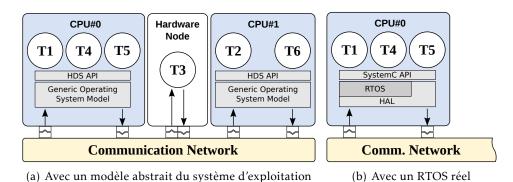

| 1.4  | Encapsulation du logiciel avec un système d'exploitation abstrait ou réal | 7        |

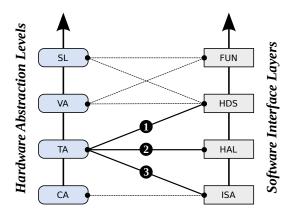

| 1.5  | Niveaux d'abstraction matérielle et couches d'interface du logiciel       | 8        |

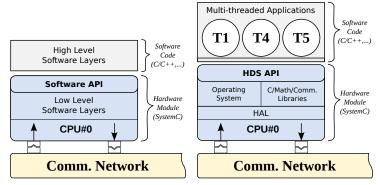

| 1.6  | L'exécution en couches du logiciel à différents niveaux de l'interface    | 8        |

| 1.7  | Représentations de la mémoire cible et hôte (Adapté de [Ger09])           | 10       |

| 1.8  | Modification de la mémoire cible pour remmapage des adresses              |          |

| 1.9  | Représentation uniforme de la mémoire                                     | 12       |

| 1.10 | Modes hôte et invité dans HAV (Les processeurs Intel)                     |          |

|      | Support pour la virtualisation de la mémoire dans HAV                     |          |

|      | Les unités de traitement natifs (NPU) et leur interfaces avec KVM         |          |

|      | Le flux d'exécution dans la simulation native                             |          |

|      | Couche d'abstraction matérielle dépendant de la machine hôte              |          |

|      | Accès mémoire et d'entrées / sorties                                      |          |

|      | Processeur natives, bibliothèque KVM, KVM et la pile logicielle invité    |          |

| 2.1  | SoC Consumer Portable Design Complexity Trends                            |          |

| 2.2  | Future MPSoCs with Many GPPs along with a few DSPs and Hardware IPs .     |          |

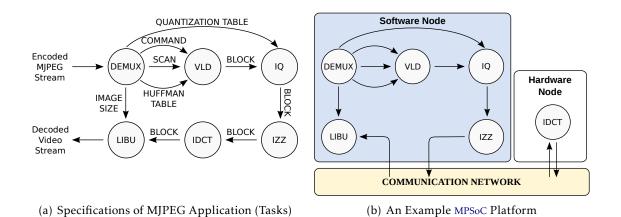

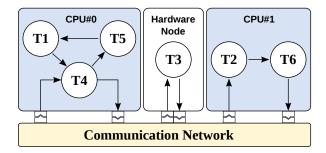

| 3.1  | Tasks in the MJPEG Application                                            |          |

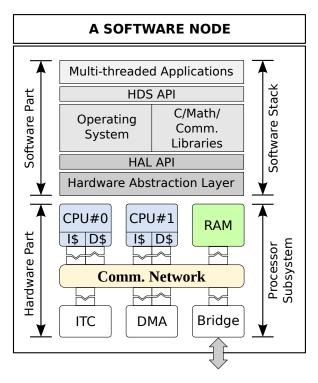

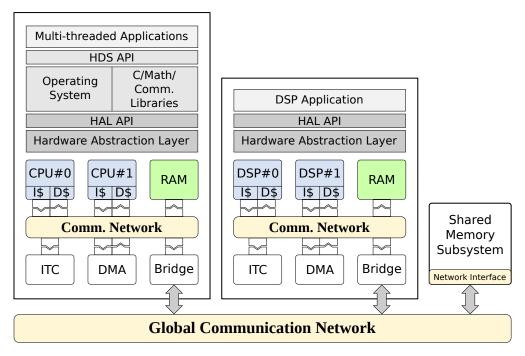

| 3.2  | Architecture of a Software Node                                           |          |

| 3.3  | Multiple Software Nodes with Different Types of Processors                |          |

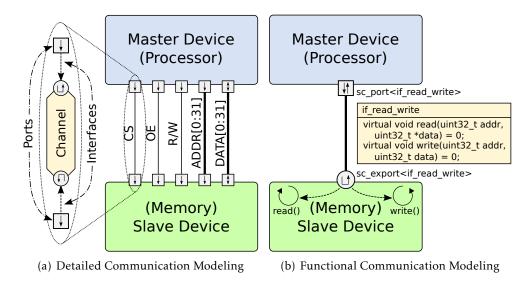

| 3.4  | Communication Modeling Abstractions in SystemC                            |          |

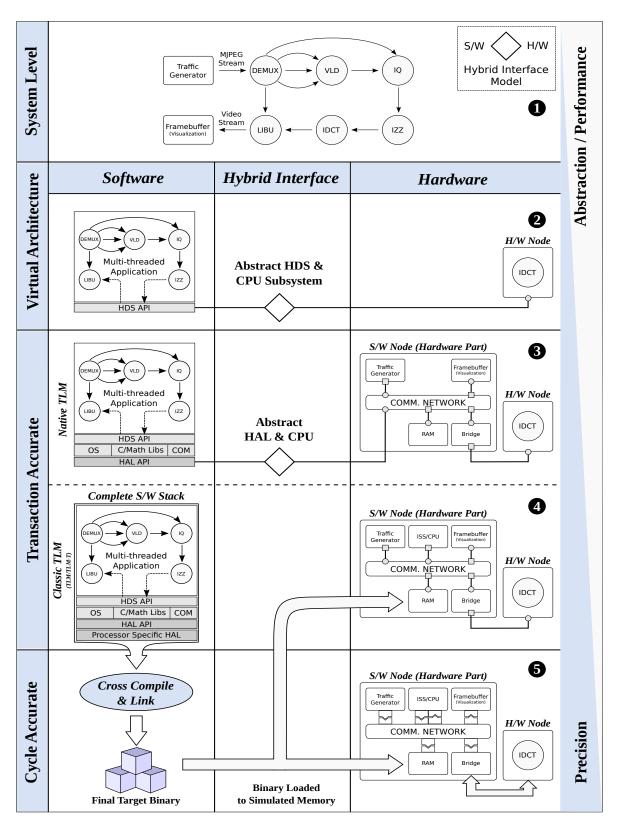

| 3.5  | Abstraction Levels and Simulation Models                                  |          |

| 3.6  | Principle of Native Execution on a Transaction Accurate Platform          |          |

| 3.7  | Target vs. Host Memory Representations                                    |          |

| 3.8  | Native Uniform Memory Representation                                      |          |

| 3.9  | Native Software Compilation with Target Specific Annotations              |          |

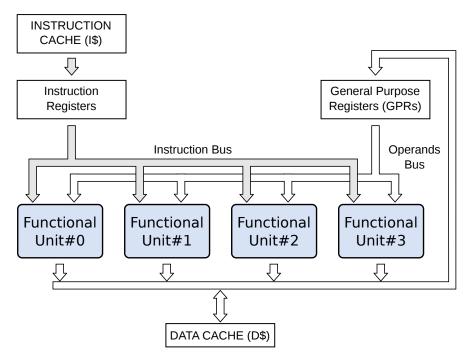

|      | Generic Architecture of a VLIW Processor                                  | 49<br>50 |

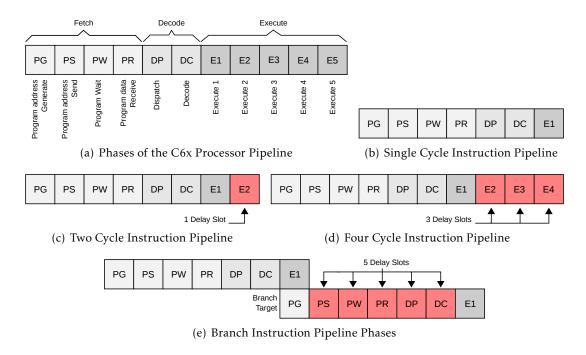

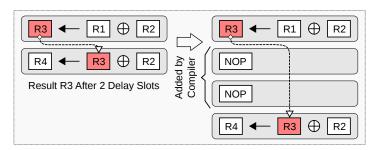

|      | Pipeline Stages and Delay Slots in TI C6x Processors                      |          |

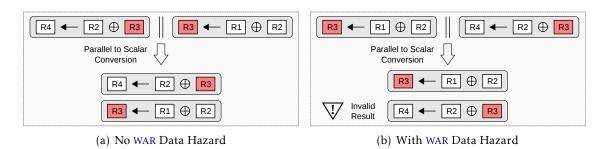

|      | WAR Hazards in Parallel to Scalar Conversion                              |          |

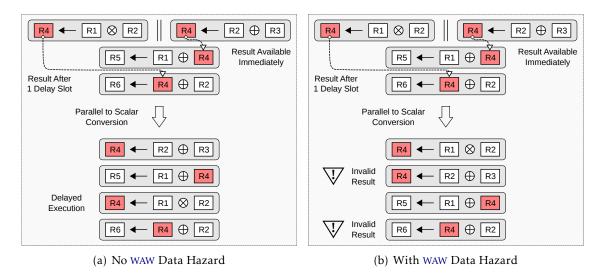

|      | WAW Hazards Resulting from Instruction Scheduling                         | 52       |

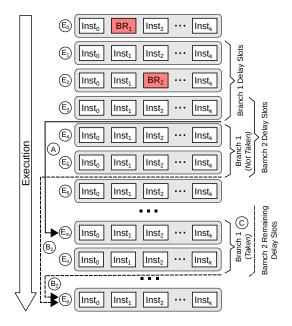

|      | Control Hazards in VLIW Processors                                        | 53       |

| 4.1  | Software Encapsulation in Native Simulation                               |          |

| 4.2  | Software Encapsulation with an Abstract/Real Operating System             |          |

| 4.3  | Hardware Abstraction Levels and Software Interface Layers                 |          |

| 4.4  | Layered Software Execution at Different Interface Levels                  |          |

| 1.1  | Day crea doremare Execution at Different interface Develo                 | 01       |

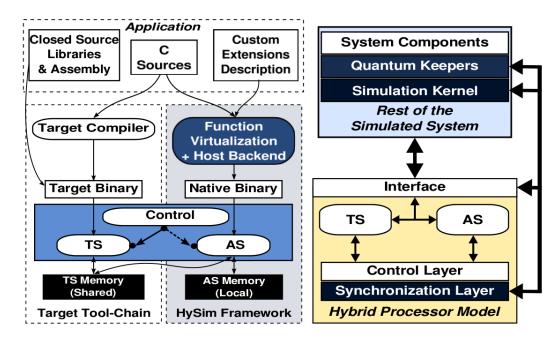

| 4.5  | Architecture of the HySim Framework                                      | 63  |

|------|--------------------------------------------------------------------------|-----|

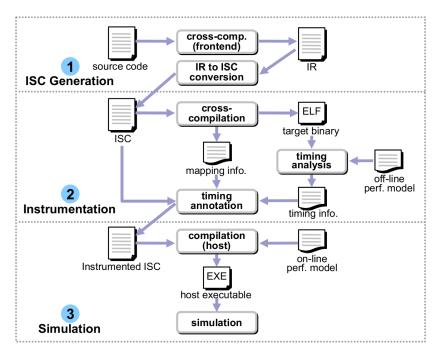

| 4.6  | Design Flow of the iSciSim Approach                                      | 66  |

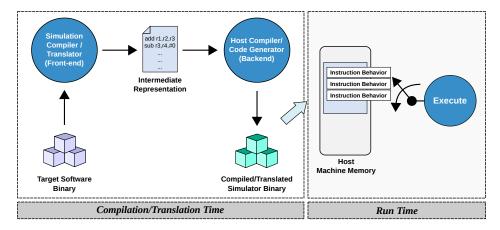

| 4.7  | Basic Compiled Simulation/Static Translation Principle                   | 68  |

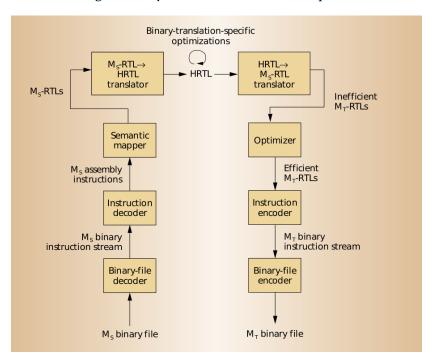

| 4.8  | Static Binary Translation Flow in UQBT                                   | 69  |

| 4.9  | Generic Principle of Dynamic Compiled Simulation                         | 71  |

| 4.10 | Principle of Hybrid Compiled Simulation                                  | 72  |

| 5.1  | Guest vs. Host Modes in Hardware-Assisted Virtualization                 | 75  |

| 5.2  | Memory Virtualization Support in Hardware-Assisted Virtualization        | 78  |

| 5.3  | Native Processing Units and their interfacing with KVM                   | 80  |

| 5.4  | Execution Flow in Native Simulation                                      | 81  |

| 5.5  | Host Dependent Hardware Abstraction Layer                                | 83  |

| 5.6  | Multiple External Event Sources, their Cost and Load Condition           | 84  |

| 5.7  | Hardware Abstraction Layer with Synchronizations                         | 86  |

| 5.8  | Memory and I/O Address Space Accesses                                    | 87  |

| 5.9  | Platform Address Decoder with Statically Allocated Addresses             | 90  |

| 5.10 | Native Processor, KVM and Software Stack                                 | 92  |

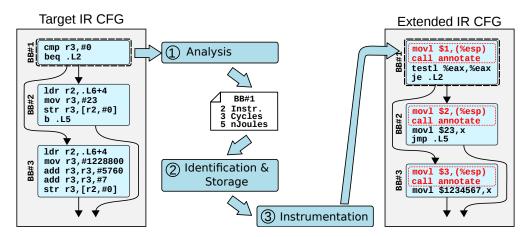

| 5.11 | Basic Block Annotation Process using LLVM Infrastructure                 | 93  |

| 5.12 | Forwarding Annotation Calls to SystemC using PMIO                        | 94  |

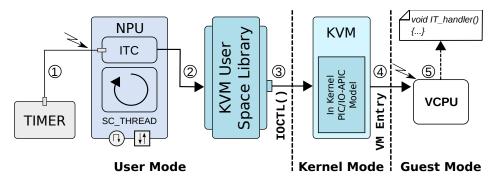

|      | Handling External Events using Interrupt Injection in KVM                | 97  |

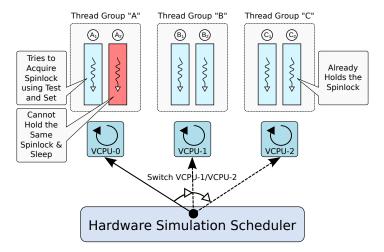

| 5.14 | Guest Software Threads and VCPU Locking Issue                            | 99  |

| 5.15 | VCPU Execution Flow within KVM and Blocking States                       | 101 |

| 5.16 | SystemC Timing Modifications on Execution of Test and Set                | 103 |

| 5.17 | Multiprocessor Simulation using KVM with Debug and Interrupt Support .   | 104 |

| 5.18 | Hybrid Simulation Platform using DBT and Native Processors               | 105 |

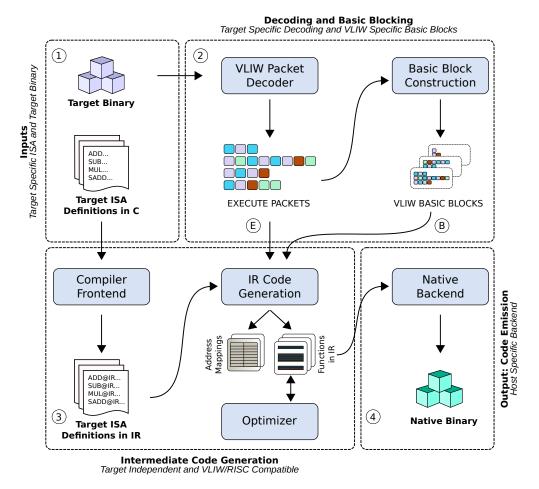

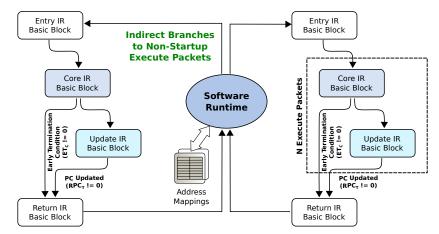

| 6.1  | Static Binary Translation Flow for VLIW Binaries                         | 111 |

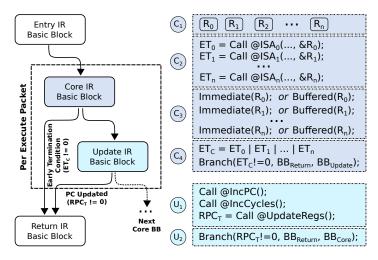

| 6.2  | Intermediate Code Generation for VLIW Basic Blocks                       | 114 |

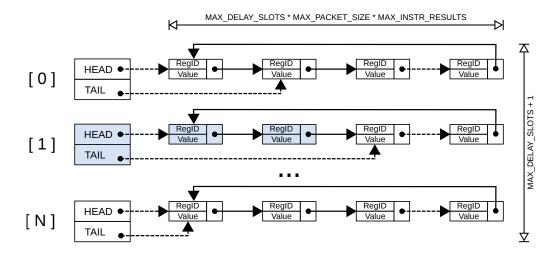

| 6.3  | Delay Slot Buffers for Register Updates                                  | 116 |

| 6.4  | Memory Mapping for Statically Generated VLIW equivalent Native Binaries  | 117 |

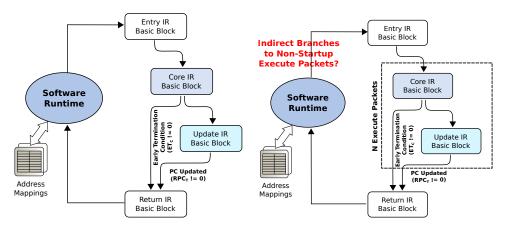

| 6.5  | Code Generation Modes in Static Translation for VLIW Binaries            | 118 |

| 7.1  | Functional Decomposition of Parallel-MJPEG Application                   | 129 |

| 7.2  | NaSiK MPSoC Simulation Platform for Native and VLIW Simulation           | 130 |

| 7.3  | Hybrid Simulation Platform using KVM and QEMU Based Processor Models     | 131 |

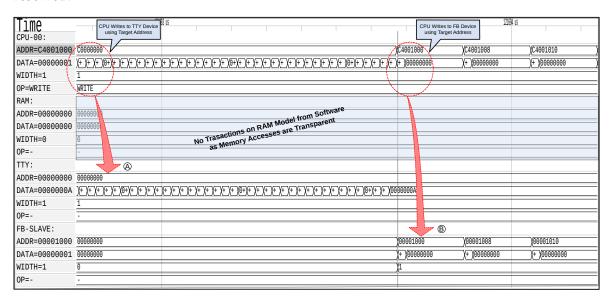

| 7.4  | Target Memory and I/O Address Space Accesses                             | 132 |

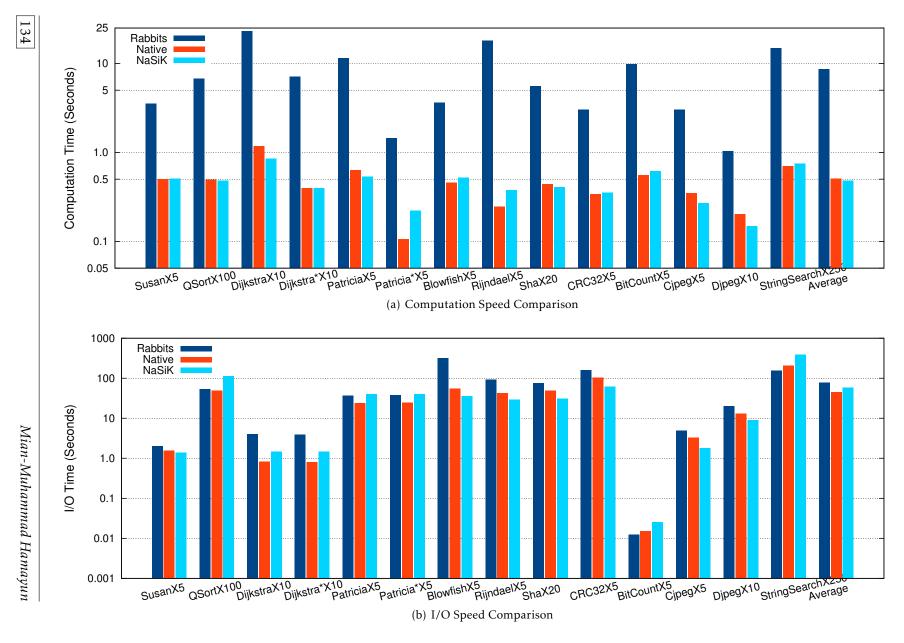

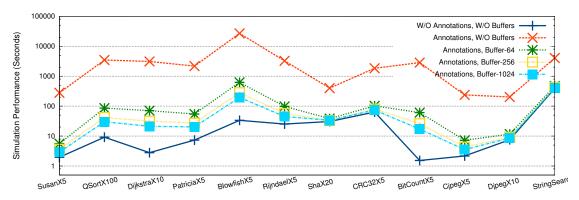

| 7.5  | Computation and I/O Speed Comparison between Rabbits, Native and NaSiK   | 134 |

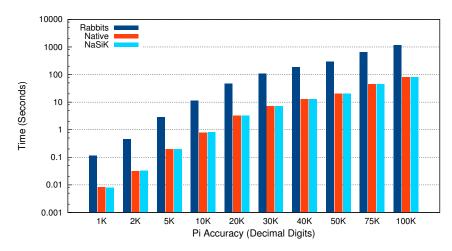

| 7.6  | Computation Performance of PI Application                                | 135 |

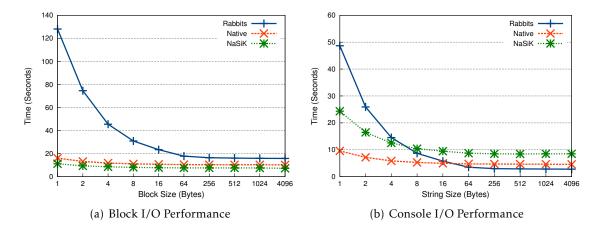

| 7.7  | Block and Console I/O Performance for Rabbits, Native and NaSiK          | 136 |

| 7.8  | NaSiK Simulation Platform with Annotations and Annotation Buffers        | 137 |

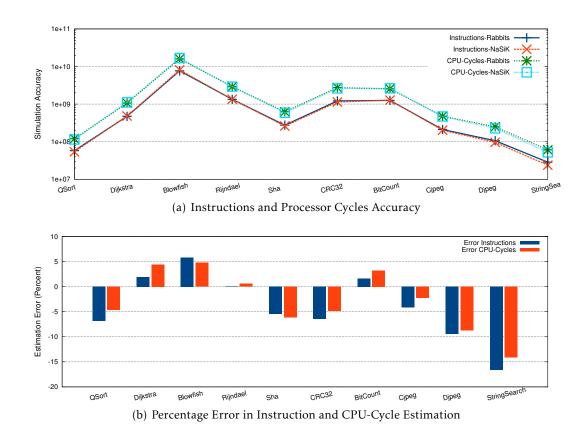

| 7.9  | Instruction and Cycle Accuracy Comparison between Rabbits and NaSiK      | 139 |

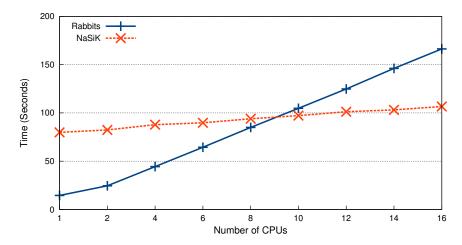

|      | MPSoC Simulation Speed Comparison between QEMU and KVM Platforms .       | 141 |

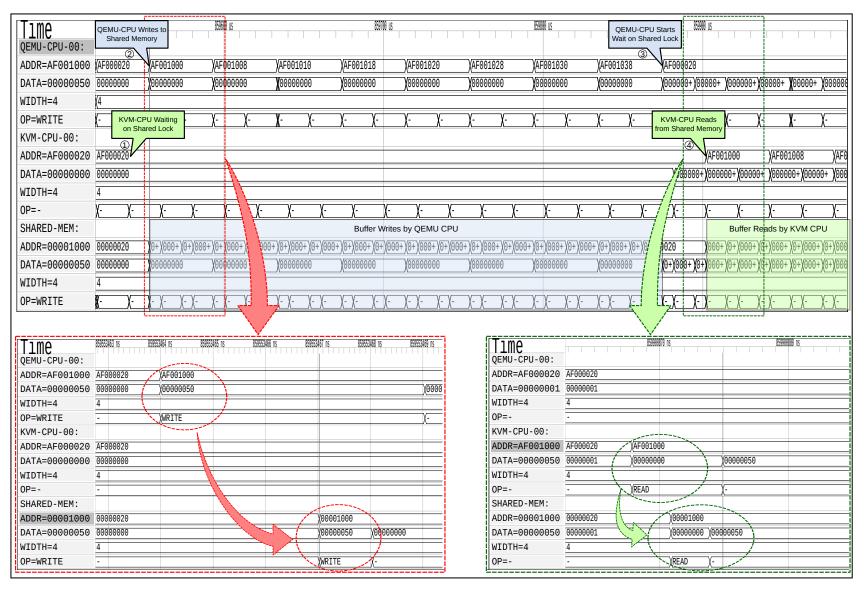

|      | Shared Memory Access between QEMU and KVM Processors                     | 143 |

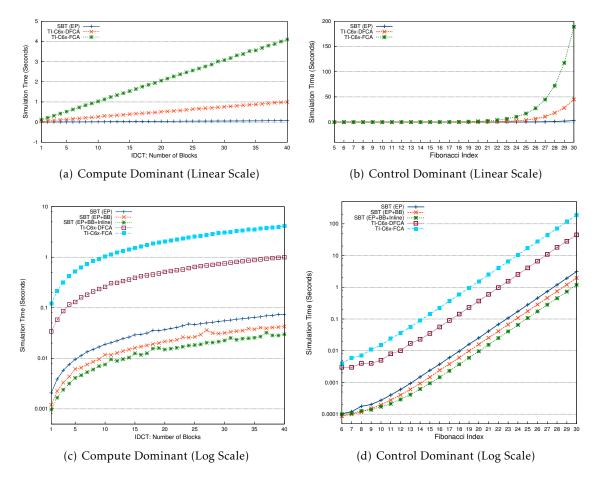

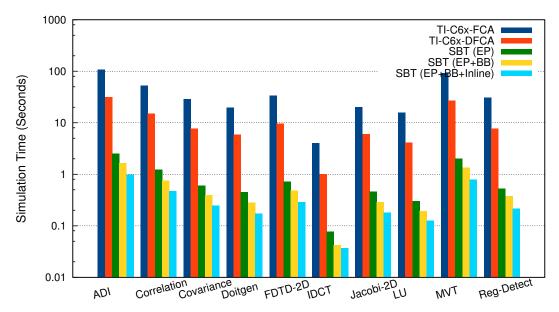

|      | Performance of Compute vs. Control Dominant DSP Kernels                  | 144 |

|      | Performance Comparison for Different DSP Kernels                         | 145 |

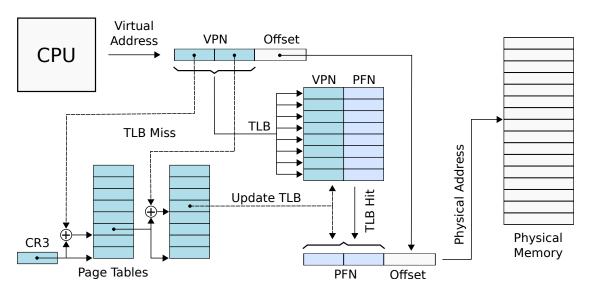

| B.1  | Virtual to Physical Address Translation and Translation Lookaside Buffer | 157 |

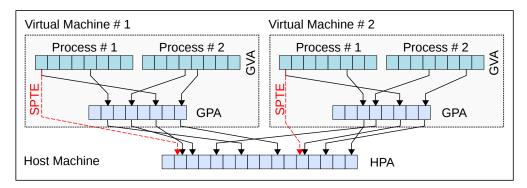

| B.2  | Role of Shadow Page Tables in Guest Address Space Translation            | 158 |

| B.3  | Guest Page Table Accesses and Synchronization with Shadow Page Tables    | 158 |

| B.4  | Role of Extended Page Tables in Guest Address Space Translation          | 159 |

| B.5  | Guest Physical Address Translation using Extended Page Tables            | 160 |

# List of Tables

|                                                                            | Page                                                                       |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Nested Branch Control Flows in VLIW Software: An Example                   | 53                                                                         |

| Basic KVM APIs for Virtual Machine Initialization and Execution            | 80                                                                         |

| Local Memories, I/O and Shared Memory Accesses in QEMU, Traditional Native |                                                                            |

| and KVM-based Platforms                                                    | 108                                                                        |

| Operand Types in ISA Definitions                                           | 112                                                                        |

| Possible Code Generation Modes for VLIW Software Binaries                  | 119                                                                        |

| HAL API Functions for DNA-OS                                               | 127                                                                        |

| Selected DSP Kernels for VLIW Simulation                                   | 129                                                                        |

| Computation Speed-up in KVM Simulation                                     | 133                                                                        |

| I/O Speedup/Slowdown in KVM Simulation                                     | 135                                                                        |

| KVM Simulation Performance With Annotations and Annotation Buffers         | 138                                                                        |

| KVM Simulation Accuracy Best and Worst Cases                               | 138                                                                        |

| Decoding Time for 100 Frames using Parallel-MJPEG Application              | 141                                                                        |

| Maximal Speed-ups of SBT Simulation using Hybrid Translation               | 146                                                                        |

| Sensitive/Non-Sensitive vs. Privileged/Unprivileged Instructions           | 153                                                                        |

| Sensitive Register Instructions in IA-32 (x86)                             | 154                                                                        |

| Sensitive Protection System Instructions in IA-32 (x86)                    | 155                                                                        |

|                                                                            | Local Memories, I/O and Shared Memory Accesses in QEMU, Traditional Native |

# Contents

|         | Po                                                                                                                                                                                                                                                                                                                                              | age                                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| At      | ostract                                                                                                                                                                                                                                                                                                                                         | iii                                          |

| Ré      | esumé                                                                                                                                                                                                                                                                                                                                           | v                                            |

| Ac      | cknowledgments                                                                                                                                                                                                                                                                                                                                  | vii                                          |

| Li      | st of Figures                                                                                                                                                                                                                                                                                                                                   | ix                                           |

| Lis     | st of Tables                                                                                                                                                                                                                                                                                                                                    | хi                                           |

| I       | Résumé Français                                                                                                                                                                                                                                                                                                                                 | 1                                            |

| 1<br>II | Simulation Native de MPSoC à l'aide de la Virtualisation Assistée par le Matériel  1.1 Introduction                                                                                                                                                                                                                                             | 3<br>5<br>7<br>9<br>11<br>14<br>19           |

| 2       | Introduction                                                                                                                                                                                                                                                                                                                                    | 23                                           |

| 2       | 2.1 The Hardware/Software Co-Design Challenge                                                                                                                                                                                                                                                                                                   | 23<br>25                                     |

| 3       | Native Simulation of MPSoC: A Retrospective Definition & Problems  3.1 Generic Architecture of An MPSoC  3.2 Architecture of Software Nodes  3.2.1 Key Terms  3.3 Description Languages for Simulation Models  3.3.1 SystemC: A Modeling Language  3.4 Abstraction Levels and Simulation Models  3.4.1 System Level  3.4.2 Cycle Accurate Level | 27<br>28<br>29<br>30<br>31<br>33<br>34<br>34 |

|   |      | 3.4.3    | Virtual Architecture Level                                     |

|---|------|----------|----------------------------------------------------------------|

|   |      | 3.4.4    | Transaction Accurate Level                                     |

|   | 3.5  |          | Transaction Accurate Simulation                                |

|   |      |          | Hardware Abstraction Layer                                     |

|   |      |          | Native Software Execution                                      |

|   |      |          | Target vs. Host Address Spaces                                 |

|   |      |          | Using a Unified Address Space                                  |

|   |      | 3.5.5    | Software Performance Estimation                                |

|   | 3.6  |          | Processor Architecture Simulation                              |

|   | 0.0  |          | Modeling Parallelism and VLIW Pipelines                        |

|   |      |          | Memory Addressing in Translated Software                       |

|   |      |          | Software Execution Timings and Synchronization                 |

|   |      |          | Hybrid and Heterogeneous MPSoC Simulation                      |

|   | 3.7  |          | sion and Key Questions                                         |

|   | 3.7  | Conciu   | ision and key Questions                                        |

| 4 | Stat | e of the | Art: On Software Execution for MPSoC Simulation 57             |

|   | 4.1  | Native   | Platforms for MPSoC Simulation                                 |

|   |      | 4.1.1    | Software Encapsulation                                         |

|   |      |          | Hardware-Software Interfaces                                   |

|   |      |          | Hybrid Techniques                                              |

|   | 4.2  |          | nance Estimation in Native Simulation                          |

|   |      | 4.2.1    | Source Level Simulation                                        |

|   |      |          | Intermediate Representation Level Simulation                   |

|   |      |          | Binary Level Simulation                                        |

|   | 4.3  |          | sion and Conclusions                                           |

|   |      |          |                                                                |

| 5 |      |          | oC Simulation Platform Using Hardware-Assisted Virtualization  |

|   | 5.1  |          | are-Assisted Virtualization (HAV)                              |

|   |      |          | Processor Virtualization                                       |

|   |      |          | Memory Virtualization                                          |

|   |      |          | I/O Virtualization/Emulation                                   |

|   | 5.2  |          | Simulation Using Hardware-Assisted Virtualization              |

|   |      |          | Native Processing Units                                        |

|   |      |          | Host Dependent Hardware Abstraction Layer                      |

|   |      | 5.2.3    | Using Hardware Abstraction Layer as a Synchronization Point 83 |

|   |      |          | Memory and I/O Address Space Accesses                          |

|   | 5.3  | _        | Annotations in Software                                        |

|   |      | 5.3.1    | Minimizing Guest <i>vs.</i> Host Mode Switches                 |

|   | 5.4  |          | Simulation using Hardware-Assisted Virtualization 96           |

|   |      |          | Asynchronous External Events                                   |

|   |      | 5.4.2    | Simulating Multiple Processors                                 |

|   |      |          | Virtual CPU Scheduling in Kernel Virtual Machine               |

|   | 5.5  |          | MPSoC Simulation                                               |

|   |      |          | Memory and I/O Access Comparison                               |

|   | 5.6  | Conclu   | sions and Limitations                                          |

### CONTENTS

| 6 | Stat | ic Binary Translation Targeting VLIW Processor Simulation         | 109 |

|---|------|-------------------------------------------------------------------|-----|

|   | 6.1  | Static Binary Translation Principle and Constraints               | 109 |

|   |      | 6.1.1 Static Translation Specific Constraints                     | 110 |

|   |      | 6.1.2 Virtualization Specific Constraints                         | 110 |

|   | 6.2  | Retargetable Static Translation of VLIW Software                  | 111 |

|   |      | 6.2.1 Instruction Representation                                  | 112 |

|   |      | 6.2.2 Execute Packet Decoding and Basic Block Construction        | 113 |

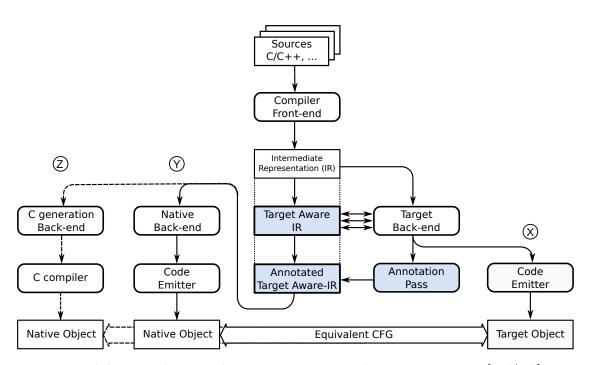

|   |      | 6.2.3 Intermediate Code Generation                                | 113 |

|   |      | 6.2.4 VLIW Processor State and Circular Buffers                   | 115 |

|   |      | 6.2.5 Data and Instruction Memory Accesses                        | 116 |

|   |      | 6.2.6 Code Generation Modes                                       | 117 |

|   |      | 6.2.7 Optimization and Inlining                                   | 119 |

|   | 6.3  | Conclusions and Limitations                                       | 123 |

| 7 | Exp  | erimentation and Results                                          | 125 |

|   | 7.1  | Software Environment and Benchmarks                               | 125 |

|   |      | 7.1.1 MiBench Suite                                               | 126 |

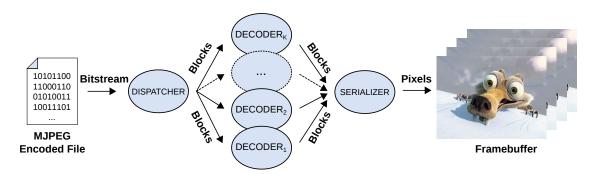

|   |      | 7.1.2 Parallel Motion-JPEG                                        | 126 |

|   |      | 7.1.3 Audio Filter                                                | 128 |

|   |      | 7.1.4 DSP Kernels                                                 | 129 |

|   | 7.2  | Hardware Environment and Reference Platforms                      | 129 |

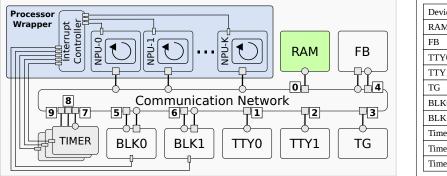

|   |      | 7.2.1 Native MPSoC Simulation Platform                            | 130 |

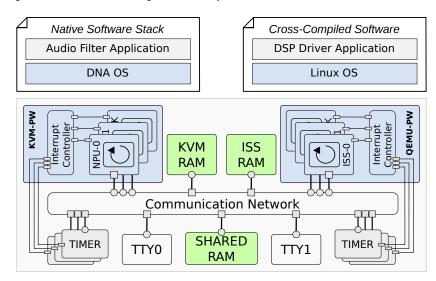

|   |      | 7.2.2 Hybrid Simulation Platform                                  | 131 |

|   |      | 7.2.3 Reference Platforms and Simulators                          | 131 |

|   | 7.3  | Mono-processor Experiments                                        | 131 |

|   |      | 7.3.1 Software Execution in Target Address Space                  | 132 |

|   |      | 7.3.2 Compute <i>vs.</i> I/O Intensive Applications               | 132 |

|   |      | 7.3.3 Software Annotations and Simulation Accuracy                | 137 |

|   | 7.4  | Multi-processor Experiments                                       | 140 |

|   |      | 7.4.1 Multi-threaded Applications on SMP Platforms                | 140 |

|   |      | 7.4.2 Hybrid Simulation Platform                                  | 141 |

|   | 7.5  | Simulation of Cross-Compiled DSP Kernels                          | 142 |

|   | 7.6  | Conclusions and Limitations                                       | 146 |

| 8 | Con  | clusions and Perspectives                                         | 149 |

|   | 8.1  | Conclusions                                                       | 149 |

|   | 8.2  | Perspectives                                                      | 151 |

| A | Sens | sitive and Unprivileged Instructions in IA-32 (x86) Architectures | 153 |

| В | Mer  | nory Virtualization Support in Hardware-Assisted Virtualization   | 157 |

|   | B.1  | Memory Virtualization using Shadow Page Tables                    | 158 |

|   | B.2  | Memory Virtualization using Extended Page Tables                  | 159 |

| C | Cod  | e Generation Algorithms for VLIW Software Simulation              | 161 |

|   | C.1  | IR Generation for VLIW Basic Blocks                               | 161 |

|   | C.2  | IR Generation for VLIW Execute Packets                            | 162 |

|                      | CONTENTS |

|----------------------|----------|

|                      |          |

| Glossary             | 165      |

| List of Publications | 169      |

| References           | 171      |

# Part I Résumé Français

Le temps est un grand maître, dit-on, le malheur est qu'il tue ses élèves.

Berlioz

1

# Simulation Native de MPSoC à l'aide de la Virtualisation Assistée par le Matériel

'ÉTAT actuel de l'art en matière de technologie de VLSI (VLSI pour Very-Large-Scale Integration) permet la fabrication de plusieurs milliards de transistors sur une seule puce. La conception et l'intégration du matériel avec un si grand nombre de transistors est très difficile. Une solution simple pour les concepteurs de matériel est de mettre plusieurs processeurs relativement simples sur une seule puce plutôt que de concevoir une machine mono-processeur complexe. Par ailleurs, l'évolutivité des mono-processeurs est limitée par les facteurs de dissipation de puissance, comme on ne peut pas simplement augmenter la vitesse d'horloge pour obtenir d'avantage de performance.

Dans le domaine des systèmes intégrés, des problèmes de consommation et de rendement nécessitent l'utilisation d'architectures simples. Il s'agit notamment de processeurs qui disposent un rapport MIPS (MIPS pour Million Instructions Per Second) plus elevé par rapport à la consommation en Watt. Cette tendance se poursuit vers des structures plus régulières et homogènes mais comprenant encore, éventuellement, du matériel spécifique et des extensions de jeu d'instructions dans les éléments de traitement. Ces multiprocesseurs spécifiques à une classe d'application sont appelés MPSoC (MPSoC pour Multi-Processor System-on-Chip). De nombreux secteurs industriels, tels que les télécommunications, l'aérospatiale, l'automobile, le militaire et l'électronique grand public utilisent actuellement ces systèmes.

### 1.1 Introduction

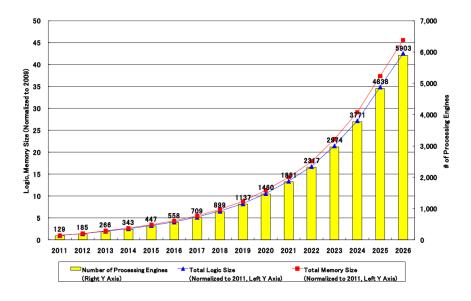

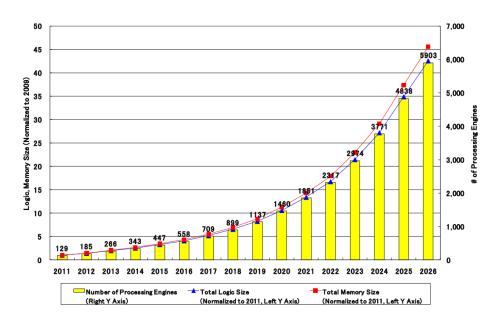

La complexité de conception de MPSoC est en augmentation à cause du nombre et du type d'éléments de calcul inclus dans ces systèmes. Selon l'ITRS, jusqu'à 6000 processeurs sont attendus sur un seul SoC d'ici la fin de l'année 2026, comme indiqué dans la Figure 1.1. La conception et la vérification d'une solution matérielle avec tel nombre d'éléments de calcul, qui de plus tourne un logiciel encore plus complexe, est un énorme défi.

De même, les délais de mise sur le marché sont d'une importance primordiale dans

l'électronique grand public, pour les fabricants de produits pour rester compétitif et de réussir à répondre aux exigences du marché. Les delais dans la conception et la fabrication de systèmes MPSoC plus en plus complexe minent cet objectif, car le développement du logiciel dépend de la disponibilité du matériel. Les plates-formes virtuelles, ou modèles de simulation, offrent une alternative, car le développement de logiciels peut commencer tôt et en parallèle avec la conception du matériel. Par ailleurs, les équipes de développement du logiciel ont besoin des plateformes de simulation, même si le matériel est disponible, car les premiers prototypes sont généralement très coûteux.

Figure 1.1: Les tendances de marché SoC et complexité de conception des systèmes portable [ITR]

La simulation s'appuie sur des modèles et comme il peut être entendu que si les modèles sont proches de la réalité, la simulation sera lente, et s'ils sont abstraits, la précision des résultats peut être contestable. Plusieurs strategies de simulation existent pour l'exécution du logiciel : la première s'appuie sur l'ISS (ISS pour Instruction Set Simulator) qui est la technologie de virtualisation du processeur la plus mature et couramment utilisée. L'ISS exécute les fichiers binaires cible (target) cross-compilé (Système d'Exploitation et Applications) et imitent le comportement des processeurs cibles par l'interprétation exacte des instructions [Bel73]. Leur principal inconvénient vient de la vitesse de simulation très lente. La seconde repose sur l'émulation, principalement par DBT [Bel05] (DBT pour Dynamic Binary Translation) mais nécessite des coûts de développement relativement élevé. La troisième utilise la simulation native, c'est-à-dire l'exécution de code sans compilation croisée. Des techniques de simulation natives [BBY+05, JBP06] atteingnent des vitesses de simulation supérieures comme ils surmontent l'interprétation / coût de la traduction, par la compilation du logiciel embarqué au format binaire hôte et l'exécutent directement sur les processeurs hôtes. Afin d'accéder à des ressources matérielles modélisées, le logiciel doit utiliser une API (API pour Application Programming Interface) spécifique, que ce soit au niveau du Système d'Exploitation [GCKR12] ou niveau du HAL (HAL pour Hardware Abstraction Layer) [GHP09].

Généralement la partie fonctionnelle des systèmes de simulation natifs ne dépend pas de l'ISAs de processeurs cibles, ce qui les rend attrayant du point de vue du développement.

D'autre part cela rend le simulation subtilement différent du point de vue du flux de contrôle d'exécution cible, comme les optimisations spécifiques cibles ne peuvent pas être facilement appliquées sur le logiciel natif. En dehors du fait ci-dessus, les techniques de simulation natives introduisent leurs propres problèmes qui les éloignent de l'architecture modélisée. Il s'agit notamment de différences de l'espace d'adressage de la cible par rapport la machine hôte, comme le logiciel natif utilise l'espace d'adressage de la machine hôte pour toutes les références de mémoire. Cela se traduit par des espaces d'adressage contradictoires et qui peuvent se chevaucher entre la machine hôte et les architectures cibles simulées. Certaines interactions entre le matériel et le logiciel devienent impossibles, comme le DMA (DMA pour Direct Memory Access) vers les régions de mémoire allouées par le logiciel.

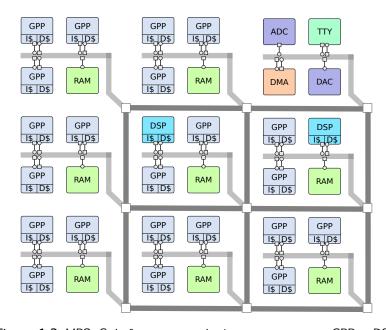

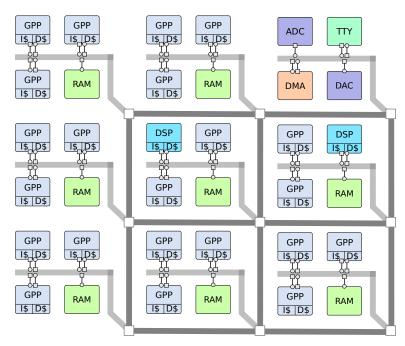

Plus la complexité des architectures modélisées augmente (tant au niveau matériel et logiciel), plus les solutions natives sont loin des architectures cibles. Ces situations proviennent généralement lors de la modélisation des machines parallèles en utilisant des techniques natives, c'est-à-dire en utilisant le logiciel compilé nativement pour modéliser l'exécution d'un flux d'instructions parallèles, par exemple, dans le cas des architectures VLIW (VLIW pour Very Long Instruction Word). Ainsi, la modélisation de MPSoC hétérogène contenant des processeurs VLIW ainsi que des GPP est un objectif important. Nous devons nous concentrer sur ces architectures futures à l'aide des solutions natives ainsi que sur des solutions de simulation mixte. La Figure 1.2 illustre ces tendances dans les architectures mpsoc hétérogènes du futur.

Figure 1.2: MPSoC de future avec plusieurs processeurs GPP et DSP

# 1.2 Problématique

Simulation native de logiciel est un concept bien connu, allant des techniques primitives basées sur l'exécution directe des algorithmes sur l'hôte pour la vérification fonctionnelle à des implémentations plus avancées reposant sur l'HAL et les notions de liaison dynamique.

Dans sa formulation la plus générale, la simulation du logiciel natifs vise l'exécution

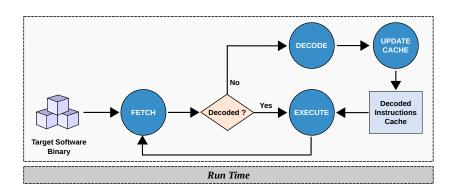

directe du code logiciel sur la machine hôte à l'aide d'une "enveloppe" pour se connecter à un environnement de simulation événementielle. Les propositions initiales suggèrent d'encapsuler le code de l'application dans les modules TLM en utilisant des threads matériels, comme si elles étaient implémentées comme des composants matériels [GCDM92, GYNJ01, BYJ02, WSH08, CHB09a]. Un sous-ensemble des tâches logicielles est encapsulé dans les modules matériel, c'est-à-dire des éléments de traitement de la plate-forme, comme représenté sur la Figure 1.3. Le noyau de simulation matériel ordonance à la fois des fils d'exécution matériels et logiciels, apportant concurrence implicite et non intentionnelle à des tâches logicielles. Effectivement, cela ne permet pas de rendre compte du comportement du système d'exploitation.

Figure 1.3: Encapsulation du logiciel pour la simulation native

Ces solutions sont simples mais présentent deux inconvénients graves. Premièrement, le code simulé donne une forme très limité de parallélisme, c'est-à-dire des co-routines. Deuxièmement, puisque le logiciel s'exécute dans un module matériel, toutes les allocations de données par le logiciel sont alloués dans l'espace d'adressage du processus de simulation au lieu de la mémoire de la plate-forme cible simulée. Il n'existe aucun moyen pour un composant de la plate-forme d'accéder à un buffer alloué par le logiciel parce que le buffer n'est pas visible d'elle alors qu'il doit l'être, les adresses de la plate-forme de simulation n'ont aucun lien avec les adresses du processus de simulation. En outre, l'exécution du logiciel est limité dans le contexte matériel, tels que la façon dont il accède aux ressources de la plate-forme sous-jacente à l'aide des interfaces de la plateforme par exemple en utilisant les ports dans les modèles TLM (TLM pour Transaction Level Modeling). Ces approches ne sont clairement pas aptes à supporter le code pré-existant.

En raison de la complexité du logiciel embarqué et des exigences de dépendance d'exécution, l'intégration de modèles abstraits du système d'exploitation directement dans les environnements de simulation natifs a été proposé. L'objectif est de fournir une implémentation légère d'un système d'exploitation en utilisant les primitives basées sur des événements de l'environnement de simulation, ainsi chaque tâche logicielle devient un module matériel. En utilisant cette approche, le RTOS (RTOS pour Real-Time Operating System) modélisé repose sur l'ordonnanceur du simulateur de matériel au lieu de l'ordonnanceur que le RTOS aurait utilisé, même si certaines solutions suggèrent de modifier le noyau de simulation de matériel à cet effet. Ces travaux rendent compte des algorithmes d'ordonnancement de RTOS à l'intérieur des de threads matériels simulés pour exécuter des tâches d'application, avec diffèrents contraintes et des priorités. Un ensemble d'APIS HDS (HDS pour Hardware Dependent Software) y compris la création des tâches, IPC (IPC pour Inter-Process Communication) et services de sémaphores sont mises en oeuvre pour s'adapter aux exigences de tâches d'application, comme montre le Figure 1.4.

Malheureusement, ces modèles de système d'exploitation ne sont pas suffisamment détaillés car tous les appels de la bibliothèque C (entre autres), y compris les fonctions de gestion de la mémoire, sont hors du contrôle du modèle de système d'exploitation. Cette limitation rend le développement des pilotes des périphériques impossible en utilisants ces modèles. De même, ces modèles nécessitent la réécriture du logiciel d'application, ils empêchent effectivement l'utilisation du code "legacy".

Figure 1.4: Encapsulation du logiciel avec un système d'exploitation abstrait ou réal

Pour améliorer le réalisme de l'exécution du logiciel, certains travaux ont proposé d'utiliser un RTOS réel au lieu d'un modèle de systèmes d'exploitation abstrait, comme montré dans la Figure 1.4(b). La pile logicielle est toujours encapsulée dans les modèles de matériel, mais le système d'exploitation est le même que celui de la plate-forme réelle. Celui donne certains avantages, par exemple les fils logiciels sont ordonnancés par le RTOS réel, fournissant une modélisation réaliste des propriétés des logiciels temps-réel. De même, ces systèmes fournissent des moyens faciles pour l'exploration de l'architecture comme ils prennent en charge différents niveaux d'abstraction et permettent la modification des types de composants du matériel au logiciel et vice versa. Enfin, ces modèles permettent l'exécution et la validation d'une certaine quantité de logiciel en utilisant la simulation native.

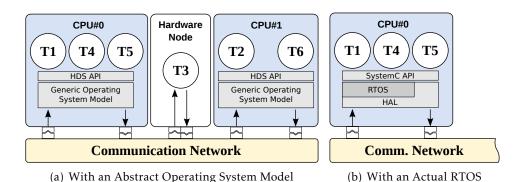

### 1.2.1 Interfaces Matériel Logiciel

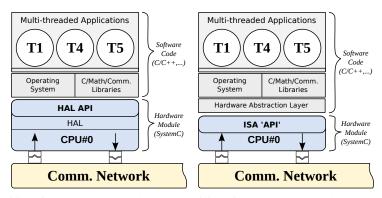

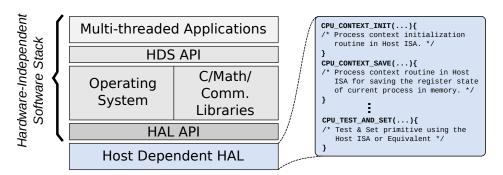

L'abstraction est définie comme un processus de simplification où seules les détails essentiels d'une entité complexe sont maintenus, pour un objectif spécifique. La notion d'abstraction peut être appliquée au logiciel, ainsi que des composants de matériel d'un système MPSoC donné. Une interface matérielle / logicielle sert comme une machine virtuelle, où elle exécute des commandes, par exemple, des instructions, des fonctions, etc, depuis le logiciel et interagit correctement avec la plate-forme matérielle. Des nombreuses interfaces matérielles / logicielles sont possibles dans des environnements de simulation MPSoC [BYJ04, SGP08, GGP08]. Nous nous focalisons sur le niveau TLM pour les composants matériels et comparons diffèrents niveaux d'abstraction du logiciel dans les plates-formes TA (TA pour Transaction Accurate) ainsi que leurs interfaces c'est-à-dire HDS ①, HAL ② et ISA ③, comme presenté dans la Figure 1.5.

Les couches du logiciel bénéficent du fait que la plate-forme matérielle peut fournir une véritable API pour interagir avec le monde du logiciel. Cette API définit le niveau de l'interface et est généralement mis en oeuvre à l'intérieur des modèles de matériel en utilisant un langage de programmation de logiciels. Cette interface d'API rend les couches logicielles

Figure 1.5: Niveaux d'abstraction matérielle et couches d'interface du logiciel

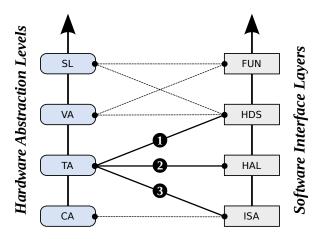

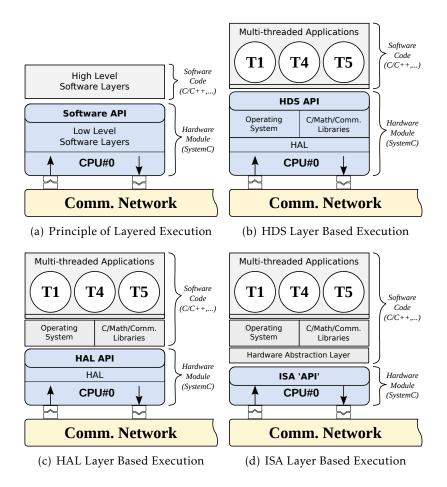

(a) Principe d'exécution en couche (b) Exécution sur la couche d'HDS

(c) Exécution sur la couche d'HAL (d) Exécution sur la couche d'ISA

Figure 1.6: L'exécution en couches du logiciel à différents niveaux de l'interface

supérieures complètement indépendants des modèles matériels inférieurs, car ils peuvent être compilés et exécutés sur l'interface fournie. La Figure 1.6(a) montre le principe de ces modèles d'exécution.

Les modèles de logiciels à couches les plus fréquemment utilisés [BBY+05, TRKA07, PJ07, CSC+09] implémentent l'API HDS pour des applications logicielles de haut niveau. Il s'agit d'une solution difficile car, pour construire des applications réalistes en utilisant cette interface de haut niveau, les modèles matériels doivent mettre en oeuvre de nombreuses APIs.

La quantité de logiciels qui pourraient être validée en utilisant ces interfaces est très limitée, ce qui reduit leur utilisation en pratique. Aucune de ces approches ne cible la création dynamique des tâches ou de migration des threads entre les processeurs, comme cela a lieu sur les plateformes SMP (SMP pour Symmetric Multi-Processor). La Figure 1.6(b) montre l'organisation des plateformes de simulation à la base d'interfaces HDS.

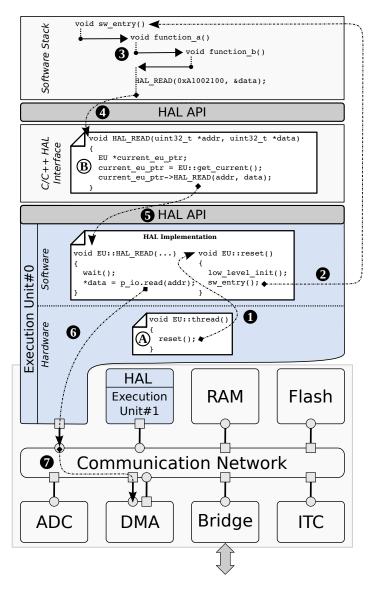

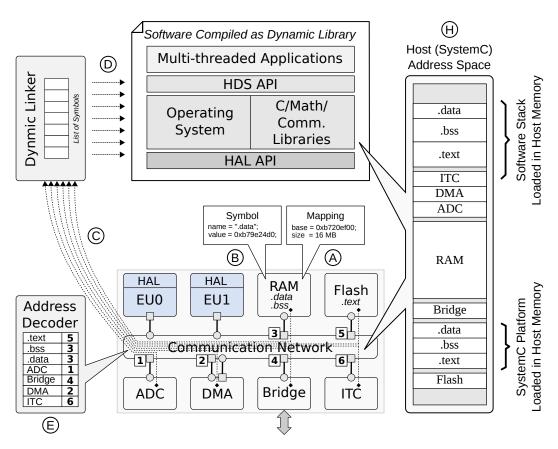

Quelques approches [YJ03, YBB+03, BYJ04, GGP08] reposent sur la définition d'une couche HAL fine qui doit être utilisé pour tous les accès liés au matériel. La couche HAL est mise en oeuvre dans une enveloppe qui comprend un thread matériel pour chaque processeur, appelé l'EU (EU pour Execution Unit). La pile logicielle entière au-dessus du HAL peut être compilée de manière indépendante, y compris le système d'exploitation et les bibliothèques standard et exécuté nativement. Chaque appel de fonction HAL est réalisé dans le contexte d'un EU en supposant que tous EUs appartenant de l'enveloppe partagent le code du système d'exploitation et des structures de données. Comme les fonctions de commutation de contexte appartienent à la couche d'HAL, la migration des threads de logiciel comme dans le SMP est pris en charge dans de telles plates-formes. La Figure 1.6(c) montre la structure des modèles basés sur l'interface d'HAL.

Les plates-formes de simulation natives qui sont basées sur ce qu'on appelle l'API ISA (ou ISA Hôte), comme montre la Figure 1.6(d), n'ont pas été discutées dans la littérature. Les plates-formes TA les plus communes qui assurent un niveau d'exécution à l'ISA du logiciel, cible l'usage des ISSes. La déficience principale de ces modèles ressort de l'utilisation soit des ISSes [LP02, HJ08] ou des solutions à base de DBT [GFP09] (DBT pour Dynamic Binary Translation), qui interprètent / traduisent les instructions au moment de l'exécution et entraînent des simulations plus lentes. L'ensemble des techniques de simulation natives discuté jusqu'ici souffre du problème des espaces d'adressages où le logiciel natif s'exécute dans l'espace d'adressage d'hôte et la plate-forme matérielle simule l'espace d'adressage de la cible. Ces différences rendent difficile la modelisation de certaines interactions entre le matériel et le logiciel, comme expliqué dans la section suivante.

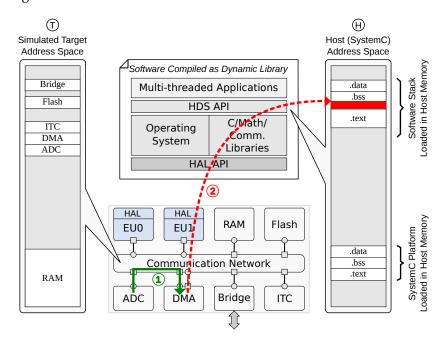

### 1.2.2 Les Espaces d'Adressage Cible et Hôte

Les plates-formes de simulation natives font face à deux types de dépendances, résultant principalement de la compilation native du logiciel. Les différences dans ISA des processeurs hôte et cible, ainsi que les détails spécifiques des modules matériel doivent être abordées au départ. Ces différences sont résolues en utilisant explicitement l'API HAL pour toutes les interactions entre les composants logiciels et matériels, ce qui donne une pile logicielle indépendante du matériel, à l'exception de la mise en oeuvre de HAL. La deuxième source de dépendance se manifeste par les représentations de la mémoire dans les composants matériels et logiciels. Pour être précis, deux espaces d'adressage différents et parfois contradictoires doivent être considérés, l'espace d'adressage cible (①) et hôte (⑪), comme montré dans la Figure 1.7.

- ① La plate-forme matérielle, compilé sur la machine hôte, simule les adresses cibles qui sont connues au moment de la compilation, c'est-à-dire le mappage des adresses dans les composants matériels qui ont été définis à l'avance par le concepteur du système et les décodeurs d'adresse de la plateforme utilisent ces plages d'adresses pour la communication entre les modèles de matériel.

- (H) La pile logicielle est compilé pour la machine hôte et toutes les références à la mémoire

sont inconnues au moment de la compilation. Les adresses du logiciel sont connues à l'exécution lorsque la bibliothèque représentant le logiciel est effectivement chargé dans la mémoire de l'hôte. En général c'est le processus SystemC qui charge la bibliothèque et fournit le contexte d'exécution.

Le problème des espaces d'adressage cible et l'hôte n'apparaît pas dans les plates-formes de simulation basées sur l'ISS, où à la fois des composants matériels et logiciels voient le même espace d'adressage, c'est-à-dire l'espace d'adressage cible. Ces différences dans les espaces d'adressage ne permettent pas de modéliser certaines interactions entre les composants matériels et logiciels.

Figure 1.7: Représentations de la mémoire cible et hôte (Adapté de [Ger09])

Deux principales classes de solutions ont été proposées pour résoudre ce problème, le remappage des adresses et l'unification des espaces d'adressages.

### 1.2.2.1 Les Techniques de Remappage des Adresses

Des techniques simples de remappage effectuent la conversion d'adresses entre l'espace cible et l'espace d'adressage du processus de simulation par l'utilisation de primitives spécifiques pour les entrées / sorties. Cela ne résout pas le problème des accès externes vers des buffers alloués nativement. Les stratégies de remappage plus complexes reposent sur le fait qu'une exception du système d'exploitation de l'hôte sera soulevée lors d'un accès à une mauvais adresse virtuelle.

Le principe est de marquer comme non valides (invalid) toutes les pages mémoires visibles par les composants de la plateforme, en utilisant le système d'exploitation hôte. Tout les accès à ces pages déclenchent une exception que le processus de simulation peut intercepter et gérer. Il peut y avoir des problèmes de performance, si de nombreuses exceptions sont levées, et les aspects techniques de manipulation des chevauchements entre les deux espaces de la mémoire reste un problème. Par exemple, les adresses mémoire au delà de 3 Go

(0xC000000) dans l'architecture x86 sont réservées pour le code du noyau Linux. La Figure 1.8 met en évidence le principe général des techniques de remappage des adresses.

Figure 1.8: Modification de la mémoire cible pour remmapage des adresses

### 1.2.2.2 Représentation de la Mémoire Uniforme et Edition de Liens Dynamiques

L'unification repose sur l'utilisation d'un mappage de mémoire unique pour le logiciel, et les composants matériels de l'environnement de simulation natifs. Le mappage du processus de simulation est sélectionné à cet effet comme il est également utilisé par la pile logicielle de simulation. L'unification nécessite de modifier la plate-forme matérielle de sorte que chaque composant exporte un ensemble de symboles obligatoires qui doivent être résolus au moment de la liaison pour effectuer un remappage à faible coût. Ces plates-formes requièrent également des modifications du système d'exploitation, afin qu'il accède au matériel uniquement par le biais des appels de fonctions HAL et n'utilise jamais des adresses codées en dur. La Figure 1.9 représente le principe de ces techniques.

Les inconvénients comprennent la modification des modèles de simulation pour créer l'espace de mémoire unifié, l'ajout d'une étape de liaison spécifique visible à l'utilisateur, et le port du système d'exploitation sur la couche HAL natif. Afin de simuler la bibliothèque C complète, en particulier les fonctions de gestion de la mémoire, un espace d'adressage bien séparés doit être fourni au système d'exploitation s'exécutant de façon native.

# 1.3 Virtualisation Assistée par le Matériel

La virtualisation des ressources informatiques physiques est un concept bien connu [Gol74, Cre81] et fournit des moyens pour le partage de ces ressources pour améliorer l'utilisation du système. Il est similaire à l'abstraction, mais les détails des ressources sous-jacentes ne sont

Figure 1.9: Représentation uniforme de la mémoire dans l'espace d'adressage de machine hôte

pas nécessairement cachés pour le logiciel, car il traite de la création de structures logiques qui fonctionnent comme la machine physique réelle.

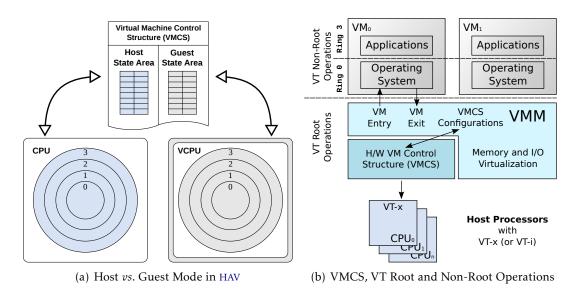

Dans un système non virtualisé, un seul système d'exploitation contrôle des ressources matérielles alors que dans un environnement virtualisé une nouvelle couche logicielle est introduite, connu sous le nom VMM (VMM pour Virtual Machine Monitor) ou hyperviseur, qui contrôle et arbitre les accès aux ressources de la plateforme. Cela permet l'utilisation de plusieurs systèmes d'exploitation sur une seule machine matérielle, communément connus en tant qu'invités de la VMM. La VMM présente un ensemble d'interfaces virtuelle qui constituent une machine virtuelle à chaque système d'exploitation invité, en leur faisant croire qu'ils ont un contrôle total sur la machine "physique". La terme hôte est couramment utilisé pour désigner le contexte d'exécution de VMM ou le système d'exploitation hôte.

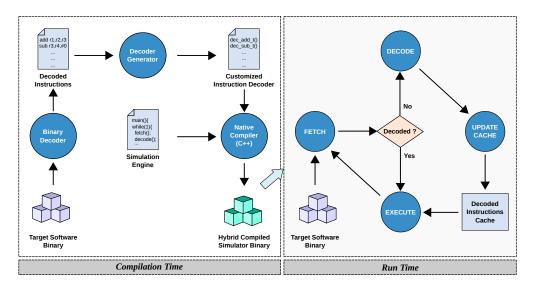

Cette section présente la contribution principale de cet thèse et presente l'utilisation du HAV dans le cadre d'environnements de simulation natifs événementiels pour la modélisation des architectures MPSoC. La technologie d'HAV fournit du matériel dédié à la virtualization et prend en charge les fonctionnalités clés suivantes:

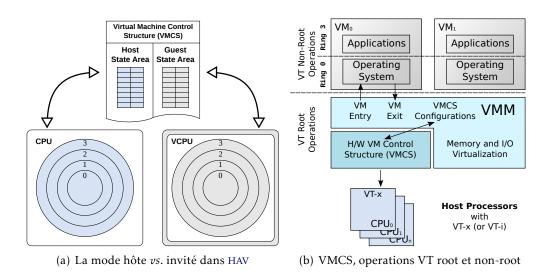

- ❖ Nouveau mode de fonctionnement invité: Ce mode offre un nouveau contexte d'exécution de la machine hôte dans lequel l'espace d'adressage peut être entièrement adapté. Le logiciel invité s'exécute en mode de fonctionnement non-root alors que le logiciel hôte et VMM s'exécutent en mode de fonctionnement root. La Figure 1.10(a) montre les modes de fonctionnement invité et hôte.

- ❖ Commutation de contexte basée sur le matériel: Une prise en charge matérielle a été introduite pour la commutation atomique entre les modes hôte et invité et vice-versa, de manière complète et efficace. Le matériel commute les registres de contrôle, les registres de segments et le pointeur d'instruction de telle sorte que la commutation des espaces d'adressage et de transfert de contrôle sont effectué de façon atomique. La

Figure 1.10(b) montre les transitions de VM Entry et VM Exit entre les modes hôte et invités.

\* Rapport de changement de mode invité à hôte: Chaque fois que le logiciel invité quitte le mode invité, il rend compte du motif de la sortie à la VMM, qui utilise cette information pour prendre une action correspondant.

Figure 1.10: Modes hôte et invité dans HAV (Les processeurs Intel)

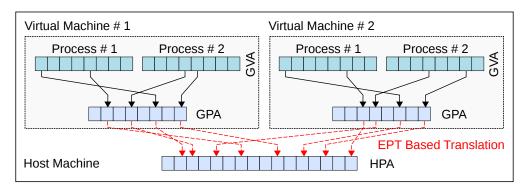

Chaque transition VMX entre l'hôte et l'invité peut commuter des espaces d'adressage. Cette fonction permet au logiciel invité d'utiliser son espace d'adressage complet, qui peut être différent de celui de l'hôte et de la VMM. L'espace d'adressage invité fait partie de l'espace d'adressage utilisateur sur la machine hôte, qui définit des traductions des adresses physiques de l'invité vers les adresses virtuelles de l'hôte. La VMM fournit les traductions d'adresses suivantes:

- ❖ La traduction de GPA (GPA pour Guest Physical Address) vers HPA (HPA pour Host Physical Address) quand la pagination est désactivée dans mode invité et le logiciel utilise des adresses physiques.

- Les traductions de GVA (GVA pour Guest Virtual Address) à GPA et à HPA quand la pagination est activée en mode invité.

- ❖ Les traductions NGVA (NGVA pour Nested Guest Virtual Address) à NGPA (NGPA pour Nested Guest Physical Address) à GPA et à HPA quand l'invité lance son propre invité, et la pagination est activée à la fois dans l'invité et l'invité emboîté.

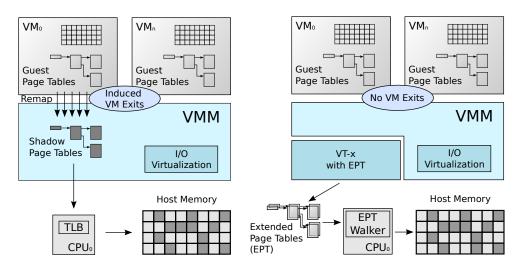

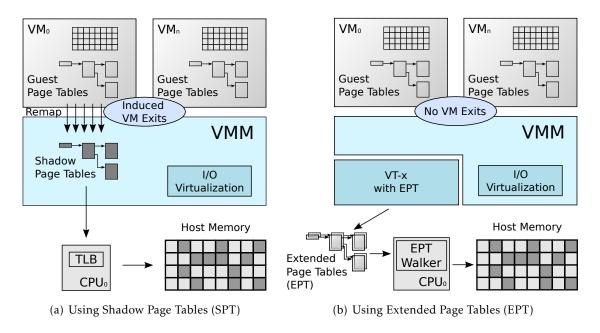

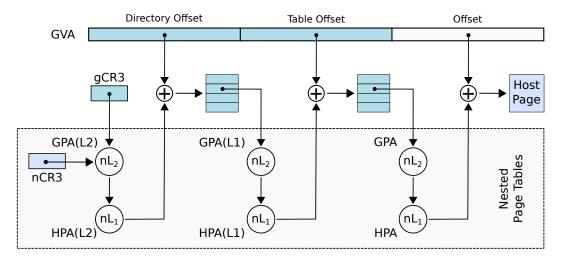

Les traductions précitées sont fournies en utilisant soit les SPT (SPT pour Shadow Page Tables) ou en exploitant le support matériel de pagination à deux dimensions appelé EPT (EPT pour Extended Page Tables) ou RVI (RVI pour Rapid Virtualization Indexing) par Intel et AMD, respectivement. En essence, la VMM est responsable de l'exposition d'une MMU (MMU pour Memory Management Unit) hôte au logiciel invité, lors de la traduction des

(a) Using Shadow Page Tables (SPT) / (b) Using Extended Page Tables / Utilisant Extended Utiliser Shadow Page Tableaux Page Tables

Figure 1.11: Support pour la virtualisation de la mémoire dans HAV

adresses virtuelles ou physiques invitées en adresses physiques de l'hôte, en utilisant l'une de ces technologies.

La virtualisation de la mémoire en utilisant SPT est fourni par la VMM basé sur HAV par d'interception des toutes les opérations de pagination du logiciel invité, y compris les défauts de page, l'invalidations des pages et l'accès aux registres de contrôle émulés des invités (CR0, CR2, CR3 et CR4). Essentiellement, toutes les tentatives du logiciel invité d'accéder au matériel de traduction d'adresse sont trappées par la VMM et émulées.

Lorsque le support de pagination à deux dimensions est activé dans l'HAV, les adresses physiques employées dans le mode de fonctionnement non-root *i.e.* invité, sont converties en parcourant un ensemble de structures de pagination EPT. Ces structures sont mises en oeuvre dans le matériel, et un composant matériel *i.e.* EPT Page Walker traduit les GPAs à HPAs finaux qui sont utilisés pour accéder à la mémoire de l'hôte. Les Figure 1.11(a) et Figure 1.11(b) montrent les principes génériques des pages shadow et des tables de pages étendues.

# 1.4 Simulation Native à l'Aide de la Virtualisation Assistée par le Matériel

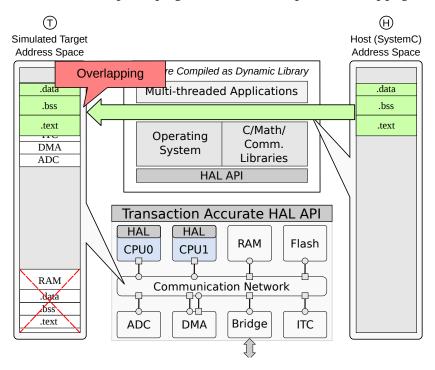

Nous résoudrons le problème des espaces d'adressage cible et hôte dans la simulation native en introduisant une couche de traduction d'adresses transparente et basée sur le support matériel fourni par la technologie d'HAV. Cette technique de traduction est différente des ISSes basés sur DBT (DBT pour Dynamic Binary Translation), qui invoquent des fonctions de traduction d'adresses à base de logiciel pour chaque accès mémoire, dégradant ainsi la performance de simulation. Cet section donne un aperçu de la façon dont on résout le problème des espaces d'adressage en intégrant une VMM dans un environnement de simulation basée sur les événements.

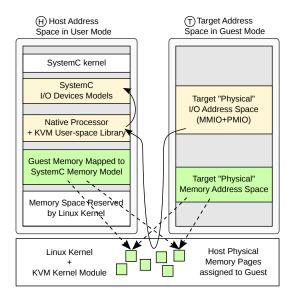

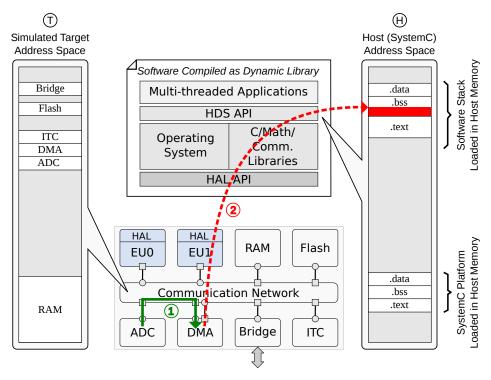

Concrètement, nous intégrons l'open source KVM basé sur Linux dans l'environnement

SystemC. Notre contribution n'est pas de créer une nouvelle machine virtuelle fondamentale basé sur HAV, mais d'utiliser un existant et de l'intégrer dans un environnement de simulation SoC événementiels pour résoudre le problème des espaces d'adressage décrit dans la section Section 1.2.2.

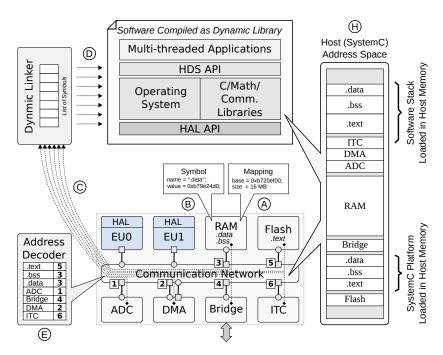

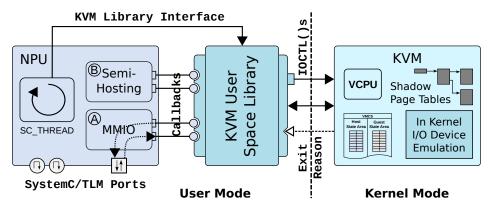

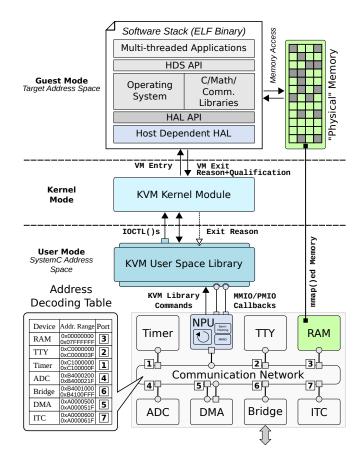

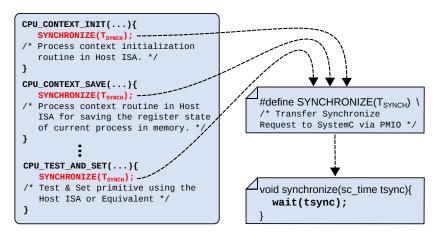

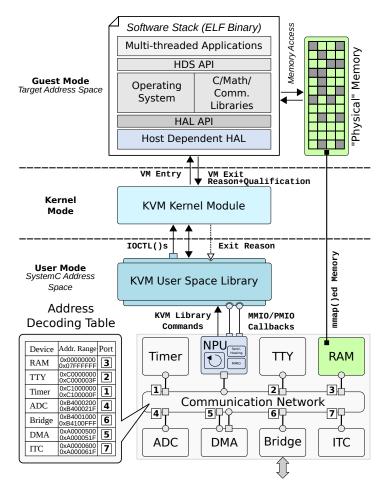

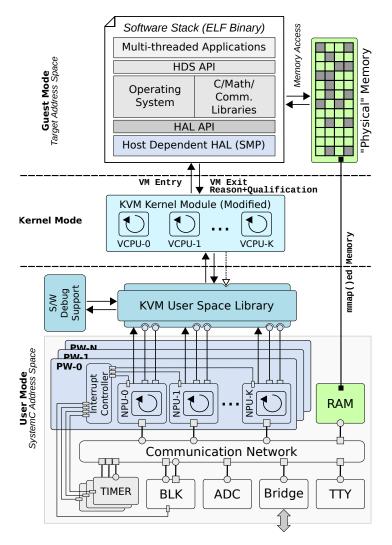

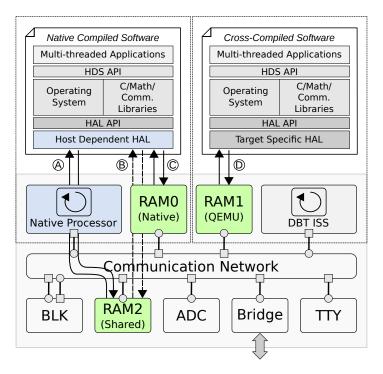

Les NPU (NPU pour Native Processing Units) sont basées sur le concept de module SystemC et constituent la base de notre framework de simulation. Chaque NPU modélise un processeur natif et fournit l'interface entre les composants SystemC matériels et KVM. Pour l'interfaçage avec KVM, il utilise la bibliothèque de l'espace utilisateur KVM, qui exporte les fonctions clés pour la manipulation de la machine virtuelle. Le module de noyau KVM expose l'ISA du processeur hôte à la pile logicielle, c'est-à-dire l'ISA x86 dans notre cas. La pile logiciel, y compris le système d'exploitation embarqué, la couche d'HAL et l'application est compilée au format binaire hôte et exécutée dans une machine virtuelle.

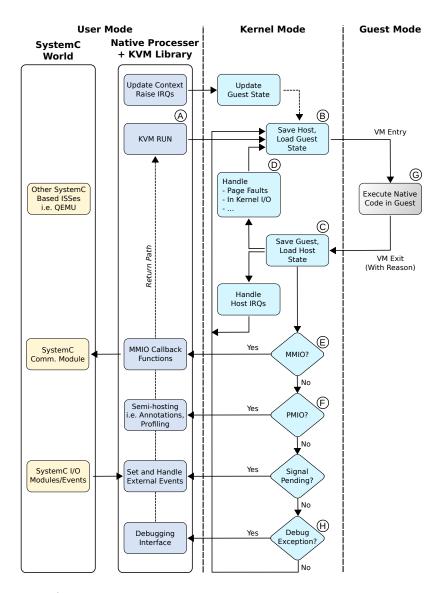

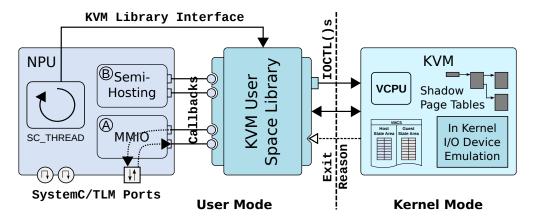

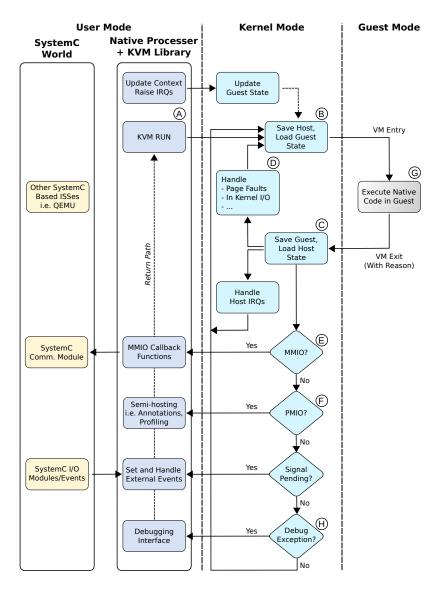

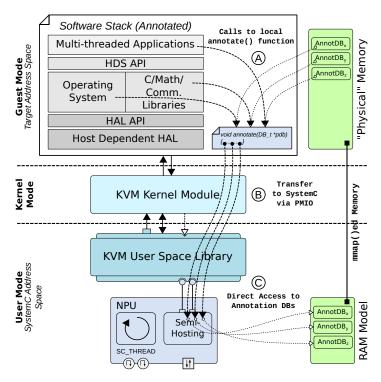

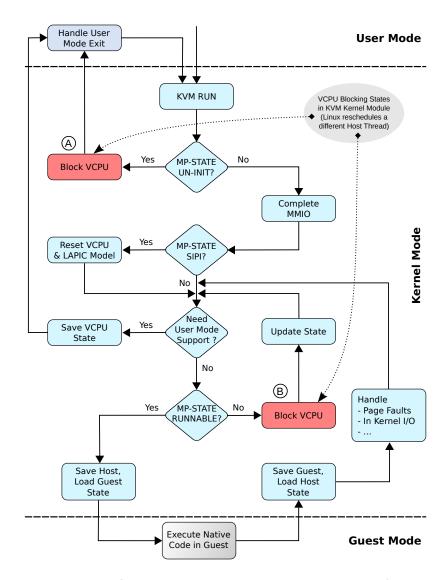

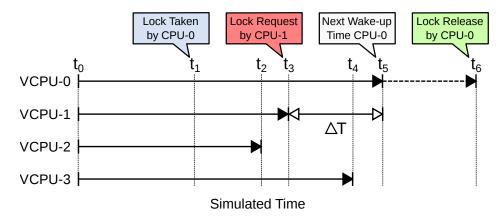

Chaque processeur natif comprend un fil SystemC pour modéliser le processeur et les composants pour interagir avec la bibliothèque de l'espace utilisateur KVM, tels que les fonctions de rappel et de fonctionnalités pour exploiter l'interface de la bibliothèque de KVM. Les plate-formes de simulation natives demandent certains services à KVM, tels que la création d'une nouvelle machine virtuelle comprenant un ou plusieurs VCPU (VCPU pour Virtual CPU), l'initialisation de l'espace mémoire de l'invité et le lancement d'exécution du logiciel. Chacune de ces demandes est envoyée au module KVM en utilisant l'interface ioctl fournies par le noyau Linux. Chaque ioctl retourne une valeur pour indiquer le succès ou l'échec du service demandé. La Figure 1.12 fournit une vue de haut niveau des unités de traitement natifs et leur relation à KVM et la Figure 1.13 donne le flux global d'exécution de la plate-forme de simulation natifs proposée.

**Figure 1.12:** Les unités de traitement natifs (NPU) et leur interfaces avec KVM en utilisant la bibliothèque utilisateur

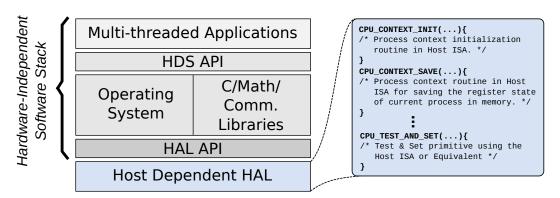

Les plates-formes de simulation natives font face à deux types de dépendances, résultant principalement de la compilation native du logiciel. Les différences dans l'ISA des processeurs hôtes et cible, ainsi que les détails spécifiques de modules matériel doivent être abordés au départ. Ces différences sont résolues en utilisant explicitement l'API HAL pour toutes les interactions entre les composants matériels et le logiciel. Il en résulte une pile logicielle indépendante du matériel, à l'exception de la mise en oeuvre de la couche HAL. En conséquence, notre approche est similaire à la paravirtualisation. La couche d'HAL fournit une interface qui est spécifique au système d'exploitation s'exécutant sur le dessus de celui-ci ainsi que met en oeuvre l'interface HAL en fonction de la plate-forme sous-jacente. Nous avons mis en place notre approche basée sur HAV pour le DNA-OS [GP09]. La deuxième

**Figure 1.13:** Le flux d'exécution dans la simulation native basée sur la virtualisation à l'assistance matérielle

source de dépendances se manifeste par les représentations de la mémoire dans le matériel et les composants logiciels, comme déjà discuté dans la Section 1.2.2. Comme nous basons notre solution sur la technologie d'HAV, qui exporte l'ISA spécifique de l'hôte à ses invités, la couche de d'HAL est implémentée en utilisant l'ISA hôte (x86 dans notre cas).

En utilisant la technologie d'HAV, toutes les interactions entre les composants logiciels et matériels ont lieu au niveau ISA hôte, comme cela a été discuté dans Section 1.2.1 (Figure 1.6(d)). La couche d'HAL fournit les APIs pour gérer les contextes de processus, les primitives de synchronisation, endianness, la mémoire et les accès entrée/sortié et la gestion des interruptions. La Figure 1.14 indique le fait que l'ensemble des couches logicielles supérieures d'HAL sont indépendantes de la plate-forme sous-jacente, et que l'HAL est spécifique à l'architecture de la machine hôte.

Une fois l'exploration initiale de espace de conception terminée pour un SoC donné, la

Figure 1.14: Couche d'abstraction matérielle dépendant de la machine hôte

même pile logicielle peut être re-compilée pour l'architecture cible sauf la couche HAL et remplacée par une mise en oeuvre spécifique à la cible. Cela permet de valider une certaine quantité de logiciel pour l'architecture cible, y compris le système d'exploitation et toutes les couches logicielles au-dessus. Comme l'initialisation du contexte et des fonctions de commutation sont inclus dans la couche d'HAL, la modélisation de la création de tâches dynamique et de migration de threads dans les architectures SMP est possible - une condition essentielle dans les systèmes sur puce récents.

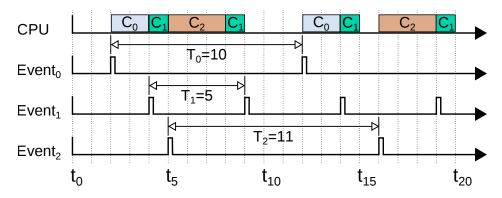

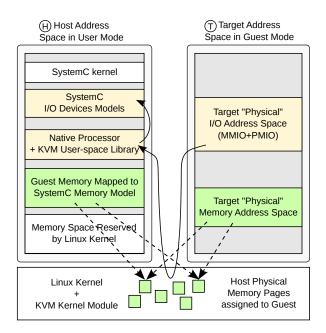

La Figure 1.15 est empruntée de [KKL+07] et modifiée pour se concentrer sur la façon dont à la fois la mémoire et entrées/sorties du système cible sont mappées dans l'espace d'adressage de l'utilisateur, ce qui les rend accessibles au modèles de mémoire SystemC. Pour la pile logicielle simulée qui ne connaît que l'espace d'adressage de la cible, les adresses mémoire "physiques" utilisées par le binaire cible sont les adresses virtuelles mappées par le module KVM du noyau Linux à une série de pages réelles de mémoire physique de la plateforme hôte. Tous les modèles SystemC peuvent accéder à ces pages physiques en utilisant un autre mappage de la MMU qui est également maintenu par le module KVM. L'accès à ces pages est entièrement transparent, c'est-à-dire qu'une application qui s'exécute en mode invité restera en mode invité. Cela conduit à une partage optimale des données bi-directionnelles entre les binaires cible et de l'environnement SystemC.

En outre les accès mémoire, le logiciel embarqué cible doit également accéder aux périphériques d'entrée/sortie. Le MMIO (MMIO pour Memory-Mapped I/O) et le PMIO (PMIO pour Port-Mapped I/O) sont les deux méthodes bien connues qu'un processeur peut utiliser pour effectuer des accès entrées/sorties. Comme l'architecture x86 supporte les deux méthodes, le logiciel cible simulé peut accéder aux périphériques d'entrée/sortie avec ces deux méthodes. Cependant, puisque la plupart des processeurs embarqués ne supportent que MMIO, comme ARM par exemple, nous supposons que les composants matériels sont accessibles par MMIO seulement.

Par opposition à l'accès mémoire, le MMIO ne peut pas être mappé et être directement accessible car le comportement de lecture / écriture d'accès à un registre matériel est normalement différent de celui de la mémoire. Un accès registre du matériel peut déclencher certaines actions du composant matériel cible au lieu de simplement lire / écrire une valeur de données. Comme tous les périphériques d'entrée / sortie d'un MPSoC sont réellement modélisés au sein de SystemC, à la place du vrai matériel, SystemC doit obtenir le contrôle et le transmettre à des composants matériels, chaque fois qu'une instruction de chargement ou stockage est exécuté. Ce processus peut se réaliser naturellement sur une plate-forme de virtualisation basée sur KVM.

Figure 1.15: Accès mémoire et d'entrées / sorties

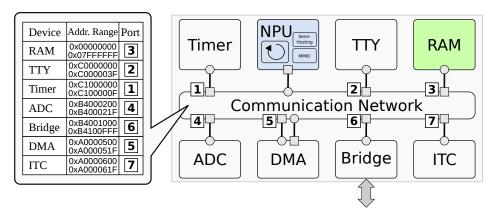

Lorsque le logiciel cible simulé effectue l'accès MMIO d'une adresse qui n'appartient pas à l'espace de mémoire, une exception de page est lancée par la MMU du matériel qui impose au processeur de quitter le mode invité et permet au pilote KVM de gèrer l'exception. Le pilote transfère l'accès MMIO à la bibliothèque KVM dans l'espace utilisateur, qui transmet cet accès au processeur natif (NPU), en utilisant les fonctions de rappel installées lors de l'initialisation, comme le montre la Figure 1.13 ①. A l'aide de l'API KVM, le processeur natif peut obtenir les adresses d'entrée/sortie cible et lancer les opérations d'accès SystemC normales en utilisant les ports TLM et les composants de communication, comme le montre la Figure 1.12 ②.

Comme le logiciel invité utilise des adresses d'entrée/sortie cibles qui sont exactement les mêmes que celle simulées par la plateforme SystemC, les composants de communication peuvent utiliser des tables de décodage d'adresses attribuées de manière statique. Cet aspect particulier nous donne la liberté d'utiliser des modèles de matériel non modifiés, par opposition à la technique proposée dans [Ger09, GHP09], où les composants matériels doivent être modifiés pour supporter la liaison dynamique, comme montre la Figure 1.9. Grace à l'attribution des adresses statiques dans le décodeur de la plate-forme, la pile logicielle compilé statiquement peut être utilisée, et ne nécessite pas de support de liaison des composants de la plateforme à l'execution.

La solution globale se compose d'une couche HAL dependant de machine hôte, le module KVM de noyau Linux, la bibliothèque KVM en espace utilisateur et les modèles de processeurs natifs basés sur SystemC, comme le montre la Figure 1.16. Deux points importants doivent être revus; tout d'abord, l'espace d'adressage de la mémoire visible par le logiciel invité est le même que celui mappé par le modèle de mémoire SystemC et il est accessible de façon transparente au logiciel invité. En second lieu, les accès d'entrée/sortie initiés par le logiciel embarqué passent par le module KVM du noyau et une bibliothèque dans l'espace utilisateur pour atteindre le modèle de processeur natif, ce qui lance les transactions réelles de lecture/écriture sur le réseau de communication de la plate-forme matérielle.

Figure 1.16: Processeur natives, bibliothèque KVM, KVM et la pile logicielle invité

#### 1.5 Conclusion

Ce chapitre a présenté la contribution principale de cette thèse. Nous avons démontré que le problème des espaces d'adressage introduit par les techniques natives peut être résolu en utilisant la technologie HAV. Les éléments clés de la solution proposée sont les NPUs, une couche d'HAL dépendant d'hôte et des accès entrée / sortie à l'aide de MMIO fournie par KVM.

La solution proposée résout efficacement le problème des espaces d'adressage cible et hôte. Elle permet d'utiliser le matériel et des composants logiciels non modifiés. En outre, elle permet de valider une certain quantité de logiciel au dessus de la couche d'HAL et n'impose pas de contraintes de codage du logiciel. La solution proposée est évolutive et peut être utilisé pour la simulation de plusieurs éléments de traitement, et en même temps flexible pour les modèles de plate-formes de simulation y compris de plate-formes hybrides (avec d'autres technologies d'exécution du logiciel) et des modèles de mémoire partagée. La prise en charge des techniques d'instrumentation automatique est également possible dans la technique proposée.

Certaines limitations comprennent l'utilisation de la couche d'HAL et la nécessité pour toutes les interactions de logiciel/matériel de passer à travers de cette couche. Les opérations d'entrée/sortie nécessitent la commutation de mode invité à mode hôte, dégradant ainsi la performance des applications intensives en entrée/sortie. La prise en charge de code auto-modifiant n'est pas disponible dans notre solution, comme la pile logicielle est compilée

statiquement et aucune aide pour la traduction à l'exécution est disponible. La précision de la simulation du point de vue de l'estimation de la performance est très dépendante de l'exactitude de l'annotation; ainsi l'estimation de la performance des architectures complexes est difficile en utilisant des techniques d'annotation traditionnelles. Bien que la solution proposée présente certaines limitations, l'intérêt de cette approche est indiscutable.

# Part II Unabridged English Version

A dream doesn't become reality through magic; it takes sweat, determination and hard work.

Colin Powell

## 2 Introduction

The current state-of-the-art in *Very-Large-Scale Integration* (VLSI) technology allows the fabrication of several billion transistors on a single chip. Designing and integrating hardware with such a huge number of transistors is very difficult. One simple solution for the hardware designers, is to put many relatively simple processors on a single chip rather than designing a complex uniprocessor machine. Moreover, the scalability of mono-processors is constrained by the power dissipation factors, as one cannot simply increase the clock speed to gain performance benefits.

High-Performance Computing field is going towards multi-core or *Chip Multiprocessor* (CMP) with dozens of high performance *General Purpose Processors* (GPPs). In the integrated systems field, power and yield issues require the use of simpler architectures. These include processors that feature a higher MIPS to Watt ratio, as well as specialized hardware IPs. This trend continues towards more regular and homogeneous structures but still including specific hardware and possibly instruction set extensions in processing elements. These multiprocessors are specific to a design class known as *Multi-Processor System-on-Chip* (MPSoC). Many industrial sectors, such as telecommunications, aerospace, automotive, military and consumer electronics are currently using such systems.

#### 2.1 The Hardware/Software Co-Design Challenge

The MPSoC design complexity is increasing due to the number and type of processing elements found in such systems. According to ITRS, as many as 6000 processors are expected on a single SoC by the end of year 2026, as shown in Figure 2.1. Designing and verifying a hardware solution with such high number of processing elements, with even more complex software including hundreds of applications to exploit it, is an enormous challenge.

Similarly, time-to-market is of prime importance in consumer electronics life-cycle, for product manufacturers to remain competitive and be successful in meeting market demands. The ever longer design and fabrication delays of MPSoC systems undermine this goal, as software development depends on hardware availability. Virtual platforms *i.e.* simulation

models provide a feasible alternative, as software development can start early and in parallel with hardware design. Moreover, software teams need simulation platforms, even if the hardware is available, as early prototypes are usually very expensive.

Figure 2.1: SoC Consumer Portable Design Complexity Trends [ITR]