# High Level Design and Control of Adaptive Multiprocessor Systems-on-Chip

Xin An

# ▶ To cite this version:

Xin An. High Level Design and Control of Adaptive Multiprocessor Systems-on-Chip. Embedded Systems. Université de Grenoble, 2013. English. NNT: . tel-00904884

# HAL Id: tel-00904884 https://theses.hal.science/tel-00904884

Submitted on 15 Nov 2013  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# THÈSE

Pour obtenir le grade de

# **DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE** Spécialité : Informatique

Arrêté ministériel : 7 août 2006

Présentée par

Xin An

Thèse dirigée par **Eric Rutten** et codirigée par **Abdoulaye Gamatié**

préparée au sein INRIA-Grenoble et de École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# High Level Design and Control of Adaptive Multiprocessor Systems-on-Chip

Thèse soutenue publiquement le **16 octobre 2013**, devant le jury composé de :

**Mr Jean-Marc Faure** LURPA, ENS Cachan, Professeur, Rapporteur Mr Frédéric Mallet U. Nice Sophia-Antipolis, Maître de Conférences (HdR), Rapporteur **Mme Dominique Borrione** TIMA, Grenoble, Professeur, Examinatrice Mr Jean-Philippe Diguet CNRS Lab-Sticc, Lorient, Directeur de Recherche, Examinateur Mr Hervé Marchand INRIA, Rennes, Chargé de Recherche, Examinateur Mr Jean-François Méhaut UJF-CEA/LIG, Grenoble, Professeur, Examinateur Mr Eric Rutten INRIA, Grenoble, Chargé de Recherche, Directeur de thèse Mr Abdoulaye Gamatié CNRS LIRMM, Montpellier, Chargé de Recherche, Co-Directeur de thèse

## Abstract

The design of modern embedded systems is getting more and more complex, as more functionality is integrated into these systems. At the same time, in order to meet the computational requirements while keeping a low level power consumption, MPSoCs have emerged as the main solutions for such embedded systems. Furthermore, embedded systems are becoming more and more adaptive, as the adaptivity can bring a number of benefits, such as software flexibility and energy efficiency. This thesis targets the safe design of such adaptive MPSoCs.

First, each system configuration must be analyzed concerning its functional and nonfunctional properties. We present an abstract design and analysis framework, which allows for fast and cost-effective implementation decisions. This framework is intended as an intermediate reasoning support for system level software/hardware co-design environments. It can prune the design space at its largest, and identify candidate design solutions in a fast and efficient way. In the framework, we use an abstract clock-based encoding to model system behaviors. Different mapping and scheduling scenarios of applications on MPSoCs are analyzed via clock traces representing system simulations. Among properties of interest are functional behavioral correctness, temporal performance and energy consumption.

Second, the reconfiguration management of adaptive MPSoCs must be addressed. We are specially interested in MPSoCs implemented on reconfigurable hardware architectures (i.e., FPGA fabrics), which provide a good flexibility and computational efficiency for adaptive MPSoCs. We propose a general design framework based on the discrete controller synthesis (DCS) technique to address this issue. The main advantage of this technique is that it allows the automatic controller synthesis w.r.t. a given specification of control objectives. In the framework, the system reconfiguration behavior is modeled in terms of synchronous parallel automata. The reconfiguration management computation problem w.r.t. multiple objectives regarding e.g., resource usages, performance and power consumption is encoded as a DCS problem. The existing BZR programming language and Sigali tool are employed to perform DCS and generate a controller that satisfies the system requirements.

Finally, we investigate two different ways of combining the two proposed design frameworks for adaptive MPSoCs. Firstly, they are combined to construct a complete design flow for adaptive MPSoCs. Secondly, they are combined to present how the designed runtime manager by the second framework can be integrated into the first framework so as to perform combined simulations and analysis of adaptive MPSoCs.

# Contents

| 1 | Intr | roduction                                            | 1               |

|---|------|------------------------------------------------------|-----------------|

|   | 1.1  | Trends in Embedded Systems                           | 1               |

|   | 1.2  | Problem Statement                                    | 2               |

|   | 1.3  | Contributions                                        | 3               |

|   | 1.4  | Thesis Overview                                      | 5               |

|   |      |                                                      | Ŭ               |

| Ι | Sta  | ate of the Art                                       | 7               |

| 2 | Mu   | ltiprocessor Systems-on-Chip (MPSoCs)                | 9               |

|   | 2.1  | General Presentation                                 | 9               |

|   |      | 2.1.1 Processing Elements                            | 10              |

|   |      | 2.1.2 Memory Architecture                            | 11              |

|   |      | 2.1.3 Interconnect                                   | 12              |

|   | 2.2  | MPSoC Design                                         | 13              |

|   |      | 2.2.1 A Design Flow Model                            | 13              |

|   |      | 2.2.2 Design Space Exploration                       | 15              |

|   |      | 2.2.3 A Survey of Existing Approaches                | 16              |

|   | 2.3  | Adaptivity of MPSoCs                                 | 19              |

|   |      | 2.3.1 Motivation for Adaptivity in MPSoCs            | 19              |

|   |      | 2.3.2 FPGAs as Implementation Platforms for MPSoCs   | 19              |

|   |      | 2.3.3 Adaptivity Management                          | 20              |

|   | 2.4  | Summary and Discussion                               | 23              |

| 9 | Ъ    | the Low many and The left and Department Southerne   | 25              |

| 3 |      | dels, Languages and Tools for Reactive Systems       | <b>25</b><br>26 |

|   | 3.1  | Data-Flow Based Modeling Formalisms                  |                 |

|   |      | 3.1.1 Kahn Process Network and Synchronous Data Flow | 26              |

|   |      | 3.1.2 Data-Flow Synchronous Languages                | 27              |

|   | 0.0  | 3.1.3 The UML Profile MARTE and CCSL Language        | 29              |

|   | 3.2  | Automata-Based Modeling Formalisms                   | 31              |

|   |      | 3.2.1 StateCharts                                    | 31              |

|   |      | 3.2.2 Automata-Based Synchronous Languages           | 31              |

|   |      | 3.2.3 Heptagon Language                              | 32              |

|   | _    | 3.2.4 Formal Definition of Automata                  | 33              |

|   | 3.3  | Discrete Controller Synthesis (DCS)                  | 35              |

|   |      | 3.3.1 General Presentation                           | 35              |

|   |      | 3.3.2 Control Objectives                             | 36              |

|   | 3.4  | BZR Synchronous Language and DCS                     | 37              |

|   | 3.5  | Some Approaches Applying Discrete Control            | 38              |

|   | 3.6  | Summary and Discussion                               | 38              |

| Π | С           | ontril                 | butions                                                      |  |  |  |  |  |

|---|-------------|------------------------|--------------------------------------------------------------|--|--|--|--|--|

| 4 | CL          | ASSY:                  | A High Level Design and Analysis Framework for MPSoCs        |  |  |  |  |  |

|   | 4.1         | Motiva                 | ation and Contribution                                       |  |  |  |  |  |

|   | 4.2         | High-l                 | Level Modeling of Adaptive MPSoCs                            |  |  |  |  |  |

|   | 4.3         | An Al                  | bstract Design Framework for Adaptive Systems                |  |  |  |  |  |

|   |             | 4.3.1                  | Application Behavior                                         |  |  |  |  |  |

|   |             | 4.3.2                  | Execution Platform Behavior                                  |  |  |  |  |  |

|   |             | 4.3.3                  | Application Mapping on Platforms                             |  |  |  |  |  |

|   | 4.4         | Sched                  | uling and Design Analysis                                    |  |  |  |  |  |

|   |             | 4.4.1                  | Clock Modeling of System Executions                          |  |  |  |  |  |

|   |             | 4.4.2                  | Admissible Scheduling of Applications                        |  |  |  |  |  |

|   |             | 4.4.3                  | Scheduling Algorithm                                         |  |  |  |  |  |

|   |             | 4.4.4                  | Performance Analysis                                         |  |  |  |  |  |

|   | 4.5         |                        | n Space Exploration                                          |  |  |  |  |  |

|   | 4.6         | Implei                 | mentation and Experiments                                    |  |  |  |  |  |

|   |             | 4.6.1                  | CLASSY Tool                                                  |  |  |  |  |  |

|   |             | 4.6.2                  | Experimental results                                         |  |  |  |  |  |

|   | 4.7         | Summ                   | ary and Discussion                                           |  |  |  |  |  |

| 5 | Dis         | crete (                | Control for Reconfiguration Management of Adaptive MPSoCs    |  |  |  |  |  |

|   | 5.1         | Motiva                 | ation and Contribution                                       |  |  |  |  |  |

|   | 5.2         | Adapt                  | tive MPSoCs Implemented on FPGAs                             |  |  |  |  |  |

|   |             | 5.2.1                  | Hardware Architecture                                        |  |  |  |  |  |

|   |             | 5.2.2                  | Application Software                                         |  |  |  |  |  |

|   |             | 5.2.3                  | Task Implementation                                          |  |  |  |  |  |

|   |             | 5.2.4                  | System Reconfiguration                                       |  |  |  |  |  |

|   |             | 5.2.5                  | System Objectives                                            |  |  |  |  |  |

|   |             | 5.2.6                  | High Level Modeling of Adaptive MPSoCs                       |  |  |  |  |  |

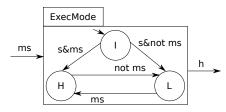

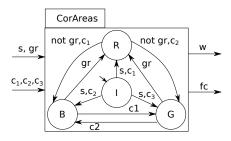

|   | 5.3         | Model                  | ling Reconfiguration Management Computation as a DCS Problem |  |  |  |  |  |

|   |             | 5.3.1                  | Architecture Behaviour                                       |  |  |  |  |  |

|   |             | 5.3.2                  | Application Behaviour                                        |  |  |  |  |  |

|   |             | 5.3.3                  | Task Execution Behaviour                                     |  |  |  |  |  |

|   |             | 5.3.4                  | Global System Behaviour Model                                |  |  |  |  |  |

|   |             | 5.3.5                  | System Objectives                                            |  |  |  |  |  |

|   | 5.4         | Auton                  | natic Manager Generation by Using BZR                        |  |  |  |  |  |

|   |             | 5.4.1                  | BZR Encoding of the System Model                             |  |  |  |  |  |

|   |             | 5.4.2                  | Enforcing Logical Control Objectives                         |  |  |  |  |  |

|   |             | 5.4.3                  | Enforcing Optimal Control Objectives                         |  |  |  |  |  |

|   |             | 5.4.4                  | Enforcing the Combined Logical and Optimal Objectives        |  |  |  |  |  |

|   | 5.5         | 5 Experimental Results |                                                              |  |  |  |  |  |

|   | 5.6         | Case S                 | Study                                                        |  |  |  |  |  |

|   |             | 5.6.1                  | Case Study Description                                       |  |  |  |  |  |

|   |             | 5.6.2                  | Controller Generation and Integration                        |  |  |  |  |  |

|   |             | 5.6.3                  | System Implementation                                        |  |  |  |  |  |

|   | 5.7         | Summ                   | nary and Discussion                                          |  |  |  |  |  |

| 6 |             | nbinin<br>'SoCs        | g Configuration and Reconfiguration Designs for Adaptive     |  |  |  |  |  |

|   | <b>6</b> .1 |                        | ation and Contribution                                       |  |  |  |  |  |

|   | 0.1         | 110010                 |                                                              |  |  |  |  |  |

|                                       | 6.2              | A Design Flow for Adaptive MPSoCs                                     | 96  |  |  |  |  |  |  |  |

|---------------------------------------|------------------|-----------------------------------------------------------------------|-----|--|--|--|--|--|--|--|

|                                       |                  | 6.2.1 The Design Flow                                                 | 96  |  |  |  |  |  |  |  |

|                                       |                  | 6.2.2 Case Study: Continuous Multimedia Player                        | 97  |  |  |  |  |  |  |  |

|                                       | 6.3              | CLASSY for the Design and Evaluation of Run-Time Managers             | 105 |  |  |  |  |  |  |  |

|                                       |                  | 6.3.1 An Illustrative Example                                         | 105 |  |  |  |  |  |  |  |

|                                       |                  | 6.3.2 Run-Time Manager Design                                         | 106 |  |  |  |  |  |  |  |

|                                       |                  | 6.3.3 Simulation and Analysis of the Designed Manager by using CLASSY | 108 |  |  |  |  |  |  |  |

|                                       | 6.4              | Summary and Discussion                                                | 111 |  |  |  |  |  |  |  |

|                                       |                  |                                                                       |     |  |  |  |  |  |  |  |

| 7                                     |                  | 113                                                                   |     |  |  |  |  |  |  |  |

|                                       | 7.1              | Conclusion                                                            |     |  |  |  |  |  |  |  |

|                                       | 7.2              | Perspectives                                                          |     |  |  |  |  |  |  |  |

| Li                                    | List of Figures  |                                                                       |     |  |  |  |  |  |  |  |

| Li                                    | List of Tables 1 |                                                                       |     |  |  |  |  |  |  |  |

| List of Tables 120<br>Bibliography 12 |                  |                                                                       |     |  |  |  |  |  |  |  |

|                                       |                  |                                                                       |     |  |  |  |  |  |  |  |

v

# CHAPTER 1 Introduction

#### Contents

| 1.1 | Trends in Embedded Systems | 1        |

|-----|----------------------------|----------|

| 1.2 | Problem Statement          | <b>2</b> |

| 1.3 | Contributions              | 3        |

| 1.4 | Thesis Overview            | 5        |

# 1.1 Trends in Embedded Systems

Embedded systems are specific-purpose computer systems combining software and hardware components. They are used almost in everything that runs on electricity in our daily life. Examples include consumer electronics, avionics, telecommunication, automotive electronics, etc. Some trends can be observed in emerging embedded systems.

- First, the functionality integrated into embedded systems is ever increasing. Mobile phones, for example, have evolved from a simple device that supports only telephone calls over radio links to the so-called smart phones (e.g., Apple iPhone, Samsung Galaxy) that offer a wide variety of other services such as text messaging, Internet accessing, music and video playing, camera, gaming and photography. Another example is the car entertainment system [Schor *et al.* 2012], which integrates many similar functions such as GPS, music playing, radio etc.

- Second, the high integration of functionality into embedded systems leads to a tremendous increase in the amounts of data being processed by the systems. A mobile phone, for example, can contain gigabytes of video, photo and music data files to process. The amount of manipulated data is expected to double every two years in the future in these domains [Byna & Sun 2011]. To be made useful, the data must be processed in real-time for the users. The execution platforms must thus provide the required computational power to do this. On the other hand, power/energy consumption minimization becomes more and more important as many of these devices are battery powered. Parallel execution platforms play a key role for providing these applications with the required computational power to achieve data-intensive processing under real-time and energy-efficient constraints. In order to obtain adequate execution performances, a state-of-the-art solution consists in integrating multiple cores or processors on a single chip, leading to as **multiprocessor systems-on-chip** (MPSoCs) [Wolf et al. 2008]. For example, instead of accelerating the clock frequency of each new processor generation, Intel [Borkar et al. 2005] has shifted to a strategy for which multiple cores or processors are integrated on a single chip. Another example is the STMicroelectronics Nomadik [Artieri et al. 2003], which contains an ARM926EJ as its host processor, and two programmable accelerators for video and audio processing respectively.

- Third, *adaptivity*, the ability of a system to adapt itself, is becoming increasingly desirable in embedded systems. This trend can be observed in the following three aspects.

- Embedded applications are becoming increasing adaptive. For example, a videosurveillance application for street observation needs to adapt its image analysis algorithms according to factors like the human activity (crowded place or not), luminosity (day or night) or the weather.

- Hardware components are becoming increasingly adaptive. An example is the FPGAs, which allow run-time reconfiguration to implement different functionalities. It provides a better trade-off of performance and flexibility compared to application specific integrated circuits (ASICs) and general purpose processors. Another example is the *Dynamic Voltage/Frequency Scaling (DVFS)* technique, which allows the dynamic adjustments of supply voltage and clock frequency for hardware like processors so as to reduce power/energy consumption. A third example is the *clock gated* mechanism which allows processors or parts of circuits to switch from active mode to sleep mode so as to save power/energy.

- Mapping and scheduling of applications are becoming increasing adaptive. For example, application tasks that run on a faulty or over-heated processor need to be dynamically migrated or remapped to another one.

The *adaptation* ability allows a system to adapt its behaviors in reaction to changing environment conditions to maintain and/or optimize its behavior w.r.t. objectives on, e.g., safety, performance and power/energy consumption. However, it further complicates the system design.

Fourth, the continuous increase in the size and complexity of future embedded systems, and the strict time-to-market pressures and design costs faced by the designers have demanded the use of *abstract models* for early design analysis, evaluation and validation. Traditional low-level approaches such as RTL level designs or physical prototyping on FPGAs (e.g., [Lee *et al.* 2006] [May *et al.* 2010]), are becoming too slow, tedious and even infeasible to meet design requirements. As a result, system level methodologies based on models at different abstraction levels (e.g., [Cai & Gajski 2003] [Thompson *et al.* 2007] [Stuijk *et al.* 2006b]) have been proposed to handle the given complexities with increased productivity and decreased time-to-market. Such methodologies perform design space exploration (DSE) and evaluation at an early design stage, and thus significantly reduce the design efforts. On the other hand, embedded systems are often safety critical, and must function correctly. Reliability and safety are more important than performance for such systems. *Formal modeling and analysis* techniques are thus required for their designs [Edwards *et al.* 1997].

## **1.2** Problem Statement

The trends outlined in the previous section show that with more and more new features integrated into embedded systems, multiprocessor systems-on-chips (MPSoCs) have become a state-of-the-art solution to achieve high performance and energy-efficiency. Their design complexity has significantly escalated. Meanwhile, they have to be adaptive, i.e., adapt their behavior regarding frequent environment changes for better execution performances, lower energy consumption, etc. Though the adaptivity feature can draw a lot of benefits, it further complicates their design. This leads to a real challenge about cost-effective and safe design methodologies of adaptive/reconfigurable MPSoCs.

- Firstly, design correctness must be addressed to ensure system reliability in every possible system configuration.

- Secondly, reconfiguration correctness must also be established to safely control the variation between system configurations.

We further discuss these two design issues in some more details in the remainder of this section.

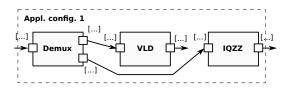

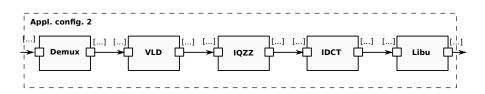

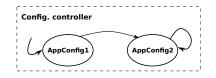

Modern embedded systems often execute multiple tasks concurrently, invoke and finish their executions at different moments in time. At different moments, different combinations of executing tasks form different *application configurations* or scenarios that an embedded system supports. A typical user expects that each application configuration provides predictable performance and reliability. This requires that the proper resource allocation and mapping (i.e., the binding and scheduling of application tasks on the allocated resources) decisions must be made for each application configuration w.r.t. system functional and non-functional requirements. We refer this design issue as **the design of a configuration of an adaptive MPSoC**.

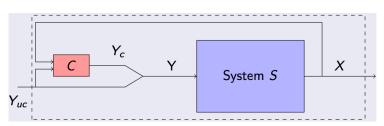

Embedded systems are usually *reactive*, i.e., interact continuously with their environment at a speed imposed by the environment, and *adaptive*, i.e., must adapt their configurations in reaction to the run-time situations. To build such systems, the **reconfiguration management** issue, i.e., how to safely manage the system adaptive behavior w.r.t. system run-time situations and system requirements, must be addressed. Such a run-time manager needs to control and coordinate the system reconfiguration behavior in reaction to system run-time situations according to system requirements.

Especially, different run-time situations may require a different design decision for an application configuration. The reactive and adaptive features must be taken into account when addressing the first design issue, i.e., the design of a configuration of an adaptive MPSoC. The design for each application configuration thus should result in *a number of different solutions* that provide a trade-off in e.g., resource usage, performance and energy/power consumption, so that the run-time manager can choose among the design solutions w.r.t. run-time situations. This thesis aims to deal with these two identified design issues of adaptive MPSoCs.

## **1.3** Contributions

This thesis is carried out within the context of the French ANR project FAMOUS<sup>1</sup>, the acronym for FAst Modeling and design flOw for dynamically reconfigUrable Systems. The FAMOUS project aims at introducing a complete methodology for the design of embedded systems, focusing on MPSoCs implemented on FPGA-based architectures. It covers research in the following three key design aspects of reconfigurable/adaptive embedded systems.

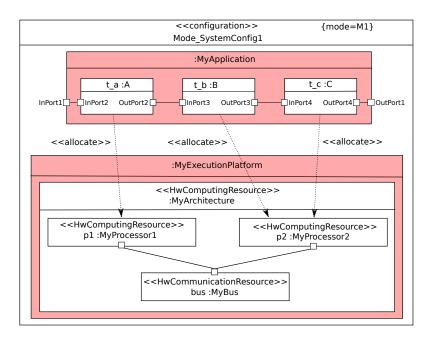

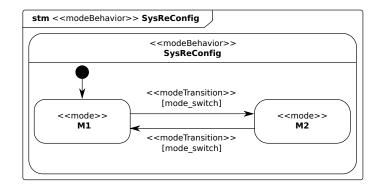

• High-level system modeling: it aims to define concepts necessary for modeling reconfigurable embedded systems through a Unified Modeling Language (UML) profile based on the Model-Driven Engineering (MDE) approach. The UML Modeling and Analysis of Real-Time Embedded systems (MARTE) profile, which provides a common way of modeling both hardware and software aspects of a system but does not

<sup>&</sup>lt;sup>1</sup>http://www.lifl.fr/~meftali/famous/

contain any concepts for modeling dynamic and reconfigurable behaviors, is considered and will be extended to include concepts for modeling reconfigurable behaviors.

- Transformation and code generation: starting from high level application models, it aims to develop necessary model to model transformation rules, in order to allow safe and fast code generation for both simulation and synthesis.

- Verification and analysis: it aims to develop formal and automated verification and analysis methods for reconfigurable embedded systems, in order to guarantee that their final implementations correspond with the initial system requirements.

This thesis targets the *verification and analysis* task of the project. It makes several contributions to the identified design issues mentioned in the previous section.

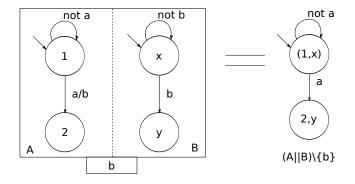

- We propose a high-level framework named CLASSY for the rapid and cost-effective design space exploration (DSE) devoted to the design of adaptive MPSoCs. A multiclock modeling of both software and hardware has been considered by exploiting the notion of abstract clocks borrowed from synchronous data-flow languages. Our approach is an ideal complement to lower-level design assessment techniques for MP-SoCs, such as physical prototyping and simulation. It also aims to serve as an in-termediate reasoning support that is usable, from very high-level MPSoC models (e.g., in UML MARTE profile), to deal with critical design decisions. The framework can be used to deal with the first design issue, i.e., the design of a configuration of adaptive MPSoCs. Furthermore, it is also flexible enough to capture the adaptive behaviors of MPSoCs, and can be used as a high level simulator for adaptive MPSoCs to evaluate customized run-time managers. Some results of this work are presented in [An *et al.* 2012b].

- We propose a general framework based on a tool-supported synchronous variant [Marchand & Samaan 2000] of the discrete control [Ramadge & Wonham 1989] for the reconfiguration management of adaptive MPSoCs. It favors automatic and correct-by-construction manager derivation. We illustrate our approach by considering MP-SoCs implemented on FPGA-based reconfigurable architectures, which can draw various benefits such as efficiency and flexibility. In the framework, the system reconfiguration behavior is modeled in terms of synchronous parallel automata. The reconfiguration management computation problem w.r.t. multiple objectives regarding e.g., resource usages, performance and power consumption is encoded as a discrete controller synthesis (DCS) problem. The existing BZR programming language and Sigali tool are employed to perform DCS and generate a controller that satisfies the system requirements. The results of this work are presented in [An et al. 2013a] [An et al. 2013c].

- We investigate two different ways of combining the two proposed design frameworks for adaptive MPSoCs.

- First, they are combined to construct a complete design flow for adaptive MP-SoCs. The design flow starts from the MARTE high level system modeling, and then employs the two proposed design frameworks to respectively tackle the two design issues. At last, the design results are integrated into the original MARTE modeling framework, with which existing tools such as Gaspard2 [Gamatié *et al.* 2011] can be used to generate low level codes for further analysis and implementation.

- Second, they are combined to present how the CLASSY framework could serve as a high level simulator and assist the designers to design and evaluate runtime managers. To do this, the second framework based on the *discrete control* technique is used for designing a run-time manager, which is integrated into the CLASSY simulation process for analysis and evaluation.

## 1.4 Thesis Overview

This thesis is divided into two parts. Part I presents the state-of-the-art. It has two chapters. Chapter 2 presents the adaptive MPSoCs, discusses their design issues and existing design methodologies, and identifies the targeted design issues of the thesis. Chapter 3 presents the existing models, languages and tools that can be employed to address the targeted design issues. Among them, we identify and introduce the synchronous models, and discrete control techniques and tools that will be applied in the thesis.

Part II exhibits the contributions of the thesis. It has three chapters. Chapter 4 presents the abstract clock based design framework for the first design issue, i.e., the design of a configuration of an adaptive MPSoC. Chapter 5 presents the discrete control technique based design framework for the second design issue, i.e., the reconfiguration management of adaptive MPSoCs. Chapter 6 presents the two different ways of combining the two proposed design frameworks for adaptive MPSoCs. Finally, Chapter 7 concludes.

# Part I State of the Art

# Chapter 2

# Multiprocessor Systems-on-Chip (MPSoCs)

#### Contents

| 2.1 | Genera | al Presentation                              | 9         |

|-----|--------|----------------------------------------------|-----------|

|     | 2.1.1  | Processing Elements                          | 10        |

|     | 2.1.2  | Memory Architecture                          | 11        |

|     | 2.1.3  | Interconnect                                 | 12        |

| 2.2 | MPSo   | C Design                                     | <b>13</b> |

|     | 2.2.1  | A Design Flow Model                          | 13        |

|     | 2.2.2  | Design Space Exploration                     | 15        |

|     |        | Multi-Objective Optimization                 | 15        |

|     |        | Y-Chart Scheme for Automated DSE             | 16        |

|     | 2.2.3  | A Survey of Existing Approaches              | 16        |

| 2.3 | Adapt  | ivity of MPSoCs                              | 19        |

|     | 2.3.1  | Motivation for Adaptivity in MPSoCs          | 19        |

|     | 2.3.2  | FPGAs as Implementation Platforms for MPSoCs | 19        |

|     | 2.3.3  | Adaptivity Management                        | 20        |

|     |        | Some Existing Management Strategies          | 21        |

|     |        | Run-Time Management of an FPGA Fabric        | 21        |

|     |        | Autonomic Computing Approach                 | 22        |

| 2.4 | Summ   | ary and Discussion                           | 23        |

An MPSoC is a system-on-chip that uses multiple processors as well as additional components such as peripheral devices and memories for an application. Nowadays, MPSoCs have emerged as the main solution for modern embedded systems [Siala & Saoud 2011], due to their ability to meet the computation requirements of their applications while keeping a low level power consumption. The adaptivity, an important feature of emerging MPSoCs, draws a lot of benefits for embedded systems, and meanwhile further complicates their design.

This chapter is organized as follows: Section 2.1 gives a general presentation of MPSoCs. Section 2.2 presents the design issues of MPSoCs. Section 2.3 focuses on the MPSoC adaptivity and its design issues.

# 2.1 General Presentation

The functionality integrated into embedded systems is ever increasing. This is typically observed in embedded multimedia systems. The Apple iPhone, for example, has a variety of applications that allow users to watch movies, listen to music, browse the Internet, send emails, use online Google navigation, etc. The users typically expect that they have high performance, and at the same time, their energy consumption is kept at a minimal level, especially for battery-powered embedded systems. MPSoCs have been constructed to meet these requirements. In the following, we present the main components of MPSoC platforms.

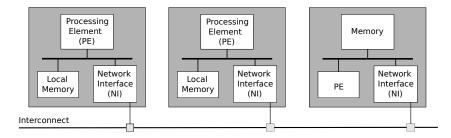

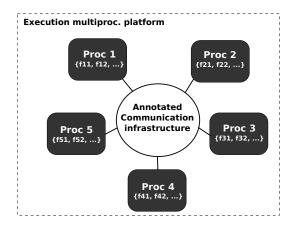

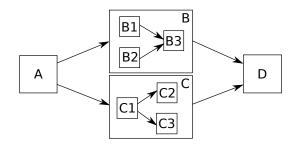

The main components of an MPSoC platform are the processing elements (PEs), responsible for executing the applications, the on-chip memories, responsible for storing both the application data and instructions, I/O components, responsible for communicating with the outside world and, finally, the on-chip interconnect structure, responsible for linking the processing elements with the memories and the I/O components [Nollet 2008]. Figure 2.1 details the MPSoC platform template considered throughout this thesis. It is based on the tile-based multiprocessor platform described in [Culler *et al.* 1999] and consists of multiple tiles interconnected by an interconnect fabric. Each tile contains a local processing element, a local memory and a network interface (NI), which is accessed both by the local elements inside the tile and by the interconnect. Besides, the MPSoC platform could also contain some shared memory tiles to store large data sets (as shown in the third tile of Figure 2.1). In the rest of this section, we give some more details of the main MPSoC components.

Figure 2.1: MPSoC platform template.

#### 2.1.1 Processing Elements

Generally speaking, there exist three categories of processing elements: application-specific integrated circuits (ASICs), general-purpose processors (GPP) and reconfigurable logic. These three computing technologies are quite different concerning their performance, energy efficiency and degree of flexibility. The ASICs are designed to perform some specific application, and can achieve the maximum energy efficiency and performance [Marwedel 2011]. However, they suffer long design times and the lack of flexibility. The key advantage of general purpose processors, on the contrary, is their flexibility and rapid developments: embedded system behavior can be changed by just changing the software running on such processors. However, they are usually very slow and much less energy-efficient. The reconfigurable computing technology combines the flexibility of general-purpose computing, and high performance and energy efficiency of application-specific computing.

The number and types of PEs contained in an MPSoC platform are obviously connected to the given application characteristics and requirements. Based on the types of PEs integrated in an MPSoC platform, two MPSoC architecture families can be distinguished: *homogeneous* and *heterogeneous* MPSoCs. In a homogeneous MPSoC, PEs are of the same type. Examples are multi- or many-core architectures used for general computing and PCs. Heterogeneous MPSoCs are composed of different types of PEs, such as micro-controllers, digital signal processing (DSP) processors, ASICs. In order to meet the computational performance of novel applications, while, at the same time, reducing

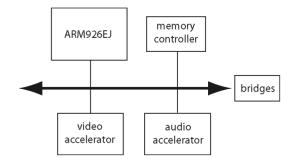

Figure 2.2: STMicroelectronics Nomadik platform, taken from [Wolf et al. 2008].

the power/energy consumption and remain flexible, there is a trend to use heterogeneous MPSoC platforms. In [Wolf *et al.* 2008], the authors present a wide range of MPSoC architectures developed over the past decade, such as STMicroelectronics Nomadik, Philips Viper Nexperia, Texas Instruments (TI) OMAP 5912. Figure 2.2, taken from [Wolf *et al.* 2008], shows the STMicroelectronics Nomadik [Artieri *et al.* 2003], an heterogeneous MPSoC platform for cellphones. It contains an ARM926EJ as its host processor, and two programmable accelerators for video and audio processing respectively. In the thesis, both architecture families are considered.

As mentioned at the beginning of this section, the key advantage of GPPs is their flexibility but they are energy inefficient compared to ASICs [Marwedel 2011]. To make them energy efficient, a number of techniques have been developed at various levels of abstraction [Burd & Brodersen 2002]. Clock gating is an example of such a technique. It is based on the consideration that clock signals do not perform any computation and are mainly used for synchronization, while they are a great source of power dissipation because of high frequency and load [Kathuria et al. 2011]. With clock gating, one can save power by disconnecting parts of a processor from the clock during idle periods [Marwedel 2011]. Another commonly-used technique that can be applied at a rather high abstraction level is the dynamic voltage and frequency scaling (DVFS). With DVFS, the clock frequency of a processor can be decreased at run-time to obtain a corresponding reduction in the supply voltage, which reduces power consumption and leads to significant reduction in the energy required for a computation [Le Sueur & Heiser 2010] [Milutinovic et al. 2009]. For example, the clock of the  $Crusoe^{TM}$  processor [Klaiber 2000] could be varied between 200 MHz and 700 MHz in increments of 33 MHz w.r.t. 32 voltages levels between 1.1 and 1.6 volts. It takes about 20 ms for the transition from one frequency/voltage pair to the next.

#### 2.1.2 Memory Architecture

Memories are used to store data, programs, etc. Memory architecture has a direct impact on the performance and energy cost of MPSoCs. Memory access latency could make the PE computations to wait, and thus drop overall system performance. On the other hand, memory access also contributes to the overall system energy cost. As accessing smaller memories usually require less time and less energy, there is a trend to use new hierarchical memories organizations in MPSoCs instead of using a single on-chip memory. The hierarchy can store data used by a PE in a local memory close to it, such as the MPSoC template in Figure 2.1. Such a hierarchy can also avoid the access contention of PEs on a central shared memory.

Caches and scratch pad memories (SPMs) are examples of small memories. They both

have only one processor clock cycle access latency [Wolf *et al.* 2008]. Caches represent on chip interfaces between PEs and memories. It requires a hardware controller to check whether the cache has a valid copy of the data associated with a certain memory address. In the contrary, SPMs are mapped into the address space, and thus do not need a hardware controller. This makes SPMs more energy efficient than caches.

Some applications like multimedia applications may require access to quite large data sets. A video processing application, for example, might require access to a complete videoframe at HDTV resolution. Such a frame could be composed of over two million pixels, and each pixel needs three bytes of memory. In this case, the local small memories within a tile will typically not be large enough. An external memory is thus required in this case. This can be seen as a memory tile of the MPSoC platform template as shown in Figure 2.1.

#### 2.1.3 Interconnect

There are a number of interconnect technologies that can be used by an MPSoC platform. The authors of [Siala & Saoud 2011] give a survey of existing interconnects w.r.t. communication topology and strategy. In the thesis, we mainly consider bus and Network-on-Chips (NoCs).

Bus is the traditional interconnection architecture in MPSoCs. The arbitration policy of the bus has a direct impact on the performances of an MPSoCs. The communication by bus has the main advantage of simplicity (i.e., a single channel of communication), and requires thus relatively less design time. On the other hand, the bus architecture is not efficient [Lee *et al.* 2008], since it has a limited bandwidth and the available throughput between two PEs connected to it is inversely proportional to the number of PEs connected to it [Siala & Saoud 2011]. Therefore, bus is the good choice for the architectures with small number of PEs, but it would cause low performance and high power/energy consumption issues when the number of PEs grows big.

Network-on-Chip (NoC) is an emerging paradigm for the communication within MP-SoCs. An NoC consists of network adapters, routing nodes (or routers), and links that connect the routing nodes [Bjerregaard & Mahadevan 2006]. Routing nodes are used to route data according to their implemented routing strategies or algorithms. Network adapters are used to interface routing nodes with PEs. The authors of [Bjerregaard & Mahadevan 2006] characterize an NoC by its i) topology: nodes positions and connectivity, and ii) routing protocol: how the nodes and links are used for communication.

There exist a number of topologies for NoCs, such as Spidergon [Moadeli *et al.* 2007], Mesh [Ali *et al.* 2009], and Tree [Adriahantenaina *et al.* 2003]. We take the Mesh topology as an example to describe how such an NoC works. A  $n \times n$  2D Mesh topology NoC is formed by [Siala & Saoud 2011]:

- n\*n routers, each router, except for those on the sides, is connected to 4 neighbor routers and a PE via input/output channels.

- an input/output channel performs unidirectional communication between two routers or between a router and a PE.

Figure 2.3 shows such a  $4 \times 4$  Mesh topology NoC.

NoC routing protocols determine how a message packet traverses the NoC channels from its source router to its destination router [Chiu 2000]. Routing protocols can be deterministic or adaptive [Mirza-Aghatabar *et al.* 2007]. Deterministic protocols route packages by predefined paths [Chiu 2000]. An example is the "XY" routing algorithm for 2D meshed NoC presented above. It routes packages, from its source to its destination, first in the X

Figure 2.3: A 4×4 Mesh topology NoC [Ali et al. 2009].

direction then in the Y direction. Such protocols are deterministic, but lack flexibility and do not adapt to the network state dynamically. Adaptive protocols, on the contrary, detect the network traffic and channel status during the package routing, and adapt routing path so as to avoid congested regions of the network [Mirza-Aghatabar *et al.* 2007]. The routing protocol also plays an important role in the performance of MPSoCs, and the user thus needs to find out a proper one for his or her design.

Compared to bus, NoCs are more expensive in surface, but more scalable and efficient with less power consumption. NoCs provide a better compromise of cost and performance.

## 2.2 MPSoC Design

The design of modern embedded systems, which are usually based on MPSoC architectures, is becoming increasingly complex. To deal with this complexity, the common practice in this area is to raise the level of abstraction and adopt system level design methodologies [Gerstlauer *et al.* 2009] [Cannella *et al.* 2011]. Typically, system level design approaches follow a top-down approach. They rely on computational abstract models for the description of system functional and non-functional requirements, and traverse the design space by means of an iterative process, known as *design space exploration* (DSE), which evaluates and refines different design decisions to find an optimal solution. In this section, we firstly introduce the popular Y chart design flow model, which most of system level design approaches follow, in Section 2.2.1. Section 2.2.2 presents the design space exploration problem. A survey of existing design approaches is presented in Section 2.2.3.

#### 2.2.1 A Design Flow Model

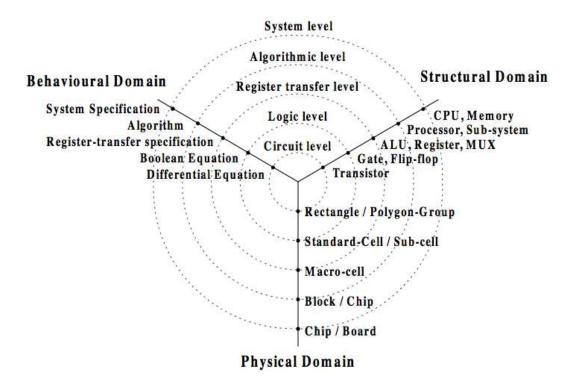

Embedded system design is a rather complex task, consisting of a number of sub-tasks such as functionality and platform modeling, application-architecture mapping, software code generation and hardware synthesis. A complete design flow must combine and perform these sub-tasks to generate the final systems. A very popular design flow model is the Y chart, as shown in Figure 2.4, proposed by Gajski and Kuhn [Gajski & Kuhn 1983]. In the Y chart, the design information is presented in three dimensions: behavioral, structural, and physical, represented by the three axes.

• Behavioral representation: it describes the system functionality, i.e., what the system does, and says nothing about the implementation and structure.

Figure 2.4: The Y chart design model, taken from [Tammemäe & Ellervee].

- Structural representation: it describes a set of computing components and connections that a behavioral representation maps onto. However, it does not specify any physical parameters, like the positions of components on a board.

- Physical representation: it is a layout planning, and describes the physical system.

Along the axes, the circles represent various levels of abstractions. Moving down along an axis represents moving down in the level of abstraction. In the graph, five levels of abstraction are identified: system level, algorithmic level, register transfer level (RTL), logic level and circuit level. Near the intersection points of the circles and the axes, the corresponding abstraction information corresponding the three dimensions are noted.

The considered level of abstraction has an great impact on the design analysis time and accuracy. Typically, the lower the abstraction level is considered, the more accurate analysis result can be obtained, while the more analysis time is required. This is due to the fact that more architectural details are taken into account when moving down in the level of abstraction. For example, the MPSoC design simulation at the register transfer level (RTL) could be about 400 times slower than at the transaction level (i.e., algorithmic level), as shown in [Boukhechem 2008]. However, RTL level is more accurate.

In the literature, nearly all system level design flows follow a top-down approach. They [Gerstlauer *et al.* 2009] typically start with a system level description consisting of a behavioral description, which is often some kind of data-flow graphs, and a platform model, which is typically a set of architectural components such as processors, memories. Additionally, some implementation constraints regarding mapping, performance, energy and cost are also given. A synthesis task is then performed to select an appropriate platform, determine a binding of the behavioral model to the platform, and generate an implementation, e.g., a scheduling on each platform resource. The resulting implementation is a refined model,

which integrates design decisions such as binding and scheduling. The refined model is then used as input to the design flow at lower levels of abstraction, where each software and hardware component is further implemented separately. In order to optimize the design for the synthesis task, a *design space exploration* (DSE) should be performed to evaluate and traverse the design space.

#### 2.2.2 Design Space Exploration

The term "design space exploration" (DSE) has its origin in the logic synthesis context [Gries 2003]. Today, however, it usually deals with system-level design problems such as hardware/software partitioning, application-architecture mapping w.r.t. multiple objectives regarding, e.g., correctness, execution time, energy consumption. DSE is in general a multi-objective optimization problem. It is not advisable to merge all these objectives into a single objective function by e.g., using a weighted average, as this would hide some essential characteristics of designs [Marwedel 2011]. Returning a set of reasonable designs among which the designer can select an appropriate one is rather advisable. In this section, the multi-objective optimization is firstly presented. We then present the popular Y-chart scheme that enables systematic design space exploration.

#### **Multi-Objective Optimization**

Design Space Exploration (DSE) is a multi-objective optimization problem [Zitzler 1999] that tries to find out one or several "optimal" design solutions w.r.t multiple objectives regarding functional and non-functional properties such as correctness, execution time and power/energy consumption. The multi-objective design space exploration optimization problem can be defined as follows:

min or max

$$f(x) = (f_1(x), f_2(x), \dots, f_n(x))$$

subject to C.

where  $x \in X$  is the decision vector, representing decisions such as which application tasks are mapped onto which PEs, C denotes the constraints (e.g., two tasks communicating with each other cannot be mapped onto two PEs that are not connected), and f is the objective function composed of n objectives  $f_1, f_2, ..., f_n$ .

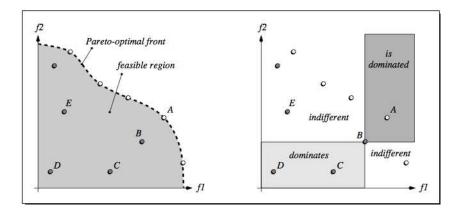

Suppose  $X_f \in X$  is the set of feasible solutions that meet constraints C. In singleobjective optimization, the feasible set is totally ordered according to objective f: for any two solutions  $a, b \in X_f$ , either  $f(a) \neq f(b)$  or  $f(b) \neq f(a)$ . The solution(s) optimizing objective f can always be found. However, when two or more objectives are involved, the feasible solution set  $X_f$  is, in general, not totally ordered any more. This situation is illustrated in Figure 2.5: the left gives a solution space that aims to maximize objectives f1 and f2, and the right describes the three possible relations of solutions. For any two solutions a and b, a dominates b if and only if a is better than b w.r.t. at least one objective and not worse than b w.r.t. all other objectives. For example, in Figure 2.5, A dominates B in the example where  $f_1(A) > f_1(B) \land f_2(A) > f_2(B)$ ; C dominates D in the example where  $f_1(C) > f_1(D) \land f_2(C) \ge f_2(D)$ . A solution a is **indifferent** to solution b if neither a dominates b nor b dominates a. For example, E and B are indifferent, as they are better w.r.t. one objective and worse w.r.t. the other:  $f_1(B) > f_1(E) \land f_2(E) > f_2(B)$ . As a result, there is usually no single optimal solution for a multi-objective optimization problem, but rather a set of optimal trade-offs. A solution x is said to be **Pareto optimal** if and only if x is not dominated by any solution in  $X_f$ , e.g., the white points in Figure 2.5. The set of all Pareto optimal solutions form the **Pareto front** or **Pareto-optimal set**.

Figure 2.5: Illustrative example of Pareto optimality in objective space (left) and the possible relations of solutions in objective space (right), taken from [Zitzler 1999].

Design space exploration (DSE) based on Pareto points is the process of finding a set of Pareto-optimal solutions for the designer, enabling him or her to select the appropriate one(s) among them.

The solution space of the DSE problem becomes large quickly if arbitrary mapping is allowed. Considering an application consisting of m tasks and a platform with n PEs, the feasible mapping choices would be  $n^m$ . The complexity increases even further if multiple objectives are considered during the exploration. In order to evaluate if a design choice is Pareto-optimal w.r.t. a set of solutions, all objective values of the design must be compared with those of the other designs. The use of the exhaustive exploration of the design space is thus limited, if not infeasible. A common solution is to trade optimality for speed, and use heuristic techniques to guide the exploration process.

#### Y-Chart Scheme for Automated DSE

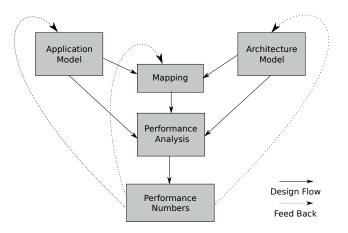

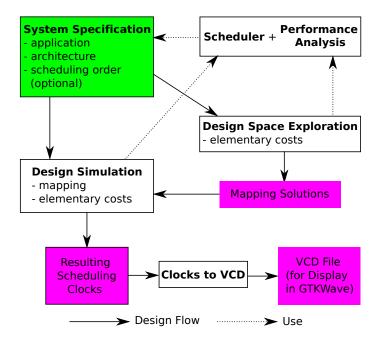

The Y-chart scheme, proposed by Kienhuis et al. [Kienhuis et al. 2002], presents a methodology that allows designers to perform systematic exploration of embedded system design space. It advocates separation of concerns, i.e., the separation of various design aspects to allow more effective design space exploration. Two fundamental separations are i) the separation of application behavior (what the system is supposed to do) and architecture (how it does it), and ii) the separation of communication and computation. Figure 2.6 shows the Y-chart scheme for design space exploration. It requires an explicit definition of the application and architecture models. The application model captures the application functional behaviors, whereas the architecture model describes the hardware resources as well as their performance constraints. A mapping step is applied to map application tasks onto architecture resources, and the performance analysis is then carried out to quantify design choices. This yields the performance numbers that designers interpret so that they can improve the designs by changing the design parameters such as the mapping denoted by dotted lines. This procedure is repeated in an iterative way until one or more satisfactory designs are found.

#### 2.2.3 A Survey of Existing Approaches

As mentioned at the beginning of Section 2.2.1, embedded system design is a rather complex problem, and has a number of design tasks. A classification framework of design tasks has

Figure 2.6: The Y-chart design scheme.

been defined in [Densmore & Passerone 2006], which identifies the individual design tasks, such as modeling, functional verification, software code generation, C-to-RTL synthesis, of more than 90 different design flows or methodologies. In contrary, [Gerstlauer *et al.* 2009] focuses on the complete design flows that combine all design tasks across hardware and software boundaries. In the thesis, we consider the system behavior and platform synthesis task, i.e., the application mapping design task as shown in Figure 2.6. *Application mapping*, which refers to the binding and scheduling of behavioral models onto platform models, has a strong impact on the quality of design results, and is the key design issue of MPSoCs [Marwedel *et al.* 2011].

Based on the Y-Chart scheme (see Figure 2.6), we survey and classify the existing approaches based on their used behavioral and architectural models. The behavioral model can be captured by model of computations (MoCs) [Lee & Sangiovanni-vincentelli 1998], programming languages like C, java, system level description languages such as SystemC, etc. We distinguish three levels of architecture modeling:

- system level models, which consists of an abstract architecture template, e.g., the PEs, memories, and interconnects, and for each architecture component, a list of supported behavioral model components and their performance requirements;

- transaction level model (TLM), which models the architecture by using system level description languages such as SystemC or SpecC;

- register transfer level (RTL) or lower level: which models architecture by using hardware description languages such as VHDL or Verilog.

The abstraction levels of architecture models have a great impact on the design analysis time and accuracy. In the following, some existing approaches are presented based on the identified architectural modeling levels.

We firstly introduce several complete design flows that allow gradual refinement of (abstract) system-level architecture models as mentioned in [Gerstlauer *et al.* 2009]. Most of the design flows cover all the identified architecture modeling levels.

• Daedalus [Thompson *et al.* 2007] provides a highly-automated framework for systemlevel architectural exploration and synthesis, programming, and prototyping of heterogeneous MPSoC platforms. It models the system behavior by means of the Kahn Process Network (KPN) MoC. It leads the designer in a number of refinement steps to produce an MPSoC implementation on an FPGA at the RTL and ISA levels for hardware components and software processes, respectively. It uses a modeling and simulation environment called Sesame to perform system-level architectural DSE. Sesame supports both exhaustive and heuristic exploration methods.

- Metropolis [Balarin *et al.* 2003] provides a general framework which allows the description and refinement of a design at different levels of abstraction. The behavioral description is captured as a set of processes that communicate through channels. A backend is provided for the translation of meta-models into C++/SystemC simulation code.

- Koski [Kangas *et al.* 2006] provides a framework for modeling, automatic architectural design space exploration, and system level synthesis, programming, and prototyping of MPSoCs. The behaviral description is based on the KPN MoC from a UML description. It has an automatic architecture exploration step which transforms the application and architecture models to an abstracted model for fast exploration. It allows the automatic code generation to analyze and simulate the system at multiple levels of abstraction. The generated low-level software code and the RTL hardware descriptions (derived from its platform library) can be used for physical implementation.

- Ptolemy [Lee 2003] is an environment for simulation and prototyping of heterogeneous systems, which supports several different models of computation such as SDF, KPN, synchronous reactive models. It allows the designers to specify and simulate applications with different computational models on heterogeneous architectures at different levels of abstractions.

Some other examples of such design flows are PeaCE/HOPES [Ha *et al.* 2008], System-CoDesigner [Keinert *et al.* 2009], etc.

Some other existing approaches are presented as follows following the identified architecture modeling levels from RTL to system level.

At RTL or lower level modeling of architectures, [Bailey & Martin 2010] applies physical prototyping which uses circuit board and SoC in the form of working silicon. The authors in [Hedde *et al.* 2009] propose a MPSoC prototyping platform that relies on fieldprogrammable gate arrays (FPGAs) and register transfer level (RTL) descriptions. The major advantage of these two techniques is their high accuracy, but they require a long time and provide a limited flexibility when it comes to an efficient DSE of multiple architectures.

Design approaches that adopt the transaction level modeling (TLM) of architectures include [Petrot *et al.* 2011] [Abdi *et al.* 2011]. SystemC are usually used for the behavior modeling as well. Some simulation environments such as SoCLib [SoClib 2012] and StepNP [Paulin *et al.* 2002] use cycle-accurate model or TLM for hardware modeling and ISS for software simulation. The programming languages such as C, C++ are employed to describe the system behavior in these environments. Approaches based on MoCs and UML for behavioral modeling such as [Robert & Perrier 2010], [Chen *et al.* 2004] exist as well. The simulation speed and timing accuracy of TLM and ISS based techniques are faster, but less accurate than those of prototyping and emulation.

Since all these approaches based on TLM and RTL modeling of architectures need very detailed architecture information, they are very slow, tedious, and complex for cost-effective design and verification of modern MPSoCs that are complex and have big or even huge design space. They are thus only be used at the very late design stage.

At the early design stage, the system level modeling of architectures are usually considered. They usually use MoCs to model system behaviors. Some approaches based on Kahn Process Networks (KPNs) [Kahn 1974] are [Haid *et al.* 2009], [Schor *et al.* 2012]. Examples of approaches based on Synchronous Data Flow (SDF) [Lee & Messerschmitt 1987] are [Stuijk 2007], [Zhu *et al.* 2010], [Yang *et al.* 2009], [Stuijk *et al.* 2011]. The synchronous reactive MoC [Benveniste *et al.* 2003] is another well-known support for the high level modeling and analysis of embedded systems.

The design approaches based on system level modeling of hardware architectures abstract away the architectural information, and thus significantly reduce the design time. On the other hand, the missing of architectural information also makes the analysis results less accurate. Furthermore, their analysis results highly depend on the input performance model, i.e., the information of performance requirements of the application operations or tasks on resources. These values are usually obtained by statically profiling or analyzing corresponding worst case performance metrics. This could make the final results too pessimistic, and over-estimate the resource usages.

# 2.3 Adaptivity of MPSoCs

The adaptivity of an MPSoC refers to its ability to dynamically adapt its behaviors and structure over time. Reconfigurable hardware architectures (i.e., FPGA fabrics), due to their ability to combine some of the flexibility of software with the high performance of hardware, are becoming increasingly attractive for adaptive MPSoCs. In this section, the motivation for adaptivity is presented in Section 2.3.1. Section 2.3.2 introduces FPGAs as the implementation platforms for MPSoCs. Some adaptivity management issues are discussed in Section 2.3.3.

#### 2.3.1 Motivation for Adaptivity in MPSoCs

Over the recent decades, there have been increasing requirements for embedded systems to be adaptive. The motivations for this trend can be observed in the following three levels:

- applications are becoming intrinsically dynamic: e.g., a surveillance embedded system for street observation must adapt its image analysis algorithms according to the luminosity of the weather.

- the execution platform should be adaptive to provide a better performance and/or reduce energy consumption: e.g., a hardware accelerator gives a more powerful execution in terms of performance than a general purpose processor; PEs that are idle should be turned off or switched to low level energy consumption mode, thanks to techniques like gate clocking.

- the mapping of the running application tasks should be adaptive to provide execution efficiency and/or fault tolerance: e.g., running application tasks need to adapt their mapping when some new tasks are invoked, so that they can execute on the shared computing resources in a more efficient way; a running task must adapt its mapping when some of its used resource becomes unavailable.

#### 2.3.2 FPGAs as Implementation Platforms for MPSoCs

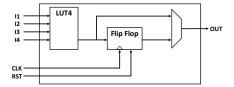

An Field-Programmable Gate Array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing. An FPGA is composed of an array of logic cells and programmable routing channels to implement custom hardware functionality. The basic components of a logic cell (as shown in Figure 2.7) are a LUT (Look Up Table):

Figure 2.7: Simplified logic cell implementation.

a memory used as a programmable device to implement any logic function between inputs and outputs of a cell, and a D flip-flop: to hold a state between two clock cycles.

An FPGA configuration program consists of one or more *bitstreams*, which are binary files storing information to configure the LUTs and the routing switches. The bitstreams are usually generated by design tools such as the Xilinx Embedded Development Kit (EDK) [Xilinx 2013], which includes a tool suite called Xilinx Platform Studio (XPS) used to design an embedded system. Recent large FPGAs contain more than 200K logic cells that can be combined and interconnected to implement very complex designs. Multiprocessor architectures with tens of large hardware accelerators and processors can be implemented.

**Run-time partial reconfiguration.** In the new generation of FPGAs, the hardware configuration can be updated at run-time by using the partial reconfiguration feature. A portion or region of the FPGA which implements some logic functions can be swapped with another one. This feature also enables the FPGAs to update the functionality of any logic function at run-time if required. When multiple functions are called sequentially, the same region can be reused so that the required size can be minimised. The best advantage of this type of reconfiguration is its ability to reconfigure hardware during the running of the static part, i.e., the part which does not contain any reconfigurable area. It assumes that the hardware reconfiguration does not disturb the execution of the application. The bitstreams therefore cover only some regions of the FPGA array.

Such *Dynamically Partially Reconfigurable* (DPR) FPGAs make them suitable for addressing constraints on resources (re-using some areas for different functions for applications that can be partitioned into phases) by adapting resources to available parallelism according to environment variations. DPR FPGAs represent a trade-off in that they are slower than dedicated Application-Specific Integrated Circuit (ASIC) hardware, but much faster than software running on general purpose CPUs.

#### 2.3.3 Adaptivity Management

The management of an adaptive MPSoC concerns three possible dynamic aspects (as mentioned in Section 2.3.1) of the system over time: dynamic application behavior, dynamic platform behavior and the dynamic application mapping. A run-time manager needs to monitor the system run-time situations, make adaptation decisions based on observed information and system requirements, and perform adaptation actions.

Reconfigurable hardware architectures (i.e., FPGA fabrics) have the ambition to deliver the same flexibility level as general purpose processors while providing a performance and energy efficiency level close to that of an ASIC. Such architectures are becoming increasingly attractive for MPSoCs. They operate in a very different way compared to a multi-core or instruction set processor (ISP) architecture. The run-time management of such specific architectures thus needs to be addressed differently. The run-time management problem of adaptive systems can be seen as a self-management problem in *autonomic computing*. It proposes a general feedback loop structure address the automatic management of adaptive systems, which is well suited for the management of adaptive MPSoCs.

In the following, first, we present the existing management strategies for MPSoCs; second, the management issue of embedded systems implemented on FPGAs is discussed; at last, the autonomic computing paradigm is introduced.

#### Some Existing Management Strategies

Most of the existing approaches regarding the management of adaptive MPSoCs target the run-time mapping problem, i.e., how to map and schedule application tasks w.r.t. the availability of platform resources and system requirements. These approaches can be classified into two categories: purely run-time mapping approaches and hybrid design time/run-time mapping approaches.

Purely run-time mapping approaches do not have a pre-analysis phase. Finding a reasonably good solution in a reasonable short computation time, for such approaches, is more important than seeking optimality requiring much computation time. They thus resort to heuristic algorithms to generate fast and lightweight solutions on-line [Nollet *et al.* 2008]. For example, in [Smit *et al.* 2005] such a technique proposes an iterative hierarchical approach with simple heuristics in each individual level to solve the application mapping on a parallel heterogeneous SoC architecture at run-time. In [Ghaffari *et al.* 2007], an on-line partitioning algorithm is associated with a scheduling heuristic to address the application mapping problem. Since all the mapping analysis is done on-line, Such approaches can deal with the mapping of applications that are unknown a priori. However, such approaches cannot guarantee optimal solutions and/or strict system constraints, due to unknown situations, and are usually validated by (limited) simulations.

The hybrid approaches [Schor *et al.* 2012] [Schranzhofer *et al.* 2010] [Singh *et al.* 2011] firstly perform intensive analysis at design time, and then propose a run-time manager integrating the knowledge of design time analysis. However, they do not address run-time management problem systematically, and usually encode the run-time manager manually by considering a limited number of run-time configurations. This is tedious and error-prone [Gohringer *et al.* 2008] in consideration of more complex and dynamic system behavior.

Regarding the design verification, while simulation and testing are still widely considered in industry, they often imply a tedious and expensive validation process that necessarily requires a system implementation, some adequate test benches and a simulator to achieve experiments. Formal verification, such as model-checking, is therefore a useful complement to simulation and testing as it relies on abstract models [Mitra *et al.* 2010]. Two examples of applying model checking to validate the run-time manager design are [Adler *et al.* 2007] [Schaefer & Poetzsch-Heffter 2009], while the authors in [Yang *et al.* 2012] apply a game theory-based approach to construct a run-time manager.

#### **Run-Time Management of an FPGA Fabric**

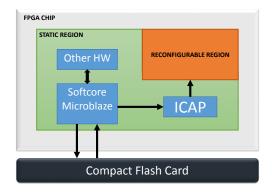

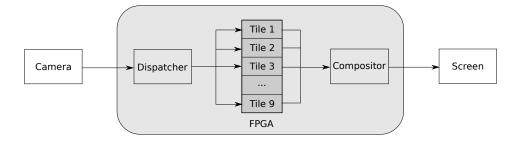

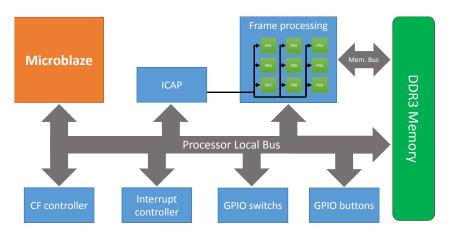

The reconfiguration of a DPR FPGA fabric involves the process of loading configuration files to part of the reconfigurable surface. Figure 2.8 shows the structure of an FPGA chip, which is abstracted from the Xilinx ML605 board. The configuration files used for the different configurations of the partially reconfigurable regions are stored in a compact flash card. A soft-core processor e.g., microblaze is responsible for loading them. It performs the reconfiguration of the reconfigurable region through the Internal Configuration Access Port (ICAP).

Figure 2.8: FPGA with a microblaze softcore.

The run-time management of reconfiguration involves a control loop, taking decision according to events monitored on the architecture, choosing the appropriate next configuration to install, and executing appropriate reconfiguration actions. The dynamism in the architecture dimension further increases the design complexity, for which a complete tool-chain is lacking [Santambrogio 2010].

Due to the relative novelty of DPR technologies, the management of reconfiguration has to be designed manually for important parts. For instance, [Quadri *et al.* 2010b] proposes a design flow, from high level models to automatic code generation, for the implementation of reconfigurable FPGA based SoCs. The system control aspects need to be modeled manually and integrated into the flow. Some other work employs model checking to verify the controller designs. For example, in [Dahmoune & Johnston 2010], the authors address post-silicon verification by connecting a model-checker to a physical implementation of reconfigurable systems on FPGAs.

In the current practice, though the numbers of considered tasks and reconfigurable regions are low (few units), ensuring a correct and optimal management by using manual encoding and analysis is tedious and error-prone [Gohringer *et al.* 2008]. Automatic techniques are required to better address this problem, with the foreseeable increase in complexity.

#### Autonomic Computing Approach

The autonomic computing paradigm [Parashar & Hariri 2005] [Kephart & Chess 2003], inspired by biological systems such as the autonomic human nervous system, enables the development of self-managing computing systems to handle the emerging complexity in computing systems, services and applications. The function of a self-management capability is a control loop that collects details from the system and acts accordingly [IBM 2006]. Typically, self-managing capabilities of autonomic systems can be classified into four categories:

- self-configuration: configure and reconfigure a system under varying conditions following high-level policies;

- self-optimization: detect sub-optimal behaviors and tune itself to optimize its execution;

- self-healing: discover, diagnose and recover from potential problems without disrupting the whole system environment;

• self-protection: detect hostile behaviors as they occur, protect itself from both internal and external attacks, and maintain system security and integrity.

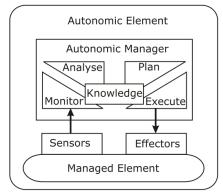

Figure 2.9: IBM's Monitor, Analyze, Plan, Execute, Knowledge (MAPE-K) reference model for autonomic control loops, taken from [Huebscher & McCann 2008].

To achieve autonomic management, IBM has suggested a reference model for autonomic control loops as shown in Figure 2.9, which is usually referred to as *Monitor, Analyse, Plan, Execute, Knowledge* (MAPE-K) [IBM 2006]. In the MAPE-K loop, the *managed element* represents any system software or hardware component that is managed by a coupled autonomic manager. To connect to the autonomic manager, the managed element requires a *sensor* to sense the changes in the internal and external environment, and an *effector* or actuator to react to and counter the effects of the changes in the environment. The autonomic manager consists of four components:

- the *monitor*, which collects the details from the managed resource via the sensor;

- the *analyze*, which models and analyzes the collected data by the monitor;

- the *plan*, which constructs the response actions needed to achieve objectives;

- the *execute*, which performs the execution of the plan via the effector.

All the four components function based on a *knowledge* representation of the system. The autonomic manager can be designed and developed in many different ways, relying on techniques e.g., heuristics, model checking, control theory, machine learning [Maggio *et al.* 2012].

## 2.4 Summary and Discussion

MPSoCs are becoming the main solution of modern embedded systems, as they can provide powerful computing ability at affordable power consumption. In this chapter, we firstly presented the main components of MPSoC platforms. Regarding the design of MPSoCs, which is quite complex and challenging, we have seen a common practice that advocates raising the levels of abstraction and adopting system level design methodologies. By reviewing the existing system-level design methodologies, and the design approaches at different levels of abstractions, we can observe the importance of performing design space exploration at early design stages. It can prune the design space when it is largest, and identify candidate design solutions in a fast and efficient way before performing lower level refinements for more accurate results, so that significantly reduce the design efforts. Furthermore, MPSoCs are getting more and more adaptive. The adaptivity adds a new design dimension in addition to the design issue of MPSoCs as presented in Section 2.2 for which the adaptivity is usually not explicitly addressed. We have briefly reviewed the reconfiguration management strategies of adaptive MPSoCs, and focused on particularly adaptive MPSoCs implemented on reconfigurable architectures, i.e., FPGAs. Such architectures provide a good trade-off of flexibility and performance for implementing adaptive MPSoCs. Regarding the control of their reconfiguration, we have observed that manual encoding is adopted in most cases. In anticipating the increase in complexity, automatic manager derivation thus could be more favorable.

To sum up, we have looked at two design aspects of adaptive MPSoCs in this chapter: the design of MPSoCs without considering adaptivity, which can be seen as the design of a configuration of adaptive MPSoCs, and the reconfiguration management of adaptive MPSoCs. Embedded systems are typically reactive systems that are in continual interaction with their environment and run at a pace determined by that environment [Halbwachs 1993]. These two design issues correspond intrinsically to the analysis and control of reactive systems, for which there exist a variety of models, languages and tools.

## CHAPTER 3

# Models, Languages and Tools for Reactive Systems

#### Contents

|  | 3.1 | Data-I                                        | Flow Based Modeling Formalisms                 | <b>26</b> |  |  |  |  |  |

|--|-----|-----------------------------------------------|------------------------------------------------|-----------|--|--|--|--|--|

|  |     | 3.1.1                                         | Kahn Process Network and Synchronous Data Flow | 26        |  |  |  |  |  |

|  |     |                                               | Kahn Process Network (KPN)                     | 26        |  |  |  |  |  |

|  |     |                                               | Synchronous Data Flow (SDF)                    | 26        |  |  |  |  |  |

|  |     | 3.1.2                                         | Data-Flow Synchronous Languages                | 27        |  |  |  |  |  |

|  |     |                                               | Lustre                                         | 27        |  |  |  |  |  |

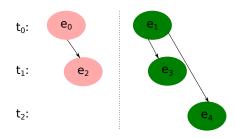

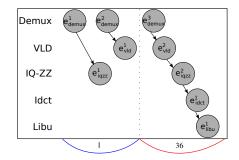

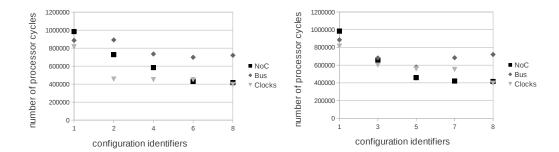

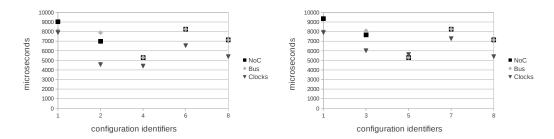

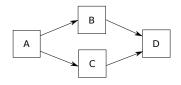

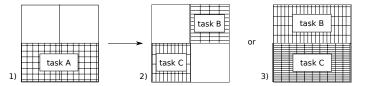

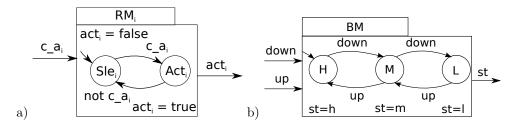

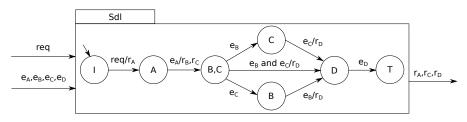

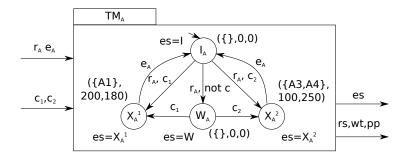

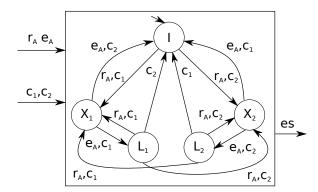

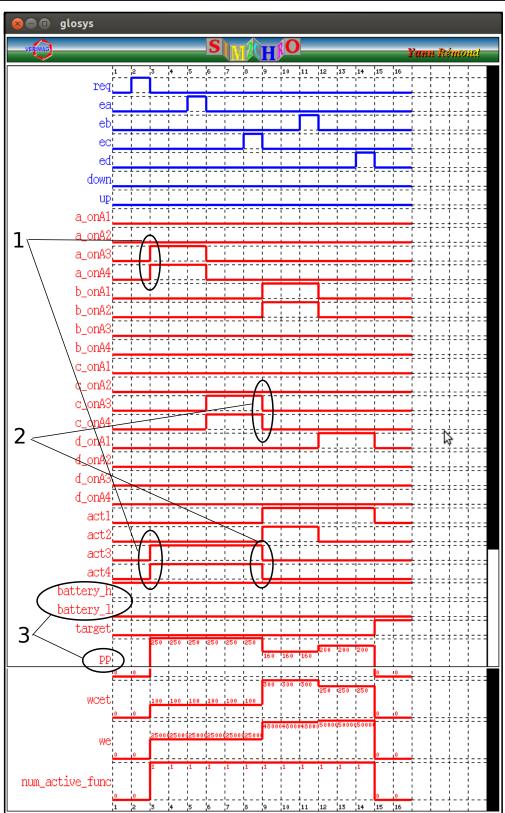

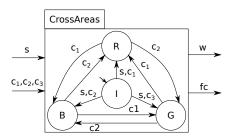

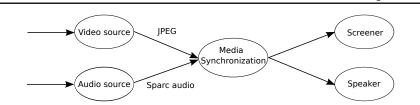

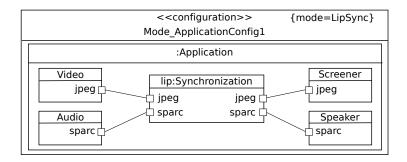

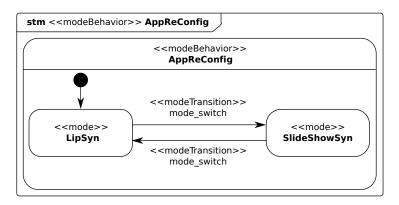

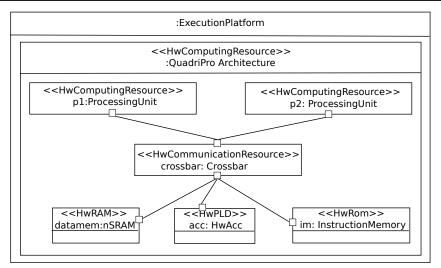

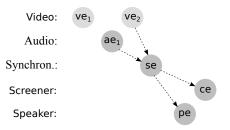

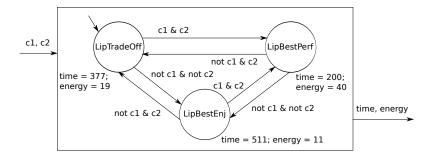

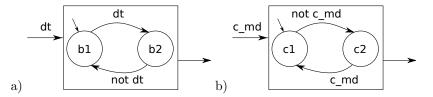

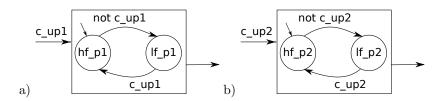

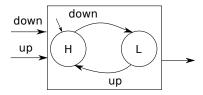

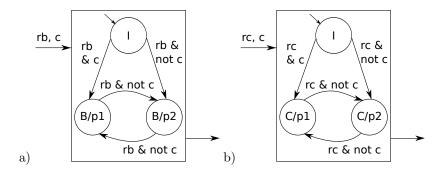

|  |     |                                               | Signal                                         | 29        |  |  |  |  |  |