### Management d'opérateurs communs dans les architectures de terminaux multistandards

Malek Naoues

#### ▶ To cite this version:

Malek Naoues. Management d'opérateurs communs dans les architectures de terminaux multistandards. Traitement du signal et de l'image [eess.SP]. Supélec, 2013. Français. NNT: . tel-00931390v1

### HAL Id: tel-00931390

https://theses.hal.science/tel-00931390v1

Submitted on 15 Jan 2014 (v1), last revised 22 Sep 2014 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre : 2013-26-TH

### **SUPELEC**

#### **Ecole Doctorale MATISSE**

« Mathématiques, Télécommunications, Informatique, Signal, Systèmes Electroniques »

### SUP'Com

**Ecole Supérieure des Communications de Tunis**

### THÈSE DE DOCTORAT

DOMAINE : STIC SPECIALITE : Télécommunications

Présentée par :

### **Malek NAOUES**

Sujet:

# Management d'opérateurs communs dans les architectures de terminaux multistandards

Soutenue le 26 Novembre 2013

devant les membres du jury :

M. Mohamed ABID Professeur à l'ENIS, Sfax Rapporteur M. Adel GHAZEL Professeur à Sup'com, Tunis Directeur de thèse M. Bertrand GRANADO Professeur à l'UPMC, Paris Rapporteur M. Khaled GRATI Maître assistant à Sup'Com, Tunis Co-encadrant M. Yves LOUET Professeur à Supélec Rennes Directeur de thèse M. Dominique NOGUET Expert senior CEA-LETI, Grenoble Co-encadrant M. Jacques PALICOT Professeur à Supélec, Rennes Examinateur M. Sami TABBANE Professeur à Sup'Com, Tunis Président

## Résumé

Les équipements de communications numériques intègrent de plus en plus de standards. Cette tendance se confirme et les équipements mettant en oeuvre ces standards se devront d'être reconfigurables pour deux raisons principales. Tout d'abord, la mise rapide sur le marché (time-to-market) impose de concevoir un nouvel équipement en réutilisant autant que possible les blocs de la version précédente. Ensuite, lors de l'utilisation de l'équipement, la commutation d'un standard à l'autre doit pouvoir se faire au prix d'un surcoût matériel modéré, ce qui impose l'utilisation de ressources communes à ces standards dans des instanciations différentes. Cette notion de reconfigurabilité introduite à tous les niveaux (couches physiques, piles protocolaires, applications) des systèmes radio (stations de base, terminaux) est donc fondamentale. La plateforme matérielle nécessaire à l'exécution d'une couche physique multistandard est le segment du système présentant le plus de contraintes par rapport à la reconfiguration : réactivité, consommation et occupation de ressources matérielles. Cependant, la réponse à ces contraintes ne réside pas dans un processeur généraliste puissant supportant l'ensemble des traitements comme l'avait défini les premiers travaux de la radio logicielle. Le défi est important de par le fait que l'utilisation seule de processeurs généralistes ne semble pas être une solution ni à court, ni à long terme. Une approche pragmatique de conception des plateformes reconfigurable est alors nécessaire pour traiter efficacement la diversité des fonctions en bande de base issues des différents standards.

La paramétrisation se situe parmi les techniques de reconfiguration actuelles et vise une implémentation multistandards plus efficace. L'objectif de cette technique est d'identifier des traitements communs entre les standards, voire entre blocs de traitement au sein d'un même standard, afin de définir des blocs génériques pouvant être réutilisés facilement. Dans ce contexte, l'approche des opérateurs communs (OC) a été proposée. Celle-ci consiste à identifier des entités, appelées opérateurs communs, utilisées massivement par les différents modules d'un équipement multistandards. Étant reconfigurables par un simple chargement de paramètres, les opérateurs communs permettent d'obtenir un équipement multistandards reconfigurable tout en limitant le nombre d'éléments physiques à implémenter. Par conséquent, cette approche vise principalement à concevoir des équipements évolutifs pouvant

4 RÉSUMÉ

s'adapter à un large éventail de standards.

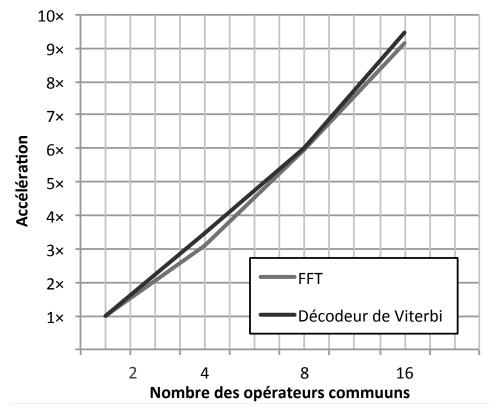

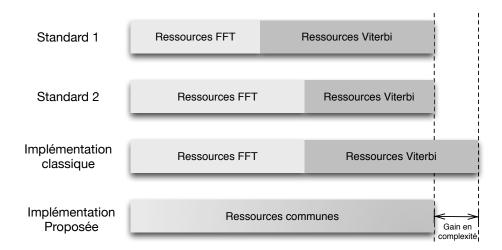

Le travail de recherche présenté propose une approche de conception qui a pour objectif de permettre le déploiement d'applications reconfigurables sur une plateforme matérielle hétérogène basée sur des opérateurs communs. Nous définissons dans ce manuscrit le management des opérateurs communs et nous étudions l'implémentation des opérateurs en se basant essentiellement sur des évaluations de complexité pour quelques standards utilisant la modulation OFDM. Nous montrons que les algorithmes de FFT et décodage de canal sont des traitements lourds en terme de calcul. Donc, nous nous concentrons sur la définition d'une technique de gestion efficace des ressources entre ces familles d'algorithmes en définissant une nouvelle structure matérielle d'un opérateur commun FFT/Viterbi. Nous proposons ainsi une architecture d'un processeur commun permettant la gestion efficace des ressources matérielles entre les algorithmes FFT et décodage de Viterbi. L'architecture, que nous avons proposé et implémenté sur FPGA, permet d'adapter le nombre d'opérateurs communs alloués à chaque algorithme et donc permet l'accélération des traitements.

Les résultats des implémentations montrent que l'utilisation de cette architecture commune offre des gains en complexité pouvant atteindre 30% dans les configurations testées par rapport à une implémentation classique avec une réduction importante de l'occupation mémoire due au partage de la mémoire entre les algorithmes. Ainsi, notre approche permet de profiter du partage des ressources et de parallélisme des traitements, non seulement pour ajouter de la flexibilité au design, mais aussi pour diminuer la complexité et la surface des circuits.

#### Mots-clés

Radio reconfigurable ; Conception flexible ; Paramétrisation ; Opérateurs communs ; FFT ; Décodage de Viterbi.

### Abstract

Today's telecommunication systems require more and more flexibility, and reconfiguration mechanisms are becoming major topics especially when it comes to multistandard designs. In typical hardware designs, the communication standards are implemented separately using dedicated instantiations which are difficult to upgrade for the support of new features. To overcome these issues, Software Defined Radio (SDR) describes a softwarereconfigurable multistandard, and multiband radios. The SDR technique is the main way to design flexible and reconfigurable architectures capable of supporting different transmission standards in a single platform. A digital communication chain, when supporting different standards, uses typical signal processing operations such as modulation, channel coding, equalization, etc. These common operations can be identified and then explored to take advantage of the commonalities among tasks in order to enhance power efficiency and area occupation. In this context, parameterization technique has been introduced in the area of digital communications. It consists in identifying the common aspects among the targeted modes and standards in order to define a generic operation capable of handling the required tasks. This generic operation can switch from a configuration to another by a simple change of its parameters.

In this work, we exploit a parameterization approach called the common operator technique that can be considered to build a generic terminal capable of supporting a large range of communication standards. The main principle of the common operator technique is to identify common elements based on smaller structures that could be widely reused across signal processing functions. This technique aims at designing a scalable terminal based on medium granularity operators, larger than basic logic cells and smaller than signal processing functions. Similarly to flip flop or logic gate, a Common Operator (CO) is used regardless of its calling functions. From this point, the common operator technique aims at being less standard dependent than the highest level reuse approaches where the functionality required by a standard is implemented and executed when needed. It is expected that the reduction of the exploration space to telecommunication baseband functions will help defining such medium-grain common operators. The resulted implementation is expected to be more flexible and scalable for a wide range of standards.

6 ABSTRACT

Such a regular structure is also well adapted to cope with silicon technology process variability. Indeed, as CMOS technology shrinks, the performance of the operator instances may vary across space (on the silicon wafer) and time. Dealing with regular building blocks helps to map the most demanding algorithms onto the best performing cells, making the design dependable and self-healing. Many previous works focused on defining implementing and managing the Common Operators are presented in this manuscript.

The present work deals with two widely used algorithms in wireless communication systems: Viterbi decoding and Fast Fourier Transform (FFT). These algorithms require a significant computational complexity, and combining them would result in a significant step forward. Implementing the FFT and Viterbi algorithms in a multistandard context through a common architecture poses significant architectural constraints. Indeed, to meet the needs of the Common Operators technique and support multiple standards, a flexible FFT/Viterbi processor architecture allowing variable FFT size and variable Viterbi constraint length is necessary. The idea is to divide the problem into equal parts for each algorithm and share equally the execution time in each physically implemented common butterfly units. In this thesis, we focus on the design of a flexible processor to manage the common operators and take advantage from structural similarities between FFT and Viterbi trellis.

A flexible FFT/Viterbi processor was proposed and implemented on FPGA and compared to dedicated hardware implementations. The results show a considerable gain in flexibility. This gain is achieved with no complexity overhead since the complexity if even decreased by more than 30% in some configurations.

### Keywords

Reconfigurable Radio ; Flexible Design ; Parametrization ; Common Operators : FFT : Viterbi.

## Remerciements

Les travaux de recherche présentés dans cette thèse de doctorat se sont déroulés principalement au sein du Laboratoire Solutions sans fil et Plateformes numériques (LSP) du Service Technologies de la Communication et de la Sécurité (STCS) au CEA-LETI à Grenoble. Je tiens à remercier toutes les personnes qui ont contribué de près ou de loin à la réalisation de ces travaux.

Je voudrais remercier aussi mes deux directeurs de thèse Prof. Yves Louët de Supélec Rennes et Prof. Adel Ghazel de SUP'Com Tunis. Leurs encadrements, les conseils et le soutien dont ils m'ont fait bénéficier durant ce travail se sont révélés précieux.

Je tiens à remercier Dominique Noguet mon encadrant CEA de m'avoir proposé le sujet de thèse pour sa disponibilité, les échanges d'idées et le suivi attentif tout au long de cette thèse. Je tiens à remercier aussi Khaled Grati, mon deuxième encadrant universitaire, pour son implication et conseils pendant mes séjours à SUP'Com.

Mes sincères remerciements s'adressent aussi aux membres du jury qui ont accepté d'évaluer ce travail.

En fin, je remercie les membres du service STCS au CEA-LETI et les membres des laboratoires GRESCOM à SUP'Com et IETR-SCEE à Supélec pour les échanges constructifs, les conseils, et les moments de distractions.

Tunis, Juin 2013 Malek Naoues

## Table des matières

| R  | ésum  | né                                                          | 3         |

|----|-------|-------------------------------------------------------------|-----------|

| Ta | able  | des figures                                                 | 11        |

| Li | ste d | les tableaux                                                | 13        |

| Li | ste d | les acronymes et abréviations                               | 15        |

| In | trod  | uction générale                                             | 19        |

| 1  | La    | technique des opérateurs communs                            | <b>25</b> |

|    | 1.1   | Introduction                                                | 25        |

|    | 1.2   | Contexte de la radio reconfigurable                         | 26        |

|    | 1.3   | Les plateformes de la radio reconfigurable                  | 28        |

|    |       | 1.3.1 Les contraintes des standards                         | 29        |

|    |       | 1.3.2 Plateforme de traitement parallèle                    | 30        |

|    |       | 1.3.3 Gestion des ressources                                | 32        |

|    | 1.4   | Réutilisation des ressources                                | 32        |

|    | 1.5   | La paramétrisation                                          | 35        |

|    |       | 1.5.1 Approache par fonctions communes                      | 36        |

|    |       | 1.5.2 Approche par opérateurs communs                       | 39        |

|    | 1.6   | Identification des opérateurs communs                       | 39        |

|    |       | 1.6.1 Approche théorique                                    | 40        |

|    |       | 1.6.2 Approche pragmatique                                  | 44        |

|    | 1.7   | Un premier jeu d'opérateurs communs                         | 44        |

|    |       | 1.7.1 Les opérateurs de faible granularité : LFSR et Cordic | 45        |

|    |       | 1.7.2 Les opérateurs à forte granularité : FFT et FEC $$    | 47        |

|    | 1.8   | Conclusion                                                  | 49        |

| 2  | Ma    | nagement des opérateurs communs                             | 51        |

|    | 2.1   | Introduction                                                | 51        |

|    | 2.2   | Définition du management des OCs                            | 52        |

|    |       | 2.2.1 Le management des OCs pendant la conception           | 53        |

|    |       | 2.2.2 Le management des OCs pendant l'exécution             | 53        |

|    | 2.2   | 2.2.3 Définition du problème de management des OCs |     |

|----|-------|----------------------------------------------------|-----|

|    | 2.3   | Techniques de management des OCs                   | 57  |

|    |       | 2.3.1 Couches logicielles de reconfiguration       |     |

|    |       | 2.3.2 Mécanismes de management des OCs             |     |

|    |       | 2.3.3 La librairie des opérateurs communs          |     |

|    |       | 2.3.4 Espace d'implémentation du manageur des OCs  |     |

|    | 2.4   | Considérations sur l'implémentation des OCs        |     |

|    |       | 2.4.1 Classification des accélérateurs matériels   |     |

|    |       | 2.4.2 Sélection des accélérateurs matériels        |     |

|    |       | 2.4.3 Analyse des coûts en traitement pour les OCs |     |

|    | 2.5   | Modèle d'architecture reconfigurable à base d'OCs  |     |

|    | 2.6   | Conclusion                                         | 75  |

| 3  |       | pérateur commun FFT/Viterbi                        | 77  |

|    | 3.1   | Introduction                                       | 77  |

|    | 3.2   | Similarités entre FFT et Viterbi                   | 78  |

|    |       | 3.2.1 Structure du décodeur de Viterbi             |     |

|    |       | 3.2.2 Structure de la FFT                          |     |

|    |       | 3.2.3 Vers une structure commune FFT/Viterbi       |     |

|    | 3.3   | Premières structures de l'OC FFT/Viterbi           |     |

|    | 3.4   | Structure optimisée pour l'OC FFT/Viterbi          |     |

|    |       | 3.4.1 Calcul du papillon FFT Radix-2 (1er mode)    |     |

|    |       | 3.4.2 Calcul du ACS (2ème mode)                    |     |

|    |       | 3.4.3 Calcul du BMC (3ème mode)                    |     |

|    | 3.5   | Comparaison des implémentations proposées          | 96  |

|    | 3.6   | Le jeu d'opérateurs FFT/FEC                        | 98  |

|    | 3.7   | Conclusion                                         | 99  |

| 4  | Mé    | canismes de management de l'operateur FFT/Viterbi  | 101 |

|    | 4.1   | Introduction                                       |     |

|    | 4.2   | Contraintes sur le mgmt. de l'OC FFT/Viterbi       |     |

|    | 4.3   | Architectures de mgmt. de l'OC FFT/Viterbi         | 104 |

|    |       | 4.3.1 Architecture en pipeline                     | 105 |

|    |       | 4.3.2 Architecture à colonne partielle             | 107 |

|    |       | 4.3.3 Architecture séléctionnée                    | 110 |

|    | 4.4   | Mgmt. des interconnexions en colonne partielle     | 111 |

|    |       | 4.4.1 Génération des interconnexions               | 112 |

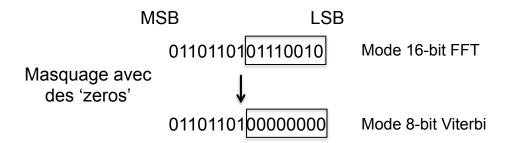

|    |       | 4.4.2 Mgmt. des largeurs de chemin de données      | 112 |

|    | 4.5   | Implémentation du processeur FFT/Viterbi           | 113 |

|    |       | 4.5.1 Description de l'architecture implémentée    | 113 |

|    |       | 4.5.2 Résultats de l'implémentation                |     |

|    | 4.6   | Conclusion                                         | 115 |

| Co | onclu | usion générale                                     | 119 |

|       |     |     | `   |    |

|-------|-----|-----|-----|----|

| TABLE | DES | MAT | IER | ES |

| Pυ           | ıblica | ations de l'auteur                                | 123 |

|--------------|--------|---------------------------------------------------|-----|

| $\mathbf{A}$ | Teri   | minologie et concepts des systèmes radio avancés  | 125 |

|              | A.1    | La radio matérielle                               | 125 |

|              | A.2    | La radio reconfigurable                           | 126 |

|              | A.3    | La radio contrôlée par logiciel                   | 126 |

|              | A.4    | La radio logicielle                               | 126 |

|              |        | La radio adaptative                               |     |

|              |        | La radio cognitive                                |     |

|              | A.7    | La radio intelligente                             | 127 |

| В            | L'or   | pérateur commun transformée de Fourier rapide     | 129 |

|              | B.1    | Utilisation dans les modulations multi-porteuses  | 130 |

|              | B.2    | Utilisation dans le codage canal                  | 131 |

|              | B.3    | Utilisation dans la convolution et de corrélation | 132 |

|              | B.4    | Utilisation dans d'autres fonctions               | 133 |

| Bi           | bliog  | raphie                                            | 135 |

# Table des figures

| 1.1  | Différents types de « Handover »                               | 27 |

|------|----------------------------------------------------------------|----|

| 1.2  | Exemple d'une implémentation classique d'un récepteur          | 27 |

| 1.3  | Rapport flexibilité/performance des circuits en BB             | 29 |

| 1.4  | Le circuit MAGALI                                              | 31 |

| 1.5  | Exemple de partage des ressources entre trois standards        | 32 |

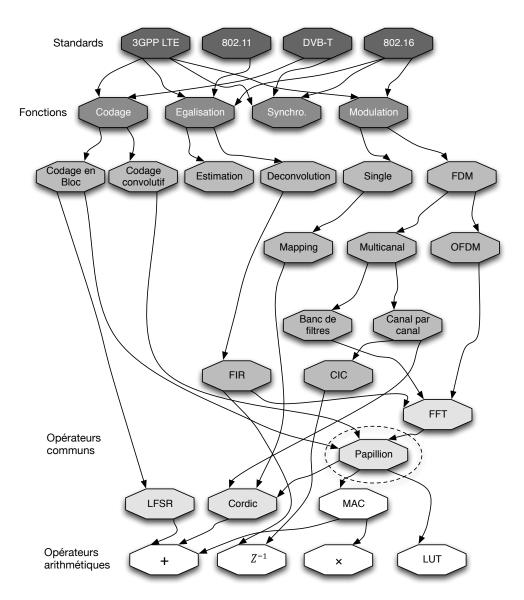

| 1.6  | Les fonctions réalisées par un processeur de traitement en BB  | 34 |

| 1.7  | Classification des traitements communs proposée par Alaus  .   | 35 |

| 1.8  | Fonction de modulation paramétrable                            | 37 |

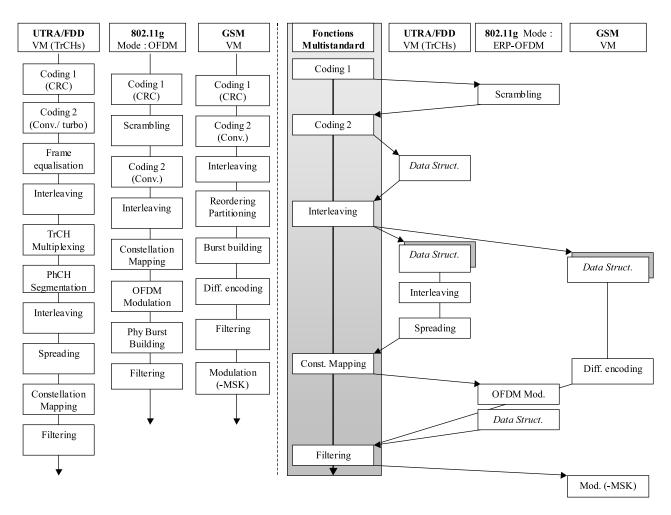

| 1.9  | Vers une chaîne de transmission multistandards unifiée         | 38 |

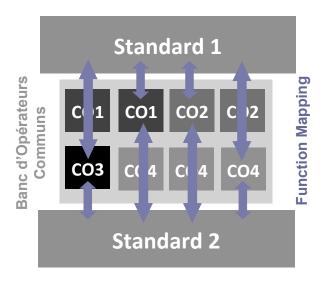

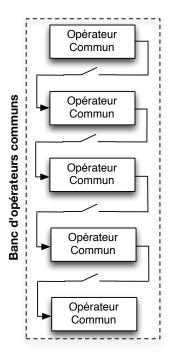

| 1.10 | Banc d'opérateurs communs                                      | 40 |

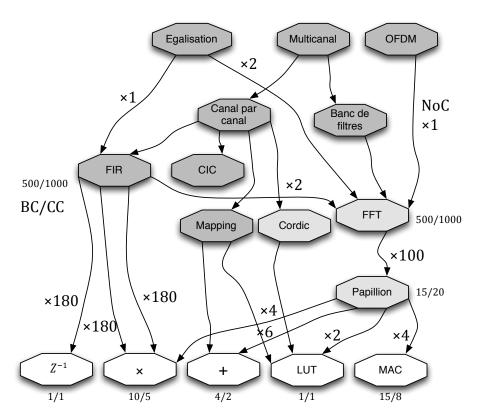

| 1.11 | Exemple de décomposition partielle en graphe des OCs           | 41 |

| 1.12 | Exemple de décomposition en graphe avec les coûts associés .   | 42 |

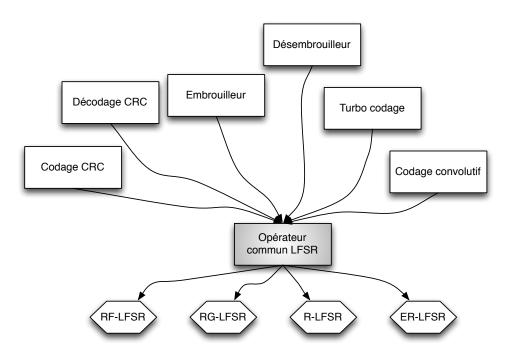

| 1.13 | Illustration de l'utilisation des opérateurs LFSR              | 45 |

| 1.14 | Etage itératif pour les opérateurs LFSR ou Cordic              | 47 |

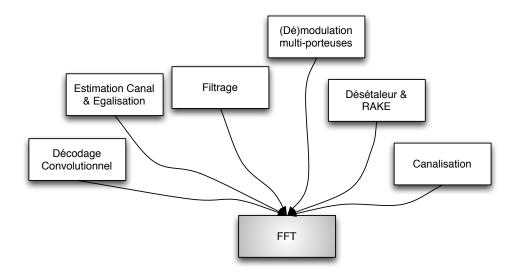

| 1.15 | Illustration de l'utilisation de l'opérateur FFT               | 48 |

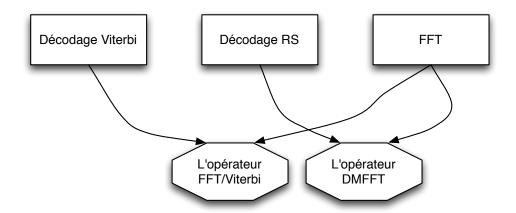

| 1.16 | Partage des opérateurs communs entre la FFT, RS et Viterbi     | 49 |

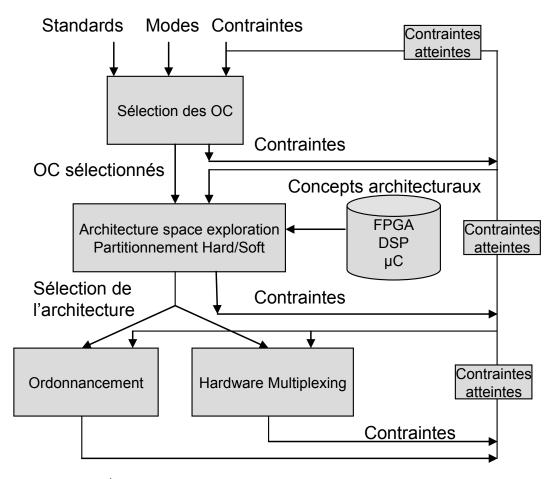

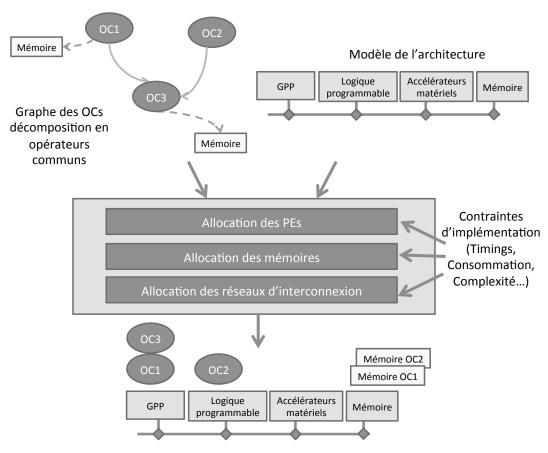

| 2.1  | Étapes de conception d'un équipement avec la tech. des OCs     | 54 |

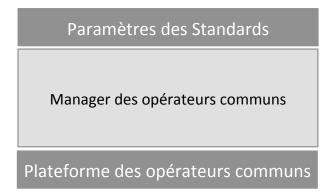

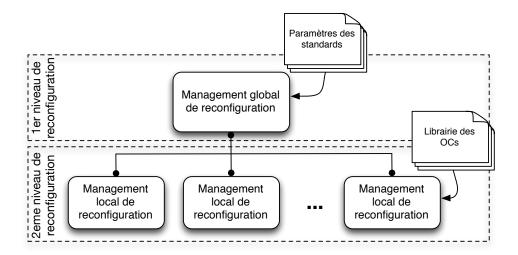

| 2.2  | Représentation en couches du manager des OCs                   | 55 |

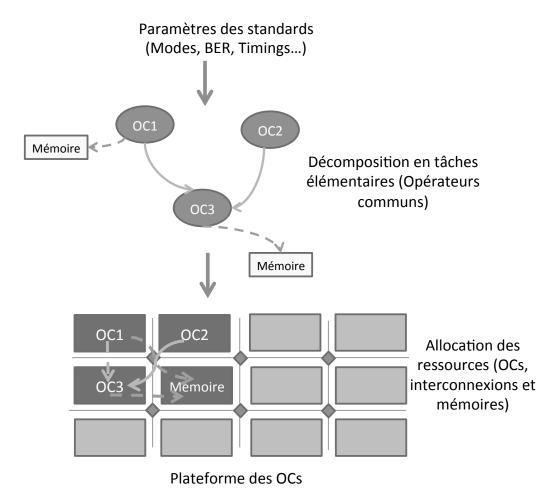

| 2.3  | Étapes du management des OCs                                   | 57 |

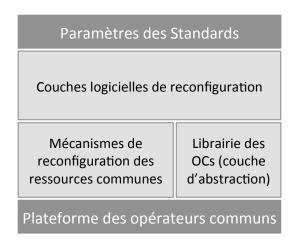

| 2.4  | Les composants du manager des OCs                              | 58 |

| 2.5  | Mécanismes de management des OCs                               | 60 |

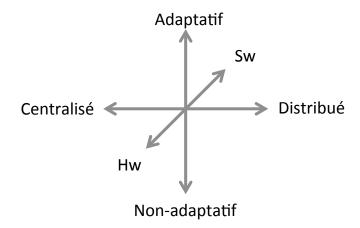

| 2.6  | Degrés de libertés dans l'implémentation du manager des OCs    | 62 |

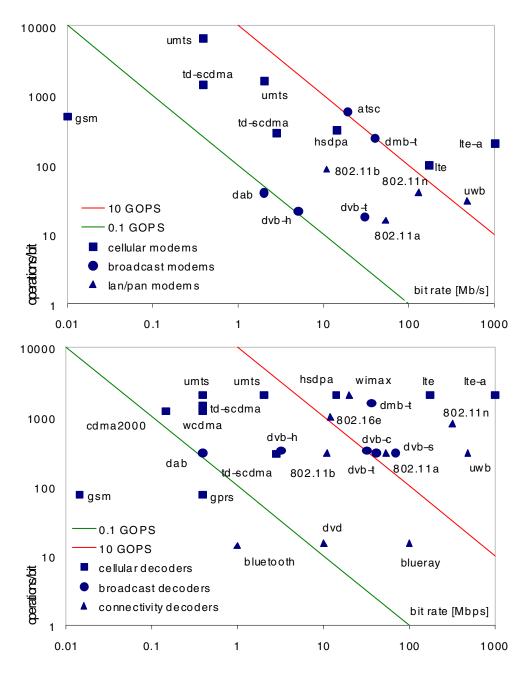

| 2.7  | Les besoins de calculs pour la (dé)modulation et le décodage   | 65 |

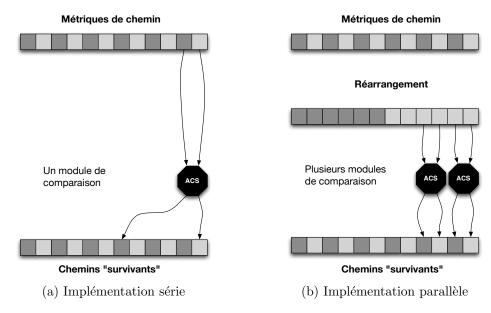

| 2.8  | Parallélisations des traitements pour le décodeur de Viterbi . | 72 |

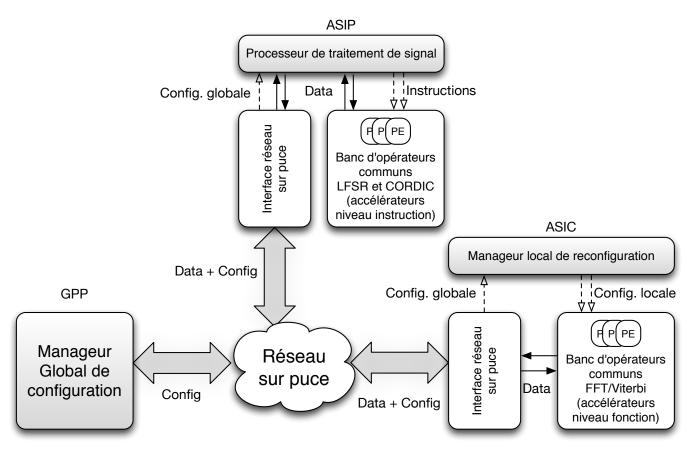

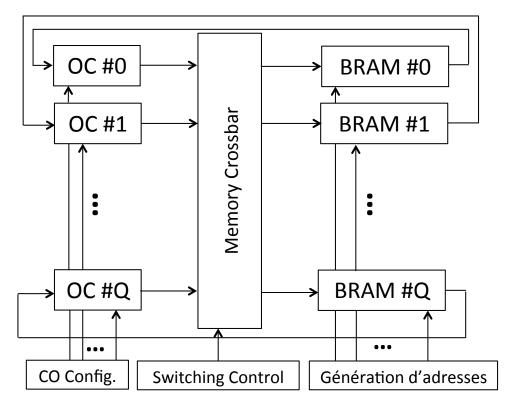

| 2.9  | Modèle de gestion de configuration des OCs                     | 73 |

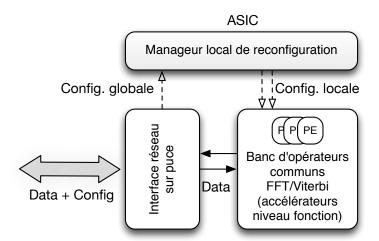

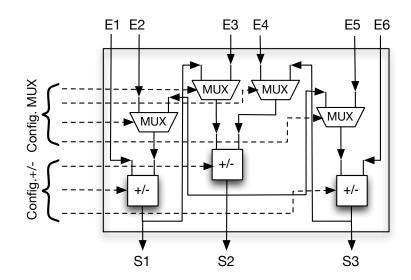

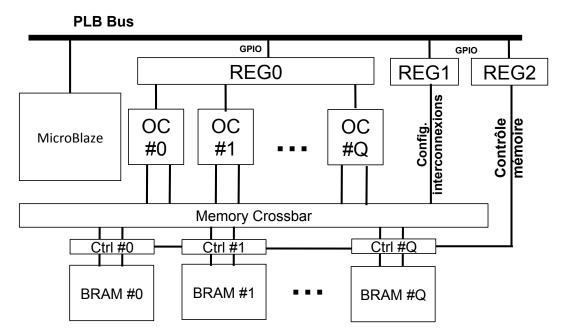

| 2.10 | Architecture de management local de l'OC FFT/Viterbi           | 74 |

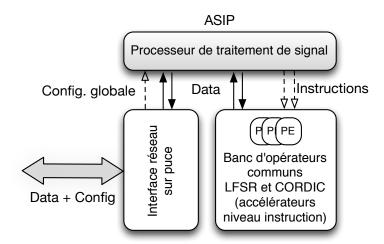

| 2.11 | Architecture de management local de l'OC LFSR et CORDIC        | 75 |

| 2.12 | <u> </u>                                                       | 76 |

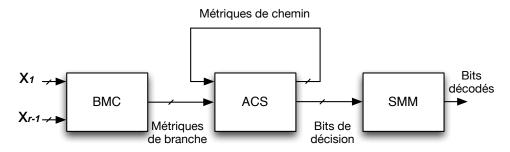

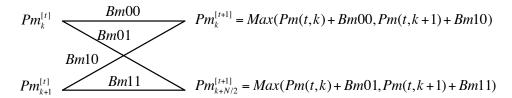

| 3.1  | Structure globale d'un décodeur de Viterbi                     | 79 |

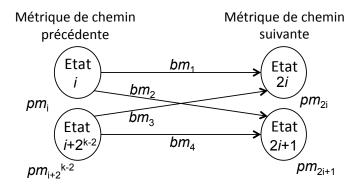

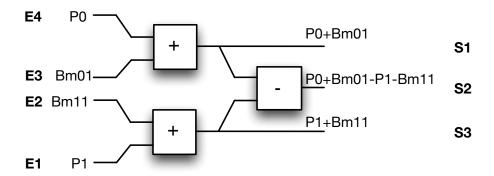

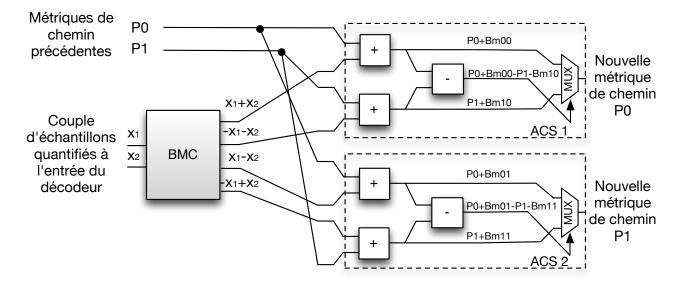

| 3.2  | Le papillon Viterbi et l'actualisation des métriques de chemin | 79 |

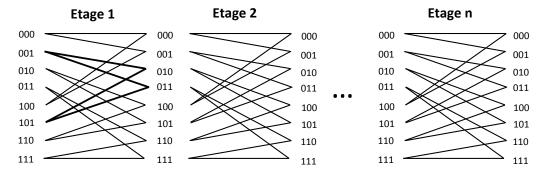

| 3.3  | La représentation du treillis Viterbi                          | 81 |

|      |                                                                |    |

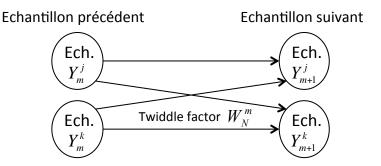

| 3.4                                                                          | Le papillon FFT Radix-2                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82                                                             |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

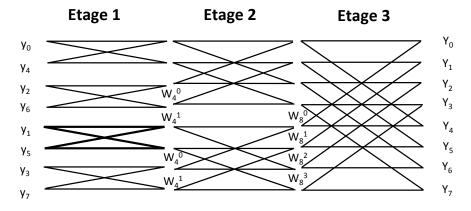

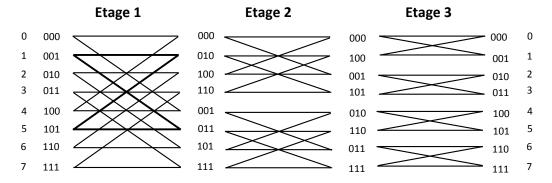

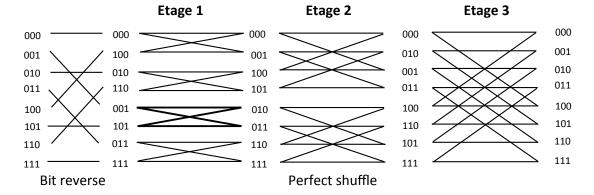

| 3.5                                                                          | La représentation du treillis FFT                                                                                                                                                                                                                                                                                                                                                                                                                       | 82                                                             |

| 3.6                                                                          | Repréentation commune du treillis FFT et Viterbi DIF                                                                                                                                                                                                                                                                                                                                                                                                    | 83                                                             |

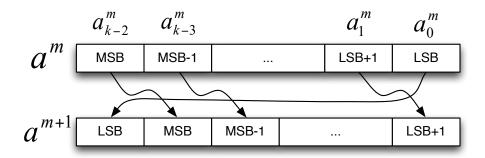

| 3.7                                                                          | Génération des adresses pour les papillons Viterbi et FFT                                                                                                                                                                                                                                                                                                                                                                                               | 84                                                             |

| 3.8                                                                          | Repréentation commune du treillis FFT et Viterbi DIT                                                                                                                                                                                                                                                                                                                                                                                                    | 84                                                             |

| 3.9                                                                          | Opérateur AS3                                                                                                                                                                                                                                                                                                                                                                                                                                           | 85                                                             |

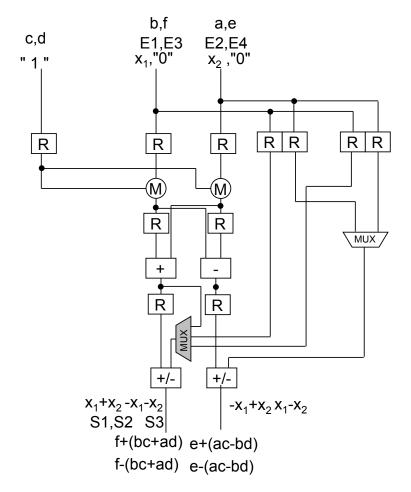

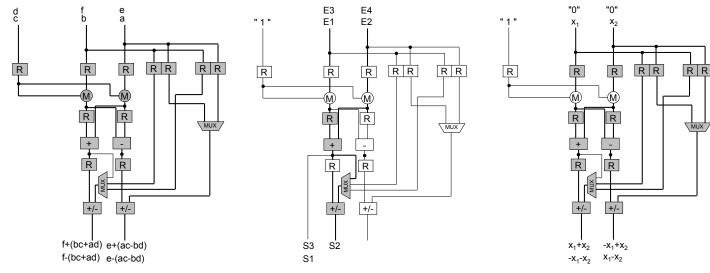

| 3.10                                                                         | Opérateur commun FFT/Viterbi parallèle                                                                                                                                                                                                                                                                                                                                                                                                                  | 86                                                             |

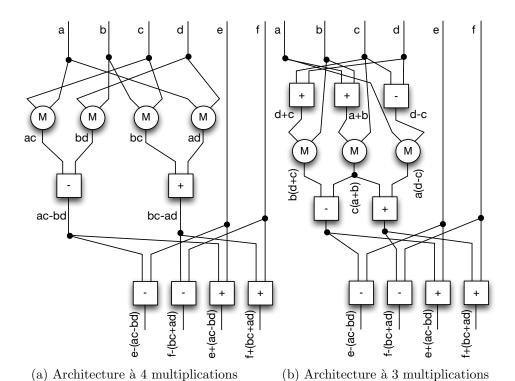

| 3.11                                                                         | Architectures du papillion FFT Radix-2 (2 et 3 multiplications)                                                                                                                                                                                                                                                                                                                                                                                         | 87                                                             |

| 3.12                                                                         | Architecture du papillon FFT Radix-2 à 2 multiplications $$                                                                                                                                                                                                                                                                                                                                                                                             | 88                                                             |

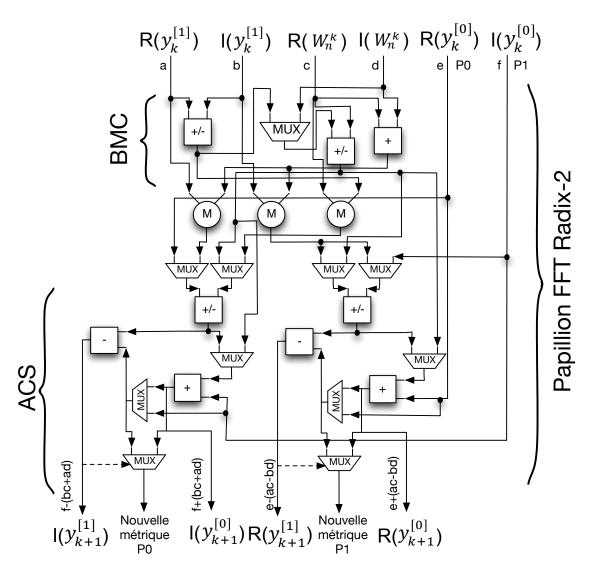

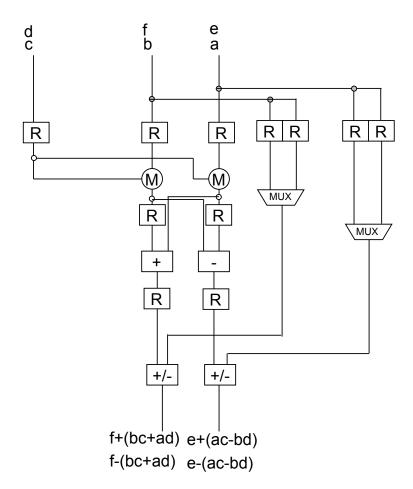

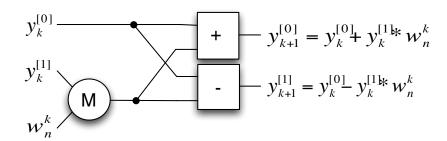

| 3.13                                                                         | Cellule en pipeline proposée pour les algorithmes FFT et Viterbi                                                                                                                                                                                                                                                                                                                                                                                        | 90                                                             |

| 3.14                                                                         | Structure du papillon FFT Radix-2                                                                                                                                                                                                                                                                                                                                                                                                                       | 91                                                             |

| 3.15                                                                         | Les trois modes de fonctionnement de la cellule proposée                                                                                                                                                                                                                                                                                                                                                                                                | 92                                                             |

| 3.16                                                                         | Implémentation des opérations de calcul de chemins                                                                                                                                                                                                                                                                                                                                                                                                      | 93                                                             |

| 3.17                                                                         | Entrées/Sorties du papillion de Viterbi                                                                                                                                                                                                                                                                                                                                                                                                                 | 94                                                             |

| 3.18                                                                         | Représentation schématique des opérations BMC et ACS                                                                                                                                                                                                                                                                                                                                                                                                    | 95                                                             |

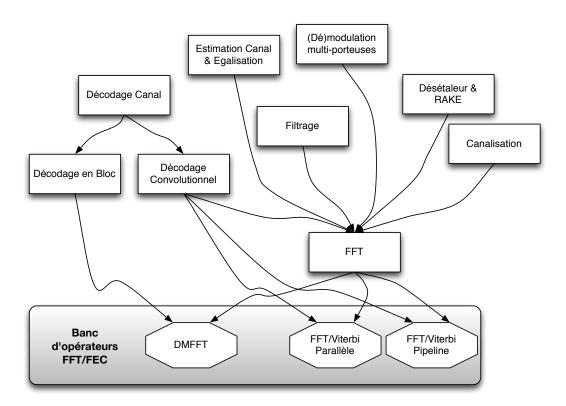

| 3.19                                                                         | Jeu d'opérateurs FFT/FEC                                                                                                                                                                                                                                                                                                                                                                                                                                | 98                                                             |

| 1 1                                                                          | Everente d'architecture novellèle à méanaétrie constants                                                                                                                                                                                                                                                                                                                                                                                                | 109                                                            |

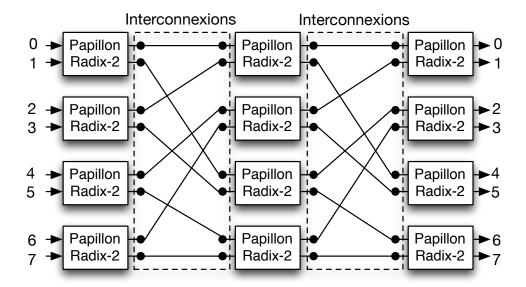

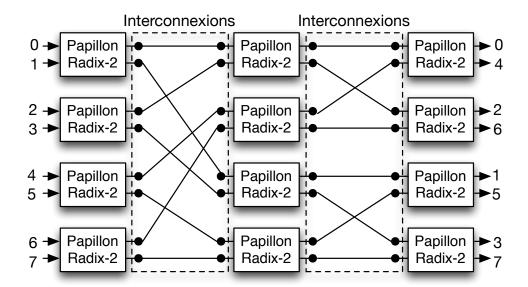

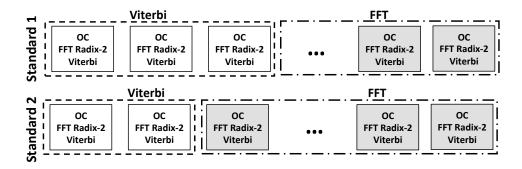

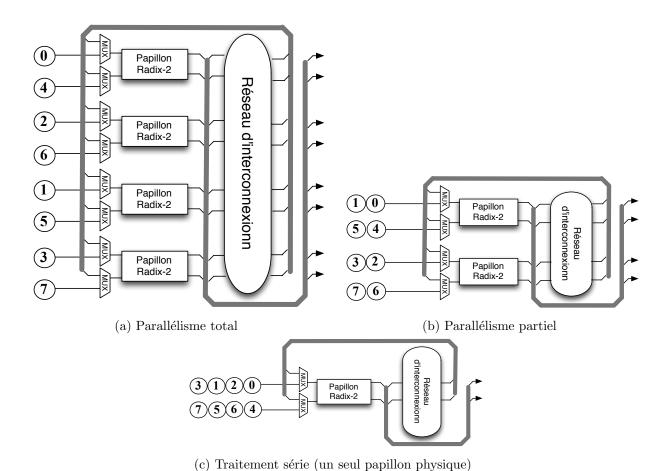

| 4.1                                                                          | Exemple d'architecture parallèle à géométrie constante                                                                                                                                                                                                                                                                                                                                                                                                  | 103                                                            |

| 4.2                                                                          | Exemple d'architecture parallèle à géométrie variable                                                                                                                                                                                                                                                                                                                                                                                                   | 103                                                            |

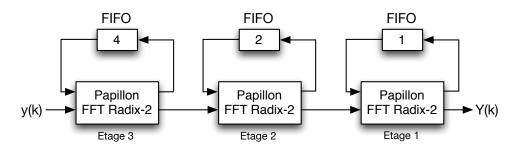

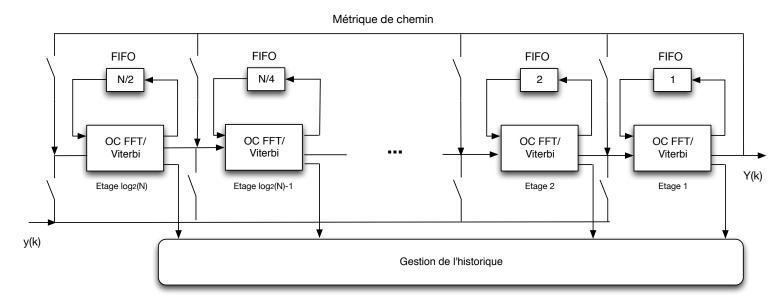

|                                                                              | Exemple d'architecture parallèle à géométrie variable                                                                                                                                                                                                                                                                                                                                                                                                   | 103<br>104                                                     |

| 4.2                                                                          | Exemple d'architecture parallèle à géométrie variable                                                                                                                                                                                                                                                                                                                                                                                                   | 103                                                            |

| $4.2 \\ 4.3$                                                                 | Exemple d'architecture parallèle à géométrie variable                                                                                                                                                                                                                                                                                                                                                                                                   | 103<br>104                                                     |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6                                              | Exemple d'architecture parallèle à géométrie variable Allocation dynamique des ressources entre les algorithmes Architecture en pipeline classique d'une FFT Radix-2 Architecture en pipeline pour le mgmt. de l'OC FFT/Viterbi Exemple d'adaptation du parallélisme des traitements                                                                                                                                                                    | 103<br>104<br>105<br>106<br>109                                |

| 4.2<br>4.3<br>4.4<br>4.5                                                     | Exemple d'architecture parallèle à géométrie variable                                                                                                                                                                                                                                                                                                                                                                                                   | 103<br>104<br>105<br>106                                       |

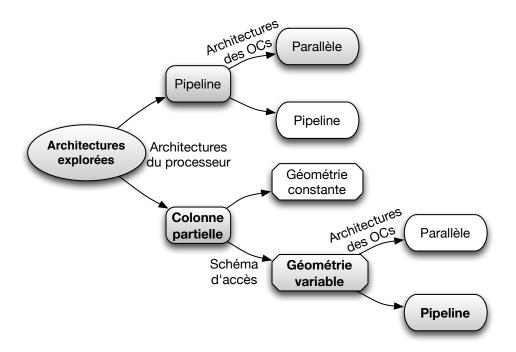

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                                | Exemple d'architecture parallèle à géométrie variable Allocation dynamique des ressources entre les algorithmes Architecture en pipeline classique d'une FFT Radix-2 Architecture en pipeline pour le mgmt. de l'OC FFT/Viterbi Exemple d'adaptation du parallélisme des traitements Architecture à colonne partielle du processeur FFT/Viterbi Exploration des architectures de gestion de l'OC FFT/Viterbi                                            | 103<br>104<br>105<br>106<br>109<br>110                         |

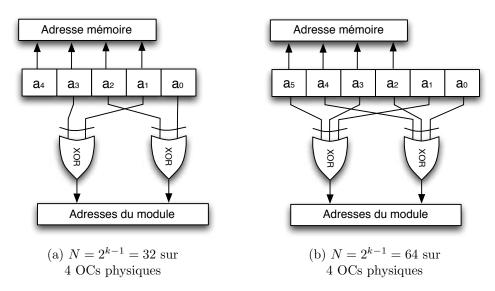

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7                                       | Exemple d'architecture parallèle à géométrie variable Allocation dynamique des ressources entre les algorithmes Architecture en pipeline classique d'une FFT Radix-2 Architecture en pipeline pour le mgmt. de l'OC FFT/Viterbi Exemple d'adaptation du parallélisme des traitements Architecture à colonne partielle du processeur FFT/Viterbi . Exploration des architectures de gestion de l'OC FFT/Viterbi Exemple de génération d'adresses mémoire | 103<br>104<br>105<br>106<br>109<br>110<br>111                  |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                                | Exemple d'architecture parallèle à géométrie variable Allocation dynamique des ressources entre les algorithmes Architecture en pipeline classique d'une FFT Radix-2 Architecture en pipeline pour le mgmt. de l'OC FFT/Viterbi Exemple d'adaptation du parallélisme des traitements Architecture à colonne partielle du processeur FFT/Viterbi . Exploration des architectures de gestion de l'OC FFT/Viterbi Exemple de génération d'adresses mémoire | 103<br>104<br>105<br>106<br>109<br>111<br>111<br>112           |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                         | Exemple d'architecture parallèle à géométrie variable Allocation dynamique des ressources entre les algorithmes Architecture en pipeline classique d'une FFT Radix-2 Architecture en pipeline pour le mgmt. de l'OC FFT/Viterbi Exemple d'adaptation du parallélisme des traitements Architecture à colonne partielle du processeur FFT/Viterbi . Exploration des architectures de gestion de l'OC FFT/Viterbi Exemple de génération d'adresses mémoire | 103<br>104<br>105<br>106<br>109<br>111<br>111<br>112           |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12 | Exemple d'architecture parallèle à géométrie variable Allocation dynamique des ressources entre les algorithmes Architecture en pipeline classique d'une FFT Radix-2 Architecture en pipeline pour le mgmt. de l'OC FFT/Viterbi Exemple d'adaptation du parallélisme des traitements Architecture à colonne partielle du processeur FFT/Viterbi . Exploration des architectures de gestion de l'OC FFT/Viterbi Exemple de génération d'adresses mémoire | 103<br>104<br>105<br>106<br>110<br>111<br>1112<br>1113<br>1114 |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12 | Exemple d'architecture parallèle à géométrie variable Allocation dynamique des ressources entre les algorithmes Architecture en pipeline classique d'une FFT Radix-2 Architecture en pipeline pour le mgmt. de l'OC FFT/Viterbi Exemple d'adaptation du parallélisme des traitements Architecture à colonne partielle du processeur FFT/Viterbi . Exploration des architectures de gestion de l'OC FFT/Viterbi Exemple de génération d'adresses mémoire | 103<br>104<br>105<br>106<br>109<br>111<br>111<br>113<br>114    |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12 | Exemple d'architecture parallèle à géométrie variable Allocation dynamique des ressources entre les algorithmes Architecture en pipeline classique d'une FFT Radix-2 Architecture en pipeline pour le mgmt. de l'OC FFT/Viterbi Exemple d'adaptation du parallélisme des traitements Architecture à colonne partielle du processeur FFT/Viterbi . Exploration des architectures de gestion de l'OC FFT/Viterbi Exemple de génération d'adresses mémoire | 103<br>104<br>105<br>106<br>110<br>111<br>1112<br>1113<br>1114 |

## Liste des tableaux

| 1.1 | Evolution des besoins des standards                             | 30  |

|-----|-----------------------------------------------------------------|-----|

| 2.1 | Domaines à explorer pour le management des opérateurs com-      |     |

|     | muns                                                            | 53  |

| 2.2 | Coûts d'implémentation des terminaux W-CDMA et 802.11a          |     |

|     | sur un GPP                                                      | 66  |

| 2.3 | Classification du degré de programmabilité pour quelques fonc-  |     |

|     | tions de traitement de signal                                   | 67  |

| 2.4 | Coût en MOCPS pour quelques standards à base de la modu-        |     |

|     | lation OFDM                                                     | 68  |

| 2.5 | Comparaison des implémentations matérielles et logicielles des  |     |

|     | FFTs Radix-2                                                    | 69  |

| 2.6 | Contraintes des standards considérés pour le décodeur           | 71  |

| 2.7 | Contraintes des standards considérés pour le décodeur en cycles |     |

|     | par bit décodé                                                  | 71  |

| 3.1 | Comparaisons de consommation entre les architectures de pa-     |     |

|     | pillons à 2 et à 3 multiplieurs                                 | 89  |

| 3.2 | Comparaisons de complexité des opérateurs FFT/Viterbi $$ .      | 97  |

| 4.1 | Comparaison des ressources utilisées entre une implémentation   |     |

|     | classique et architecture proposée                              | 116 |

| 4.2 | Comparaison des performances de l'opérateur FFT/Viterbi         |     |

|     | par rapport à une cellule classique FFT-Radix 2                 | 116 |

## Liste des acronymes et abréviations

**2G** Mobile de 2nd Generation

**3G** Mobile de 3rd Generation

**3GPP LTE** 3rd Generation Partership Project Long Term Evolution

4G Mobile de 4rd Generation

ACS Add-Compare-Select

**ADC** Analog-to-Digital Converter

**ASIC** Application Specific Integrated Circuit

**ASIP** Application Specific Instruction set Processor

**BOC** Banc d'Opérateurs Communs

BMC Branch Metric Calculation

**BRAM** Block RAM

**CORDIC** Coordinate Rotation Digital Computer

**CRC** Cyclic Redundancy Check

**DAC** Digital-to-Analog Converter

**DECT** Digital Enhanced Cordless Telecommunications

**DFT** Discrete Fourier Transform

**DIF** Decimation In Frequency

$\mathbf{DIT}\:$  Decimation In Time

**DSP** Digital Signal Processor

**DVB** Digital Video Broadcasting

WIFI Wireless Fidelity ou IEEE802.11

**EDGE** Enhanced Data rates for GSM Evolution

**FDD** Frequency-Division Duplexing

FDM Frequency Division Multiplexing

FEC Forward Error Correction

**FFT** Fast Fourier Transform

**FIFO** First-In-First-Out

FIR Finite Impulse Response

FLMS Frequency Domain Least Mean Square

FPGA Field Programmable Gate Array

**GF** Galois Field

GIPS Giga Instruction per second

GMSK Gaussian Minimum Shift Keying

GPP General Purpose Processor

**GPRS** General Packet Radio Service

**GSM** Global System for Mobile communications

**HSPA** High Speed Downlink Package Access

**HW** Hardware

IEEE the Institute of Electrical and Electronics Engineers

**IF** Intermediate Frequency

IFFT Inverse Fast Fourier Transform

**IP** Intellect Property

LFSR Linear Feedback Shift Register

LSB Least Significant Bit

**LUT** LookUp Table

M Multiplier

MAC Media Access Control

MIPS Million Instruction per Seconde

MPSoC Multiprocessor System-on-Chip

MSB Most Significant Bit

MUX Multiplexer

**NoC** Network-on-Chip

OC Opérateur Commun

**OFDM** Orthogonal Frequency Division Multiplexing

PE Processing Element

**QAM** Quadrature Amplitude Modulation

**QPSK** Quadrature Phase Shift Keying

R Register

RAM Random-Access Memory

RF Radio fréquence

**RL** Radio Logicielle

RI Radio Intelligente

**RS** Reed-Solomon

SDR Software Defined Radio

SIMD Single Instruction stream, Multiple Data stream

SMM Survivor Memory Management

SoC System-on-Chip

SDF Single-path Delay Feedback

SW Software

UMTS Universal Mobile Telecommunications System

UWB Ultra-WideBand

VHDL Very High Speed Integrated Circuit Hardware Description Language

VLSI Very-Large-Scale Integration

W-CDMA Wideband Code Division Multiple Access

WIMAX Worldwide éInteroperability For Microwave Access

WWRF Wireless World Research Forum

XOR eXclusive-OR

## Introduction

La prolifération des solutions reconfigurables constitue une évolution considérable dans le domaine des radiocommunications qui a déjà été partiellement amorcée avec le développement des équipements multi-modes et multi-bandes. Cette évolution est alimentée par les demandes croissantes des communications sans fil pour un large éventail de besoins. A titre d'exemple, en 2012 il y a déjà plus de 4 milliards d'utilisateurs de téléphones mobiles dans le monde. De plus, des estimations telles que celles du Forum mondial de recherche sans fil (WWRF) prévoient que d'ici 2017 il y aura 7 billions d'appareils sans fil desservant 7 milliards d'utilisateurs [1]. Pour répondre à ces attentes avec la limitation du spectre radio, des méthodes plus souples pour partager les ressources matérielles et spéctrales entre plusieurs services et réseaux de communication sont nécessaires. À cet égard, il y a un intérêt croissant pour les solutions reconfigurables qui permettent la cohabitation de plusieurs systèmes radios dans le même équipement <sup>1</sup> multistandards [2]. Dans ce contexte, le concept de radio logicielle [3] a poussé les travaux de recherches vers les techniques de traitement pouvant s'adapter à plusieurs standards. Une architecture radio logicielle idéale est constituée d'une antenne large bande directement suivie par un convertisseur analogique/numérique à haute fréquence d'échantillonnage permettent à un circuit de type processeur de traiter ensuite un signal numérique contenant l'ensemble des signaux caractérisant une radio multistandards. La reprogrammabilité des processeurs permet l'adaptation des traitements numériques aux différents standards par simple téléchargement des logiciels. Toutefois, il existe à l'heure actuelle de nombreuses limitations technologiques ne permettant pas de concrétiser un tel concept, dont par exemple le manque de puissance de calcul, la forte consommation des processeurs, les limites de performances des convertisseurs et la limitation en terme de bande passante des circuits Radio Fréquence (RF).

La réalisation classique d'équipements multistandards se limite à la juxtaposition au sein d'un même équipement les différentes chaînes de traitement des modes et/ou standards ciblés. Cette solution, dite Velcro [4], permet de

<sup>1.</sup> Ce terme sera utilisé pour désigner indifféremment un terminal, une station de base ou un modem de télécommunication capable de traiter plusieurs modes ou plusieurs standards de communication.

22 INTRODUCTION

traiter plusieurs standards par le biais d'un seul équipement. Néanmoins, son évolutivité est limitée aux standards considérés initialement et la complexité de sa mise en œuvre, voire la consommation, ne sont pas optimales. En effet, la complexité de la solution classique correspond à la somme des complexités de chaque standard à laquelle s'ajoute celle des organes de reconfiguration. La paramétrisation [5] [6] se situe parmi les techniques de reconfiguration actuelles et vise une implémentation multistandards plus efficace. L'objectif de cette technique est d'identifier des traitements communs entre les standards, voire entre blocs de traitement au sein d'un même standard, afin de définir des blocs génériques pouvant être implémentés indépendamment des spécifications des normes. Dans ce contexte, l'approche des opérateurs communs (OC) [7] a été proposée. Celle-ci consiste à identifier des entités, appelées opérateurs communs, utilisées massivement par les différents modules d'un équipement multistandards. La granularité de ces opérateurs communs se situe à un niveau intermédiaire entre les fonctions de hauts niveaux et les opérateurs arithmétiques de bas niveaux (opérateurs MAC<sup>2</sup> par exemple). La définition d'un opérateur commun est fondée sur des aspects fonctionnels et structurels et est effectuée indépendamment des standards. Ainsi, un opérateur commun est défini pour effectuer des opérations élémentaires de traitement du signal indépendamment de la fonction qui l'exécute. Étant reconfigurables par un simple chargement de paramètres, ils permettent d'obtenir un équipement multistandards reconfigurable tout en limitant le nombre d'éléments physiques à implémenter. Par conséquent, cette approche vise principalement à concevoir des équipements évolutifs pouvant s'adapter à un large éventail de standards.

### Problématique

Plusieurs travaux réalisés au sein de l'équipe SCEE à Supélec et au CEA-LETI ont permis la définition de plusieurs opérateurs communs (thèses d'Al-Ghouwayel [8], Wang [9] et Alaus [10]). D'autres travaux des mêmes équipes ont traité l'identification des opérateurs communs en se basant sur une approche mathématique avec la théorie des graphes (thèses de Gul [11] et Kaiser [12]). Cependant, tous ces travaux se limitent à l'identification et la définition des opérateurs communs et ne traîtent pas à la gestion de ces opérateurs dans un contexte multistandards. En effet, face à la diversité des traitements numériques et à l'hétérogénéité incontournable des ressources pour répondre efficacement aux besoins de traitement, il est nécessaire d'offrir une architecture de management des opérateurs communs répondant à la fois aux besoins de changement de contextes applicatifs et capable d'exploiter la reconfigurabilité offerte par une plateforme hétérogène des opérateurs. Donc nous pouvons résumer la problématique abordée dans cette thèse par la définition

<sup>2.</sup> Multiply-ACcumulate

des techniques et mécanismes de management des opérateurs communs dans un contexte multistandards et l'amélioration du jeu d'opérateurs existant.

#### Contributions

Les contributions de ces travaux s'articulent, autour du management des opérateurs communs, sur trois thèmes complémentaires :

- Définition du management des opérateurs communs.

- Proposition d'une nouvelle structure matérielle d'un opérateur pour les algorithmes de FFT et Viterbi.

- Définition des mécanismes de management pour l'opérateur FFT/Viterbi en implémmenant des architectures communes aux deux algorithmes sur FPGA.

Les travaux décrits dans ce manuscrit proposent un modèle fonctionnel qui a pour objectif de permettre le déploiement des applications reconfigurables sur une plateforme matérielle hétérogène basée sur les opérateurs communs. Nous définissons donc le management des opérateurs communs et nous étudions leurs implémentations en se basant essentiellement sur des évaluations de complexité pour quelques standards utilisant la modulation OFDM. Nous montrons que les algorithmes de FFT et décodage de canal sont des traitements lourds en terme de calcul. Donc, nous nous concentrons sur la définition d'une technique de gestion efficace des ressources entre ces familles d'algorithmes en définissant une nouvelle structure matérielle d'un opérateur FFT/Viterbi. Nous proposons ainsi une architecture d'un processeur commun permettant la gestion efficace des ressources matérielles entre les algorithmes FFT et Viterbi. L'architecture que nous proposons permet d'adapter le nombre d'opérateurs communs alloués à chaque algorithme et donc permet l'optimisation de l'utilisation des ressources matérielles. Il en résulte une meilleure gestion de la consommation énergétique.

Les travaux présentés dans cette thèse ont fait l'objet de plusieurs publications scientifiques et deux brevets listés à la fin de ce manuscrit.

### Environnement de recherche

Les travaux de recherche présentés dans cette thèse ont été réalisés dans les locaux du CEA-LETI $^3$  à Grenoble en collaboration avec deux laboratoires de recherche universitaires : GRESCOM $^4$  à SUP'Com Tunis et l'IETR-SCEE $^5$  à Supélec campus de Rennes. Ces travaux, notamment ceux autour de la définition des architectures communes FFT/Viterbi, sont engagés dans

<sup>3.</sup> http://www-leti.cea.fr

<sup>4.</sup> http://www.supcom.mincom.tn/

<sup>5.</sup> http://www.rennes.supelec.fr/ren/rd/scee/

24 INTRODUCTION

des projets européens dont le réseau d'excellence NEWCOM++  $^6$  et le projet collaboratif C2POWER  $^7.$

#### Plan du mémoire

Ce document se décompose en quatre chapitres (un chapitre introductif suivi de trois chapitres qui préentent nos contributions). Ces chapitres se répartissent comme suit :

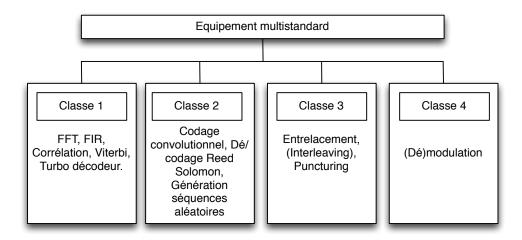

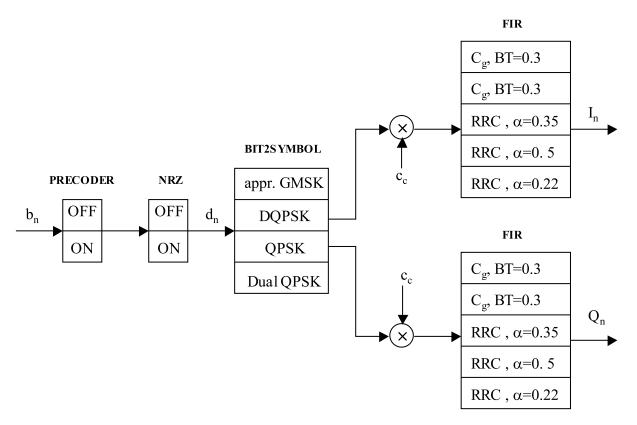

Le premier chapitre donne au lecteur un aperçu sur le contexte de notre travail de recherche ce qui permet de situer de manière technique les choix et motivations de nos travaux. Nous présentons d'abord le contexte de la radio reconfigurable avec les plateformes utilisées et les contraintes des standards. Ensuite, nous décrivons l'approche de paramétrisation et la technique des opérateurs communs pour les architectures reconfigurables. A la fin de ce chapitre, nous résumons les travaux antérieurs à nos recherches en cataloguant un premier jeu d'opérateurs communs que nous avons classés par leurs niveaux de granularité.

Le deuxième chapitre définit un modèle fonctionnel abstrait qui a pour objectif de permettre le déploiement des fonctionnalités reconfigurables sur une plateforme matérielle hétérogène basée sur les opérateurs communs présentés dans le premier chapitre. Dans une première section nous définissons d'une façon générale le management des opérateurs communs. Nous détaillons ensuite les techniques de management des opérateurs communs en se basant sur des approches de la littérature traitant de la gestion de ressources matérielles reconfigurables. Ensuite, nous étudions l'implémentation de ces opérateurs en se basant essentiellement sur des évaluations de complexités sur quatre standards considérés. A la fin de ce chapitre, nous proposons des modèles d'architectures permettant le management des opérateurs communs.

Le troisième chapitre propose des cellules de traitement matériel reconfigurables pour les algorithmes FFT et Viterbi, capables de prendre en compte leurs différences fonctionnelles et de s'adapter à l'utilisation qui en est faite. Ces travaux sur l'opérateur FFT/Viterbi viendront compléter le jeu d'opérateurs présenté dans le premier chapitre. Dans ce chapitre, nous commençons par étudier les similarités structurelles entre les algorithmes FFT et Viterbi. Ensuite nous présentons deux premières architectures parallèles du papillon commun pour proposer une architecture en pipeline plus efficace que les deux premières. Nous discutons à la fin de ce chapitre les comparaisons entre les cellules de l'opérateur FFT/Viterbi proposé avec celles de la

<sup>6.</sup> http://www.newcom-project.eu/

<sup>7.</sup> http://www.ict-c2power.eu/

littérature.

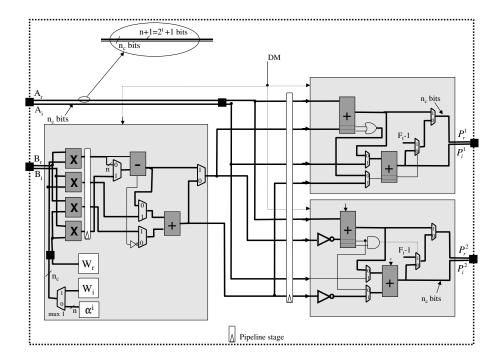

Le quatrième chapitre se concentre sur les mécanismes de gestion de l'opérateur FFT/Viterbi défini dans le chapitre précèdent. Dans ce chapitre, nous proposons des architectures de traitement matériel reconfigurables pour les algorithmes FFT et Viterbi, capables de partager efficacement les ressources matérielles entre les deux algorithmes. Notre objectif est d'assurer une affectation efficace des ressources entre les deux algorithmes FFT et de décodage de Viterbi. Ainsi, nous commençons par l'exploitation des similitudes structurelles entre la FFT et algorithme de Viterbi (présentés dans le troisième chapitre) et nous proposons une implémentation efficace et flexible du processeur commun FFT/Viterbi.

La conclusion propose une synthèse des travaux présentés pour amener le lecteur à une discussion sur les perspectives de ces travaux. Les annexes concernent les rappels sur l'utilisation de l'opérateur FFT dans différentes fonctions de traitement de signal et la définition des termes et concepts utilisés dans ce manuscrit en relation avec les systèmes radio avancés.

## Chapitre 1

# Technique des opérateurs communs pour la radio reconfigurable

| Sommaire |                                        |                                                       |           |  |  |

|----------|----------------------------------------|-------------------------------------------------------|-----------|--|--|

| 1.1      | Intro                                  | oduction                                              | 25        |  |  |

| 1.2      | Contexte de la radio reconfigurable 26 |                                                       |           |  |  |

| 1.3      | Les                                    | plateformes de la radio reconfigurable                | 28        |  |  |

|          | 1.3.1                                  | Les contraintes des standards                         | 29        |  |  |

|          | 1.3.2                                  | Plateforme de traitement parallèle                    | 30        |  |  |

|          | 1.3.3                                  | Gestion des ressources                                | 32        |  |  |

| 1.4      | Réut                                   | tilisation des ressources                             | 32        |  |  |

| 1.5      | La p                                   | aramétrisation                                        | <b>35</b> |  |  |

|          | 1.5.1                                  | Approche par fonctions communes                       | 36        |  |  |

|          | 1.5.2                                  | Approche par opérateurs communs                       | 39        |  |  |

| 1.6      | $\operatorname{Iden}$                  | tification des opérateurs communs                     | <b>39</b> |  |  |

|          | 1.6.1                                  | Approche théorique                                    | 40        |  |  |

|          | 1.6.2                                  | Approche pragmatique                                  | 44        |  |  |

| 1.7      | Un p                                   | premier jeu d'opérateurs communs                      | 44        |  |  |

|          | 1.7.1                                  | Les opérateurs de faible granularité : LFSR et Cordic | 45        |  |  |

|          | 1.7.2                                  | Les opérateurs à forte granularité : FFT et FEC $$ .  | 47        |  |  |

| 1.8      | Cone                                   | clusion                                               | 49        |  |  |

### 1.1 Introduction

Les techniques radio reconfigurable visent à offrir un accès à un large choix d'applications et de standards de radiocommunications sur une architecture matérielle unique. Une grande flexibilité du système reconfigurable

28 CHAPITRE 1

est nécessaire afin de répondre à la diversité des traitements à exécuter. Les techniques de communications numériques employées dans les standards entraînent des besoins en ressources de traitements hétérogènes. La reconfigurabilité d'une plate-forme d'exécution hétérogène est donc un point clef technologique à l'apparition de systèmes radio reconfigurables. La diversité des traitements induit aussi une variété de configurations de l'architecture d'un équipement multistandard.

Nos travaux de recherche portent sur la définition d'un terminal multistandard reconfigurable permettant une gestion efficace des ressources matérielles. En effet, la reconfigurabilité est dépendante des contraintes (temporelles, de consommation, de coût,...) imposées par les standards de communication et devient donc tributaire des capacités de la plateforme. Dans ce contexte, nous présentons dans ce chapitre les techniques de paramétrisation comme solution à cette problématique. Cette technique offre la possibilité de reconfigurer en temps réel les éléments de la plateforme reconfigurable et de garantir l'aspect évolutif de l'implémentation. Nous orientons nos travaux dans la définition et mise en application des techniques de paramétrisation. Pour atteindre cet objectif, nous considérons l'idée d'identifier des éléments communs entre différents standards. Les travaux antérieurs à nos recherches ont définis un premier jeu d'opérateurs communs que nous présenterons à la fin de ce chapitre.

### 1.2 Contexte de la radio reconfigurable

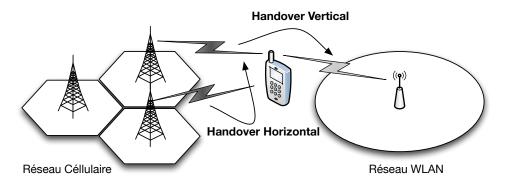

Les équipements de communication actuels doivent répondre à des besoins croissants en termes de flexibilité et d'adaptabilité à plusieurs standards. Ces besoins proviennent non seulement de la prolifération des applications mais aussi des différences de standardisation entre zones géographiques. En effet, les terminaux cellulaires actuels doivent pouvoir gérer plusieurs standards à la fois tel que le GSM, EDGE, l'UMTS et la 3GPP LTE. Outre ces réseaux, un terminal cellulaire doit pouvoir se connecter à des réseaux locaux tels que le Wifi et le Bluetooth, des services de localisation, et recevoir la télévision et radio numériques. Ainsi, les différences entre les standards de communication et l'incompatibilité entre nouveaux et anciens standards posent des problèmes de flexibilité et d'adaptabilité dès la conception des équipements. Ce besoin de s'adapter à différents standards et services a été défini sous le nom de « Handover Vertical », par complémentarité avec le « Handover Horizontal » qui qualifie la mobilité géographique d'une cellule à l'autre [13] (Figure 1.1).

La conséquence de la prolifération des standards de communication est le coût croissant des circuits en termes de surface de silicium et de consommation électrique. La complexité des processeurs augmente bien plus vite que la capacité des batteries, fait qu'il devient de plus en plus nécessaire

Figure 1.1 – Différents types de « Handover »

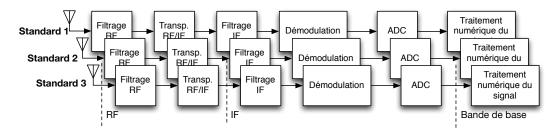

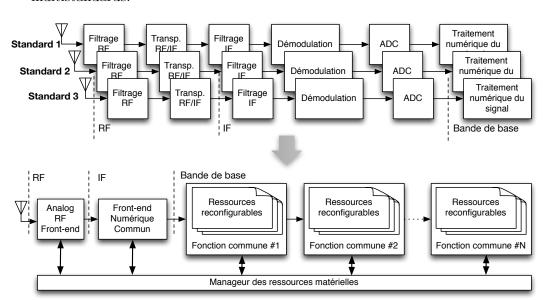

de changer l'approche de conception des équipements multistandards [14]. L'approche classique pour implémenter les fonctionnalités d'un équipement multistandard est d'instancier plusieurs chaînes d'émetteurs-récepteurs, où chaque chaine instanciée est dédiée à un seul mode ou standard (Figure 1.2). Avec cette approche, une grande partie du matériel doit être repensée pour chaque évolution des standards ou des applications. Cette approche conventionnelle appelée « Velcro » n'exploite pas les points communs entre les différents standards de communication [4]. Ainsi, un équipement radio ne peut réaliser qu'un nombre donné de standards. L'implémentation est limitée par le coût des circuits dédiés, concaténés dans la même architecture. Cette approche classique utilise un ensemble de composants spécialisés à chaque type de traitement, dupliqués pour chaque standard que doit exécuter l'équipement multistandard. Ces architectures de traitement classiques sont figées dès la conception et il est difficile de les faire évoluer pour supporter des nouvelles fonctionnalités.

Le concept de la radio reconfigurable vient contourner ce problème en exploitant les capacités des réseaux et des équipements à l'auto-adaptation à un environnement dynamique, avec l'objectif d'améliorer la qualité du service, l'efficacité de l'utilisation des ressources matérielles et spectrales. La radio reconfigurable se base essentiellement sur l'idée de la Radio Logicielle

FIGURE 1.2 – Exemple d'une implémentation classique d'un récepteur tristandards (Approche Velcro)

30 CHAPITRE 1

(RL) introduite par Mitola [3] qui est restée historiquement associée à des implémentations logicielles (voir Annexe A). Le principe de la numérisation du signal au plus près de l'antenne permet le traitement des opérations (filtrage, décimation, décodage etc.) en numérique, ce qui ajoute beaucoup de flexibilité aux architectures de traitement. Ainsi, il serait possible de traiter un grand nombre de standards de communication par simple chargement des paramètres associés au standard.

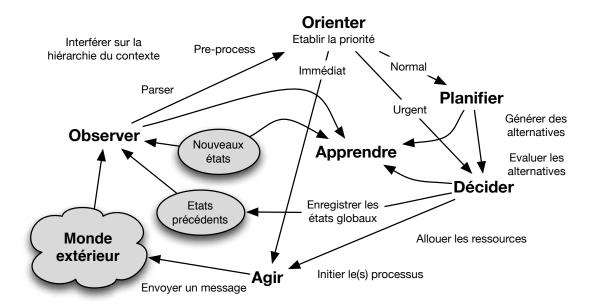

De plus, la Radio Intelligente (RI), définie par Mitola également [15], répond aux besoins des équipements d'effectuer en permanence un Handover vertical et de passer automatiquement d'un standard à un autre sans interrompre la communication. La radio intelligente est un concept qu'on pourrait définir comme une interface radio avec des capacités d'apprentissage, c'est à dire une radio en mesure de connaître son environnement et d'ajuster ses paramètres et mécanismes de fonctionnement en conséquence. Il est clair qu'une telle approche offre beaucoup d'avantages en termes d'efficacité spectrale ce qui est très important lorsque les ressources spectrales sont rares, comme c'est le cas aujourd'hui.

Ainsi, il existe un grand intérêt dans les technologies de la radio reconfigurable qui a pour objectif de répondre aux besoins de flexibilité et d'adaptabilité nécessaires pour la RI. L'équipement reconfigurable dispose de ressources matérielles génériques et reconfigurables par un logiciel qui permet de s'adapter aux besoins des traitements de chaque standard. L'évolution et l'ajout de nouvelles fonctionnalités se fait par modification ou ajout de nouveaux logiciels permettant de reconfigurer les paramètres des blocs de traitements.

### 1.3 Les plateformes de la radio reconfigurable

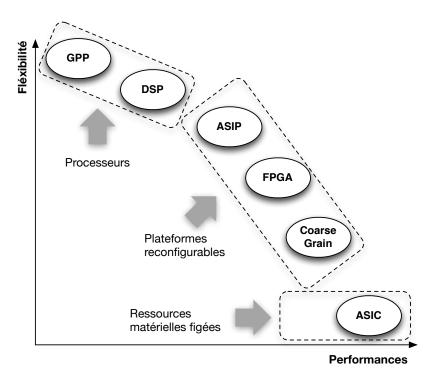

Historiquement, les circuits utilisés en bande de base sont les circuits spécialisés de type Application-Specific Integrated Circuit (ASIC), les processeurs de type General Purpose Preprocessor (GPP) et Digital Signal Processor (DSP). Les ASIC offrent de hautes performances de traitement (nécessaires pour les besoins des standards récents) mais leur point faible est la flexibilité qui est une caractéristique indispensable dans la définition de la radio reconfigurable. En revanche, la programmabilité des circuits de type processeurs en font les cibles les plus adaptés à la reconfiguration. Mais cette flexibilité a un coût, notamment en consommation, et les performances de ces processeurs sont souvent insuffisantes face aux besoins de traitement du signal des applications récentes. Le manque d'efficacité énergétique par rapport aux performances est par ailleurs un obstacle pour l'intégration de ce type de circuits dans des terminaux mobiles.

Pour réaliser un compromis entre la flexibilité et la performance, il existe des solutions reconfigurables pour les applications de traitement du signal qui offrent les capacités de faire des changements structurels d'éléments de cal-

culs câblés. Comme le montre la figure 1.3, les circuits de type ASIP, FPGA et Coarse Grain peuvent remplir les compromis flexibilité/performance attendus par la radio reconfigurable. Par contre, le choix de ces éléments de calcul n'est pas toujours évident. En fait, le bilan de puissance très serré des équipements actuels fait souvent pencher la balance du coté performance plutôt que celui de la flexibilité.

FIGURE 1.3 – Rapport flexibilité/performance des circuits de traitement en bande de base

#### 1.3.1 Les contraintes des standards

Les plateformes matérielles de la radio reconfigurable suivent essentiellement les contraintes des standards et l'évolution de l'offre des circuits. Dans ce paragraphe, nous donnons un aperçu de ces contraintes et nous présentons quelques architectures et circuits adaptés aux traitements numériques en bande de base dans le contexte de la radio reconfigurable.

L'évolution des standards de communication entraine de forts besoins de calculs [16]. Comme le montre le tableau 1.1 l'évolution des besoins des calculs des nouveaux standards est plus rapide que l'évolution de la technologie surtout aux niveaux des puissances de calculs et des capacités des batteries. En effet, les capacités des batteries évoluent lentement (de l'ordre de 1Wh tous les 5 ans) par rapport à l'évolution des charges de calculs ( $\times 10$  tous les 5

32 CHAPITRE 1

ans). Ces charges de calculs, qui dépassent les 1000 GOPS (Giga Opérations Par Seconde) pour la 4e génération des terminaux cellulaires, seront de plus en plus difficiles à satisfaire surtout pour les terminaux mobiles qui fonctionnent sous des contraintes de consommation très strictes.

| Année      | 1995 | 2000      | 2005 | 2010     | 2015      |

|------------|------|-----------|------|----------|-----------|

| Génération | 2G   | 2.5-3G    | 3.5G | pre-4G   | 4G        |

| Standard   | GSM  | GPRS-UMTS | HSPA | HSPA-LTE | LTE/LTE-A |

| Débit      | 0.01 | 0.1       | 1    | 10       | 100       |

| [Mb/s]     |      |           |      |          |           |

| Capacité   | 1    | 2         | 3    | 4        | 5         |

| des bat-   |      |           |      |          |           |

| teries     |      |           |      |          |           |

| [Wh]       |      |           |      |          |           |

| Charge     | 0.1  | 1         | 10   | 100      | 1000      |

| de calcul  |      |           |      |          |           |

| [GOPS]     |      |           |      |          |           |

| #Cœurs     | 1    | 2         | 4    | 8        | 16        |

| program-   |      |           |      |          |           |

| mables     |      |           |      |          |           |

Table 1.1 – Evolution des besoins des standards (adapté de [16])

Le tableau 1.1 montre que la tendance actuelle est d'augmenter le nombre des cœurs programmables dans les terminaux mobiles pour faire face aux contraintes de la consommation et des charges de calculs. Dans ce contexte, les technologies de traitement parallèle (Parallel processing) couvrent une multitude d'approches différentes.

### 1.3.2 Exemple d'une plateforme de traitement parallèle reconfigurable

Il existe une grande variété de technologies de traitement parallèle reconfigurables qui vont des structures à faible granularité (reconfiguration niveau bit comme dans les FPGA) jusqu'aux structures à gros grain (reconfiguration niveau processeur comme dans les MPSoC). Ces structures à gros grain ont émergé ces dernières années grâce aux réseaux sur puce (Network on Chip NoC) qui ont permis le traitement parallèle à travers un réseau de processeurs reconfigurables.

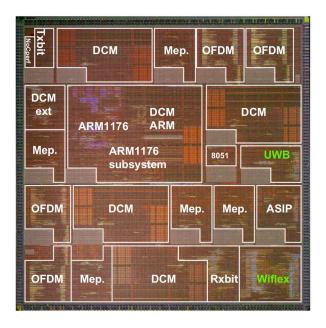

Dans ce contexte, plusieurs projets sur ces technologies reconfigurables ont été réalisés au CEA-LETI dans la conception des NoCs pour les applications télécoms. Parmi ces projets, nous citons le projet MAGALI qui est un circuit

développé pour les terminaux cellulaires de 4e génération [17]. Il est basé sur une architecture innovante de type réseau sur puce asynchrone (NoC) supportant des liaisons à 2.2GB/s. Le circuit embarque 23 processeurs intégrés dédiés au traitement du signal et au traitement au niveau digit. Il contient un processeur intégré ARM1176 supportant les piles protocolaires et plusieurs accélérateurs matériels dédiés aux traitements en bande de base pour la 4e génération des réseaux sans-fil (Comme des modules OFDM, UWB, Wiflex dans la Figure 1.4) [18].

L'innovation majeure dans ce projet porte sur la reconfiguration. Le circuit bande de base peut être entièrement reconfiguré en moins de  $50\mu s$  (temps maximum). Lors de tests applicatifs, on observe une reconfiguration en  $4\mu s$  en moyenne. De plus, le circuit est capable de supporter plusieurs applications en parallèle. En effet, la puissance de calcul peut être partagée sur les mêmes unités de calcul entre plusieurs applications radio. Ces deux caractéristiques font de MAGALI un circuit particulièrement adapté aux applications de radio reconfigurable. Grâce à l'architecture réseau sur puce asynchrone, chacun des 23 processeurs est un ilot de fréquence programmable dynamiquement. On obtient ainsi le rapport optimal entre la consommation et les performances. Au final, le circuit MAGALI a une consommation inférieure à 500mW pour des performances atteignant les 40 GOPS (Giga Operations Per Second).

FIGURE 1.4 – Le circuit MAGALI [17]

34 CHAPITRE 1

## 1.3.3 Gestion des ressources dans les plateformes reconfigurables

Les ressources offertes par les plateformes matérielles nécessitent une gestion efficace afin de respecter les contraintes des standards de points de vue des délais et de la consommation. L'aspect reconfigurable et l'utilisation multistandard ajoutent plus de complexité à la gestion de ressources. En effet, chaque élément de traitement de la plateforme peut être reconfiguré et partagé entre plusieurs standards. Cela nécessite donc une décomposition efficace des fonctions de traitement en bande de base afin d'assurer une bonne réutilisation des ressources matérielles. La figure 1.5 montre un exemple de partage des ressources entre trois standards.

Nous présentons par la suite comment les ressources des plateformes de la radio reconfigurable peuvent être réutilisé efficacement dans les terminaux multistandards.

FIGURE 1.5 – Exemple de partage des ressources entre trois standards dans une plateforme radio reconfigurable

# 1.4 Réutilisation des ressources dans les terminaux multistandards

Avec les limites technologiques actuelles, il est possible de répondre aux besoins des standards en utilisant des architectures à multiprocesseurs comme nous l'avons montré dans les paragraphes précédents. Mais aussi, il est nécessaire d'utiliser une stratégie de gestion des ressources offertes par les processeurs

afin d'optimiser la performance et la consommation du système. Parmi les stratégies à considérer, l'utilisation de l'allocation dynamique des ressources de traitement hétérogènes qui touche directement les caractéristiques de flexibilités (objectif de notre travaux de recherche). L'allocation dynamique des ressources dans ce contexte d'étude peut être appliquée à plusieurs niveaux :

- La réutilisation des ressources matérielles et logicielles (associées) réduit la quantité du matériel physiquement implémenté et donc réduit la surface du circuit,

- La réutilisation des noyaux logiciels (kernels) entre plusieurs standards peut réduire les besoins de mémoire et spécialement la mémoire du programme,

- La réutilisation du matériel et du logiciel developpés entre différents projets réduit considérablement les délais et les coûts de développement.

Concrètement, l'allocation dynamique peut devenir très intéressante dans les équipements multistandard et/ou multimodes puisque le basculement d'un standard/mode à un autre peut libérer des ressources et en occuper d'autres. Par exemple, les variations de l'état du canal de transmission peuvent provoquer un grand changement dans les ressources utilisées. En effet, pendant les conditions de fading sévère, des algorithmes de compensation et de codage canal sophistiqués et gourmands en ressources sont utilisés pour maintenir une communication fiable. En revanche, pendant les bonnes conditions de propagation, plus de ressources sont allouées aux traitements niveau symboles dans le but d'augmenter le débit. Cela suppose donc que les ressources partagées ne sont pas trop spécialisées et sont suffisamment génériques pour s'acquitter de plusieurs tâches différentes.

L'optimisation de la gestion des ressources de la plateforme radio reconfigurable nécessite alors l'étude des chaines de traitement de signal et l'identification des éléments de traitements qui peuvent être partagés entre les standards et les fonctions.

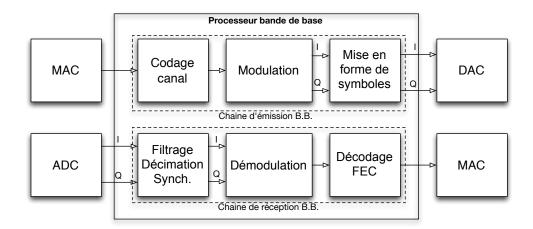

La plupart des systèmes radio contiennent deux chaines de traitement en bande de base, la chaine de réception et la chaîne d'émission. D'une façon générale dans la chaine d'émission, le processeur de traitement Bande de Base reçoit les données de la couche MAC et effectue principalement les fonctions suivantes :

- Codage canal

- Modulation numérique

- Filtrage de mise en forme

A la réception, les données envoyées par l'ADC sont traitées par les fonctions suivantes :

- Filtrage, synchronisation, décimation et contrôle de gain

- Démodulation, estimation du canal et égalisation

- Décodage et correction des erreurs

Ces principales fonctions de traitement de signal en Bande de Base sont illustrées dans la figure 1.6.

FIGURE 1.6 – Les fonctions réalisées par un processeur de traitement bande de base

Il existe des similarités entre les fonctions bande de base surtout entre fonctions des standards utilisant la modulation multi-porteuse. En se focalisant sur les standards basés sur l'OFDM (Orthogonal Frequency-Division Multiplexing) qui regroupent un grand nombre des standards de télécommunication actuels, on peut constater que les algorithmes utilisés et la dépendance de données à travers les chaines de traitement sont très proches. Nous proposons de tirer profit de ces similarités entre standards et fonctions afin de gagner en flexibilité et en complexité avec la réutilisation des ressources.