## A high-level methodology for automatically generating dynamically reconfigurable systems using IP-XACT and the UML MARTE profile

Gilberto Ochoa Ruiz

#### ► To cite this version:

Gilberto Ochoa Ruiz. A high-level methodology for automatically generating dynamically reconfigurable systems using IP-XACT and the UML MARTE profile. Other [cs.OH]. Université de Bourgogne, 2013. English. NNT: 2013DIJOS012. tel-00932118

#### HAL Id: tel-00932118 https://theses.hal.science/tel-00932118v1

Submitted on 16 Jan 2014  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# SPIM Thèse de Doctorat

IVERSITÉ

U N

A High-level Methodology for Automatically Generating Dynamically Reconfigurable Systems using IP-XACT and the UML MARTE Profile

école doctorale sciences pour l'ingénieur et microtechniques

Gilberto OCHOA RUIZ

# SPIM Thèse de Doctorat

S

I T

R

THÈSE présentée par

É

école doctorale <mark>sciences pour l'ingénieur et microtechniques</mark>

B 🔨 O

### Gilberto OCHOA RUIZ

pour obtenir le Grade de Docteur de l'Université de Bourgogne

Spécialité : Instrumentation et Informatique de l'Image

## A High-level Methodology for Automatically Generating Dynamically Reconfigurable Systems using IP-XACT and the UML MARTE Profile

Soutenue le 14 novembre 2013 devant le Jury :

| ł |

|---|

| ł |

| ł |

| ł |

| ł |

| ( |

| [ |

|   |

U

N° X X X

Rapporteur Rapporteur Examinateur Examinateur Examinateur Co-encadrant Directeur de thèse Professeur à l'Université Joseph Fourier Professeur à l'Université de Lorraine Professeur à l'Université de Lorraine MdC à l'Université de Saint -Etienne MdC à l'Université de Lille 1 - INRIA MdC à l'Université de Bourgogne Professeur à l'Université de Bourgogne

#### ACKNOWLEDGMENTS

First, I wish to express my sincere gratitude to my advisors, Prof. E-Bay Bourennane and Dr. Ouassila Labbani-Narsis, for their guidance, ecouragement, and patience during my the last three and half years. Moreover, I would like to thank the Agence Nationale de la Recherche Scientifique for the financial support for the FAMOUS project, under which my research was carried out. I owe thanks to all people involved in this endeavour, both professors and colleague PhD students, for their constructive critiques and stimulating discussions during many of the project meetings.

Furthermore, I wish to express my deepest gratitute to the reviewers of the thesis, Prof. Serge Weber and Prof. Frédéric Rousseau for their insightful comments and constructive critiques that have led to and improved verson of thesis manuscript, and to the members of the jury Dr. Samy Meftali, Prof. Hassan Rabah and Dr. Virginie Fresse, for their remarks, questions and recommentations during my thesis defence.

I want to express my gratitude to other colleagues in the LE2I laboratory, especially to Elhillali Kerkouche, Kamel Messaoudi and Touiza Maamar, for their collaborative spirit and friendship. Moreover, I wish to express my sincere gratitude to the ensemble of the LE2I, which have supported me in many ways during my studies in France.

Furthermore, I want thank to many former colleagues and guiding lights in my professional life. First of all, I extend my gratitude to Dr. Miguel Arias-Estrada, for giving me the opportunity to create my first FPGA-based smart cameras, first at the FPGA Lab (INAOE), then in Prefixa Vision Systems. His constant inspiration has led me to pursue a scientific career in reconfigurable computing. In the same vein, I owe thanks to Prof. Fabrice Meriaudeau for his continous support during my master and PhD studies, and for putting me in contact with the RaPToM team at Le2i.

Moreover, I would like to express my utmost gratitute to the many friends that I have met during this entire time, without any particular order: Pamela Wattebled, Guillaume Spalla, Bruno Cisneros, Hayyan Alia, Sergio Martinez, Christian Mata, Fitrin Syharul, and Marcos Salazar, for providing me with an environment which was the closest that I have had to a family.

Last but not the least, I would like to thank my family: my parents and sisters, for their love and support.

# CONTENTS

| I                       | Cor                                                                    | Context and Problematic                                                                                                                                       |                                                      |    |  |

|-------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----|--|

| 1                       | Rec                                                                    | onfigurable Architectures and Dynamic Partial Reconfiguration                                                                                                 |                                                      |    |  |

|                         | 1.1                                                                    | Introd                                                                                                                                                        | uction                                               | 22 |  |

|                         | 1.2                                                                    | Reconfigurable Architectures                                                                                                                                  |                                                      |    |  |

|                         |                                                                        | 1.2.1                                                                                                                                                         | Logic Resources, Routing and interconnections        | 24 |  |

|                         |                                                                        | 1.2.2                                                                                                                                                         | Heterogeneous Platforms                              | 26 |  |

| 1.3 Use of FPGAs in SoC |                                                                        |                                                                                                                                                               | f FPGAs in SoC Systems and their limitations         | 28 |  |

|                         |                                                                        | 1.3.1                                                                                                                                                         | Traditional FPGA design flow                         | 28 |  |

|                         |                                                                        | 1.3.2                                                                                                                                                         | Limitations of traditional FPGA designs flow         | 30 |  |

|                         |                                                                        |                                                                                                                                                               | 1.3.2.1 Run-time partial reconfiguration             | 31 |  |

|                         |                                                                        |                                                                                                                                                               | 1.3.2.2 Benefits of Run-time Partial Reconfiguration | 32 |  |

|                         | 1.4                                                                    | Xilinx Partition Partial Reconfiguration design flow                                                                                                          |                                                      | 33 |  |

|                         |                                                                        | 1.4.1 Design partitioning                                                                                                                                     |                                                      | 34 |  |

|                         |                                                                        | 1.4.2                                                                                                                                                         | Synthesis                                            | 34 |  |

|                         |                                                                        | 1.4.3                                                                                                                                                         | Planning                                             | 35 |  |

|                         |                                                                        | 1.4.4                                                                                                                                                         | DPR System Implementation                            | 37 |  |

|                         |                                                                        |                                                                                                                                                               | 1.4.4.1 Static Design Implementation                 | 37 |  |

|                         |                                                                        |                                                                                                                                                               | 1.4.4.2 PRM Implementation                           | 38 |  |

|                         |                                                                        | 1.4.5                                                                                                                                                         | Bitstream Generation                                 | 38 |  |

|                         |                                                                        | 1.4.6                                                                                                                                                         | Reconfiguration management                           | 39 |  |

|                         | 1.5 Challenges in the conception of Partially Reconfigurable Systems-c |                                                                                                                                                               |                                                      | 41 |  |

|                         |                                                                        | 1.5.1                                                                                                                                                         | Dynamic Partial Reconfiguration Tool Flow            | 41 |  |

|                         |                                                                        | 1.5.2                                                                                                                                                         | The FAMOUS Framework for DPR Systems                 | 43 |  |

|                         | 1.6                                                                    | <ul> <li>1.5 Challenges in the conception of Partially Reconfigurable Systems-on-Chip . 41</li> <li>1.5.1 Dynamic Partial Reconfiguration Tool Flow</li></ul> |                                                      | 45 |  |

| 2 | 2 | IP Reuse in MDE-based Co-Design Methodologies |         |                                                                | 47 |

|---|---|-----------------------------------------------|---------|----------------------------------------------------------------|----|

|   |   | 2.1                                           | Introdu |                                                                | 48 |

|   |   | 2.2                                           | Model   | -Driven Engineering                                            | 49 |

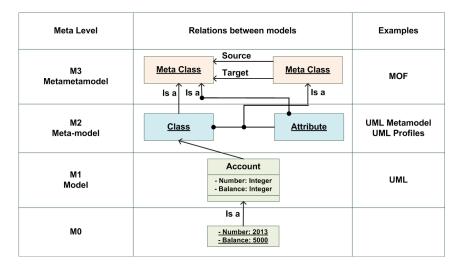

|   |   |                                               | 2.2.1   | MDE Basics                                                     | 50 |

|   |   |                                               |         | 2.2.1.1 Models                                                 | 50 |

|   |   |                                               |         | 2.2.1.2 Meta-models                                            | 50 |

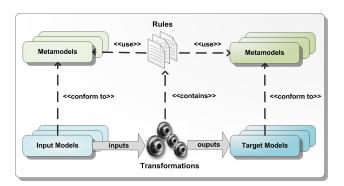

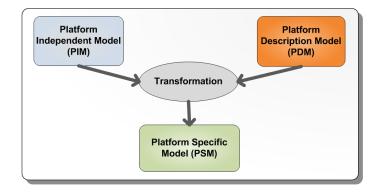

|   |   |                                               |         | 2.2.1.3 Model Transformations                                  | 51 |

|   |   |                                               |         | 2.2.1.4 A multi-level approach in modeling and transformations | 52 |

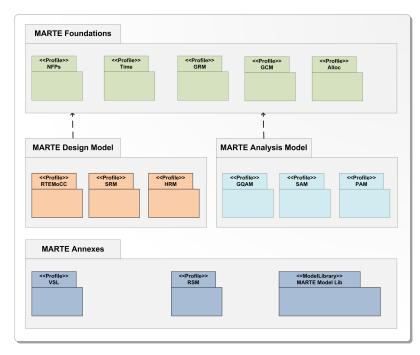

|   |   |                                               | 2.2.2   | The UML MARTE Profile for Embedded Systems Design              | 53 |

|   |   |                                               | 2.2.3   | MDE applied to SoC Co-design methodologies                     | 56 |

|   |   | 2.3                                           | IP Reu  | JSE                                                            | 59 |

|   |   |                                               | 2.3.1   | IP Reuse Basics                                                | 60 |

|   |   |                                               | 2.3.2   | Reusable IP                                                    | 62 |

|   |   |                                               | 2.3.3   | Classes of IPs                                                 | 63 |

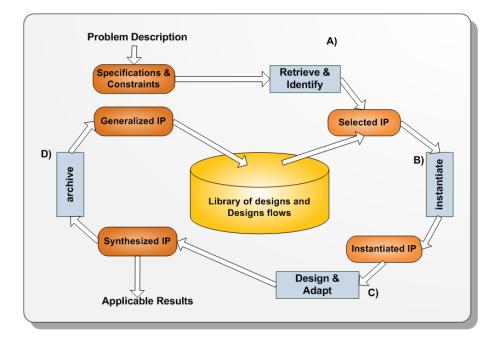

|   |   |                                               | 2.3.4   | The IP Reuse Cycle                                             | 64 |

|   |   | 2.4                                           | Metad   | ata-driven SoC IP Reuse and Integration                        | 67 |

|   |   |                                               | 2.4.1   | The Metadata-driven Component Composition Framework            | 68 |

|   |   |                                               | 2.4.2   | Interoperability Issues                                        | 70 |

|   |   |                                               | 2.4.3   | The merge of two worlds: IP-XACT and MDE                       | 71 |

|   |   | 2.5                                           | The IE  | EE 1685 IP-XACT Standard                                       | 72 |

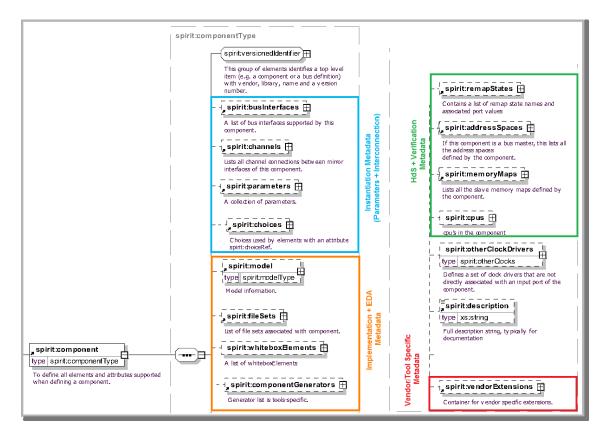

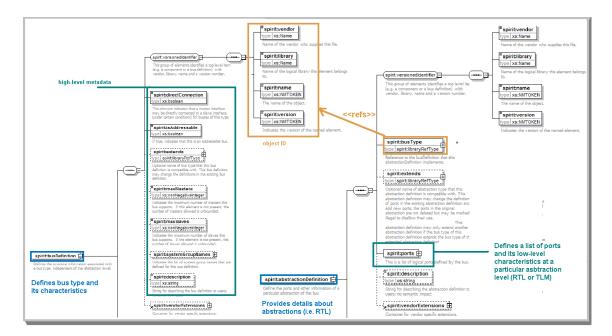

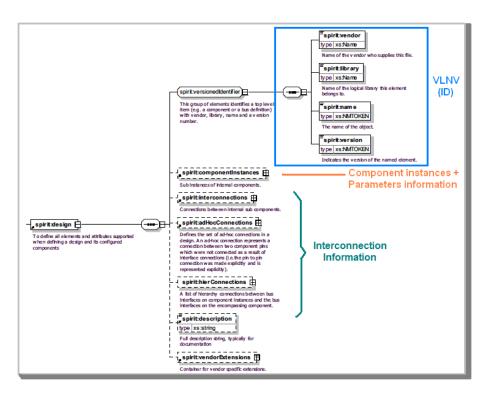

|   |   |                                               | 2.5.1   | IP-XACT modeling objects                                       | 73 |

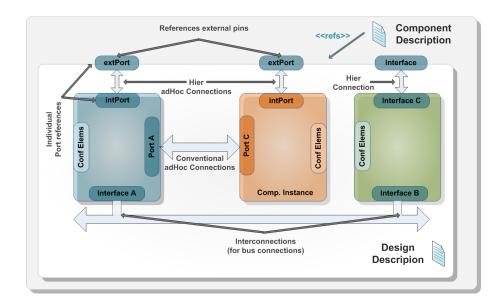

|   |   |                                               | 2.5.2   | The IP-XACT Design Environment                                 | 75 |

|   |   | 2.6                                           | Discus  | ssion and Conclusions                                          | 76 |

|   | 3 | MDE                                           | E-based | d methodologies for the creation of SoC                        | 79 |

|   |   | 3.1                                           |         |                                                                | 80 |

|   |   | 3.2                                           |         | nework for comparing MDE approaches for SoC                    |    |

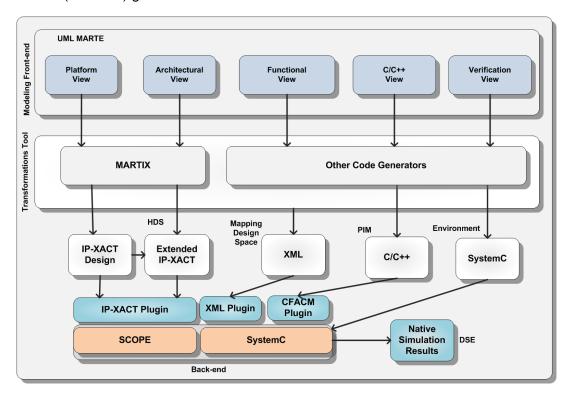

|   |   | 3.3                                           |         | m Modeling using UML MARTE                                     |    |

|   |   |                                               | 3.3.1   | The MoPCoM Methodology                                         |    |

|   |   |                                               | 3.3.2   | The GASPARD Approach                                           |    |

|   |   |                                               | 3.3.3   | The MADES Approach                                             |    |

|   |   |                                               |         |                                                                |    |

|    | 3.4  | Hardw   | are Modeling using UML and IP-XACT                                                     | 87  |

|----|------|---------|----------------------------------------------------------------------------------------|-----|

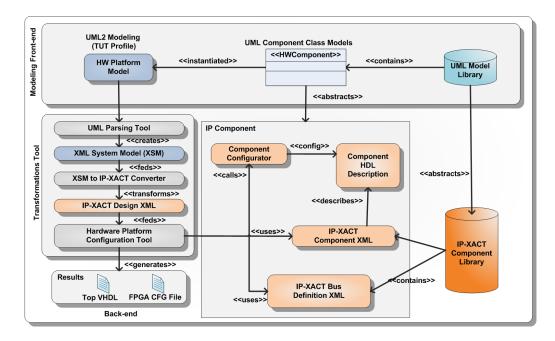

|    |      | 3.4.1   | The SPRINT Methodology                                                                 | 87  |

|    |      | 3.4.2   | The HELP Approach                                                                      | 88  |

|    |      | 3.4.3   | The TUT Profile and Methodology                                                        | 89  |

|    |      | 3.4.4   | The COMPLEX Approach                                                                   | 91  |

|    | 3.5  | Discus  | ssion and Conclusions                                                                  | 93  |

| II | Pro  | posed   | Methodology for DPR IP reuse and platform generation                                   | 97  |

| 4  | The  | role of | the proposed approach in the DPR design flow                                           | 99  |

|    | 4.1  | Introdu |                                                                                        | 100 |

|    | 4.2  | Comp    | onent-based approaches for SoC design: a hardware perspective                          | 102 |

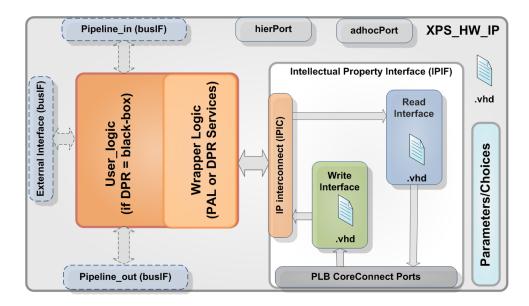

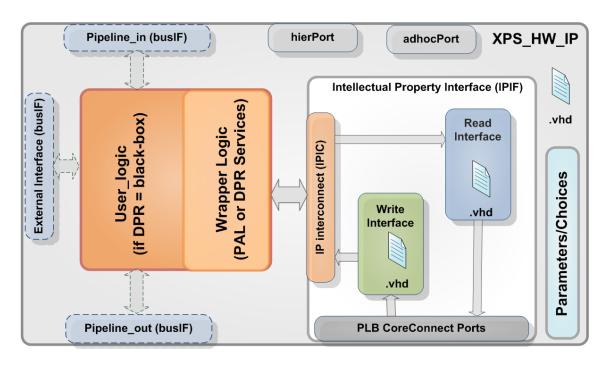

|    |      | 4.2.1   | The Intellectual Property Interface Wrapper                                            | 103 |

|    |      | 4.2.2   | Advantages of component-based design                                                   | 104 |

|    | 4.3  | Simpli  | fying DPR IPs management through componentizing                                        | 105 |

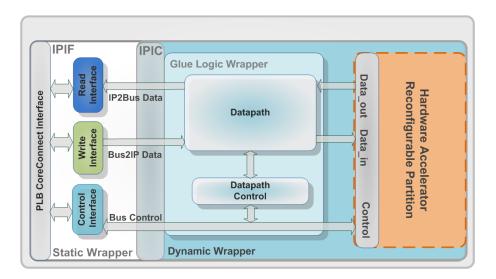

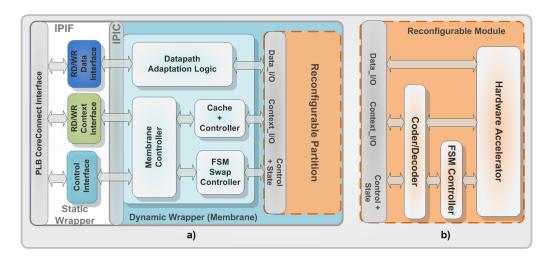

|    |      | 4.3.1   | Wrapper-based design for DPR IPs                                                       | 105 |

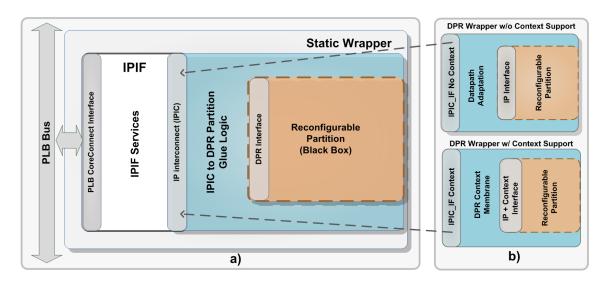

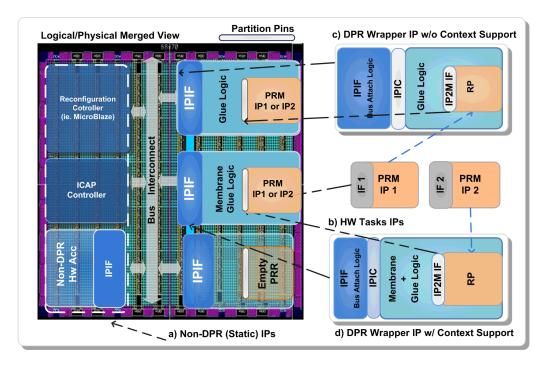

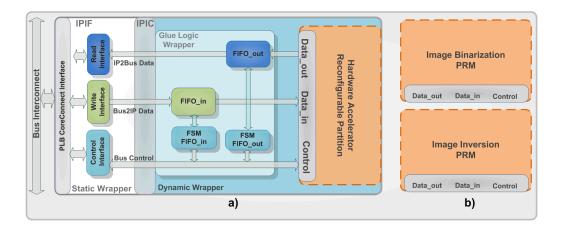

|    |      | 4.3.2   | IP wrappers deployed in the FAMOUS Framework                                           | 107 |

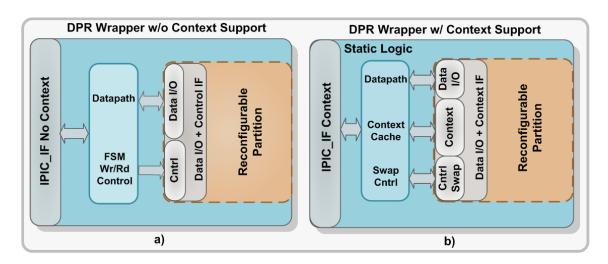

|    |      |         | 4.3.2.1 DPR Wrapper without context saving services                                    | 109 |

|    |      |         | 4.3.2.2 DPR wrapper supporting context saving services                                 | 110 |

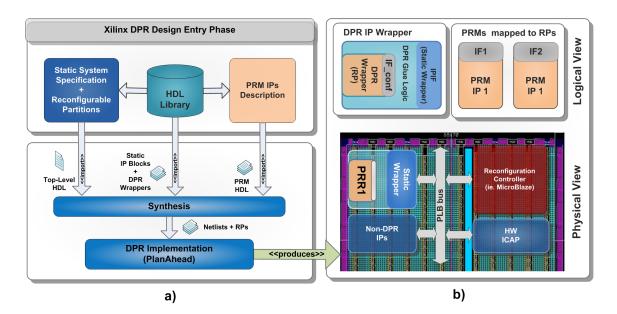

|    |      | 4.3.3   | Relationship of the wrapped DPR components and the design flow $% \mathcal{A}^{(n)}$ . | 112 |

|    |      | 4.3.4   | An IP Taxonomy for the Hardware Branch of the FAMOUS Approach                          | 114 |

|    |      | 4.3.5   | IP Reuse and Design by Reuse in a Component-based Design<br>Methodology                | 117 |

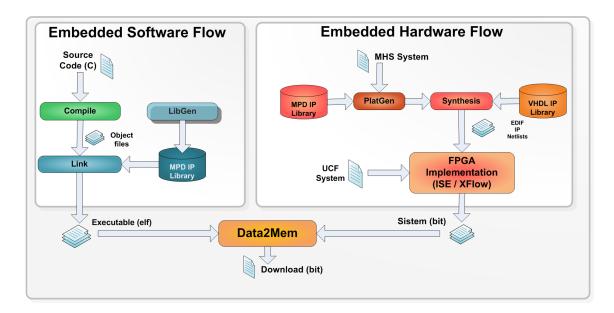

|    |      | 4.3.6   | The EDK Framework for the creation of FPGA-based SoC Platforms                         | 119 |

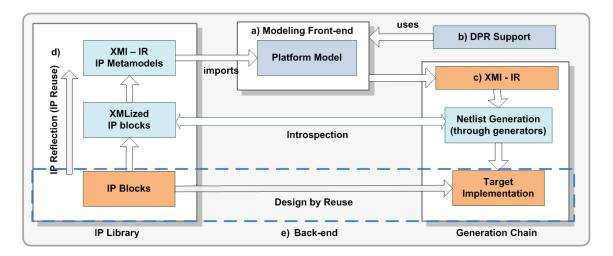

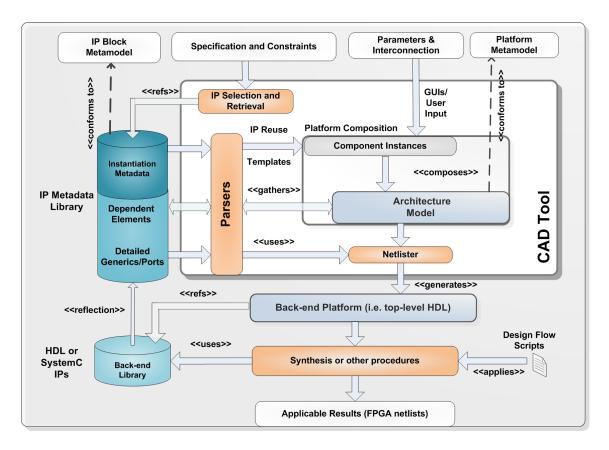

|    | 4.4  | FAMO    | US Metadata-driven DPR Composition Framework                                           | 122 |

|    | 4.5  | Propo   | sed Metadata Driven Composition Framework for DPR Systems                              | 125 |

|    | 4.6  | Discus  | ssion and Conclusions                                                                  | 126 |

| 5  | Prop | oosed I | methodology for IP reuse and system composition                                        | 129 |

|    | 5.1  | Introdu |                                                                                        | 130 |

| 5.3 | Creation of the reusable IP library through metadata reflection |                                                                                                                             |  |  |  |

|-----|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

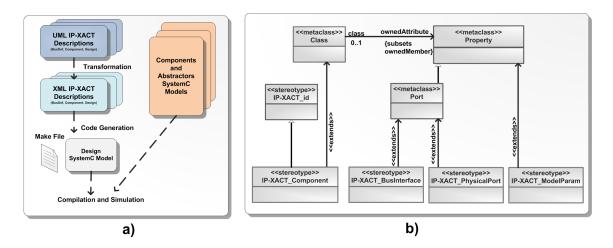

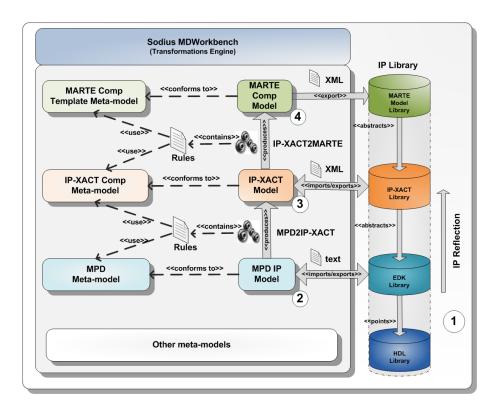

|     | 5.3.1                                                           | MDE-based metadata reflection approach                                                                                      |  |  |  |

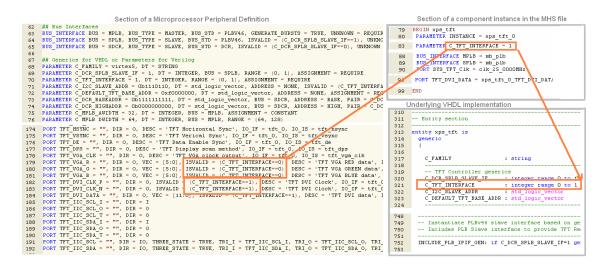

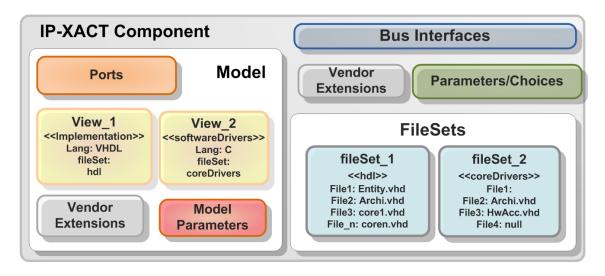

|     | 5.3.2                                                           | IP-XACT Representation of the IP Components                                                                                 |  |  |  |

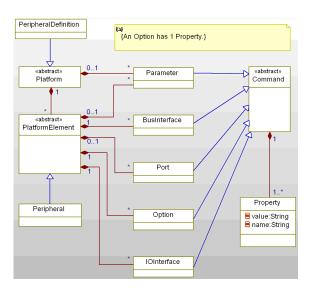

|     | 5.3.3                                                           | Generic model of a Xilinx Platform Studio IP Component 139                                                                  |  |  |  |

|     | 5.3.4                                                           | Requirements on UML MARTE modeling of the platform 140                                                                      |  |  |  |

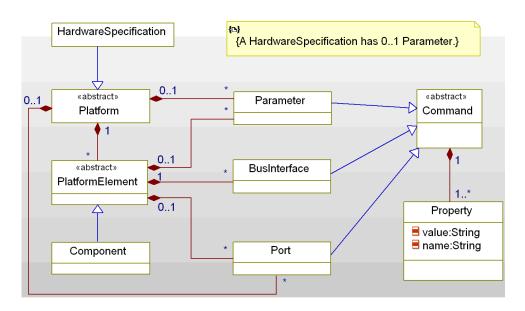

| 5.4 | Meta-ı                                                          | models for each of the level in the library                                                                                 |  |  |  |

|     | 5.4.1                                                           | Microprocessor Peripheral Definition metamodel                                                                              |  |  |  |

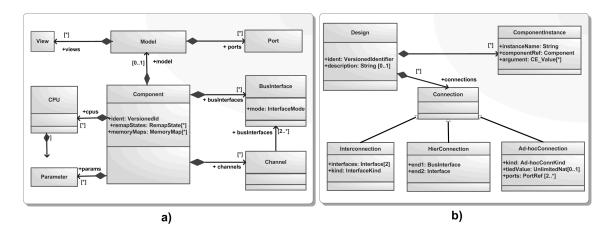

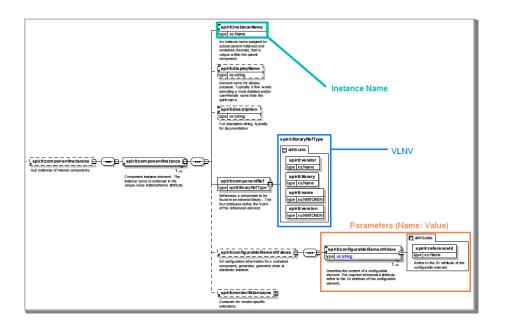

|     | 5.4.2                                                           | IP-XACT Component metamodel                                                                                                 |  |  |  |

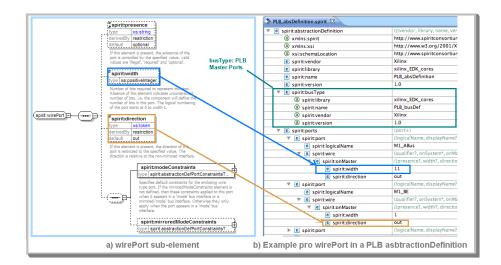

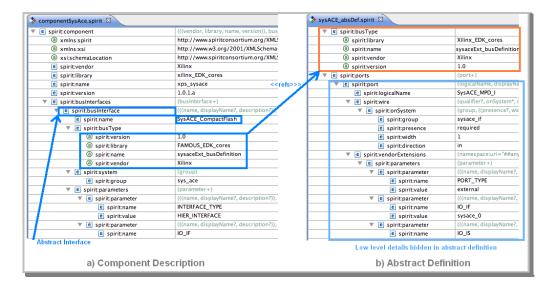

|     |                                                                 | 5.4.2.1 Bus and Abstract Definitions                                                                                        |  |  |  |

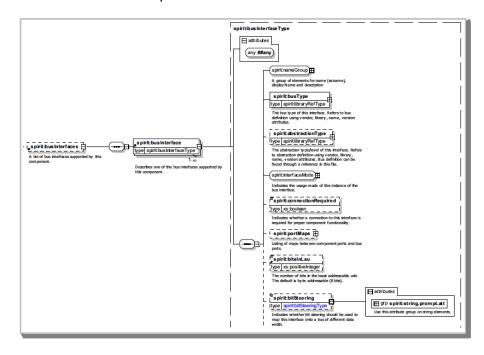

|     |                                                                 | 5.4.2.2 Bus Interfaces and Ports                                                                                            |  |  |  |

|     |                                                                 | 5.4.2.3 Models and Views                                                                                                    |  |  |  |

|     |                                                                 | 5.4.2.4 Files and fileSets                                                                                                  |  |  |  |

|     |                                                                 | 5.4.2.5 Parameters and Choices                                                                                              |  |  |  |

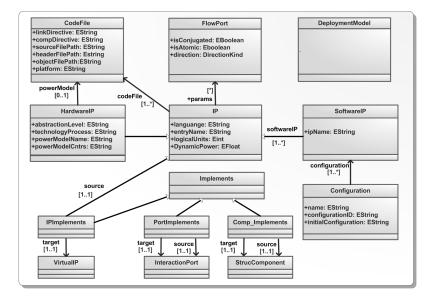

|     | 5.4.3                                                           | UML MARTE Proposed IP Deployment Package                                                                                    |  |  |  |

| 5.5 | Propo                                                           | sed Model Transformations for creating he multi-level IP library 160                                                        |  |  |  |

|     | 5.5.1                                                           | $MPD \rightarrow IP-XACT \text{ component transformation rules.} \dots \dots \dots \dots \dots 160$                         |  |  |  |

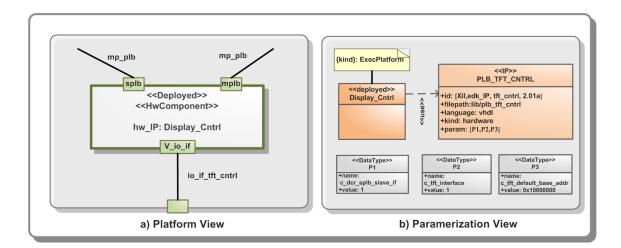

|     | 5.5.2                                                           | IP-XACT $\rightarrow$ MARTE component transformation rules                                                                  |  |  |  |

| 5.6 | Desigi                                                          | n by reuse in the FAMOUS methodology                                                                                        |  |  |  |

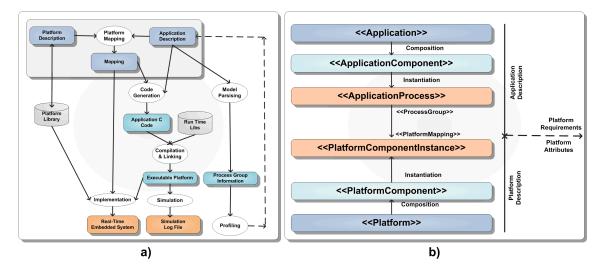

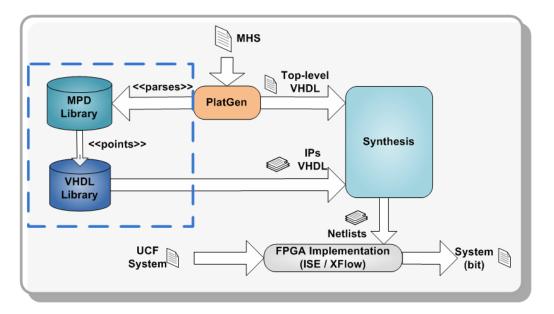

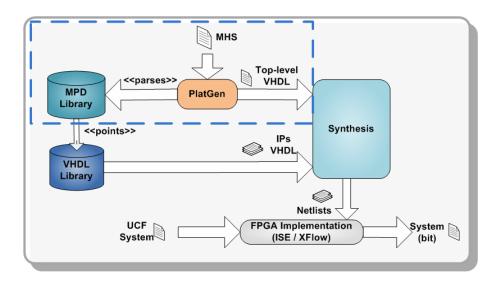

|     | 5.6.1                                                           | Xilinx Platform Studio Back-end System Generation                                                                           |  |  |  |

|     | 5.6.2                                                           | Platform Generation Chain: from MARTE to Xilinx XPS 166                                                                     |  |  |  |

| 5.7 | Metan                                                           | nodels for Platform Generation                                                                                              |  |  |  |

|     | 5.7.1                                                           | Microprocessor Hardware Definition metamodel                                                                                |  |  |  |

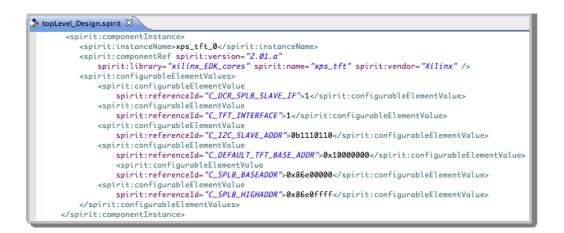

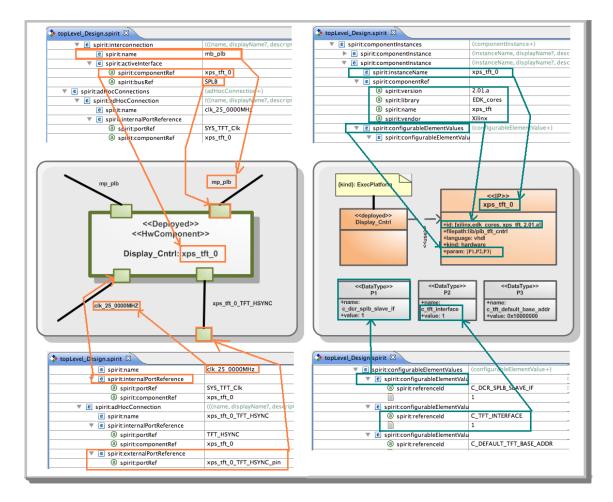

|     | 5.7.2                                                           | IP-XACT Design Metamodel                                                                                                    |  |  |  |

| 5.8 | UML N                                                           | MARTE Proposed Modeling of the platform                                                                                     |  |  |  |

| 5.9 | Propo                                                           | sed Model Transformations for creating the hardware platform 176                                                            |  |  |  |

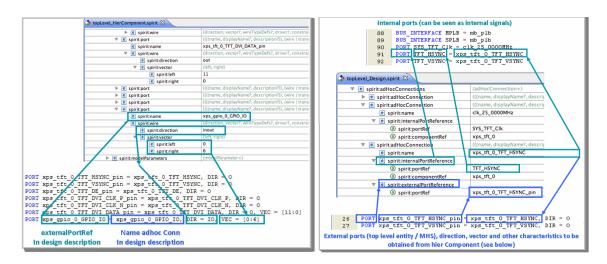

|     | 5.9.1                                                           | MARTE $\leftrightarrow$ IP-XACT Transformation Rules                                                                        |  |  |  |

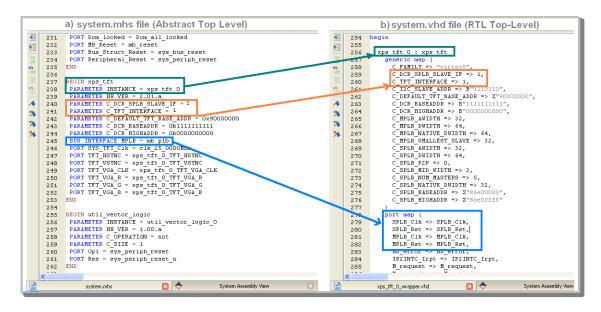

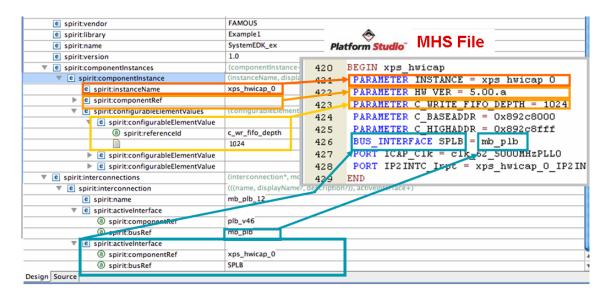

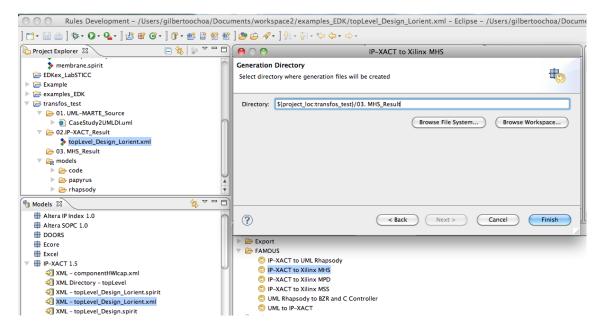

|     | 5.9.2                                                           | $IP-XACT \leftrightarrow MHS \text{ transformation rules.} \dots 178$ |  |  |  |

|     |                                                                 | 5.9.2.1 Mapping of the bus parameters                                                                                       |  |  |  |

|     |                                                                 | 5.9.2.2 Mapping of the bus interfaces                                                                                       |  |  |  |

|     |                                                                 | 5.9.2.3 Mapping of the internal and external connections and ports 179                                                      |  |  |  |

8

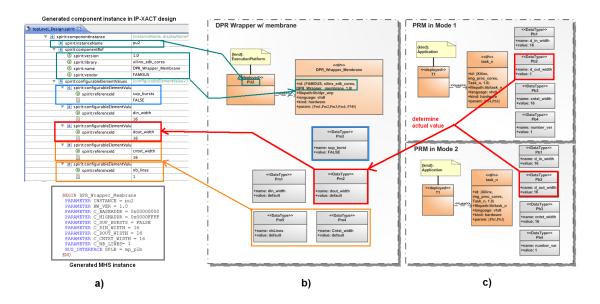

|     |       | 5.9.3   | Role of the Partially Reconfigurable Modules in the flow                                 | . 181 |

|-----|-------|---------|------------------------------------------------------------------------------------------|-------|

|     | 5.10  | Discus  | ssion and Conclusions                                                                    | . 183 |

| 6   | Cas   | e Study | y: DPR Architecture for Image Processing                                                 | 187   |

|     | 6.1   | Introdu |                                                                                          | . 188 |

|     | 6.2   | Used    | DPR image processing architecture and implemented applications.                          | . 189 |

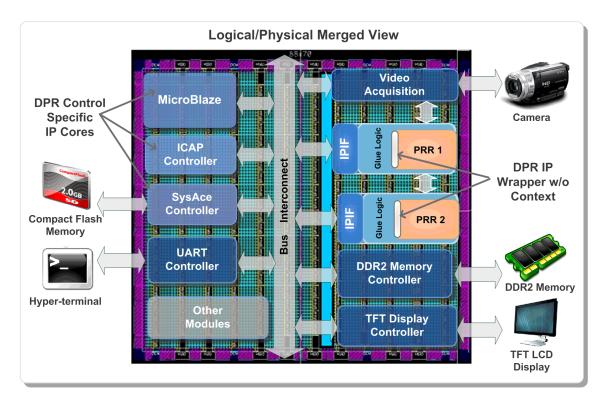

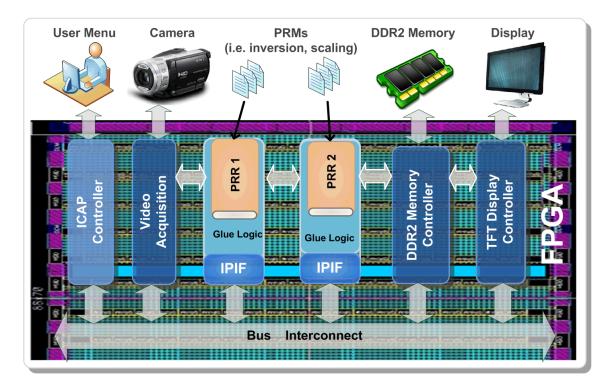

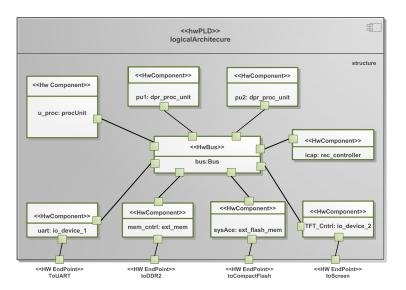

|     |       | 6.2.1   | Utilized System-on-Chip architecture                                                     | . 189 |

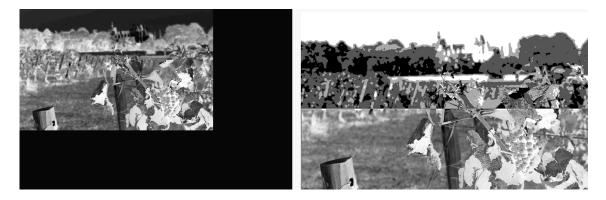

|     |       | 6.2.2   | Target applications                                                                      | . 191 |

|     | 6.3   | Case    | Study: a DPR image processing architecture                                               | . 193 |

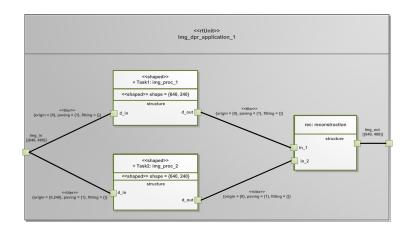

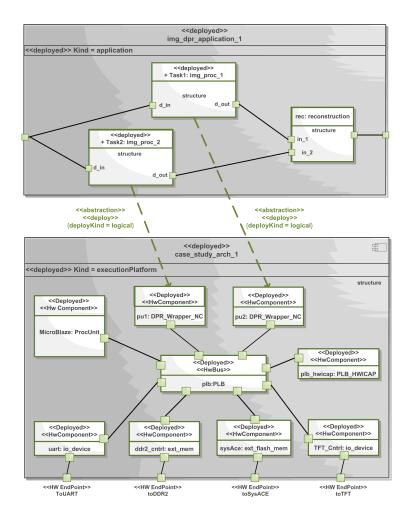

|     |       | 6.3.1   | Modeling of the application and its allocation onto the architecture                     | . 193 |

|     |       | 6.3.2   | Modeling of the architecture at the deployment level                                     | . 194 |

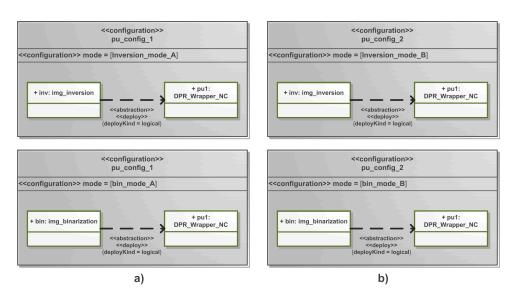

|     |       | 6.3.3   | Assigning configurations to the reconfigurable partitions                                | . 197 |

|     |       | 6.3.4   | Parameterization of the application hardware IP blocks                                   | . 199 |

|     |       | 6.3.5   | Parameterization of the static platform hardware IP blocks                               | . 201 |

|     |       | 6.3.6   | Generation of the Xilinx Platform Studio design description                              | . 201 |

|     | 6.4   | Gener   | ation and System Implementation Results                                                  | . 202 |

|     |       | 6.4.1   | Implementation of the transformation rules and used tools                                | . 203 |

|     |       | 6.4.2   | The platform transformation chain and its benefits over the tradi-<br>tional design flow | . 205 |

|     |       | 6.4.3   | Implementation results in an actual FPGA platform                                        | . 207 |

|     | 6.5   | Discus  | ssion and Conclusions                                                                    | . 208 |

| III | Ge    | neral   | Conclusion, Perspectives and Scientific Publications                                     | 211   |

| Bil | bliog | raphy   |                                                                                          | 239   |

**GENERAL INTRODUCTION**

# **INTRODUCTION**

#### CONTEXT AND PROBLEMATIC

In a changing world there is an ever increasing requirement for embedded systems to be able to adapt to their environment or to meet new application demands. This adaptability is not always limited to software running on processors: many embedded applications also require that the hardware supporting them also adapts. Reconfigurable hardware is the key enabler for these systems. Hardware supported adaptation mechanisms provide a cost effective way of coping with changing environmental requirements, improvements in system features, changing protocol and data-coding standards, etc. This is in addition to providing the required flexibility to allow functionality to be defined after a system has been manufactured.

Run-time reconfiguration (RTR) has been introduced in recent years as a means of virtualizing hardware tasks in FPGA systems. However, it was not was not until the introduction of Dynamic Partial Reconfiguration (DPR) technologies by Xilinx that these systems became a reality. In DPR systems, parts of the system can be reconfigured at run-time while the other functionalities in the FPGA remain operational. This capability can provide many benefits to the systems designers, such as power and resources reduction, amongst others. However, despite the efforts by Xilinx and many industrial and academic endeavours, using DPR in very complex systems remains a daunting task. This is due, in the first place, to the complexity of the design flow, which requires an in-depth knowledge of many low level aspects of the FPGA technology. Secondly, efforts in the academia to extend the capabilities of DPR design flow have further increased the complexity of DPR SoC designs. Furthermore, the creation of SoC DPR-based systems has very specific requirements, in particular, IP reuse capabilities in which the parameterization and integration of IP cores (both DPR and non-DPR components) is performed in such a way that facilitates the design process.

The key to being able to create ever more complex systems has been the ever-increasing level of abstraction at which designers capture and reason about these systems. As an example over a decade ago, the EDA industry moved from gate level to a register-transfer level abstraction. This has been the single key factor in being able to create complex silicon systems. However in the area of system level design there have been significant efforts in developing system level languages and to define new design methodologies at this abstraction level. The reason for all this activity is simple. Register-transfer level

(RTL) hardware design is too low an abstraction level to start designing multimillion-gate systems. What is needed is a way to describe an entire system, including embedded software and analog functions, and formalize a set of constraints and requirements - all far beyond the capabilities of existing HDL-based RTL design practices.

System level languages proposals can be classified into three main classes. First, by reusing classical hardware languages such as extending Verilog to SystemVerilog. Second, by creating new languages specified for system level design. Third, by adapting software languages and methodologies as ADA or behavioural VHDL, C/C++, JAVA and UML. Actually, this third class has been of special interest to the hardware design community for the last few years. Here additional hardware related concepts are added to an existing software language in the hope that it would allow hardware to become accessible to software designers.

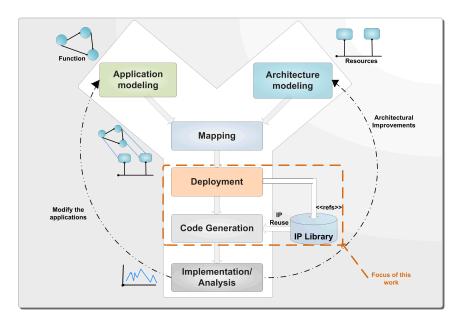

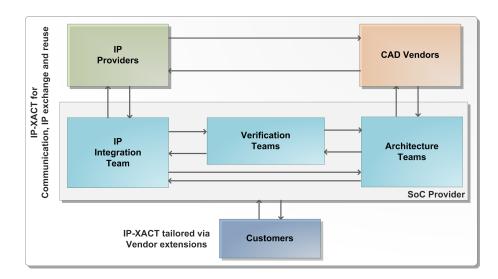

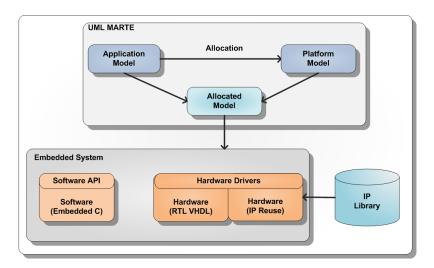

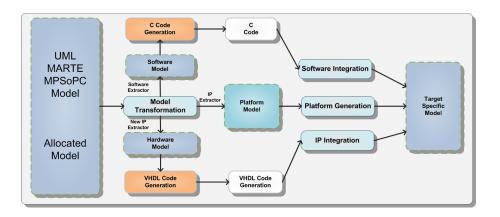

Among the emergent proposals in recent years, Model-Driven Engineering (MDE) has been used in co-design methodologies with relatively success in embedded systems modeling. Many of them make use of the UML profile for Modelling and Analysis of Real Time and Embedded Systems (MARTE). UML/MARTE models are used not only for communication purposes but, using model transformations, to produce concrete results such as a source code. For this purpose, MDE methodologies for SoC make use of a deployment phase in which the building blocks of the high-level models are linked to the low-level implementations that embody the related behaviour. This is basically an IP reuse problem, and in this way the components can be configured, and a synthesizable top-level implementation can be obtained. The main issue is that most MDE methodologies found in the literature make use of non-standardized IP and platform intermediate representations to move from the high-level models to the code generation phase. This fact has several implications, the first one being that UML MARTE platform models cannot easily exchangeable, limiting the interaction of MDE tools with other industrial ongoing efforts. Furthermore, the IP reuse tactics fostered by several methodologies based on customized metamodels are highly methodology-dependent, making it more difficult to adapt to different back-ends or evolve to the changing demands in the SoC industry.

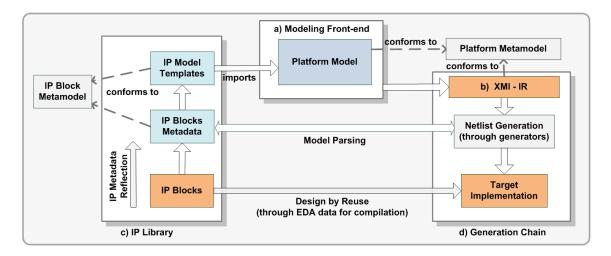

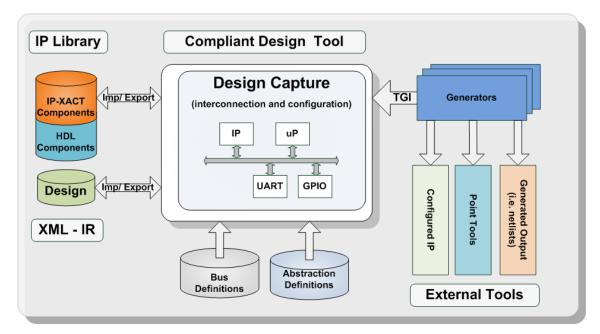

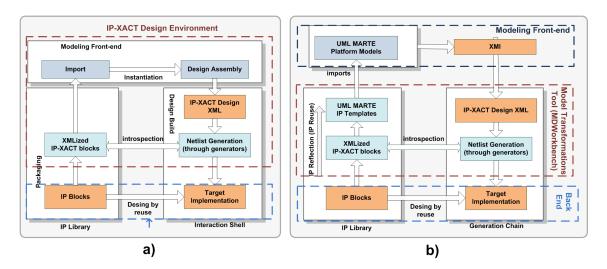

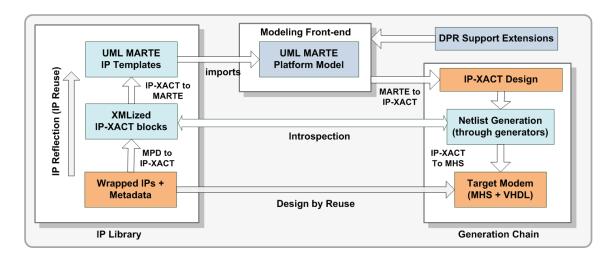

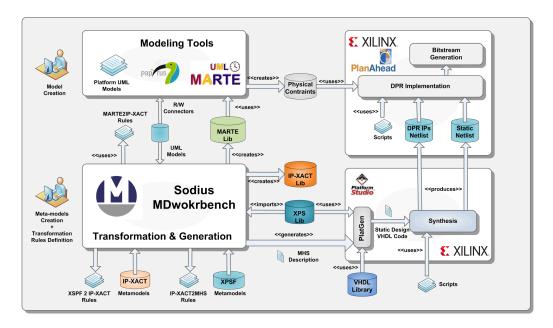

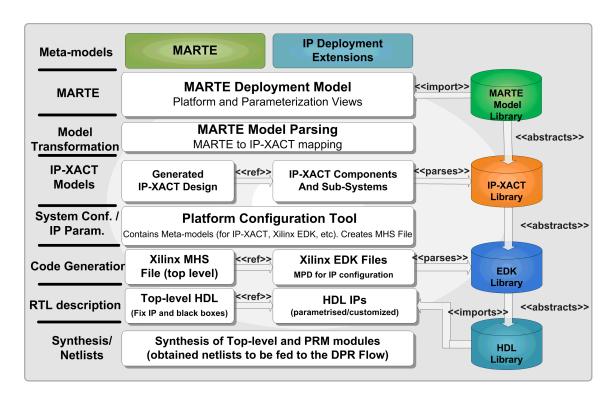

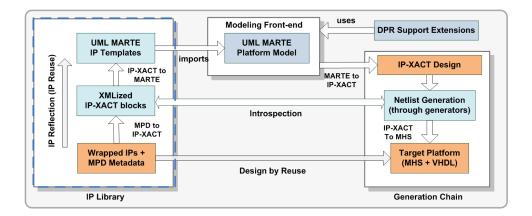

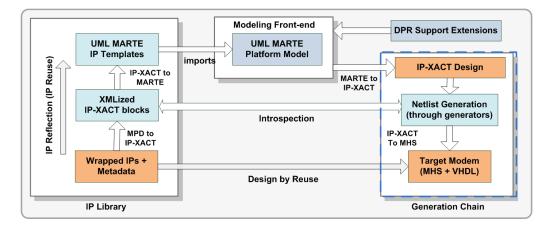

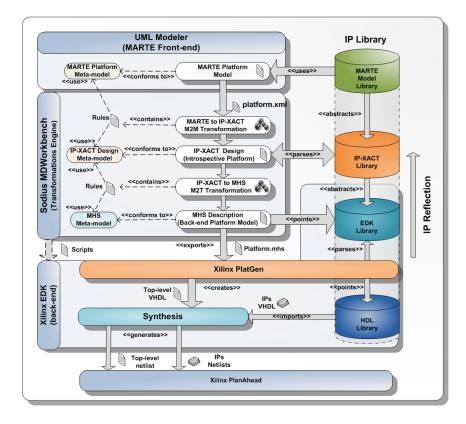

However, in recent years, the SPIRIT consortium has developed the IP-XACT specification that describes a standard way documenting IP meta-data for SoC integration, and which has culminated by its adoption as an IEEE standard. Several industrial case studies have demonstrated that the adoption of IP-XACT facilitates the configuration, integration, and verification in multi-vendor SoC design flows. Additionally to the IP packaging and integration, IP-XACT can also provide an effective means for IP reuse by linking the low level implementation to their high-level counterparts in an MDE approach. IP-XACT has gathered great interest during the last recent years, with more and more tools being developed around the standard; in parallel, the MDE community have recognized the importance of being compliant with other hardware description environments, and a great deal of research has been carried out for integrating both efforts. We believe that the combination of UML MARTE and IP-XACT can improve the applicability of the model-driven approaches to the development of FPGA-based SoC platforms, and in particular, facilitate the conception of DPR systems. This can be achieved by combining a component-based approach (for which IP-XACT was conceived) and a well fixed IP taxonomy for easily associating different blocks in the UML MARTE models to their IP-XACT counterparts that in fact abstract the HDL low-level IP implementations. However, targeting pure VHDL generation might be counter-intuitive, since it does not lend itself to further IP reuse; it is thus preferable to exploit the capabilities of IP-XACT as a standard intermediate representation (for both IP blocks and the platforms they compose) for generating the desired back-end representations. We have proceeded in this manner: we use IP-XACT for promoting IP reuse (IP reflection from the Xilinx XPS library) and design by reuse by generating the platform representation from IP-XACT. In both cases, the model transformations enable this passage seamlessly, without compromising the necessary abstraction in UML MARTE and the flow agnostic philosophy of IP-XACT regarding the target back-end.

Nevertheless, the IP-XACT standard, in its current version, does not support all the modeling aspects that approaches such as the MDE look after. Examples of these modeling endeavours are the conception of the application through Models of Computation, Schedulability or Design Space Exploration. However, the inclusion of IP-XACT in an MDE-based design flow can alleviate the interoperability issues of many current methodologies, greatly benefiting from the standard nature of the intermediate representation of the IPs and the SoC platform. However, in order to integrate IP-XACT in an MDE methodology, two aspects must be ensured. First an IP reuse mechanism through IP reflection that permits visualizing IP components in high-levels of abstraction, so a platform can be composed from these IP templates, must be set. Secondly, a mechanism for transforming the UML MARTE platform specification (stored as an XMI-IR) into its IP-XACT counterpart, and design object description has to be developed. The model transformations are the central part of any MDE methodology. A Model Transformation Tool (MTT) would permit the creation of the XMLized component descriptions, and on the other hand, the transformation from the XMI platform representation into the IP-XACT corresponding object. Furthermore, the MTT is also exploited for transforming the IP-XACT design description into the target implementation model, effectively decoupling the high-level models from the intended back-end.

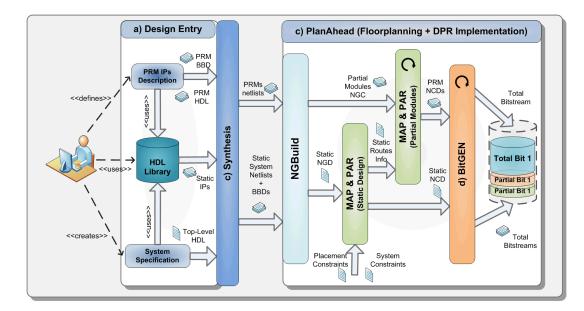

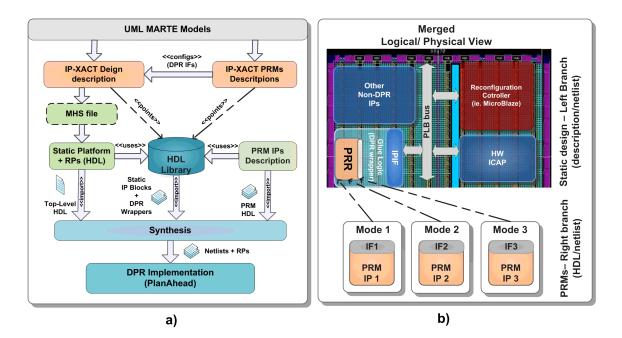

The contributions of this thesis relate then to the study and implementation of a MDEbased flow based on IP-XACT that enables the modeling of the hardware artifacts of the DPR design flow (the composition of the SoC platform, along the specification of the modules to be dynamically reconfigured), and its subsequent transformation into synthesizable code, which can be used for the final implementation on FPGA devices. More details will be provided in the next section, when discussing each chapter.

#### PLAN

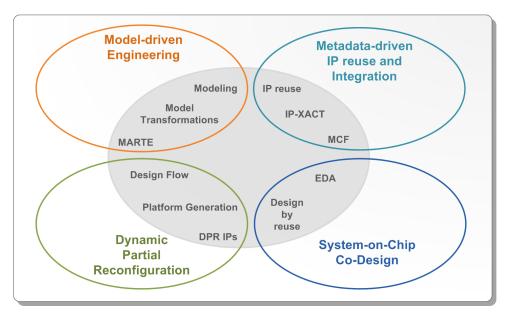

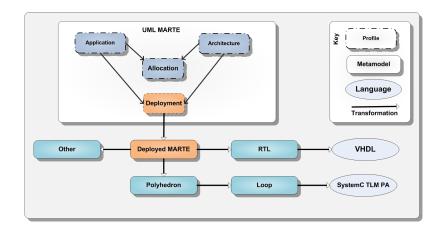

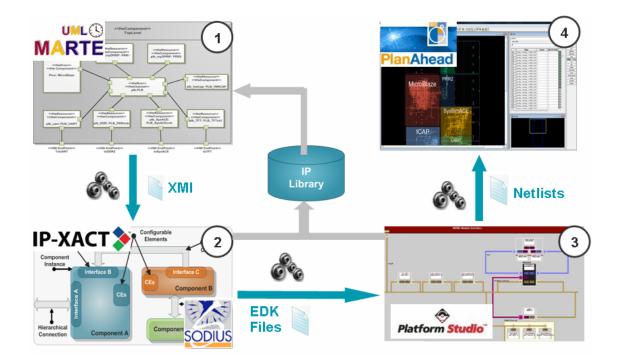

This thesis manuscript is divided into three main parts, the first one dealing with theoretical aspects necessary to understand the contributions of this work, which fall in four main research topics, as depicted on Figure 1.

Figure 1: Main topics of this thesis work

The subjects treated in each of the chapters is described as follows:

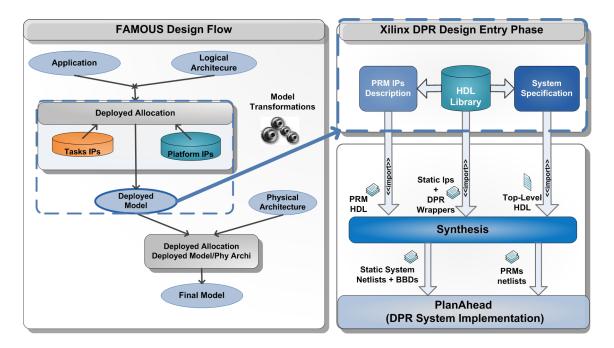

**Chapter 1: Reconfigurable Architectures and Dynamic Partial Reconfiguration:** The first chapter of this thesis introduces the concept of reconfigurable computing and the use of reconfigurable architectures in the creation of complex System-on-Chip Systems. The architecture of the FPGA devices is described with sufficient detail so that the reader can have enough elements to understand the complexity of the subject matter. Then, the limitations of FPGA-based SoCs, which are mainly due to the design flow employed for the conception of such systems, are explored, and the concepts of Run-Time Reconfiguration and Dynamic Partial Reconfiguration are introduced, as well as the advantages of such approaches. Afterwards, the Dynamic Partial Reconfiguration design flow is analyzed in detail, as well as its inherent complexities; this analysis is used to introduce the FAMOUS framework, in which this work is circumscribed, as well as the main contributions of this thesis.

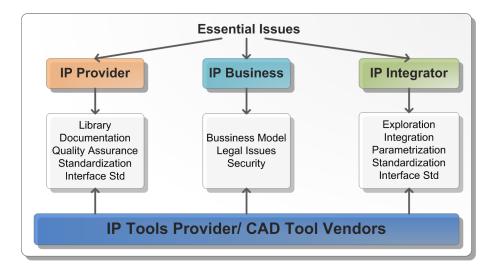

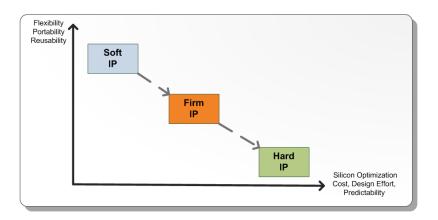

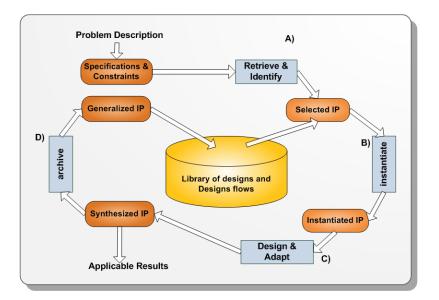

**Chapter 2: IP Reuse in MDE-based Co-design Methodologies:** This chapter explores in detail the Model-Driven Engineering paradigm, as well as the basic concepts required for understanding the main contributions of the thesis. Subsequently, one of the contributions of the thesis, in terms of providing IP reuse capabilities to the FAMOUS framework are delineated. We embark then into an in-depth description of the problems faced by the

SoC industry for promoting IP reuse and design for reuse, two ingredients that must be provided by any methodology aiming at the automatic generation of executable platform descriptions. With these basic concepts, we introduce the metadata-driven component composition framework (MCF) paradigm, and its limitations in terms of the intermediate systems representations (IR) used to pass from high-level models to the creation of synthesizable platform descriptions. We introduce then the IP-XACT standard, the chosen IR in the FAMOUS approach, and how this standard can alleviate the tool interoperability problems of many current MDE methodologies.

**Chapter 3: MDE-based methodologies for the creation of SoC**: Using the MCF paradigm as a launching pad, in this chapter we compare MDE methodologies that make use of MDE techniques for the modeling of SoC. We do not limit the comparison to FPGA targeted approaches, but to SoC design in general, dividing the comparisons into two categories: approaches that make use of UML and/or UML MARTE extensions for the modeling of complex SoC platforms (making use of custom metadata IR representations), and those who integrate IP-XACT as an intermediate system description. We situate the contributions of this work with respect to these approaches and make emphasis on the originality of this work in the closing discussion section.

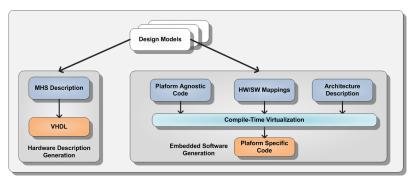

In the second part of this manuscript we embark in a detailed description of the proposed MDE-based framework for the generation of DPR platforms from UML MARTE. Chapter 4 deals with the use of Xilinx Platform Studio (XPS) for creating FPGA targeted SoC platforms, and how this tool can be used for composing complex DPR systems. We describe the Xilinx-specific IP and system description models, and how they are used for storing information about different components in the tool suite. The first part of Chapter 5 presents how the IP reuse library is obtained from the XPS IPs descriptions, using IP-XACT as an intermediate representation, via model transformations. Afterwards, we deal with the composition of complex SoC platforms from the previously obtained IP library, making emphasis on the MDE paradigm, and how an executable description can be created through a compilation chain consisting on a set of model transformations.

The last chapter of this thesis manuscript presents implementation results of two different DPR platforms. The contributions introduced in the previous three chapters are used here to present full-fledged examples of how the presented methodology is used for creating such platforms in UML MARTE. Some perspectives and conclusions are presented in the final chapter.

Chapter 4: The role of the proposed approach in the DPR Design Flow: In this chapter we discuss how the proposed IP reuse and system composition methodology interacts with the Xilinx Dynamic Partial Reconfiguration design flow. Since we aim at a component-based approach, we make use of IPs with CoreConnect interfaces using the

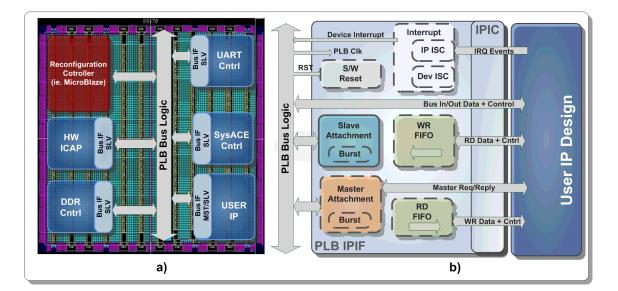

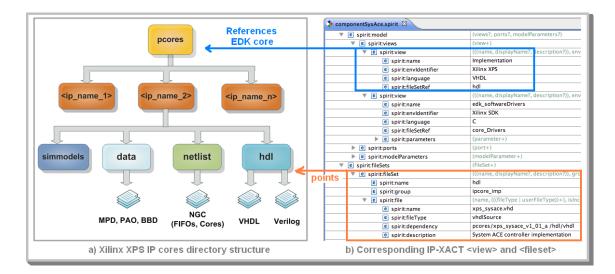

Xilinx Platform Studio suite, a software tool the enable us to generate SoC platforms in a straightforward manner. We describe how the IPs are wrapped by the CoreConnect interfaces and we define an IP taxonomy for the MCF, dividing IPs into static and partially reconfigurable IPs containing or not Reconfiguration Services. Then, we discuss how XPS stores the IP and system representations, and how we plug our methodology into this back-end for promoting IP reuse and design by reuse of these components.

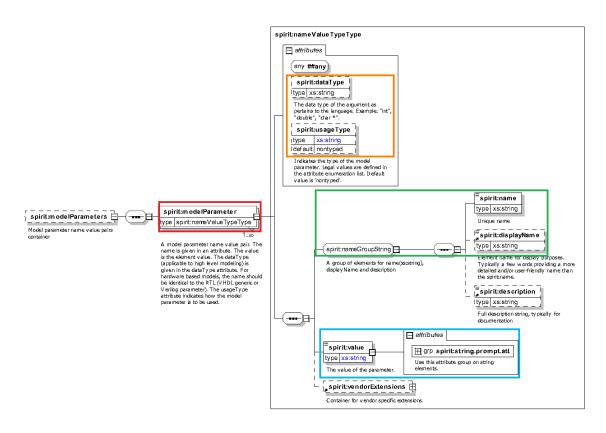

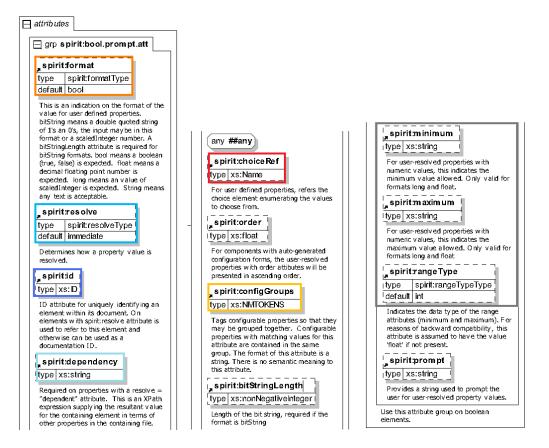

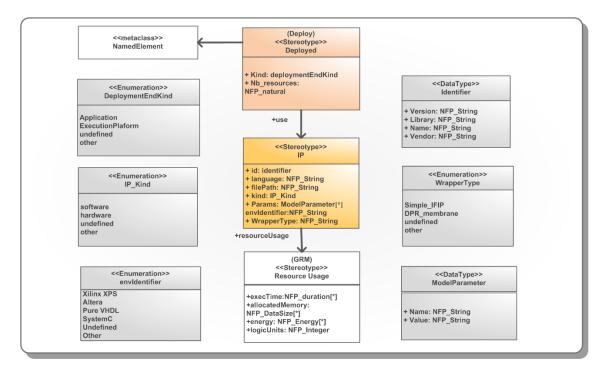

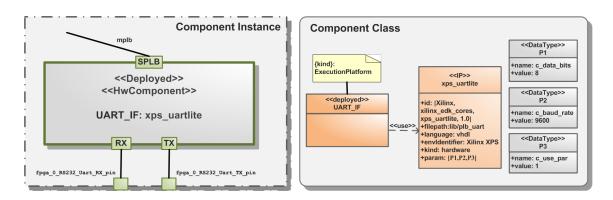

**Chapter 5: Proposed Methodology**: Using the IP taxonomy proposed in the previous chapter, and the knowledge of how the IPs are wrapped and used in the XPS framework. We introduce how the IP-XACT standard is exploited in our methodology for creating a vendor-agnostic IP library through model transformations from the Xilinx XPS intermediate representation. We present the main IP-XACT concepts related to interfaces and components, as well as necessary vendor extensions for making this transformation possible. Then, we introduce an IP deployment metamodel that enables us to obtain a MARTE representation of the IPs contained in the IP-XACT library. In this manner, we obtain a multi-level library through metadata reflection, which can be used for composing a platform at high levels of abstraction.

Once the multi-level component IP library has been created, it can be used for composing a SoC DPR platform. The deployment IP extensions introduced in the first part of the chapter are used in the second part of the chapter to describe how an UML MARTE platform description is transformed into an IP-XACT dessign, through model transformations. The concept of IP-XACT design description is analyzed in detail, as well as its purpose in a system generation flow. This object is employed as an introspective description, which is used for parsing the instantiated components for propagating constraints, and through a second model transformation, to automatically generate the XPS platform description

**Chapter 6: Case Study**: In the last chapter, we present two case studies to demonstrate how the proposed IP reuse and system composition framework are used for creating a DPR platforms in UML MARTE. And then how through model transformations, a synthesizable platform description can be obtained along the Partially Reconfigurable Modules to be mapped into the platform at run-time. We present synthesis results and more importantly, a discussion on how the proposed approach eases the conception of DPR systems at the entry level phase of the Xilinx design flow. Some metrics on the required design effort are presented, along a discussion on how MDE methodologies can automate the many complex tool interactions in the flow and furthermore, abstract the technologic dependent aspects of the flow to users working at a high-level of abstraction.

# CONTEXT AND PROBLEMATIC

1

# RECONFIGURABLE ARCHITECTURES AND DYNAMIC PARTIAL RECONFIGURATION

#### Contents

| 1.1 | Introduction                                                 |                                                                     |    |

|-----|--------------------------------------------------------------|---------------------------------------------------------------------|----|

| 1.2 | 1.2 Reconfigurable Architectures                             |                                                                     |    |

|     | 1.2.1                                                        | Logic Resources, Routing and interconnections                       | 24 |

|     | 1.2.2                                                        | Heterogeneous Platforms                                             | 26 |

| 1.3 | <b>1.3</b> Use of FPGAs in SoC Systems and their limitations |                                                                     |    |

|     | 1.3.1                                                        | Traditional FPGA design flow                                        | 28 |

|     | 1.3.2                                                        | Limitations of traditional FPGA designs flow                        | 30 |

| 1.4 | Xilinx                                                       | Partition Partial Reconfiguration design flow                       | 33 |

|     | 1.4.1                                                        | Design partitioning                                                 | 34 |

|     | 1.4.2                                                        | Synthesis                                                           | 34 |

|     | 1.4.3                                                        | Planning                                                            | 35 |

|     | 1.4.4                                                        | DPR System Implementation                                           | 37 |

|     | 1.4.5                                                        | Bitstream Generation                                                | 38 |

|     | 1.4.6                                                        | Reconfiguration management                                          | 39 |

| 1.5 | Challe                                                       | enges in the conception of Partially Reconfigurable Systems-on-Chip | 41 |

|     | 1.5.1                                                        | Dynamic Partial Reconfiguration Tool Flow                           | 41 |

|     | 1.5.2                                                        | The FAMOUS Framework for DPR Systems                                | 43 |

| 1.6 | Discus                                                       | ssion and Conclusions                                               | 45 |

#### 1.1/ INTRODUCTION

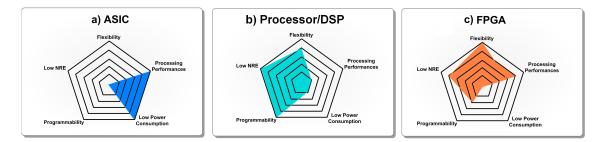

Reconfigurable computing systems use FPGAs or other programmable hardware to implement complex algorithms execution by mapping computationally-intensive calculations to the reconfigurable substrate [1].Traditionally, there have been two primary methods in conventional computing for the implementation of algorithms into hardware. The first is to use Application Specific Integrated Circuits (ASIC). They are designed to specifically perform a given task, and thus they are very fast and efficient; however, the circuit cannot be altered or updated after fabrication, forcing to redesign and fabricate a new platform if a change or upgrade is necessary, a very expensive process (presenting a high Non-Recursive Engineering cost, NRE), as depicted on Figure 1.1 a). Then, the use of ASICs is only justified in consumer electronics that are characterized by very short time to market, and high volumes [2].

The second approach is to use software-programmed microprocessors (and by extension, DSPs), a far more flexible solution. Processors execute a set of instructions to perform a computation. By changing the software instructions, the functionality of the system is altered without changing the hardware. However, the downside of this flexibility is that the performance can suffer, if not in clock speed then in work rate, and is far below that of an ASIC [3] and they suffer from the sequential execution constraint, making them not suitable for many applications in which real-time performances are necessary, as depicted on Figure 1.1 b).

Figure 1.1: Comparison between different technologies used in SoC

Reconfigurable computing, making use of FPGA devices, is intended to fill the gap between hardware and software approaches, achieving potentially much higher performance than microprocessors, while maintaining a higher level of flexibility than ASICs [4], as depicted on Figure 1.1 c). Reconfigurable devices, including Field-Programmable Gate Arrays (FPGAs), contain an array of computational elements whose functionality is determined through multiple programmable configuration bits. These elements, sometimes known as logic blocks, are connected using a set of routing resources that are also programmable. In this way, custom digital circuits can be mapped to the reconfigurable hardware by computing the logic functions of the algorithm within the logic blocks, and using the configurable routing to interconnect the blocks to create the necessary function [5].

However, FPGA systems suffer the handicap of having a high-power consumption and a very low programmability, a factor that has limited their adoption, as depicted on the parametric graph.

In recent years, the research community has carried many endeavours in the adaptivity of electronic systems to environmental conditions and inner system status, which in theory can enable the processing of different applications in time slots on a single FPGA. This adaptivity on-demand, related to non-predictable requirements from the user or the environment implies the optimization of power dissipation and performance at run-time by providing on-chip computation capacities [6]. Traditional FPGA systems cannot provide these capacities due the nature of the design flows in which they inserted; most FPGAs are currently used as drop-in ASIC replacements or in many cases, as a platform for developing Systems-on-Chip. In order to provide devices at a competitive cost, most FPGA vendors forgo innovative configuration architectures in favour of simpler single-context designs, which the community has found somewhat limiting for implementing full-fledged run-time reconfigurable systems. However, in recent years, Xilinx and other FPGA vendors have introduced the concept of Dynamic Partial Reconfiguration (DPR), which enables to adapt small sections of the hardware platform on run-time, without halting the system functionality. Using DPR, systems behaviour can be tuned for improving its power consumption, ameliorating one of the handicaps mentioned above.

However, and despite the efforts by Xilinx and many industrial and academic endeavours, using DPR in very complex systems remains a daunting task. This is due, in the first place, to the complexity of the design flow, which requires an in-depth knowledge of many low level aspects of the FPGA technology. Secondly, efforts in the academia to extend the capabilities of DPR design flow have further increased the complexity of such systems. Nevertheless, the creation of SoC DPR-based systems could alleviate the programmability issues traditionally associated with FPGA-based systems, a trend that is becoming widespread, with the introduction of Extensible Processor Platforms. Such systems have very specific requirements, in particular, IP reuse and design by reuse capabilities must be provided, in which the parameterization and integration of IP cores (both DPR and non-DPR components) can performed in such a way that facilitates the design process.

The purpose of this chapter is to provide the reader with an in-depth knowledge of FPGAs architectures and how they are used for implementing complex embedded systems. The adaptivity limitations discussed above are then analyzed in detail, and the concept of run-time reconfiguration, as well as its advantages, is then described. Since one of the main goals of the FAMOUS project, and of this thesis work in particular, is facilitating the conception of DPR systems, as well as abstracting the burden of the design flow and the associated tools, these subjects are both described thoroughly. At the end of the chapter, the FAMOUS framework for facilitating the modeling and generation of DPR systems is introduced, as well as the main goals of this work.

#### 1.2/ RECONFIGURABLE ARCHITECTURES

Before discussing the detailed aspects of dynamic partial reconfiguration, we will describe the architecture of FPGA devices, since DPR cannot be understood without a minimum of knowledge of the underlying FPGA resources (Configurable Logic Blocks, programmable interconnection and routing, and finally, heterogeneous blocks). More detailed surveys of FPGA architectures can be found elsewhere [7,8] whereas schemes for configuration can be found in the manuals of the manufacturers.

#### 1.2.1/ LOGIC RESOURCES, ROUTING AND INTERCONNECTIONS

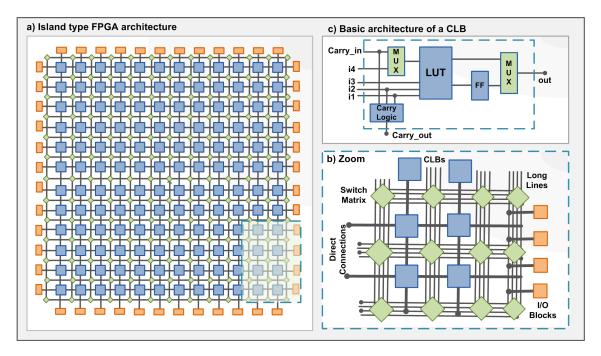

An FPGA device is an integrated circuit with a central array of logic blocks that can be connected through a configurable interconnect routing matrix. Around the periphery of the logic array is a ring of I/O blocks that can be configured to support different interface standards. This flexible architecture can be used to implement a wide range of synchronous and combinatorial digital logic functions. It is common to categorize FPGA platforms as either fine grained or coarse grained. This is due to the fact that their underlying fabric predominantly consists of large numbers of relatively simple programmable logic block islands embedded in a sea of programmable interconnect, as depicted on Figure 1.2 a)

Figure 1.2: Generic FPGA hardware architecture

After several decades of research, it has been established that the best function block for a standard FPGA is a Logic Block built around a lookup table (LUT). An N-input LUT is basically a memory that, when programmed appropriately, can compute any function of up to N inputs. This flexibility, with relatively simple routing requirements (each input needs only to be routed to a single multiplexer control input) turns out to be very powerful for logic implementation. The typical FPGA has a logic block with one or more N-input LUT(s), optional D flip-flops (FF), and some form of fast carry logic, as depicted in Figure 1.2 b). For instance, Xilinx has introduced 6-input LUT(s) in their Virtex 6, Virtex 7 and Spartan 6 FPGA families. The LUTs allow any function to be implemented, providing generic logic. The flip-flop can be used for pipelining, implementing registers, state-holding functions for finite state machines, or any other situation where clocking is required. The fast carry logic is used to speed up carry-based computations, such as addition, parity, wide AND operations, and other functions. In the case of a fine-grained architecture, each logic block can be used to implement only a very simple function. For example, it might be possible to configure he block to act as any 3-input function, such as a primitive logic gate (AND, OR, NAND, etc.) or a storage element (D-type flip-flop, D-type latch, etc.). In the case of a coarse-grained architecture, each logic block contains a relatively large amount of logic compared to their fine-grained counterparts.

Just as there has been a great deal of research in FPGA logic block architectures, there has been equally as much investigation into interconnect structures. As logic blocks have basically been standardized on LUT-based structures, routing resources have become primarily island-style, with logic surrounded by general routing channels. Most FPGA architectures organize their routing structures as a relatively smooth sea of routing resources, allowing fast and efficient communication along the rows and columns of logic blocks. As shown on Figure 1.2 c), the logic blocks are embedded in a general routing structure, with input and output signals attaching to the routing fabric through connection blocks. The connection blocks provide programmable multiplexers, selecting which of the signals in a given routing Switches) are also programmable, and allow connections between the horizontal and vertical routing resources to permit the signals to change their routing direction. In this manner, relatively arbitrary interconnections can be achieved between logic blocks in the system.

The ring of I/O banks surrounding the array of CLBs is used to interface the FPGA device to external components. Traditionally, the ring of I/O banks is either staggered or in-line around the FPGA device. The difference between staggered and in-line I/O is just as the names describe. A trade-off must be made architecturally between the number of available signal pins and the amount of resources implemented within the device. I/O block (IOB) is a common term used to describe an I/O structure, although other names may also be used. An IOB includes input and output registers, control signals, multiplexers and clock signals. The signals routed through the I/O block can be registered or unregistered. In order to interface to different types of logic, an FPGA device IOB must support multiple IO interface standards. Both single-ended (e.g. PCI, LVTTL) and differential operational modes (i.e. LVDS) are typically supported.

#### 1.2.2/ HETEROGENEOUS PLATFORMS

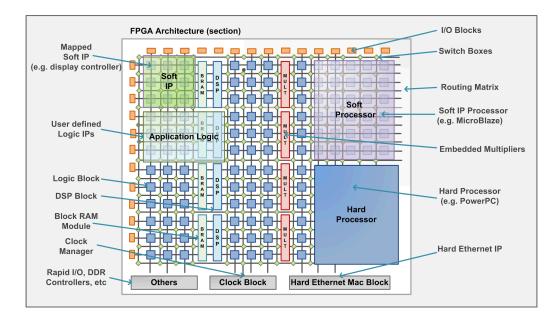

In order to provide greater performance or flexibility in computation, FPGA vendors have gradually incorporated more functionalities into their programmable chips [9]. These functionalities are embedded into the circuit logic resources, producing a heterogeneous structure, where the capabilities of the logic cells are not the same throughout the system. This approach has become a necessity due to the widespread adoption of FPGAs for implementing complex platforms, such as Systems on Chip, where multiple processors, communication standards and memory controllers are required.

Furthermore, DSP applications (such as image and video processing) often require of complex functions such adders and multipliers, along complex and highly parametrisable DSP functions (DSP Blocks). In both scenarios, such modules are difficult to implement in an optimal manner using generic FPGA logic resources; therefore, FPGA vendors have introduced such complex blocks in the form of hardwired functions. These blocks are designed to be as efficient as possible in terms of power consumption, silicon real estate, and performance. Each FPGA family features different combinations of such blocks, together with various quantities of programmable logic blocks, as depicted on Figure 1.3

Another type of heterogeneous logic structures are memory blocks, known as Block-RAMs, which are scattered throughout the reconfigurable hardware. These blocks enable the storage of frequently used data and variables, and permit a quick access to these values due to the proximity of the memory inside the FPGA to the logic blocks that access it [3]. These blocks can also be used for a variety of purposes, such as implementing standard single- or dual-port RAMs, FIFO functions, state machines, and so forth.

Figure 1.3: Heterogeneous FPGA platform, depicting general configurable resources, hard blocks and eventual soft IPs

Another major trend, briefly introduced in the previous section, its the introduction of complete microprocessor solutions into the FPGA fabric, known as hard processors [10]. Similarly, the so called soft core processors (i.e. components that made use of the FPGA logic resources for their implementation) have been designed and employed in a variety of applications, particularly in tasks that cannot be parallelized or in situations where the control of the system is better suited for a processor solution. Using embedded processors brings many advantages, particularly the reduction in chip count, the number of tracks, signal integrity issues, and a decrease on the board complexity.

At the other end of the spectrum, soft IP refers to a source-level library of high-level functions that can be included in the design. These functions are typically represented using a hardware description language, or HDL, such as Verilog or VHDL at the register transfer level (RTL) of abstraction. Any soft IP functions the designers decide to use are incorporated into the main body of the design which is also specified in RTL and subsequently synthesized down into a group of programmable logic blocks (possibly combined with some hard IP blocks like multipliers, DPR and BRAMs) and then mapped onto the FPGA. For instance, Figure 1.3 depicts two scenarios for the use of Soft IPs: in the first case, the function can be an functionality provided by FPGA vendors, such as the TFT interface; a second scenario is that a custom implementation of an IP is created by the user for a given application, and which can be implemented using a set of CLBs, DSP and Block RAM modules.

As performance and throughput become increasingly important, modern FPGA devices offer support for various high-speed communication standards. This is due to the high-performance of FPGA in accelerating complex computations: data needs to be transmitted rapidly and efficiently to other nodes of the system, while preventing the FPGA to become the bottleneck of the platform. Examples of these standards are Infiniband, PCI Express, RapidIO, and 10-gigabit internet, among others. In a similar manner, vendors offer optimized hardwired cores for a variety of solutions; examples of these cores are DDR, DDR2 and DDR3 controllers, MAC controllers, and LVDS Transmitters. For a more detailed description in these technologies the reader is directed to the vendors websites [11] or to excellent compendiums in the literature [5].

Finally, the primary FPGA element for handling, managing and adjusting FPGA local and system clocks is the Clock block. Input clocks, from external sources and connected to specialized FPGA pins can then be used to drive a special hard-wired function (block) known as clock managers, which are programmed to generate a number of daughter clocks, then fed to different components on the platform. In this manner, subsystems running at different frequencies can be created, either to work independently or in conjunction, adding for the heterogeneity of the target applications compared to both ASICs and processor-based solutions.

#### 1.3/ Use of FPGAs in SoC Systems and their limitations

#### 1.3.1/ TRADITIONAL FPGA DESIGN FLOW

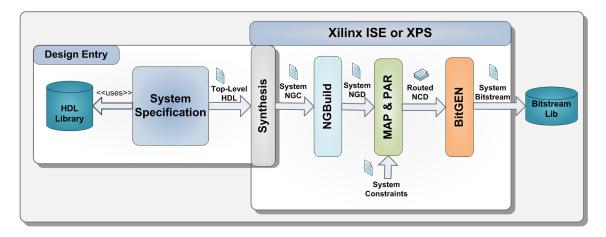

The standard FPGA design flow (in this case, Xilinx), as depicted on Figure 1.4 transforms an FPGA design description into a configurable bitstream. Typically, the FPGA design description is written in Hardware Description Language, like Verilog, VHDL, System C or Handel C. More complex designs often make use of system integration tools to construct the initial design description from libraries of intellectual property (IP) components, which are used along user defined functions to create System-on-Chip applications. Each pass through the standard design flow is independent of subsequent passes. The bitstream produced at the end of the flow is dependent only of the initial design specification and it is used to configure the entire device.

Figure 1.4: Traditional FPGA design flow

An in-depth discussion of each of these steps is outside of this scope of this work given their complexity, but the reader is directed to the manufacturer IO Command Line Tools User Guide(formerly known as the Development System Reference Guide) [12] for more details. Nevertheless, it is important to understand the basic principles in order to provide some insight into the methodology and thus each of the steps is briefly discussed as follows.

1.Design Entry: In this stage of the design flow, the design is created using a FPGA-vendor supported schematic editor, text-based entry (HDL), or both (i.e. Xil-inx ISE). In a similar way, the platform can be based in a combination of embedded processor, peripherals and user created logic; in such scenario, the design can be created using a specialized tool, such as Xilinx Platform Studio (XPS) [13].

These tools enable the designer to create a design in a user-friendly environment, while the design effort to obtain the VHDL top-level description is greatly reduced.

- 2.Design Implementation: Usually, the design specification is done regardless of the target implementation FPGA family. However, if certain features from a specific FPGA are necessary, then these constrains are taken into account from the very beginning; nonetheless, at the synthesis phase, the tool support targets a particular FPGA device. Then, a conversion of the logical design file format, such as EDIF, that was created in the design entry stage is translated to physical file format. The physical information is contained in the NGC file for FPGAs.

- 3.NGDBuild: This stage performs all the steps necessary to read a netlist file in NGC or EDIF format and creates a NGD file describing the logical design (a logical design in terms of logic elements such as AND gates, OR gates, decoders, flipflops, and RAMs). The NGD file resulting from an NGDBuild run contains both a logical description of the design reduced to Xilinx NGD (Native Generic Database) primitives and a description in terms of the original hierarchy expressed in the input netlist. The output NGD file can be mapped to the desired device family.

- 4. Map: The mapping algorithms translate a logical design into a description that can be implemented into a specific FPGA device. The input to mapping is an NGD file, which contains a logical description of the design in terms of both the hierarchical components used to develop the design and the lower level Xilinx primitives, and any number of NMC (macro library) files, each of which contains the definition of a physical macro.

MAP first performs a logical DRC (Design Rule Check) on the design in the NGD file. MAP then maps the logic to the components (logic cells, I/O cells, and other components) in the target Xilinx FPGA. The output design is an NCD (Native Circuit Description) file, a physical representation of the design mapped to the components in the Xilinx FPGA. The NCD file can then be placed and routed.

- 5.PAR: After a design has undergone the necessary translation to bring it into the NCD (Circuit Description) format, it is ready for placement and routing. This phase is done by PAR (Xilinx's Place and Route program). PAR takes an NCD file, places and routes the design, and outputs an NCD file which is used by the bitstream generator (BitGen).

- 6.Bitstream Generation: Produces a bitstream for Xilinx device configuration. After the design has been completely routed, it is necessary to configure the device so that it can execute the desired function. This is done with BitGen, Xilinx bitstream generation program. BitGen takes a fully routed NCD file and produces a configuration bitstream. The bit file contains all of the configuration information from the NCD defining the internal logic and interconnections of the FPGA. The binary data in the BIT file can then be downloaded into the FPGA memory.

#### 1.3.2/ LIMITATIONS OF TRADITIONAL FPGA DESIGNS FLOW

Despite of the success of FPGAs in several domains, many system architects have found the traditional FPGA implementations too limiting [14], since once the design has been implemented in the circuit, any change would require undergoing the entire specification stages on Figure 1.4. This fact poses a problem in applications where a higher adaptivity on the application would be desirable, due to the manner in which the FPGA is programmed. In fact, the bitstream obtained from the design flow is charged onto the FPGA at power-up; this is due to technological reasons: the FPGAs are based on SRAM cells; thus, once the device is switched off, the totality of its functionality is lost. As mentioned previously, FPGAs are the preferred solution in applications where fabricating millions of ASICs is not an option; they also provide a bigger flexibility, since they can be re-programmed on field (hence the Field Programmability in the name), allowing for updates to be made, just as with processor-based applications, which usually only require a change in the firmware to perform a new mission.

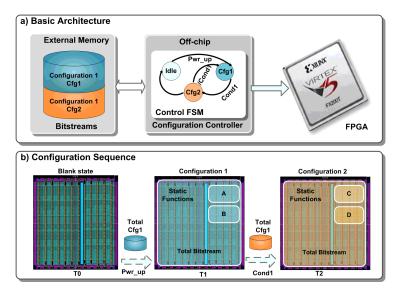

Figure 1.5: Run-time reconfiguration in a non-DPR design

Nevertheless, if the application needs to be changed at-run time [3] (some of these scenarios will be described as follows), the application would require to stop the FPGA and reconfigure it in its totality, as depicted on Figure 1.5. Furthermore, this process traditionally requires the use of an external processor, which is in charge of retrieving the configuration bitstreams from non-volatile memory using a relatively simple state machine [15]. Using an external processor increases the chip count and thus the cost of such a system, but a second problem arises: storing the totality of the bitstream for each configuration (even if the differences between each implementation is very small, as depicted on Figure 1.5 b), where only functions A and C are replaced by modules D and E) leads to increased memory storage requirements, further augmenting the cost of the system. Last, but not less important, is the time required for the system to be reconfigured; as the totality of

Figure 1.6: Run-time dynamic partial reconfiguration

the FPGA needs to be modified, a non-negligible amount of time (in the order of several seconds for large FPGAs) is lost to perform the reconfiguration process [16] [17], without even taking into account the access to the bitstreams from the non-volatile memory [2].

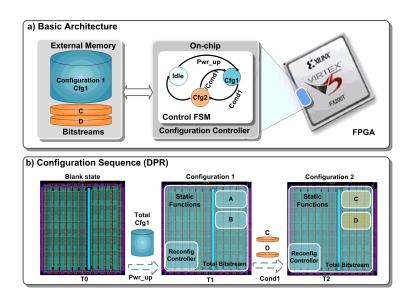

#### 1.3.2.1/ RUN-TIME PARTIAL RECONFIGURATION

In the last two decades, the concept of runtime reconfiguration (RTR) was introduced to describe systems capable of swapping in and out different configurations of the reconfigurable hardware as they are needed during the application execution [18]. However, the nature of the traditional design flows and other technological underpinnings had prevented the adoption of RTR techniques, since slow-downs in system performance or its viability in critical systems had made their implementation downright prohibitive. In recent years, Dynamic Partial Reconfiguration (DPR) has been introduced as a method to add flexibility to FPGA-based solutions. Through the use of DPR, a module of the system can be substituted by other functionality or simply taken out the reconfigurable fabric on demand, as depicted on Figure 1.6, without halting the device to perform the desired modification, and thus without impacting the execution of the system.

This is achieved by separating the logic into static and dynamically reconfigurable areas; this means that a section of the FPGA remains operational during the totality of the applications execution, whilst small areas of the FPGA can be reconfigured on the fly. For instance, our example shows a system containing a microprocessor and some peripherals as part of the static logic, whereas two modules comprise the dynamic part of the system. Each of the dynamic areas is reconfigured independently, by charging solely the reconfiguration information (know an as partial bitstream) required to modify its functionality. Apart from providing an increased flexibility to the application, DPR has many intrinsic

advantages. For instance, the reconfiguration time is diminished, since only a fraction of the total configuration information is retrieved from external memory. Moreover, these partial bitstreams are much smaller than a complete bitstream, which leads to a reduced external memory footprint, as depicted on Figure 1.6 b). The use of a processor (as in the previous case) is also necessary, but as it can be embedded along the rest of the static logic (using and on-chip processor such as the MicroBlaze), reducing the chip count and the complexity of the system.

#### 1.3.2.2/ BENEFITS OF RUN-TIME PARTIAL RECONFIGURATION

Partial Reconfiguration allows using more hardware than that physically present in the FPGA by virtualizing hardware tasks and mapping them on-demand. This capability can be exploited to reduce the size of the FPGA and its overall power consumption. This also permits to execute an algorithm with an optimized implementation depending on its parameters and data set. Furthermore, upon the usual speed and power research goals, DPR offers system-level advantages for professional electronics [19]. Some of the scenarios in which DPR has proven successful are listed as follows.

- (a) Hardware virtualization. Frequently, the areas of a program that can be accelerated through the use of reconfigurable hardware are too numerous or complex to be loaded simultaneously onto the available hardware. For these cases, it might be beneficial to swap different configurations in and out of the FPGA as they are needed. Since this mapping is performed on-demand, the system can adapt dynamically, effectively promoting software-like component virtualization.

- (b) Logic Resources Utilization and Power Reduction A system might need to contain multiple implementations of a module that performs a similar task, but which are mutually exclusive. These multiplicity reduces the amount of logic that can be accommodated into a single device; by being able to reduce the amount of logic (and the required static power consumption) that an application uses at any given time, more functionalities can be integrated into a smaller FPGA.

- (c) Survivability. There is a great deal of research in the areas of evolvable hardware and fault tolerant systems; in the second case, the system could operate in a degraded mode when a part of the system is damaged. This can be achieved by moving the function initially mapped to a damaged area of the FPGA to another.

- (d) Mission change. A system can be reconfigured for a new mission without halting its functionality. This capability enables for adding functionalities that were not specified at the beginning, or in many instances, updates that can ameliorate the application performance.

#### 1.4/ XILINX PARTITION PARTIAL RECONFIGURATION DESIGN FLOW

In the previous sections we have discussed the limitations of traditional FPGA designs, which are constrained by the manner in which the original system specification is mapped, placed and routed on the FPGA. As discussed before, the obtained bitstream configures the totality of the FPGA, even if internally the FPGA resources can be addressed in units called frames. An in-depth discussion the architectural features limiting the adoption of partial reconfiguration in many Xilinx FPGA devices (mostly Virtex families) is outside of the scope of this work; for an in depth discussion of the evolution of these features, as well the evolution of the Partial Reconfiguration design flow, the reader is directed to previous work [20], or to excellent reviews in the literature [2,21]. As stated above, the main difference between DPR and non-DPR systems using Virtex devices, lies not on architectural constraints, but in the nature of the design flow; the DPR design flow makes use of techniques and tools usually not required in traditional designs, making it more difficult to exploit [22]. However, significant advances have been made by Xilinx to improve the usability of the tools, automating many previously burdensome design flow-specific phases.

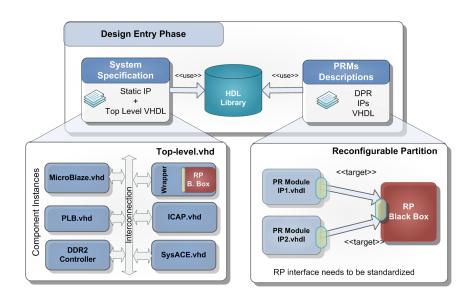

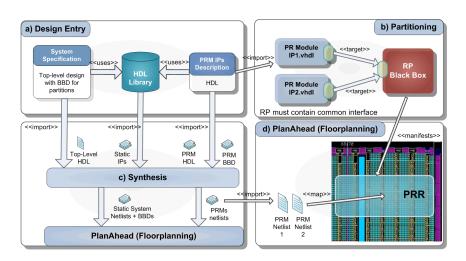

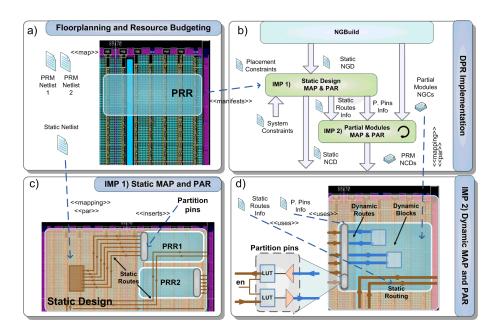

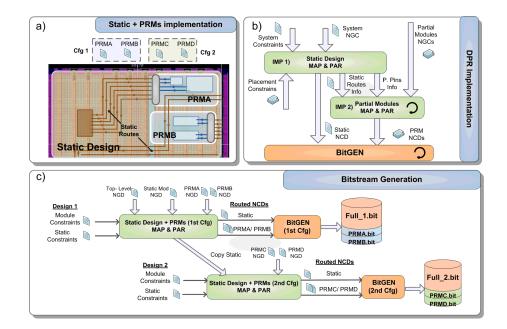

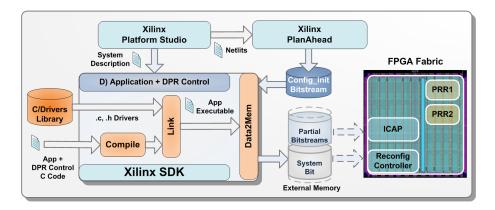

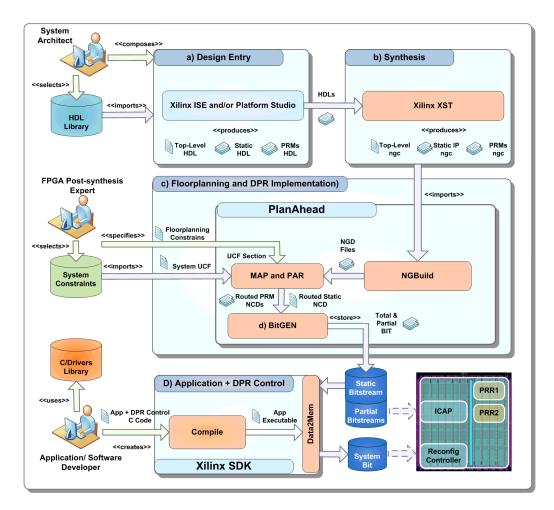

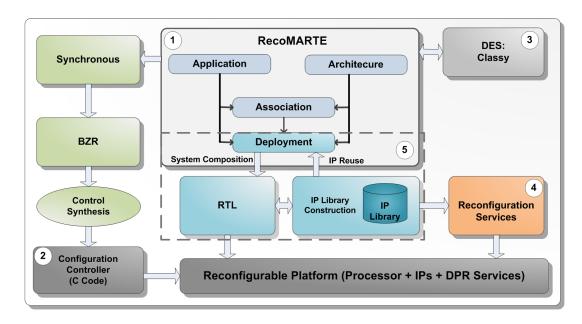

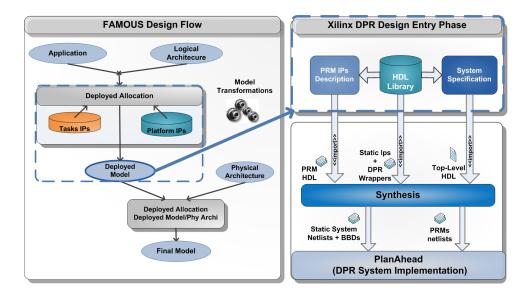

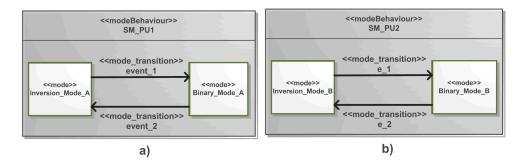

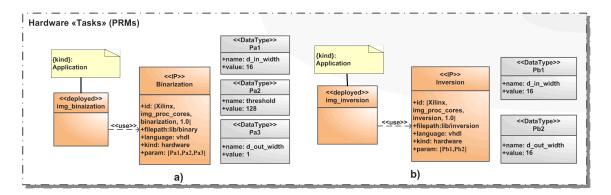

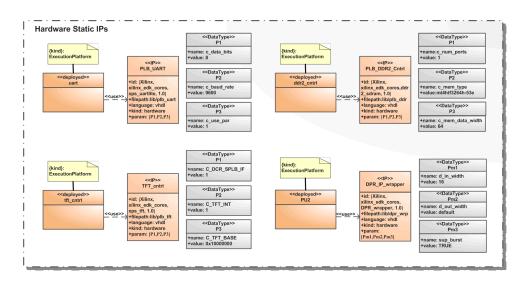

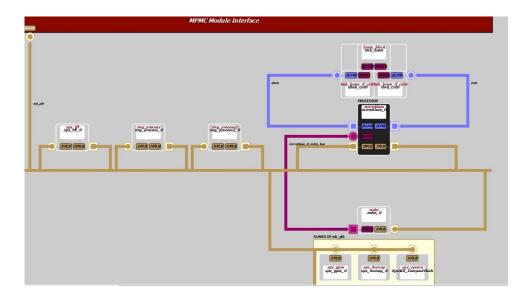

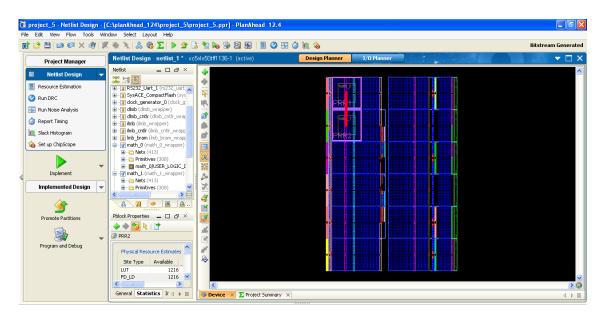

Figure 1.7: Schematic representation Partition Partial Reconfiguration design flow