# Méthodologies de conception ASIC pour des systèmes sur puce 3D hétérogènes à base de réseaux sur puce 3D

Mohamad Jabbar

## ▶ To cite this version:

Mohamad Jabbar. Méthodologies de conception ASIC pour des systèmes sur puce 3D hétérogènes à base de réseaux sur puce 3D. Autre. Université de Grenoble, 2013. Français. NNT: 2013GRENT006. tel-00934780

# HAL Id: tel-00934780 https://theses.hal.science/tel-00934780

Submitted on 22 Jan 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Nano-Electronique et Nano-Technologies

Arrêté ministériel : 7 août 2006

Présentée par

# « Mohamad Hairol / JABBAR »

Thèse dirigée par « **Dominique** / **Houzet** » codirigée par « **Omar** / **Hammami** »

préparée au sein du Laboratoire GIPSA-Lab, Grenoble and ENSTA ParisTech, Paris dans l'École Doctorale EEATS

# Méthodologies de Conception ASIC Pour des Systèmes sur Puce 3D Hétérogènes à Base de Réseaux sur Puce 3D

Thèse soutenue publiquement le « 21/03/2013 », devant le jury composé de :

### M. Ian O Connor

Professeur, Ecole Centrale de Lyon, France, Président, Rapporteur

#### M. Paul Franzon

Professeur, North Carolina State University, États-Unis, Rapporteur

#### M. Said Hamdioui

Professeur, Delft University of Technology, Pays-Bas, Membre

## M. Kholdoun Torki

Directeur Technique, Circuits Multi-Projets (CMP), France, Membre

#### M. Yvain Thonnart

Ingénieur de Recherche, CEA-Leti, France, Membre

# Title in English:

ASIC Design Methodologies for 3D NoC-Based 3D Heterogeneous MPSoC

# **Keywords:**

3D IC, Exploration, MPSoC, NoC, Physical design implementation

# Titre en Français:

Méthodologies de Conception ASIC Pour des Systèmes sur Puce 3D Hétérogènes à Base de Réseaux sur Puce 3D

## Mots clés:

3D IC, Exploration, MPSoC, NoC, Mise en œuvre de conception physique

#### **ABSTRACT**

For many years, Moore's Law has been the primary driving force enabling the evolution of semiconductor industry with the ability to double the transistor count on a silicon die for every two years. However, shrinking transistor dimensions, also known as CMOS scaling to be able to design and manufacture higher performance devices has become much more difficult than it is previously as we are approaching very deep submicron technologies such as 20 nm and beyond. The issues of design complexity and the exponential increase of cost to manufacture devices based on these very deep submicron technologies are among the great hurdles currently being faced by the industry making it unattractive performance per cost solution. The transition to 450 mm (18") wafer to help reducing manufacturing cost for advanced process technology and the development of extreme ultraviolet (EUV) lithography tools are also facing technical difficulties that remain to be solved in the next several years while at the same time requires multi billion dollar investment to build new manufacturing facilities as well as new processing equipments.

3D integration has been around since decades ago but only now the industry is paying great attention to this technology as a result of economical and technical difficulties that arise from the transistor shrinking in 2D technology. It has been the subject of extensive research in the industry and academia due to benefits it could potentially offer such as higher performance, lower power consumption, larger memory bandwidth, small form factor and support for heterogeneous technology integration making it suitable for several application domains particularly in mobile devices. 3D technology could provide higher memory bandwidth through its excessive vertical connections using TSV or microbumps as in wide I/O memory architecture and can also accomodate high memory capacity when using memory-on-logic or memory-on-memory stacking. Shorter vertical interconnection between stacked dies or wafers as well as reduction of horizontal wirelength due to stacking will eventually provide higher performance per watt. However, there are also some challenges that exist in 3D technology and they have to be solved before it can be widely adopted as a mainstream technology for high volume production such as high temperature effect, testing of 3D architecture and most importantly for the designers is 3D design tools, specifically the tools that are capable of doing 3D synthesis, 3D place and route as well as 3D optimization at each step.

With the recent trend of mainstream multiprocessor technology that is moving towards increasing the number of processing cores to support higher performance applications, Network-on-Chip (NoC) has become the primary technology in meeting the demand of high performance, scalability and flexibility for processor's and Intellectual Property (IP) cores' communication. Works on multiprocessor and NoC architecture in 3D technology have been carried out for many years covering various issues such as partitioning method and NoC topologies but most of the prior works only consider software simulation for the performance analysis where the results is less accurate and therefore cannot be truly used for evaluating the benefits bring by 3D technology. The need for performance analysis from design implementation results is highly desirable to be able to make the right conclusions regarding the potential benefits it offers. In this thesis, we study the 3D NoC architectures through physical design implementations using real 3D technology being implemented in the industry. Based on the routed netlists, we conduct performance analysis to evaluate the benefit of 3D architecture compared with its 2D implementation. But firstly, we present our initial work designing and implementing a 2D NoC-based MPSoC architecture on FPGA intended to identify design issues related to the 2D MPSoC design.

Based on the proposed 3D design flow focusing on timing verification by leveraging the benefit of negligible delay of microbumps structure for vertical connections, we have conducted partitioning techniques for 3D NoC-based MPSoC architecture including homogeneous and heterogeneous stacking using Tezzaron 3D IC technlogy. Design and implementation trade-off in both partitioning methods is investigated to have better insight about 3D architecture so that it can be exploited for optimal performance. Using homogeneous 3D stacking approach, NoC architectures are explored to identify the best topology between 2D and 3D topology for 3D MPSoC implementation. The architectural explorations have also considered different process technologies highlighting the wire delay effect to the 3D architecture performance especially for interconnect-dominated design. Additionally, we performed heterogeneous 3D stacking of NoC-based MPSoC implementation with GALS style approach and presented several physical designs related analyses regarding 3D MPSoC design and implementation using 2D EDA tools.

Finally we conducted an exploration of 2D EDA tool on different 3D architecture to evaluate the impact of 2D EDA tools on the 3D architecture performance. Since there is no commercialize 3D design tool until now, the experiment is important on the basis that designing 3D architecture using 2D EDA tools does not have a strong and direct impact to the 3D architecture performance mainly because the tools is dedicated for 2D architecture design. Integrating manual tools (scripts to constraint the design) to the 2D EDA tools to design 3D architecture is the common method to achieve performance benefit but this method loses the most important design step of 3D optimization that normally exists in the 2D EDA tools when designing 2D architecture.

## **RÉSUMÉ**

Pendant de nombreuses années, la loi de Moore a été la principale force motrice permettant l'évolution de l'industrie des semiconducteurs avec la possibilité de doubler le nombre de transistors sur une puce de silicium pour tous les deux ans. Toutefois, la diminution des dimensions des transistors, appelés aussi mise à l'échelle CMOS pour être en mesure de concevoir et de fabriquer des appareils plus performants est devenu beaucoup plus difficile qu'elle ne l'est déjà que nous nous approchons de technologies submicroniques profondes tels que 20 nm et au-delà. Les questions de la complexité de la conception et de l'augmentation du coût exponentiel pour la fabrication de dispositifs basés sur ces technologies submicroniques profondes sont parmi les grands obstacles actuellement rencontrés par l'industrie qui rend la performance peu attrayante pour solution économique. La transition à plaquette de 450 mm (18 ") pour aider à réduire le coût de fabrication pour la technologie avancée des processus et le développement d'outils de lithographie par ultraviolets extrême (EUV) sont également confrontés à des difficultés techniques qui restent à résoudre dans les prochaines années alors que dans le même temps nécessite investissements de plusieurs milliards de dollars pour construire de nouvelles usines ainsi que des équipements de traitement de nouvelles.

L'intégration 3D a été autour depuis des décennies auparavant, mais que maintenant l'industrie accorde une grande attention à cette technologie en raison des difficultés économiques et techniques proviennent du contraction du transistor dans la technologie 2D. Il a fait l'objet de recherches approfondies dans l'industrie et le milieu universitaire en raison de certains avantages qu'elle pourrait potentiellement offrir telles de meilleures performances, faible consommation d'énergie, la mémoire de bande passante plus large, plus petit facteur de forme et de soutien pour l'intégration des technologies hétérogènes ce qui convient pour plusieurs domaines d'application particulièrement dans des appareils mobiles. La technologie 3D peut fournir une mémoire de bande passante plus élevée par l'intermédiaire de ses connexions verticales excessives à l'aide TSV ou microbilles selon l'architecture de la mémoire éventail d'E/S et peut également accueillir une grande capacité de mémoire pour l'utilisation de la mémoire-à-mémoire logique ou mémoire-à-logique d'empilement. Interconnexion verticale plus courte entre des matrices empilées ou de plaquettes ainsi que la réduction des longueur de fil horizontale due à l'empilement finira par offrir de meilleures performances par watt. Cependant, il y a aussi des défis existent dans la technologie 3D, et ils doivent être résolus avant de pouvoir largement adopté comme une technologie majeure pour la production de volume élevé, comme l'effet de la température élevée, les tests d'architecture 3D et le plus important pour les concepteurs sont des outils de conception 3D, spécifiquement les outils

qui sont capable de faire la synthèse 3D, le lieu et l'itinéraire en 3D ainsi que l'optimisation 3D à chaque étape.

Avec la tendance récente, la technologie multiprocesseurse déplace vers l'augmentation du nombre de cœurs de traitement pour supporter les applications haute performance, réseau sur une puce (NoC) est devenue la principale technologie pour répondre à la demande des performances, une évolutivité et une flexibilité élevées pour le processeur et propriété intellectuelle (PI) de communication de cœurs ». Travaux de multiprocesseur et de l'architecture NoC dans la technologie 3D ont été réalisées depuis de nombreuses années sur divers sujets tels que la méthode de partage de topologies NoC mais la plupart des travaux antérieurs ne considère pas le logiciel de simulation pour l'analyse de la performance où les résultats sont moins précis et ne peuvent donc pas être vraiment utilisées pour évaluer les bénéfices apporter par la technologie 3D. La nécessité d'une analyse de la performance des résultats de la mise en œuvre de conception est fortement souhaitable d'être en mesure de faire les bonnes conclusions quant aux avantages potentiels qu'ils peuvent offrir. Dans cette thèse, nous étudions les architectures 3D NoC grâce à des implémentations de conception physiques en utilisant la technologie 3D réel mis en œuvre dans l'industrie. Sur la base des listes d'interconnexions en déroute, nous procédons à l'analyse des performances d'évaluer le bénéfice de l'architecture 3D par rapport à sa mise en œuvre 2D. Mais tout d'abord, nous vous présentons notre travail initial de conception et la mise en œuvre d'un NoC 2D basé sur l'architecture MPSoC sur FPGA pour but d'identifier les problèmes de conception liés à la conception 2D MPSoC.

Sur la base du flux de conception 3D proposé en se concentrant sur la vérification temporelle en s'appuyant sur l'intérêt de retard négligeable de la structure de microbilles pour les connexions verticales, nous avons mené des techniques de partitionnement de NoC 3D basé sur l'architecture MPSoC y compris empilement homogène et hétérogène en utilisant la technologie Tezzaron 3D IC. La conception et la mise en œuvre de compromis dans les deux méthodes de partitionnement est étudiée pour avoir un meilleur aperçu sur l'architecture 3D de sorte qu'il peut être exploitée pour des performances optimales. En utilisant l'approche empilage 3D homogène, les topologies NoC est explorées afin d'identifier la meilleure topologie entre la topologie 2D et 3D pour la mise en œuvre MPSoC 3D sous l'hypothèse que les chemins critiques est fondée sur les liens inter-routeur. Les explorations architecturales ont également examiné les différentes technologies de traitement en mettant en évidence l'effet de la technologie des procédés à la performance d'architecture 3D en particulier pour l'interconnexion dominant du conception. En outre, nous avons effectué l'empilage 3D hétérogène pour la mise en œuvre MPSoC avec l'approche de modéle de GALS et présenté

plusieurs analyses de conception physiques lié concernant la conception 3D et la mise en œuvre MPSoC en utilisant des outils de CAO 2D.

Enfin, nous avons procédé à une exploration de l'espace de conception d'architecture en 3D en utilisant l'outil du lieu et d'itinéraire 2D pour but d'évaluer l'impact de l'utilisation des outils de CAO 2D sur la performance d'architecture 3D. Comme il n'y a pas de l'outil de conception 3D jusqu'à présent dans le marché, l'expérience est importante pour le motif que la conception de l'architecture 3D en utilisant les outils EDA 2D n'a pas un impact fort et direct pour la performance d'architecture 3D principalement parce que les outils est dédié à la conception de l'architecture 2D. L'utilisation d'outils de support aux outils de CAO 2D pour concevoir l'architecture 3D est une méthode courante pour obtenir le gain de performances, mais cette méthode perd l'étape de conception le plus important de l'optimisation 3D existent normalement dans les outils de CAO 2D lors de la conception d'architecture 2D.

# **DEDICATION**

To my wife, Siti Noor Saadah and my family.

#### **ACKNOWLEDGMENTS**

First and foremost, I would like to thank Allah for always helping and giving me courage throughout the period of this study to complete the research works as well as writing this thesis.

Thank you to Professor Omar Hammami and Professor Dominique Houzet for being my thesis directors during this PhD study. Without them, I will not be involved in this fascinating technology doing state of the art research works where not many people have the opportunity as I have. I really appreciate all the time they have spent discussing and evaluating the research works and also for the technical as well as non-technical advices they have given to improve research outcomes as well as to teach me to be a better researcher in the future. I pray for them to have long lasting happiness in whatever they do and to success in whatever dream they want to achieve.

I am really honoured to have Professor Ian O Connor of EC Lyon and Professor Paul D. Franzon of North Carolina State University as my PhD thesis reviewers. Their comments have greatly helped me to improve the quality of this manuscript. I am grateful to have Professor Said Hamdioui of Delft University of Technology, Dr. Kholdoun Torki of CMP Grenoble and Mr. Yvain Thornnart of CEA-Leti for being in my PhD defense committee.

I would like to thank Dr. Kholdoun Torki of CMP for the help on ASIC design and most importantly on Tezzaron Design Kit. Thank you also to Dr. Alejandro Chagoya who has helped me with the EDA tools at CIME NANOTECH, MINATECH to run all the experiments in this thesis.

For my colleagues at ENSTA as well as at GIPSA LAB, specifically to Dr. Abir M'zah, Khawla Hamwi and Dr. Xinyu Li, thank you for helping me in various difficult times during my stay here either in academic as well as in life. Thank you for the friendship and I hope we will meet again.

I would like also to express deep gratitude to my sponsor both University Tun Hussein Onn Malaysia (UTHM) and Ministry of Higher Education of Malaysia (MOHE) for funding my PhD study.

Finally, my thank you goes to my wife who is very patient while I was spending most of the time doing research works as well as writing papers and thesis. Thank you also to my parents who always pray for my success in academic from far away.

# TABLE OF CONTENTS

| ABSTRACT                                                                          | v     |

|-----------------------------------------------------------------------------------|-------|

| RÉSUMÉ                                                                            | vii   |

| DEDICATION                                                                        | xi    |

| ACKNOWLEDGMENTS                                                                   | xiii  |

| LIST OF FIGURES                                                                   | xviii |

| LIST OF TABLES                                                                    | xxii  |

| VERSION FRANÇAISE                                                                 | 23    |

| 1. INTRODUCTION                                                                   | 55    |

| 1.1 Research Motivations                                                          | 58    |

| 1.2 Summary of Arguments                                                          | 59    |

| 1.2.1 Deep Understanding about the Target Architecture to Maximize Performance    |       |

| Improvement                                                                       | 59    |

| 1.2.2 Process Technologies for 3D IC Technology Depending on the Different Target |       |

| Implementations                                                                   | 60    |

| 1.2.3 3D-aware EDA Tools with 3D Optimization Capability for Designing 3D IC      |       |

| Technology                                                                        | 60    |

| 1.3 Thesis Contributions                                                          | 61    |

| 1.4 Thesis Organization.                                                          | 62    |

| 2. 2D NOC-BASED MPSOC DESIGN AND IMPLEMENTATION ON FPGA                           | 65    |

| 2.1 Introduction                                                                  | 65    |

| 2.2 Related Works                                                                 | 67    |

| 2.3 EDA Tools Integration                                                         | 67    |

| 2.3.1 Design Flow                                                                 | 69    |

| 2.4 Target Hardware Implementation                                                | 70    |

| 2.5 MPSoC Architecture                                                            | 73    |

| 2.5.1 Processor Architecture                                                      | 73    |

| 2.5.2 NoC Architecture                                                            | 73    |

| 2.6 Application: Discrete Cosine Transform                                        | 75    |

| 2.7 FPGA Implementation                                                           | 78    |

| 2.7.1 ENSTA APIs                                                                  | 78    |

| 2.7.2 Parallel Programmming                                                       | 79    |

| 2.8 Results and Discussion                                          | 80         |

|---------------------------------------------------------------------|------------|

| Conclusion                                                          | 83         |

| 3. OVERVIEW OF 3D IC TECHNOLOGY                                     | 95         |

| 3.1 2D Architecture and Its Issues                                  |            |

| 3.2 3D IC Technology                                                |            |

| 3.2.1 Advantages of 3D IC Technology                                |            |

| 3.2.2 TSV Technology                                                |            |

| 3.2.3 Stacking Techniques for 3D IC Technology Manufacturing        |            |

| 3.2.4 Partitioning Granularities for 3D Architecture Implementation |            |

| 3.2.5 Tezzaron 3D IC Technology                                     |            |

| 3.3 CMOS Scaling vs 3D IC Technology                                |            |

| 3.4 Challenges of 3D IC Technology                                  |            |

| 3.5 3D IC Technology Standards                                      |            |

| 3.6 State of the art of 3D IC Architecture Implementations          |            |

| Conclusion                                                          |            |

| 4. 3D DESIGN FLOW FOCUSING ON TIMING VERIFICATION                   | 117        |

| 4.1 Related Works on 3D Design Flow                                 |            |

|                                                                     |            |

| 4.2 Proposed 3D Design Flow with Timing Verification                |            |

| 4.2.1 3D Physical Design Implementation Flow                        |            |

| 4.2.3 Back-end Design Flow                                          |            |

| 4.2.4 3D Timing Analysis Design Flow                                |            |

| 4.2.5 Limitation of the Flow                                        |            |

| Conclusion                                                          |            |

| Conclusion                                                          | 131        |

| 5. EXPLORATION OF 3D NOC ARCHITECTURES THROUGH PHYSI                | CAL DESIGN |

| IMPLEMENTATION                                                      | 133        |

| 5.1 Related Works                                                   | 134        |

| 5.2 Standard Cell Libraries                                         | 136        |

| 5.3 Baseline NoC Architecture                                       | 137        |

| 5.3.1 Router and NIU Architecture                                   | 137        |

| 5.3.2 Baseline 3D Mesh NoC                                          | 140        |

| 5.4.3D NoC Architectures Exploration                                | 1/11       |

|   | 5.4.1 3D NoC Partitioning                                                | 142      |

|---|--------------------------------------------------------------------------|----------|

|   | 5.4.2 3DNoC1: 3D Stacked Mesh NoC                                        | 143      |

|   | 5.4.3 3DNoC2: 3D Stacked Hexagonal NoC                                   | 145      |

|   | 5.5 Experimental Results                                                 | 149      |

|   | 5.5.1 Wirelength Analysis                                                | 153      |

|   | 5.5.2 Impact of Wire Delay                                               | 154      |

|   | 5.5.3 Extrapolation of Physical Implementation Result                    | 155      |

|   | 5.5.4 Impact of 3D IC design using 2D EDA Tools                          | 156      |

|   | 5.6 3D IC Implementation for MPSoC Architectures: Mesh and Butterfly NoC | 157      |

|   | 5.6.1 3DMPSoC1: Mesh Topology                                            | 158      |

|   | 5.6.2 3DMPSoC2: Butterfly Topology                                       | 160      |

|   | 5.6.3 3D MPSoC Implementations Comparison                                | 162      |

|   | Conclusion                                                               | 163      |

|   |                                                                          |          |

| 6 | 6. HETEROGENEOUS STACKING OF 3D NOC-BASED MPSOC ARCHITECTURE             |          |

|   | 6.1 Introduction                                                         |          |

|   | 6.2 Related Works                                                        |          |

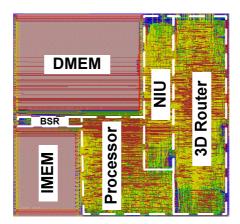

|   | 6.3 Baseline 2D NoC-based MPSoC Architecture                             |          |

|   | 6.3.1 Processor Architecture                                             |          |

|   | 6.3.2 NoC Architecture                                                   |          |

|   | 6.3.3 GALS Implementation                                                |          |

|   | 6.3.4 Baseline 2D MPSoC Architecture                                     |          |

|   | 6.4 Heterogeneous Stacking of 3D NoC-Based MPSoC Architecture            |          |

|   | 6.4.1 Partitioning Technique                                             |          |

|   | 6.5 Experimental Results                                                 |          |

|   | 6.5.1 2D vs 3D Clock Tree Analysis                                       |          |

|   | 6.5.2 2D vs 3D Critical Path Analysis                                    |          |

|   | 6.5.3 Impact of Microbumps Pitch                                         |          |

|   | 6.5.4 Implications of 3D IC Design using 2D EDA Tools                    | 190      |

|   | Conclusion                                                               | 190      |

| 7 | . DESIGN SPACE EXPLORATION OF 2D EDA TOOL IMPACT ON THE 3D MPSO          | <b>C</b> |

| 1 | ARCHITECTURE                                                             |          |

|   | 7.1 Introduction                                                         |          |

|   | 7.2 Related Works                                                        | 192      |

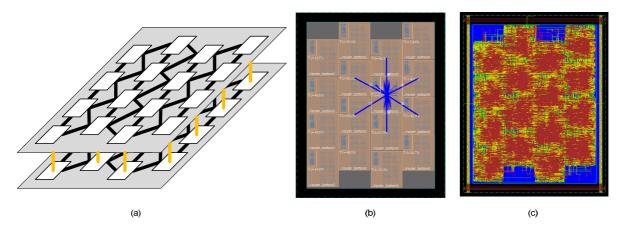

| 7.3 Exploration Configuration                                         | 193 |

|-----------------------------------------------------------------------|-----|

| 7.3.1 Parameters Exploration                                          | 193 |

| 7.3.2 Exploration Design Flow                                         | 193 |

| 7.4 3D MPSoC Architectures for the Exploration                        | 194 |

| 7.5 Exploration Results                                               | 197 |

| 7.5.1 Pocessor Timing Slack Analysis                                  | 197 |

| 7.5.2 NoC Timing Slack Analysis                                       | 199 |

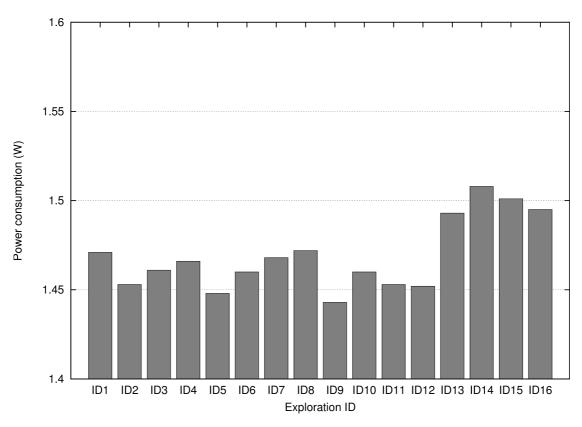

| 7.5.3 3D Power Consumption Analysis                                   | 200 |

| 7.6 Impact of using 2D EDA Tool on the Design of 3D MPSoCArchitecture | 202 |

| Conclusion                                                            | 202 |

|                                                                       |     |

| 8. CONCLUSION AND FUTURE WORKS                                        | 203 |

| 8.1 Summary of Works                                                  | 203 |

| 8.2 Future Works                                                      | 205 |

| REFERENCES                                                            | 207 |

# LIST OF FIGURES

| Figure 1: Number of processing engine and logic memory size trends in electrons | onic systems55     |

|---------------------------------------------------------------------------------|--------------------|

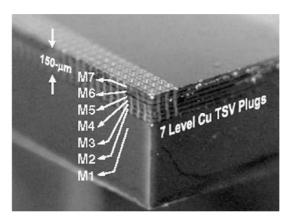

| Figure 2: 3D integration example showing seven stacks of wafer connecting u     | sing Cu TSV [6] 57 |

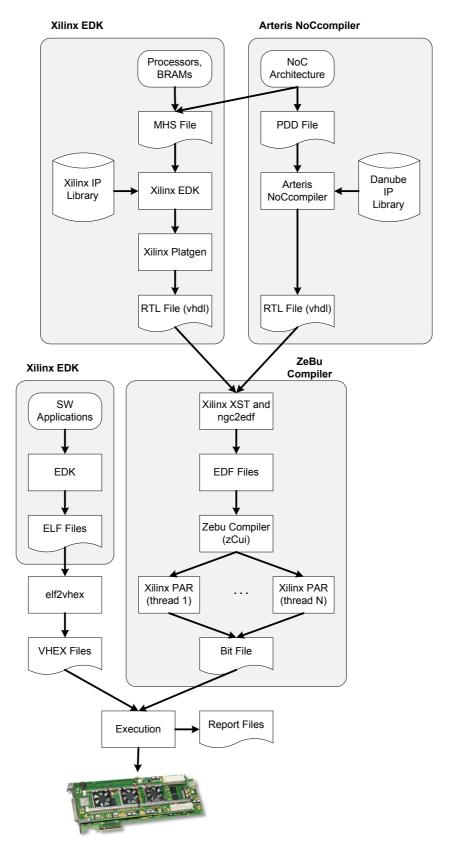

| Figure 3: Design flow and EDA tools integration                                 | 71                 |

| Figure 4: ZeBu UF-4 emulation board                                             | 72                 |

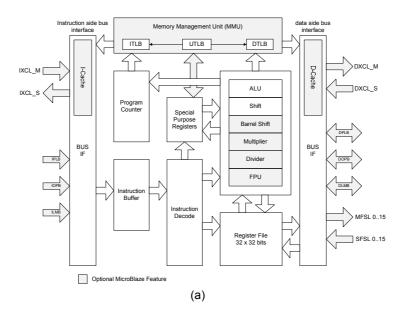

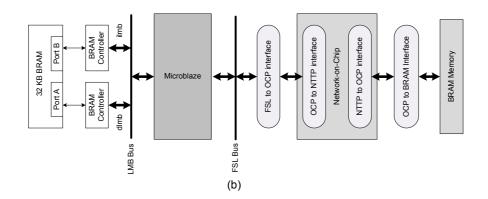

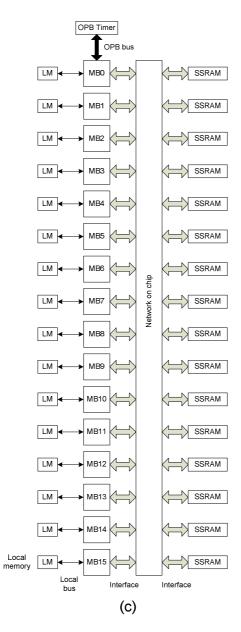

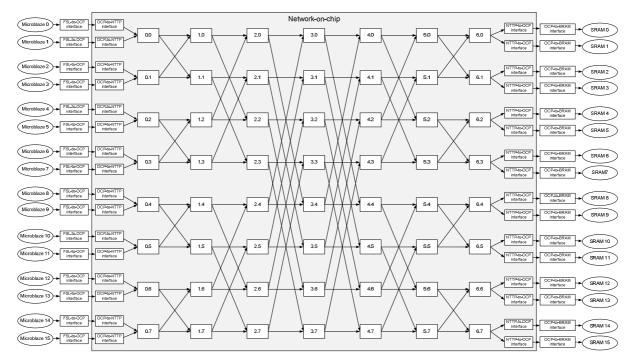

| Figure 5: MPSoC with NoC architecture (a) MicroBlaze core block diagram [       | 31] (b) interfa-   |

| ces between components for one MicroBlaze processor (c) complete                | block diagram of   |

| the system                                                                      | 75                 |

| Figure 6: 2D NoC-based MPSoC architecture with masters and slaves connec        | tion76             |

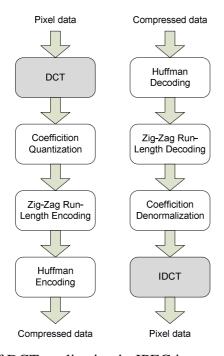

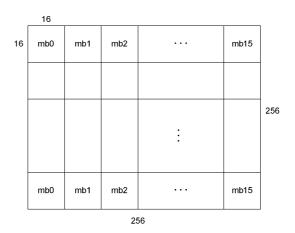

| Figure 7: Example of DCT application in JPEG image compression standard.        | 77                 |

| Figure 8: Processor allocation for data parallel of DCT application on 256 x 2  | 56 pixels image 79 |

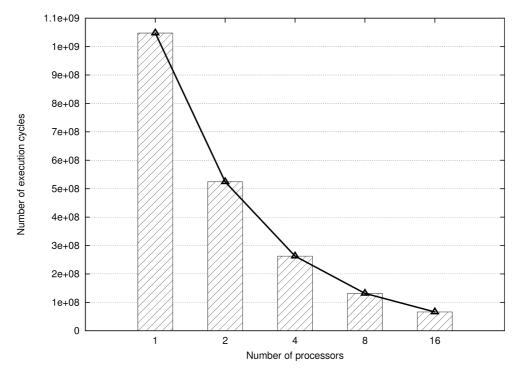

| Figure 9: Execution cycles of MicroBlaze with basic configuration               | 81                 |

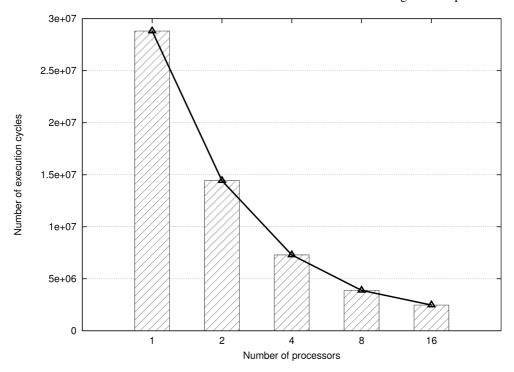

| Figure 10: Execution cycles of MicroBlaze with enhanced configuration           | 82                 |

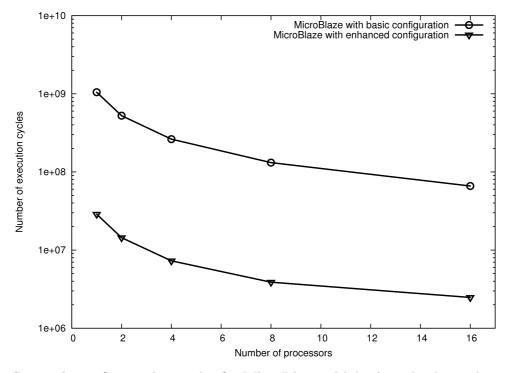

| Figure 11: Comparison of execution cycles for MicroBlaze with basic and enl     | nanced configura-  |

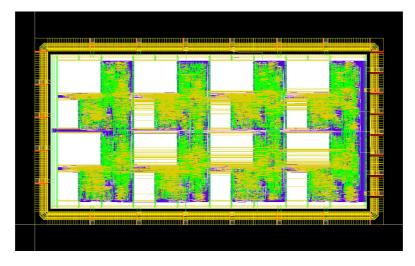

| tion                                                                            | 82                 |

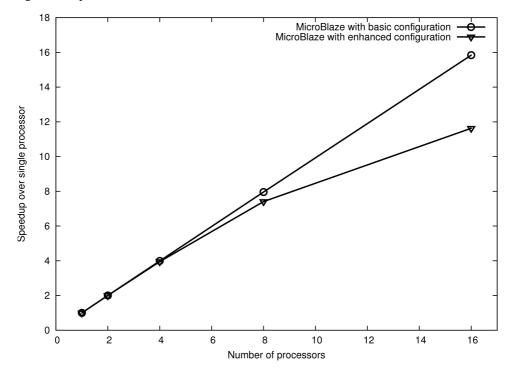

| Figure 12: Comparison of speedup between MicroBlaze with basic configurat       | ion and Micro-     |

| Blaze with enhanced configuration                                               | 83                 |

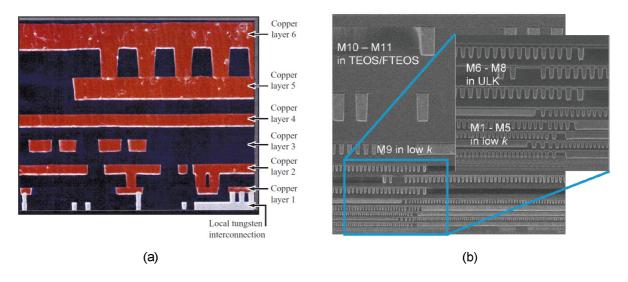

| Figure 13: Evolution of the interconnection architecture for high performance   | CMOS logic (a)     |

| CMOS 7S process in 0.2 µm [39] (b) 45 nm process technology [4                  | 0]86               |

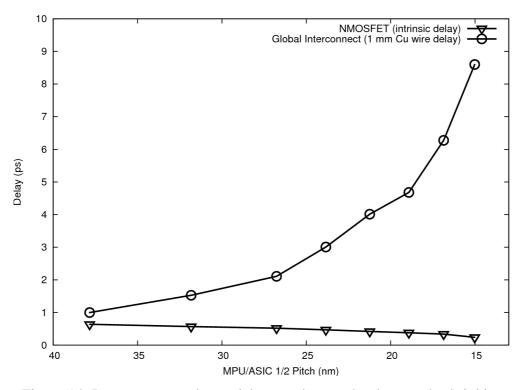

| Figure 14: Interconnect and gate delay trends as technology node shrinking      | 87                 |

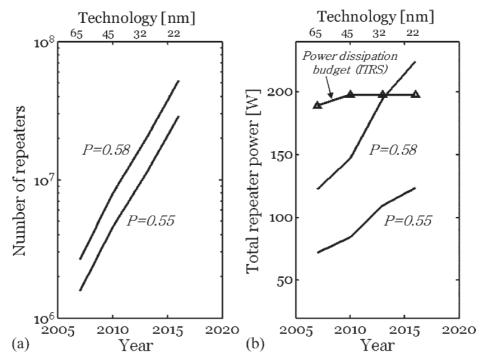

| Figure 15: Technology scaling effects on (a) number of repeaters (b) total repe | eater power [41]   |

| where P is Rent's coefficient                                                   | 87                 |

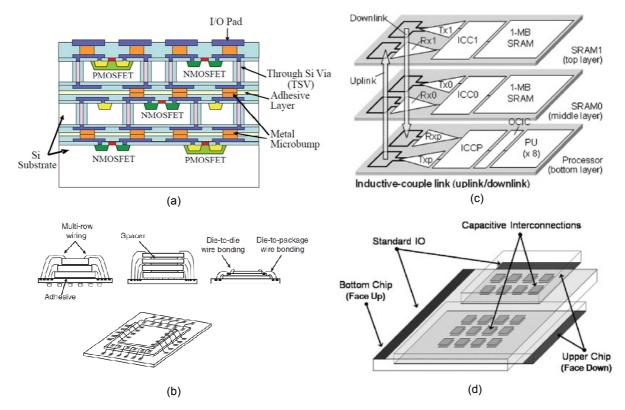

| Figure 16: Different type of stacking methods (a) TSV [48] (b) wire bonding     | [49] (c) contact-  |

| less using inductive coupling [46] (d) contactless using capacitive             | coupling [45]89    |

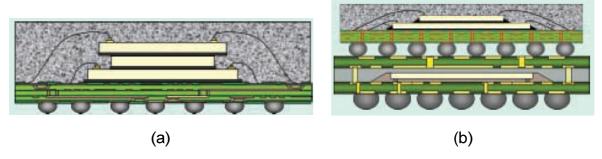

| Figure 17: Packaging types (a) System-in-Package (SiP) (b) Package-on-Pack      | age (PoP)89        |

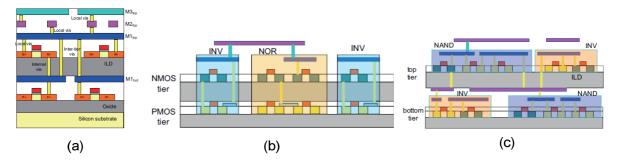

| Figure 18: (a) Monolithic 3D IC complete structure (b) transistor level monoli  | ithic (c) gate le- |

| vel monolithic [54]                                                             | 90                 |

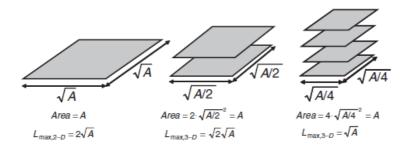

| Figure 19: Reduction of wire length from 2D architecture to 3D architecture v   | vith different     |

| stacking levels [49]                                                            | 91                 |

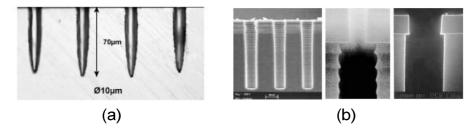

| Figure 20: TSV manufacturing using (a) laser drilling process and (b) DRIE p    | rocess [77]94      |

| Figure 21: TSV stacking methods (a) via-first and via-last in bulk CMOS (b)     | via-first TSV in   |

| SOI CMOS [81]                                                                   | 94                 |

| Figure 22: 3D stacking methods comparison [82]                                  | 95                 |

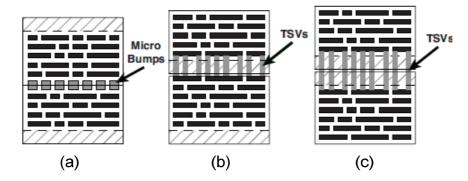

| Figure 23: 3D stacking orientations (a) face-to-face (b) face-to-back (c) back- | to-back96          |

| Figure 24: | Examples of 3D stacking orientations (a) face-to-face and face-to-back using MIT   |      |

|------------|------------------------------------------------------------------------------------|------|

|            | LL technology [84] (b) face-to-face and back-to-back using Tezzaron Technology     |      |

|            | [83]                                                                               | 96   |

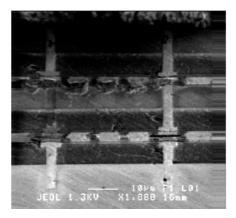

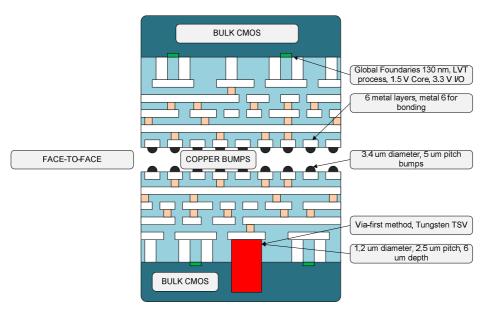

| Figure 25: | Two-tier Tezzaron 3D face-to-face stacking (a) cross section image of the manufac- |      |

|            | tured device (b) cross section of the stacking technology with the corresponding   |      |

|            | parameters                                                                         | 101  |

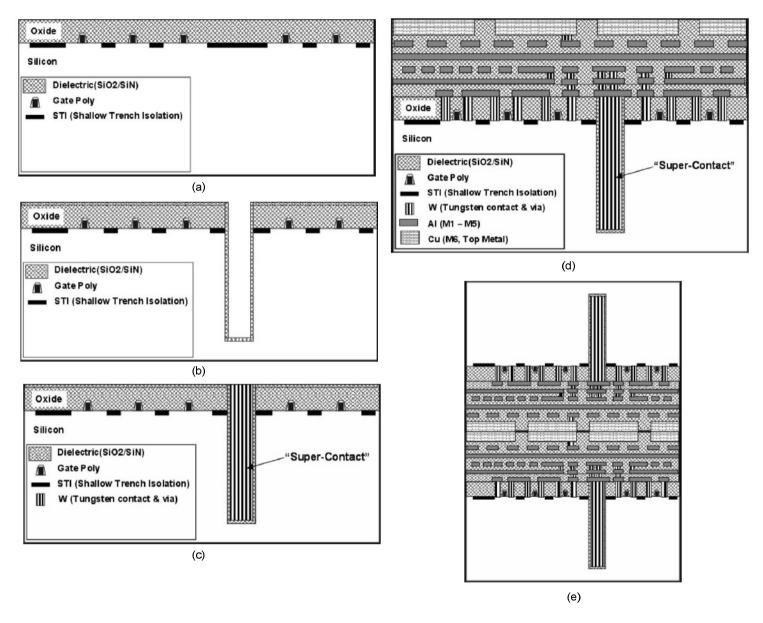

| Figure 26: | Tezzaron 3D technology manufacturing process                                       | 103  |

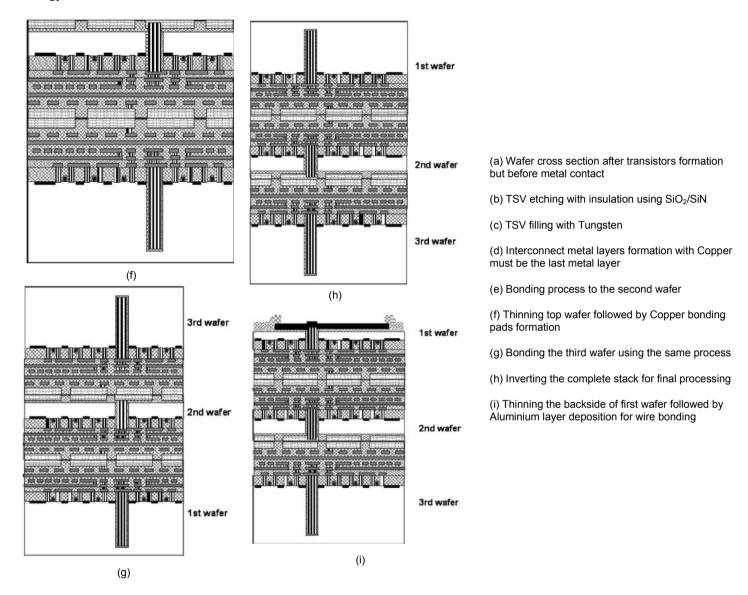

| Figure 27: | Performance improvement comparison of CMOS migration vs 3D integration [76]        | 105  |

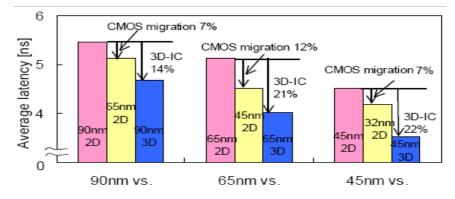

| Figure 28: | Thermal stress from Copper and Tungsen TSV material [114]                          | 107  |

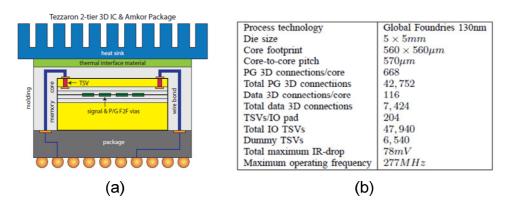

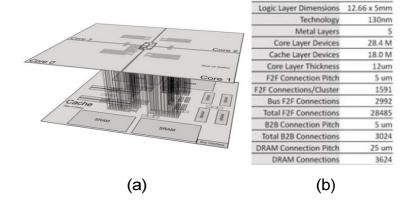

| Figure 29: | 3D-MAPS (a) architecture and (b) design summary                                    | 110  |

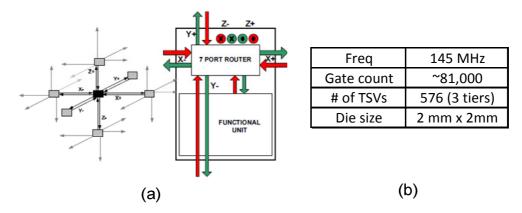

| Figure 30: | 3D NoC (a) architecture and (b) design summary                                     | 111  |

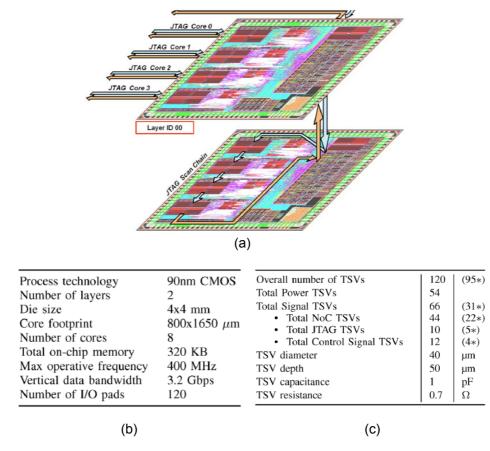

| Figure 31: | 3D FFT processor layout                                                            | 111  |

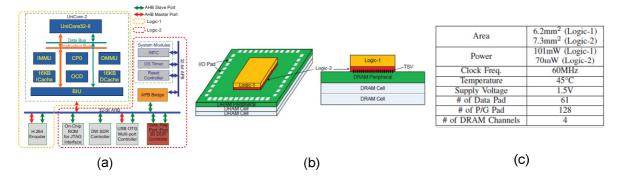

| Figure 32: | 3D SoC (a) architecture (b) 3D stacking diagram (c) design summary                 | 112  |

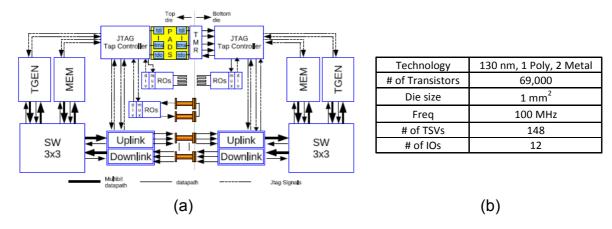

| Figure 33: | 3D NoC with fault tolerant (a) architecture (b) design summary                     | 112  |

| Figure 34: | Centip3De (a) architecture and (b) design summary                                  | 114  |

| Figure 35: | 3D modular multiprocessor (a) architecture (b) design summary (c) TSV parameters   | .115 |

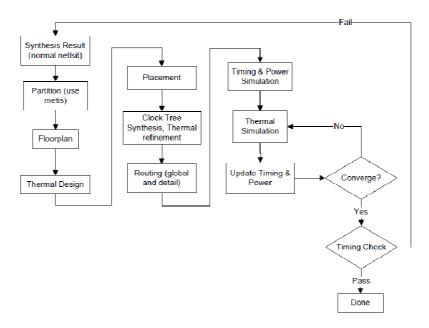

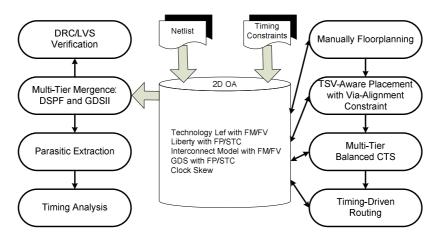

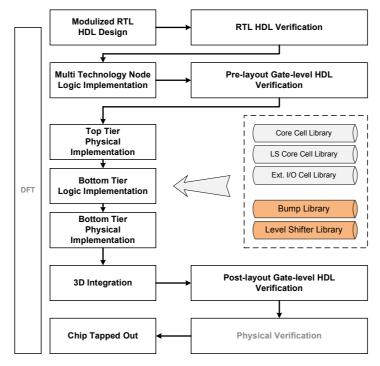

| Figure 36: | 3D design methodology for timing, power and temperature exploration [131]          | 118  |

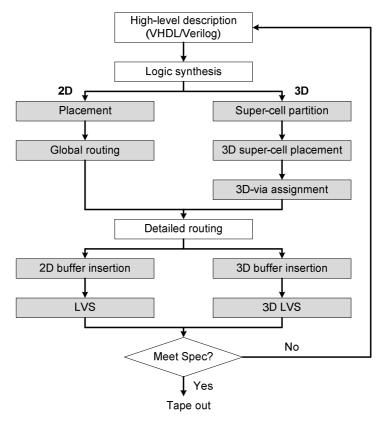

| Figure 37: | 3D ASIC design flow based on standard supercell layout [132]                       | 119  |

| Figure 38: | CAD flow for via-last face-to-back 3D integration [133]                            | 119  |

| Figure 39: | 3D design flow for three-tier FFT architecture using MIT Lincoln Lab technology    |      |

|            | [134]                                                                              | 120  |

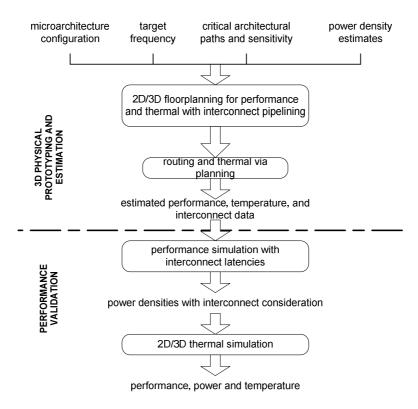

| Figure 40: | Automatic design for 3D microarchitecture performance evaluation [135]             | 121  |

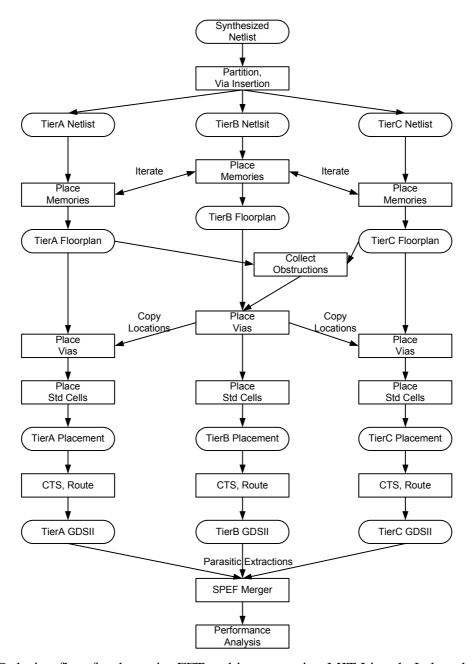

| Figure 41: | Design flow for 3D SAR processor [59]                                              | 122  |

| Figure 42: | Design flow for 3D hybrid process architecture [69]                                | 123  |

| Figure 43: | 3D design flow focusing on timing verification                                     | 124  |

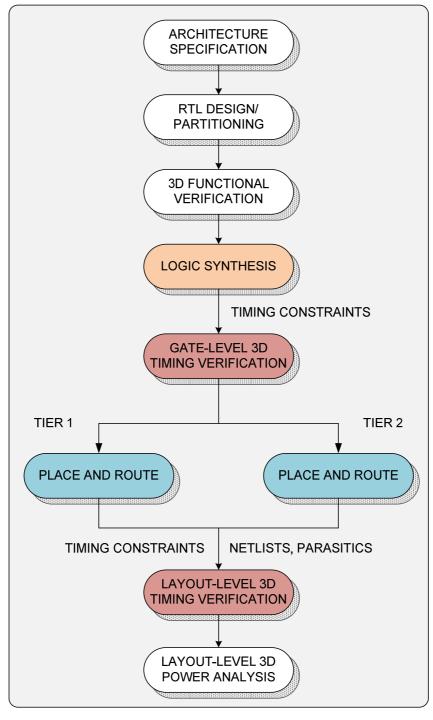

| Figure 44: | Front-end design flow with timing budgeting flow                                   | 126  |

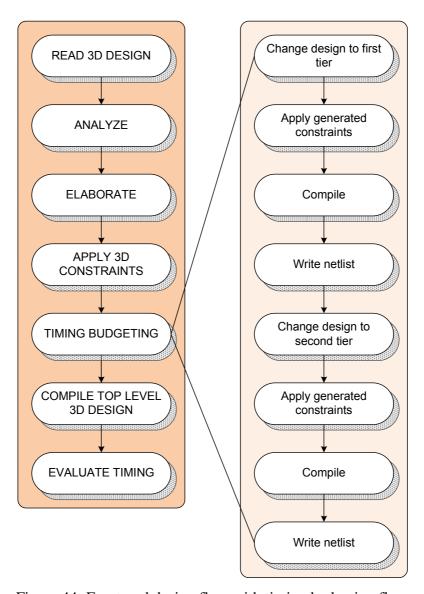

| Figure 45: | Back-end design flow with inter-tier signal assignments                            | 128  |

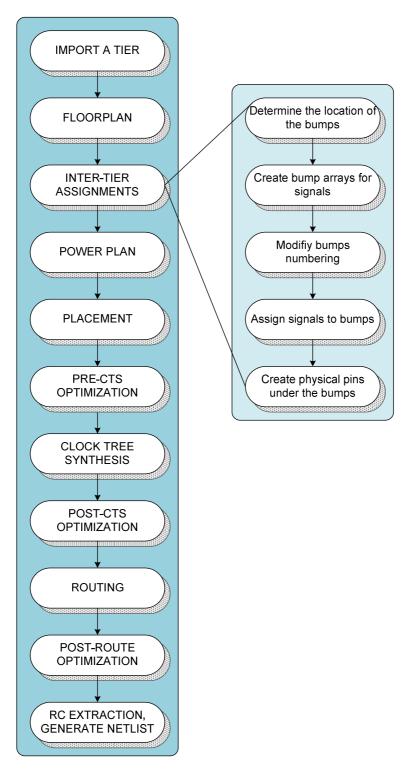

| Figure 46: | 3D timing analysis (a) gate-level (b) layout-level with power analysis             | 130  |

| Figure 47: | NIU architecture                                                                   | 139  |

| Figure 48: | 3D Router architecture                                                             | 139  |

| Figure 49: | Packet format of the NoC                                                           | 140  |

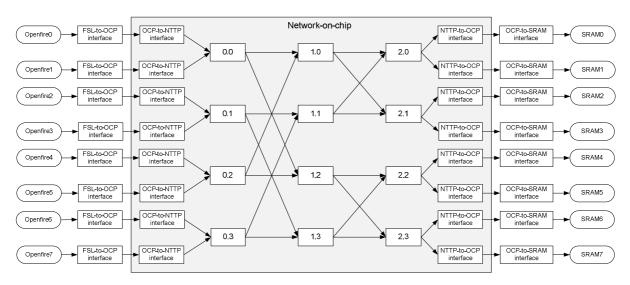

| Figure 50: | Block diagram of 3D Mesh NoC                                                       | 140  |

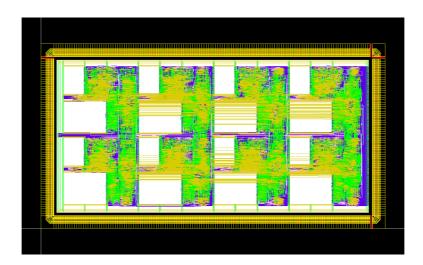

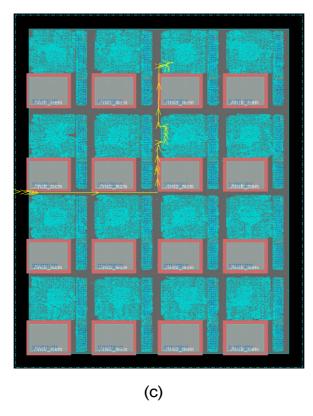

| Figure 51: | Floorplan of 3D Mesh NoC                                                           | 141  |

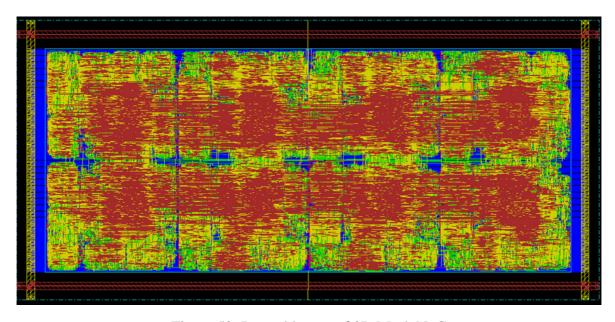

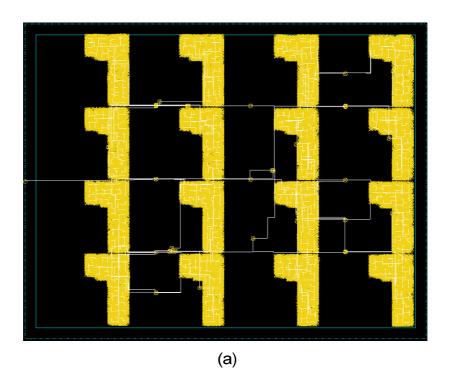

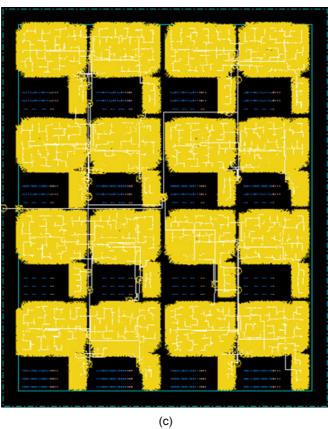

| Figure 52: | Routed layout of 3D Mesh NoC                                                       | 141  |

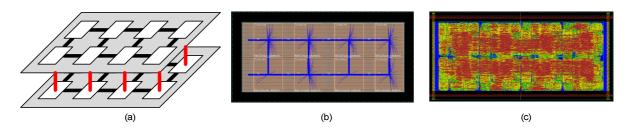

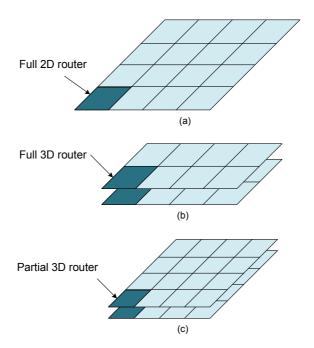

| Figure 53: | Partitioning method for the 3D NoC architecture (a) baseline 2D Mesh NoC (b)       |      |

|            | baseline 3D Mesh NoC (c) stacked 3D Mesh NoC                                    | 143 |

|------------|---------------------------------------------------------------------------------|-----|

| Figure 54: | Block diagram of 3D Stacked Mesh NoC                                            | 144 |

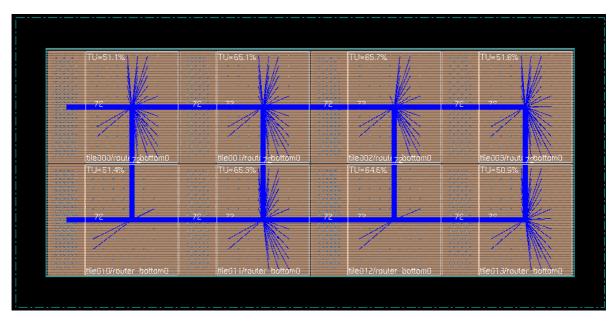

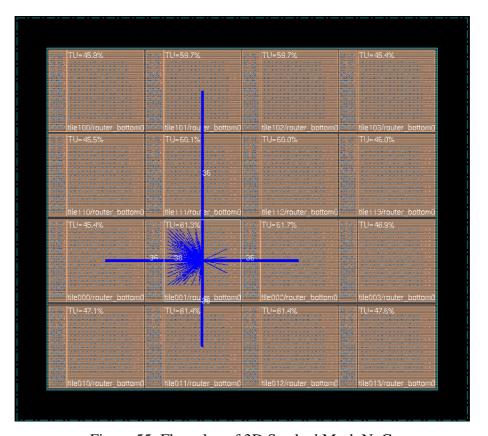

| Figure 55: | Floorplan of 3D Stacked Mesh NoC                                                | 144 |

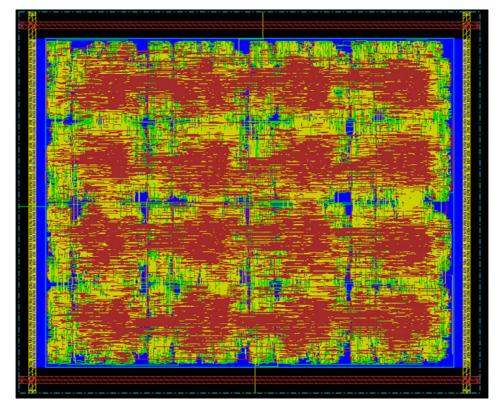

| Figure 56: | Routed layout of 3D Stacked Mesh NoC                                            | 145 |

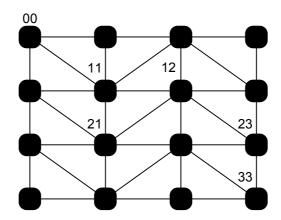

| Figure 57: | Routing method for hexagonal topology                                           | 146 |

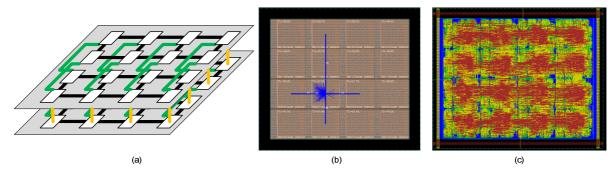

| Figure 58: | Block diagram of 3D Stacked Hexagonal NoC                                       | 148 |

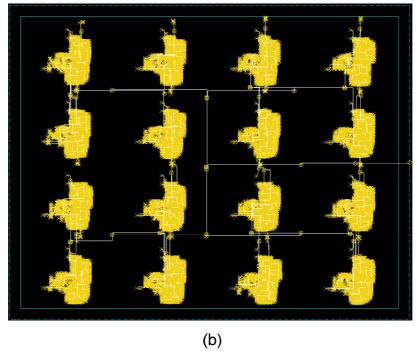

| Figure 59: | Floorplan of 3D Stacked Hexagonal NoC                                           | 148 |

| Figure 60: | Routed layout of 3D Stacked Hexagonal NoC                                       | 149 |

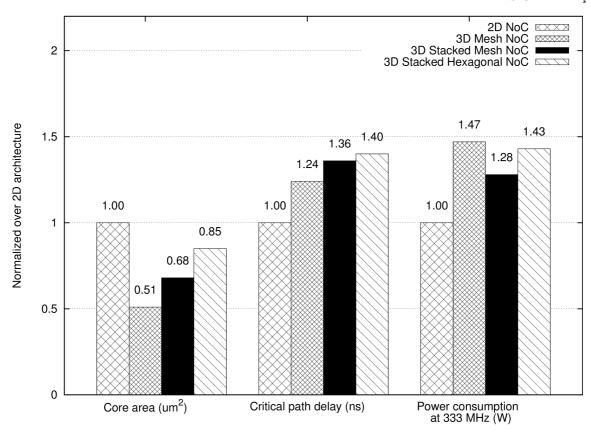

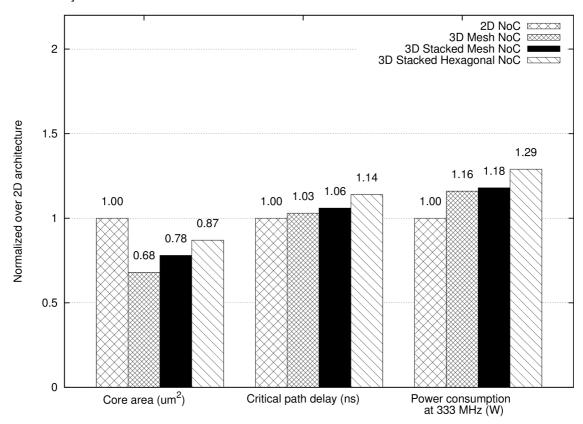

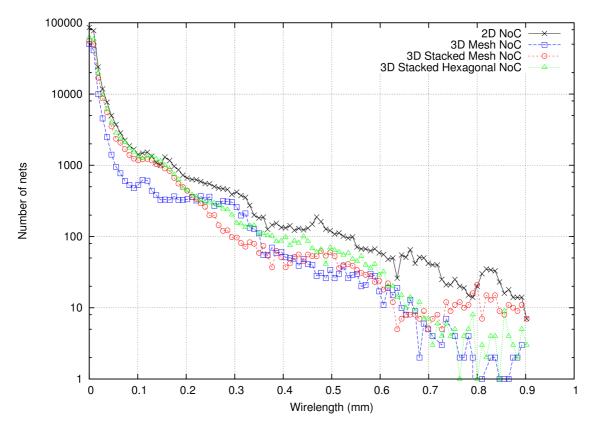

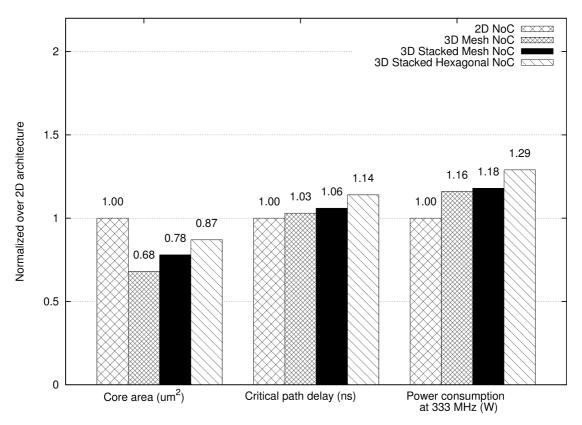

| Figure 61: | Performance comparison of 3D NoC architectures over 2D NoC in 130 nm techno-    |     |

|            | logy                                                                            | 151 |

| Figure 62: | Horizontal wirelength distribution for NoC architectures in 130 nm technology   | 151 |

| Figure 63: | Performance comparison of 3D NoC architectures over 2D NoC in 45 nm techno-     |     |

|            | logy                                                                            | 152 |

| Figure 64: | Horizontal wirelength distribution for NoC architecture in 45 nm technology     | 153 |

| Figure 65: | Tile block floorplan of 3D MPSoC1 (top tier)                                    | 159 |

| Figure 66: | Virtuoso layout of 3D MPSoC1 (top tier)                                         | 159 |

| Figure 67: | Tile block floorplan of 3D MPSoC1 (bottom tier)                                 | 159 |

| Figure 68: | Virtuoso layout of 3D MPSoC1 (bottom tier)                                      | 160 |

| Figure 69: | NoC block diagram for 2D MPSoC2 architecture                                    | 161 |

| Figure 70: | 3D MPSoC2 block diagram                                                         | 161 |

| Figure 71: | Routed layout of MPSoC2 architecture (bottom tier)                              | 162 |

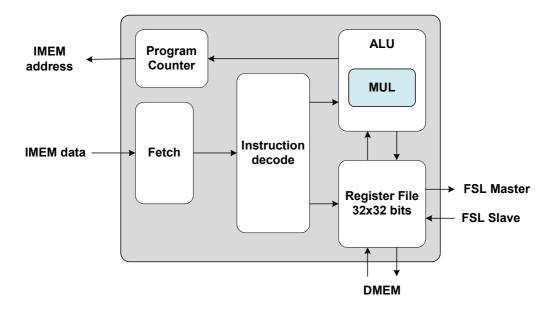

| Figure 72: | Openfire processor block diagram                                                | 169 |

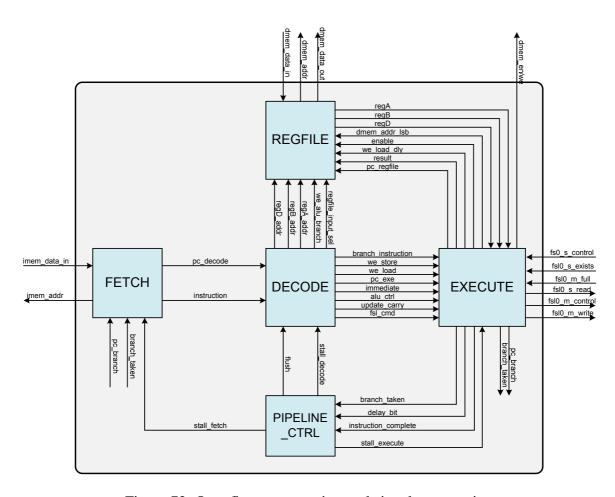

| Figure 73: | Openfire processor internal signals connection                                  | 170 |

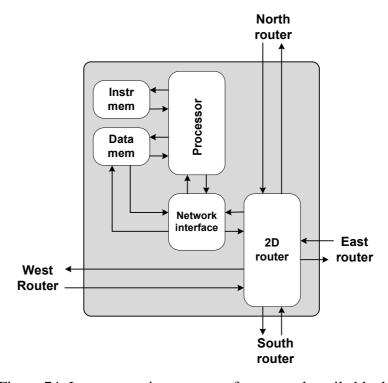

| Figure 74: | Interconnection structure for a complete tile block                             | 170 |

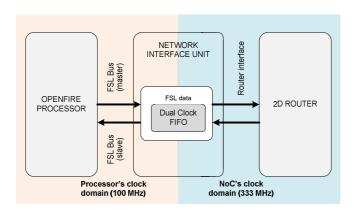

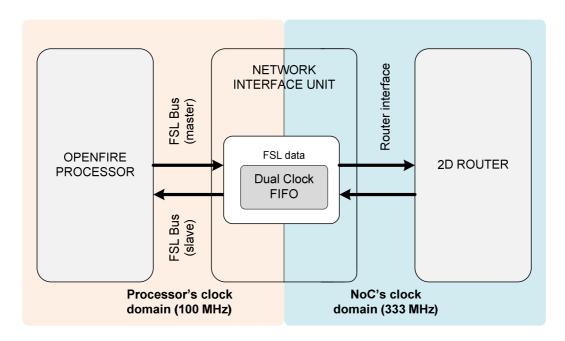

| Figure 75: | GALS implementation style using a dual clock FIFO architecture                  | 171 |

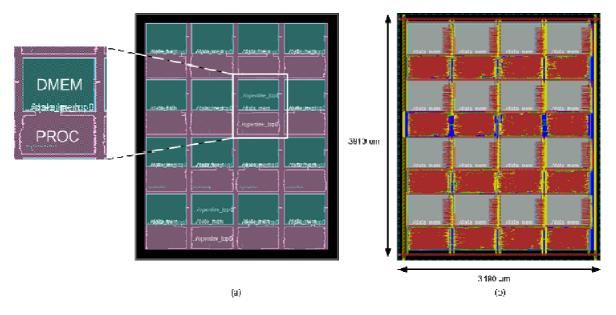

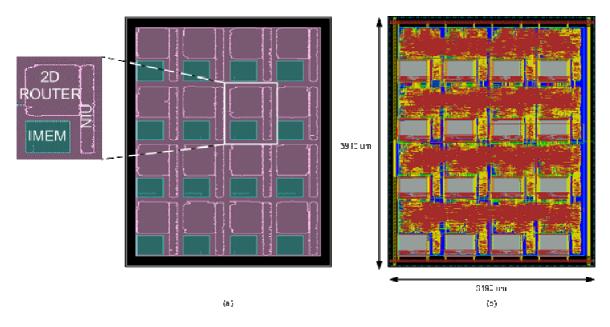

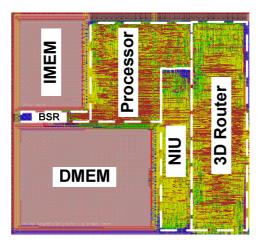

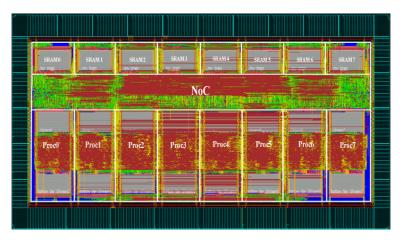

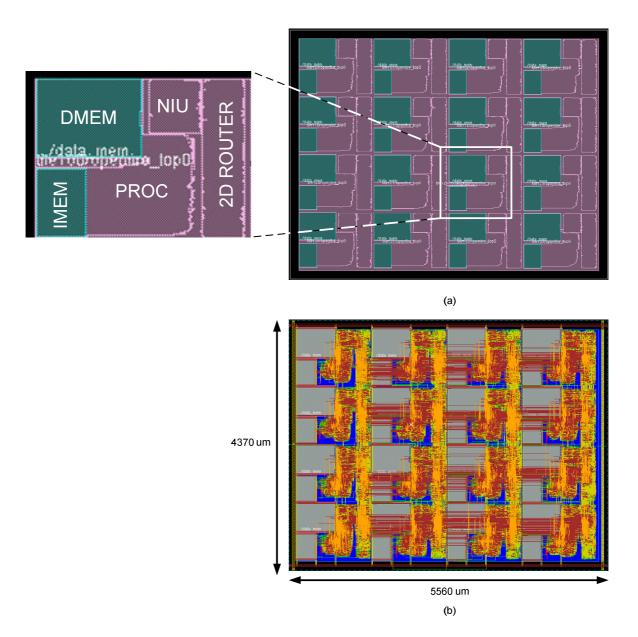

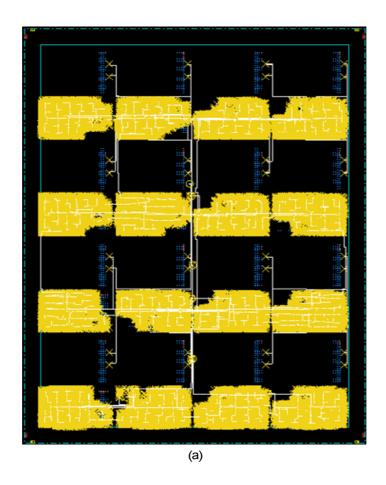

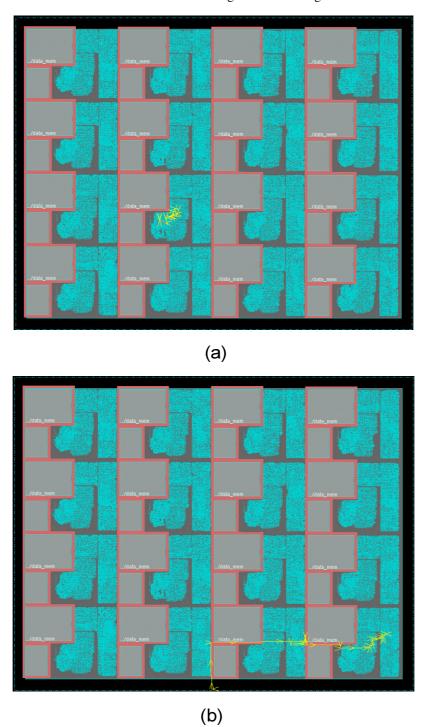

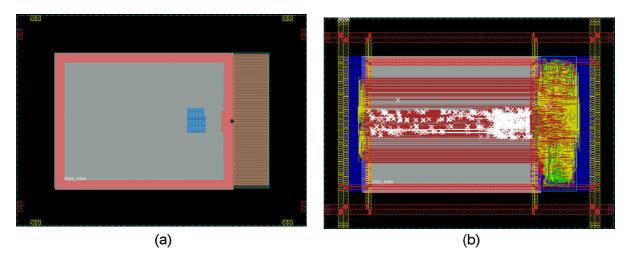

| Figure 76: | Baseline 2D MPSoC architecture (a) amoeba view (b) routed layout                | 172 |

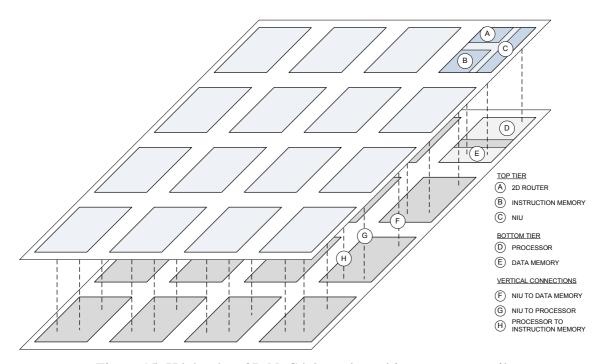

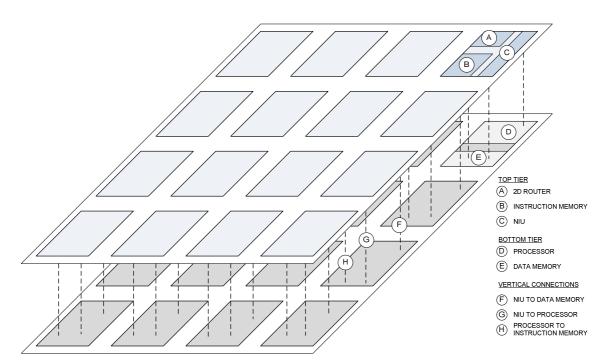

| Figure 77: | Heterogeneous 3D MPSoC stacking                                                 | 173 |

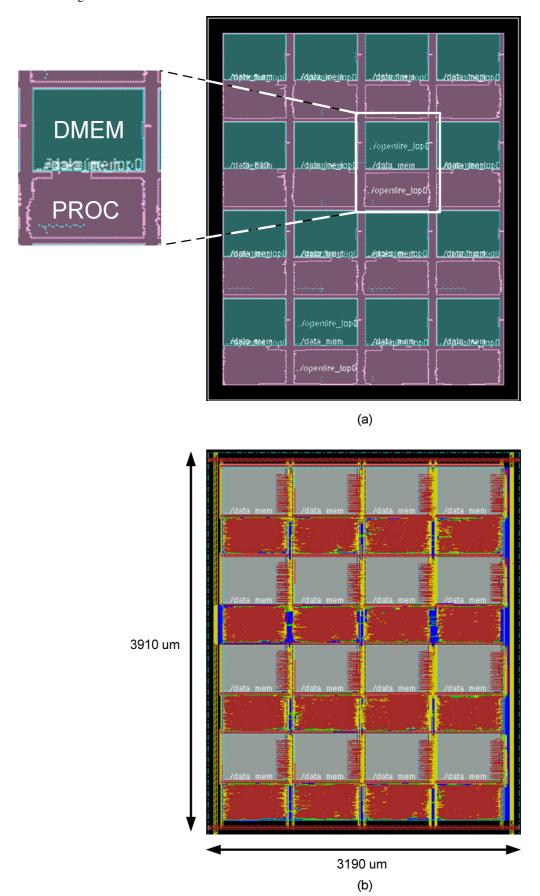

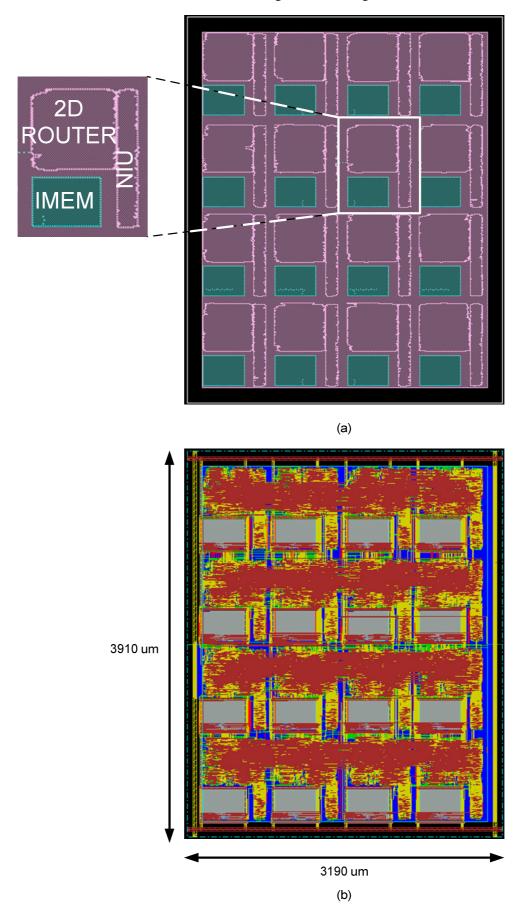

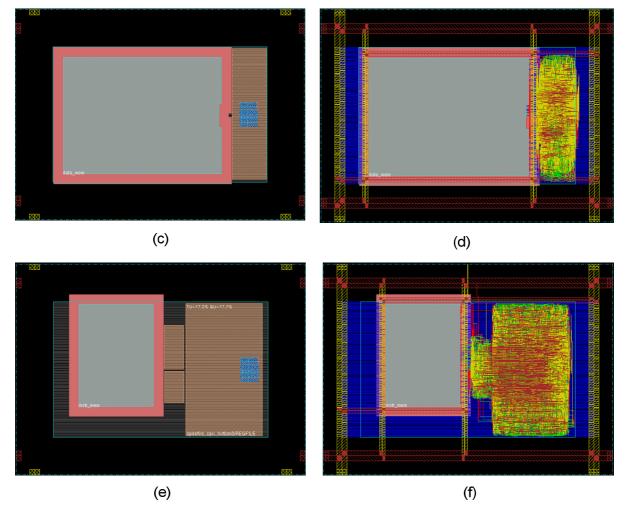

| Figure 78: | Bottom tier of heterogeneous 3D stacking (a) amoeba view (b) routed layout      | 175 |

| Figure 79: | Top tier of heterogeneous 3D stacking (a) amoeba view (b) routed layout         | 176 |

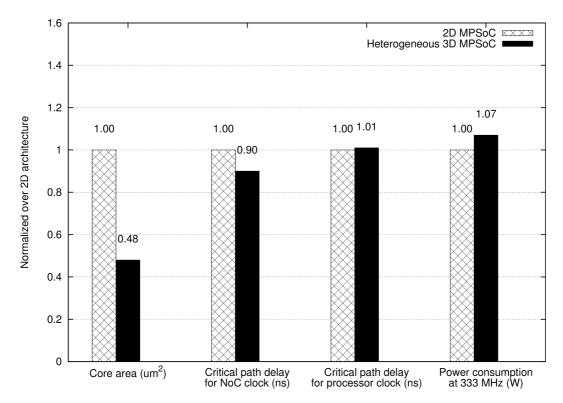

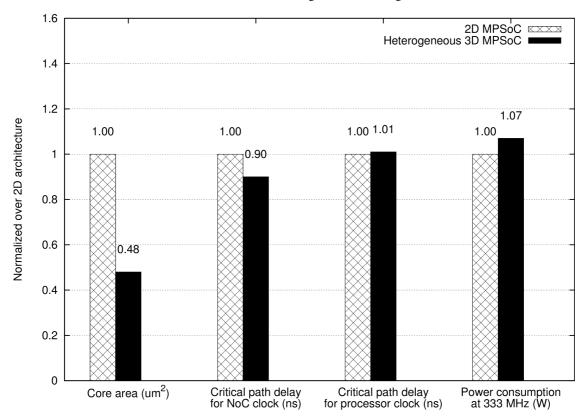

| Figure 80: | Performance comparison for 2D and heterogeneous 3D MPSoC architecture           | 178 |

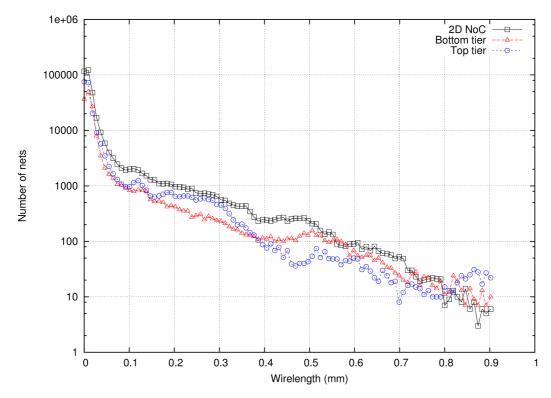

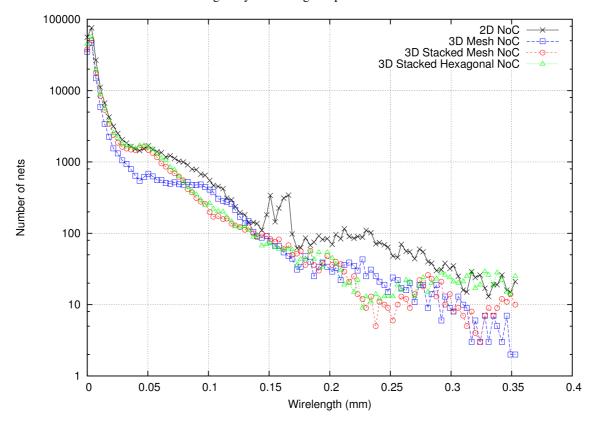

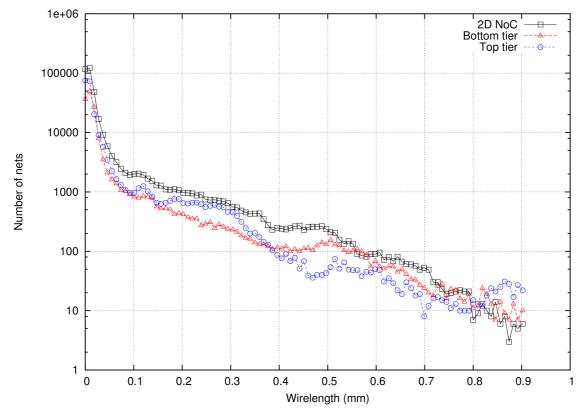

| Figure 81: | Horizontal wirelength distribution for 2D MPSoC and 3D MPSoC (bottom and top    |     |

|            | tier)                                                                           | 178 |

| Figure 82: | Clock tree structure of 2D MPSoC architecture (a) NoC clock (b) processor clock | 181 |

| Figure 83: | Clock tree structure for heterogeneous 3D MPSoC stacking (a) processor clock of |     |

|            | bottom tier (b) processor clock of top tier (c) NoC clock of top tier           | 182 |

| Figure 84: Critical path for 2D MPSoC (a) processor clock (b) NoC clock                       | 84 |

|-----------------------------------------------------------------------------------------------|----|

| Figure 85: Critical paths of each tier separately in SoC Encounter for the heterogeneous 3D   |    |

| MPSoC (a) processor clock in bottom tier (b) processor clock in top tier (c) NoC              |    |

| clock in top tier18                                                                           | 86 |

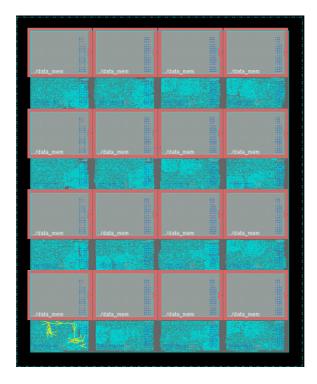

| Figure 86: Openfire 3D architecture with 5 µm microbump pitch (a) floorplan of bottom tier    |    |

| with microbumps array on top of memory block (b) routed layout of bottom tier                 |    |

| with many DRC violation (c) floorplan of bottom tier with microbumps array on                 |    |

| top of processor logic (d) routed layout of bottom tier (e) floorplan of top tier (f)         |    |

| routed layout of top tier                                                                     | 88 |

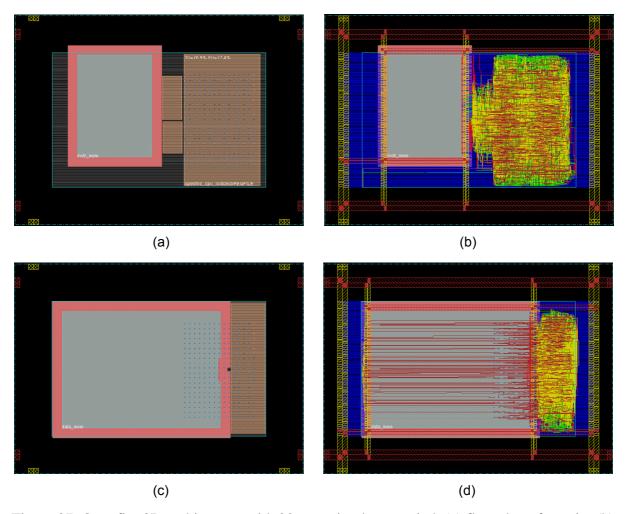

| Figure 87: Openfire 3D architecture with 20 µm microbumps pitch (a) floorplan of top tier (b) |    |

| routed layout of top tier (c) floorplan of bottom tier (d) routed layout of bottom tier 18    | 89 |

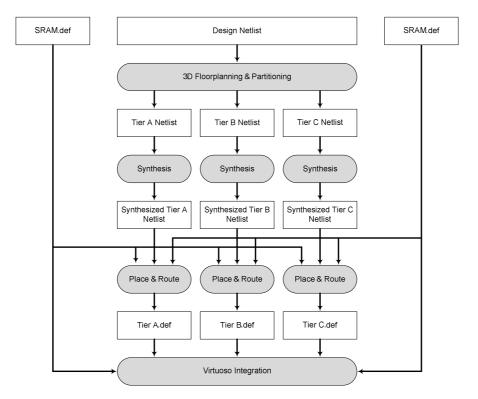

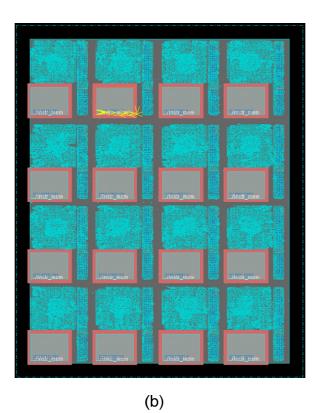

| Figure 88: Design flow for EDA tool exploration                                               | 95 |

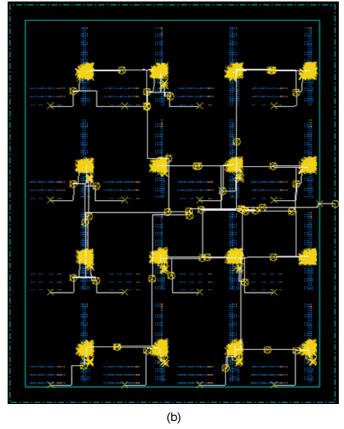

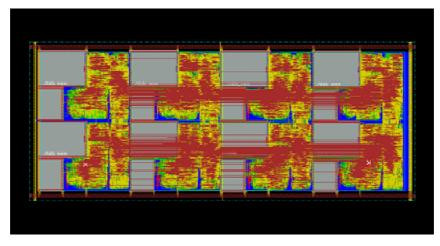

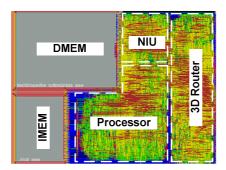

| Figure 89: Bottom tier routed layout (top tier has the same layout)                           | 96 |

| Figure 90: Close-up diagram of tile routed layout                                             | 96 |

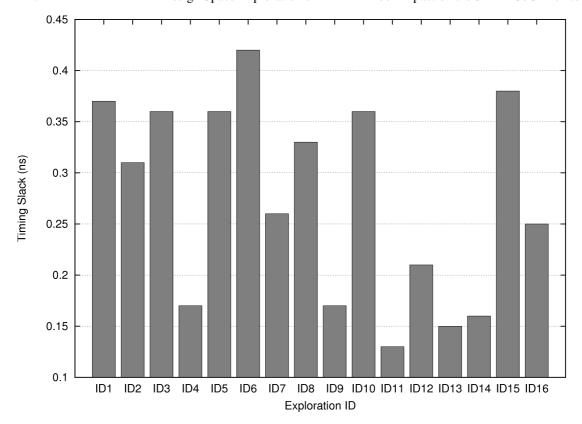

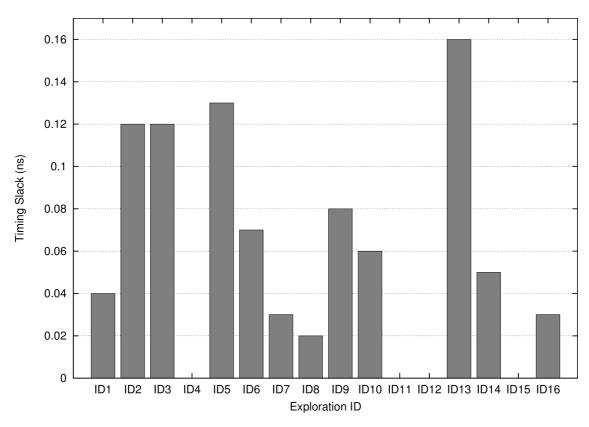

| Figure 91: Processor timing slack (WNS) distribution for 3D Mesh MPSoC                        | 98 |

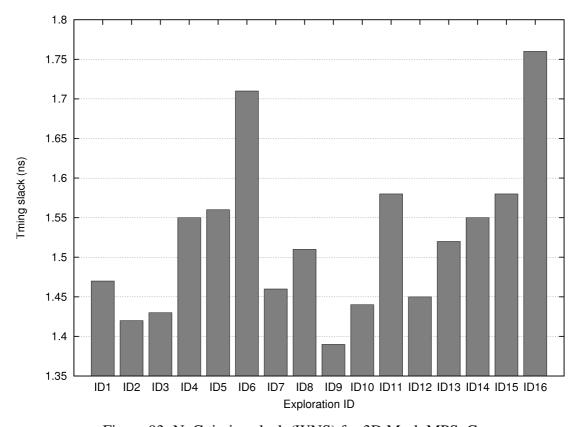

| Figure 92: Processor Timing slack (WNS) distribution for heterogeneous 3D MPSoC               | 98 |

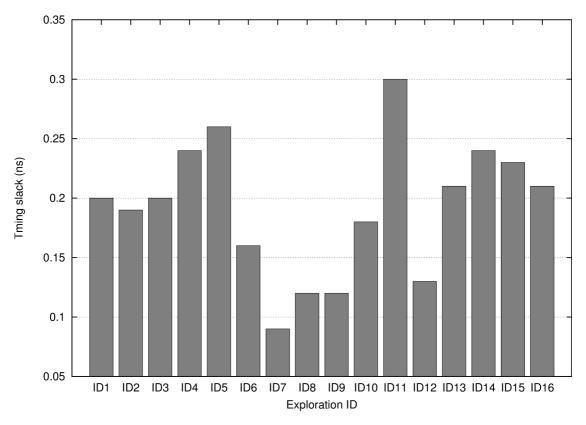

| Figure 93: NoC timing slack (WNS) for 3D Mesh MPSoC                                           | 99 |

| Figure 94: NoC timing slack (WNS) for heterogeneous 3D MPSoC                                  | 00 |

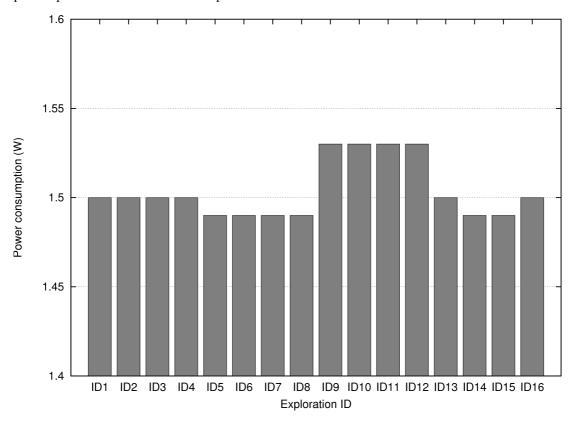

| Figure 95: 3D power consumption for 3D Mesh MPSoC                                             | 01 |

| Figure 96: 3D power consumption for heterogeneous 3D MPSoC                                    | 01 |

# LIST OF TABLES

| Table 1: OCP-IP interface signals                                                               | 70   |

|-------------------------------------------------------------------------------------------------|------|

| Table 2: ZeBu UF-4 emulation board detail                                                       | 72   |

| Table 3: Logic resources in Virtex 4 LX200                                                      | 72   |

| Table 4: ZeBu UF4 operating mode and performance                                                | 72   |

| Table 5: Post place and route logic utilization for MicroBlaze with basic and enhanced configu- |      |

| ration                                                                                          | 78   |

| Table 6: OCP master command signals                                                             | 79   |

| Table 7: Execution cycles for different number of processors and different MicroBlaze configu-  |      |

| rations                                                                                         | 81   |

| Table 8: Comparison of wafer bonding technology [92]                                            | 98   |

| Table 9: Comparison of stacking granularities for 3D architecture design                        | 99   |

| Table 10: Electrical and thermal properties of several materials                                | .107 |

| Table 11: Summary of published 3D standards                                                     | .109 |

| Table 12: 3D architecture implementations summary                                               | .116 |

| Table 13: Physical design parameters using 130 nm standard library                              | .136 |

| Table 14: Physical design parameters using 45 nm standard library                               | .137 |

| Table 15: NoC topology comparison                                                               | .147 |

| Table 16: Performance comparison of 3D NoC architectures in 130 nm technology                   | .150 |

| Table 17: Performance comparison of 3D NoC architectures in 45 nm technology                    | .152 |

| Table 18: Extrapolation of delay for 3D NoC topologies using different process technologies     |      |

| and network diameter comparison                                                                 | .156 |

| Table 19: MPSoC1 physical design characterics                                                   | .160 |

| Table 20: 3D MPSoC implementations comparison                                                   | .162 |

| Table 21: Synthesize area for each block in a tile                                              | .172 |

| Table 22: Performance comparison for 2D and 3D heterogeneous stacking                           | .177 |

| Table 23: Clock tree structure properties for 2D and 3D designs                                 | .183 |

| Table 24: Timing performance of different microbumps pitches (target clock period of 10 ns)     | .189 |

| Table 25: EDA tool options for design space exploration                                         | .193 |

| Table 26: Summary of design space exploration                                                   | .194 |

| Table 27: 3D architectures design summary for the exploration                                   | .196 |

#### Introduction

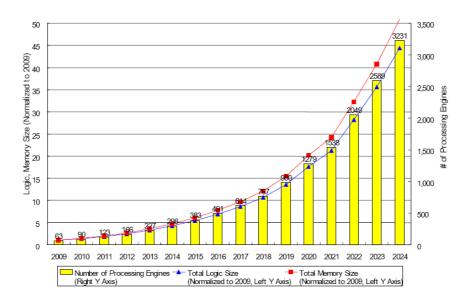

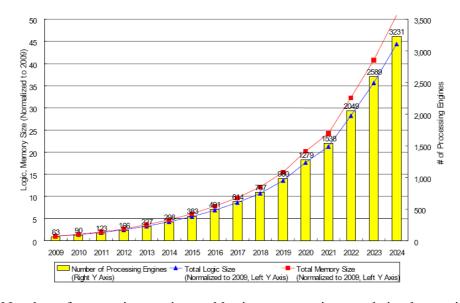

Conceptions électroniques ont connu une croissance rapide au cours des dernières années et qui s'est déclenchés par l'introduction des smartphones et des tablettes dans les marchés. Petit facteur de forme, de meilleures performances et moins d'énergie figurent parmi les exigences d'appareils mobiles afin de fournir plus petit, moins cher, plus rapide appareils électroniques au grand public. La Figure 1 montre l'évolution du nombre d'éléments de traitement dans les appareils grand public portables SoC selon l'International Technology Roadmap semi-conducteurs (ITRS). Comme la montre la figure, dans un proche avenir, le nombre d'éléments de traitement devrait augmenter de plus de 100 processeurs. En outre, la taille de la mémoire est également prévue d'augmenter considérablement à l'avenir avec l'augmentation du nombre d'éléments de traitement.

Figure 1: Nombre de processeurs et l'évolution de logique de mémoire de taille dans les systèmes électroniques

Améliorer la performance de la conception de processeur unique grâce à la fréquence d'horloge plus élevée pose inconvénient de forte consommation et de l'architecture multiprocesseur qui a été mise en place lorsqu'un dessin ou modèle à plusieurs processeurs simples fonctionnent à une fréquence plus basse et l'approvisionnement en basse tension. Nous passons d'une vaste architecture de calcul d'architecture de communication vaste place de cette architecture multiprocesseur. Cependant, la conception de haute performance architecture multi cœur du processeur nécessite plusieurs défis à résoudre, comme différents interfaçage de IP Core, automatisation de la conception, vérification et

la programmation logicielle [1]. Afin de répondre à la demande de l'exigence de communication, réseau sur puce (NoC) est développé surmonter la limitation de l'architecture de bus base telles que celles à long temps de retard en raison de la politique d'arbitrage, le câblage complexe et donc d'augmenter la consommation d'énergie du système. En contraste, NoC offre une évolutivité en augmentant le nombre de processeurs.

Au départ, nous nous appuyons sur la fonction de mise à l'échelle CMOS pour avoir plus de performance qui est obtenue par réduction de la dimension physique du transistor afin que les transistors de nombreux autres peuvent être emballés dans une seule puce et ainsi augmenter les performances grâce à une architecture pipeline plus profondément. Toutefois, le passage vers les nœuds de processus plus petites introduit beaucoup de grands défis économiques et technologiques et en même temps diminuer les avantages de performance à tous les nœuds d'échelle [2]. En outre, la limitation de la mise à l'échelle CMOS comme les limites maximales de tension et de la variabilité dispositif ont également eu des répercussions techniques de conception au niveau système et circuit où les techniques de conception supplémentaires sont nécessaires pour permettre l'amélioration des performances et de réduction de la puissance croissante de la réduction des coûts [3].

D'autre part, il existe une alternative pour augmenter les performances de la conception électronique sans passer par un chemin difficile avec mise à l'échelle CMOS appelé l'intégration 3D. Cette technologie permet la construction de circuits en 3 dimensions (3D) des structures en empilant les plaquettes en plusieurs couches. Cette nouvelle technologie offre des avantages potentiels de la plus grande vitesse, faible consommation d'énergie, l'intégration des technologies hétérogènes, petit facteur de forme et de haute densité d'intégration appareil. Contrairement à la technologie CMOS mise à l'échelle, l'intégration 3D est une solution prometteuse pour conduire l'avenir de circuits VLSI pour soutenir la demande continue des systèmes électroniques de haute performance. Ces avantages seront décrits en détail dans les sections suivantes.

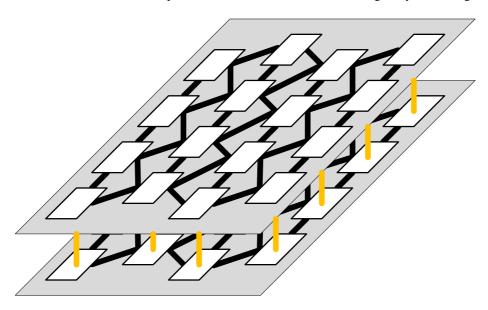

L'intégration 3D, la longueur d'interconnexion à long fil métallique est réduite à la racine carrée de la longueur de l'intégration 3D grâce à la connexion en utilisant soit verticale courte TSV ou microbumps. Ceci améliore la vitesse où il réduit le retard RC du long fil d'interconnexion dans l'architecture 2D et également de réduire le nombre de tampons le long du fil d'interconnexion dans laquelle finalement la consommation d'énergie est réduite aussi. Intégration 3D supporte également l'intégration de technologies telles que hétérogène numérique, analogique, RF et la technologie MEMS, où ils peuvent être fabriqués selon la leur technologie de processus optimal et ensuite

empilées avec l'autre technologie des procédés. Malgré l'avantage amené par cette technologie, il est également confronté à plusieurs obstacles critiques tels que les problèmes thermiques, la structure de livraison de puissance et de synthèse d'horloge en arbre. Comme l'intégration 3D empilées plusieurs couches de silicon actifs, la densité du dispositif par unité de volume est augmenté et augmente donc la densité de puissance. Un autre effet est qu'il existe des points chauds thermiques dus au différent profil de consommation de puissance de blocs logiques dans chaque couche. Cela crée gradient thermique sur la puce qui crée des variations qui pourraient affecter l'intégrité et la fiabilité des dispositifs au fil du temps. Bien que certaines des techniques d'essai pour l'architecture 2D peut être étendu pour permettre de tester l'architecture 3D tels intégré d'autotest intégré (BIST) et la méthode de boundary scan, mais la fabrication de TSV introduit nouveau défaut du mécanisme tels que des shorts ou ouvre due à un mauvais alignement et microvoids et donc nécessite une nouvelle approche pour tester ces défauts. Voici quelques principales questions en matière de technologie d'intégration 3D qui doivent être surmontés avant de pouvoir être commercialement viable dans de nombreux produits.

# **Motivations De Recherche**

Comme il s'agit d'une technologie relativement nouvelle à l'heure actuelle, de nombreuses questions sont encore à l'étude approfondie de l'industrie et du milieu universitaire. En regardant la publication dans des conférences et des revues, nous avons réalisé qu'il y a un manque de vraie conception et la mise en œuvre effectuée pour avoir des résultats plus réalistes sur l'analyse de la performance de cette technologie. En particulier, les travaux de recherche en 3D NoC architecture ont été fait principalement à l'aide de logiciels de simulation basé sur le cycle-précis simulateur qui fournissent des résultats irréalistes qui sont insuffisantes pour évaluer les avantages et les inconvénients de la technologie 3D. Par conséquent, l'une des principales motivations de ce travail est de procéder à l'analyse des performances à l'aide de la conception et de la mise en œuvre réelle de la technologie 3D grâce à la technologie qui sont disponibles à utiliser. Grâce à cette approche, nous cherchons à avoir des résultats plus réalistes et donc pourrait nous aider à mieux comprendre les offres de compromis pour utilisent cette technologie. A part cela, nous concentrerons notre travail sur l'aspect architectural de cette technologie que nous avons utilisée spécifiquement la technologie 3D de Tezzaron à deux niveaux pour l'aspect technologique. La plupart des dispositifs électroniques actuels ont plus d'un cœur de traitement afin d'avoir une plus grande capacité pour exécuter des différentes applications avec des performances supérieures. Cela est dû au fait que les performances de l'architecture monoprocesseur ne peut pas être encore améliorée à cause de le mur de puissance et de le mur de mémoire. Par conséquent, il est intéressant de savoir comment cette

technologie 3D pourrait être utilisée pour surmonter les problèmes multiprocesseurs qui se posent aujourd'hui pour être en mesure d'améliorer ses performances. Plusieurs travaux ont été fait effectuer la conception et la mise en œuvre de l'architecture multiprocesseur utilisant la technologie 3D où un certain nombre de travaux ont montré poignée amélioration des performances tout à fait significative en utilisant la technologie 3D quand comparer avec l'architecture 2D. Cependant, aucun des précèdent travaux d'analyse de l'architecture des performances de 3D NoC qui est basé sur les résultats de conception et de mise en œuvre, ce qui est l'objectif principal de ce travail. Par ailleurs, l'enquête de topologies de NoC en architecture 3D basé sur la conception et la mise en œuvre des résultats aussi n'ont pas été réalisées. Il est intéressant de comprendre quel genre de topologies de NoC (2D ou 3D) est meilleur dans l'architecture 3D en termes de performances où nous ne l'avons pas considérer comme lors de la conception d'une architecture 2D.

#### **Contributions**

- 1. Proposition de méthodologie de conception originale pour la conception d'architecture en 3D à l'aide des outils de CAO 2D disponibles principalement axés sur la vérification temporelle 3D. Cette vérification temporelle 3D est possible parce que la connexion verticale entre les niveaux est créée en utilisant microbumps qui a retard négligeable dans cette technologie particulière 3D. La méthode de conception proposée 3D a été utilisé pour les expériences dans cette thèse menée pour étudier les différentes mis en œuvre de l'architecture qui sont réalisables en utilisant la technologie 3D.

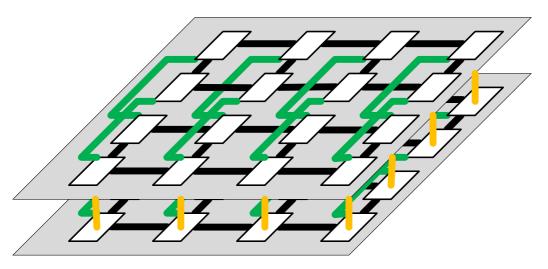

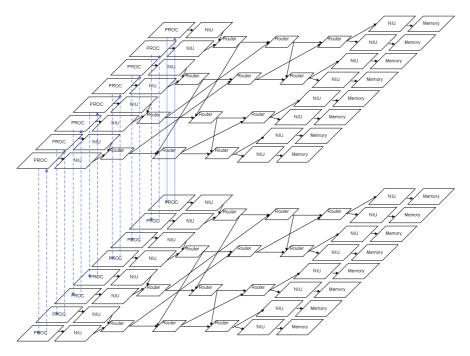

- 2. NoC présenté des topologies d'exploration dans l'architecture 3D grâce à la mise en œuvre de la conception physique motivé par les études antérieures dans la littérature qui a effectué l'analyse des performances de la mise en œuvre du logiciel. Nous avons conçu et mis en œuvre en 3D mesh NoC topologie à l'aide du routeur 3D pour la connexion verticale entre les niveaux et 3D maille empilés NoC topologie à l'aide de l'architecture d'empilage homogène routeur 2D en 2 niveaux d'architecture 3D basé sur la technologie Tezzaron et comparé ses performances avec l'architecture 2D. Enfin, nous avons proposé une nouvelle topologie de NoC d'architecture 3D qui est la topologie hexagonale qui offre de meilleures performances que d'autres topologies dans la mise en œuvre de la technologie 3D en raison des liens entre l'égalité de fil-routeur.

- 3. La mise en œuvre d'empilage hétérogène 3D de GALS architecture multiprocesseur par l'empilement de l'architecture NoC sur le dessus du processeur en raison du nombre limité d'œuvres de l'architecture 3D basé sur la mise en œuvre GALS. Dans cette étude, nous avons analysé les performances de l'architecture hétérogène empilées en 3D qui ont été manuellement la partition en 2 niveaux et par rapport à son architecture correspondance 2D à la conception

identifié.

4. Ayons effectué une exploration de l'espace de conception de l'architecture MPSoC 3D pour analyser l'impact des outils de CAO 2D pour sa performance comme la qualité de calendrier, la consommation d'énergie et mesure de longueur. Depuis, il est compréhensible de la limitation de l'utilisation des outils de CAO 2D pour concevoir et mettre en œuvre l'architecture 3D, cette étude a examiné l'impact sur les performances de l'architecture 3D 2D lorsque des options d'outils EDA, en particulier le placement et le routage des options est variée nous permet de comprendre plusieurs questions de mise en œuvre importants qui n'ont pas été souligné précédemment. Nous nous concentrons sur le calendrier et les options d'optimisation d'énergie dans l'outil 2D CAO électronique pour l'exploration parce que les deux mesures sont parmi les paramètres les plus essentiels qui sont considérés lors de la conception de l'architecture 3D.

## Technologie 3D: Vue D'ensemble, Les Avantages Et Les Défis

L'intégration 3D offre méthode moins difficile de parvenir à une intégration plus élevé pour les besoins de l'application transistor actuelle par rapport au transistor d'échelle pour les nœuds technologiques plus petits. Avec les technologies de semi-conducteurs d'aujourd'hui, la technologie 3D est possible d'être conçus et mis en œuvre à un coût relativement faible. En utilisant la technologie 3D TSV est une approche où les matrices ou de plaquettes sont empilées et en utilisant TSV pour leur interconnexions électriques dans un seul paquet. Cette technologie offre une meilleure densité des interconnexions entre les matrices et les plus petits en raison de la structure de raccordement vertical situé à l'intérieur de la zone de matrice. Il existe aussi une autre forme de ce type de technologie connue sous le nom 2.5D à l'aide de plusieurs matrices où est placé au-dessus d'un élément d'interposition de silicon (interposition active ou passive), qui se compose de plusieurs couches de métal d'interconnexion formée avec TSV que la liaison entre matrices et de l'interface externe.

L'un des principaux avantages de la technologie 3D, c'est que la longueur d'interconnexion à long fil est réduite en raison de l'empilement. Il peut réduire les cent micromètres de fil d'interconnexion horizontales de l'architecture 2D à une longueur quelques micromètres en utilisant la structure TSV. Ceci améliore la vitesse où il réduit le retard RC du fil d'interconnexion et également de réduire le nombre de tampons le long du fil d'interconnexion et éventuellement le retard global. Une expérience sur l'architecture 3D FFT [4] et d'une architecture de microprocesseur [5] a montré l'amélioration de la vitesse de conception 3D. Pour l'architecture 2D, le nombre de couches métalliques augmente de manière à faire face à l'augmentation du nombre de transistors dans la

matrice de silicon qui jusqu'à 12 couches de métal pour la technologie de pointe. En ce qui concerne l'intégration 3D, la réduction des fils d'interconnexion globaux due à la réduction de la congestion de routage éventuellement augmente les performances. Stratégie de partitionnement a une forte influence à l'amélioration de la latence et son évolutivité lors de l'empilement des couches supplémentaires [6].

Le retard de TSV devrait être considéré lors de la mesure d'amélioration de ses performances. Les résultats expérimentaux montrent que le retard de TSV est compris entre 35 ps à 135 ps [7] et 16 ps pour 20 µm de hauteur, ce qui est inférieur au fil de retard dans l'architecture 2D par exemple 219 ps de 2500 µm longueur de fil de 4,5 GHz de vitesse. Le r de TSV est en fonction de plusieurs facteurs tels que le diamètre, la hauteur, le pitch et la technologie. La hauteur et le pitch du TSV largement affecter son retard alors que le diamètre TSV a un effet de petite taille [8]. La résistance TSV a moins à se prononcer à son effet retard de la capacité TSV [9]. En termes de technologie, basée sur la technologie SOI-3D aura moins de retard TSV que le vrac de la technologie CMOS en raison de la dimension plus petite de TSV qui réduisent le retard de RC [6]. Comme nous l'avons inclure plus de couches dans la structure 3D, supérieur retard de TSV sera remarqué due à l'augmentation de la numération TSV.

Avec l'existant de l'interconnexion verticale comme nous empilons des plaquettes, ce qui permet plus de possibilités d'optimisation de la conception qui ne peut être fait qu'en utilisant l'architecture 2D. Par exemple, nous pouvons avoir grande variété d'optimisation du partitionnement dans différents niveaux d'empilement de mémoires et les processeurs afin d'optimiser les performances de communication [4]. En dehors de cela, en utilisant l'outil de partitionnement automatisé pour la conception en architecture 3D pourraient fournit également l'amélioration des performances considérables en contraste avec la méthode le partitionnement manuel optimisé.

La consommation d'énergie peut également être réduite en raison de la réduction de la longueur du câble d'interconnexion qui diminue la capacité du câble [10] et de réduire le nombre de répéteurs. En outre, l'intégration 3D est non seulement dépassé en termes de performances, il est également évolutive que la conception deviennent plus complexes, comme par exemple l'amélioration de la consommation d'énergie d'environ 11%, 21% et 46% pour les 12, 36 et 72 bits Kogge-Stone adder [11].

En raison de la forte densité d'interconnexion entre des matrices empilées ou de plaquettes, d'architecture 3D peut être utilisé pour atténuer les problèmes de mémoire mur en fournissant

courtes liaisons verticales et permet également une plus grande capacité de mémoire sur puce nécessaire en particulier par la grande architecture multicore [12]. L'architecture wide I/O est une autre approche pour atténuer les problèmes de mur de mémoire en offrant des données d'une bande passante élevée grâce à plus grand nombre de broches d'I/O pour l'accès mémoire [13].

Construire l'architecture empilement 3D permet petit facteur de forme de l'architecture 2D. L'épaisseur de la puce après l'empilement est de plusieurs centaines de microns, ce qui est relativement faible par rapport à la puce 2D classique. L'avantage de petit facteur de forme permet une intégration à haute densité. Par exemple, l'empreinte puce est réduite de 44% pour les quatre couches empiler contre deux couches de la pile de 65 nm [14].

L'intégration des technologies hétérogènes est moins complexe que dans la conception 2D où les architectures différentes, par exemple analogiques, RF, capteur, mémoire pour être intégré sans processus de fabrication difficile, car chaque architecture qui est produit en utilisant leur propre technologie de processus optimale et puis ils sont intégrés dans la structure 3D à l'aide méthodes telles que collage de plaques. En outre, l'architecture hétérogène peut également être implémenté en utilisant la technologie des procédés différents, tels que 95 nm pour le processeur à 65 nm de mémoire tel que démontré dans [15]. Ceci permet aux applications SoC avec une meilleure capacité de répondre aux besoins des systèmes embarqués tels que le traitement en temps réel et une faible consommation électrique et aussi un support pour la conception de SoC avenir qui est une structure très hétérogène [16]. Du point de vue SoC qui a des blocs numériques et analogiques dans une matrice, l'intégration 3D aussi surmonter le problème d'isolation du bruit de l'architecture de signal mixte 2D parce analogique / RF et des composants numériques peuvent être placés séparément dans différentes couches de silicon [17].

TSV est une méthode qui utilise par l'intermédiaire de l'autre côté les différentes couches de silicon actif. Utilisations pour TSV est Tungstène (W) [18], le Cuivre (Cu) [19] [20] et Poly-Silicon (Poly-Si) [21]. Poly-Si matériau est stable et a moins d'effet sur la caractéristique du dispositif que les autres matériaux. Cependant, Cuivre ou Tungstène est plus approprié pour la cause de diminution de la résistance TSV. Cuivre est le plus couramment utilisé car il a une bonne conductivité thermique par rapport à Tungstène et Poly-Si. Cependant, comme on le verra plus tard dans les défis et des enjeux de 3D, Cuivre TSV créer un effet de stress dû à la grande différence de coefficient de dilatation thermique (CTE) entre le substrat de silicon et de cuivre, ce qui n'est pas le cas pour Tungstène TSV. Une comparaison détaillée de la via filling material se trouve dans [22]. Tungstène a plus retarder par rapport à Cuivre TSV pour n'importe quelle taille de diamètre et est

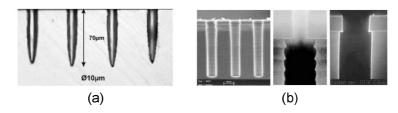

donc utilisé dans la recherche [23]. TSV peut être formée soit à l'aide du MEIR ou perçage laser qui, comme représenté dans la Figure 2 affectant sa taille. Utilisation MEIR, aussi connu comme Procès Bosch, est une méthode largement utilisé qui peut produire un rapport d'aspect élevé, mais au détriment de la hausse du coût par rapport à la méthode de forage au laser. Utilisation la méthode de perçage au laser limite le diamètre TSV à environ 10 µm. En outre, cette méthode est un processus de série et ne donc pas adapté pour des conceptions de nombre élevé de TSV [24].

Figure 2: Formation TSV en utilisant (a) forage au laser et (b) DRIE

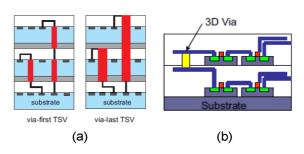

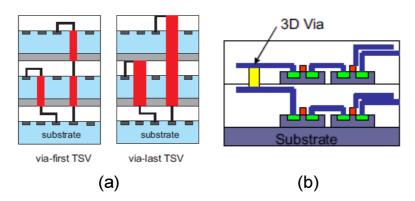

Il y a différentes techniques pour mettre en œuvre TSV comme par l'intermédiaire du premier, par l'intermédiaire du milieu ou par l'intermédiaire de dernier, tel qu'illustré à la Figure 3. Dans première technique, TSV est formée avant que la structure BEOL. Par conséquent, nous avons une taille relativement petite par rapport aux deux autres méthodes [25]. Alors que par le dernière approche TSV se forme après la formation BEOL, ce qui entraîne plus grande dimension TSV. La dernière méthode est un processus plus difficile car la formation de TSV pourrait endommager les appareils qui ont déjà été formés. Le processus de fabrication TSV se compose de plusieurs étapes qui sont de forage, d'isolation, de remplissage ou de métallisation, la formation FEOL, la formation BEOL, la manipulation d'attachement, plaquette amincissement et le traitement au verso. L'ordre dépend des techniques de formation TSV soit par l'intermédiaire dernière ou par l'intermédiaire premier. Comme la manipulation de fine plaquette est un grand défi, elle peut être évitée par l'amincissement de la plaquette après collage avec une autre plaquette d'épaisseur. Il pourrait également empêche une baisse de rendement en raison des processus supplémentaires pour le collage de la poignée de plaquettes et de décollage.

Figure 3: TSV méthodes d'empilage (A) par-premier-dernier et par l'intermédiaire d'CMOS en nombre (b) par l'intermédiaire de premier TSV-CMOS SOI dans [26]

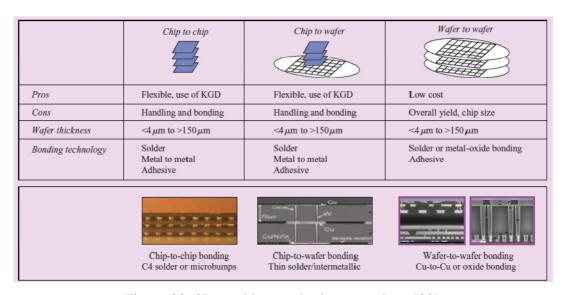

Méthodes d'empilement peut être implémenté de plusieurs manières telles que wafer-to-wafer, die-to-wafer ou die-to-die. La méthode de plaquette à plaquette est surtout utilisée pour l'intégration 3D en raison du faible coût que les deux autres méthodes. Cependant, il souffre de faible rendement en raison de die de mauvais rendement d'adhérence par rapport à d'autres méthodes de collage qui prennent en charge known good die (KGD). Un autre inconvénient d'empilage plaquette à plaquette est qu'elle est limitée aux die de même taille dans les plaquettes rendant offre un débit de production élevé. La méthode de die-to-die engendre de coût élevé dû à la liaison de chaque filière, mais peut être utilisé pour différentes tailles de die obligataires.

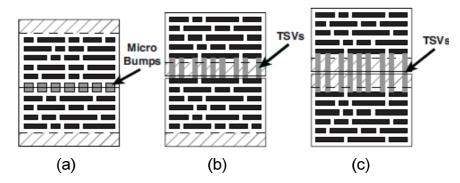

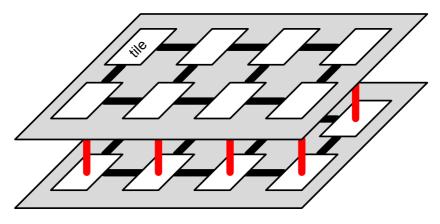

Du point d'orientation de collage, il existe en plusieurs méthodes, comme face-to-face, face-to-back et back-to-back comme le montre la Figure 4. Pour 2 niveaux comme dans la mise en œuvre technologie 3D Tezzaron, l'orientation face-to-face est la meilleure façon où l'inter-moule connexions microbumps est utilisée, et donc ne bloque pas les couches de routage. Pour plus de 2 niveaux comme dans MIT Lincoln Lab 3 niveaux de technologie, à la fois face-to-face et face-to-back l'orientation est utilisé lorsque toutes les connexions inter-tier se fait à travers la structure TSV.

Figure 4 : Orientations d'empilement (a) face-to-face (b) en face-to-back (c) back-to-back

En termes de mise en œuvre lien physique, plusieurs méthodes peuvent être employées comme du métal à la liaison métallique, l'oxyde de collage direct et collage adhésif. En règle générale, la liaison métal-a-métal est meilleur car elle donne une connexion mécanique et électrique entre plaquette et Cu est le matériau le plus couramment utilisé. Cependant, il souffre d'un traitement à température élevée, par exemple supérieure à 350°C. L'alignement de collage est le paramètre clé pour atteindre la densité d'interconnexion haute de la liaison métal-a-métal [27]. Cette température élevée doit être soigneusement surveillé car il peut endommager la couche inférieure et affecter l'appareil. Collage adhésif utilise un traitement à basse température. Cependant, il y a des possibilités de contamination par le matériau adhésif sur les appareils. Parmi les matériaux utilisés

sont benzocyclobutène (BCB), polyamide et pyralène. BCB est le plus couramment utilisé car il a la plus grande force de liaison qui est supérieure à 20 MPa [28]. Le collage direct utilise substrat d'oxyde de silicon ou de la matière de collage [29]. Il se fait à température ambiante, puis recuit à haute température pour obtenir covalente Si-O-Si. Par conséquent, il a la plus grande force de collage par rapport à d'autres méthodes. Le problème est qu'il est très sensible à la contamination par exemple 1 µm de diamètre des particules pourrait créer 1 cm de diamètre vide lors du collage de huit plaquettes [28]. Techniques de collage hybrides a également été rapportée en utilisant Cu avec collage [30].

#### **Tezzaron 3D Technologie**

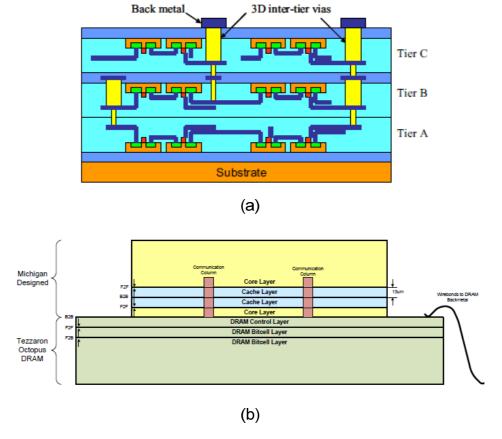

Tezzaron technologie 3D est basé sur le niveau plaquette d'empilage. La tranche est collée au moyen d'une liaison en utilisant un matériau métallique Cu thermique tel que représenté sur la Figure 6 [31]. Tezzaron a été mis au point plusieurs architectures TSV, l'un d'eux est la technologie FaStack. Ils atteignent une précision d'alignement pour la tranche d'environ 0,5 μm. Tezzaron utilisé des méthodes via le premier face-à-face de liaison et ses propriétés d'empilement sont indiquées dans Figure 7. Plusieurs puces de test 3D a été démontrée en utilisant cette technologie comme un capteur CMOS, 3D FPGA, ASIC à signaux mixtes et processeur / mémoire pile. Parce que la plaquette est amincie après le collage, il n'ya donc pas besoin d'un processus de manipulation des plaquettes aider à réduire les pertes de rendement en raison des processus supplémentaire de liaison et de dé liaison de la poignée plaquette.

Figure 6: Tezzaron face-to-face superposition à l'aide microbumps

Figure 7: les paramètres de la technologie Tezzaron 3D

Malgré les avantages qu'il offre, il existe plusieurs problèmes qui doivent être résolus pour faire de l'intégration 3D peut être appliquée dans les appareils électroniques grand public. La nature de la 3D stacking provoqué une surchauffe ne peut pas facilement être transférée hors de la puce, en particulier la chaleur générée loin du réservoir de chaleur. Contrairement à l'architecture 2D laquelle la chaleur générée pour tous les composants peut être transférées directement sur le heat sink par dissipateur thermique car il peut être placé juste au-dessus des composants. L'importance de l'effet d'empilement dans la structure 3D est augmentation de la pic de température [32] [33] dans la puce où il peut s'élever à plus de 100 °C. Deux choses sont très importantes à la suite de cette température élevée qui est la variation de température et point d'accès. Ces deux éléments influents sur la fiabilité de la puce sont le temps moyen de taux d'échec (MTTR) et temps de claquage (TTBD). La puissance de fuite augmente exponentiellement avec la température. Chaque augmentation de 15 °C de température provoquent la variation du délai d'interconnexion autour de -15% à 10%. L'augmentation de la température est également à l'origine d'électro-migration qui augmente de facon exponentielle et réduit éventuellement la durée de vie du produit par quatre fois [34]. Plusieurs méthodes ont été proposées pour les techniques de gestion thermique pour résoudre le problème thermique dans l'intégration 3D telles que l'élevage thermiques qui placent les blocs le plus souvent passer près de heat sink [35] et l'utilisation de thermal vias pour transférer la chaleur de la puce [36]. La tension thermique est un autre effet du problème thermique lors de l'intégration à l'aide TSV. Cela est dû à la propriété différente de la Silicon CTE, Cu, dioxyde de silicon et W. La tension thermique est une source de timing variation autour de ± 10% pour une cellule individuelle [37]. Thermique induite par la tension dans l'intégration 3D provoque des fissures à l'interface du substrat de silicon et TSV et Cu entre les interconnexions et low-k isolateur [38].

Question de rendement est également un autre facteur important qui doit être pris en considération pour la structure 3D. L'intégration 3D réduit le rendement global en raison du processus de fabrication qui seront devenus plus petits que d'autres filières est empilé [39]. Modèle de rendement a été développé pour aider à la prise de décision concernant le montage des compromis pour l'intégration 3D comme le nombre de piles à construire et à ce qui est la taille du die optimale [40]. Certaines des techniques pour améliorer les pertes de rendement tels que les ressources redondantes telles que les mémoires et les réseaux de capteurs et en améliorant le processus d'intégration 3D [41]. Autre défi pour l'intégration 3D est l'essai. L'essai de TSV est un problème parce que la taille de la sonde est grande (35 µm) par rapport à la petite taille TSV tels que 5 µm de diamètre avec 10 µm pitch [42]. C'est parce que normalement cette sonde est utilisée pour tester l'architecture 2D qui est normalement utilisé pour les essais de collage du fil.

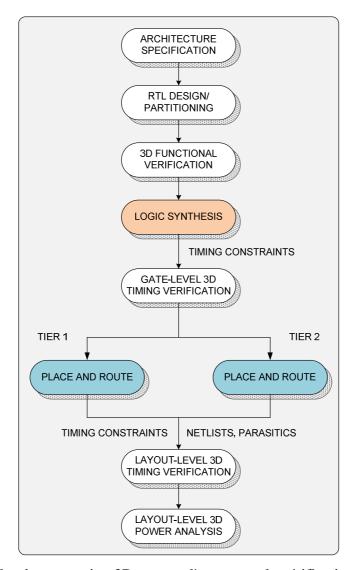

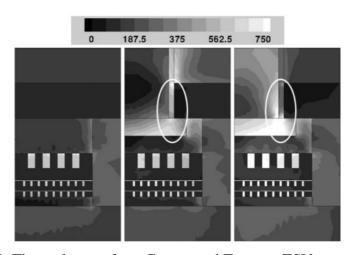

## **Flux De Conception**

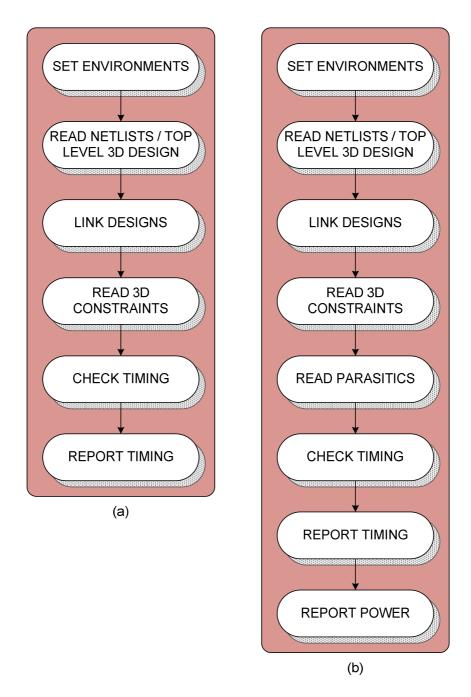

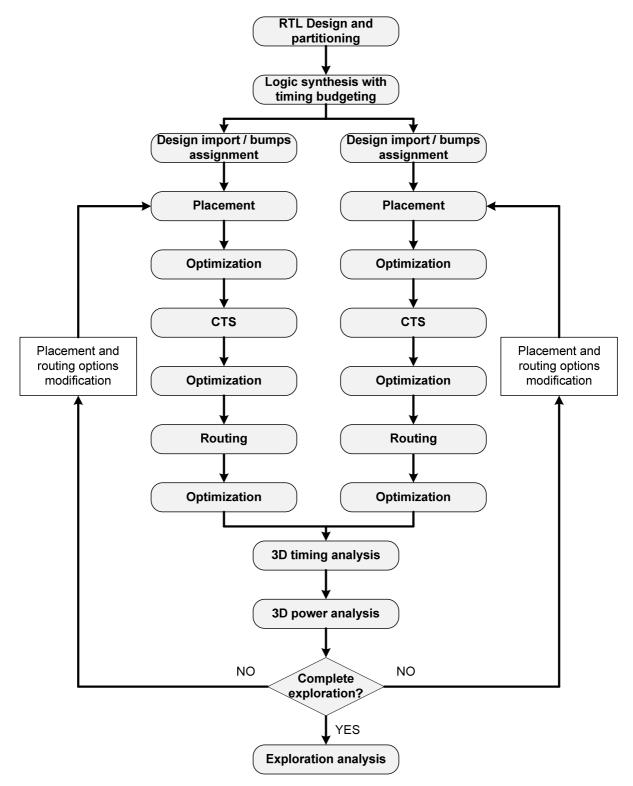

La conception 3D proposée dans notre travail est montré dans la Figure 8 tire profit du petit retard des connexions inter-rang en raison de la structure de microbumps. Ce flux de conception 3D générique peut être réutilisé pour n'importe quelle architecture 3D ciblage technologie 3D Tezzaron contrairement à certains flux de conception rapporté qui est adapté à la technologie particulière. En outre, par rapport aux flux de conception précédente, nous procédons à la vérification 3D à chaque étape du flux dans backend et frontend. Pour la vérification après synthèse 3D, il est possible, car les retard des bosses est très faible et donc négligeable. Par conséquent nous pouvons avoir estimation de performance précoce de la conception 3D après l'étape de synthèse et de gagner du temps parce que nous pouvons avoir la modification architecturale pour satisfaire les spécifications de performance avant de procéder à l'étape de lieu et l'itinéraire que cela prend du temps assez long en particulier pour la conception relativement importante avec un nombre très élevé de microbumps ainsi que la fixation d'autres violations en DRC.

Le conception est d'abord divisé en 2 blocs correspondant à 2 niveaux d'architecture 3D au niveau RTL. Par la suite, avant le fin flot de conception est réalisée à l'aide Synopsys Design Compiler avec un débit de budgétisation chronogramme. Flux de synchronisation budgétaire est une méthode de distribution des contraintes temporelles entre les blocs logiques (dans notre cas, les blocs de partition) de sorte que chaque bloc peut être mis en œuvre séparément et optimisé par leur refoulement propre fin. Tout d'abord, la conception de haut niveau 3D contenant deux blocs partitionnés sont analysées et élaborées avant contraintes temporelles 3D est appliqué. Ensuite, la commande synchronisation budgétaire est exécutée pour générer des contraintes temporelles pour

chaque partition où il sera utilisé pour compiler et générer netlist de chaque partition. Une fois la compilation de blocs partitionnés est terminée, la compilation de niveau haut de conception 3D est alors effectuée et le synchronisation est analysé. En cas de violations de synchronisation existent à chaque partition ou le bloc à la conception 3D de haut niveau, les contraintes temporelles 3D modifient est en relâchant la fréquence d'horloge et le flux budgétaire est répété.

Figure 8: Flot de conception 3D mettant l'accent sur la vérification temporelle

Netlists générés à partir des niveaux de porte et des contraintes de cadencement de chaque partition, est placé et routé. Figure 8 montre l'endroit détail et de débit itinéraire où il est comme flux de conception 2D normale, sauf que l'insertion supplémentaire microbumps pour les connexions interrang, y compris les mesures pour des missions bosses pour inter-rang connexions. L'emplacement des microbumps est déterminé manuellement en regardant le net, il sera connecté afin de ne pas avoir à long longueur horizontale avant d'atteindre l'interconnexion verticale. Une fois l'emplacement est fixé, les tableaux de bosses sont créés, puis la numérotation des bosses est

### VERSION FRANÇAISE

modifié de sorte qu'il est plus facile d'attribuer aux signaux. Enfin, broches physiques sont créés dans chaque microbumps d'être en mesure d'acheminer par le NanoRoute dans SoC Encounter. Au cours de l'étape de planification de l'énergie, les microbumps est également utilisé pour la connexion à la masse entre les deux niveaux de puissance en alignant la position de bosses en tant que tel palier est recouverte sur le dessus de l'autre une fois que l'empilement est réalisé. Une vaste gamme de microbumps est formée par un fils électriques au sol étant donné que ces cours peuvent être assez fournies aux autres niveaux pour assurer un fonctionnement correct. Elle est suivie par le flux de conception 2D classique qui est mise en place, l'horloge de synthèse en arbre et de routage avec l'optimisation est guidé par les contraintes temporelles générées par des flux extrémité avant.

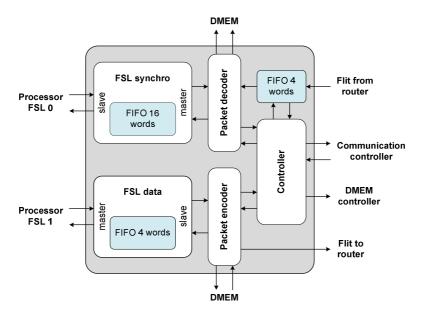

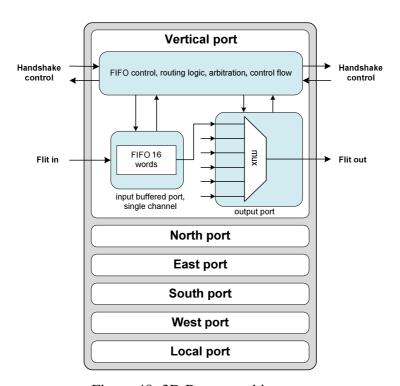

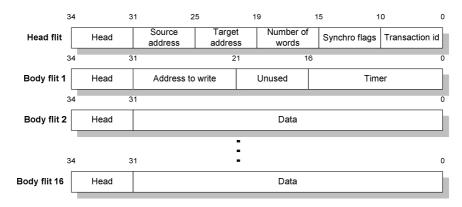

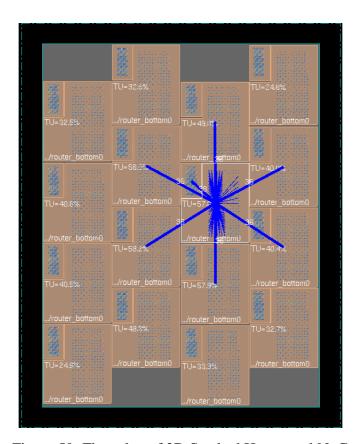

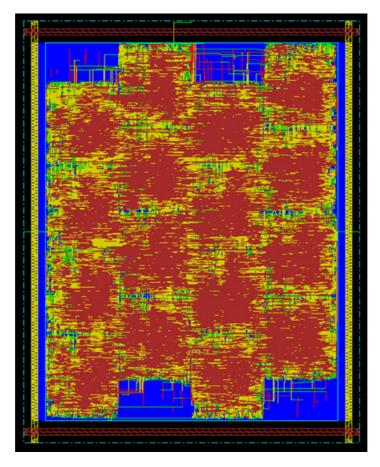

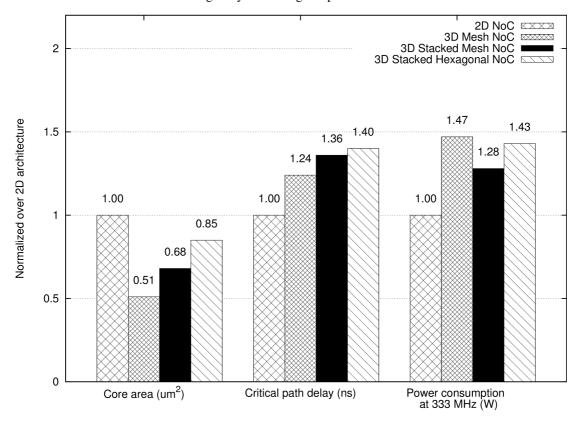

# **Exploration De Conception Physique Des Topologies 3D Noc**