### Certification of an Instruction Set Simulator

#### Xiaomu Shi

#### ▶ To cite this version:

Xiaomu Shi. Certification of an Instruction Set Simulator. Systèmes embarqués. Université de Grenoble, 2013. Français. NNT: . tel-00937524v1

## HAL Id: tel-00937524

https://theses.hal.science/tel-00937524v1

Submitted on 28 Jan 2014 (v1), last revised 28 Jun 2017 (v2)

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique Arrêté ministérial : 7 août 2006

Présentée par

#### Xiaomu SHI

Thèse dirigée par **Jean-François MONIN** et codirigée par **Vania JOLOBOFF**

préparée au sein de VERIMAG et de Mathématiques, Sciences et Technologies de l'Information, Informatique

# **Certification of an Instruction Set Simulator**

Thèse soutenue publiquement le **10 juillet 2013**, devant le jury composé de :

#### M. Yves Bertot

Directeur de Recherche, INRIA Sophia-Antipolis, Examinateur

#### **Mme Sandrine Blazy**

Professeur, IRISA, Rapporteur

#### M. Vania Joloboff

Directeur de Recherche, LIAMA, Co-Directeur de thèse

#### M. Xavier Leroy

Directeur de Recherche, INRIA Rocquencourt, Examinateur

#### M. Laurent Maillet-Contoz

Ingénieur, STMicroelectronics, Examinateur

#### M. Claude Marché

Directeur de Recherche, INRIA Saclay - Île-de-France et LRI, Rapporteur

#### M. Jean-François Monin

Professeur, Université de Grenoble 1 UJF, Directeur de thèse

#### M. Frédéric Rousseau

Professeur, Université de Grenoble 1 UJF, Examinateur

## Table des matières

| Ta           | Table des figures |         |                                                         |      |  |

|--------------|-------------------|---------|---------------------------------------------------------|------|--|

| Li           | ste d             | les tab | oleaux                                                  | vii  |  |

| $\mathbf{A}$ | Abstract          |         |                                                         |      |  |

| $\mathbf{R}$ | ésum              | ıé      |                                                         | 5    |  |

| 1            | Intr              | oduct   | ion                                                     | 7    |  |

|              | 1.1               | Certif  | ication of SimSoC                                       | . 7  |  |

|              | 1.2               | SimSc   | oC                                                      | . 11 |  |

|              |                   | 1.2.1   | Instruction Set Simulation                              | . 12 |  |

|              |                   | 1.2.2   | Performances                                            | . 13 |  |

|              |                   | 1.2.3   | From ARMv5 to ARMv6                                     | . 13 |  |

|              | 1.3               | Outlin  | ne                                                      | . 14 |  |

|              | 1.4               | Relate  | ed work                                                 | . 15 |  |

|              | 1.5               | Contr   | ibutions                                                | . 21 |  |

| 2            | Background        |         |                                                         |      |  |

|              | 2.1               | Opera   | ational Semantics                                       | . 24 |  |

|              | 2.2               | Coq     |                                                         | . 29 |  |

|              |                   | 2.2.1   | Short introduction                                      | . 29 |  |

|              |                   | 2.2.2   | Inductive definitions                                   | . 31 |  |

|              |                   | 2.2.3   | Proofs and tactics                                      | . 32 |  |

|              |                   | 2.2.4   | Interactive proof assistant vs automated theorem prover | . 33 |  |

|              |                   | 2.2.5   | Applications                                            | . 34 |  |

|              | 2.3               | Comp    | OCert                                                   | . 34 |  |

#### TABLE DES MATIÈRES

|   |     | 2.3.1  | CompCert library                     | 36         |

|---|-----|--------|--------------------------------------|------------|

|   |     | 2.3.2  | CompCert C semantics                 | 37         |

| 3 | For | mal m  | odel of ARMv6                        | 41         |

|   | 3.1 | The A  | RM reference manual                  | 41         |

|   | 3.2 | Forma  | lization in Coq                      | 47         |

|   |     | 3.2.1  | Running an instruction               | 49         |

|   |     | 3.2.2  | Decoder                              | 52         |

|   | 3.3 | Exper  | imentations                          | 54         |

| 4 | Sim | ulatio | n of ARMv6 in C                      | <b>5</b> 5 |

|   | 4.1 | Simlig | ht                                   | 55         |

|   | 4.2 | Optim  | nization on Simlight version 2       | 59         |

| 5 | Des | igning | the generation chain                 | 61         |

|   | 5.1 | Archit | ecture                               | 62         |

|   | 5.2 | Analy  | sis of the ARM reference manual      | 63         |

|   | 5.3 | Intern | nediate representation               | 64         |

|   | 5.4 | Code   | generation                           | 66         |

|   | 5.5 | Forma  | ts for C code                        | 67         |

|   | 5.6 | Mistal | kes in the ARM reference manual      | 69         |

| 6 | Cor | rectne | ss proofs                            | 71         |

|   | 6.1 | Gener  | al idea                              | 72         |

|   | 6.2 | The A  | RMv6 model in CompCert C             | 74         |

|   | 6.3 | The p  | rojection                            | 76         |

|   | 6.4 | Proofs |                                      | 80         |

|   |     | 6.4.1  | Proofs for an ARM instruction        | 80         |

|   |     | 6.4.2  | Proof design                         | 86         |

|   |     | 6.4.3  | Proofs for shared library functions  | 88         |

|   |     | 6.4.4  | Proofs on tricky operations on words | 88         |

|   | 6.5 | Tactic | s                                    | 89         |

|   |     | 6.5.1  | Load/store operations                | 89         |

|   |     | 6.5.2  | Outcome of a statement               | 90         |

|   |     | 653    | Function calls                       | 90         |

### TABLE DES MATIÈRES

|         | 6.6                                       | Dealin                                                          | g with version changes of CompCert                                                                                                        |   | 91                                                         |

|---------|-------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------------|

|         |                                           | 6.6.1                                                           | Changes from CompCert-1.9 to 1.10                                                                                                         |   | 91                                                         |

|         |                                           |                                                                 | 6.6.1.1 Volatile types                                                                                                                    |   | 91                                                         |

|         |                                           |                                                                 | 6.6.1.2 Booleans                                                                                                                          |   | 92                                                         |

|         |                                           | 6.6.2                                                           | Changes from CompCert-1.10 to 1.11                                                                                                        |   | 92                                                         |

|         |                                           |                                                                 | 6.6.2.1 Memory model                                                                                                                      |   | 92                                                         |

|         |                                           |                                                                 | 6.6.2.2 Permission guard                                                                                                                  | • | 93                                                         |

| 7       | Des                                       | igning                                                          | our own inversion                                                                                                                         |   | 95                                                         |

|         | 7.1                                       | Why a                                                           | new inversion                                                                                                                             |   | 96                                                         |

|         |                                           | 7.1.1                                                           | Inversion tactic in Coq                                                                                                                   |   | 96                                                         |

|         |                                           | 7.1.2                                                           | Issue from CompCert C semantics                                                                                                           |   | 96                                                         |

|         | 7.2                                       | Design                                                          | of hc_inversion                                                                                                                           |   | 98                                                         |

|         |                                           | 7.2.1                                                           | General design concept and example                                                                                                        |   | 98                                                         |

|         |                                           | 7.2.2                                                           | Using our hand-crafted inversion in SimSoC-Cert                                                                                           |   | 104                                                        |

|         |                                           | 7.2.3                                                           | Comparing $hc_{inversion}$ with Coq built-in inversions                                                                                   |   | 107                                                        |

| 0       | <b></b>                                   |                                                                 |                                                                                                                                           |   |                                                            |

| 8       | Tes                                       | ts gene                                                         | erator for the decoder                                                                                                                    |   | 111                                                        |

| 9       |                                           |                                                                 | a and conclusion                                                                                                                          |   | 111<br>115                                                 |

|         |                                           | cussion                                                         |                                                                                                                                           |   | 115                                                        |

|         | Disc                                      | cussion<br>Using                                                | and conclusion                                                                                                                            | • | <b>115</b><br>115                                          |

|         | <b>Disc</b> 9.1                           | cussion<br>Using<br>Hand-                                       | a and conclusion operational semantics for proving C programs                                                                             |   | <b>115</b><br>115<br>116                                   |

|         | <b>Disc</b> 9.1 9.2                       | cussion Using Hand-                                             | a and conclusion operational semantics for proving C programs                                                                             |   | 115<br>115<br>116<br>117                                   |

|         | 9.1<br>9.2<br>9.3                         | Cussion Using Hand- Develo                                      | a and conclusion operational semantics for proving C programs                                                                             |   | 115<br>115<br>116<br>117                                   |

| 9       | 9.1<br>9.2<br>9.3<br>9.4<br>9.5           | Cussion Using Hand- Develo                                      | a and conclusion operational semantics for proving C programs                                                                             |   | 115<br>116<br>117<br>119                                   |

| 9       | 9.1<br>9.2<br>9.3<br>9.4<br>9.5           | Using Hand- Develo Truste Future                                | a and conclusion operational semantics for proving C programs                                                                             |   | 115<br>116<br>117<br>119<br>119                            |

| 9       | 9.1<br>9.2<br>9.3<br>9.4<br>9.5           | Using Hand- Develor Truste Future n frang                       | a and conclusion operational semantics for proving C programs                                                                             |   | 1115<br>1116<br>1117<br>1119<br>1119<br>1123               |

| 9       | 9.1<br>9.2<br>9.3<br>9.4<br>9.5           | Using Hand- Develo Truste Future  n franç  oduction Certifi     | a and conclusion operational semantics for proving C programs                                                                             |   | 1115<br>1115<br>1116<br>1117<br>1119<br>1123<br>123        |

| 9       | 9.1<br>9.2<br>9.3<br>9.4<br>9.5           | Using Hand- Develo Truste Future n frang oduction Certifi SimSo | a and conclusion operational semantics for proving C programs                                                                             |   | 1115<br>1116<br>1117<br>1119<br>1123<br>123<br>123<br>127  |

| 9       | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>Prsion | Using Hand- Develor Truste Future oduction Certifi SimSo Contri | a and conclusion operational semantics for proving C programs crafted inversion opment size d Code Base e work cation de SimSoC           |   | 1115<br>1116<br>1117<br>1119<br>1119<br>1123<br>123<br>127 |

| 9<br>Ve | 9.1 9.2 9.3 9.4 9.5 ersion Intro          | Using Hand- Develor Truste Future oduction Certifi SimSo Contri | a and conclusion operational semantics for proving C programs crafted inversion opment size d Code Base e work caise n cation de SimSoC C |   | 1115<br>1116<br>1117<br>1119<br>1123<br>123<br>127<br>130  |

#### TABLE DES MATIÈRES

| B Example: the proof script related to instruction ADC | 147         |

|--------------------------------------------------------|-------------|

| Bibliography                                           | <b>15</b> 1 |

## Table des figures

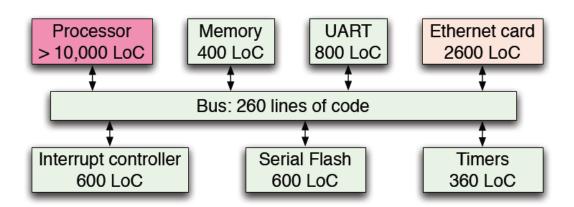

| 1.1 | Development size of SimSoC                                                      | 9  |

|-----|---------------------------------------------------------------------------------|----|

| 2.1 | Syntax of toy language ese                                                      | 26 |

| 2.2 | Big-step operational semantics of the toy language $ese$                        | 26 |

| 2.3 | Small-step operational semantics of the toy language $ese$                      | 28 |

| 2.4 | Some rules for CompCert C operational semantics                                 | 38 |

| 3.1 | ARM processor state                                                             | 42 |

| 3.2 | ARM processor modes                                                             | 43 |

| 3.3 | ADC instruction encoding table                                                  | 44 |

| 3.4 | ADC assembler syntax                                                            | 45 |

| 3.5 | ADC instruction operation Pseudo-code                                           | 46 |

| 3.6 | Formalized decoder of conditional executed instructions                         | 52 |

| 4.1 | ARM Processor state in C                                                        | 56 |

| 4.2 | ARM status register structure in C                                              | 57 |

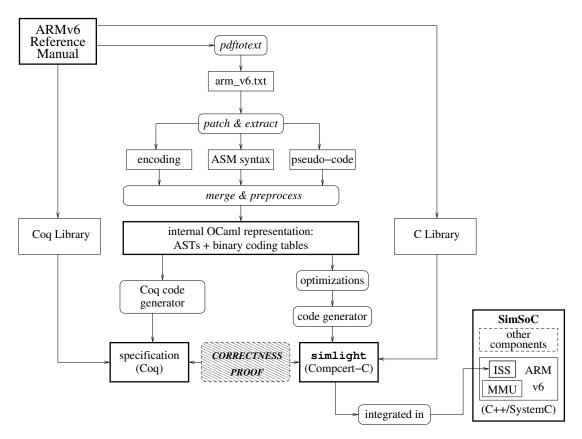

| 5.1 | Overall generation chain                                                        | 62 |

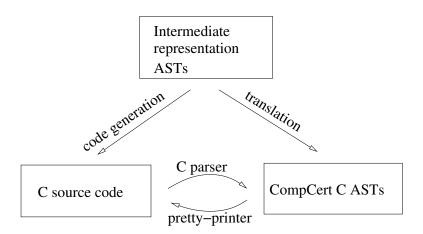

| 5.2 | The abstract syntax of intermediate representation expressions $\dots$ .        | 65 |

| 5.3 | The abstract syntax of intermediate representation statements $\dots$ .         | 66 |

| 5.4 | Flattening the ADC instruction with the shift left by immediate operand         | 67 |

| 5.5 | Generating C code                                                               | 68 |

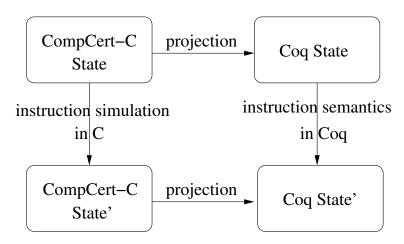

| 6.1 | Main theorem for a given ARM instruction                                        | 73 |

| 6.2 | More accurate theorem statement for a given ARM instruction $\ \ldots \ \ldots$ | 76 |

| 6.3 | Projection                                                                      | 79 |

#### TABLE DES FIGURES

## Liste des tableaux

| 7.1 | Time costs (in seconds)                        |

|-----|------------------------------------------------|

| 7.2 | Size of compilation results (in KBytes)        |

| 8.1 | Generated tests for C decoder                  |

| 9.1 | Sizes (in number of lines)                     |

| 9.2 | ARM instructions having a correctness proof    |

| F.1 | Tailles (en nombre de lignes)                  |

| F.2 | Instructions ARM avec une preuve de correction |

#### LISTE DES TABLEAUX

## Acknowledgements

First and foremost, I would like to express my sincere gratitude toward Prof. Jean-François Monin, my supervisor, for his guidance and kind support. He inspired me greatly during writing my thesis. I sincerely thank Mr. Vania Joloboff and the whole SimSoC-Cert team for rendering their help during the period of the project work. I also wish to give many thanks to my thesis reviewers Prof. Sandrine Blazy and Mr. Claude Marché for their patient reading and constructive suggestions, and to all the other jury members Mr. Yves Bertot, Mr. Xavier Leroy, Mr. Laurent Maillet-Contoz, and Prof. Frédéric Rousseau, who kindly accepted to take part in the jury. It has been a wonderful time and valuable opportunity to work in the FORMES group with people from all over the world sharing their knowledge and ideas. Special thanks to the Dr. Jianqi LI and the others from Tsinghua University for giving me helps in daily life and a good working environment. Last but not least I am grateful to my parents for their supports during my studies.

### Abstract

This thesis introduces the work of certifying a part of a C/C++ program called SimSoC (Simulation of System on Chip), which simulates the behavior of architectures based on a processor such as ARM, PowerPC, MIPS or SH4.

A system on chip simulator can be used for software development of a specific embedded system, to shorten the development and test phases, especially when, as is the case for SimSoC, it offers a realistic simulation speed (about 100 Millions of instructions per second per individual core). Simulation makes it possible to reduce development time and development cost, allowing for co-design engineering, and possibility for the software engineers to run fast iterative cycles without requiring a hardware development board.

SimSoC is a complex software, including about 60,000 lines of C++ code, many complex features from SystemC library, and optimizations to achieve high simulation speed. The subset of SimSoC dedicated to the ARM processor, one of the most popular processor design, somehow translates in C++ the contents of the ARM reference manual, which is 1138 pages long. Mistakes are then unavoidable for such a complex application. Indeed, some bugs were observed even after the previous version of SimSoC, for ARMv5, was able to boot linux.

Then a critical issue is: does the simulator actually simulate the real hardware? In our work, we aim at proving a significant part of the correctness of SimSoC in order to support the claim that the implementation of the simulator and the real system will exhibit the same behavior. Then a SimSoC user can trust the simulator, especially in very critical uses.

We focused our efforts on a critical part of SimSoC: the instruction set simulator of the ARMv6 architecture, which is considered in the current version of SimSoC.

Approaches based on axiomatic semantics (typically, Hoare logic) are the most popular for proving the correctness of imperative programs. However, we prefered to try a less usual but more direct approach, based on operational semantics: this was made possible in theory since the development of an operational semantics for the C language formalized in Coq in the CompCert project, and allowed us to use the comfortable logic of Coq, of much help for managing the complexity of the specification. Up to our knowledge, this is the first development of formal correctness proofs based on operational semantics, at least at this scale.

We provide a formalized representation of the ARM instruction set and addressing modes in Coq, using an automatic code generator from the instruction pseudo-code in the ARM reference manual. We also generate a Coq representation of a corresponding simulator in C, called Simlight, using the abstract syntax defined in CompCert.

From these two Coq representations, we can then state and prove the correctness of Simlight, using the operational semantics of C provided by CompCert. Currently, proofs are available for at least one instruction in each category of the ARM instruction set.

During this work, we improved the technology available in Coq for performing *inversions*, a kind of proof steps which heavily occurs in our setting.

## Résumé

Cette thèse expose nos travaux de certification d'une partie d'un programme C/C++ nommé SimSoC (Simulation of System on Chip), qui simule le comportement d'architectures basées sur des processeurs tels que ARM, PowerPC, MIPS ou SH4.

Un simulateur de System on Chip peut être utilisé pour developper le logiciel d'un système embarqué spécifique, afin de raccourcir les phases des développement et de test, en particulier quand la vitesse de simulation est réaliste (environ 100 millions d'instructions par seconde par cœur dans le cas de SimSoC). Les réductions de temps et de coût de développement obtenues se traduisent par des cycles de conception interactifs et rapides, en évitant la lourdeur d'un système de développement matériel.

SimSoC est un logiciel complexe, comprenant environ 60 000 de C++, intégrant des parties écrites en SystemC et des optimisations non triviales pour atteindre une grande vitesse de simulation. La partie de SimSoC dédiée au processeur ARM, l'un des plus répandus dans le domaine des SoC, transcrit les informations contenues dans un manuel épais de plus de 1000 pages. Les erreurs sont inévitables à ce niveau de complexité, et certaines sont passées au travers des tests intensifs effectués sur la version précédente de SimSoC pour l'ARMv5, qui réussissait tout de même à simuler l'amorçage complet de linux.

Un problème critique se pose alors : le simulateur simule-t-il effectivement le matériel réel ? Pour apporter des éléments de réponse positifs à cette question, notre travail vise à prouver la correction d'une partie significative de SimSoC, de sorte à augmenter la confiance de l'utilisateur en ce similateur notamment pour des systèmes critiques.

Nous avons concentré nos efforts sur un composant particulièrement sensible de SimSoC : le simulateur du jeu d'instructions de l'ARMv6, faisant partie de la version actuelle de SimSoC.

Les approches basées sur une sémantique axiomatique (logique de Hoare par exemple) sont les plus répandues en preuve de programmes impératifs. Cependant, nous avons préféré essayer une approche moins classique mais plus directe, basée sur la sémantique opérationnelle de C : cela était rendu possible en théorie depuis la formalisation en Coq d'une telle sémantique au sein du projet CompCert et mettait à notre disposition toute la puissance de Coq pour gérer la complexitité de la spécification. À notre connaissance, au delà de la certification d'un simulateur, il s'agit de la première expérience de preuve de correction de programmes C à cette échelle basée sur la sémantique opérationnelle.

Nous définissons une représentation du jeu d'instruction ARM et de ses modes d'adressage formalisée en Coq, grâce à un générateur automatique prenant en entrée le pseudo-code des instructions issu du manuel de référence ARM. Nous générons également l'arbre syntaxique abstrait CompCert du code C simulant les mêmes instructions au sein de Simlight, une version allégée de SimSoC.

À partir de ces deux représentations Coq, nous pouvons énoncer et démontrer la correction de Simlight, en nous appuyant sur la sémantique opérationnelle définie dans CompCert. Cette méthodologie a été appliquée à au moins une instruction de chaque catégorie du jeu d'instruction de l'ARM.

Au passage, nous avons amélioré la technologie disponible en Coq pour effectuer des *inversions*, une forme de raisonnement utilisée intensivement dans ce type de situation.

## Chapter 1

## Introduction

#### 1.1 Certification of SimSoC

This thesis describes the work that consists in certifying a part of a C/C++ program called SimSoC (Simulation of System on Chip) (22), which simulates the behavior of embedded systems architectures based on processors such as ARM, PowerPC, MIPS or SH4.

A system on chip simulator can be used for software development of a specific embedded system, to shorten the development and test phases, especially when, as is the case for SimSoC, it offers a realistic simulation speed (about 100 Millions of instructions per second per individual core). Simulation makes it possible to reduce development time and development cost, allowing for co-design engineering, and possibility for the software engineers to run fast iterative cycles without requiring a hardware development board.

Then a critical issue is: does the simulator actually simulate the real hardware? In our work, we aim at proving a significant part of the correctness of SimSoC in order to support the claim that the implementation of the simulator and the real system will exhibit the same behavior. Then a SimSoC user can trust the simulator, especially in very critical uses.

Considering only one module in SimSoC, namely the ARM simulator, it somehow encodes the 1138 pages of the ARM reference manual in C++. The whole simulator, which simulate ARM and PowerPC architecture, includes about 60,000 lines of C++ code. The software is very large and complicated with many complex features from

SystemC library, and optimizations to achieve high simulation speed. The first implementation of SimSoC ARM simulator was manually coded. Then, mistakes in the hand written code are unavoidable and difficult to find due to the complexity. Not only speed, but also accuracy is highly required. All simulated instructions must behave exactly like what is described in the specification (assuming the real hardware is conformant to the specification). From the experiments performed on SimSoC, bugs bringing a wrong behavior were observed from time to time but it was hard to reveal where they were. Using intensive tests can cover most of the instructions, but still left some untested rare cases of instructions, which lead to potential problems.

Therefore, a better approach is required to gain confidence in the correctness of the simulator. Our proposal is to certify the simulator SimSoC using formal methods.

In this thesis, we consider one of the modules in SimSoC: the ARM architecture simulator. ARM architecture is one of the most popular processor design in the embedded systems market, in particular mobile phones and tablets. As reported by ARM Holding company, 6.1 billion ARM-based processors have been brought to the market in year 2010 and 95% is used in the smart phone market.

As mentioned, the simulator is a large amount of software. And the specification itself is rather complex due to the rich architecture of ARM that consists of many components (to be detailed in Chapter 3). Before taking all features of the ARM simulator into account, we decided to focus on the basic parts, which are the most important and sensitive: the CPU part of the ARM architecture (such as used by the ARM11 processor family). At the time we started our work, the ARM simulator module implemented in SimSoC was the ARM Version 5 (ARMv5) architecture. Instead of applying certification for this old architecture, we decided to anticipate the evolution of SimSoC and to work on the next version: ARM Version 6 (ARMv6). For reasons explained below, related to the availability of proof technologies for C (especially CompCert), it was more convenient to have this module written in the C language rather than in C++. This module called Simlight (6) can run standalone, or as a component integrated in SimSoC. It is a simplified executable version of ARMv6 simulator.

More than 60% of the development size of SimSoC is in the CPU part, see Figure 1.1, the remaining parts consists in memory management (virtual memory and paging) interrupt handling and communications with peripherals. In summary, the complexity of the target could be reduced, but it still represents more than 10,000 lines of C code

Figure 1.1: Development size of SimSoC

to be certified. Moreover, the complexity of the specification is invariant, as it is given by a heavy document, the ARM Version 6 Architecture reference manual.

Hence the issue at stake is how to certify a program of this size in relation to a rather complex specification.

Let us first recall that program certification is always based on a formal model of the program under study. Such a formal model is itself derived from a formal semantics of the programming language. For imperative programming languages such as C, a popular approach is to consider tools based on axiomatic semantics (Hoare logic), like Frama-C (12), a framework for a set of interoperable program analyzers for C. Most of the modules integrated inside rely on ACSL (ANSI/ISO C Specification Language), a specification language based on an axiomatic semantics for C. ACSL is powerful enough to express axiomatizations directly at the level of the C program. State labels can be defined to denote a program control point, and can then be used in logic functions and predicates. Frama-C is already quite a mature platform for C program static analysis and automatic deductive verification. An advantage of Frama-C or similar tools is that it is supported by automatic proof technologies, which save manpower consumption and make this approach quite convenient for the user. It was successfully applied to complex and tricky programs, e.g., Schorr-Waite algorithm, which deals with linked data structures.

#### Frama-C is able to perform:

Analyzing the value of variables: Frama-C is able to compute and predict the range of numerical variables.

- Passing the proof obligations, (called *Verification Conditions*, VC for short) generated by Why (7) to automatic or interactive theorem provers.

- Slicing C program into shorter ones which preserve some properties.

- Navigating in C program.

However, in general, high automation tends to weaken the claims for certification, as automatic provers are themselves complex, then error-prone programs. In theory, such programs could produce certificates which could be checked by a reliable (e.g., LCF-based) proof assistant. But currently it is still far from being the case. An additional issue lies in the gap between the axiomatic semantics used and the real implementation, unless the VC generator is itself certified. This issue was considered recently, see below related work by Paolo Herms on WhyCert 1.4 – which was not available at the time we started to work on the certification of SimSoC.

Another important issue is that automation is possible only on theories or logics with limited expressive power. It can make it difficult to express specifications and expected properties at the right abstraction level, especially in a framework where the specification is very complex. Currently, Frama-C implements a superset of first order logic. An important current limitation for us is that ACSL is not able to describe pointer casting. On the contrary, the operational semantics defined for CompCert C (to be introduced below) is able to deal with any type casting.

The Why software is one of the most important components of Frama-C It is an implementation of Dijkstra's calculus of weakest preconditions. Why is the basis of the Jessie front-end, a plug-in of Frama-C which compiles ACSL annotated C code into the Jessie intermediate language. The result is given as input to the VC (Verification Conditions) generator of Why. Why then produces formulas to be sent to both automatic provers or interactive provers like Coq.

Why version 3 is a new and completely redesigned version of Why. It does not yet have its own front-end for C. It has become a standard library of logical theories (integer and real arithmetic, Boolean operations, sets and maps, etc.) and basic programming data structures (arrays, queues, hash tables, etc.). In order to transmit ACSL annotated C code to the Why 3 VC generator, Jessie generates an intermediate code in WhyML, which is a rich language for specification and imperative programming. In the new architecture, the specification language is enriched in order to support additional automatic provers. Furthermore, a formal interface is provided to facilitate the addition

of new external provers. Therefore, choosing Why or Why 3 in our case would make us depend on the transformation chain provided by Jessie and Why together, from ACSL annotated C code to verification conditions for Coq.

In the case of SimSoC, we need to deal both with a very large specification including tricky features of the C language, such as type casting, which are used in tough functions related to memory management. In other words, we need a framework that is rich enough to make the specification manageable, using abstraction mechanisms for instance, in which an accurate definition of enough features of C is available. For the reasons explained above, it was unclear that Frama-C would satisfy those requirements, even with Coq as a back-end. Automated computations of weakest preconditions and range of variation are not relevant in our case. We need to verify more specific properties referring to a formal version of ARMv6 architecture. This specification is quite complex, for instance regarding the major data type to express the processor state (to be defined in Section 4.1).

In order to get the required flexibility and accuracy, we wanted to experiment a more direct approach based on a general proof assistant such as Coq. Fortunately, an operational semantics formalized in Coq of a large enough subset of the C language happened to be available from the CompCert project. We then decided to base our correctness proofs on this technology. Up to our knowledge, this is the first development of formal correctness proofs based on operational semantics, at least at this scale.

#### 1.2 SimSoC

In this section, we introduce our certification target, SimSoC, a Simulator of System-on-Chip that can simulate various processors at a realistic speed. As a simulator of System-on-Chip, its objects are embedded system processors used in modern devices such as consumer electronics or industrial systems (e.g. ARM, PowerPC, MIPS). It is a so called *full system simulator* because it can simulate the entire hardware platform and run the embedded software "as is", including the operating system. Such kind of simulator plays an important role in embedded systems development, because the embedded software can be tested and developed on the simulator. In order to have software and hardware ready for the market at the same time, the software must by developed sometimes before the hardware is available. Then a executable model of the

SoC is required. A simulator also provides additional advantages combining simulation with usage of formal methods such as model checking or trace analysis to discover hardware or software bugs.

Our simulator, SimSoC, works at the low-level of the system. It takes real binary code as input and requires simulation models of the complete board: processor, memory units, bus, network controller, etc. It can emulate the behavior of instruction executions, exceptions, and peripheral interrupts. Other than software development, it may be used also for hardware design. When there are additional components provided by a third party, the software developers can test them in the full simulation environment with modularity.

SimSoC is developed in SystemC, which is itself a C++ library, and uses transaction level modeling (TLM) to model communications between the simulation modules. In order to simulate processors with a reasonably high speed, the instruction set simulation uses a technique named dynamic translation, which translates the binary input into an intermediate representation that is itself compiled into host code. Since SimSoC is a rather large and complex framework that influences the development of both hardware and software, we have to understand the most significant parts in order to be able to decide the certification object.

#### 1.2.1 Instruction Set Simulation

A full system simulator must include the instruction set simulator, which reads the instructions of the program and exactly emulates the behavior of the target processor. In order to illustrate our certification target, we detail here the techniques to implement an instruction set simulator. There are three kinds of techniques implemented for SimSoC instruction simulation, that make trade-offs between accuracy and efficiency. They are: interpretive simulation, dynamic translation with no specialization, and dynamic translation with specialization. The interpretive simulation is the classical method, it includes the three stages: fetching, decoding and executing instructions. Although it is slow because of multiple redundant decoding phases, it is simple to implement and reliable. It is also used as the reference of performance for the other two techniques. The second and the third methods are based on dynamic translation, which uses an intermediate representation as the decoding result. Such intermediate representations of decoded instructions are stored into a cache and are re-used when

the same instructions are to be re-executed. The last method dynamic translation with specialization combines dynamic translation with partial evaluation. Partial evaluation specialization is a well known technique to optimize compilation of programs. The idea is to translate a program P which applies on data d into a faster specific program Pd. One can use partial evaluation in simulation to specialize one instruction into a simpler instruction, based on data known at decoding time. The SimSoC decoder implements partial evaluation. At decoding time, the dynamic translation maps the binary instructions to their partial evaluation specializations. Although specialization of instructions results into more memory usage, it is reasonable small compared to the memory size available on host machines nowadays.

The technologies used in SimSoC instruction set simulation are detailed in (23).

#### 1.2.2 Performances

The ARM module of SimSoC used to implement the ISS of ARMv5 architecture was manually coded. The simulator is able to simulate the commercial System-on-Chip SPEAr Plus600 circuit from ST Microelectronics which is a dual core system based on over forty additional components, as well as the Texas Instruments AM1705 circuit. The simulator is able to emulate the interrupt controller, the memory controller, the serial memory controller, the Ethernet controller, and all peripherals which are necessary to boot Linux. Therefore, running the Linux kernel on the SPEAr Plus simulator module is a way of testing and debugging the simulator. First it reads the compressed Linux kernel binary from serial memory, uncompresses it, then starts Linux. The booting process takes only several seconds. The Ethernet controller can connect several simulators of the same SoC running on the same machine or not, through TCP/IP protocol. In SimSoC, a mature simulator for the ARMv5 architecture has been completed before starting our project, and two instruction set simulators for PowerPC and MIPS were also developed.

#### 1.2.3 From ARMv5 to ARMv6

For this thesis, we decided to consider the next version (ARMv6) of the ARM architecture, which represented a step up in performance from ARMv5 cores. ARMv6 is essentially backward compatible with ARMv5. Here are the new features of ARMv6 architecture.

- The instruction set has been enlarged with extra instructions in six areas: media instruction, multiply instruction, control and DSP instruction, load/store instruction, architecture undefined instruction, and unconditional instruction. Fortunately, all ARMv5 mandatory instructions are ARMv6 mandatory instructions too. For simulator users, application code compiled with compilers for ARMv5 can be run over the ARMv6 simulator. If application users want to benefit from the new V6 instructions, they need to re-compile the code in the new environment.

- The Thumb mode has changed. Thumb instructions of ARMv5 are not portable to Thumb2 (ARMv6+), nor completely backwards compatible.

#### 1.3 Outline

In summary, our goal is to certify (a part of) SimSoC, a system on chip simulator, using a framework based on the operational semantics of C formalized in Coq, and Coq itself. This thesis explains our achievements in this respect. Subsection 1.4 discusses relevant projects which use formal methods in the area of hardware processors, and why we need a new approach in our experiment. The contributions of our work are outlined in Subsection 1.5. Next, Chapter 2 provides the background on the main technologies used in our project, including a brief introduction to operational semantics, to Coq, and to the CompCert project. Our certification basis is the formal model of the ARMv6 instruction set simulator, which is described in Chapter 3. Then the certification target, a C program for simulating the ARMv6, is introduced in Chapter 4. The next chapter explains how repetitive and potentially error-prone tasks in the production of the two previous models are automated (Chapter 5). Chapter 6 describes how correctness proofs are carried out. In order to improve the performance and the management of the proofs, we had to develop a key proof technique for the "inversion" of assumptions related to the operational semantics of C expressions, which is described in Chapter 7. Chapter 8 is dedicated to an additional work using exhaustive testing for checking the coverage and correctness of the simulator decoder. Then we conclude in Chapter 9 and outline future research prospects.

#### 1.4 Related work

The main difference between SimSoC-Cert (the certification of SimSoC) and the following projects is that we aim at proving the correctness of a hardware simulation whereas the target of the others is a certified hardware. The common point is that we need a formal specification of the instruction set of a specific processor architecture. Different proof assistants have been used to perform the certification on the formal model itself: Coq in our case; ACL2, HOL, etc. in other experiments. In our project, the formalization of the real chip ARMv6 is used as a reference for the behavior of an ARMv6 simulator written in C.

#### Using ACL2 for embedded systems

Researchers from Computational Logic, Inc., used ACL2 (A Computational Logic for Applicative Common Lisp) or Nqthm (Boyer-Moore Theorem Prover) (8) to specify and prove properties of several commercial processors as summarized in (10). ACL2 is a software system consisting of a programming language, an extensible theory in a first-order logic, and a mechanical theorem prover. It can act as both an automatic theorem prover and an interactive proof assistant. It supports automated reasoning in inductive logical theories, which is convenient for both software and hardware verification. Its programming language is a side-effect free extension of Common Lisp. And it is untyped. The base theory of ACL2 axiomatizes its programming language semantics and its built-in functions. User definitions in ACL2 programming language that satisfy a definitional principle extend the theory in a way that maintains the theory's logical consistency. The core of ACL2's theorem prover is based on term rewriting, and it is extensible in the following way: theorems discovered by the user can be used as ad-hoc proof techniques for subsequent conjectures.

Nqthm is a theorem prover sometimes referred to as the Boyer–Moore theorem prover. ACL2 system is essentially a re-implemented extension of Nqthm. We consider projects based on them together.

ACL2 and Nqthm are used to deal with different processor models in several projects. Among them, the work for Motorola's MC68020 is very close to ours (9). A large part of the user programming model of the MC68020 microprocessor is formalized as an abstract machine and its instruction operation as state transitions according

to its user's manual, which is similar to what we did for ARMv6. But the specification in Nqthm is formalized by hand; no automatic generator is used. The formal specification of the instruction set is defined in a functional way, as in our case. The target is the object code itself, considering that industrial strength compilers are not completely reliable; indeed, a certified compiler generating a machine code which is strictly equivalent to a high-level code was not available at that time. To keep the formalized system deterministic, they abandoned the instructions which may cause an undefined effect on the machine state. Comparing to this, we formalized our ARMv6 processor state differently in order to consider all the ARM instructions, including those instructions which produce an undefined state (see Section 3.2.1). The specification is written in the logic of Nqthm and proofs are obtained using the Nqthm fully automatic theorem prover, which cannot interact with the user once it is started. This is totally different from the Coq proof assistant we used, where proofs are designed in constant interaction with the user. The main theorems state that the execution of object code terminates and the returned machine state is considered normal, that all registers are set to the right location and that the effect of the execution is only on the relevant memory blocks.

The use of fully automatic theorem provers like Nqthm requires less man-power on theorem proving but much work on the specification. Once the formalization and the stated theorems are put in Nqthm logic system, we expect the automatic prover to do the rest. With this technique the object code produced by GNU C compiler for hundreds lines of C could be mechanically verified.

Still, the gap between C and the GNU C produced object code is not solved, because the GNU C compiler can not be considered fully trusted. So this method cannot be used for providing results which would be meaningful (and conveniently expressed) at the level of a C program.

Another project used ACL2 on the object processor CAP from Motorola company. The full ALU and I/O system of CAP is formalized in ACL2. The CAP implementation is a three-stage instruction pipeline; an appropriate correspondence between the CAP model with pipe-line and a simpler pipeline-free one is proven. Also the implemented DSP algorithm FIR (Finite Impulse Response) is proved to be equivalent to the formal specification. Moreover, the basic library for ACL2 on data structure was enriched, for example with array, list, record, bit vector, etc. New modules on modular arithmetic,

integers, hardware operations, and so on were built. These developments are reusable by other projects because the definitions are not specific to the CAP model.

A very recent work used ACL2 for developing a significant subset of X86 instruction set (19). The formal model of the X86 processor is executable and can run some binary programs. Some small binary programs are automatically verified under ACL2's interactive theorem proving environment using a symbolic execution technique.

#### Formalized x86 in Coq

In a recent work done in a cooperation between Harvard University, Lehigh University, NSF, and Google, a model of x86 has been formalized in Coq (41). The whole project is called Native Client (NaCl). It is a platform allowing Google's Chrome browser users to execute native code on the browser. A sandbox policy is used to ensure several properties. The most important ones are to ensure that read/write operation on arbitrary memory blocks are only caused by trusted code, instructions related to system calls are avoided, and communication can only happen within well-defined entry points. These properties of the sandbox policy protect the system from bugs or concurrent access to memory. The aim of this work is to obtain a highly trusted assurance checker for the sandbox policy. A checker for a 32-bit x86 (IA32) processor without floating-point instructions, RockSalt was built. This new achievement is better than the original version provided by Google in three aspects: it is faster, lighter, and more flexible.

This project has some similarities with ours: the core of RockSalt was automatically generated from the Coq formal specification using extraction to OCaml code; then it was manually translated in C language in order to have an implementation for NaCl. A new Coq model for x86 was defined. In the future, it is expected to support reasoning about the behavior of x86 machine code using a verified compiler such as CompCert. RockSalt relies only on a DFA (Deterministic Finite-state Automaton) encoding table and some trusted C code. The checker is extremely fast: 1M instructions can be checked within one second. Also, it has a small run-time trusted computing base and can be integrated into NaCl runtime easily. The formal model of x86 ISS (Instruction Set Simulator) has the same architecture as a translator: a decoder from binary code to an abstract syntax, a compiler from this abstract syntax to RTL instructions; and an interpreter for RTL instructions. Because no predefined formal model could be

considered as a trust-base, tests were created for this complex model, in order to gain confidence.

For validation, an executable OCaml model is extracted from the Coq specification, and the behavior of the OCaml model is compared with the real x86. More than ten million binary instructions could be simulated in around sixty hours on Intel Xeon. Moreover, fuzz tests are used to cover problems that cannot be considered by the previous tests. Fuzz test can cover all forms of one kind of instruction, and all of them can be exercised. The Coq processor model in this project is essentially an intermediate specification which is used to obtain more secure C code. However the manual translation from extracted OCaml code to C is not explained in (41). Tests are only used at the level of OCaml code. Altogether, it is unclear that the resulting C code has the same behavior as the Coq specification.

#### An instruction set generator for an ideal processor

A German project describes in (28) an Instruction Set Simulator generation technique which aims at generating an efficient ISS from the RTL (Register Transfer Level) description. The ITL (Iterative Temporal Logic) language is used to design the ISS at the RTL level, then C++ code is generated from it. The interval temporal logic is a combination of temporal logic and first-order logic able to deal with sequential and parallel composition. It includes a notion of finite sequences. First order interval logic was first designed for formalizing and verifying hardware protocols. It is sufficient for specifying computer-based systems, both hardware and software. Some of the standard operations of VHDL or Verilog language can be expressed as temporal logic expressions to describe the behavior of a synchronous sequential system.

The verification of safety properties is performed using a technique called IPC (Interval Property Checking) which is designed to check if a model satisfies a set of properties written in a dedicated verification language, ITL in this case. The main idea followed here is to use an arbitrary initial state instead of the initial state of BMC (Bounded Model Checking). Any property that holds from an arbitrary initial state also holds from any reachable state. Conversely, false negatives can occur in IPC. These false negatives need to be removed by adding invariants in order to restrict the set of initial states. In order to gain speed for simulation, optimizations are performed on the C++

code generation like in any other state-of-the-art simulators by the following two methods: first, arithmetic and simple logic operation are mapped to corresponding native C++ operations; second, additional variables are used to store temporary results and to cache intermediate results of computations. The formal verification aims at proving the equivalence between RTL and ISA models. The main idea of the equivalence proof is very similar to ours (see Chapter 6): it is based on a mapping from the RTL state representing CPU to the corresponding ISA state in C, and on next-state transitions for both the RTL model and the ISA model of the C program. Proving that the interface signals of the design is correctly implemented is also performed in the same way. For code generation, the input source is specified in VHDL. The first experiment was achieved on an invented ideal simplified CPU model. It contains eight 16-bit registers and a special register used as interrupt return vector. There are only seven instructions for logic, arithmetic, memory accessing, and jump. For the second experiment, an industrial processor design was chosen. It contains 64 32-bits registers and 88 instructions based on the DLX instruction set architecture and a memory model with simple interface. This corresponds to 10,000 lines of VHDL code, reformulated into a 2000 lines ITL specification to be used as the source of the C++ code generator. Compared to SimSoC, the size of the formal specification is smaller and with ITL specifications, less properties can be expressed and proved than with Coq.

## A trustworthy monadic formalization of ARMv7 instruction set architecture

The computer laboratory in Cambridge University used HOL4 to formalize the instruction set architecture of ARMv7 (17). The target here was to verify an implementation of this architecture with *logical gates*, whereas for SimSoC, we consider a simulation written in C. Reusing the work done at Cambridge was considered for SimSoC. However, as our approach is based on CompCert, which is itself written in Coq instead of HOL4, it was more convenient to write our own specification. The achievements obtained at the Cambridge projects are:

- A model of the ARM instruction set architecture in the HOL language. Other than ARMv7 instruction set which is backward compatible with previous versions, the model considered here has the full support for the Thumb-2 instruction set, too.

- Additional software for simulation, an assembler, and a disassembler in ML.

- Automatic extraction of single step theorems from a monadic representation of a single ARM instruction, for evaluation.

- Besides the tools and specifications formalized or derived inside HOL logic, some other tools that are outside HOL logic: the assembly code parser, the disassembler, and the encoder. They are considered not completely reliable.

- The formalized model can operate on machine code level.

- The execution results are used for comparison with the real hardware in order to validate the model.

The instructions have been grouped together with related ones. This reduces greatly the specification size. But the HOL 4 model is a little too precise. For example, it specifies the resource accessing order when updating the PC. But this order is not specified in the reference manual. During validation, three boards are used to assess the execution results. And the tests are generated randomly by a test generator. Additional confidence in this development was achieved by observing the behavior of verified code, and running the model on ARM code that calculates a non-trivial known function. Some weaknesses are: storing instructions are not completed; problems happen when updating on registers PC or SP occur; exceptions are not well handled; tests do not cover unpredictable and undefined instruction, which have been filtered in test generation; the model does not include the privileged mode, nor the instruction changing the current processor mode; implementation dependence or system features cannot be fully tested.

#### WhyCert: A certified implementation of VC generator

Paolo Herms's Ph.D thesis (24) (25) provides a certified verification condition generator for several provers, called WhyCert. The work is also based on CompCert C operational semantics. Using a VC generator is another way of ensuring the safety requirements of programs written in high-level programming languages, as mentioned in Section 1.1, as well as the importance of certifying a VC generator. In WhyCert, the VC generator was implemented and proved sound in Coq, then extracted to an executable OCaml program. As suggested by the name WhyCert, this work is inspired by Why (16), a platform for deductive program verification. To make it usable with arbitrary theorem provers as back-ends, it is generic with respect to a logical context, containing

arbitrary abstract data types and axiomatisations. This is suitable to formalized memory models needed to design front-ends for mainstream programming language, as it is done for C by VCC above Boogie or by Frama-C/Jessie above Why. The inputs are imperative programs written in a core language which operates on mutable variables which are typed in the logical context. The output is made of logic formulas which are built upon the same logical context.

#### The seL4 project

The NICTA company provides a secured microkernel seL4 (27), a member of L4 microkernel family. The formal verification is based on the interactive theorem prover Isabelle/HOL. The correctness proofs are established according to a correspondence between an abstract and a concrete representations of the seL4 system. The concrete model is the C implementation, which is translated to Isabelle using a intermediate language called com, which has an operational semantics like CompCert C. However this language handles a smaller subset of C than CompCert C. Unsupported features of com that are supported in CompCert C include:

- pointers to automatic storage

- float, function pointer, union

- switch, goto, break, continue

Note that for SimSoC, we need function pointer, switch, break.

#### 1.5 Contributions

In this work we developed a correctness proof of a part of the hardware simulator SimSoC. This is not only an attempt to certify a simulator, but also a new experiment on the certification of non-trivial programs written in C. In our approach, we do not use the popular axiomatic semantics, but the C operational semantics defined by the CompCert project.

We provide a formalized representation of the ARM instruction set and addressing modes in Coq, using an automatic code generator from the instruction pseudo-code in the ARM reference manual. We also generate a Coq representation of a corresponding simulator in C, called Simlight, using the abstract syntax defined in CompCert. The

text version of Simlight was previously developed as a component of SimSoC by C. Helmstetter (6).

From these two Coq representations, we can then state and prove the correctness of Simlight, using the operational semantics of C provided by CompCert. Our first achievement in this direction was described in (50). Currently, proofs are available for at least one instruction in each category of the ARM instruction set.

During this work, we improved the technology available in Coq for performing *inversions*, a kind of proof steps which heavily occurs in our setting (40).

Additional contributions include a generator of a decoder for ARM instructions, also based on the analysis of the ARM reference manual, and a test generator for the instruction decoder, which can generate massive tests covering all ARM instructions.

## Chapter 2

## Background

This chapter provides a short introduction to the scientific background of our work: operational semantics, to define the meaning of programs; the Coq proof assistant, which is used to define the formal model of ARMv6 architecture and to perform correctness proofs; finally CompCert, which contains an operational semantics of C formalized in Coq, and is then the basis of the formal model that we use for the instruction set simulator Simlight. We pay a particular attention on underspecified behaviours: this happens when different compilation strategies may provide different behaviours for the same program, as is the case for C. Such issues are illustrated on a very simple toy language, ese.

#### Résumé

Ce chapitre contient une courte introduction au cadre scientifique dans lequel notre travail a été developpé. On commence par quelques notions de sémantique opération-nelle, permettant de définir la signification des programmes. On présente ensuite l'assistant à la preuve Coq, que nous avons utilisé pour définir notre modèle formel de l'architecture ARMv6 et d'effectuer des preuves de correction. Nous terminons par CompCert, qui fournit notamment une sémantique opérationnelle de C formalisée en Coq – c'est l'ingrédient essentiel que nous utilisons pour produire un modèle formel du simulateur d'instructions Simlight.

Une attention particulière est portée aux comportement sous-spécifiés : cela se produit lorsque différentes stratégies de compilation peuvent aboutir à des comportements

#### 2. BACKGROUND

différents pour un même programme, ce qui est le cas avec le langage C. Pour illustrer ce genre de problèmes, nous introduisons un langage jouet, *ese*, contenant des expressions avec effet de bord.

#### 2.1 Operational Semantics

In computer science, there are three traditional ways to express how programs perform computations: axiomatic semantics, denotational semantics, and operational semantics. Formal semantics are important because it can give an abstract, mathematical, and standard interpretation of a programming language. It helps to understand what a program written in this language does and to verify what we expect from the program. In a few words:

- Denotational semantics constructs mathematical objects which describe the meaning of expressions of the language using stateless partial functions. All observably distinct programs have distinct denotations.

- Operational semantics is more concrete because it is based on states. However, in contrast with a low-level implementation, operational semantics considers abstract states. The behavior of a piece of program corresponds to a transition between abstract states. This transition relation allows us to define the execution of programs by a mathematical computation relation. This approach is quite convenient for proving the correctness of compilers, using operational semantics for the source and target languages (and, possibly intermediate languages). Operational semantics is used in CompCert to define the execution of C programs, or more precisely programs in the subset of C considered by the CompCert project. The work presented in this thesis is based on this approach.

- Axiomatic semantics describes the effect of programs by assertions. A well-known example is Hoare logic. It is one of the most popular approaches for proving the correctness of programs.

A good tutorial on programming language semantics is Benjamin C. Pierce's *Software Foundation*<sup>1</sup>. It is mainly dedicated to operational semantics and it contains an introduction to Hoare Logic. The material presented in this tutorial is formalized in

<sup>1.</sup> http://www.cis.upenn.edu/ bcpierce/sf/

the Coq proof assistant. Another interesting introduction can be found in (42). It is more detailed than *Software Foundation*, but it is not supported by a proof assistant.

Operational semantics can be used to reliably prove results on a programming language. Operational semantics can be presented in two styles. Small-step semantics, often known as structural operational semantics, is used to describe how the single steps of computations evaluate. The other is big-step semantics, or natural semantics, which returns the final results of an execution in one big step. The corresponding transition relation is defined by rules, according to the syntactic constructs of the language, in a style which is inspired by natural deduction.

The book (42) explains that the choice between small-step semantics and big-step semantics depends on the objective. They sometimes can be equivalent. But in general, they provide different views of the same language and we have to choose an appropriate one for a particular usage. Moreover, some language constructs can be hard or even impossible to define with one of these semantics whereas it is easy with the other style. In general, when big-step semantics can be used, it is simpler to manage than small-step semantics.

In order to illustrate some issues on operational semantics and its different flavors which are important for us, let us consider a simple language called *ese*, for expressions with side-effects. This language allows us to present some typical issues of C language, related to the the evaluation order of expressions and statements. The ISO-C standard that mentions the evaluation order of expressions with side-effect on the same object is undefined, for example:

```

i = ++i + 1;

a[i++] = i;

```

Several orders are allowed for each of the previous assignments, because they include two side effects on variable i – according to ISO-C standard, there are two "sequence points" in them.

Other examples are given by Brian Campbell in the CerCo project (11), in order to show that the evaluation order constraints in C are very lax and not uniform.

```

x = i++ && i++;

x = i++ & i++;

```

#### 2. BACKGROUND

Our toy language ese is designed to illustrate similar issues. The constructs of ese are: constants C n, where n is a natural number, a unique variable V, the addition P ese ese of two arguments of type ese, and the assignment of the variable with a value expressed by an ese. Its abstract syntax is as follows.

$$ese ::= C n \mid V \mid P ese ese \mid A ese$$

Figure 2.1: Syntax of toy language ese

The semantics in big-step style is inductively defined using the following rules. The parameter state of type natural number is introduced here to store the current value of V. After an evaluation, a new state is returned. The evaluation takes an initial state and an expression to compute, and returns a new state and a natural number which is the evaluation result. The notation  $\xrightarrow{bs}$  means "evaluates to".

$$\frac{}{st, C n \xrightarrow{bs} st', n} \tag{2.1}$$

$$\frac{}{st, \ V \xrightarrow{bs} st, \ st} \tag{2.2}$$

$$\frac{st, e_1 \xrightarrow{bs} st', n_1 \qquad st', e_2 \xrightarrow{bs} st'', n_2}{st, P e_1 e_2 \xrightarrow{bs} st'', (n_1 + n_2)}$$

$$(2.3)$$

$$\frac{st, \ e \xrightarrow{bs} \ st', \ n_1 \qquad n_1, \ V \xrightarrow{bs} \ st'', n_2}{st, \ A \ e \xrightarrow{bs} \ st'', \ n_2}$$

(2.4)

Figure 2.2: Big-step operational semantics of the toy language ese

Rule 2.4 is for assignment. A simpler and equivalent version is:

$$\frac{st, \ e \xrightarrow{bs} st', \ n}{st, \ A \ e \xrightarrow{bs} n, \ n}$$

(2.5)

The version given in rule 2.4 is closer to the small-step semantics to be presented later, which exposes an explicit evaluation order. To this effect, the assignment is split into two parts: evaluating the right-hand side then putting the result into the left-hand side.

For instance, from the state where V contains 0, the expression in C syntax

$$V + ((V = 1) + (V = 2))$$

evaluates to 3, with a final state where V contains 2. This expression is formalized by the term PV(P(A(C1))(A(C2))), and the previous statement is formalized by:

$$0, P V (P (A (C 1)) (A (C 2))) \xrightarrow{bs} 2, 3.$$

This statement is proved by systematic applications of the rules given in Figure 2.2. The proof is driven by the shape of the expression. Each constructor (C, V, P, A) is handled by a specific rule and leads to premises with smaller expressions (in this language), which means that the execution will terminate for any expression. Moreover, the semantics defined here is deterministic; the evaluation order is leftmost and innermost. This is expressed by the following lemma:

**Lemma 2.1.** If

$$st$$

,  $t \xrightarrow{bs} st'v$ , and  $st$ ,  $t \xrightarrow{bs} st''v'$ , then  $v = v'$  and  $st = st''$ .

Using big-step semantics, we can also describe a non-deterministic system by adding one rule for right to left evaluation to offer another evaluation order:

$$\frac{st, e_2 \xrightarrow{bs} st', n_2 \qquad st', e_1 \xrightarrow{bs} st'', n_1}{st, P e_1 e_2 \xrightarrow{bs} st'', (n_1 + n_2)}$$

$$(2.6)$$

Then the output of the evaluation cannot be predicted: the same expression can return different states and results. For instance, we have

$$\begin{array}{c} 0, P \; V \; (P \; (A \; (C \; 1)) \; (A \; (C \; 2))) \xrightarrow{bs} 2, 3 \\ 0, P \; V \; (P \; (A \; (C \; 1)) \; (A \; (C \; 2))) \xrightarrow{bs} 1, 3 \\ 0, P \; V \; (P \; (A \; (C \; 1)) \; (A \; (C \; 2))) \xrightarrow{bs} 2, 5 \\ 0, P \; V \; (P \; (A \; (C \; 1)) \; (A \; (C \; 2))) \xrightarrow{bs} 1, 4 \end{array}$$

Next, the following description gives the small-step operational semantics rules of the same toy language. This time, the small-step rules take an expression of type ese and the initial state which stores the current value of variable V, and return the reduced expression and the new state. The symbol  $\xrightarrow{ss}$  means "reduces to in one small step".

In small-step semantics, two rules ((2.9) and (2.10)) are needed to define the leftmost and innermost evaluation order. And there is no rule for reducing a single constant. From the number of rules, we see that the definition of deterministic computations with a given evaluation order is more complex with small-step operational semantics than with big-step semantics.

$$\frac{}{V. st \xrightarrow{ss} (C st). st}$$

(2.7)

$$\frac{}{(P(C n_1)(C n_2)), st \xrightarrow{ss} (C(n_1 + n_2)), st}$$

(2.8)

$$\frac{e_1, st \xrightarrow{ss} e'_1, st'}{(P e_1 e_2), st \xrightarrow{ss} (P e'_1 e_2), st'}$$

$$(2.9)$$

$$\frac{e_2, st \xrightarrow{ss} e'_2, st'}{(P(C n_1) e_2), st \xrightarrow{ss} (P(C n_1) e'_2), st'}$$

$$(2.10)$$

$$\frac{}{(A\ (C\ n)),\ st \xrightarrow{ss}\ V,\ n} \tag{2.11}$$

$$\frac{e, st \xrightarrow{ss} e', st'}{(A e), st \xrightarrow{ss} (A e'), st'}$$

(2.12)

Figure 2.3: Small-step operational semantics of the toy language ese

We can also have a non-deterministic small-step semantics by modifying one of the rules of the plus operation to remove the leftmost and innermost order: changing rule (2.10) in Figure 2.3 into:

$$\frac{e_2, st \xrightarrow{ss} e'_2, st'}{(P e_1 e_2), st \xrightarrow{ss} (P e'_1 e_2), st'}$$

$$(2.13)$$

Considering the set of possible executions allowed by the non-deterministic semantics, we have more results by using small-step semantics than using big-step semantics. Taking the same example  $P \ V \ (P \ (A \ (C \ 1)) \ (A \ (C \ 2)))$  as above, the possible executions in small-step semantics are:

$$0, P \ V \ (P \ (A \ (C \ 1)) \ (A \ (C \ 2))) \xrightarrow{ss} 3, 1$$

$$0, P \ V \ (P \ (A \ (C \ 1)) \ (A \ (C \ 2))) \xrightarrow{ss} 3, 2$$

$$0, P \ V \ (P \ (A \ (C \ 1)) \ (A \ (C \ 2))) \xrightarrow{ss} 4, 1$$

$$0, P \ V \ (P \ (A \ (C \ 1)) \ (A \ (C \ 2))) \xrightarrow{ss} 5, 2$$

$$0, P \ V \ (P \ (A \ (C \ 1)) \ (A \ (C \ 2))) \xrightarrow{ss} 6, 2$$

The last result is obtained by performing the assignment A (C 1), then the assignment A (C 2); at this point, the value stored in the state equals 2. Next, performing plus in any order will compute the result of 6 and the state still stores 2. On the other hand, the big-step semantics fails to express that 6 can be returned.

In contrast with big-step semantics, the sequence corresponding to an assignment (evaluation the right-hand side, then putting the result into the left-hand side) can actually be interrupted when we consider small-step semantics, and the evaluation of another sub-expression can then occur.

In general, big-step semantics is not the right approach for dealing with nondeterministic executions or under-specified semantics, because it is not able to cover all the possible execution cases.

Note that CompCert includes a big-step deterministic semantics and a small-step non-deterministic semantics for CompCert C.

## 2.2 Coq

#### 2.2.1 Short introduction

Coq(5) is an interactive theorem prover, implemented in OCaml. It allows the expression of mathematical assertions, mechanically checks proofs of these assertions, helps to find formal proofs, and extracts a certified program from the constructive proof of its formal specification. Coq can also be presented as a dependently typed  $\lambda$ -calculus (or functional language). Here we just illustrate the syntax on simple examples. For a detailed presentation, the reader can consult (13) or (5).

- $-fun\ (n:nat) \Rightarrow n$  is the identity function on natural numbers; its type is written as  $nat \rightarrow nat$ . Function application is not written as f(x) but f(x) or f(x) if grouping is needed. With several arguments, the syntax is f(x) or f(x) instead of f(x).

- We can write definitions as follows:

Definition idn := fun (n: nat)

$$\Rightarrow$$

n.

An equivalent and more common syntax for this definition is:

```

Definition idn (n : nat) := n.

```

For instance, the application of idn to 3 is written (idn3) and this term reduces to 3.

#### 2. BACKGROUND

-  $fun(X:Type)(n:X) \Rightarrow n$  is the polymorphic identity function on an arbitrary type X; its type is written  $\forall X:Type, X \rightarrow X$ .

Note that it expects 2 arguments, for instance, we can write  $(id \ nat \ 3)$ . Like most of functional programming languages, Coq can also perform type inference. If we define id as following:

Definition id

$$\{X : Type\} (n : X) := n.$$

The application can be just written as id 3. Coq can get the explicit X from the type of 3.

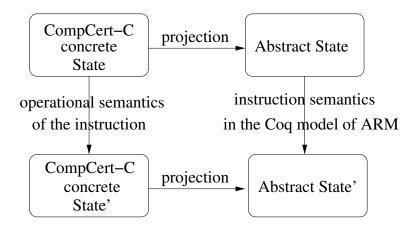

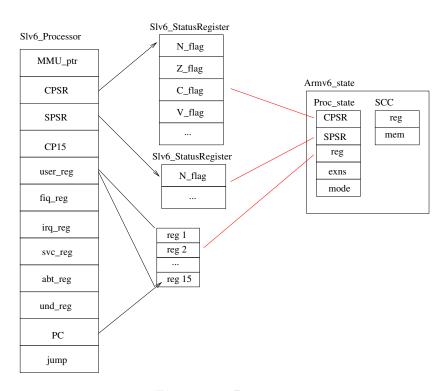

- A dependent type is a type that depends on a value. It is very flexible to use, as to refine the type of a function without including the whole specification. A very simple example is to define a predecessor with only the rule for case 0: