# Transport properties and functional devices on CVD grown Silicon nanowires

Massimo Mongillo

#### ▶ To cite this version:

Massimo Mongillo. Transport properties and functional devices on CVD grown Silicon nanowires. Mesoscopic Systems and Quantum Hall Effect [cond-mat.mes-hall]. Université Joseph-Fourier - Grenoble I, 2010. English. NNT: . tel-00939480

#### HAL Id: tel-00939480 https://theses.hal.science/tel-00939480v1

Submitted on 30 Jan 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour l'obtention du grade de

Docteur de l'université de Grenoble

Discipline: Physique, nanophysique

# Transport properties and functional devices on CVD grown Silicon nanowires

présenté et soutenue publiquement le 15 octobre 2010

par

#### Massimo MONGILLO

Composition du jury : Mikael Björk Rapporteur

Renaud Leturcq Rapporteur

Laurent Saminadayar Président

Marc Bescond Examinateur

Marc Sanquer Directeur de thèse

Silvano de Franceschi Directeur de thèse

Laboratoire de transport électronique quantique et supraconductivité Service de physique statistique, magnétisme et supraconductivité Institut Nanosciences et Cryogénie CEA Grenoble

Per Mamma

# Contents

| Fo | orewo | ord                                                                     | 7         |

|----|-------|-------------------------------------------------------------------------|-----------|

| In | trod  | uction                                                                  | 9         |

| 1  | Dev   | rice fabrication                                                        | 14        |

|    | 1.1   | Nanowire growth                                                         | 14        |

|    | 1.2   | Electron beam and optical lithography                                   | 15        |

|    | 1.3   | Metal Silicides                                                         | 18        |

|    |       | 1.3.1 Self aligned silicide                                             | 18        |

|    |       | 1.3.2 Ni-Si solid state reaction                                        | 20        |

|    |       | 1.3.3 Silicidation in silicon nanowires                                 | 21        |

|    |       | 1.3.4 Control of the silicidation process                               | 23        |

| 2  | Cor   | atacts on Silicon nanowires.                                            | 30        |

|    | 2.1   | The Schottky barrier                                                    | 30        |

|    | 2.2   | Undoped Silicon nanowires: impact of the silicidation on the electrical |           |

|    |       | properties                                                              | 33        |

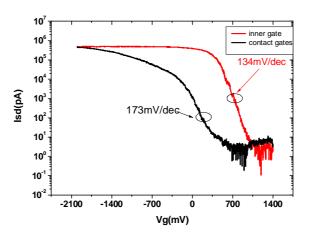

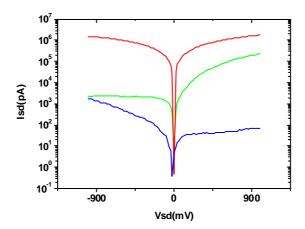

|    | 2.3   | Transport properties of multigated Schottky barrier transistors         | 33        |

|    | 2.4   | Bulk and contact switching                                              | 37        |

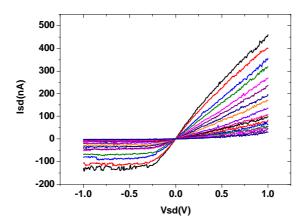

|    | 2.5   | Barrier height estimation                                               | 39        |

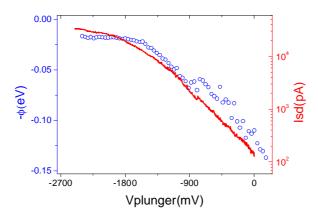

|    |       | 2.5.1 Plunger gate barrrier                                             | 39        |

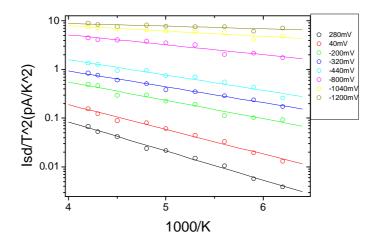

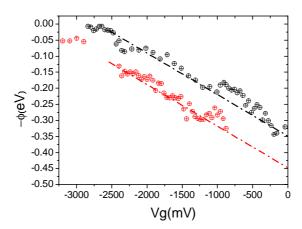

|    |       | 2.5.2 Contact Schottky barriers                                         | 40        |

|    |       | 2.5.3 Low temperature carrier injection                                 | 43        |

|    | 2.6   | Multifuction circuits                                                   | 44        |

|    |       | 2.6.1 pn junction                                                       | 44        |

|    |       | 2.6.2 Logic gate with gain                                              | 45        |

| 3  | Silio | cidation by Joule effect                                                | <b>52</b> |

|    | 3.1   | Silicidation by Joule effect                                            | 52        |

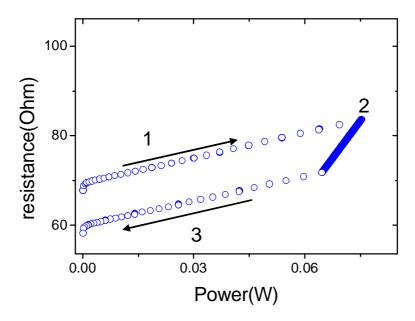

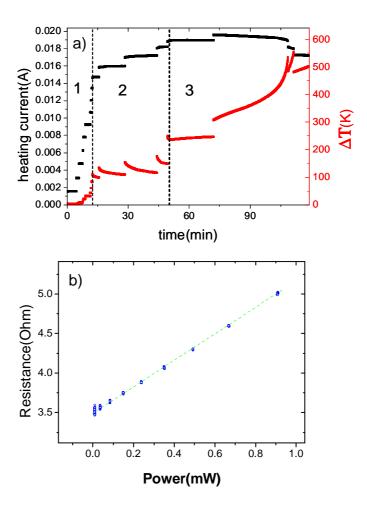

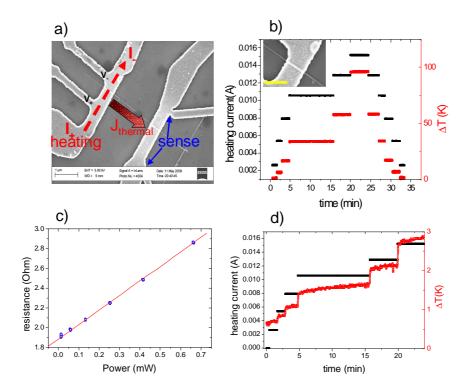

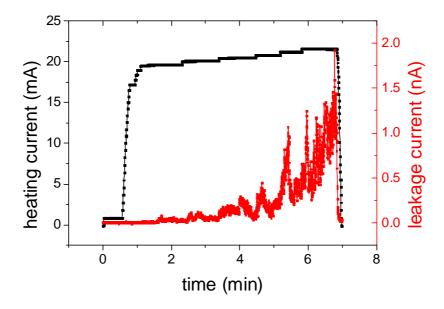

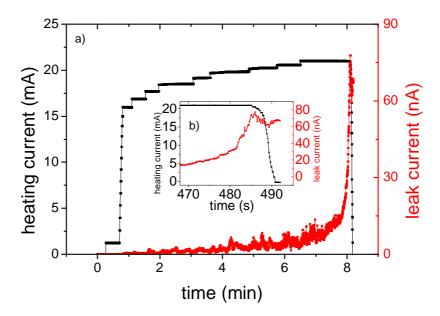

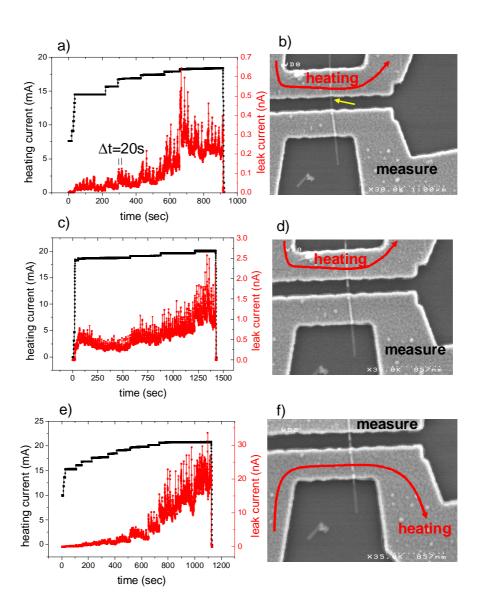

|    | 3.2   | Current driven experiments                                              | 54        |

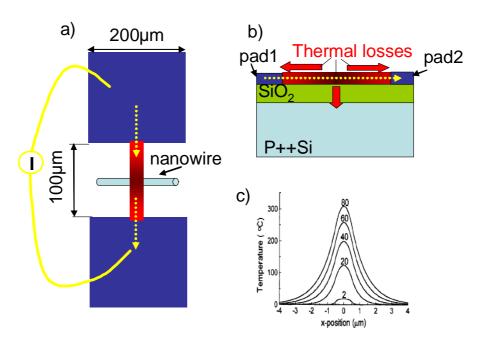

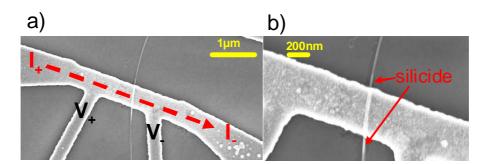

|    |       | 3.2.1 Electrical characterization of the striplines                     | 56        |

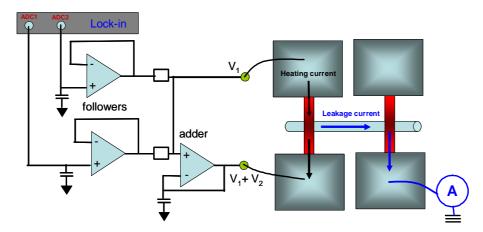

|    | 3.3   | Constant voltage biasing and measurement apparatus                      | 57        |

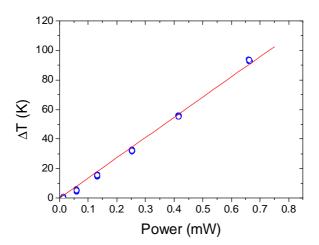

|    |       | 3.3.1 Temperature estimation                                            | 59        |

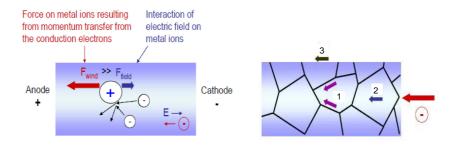

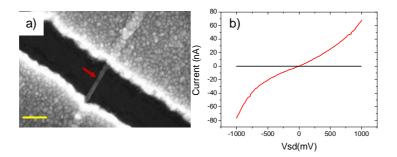

|    | 3.4   | Electrical control of the silicidation                                  | 64        |

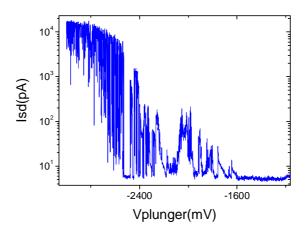

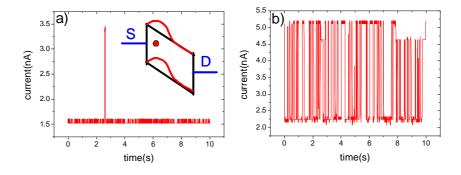

|    |       | 3.4.1 Electrical characterization: tunnel devices and Random Telegraph  |           |

|    |       | Signal                                                                  | 68        |

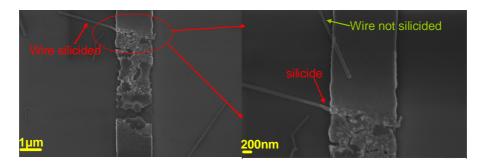

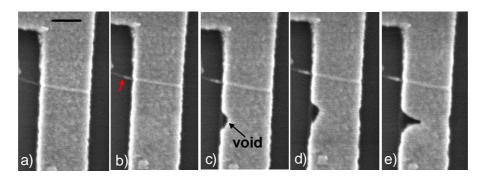

|    | 3.5   | In-situ observation of silicidation                                     | 71        |

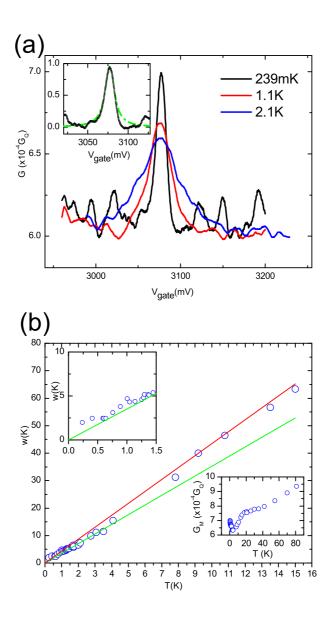

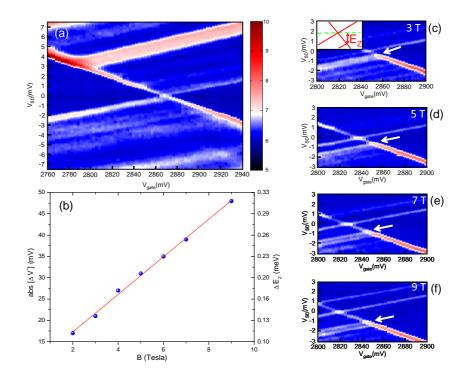

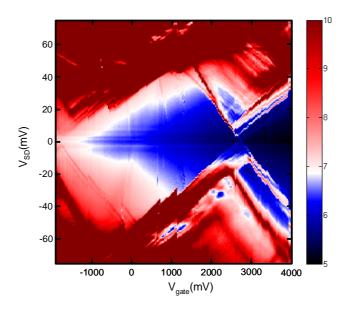

| 4  | PtSi clustering in silicon probed by transport spectroscopy |                                              |     |

|----|-------------------------------------------------------------|----------------------------------------------|-----|

|    | 4.1                                                         | Introduction                                 | 78  |

|    | 4.2                                                         | Platinum as contact material                 | 79  |

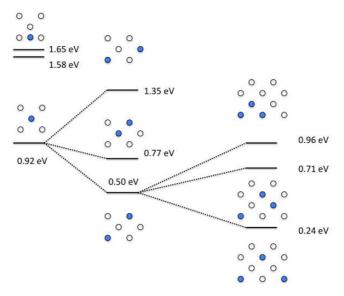

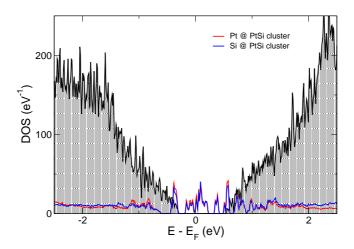

|    | 4.3                                                         | Electronic properties of Platinum in Silicon | 79  |

|    | 4.4                                                         | PtSi nanocluster agglomeration               | 80  |

|    | 4.5                                                         | Resonant Tunneling phenomena                 | 82  |

|    | 4.6                                                         | Tunneling Spectroscopy                       | 85  |

| C  | onclu                                                       | asions and perspectives                      | 96  |

| Li | ${f st}$ of                                                 | publications                                 | 100 |

### Foreword

So there we go! I have finally made it! After adding the last chapter and cheking the body of the manuscript I didn't find evident mistakes. Well, at least the pictures have colors and the writing is from left to right as it should be. I cannot guarantee for silly statements though. Now it's time to write the most important part of the thesis, the one which is hidden by tens of pages stuffed with hypothesis, wrong conclusions, failed experiments and few blinking glimpses of glory.

Even though my PhD cannot be really be defined as plug and play, it was a very valuable human experience for me. For this I thank my supervisors Silvano de Franceschi and Marc Sanquer for having welcomed me in the lab and giving me the possibility to embark this adventure. Don't take me wrong, of course I do see the advantages of entering a lab where everything is working since the very first day and the subject has been explored since decades and you simply rewrite some chapters of your predecessor's thesis. Eventually you change the sample if it is really needed. But not having even the chairs to sit (not to mention the desk) the first day you enter the lab makes this PhD a special one in the end. For the reasons written above. Because the (very) few nice good things the interested reader will eventually find in the following are the results of a real passion. The one that doesn't let you sleep at night and doesn't let you step back facing countless hours at work and unsuccessfull experiments. Every chapter in this thesis has been a fight, a fight on a virgin battlefield. And to me this is special as much as the formidable companions who backed me during the journey.

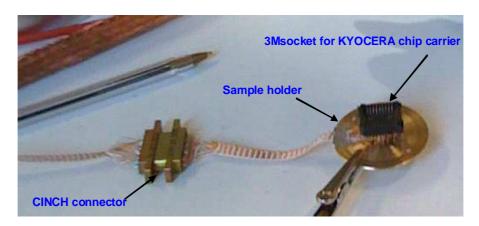

Without Giorgos and Pana nothing would have been possible. I owe them much of the results of this thesis. They were for me mentors and friends always ready to help out and support my bad moods. In other words they are for me the best labmates and most of all team players I could have ever dreamt of. Thanks to them the atmosphere in the lab (and I would say in the building) has been always cool and fresh with nice music in the air and singing echos of Dean Martin and Franck Sinatra in the corridors. Not only in the very few moments where things were going smoothly but expecially in the early days when we had "fun" while soldering tiny cables, building new sample holders, tweaking misterious electronic equipments, unvealing the secrets and the art of nanofabrication, programming and automatizing data collection and analysis, dealing with the heaviest administrative rules ever conceived by human being. Yes man, we made it!!.

I would also like to thank Xavier Jehl for his kindness, support and advices. He has given me a lot, always supportive and willing to proof read my papers, a real friend. Thanks Xa!!

A particular mention has to be given to Jean-Luc Thomassin, Frederic Gustavo and the technical staff of PTA for having coped with our endless requests of support in the cleanroom, trying to grasp the most intimate details of nanofabrication. Thank you guys for your competence, professionality and patience. I would have never been able to fabricate nice nanodevices without you guys.

Many thanks to Francois Lefloch and Claude Chapelier for their competences and advices in physics, nanofabrication, project managing. Thank you for having supported me in the mighty techno-meetings of friday afternoon and for popping in the lab downstairs every now and then having fun with us on silly greek-italo subjects.

Thanks to Gerard Lapertot and Christophe Marin, the mighty D5 crew, for the support in the annealing experiments and for having opened me the doors of their marvellous laboratory plenty of cool machines. I had a lot of fun working with you guys. Thanks to you I sowed the seeds of our *manip du siècle*.

Thanks to Frederic Poletti and Pierre Payet Bruin for their support in informatics and electronic equipments.

Thanks to my friends Alex, Francesca, Eva, Mario, Georg, my thesis labmates Mathieu, Thomas, Guillaume, the Chemtronics fellows Martien, Emanuela, Big Robert, Alejandro, Isabelle. I hope I didn't forget anybody.

I want to thank also my friend Edoardo for his closeness, the trips and the evenings spent drinking beers.

Lastly, I want to thank my family for the unconditional support and nurturing love, I love you all. If I am a good man it's because of them.

Thanks to my beloved sister always ready to sustain me in my darkest hours when I had to face the toughest period of my life.

And mum, even if you didn't make it to my defense I hope you will be proud of me looking from up there in the sky. I will try to do my best.

Grazie a tutti.

Massimo

## Introduction

The spectacular success of nowadays Information Technology stems from the capability to fabricate logic circuits based on Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) with increasing performances in terms of speed and packing density. This revolution has been triggered by the fundamental paradigm of scaling pionereed at the beginning of 70's [4]. The basic MOSFET building block works on the principle that flowing between two electrical terminals, the so called source and drain leads, is modulated by a control voltage applied to a third terminal, the so called gate electrode. Advance in circuit performance have been obtained through progressive scaling of device dimensions which has led to an increase density of transistor per unit area, higher speed and lower cost per function. Shrinking device dimensions has been possible by applying the so-called constant electric field scaling scheme. This scheme aims to reproduce the same electric field pattern in the smaller transistor by reducing the applied voltage along with the device relevant dimensions such as the junction depth, the channel length, the oxide thickness. This scaling requires an increasing doping level. In this transformation all the important characteristic of the device are modified by a common scaling factor  $\alpha$ . This approach gives three important results. The packing density and speed are increased because of the smaller device dimensions and parasitic capacitances. Lastly, the power dissipation per device is reduced because of the reduction of the voltage and current in each device. This is important since a bigger number of devices can be present on the chip area withouth increasing power dissipation. This trend has been followed with extraordinary success up to recent days when the current semiconductor technology has reached the 'nano' era. Current semiconductor manufacturing protocols have entered the 32nm node for the gate length of a planar MOSFET but concerns are widespreading about the real limits of a seamingly endless downscaling. Important limits could be quickly encountered in the next years due to limitations in lithographic techniques, to an increased leakage through the gate oxide and to random dopant fluctuation in the channel [16]. In this context new emerging devices based on bottom-up architectures [13], in particular nanowires, are currently being investigated as a possible alternative route to extend the stream of miniaturization even further [1]. The advantage of bottom-up nanodevices derives not only by their intrinsic smallness which makes them appealing with respect to a bare geometric scaling request, but also because their electronic properties can be taylored in-situ during the growth. Replacing the channel of a bulk planar MOSFET with a nanowire seems to be a logic choice in view of the above mentioned issues related to scaling. Both III-V and II-VI semiconductor nanowire compounds can be synthesized with a bottom-up approach but Silicon Nanowires (SiNWs) are of course a straightforward choice because they are fully compatible with CMOS technology. Among them, Schottky barrier SiNWs transistors offers many advantages concerning scaling issues with respect to conventional doped source-drain contacts [11],[10].

Besides, quasi 1-D nanostructures like Silicon nanowires offer an interesting playground where rich physics of low dimentional systems could be explored. In this respect Silicon is an attractive material for electronic applications involving the spin degree of freedom of the carriers [17]. This new possibility is explored in the field called spintronics where the spin degree of freedom carries the information as opposed to the charge. This brings some advantages like the integration of electronic, optoelectronic and magnetoelectronic multifunctionality on a single device that can perform much more than is possible with today's microelectronic devices. One device which is already in use is the Giant Magneto Resistive, or GMR, sandwich structure consisting of alternating ferromagnetic and non-magnetic metal layers. Depending on the relative orientations of the magnetizations in the magnetizations) to large (antiparallel magnetizations) [2]. This effect is the working principle of the data storage in nowaday's hard-disks.

Moreover, there are other proposals to use single spins as quantum bits [7], [12] and to encode the information in a quantum superposition of two levels (spin-up, spin-down). A key requirement for the implementation of quantum computing schemes is to prepare, manipulate and read the quantum bit. Coherent control of one and two spin states has been already accomplished in III-V etherostructures [15], [9], but efforts are going towards group IV materials like silicon, for which the spin lifetimes are expected to be larger due to the absence of hyperfine coupling with the nuclear spin moments and the absence of spin-orbit interaction. Read-out of a single spin in silicon has been accomplished in a device consisting of a top-down implanted phosporus donors coupled to a metal-oxidesemiconductor single-electron transistor [14]. The measured spin lifetimes approaches 1 second. Chemically sinthesized bottom-up nanostructures, on the other hand, offer the unique advantage that their properties like doping, size, composition can be taylored in-situ during the growth. This is an advantage as compared to top-down planar silicon devices where the critical feature sizes are defined by etching or lithography and doping achieved by implantation. This means that control of these important parameters cannot be extended to the atomic scale. For bottom-up silicon nanowires, the first evidence of transport through a single quantum structure with discrete energy levels was observed early as 2005 in molecular scale nanowires with diameter comprised between 3 and 6nm [18]. Electronic transport through these system is truly 1-D at low temperatures (4K) with typical subband spacing around 300meV. In these systems a single quantum dot accommodating few tens of holes could be formed between the leads with separations up to 400nm. The source-drain separation defined the dot size and suggested that structural variation or dopant fluctuations are to a large degree absent. Quantum computation with spins requires not only the isolation of single charges, but also the identification of single spins, a task that can only be accomplished in very small nanowires due to the relatively high electron and hole effective mass in silicon. This was done [19] by forming silicide/silicon/silicide nanostructures with a silicon channel length as small as 12nm. Lastly, charge detection on a double dot system [6] has been accomplished demonstrating the potential of these nanostructures for implementing solid-state spin quantum bits.

This work is devoted to the study of transport properties of Silicon Nanowires obtained by a bottom-up approach. The choice for the material system has been limited

to undoped SiNWs because they are considered as the ultimate choice for ultrascaled devices. Doping can in fact be challenging in very small nanostructures due to effects related to quantum confinement [8], surface segregation [5], and the increase of the ionization energy for the dopants as the nanowire diameter decreases [3]. The reduction of the wire diameter is on the oher hand unavoidable for tackling short channel effects in scaled transistors. The choice of undoped nanowires brings some drawbacks related to the presence of Schottky barriers formed at the contacts, rendering the problem of an effective carrier injection in the semiconductor particularly important. The thesis covers technological aspects related to the use of silicon nanowires as potential building blocks for nanoscale electronics and at the same time explores some opportunities offered in term of single-electronic devices, by developing fabrication techniques outperforming conventional nanolithography.

Chapter I describes the techniques employed for the fabrication of the nanowire devices investigated in this PhD work. The protocol developed for the formation of nickel silicide contacts is described in detail.

Chapter II deals with the study of a Gate-All-Around Schottky barrier transistor. Multiple gates are used to discriminate between different device switching mechanisms occurring either at the source and drain contacts, or at the level of the silicon channel. The gate dependent Schottky barrier height is measured for each of the contacts by means of a field emission model. The contact gates are proved be effective in suppressing the Schottky barrier enabling carrier injection at low temperature. Moreover, a p-n diode is formed by gate induced electrostatic doping in an undoped silicon nanowire. Lastly, a two inputs logic NAND gate with gain is assembled taking advantage of the local gate modulation of carrier injection at the contacts.

Chapter III reports a novel technique for the fabrication of metal silicide contacts to individual silicon nanowires. This technique, based on an electrically-controlled Joule annealing process, has enabled the realization of silicide-silicon-silicide tunnel junctions with silicon channel lengths down to 8nm. The transport behaviour of these short junctions were measured at low temperatures. The silicidation of silicon nanowires by Nickel and Platinum could be observed in-situ and in real time by performing the experiments of Joule assisted silicidation in the chamber of a Scanning Electron Microscope.

Chapter IV describes resonant tunneling through an isolated Platinum silicide nanocluster acting as a metallic Quantum Dot enbedded in a Silicon tunnel junction fabricated by Joule assisted Platinum silicidation. In particular, the Zeeman splitting of the ground and the excited states of a single nanocluster orbital could be measured by tunneling spectroscopy in a magnetic field.

# **Bibliography**

- [1] http://www.itrs.net/links/2009itrs/2009chapters\_2009tables/2009\_erd.pdf, 2009.

- [2] Baibich, M. N., Broto, J. M., Fert, A., Van Dau, F. N., Petroff, F., Etienne, P., Creuzet, G., Friederich, A., and Chazelas, J. Giant magnetoresistance of (001)fe/(001)cr magnetic superlattices. *Phys. Rev. Lett.* 61, 21 (Nov. 1988), 2472–.

- [3] BJORK, M. T., SCHMID, H., KNOCH, J., RIEL, H., AND RIESS, W. Donor deactivation in silicon nanostructures. *Nat Nano* 4, 2 (Feb. 2009), 103–107.

- [4] Dennard, R., Gaensslen, F., Rideout, V., Bassous, E., and Lebland, A. Design of ion-implanted mosfet's with very small physical dimensions. *Solid-State Circuits, IEEE Journal of DOI 9*, 5 (1974), 256–268.

- [5] FernÁ NDEZ-Serra, M. V., Adessi, C., and Blase, X. Surface segregation and backscattering in doped silicon nanowires. *Phys. Rev. Lett.* 96, 16 (Apr. 2006), 166805—.

- [6] Hu, Y., Churchill, H. O. H., Reilly, D. J., Xiang, J., Lieber, C. M., and Marcus, C. M. A ge//si heterostructure nanowire-based double quantum dot with integrated charge sensor. *Nat Nano* 2, 10 (Oct. 2007), 622–625.

- [7] KANE, B. E. A silicon-based nuclear spin quantum computer. *Nature 393*, 6681 (May 1998), 133–137.

- [8] Khanal, D. R., Yim, J. W. L., Walukiewicz, W., and Wu, J. Effects of quantum confinement on the doping limit of semiconductor nanowires. *Nano Letters* 7, 5 (May 2007), 1186–1190.

- [9] KOPPENS, F. H. L., BUIZERT, C., TIELROOIJ, K. J., VINK, I. T., NOWACK, K. C., MEUNIER, T., KOUWENHOVEN, L. P., AND VANDERSYPEN, L. M. K. Driven coherent oscillations of a single electron spin in a quantum dot. *Nature* 442, 7104 (Aug. 2006), 766–771.

- [10] LARSON, J., AND SNYDER, J. Overview and status of metal s/d schottky-barrier mosfet technology. *Electron Devices, IEEE Transactions on DOI* 10.1109/TED.2006.871842 53, 5 (2006), 1048–1058.

- [11] Lepselter, M., and Sze, S. Sb-igfet: An insulated-gate field-effect transistor using schottky barrier contacts for source and drain. *Proceedings of the IEEE DOI* 56, 8 (1968), 1400–1402.

- [12] Loss, D., and Divincenzo, D. P. Quantum computation with quantum dots. *Phys. Rev. A* 57, 1 (Jan. 1998), 120–.

- [13] Lu, W., and Lieber, C. M. Nanoelectronics from the bottom up. *Nat Mater 6*, 11 (Nov. 2007), 841–850.

- [14] MORELLO, A., PLA, J. J., ZWANENBURG, F. A., CHAN, K. W., HUEBL, H., MOTTONEN, M., NUGROHO, C. D., YANG, C., VAN DONKELAAR, J. A., ALVES, A. D. C., JAMIESON, D. N., ESCOTT, C. C., HOLLENBERG, L. C. L., CLARK, R. G., AND DZURAK, A. S. Single-shot readout of an electron spin in silicon. ArXiv e-prints (Mar. 2010).

- [15] Petta, J. R., Johnson, A. C., Taylor, J. M., Laird, E. A., Yacoby, A., Lukin, M. D., Marcus, C. M., Hanson, M. P., and Gossard, A. C. Coherent manipulation of coupled electron spins in semiconductor quantum dots. *Science* 309, 5744 (2005), 2180–2184.

- [16] TAUR, Y., BUCHANAN, D., CHEN, W., FRANK, D., ISMAIL, K., LO, S.-H., SAI-HALASZ, G., VISWANATHAN, R., WANN, H.-J., WIND, S., AND WONG, H.-S. Cmos scaling into the nanometer regime. *Proceedings of the IEEE DOI 10.1109/5.573737 85*, 4 (1997), 486–504.

- [17] WOLF, S. A., AWSCHALOM, D. D., BUHRMAN, R. A., DAUGHTON, J. M., VON MOLNAR, S., ROUKES, M. L., CHTCHELKANOVA, A. Y., AND TREGER, D. M. Spintronics: A spin-based electronics vision for the future. *Science* 294, 5546 (2001), 1488–1495.

- [18] ZHONG, Z., FANG, Y., Lu, W., AND LIEBER, C. M. Coherent single charge transport in molecular-scale silicon nanowires. *Nano Letters* 5, 6 (June 2005), 1143–1146.

- [19] ZWANENBURG, F. A., VAN RIJMENAM, C. E. W. M., FANG, Y., LIEBER, C. M., AND KOUWENHOVEN, L. P. Spin states of the first four holes in a silicon nanowire quantum dot. *Nano Letters* 9, 3 (Mar. 2009), 1071–1079.

# Chapter 1

## Device fabrication

Considerable effort throughout this thesis has been put on the device fabrication. The fabrication of a working nanoscopic electronic device goes through multiple steps each of them as much important as the previous one. Basically, one intends to attach macroscopic electrodes to the nanometer sized objects like the nanowires and build an electronic circuit. For this purpose, we extensively used lithographic techniques which allow the patterning of custom designed contact electrodes. Although lithography is a very important step in the fabrication, a finished device is rather complex since different steps like cleaning, etching, thermal treatments, oxide deposition, sample bonding and mounting must be carefully done.

#### 1.1 Nanowire growth

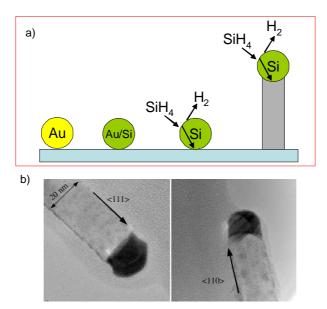

In this section I describe the growth process of the silicon nanowires studied in this thesis. The majority of devices were fabricated from undoped Silicon nanowires grown in the Laboratoire Silicium, Nanoelectronique, Photonique et Structure (SiNaPS) located in CEA-Grenoble. The nanowires were grown following a bottom-up approach through Low Pressure Chemical Vapour Deposition (LPCVD) [6] based on the Vapor-Liquid-Solid (VLS) mechanism [19]. The growth was catalyzed by size-calibrated catalysts from a gold colloid solution (Ted Pella) deposited on top of a (111) silicon substrate cleaned in alcohol and deoxidized into an ammonium fluoride mixture. Deposition of gold colloids dispersed in water was done in an electrochemical cell where the control of the density is accomplished by using an external electric field to drive the motion of the nanoparticles on the substrate. Besides, control over the nanowires diameter is set by the dimension of the seed colloids. After deposition of the catalysts the sample is introduced in the LPCVD reactor and annealed under  $H_2$  flow in the temperatures range 450 - 750°C. After this annealing step temperature is decreased to the  $400 - 500^{\circ}$ C range and silane (SiH<sub>4</sub>) is introduced in the reactor initiating the growth fig.(1.1a). The silane decomposes and Si atoms condense into Si-rich liquid nanoclusters. The metallic clusters will be supersaturated by silicon which will start to crystallize below the gold particle promoting the growth from the top of the substrate.

Occasionally, other kinds of devices were instead processed starting from wires grown in LITEN laboratory [3] at CEA-Grenoble and consists of either homogeneously or modulation doped silicon nanowires. The doping was achieved in-situ through addiction

**Figure 1.1:** a) Schematic of the VLS growth mechanism. b) High Resolution Transmission Electron Microscopy of two 20nm diameter silicon nanowires. From ref. [6]

of phosphine (1% PH<sub>3</sub> in hydrogen) with a P:Si ratio set to  $2 \times 10^{-2}$ . The modulation doped nanowires consisted in a  $n^{++}$ -i- $n^{++}$ , with  $n^{++}$  corresponding to the highly doped parts and i to the intrinsic or unintentionally doped part.

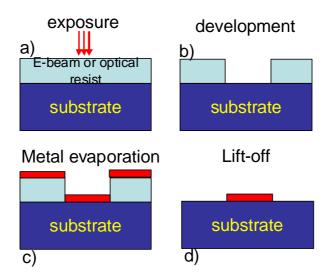

#### 1.2 Electron beam and optical lithography

The fabrication of nanowire based devices described in this thesis is pursued by taking advantage of lithographic techniques. Two main lithography schemes were adopted: optical and e-beam lithography. The lithographies have been performed on top of a  $5 \times 5$ mm<sup>2</sup> substrate consisting of a degenerately doped  $p^{++}$  silicon wafer covered by a 285nm thick dry thermal oxide. The presence of a highly doped silicon substrate is useful when a global back gate field is needed. The basic process flow for both of these fabrication techniques is described schematically in fig(1.2). It goes through 4 sequential steps:

- spinning of the resist

- exposure of the resist by an electron beam current or by an ultraviolet lamp shined on the sample through an optical mask

- metal deposition

- lift off

The choice of the lithographic technique to be used is dictated by the particular type of experiment one intend to perform. The optical lithograpy is inherently faster than the e-beam one and is mostly useful when a parallel processing is needed. The nanowires are multiply contacted randomly by specifically designed electrodes. This parallel processing has been extensively used for annealing tests as described in more details in the following

Figure 1.2: Schematic process flow for the fabrication of the samples by optical or e-beam lithography. a) The layer of resist is exposed to an UV lamp (optical lithography) or to a beam of electrons (e-beam lithography). The development b) in a suitable solution opens up a window in the exposed area of the resist. With a low pressure  $P \approx 10^{-7}$  mbar e-beam metal evaporation, a layer of metal is deposited on the sample c). The thickness of the metal layer is kept smaller than the thickness of the resist such that the metallic film is not continuous over the exposed area. The excess metal is removed everywhere d) except in the patterned areas by dissolving the polymer in acetone at  $50^{\circ}C$  for 10 minutes.

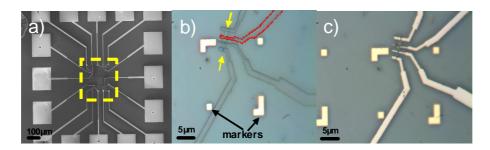

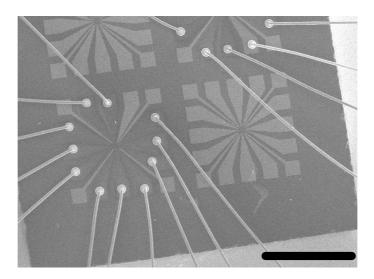

sections. With the electron beam lithography, on the other hand, we can address individual nanowires. For this purpose the samples dedicated to e-beam lithography need to have additional structures already patterned on them. These additional structures are the alignment markers and the bonding pads. The alignment markers have a double function: they help on localizing the exact position of the nanostructures we want to contact and provide a reference system to the software governing the beam of electrons. The e-beam samples were fabricated with the aid of a JEOL Scanning Electron Microscope equipped with a beam blanker. The accuracy in repositioning of such a system is limited to around 300nm and the smallest features that could be routinely patterned on the resist layer depend on the particular e-beam resist and write field used. For the fabrication of the e-beam samples described in this thesis I have used a layer of polymethyl methacrylate (PMMA) spun on the subtrate for 60 seconds at 4000rpm and subsequently baked at 180° C for 5 minutes. The exposure of the PMMA layer by the electron beam causes the breaking of the chemical bondings in the polymer such that the resist becomes soluble in a developer. After e-beam exposure the samples are developed in a solution of methyl-isobutyl-ketone (MIBK): Isopropyl-alchool (IPA) 1:3 for 60 seconds followed by a final 60 seconds rinse in IPA. The samples are then finally gently blown dry with a nitrogen flow. The typical devices processed by means of e-beam lithography consists of four cells covering areas of  $100 \times 100 \text{ nm}^2$  or  $250 \times 250 \text{ nm}^2$  fig.(1.3a). Each cell defines the actual active area of the sample where the nanowires are contacted to the micrometer sized predefined bonding pads. In each of these four cells an array of alignment markers is patterned to allow for the identification of the nanowire to be contacted. The

**Figure 1.3:** a) SEM picture of one of the four subcells. The active part of the device, high-lighted by the yellow dashed box, is enclosed in macroscopic sized contact pads already predefined on the sample along with alignment markers. b) Optical micrograph showing the contacts patterned in the resist right after the developing step described in 1.2 and c) the finished device after metal evaporation and lift-off.

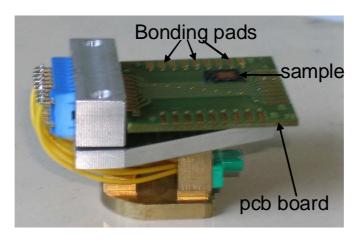

nanowires coming from the growth substrate, are deposited on the substrate by direct transfer, or released from a solution. The direct transfer technique consists simply on pressing gently the growth chip against the target substrate. Otherwise the growth chip can be inserted in IPA followed by a small ultrasonic agitation. The nanowires are then dispersed on the substrate with the aid of a micropipette. Few droplets of the solution are let dry on top of a hot plate at moderate temperature. After the sample had dried the chip is rinsed in acetone and IPA followed by nitrogen blow. This step is helpful in cleaning the bonding pads by organic residuals that could complicate the bonding. The as dispersed nanowires are located with respect to the alignment markers either by an optical microscope or by SEM inspection. Wires whose diameter is between 50 to 100 nm can be easily imaged by an optical microscope. In this case we import digital optical images of the wires in areas of the chip containg at least 4 markers fig. (1.3b) after the resist has been spinned. Imaging the wires after resist spinning is important since 100 nm diameter wires are prone to move in the spinning step. Small ( $\approx 20$ nm) diameter wires are instead imaged by SEM. In both cases the images are imported in a Computer Aided Design (CAD) software and the pictures are superimposed to the markers pattern. Individual electrodes to the nanowires (red dotted line fig.(1.3b)) are computer generated and the sample is then ready to be loaded in the e-beam lithography system. The metallization step fig.(1.3c) is performed in general by e-beam metal evaporation under a pressure of  $3 \cdot 10^{-7}$ mBar at deposition rates of 0.1 nm/sec. Prior to the deposition of metal the samples undergo to a 5 seconds wet etching under a solution of Buffered Hydrofluoridric Acid (BHF) to remove the layer of native oxide, typically few nanometers thick from the surface. Nickel electrodes are then evaporated to a thickness of 120 nm. After metal deposition and lift-off the samples are then ready to be eventually tested in a probe station but in most of the cases they are directly mounted on a 24 pin chip carrier either by gluing them with silver paint or with carbon tape. The samples glued with silver paint are subsequently bonded and are ready to be measured, eventually to cryogenic temperatures, while samples glued with a conductive carbon tape can be easily unmounted from the chip-carrier and reprocessed.

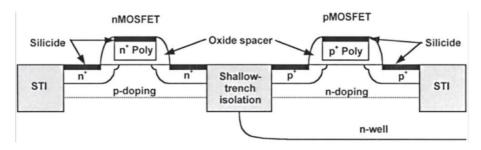

#### 1.3 Metal Silicides

The attractiveness of silicon nanowires as material system to build functional nanoscale circuits stems from its intrinsic compatibility with Silicon technology. The basic building block for the absolute majority of today's electronic systems is the Metal-Oxyde-Semiconductor-Field-Effect-Transistor (MOSFET). Silicon nanowires are considered as the natural evolution of a bulk silicon transistor into the nanoscopic world and hold promise as the final candidates in ultrascaled circuits. Due to this compatibility with the existing fabrication technology it is natural to extend to silicon nanowires the same contacting schemes which found success in modern Silicon Integrated Circuits (SICs). In

**Figure 1.4:** Cross section of modern CMOS transistors where the source, drain and gate terminals are contacted with metal silicides.

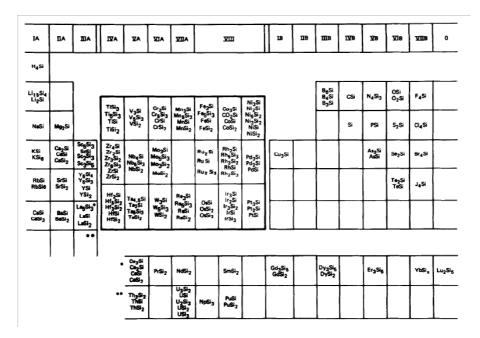

a modern MOSFET, the source, drain and gate terminals are contacted with a metallic silicide fig.(1.4). A silicide is basically a compound of Silicon with another element of the periodic table fig.(1.5). The most famous one is perhaps silicon dioxide  $(SiO_2)$  which is the most abundant compound found on Earth's crust. The use of a silicide as contacting material has been driven by the continuous demands for increasing the speed of a switching circuit. To this end parasitic capacitance and series resistance should both be minimized to reduce the RC delay time and increase the clock frequency [17],[13]. For this purpose metal silicides meet the basic requirements to lower the parasitic resistances at the level of the source drain and gate terminals. Metallic silicides used for contact metallization and local interconnections have the desired low specific resistivity and low contact resistivity to both p- and n- type silicon. Moreover, since the gate length in nowadays MOSFET has reached 32nm the resulting low channel resistance demands for an increased reduction of the parasitic series resistances in the source and drain regions.

The most important silicides for SICs are formed by combining silicon and a transition metal and fall in the category called Intermetallics. These compounds behave more or less like metals, and were first introduced in SICs essentially as contacting materials.

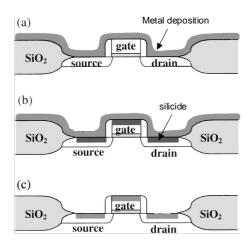

#### 1.3.1 Self aligned silicide

In modern silicon industry the contacting process for the source, drain and gate terminals is done in one step without the use of a mask, through a technique which allows the metallisation of these three terminals in a self aligned fashion. The process is called Self ALIgned siliCIDE (SALICIDE) fig.(1.6) [22]. In the SALICIDE process a layer of a transition metal is deposited over all the MOSFET structure fig.(1.6a). With a first

Figure 1.5: Periodic table of silicides. (Adapted from [14])

annealing step at a suitable temperature the metal react with the silicon allowing the formation of a silicide phase on the source, drain and gate leaving unaltered the oxides fig.(1.6b). The excess metal is then removed by a selective wet chemical etching. The etching step will only remove the metal which didn't react with silicon. After the etching process other thermal treatments could be eventually performed to form different silicide phases of lower resistivity. The choice of a particular silicide over the others is made taking into account several requirements, namely

- a low resitivity

- easiness of fabrication

- existence of a selective etching process for the excess metal

- minimum silicon consumption

- good thermal stability

- smooth interface with silicon

The most important silicides used in the SALICIDE process have been those with the rather low resistivity of  $10-20\mu\Omega {\rm cm}$ , i.e.  ${\rm TiSi_2}$ ,  ${\rm CoSi_2}$  and NiSi. Hystorically,  ${\rm TiSi_2}$  was the first silicide used for metallization.  ${\rm TiSi_2}$  occur in two different crystallographic structures C49 with high resistivity and C54 of low resistivity. The transition between the high to low resistivity phase is difficult to accomplish as the gate length of the devices approaches 100nm.  ${\rm CoSi_2}$  has been used up to 40nm gate lengths but as for  ${\rm TiSi_2}$ ,when the production of transistors reaches gate lengths significantly shorter, the formation of cobalt silicide contacts becomes more difficult mainly due to a increase of the resistance for very thin lines (fine line effect). Nickel silicide has been envisioned to

**Figure 1.6:** Flow chart for the SALICIDE process. a) The metal layer is deposited over the MOSFET structure. b)A themal annealing promotes the formation of the silicide on the source, drain and gate terminals, no reaction takes place on the oxide spacers if the metal atoms are the dominant diffusing species like in the case of Nickel. c) After a selective wet chemical etch the excess metal is removed.

be the ultimate silicide [10],[7], since it brings some advantages as compared to the other silicides. It can be formed at relatively low temperatures between 250 and 500°C which translates into a lower thermal budget for the fabrication of ICs, it has a low resistivity and consumes less silicon, characteristic very important for shallow junction transitors fabricated on Silicon On Insulator (SOI). Moreover in NiSi, nickel is the main diffusing species such that there is no lateral silicidation over the sidewalls of the dielectric and problems related to shortening of the source, drain and gate (bridging) are avoided. Lastly, the interface between the nickel silicide and silicon can be atomically sharp, thus avoiding early breakdown of the devices when bias is applied due for istance to the high electric field at the gate edges.

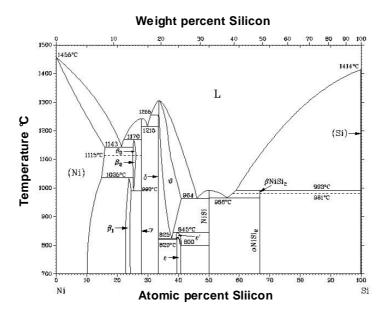

#### 1.3.2 Ni-Si solid state reaction

In this section we briefly describe the formation of nickel silicide phase in thin films. The solid state reaction of nickel thin films on silicon gives rise to a quite complex phase diagram fig(1.7) [15]. Up to eleven phases in the Ni-Si phase diagram can be counted, six of which being stable at room temperature: Ni<sub>3</sub>Si , Ni<sub>3</sub>ISi<sub>12</sub>, Ni<sub>2</sub>Si , Ni<sub>3</sub>Si<sub>2</sub>, NiSi and NiSi<sub>2</sub>. It has been observed that the formation of the Nickel silicide through solid state reaction of Nickel thin films deposited on a silicon subtrate is sequential [16]. Without loss of generality, the formation of the silicide in thin films is governed in a first stage by the reaction of the metal (M) and the silicon (Si) at the interface. The first phase which is formed in the early stages of the reaction is the metal rich phase M<sub>2</sub>Si. Once the metal layer has been totally consumed, the formation of the monosilicide phase (MSi) starts to take place at the expenses of the metal rich phase. The final silicon rich phase MSi<sub>2</sub> will grow to consume totally the monosilicide layer. Although formation temperatures for the M<sub>2</sub>Si and MSi phases can be as low as 250°C, the silicon rich phases are in general observed at higher temperatures around 700-800°C and their formation

Figure 1.7: Phase diagram for the Ni-Si binary system.

is instead governed by nucleation [12]. For top-down transistors fabricated on bulk p-njunctions or thin SOI the SALICIDE fabrication process aims to reach the growth of the nickel monosilicide phase which has the lowest resistivity. In the framework of the above described kinetics for the nickel silicide phase formation, the monosilicide phase can occur only after the total consumption of the metal layer in the form Ni<sub>2</sub>Si. To achieve the monosilicide in shallow junctions the first annealing step promoting the formation of the metal rich phase could be followed by a second thermal treatment done after etching the excess metal layer [4]. The above described mechanism for the metal-Silicon binary system is relatively well understood in the case of thin films on bulk substrates, where the metal thickness  $t_M$  is usually much less than the silicon thickness  $t_{Si}$ . In the opposite case  $t_M >> t_{Si}$  different metal rich phases could be present in the early stages of the silicide formation [2]. This aspect is important for the point of view of device application, since different phases of the metal silicides could have different resistivities and in turn affect the performances of ultrascaled devices. In this thesis we are interested in controlling the extension of the metal-like silicide phase into the silicon regardless of the phase sequence underlying its formation.

#### 1.3.3 Silicidation in silicon nanowires

In current MOSFET technology, the process of silicidation has been conceived to provide a suitable contacting scheme for the terminals of the active device like source, drain and gate. As explained in the previous sections, research on the contact metallisation through silicides has been triggered by the demand of lowering the parasitic series resistances arising from the contact. An important aspect in the technology of metallisation in common transistors is the fact that the contact silicides are in general shallow. The amount of silicon consumed in the process of silicide formation must be minimal [9] to allow smaller design rules. In this thesis we have adapted the silicidation technique by

nickel already developed in the case of bulk planar transistors for defining the contact regions for the nanowires. Our contacting schemes differs from the process flow adopted in the case of top-down defined transitors. In particular:

- our geometry is not planar

- the metal silicide-silicon interface is not shallow

- we don't make use of the selective etching process to remove the excess metal as in conventional MOSFETs

- we promote lateral silicidation

The contact metallization procedure through silicides has been applied with success in the case bulk junction transitors and SOI thin films. In both cases the metal-silicon interaction occurs at the plane of the interface. A nanowire is inherently different in its geometry and the early stages of silicide reaction takes place in the radial direction [8]. Moreover, the interface in our devices is never shallow since we are not concerned about vertical scaling issues which are instead governed by the nanowire diameter. Another difference is that a completed device doesn't go through the metal etching process typical of the SALICIDE technique. In our silicided nanowires the metal layer provides at the same time the material for the solid state reaction and the connecting path for the complete circuit in which the nanowire is embedded. The last and most important difference is that we are expecially interested in promoting a lateral silicidation for our devices. We can speak about lateral silicidation when the nickel silicide-silicon interface is not only moving parallel to a fixed interface plane but the silicide formation kinetics allow for the growth of the silicide phase in a plane orthogonal to the metal/silicon interface. The lateral silicidation can occur in ultrathin SOI MOSFETs when the contact metallization is done with a nickel film thicker than the silicon. The lateral penetration of the nickel silicide under the isolation spacers towards the channel is strongly detrimental for the transitor operation because if the silicide extends to the low doped channel region, the source and drain contact exihibit a Schottky behaviour [18]. Although the actual growth mechanism of the silicide phase in silicon nanowire is not well understood, through thermal annealing we promote radial and longitudinal diffusion of nickel in the nanowires. This is accomplished by taking advantage of the unique property of nickel in the binary nickel-silicon system to be the dominant diffusion species. The formation of Ni-silicides by means of solid state reaction of lithographically defined nickel contacts on Si nanowires has been demonstrated in a few earlier works [21], [20], [1]. The actual growth mechanism of the nickel silicides leading to the axial intrusion of the metallic phase in the nanowire is thermally activated and involves different processes like volume, surface and interface diffusion and lateral growth of Ni silicide [8]. The thermal energy is provided typically by heating sources like lamps or lasers in the case of a Rapid Thermal Process (RTP) or more simply by resistive elements in furnaces. Conventional semiconductor device manufacturing is done by using RTP techniques because they are faster and provide high throughput. The silicidation of silicon nanowires in this thesis was instead performed in a furnace. The samples contacted with the lithographic techniques described before were loaded in a quartz tube attached to a vacuum system. Prior to the thermal annealing, the quartz tube was pumped by primary vacuum pumps

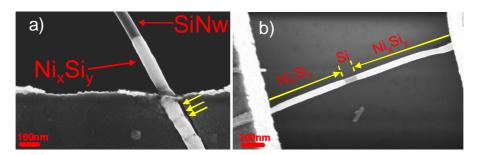

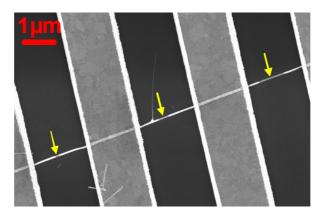

Figure 1.8: a) SEM micrograph of a nanowire reacted with a nickel film afer a thermal annealing. The brigher region in the nanowire is the metallic nickel silicide phase grown by the thermal annealing performed at  $500^{\circ}$ C for 5 minutes. The lithographically defined metal film covering the nanowire has been deposited to a thickness comparable to the nanowire diameter  $d \approx 100$ nm causing the discontinuity of the metal contact on top of the nanowire (yellow arrows). b) Nickel silicide/silicon/Nickel silicide etherostructure formed on a 50nm diameter silicon nanowire. After the silicidation an unreacted silicon portion of 120nm could serve as channel for a transistor.

to a pressure  $P \approx 4 \times 10^{-2}$  mBar and subsequently purged with a constant Argon flow for several minutes. This cycling through vacuum was done to prevent any oxygen contamination. Subsequently, the quartz tube was guided into the furnace heated at the desired temperature and the samples annealed for various time intervals. Scanning electron microscopy is a powerfool tool that can be used in order to study the solid state reaction occurring during the silicidation. Fig. 1.8a is a Scanning Electron Microscope (SEM) picture which shows a 100nm diameter Silicon nanowire contacted by a nickel electrode after a process of thermal annealing. The bright contrast along the nanowire axis is due to a metallic nickel silicide phase protruding from the electrode. Through this lateral silicidation we promote the diffusion of nickel along the nanowire axis to form an abrupt interface between the nickel silicide and the silicon. The nickel electrode has the role of a reservoir for the nickel atoms which have to diffuse in the silicon lattice of the nanowire. If the amount of metal covering the nanowire and its radius are comparable, a long annealing of several minutes could provoke the craking of the metal film just on top of the nanowire, as enlighted by the yellow arrows in fig.1.8a and a consequent failure of the electrical contact defined by lithography. The promotion of a lateral silicidation in silicon nanowires offers intriguing possibilities in terms of device fabrication. This is enlighted in fig. 1.8b which shows a silicon nanowire bridging two nickel electrodes after an annealing step. The diffusion of nickel into the nanowire from both the contacting electrodes forms two metal-like extensions of the contacts leaving an unreacted silicon portion in the middle of the device. The ability to control the lateral silicidation can give then access to nanoscale device architectures with applications ranging from ultrascaled transistors or quantum devices like quantum dots or tunnel junctions.

#### 1.3.4 Control of the silicidation process

Control of the lateral silicidation is very crucial from the point of view of device applications. If, for istance, the silicidation process is used to define the channel of a transitor like in fig.1.8b then, one needs a fine control on the lengths of the two silicide extensions. This is important since in principle different transistors on the same chip should have the same channel length. This is also true for other devices like Single Electron Transistors (SETs) or tunnel junctions which could be fabricated through a lateral silicidation process leading to the definition of a very small area of a semiconductor sandwiched between two metallic leads. Controlling the lateral silicidation is necessary also for fundamental studies aimed at understanding transport phenomena like carrier injection and field emission occurring at the interface between the metal silicide and the silicon. This is of fundamental importance expecially when the overall electrical behaviour of the devices is determined by the interface properties. This point is clarified in fig.1.9 where a single nanowire is contacted by three equidistant metal contacts. The thermal annealing leads to the formation of three different unreacted parts in between two adjacent contacts of different dimensions. The silicide propagates into the same nanowire at differents growth rates. Many factors could actually be responsible for the observed

Figure 1.9: SEM micrograph of a  $10\mu$ m long nanowire contacted with three equidistant contacts. The silicides extending from the contacts grew at different rates and as a consequence the three unreacted silicon portions highlighted by the yellow arrows have different dimensions.

non-homogeneties in the silicide growth. The presence of a native oxide layer on the surface of silicon nanowires is known to have a detrimental effect since it could act as a diffusion barrier layer to stop or delay the reaction between the metal and the silicon [11]. Moreover, there could be organic residues on the surface of the nanowires, coming from the lithography and/or from the solutions in which the nanowires are dispersed. Purity, roughness and mechanical adhesion of the metal layer deposited could also have an influence on the overall process.

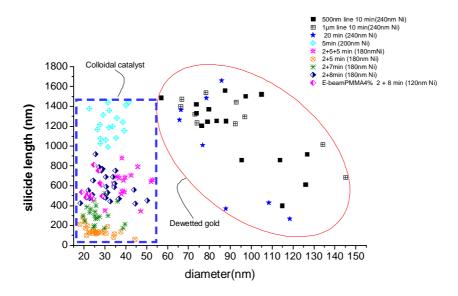

To better understand and control the silicidation process in the nanowires, we studied the statistical distribution of the lengths of the silicides in two different sets of samples. In the first set called set1 there are wires obtained through a growth catalyzed by gold nanoparticles obtained by dewetting a thin layer of gold deposited on the substrate; in the second set called set2 the nanowires are instead catalyzed by gold colloids. The difference in the two sets of samples are mainly ascribed to the dispersion and average diameters of the nanowires. The samples of the set1 are characterized by an average diameter  $89 \pm 23$ nm with a relative dispersion of 26% in the diameters. Samples of the set2 obtained by colloidal nanoparticles have an average diameter of  $28 \pm 6$ nm with a

relative dispersion of 20%. The wires of set1 and set2 are contacted randomly by means of optical lithography to assure high throughput and statistical significance or by e-beam lithography for specific device geometries. The metal thickness is chosen according to the wire diameter and it's always bigger the nanowire diameters in both sets. The ratio between the metal thickness deposited and the nanowire diameter is between 1.7 and 3.4 for set1 and between 3.6 and 9 for set2. These ratios are big enough to guarantee enough supplying material from the metal reservoirs in the process of diffusion. Different parameters can influence the silicide growth. The most important ones are:

- the annealing temperature

- the nanowire diameter

- time

Although a nickel silicide phase could be formed at temperatures as low as 130°C [10] the annealing experiments were performed by keeping fixed the temperature at 500°C. This value is high enough to cause the formation of a silicide phase on the time scale of several minutes but lower than the temperature where other effects, like agglomeration and formation of the high resistive Si-rich phase, start to take place [12]. Fig.1.10 summarizes

**Figure 1.10:** Silicide lengths as a function of diameter for different annealing protocols.

the results obtained for the penetration length of the silicide after the annealing process. Two blocks of data are shown: data on set1 enclosed by the red circle referring to wires catalyzed by dewetted gold on the surface and data on set2 highlighted by the dashed blue box, summarizing the results for the wires catalyzed by colloidal particles. The wires from set1 have been subjected to annealings of 10 and 20 minutes. A volumetric effect [1] in the silicide penetrations is visible for this set of data, leading to a decrease of the silicide length as a function of the nanowire diameter for both the annealing times. The electrode's width, varied from  $1\mu m \rightarrow 500 nm$ , for the wires annealed for 10 minutes

doesn't have influence on the average silicide length for the two set of data overall silicide length for a given diamater. Interestingly, doubling the annealing time doesn't have a dramatic effect on the silicide growth rate and the subset of data corresponding to the 20 minutes annealing, shows almost the same dispersion of the silicide lengths as a function of diameter. This fact allows us to exclude that the phase growth is assisted by a linearparabolic law [5]. According to this picture, in the early stages of the phase formation metal and silicon are always available at the interface and the thickness of the silicide increases linearly with time. When the silicide thickness increases, the growth becomes limited by the flux of the supplying nickel atoms through the growing phase towards the interface with silicon, leading to a growth mechanism which is diffusion limited, with a characteristic square root dependence on time. The situation is much more complicated if two or more phases are present in the early stages of the reaction. In this case the growth rates of the existing phases are coupled resulting in a different kinetics for the phase formation. On the set of nanowires annealed for 5 minutes, belonging to the set 2 we measure an average penetration comparable to the one observed for 10 and 20 minutes annealing times which amounts to  $1224 \pm 144$ nm while a volume effect due to the dispersion of the wires diameters is not visible. This is most probably due to a rather smaller dispersion in the wires diameter for this subset of samples where the average diameter is  $32\pm5$ nm, leading to a relative dispersion of around 16%, whereas the relative dispersion for the subsets of data belonging to set 1 ranges between 22 - 30%. Indeed, the volumetric effect manifests itself in the fact that the same average penetration lenghts for the silicides can be obtained by reducing the time and the diameter of the nanowire accordingly.

As an attempt to limit the statistical dispersion of the silicide lengths, we modified the annealing procedure by performing thermal cyclings for the wires belonging to set 2. The samples were firstly annealed at  $500^{\circ}$ C for 2 minutes and then annealed for different periods of time (at the same temperature) in a second step. The time for the second annealing step was ranging from 5 to 8 minutes. In between the two steps the silicidation process was left quenching at room temperature for a period of time of about 10-15 minutes under a constant Argon flow. As is evident from fig.1.10 the thermal cycling process has as first effect to limit the growth rate of the silicides. This conclusion is drawn by confronting the silicide lengths for the subset of samples annealed for 5 minutes and the lengths obtained by thermally cycling the samples through two thermal treatments. Although the total annealing time for the subset of samples which received the second annealing step can be 1.4-2 times bigger than the single 5 minutes step time, the average penetration lengths are smaller for the same nanowire diameter. The first annealing step is then effective on limiting the lateral growth of the silicides by posing an interfacial barrier layer for the diffusion of the Nickel atoms in the second step.

To summarize, we have performed a systematic study of the formation of silicides in Silicon Nanowires with the aim to control the length of the lateral silicidation. Our goal was to find a recipe for the annealing treatments capable to promote the silicidation growth in a reproducible way. The dispersion in the lengths of the silicide phases is mainly ascribed to the dispersion in the wire diameters for a given annealing temperature. The smaller will be this dispersion the better we can control the penetration lengths. The main advantage of the double step annealing technique as compared to the single step is that we are able to avoid excess lateral silicidation. SEM inspection of samples which

received only the first 2 minutes annealing step showed a slight lateral growth of the silicides amounting to 10-20nm from the edge of the contact, revealing that the first step is long enough to promote a fully radial silicidation and to start the lateral one. The silicidation lengths measured for wires of  $set\ 2$  corresponding to an annealing of 5 minutes differ by a factor of more than 60 with respect to the 2 minutes step reveiling that the growth rates are far from being linear or assisted by a bare diffusion process. Through a double step we can reasonably control the silicidation process and obtain penetrations between 140-580nm by changing the annealing time in the second step on a minute time scale.

# **Bibliography**

- [1] APPENZELLER, J., KNOCH, J., TUTUC, E., REUTER, M., AND GUHA, S. Dualgate silicon nanowire transistors with nickel silicide contacts. In *Electron Devices Meeting*, 2006. IEDM '06. International (2006), pp. 1–4.

- [2] CANALI, C., MAJNI, G., OTTAVIANI, G., AND CELOTTI, G. Phase diagrams and metal-rich silicide formation. J. Appl. Phys. 50, 1 (Jan. 1979), 255–258.

- [3] Celle, C., Carella, A., Mariolle, D., Chevalier, N., Rouviere, E., and Simonato, J.-P. Highly end-doped silicon nanowires for field-effect transistors on flexible substrates. *Nanoscale* 2, 5 (2010), 677–680.

- [4] FOGGIATO, J., YOO, W. S., OUAKNINE, M., MURAKAMI, T., AND FUKADA, T. Optimizing the formation of nickel silicide. *Materials Science and Engineering B* 114-115 (Dec. 2004), 56–60.

- [5] Gambino, J., and Colgan, E. Silicides and ohmic contacts. *Materials Chemistry* and Physics 52, 2 (Feb. 1998), 99–146.

- [6] GENTILE, P., DAVID, T., DHALLUIN, F., BUTTARD, D., PAUC, N., DEN HERTOG, M., FERRET, P., AND BARON, T. The growth of small diameter silicon nanowires to nanotrees. *Nanotechnology* 19, 12 (Feb. 2008), 125608–125613.

- [7] IWAI, H., OHGURO, T., AND OHMI, S.-I. Nisi salicide technology for scaled cmos. *Microelectronic Engineering* 60, 1-2 (Jan. 2002), 157–169.

- [8] Katsman, A., Yaish, Y., Rabkin, E., and Beregovsky, M. Surface diffusion controlled formation of nickel silicides in silicon nanowires. *Journal of Electronic Materials* 39, 4 (Apr. 2010), 365–370.

- [9] LAUWERS, A., DE POTTER, M., CHAMIRIAN, O., LINDSAY, R., DEMEURISSE, C., VRANCKEN, C., AND MAEX, K. Silicides for the 100-nm node and beyond: Co-silicide, co(ni)-silicide and ni-silicide. *Microelectronic Engineering* 64, 1-4 (Oct. 2002), 131–142.

- [10] LAVOIE, C., D'HEURLE, F. M., DETAVERNIER, C., AND CABRAL, C. Towards implementation of a nickel silicide process for cmos technologies. *Microelectronic Engineering* 70, 2-4 (Nov. 2003), 144–157.

- [11] LEE, P. S., MANGELINCK, D., PEY, K. L., DING, J., DAI, J. Y., HO, C. S., AND SEE, A. On the ni-si phase transformation with/without native oxide. *Microelectronic Engineering* 51-52 (May 2000), 583-594.

- [12] MA, D., CHI, D., LOOMANS, M., WANG, W., WONG, A., AND CHUA, S. Kinetics of nisi-to-nisi2 transformation and morphological evolution in nickel silicide thin films on si(0ă0ă1). *Acta Materialia* 54, 18 (Oct. 2006), 4905–4911.

- [13] Morimoto, T., Ohguro, T., Momose, S., Iinuma, T., Kunishima, I., Suguro, K., Katakabe, I., Nakajima, H., Tsuchiaki, M., Ono, M., Katsumata, Y., and Iwai, H. Self-aligned nickel-mono-silicide technology for high-speed deep submicrometer logic cmos ulsi. *Electron Devices, IEEE Transactions on* 42, 5 (1995), 915–922.

- [14] MURARKA, S. P. Silicide thin tilms and their applications in microelectronics. *Intermetallics* 3, 3 (1995), 173–186.

- [15] NASH, P., AND NASH, A. The niâĹŠsi (nickel-silicon) system. *Journal of Phase Equilibria* 8, 1 (Feb. 1987), 6–14.

- [16] Nemouchi, F., Mangelinck, D., Lábár, J., Putero, M., Bergman, C., and Gas, P. A comparative study of nickel silicides and nickel germanides: Phase formation and kinetics. *Microelectronic Engineering* 83, 11-12, 2101–2106.

- [17] NG, K., AND LYNCH, W. The impact of intrinsic series resistance on mosfet scaling. *Electron Devices, IEEE Transactions on DOI 34*, 3 (1987), 503–511.

- [18] SEGER, J., HELLSTROM, P.-E., Lu, J., Malm, B. G., von Haartman, M., Ostling, M., and Zhang, S.-L. Lateral encroachment of ni-silicides in the source/drain regions on ultrathin silicon-on-insulator. *Appl. Phys. Lett.* 86, 25 (June 2005), 253507–3.

- [19] Wagner, R. S., and Ellis, W. C. Vapor-liquid-solid mechanism of single crystal growth. *Appl. Phys. Lett.* 4, 5 (Mar. 1964), 89–90.

- [20] Weber, W. M., Geelhaar, L., Graham, A. P., Unger, E., Duesberg, G. S., Liebau, M., Pamler, W., Cheze, C., Riechert, H., Lugli, P., and Kreupl, F. Silicon-nanowire transistors with intruded nickel-silicide contacts. *Nano Letters* 6, 12 (Dec. 2006), 2660–2666.

- [21] Wu, Y., Xiang, J., Yang, C., Lu, W., and Lieber, C. M. Single-crystal metallic nanowires and metal/semiconductor nanowire heterostructures. *Nature* 430, 6995 (July 2004), 61–65.

- [22] Zhang, S.-L., and Smith, U. Self-aligned silicides for ohmic contacts in complementary metal—oxide—semiconductor technology: Tisi[sub 2], cosi[sub 2], and nisi. J. Vac. Sci. Technol. A 22, 4 (July 2004), 1361–1370.

# Chapter 2

## Contacts on Silicon nanowires.

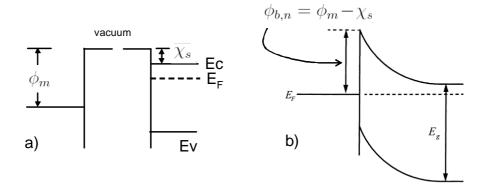

#### 2.1 The Schottky barrier

For electronic applications using Silicon nanowires making satisfactory contacts is of crucial importance. In semiconductor technology the issue of carrier injection from metallic leads to the semiconductors is vital because in all the applications is very important to model and taylor the contact properties for a correct device operation. Metal-semiconductor contacts have been studied extensively since the beginning of the  $20^{th}$  century and the widely accepted model is called Schottky barrier (SB)[24]. When a metal is put in intimate contact with a semiconductor a barrier is formed at the interface fig.(2.1). Its height and width controls the carrier injection from the metal and collec-

**Figure 2.1:** Schematic energy band diagram between a metal and a semiconductor when a) they are separated or b) form an interface

tion from the semiconductor. The formation of the barrier is due to the misalignment between the Fermi levels in the metal and semiconductor. At equilibrium the two Fermi levels must line up and this is accomplished by a charge transfer from the metal or the semiconductor throught the contact interface. Depending wheter the semiconductor is n or p-type its Fermi level lowers or raises respectively with respect to the metal Fermi level by an amount equal to the difference between the two working functions of the

two materials. The working function is just the energy gap between the vacuum level and the Fermi level. The charge transfer builds up an electric field extending in the semiconductor through a region depleted of carriers whose width depends on the doping level of the semiconductor. The space charged region in the semiconductor is balanced by a surface charge layer equal in magnitude and opposite in sign on the metal. The SB is the misalignment at the interface between the metal conduction band and the semiconductor conduction or valence band. This misalignment poses a barrier to the carrier flow, either electrons or holes depending on the majority type of carriers in the semiconductor. To a first order, for a *n*-type semiconductor the Schottky Barrier Height (SBH) is given by

$$\phi_{b,n} = \phi_m - \chi_s \tag{2.1}$$

where  $\phi_m$  and  $\chi_s$  are the metal work function and the semiconductor electronic affinity respectively. Conversely, for a p-type semiconductor

$$\phi_{b,p} = E_g - (\phi_m - \chi_s) \tag{2.2}$$

where  $E_g$  is the energy gap of the semiconductor. In practice however these simple expressions for the barrier heights based on the bare knowledge of the working function and electronic affinity of the materials don't apply in the majority of cases and deviation of the SBH from the simple predictions of equations (2.1),(2.2) are caused by the presence of interface states which can have different origin. The height and width of

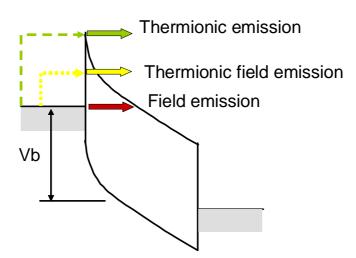

**Figure 2.2:** Schematic of the principal transport mechanisms occurring across a biased interface between a metal and a *n*-type semiconductor where a sizeable SB is present.

the SB influences the carrier injection from the metallic contact and several transport mechanisms can be identified across the barrier. For simplicity we can limit ourselves to the three transport mechanisms depicted schematically in fig.(2.2). With or without external applied bias the carriers can be thermally emitted over the SB since at any non zero temperature the carrier density at any finite energy is not zero due to the Fermi- Dirac statistics. In presence of an external bias voltage the curvature of the semi-conductor bands at the interface can be modified such that the carriers can be firstly thermally emitted to an intermediate energy between the Fermi level of the metal and

the top of the SB and then tunnel through the SB. Lastly, the carriers can be subjected to a bare field emission across the barrier which is a pure tunneling process not assisted by the thermal energy. The complete expression at a given temperature T for the current density across a metal-semiconductor interface taking into account thermionic, field emission and tunneling reads:

$$J = A^{\star} T^2 exp\left(-\frac{q\phi_b}{kT}\right) \left[exp\left(\frac{qV}{kT}\right) - 1\right]$$

(2.3)

where  $\phi_b$ ,  $A^*$  and V are the SBH, the Richardson constant and the potential applied respectively. Equation 2.3 describes the transport across a metal-semiconductor junction commonly referred as Schottky junction. In the limit of low SBH and/or high doping level for the semiconductor the resistance associated to the barrier can be made negligibly small as compared to the total resistance of the semiconductor device. In this case the contact is said to be ohmic. To better understand the role of the SB in the device electrical performances I fabricated devices from different types of silicon nanowires: undoped, with heavily doped edges and uniformly doped. The doping of the nanowires was achieved in-situ during the growth using phosphine (PH<sub>4</sub>) as precursor gas to incorporate phosphorous atoms giving rise to n-type doping. It was possible also to grow modulation doped nanowires by removing the feeding gas carrying the dopant precursor. In this way n-type/intrinsic/n-type (nin) nanowires could be grown. The nanowires were doped with a feed gas ratio P:Si=2 × 10<sup>-2</sup>. Fig.(2.3) compares room temperature

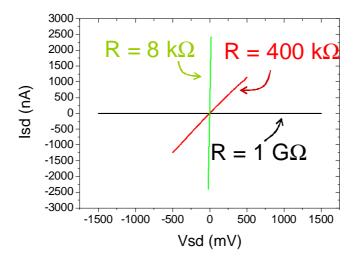

Figure 2.3: IV comparison between nanowires with degenerate uniform n-type doping (green curve), heavily doped sections with an intrinsic channel (red curve) and undoped (black curve). In all the three cases the contacting material is Nickel and the channel length is  $1\mu$ m.

IV characteristics for the three kinds of samples contacted by nickel electrodes without silicidation. Doping has a substantial effect on the overall electrical resistance. Although the channel length for all the three devices was  $1\mu$ m the highly doped device has a metallic behaviour with a resistance of  $8k\Omega$  while the nin nanowire with the contacts

patterned on top of the heavily doped sections has a resistance of  $400k\Omega$ . These resistances are orders of magnitude lower than the device resistances for undoped nanowires. In these devices transport is strongly limited by the SB. The SB in all the three cases is the same since the nanowires were contacted with the same metal. However, doping the nanowires has the effect of thinning down the SB and enhance the tunneling component of transport across it such that the contact behaviour becomes ohmic. Although both the uniformly doped and the modulation doped nanowires had low contact resistances allowing an easy carrier injection even at low temperatures (4K), we preferred focus our attentions on intrinsic nanowires for different reasons. Nanowires with uniform doping, have metallic character which translates in a poor or even absent electrostatic control of the carrier density in the channel. This is an important requirement for all the studies which focus on carrier interaction in low dimensional systems. The modulation doped nanowires on the other hand could not be grown with enough flexibility in terms of length and diameter of the intrinsic channel. Ideally the channel length and thickness should be sufficiently small for single electronic effects to take place. In view of these difficulties we focused our attention on undoped nanowires that could be grown with diameters as small as 20nm. Moreover, the conductance of these undoped wires could be modulated over several orders of magnitude with the aid of a gate voltage.

# 2.2 Undoped Silicon nanowires: impact of the silicidation on the electrical properties

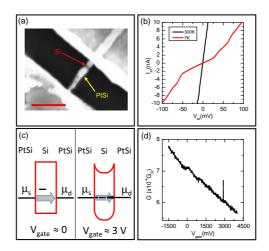

In this section the results obtained for the control of the silicide formation will be used for the fabrication of devices with specific architectures. Silicidation of the contacts has an important impact on the transport properties of silicon nanowires [11]. This is particularly evident in the case where the nanowires are not intentionally doped during the growth. As grown undoped silicon nanowires have a residual p-type background doping arising most probably by acceptor states introduced by the gold catalyst [28]. Fig.(2.4a) shows the IV characteristics of an undoped silicon nanowire contacted by Nickel electrodes before and after a thermal treatment leading to the formation of two silicide extensions extending from the contacts. The formation of the silicides greatly improved the two point resistance of the device. Before the annealing the current flowing in the device is vanishingly small and its detection is beyond the instrumental capabilities. A final resistance around  $130\mathrm{M}\Omega$  is achieved after annealing the contacts for 5 minutes at  $500^{\circ}\mathrm{C}$ . A rectifying behaviour fig.(2.4b) is instead observed in the case where just one contact is silicided. The formed silicide will ease the transport of carriers across the Schottky barrier at the corresponding contact.

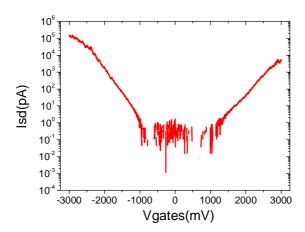

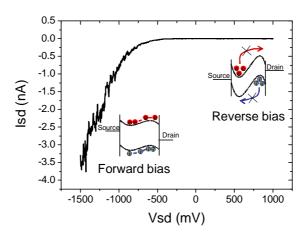

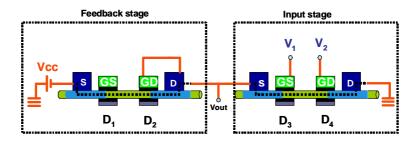

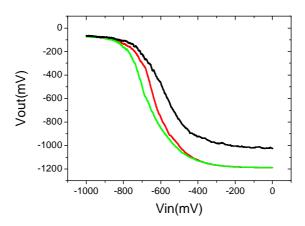

# 2.3 Transport properties of multigated Schottky barrier transistors

Functional devices built from CVD grown silicon nanowires have drawn particular attention in view of their potential to fulfill the demands for the ultimate downscaling of conventional MOSFETs.

Figure 2.4: IV comparisons before and after annealing of the contacts (red and black curves respectively) for 100nm diameter undoped nanowires leading to the formation of a Nickel silicide. The unannealed devices have extremely high resistances and current flow was not detectable. In a) the silicide was extending from both the contacts and the IV characteristic after the annealing is symmetric. In b) only the drain contact was silicided and the characteristic shows a rectifying behaviour. Holes can be efficiently injected from the silicided contact having a lower Schottky barrier as compared as to the non silicided one. The inset shows a schematic band diagram for a negative source-drain bias. Holes are injected from the silicided drain contact while for positive bias the higher Schottky barrier at the source contact limits the carrier injection. Insets: SEM micrograph of the devices, scale bar  $1\mu m$

Concerning the use of Silicon nanowires (SiNWs) as MOSFETs, the ultimate request of scalability and device performance demands for the use of intrinsic material to avoid issues associated with dopant diffusion and fluctuation [4] and to tackle the request for low power static consumption.

A key point for the successful operation of electronic devices assembled from bottomup nanostructures like semiconductor nanowires or carbon nanotubes is to achieve efficient carrier injection. This becomes particularly challenging when no intentional doping is present in the nanostructures since a sizeable Schottky barrier develops between the metal and the semiconductor which is not thinned down in the region close to the contacts by the local field produced by the ionized dopants.

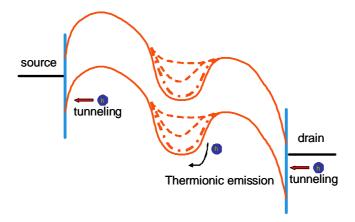

Undoped silicon nanowires with metallic source and drain leads made out of silicide, can be considered as good candidates to face the challenges of extreme device downscaling. This option takes advantage from the very low parasitic contact resistances of the metal silicide as compared to heavily doped source/drain silicon contacts, from high scalability in terms of channel length and width which can be pushed well beyond the limits of conventional lithography, from the low thermal budget required for the formation of the silicide contact [17]. Bottom-up silicon nanowire transistors have been extensively reported in the literature [9],[11],[25],[26],[19],[13],[8] but an exhaustive description of their transport properties is still lacking. The operation of such devices is strongly influenced by the contact properties where transport is determined by a combination of field and thermionic emission over the SB. These two physical mechanisms compete between them to give the overall current response and they can be ultimately controlled by the action of a gate induced electric field producing a band bending in correspondence of the contact regions.

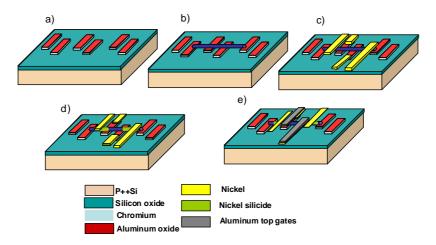

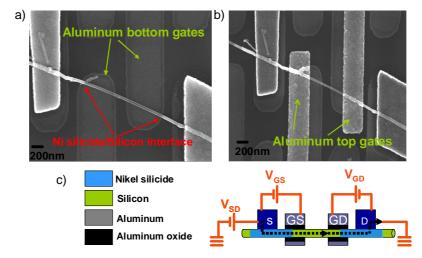

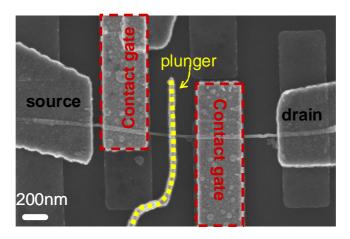

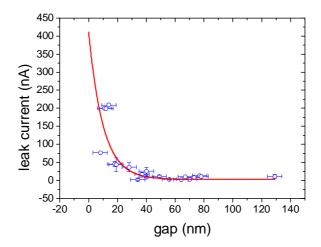

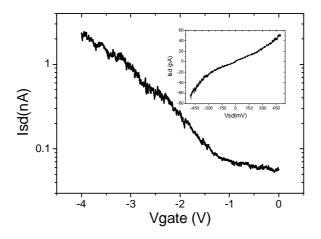

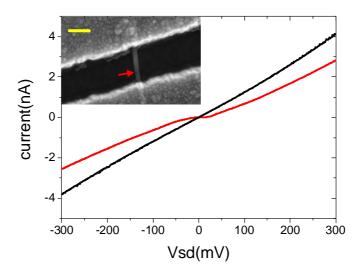

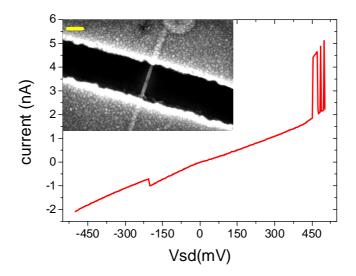

The approach pursued in my PhD work is local gating of the contact SB. I have investigated the possibility to individually control the contacts and the channel region of a silicon nanowire device by means of independent gate electrodes. The capability to address independently in the same device the gating fields allows not only a quantitative extraction of the energy barrier at specific locations but also the implementation of different functionalities on one single nanowire. This local gating approach requires two or three independent gates. A key issue for controlling the carrier injection and extraction is the physical identification of the contact regions. In our system this is obtained through the controlled formation of metallic nickel silicide phases protruding from the contacts. The formation of such metallic phases is accomplished by a thermal annealing process which promotes the diffusion of nickel atoms through the silicon lattice to form a sharp interface between the silicide and the silicon. Injection and extraction of the carriers is taking place at these interfaces which are away from the as-deposited metal contact to allow for efficient gating. A substantial band bending at these interfaces can be achieved since the gating fields are not screened by the large contacts defined by lithography. The gating of the nanowire in correspondence of the injection junctions is accomplished via a Gate-All-Around geometry which gives the best electrostatic coupling [23]. Fig. (2.5) describes the process flow adopted for the fabrication of the samples. The preparation