# Technologie d'intégration monolithique des JFET latéraux

Farah Laariedh

## ▶ To cite this version:

Farah Laariedh. Technologie d'intégration monolithique des JFET latéraux. Autre. INSA de Lyon, 2013. Français. NNT: 2013ISAL0031. tel-00940370

# HAL Id: tel-00940370 https://theses.hal.science/tel-00940370

Submitted on 31 Jan 2014

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Thèse

# Technologie d'intégration monolithique des JFET latéraux

Présentée devant L'institut national des sciences appliquées de Lyon

> Pour obtenir Le grade de docteur

Formation doctorale : Génie électrique École doctorale: EEA de Lyon

Par

# Farah Laariedh

Soutenue le 13 Mai 2013 devant la Commission d'examen

#### Jury MM.

Président Jean François Barbot, Professeur (Institut Pprime, Poitiers) Rapporteur Konstantinos Zekentes, Professeur (IESL, Grèce)

Rapporteur Jean François Barbot, Professeur (Institut Pprime, Poitiers)

Adel Kalboussi, Professeur (FSM, Tunisie)

Jean Louis Leclercq Chargé de recherche (CNRS) (ECL de Lyon)

Mihai Lazar Chargé de recherche (CNRS) (INSA de Lyon)

Dominique Planson Professeur (INSA de Lyon)

Laboratoire de recherche : AMPERE

| SIGLE     | ECOLE DOCTORALE                                                                                                                                            | NOM ET COORDONNEES DU<br>RESPONSABLE                                                                                                                                                                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СНІМІЕ    | CHIMIE DE LYON http://www.edchimie-lyon.fr Insa: R. GOURDON                                                                                                | M. Jean Marc LANCELIN Université de Lyon – Collège Doctoral Bât ESCPE 43 bd du 11 novembre 1918 69622 VILLEURBANNE Cedex Tél : 04.72.43 13 95 directeur@edchimie-lyon.fr                                |

| E.E.A.    | ELECTRONIQUE, ELECTROTECHNIQUE, AUTOMATIQUE http://edeea.ec-lyon.fr  Secrétariat: M.C. HAVGOUDOUKIAN                                                       | M. Gérard SCORLETTI Ecole Centrale de Lyon 36 avenue Guy de Collongue 69134 ECULLY Tél: 04.72.18 65 55 Fax: 04 78 43 37 17 Gerard.scorletti@ec-lyon.fr                                                  |

| E2M2      | eea@ec-lyon.fr  EVOLUTION, ECOSYSTEME, MICROBIOLOGIE, MODELISATION  http://e2m2.universite-lyon.fr  Insa: H. CHARLES                                       | Mme Gudrun BORNETTE CNRS UMR 5023 LEHNA Université Claude Bernard Lyon 1 Bât Forel 43 bd du 11 novembre 1918 69622 VILLEURBANNE Cédex Tél: 06.07.53.89.13 e2m2@ univ-lyon1.fr                           |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-SANTE  http://www.ediss-lyon.fr  Sec : Samia VUILLERMOZ Insa : M. LAGARDE                                                      | M. Didier REVEL  Hôpital Louis Pradel  Bâtiment Central 28 Avenue Doyen Lépine 69677 BRON Tél: 04.72.68.49.09 Fax:04 72 68 49 16 Didier.revel@creatis.uni-lyon1.fr                                      |

| INFOMATHS | INFORMATIQUE ET MATHEMATIQUES  http://infomaths.univ-lyon1.fr  Sec :Renée EL MELHEM                                                                        | Mme Sylvie CALABRETTO Université Claude Bernard Lyon 1 INFOMATHS Bâtiment Braconnier 43 bd du 11 novembre 1918 69622 VILLEURBANNE Cedex Tél: 04.72. 44.82.94 Fax 04 72 43 16 87 infomaths@univ-lyon1.fr |

| Matériaux | MATERIAUX DE LYON http://ed34.universite-lyon.fr  Secrétariat: M. LABOUNE PM: 71.70 -Fax: 87.12 Bat. Saint Exupéry Ed.materiaux@insa-lyon.fr               | M. Jean-Yves BUFFIERE INSA de Lyon MATEIS Bâtiment Saint Exupéry 7 avenue Jean Capelle 69621 VILLEURBANNE Cedex Tél: 04.72.43 83 18 Fax 04 72 43 85 28 Jean-yves.buffiere@insa-lyon.fr                  |

| MEGA      | MECANIQUE, ENERGETIQUE, GENIE CIVIL, ACOUSTIQUE http://mega.ec-lyon.fr  Secrétariat: M. LABOUNE PM: 71.70 -Fax: 87.12 Bat. Saint Exupéry mega@insa-lyon.fr | M. Philippe BOISSE INSA de Lyon Laboratoire LAMCOS Bâtiment Jacquard 25 bis avenue Jean Capelle 69621 VILLEURBANNE Cedex Têl :04.72 .43.71.70 Fax : 04 72 43 72 37 Philippe.boisse@insa-lyon.fr         |

| ScSo      | ScSo* http://recherche.univ-lyon2.fr/scso/ Sec: Viviane POLSINELLI Brigitte DUBOIS                                                                         | M. OBADIA Lionel<br>Université Lyon 2<br>86 rue Pasteur<br>69365 LYON Cedex 07<br>Tél: 04.78.77.23.86 Fax: 04.37.28.04.48                                                                               |

Remerciements

Je tiens à débuter ces remerciements en exprimant toute ma gratitude à Dominiqe Planson

et Mihai Lazar qui ont dirigé cette thèse. Merci de m'avoir fait confiance, de m'avoir encadré

comme vous l'avez fait, d'avoir su donner de votre temps lorsque c'était nécessaire.

Mes remerciements vont aussi à Jean-Louis Leclercq pour les échanges scientifiques

intéressants que nous avons pu avoir durant ces quelques années et pour l'examen final de ce

manuscrit.

Je voudrais remercier Jean-François Barbot d'être le rapporteur et d'avoir accepté de présider

le jury de ma soutenance de thèse. Merci à Konstantinos Zekentes de m'avoir fait l'honneur

d'être le rapporteur de ces travaux de recherche. Je remercie également Adel Kalboussi

d'avoir accepté d'examiner ces travaux.

Ces travaux n'auraient pas pu être réalisés sans l'aide des membres de la plate forme

NanoLyon. Je les remercie tous pour le travail qu'ils réalisent, en particulier Pierre Cremillieu

qui m'a pris en charge pendant mes travaux en salle blanche. Je remercie également Radoslaw

Mazurczyk, Khaled Ayad et Joëlle Grégoire et ceux que j'aurais oubliés.

Pour les mêmes raisons, je souhaite remercier les membres de l'équipe EPI, Nicolas, Thibault,

Stan, Raphaël, Amira, Pascal, Maher, Alaa, Hassen, Cyril, Jonathan, Arthur, Tony...

Un grand merci à Davy Carole pour les analyses EDX et José Penuelas pour les analyses

DRX ainsi qu'à Christiane Dubois pour les analyses SIMS.

Merci aux personnes du laboratoire Ampère et Institut de Nanotechnologie de Lyon avec

lesquelles j'ai eu l'occasion de travailler durant cette thèse.

Farah Laariedh / "Technologie d'intégration monolithique des JFET latéraux" Thèse INSA de Lyon – AMPERE

4

## Résumé:

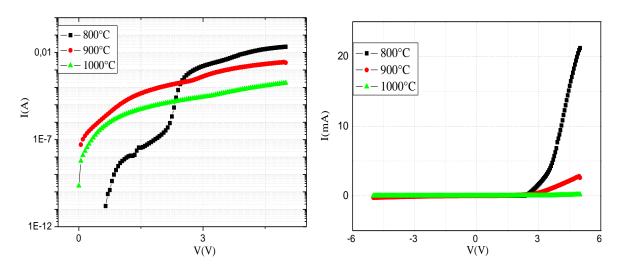

Le carbure de silicium (SiC) est un semi-conducteur à large bande d'énergie interdite, remarquable par ses propriétés physiques situées à mi-chemin entre le silicium et le diamant. Ceci suscite actuellement un fort intérêt industriel pour son utilisation dans la fabrication de composants susceptibles de fonctionner dans des conditions extrêmes : forte puissance et haute température. Les travaux de thèse se sont focalisés sur la levée de verrous technologiques pour réaliser des composants latéraux de type JFET (Junction Field Effect Transistor) et les intégrer monolithiquement dans des substrats SiC-4H. L'objectif est de réaliser un bras d'onduleur intégré en SiC avec deux étages commande et puissance. Dans un premier temps, nous avons entamé cette thèse par une caractérisation de deux lots de composants JFET latéraux à canaux N et P réalisés dans le cadre de deux projets ANR précédents cette thèse. De cette étude nous avons extrait plusieurs points positifs, comme celui qui concerne la tenue en tension des JFET de puissance et l'intégration monolithique des JFET basse tension. Mais, nous avons aussi mis en évidence, la nécessité d'optimiser la structure de composants et d'améliorer certaines étapes technologiques, principalement, la définition des canaux par implantation ionique, le contact ohmique et la gravure profonde. Des études approfondies pour réaliser le contact ohmique sur SiC type P et des procédés pour réaliser une gravure profonde dans le SiC ont été développés. Ces études ont permis d'obtenir une faible résistance de contact comparable à l'état de l'art mondial, d'avoir des calibres en courant plus élevés et par conséquent une meilleure modulation. Pour la gravure, un masque dur à base de silicium et nickel (NiSi), nous a permis de mettre en place un procédé original qui permet des gravures profondes du SiC et réaliser les structures intégrés des JFET. L'ensemble de ces améliorations technologiques nous a permis d'obtenir des nouveaux lots de composants JFET P et N intégrés sur la même puce, avec des meilleures performances par rapport aux précédentes réalisations, notamment avec une conduction dans les canaux 10 à 100 fois plus importante. Nous avons également obtenu une modulation du courant I<sub>ds</sub> en fonction de la tension V<sub>gs</sub> sur un nombre très important de JFET en augmentant significativement le rendement par rapport aux lots précédents.

**Mots-Clés**: Carbure de silicium, JFET latéraux, Contact ohmique, Gravure profonde, Caractérisation électriques.

**Abstract:**

Silicon carbide (SiC) is as a wide band gap semiconductor, notable for its physical

properties at midway between silicon and diamond. The interesting properties of silicon

carbide as high thermal conductivity and high breakdown voltage make it a very promising

material for high power, high temperature and high-frequency device applications.

The thesis focused on the removal of technological barriers to achieve lateral JFET (Junction

Field Effect Transistor) monolithically integrated in 4H-SiC substrates.

The final objective is to realize an inverter in SiC by integrating the two stages command and

power.

Initially, we started this thesis by electrical characterization of two batches of JFET with N

and P-type channels. These devices have been realized during two previous ANR projects.

In this study, we extracted several positive points, such, the breakdown voltage of the power

JFET which correspond to the escomtated value. The monolithic integration of the low

voltage JFET stage was also demonstrated. But we have also highlighted the need to optimize

the device structures and improve some technological steps, mainly the definition channels by

ion implantation, the ohmic contact and deep etching.

Therefore we focused our study to achieve ohmic contact on SiC P-type and to find methods

for performing deep etching in SiC. These studies have resulted in a low specific contact

resistance comparable to the world state of the art on the ohmic contact on P-type SiC. Low

contact resistances will allow us to obtain higher current and a better modulation on our JFET

devices.

Concerning the SiC etching, a hard mask of silicon and nickel (NiSi) has enabled us to

develop a novel method that allows us to obtain deep and tight etching structures, very useful

to achieve the JFET integrated devices

All these technological improvements allowed us to fabricate new batches of P and N-type

JFET integrated on the same chip with better performance compared to previous

achievements, especially with a conduction channels 10 to 100 times higher. We also got a

modulation current Ids as a function of the voltage Vgs on a large number of JFET

significantly increasing the performance compared to previous batches.

**Keywords:** Silicon Carbide, Ohmic contact, deep etching, electrical characterization, JFET.

Farah Laariedh / "Technologie d'intégration monolithique des JFET latéraux" Thèse INSA de Lyon – AMPERE

6

# **Sommaire**

| Introduction générale                                                               | 11 |

|-------------------------------------------------------------------------------------|----|

| Chapitre 1: Le carbure de silicium pour l'intégration de composant<br>électroniques | ts |

| Introduction                                                                        |    |

| 1.1 Contexte - Positionnement du carbure de silicium                                | 18 |

| 1.1.1 Propriétés physiques du SiC                                                   | 20 |

| 1.1.2 Facteur de mérite du SiC                                                      |    |

| 1.1.3 Propriétés électroniques intrinsèques du SiC                                  | 22 |

| 1.2 Etat de l'art de la filière du carbure du silicium                              |    |

| 1.2.1 Fournisseurs de substrat SiC                                                  |    |

| 1.2.2 Aspects cristallographiques                                                   |    |

| 1.2.3 Défauts dans le SiC                                                           |    |

| 1.3 Spécificités technologiques du SiC                                              |    |

| 1.3.1 L'épitaxie du SiC                                                             | 29 |

| 1.3.2 Dopage                                                                        | 31 |

| 1.3.2.1 Eléments dopants                                                            |    |

| 1.3.2.2 Dopage in situ                                                              | 31 |

| 1.3.2.3 Dopage localisé par diffusion                                               |    |

| 1.3.2.4 Dopage localisé par implantation ionique                                    |    |

| 1.3.3 La gravure du SiC                                                             |    |

| 1.3.3.1 Gravure humide                                                              | 34 |

| 1.3.3.2 Gravure sèche par plasma                                                    |    |

| 1.3.3.2.1 Propriétés du plasma.                                                     |    |

| i) Interaction plasma-surface                                                       |    |

| ii) sélectivité de la gravure                                                       |    |

| 1.3.3.2.2 Les principaux réacteurs                                                  |    |

| a) RIE (Reactive Ion Etching)                                                       |    |

| b) ICP (Inductively Coupled Plasma)                                                 |    |

| 1.3.3.2.2 Synthèse des procédés utilisées dans la gravure du SiC                    |    |

| 1.3.4 Le contact ohmique sur le SiC                                                 |    |

| 1.3.4.1 Le contact ohmique sur SiC-4H type N                                        |    |

| 1.3.4.2 Le contact ohmique sur SiC-4H type P                                        |    |

| 1.3.5 Packaging                                                                     |    |

| 1.3.6 Passivation                                                                   |    |

| 1.3.6.1 Passivation primaire                                                        |    |

| 1.3.6.2 Passivation secondaire                                                      |    |

| 1.4 Les composants d'électronique de puissance en SiC                               |    |

| 1.4.1 Les diodes en SiC                                                             |    |

| 1.4.2 Le JFET                                                                       |    |

| 1.4.3 Le MOSFET                                                                     |    |

| 1.4.4 Le BJT                                                                        |    |

| 1.5 L'intégration en électronique de puissance                                      |    |

| 1.5.1 Pourquoi l'intégration en électronique de puissance                           |    |

| 1.5.2 Vers l'intégration monolithique                                               |    |

| 1.6. Conclusion du chapitre:                                                        |    |

| 1.7. Références:                                                                    | 60 |

| Chapitre 2 : Analyse des composants JFET latéraux pour améliorer la                                                         |     |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

| technologie de fabrication                                                                                                  |     |

| 2.1 Le contexte                                                                                                             | 71  |

| 2.2 Description des échantillons                                                                                            | 71  |

| 2.2.1 Description des échantillons de l'étage de puissance (1 <sup>er</sup> lot)                                            |     |

| 2.2.2 Description de l'échantillon de l'étage de commande basse puissance                                                   |     |

| 2.3 Caractérisations électriques des composants                                                                             |     |

| 2.3.1. Méthodologie de l'analyse I-V                                                                                        |     |

| 2.3.2 Résultats sur les composants de puissance                                                                             | 84  |

| 2.3.2.1 Etude préliminaire des JFET type N (FL0288-09)                                                                      | 84  |

| 2.3.2.1.1 Mesures Grille – Source (P <sup>+</sup> -N-N <sup>+</sup> ) et Drain – Source (N <sup>+</sup> -N-N <sup>+</sup> ) | 84  |

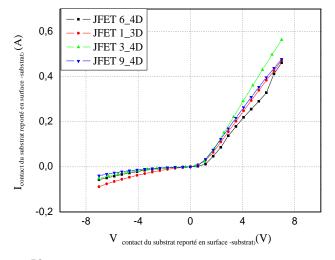

| 2.3.2.1.2 Mesures contact du substrat reporté en surface — Substrat (P <sup>+</sup> -P <sup>-</sup> - P <sup>+</sup> )      |     |

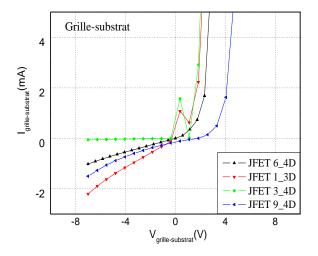

| 2.3.2.1.3 Mesures Grille – Substrat (P <sup>+</sup> -N-P <sup>-</sup> -P <sup>+</sup> )                                     |     |

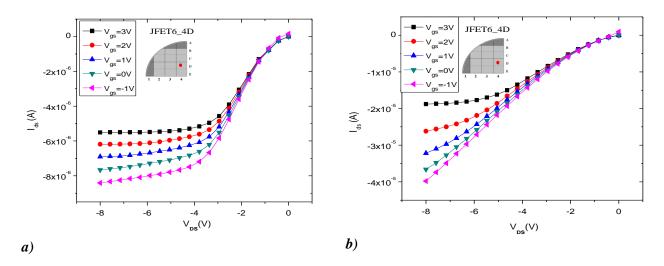

| 2.3.2.2 Fonctionnement des composants JFET type N (FL0288-09)                                                               | 87  |

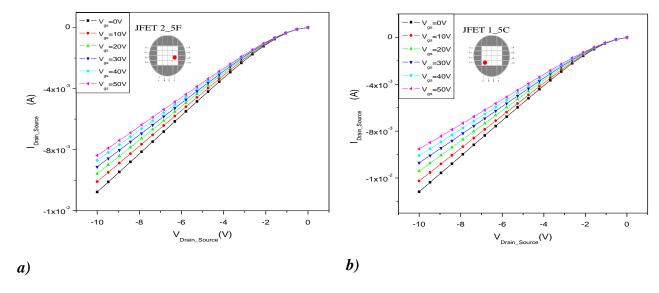

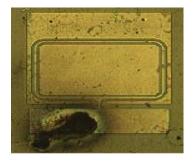

| 2.3.2.2.1 Caractérisation $I_{ds}(V_{ds})$ en fonction de $V_{gs}$                                                          | 87  |

| 2.3.2.4 Etude préliminaire des JFET type P (AE0695-02)                                                                      |     |

| 2.3.2.4.1 Mesures Grille – Source ( $N^+$ -P-P $^+$ ) et Drain – Source ( $P^+$ -P-P $^+$ )                                 | 91  |

| 2.3.2.4.2 Mesures contact de surface reporté en surface – Substrat (N <sup>+</sup> -N <sup>-</sup> -N <sup>+</sup> )        |     |

| 2.3.2.4.3 Mesures Grille – Substrat (N <sup>+</sup> -P-N <sup>-</sup> -N <sup>+</sup> )                                     |     |

| 2.3.2.5 Fonctionnement des composants JFET type P (AE0695-02)                                                               |     |

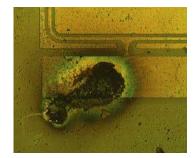

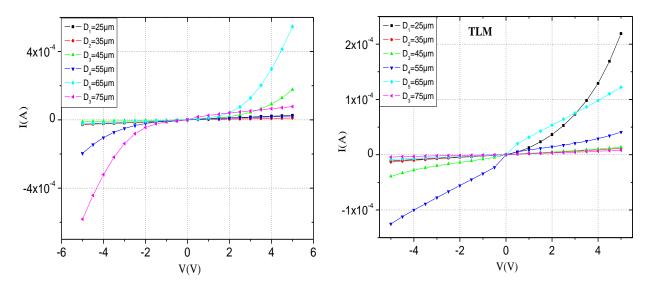

| 2.3.2.6 Mesures TLM                                                                                                         |     |

| 2.3.2.7 Tenue en tension des JFET de puissance                                                                              |     |

| 2.3.2.8 Analyse des résultats obtenus sur les JFET de puissance                                                             |     |

| 2.3.2.8 Analyse des resultats obtenus sur les 31-21 de puissance                                                            |     |

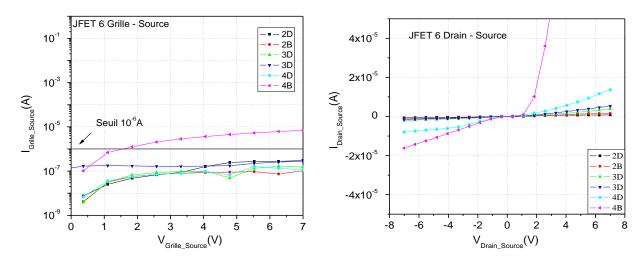

| 2.3.3.1 Etude préliminaire des JFET type N et P (R0413-01)                                                                  |     |

| 2.3.3.1.1 Mesures Grille – Source, Drain – Source                                                                           |     |

| 2.3.3.2 Fonctionnement des composants JFET type N et P (R0413-01)                                                           |     |

|                                                                                                                             |     |

| 2.3.3.3 Mesures TLM                                                                                                         |     |

| 2.3.3.4 Analyse des résultats obtenus sur les JFET de l'étage de commande                                                   |     |

| 2.4 Conclusion du chapitre 2                                                                                                |     |

| 2.5 Références :                                                                                                            | 111 |

| Chapitre 3: Réalisation de contacts ohmiques sur SiC type P                                                                 |     |

| 3.1 Introduction.                                                                                                           | 116 |

| 3.2 Etudes précédentes réalisées au laboratoire Ampère.                                                                     |     |

| 3.2.1 Alliage SiC-Al/Ti                                                                                                     |     |

| 3.2.2 Alliage SiC-Ni/Al                                                                                                     |     |

| 3.2.3 Alliage SiC-Ti/Ni                                                                                                     |     |

| 3.3 Réalisation du contact ohmique Ni/Ti/Al sur SiC-4H type P                                                               |     |

| 3.3.1 Préparation des échantillons et procédé de réalisation des contacts                                                   |     |

| 3.3.1.1 Présentation des substrats utilisés                                                                                 |     |

| 3.3.1.2 Préparation des échantillons                                                                                        |     |

| 3.3.1.3 Procédé de réalisation des contacts                                                                                 |     |

| 3.3.1.3.1 Dépôt des métaux :                                                                                                |     |

| 3.2.1.3.2 Le recuit (description des fours utilisés)                                                                        |     |

| 3.3.2 Caractérisation électrique des contacts                                                                               |     |

| 3.3.2.1 Mesure I(V) à 25 °C                                                                                                 |     |

| 3.3.2.1 Westife I(v) a 25 C                                                                                                 |     |

| 3.3.2.1.2 Contact avec les emplements Ni/Ti/Al/Ni                                                                           |     |

| 5.5.2.1.2 Contact avec tes emphements 14// 11/Al/14                                                                         | 131 |

| 3.3.2.1.2.1 Influence de la température de recuit sur la résistan  |           |

|--------------------------------------------------------------------|-----------|

| contact.                                                           | 132       |

| 3.3.2.1.2 Tableau récapitulatif                                    | 135       |

| 3.3.3 Analyses physico-chimiques des contacts                      | 136       |

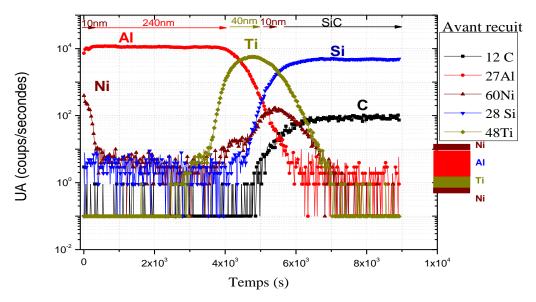

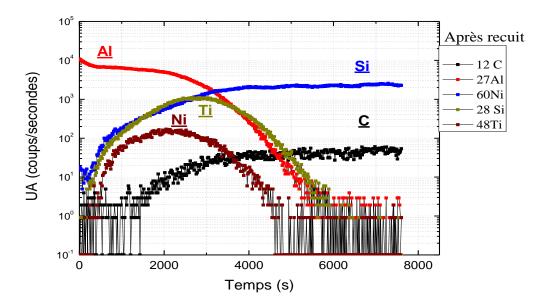

| 3.3.3.1 Analyses SIMS                                              | 136       |

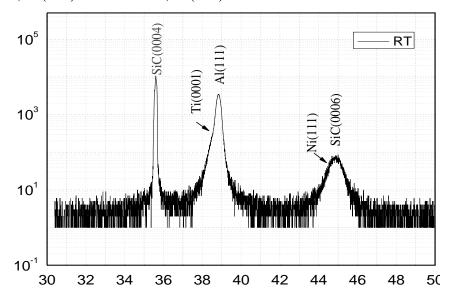

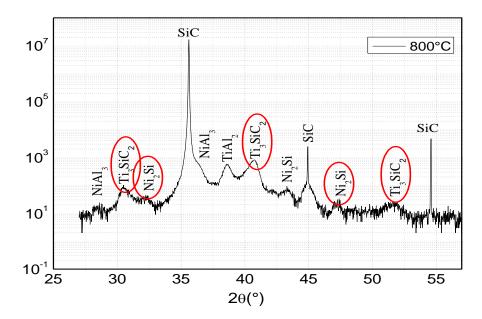

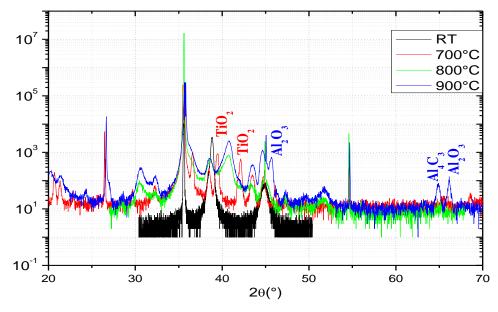

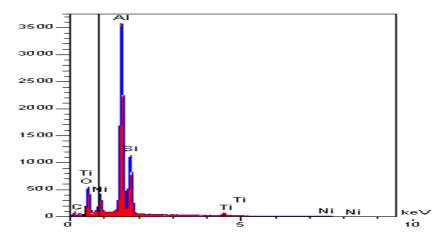

| 3.3.3.2 Analyse DRX                                                |           |

| 3.3.2.3 Analyse EDX                                                |           |

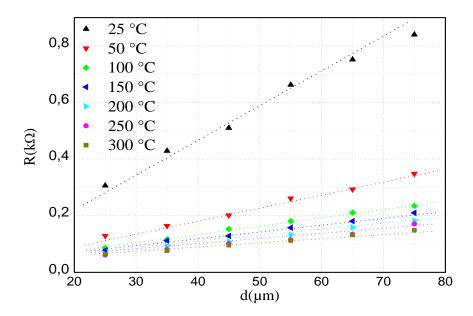

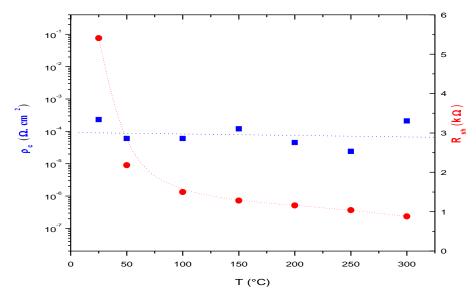

| 3.3.4 Caractérisations électrique des contacts en température      | 143       |

| 3.4 Conclusion.                                                    | 145       |

| 3.5 Références :                                                   | 147       |

| Chapitre 4: Technologie pour l'intégration monolithique de co      | omposants |

| JFET latéraux type N et P en SiC                                   | •         |

| 4.1 Introduction                                                   | 154       |

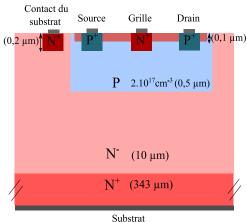

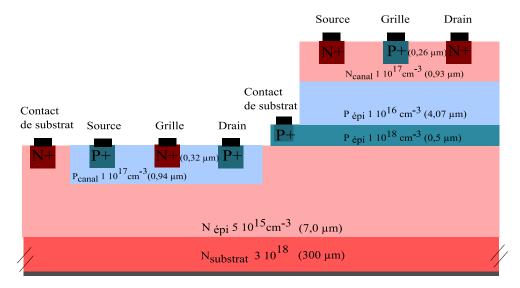

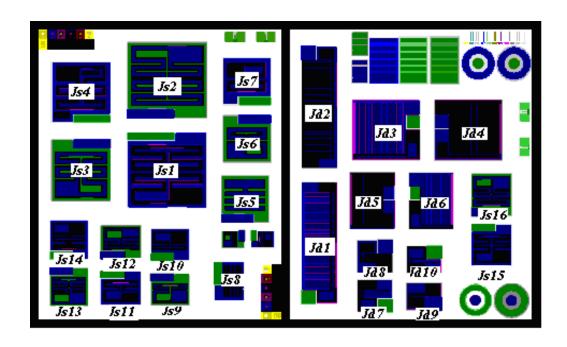

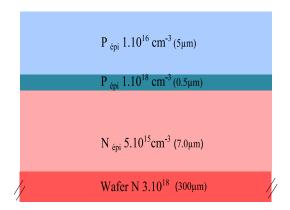

| 4.2 Description des échantillons                                   | 155       |

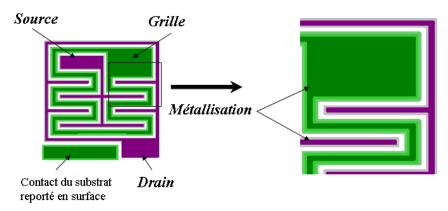

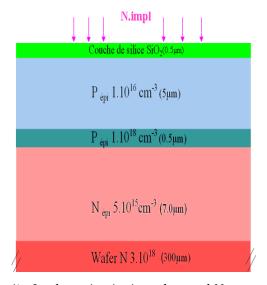

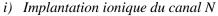

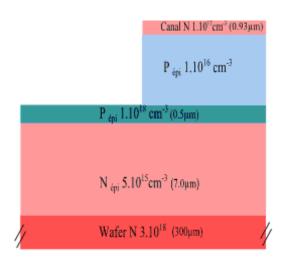

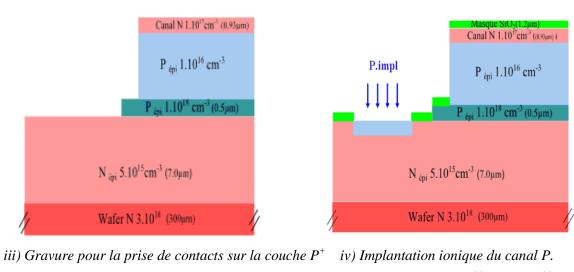

| 4.2.1 Description de l'étage de commande basse puissance           | 156       |

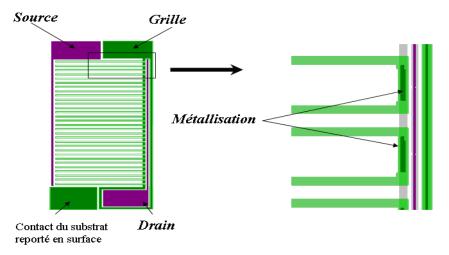

| 4.2.2. Description des échantillons de l'étage de puissance        | 158       |

| 4.2.2.1 Conception la structure gravée de l'étage de puissance     |           |

| 4.2.2.2 Présentation de la structure                               |           |

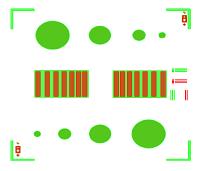

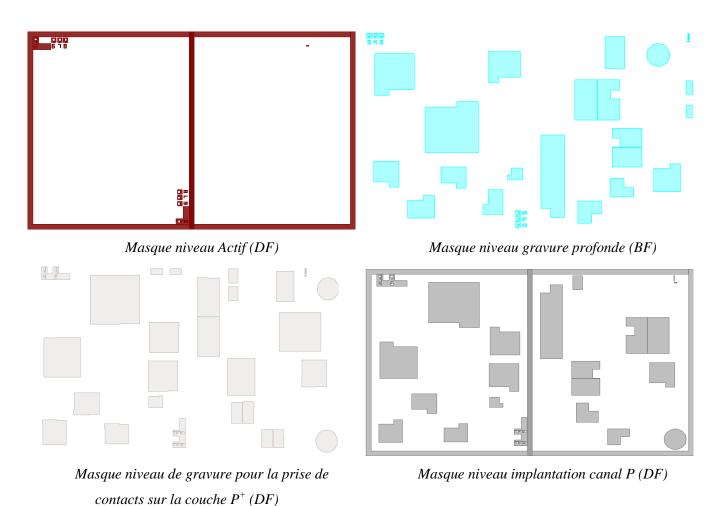

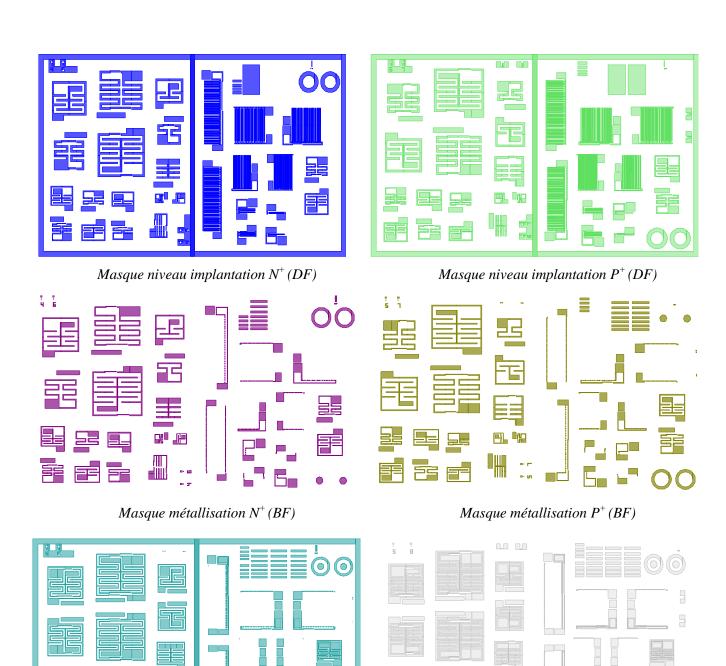

| 4.2.2.3 Organisation du jeu de masques                             | 160       |

| 4.3 Déroulement technologique                                      | 164       |

| 4.3.1 Chimie – nettoyage des surfaces                              |           |

| 4.3.2 Photolithographie                                            |           |

| 4.3.2.1 Nettoyage des masques Cr-verre                             | 167       |

| 4.3.3 Métallisation                                                | 168       |

| 4.3.4 Dopage par implantation ionique                              |           |

| 4.3.4.1 Les simulateurs SRIM et I <sup>2</sup> SiC                 | 169       |

| 4.3.4.2. Masque d'implantation                                     | 170       |

| 4.3.4.3 Implantation d'azote                                       | 172       |

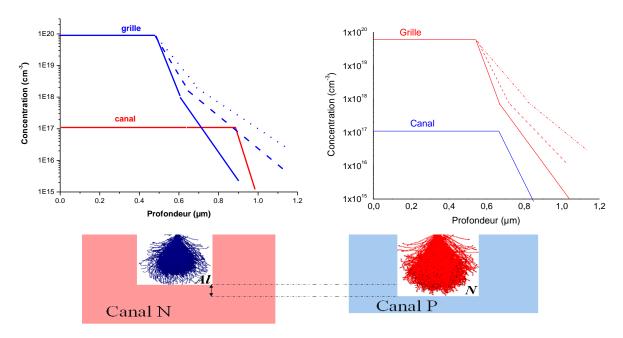

| 4.3.4.3.1 Canal N                                                  | 172       |

| 4.3.4.3.2 Caissons drain, grille, source N <sup>+</sup>            |           |

| 4.3.4.4 Implantation d'aluminium                                   |           |

| 4.3.4.4.1 Canal P                                                  |           |

| 4.3.4.4.2 Caissons drain, grille, source P <sup>+</sup>            |           |

| 4.3.4.5 Recuit post implantation                                   |           |

| 4.3.5 Passivation-isolation.                                       |           |

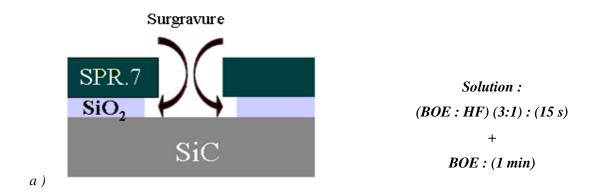

| 4.3.6 La gravure plasma du SiC                                     |           |

| 4.3.6.1 Introduction                                               |           |

| 4.3.6.2 Masque de gravure – sélectivité et volatilité              |           |

| 4.3.6.2.1 Masque Silicium et Carbone                               |           |

| 4.3.6.2.2 Masque TiNiSi                                            |           |

| 4.3.6.2.3 Masques en résines photosensibles                        |           |

| 4.3.7 Diagramme de cheminement                                     |           |

| 4.4 Caractérisations électriques des composants                    |           |

| 4.4.1. Méthodologie de l'analyse I-V                               |           |

| 4.4.2 Résultats sur les composants de puissance                    |           |

| 4.4.2.1 Etude préliminaire                                         |           |

| 4.4.2.1.1 Mesures Drain – Source                                   |           |

| 4.4.2.2 Fonctionnement des composants                              |           |

| 4.4.2.2.1 Caractérisation $I_{ds}(V_{ds})$ en fonction de $V_{gs}$ |           |

| 4.4.2.3 Analyse des résultats obtenus sur les JFET de puissance    |           |

| 4.4.3 Résultats sur les composants de l'étage de commande          | 195       |

| 4.4.3.1 Etude préliminaire                                                | 195 |

|---------------------------------------------------------------------------|-----|

| 4.4.3.1.1 Mesures Drain – Source                                          |     |

| 4.4.3.2 Fonctionnement des composants                                     |     |

| 4.4.3.2.1 Caractérisation $I_{ds}(V_{ds})$ en fonction de $V_{gs}$        |     |

| 4.4.3.3 Analyse des résultats obtenus sur les JFET de l'étage de commande |     |

| 4.4.4 Mesures TLM                                                         |     |

| 4.5 Conclusion du chapitre                                                | 202 |

| 4.6.Références                                                            |     |

| Conclusion générale et perspectives                                       | 204 |

| Annexe 1                                                                  |     |

| Annexe 2                                                                  |     |

| Annexe 3                                                                  |     |

| Annexe 4                                                                  | 226 |

| Folio administratif                                                       | 229 |

# Introduction générale

La miniaturisation des composants électroniques constitue aujourd'hui un axe fort de recherche en soi. Durant les trois dernières décennies, les développements de dispositifs à semiconducteurs de puissance ont abouti à l'apparition de nouveaux composants avec des technologies qui ont atteint des niveaux proches de limites.

Pour améliorer les performances des nouvelles générations de dispositifs de forte puissance ainsi que pour élargir leur spectre de fonctionnement et la gamme d'applications industrielles, le carbure de silicium (SiC) se positionne comme un candidat incontournable, là où le silicium atteint ses limites.

Bien que Schockley aie déjà affirmé dans les années 1950 que le carbure de silicium remplacera le silicium grâce à ses propriétés supérieures [Scho 52], soixante ans après, le silicium est encore le matériau le plus employé dans le domaine de la micro-électronique et des microsystèmes. Cependant dans la majorité des cas le choix du silicium est dû au coût de la matière première et surtout à la maitrise de la technologie de fabrication, plutôt qu'a ses propriétés physiques intrinsèques. En effet, ce matériau atteint rapidement ses limites lorsqu'on travaille à des températures élevées ou à des atmosphères chimiquement agressives. Grâce aux progrès réalisés dans les filières technologiques depuis ces dernières années, plusieurs composants à semi-conducteurs en SiC sont apparus dans le domaine des applications de puissance, de l'industrie automobile, de l'aéronautique, des forages pétroliers. Ces composants représentent aujourd'hui un marché de niche mais leur forte valeur ajoutée rend ce matériau très attractif.

Le laboratoire Ampère mène des recherches depuis plusieurs années pour concrétiser l'intégration d'un onduleur à base de transistors JFET P et N au sein d'une même puce. Après des travaux théoriques qui ont montré la faisabilité de ce système et après une première tentative de fabrication de deux lots de composants, l'objectif de cette thèse a été d'améliorer la technologie de fabrication pour ces composants en réalisant également des nouveaux lots. D'une manière générale, nous avons choisi une technologie SiC et de ne pas traiter le cas du nitrure de galium, GaN qui a aussi de très grands potentiels pour l'intégration de puissance. En effet le SiC conservera probablement un avantage décisif pour les applications à haute température que vise le laboratoire Ampère.

Le chapitre introductif se propose d'établir un état de l'art sur le matériau semiconducteur carbure de silicium. Nous présenterons, dans une première partie, un bref

historique de ce semi-conducteur avant de décrire quelques-unes de ses propriétés structurales, physiques et électroniques qui lui confèrent des aptitudes remarquables pour des utilisations très diversifiées en environnement sévère. Nous expliciterons ensuite les différentes techniques de croissance employées pour l'élaboration de ce matériau et évoquerons enfin les principaux champs d'applications du SiC, pour une utilisation à court terme dans les domaines de l'électronique de puissance.

Nous introduisons dans le deuxième chapitre les résultats de mesures électriques que nous avons réalisées sur des transistors JFET-SiC latéraux fabriqués dans notre laboratoire.

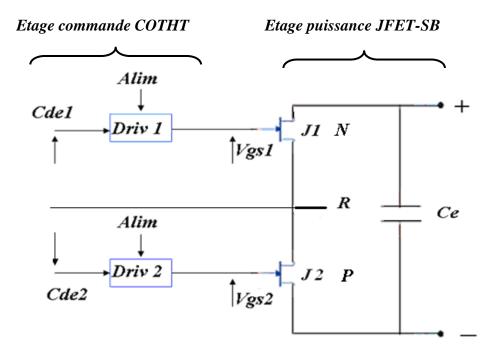

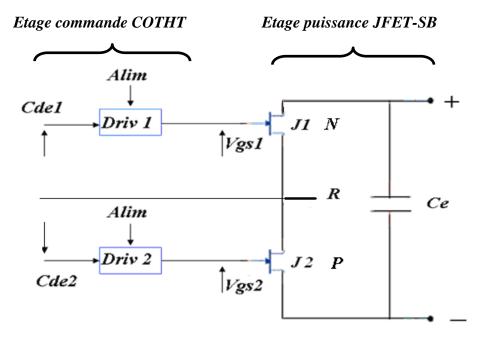

Ce travail a été proposé afin d'approfondir et exploiter d'une manière académique les résultats obtenus dans deux projets ANR, COTHT (COnvertisseurs Très Haute Température) projet blanc 2006-2009 et JFET-SB (JFET Switch Bridge) projet jeune chercheur 2005-2008, dont le laboratoire AMPERE a été porteur. Le but est de comprendre et d'améliorer les différentes briques technologiques afin de relever les performances de nouveaux composants.

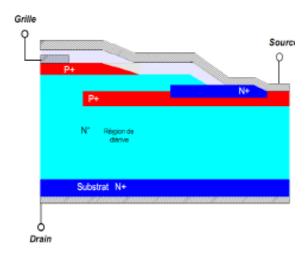

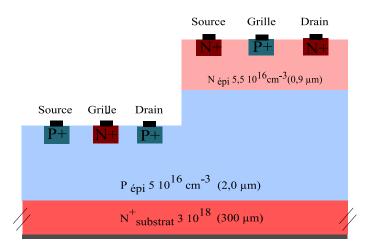

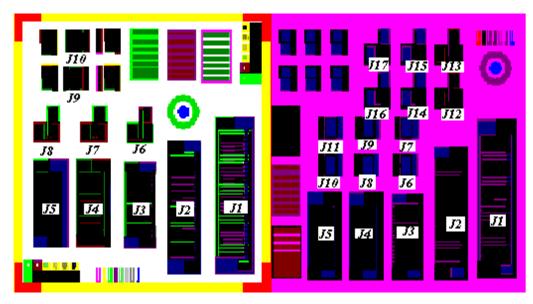

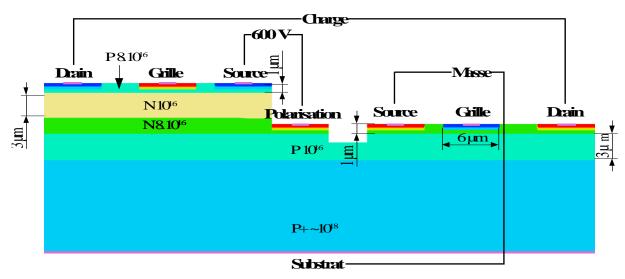

Deux types de transistors JFET latéraux en SiC-4H ont été conçus et fabriqués lors de ces projets ANR avec l'objectif final de réaliser un onduleur monolithique en SiC haute température (300 °C). Les JFET pour l'étage de commande (40 V/30 mA-1 A) ont été réalisés dans le cadre du projet COTHT et ceux pour l'étage puissance (600 V/30 mA-1 A) dans le projet JFET-SB.

Afin de faciliter la commande individuelle de ces transistors, des structures complémentaires ont été choisies pour les deux JFET de puissance, un JFET à canal N et l'autre à canal P. Le fait d'avoir choisi des structures complémentaires permet de minimiser les interférences mutuelles et de diminuer (voire éliminer) l'injection de porteurs entre les deux JFET.

Remarquons qu'aucun JFET à canal type P à base de SiC n'a été réalisé à l'heure actuelle. Ainsi la nouveauté porte sur la réalisation d'un JFET à canal type P ainsi que son intégration monolithique avec un JFET complémentaire à canal type N sur une même puce en carbure de silicium.

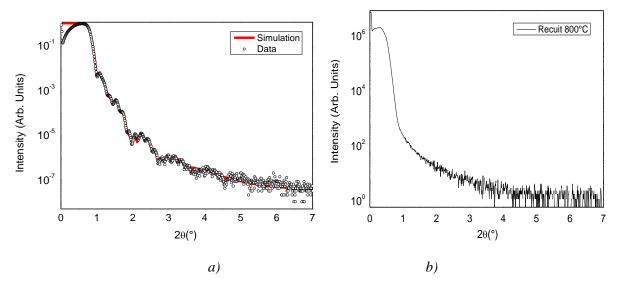

L'étude des contacts ohmiques sur SiC-4H type P – verrou technologique à lever pour la fabrication de composants de puissance - fait l'objet du 3<sup>ème</sup> chapitre. Différentes métallisations à base de nickel, de titane et d'aluminium sont étudiées pour la réalisation des contacts ohmiques. Leurs conditions de recuits de type RTA (Rapid Thermal Annealing) sont exploitées sur plusieurs fours pour chaque type de métallisation afin de déterminer la condition qui engendre la résistance spécifique de contact la plus faible. Des analyses structurales SIMS (Secondary Ion Mass Spectrometer), EDX (Energy-Dispersive X-ray) et

DRX (Diffractométrie de Rayons X) sont exploitées pour comprendre la formation des nos contacts.

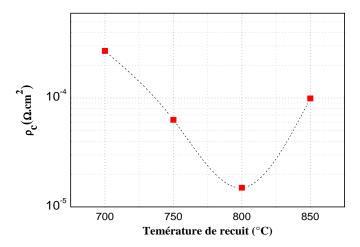

Cette étude a abouti à un résultat très important sur le contact ohmique sur SiC type P, une faible résistance spécifique comparable à l'état de l'art mondial ( $\rho_c \sim 1 \times 10^{-5}~\Omega.cm^2$ ). Nous avons utilisé un alliage à base de Ni/Ti/Al/Ni.

Le quatrième chapitre s'intéresse à la réalisation des nouveaux lots de JFET latéraux avec l'objectif de les intégrer monolthiquement en carbure de silicium. Parmi l'ensemble des étapes technologiques nécessaires à la réalisation des composants, nous nous attardons sur la gravure plasma utilisée pour définir les différentes structures de nos composants. Enfin, nous présentons les performances électriques des composants JFET latéraux fabriqués selon notre procédure établie tout au long de ce travail.

Précisons que toutes les optimisations faites tout au long de ce travail comme celui sur le contact ohmique ou bien celui sur la gravure du SiC nous a permis de réaliser des JFET latéraux de deux types N et P et les intégrer sur une même puce de carbure de silicium.

Nous terminons par une synthèse et les perspectives de nos travaux.

Avant de clôturer cette introduction générale nous précisions que ces travaux ont pu être réalisés d'une part grâce au contrat doctoral obtenu par le candidat pour ce sujet de thèse. Nous avons utilisé les échantillons et les moyens technologiques qui ont été financés par deux projets ANR qui ont précédés cette thèse : le projet COTHT (COnvertisseurs Très Haute Température) projet blanc 2006-2009 et JFET-SB (JFET Switch Bridge) projet jeune chercheur 2005-2008.

# Chapitre 1: Le carbure de silicium pour l'intégration de composants électroniques

| Introduction                                                     | 18 |

|------------------------------------------------------------------|----|

| 1.1 Contexte - Positionnement du carbure de silicium             | 18 |

| 1.1.1 Propriétés physiques du SiC                                | 20 |

| 1.1.2 Facteur de mérite du SiC                                   |    |

| 1.1.3 Propriétés électroniques intrinsèques du SiC               |    |

| 1.2 Etat de l'art de la filière du carbure du silicium           |    |

| 1.2.1 Fournisseurs de substrat SiC                               |    |

| 1.2.2 Aspects cristallographiques                                |    |

| 1.2.3 Défauts dans le SiC                                        |    |

| 1.3 Spécificités technologiques du SiC                           |    |

| 1.3.1 L'épitaxie du SiC                                          |    |

| 1.3.2 Dopage                                                     |    |

| 1.3.2.1 Eléments dopants                                         |    |

| 1.3.2.2 Dopage in situ                                           |    |

| 1.3.2.3 Dopage localisé par diffusion                            |    |

| 1.3.2.4 Dopage localisé par implantation ionique                 |    |

| 1.3.3 La gravure du SiC                                          |    |

| 1.3.3.1 Gravure humide                                           |    |

| 1.3.3.2 Gravure sèche par plasma                                 |    |

| 1.3.3.2.1 Propriétés du plasma.                                  |    |

| i) Interaction plasma-surface                                    |    |

| ii) sélectivité de la gravure                                    |    |

| 1.3.3.2.2 Les principaux réacteurs                               |    |

| a) RIE (Reactive Ion Etching)                                    |    |

| b) ICP (Inductively Coupled Plasma)                              |    |

| 1.3.3.2.2 Synthèse des procédés utilisées dans la gravure du SiC |    |

| 1.3.4 Le contact ohmique sur le SiC                              |    |

| 1.3.4.1 Le contact ohmique sur SiC-4H type N                     |    |

| 1.3.4.2 Le contact ohmique sur SiC-4H type P                     |    |

| 1.3.5 Packaging                                                  |    |

| 1.3.6 Passivation                                                |    |

| 1.3.6.1 Passivation primaire                                     |    |

| 1.3.6.2 Passivation secondaire                                   |    |

| 1.4 Les composants d'électronique de puissance en SiC            |    |

| 1.4.1 Les diodes en SiC                                          |    |

| 1.4.2 Le JFET                                                    |    |

| 1.4.3 Le MOSFET                                                  |    |

| 1.4.4 Le BJT                                                     |    |

| 1.5 L'intégration en électronique de puissance                   |    |

| 1.5.1 Pourquoi l'intégration en électronique de puissance        |    |

| 1.5.2 Vers l'intégration monolithique                            |    |

| 1.6. Conclusion du chapitre:                                     |    |

| 1.7 Déférences                                                   | 60 |

# Liste de figures :

| Figure 1: Volume des publications dans « Journal of Applied Physics » et « I                          | IEEE         |

|-------------------------------------------------------------------------------------------------------|--------------|

| Transactions on Electron Devices » concernant la physique ou des dispositifs en SiC [T                | Thom         |

| 13]                                                                                                   |              |

| Figure 2 : Évolution de la concentration intrinsèque en fonction de la température, en te             |              |

| compte de la variation de $E_g$ avec la température [Rayn 10]                                         |              |

| Figure 3 : Evolution de la taille des wafers en carbure de silicium a) SiCrystal [Stra 10]            |              |

| Cree                                                                                                  |              |

| Figure 4: Diagramme de phase binaire du Si–C (V: vapeur, L: liquide) [Fut 10]                         |              |

| Figure 5: Structure: Si-C.                                                                            |              |

| Figure 6 : Image après gravure au KOH des défauts Threading Screw Dislocation (1                      |              |

|                                                                                                       |              |

| Threading Edge Dislocation (TED), et micropore (µPs) [Shri 08]                                        |              |

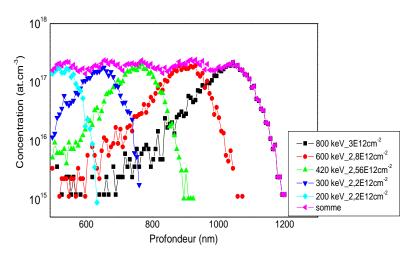

| Figure 7: Profil SRIM d'une implantation multiple d'azote pour la formation d'un canal.               |              |

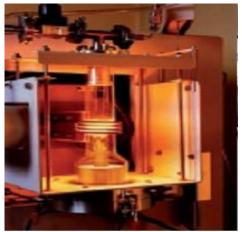

| Figure 8 : Photographie et coupe schématique de la chambre chaude du four de recuit                   |              |

| Figure 9 : Schéma descriptif de la sélectivité de la gravure du SiC qui monti                         |              |

| consommation du masque et du SiC pendant le procédé de gravure                                        |              |

| Figure 10 : La sélectivité de certains masques utilisés pour graver SiC [Laza 06]                     |              |

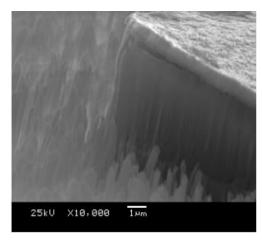

| Figure 11 : Phénomène de micromasquage produit lors d'un procédé de gravure SiC                       |              |

| observe que la surface du SiC gravé est devenue très rugueuse                                         |              |

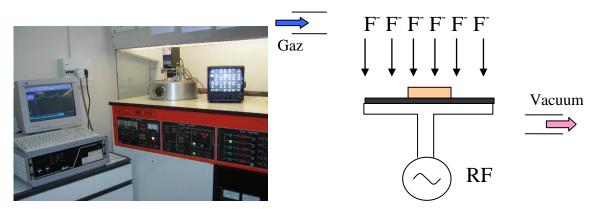

| Figure 12 : Photographie et schéma simplifié du bâti de gravure RIE Nextral NE110                     |              |

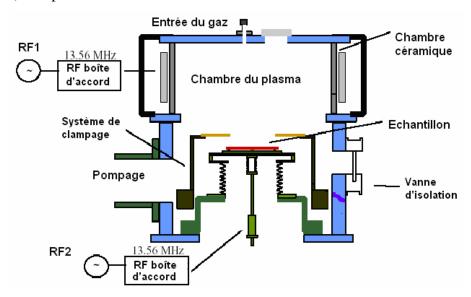

| Figure 13 : Schéma simplifié du bâti de gravure ICP                                                   |              |

| Figure 14 : Evolution de la vitesse de gravure en fonction de la pression, paramétre                  | ée en        |

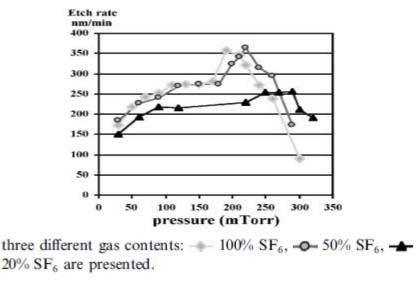

| pourcentage de SF <sub>6</sub>                                                                        | 40           |

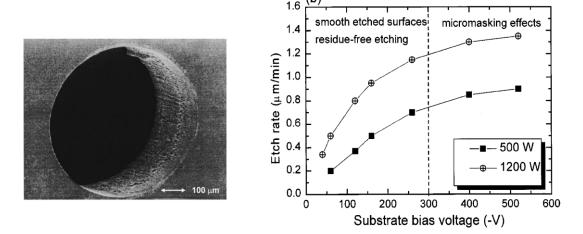

| Figure 15: a)Trou de 330 µm de profondeur gravé en 6 h avec une vitesse 0,95 µm/mi                    | in, b)       |

| profondeur en fonction de la tension de bias [Chab 00]                                                | 40           |

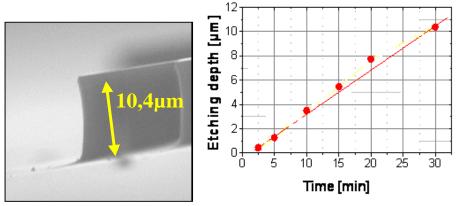

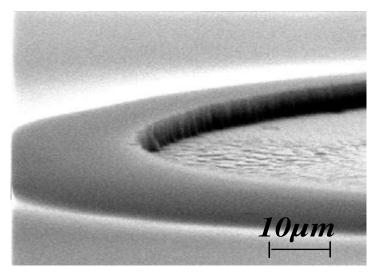

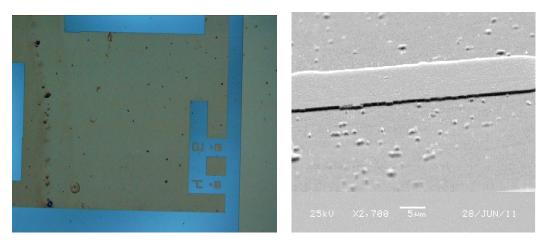

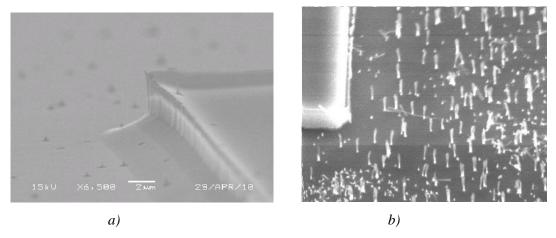

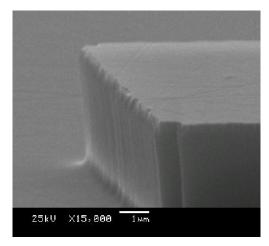

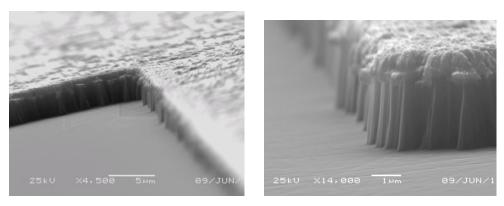

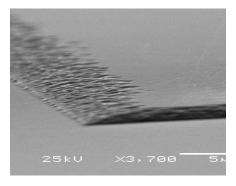

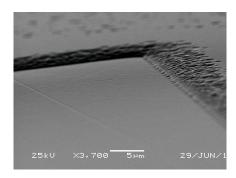

| Figure 16 : a) Image MEB d'une gravure profonde, b) profondeur de gravure en fonctio                  | on du        |

| temps                                                                                                 | 41           |

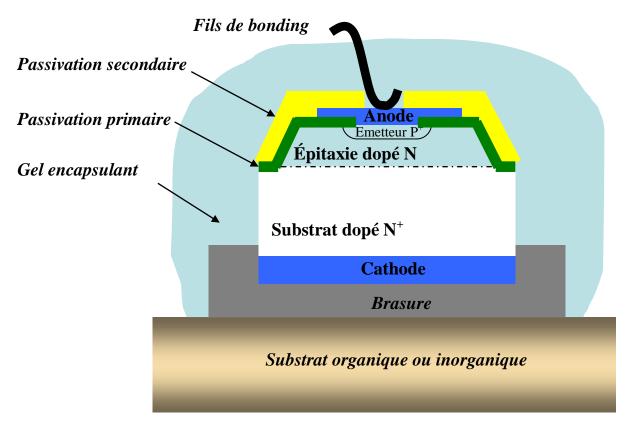

| Figure 17 : Présentation schématique des éléments de packaging sur une diode PiN vi                   | ue en        |

| coupe                                                                                                 |              |

| Figure 18 : démonstrateur d'une diode JBS [Alex 03]                                                   |              |

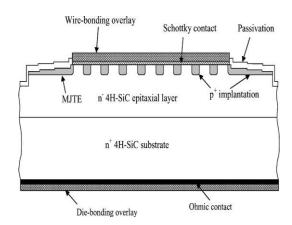

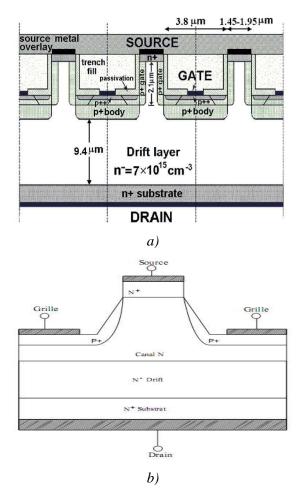

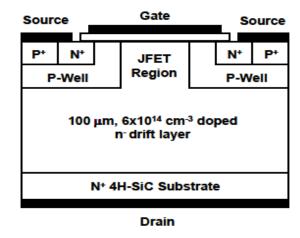

| Figure 19: Structure d'un JFET et sa topographie [Rudo10]                                             |              |

| Figure 20 : a) Démonstrateur d'un transistor JFET [Zaho04], b) Structure du VJFET                     |              |

| 1200 V-15 mm² fabriqué par SemiSouth [Rite 10]                                                        |              |

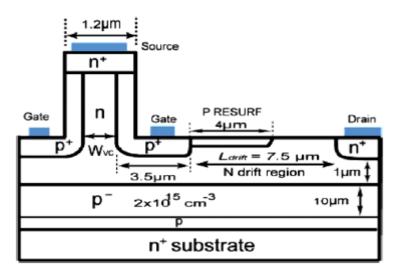

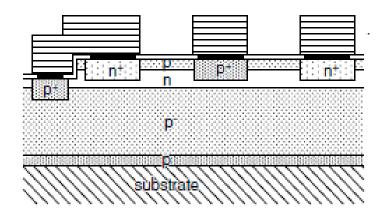

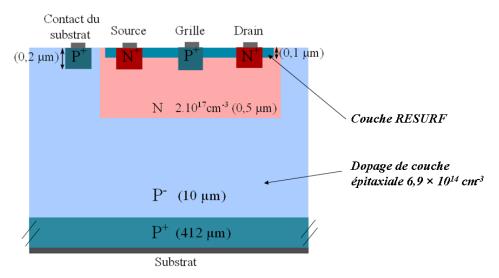

| Figure 21 : Structure d'un JFET latéral avec une tenue en tension 1100 V et $R_{sp}$ = 9.5 m $\Omega$ |              |

| [Shen 08]                                                                                             | 2 CIII<br>52 |

|                                                                                                       |              |

| Figure 22 : Structure d'un JFET latéral avec une tenue en tension $800~V$ et $R_{sp}$ = $50~m\Omega$  |              |

| [Fuji 06]                                                                                             |              |

| Figure 23 : Structure DMOSFET 10 kV réalisée par Ryu [Ryu 04]                                         |              |

| Figure 24 : Structure a) DEMOSFET et b) IEMOSFET réalisées par Harada. La couch                       |              |

| réalisée par épitaxie pour le DEMOSFET et par implantation pour l'IMOSFET [Hara 06]                   |              |

| Figure 25 : a) Structure de BJT, b) circuit Darlington, c) photographie de BJT réalise                | •            |

| [Zhan 10]                                                                                             |              |

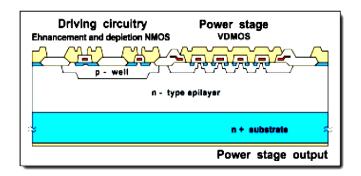

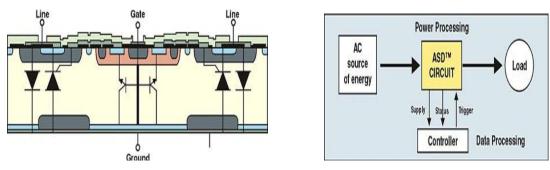

| Figure 26 : Vers l'intégration monolithique.                                                          |              |

| Figure 27 : Technologie VIPer intégrant monolithiquement des fonctions de command                     | le au        |

| sein d'un transistor vertical de puissance 600V [Marm 00]                                             |              |

| Figure 28 : Exemple d'intégration monolithique fonctionnelle d'un composant fabriqué                  | avec         |

| la technologie ASDTM de la société ST Microelecrtonics.                                               |              |

# Liste de tableaux :

| Tableau 1 : Propriétés physiques des principaux matériaux semi-conducteurs à large bande      |

|-----------------------------------------------------------------------------------------------|

| interdite comparés au silicium [Rayn 95][Cama 98][Nall 01, 02]20                              |

| Tableau 2 : Facteurs de mérite pour plusieurs semi-conducteurs à large bande interdite en     |

| comparaison avec le silicium                                                                  |

| Tableau 3 : Propriétés électroniques intrinsèques de différents polytypes SiC22               |

| Tableau 4 : Liste des principaux fabricants de substrat SiC et la qualité des substrats, pour |

| les deux polytypes les plus courants 4H et 6H24                                               |

| Tableau 5 : Notation de Ramsdell utilisée pour les principaux polytypes de carbure de         |

| silicium et séquence d'empilements correspondants                                             |

| Tableau 6 : Niveaux énergétiques des centres de défauts intrinsèques dans le SiC [Lebe 99.]   |

| 28                                                                                            |

| Tableau 7: Niveau d'énergie des impuretés dans SiC-6H et SiC-4H. Ec et Ev sont                |

| respectivement les énergies des bandes de conduction et de valence [Frei 95] [Mats 99]        |

| [Jenn 96] [Srid 98] [Kaka 02]31                                                               |

| Tableau 8 : Une synthèse non exhaustive des contacts ohmiques sur le SiC type N               |

| Tableau 9 : Une synthèse non exhaustive des contacts ohmiques sur SiC-4H de type P 43         |

| Tableau 10 : Caractéristiques électriques de quelques diodes Shottky commerciales à base de   |

| SiC par Cree, Microsemi, Infineon.et ST Microelectronics [ST 12]48                            |

| Tableau 11 : Caractéristiques électriques des quelques MOSFET-SiC commercialisés par          |

| Cree et Rhom.                                                                                 |

# Introduction

Après la découverte de ses propriétés semi-conductrices en 1907 [Roun 07], le carbure de silicium apparaît extrêmement intéressant de par ses propriétés de conduction ainsi que ses propriétés de résistance aux températures élevées. La révolution de l'électronique de puissance qui apparaît avec ce nouveau matériau semble exceptionnelle, illustrée par les performances atteintes par plusieurs démonstrateurs qui suggèrent un avenir prometteur pour les composants de puissance en SiC. Tous ces composants ont une propriété commune qui les rendent extrêmement intéressants du point de vue de l'électronique de puissance dans leur capacité à pouvoir opérer à haute température et à supporter de fortes tensions inverses. Les technologies SiC sont donc appelées à jouer un rôle majeur au cours des années à venir. Pour atteindre ce but, il est toutefois nécessaire d'en maitriser toutes les étapes technologiques de fabrication des composants. Ainsi, la réalisation de dispositifs de puissance plus performants que ceux en silicium permettra aux industriels fabricants de modules électroniques de puissance de diminuer leurs coûts et surtout d'améliorer leurs performances.

Depuis une dizaine d'année, nous voyons apparaître la mise sur le marché des premiers composants en SiC commerciaux telles que les diodes Schottky en 2001 par Microsemi [Micr 01] et Infineon [Rupp 03] et plus récemment les transistors JFET par Semisouth [Semi 09] et MOSFETs par [Cree 11] et [Rhom 13]. Il est à noter aussi l'exploitation de ce matériau dans le domaine des hyperfréquences où l'on trouve des MESFET [Cree 04].

#### 1.1 Contexte - Positionnement du carbure de silicium.

Trouvé dans les météorites, le carbure de silicium n'existant pas à l'état naturel sur la terre, la plupart des substrats naturels sont d'origine extraterrestre ou de synthèse [Berz 24]. Les travaux de Jöns Jakob Berzelius montrent en 1824 l'existence d'une liaison chimique stable, partiellement ionique, entre le silicium et le carbone et la possibilité de synthétiser sous forme stœchiométrique le composé binaire SiC. Vers 1885, Eugène G. Achelson réussit à faire croître une couche de SiC. La méthode utilisée consistait à faire passer une décharge électrique dans un mélange de poudres de carbone et de silice. Elle est encore utilisée pour la synthèse des poudres abrasives et donne un mélange de blocs de SiC de mauvaise pureté chimique, mais relativement monocristallines [Ache 82]. Round a montré en 1907 le phénomène d'électroluminescence sur le carbure de silicium [Roun 07].

La synthèse du matériau présente cependant des difficultés évidentes : en particulier, la température mise en jeu lors de la synthèse est très élevée de l'ordre de 2000 °C. En 1955 la méthode de «Lely» [Lely 55], basée sur la condensation de SiC, permit de faire croître des couches de SiC de hautes qualités monocristallines et de pureté électronique. En 1978 fut montrée une nouvelle méthode de croissance avec la technique de sublimation qui est en fait une méthode dérivée de celle de Lely [Voda 78]. Les études des performances du SiC démarrèrent alors parallèlement aux Etats-Unis et en Union soviétique. En 1990, la start-up américaine *CREE* Research fondée trois ans plus tôt, fut à même de proposer des substrats de qualité acceptable pour réaliser des prototypes de composants en SiC à partir d'une méthode proche de celle développée par Lely en 1955.

Depuis, la mise sur le marché de substrats SiC de 100 mm a été atteinte. Non seulement Cree Research a commencé à mettre sur le marché des substrats de 4 pouces de polytype 4H et 6H mais de nouveaux fabricants sont apparus comme SiCrystal (racheté par Rhom en 2010) [Sicr 12], Norstel [Nors 06], Tankeblue [Tank 09] et II-VI Incorporated [II-VI 12]. Cree a annoncé en 2012 la commercialisation de la nouvelle génération de substrats de 6 pouces (150 mm) [Cree 12].

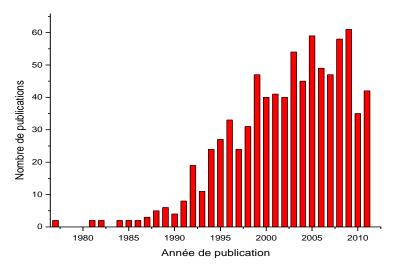

Depuis quelques années, l'effort de recherche porte principalement sur les composants de puissance et RF pour lesquels la filière classique du Silicium atteint ses limites. Le nombre de publications scientifiques, indicateur de l'activité du domaine de recherche, augmente rapidement suite aux travaux lancés au début des années 90 dans le monde entier. Cette forte tendance est illustrée par la figure 1 qui représente l'évolution des recherches sur le carbure de silicium par les nombres de brevets et les papiers scientifiques dans deux journaux spécialisés, IEEE Transactions on Electron Devices et Journal of Applied Physics. (Figure 1).

Figure 1: Volume des publications dans « Journal of Applied Physics » et « IEEE Transactions on Electron Devices » concernant la physique ou des dispositifs en SiC [Thom 13].

# 1.1.1 Propriétés physiques du SiC

Le SiC présente des propriétés physiques peu communes. Ceci provient de la faible valeur des distances interatomiques dans la liaison Si-C, 0,194 nm, à comparer avec 0,234 nm pour le silicium et 0,154 nm pour le diamant. Cette liaison n'est pas purement covalente, elle est ionique à 12% du fait de la différence d'électronégativité entre le silicium et le carbone. A partir des caractéristiques de cette liaison Si-C, en résultent les propriétés physico-chimiques, mécaniques et thermiques particulières du matériau SiC. La dureté du matériau est très élevée ainsi que la forte résistance à la corrosion et la résistance aux irradiations. La conductivité thermique  $\lambda$  du SiC -4,5 W/cm.K - est très largement supérieure à celle du silicium (Tableau1).

| Matériau | E <sub>g</sub> (eV) | n <sub>i</sub> (cm <sup>-3</sup> ) | ε <sub>r</sub> | $\mu_n \\ (cm^2.V^{-1}.s^{-1})$ | $\mu_{p \text{ (cm}}^{2}.$ | E <sub>c</sub> (MV/cm) | $v_{sat}$ (10 <sup>7</sup> .cm.s <sup>-1</sup> ) | $\lambda (\mathbf{W} \cdot \mathbf{cm}^{-1} \\ \cdot \mathbf{K}^{-1})$ |

|----------|---------------------|------------------------------------|----------------|---------------------------------|----------------------------|------------------------|--------------------------------------------------|------------------------------------------------------------------------|

| Si       | 1,1                 | $1,5 \times 10^{10}$               | 11,8           | 1350                            | 450                        | 0,2                    | 1                                                | 1,5                                                                    |

| GaN-2H   | 3,39                | $1,9 \times 10^{-10}$              | 9              | 900                             | 350                        | 3,3                    | 2,5                                              | 1,3                                                                    |

| SiC-3C   | 2,2                 | 8,42                               | 9,6            | 900                             | 45                         | 1,2                    | 2                                                | 4,5                                                                    |

| SiC-4H   | 3,26                | $6.1 \times 10^{-8}$               | 10             | 600                             | 115                        | 2                      | 2                                                | 4,5                                                                    |

| SiC-6H   | 3                   | $1,4 \times 10^{-5}$               | 9,7            | 370                             | 90                         | 2,4                    | 2                                                | 4,5                                                                    |

| Diamant  | 5,45                | $1,6 \times 10^{-27}$              | 5,5            | 1900                            | 3800                       | 5,6                    | 2,7                                              | 2                                                                      |

Tableau 1 : Propriétés physiques des principaux matériaux semi-conducteurs à large bande interdite comparés au silicium [Rayn 95][Cama 98][Nall 01, 02].

Le SiC possède une bande d'énergie interdite  $E_g$  entre 2,2 et 3,3 eV avec une conductivité thermique du SiC monocristallin environ 3 fois supérieure à celle du silicium ce qui permet d'avoir un nombre de porteurs intrinsèques  $n_i$  très faible. Cette large bande interdite et le coefficient thermique important lui offrent une opportunité très attirante pour le fonctionnement à haute température là où le silicium atteint ses limites.

En regardant le tableau 1, on note que le champ électrique critique du carbure de silicium est jusqu'à dix fois plus grand que celui du silicium. Ceci permet d'envisager une augmentation forte de la tenue en tension pour une couche SiC qui présente une épaisseur réduite avec un dopage plus élevé. Ces propriétés permettent de réaliser des dispositifs unipolaires (Schottky,

$<sup>-</sup>n_i$ : concentration de porteurs (électrons) intrinsèques dans le semi-conducteur à une température donnée.

$E_c$ : champ critique, c'est le champ électrique limite au-delà duquel le claquage dans le semi-conducteur peut apparaitre.

$<sup>-\</sup>mu_n (\mu_p)$ : mobilité des porteurs électrons (trous).

<sup>-</sup>v<sub>sat</sub>: vitesse de saturation des électrons accélérés par champ électrique dans un semi-conducteur.

$<sup>-\</sup>lambda$ : conductivité thermique.

JFET, MOSFET) présentant une perte à l'état passant considérablement réduite tout en augmentant encore la rapidité des commutations des composants bipolaires.

Pour comparer, dans le tableau 1 nous avons également ajouté d'autres semiconducteurs à large bande interdite, le GaN et le Diamant.

Le diamant apparait comme un semi-conducteur plus intéressant pour l'électronique de puissance mais à l'heure actuelle, il subsiste des limitations technologiques importantes pour utiliser ce matériau dans la réalisation de composants de puissance. En particulier, il est encore très difficile de fabriquer des substrats de grande dimension (aujourd'hui leur taille est d'environs  $3 \times 3$  mm²) pour pouvoir produire des composants en masse et le dopage de type N reste très difficile à réaliser [Koiz 02].

Le GaN présente également des propriétés physiques très intéressantes, comme le champ électrique critique, large bande interdite et faible concentration intrinsèque des porteurs. Mais sa faible conductivité thermique et la concentration élevée des défauts dans les couches de GaN font que le SiC soit préféré par le laboratoire Ampère pour la réalisation de composants intégrés pour des applications hautes tensions (HV) et haute température (HT).

## 1.1.2 Facteur de mérite du SiC

Dans ce paragraphe, on revient situer l'importance du carbure de silicium par un classement par ordre comparé au silicium et d'autres semi-conducteurs à large bande interdite (tableau 2). Les facteurs de mérite sont ceux de Johnson [John 63], Keyes [Keye 72] et Baliga [Bali 82].

Le facteur de mérite de Johnson JMF détermine l'aptitude du matériau pour les applications haute fréquence et haute puissance, il est proportionnel au champ électrique critique et à la vitesse de saturation :

$$JMF = \frac{E_c.v_{sat}}{2\pi}$$

Le facteur de mérite de Keyes KMF nous informe sur les performances thermiques et fréquentielles, il prend en considération la conductivité thermique du matériau, la vitesse de saturation et sa permittivité :

$$KMF = \lambda \sqrt{\frac{c.v_{sat}}{4\pi\varepsilon_r}}$$

Enfin le facteur de mérite de Baliga BMF est proportionnel à la mobilité des porteurs, à la permittivité du matériau et au champ électrique :

BMF =

$$\mu \varepsilon_r E_c^3$$

Ces facteurs de mérite traduisent alors bien les performances du SiC pour les composants de puissance, plus le facteur est important plus les composants présentent de bonnes performances. Les valeurs relevées font du SiC un excellent candidat pour la réalisation des composants de puissance.

| Matériaux | Si | SiC-3C | 4H-SiC | SiC-6H | GaN | Diamant |

|-----------|----|--------|--------|--------|-----|---------|

| JFM       | 1  | 65     | 180    | 260    | 760 | 2540    |

| KFM       | 1  | 1,6    | 4,61   | 4,68   | 16  | 32,1    |

| BFM       | 1  | 33,4   | 130    | 110    | 650 | 4110    |

Tableau 2 : Facteurs de mérite pour plusieurs semi-conducteurs à large bande interdite en comparaison avec le silicium.

# 1.1.3 Propriétés électroniques intrinsèques du SiC

La concentration  $n_i$  est liée à la largeur de la bande interdite ainsi qu'aux densités d'états permis dans les bandes de conduction  $N_c$  et bandes de valence  $N_v$ . Le tableau 3 présente les valeurs de ces paramètres pour différents polytypes de SiC. Le carbure de silicium possède une large bande interdite (3,2 eV) ce qui donne une concentration de porteurs intrinsèques  $n_i$  extrêmement faible comparée à celle du silicium. Cette propriété lui permet donc de fonctionner à haute température et c'est un paramètre important car il influe les niveaux de courants de fuite en inverse des diodes à jonctions bipolaires ou Schottky.

| Polytypes                                                    | 6H-SiC                | 4H–SiC                  | 3C-SiC                |

|--------------------------------------------------------------|-----------------------|-------------------------|-----------------------|

| $N_C(\text{cm}^{-3})$                                        | $8,65 \times 10^{19}$ | $1,68 \times 10^{19}$   | $1,56 \times 10^{19}$ |

| $N_{\rm v}({\rm cm}^{-3})$                                   | $3,30 \times 10^{19}$ | $3,30 \times 10^{19}$   | $3,30 \times 10^{19}$ |

| $n_{\rm i} = \sqrt{N_C N_V} \exp(\frac{-E_g}{2KT})(cm^{-3})$ | $1,4 \times 10^{-5}$  | 6,12 × 10 <sup>-8</sup> | 8,42                  |

Tableau 3 : Propriétés électroniques intrinsèques de différents polytypes SiC.

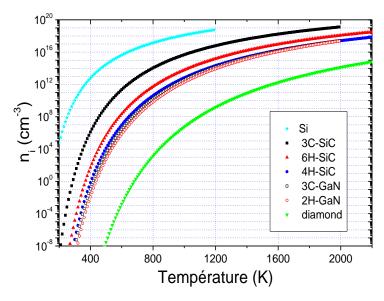

D'après la figure 2 qui représente l'évolution de la densité de porteurs intrinsèques en fonction de la température pour différents matériaux on voit clairement que pour le SiC-6H et le SiC-4H, la concentration intrinsèque reste très inférieure aux dopages généralement utilisés (> 10<sup>14</sup> cm<sup>-3</sup>). Par conséquent, le SiC peut fonctionner en régime extrinsèque au-delà de 1000 K.

-

<sup>&</sup>lt;sup>1</sup> La notion de polytype sera expliquée dans le paragraphe 1.2.2 ci-après

Figure 2 : Évolution de la concentration intrinsèque en fonction de la température, en tenant compte de la variation de  $E_g$  avec la température [Rayn 10].

#### 1.2 Etat de l'art de la filière du carbure du silicium

## 1.2.1 Fournisseurs de substrat SiC

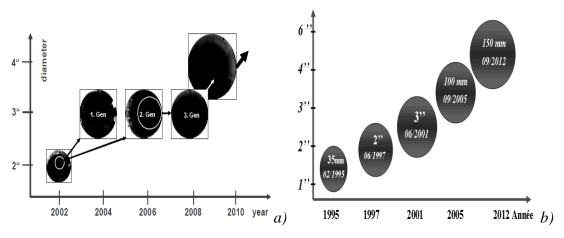

Les substrats de carbure de silicium (SiC) disponibles actuellement, en SiC-6H et en SiC-4H, suivent une évolution de la taille de la plaque (wafer) qui permet des progrès technologiques (figure 3). La taille des plaques augmente, elle a atteint 100 mm (~4'') pour des plaques commercialisées depuis 2006 et la commercialisation de substrats 150 mm (~6") a été envisagée en 2012 par Cree [Cree 12].

Cette évolution va permettre de réaliser des composants sur des plaques SiC avec des équipements déjà largement exploités dans les fonderies de la filière silicium classique. Le marché du substrat SiC est assez largement dominé par Cree qui est leader en termes de vente et de qualité de matériau. L'achat de la société Intrinsic par Cree en 2006 a permis la commercialisation de substrats sans micropores. Mais des nouveaux acteurs ont fait leur apparition, notamment SiCrystal (racheté par Rohm en 2010) et II-VI qui ont pris des parts de marché importantes à CREE. Depuis quelques années la Chine est présente, avec notamment Tankeblue, qui affiche une forte volonté de progresser malgré la qualité moindre des plaques commercialisées actuellement (tableau 4).

Figure 3: Evolution de la taille des wafers en carbure de silicium a) SiCrystal [Stra 10] b) Cree

| Fabricant                         | Polytype | Diamètre | micropore           | Polytype | Diamètre r | nicropore           |

|-----------------------------------|----------|----------|---------------------|----------|------------|---------------------|

| Faoricant                         | 4H       |          | (cm <sup>-2</sup> ) | 6H       | (pouce)    | (cm <sup>-2</sup> ) |

| Cree                              | Oui      | 150mm    | 10                  | Oui      | 2"         | NC                  |

| SiCrystal (racheté par Rhom)      | Oui      | 100 mm   | n 30                | Oui      | 2"         | 100                 |

| II-VI Inc                         | Oui      | 3"       | 100                 | Oui      | 3"         | 100                 |

| Tankeblue                         | Oui      | 3"       | 10                  | Oui      | 2"         | 10                  |

| Xiamen Powerway Advanced Material | Oui      | 3"       | 20                  | Oui      | 2"         | 30                  |

Tableau 4 : Liste des principaux fabricants de substrat SiC et la qualité des substrats, pour les deux polytypes les plus courants 4H et 6H.

# 1.2.2 Aspects cristallographiques

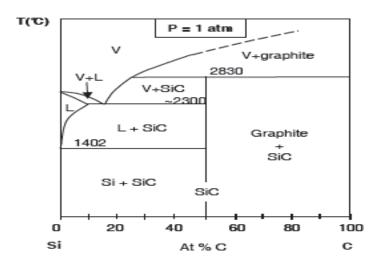

Le carbure de silicium se compose par des atomes de silicium et des atomes de carbone en égalité numérique. D'après le diagramme de phase entre silicium et carbone de la figure 4, le SiC n'existe pas en phase liquide. En plus de la croissance du SiC par sublimation, l'existence d'un domaine 'liquide + SiC' à une température inférieure à 2300 °C permet de réaliser des croissances de monocristaux en phase liquide, en partant de silicium liquide (ou d'une solution riche en silicium), dans laquelle on ajoute du carbone [Fut 10].

Figure 4: Diagramme de phase binaire du Si-C (V: vapeur, L: liquide) [Fut 10].

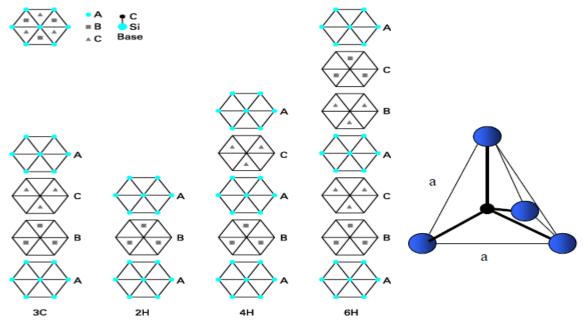

Le carbure de silicium est un matériau cristallin formé par la succession alternée d'empilements C-Si (**figure 5**). Les différentes formes d'empilement de ces plans donnent des cristaux différents appelés polytypes. Au total plus de 170 polytypes ont été identifiés et parmi ceux-ci, quatre ou cinq seulement présentent un intérêt pour les applications micro-électroniques. Ce sont ceux qui ont été le plus étudiés.

En électronique, les plus utilisés sont les polytypes 6H, 4H, et 3C. Des recherches sont également opérées sur les polytypes 15R et 2H. Les lettres H, C et R indiquent la famille cristallographique : hexagonal, cubique ou rhomboédrique, précédés par un chiffre indiquant les nombre des empilements, selon la notation de Ramsdell (tableau 5).

- SiC-2H pour le polytype wurtzite, possède la même symétrie que celle de GaN.

- SiC-3C pour le polytype cubique, possède la même symétrie que celle de GaAs.

- SiC-4H et SiC-6H présentent des liaisons à la fois à symétrie cubique et hexagonale.

Figure 5: Structure: Si-C.

La figure 5 présente une liaison silicium-carbone telle que celle qui se trouve dans chaque plan, les atomes de silicium se trouvent au centre d'un tétraèdre formé par quatre atomes de carbone dont 3 situés en position de premiers voisins dans la couche immédiatement adjacente (et réciproquement pour le carbone).

Les propriétés physiques et électriques sont dépendantes du polytype. Par la suite, nous nous limitons aux polytypes 3C, 6H et surtout 4H, les plus utilisés dans la fabrication des composants de puissance, plus particulièrement parce qu'ils présentent les propriétés les plus intéressantes pour les composants de puissance.

| Notion du Ramsdell | Polytypes    | Séquence d'empilement |  |

|--------------------|--------------|-----------------------|--|

| 2Н                 | Wurtzite     | AB/AB/                |  |

| 3C                 | zinc- blende | ABC/ABC/              |  |

| 4H                 |              | ABAC/ABAC/            |  |

| 6Н                 |              | ABCACB/ABCACB         |  |

| 15R                |              | ABCBACABACBCACB/AB    |  |

Tableau 5 : Notation de Ramsdell utilisée pour les principaux polytypes de carbure de silicium et séquence d'empilements correspondants.

### 1.2.3 Défauts dans le SiC

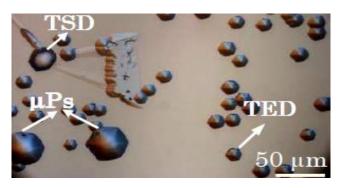

Les défauts de structure des semi-conducteurs modifient leurs propriétés électriques, optiques et mécaniques. Pour les applications en électronique, un intérêt a été porté depuis plusieurs décennies pour identifier les défauts de structure dans le carbure de silicium, généralement créés pendant la croissance du cristal. Parmi les défauts cristallins répertoriés dans les semi-conducteurs, les défauts étendus ou linéaires et les défauts ponctuels ont une importance considérable. Les défauts étendus tels que les micropipes, les dislocations et les fautes d'empilement dans le plan de base (Figure 6) peuvent modifier considérablement leurs propriétés mécaniques et surtout électriques.

Les micropipes sont des microtubes vides de matière traversant le lingot de SiC. Ce type de défaut se comporte comme un court-circuit. Les dislocations endommagent les composants et conduisent à une augmentation des courants de fuite et réduisent la tenue en tension [Neud 00]. Il a été montré que les défauts d'empilement entraînent une augmentation de la tension en direct pendant le fonctionnement sous fort courant pour des composants bipolaires et réduisent la durée de vie des porteurs [Das 05] [Suma 05]. Des recherches par Cree [Leon 09] [Berk 09] ont permis de réduire la densité de micropipes pour donner un substrat SiC-4H de 4 pouces complètement exempt de ce type de défaut mais une densité de dislocation restant relativement élevée de 425 cm<sup>-2</sup>. La société Cree en collaboration avec l'Université de Linköping a réussi à réduire la densité des fautes d'empilements à moins de 10 cm<sup>-2</sup> en proposant une nouvelle technique de croissance [Suma 06].

Pour les défauts ponctuels on peut distinguer les défauts intrinsèques (lacunes, interstitiels, antisites) et les défauts extrinsèques (impuretés en sites substitutionnels ou interstitiels). Ces défauts ponctuels intrinsèques et extrinsèques peuvent se combiner ou s'agglomérer pour donner des défauts plus complexes. Ils ajoutent des niveaux d'ionisation supplémentaires dans la bande interdite, modifiant ainsi les propriétés électriques et optiques du matériau.

Une description détaillée des défauts intrinsèques présentée dans le tableau 6 récapitule les paramètres des centres des défauts :

Figure 6: Image après gravure au KOH des défauts Threading Screw Dislocation (TSD), Threading Edge Dislocation (TED), et micropore (μPs) [Shri 08].

| Localisation d'énergie (eV) |                |                |  |  |

|-----------------------------|----------------|----------------|--|--|

| Centre                      | SiC- 6H        | SiC- 4H        |  |  |

| L                           | Ev + 0.24      | Ev + 0,24      |  |  |

| I                           | Ev + 0.52      | Ev + 0.53      |  |  |

| D                           | Ev + 0.58      | Ev + 0.54      |  |  |

| S                           | Ec - 0,35      |                |  |  |

| $E_1/E_2$                   | Ec - 0,34/0,41 |                |  |  |

| $Z_1/Z_2$                   | Ec - 0,6/0,7   | Ec - 0,63/0,68 |  |  |

| R                           | Ec – 1,27      |                |  |  |

Tableau 6 : Niveaux énergétiques des centres de défauts intrinsèques dans le SiC [Lebe 99.]

L'amélioration des techniques de croissance cristalline sur ce matériau a permis dernièrement la commercialisation par plusieurs fournisseurs de substrats SiC de très haute qualité, qui nous permettent aujourd'hui de réaliser des composants à haute performance.

# 1.3 Spécificités technologiques du SiC

Depuis 2001, des composants à base de carbure de silicium sont mis sur le marché par Microsemi et Infinon, ouvrant un nouveau marché pour l'électronique de puissance. Pour réaliser des composants électroniques il faut mettre en évidence les différentes étapes technologiques nécessaires. Les performances du composant de puissance à base de SiC sont liées non seulement à la qualité du substrat comme nous venons de le décrire au 1.2 mais aussi à la technologie de fabrication du composant qui suit après.

La technologie microélectronique met en œuvre un grand nombre d'étapes élémentaires nécessaires à la fabrication d'un circuit intégré (croissance et dépôt de couches monocristallines, métallisations de contact, dopages, implantations, gravures...). Les composants visés dans notre travail présentent un empilement de couches et un nombre d'étapes d'une grande complexité. Les principales étapes-clés que sont l'épitaxie, les procédés de dopage, la gravure et le contact ohmique seront abordées par la suite.

# 1.3.1 L'épitaxie du SiC

L'épitaxie est une technique de croissance orientée, l'un par rapport à l'autre, de deux cristaux possédant un certain nombre d'éléments de symétrie communs dans leurs réseaux cristallins (source Wikipédia). La méthode la plus courante est l'homoépitaxie qui consiste à faire croître un cristal sur un cristal de nature chimique identique. Cependant, dans le cas du SiC et pour palier le coût élevé des substrats SiC obtenus par sublimation ainsi que leur fragilité, la meilleure alternative proposée actuellement est l'intégration par hétéroépitaxie sur substrat de silicium. Cette voie rencontre beaucoup d'inconvénients, dus au fort désaccord des paramètres de mailles des deux cristaux. Plusieurs méthodes de croissance sont utilisées pour faire croître le SiC. L'épitaxie par jets moléculaires (ou MBE pour *Molecular Beam Epitaxy*), permet de contrôler la croissance à l'échelle de la couche atomique grâce à une vitesse de croissance très lente d'environ une monocouche atomique par minute. Les températures de dépôts sont relativement basses et se situent entre 500 et 1000 °C, comparées aux autres techniques. Mais dans un cadre industriel, l'application de cette méthode semble bien difficile à mettre en oeuvre, principalement à cause de l'ultra vide et la faible vitesse de dépôt [Fiss 01] [Ming 98].

L'épitaxie en phase liquide (LPE – Liquid Phase Epitaxy), où le substrat SiC est mis en contact avec une phase liquide sursaturée en silicium et en carbone, qui se précipitent et

cristallisent sur le substrat. Cette technique a l'avantage d'être rapide, mais elle est moins précise en contrôle fin des épaisseurs et pour la réalisation de couches faiblement dopées [Alex 01] [Hatt 08]. Cette technique permet d'atteindre des vitesses de croissance relativement élevées pour des températures variant de 1100 à 1700 °C.

Le dépôt chimique en phase vapeur (CVD- Chemical Vapour Deposition) est la technique de croissance épitaxiale la plus utilisée par les fournisseurs comme CREE qui est actuellement l'entreprise la plus avancée aussi bien commercialement que technologiquement pour la croissance des polytypes hexagonaux. La firme japonaise HOYA [Hoya 00] constitue la référence pour l'élaboration de couches de SiC-3C sur substrat silicium de plusieurs centaines de microns d'épaisseur et faiblement dopées en impuretés. En France, la société NOVASiC [Nova 13], en association avec le laboratoire CNRS CRHEA [Crhe 11], ont obtenu d'excellents résultats pour les structures hexagonales et cubiques [Ziel 10][Jiao 10].

Le dépôt CVD est basé sur les réactions chimiques des précurseurs gazeux - le silane et un alcane (propane, méthane, ...) dilués dans un flux porteur d'hydrogène arrivant à la surface du substrat, souvent chauffé. La croissance s'effectue à une température comprise entre 1400 °C et 1600 °C [Hass 10][Leon 10].

Une désorientation du cristal est recommandée pour avoir une couche de bonne qualité cristalline en préservant le polytype initial et obtenir une vitesse de croissance importante [Kimo 97]. Par rapport à l'axe [0001] les angles typiques utilisés sont 8° ou 4° pour le polytype 4H, 3° ou 5° pour le 6H.

La CVD permet, grâce aux réactions chimiques mises en jeu d'obtenir sur le substrat, une très bonne voire une excellente adhésion. De plus, les couches déposées présentent une excellente uniformité locale en épaisseur, là où est injectée la vapeur, même si le support présente des anomalies. Par contre, à plus grande échelle (notamment celle d'une plaque entière) cette uniformité est obtenue lorsque l'épaisseur est plus importante par l'utilisation de supports tournants. Un inconvénient propre aux techniques CVD est la création de sous-produits de réaction qui peuvent contaminer les couches déposées s'ils ne sont pas évacués efficacement.

# **1.3.2 Dopage**

### 1.3.2.1 Eléments dopants

Le dopage d'un matériau consiste à introduire, dans sa matrice, des atomes étrangers. Dans les semiconducteurs ces derniers se substituent alors à certains atomes initiaux et introduisent davantage d'électrons ou de trous modifiant les propriétés électriques et optiques. Dans le SiC, les dopants se substituent soit au carbone, soit au silicium. Au vu de la classification des éléments chimiques du tableau de Mendeleïev, le carbure de silicium est un semi-conducteur de la colonne IV, les donneurs proviennent de la colonne V (N, P et As) et les accepteurs de la colonne III (B, Al et Ga).

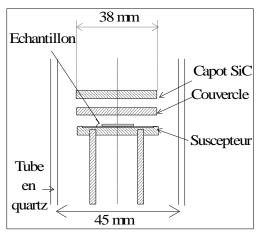

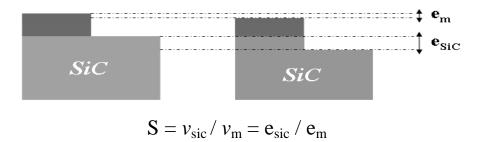

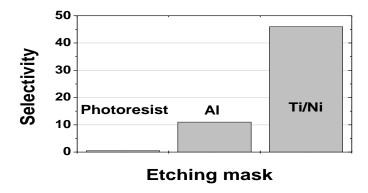

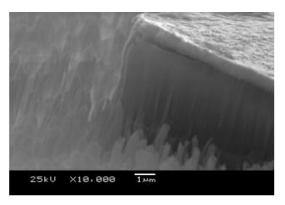

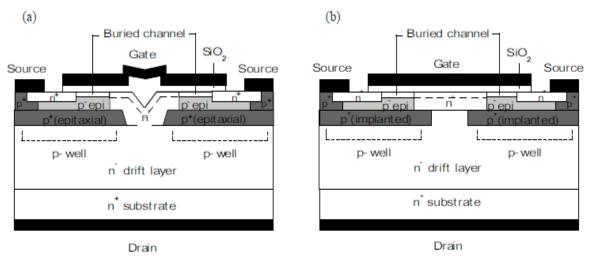

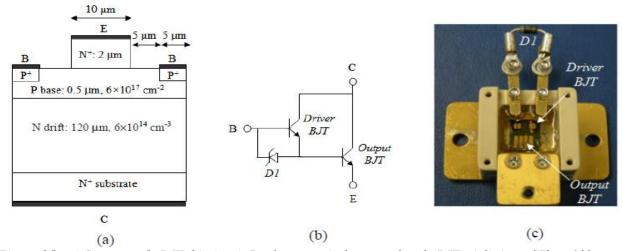

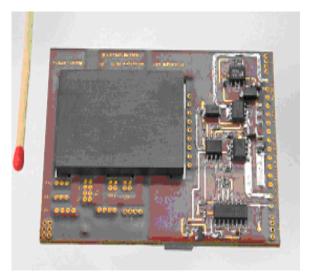

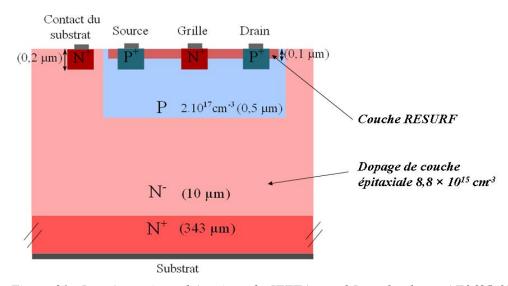

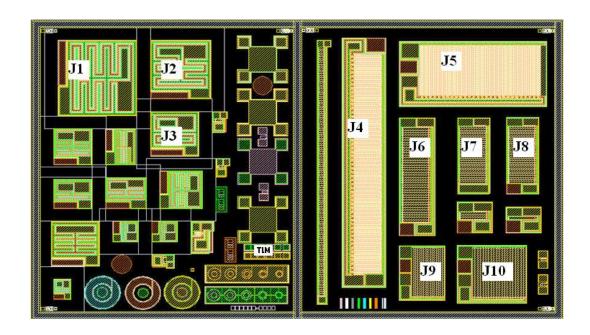

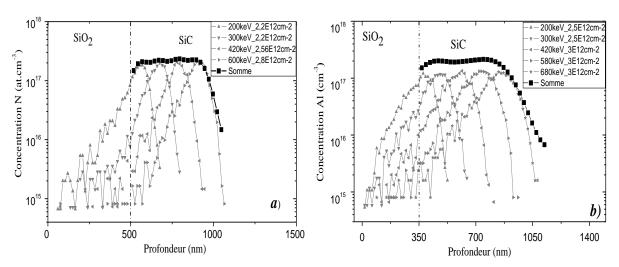

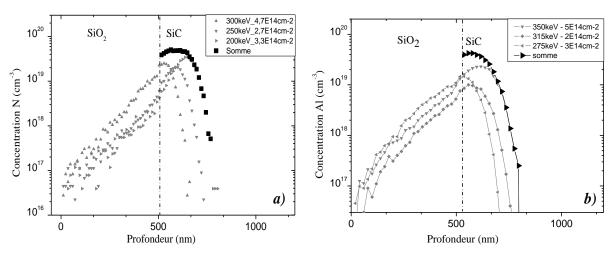

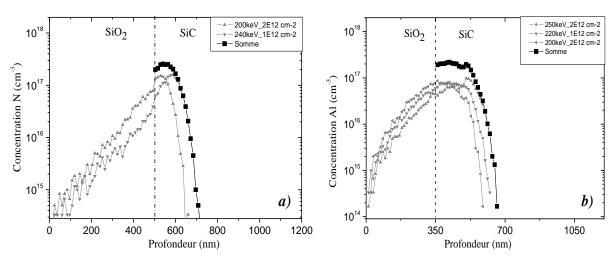

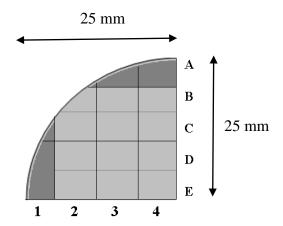

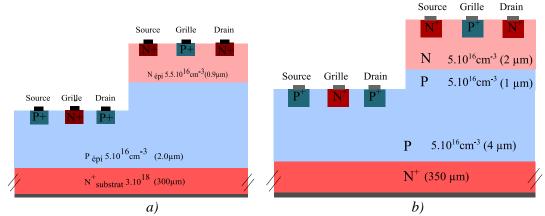

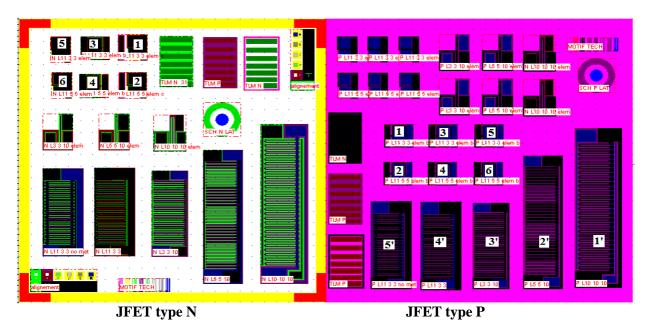

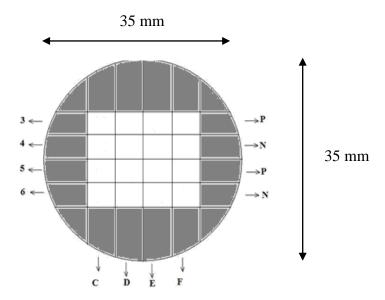

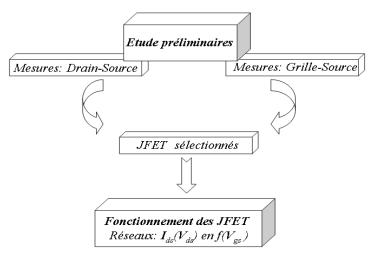

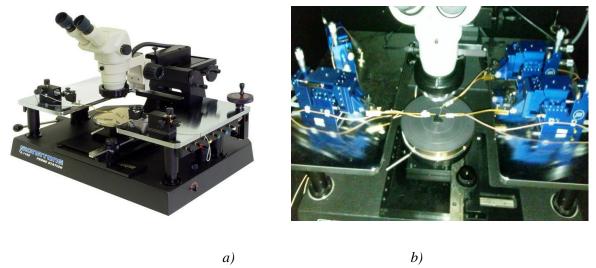

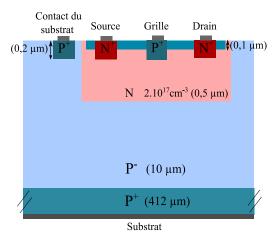

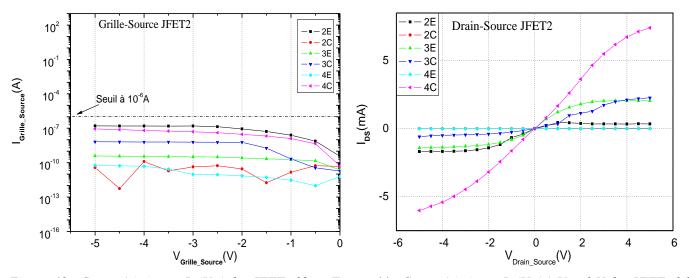

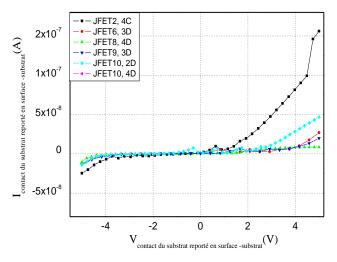

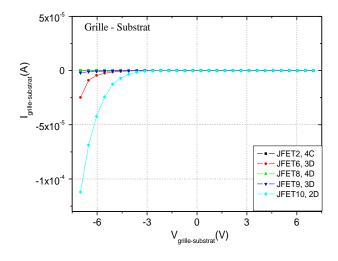

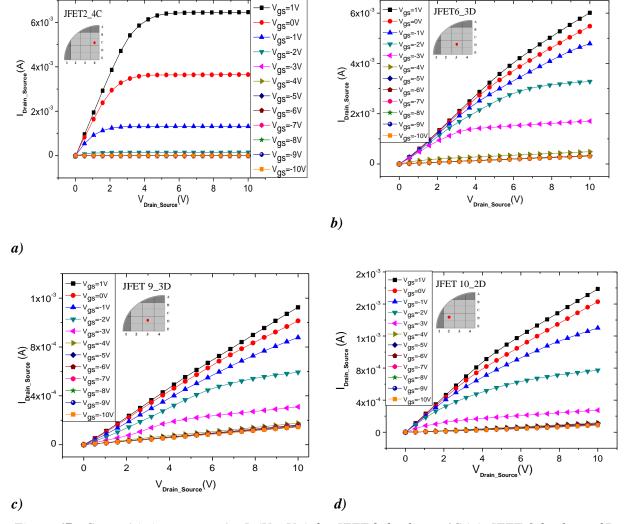

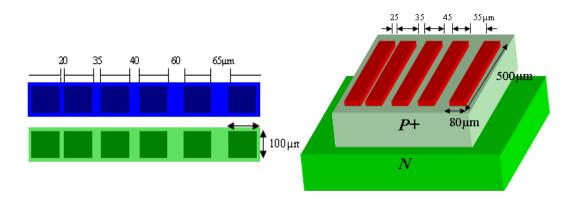

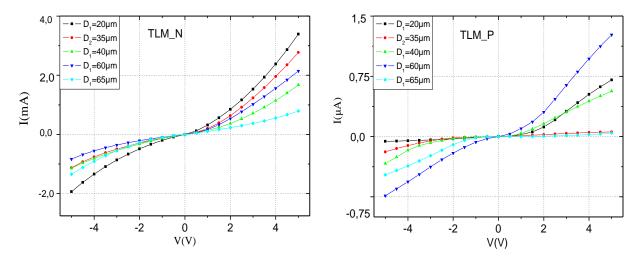

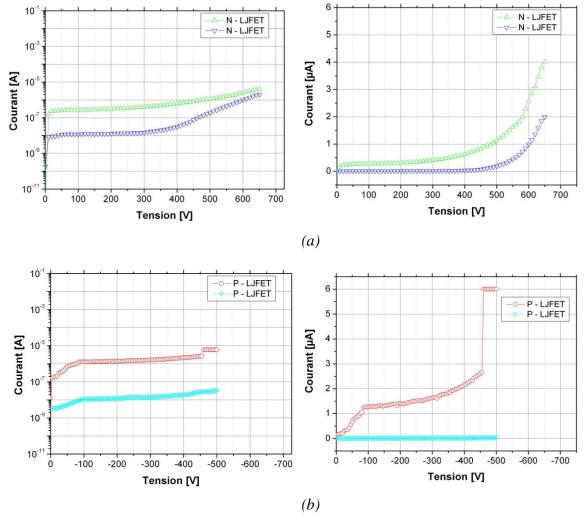

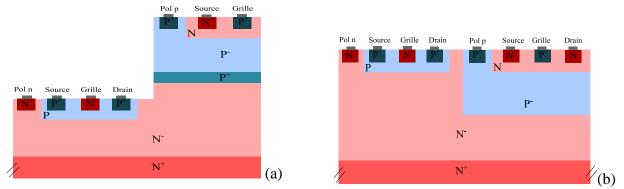

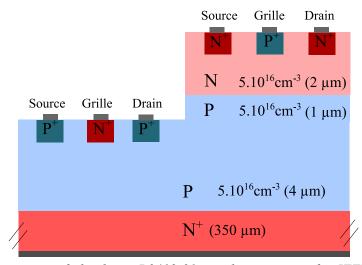

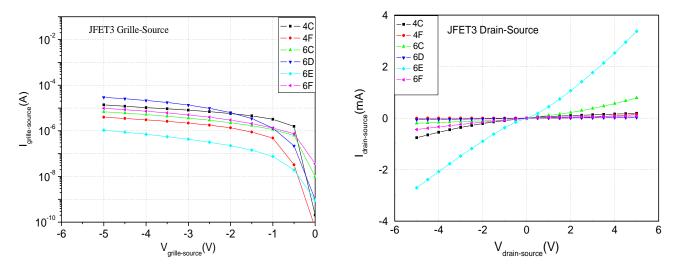

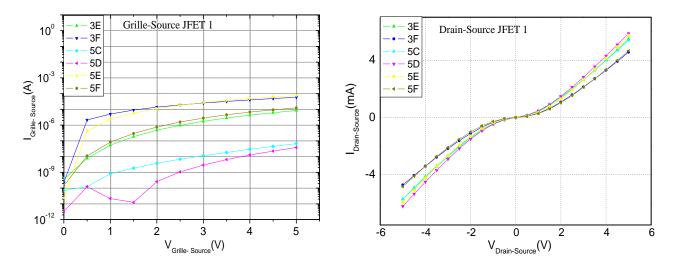

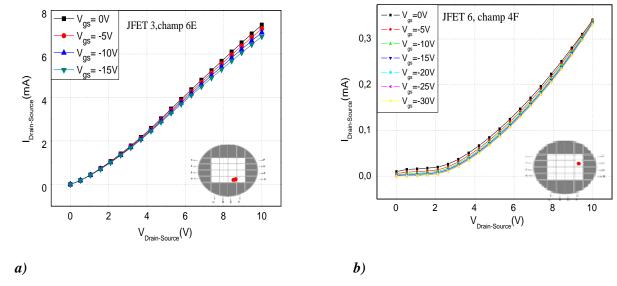

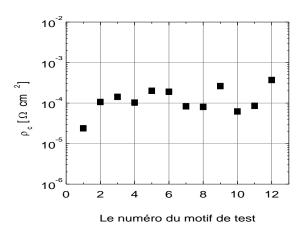

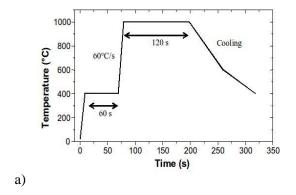

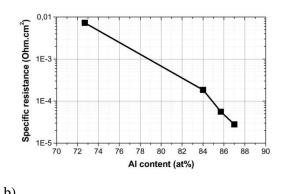

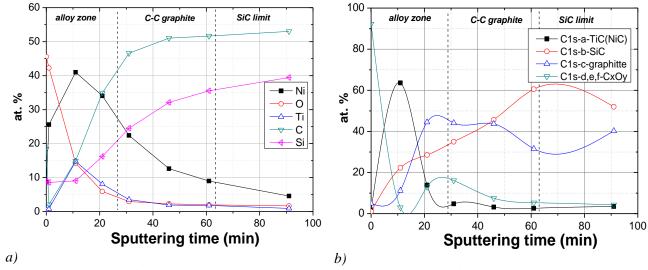

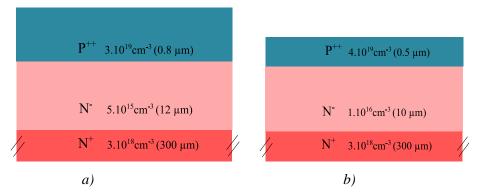

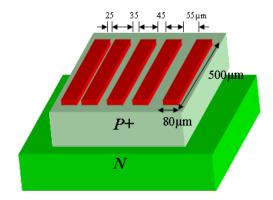

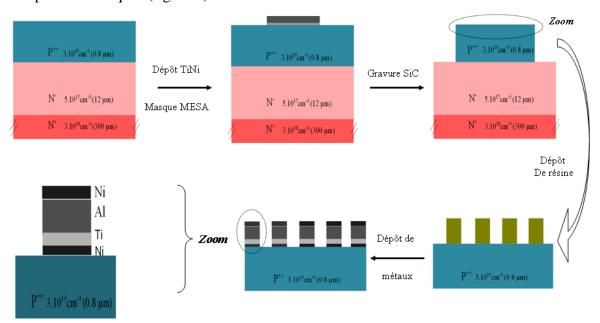

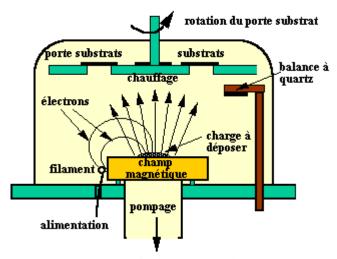

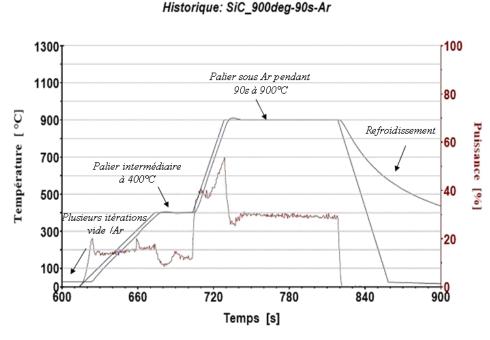

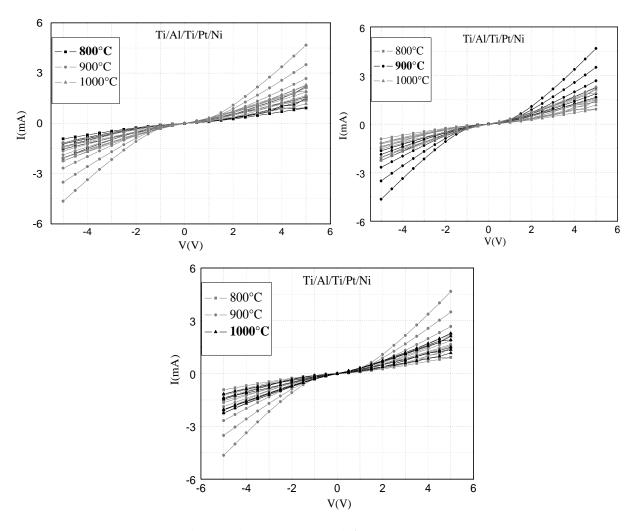

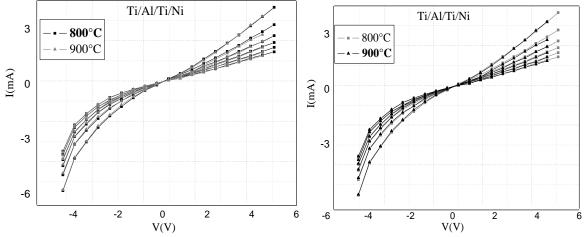

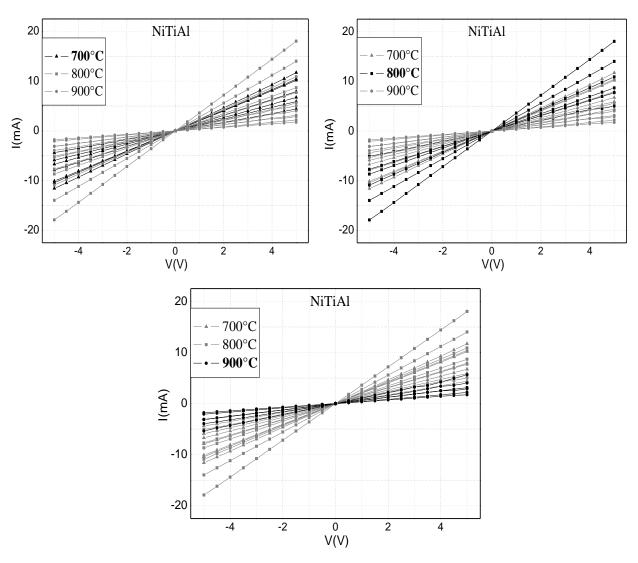

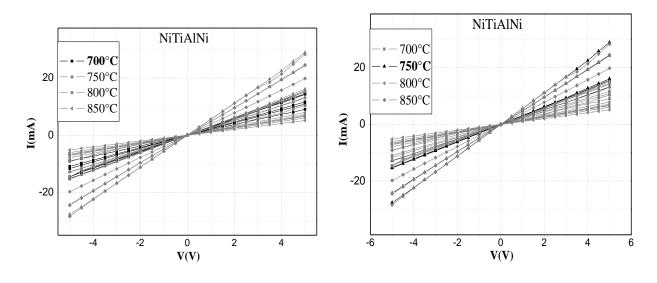

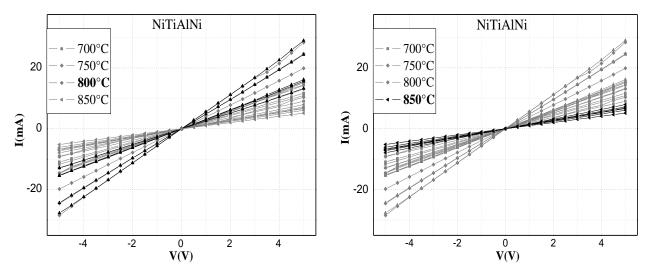

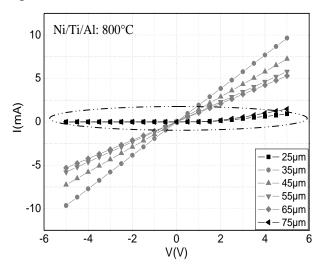

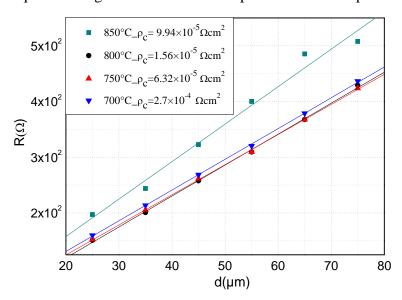

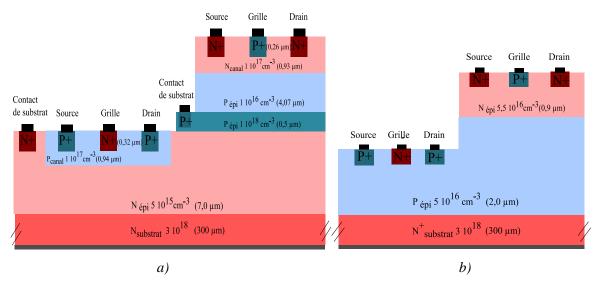

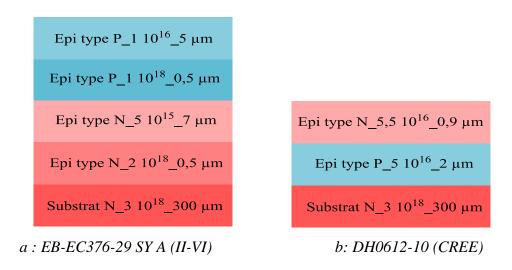

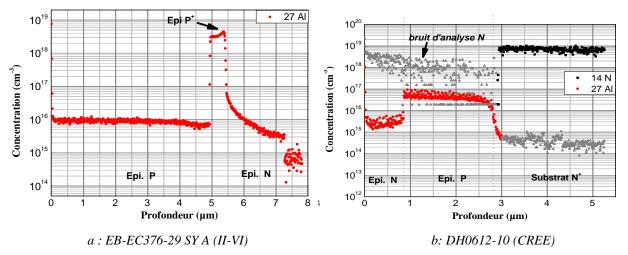

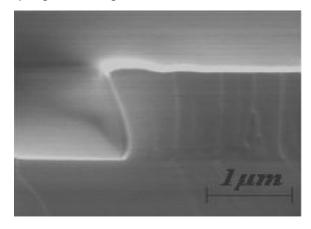

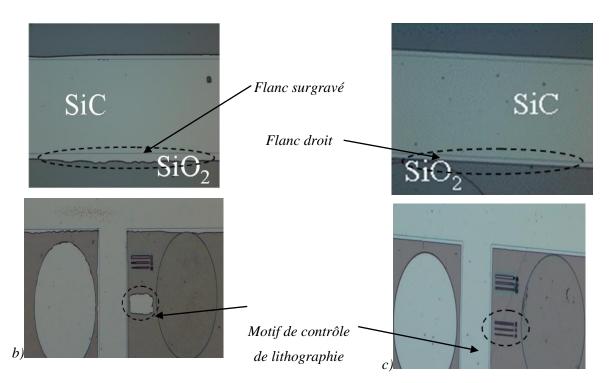

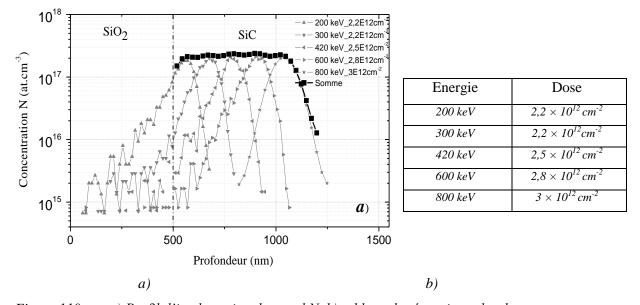

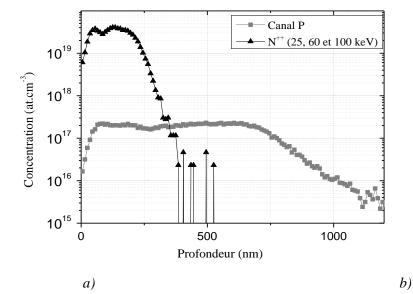

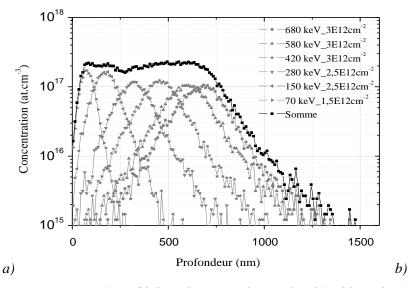

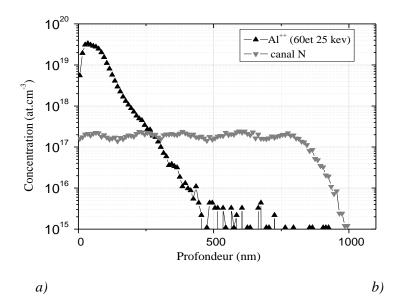

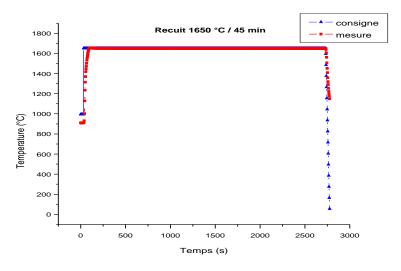

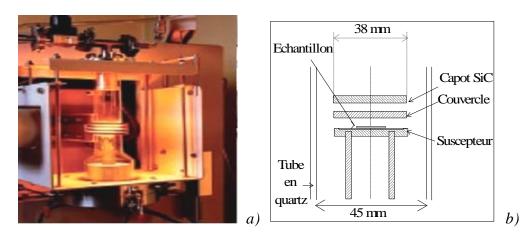

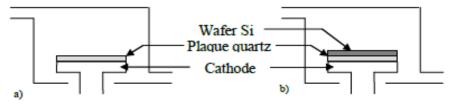

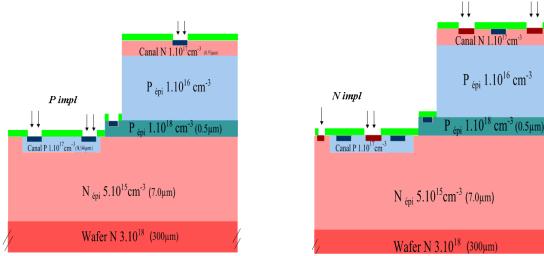

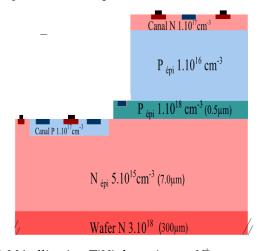

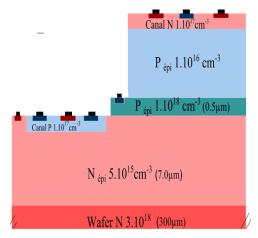

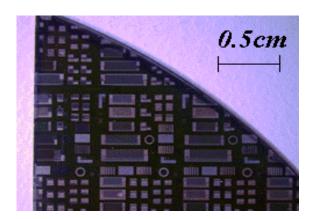

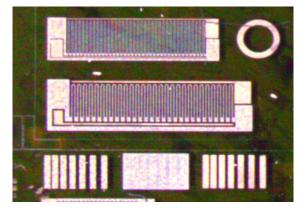

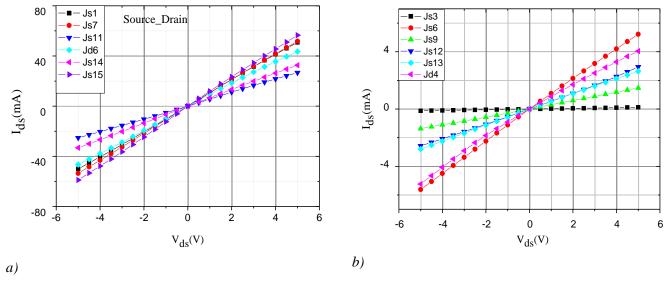

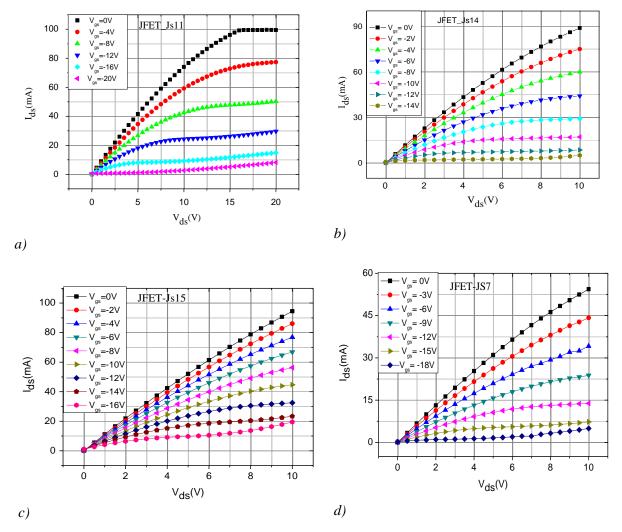

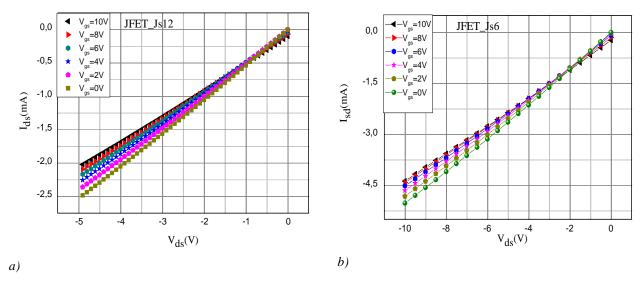

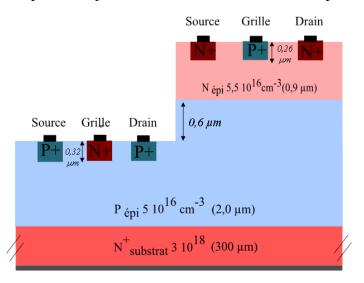

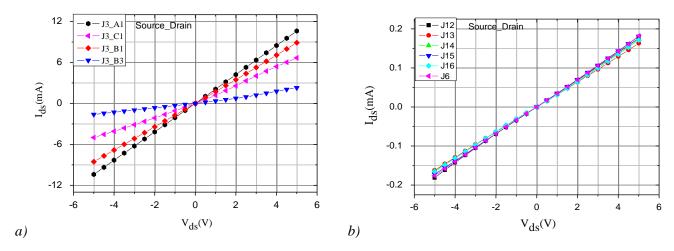

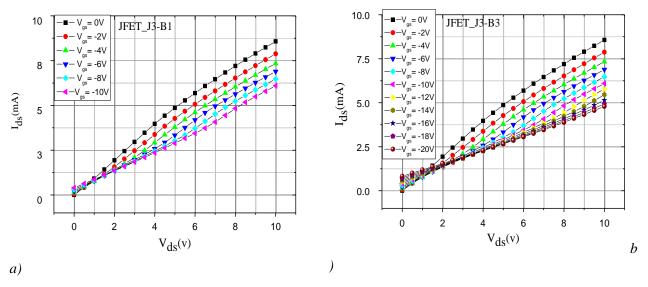

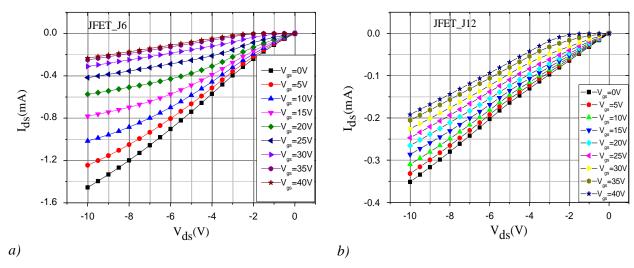

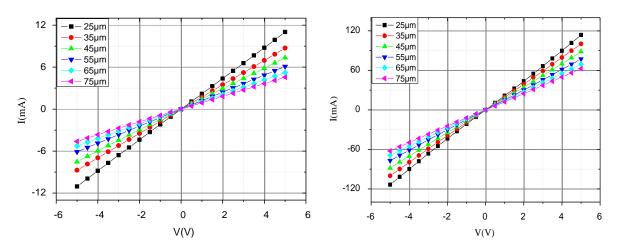

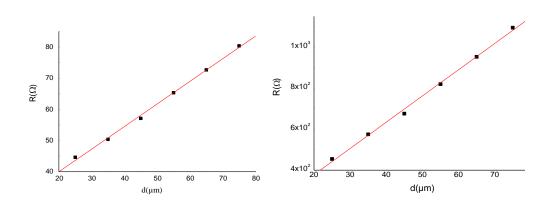

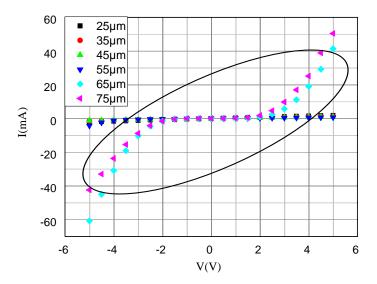

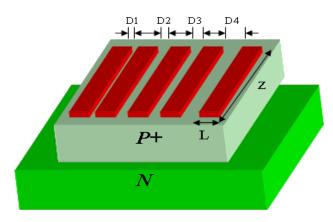

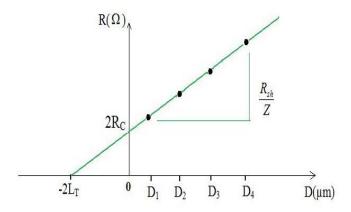

Pour l'azote (donneur), le site de substitution est le site carbone, alors que pour le phosphore (donneur) il s'agit la plupart du temps du site silicium [Rura 03]. Une étude a montré que le taux d'incorporation de dopants dépend du rapport Si/C lors de la croissance [Lark 97]. En effet, en augmentant le rapport Si/C de 0,1 à 0,5, l'incorporation intentionnelle d'azote est passée de  $10^{15} \, \mathrm{cm}^{-3}$  à  $10^{17} \, \mathrm{cm}^{-3}$ . Ces impuretés de type donneur possèdent des niveaux donneurs superficiels. Les accepteurs aluminium se substituent aux atomes de silicium. L'accepteur Bore quant à lui peut se substituer soit au site silicium en constituant un niveau superficiel, soit au site carbone en créant un centre profond. Les niveaux d'énergie des impuretés N, Al, V et B dans SiC-6H et SiC-4H sont donnés dans **le tableau 7.**