## System-Level Power Estimation Methodology for MPSoC based Platforms

Santhosh Kumar Rethinagiri

### ▶ To cite this version:

Santhosh Kumar Rethinagiri. System-Level Power Estimation Methodology for MPSoC based Platforms. Other. Université de Valenciennes et du Hainaut-Cambresis, 2013. English. NNT: 2013VALE0006. tel-00943272

## HAL Id: tel-00943272 https://theses.hal.science/tel-00943272

Submitted on 7 Feb 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Thèse de doctorat

# Pour obtenir le grade de Docteur de l'Université de VALENCIENNES ET DU HAINAUT-CAMBRESIS

Discipline, spécialité selon la liste des spécialités pour lesquelles l'Ecole Doctorale est accréditée : Informatique

Présentée et soutenue par Santhosh Kumar, RETHINAGIRI.

Le 14/03/2013, à Valenciennes

#### **Ecole doctorale:**

Sciences Pour l'Ingénieur (SPI)

### Equipe de recherche, Laboratoire :

Laboratoire d'Automatique, de Mécanique et d'Informatique Industrielles et Humaines (LAMIH)

# Une approche système pour l'estimation de la consommation de puissance des plateformes MPSoC

### **JURY**

#### Président du jury

- Valderrama, Carlos. Professeur. Université de Mons.

#### Rapporteurs

- Bourennane, El-Bay. Professeur. Université de Bourgogne.

- Belleudy, Cécile. Maître de conférences, HDR. Université de Nice-Sophia Antipolis.

#### **Examinateurs**

- Senn, Eric. Maître de conférences, HDR- IRISA. Rennes.

#### Directeur de thèse

- Dekeyser, Jean-Luc. Professeur. Université de Lille1.

#### Co-directeur de thèse

-Niar, Smail. Professeur. Université de Valenciennes.

#### Co-encadrant

-Ben Atitallah, Rabie. Maître de conférences. Université de Valenciennes.

# System-Level Power Estimation Methodology for MPSoC based Platforms

By

## Santhosh Kumar Rethinagiri

A thesis submitted for the degree of

## **Doctor of Computer Science**

## At the Université de Valenciennes et du Hainaut-Cambrésis

Ecole Doctorale Sciences Pour l'Ingénieur Université Lille Nord-de-France-072 Laboratoire d'Automatique, de Mécanique et d'Informatique Industrielles et Humaines (LAMIH)

**Speciality: Low Power Electronics and Design**

Domain: Design Tools, System and Software Design for Embedded Systems

### Dissertation

Presented and defended on: March 2013

#### **JURY**

| Reporter      | <b>Prof. El-Bay Bourennane,</b> Université de Bourgogne, Dijon    |

|---------------|-------------------------------------------------------------------|

| Reporter      | MCF HDR Cécile Belleudy, Université de Nice-Sophia Antipolis      |

| Examiner      | Prof. Carlos Valderrama, Université de Mons, Mons                 |

| Examiner      | MCF HDR Eric Senn, Université de Bretagne Sud, Lorient            |

| Superviser    | Prof. Jean-Luc Dekeyser, Université de Lille 1, Villeneuve d'Ascq |

| Superviser    | Prof. Smail Niar, Université de Valenciennes, Valenciennes        |

| Co-Superviser | Assoc. Prof. Rabie Ben Atitallah, Université de Valenciennes      |

## Acknowledgements

One of the joys of completion is to look over the journey past and remember all the friends and family who have helped and supported me along this long but fulfilling road. It is a pleasure to thank the many people who have made this thesis possible.

It is difficult to overstate my gratitude to my Ph.D. co-supervisor, Dr. Rabie BEN ATITALLAH. With his enthusiasm, inspiration, and great efforts to explain things clearly and simply, he made working on this thesis fun for me. Throughout my thesis-writing period, he provided encouragement, sound advice, good teaching, good company, and lots of good ideas. I would have been lost without him.

I feel enormously indebt to my directors at INRIA-Lille Nord Europe and at University of Valenciennes, Jean-Luc DEKEYSER and Smail NIAR, for giving me this opportunity. Furthermore, I want to thank all my colleagues of the LAMIH laboratory and the INRIA DaRT team for creating a perfect environment to work and to spend a pleasant time.

I would also like to thank my examiners, who provided encouraging and constructive feedback. It is no easy task, reviewing a thesis, and I am grateful for their thoughtful and detailed comments. To the many anonymous reviewers at the various conferences, thank you for helping to shape and guide the direction of the work with your informative and instructive comments.

This thesis was funded by National Research Agency (ANR) of France in the frame of the OPEN-PEOPLE project. As a member of OPEN-PEOPLE, I have been surrounded by wonderful colleagues who have provided me a rich and fertile environment to study and explore new ideas. At OPEN-PEOPLE, I would like to thank the project leader, Dr. Eric SENN, who has been extremely supportive in allowing me to participate in LAB-STICC laboratory activities while pursuing my PhD studies.

A special thanks to all my friends, who have accompanied me in this wonderful journey of professional and personal growth that started in Chennai and ended in Valenciennes. Thanks for putting up with me, being a support and sharing some unforgettable moments.

Lastly, I would like to thank my family for all their love and encouragement. I wish to thank my parents, Budha Purnima and Late Rethinagiri. They bore me, raised me, supported me, taught me and loved me. And most of all for my loving, supportive, encouraging and patient wife Sushma Rajaram whose faithful support during the final stages of this Ph.D. is so appreciated. I love you all dearly. Thank you.

Finally, I want to dedicate this thesis to my family, specifically to my mother and my wife. Thank you for supporting all my decisions and for your love. I hope you are proud of me and my work.

$Santhosh\ Kumar \\ Valenciennes$

## Abstract

Due to the ever increasing constraints on power consumption in embedded systems, this thesis addresses the need for an efficient power modeling and estimation methodology based tool at system-level. On the one hand, todays embedded industries focus more on manufacturing multiprocessor based platforms as they are cost and power effective. On the other hand, modern embedded applications are becoming more and more sophisticated and resource demanding: multimedia (H.264 encoder and decoder), software defined radio, GPS, mobile applications, etc. The most vital corrective measure adopted to tackle the increasing complexity of Multiprocessor System-on-Chip (MPSoC) is to commence designing at the system-level. Decisions taken at the system-level have a greater impact on the tape out of the chip in terms of power and energy but it poses a bigger challenge due to the large architectural solution space. For this reason, efficient system-level power estimation tools are therefore necessary to enable proper Design Space Exploration (DSE) based on power/energy and timing.

In this thesis, we propose a tool based on efficient hybrid system-level power estimation methodology for MPSoC. In this methodology, a combination of Functional Level Power Analysis (FLPA) and system-level simulation technique are used to compute the power of the whole system. Basically, the FLPA concept is proposed for processor architecture in order to obtain parameterized arithmetic power models depending on the consumption of the main functional blocks. In this work, FLPA is extended to set up generic power models for the different parts of the platform. In addition, a simulation framework is developed at the transactional level to evaluate accurately the activities used in the re-

lated power models. The combination of the above two parts leads to a hybrid power estimation that gives a better trade-off between accuracy and speed. The proposed methodology has several benefits: it considers the power consumption of the embedded system in its entirety and leads to accurate estimates without a costly and complex material. The proposed methodology is also scalable for exploring complex embedded architectures. Based on the proposed methodology, our Power Estimation Tool at System-Level (PETS) is developed.

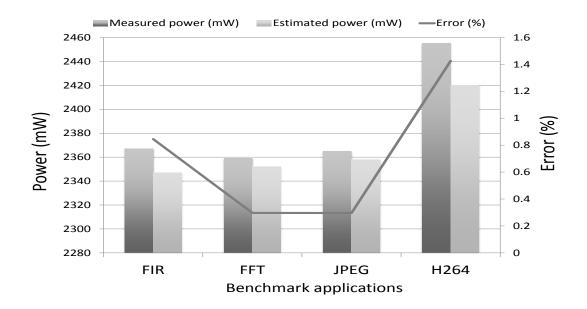

The effectiveness of our PETS tool is validated in terms of accuracy and speed through a typical mono-processor and multiprocessor embedded system designed around the TI OMAP (3530 and 5912) and the Xilinx Virtex II Pro FPGA boards. This methodology is demonstrated and evaluated by using a variety of basic programs to a complete media benchmarks. In order to ensure accuracy and speed, first we compared the estimated power value with the real board measurements for both mono-processor and multiprocessor architectures. Our obtained power estimation results provide less than 3% of error for mono-processor, 3.8% for homogeneous multiprocessor system and 4.3% for heterogeneous multiprocessor system. Second, we compared the estimation speed of our tool with the state-of-the-art power estimation tools and it resulted up to 70x faster.

## Résumé

Avec l'essor des nouvelles technologies d'intégration sur silicium submicroniques, la consommation de puissance dans les systèmes sur puce multiprocesseur (MPSoC) est devenue un facteur primordial au niveau du flot de conception. La prise en considération de ce facteur clé dés les premières phases de conception, joue un rôle primordial puisqu'elle permet d'augmenter la fiabilité des composants et de réduire le temps d'arrivée sur le marché du produit final.

Dans cette thèse, nous proposons une méthodologie efficace pour l'estimation de la consommation de puissance des plateformes MP-SoC. Cette méthodologie repose sur une combinaison d'une analyse fonctionnelle de la puissance (FLPA) pour l'obtention des modèles de consommation et d'une technique de simulation au niveau transactionnel (TLM) pour calculer la puissance de l'ensemble du système. Fondamentalement, FLPA est proposée pour modéliser le comportement des processeurs en terme de consommation afin d'obtenir des modèles paramétrés de haut niveau. Dans ce travail, FLPA est étendue pour mettre en place des modèles de puissance génériques pour les différentes parties du système (mémoire, logique reconfigurable, etc.). En outre, un environnement de simulation a été développé au niveau transactionnel afin d'évaluer avec précision les activités utilisées dans les modéles de consommation. La combinaison de ces deux parties conduit à une estimation de la puissance hybride qui donne un meilleur compromis entre la précision et la vitesse. La méthodologie proposée a plusieurs avantages: elle estime la consommation du système embarqué dans tous ses éléments et conduit à des estimations précises sans matériel coûteux et complexe. La méthodologie proposée est évolutive pour explorer des architectures complexes embarquées. Notre outil d'estimation de puissance au niveau système PETS (Power Estimation Tool at System-level) est développé sur la base de la méthodologie proposée. L'efficacité de notre outil PETS en termes de précision et rapidité est validée par des architectures embarquées monoprocesseur et multiprocesseur conçues autour des plateformes OMAP (3530 et 5912) et FPGA Pro Xilinx Virtex II.

## CONTENTS

| Co | onten | ${f ts}$                                                                  | x   |

|----|-------|---------------------------------------------------------------------------|-----|

| Li | st of | Figures                                                                   | iv  |

| Li | st of | Tables                                                                    | iii |

| 1  | Intr  | oduction                                                                  | 1   |

|    | 1.1   | Context                                                                   | 2   |

|    | 1.2   | Problem statement                                                         | 5   |

|    | 1.3   | Contributions                                                             | 7   |

|    | 1.4   | Plan of the thesis                                                        | 9   |

| 2  | Lite  | cature review                                                             | 11  |

|    | 2.1   | Introduction                                                              | 11  |

|    | 2.2   | Motivations for system-level design                                       | 12  |

|    | 2.3   | System-level modeling languages                                           | 17  |

|    |       | $2.3.1$ SystemC and Transaction Level Modeling $2.0~\mathrm{kit}$ (TLM) . | 18  |

|    |       | 2.3.2 Advantages to use TLM                                               | 19  |

|    | 2.4   | Power modeling approaches and tools                                       | 21  |

|    |       | 2.4.1 Low-level estimation techniques                                     | 23  |

|    |       | 2.4.1.1 Circuit-level                                                     | 23  |

|   |      |         | 2.4.1.2 Gate-level                                                                                                         | 23 |

|---|------|---------|----------------------------------------------------------------------------------------------------------------------------|----|

|   |      |         | 2.4.1.3 RTL                                                                                                                | 24 |

|   |      |         | 2.4.1.4 Architectural-level estimations                                                                                    | 26 |

|   |      | 2.4.2   | High-level estimation techniques                                                                                           | 28 |

|   |      |         | 2.4.2.1 Instruction Level Power Analysis (ILPA) 2                                                                          | 28 |

|   |      |         | 2.4.2.2 Functional Level Power Analysis (FLPA) 3                                                                           | 30 |

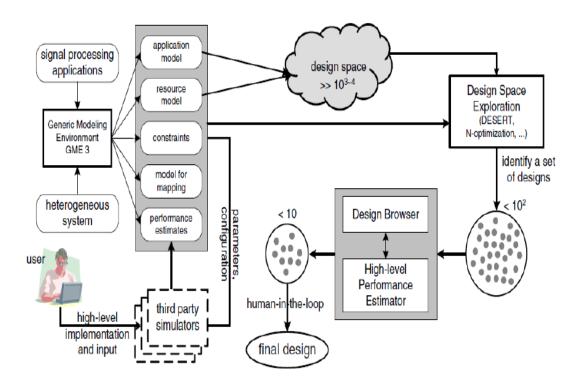

|   | 2.5  | Simula  | ation based estimation tools                                                                                               | 32 |

|   |      | 2.5.1   | SPADE 3                                                                                                                    | 33 |

|   |      | 2.5.2   | Metropolis                                                                                                                 | 34 |

|   |      | 2.5.3   | MILAN                                                                                                                      | 35 |

|   |      | 2.5.4   | MESH                                                                                                                       | 37 |

|   |      | 2.5.5   | StateC                                                                                                                     | 88 |

|   |      | 2.5.6   | CAFD                                                                                                                       | 39 |

|   | 2.6  | Analy   | tical power estimation tools                                                                                               | 10 |

|   | 2.7  | Refere  | $nced\ tools\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ 4$                                                                       | 11 |

|   | 2.8  | Overv   | liew of the industrial virtual platform tools available $4$                                                                | 12 |

|   | 2.9  | Positio | oning of methodologies                                                                                                     | 14 |

|   | 2.10 | Conclu  | ısion                                                                                                                      | 16 |

| 3 | Pow  | er mo   | deling methodology 4                                                                                                       | .9 |

|   | 3.1  | Introd  | $uction \dots \dots$ | 19 |

|   | 3.2  | Model   | ed platforms                                                                                                               | 50 |

|   |      | 3.2.1   | OMAP platforms                                                                                                             | 51 |

|   |      |         | 3.2.1.1 ARM Cortex-A8                                                                                                      | 51 |

|   |      |         | 3.2.1.2 ARM9                                                                                                               | 52 |

|   |      | 3.2.2   | Xilinx Virtex-II Pro platform                                                                                              | 54 |

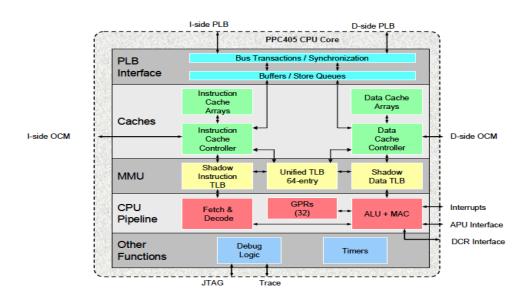

|   |      |         | 3.2.2.1 PowerPC 405                                                                                                        | 54 |

|   | 3.3  | FLPA    | methodology                                                                                                                | 55 |

|   | 3.4  | Power   | measurement environment                                                                                                    | 57 |

|   |      | 3.4.1   | Measurement environment for OMAP boards 5                                                                                  | 58 |

|   |      | 3.4.2   | Measurement environment for Virtex-II Pro FPGA 6                                                                           | 60 |

|   | 3.5  | Power   | models for uniprocessor based embedded platforms $6$                                                                       | 31 |

|   |      | 3.5.1   | ARM Cortex-A8                                                                                                              | 32 |

## CONTENTS

|   |     | 3.5.2  | ARM9                                                            | 5 |

|---|-----|--------|-----------------------------------------------------------------|---|

|   |     | 3.5.3  | PowerPC                                                         | 7 |

|   | 3.6 | Power  | models for multiprocessor platforms 6                           | 7 |

|   |     | 3.6.1  | Power model for homogeneous MPSoC 6                             | 8 |

|   |     | 3.6.2  | Power model heterogeneous MPSoC                                 | 1 |

|   | 3.7 | Valida | ation of the power models                                       | 4 |

|   |     | 3.7.1  | Evaluation of ARM Cortex-A8 power model                         | 5 |

|   |     | 3.7.2  | Evaluation of ARM9 power model                                  | 5 |

|   |     | 3.7.3  | Evaluation of PowerPC power model                               | 6 |

|   | 3.8 | Concl  | usion                                                           | 6 |

| 4 | Co- | simula | tion environment at system-level for power estimation 7         | 9 |

|   | 4.1 | Introd | luction                                                         | 9 |

|   | 4.2 | Virtua | al prototyping with the help of SoCLib environment $8$          | 1 |

|   |     | 4.2.1  | Available models at TLM-DT level for MPSoC design $8$           | 1 |

|   |     | 4.2.2  | Estimating performance with Soclib environment 8                | 4 |

|   | 4.3 | Virtua | al prototyping with the help of OVP platform 8                  | 7 |

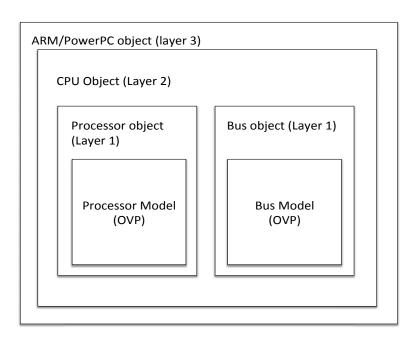

|   |     | 4.3.1  | OVP platform models for MPSoC design 8                          | 7 |

|   |     | 4.3.2  | OVPsim                                                          | 8 |

|   |     | 4.3.3  | Interfaces of OVPsim                                            | 0 |

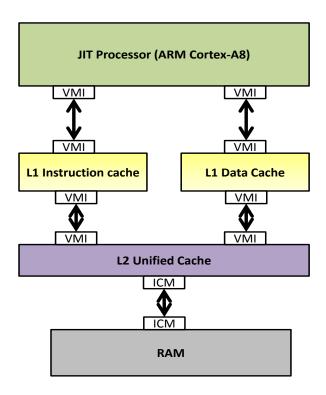

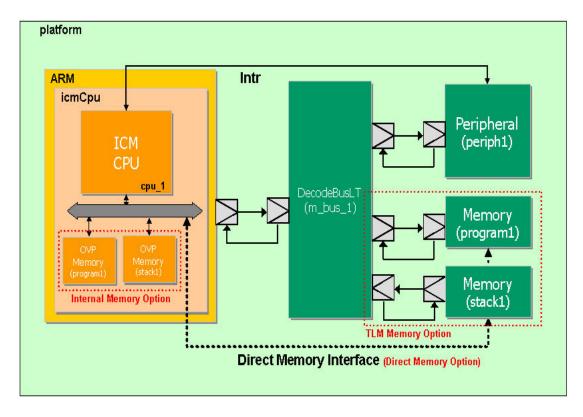

|   |     | 4.3.4  | VMI Memory Model                                                | 3 |

|   |     | 4.3.5  | Memory models                                                   | 7 |

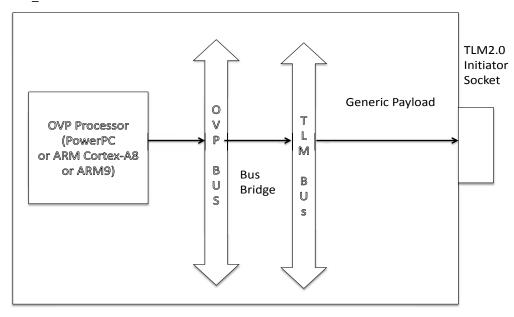

|   | 4.4 | OVP    | in SystemC/TLM environment                                      | 9 |

|   |     | 4.4.1  | OVP inside TLM2.0                                               | 0 |

|   | 4.5 | The si | imulation environment                                           | 5 |

|   | 4.6 | Exper  | imental results                                                 | 7 |

|   |     | 4.6.1  | JPEG algorithm                                                  | 7 |

|   |     | 4.6.2  | Application task graph mapping for dual processor platform $11$ | 0 |

|   |     | 4.6.3  | Performance estimation and simulation results of our pro-       |   |

|   |     |        | posed virtual platform                                          | 3 |

|   |     | 4.6.4  | Modeling efforts                                                | 6 |

|   | 47  | Concl  | usion 11                                                        | 7 |

| 5 Power Estimation Tool at System-level (PETS) and experimen |       |        | Tool at System-level (PETS) and experimental |                                                      |     |

|--------------------------------------------------------------|-------|--------|----------------------------------------------|------------------------------------------------------|-----|

| results                                                      |       |        | 1                                            | 19                                                   |     |

|                                                              | 5.1   | Introd | luction .                                    |                                                      | 119 |

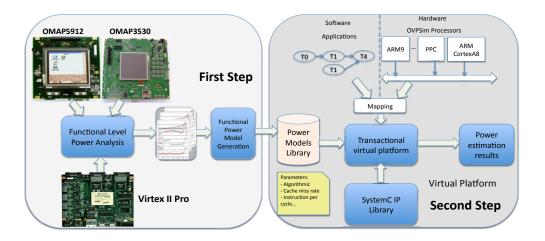

|                                                              | 5.2   | Hybri  | d power e                                    | stimation methodology                                | 120 |

|                                                              |       | 5.2.1  | Part 1:                                      | Power model generation                               | 121 |

|                                                              |       | 5.2.2  | Part 2:                                      | System-level environment development                 | 122 |

|                                                              |       | 5.2.3  | Enginee                                      | $ m ring\ efforts$                                   | 123 |

|                                                              | 5.3   | PETS   | tool desi                                    | gn flow $\dots$ $\dots$ 1                            | 124 |

|                                                              | 5.4   | Exper  | imental re                                   | ${ m esults}$                                        | 126 |

|                                                              |       | 5.4.1  | Power e                                      | stimation accuracy of monoprocessor based platform 1 | 126 |

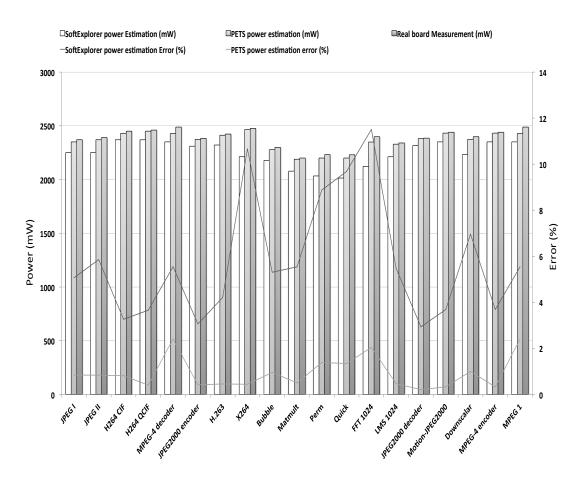

|                                                              |       |        | 5.4.1.1                                      | ARM Cortex-A8 based platform (OMAP3530) . 1          | 126 |

|                                                              |       |        | 5.4.1.2                                      | ARM9 based platform (OMAP5912)                       | 128 |

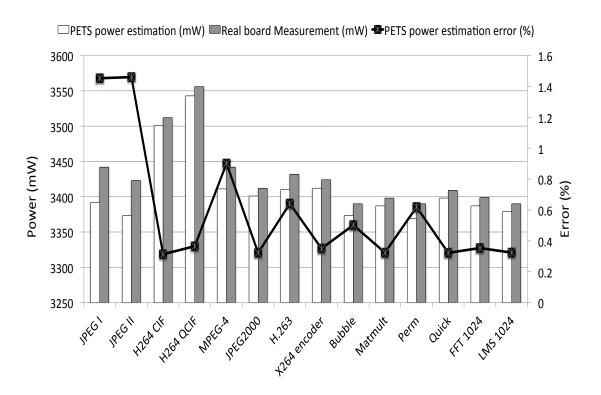

|                                                              |       |        | 5.4.1.3                                      | PowerPC based platform (Virtex II Pro) 1             | 131 |

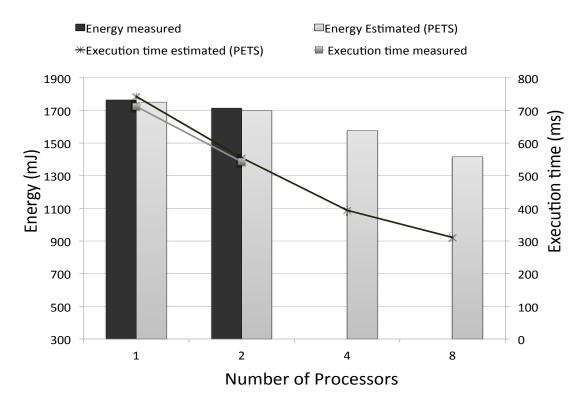

|                                                              |       | 5.4.2  | Homoge                                       | neous multiprocessor based platform                  | 133 |

|                                                              |       | 5.4.3  | Heteroge                                     | eneous multiprocessor based platform                 | 140 |

|                                                              |       | 5.4.4  | Estimat                                      | ion speed comparison                                 | 140 |

|                                                              |       |        | 5.4.4.1                                      | Estimation speed comparison of different approaches  | 140 |

|                                                              |       |        | 5.4.4.2                                      | Estimation speed comparison of different tools 1     | 141 |

|                                                              | 5.5   | Concl  | usion                                        |                                                      | 143 |

| 6                                                            | Cor   | clusio | ns and f                                     | uture works 1                                        | 45  |

|                                                              | 6.1   | Summ   | nary                                         |                                                      | 145 |

|                                                              | 6.2   | Future | e works                                      |                                                      | 147 |

| R                                                            | efere | nces   |                                              | 1                                                    | 51  |

| 1.1  | Context of the thesis in the OPEN-PEOPLE project                                                                                   | 4  |

|------|------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Gajski and Kuhn Y chart: source [44]                                                                                               | 12 |

| 2.2  | Broadness of architectural solutions according to the abstraction                                                                  |    |

|      | level                                                                                                                              | 15 |

| 2.3  | TLM speed-up in terms of modeling efforts and simulation speed                                                                     |    |

|      | : source $[46]$                                                                                                                    | 20 |

| 2.4  | TLM design flow : source $[46]$                                                                                                    | 21 |

| 2.5  | Power modeling methodologies and tools according the abstraction                                                                   |    |

|      | levels                                                                                                                             | 22 |

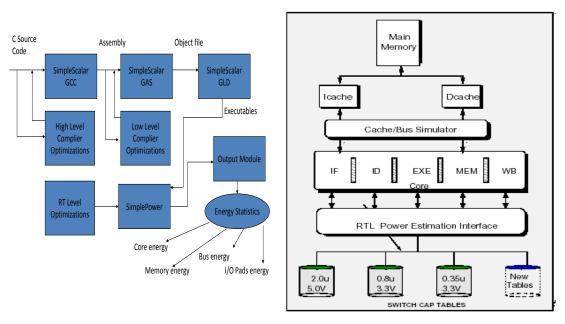

| 2.6  | Complier of SimplePower tool                                                                                                       | 27 |

| 2.7  | SimplePower simulator                                                                                                              | 27 |

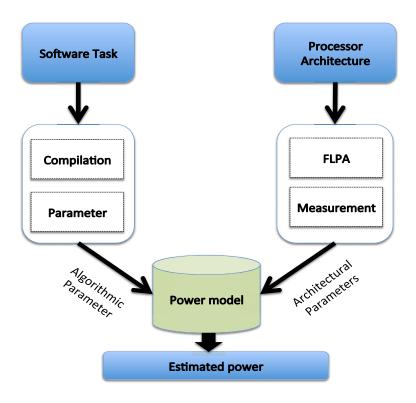

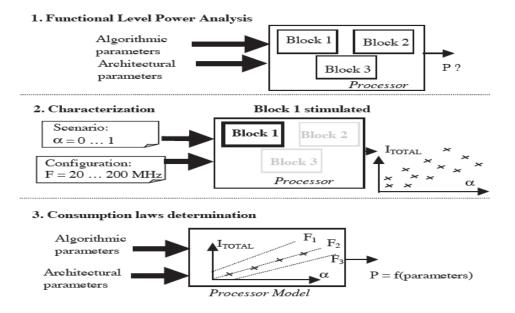

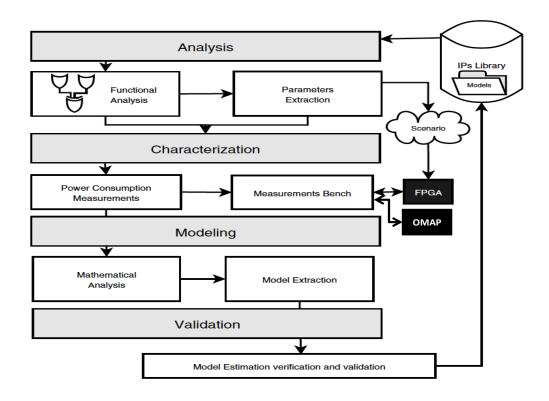

| 2.8  | FLPA general methodology                                                                                                           | 30 |

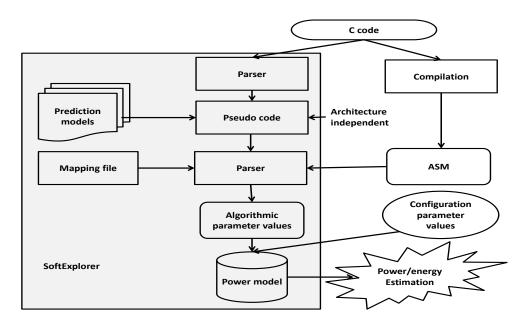

| 2.9  | SoftExplorer power estimation flow: source [59]                                                                                    | 31 |

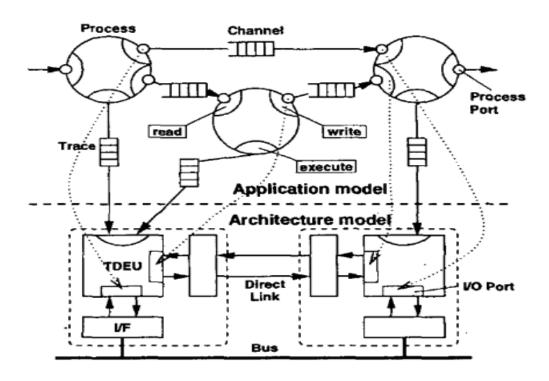

| 2.10 | SPADE design flow : source $[93]$                                                                                                  | 34 |

| 2.11 | Mapping network : source $[22]$                                                                                                    | 36 |

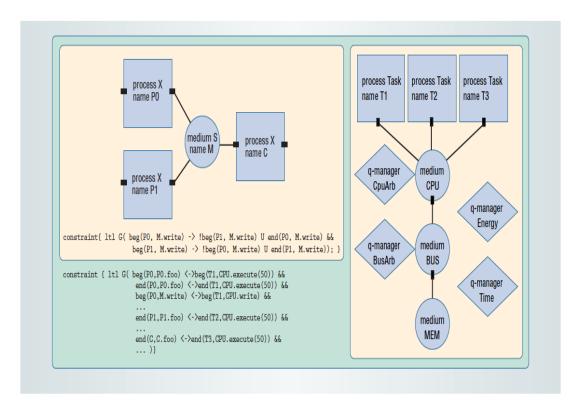

| 2.12 | $\label{eq:milder} \mbox{Milan framework: source [82]} \ \dots \ $ | 37 |

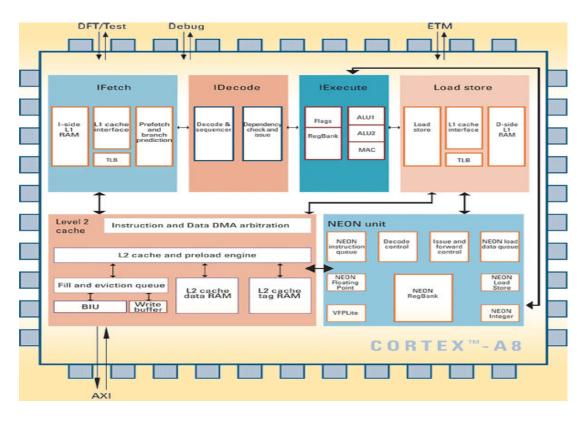

| 3.1  | Block diagram of ARM Cortex-A8 processor : source [16]                                                                             | 52 |

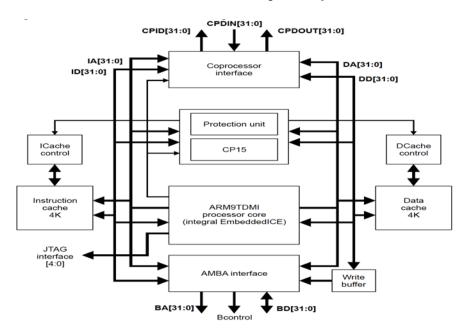

| 3.2  | Block diagram of ARM9TDMI processor: source [17]                                                                                   | 53 |

| 3.3  | Block diagram of PowerPC processor: source [55]                                                                                    | 54 |

| 5.0  | Diom diagram of Fower C processor. Source [00]                                                                                     | 01 |

| 3.4  | Functional Level Power Analysis (FLPA) general methodology :             |     |

|------|--------------------------------------------------------------------------|-----|

|      | source [69]                                                              | 55  |

| 3.5  | Power characterization and modeling methodology framework: source        |     |

|      | [41]                                                                     | 56  |

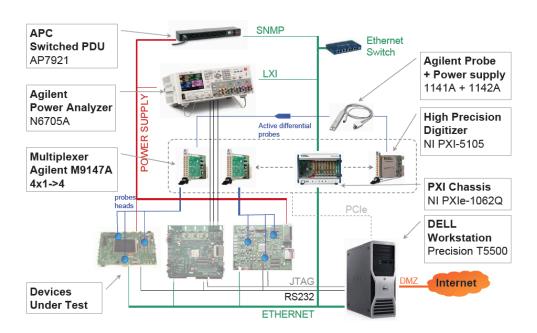

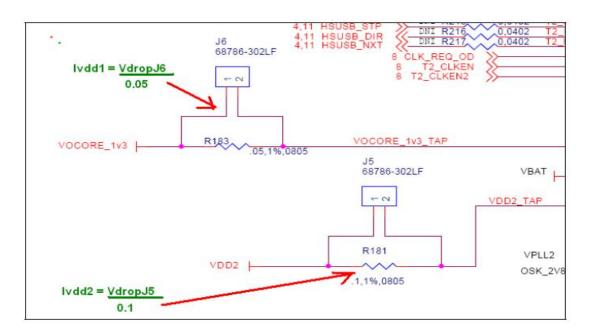

| 3.6  | Fully automated test bench for current/voltage measurement               | 58  |

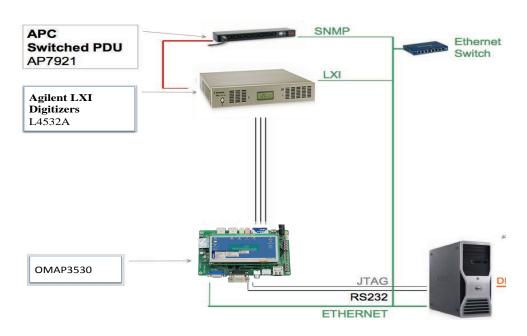

| 3.7  | Measurement environment for OMAP3530 and OMAP5912                        | 59  |

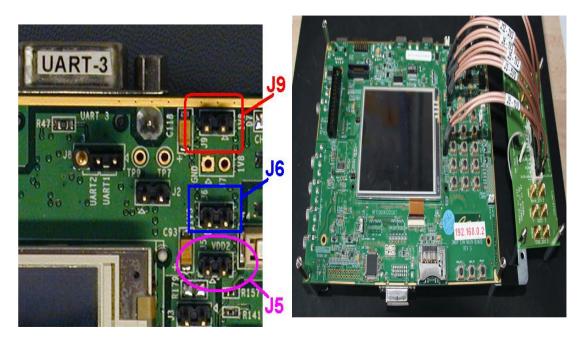

| 3.8  | Jumpers for OMAP3530                                                     | 59  |

| 3.9  | Power measurement probes across the jumpers for OMAP3530 $$              | 59  |

| 3.10 | Power measurement jumpers for the OMAP3530 platform                      | 61  |

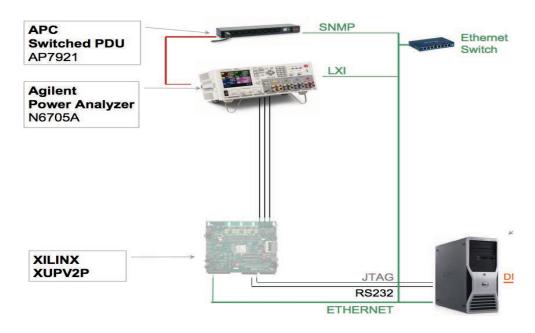

| 3.11 | Measurement environment for Virtex-II Pro FPGA                           | 62  |

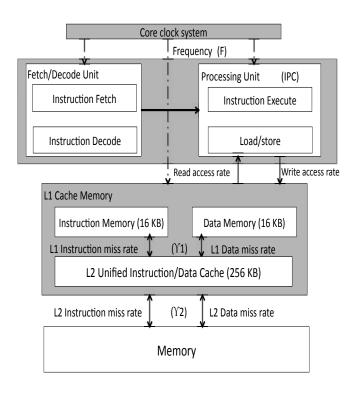

| 3.12 | Main functional blocks of ARM Cortex-A8 processor                        | 63  |

| 3.13 | Power consumption cost according to the Instruction Per Cycle            |     |

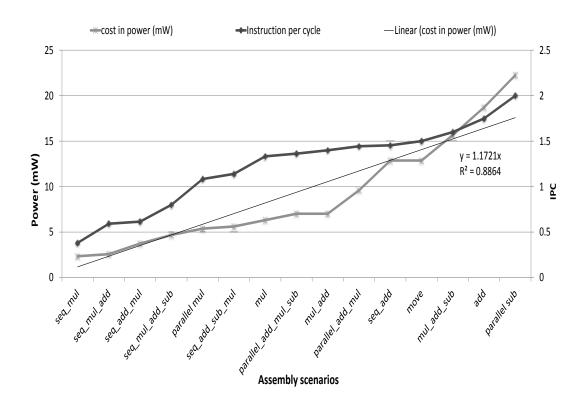

|      | $(IPC)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 64  |

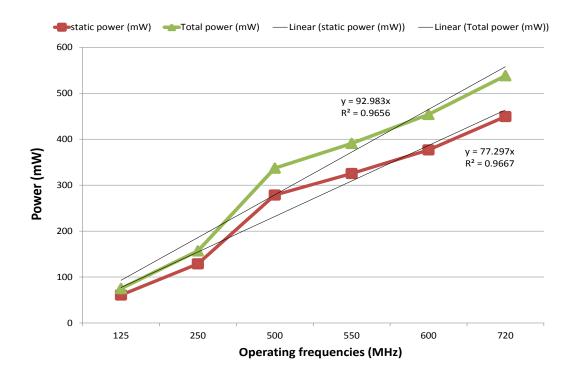

| 3.14 | Power consumption cost according to the change in frequency              | 65  |

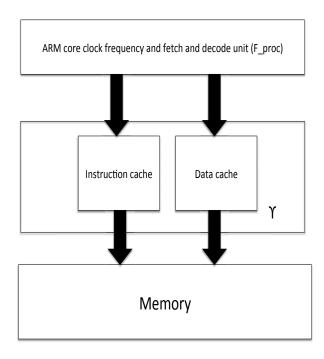

| 3.15 | Main functional blocks of ARM9 processor                                 | 66  |

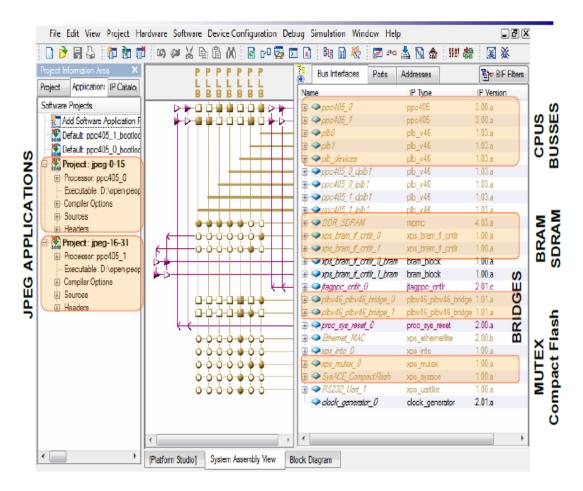

| 3.16 | Xilinx EDK 10.1 design for two PowerPC processors with shared            |     |

|      | memory                                                                   | 69  |

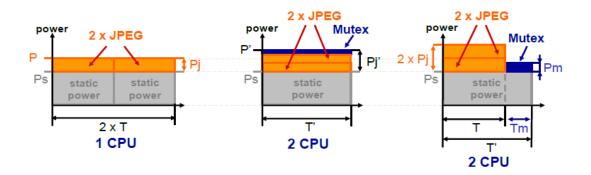

| 3.17 | JPEG mutex implementation between the two PowerPC processors             | 70  |

| 3.18 | Power/time/energy consumption and measurement                            | 71  |

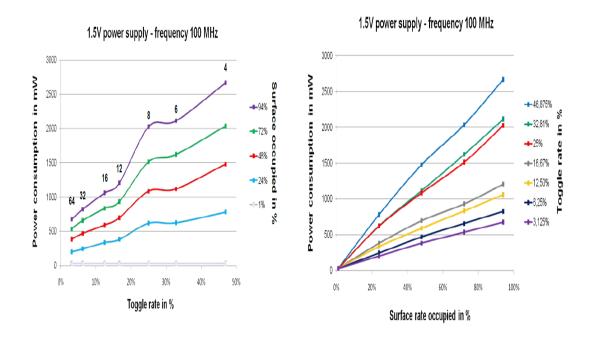

| 3.19 | FPGA power consumption with 100MHz frequency for different               |     |

|      | surfaces occupied                                                        | 72  |

| 3.20 | FPGA power consumption with 100MHz frequency for different               |     |

|      | toggle rates                                                             | 72  |

| 3.21 | Mutex power consumption                                                  | 73  |

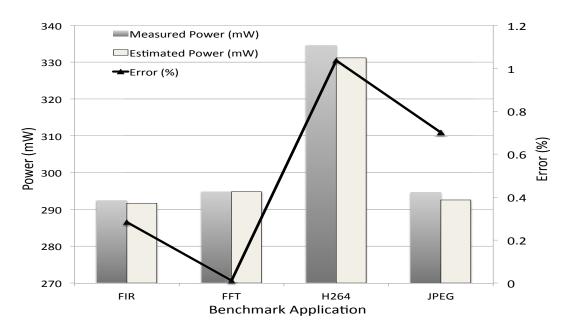

| 3.22 | Validation of the power model for ARM Cortex-A8                          | 74  |

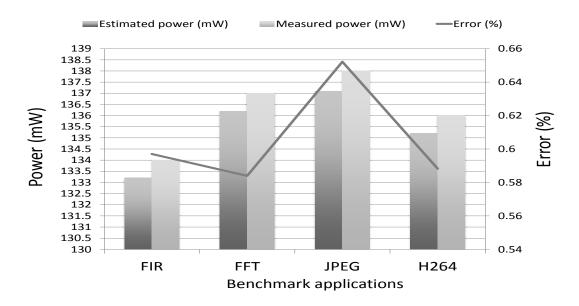

| 3.23 | Validation of the power model for ARM9                                   | 75  |

| 3.24 | Validation of the power model for PowerPC                                | 76  |

| 4.1  | Simulation Environment with SoCLib                                       | 85  |

| 4.2  | Communication of OVP interfaces                                          | 92  |

| 4.3  | Cortex-A8 interface implementation                                       | 99  |

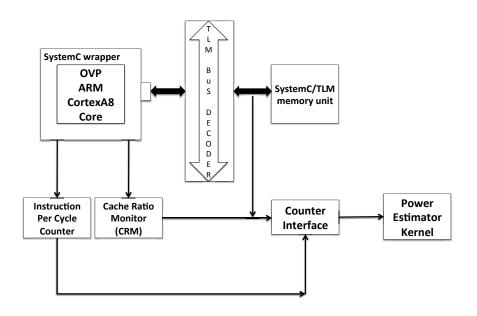

| 4.4  |                                                                          | 101 |

| 4.5  |                                                                          | 102 |

| 4.6  | Full system implementation: Source [89]                           | 103 |

|------|-------------------------------------------------------------------|-----|

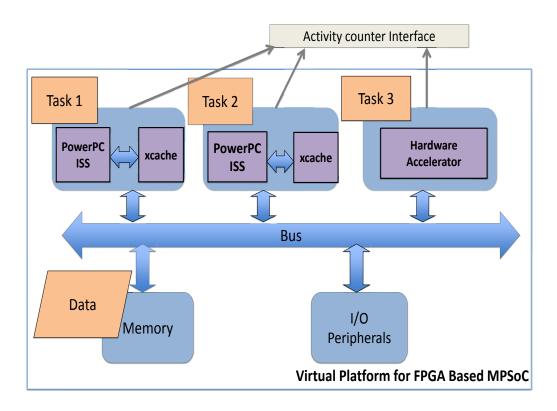

| 4.7  | Proposed virtual platform prototype                               | 105 |

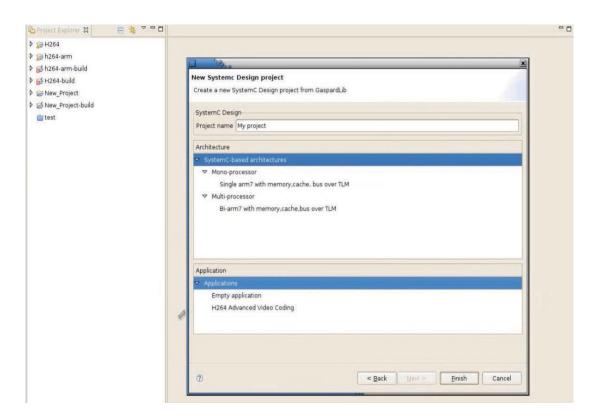

| 4.8  | Preferences for processor and application setting                 | 106 |

| 4.9  | Hardware/Software co-simulation                                   | 107 |

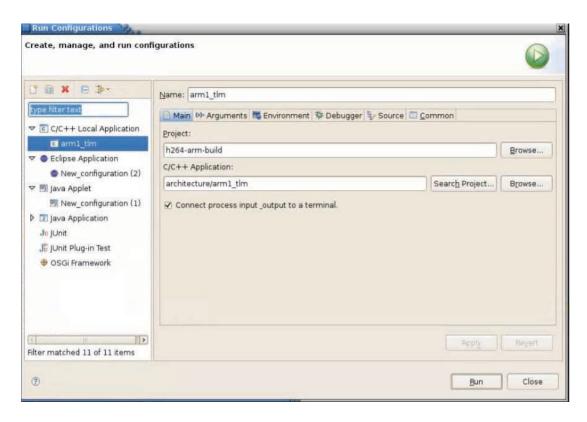

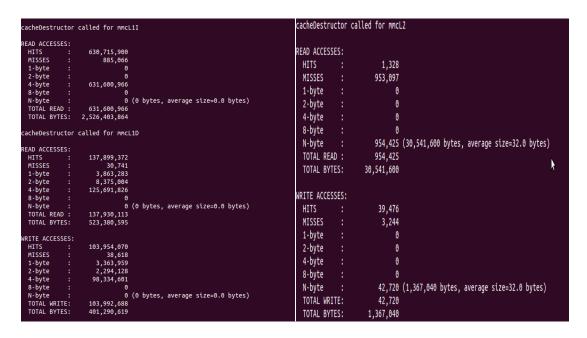

| 4.10 | L1 cache result after the simulation                              | 108 |

| 4.11 | L2 cache result after the simulation                              | 108 |

| 4.12 | IPC simulation results                                            | 109 |

| 4.13 | Simulation results for multiprocessor architecture                | 110 |

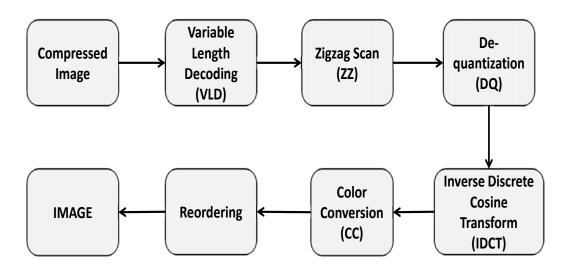

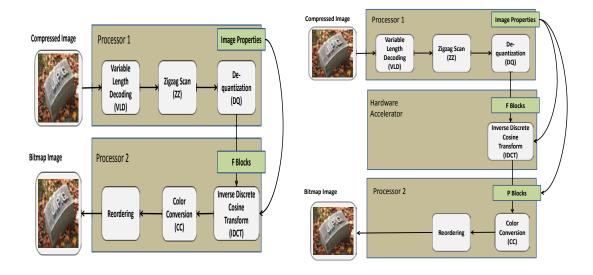

| 4.14 | JPEG decoder flow                                                 | 111 |

| 4.15 | JPEG decoding process with 2 processors                           | 112 |

| 4.16 | JPEG decoding process with 2 processors and hardware accelerator  | 112 |

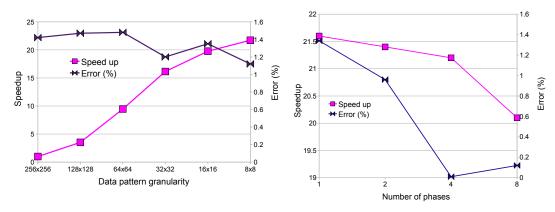

| 4.17 | Power estimation error and speedup according to the data pattern  |     |

|      | granularity                                                       | 115 |

| 4.18 | Power estimation error and speedup according to the number of     |     |

|      | phases                                                            | 115 |

| 5.1  | Power estimation flow                                             | 120 |

| 5.2  | PETS tool                                                         | 125 |

| 5.3  | Mono-processor platform of ARM Cortex-A8                          | 126 |

| 5.4  | Power estimation accuracy vs real board measurement using ARM     |     |

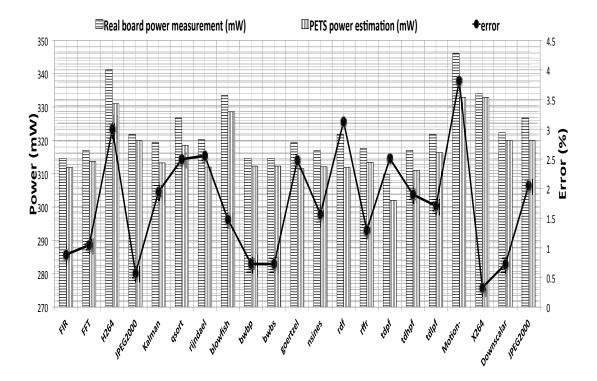

|      | Cortex-A8 at 500 MHz                                              | 127 |

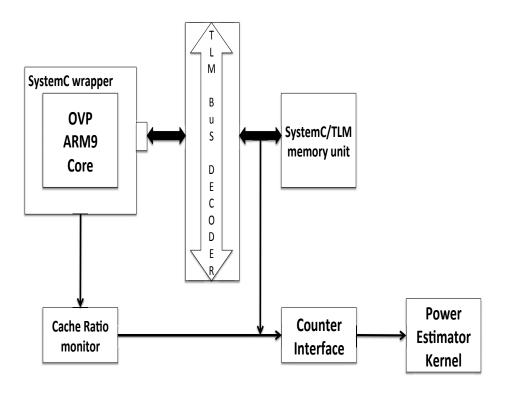

| 5.5  | Mono-processor platform (ARM9)                                    | 128 |

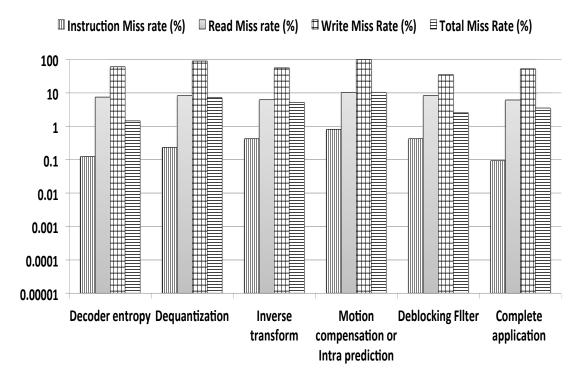

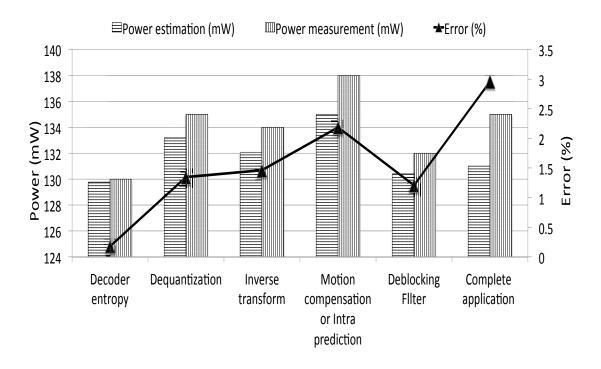

| 5.6  | Cache miss rate for the $\rm H.264$ application (ARM9 at 120 MHz) | 129 |

| 5.7  | Power estimation accuracy for the H.264 application using ARM9    |     |

|      | at 120 MHz                                                        | 130 |

| 5.8  | Power estimation accuracy vs real board measurement using ARM9    |     |

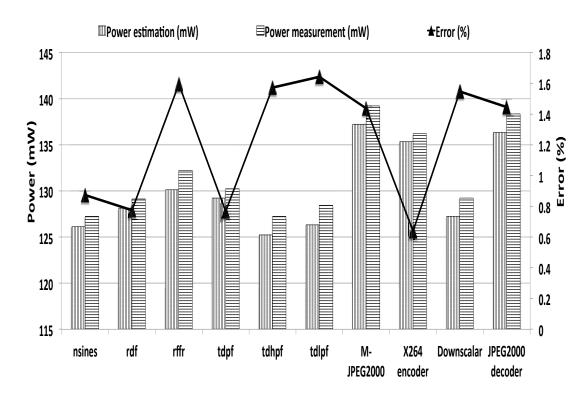

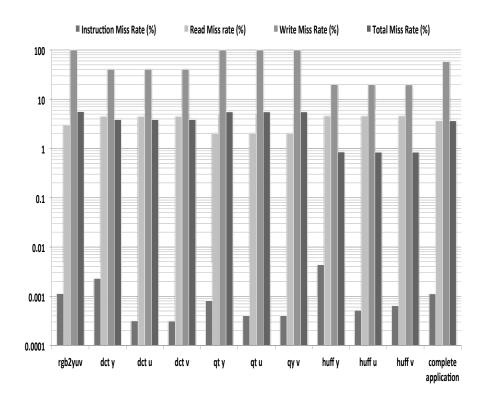

|      | at 120 MHz                                                        | 131 |

| 5.9  | JPEG application cache miss rates                                 | 133 |

| 5.10 | Power estimation accuracy                                         | 134 |

| 5.11 | Comparison of power estimation accuracy for PowerPC based ar-     |     |

|      | chitecture)                                                       | 135 |

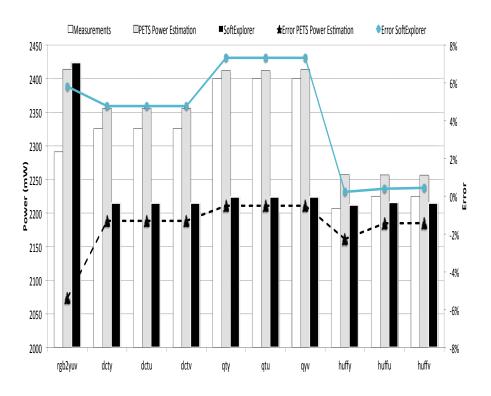

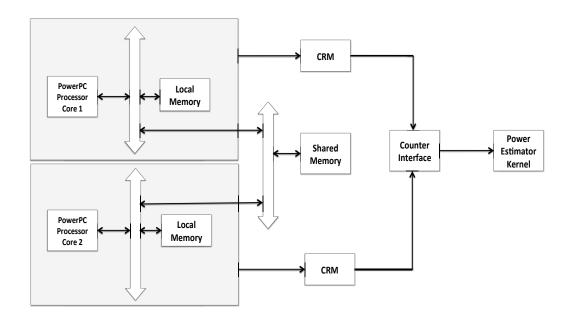

| 5.12 | Dual core PowerPC platform                                        | 136 |

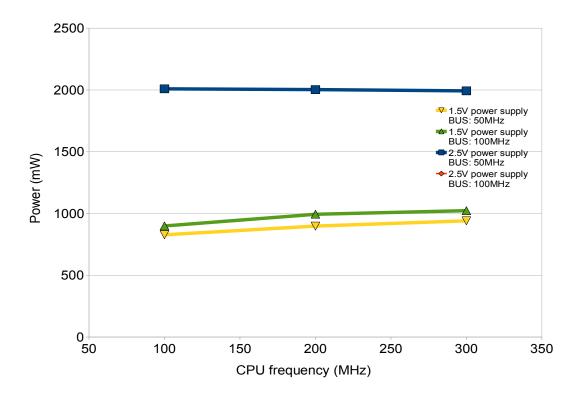

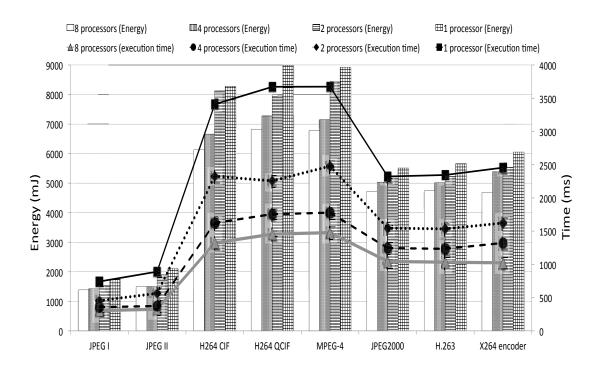

| 5.13 | Execution time and energy variation according to the number of                        |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | processors                                                                            | 137 |

| 5.14 | Power estimation of homogeneous two PowerPC multiprocessor ar-                        |     |

|      | $ \text{chitecture}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 138 |

| 5.15 | Energy estimation according to the number of processors using                         |     |

|      | PowerPC                                                                               | 139 |

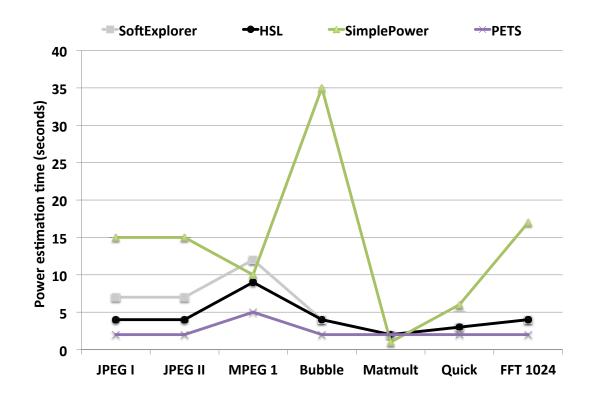

| 5.16 | Comparison of estimation time for the different tools                                 | 142 |

## LIST OF TABLES

| 2.1 | Tools used as references in this thesis                       | 41  |

|-----|---------------------------------------------------------------|-----|

| 3.1 | Consumption law for the ARM Cortex-A8 platform                | 65  |

| 3.2 | Consumption laws for the ARM9 platform                        | 66  |

| 3.3 | Consumption laws for the PowerPC 405 platform                 | 67  |

| 3.4 | Generic power model parameters                                | 68  |

| 4.1 | Application miss rates for PowerPC based ISS/TLM              | 86  |

| 4.2 | JPEG workload on 2 processors                                 | 113 |

| 4.3 | JPEG workload on 2 processors and hardware accelerator        | 113 |

| 4.4 | Application miss rates for PowerPC based virtual platform     | 114 |

| 4.5 | Timing comparison between proposed single processor environ-  |     |

|     | ment and SoCLib environment                                   | 114 |

| 4.6 | Timing comparison between proposed two processors environment |     |

|     | and SoCLib simulation environment                             | 115 |

| 4.7 | Modeling efforts                                              | 117 |

| 5.1 | JPEG application power estimation speed                       | 141 |

# LISTINGS

| 3.1 | Benchmark featuring two parallel ADD instructions | 64  |

|-----|---------------------------------------------------|-----|

| 4.1 | Instantiation of the processor                    | 92  |

| 4.2 | Instantiation of the full cache model             | 93  |

| 4.3 | Cache model settings                              | 95  |

| 4.4 | Cache Ratio Monitor (CRM)                         | 95  |

| 4.5 | Implementation of the memory models               | 97  |

| 4.6 | Instantiation of the memory models                | 103 |

## CHAPTER 1

## INTRODUCTION

This chapter describes the context, the problem statement, the contribution, and the plan of thesis. The main objective of this thesis work reclines in the scarcity of a fast and accurate power estimation tool at the system-level for complex embedded systems such as: homogeneous and heterogeneous Multi-Processor System-on-Chip (MPSoC). Without such a tool, a reliable Design Space Exploration(DSE) based on power and timing at system-level becomes impossible to achieve in a reasonable time, due to the broadness of the architectural solution space. As a consequence, taking the best architectural decisions becomes very challenging for system designers. However, since decisions taken at the system-level are the most relevant in affecting the quality of the final design, it is very important to take them right from the beginning, in order to avoid costly and time-consuming reiterations. The contribution of this work is therefore the implementation of a fast and accurate system-level power estimation methodology in a tool, which can really help system designers to take the best architectural decisions early in the design cycle.

## 1.1 Context

Due to the ongoing nano-miniaturisation in chip production, estimation of power consumption is becoming a critical pre-design metric in complex embedded systems such as homogeneous and heterogeneous Multi-Processor System-on-Chip (MPSoC). On the one hand, today's embedded industries focus more on manufacturing RISC processor-based platforms as they are cost and power effective. On the other hand, modern embedded applications are becoming more and more sophisticated and resource demanding. Examples of the concerned applications are numerous such as multimedia (H.264 encoder and decoder), software defined radio, GPS, mobile applications, etc. The computation requirements of such systems are very important in order to meet real-time constraints and high quality of services.

Recently, the ITRS [56] and HiPEAC <sup>1</sup> roadmaps promote power defines performance and power is the wall. An efficient and fast Design Space Exploration (DSE) of such systems needs a set of tools capable of estimating performance and power at higher abstraction level in the design flow. In current industrial and academic practices, power estimation using low level CAD tools is still widely adopted, which is clearly not suited to manage the complexity of modern embedded systems. Facing this issue, designers should calculate the power consumption as early as possible in the design flow to reduce the time-to-market and the development cost. Today, system-level power estimation is considered a vital premise to cope with the critical design constraints. However, the development of tools for power estimation at the system-level is in the face of extremely challenging requirements such as the efficient power modeling methodology, the rapid system prototyping and the accurate power estimates.

Hence, high-level power estimation and optimization in embedded system is the key issue in the early determination of the power budget, being infeasible to synthesize every design solution down to the gate and layout levels in a reasonable time. The goal is to shorten the design turn-around time, by widely exploring the architectural design space and to early re-target the architectural design choices. Accuracy and efficiency of a high-level power analysis should contribute to meet

$<sup>^{1} \</sup>rm http://www.hipeac.net/system/files/hipeacvision.pdf$

the power requirements and thus avoid costly re-design processes.

To address these design requirements, several industrial and academic institutes are devoting their efforts to facilitate the development of tools for MPSoC design taking into consideration the power metric as an essential parameter. The ANR-08-SEGI-013 OPEN-PEOPLE¹ project was defined in order to answer these requirements, it is funded by the National Research Agency (ANR) of France. OPEN-PEOPLE stands for Open Power and Energy Optimization PLatform and Estimator. Among the target systems, we mention heterogeneous MPSoC such as the TI OMAP 3530 and reconfigurable circuits like the Xilinx Virtex5 FPGA. Our platform allows power estimation using:

- direct access to the hardware execution boards and the measurement equipments. This first alternative enables designers to measure the real power dissipation of the target system. To do so, the low level description of the system (C, VHDL, etc.) is carried out natively on the target board. Furthermore, this alternative is used to build new power models for hardware or software components.

- a set of Electronic System Level (ESL) tools coupled with accurate power models elaborated within the first alternative. Mainly, we offer tools at the functional and transactional levels in the context of multilevel exploration of new complex architectures.

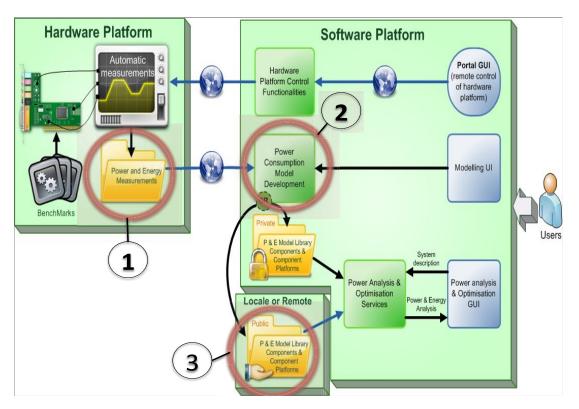

The Fig.1.1 presents a global view of the platform which is based on two main parts; the software part and the hardware part. The software user interface ensures the access to the power measurements and helps the designer to define energy models for the hardware and software system components. From the measurements, the designer can build models and compute an estimation of the energy and/or power consumption of the system. In addition, from this software user interface, the hardware platform can be controlled. The hardware part consists of the embedded system boards, the measurement equipments and the computer that controls these different elements and schedules the list of measurements required by different users. Various research and development works are currently done in the OPEN-PEOPLE project. These works include the definition

<sup>&</sup>lt;sup>1</sup>www.open-people.fr/

of new methods and tools to model the different components of a heterogeneous system architecture: processors, hardware accelerators, memories, reconfigurable circuits, operating system services, IP blocks, etc. For reconfigurable system, the dynamic reconfiguration paradigm will be modeled to estimate how this feature can be used by Operating System (OS) to reduce the energy consumption. Furthermore, this project studies how the complete estimation and validation can be performed for very complex systems with a small simulation time.

Figure 1.1: Context of the thesis in the OPEN-PEOPLE project

This PhD thesis research is a part of the OPEN-PEOPLE project. The main objectives of this work are encircled in red in the Fig.1.1. The first challenge concerns the development of power models for the selected platforms in the frame of the OPEN-PEOPLE project. The second challenge concerns the Software/Hardware co-simulation of MPSoC at the system-level where we focus on the transactional level (or TLM: Transaction Level Modeling) and virtual platform modeling in order to extract the relevant data for power estimation. The third challenge

concerns the development of a tool based on an efficient power estimation methodology offering a better trade-off between speed and accuracy, hence a reliable and a fast DSE.

### 1.2 Problem statement

In order to achieve the objective of designing efficient system-level power estimation tools for MPSoC, we started with extracting the main challenges related to the context of this thesis. We have identified three essential factors that define the problem statement and they are mentioned as follows:

- Power modeling methodology: The power modeling process is centred around two correlated aspects: the power model granularity and the main activity characterization. The first aspect concerns the granularity of the relevant activities on which the power model relies. It covers a large spectrum that starts from the fine-grain level such as the logic gate switching and stretches out to the coarse-grain level like the hardware component events. In general, fine-grain power estimation results in a more correlated model with data and to handle technological parameters, which is tedious for system-level designers. On the other hand, coarse-grain power models depend on microarchitectural activities that cannot be determined easily depending on the complexity of the system. The second aspect involves the characterization of the activities, which requires a huge number of experimental measurements and thus a significant time to extract the power model. The above described aspects yield to the definition of the power model that can be represented by a set of analytical functions or a table of consumption values. The selected power model granularity depends on the target abstraction level and the user requirements in terms of estimation accuracy and speed. For this first challenge, the main question that we have to answer is: what is the power modeling methodology suitable for MPSoC system-level design that can offer a better trade-off between the time needed to generate the power model and its corresponding accuracy?

- Software/Hardware co-simulation of MPSoC: The second challenge in-

volves the abstraction level on which the system is described. It starts from the usual Register Transfer Level (RTL) and extends upto the algorithmic level. This challenge is tackled by several frameworks by means of the development of Electronic System Level (ESL) tools. The objective is to unify the hardware and software design and to offer a rapid system-level prototyping. In the last years, significant academic and industrial efforts have been deployed to deal with the software/hardware co-simulation issue as the conventional RTL and Cycle-Accurate (CA) tools cannot adequately support the complexity of future MPSoC since they are too slow for a meaningful execution of the software. These efforts led to a taxonomy of tools based on different simulation techniques, description languages, abstraction levels, etc. However, most of these tools don't address the issue of power estimation. In general, going from low to high design level corresponds to more abstract description and then coarser activity granularity. For this second challenge, the main question that we have to answer is: what are the appropriate simulation technique and the abstraction level suitable for rapid MPSoC prototyping and for extracting accurately the activities for the defined power model (the first challenge)?

• Power based design methodology: Shifting towards higher levels of abstraction has proved to be a winning strategy for dealing with increasing complexity. Indeed, by abstracting away the lower-level details, implementation is faster, which means lower engineering effort, lower cost and lower time to market, as well as higher productivity. Decisions made at the system-level have a very strong impact on the quality of the final product, since the degree of achievable optimization is normally proportional to the abstraction level and, indirectly, to the point in the design flow where decisions are taken: the earlier the better. However, although very important, power based decisions at system-level are very hard to take and this is for two main reasons: the first is that, at the system-level, the design space to consider is extremely broad as a consequence of the limited amount of implementation details available. The second reason is that the impact of the decisions taken at system-level is not known until a very late stage of the design process, which can take months of work. From the second reason mentioned above, it can be con-

cluded that the lack of a quick and accurate System-Level Power Estimation (SLPE) approach is one of the main obstacles to successful system-level design today. In fact, if an efficient system-level methodology for energy and performance estimation was available, it would be possible to carry out a reasonably reliable DSE and thus judge from the beginning of the design flow which architecture is the most suitable for a certain applications domain, in terms of performance and power consumption. For this third challenge, the main question that we have to answer is: How to provide a tool at system-level in order to guide the designer during the different design choices based on power estimation?

## 1.3 Contributions

Our contributions through this thesis in the field of system-level power estimation for MPSoC design is to propose solutions to remove technological barriers presented in the previous section. In summary, our contributions are:

• Power modeling methodology: For modeling the power consumption of a MPSoC, we propose the application of the Functional-Level Power Analysis (FLPA), which basically allows to extract the processor power consumption model with a set of high level parameters (i.e., frequency, cache miss rate, etc.). The aim of this first step is to identify the sources of power consumption in the embedded system in its entirety (software tasks, hardware accelerators and the memory system). We have defined a power modeling methodology that concerns the software and hardware layers to cover the overall embedded system consumption. Our methodology defines the relevant activities on which the power model relies. These activities are characterized using measurements on real boards in order to guarantee the maximum level of accuracy. Afterwards, power models are elaborated by regression functions or simply recorded as multi-entries look up tables. It is important to have a scalable approach to address the complex system power/energy estimation issue. For these reasons, the developed power models are used in the frame of system-level estimation of homogeneous and heterogeneous MPSoC that may contain several processors and hardware accelerators. By extending FLPA

- methodology for the overall system, the development of power models are rapid and accurate which answers our first challenge.

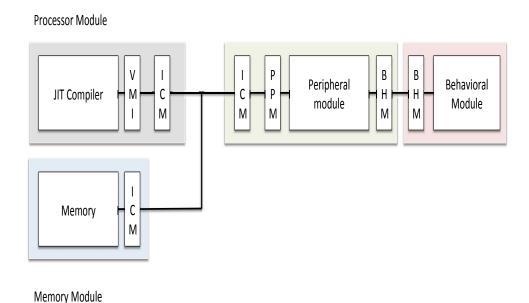

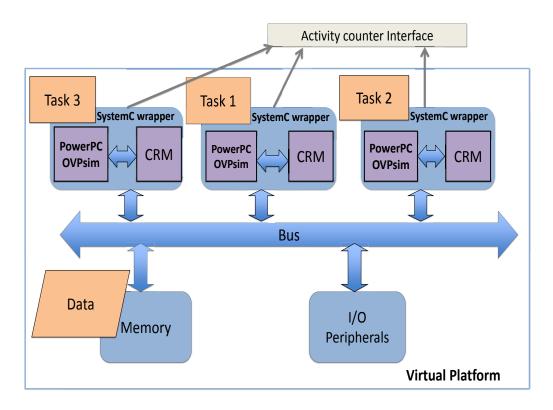

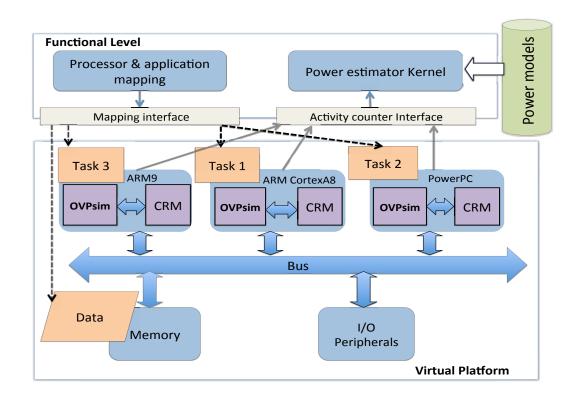

- Co-simulation of MPSoC for power estimation: To answer the second challenge, we propose an framework for hardware/software co-simulation at system-level for power estimation. A virtual platform based simulation technique is presented. It speeds up the time of the system with a good performance estimation accuracy. Virtual platform technique is implemented at a high abstraction level by using the SystemC/Transaction Level Modeling (TLM) 2.0 kit. It leverages the high-level system specification to provide a hardware/software co-simulation by using a Just In Time (JIT) simulator. The advent of design flows based on SystemC makes it possible that the modeling of a system is done by a tight and efficient coupling relationship between the hardware model and the virtual platform. A co-simulation solution proposed here is based on an architectural template consisting of a common bus and several processors SystemC with wrapper interacting with hardware IP's through the bus. There is a generic wrapper that is put around all CPU models. The wrapper can be seen as an extension of SystemC that makes hardware/software co-simulation more efficient. The SystemC simulation serves as a master that drives the overall simulation. The proposed SystemC simulation environment targets homogeneous and heterogeneous MPSoC with an ability to provide the relevant activities on which the power model relies as stated in the first contribution.

- Design methodology based on power estimation: The co-simulation environment for MPSoC has been enriched by models for estimation of power/energy in order to make possible the evaluation of the application. This parameter is the first selection criterion between different architectural solutions possible in order to have a design space exploration. The co-simulation environment also includes flexible tools for assessing the execution time. This metric is a second criterion for the selection of the most appropriate architectural solutions. This proposal was embodied in our work by developing models of performance estimation at system-level. In a detailed view, our work mainly contributes to the area of system-level estimation by proposing a system-level framework for power estimation, energy and performance,

which can indeed help system designers to take the best architectural decisions early in the design flow. The framework presented in this thesis comes as a proof of concept. Further extensions are required to make this framework more general and complete, as it will be discussed in the future works section, at the end of the thesis.

The contributions above were implemented in the environment of OPEN-PEOPLE developed by the team, especially to complement its design flow.

We can also classify the contribution of this thesis work into three sections:

- Concept related: It denotes the definition of the hybrid power estimation methodology. We start with the initial abstract idea of developing power models at the functional level and then integrating it into an independent simulation based framework for power estimation of different platforms.

- Tool related: The stated work in the thesis requires scripting, aimed at different processors and automating the operation that could not have been carried out manually. For instance, scripts have been written to automate the processor characterization, power model and also SystemC IP selection for a particular platform. At the software level, scripts have been written to set the application which has to be simulated on the SystemC environment.

- Experiment related: Experiments have been conducted throughout the entire development of hybrid power estimation methodology to validate the corresponding estimation accuracy and speed. Power estimation accuracy has been validated against real board measurements for a set of benchmarks. The target platforms used as reference for the experiments are Virtex II Pro, OMAP3530 and OMAP5912.

## 1.4 Plan of the thesis

This thesis report is organized as follows:

Chapter 2 presents an overview of the most common approaches of systemlevel design/ power estimation in use today and compares them to the proposed approach in this thesis. Large space is given to the description of simulation-based approaches with particular focus on the Transaction Level Modeling (TLM). Chapter 3 describes the proposed power modeling methodology and focuses on developing power models for processors (PowerPC, ARM9 and ARM CortexA8), homogeneous and heterogeneous MPSoC based platforms.

Chapter 4 gives the details of the development of the proposed system-level environment which is required for rapid prototyping and fast simulation for power estimation. The simulation support to integrate power models into System-C/TLM environment is also presented.

Chapter 5 shows the proposed hybrid power estimation methodology and explains the integration of power models into SystemC/TLM environment. It presents the Power Estimation Tool at System-level (PETS) which is based on hybrid power estimation methodology with the help of case-studies and the validation through the experimental results.

Chapter 6 draws the conclusions on the entire work and leaves space for some future works.

## CHAPTER 2

## LITERATURE REVIEW

## 2.1 Introduction

In this chapter, we present power estimation methodologies available in the literature and we compare them to the proposed methodology in this thesis. There are two types of approaches available: Simulation-based and analytical-based. More insight will be given on power modeling methodologies and simulation-based tools and in particular to the SystemC/TLM.

The conclusion drawn from the previous chapter is that being able to efficiently carry out system-level power estimation is a necessary condition to make design-space exploration (DSE) at system-level possible. Due to their importance and also lack of a defined model, power estimation at system-level in general is a hot research topic today. In this chapter, we will present a survey of the most significant tools for System-Level Design (SLD) with the capability of power estimation and different types of power modeling approaches. Finally, a comparison of our approach to the methodologies available in the literature is presented.

This chapter is organized as follows: Section 2.2, gives a brief description about basics, definition and motivations for system-level design. Section 2.4 presents the available power modeling methodologies in the literature. Sections 2.5 and 2.6 present the power estimation tools available respectively with

simulation-based and analytical-based approaches. Section 2.8 gives more details about the virtual platform tools available in the industries.

## 2.2 Motivations for system-level design

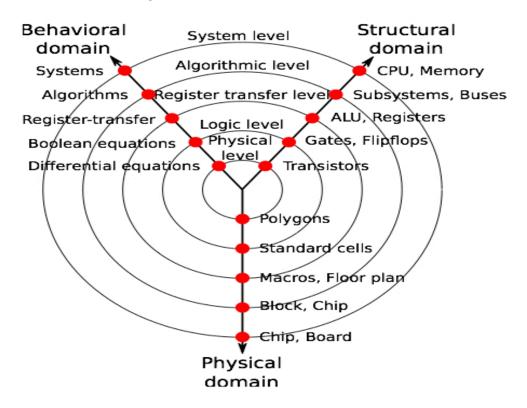

In 1983, Gajski and Kuhn derived what is today known as a Y-chart [44], which is a representation of the different abstraction levels at which a system can be modeled and estimated. This is shown in Fig. 2.1. Gajski and Kuhn distinguish five different abstraction levels, represented by concentric circles, each of which is classified according to three different domains: behavioral, structural and physical. The innermost circle corresponds to the lowest abstraction level, while the outermost one to the highest.

Figure 2.1: Gajski and Kuhn Y chart: source [44]

Until a few decades ago, it was still possible to manually describe a system directly at the physical level, since the amount of complexity was very limited.

When complexity grew, manual description at physical level became impossible and the starting point of the design flow was thus raised to a higher abstraction level, translate (synthesize) a gate-level description into a layout design. Similarly, as complexity kept growing, the starting point of the design flow was further raised up to the Register Transfer Level (RTL) was introduced. Two very well-known examples of languages used for RTL description are VHDL and Verilog. Along with the increase of complexity, todays trend is to further shift the entry level for automatic synthesis up to the system-level.

Thus, shifting towards higher levels of abstraction has proved to be a winning strategy for dealing with the increasing complexity. Indeed, by abstracting away the lower-level details, implementation is faster, which means lower engineering effort, lower cost and lower time to market, as well as higher productivity. Decisions made at the system-level have a very strong impact on the quality of the final product, since the degree of achievable optimization is normally proportional to the abstraction level and indirectly, to the point in the design flow where decisions are taken: the earlier the better. At the system-level, the question that system architects have to answer are the following: given a set of applications and a set of possible architectures, what is the best architecture on which to map this set of applications. The expression best architecture refers to the properties of an architecture in terms of metrics such as performance, power consumption and silicon area, for a given set of applications. For example, what is the power and performance impact of varying the number of levels in the memory hierarchy? What is the best interconnect to use: a bus or a NoC? What is the advantage/disadvantage of implementing part or the whole set of applications in hardware rather than software? These are just examples of the hard choices a designer has to make. Since they are so important, taking the right system-level decisions from the beginning is crucial, especially when complexity grows. Any error at this early stage would lead to annoying design reiterations with a consequent high loss of time, money and probably, a sub-optimal final implementation.

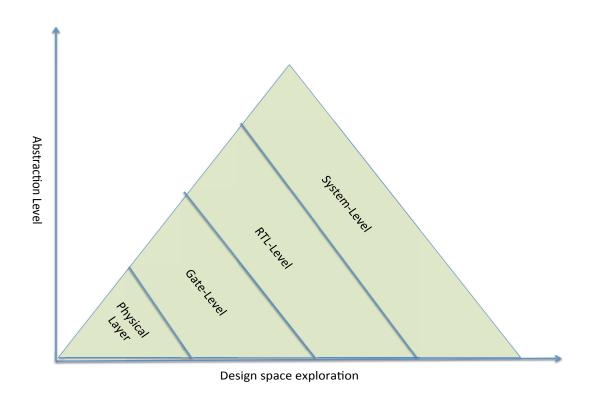

However, although very important, decisions at system-level are very hard to take and this is for two main reasons: the first is that, at the system-level, the design space to consider is extremely broad as a consequence of the limited amount of implementation details available. Fig. 2.2 shows the relation between

the design space width and the abstraction level. The second reason is that the impact of the decisions taken at system-level is not known until a very late stage of the design process, which can take months of work.

From the second reason mentioned above, it can be concluded that the lack of a quick and accurate system-level power estimation approach is one of the main obstacles to a successful system-level design today. In fact, if an efficient system-level methodology for energy and performance estimation was available, it would be possible to carry out a reasonably comprehensive DSE and thus judge from the beginning of the design flow which architecture is the most suitable for a certain application domains, in terms of performance and power consumption. In addition, estimation at any abstraction level is a requirement for the implementation of automatic synthesis tools, since it is only after estimation that the tool can judge what the best solution is.

Efficient estimation at lower abstraction levels has allowed us to have quite mature automatic tools today. Estimation at the physical level requires accounting for the individual capacitance and resistance contributions coming from each transistor and interconnecting wire. Estimation at this level is extremely accurate, but also very slow. Simulation at physical level is also very slow and is thus feasible for only very small designs and for a very short design execution time.

At the gate level, estimation is simplified by the fact that standard cells are used whose physical properties are pre-characterized. Only the impact of cell-to-cell connecting wires has to be estimated separately, which is done using so called wire load models. Estimation at this level is less accurate, although faster, and bigger design sizes can be simulated. At the RTL level, Hardware Descriptive Languages (HDL) are used to describe in words what RTL synthesis translates into logic gates. Simulation is very common at RTL and reasonably fast for medium size designs running very short chunks of application. However, estimation made at this level loses accuracy due to the lack of enough physical details. In general, the increase of the abstraction level is directly proportional to the estimation speed and inversely proportional to the estimation accuracy. When it comes to system-level, the lack of an efficient estimation methodology has been an obstacle to have mature automatic system-level tools available today. In fact, the operation of mapping the system-level functional description to the actual

Figure 2.2: Broadness of architectural solutions according to the abstraction level

architecture is still largely done manually. The decision making approach used by system designers has been mostly relying on their acquired experience, on comparison with previous designs and on rules of thumb. However, while this approach can still work with small/medium-size systems, its application to nowadays more and more complex systems has become unrealistic and the need for a more systematic and accurate approach has become a necessity. Cycle-Accurate (CA) and Transaction Level Modeling (TLM) have appeared at the beginning of the last decade as a descriptive based approach raising the abstraction level above RTL in order to reduce simulation time and development effort.

In late 1990s, many large companies started to develop their own models while research institutes and EDA start-ups were proposing a variety of modeling languages. The initial requests were to have cycle-accurate C or C++ models from certain who believed that it was the right way to get simulations running at least one order of magnitude faster than RTL models in VHDL or Verilog. It

soon became obvious that cycle-accurate modeling had several drawbacks [46]. First, the modeling effort was close to the one of creating synthesizable RTL models. It was due to fact that the model complexity was too close to RTL. The only gain was that such models had no synthesis-related constraints [46]. In addition, the RTL was still the reference due to immature synthesis tools. It led to iterations of the C++ model trying to keep in line with the RTL model of the IP under design. Introducing any specification change in the C++ model during the design was almost as long as doing so in the RTL model. The cycleaccurate modeling was actually leading to high costs. These models were not available to architects and were ready for software developers a little too late. Second, the simulation speed for a SoC model was ten times below the original objective. It was simulating at a few kHz compared to the several hundreds of Hz for RTL. Third, using specific languages or modeling optimizations to gain speed was actually locking the modeling team into a specific simulator supplier [46]. Fourth, during final RTL updates before tape-out, it was usually not possible to keep updating the cycle-accurate C++ model due to tight schedule. Thus, the cycle-accurate model was not fully consistent with the reference RTL at tape-out [46]. Normally, modeling engineers would be allocated to another project once the SoC was taped-out. The model would not be usable as a starting point for its next generation design because it was not consistent with the existing RTL and original modeling engineers were unavailable. For all these reasons, we were looking for an higher level of abstraction that would allow much quicker modeling than cycle-accuracy, yet be precise and fast enough for software developers to test the real embedded software using a standard language enabling reuse of models with a variety of simulator suppliers. Ideally, such models should also be usable for performance estimations with enough precision for SoC architects to make decisions.

In essence, TLM abstracts away the RTL details and models functionality and communication among the system modules. Communication is seen as an exchange of transactions between architectural resources. As a result, TLM has proved to be much faster than CA and RTL. The natural question that comes as a conclusion of the above discussion and also the motivation behind this thesis work is as follows: As it has been discussed that system-level estimation is essential

for a successful system-level design, how is it possible to implement a fast and accurate methodology for efficient system-level estimation.

## 2.3 System-level modeling languages

The terms of TLM defined in the last section can be attained through an appropriate electronic system level (ESL) modeling approach. The right candidate to do this job is a high-level programming language that is capable of developing not only a plain software program, but also of modeling electronic hardware at the conceptual level without describing the real implementation. The potential candidates include System [91], Spec [65], Hpascal [42], System verilog [121] and Hardware-C [49]. Specification at higher levels of abstraction is possible in environments such as SpecC. A unified and integrated approach to hardwaresoftware co-design is possible if the hardware modeling description is based on the C/C++ languages that are popular in the software community. Hardware-C [49] is an example of such a proposal. SystemC is an emerging standard modeling platform based on C++ that addresses the issues discussed above, and supports design abstraction at the RTL, behavioral and system levels. Consisting of a class library and a simulation kernel, the language is an attempt at standardization of a C/C++ design methodology, and is supported by the Open SystemC Initiative (OSCI), a consortium of a wide range of system houses, semiconductor companies, IP providers, embedded software developers, and design automation tool vendors. Apart from the modeling benefits available in C++ such as data abstraction, modularity, and object orientation, the advantages of SystemC include the establishment of a common design environment consisting of C++ libraries, models and tools, thereby setting up a foundation for hardware-software co-design; the ability to exchange IP easily and efficiently; and the ability to reuse test benches across different levels of modeling abstraction.

In the upcoming sections, we will go through SystemC/TLM used for designing tools at system-level and also advantages of using SystemC/TLM.

## 2.3.1 SystemC and Transaction Level Modeling 2.0 kit (TLM)

In the recent years, SystemC/TLM [91] has become widely popular among the simulation based approaches in academics and also in industries. This huge popularity is also due to support of the main actors in the domain such as Synopys[9] and Cadence[13].

SystemC is based on a set of C++ classes and provides an event-driven simulation kernel [48]. These facilities enable a designer to simulate concurrent processes, each described using plain C++ syntax. SystemC processes can communicate in a simulated real-time environment, using signals of all the datatypes offered by C++, some additional ones offered by the SystemC library, as well as user defined. In certain respects, SystemC deliberately mimics the hardware description languages VHDL and Verilog, but is more aptly described as a system-level modeling language. In fact, it models hardware at a higher abstraction level than RTL and, in order to do this, it uses C++ as a programming language. Higher abstraction level means higher simulation speed but also less accuracy. The way SystemC trades-off these two important metrics has been characterized in [117]. SystemC is applied to system-level modeling, architectural exploration, performance modeling, software development, functional verification and high-level synthesis. SystemC is often associated with ESL design and with TLM.

Using SystemC as a vehicle to provide the Transaction Level Modeling (TLM) abstraction proved to be the key to the fairly fast deployment of this methodology. There was no issue of proprietary language support by only one CAD vendor or university. There was also no issue of making a purchase decision by the design manager for yet another costly design tool. Eventually, with the collaboration of ARM and Cadence Design Systems, a full-blown proposal was made to the Open SystemC Initiative (OSCI), under the name PV (Programmer View) and PVT (Programmer View Timed). Indeed Programmer View clearly reflects the intent of this new abstraction level, which is to bridge the gap between the embedded software developer and the hardware architect. In 1999, companies like CoWare and Synopsys started to encouraged the Open SystemC Initiative (OSCI) in order to develop an HDL which could model hardware at a higher abstraction level

rather than widely used VHDL and Verilog. The main stimulus was to provide an improvement in the implementation and the simulation efficiency when compared to RTL, which has proved to be a bottle neck in modeling a system-level architecture. TLM tool kit was first introduced in 2000 [76]. TLM tool kit is a set of library function built on the top of an high level language, which is very often SystemC. In TLM, a transaction represents the data exchanged between the different system modules. As we said before similar to SpecC even in SystemC/TLM the computational component is separated from the communication component. For this purpose, TLM provide constructs to efficiently model the inter-module communication component, while the intra-module computational component is generally modeled at the functional/behavioral level. Standard routines have been implemented in TLM which model unidirectional versus bidirectional and blocking versus non-blocking communication. Communication is modeled using channels, interfaces and ports, which are objects provided by the underlying HLL. In the context of this thesis, TLM tool kit version 2.0 is used as a reference.

## 2.3.2 Advantages to use TLM

Based on what has been said so far, using TLM has some clear benefits:

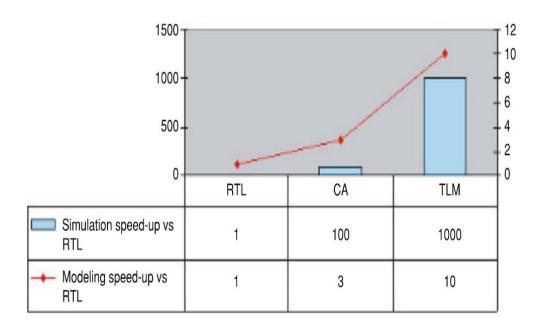

- First, there is a speed-up in the implementation when compared to the traditional RTL and Cycle-Accurate (CA) approach. This speed-up comes from the fact that most of the RTL and CA details are abstracted away. In use, only the behavioral description is used instead of the computational block details. In [46], the author reports a speed-up of up to 10x and 7x when modeling in TLM compared to RTL and CA as shown in the Fig. 2.3.

- Second, regarding synchronization issues, SystemC and TLM have helped major designers. According to Yi et al. in [131], This issue is due to multiple simulation models may have to run together and synchronize to each other. By using SystemC, there is a homogenous environment for hardware/software co-simulation, thus replacing the considerable Inter-Process Communication (IPC) overhead with a light-weighted thread switch overhead.

Figure 2.3: TLM speed-up in terms of modeling efforts and simulation speed : source [46]

- Third, compared to the traditional RTL and CA approach, TLM has higher simulation speed of 1000x and 900x respectively [46] as shown in the Fig. 2.3.

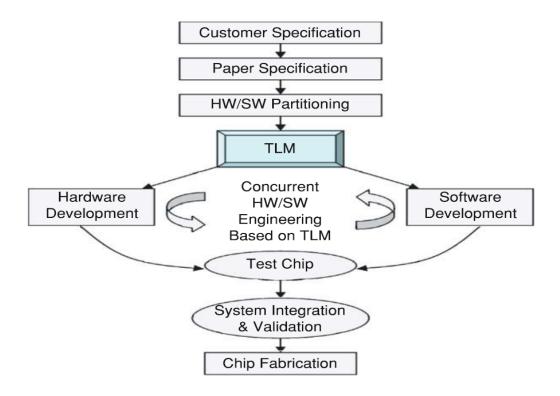

- Fourth, F. Ghenassia in [46] states that using the TLM design flow can allow a more efficient HW/SW co-design. This is shown in Fig. 2.4. In essence, the TLM flow would allow a concurrent development of hardware and software: the architectural TLM of the hardware infrastructure enables early software development and verification of hardware software interfaces. This is also a consequence of the fact that, in the classic design flow, software is usually implemented in C/C++, while hardware in VHDL/Verilog. In the TLM flow instead, both the software and hardware models are implemented in C/C++; thus concurrent testing becomes more feasible and the overall design time shorter.

Figure 2.4: TLM design flow: source [46]

• Finally, SystemC/TLM is considered the right modeling language from where High-Level Synthesis (HLS) should start. An example to substantiate this claim is the CtoS [12] tool sold by Cadence. Starting from a SystemC description, this tool outputs RTL code. Inspite of this, HLS is far from being as mature as logic synthesis and therefore requires more research.

## 2.4 Power modeling approaches and tools

In this section, we give a detail view about the most recent different approaches for power modeling at different abstraction level. The power consumption models can be distinguished into two main categories:

- Low-Level or hardware level models.

- High-Level models.

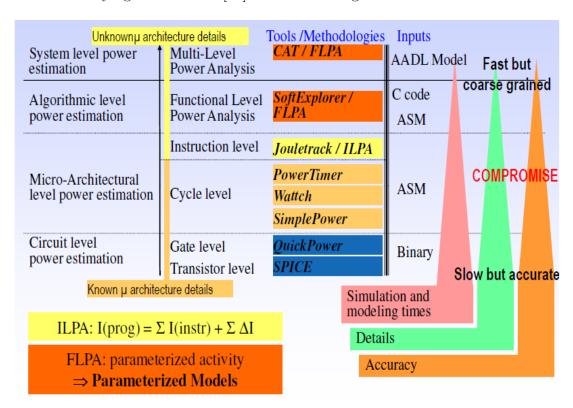

Low-level or hardware models calculate the power from detailed electrical descriptions: circuit level, gate level and RTL. Among the existing tools for low-levels we can mention, SPICE [88] at the transistor level, Diesel [96] at the gate level and Petrol [95] at the RTL level, which deal with fine-grained activities. The low-level tools require a very long simulation time for large circuits and this makes them inapplicable for complex MPSoC. However, these tools provide a good accuracy, but impractical to implement in the early design flow as they require the knowledge of the circuit details. High-level models deal with instructions and functional units of the programs and without any electrical knowledge of the underlying architecture [35] as shown in Fig. 2.5.

Figure 2.5: Power modeling methodologies and tools according the abstraction levels  $\frac{1}{2}$

#### 2.4.1 Low-level estimation techniques

The efficiency of the power simulator is influenced by both accuracy of the estimation and speed of the simulator. In this section, we will go through few frequently used power modeling techniques at lower levels. The low-level power consumption estimation techniques cover a wide range of abstractions level such as the:

- Circuit/Transistor level

- Logic gate level.

- RTL.

- Architectural level.

#### 2.4.1.1 Circuit-level