# System Profiling and Green Capabilities for Large Scale and Distributed Infrastructures

Ghislain Landry Tsafack Chetsa

#### ▶ To cite this version:

Ghislain Landry Tsafack Chetsa. System Profiling and Green Capabilities for Large Scale and Distributed Infrastructures. Other [cs.OH]. Ecole normale supérieure de lyon - ENS LYON, 2013. English. NNT: 2013ENSL0861. tel-00946583

### HAL Id: tel-00946583 https://theses.hal.science/tel-00946583v1

Submitted on 13 Feb 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### ÉCOLE NORMALE SUPÉRIEURE DE LYON

Laboratoire de l'Informatique du Parallélisme

#### THÈSE

en vue d'obtenir le grade de

## Docteur de l'Université de Lyon, délivré par École Normale Supérieure de Lyon

Spécialité : Informatique

au titre de l'École Doctorale Informatique et Mathématiques (ED 512)

Présentée et soutenue publiquement le 03 décembre 2013 par Ghislain Landry TSAFACK CHETSA

### System Profiling and Green Capabilities for Large Scale and Distributed Infrastructures

|                   |            |    |         | _       |

|-------------------|------------|----|---------|---------|

| <i>Directeurs</i> | de thèse : | Μ. | Laurent | LEFEVRE |

M. Jean-Marc PIERSON

Après avis de : M. Nouredine MELAB

M. Domenico TALIA

Devant la commission d'examen formée de :

| Μ.  | Nouredine | MELAB    | Rapporteur |

|-----|-----------|----------|------------|

| M.  | Domenico  | TALIA    | Rapporteur |

| M.  | Thomas    | LUDWIG   |            |

| M.  | Noel      | DE PALMA |            |

| M.  | Frédéric  | DESPREZ  |            |

| M.  | Laurent   | LEFÈVRE  | Directeur  |

| M.  | Jean-Marc | PIERSON  | Directeur  |

| 3 f | D         | CTOLD    |            |

Mme. Patricia STOLF

### Acknowledgments

First and foremost, I would like to express my deep gratitude to my supervisors, INRIA permanent researcher Dr. Laurent Lefévre, Pr. Jean-Marc Pierson, and Dr. Patricia Stolf, for their guidance and unmeasurable support throughout my candidature. Over the past three years, I had the privilege to work on simulating topics and cutting edge issues in computer science. I was given the opportunity to meet and collaborate with extraordinary people all around the world. None of this would have been possible without the determination of my supervisors.

I am immensely grateful to my parents including my mum's co-spouse for their unconditional love and endless support in whatever I chose to do, for always watching my back wherever I am, and for all the honesty and ethic lessons they have provided me with. I am particularly proud of my mum Téclaire, who has been and will always be a great mother to me. Thanks also to my brothers (Ervice, Francis, Darlin, Anderson, Rostand, Modeste, and Luther) and sisters (Annie, Bertine, Judithe, Leonie, Mariane, and Aurelie) for their unconditional love, support, and companionship.

I would also like to thank all past members of the RESO project team, members of the Avalon project team, members of the SEPIA project team at IRIT, and the management staff of the LIP laboratory. In particular, I thank Christian Pérez, Laetitia Lecot, Evelyne Blesle, Sylvie Boyer, Marie Bozo, Catherine Desplanches, and Damien Séon for their support and help; Olivier Glück who has led me into this amazing teaching experience; Jean-Patrick Gelas who trusted me in the first place and introduced me to Laurent with whom he co-supervised my Master 1 & 2 projects.

I am grateful to Pr. Nouredine Melab and Pr. Domenico Talia, who have accepted to review my thesis, for their valuable comments on a preliminary version of this thesis. My gratitude also goes to Pr. Thomas Ludwig, Pr. Noel De Palma, and INRIA research director Fredéric Desprez who have accepted to be part of my thesis jury.

A special thank you goes to Dr. Georges Da Costa, Mr. Olivier Mornard, and Dr. Marcos De Assuncao for their valuable time and the many useful discussions. The support they have provided me with throughout this process has been exceptional. I also thank all my friends and everybody who have contributed to this research in any form.

Many thanks to all those who have honoured me with their presence on the big day. My gratitude also goes to all those who couldn't make it. I am thinking of my mum who would have like to witness that moment.

Finally, I also express gratitude to the French Institute for Research in Computer Science and Control (INRIA) and the Hemera or Grid'5000 project without which this research would have not been possible.

#### Abstract

Nowadays, reducing the energy consumption of large scale and distributed infrastructures has truly become a challenge for both industry and academia. This is corroborated by the many efforts aiming to reduce the energy consumption of those systems. Initiatives for reducing the energy consumption of large scale and distributed infrastructures can without loss of generality be broken into hardware and software initiatives.

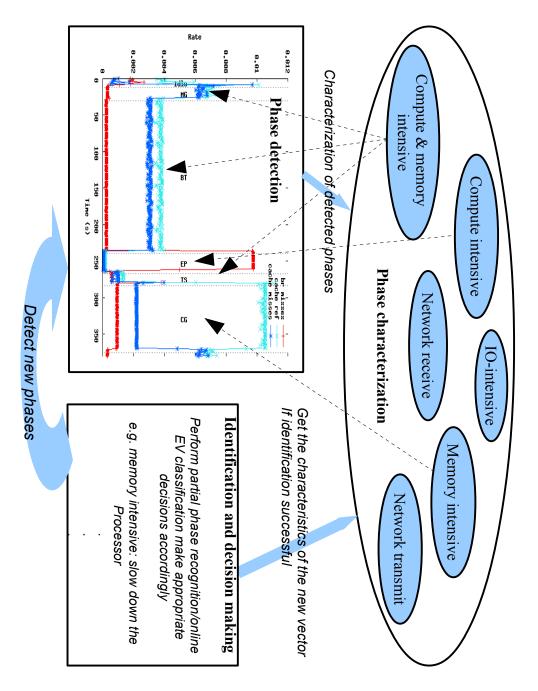

Unlike their hardware counterpart, software solutions to the energy reduction problem in large scale and distributed infrastructures hardly result in real deployments. At the one hand, this can be justified by the fact that they are application oriented. At the other hand, their failure can be attributed to their complex nature which often requires vast technical knowledge behind proposed solutions and/or thorough understanding of applications at hand. This restricts their use to a limited number of experts, because users usually lack adequate skills. In addition, although subsystems including the memory are becoming more and more power hungry, current software energy reduction techniques fail to take them into account. This thesis proposes a methodology for reducing the energy consumption of large scale and distributed infrastructures. Broken into three steps known as (i) phase identification, (ii) phase characterization, and (iii) phase identification and system reconfiguration; our methodology abstracts away from any individual applications as it focuses on the infrastructure, which it analyses the runtime behaviour and takes reconfiguration decisions accordingly.

The proposed methodology is implemented and evaluated in high performance computing (HPC) clusters of varied sizes through a Multi-Resource Energy Efficient Framework (MREEF). MREEF implements the proposed energy reduction methodology so as to leave users with the choice of implementing their own system reconfiguration decisions depending on their needs. Experimental results show that our methodology reduces the energy consumption of the overall infrastructure of up to 24% with less than 7% performance degradation. By taking into account all subsystems, our experiments demonstrate that the energy reduction problem in large scale and distributed infrastructures can benefit from more than "the traditional" processor frequency scaling. Experiments in clusters of varied sizes demonstrate that MREEF and therefore our methodology can easily be extended to a large number of energy aware clusters. The extension of MREEF to virtualized environments like cloud shows that the proposed methodology goes beyond HPC systems and can be used in many other computing environments.

#### Résumé

De nos jours, réduire la consommation énergétique des infrastructures de calcul à grande échelle est devenu un véritable challenge aussi bien dans le monde académique qu'industriel. Ceci est justifié par les nombreux efforts visant à réduire la consommation énergétique de ceux-ci. Ces efforts peuvent, sans nuire à la généralité, être divisés en deux groupes : les approches matérielles et les approches logicielles.

Contrairement aux approches matérielles, les approches logicielles connaissent très peu de succès à cause de leur complexité. En effet, elles se focalisent sur les applications et requièrent souvent une très bonne compréhension des solutions proposées et/ou de l'application considérée. Ce fait restreint leur utilisation à un nombre limité d'experts puisqu'en général les utilisateurs n'ont pas les compétences nécessaires à leur implémentation. Aussi, les solutions actuelles en plus de leurs difficultés de déploiement ne prennent en compte que le processeur alors que les composants tels que la mémoire, le stockage et le réseau sont eux aussi de gros consommateurs d'énergie.

Cette thèse propose une méthodologie de réduction de la consommation énergétique des infrastructures de calcul à grande échelle. Elaborée en trois étapes : (i) détection de phases, (ii) caractérisation de phases détectées et (iii) identification de phases et reconfiguration du système ; elle s'abstrait de toute application en se focalisant sur l'infrastructure dont elle analyse le comportement au cours de son fonctionnement afin de prendre des décisions améliorant l'efficacité énergétique.

La méthodologie proposée est implémentée et évaluée sur des grappes de calcul à haute performance de tailles variées par le biais de MREEF (Multi-Resource Energy Efficient Framework). MREEF implémente la méthodologie de réduction énergétique de manière à permettre aux utilisateurs d'implémenter leurs propres mécanismes de reconfiguration du système en fonction des besoins. Les résultats expérimentaux montrent que la méthodologie proposée réduit la consommation énergétique de 24% pour seulement une perte de performance de moins de 7%. Ils montrent aussi que pour réduire la consommation énergétique des systèmes, on peut s'appuyer sur les sous-systèmes tels que les sous-systèmes de stockage et de communication. Nos validations montrent que notre méthodologie s'étend facilement à un grand nombre grappes de calcul sensibles à l'énergie (energy aware). L'extension de MREEF dans les environnements virtualisés tel que le cloud montre que la méthodologie proposée peut être utilisée dans beaucoup d'autres environnements de calcul.

## Contents

| 1 | Inti | roduct   | ion                                                          | 1  |

|---|------|----------|--------------------------------------------------------------|----|

|   | 1.1  | Challe   | enges of High Performance Computing                          | 1  |

|   |      | 1.1.1    | Need of raw performance                                      | 1  |

|   |      | 1.1.2    | Today's HPC systems                                          | 2  |

|   |      | 1.1.3    | Problematic and objectives                                   | 4  |

|   | 1.2  | Contr    | ibutions                                                     | 5  |

|   | 1.3  | Struct   | ture of the Manuscript                                       | 6  |

| 2 | Ene  | m ergy/P | ower Aware High Performance Computing: State of the          |    |

|   | Art  |          |                                                              | 9  |

|   | 2.1  | Under    | standing HPC Systems' Power Consumption                      | 10 |

|   |      | 2.1.1    | Components' power models                                     | 10 |

|   |      | 2.1.2    | HPC applications' power: modelling and prediction approaches | 13 |

|   | 2.2  | Energ    | y Reduction in HPC Systems                                   | 15 |

|   |      | 2.2.1    | Energy efficient hardware design                             | 15 |

|   |      | 2.2.2    | Software solutions to the energy consumption issue in HPC .  | 17 |

|   | 2.3  |          | on Program Phase Detection for Energy Efficient HPC          | 19 |

|   | 2.4  | Concl    | usions and Discussion                                        | 20 |

|   |      | 2.4.1    | Discussion: need to address the energy consumption issue in  |    |

|   |      |          | HPC environments differently                                 | 20 |

|   |      | 2.4.2    | Conclusions                                                  | 21 |

| 3 | A I  | Blind I  | Methodology for Improving Computing Infrastructures'         |    |

|   | Ene  | ergy Po  | erformance                                                   | 23 |

| 4 | A F  |          | Detection Approach for HPC Systems' Analysis                 | 27 |

|   | 4.1  |          | luction                                                      | 27 |

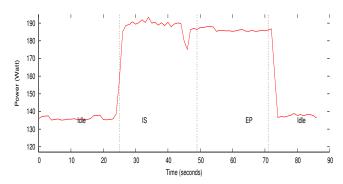

|   | 4.2  | Power    | -based Phase Detection                                       | 29 |

|   |      | 4.2.1    | Phase tracking or letter modelling                           | 29 |

|   |      | 4.2.2    | Example                                                      | 31 |

|   | 4.3  |          | ased System Phase Detection Mechanism                        | 31 |

|   |      | 4.3.1    | EV-based phase changes detection algorithm                   | 33 |

|   |      | 4.3.2    | Illustrative scenarios and analysis                          | 34 |

|   |      | 4.3.3    | Evaluation of the EV-based phase detection algorithm: false  |    |

|   |      |          | positives, sensitivity, and mean detection time              | 39 |

|   |      | 4.3.4    | Phase representation and selection of simulation points      | 40 |

|   | 4.4  |          | Study: The Advance Research Weather Research Forecasting     |    |

|   |      | · ·      | F-ARW) model                                                 | 42 |

|   |      | 4.4.1    | Phase analysis and detection results                         | 42 |

|   |      | 4.4.2    | Influence of the detection threshold                         | 45 |

vi Contents

|   | 4.5 | Conclusions                                                   | 45         |

|---|-----|---------------------------------------------------------------|------------|

| 5 | Sys | tem Phase Characterization                                    | 47         |

|   | 5.1 | Introduction                                                  | 47         |

|   | 5.2 | LLCRIR-based Workload Characterization                        | 48         |

|   |     |                                                               | 49         |

|   |     | 5.2.2 Impact of input and system parameters of LLCRIR-based   |            |

|   |     |                                                               | 51         |

|   | 5.3 |                                                               | 52         |

|   |     |                                                               | 52         |

|   |     | 5.3.2 System phase characterization using principal component |            |

|   |     |                                                               | 53         |

|   | 5.4 |                                                               | 57         |

|   | 5.5 | J ,                                                           | 58         |

|   |     |                                                               |            |

| 6 | Pha | 8                                                             | 61         |

|   | 6.1 |                                                               | 61         |

|   | 6.2 |                                                               | 62         |

|   |     | 6.2.1 Partial phase recognition                               | 62         |

|   |     | 6.2.2 Execution vectors' classification                       | 64         |

|   |     | 6.2.3 Off-line phase identification                           | 64         |

|   | 6.3 | Power Saving Schemes                                          | 65         |

|   |     | 6.3.1 Platform selection via cross platform energy prediction | 67         |

|   |     | 6.3.2 Memory size scaling                                     | 69         |

|   |     | 6.3.3 CPU cores switch on/off                                 | 71         |

|   | 6.4 | Conclusions                                                   | 74         |

| 7 | Fra | mework-based Implementation and Experimentation: Analysis     |            |

|   | and | Discussion                                                    | <b>7</b> 5 |

|   | 7.1 | Introduction                                                  | 75         |

|   | 7.2 | Implementation                                                | 76         |

|   | 7.3 | Experimental Setup and Methodology                            | 78         |

|   |     | 7.3.1 Evaluation platform description                         | 78         |

|   |     | 7.3.2 Experimental protocol and tools                         | 81         |

|   | 7.4 |                                                               | 81         |

|   |     | 7.4.1 MREEF: partial phase recognition related results        | 81         |

|   |     | 7.4.2 Execution vectors' classification related results       | 88         |

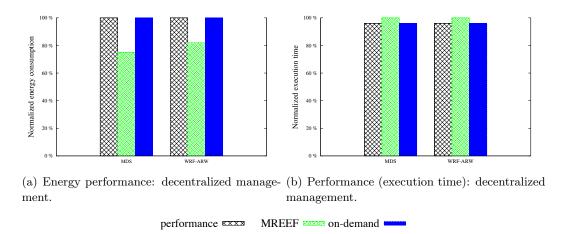

|   | 7.5 |                                                               | 92         |

|   |     | 7.5.1 Context description and results                         | 92         |

|   | 7.6 | Conclusions                                                   | 94         |

| 8 | Cor | aclusions and Perspectives                                    | 97         |

|   | 8.1 |                                                               | 97         |

|   | 8.2 |                                                               | 99         |

| Contents     | vii |

|--------------|-----|

| Publications | 101 |

| Bibliography | 103 |

# List of Figures

| 1.1 | An overview of high performance computing (HPC)                                                             | 2  |

|-----|-------------------------------------------------------------------------------------------------------------|----|

| 3.1 | A summary of the methodology on a system which successively runs five different workloads                   | 24 |

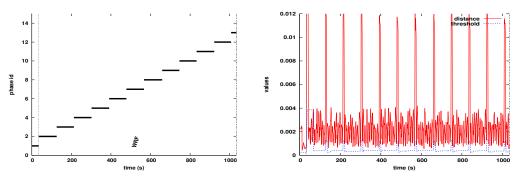

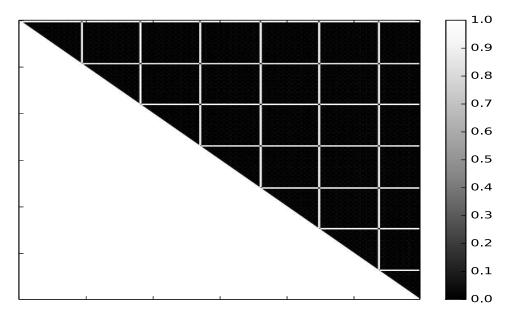

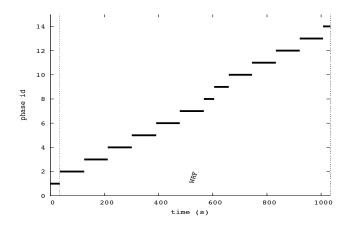

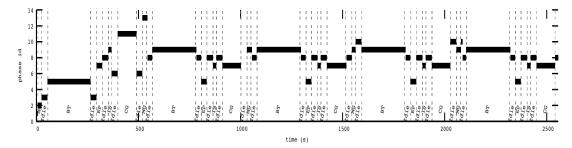

| 4.1 | Graphical representation of the output of Algorithm 1 along with PMCs access pattern                        | 32 |

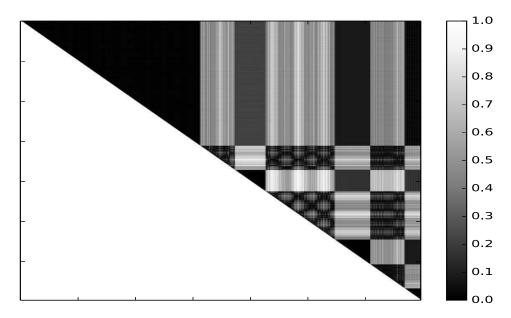

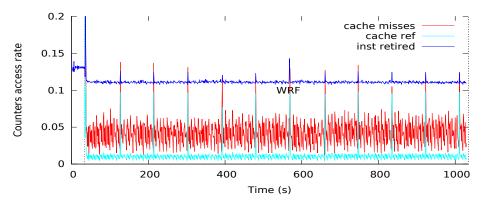

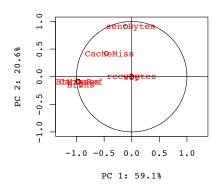

| 4.2 | Graphical representation on a greyscale of the matrix of distance (Manhattan) between execution vectors     | 34 |

| 4.3 | Phase changes detection using EVPDA when running bench_1                                                    | 37 |

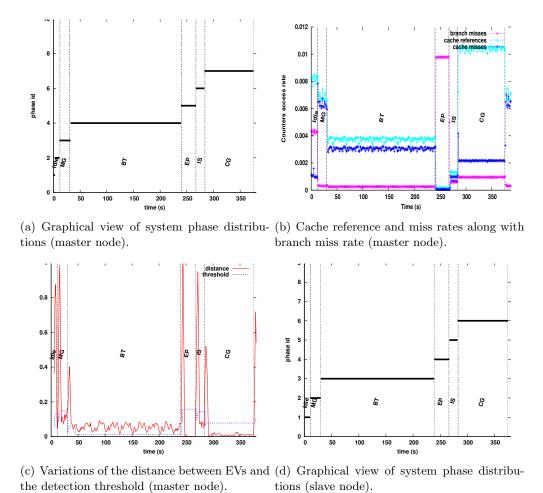

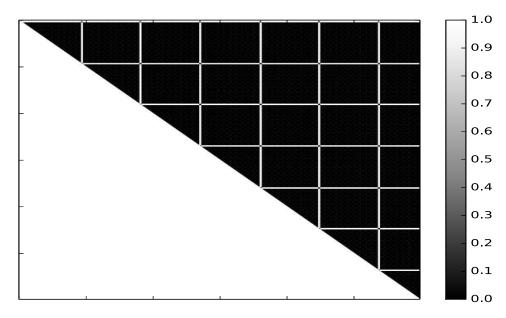

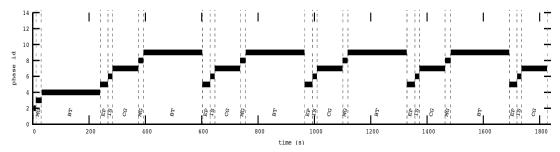

| 4.4 | Phase changes detection using EVPDA when running bench_2                                                    | 38 |

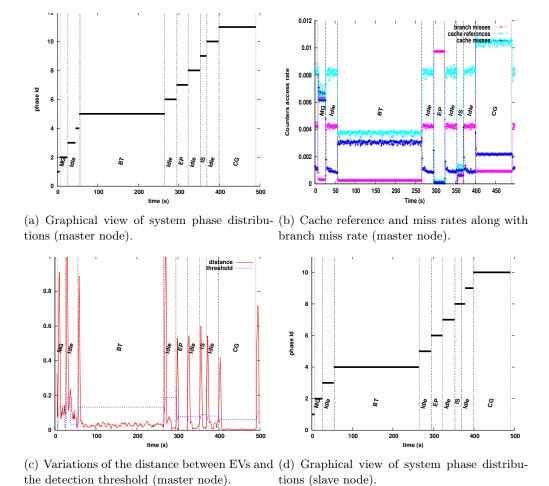

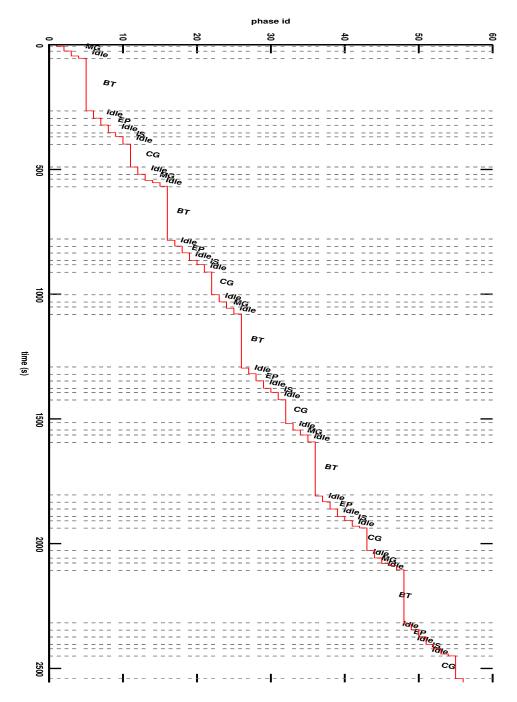

| 4.5 | Graphical view of phase detected when successively running bench_2 five times                               | 41 |

| 4.6 | Phase changes detection using the EVPDA (Algorithm 2) when running WRF-ARW                                  | 43 |

| 4.7 | Matrix of distance between EVs for WRF-ARW (the matrix corresponds to half of the execution of the program) | 44 |

| 4.8 | Phase changes detection using the EVPDA when running WRF-ARW: 10% detection threshold                       | 44 |

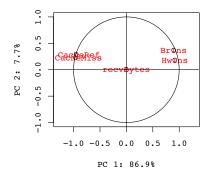

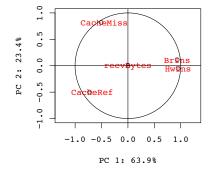

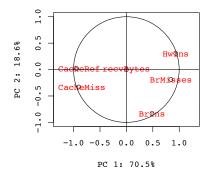

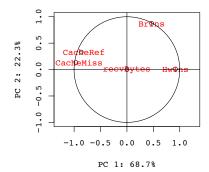

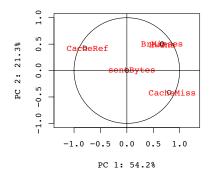

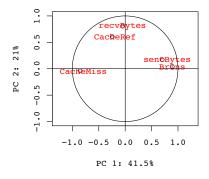

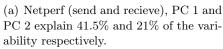

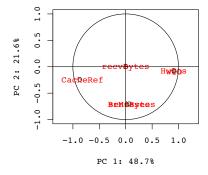

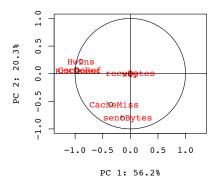

| 5.1 | Principal component analysis (PCA) of Benchmarks from NPB benchmark suite                                   | 55 |

| 5.2 | Principal component analysis (PCA) of CG benchmark Benchmarks from NPB benchmark suite                      | 56 |

| 5.3 | Principal component analysis (PCA) of network 5.3(a) and IO intensive 5.3(b) workloads                      | 56 |

| 5.4 | Principal component analysis (PCA) applied to data collected when the system was idle                       | 57 |

| 6.1 | Matrix of distance between EVs for WRF-ARW (the matrix corresponds to half of the execution of the program) | 66 |

| 6.2 | Phase identification illustrated with five successive run of each benchmark.                                | 66 |

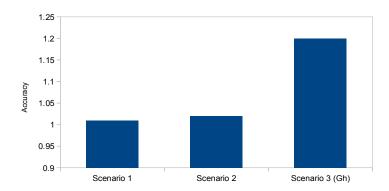

| 6.3 | Per scenario energy prediction accuracy                                                                     | 70 |

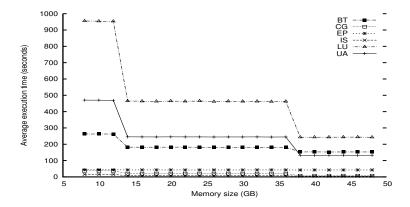

| 6.4 | Average execution time of NPB-3.3 benchmarks with respect to the memory size.                               | 70 |

| 6.5 | Difference in power usage between the optimal memory size and the total memory.                             | 71 |

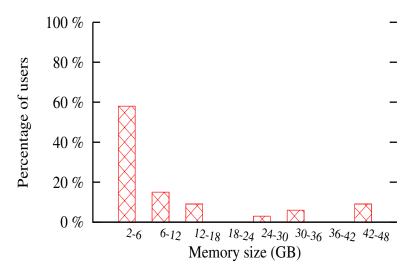

| 6.6 | Memory requirement per node on the Reims site of Grid5000 for users experiments.                            | 72 |

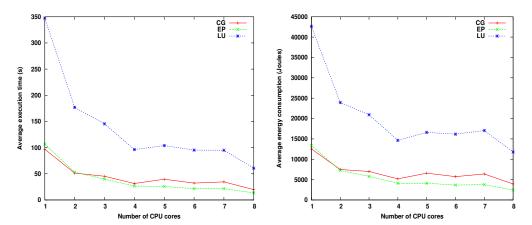

| 6.7  | Impact of CPU cores switching of workloads' execution time and en-  | -  |

|------|---------------------------------------------------------------------|----|

|      | ergy consumption.                                                   | 7: |

| 6.8  | Comparison of baseline configuration (only 1 active CPU core) to    |    |

|      | configurations wherein the number of active CPU cores ranges from   |    |

|      | 2 to 8                                                              | 7: |

| 7.1  | Overview of the way in which components of the roadmap are ar-      |    |

|      | ranged in MREEF                                                     | 7  |

| 7.2  | MREEF architecture overview                                         | 78 |

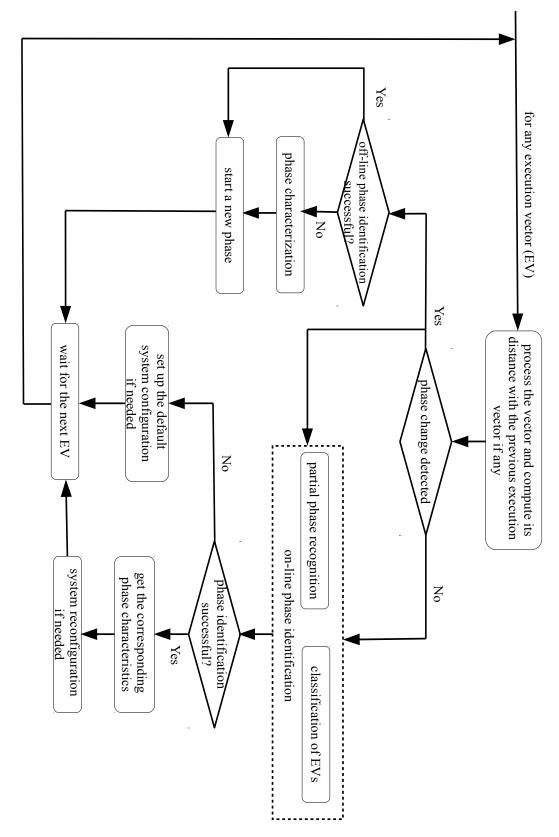

| 7.3  | The Grid'5000 infrastructure                                        | 79 |

| 7.4  | Phase tracking and partial recognition guided processor adaptation  |    |

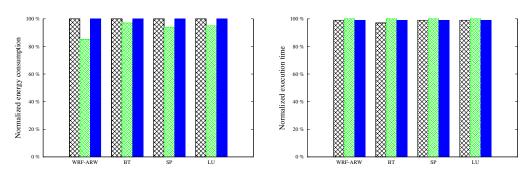

|      | results: centralized coordinator                                    | 8  |

| 7.5  | Phase tracking and partial recognition guided processor adaptation  |    |

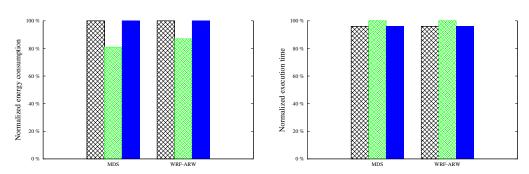

|      | results for the decentralized version of MREEF                      | 84 |

| 7.6  | Phase tracking and partial recognition guided processor, disk, and  |    |

|      | network adaptation results for a decentralized version of MREEF     | 8  |

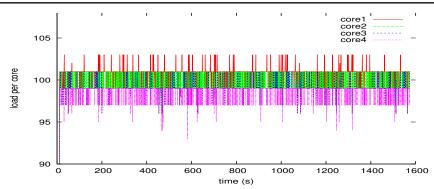

| 7.7  | Load traces for one a node participating in the computation of WRF- |    |

|      | ARW under the on-demand configuration                               | 8  |

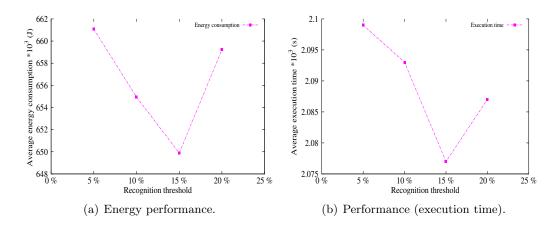

| 7.8  | Influence of the partial phase recognition threshold on WRF-ARW's   |    |

|      | performance (execution time and energy consumption)                 | 8  |

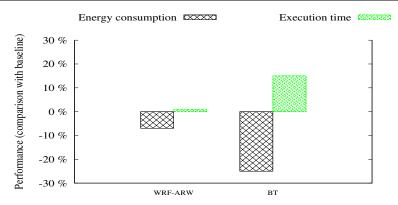

| 7.9  | Comparison of our management policy in terms of programs' energy    |    |

|      | consumption and execution time with baseline on-demand system       |    |

|      | configuration                                                       | 8  |

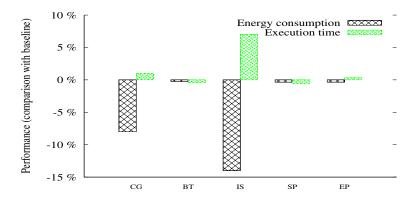

| 7.10 | Average energy variations and execution time increase with respect  |    |

|      | to the baseline execution.                                          | 9  |

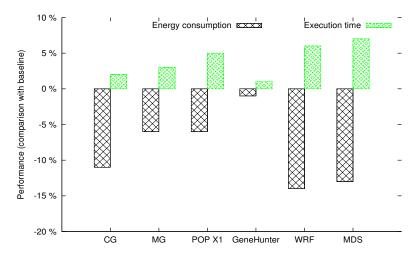

| 7.11 | Comparison of MREEF (execution time and energy consumption)         | _  |

|      | with the baseline on-demand configuration                           | 9  |

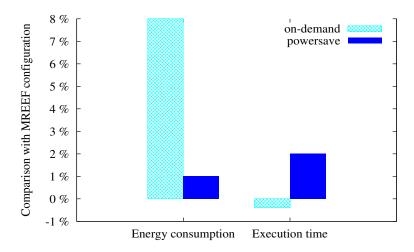

| 7 12 | MREEF versus powersave and on-demand in a cloud environment.        | 9  |

## List of Tables

| 2.1 | Performance events selected to estimate CPU and memory power consumption for Intel PXA255 processor.                                  | 15 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | List of sensors describing an execution vector (we will use more human friendly names to refer to those sensors)                      | 33 |

| 4.2 | Performance summary of our phase detection algorithm considering the two synthetic benchmarks                                         | 40 |

| 4.3 | Variation of the number of phases detected with respect to the detection threshold                                                    | 45 |

| 5.1 | HPC workloads categories and their description                                                                                        | 49 |

| 5.2 | Per program average LLC references per instruction ratio                                                                              | 50 |

| 5.3 | Order of magnitude of LLC references per instruction ratio and asso-                                                                  |    |

|     | ciated labels                                                                                                                         | 50 |

| 5.4 | Per program average LLCRIR                                                                                                            | 51 |

| 5.5 | Rules for assigning labels to phases given sensors selected from PCA.                                                                 | 53 |

| 5.6 | Sample characterization results with varied workloads. Program names are written in block letters                                     | 59 |

| 6.1 | Phase labels and associated power saving schemes                                                                                      | 63 |

| 6.2 | Optimal RAM size per workload                                                                                                         | 71 |

| 7.1 | Relative standard deviation (rsd.) of the energy consumption and execution time of each workload under our two system configurations. | 92 |

### Introduction

#### Contents

| 1.1 Challenges of High Performance Computing | 1 |  |  |  |

|----------------------------------------------|---|--|--|--|

| 1.1.1 Need of raw performance                | 1 |  |  |  |

| 1.1.2 Today's HPC systems                    | 2 |  |  |  |

| 1.1.3 Problematic and objectives             | 4 |  |  |  |

| 1.2 Contributions                            |   |  |  |  |

| 1.3 Structure of the Manuscript              |   |  |  |  |

### 1.1 Challenges of High Performance Computing

#### 1.1.1 Need of raw performance

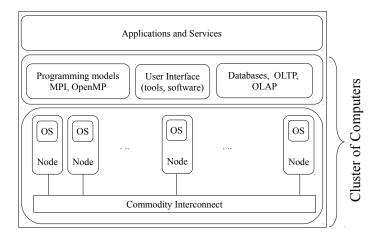

There is no single definition for High Performance Computing (HPC) or High Performance Cluster. Figure 1.1 offers an outline of HPC nowadays. At the one hand, from a user perspective HPC can be thought of as a set of services that enable new levels of innovation and insights for organisations that seek excellence in fields including Research and Development (R&D), science, engineering, among others. At the other hand, from a technological perspective, HPC is viewed as the use of clusters of servers and supercomputers, along with associated software, tools, interconnects, storage, and services involved in running an HPC environment or system<sup>1</sup>. Servers in an HPC environment are often called nodes.

The increasing reliance on computing by scientific endeavours, industry and government agencies (particularly the military) has made HPC mainstream in several areas including, but not limited to, climate research, disease control, homeland security, drug discovery. Organisations often rely upon HPC for enhancing their product line. For example, a bank uses HPC to analyse high volumes of digital transactions, maximising investments and protecting its client from frauds. Likewise, to bring superior products to market, a manufacturer may consider using HPC to built prototypes of its products. Similarly, organisations seeking for the creation of large, high fidelity models that yield accurate and detailed insight into the performance of their designs often rely upon HPC for performing extensive simulations. Along the same lines, architects use HPC to evaluate buildings/structures by simulating their

<sup>&</sup>lt;sup>1</sup>Intersect360: http://www.intersect360.com

Figure 1.1: An overview of high performance computing (HPC).

prototypes in realistic scenarios. Simulating structures in multiple environments helps improve structural design to minimise damage and save lives under disasters. As the demand for processing grows, HPC will likely gain interest in businesses of all sizes, particularly for transaction processing and data warehouse.

#### 1.1.2 Today's HPC systems

HPC inevitably owes its success to the massive computational power it is capable of achieving for solving complex problems. At the design level, to ensure that applications that run on HPC systems are reaching their maximum performance, system designers generally place a great emphasis on a handful of components. These include the processor architecture, memory subsystem, storage subsystem, communication subsystem, and the management framework. The emphasis on these components is justified by the fact that performance of the majority of HPC applications (use interchangeably with workload) relies upon them. For example, as the storage subsystem is an important factor for IO intensive applications, selecting a suitable storage subsystem for the application task can help enhance IO performance. A similar analysis can be waged by dimensioning each subsystem. In practice, although this offers reasonable performance over a wide range of applications, it often results in power dissipation/inefficiency for some workloads or specific phases of a workload. Unfortunately, addressing this at the system design stage is near to impossible; unless the designer knows all user applications that the future platform will accommodate.

Still at the design level, computer chips seem to have hit a wall, meaning that they can hardly be made any faster with current technology. Consequently, supercomputers designers just have to add more and more chips to increase computing power. However, this approach has a significant impact on energy usage. In light of what precedes, it is not surprising that, different from a decade ago where su-

percomputers were only ranked by their peak performance<sup>2</sup>, nowadays, they are also assessed based on their energy efficiency<sup>3</sup>. The ranking of supercomputers by their energy efficiency places a great emphasis on their energy consumption through the number of PFlops (petaflops) they can achieve per Watt. For example, the Tianhe-2 machine, which sits on top of the performance list (Top500 list), delivers a computing power of over 33PFlops and shows an energy efficiency of 1.9GFlops/W; while CINECA which leads the green list (Green500 list) with an energy efficiency of 3.9GFlops/W delivers a computing power of less than 2PFlops.

Tremendous efforts are being undertaken by HPC operators from multiple levels to make supercomputers greener. This is evidenced by the Green500 list; its latest issue shows that the greenest supercomputers are getting greener. Their sudden improvement in energy efficiency can be attributed to the rise of graphic processors in massive cluster servers and the acquisition of low power memories. Similar efforts are being carried out in regard to the all HPC subsystems from the processor to the memory to the storage and communications subsystems. Unfortunately, at the current speed significant efforts still need to be done if today's supercomputers want to meet the 20MW constraint for exascale.

There is a common believe that a considerable share of energy consumed by HPC systems during their operations could be potentially saved if user applications were programmed differently. Put it in another way, throughout their life cycle, user applications exhibit behaviours whose understanding allows implementing power reduction schemes which can significantly reduce the amount of energy they consume at runtime. This has been proven right by different work [Kimura et al. 2010, Kappiah et al. 2005, Rountree et al. 2009, Lim et al. 2006, Choi et al. 2006, Ge et al. 2005].

Consequently, making HPC applications more energy friendly requires designing or rewriting applications with energy constraints in mind. These alternatives may not always be feasible. Although there is not any evidence, rewriting some HPC applications is so costly that most people find paying the electrical bill worth, whereas application developers usually do not pay much attention to how much energy their applications will consume. There are several reasons to this; besides the fact that they are already struggling to get their code work, current power saving schemes are platform specific. For example, let us consider the Dynamic Voltage and Frequency Scaling (DVFS) technology which allows scaling the processor's frequency according to the workload in some cases. Integrating DVFS into a program source code assumes that the developers know all the potential platforms that will run their applications which is not realistic. Although DVFS support is available in nearly all platforms today, at some point one need to select the appropriate frequency at which a specific must run. This can be very difficult to achieve at the coding stage since CPU frequency ranges are processor specific.

One could rely upon existing approaches such as those in the above references.

<sup>&</sup>lt;sup>2</sup>Top500 List – June 2013: http://www.top500.org

<sup>&</sup>lt;sup>3</sup>Green500 List – June 2013: http://www.green500.org

Unfortunately, they require expert knowledge and/or vast technical details behind the energy saving scheme proposed. As a result, it can be extremely difficult or near to impossible to implement in once HPC environment.

The energy consumption problem in HPC has been widely investigated over the past years. However, despite the fact that nearly all HPC subsystems are provided with energy saving capabilities, current efforts for reducing the energy consumption of HPC systems from a software perspective are directed toward the processor to the best of our knowledge. In other words, current efforts ignore all subcomponents save the processor.

With the current trend, to efficiently address the power consumption issue in HPC, things need to be approached differently than in the past. The processor has traditionally dominated supercomputers energy consumption, but the tendency is being reversed. In 2010, HPC subsystems including the memory, storage, and communications subsystems accounted for up to 55% of the total energy consumption of a typical supercomputer [Liu & Zhu 2010]. Thus, a fine-grained management of these subsystems can result in significant energy savings.

#### 1.1.3 Problematic and objectives

High performance computing systems keep growing all around the globe increasing the power demand for operating them. Which in turn contributes to the carbon dioxide  $(CO_2)$  emission. In 2009, the International Telecommunication Union (ITU) has estimated the contribution of the Information and Communication Technology sector (excluding the broadcasting sector) to climate change at between 2% and 2.5% of total global carbon emissions [ITU 2009]. This thesis investigates means for reducing the energy consumption of large-scale and distributed infrastructures without a priori information about applications or services that share the infrastructure, while taking into consideration any energy reduction opportunities available to the most manageable components of the infrastructure. We concentrate on reducing the energy consumption without a priori knowledge of application and services while taking into consideration any energy reduction opportunities for several reasons including the following:

- Current, energy saving schemes fail to find their way into real HPC deployments because they often require thorough understanding of proposed scheme from a third party that would like to implement them on once system. In addition, they often rely on the assumption that the environment is a single task environment.

- Today's HPC applications are not optimized for saving energy; however, they are too complex to be rewritten or modified. This makes code instrumentation, which is also error prone, nearly impractical and significantly limits the scope of current energy saving schemes since they are application oriented.

- Although the current trend consists of adding more and more components to servers for increasing the computational power, energy saving schemes for

HPC have traditionally focused on the processor. As a misfortune, the power demand of servers increases as more components are added. This is illustrated by the increasing size of the memory subsystem. The same goes with storage and communication subsystems with the rise of Big Data. As mentioned earlier, these components account for more than half of the energy consumption of a typical HPC system. Moreover, in current mid-market and high-end servers, the memory subsystem already consumes more energy than the processor.

Our objectives in this thesis are to:

- Propose an energy reduction policy that concentrates on reducing the energy consumption of high performance computing systems instead of that of individual applications.

- Propose ways to address the energy consumption issue in HPC by taking advantage of all HPC subsystems. A basic requirement to this is developing power saving schemes that concentrate on reducing their energy.

- Propose an energy reduction policy that offers ways to benefit from variabilities among HPC workloads or within a specific workload while abstracting away from any individual applications.

- Propose a "user friendly" energy reduction policy for HPC systems. By user friendly, we mean an energy reduction policy that: (i) does not require any specific knowledge from a third party; (ii) takes into account the fact that real life environments are often shared by multiple applications; (iii) allows users to design and implement their own energy reduction strategies without extensive efforts.

- Provide a software framework for reducing the energy consumption of HPC systems that implements all features required to fulfil previously mentioned objectives.

#### 1.2 Contributions

In this thesis, we are more interested in proposing a solution to the energy consumption problem in large-scale and distributed infrastructure. We introduce an automated, and scalable approach for reducing the energy consumption of HPC systems without a priori knowledge of workloads being executed. The approach takes advantage of HPC's workloads variability along with multi-configuration or reconfigurable hardware to reduce the energy consumption of the overall computing infrastructure. The main contributions of this thesis are as follows:

• We propose a methodology for reducing the energy consumption of HPC systems, it is original in the sense that it does not require any knowledge from users. Moreover, it takes into account all HPC subsystems –

from the processor to the memory to the storage and communication subsystems – and allows users to implement their own power saving schemes [Tsafack et al. 2012a, Tsafack et al. 2012a, Tsafack et al. 2013a].

- We propose on-line and off-line phase changes detection techniques [Tsafack et al. 2013b, Tsafack et al. 2012b]. Although allowing the detection of execution phases in specific program, our phase detection techniques innovate in the sense that they concentrate on detecting phases of execution of the system. System phase detection is similar to program phase detection, but offers the advantage that it abstract away from any individual program. As proposed techniques do not require any specific information about applications being executed, users lacking technical skills or expertise can use them for system analysis.

- Multiple workload characterisation schemes are proposed and evaluated in this thesis [Tsafack et al. 2013c]. Workload characterisation schemes serve the purpose of guiding system management decisions. Their particularity lies on the fact that they allow fast and accurate on-line characterisation of system phases as well as workloads.

- We propose and evaluate simple, but effective off-line and on-line techniques for identifying recurring phases in the runtime behaviour of a system [Tsafack et al. 2013c, Tsafack et al. 2013b]. Recurring phase identification basically enable reuse of reconfiguration information. To support system reconfiguration, we investigate the relevance of non conventional (not commonly used) power saving schemes including: memory size scaling, energy consumption prediction for platform selection, and core switch off/on.

- We present and demonstrate the effectiveness of a Multi-Resource Energy Efficient Framework (MREEF), an implementation of our methodology for reducing the energy consumption of high performance computing systems. MREEF is evaluated both in HPC and cloud environments. MREEF is energy oriented, so it emphasises on the use of green capabilities that we refer to as power saving schemes for system reconfiguration.

### 1.3 Structure of the Manuscript

The remaining of the manuscript is organised as follows: Chapter 2 reviews the state of the art on power/energy aware HPC. Our methodology for reducing the energy consumption of HPC systems is summarised in Chapter 3. Two phase detection methodologies that we refer to as "power-based phase detection" and "EV-based phase detection" methodologies are presented and evaluated in Chapter 4. Chapter 5 discusses several workloads characterisation schemes for on-line workload characterization. Chapter 6 discusses about system phase identification and power saving schemes. Chapter 7 evaluates our energy reduction methodology in HPC and cloud

environments through MREEF. Finally, Chapter 8 concludes our work in this thesis and presents future directions.

# Energy/Power Aware High Performance Computing: State of the Art

#### Contents

| 2.1 | Und   | erstanding HPC Systems' Power Consumption                                                | 10        |

|-----|-------|------------------------------------------------------------------------------------------|-----------|

|     | 2.1.1 | Components' power models                                                                 | 10        |

|     | 2.1.2 | HPC applications' power: modelling and prediction approaches                             | 13        |

| 2.2 | Ener  | egy Reduction in HPC Systems                                                             | <b>15</b> |

|     | 2.2.1 | Energy efficient hardware design                                                         | 15        |

|     | 2.2.2 | Software solutions to the energy consumption issue in HPC $$ .                           | 17        |

| 2.3 | Focu  | s on Program Phase Detection for Energy Efficient HPC                                    | 19        |

| 2.4 | Cone  | clusions and Discussion                                                                  | <b>20</b> |

|     | 2.4.1 | Discussion: need to address the energy consumption issue in HPC environments differently | 20        |

|     | 2.4.2 | Conclusions                                                                              | 21        |

Over the past few years, reducing the energy consumption of High Performance Computing (HPC) systems, or making them energy efficient, has become of one of the biggest Information Telecommunication Technology (ITC) challenges. As a result, several research activities focusing on large-scale HPC have been initiated, such as understanding and/or modeling the energy consumption of HPC systems and applications to design efficient hardware and implement effective energy efficiency practices. This chapter reviews the state of the art on power/energy aware HPC. Section 2.1 discusses methodologies for modeling and predicting the energy consumption of HPC systems and applications. Section 2.2 surveys energy reduction techniques specific to HPC environments. Section 2.3 provides a comprehensive overview of phase detection techniques, whereas Section 2.4.1 discusses the need for having more sophisticated power saving schemes. Finally, Section 2.4.2 concludes the chapter.

### 2.1 Understanding HPC Systems' Power Consumption

Improving the energy efficiency of HPC can be viewed as a two-step process, where the first step may inevitably involve answering several questions, such as:

- How much energy does the system consume?

- What is the energy consumed by each system component?

- How can one measure the energy consumption of the overall system and its components?

- What is the ratio between active and static power consumption?

Answers to these questions can lead to valuable insights into the energy consumption of individual system components. This information can be a prerequisite for the second step of improving the energy efficiency of HPC, which consists of designing and evaluating energy aware architectures and algorithms (as discussed in Section 2.2).

From a technological point of view, an HPC system can be viewed as a combination of servers, clusters, supercomputers, and required software, tools, components, storage, and services, working in tandem to fulfil the intensive processing and storage requirements of scientific, engineering, or analytical applications<sup>1</sup>. Consequently, understanding how much energy an HPC system consumes boils down both to evaluating the energy consumption of massive numbers of servers and identifying how applications perform. In the scope of this thesis, an HPC system is a set of servers and application tasks they perform are referred to as HPC applications.

#### 2.1.1 Components' power models

Wattmeters, often used to measure the energy consumption of servers, can be completely external devices inserted between the wall socket and the server plug, or be integrated into Power Distribution Units (PDU). Power modelling is a technique that gained popularity as power dissipation of the most power consuming components (*i.e.* processor and memory subsystems) within a server can be accurately estimated by simple power models. Static power models rely on the relationship between the supplied voltage and the electrical current traversing a component. They are used to describe both the static power or idle power consumption – the power consumed when there is no circuit activity – and the dynamic power of some server components. The following describes power models for processor and memory subsystems.

<sup>&</sup>lt;sup>1</sup>http://www.intersect360.com

#### 2.1.1.1 Processor

The power consumption of the processor can be broken down into static and dynamic power as described next.

#### (a) Static power consumption

Static consumption refers to the amount of power used due to leakage current in the absence of any switching activity. Direct Current (DC) power dissipation also known as static power can be estimated by the worse-case equivalent equation [Maede & Diffenderfer 2003]:

$$P_{static} = IV (2.1)$$

where V is the supply voltage and I the direct current traversing the processor. Most modern processors have multiple cores, which means that processors consist of basically an integrated circuit to which more than one processor have been attached (in this case, a single processor is referred to as a CPU core or simply core). Consequently, the static power consumption of a multi-core processor can be expressed as the arithmetic sum of the static power of its cores; hence, Equation 2.1 can be rewritten as:

$$P_{static} = \sum_{k=1}^{n} I_k V_k = \sum_{k=1}^{n} P_k$$

(2.2)

where k is the number of cores, and  $V_k$  and  $I_k$  are respectively the supplied voltage and the DC current traversing the processor core k.

The power consumption of a core depends on its number of transistors; so in using Equation 2.1, the power consumption of the  $l^{th}$  transistor of the CPU core k can be estimated by Equation 2.3,

$$P_{lk} = I_{lk}V_{lk} \tag{2.3}$$

where  $I_{lk}$  and  $V_{lk}$  are the leakage current and power voltage supplied to the  $l^{th}$  transistor of the CPU core k. Substituting Equation 2.3 into Equation 2.2 yields Equation 2.4.

$$P_{static} = \sum_{k=1}^{n} \sum_{l=1}^{m} I_{lk} V_{lk}$$

(2.4)

#### (b) Dynamic power consumption

Dynamic power, the only mode of power dissipation in CMOS circuitry, represents a considerable share of the total power consumed by CMOS based processors. It is described by Equation 2.5 where C is the capacitance of switching nodes, V is the supply voltage, and f is the effective operating frequency (frequency times activity factor) [Weste & Eshraghian 1985].

$$P_{dum} = CV^2 f (2.5)$$

As for the static power consumption, the dynamic power consumption of an N core processor is described by Equation 2.6 where N is the number of CPU-cores; the remaining parameters are the same as in Equation 2.5.

$$P_{dyn} = \sum_{k=1}^{N} CV^2 f_k \tag{2.6}$$

However, Basmadjian et al. [Basmadjian & De Meer 2012] show that the power consumption of an n-core processor (n > 1) is not the exact arithmetic sum of the power consumption of all its n CPU cores as suggested by Equation 2.6. Consequently, to model the power consumption of a multi-core processor, they decompose it into three component levels, which they refer to as (i) chip, (ii) die, and (iii) core levels respectively, and model the power consumption of each. Their findings also reveals that Equation 2.6 overestimates the processor's power consumption quite often. They handle this by proposing a power consumption model that takes into account both resource-sharing and energy-saving mechanisms.

#### 2.1.1.2 Memory

The power consumption of memory can also be broken down to total static power and total dynamic power.

#### (a) Static power consumption

The static power consumption of the memory is described by Equation 2.1. Back in 1919 it was shown that there is a linear relationship between the supplied voltage V and the DC current I when a device operates between 0 volt and 2 volts [Bijl 1919]. Since standard next-generation Dual Data Rate 3 (DDR3) memory technology and Dual Data Rate 2 (DDR2) technology operate within the above voltage range, the current traversing a memory is proportional to the supplied voltage as shown by Equation 2.7 where the constant c equals 0.00043 and 0.00013 for DDR3 and DDR2 respectively.

$$I = cV (2.7)$$

The static power of a memory module of size s operating at frequency f can be described by Equation 2.8.

$$P(f,s) = cV^2 (2.8)$$

To reflect the influence of the size and frequency of the memory module the static power consumption of a memory module can also be described by Equation 2.9

$$P = cfsV^2 (2.9)$$

The memory or RAM of a typical server often comprises several memory modules; the static power of a memory with N modules is straightforward to determine. Equation 2.10 where  $f_k$ ,  $s_k$ , and  $V_k$  are respectively the operating frequency, the

size, and the supply voltage of the  $k^{th}$  memory module, describes the static power of RAM composed of N memory modules.

$$P_{static} = \sum_{k=1}^{N} c f_k s_k V_k^2 \tag{2.10}$$

#### (b) Dynamic power consumption

The dynamic power of the memory subsystem mainly results from access (there is only 1 active operating rank per channel regardless of the number of modules or module ranks in the system<sup>2</sup>). The main memory is asynchronous in operation (modern servers requiring large amounts of memory use Dynamic Read Access Memory for main memory); thus, its power (actually the DRAM array power) is not dependent on memory frequency only, but on access count. As the DRAM array draws a constant amount of power regardless of the type of operation issued (write, read, precharge) the dynamic power of the memory can be described by Equation 2.11 where  $\gamma \in [0,1]$  is the probability that a memory access is performed (i.e., either the read, write or precharge command is active).  $\beta$  equals 7W, 17W, and 10W for unbuffered DDR2, fully buffered DDR2, and unbuffered DDR3 memory modules respectively.

$\gamma$  reflects the utilisation of the memory and is expressed as the ratio of the used memory to the total memory.

$$P'_{dum} = \gamma \beta \tag{2.11}$$

# 2.1.2 HPC applications' power: modelling and prediction approaches

Although modelling the power usage of individual applications has been widely investigated in mobile computing environments, it has not received extensive attention in HPC systems. This can be extremely difficult; especially, knowing that HPC applications are likely to spread over multiple nodes. However, it creates opportunities for energy based scheduling and power optimisation techniques [Bhattacharjee & Martonosi 2009, Merkel & Bellosa 2006, Singh et al. 2009]. Moreover, hardware for direct power measurement is largely nonexistent. In this section, we review power modelling and prediction techniques.

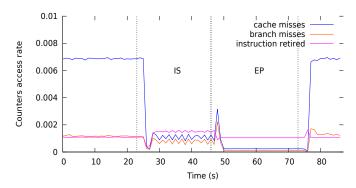

Power models have in common the fact that they monitor system components (in particular the processor and the memory) during the program's execution via hardware performance/monitoring counters (PCM) and correlate them with the power consumed by the system when running the program to derive its power model. Embedded hardware events counters of modern microprocessors, or simple hardware performance/monitoring counters are on-chip integrated facilities for counting events, so reading them can be done without any additional overhead.

<sup>&</sup>lt;sup>2</sup>http://www.rampedia.com

Analytic processor power model based on performance counters are presented in [Isci & Martonosi 2003b, Joseph & Martonosi 2001]. The proposed models are highly accurate but only model the power consumption of the processor. Authors of [Kadayif et al. 2001] propose a model, which they claim to be 2.4\% as compared to circuit level simulation, for estimating the energy consumption of the UltraSPARC memory hierarchy [SUN 1995]. They estimate the UltraSPARC CPU memory energy consumption considering PMCs providing the following information: Data cache read hits, Data cache read references, Data cache write hits, Data cache write references, Instructions cache references, Extended cache misses with writebacks. Energy consumption of the high-performance processor AMD Phenom is estimated in order to guide power aware policies in [Singh et al. 2009]. Authors use a set of micro-benchmarks that stress specific components of the processors architecture being modelled. They next categorise AMD Phenom PMCs into four buckets - FP Units, Memory, Stalls, and Instruction Retired - and consider performance events which express best their power consumption. These performance counters include L2 cache miss: all, Retired upps, Retired mmx and ft instruction: all, and Dispatch stalls. These models often require knowledge of hardware component implementation.

The assumption of a linear relationship between the processor's power consumption and several hardware monitoring counters (instruction retired and translation look-aside buffer misses) has motivated the design of "black-box" microprocessor power models. They get their name from the fact that they do not require any knowledge of hardware component implementation in contrast to above power models. Authors of [Contreras 2005] present a first order linear model that uses hardware monitoring counters to estimate the run-time energy consumption on the Intel PXA255 [INTEL 2003] processor. They show that their model exhibits an average estimation error of 4\%. Table 2.1, where the first column provides CPU related PMCs and the second provides PMCs related to the memory, offers an outline of performance monitoring counters that authors used in their power model. A scheme to associate energy usage pattern with every process for the purpose of thermal management in proposed in [Bellosa 2000]. The author correlates hardware monitoring counters to energy determinate the energy pattern of a thread. He then uses that energy information for energy-aware thread scheduling. One of the ideas behind this kind of scheduling is that by respecting the cache affinity of individual threads, and improving the cache reuse of individual threads that use share memory segment bus transactions and CPU stall cycles due to cache misses can be avoided. These models are simple and low-overhead; however, they do not model the whole system power consumption. In addition, they do not take into account all subsystem and may have portability related issues.

At the system level, [Economou et al. 2006] uses system components activity metrics such as CPU load and IO activity, and hardware monitoring counters to model the power consumption of a blade and an Itanium server. The proposed model captures power characteristics of system components by correlating hardware monitoring counters with power utilisation during the calibration phase. It

Table 2.1: Performance events selected to estimate CPU and memory power consumption for Intel PXA255 processor.

| CPU performance events   | Memory performance events |

|--------------------------|---------------------------|

| Instructions executed    | Instruction Fetch Misses  |

| Data dependencies        | Data Dependencies         |

| Instruction Cache Misses |                           |

| TLB Misses               |                           |

next uses parameters of the derived model for power consumption prediction based on the same PMCs. More recently, other researchers [Costa & Hlavacs 2010] have presented a methodology of measurement of the energy consumption of a single process application running on a standard PC. They defined a set of per process and system-wide variables to demonstrate their accuracy in measuring the energy consumption of a given process using multivariate regression. Authors of [Spiliopoulos et al. 2012] propose a profile based measurement infrastructure for measuring the power consumption of a program. The program goes through a first execution during which data required for performance and power prediction are collected. Still at the system level, some researchers attempt to take thermal issues into account when designing system-wide energy consumption models. For example, authors of [Lewis et al. 2012] propose a system-wide energy consumption models for server blades. Their energy model, which makes use of PCMs along with system ambient temperature, proposes a linear regression model that relates system energy input to subsystems' energy consumption.

To summarise, work listed above demonstrates that performance counters can accurately estimate or predict the power consumption of a program. The research also suggests that the accuracy of a power/energy model depends on the workload at hand. Put simply, a power model designed for estimating the power consumption of a compute-bound workload may not fit well a memory-bound workload. This is obvious for communication intensive workloads.

### 2.2 Energy Reduction in HPC Systems

In the past few years, HPC systems have witnessed the emergence of energy consumption reduction techniques from the hardware level to the software level. This section reviews power reduction techniques used in HPC environments.

#### 2.2.1 Energy efficient hardware design

At the hardware level, architects and equipment vendors are bringing to market multi-configuration HPC subsystems – including processor, communications, memory and storage – that can be dynamically reconfigured to reduce the energy consumption of the overall HPC infrastructure while maintaining reasonable perfor-

mance. For example, the majority of modern processors is provided with Dynamic Voltage and Frequency Scaling (DVFS) technology, which allows "on the fly" adjustment of the processor's frequency and voltage either to conserve power or to reduce the amount of heat generated by the chip. Another emerging technology is the Low Power Idle (LPI) for Network Interconnection Cards (NICs).

The power consumption of a CMOS integrated circuit (such as a modern processor) can be described by Equation 2.12 where C is the capacitance of the feature gate, f is the operating frequency and V is the supply voltage. As the supply voltage is determined by the frequency at which the circuit is clocked, it can be reduced as the frequency decreases. Consequently, DVFS can significantly reduce the power consumption of a CMOS integrated circuit because its dynamic power consumption is proportional to the square of the supply voltage as shown in Equation 2.12.

$$P = CfV^2 + P_{static} (2.12)$$

Alternatively, some architects address this issue by using the most efficient components for their equipments. This is illustrated by chip manufacturers who are bringing low voltage Dynamic Random Access Memory (DRAM) to market. Market leaders include Kingston "LoVo" (low voltage) HyperX DDR3 (DDR3 stands for dual data rate 3, similarly DDR2 stands for dual data rate 2), Micron's low voltage Aspen Memory, and Samsung Green DDR3. As opposed to standard next-generation DDR3 memory technology which operates at 1.5 volts and 1.8 volts for DDR2 memory, low power memory chips operate either at 1.25 volts or 1.35 volts. However, the impact of low power memory may not be noticeable because a large amount of servers around the globe uses chip memories which operate at 1.5 volts or higher.

Similarly, next-generation Solid State Drives (SSD) consume less power than traditional hard drives. For example, Intel's next-generation SSD DC 3700 Series reduces active power consumption to 6 watts and idle power to 650 milliwatts<sup>3</sup>, which lowers power and cooling costs. While Samsung's Green SSDs drive approximately consumes on average 60% less power than traditional hard disk drives<sup>4</sup>.

Power saving mechanisms are nonexistent in most of today's network interconnects. However, efforts are being undertaken to make interconnection networks greener. IEEE's task force on energy efficient Ethernet (IEEE 802.3az) examines power saving techniques such as dynamic link-speed reduction, and Low-power-idle (deep sleep states). In high bandwidth networks (100 Mbits/s and up), speed data links energy is used to keep the physical layer on all the time. That energy could be saved if they could be put in deep sleep when there is no data being transmitted [Merritt 2013]. Upon receiving the Low Power Idle signal the transmit chip in the system can be turned off when there is no data to sent and back on when needed. Stage-changes can take up to 10 microseconds, so HPC applications whose performance depends on the network are likely to suffer from performance degradation.

<sup>&</sup>lt;sup>3</sup>Intel, http://newsroom.intel.com

<sup>&</sup>lt;sup>4</sup>Samsung Green SSD, http://www.samsung.com

However, software mechanisms can first be used for profiling the behaviour of the application.

#### 2.2.2 Software solutions to the energy consumption issue in HPC

Software initiatives for reducing the power consumption of HPC systems take advantage of the variability of HPC workloads (in terms of resource demand) to reduce the overall system's power consumption. The power consumption is basically reduced by dynamically reconfiguring the processor via DVFS when executing some workloads or specific phases of a workload. Speaking of phases, a program phase or simply a phase is a period of execution of a program throughout which the program is relatively stable w.r.t a given metric. Initiatives for reducing the energy consumption in HPC environments can roughly be divided into off-line and on-line approaches. They are alike since they both attempt to scale the processor's frequency down/up according to a program's phases. However, on-line approaches lack detailed knowledge of the program phases.

#### 2.2.2.1 Off-line approaches

Off-line approaches necessitate human intervention and involve several steps including source code instrumentation for performance profiling; execution with profiling; determination of the appropriate processor frequency for each phase or region of execution of the program throughout which the program is relatively stable with respect to specific metrics; and source code instrumentation for inserting dynamic voltage and frequency scaling instructions. In [Freeh & Lowenthal 2005] the authors exploit MPI standard profiling interface (PMPI) to time Message Passing Interface (MPI) to insert DVFS scheduling calls based on duration, while other researches profile MPI communications [Cameron et al. 2005].

Similarly, authors of [Kimura et al. 2010] instrument the program source code to insert DVFS directives according to the program's behaviour. They divide the program into regions or phases and execute phases with low computational requirements at lower CPU frequencies. A DVFS control algorithm for sequential codes is presented in [Hsu & Kremer 2003], where the authors use compiler instrumentation to profile the program.

To reduce the energy consumption of HPC systems, some work suggested using inter-node imbalance analysis [Kappiah et al. 2005, Rountree et al. 2009]. In [Rountree et al. 2009] node imbalance is used to reduce the overall energy consumption of a parallel application. Authors track successive MPI communication calls to divide the application into tasks composed of a communication portion and a computation portion. A slack occurs when a processor is waiting for data during the execution of a task. This allows slowing the processor down with almost no impact on the overall execution time of the application. Consequently, authors developed Adagio [Rountree et al. 2009] which tracks task execution slacks and computes the appropriate frequency at which it should run. Although the first instance of a task

is always run at the highest frequency, further instances of the same task are executed at the frequency that was computed after it is first seen. [Kappiah et al. 2005] propose a tool called Jitter. Jitter detects slack moments in performance to performance inter-node imbalance and next uses DVFS to adjust the CPU frequency so that the processor does not have to wait for the completion of any task. In MPI programs, load imbalance often refers to situations where the completion of collective operations is delayed by a slower process or processes.

#### 2.2.2.2 On-line approaches

The way a program's execution changes often falls into repeating behaviours also knows as Phases. As on-line methodologies for reducing energy consumption in HPC systems lack detailed information about programs' phases they usually take advantage of those repeating behaviours. Consequently, the effectiveness of such power saving schemes depends on the accuracy of the program phase changes detection mechanism. We provide a comprehensive overview of program phase detection techniques in Section 2.3.

In [Choi et al. 2006, Isci et al. 2006], authors use on-line techniques to detect program execution phases or simply program phases, characterise them and set the appropriate CPU frequency accordingly. They rely upon hardware monitoring counters to compute run-time statistics – including cache hit/miss ratio, memory access counts, and retired instructions counts – that they use for program phase changes detection and characterisation. However, policies developed in [Choi et al. 2006, Isci et al. 2006] tend to be designed for single task environment.

[Lim et al. 2006] looked at on-line recognition of communication phases in MPI applications. Authors apply CPU DVFS to save energy once a communication phase has been reached. Their CPU DVFS accomplishes this saving by intercepting and recording the sequence of MPI calls during program execution. During this time it considers a segment of program code to be reducible if there are high concentrated MPI calls or if an MPI call is long enough. The CPU is then set to run at the appropriate frequency when the reducible region is recognised again. Authors of [Ge et al. 2007] proposed a system-wide and application-independent DVFS scheduler which scales down the processor's frequency when slower processor frequency does not have a significant impact on performance. They assume the program's run-time is a succession of time intervals or phases, gather PMCs for each phase and use past history to select the appropriate CPU frequency for the next interval.

More recently, a slack time based model for reducing the energy consumption was presented in [Spiliopoulos et al. 2011]. Authors developed analytical DVFS models with attempt to reduce slacks in the program's execution, and therefore lower the power consumption. Relying on an analytical DVFS model, authors propose a runtime framework which breaks the program into fixed length interval, uses hardware monitoring counters for characterising individual program interval and optimises them for power reduction accordingly.

# 2.3 Focus on Program Phase Detection for Energy Efficient HPC

A phase change can be thought of as a sudden change in the program's behaviour. As presented in the previous section, on-line methodologies for reducing the energy consumption of high performance computing systems generally go through program phase changes detection. There is a large body of work dealing with program phase changes detection in the literature. The most popular approaches are based on basic bloc vector, working set signature, and conditional branch counter.

Authors of [Sherwood et al. 2003, Sherwood et al. 2001] and [Ratanaworabhan & Burtscher 2008] use Basic Bloc Vectors (BBVs) to detect program phase changes. A basic bloc vector is a list of all blocs entered during program execution, and a count of how many times each basic bloc was run. They keep track of basic bloc vectors at fixed interval and then use a similarity threshold to decide whether a phase change has occurred or not. As similarity criterion, they use the Manhattan distance between consecutive basic bloc vectors. The similarity actually tells how close BBVs are to each other. Entire BBVs cannot be stored in hardware, to overcome that limitation, authors suggested to approximate them by hashing into an accumulator table containing a few larger counters.

Phase changes detection using conditional branch counters is presented in [Balasubramonian et al. 2000]. Authors keep track of conditional branches executed over a fixed execution interval, and detect a phase change when the difference in branch counts between consecutive intervals exceeds a threshold which varies throughout the program's execution. As long as a program phase is a program execution period throughout which specific metrics are relatively stable, there can be many ways of detecting program phase changes. Authors of [Huang et al. 2003] propose to use subroutines as a program phase granularity. They rely upon hardware call stack for identifying major program subroutines and detect a program phase change by comparing the program's behaviour across different subroutines. Typically, they track the time spent in each subroutine and detect a major phase when the time spent in a subroutine is greater than a preset (fixed) threshold.

In [Dhodapkar & Smith 2002b] authors use program instruction working set to detect phase changes. They define a program phase as a set of instructions touched in a fixed interval of time and refer to that as an instruction working set. Similarly to BBVs, complete working sets can be too large to efficiently represent and compare in hardware. Authors handle this by using a loosy-compressed representation of working sets called working set signature [Dhodapkar & Smith 2002a, Dhodapkar & Smith 2002b]. Instruction working sets are compared for phase changes detection. To accomplish this, authors use the relative signature distance between consecutive working set intervals to detect phase changes when that relative signature distance exceeds a predefined threshold.

Other researchers use methods from signal processing for program phase detection. In [Casas et al. 2007], signal processing techniques are used to automatically

detect periodic phases in MPI programs. The approach works by analysing the correlation of message passing activity in the application. The phase detection approach proposed in [Casas et al. 2007] and that in [Fürlinger & Moore 2008] are very similar; however, they differ in that the latter identifies iterative phases in the application by directly analysing the control flow graph of the application. In [Wimmer et al. 2009] trace compilation is used for detecting program phase changes. The program's execution is a collection of trace trees. Speaking of trace trees, a trace tree is a collection of frequently executed code paths through a code regions. Assuming that the program execution remains within a trace tree during a stable phase, a phase change occurs when there is a sudden increase in side exits from the trace tree.

ScarPhase an execution history-base on-line library for detecting and classifying phases in serial and parallel applications was recently proposed in [Sembrant et al. 2012, Sembrant et al. 2011]. The library divides the program's execution into non-overlapping windows and samples conditional branches during the execution of each window using performance monitoring counters. The address of each branch instruction is next hashed into a conditional branch vector whose entries show how many times corresponding branches were sampled during the window. Program phases are next determined by clustering branch conditional vectors so that similar vectors belong to the same phase.

A power oriented phase detection mechanism has also been investigated. In [Isci & Martonosi 2003a] authors employed run-time power measurements and power estimated with performance counters to identify execution phases of a program. The methodology lies on the assumption that changes in the program's behaviour are also reflected in its power consumption behaviour.

#### 2.4 Conclusions and Discussion

# 2.4.1 Discussion: need to address the energy consumption issue in HPC environments differently

As we have seen in the previous sections, the problem of energy consumption in high performance computing has been widely investigated. However, software solutions to that problem are less successful than their hardware counterpart. Current power reduction techniques as presented herein show that they are effective in the sense that they permit to reduce application's energy consumption without significant performance degradation. Unfortunately, to use these techniques, one would have to be an expert because of the complexity of their nature based on many different applications. Although intercepting MPI calls may be transparent, there is still the need to know what the application is doing in between those calls to set the appropriate frequency for example.

Power/energy reduction techniques presented above all have in common the fact that they attempt to reduce the energy consumption of the infrastructure from the application perspective, i.e., the focus is put on the application instead of the infrastructure itself. This is a limiting factor for several reasons including the fact that one would have to possess wast technical details behind the energy reduction scheme proposed. Moreover, the HPC infrastructure operator may not be authorised to look into users' workloads for specific reasons. In summary, more accessible (easy to use), easy to scale, and automated energy saving schemes need to be designed. In other words, energy saving schemes cannot succeed in real-life environments, unless they can be implemented without extensive efforts.

The processor has long been considered the most power hungry hardware among HPC subsystems, recent statistics place the memory subsystem at the top of the list. According to Samsung, considering the 8 hours active and 16 hours idle status in server, the memory subsystem is responsible for 15% of the overall energy consumption of a 16GB, 60nm 1GB dual data rate 2 (DDR2) based server. The share of energy consumed by the memory is even more for 32GB and 48GB servers using the same process technology, accounts for 21% and 26% of their total energy consumption respectively. In the last case, the energy consumption of the memory exceeds that of the processor (20%). Consequently, power saving schemes must take the memory subsystem more seriously. In other words, energy saving schemes must provide means for reducing the power consumption of the memory. The same goes for other HPC subsystems including the storage and communication subsystems. In a few words, it must offer users the opportunity to design system specific power saving schemes i.e., power saving schemes of their own.

#### 2.4.2 Conclusions

This chapter discussed approaches for making High Performance Computing (HPC) systems more energy efficient. Existing solutions are presented along with supporting mechanisms. Without lost of generality, these techniques include power and program analysis techniques.

Unlike hardware solutions, software approaches are often too complex and limited to the processors subsystem although other subsystems – memory, storage, and network interconnects – hold a considerable share in the overall power consumption of a typical supercomputer. By using the aforementioned steps to improve the efficiency of HPC systems the last step should emphasise on the design of user friendly solutions.

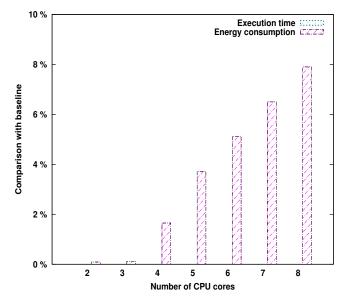

# A Blind Methodology for Improving Computing Infrastructures' Energy Performance

This introductory chapter summarizes our methodology for improving computing infrastructures' energy performance. We think of improving energy performance of a computing infrastructure as reducing its energy consumption without significant performance degradation. The term "significant performance degradation" being a relative term, it may be interpreted differently; however, a performance degradation of up to 10% is often acceptable. Note, unless expressly stated otherwise, we assume that (i) a high performance computing (HPC) system is a set of computing and storage nodes excluding network equipment such as routers and switches because of their nearly flat power consumption; (ii) whereas the term "system" designates a single node of the HPC system.

A typical HPC system throughout its life cycle exhibits several behaviours – in terms of utilization of available resources (processor, memory, storage, and communication subsystems) – reflecting phases of execution of a specific workload or workloads. Some of those phases or workloads are often similar in comparison with other workloads or regions of execution of a specific workload.