# Nouvelles Architectures Hybrides: Logique / Mémoires Non-Volatiles et technologies associées.

Giorgio Palma

#### ▶ To cite this version:

Giorgio Palma. Nouvelles Architectures Hybrides: Logique / Mémoires Non-Volatiles et technologies associées.. Autre. Université de Grenoble, 2013. Français. NNT: 2013GRENT042. tel-00951384

# HAL Id: tel-00951384 https://theses.hal.science/tel-00951384

Submitted on 24 Feb 2014

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Micro- et Nano-électronique

Arrêté ministérial: 7 août 2006

Présentée par

# Giorgio PALMA

Thèse dirigée par Prof. Amara AMARA

préparée au sein du CEA-LETI et de l' Ecole Doctorale de Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS), Grenoble

# Nouvelles Architectures Hybrides: Logique / Mémoires Non-Volatiles et technologies associées

Thèse soutenue publiquement le **29 Novembre 2013**, devant le jury composé de :

#### **M Gérard GHIBAUDO**

Prof., Université de Grenoble (IMEP-LAHC), Président

#### **M Jean-Michel PORTAL**

Prof., Polytech' Marseille (IM2NP), Examinateur

#### M Ian O CONNOR

Prof., Ecole Centrale de Lyon (ECL), Examinateur

#### **M Amara AMARA**

Prof., Institut Supérieur d'électronique de Paris (ISEP), Directeur de thèse

#### Abstract

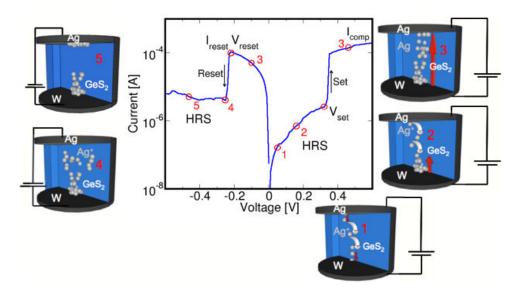

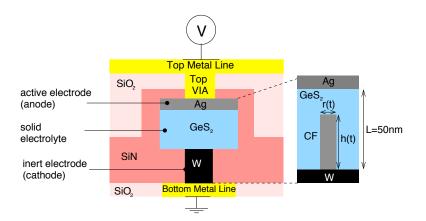

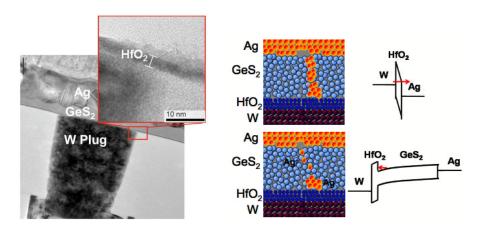

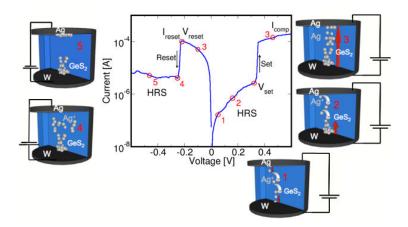

Novel approaches in the field of memory technology should enable backend integration, where individual storage nodes will be fabricated during the last fabrication steps of the VLSI circuit. In this case, memory operation is often based upon the use of active materials with resistive switching properties. A topology of resistive memory consists of silver (Ag) as electrochemically active metal and amorphous germanium disulfide (GeS<sub>2</sub>) acting as electrolyte and relies on the reversible formation and dissolution of a conductive filament. The application potential of these new memories is not limited to standalone (ultra-high density), but is also suitable for embedded applications. By stacking these memories in the third dimension at the interconnection level of CMOS logic, new ultra-scalable hybrid architectures becomes possible which exploit low energy operation, fast write/read access and high performance with respect to endurance and retention. In this thesis, focusing on memory technology aspects in view of developing new architectures, the introduction of non-volatile functionality at the logic level is demonstrated through three hybrid (CMOS logic + ReRAM devices) circuits: nonvolatile routing switches in a Field Programmable Gate Array, nonvolatile 6T-SRAMs and stochastic neurons of an hardware neural network. To be competitive or even improve existing solutions, limitations on the memory devices performances are identified and solved by stack engineering of CBRAM devices or providing fault tolerant circuits.

## RÉSUMÉ

# Nouvelles Architectures Hybrides: Logique / Mémoires Non-Volatiles et technologies associées

Les nouvelles approches de technologies mémoires permettront une intégration dite back-end, où les cellules élémentaires de stockage seront fabriquées lors des dernières étapes de réalisation à grande échelle du circuit. Ces approches innovantes sont souvent basées sur l'utilisation de matériaux actifs présentant deux états de résistance distincts. Le passage d'un état à l'autre est controlé en courant ou en tension donnant lieu à une caractéristique I-V hystérétique. Nos mémoires résistives sont composées d'argent (Ag) en métal électrochimiquement actif et de sulfure de germanium amorphe (GeS<sub>2</sub>) agissant comme électrolyte. Leur fonctionnement repose sur la formation réversible et la dissolution d'un filament conducteur. Le potentiel d'application de ces nouveaux dispositifs n'est pas limité aux mémoires ultra-haute densité mais aussi aux circuits embarqués. En empilant ces mémoires dans la troisième dimension au niveau des interconnections des circuits logiques CMOS, de nouvelles architectures hybrides et innovantes deviennent possibles. Il serait alors envisageable d'exploiter un fonctionnement à basse énergie, à haute vitesse d'écriture/lecture et de haute performance telles que l'endurance et la rétention. Dans cette thèse, en se concentrant sur les aspects de la technologie de mémoire en vue de développer de nouvelles architectures, l'introduction d'une fonctionnalité non-volatile au niveau logique est démontrée par trois circuits hybrides: commutateurs de routage non volatiles dans un Field Programmable Gate Arrays, une 6T-SRAM non volatile et les neurones stochastiques pour un réseau neuronal. Pour améliorer les solutions existantes, les limitations des performances des dispositifs mémoires sont identifiés et résolus en utilisant de nouveaux empilements ou en fournissant des circuits qui utilisent la variabilité des cellules pour avoir de meilleures performances.

## Acknowledgements

I am deeply thankful to many people (listed in alphabetical order): Amara A., Anghel C., Barci M., Becu S., Ben-Jamaa H., Bernard M., Bernard S., Bichler O., Billiot G., Blachier D., Blaise P., Boussey J., Bretegnier D., Buckley J., Cabout T., Cagli C., Carabasse C., Charbonneau M., Charpin C., Cibrario G., Clermidy F., Cluzel J., Commault C., Coquand R., Dahmani F., De Salvo B., Deleonibus S., Delaval G., Diokh T., Faynot O., Gaillardon P.-E., Garbin D., Gary M., Gaud P., Gely M., Ghibaudo G., Grosgeorges P., Guy J., Hraziia, Hubert Q., Jahan C., Jalaguier E., Jovanovic N., Kiouseloglou A., Klein J.-O., Larcher L., Liebault J., Longnos F., Lorenzi P., Makosiej A., Manzoni L., Martin O., Masoero L., Mazurier J., Molas G., Morvan S., Navarro G., Nodin J.-F., O Connor I., Onkaraiah S., Oucheick H., Ouerghi I., Perniola L., Persico A., Philippe J., Pirrotta O., Poiroux T., Portal J.-M., Poupinet L., Prouvee J., Querlioz D., Reimbold G., Reyboz M., Robert V., Rolandi P., Romano G., Roule A., Singh P., Souchier E., Souiki S., Sousa V., Suri M., Thomas O., Todorova T., Toffoli A., Traoré B., Turkyilmaz O. and last but not least Vianello E.

### Manuscript Outline

This manuscript was submitted in partial fulfillment of the requirements for obtaining the degree of Doctor of Philosophy of the Grenoble Institute of Technology (Grenoble INP). The topic addressed in this Ph.D. thesis deals with novel hybrid logic and nonvolatile memory architectures and associated technologies. The manuscript covers both emerging memory devices features, in particular related to Conductive Bridge RAM technology and design/simulation of hybrid circuits such as nonvolatile 6T-SRAM, nonvolatile routing switches in FPGAs embodiments and neuron circuits. Foreseen advantages in implementing hybrid architectures are discussed accordingly to electrical results obtained on several CBRAM technologies. In fact, a part of the thesis was devoted to electrically characterize several CBRAM cell stacks in view of developing nonvolatile memory solution for: renovating some of the FPGA blocks, design a nonvolatile SRAM, or create fault-tolerant designs, that could also exploit non optimized technologies.

It's well known that intrinsic variability of emerging technologies such as ReRAM complicates the physical understanding, the prediction of device behavior under different stresses (thermal, noise) and finally the development of reliable electrical models implemented in commercial IC design tools. Typically, the development of behavioral compact models is subjected to parameters extracted on a large number of devices but, nowadays, there is a limited number of hybrid architectures, that could validate, for example, the performances of a distributed (on logic) memory node. Hence, the integration of a CBRAM compact model in IC design tools is the critical step for proposing new concepts, for validating the main operations of new circuits and eventually for launching the fabrication on silicon.

Chap. 1 of this thesis introduces the international context, the state of the art for emerging nonvolatile memories, the limitations and the issues due to the aggressive scaling of 6T-SRAM or due to the excessive power consumption in FPGA. In a second part, we will discuss the most advanced solutions to design nonvolatile 6T-SRAMs and to renovate FPGA blocks. We will conclude the chapter with some basic concepts related to hardware neural networks.

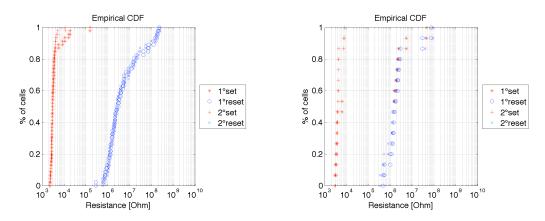

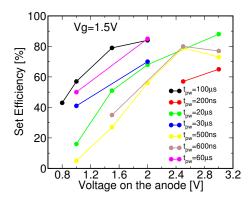

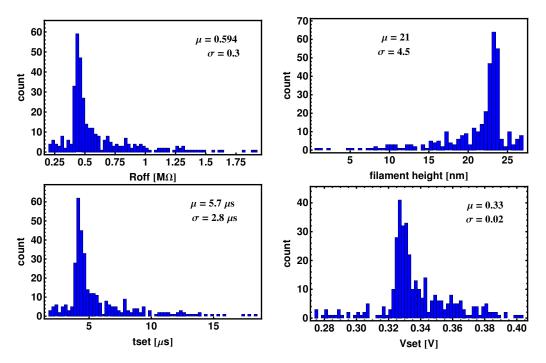

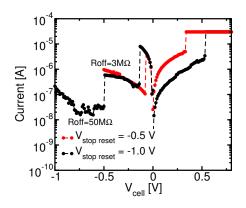

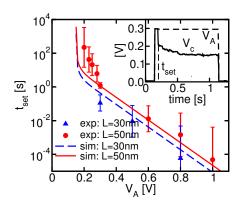

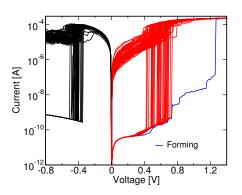

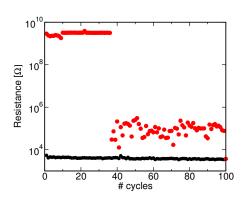

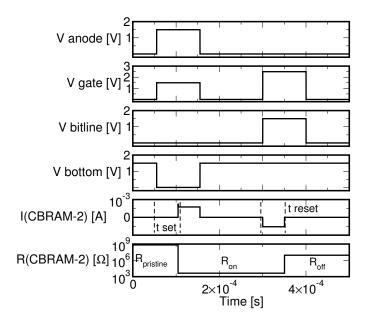

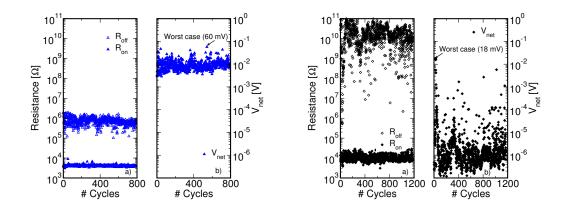

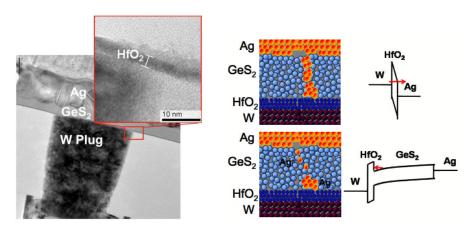

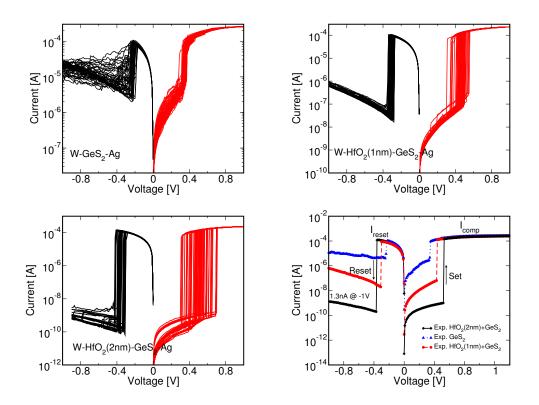

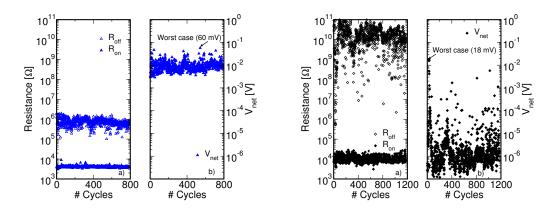

In Chap. 2 we will present some of the results of the electrical characterizations of Ag/GeS<sub>2</sub> based CBRAM devices (integrated in the 1R or the 1T-1R architecture) and the empirical model used to explain and predict the switching parameters. We will propose a statistical analysis on the switching probability based on measurements on 8×8 memory arrays to improve the model taking into account cell to cell and cycle to cycle variability.

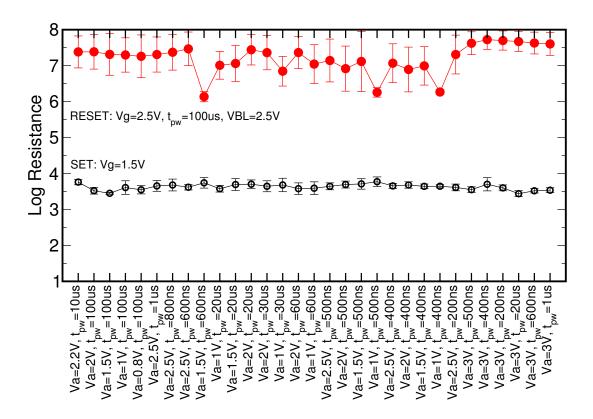

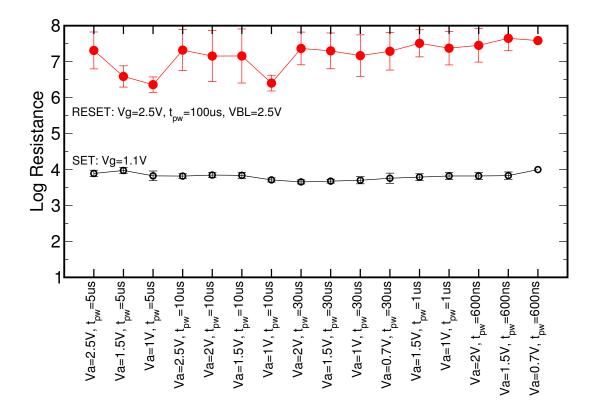

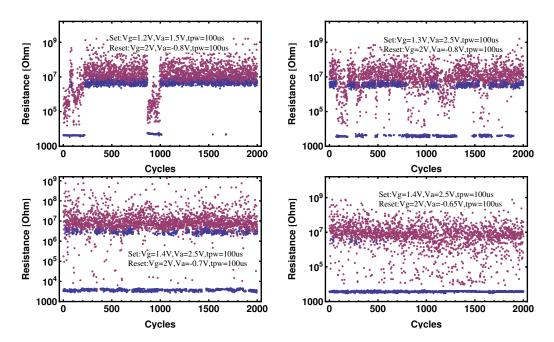

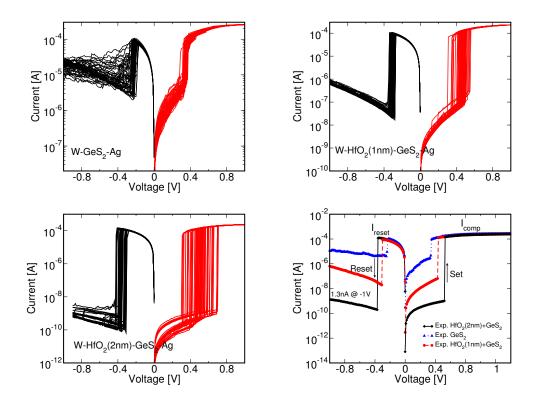

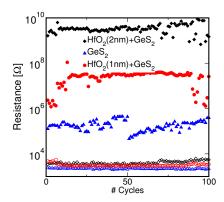

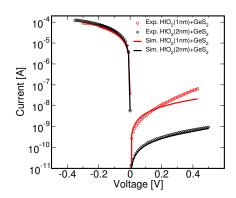

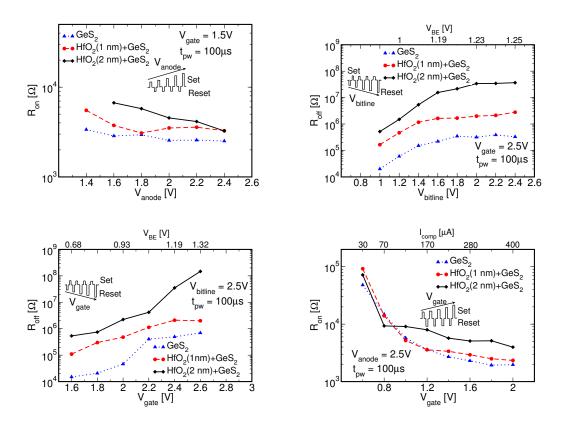

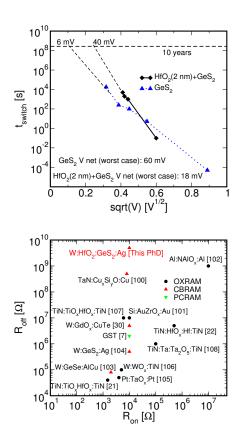

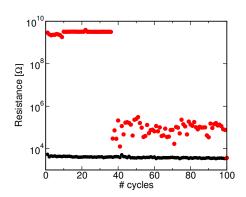

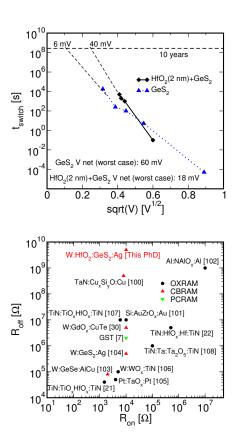

Chap. 3 is devoted to find a suitable CBRAM technology in view of design and optimize a specific block of an FPGA. Electrical results related to several CBRAM stacks fabricated with a dual-layer based electrolyte will be presented. Among other CBRAMs technologies, our dual-layer electrolyte stack  $(2 \text{ nm HfO}_2-30 \text{ nm GeS}_2)$  is the most promising. We will demonstrate a resistance ratio  $(R_{\text{off}}/R_{\text{on}})$  higher than  $10^6$ , a reset current of  $100 \,\mu\text{A}$  and no forming step.

In Chap. 4 we will discuss a nonvolatile 6T-SRAM, a nonvolatile routing switch based on 1T-2R architecture and a stochastic neuron circuit as hybrid architectures. Operation schemes will be validated by means of Eldo simulations and the effect of  $V_T$  MOSFET variability will be introduced, for the 6T-SRAM design, by Monte-Carlo and worst case simulations. Next, advantages in implementing a 1T-2R nonvolatile element in FPGA using our dual-layer electrolyte stack will be elucidated. The chapter ends with a review on a Stochastic Integrate and Fire neuron circuit that exploit the variability in the time required to set CBRAM devices.

**Chap. 5** provides the conclusions, the highlights and the perspective of the research conducted for this thesis. A description of the on-going activities is given.

# Contents

| 1 | $\mathbf{Intr}$ | oduct  | ion                                                               | 1  |

|---|-----------------|--------|-------------------------------------------------------------------|----|

|   | 1.1             | The M  | Memory hierarchy                                                  | 2  |

|   | 1.2             | Overv  | iew of next generation of nonvolatile                             |    |

|   |                 | Rando  | om Access Memories (RAM)                                          | 3  |

|   |                 | 1.2.1  | Phase Change RAM                                                  | 4  |

|   |                 | 1.2.2  | Ferroelectric RAM                                                 | 5  |

|   |                 | 1.2.3  | Spin Transfer Torque RAM                                          | 6  |

|   |                 | 1.2.4  | Resistive RAM                                                     | 8  |

|   | 1.3             | Embe   | dded nonvolatile memories                                         | 10 |

|   |                 | 1.3.1  | Mask-programmable ROM                                             | 10 |

|   |                 | 1.3.2  | Electrically programmable FLASH                                   | 11 |

|   | 1.4             | Embe   | dded volatile memories                                            | 12 |

|   |                 | 1.4.1  | 6T-Static Random Access Memories (6T-SRAM)                        | 12 |

|   |                 |        | 1.4.1.1 Architecture of a 6T-SRAM                                 | 12 |

|   |                 |        | 1.4.1.2 Scaling issues and power consumption                      | 13 |

|   | 1.5             | Embe   | dded nonvolatile SRAM (NV-SRAM) for mobile applications $\ . \ .$ | 15 |

|   | 1.6             | Field  | Programmable Gate Array (FPGA)                                    | 16 |

|   | 1.7             | 6T-SR  | RAM based FPGA                                                    | 18 |

|   |                 | 1.7.1  | Power consumption in 6T-SRAM based FPGA                           | 19 |

|   | 1.8             | FPGA   | in mobile applications                                            | 21 |

|   | 1.9             | Hybrie | d architectures: FPGA and ReRAM                                   | 23 |

|   |                 | 1.9.1  | ReRAM in switching blocks: 2T-1ReRAM architecture                 | 24 |

|   |                 | 1.9.2  | ReRAM in switching and logic blocks: 1T-2ReRAM architecture       | 25 |

|   | 1.10            | Main   | concepts on stochastic neural networks                            | 27 |

### CONTENTS

|          | 1.11 | Conclu    | sions                                                                                   | 29 |

|----------|------|-----------|-----------------------------------------------------------------------------------------|----|

| <b>2</b> | Cha  | racteri   | ization and modeling of $Ag-GeS_2$ based CBRAM devices                                  | 31 |

|          | 2.1  | W-GeS     | S <sub>2</sub> -Ag based CBRAM devices                                                  | 32 |

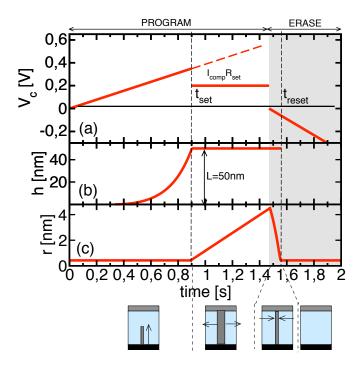

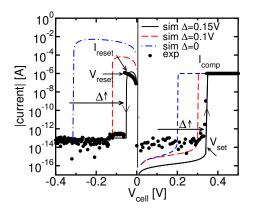

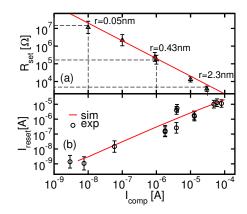

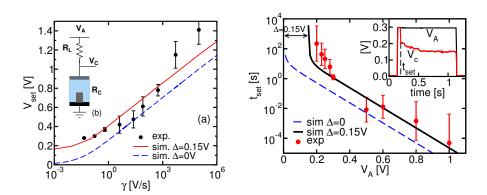

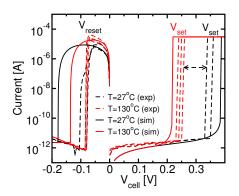

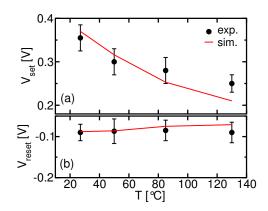

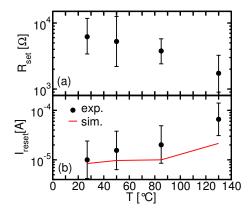

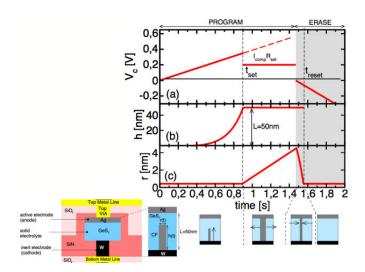

|          |      | 2.1.1     | Empirical model of the resistive switching in W-GeS2-Ag $\ \ .$                         | 33 |

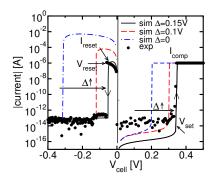

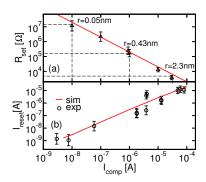

|          |      | 2.1.2     | Set and reset operation in quasi-static mode                                            | 35 |

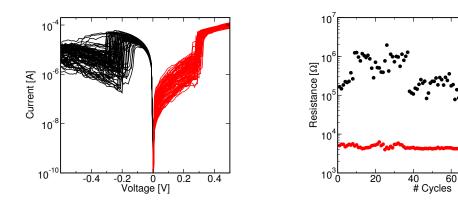

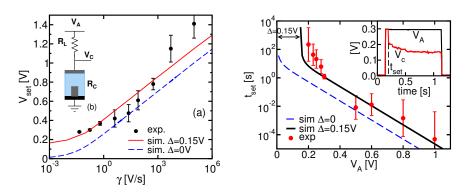

|          |      | 2.1.3     | Set and reset operation in pulse mode                                                   | 38 |

|          |      | 2.1.4     | Flow chart of the compact model                                                         | 40 |

|          |      | 2.1.5     | Temperature effects on the switching kinetics                                           | 41 |

|          | 2.2  | Switch    | ing probability in W-GeS $_2$ -Ag based                                                 |    |

|          |      | CBRA      | M devices                                                                               | 43 |

|          | 2.3  | Phenor    | menological explanation of variability in the                                           |    |

|          |      | switchi   | ing time                                                                                | 47 |

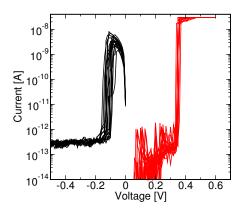

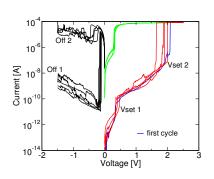

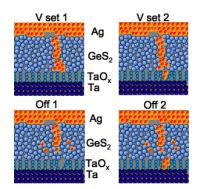

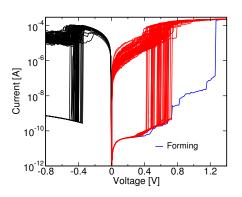

|          | 2.4  | Ta-Ges    | $S_2$ -Ag based CBRAM                                                                   | 49 |

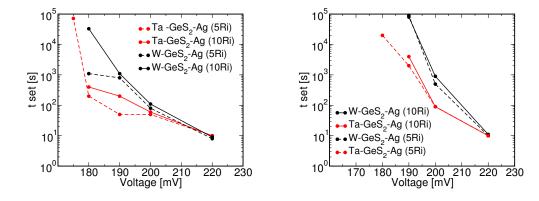

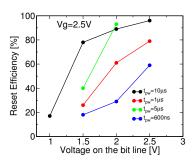

|          |      | 2.4.1     | Low-voltage pulse measurements                                                          | 50 |

|          | 2.5  | Conclu    | sions                                                                                   | 53 |

| 3        | CB   | RAM s     | stack engineering for increasing $R_{ m off}$                                           | 57 |

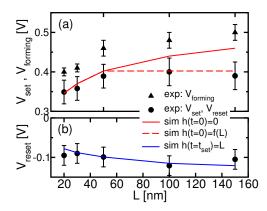

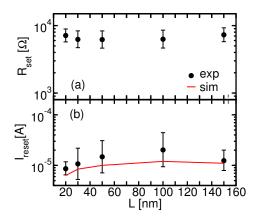

|          | 3.1  | $GeS_2$ t | hickness effects on the switching kinetics                                              | 58 |

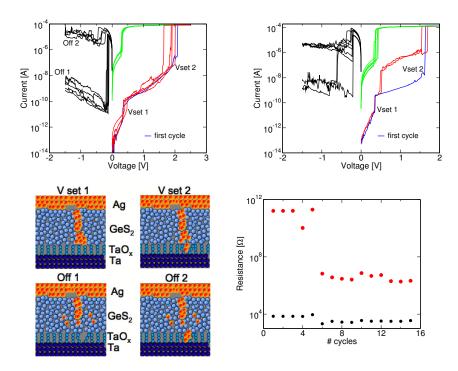

|          | 3.2  | Ta-Ta(    | $D_x$ -GeS <sub>2</sub> -Ag based CBRAM                                                 | 61 |

|          | 3.3  | W-SiO     | $_{x}$ -GeS <sub>2</sub> -Ag based CBRAM                                                | 62 |

|          | 3.4  | W-HfC     | $O_2$ -GeS $_2$ -Ag based CBRAM                                                         | 63 |

|          | 3.5  | Conclu    | sions                                                                                   | 67 |

| 4        | Non  | volatil   | e hybrid (logic and ReRAM) architectures                                                | 71 |

|          | 4.1  | OxRR.     | AM based nonvolatile SRAM (8T2R NV-SRAM)                                                | 72 |

|          |      | 4.1.1     | 8T2R NV-SRAM cell static noise margin                                                   | 74 |

|          |      | 4.1.2     | The influence of $\mathrm{V}_{\mathrm{T}}$ variability on the stability of 8T2R NV-SRAM | 76 |

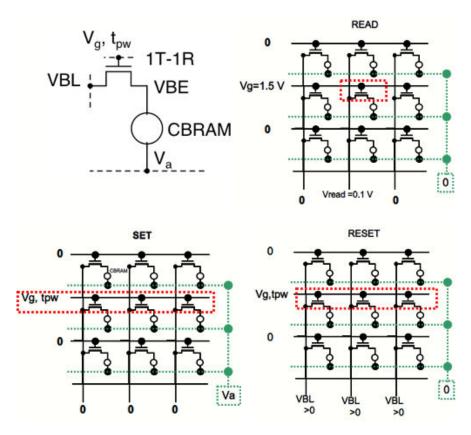

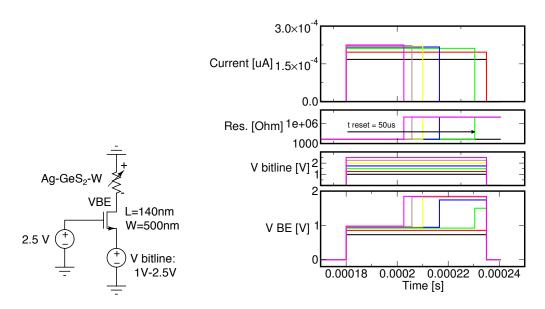

|          | 4.2  | Simula    | tions of 1T-1CBRAM structure                                                            | 80 |

|          | 4.3  | CBRA      | M based 8T2R NV-SRAM                                                                    | 81 |

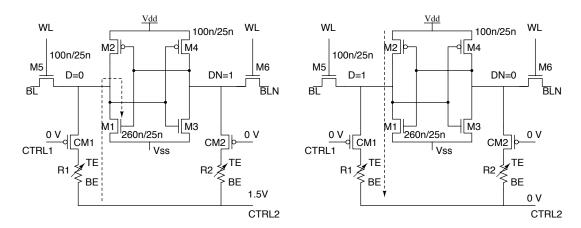

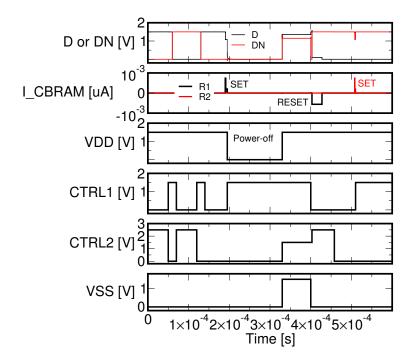

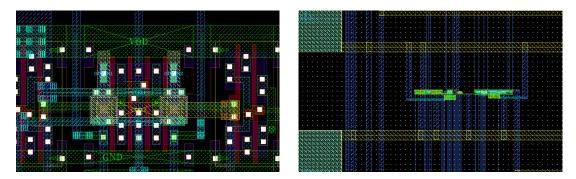

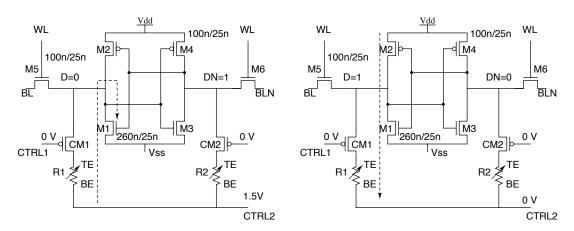

|          | 4.4  | 1T-2C     | BRAM as nonvolatile memory element in FPGA                                              | 83 |

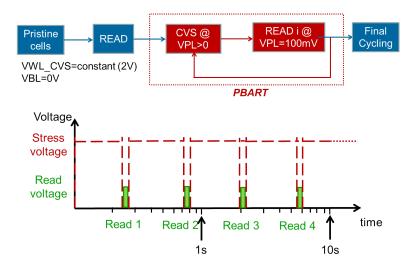

|          |      | 4.4.1     | Pulsed-tests and read disturb analysis                                                  | 85 |

|          |      | 4.4.2     | Comparison and leakage currents estimations                                             | 86 |

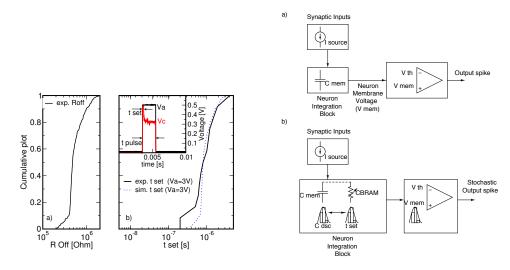

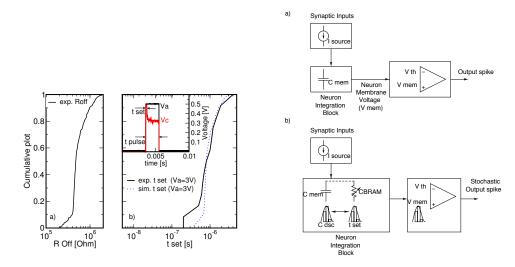

|          | 4.5  | Stocha    | stic synapses for neuromorphic applications                                             | 87 |

## CONTENTS

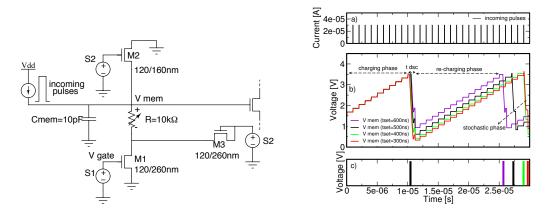

|              | 4.6<br>4.7 |        | astic neurons                                                     |     |

|--------------|------------|--------|-------------------------------------------------------------------|-----|

| 5            | Con        | clusio | ns                                                                | 97  |

|              | 5.1        | Perspe | ectives                                                           | 99  |

| $\mathbf{A}$ | List       | of Pa  | tents and Publications                                            | 101 |

|              | A.1        | Patent | ts                                                                | 101 |

|              | A.2        | Confer | rence and Journal Papers                                          | 101 |

| В            | Rés        | umé e  | n Français                                                        | 105 |

|              | B.1        | Introd | uction                                                            | 105 |

|              |            | B.1.1  | Mémoire ReRAM                                                     | 105 |

|              |            | B.1.2  | SRAM non volatile pour applications embarquées à faible con-      |     |

|              |            |        | sommationes                                                       | 106 |

|              |            | B.1.3  | Architecture hybride de type FPGA et ReRAM                        | 107 |

|              |            | B.1.4  | Systeme neuromorphiques                                           | 109 |

|              | B.2        | Caract | térisation et modélisation de mémoire CBRAM basée sur Ag-GeS $_2$ | 110 |

|              | В.3        | Ingéni | erie de l'empilement pour augmenter $R_{\rm off}$                 | 114 |

|              |            | B.3.1  | ${ m Ta-TaO}_x{ m -GeS}_2{ m -Ag}$ CBRAM                          | 115 |

|              |            | B.3.2  | $W$ -SiO $_x$ -GeS $_2$ -Ag CBRAM                                 | 116 |

|              |            | B.3.3  | W-HfO <sub>2</sub> -GeS <sub>2</sub> -Ag CBRAM                    | 116 |

|              | B.4        | Nouve  | lles architectures hybrides: Logique et Mémoire ReRAM $\dots$     | 118 |

|              |            | B.4.1  | NVSRAM basée sur des elements OxRRAM                              | 118 |

|              |            | B.4.2  | 1T-2CBRAM en tant qu' élément non volatile dans les FPGA          | 121 |

|              | B.5        | Neuro  | nes stochastiques                                                 | 123 |

|              | B.6        | Conclu | asion                                                             | 124 |

| Lis          | st of      | Figure | es                                                                | 129 |

| Lis          | st of      | Tables | S                                                                 | 145 |

| Bi           | bliog      | raphy  |                                                                   | 147 |

## CONTENTS

## 1

# Introduction

This chapter introduces some of the trends in the memory research both at device level and at the circuit integration level. There are two great motivations that push the research in finding new memory materials, new storage mechanism and new stacking architectures: the filling of the latency gap in the memory hierarchy and the replacement of flash memories for the sub-20 nm node. Both stand-alone and embedded applications will be renovated by the introduction of nonvolatile, byte addressable, and in place writable Random Access Memory (RAM), also called Storage Class Memory (SCM). Moreover, because of the low voltage, CMOS compatibility, projected 10 years retention at 110 °C and good cyclability other important markets such as low power mobile can be greatly improved. A brief survey of the main emerging non volatile memories such as: Phase Change RAM (PCM), Ferroelectric RAM (FeRAM), Spin Transfer Torque RAM (STT-RAM) and Resistive RAM (ReRAM) will be presented. Next, starting from a description of embedded volatile memories, we will introduce the benefits in implementing a nonvolatile 6T-SRAM, hence explaining motivations in investigating further this architecture. Novel 3D hybrid FPGA architectures leading to better performance than that of existing planar FPGA will also be discussed. We will describe some of the constraints at memory level in implementing novel architectures in the main blocks of an FPGA, boosting our research in finding the most suitable ReRAM technology expected to minimize the power consumption. Finally, a brief introduction on stochastic neural network will be given to propel the conception of a stochastic neuron.

| ${f Metric}$         | NAND Flash       | NOR Flash              | $\mathbf{PCM}$      | $\mathbf{SRAM}$       | $\mathbf{DRAM}$  |

|----------------------|------------------|------------------------|---------------------|-----------------------|------------------|

| Technology Node [nm] | 22               | 40                     | 45                  | 22                    | 32               |

| Cell Size            | $4 \mathrm{F}^2$ | $10 \; \mathrm{F}^2$   | $5.5~\mathrm{F}^2$  | $120 \; \mathrm{F}^2$ | $8~\mathrm{F}^2$ |

| Chip Size            | 128 Gb           | 8 Gb                   | 1-8 Gb              | 30 MB                 | 4 Gb             |

| Write Bandwidth      | 100 MB/s         | 2  MB/s                | 9 MB/s              | $500~\mathrm{GB/s}$   | 1  GB/s          |

| Read Bandwidth       | 200 MB/s         | $100 \; \mathrm{MB/s}$ | $266~\mathrm{MB/s}$ | $500~\mathrm{GB/s}$   | 1  GB/s          |

| Latency              | 30 us            | 70 ns                  | 85 ns               | 5 ns                  | 20 ns            |

| Endurance            | $10^{4}$         | $10^{5}$               | $10^{9}$            | $10^{15}$             | $10^{15}$        |

Table 1.1: Comparison of metrics for memories on the market.

### 1.1 The Memory hierarchy

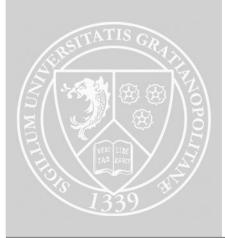

In recent years, Central Processor Units (CPUs) speeds have increased significantly [1]. On the other hand, memory improvements have mostly been in density rather than transfer rates (read/write bandwidth) (Fig. 1.1 (a)-(b)). As speeds have increased, the CPU has spent an increasing amount of time waiting for data to be fetched from memory. No matter how fast a given CPU can work, in some cases it is limited to the rate of transfer allowed by the bottleneck between memories and processor (Von Neumann bottleneck). Currently, state of the art CPUs operate at 5.7 GHz [1], whereas even the fastest off-chip memories operate between 1 GHz [2] and 2.66 GHz [3]. The memory hierarchy is an arrangement of different types of memories with different capacities and operation speeds to approximate the ideal memory request of a processor in a cost-efficient way [4].

Fig. 1.1(c) shows the typical access latency (in cycles assuming a 4 GHz machine) of different memory technologies, and their relative place in the memory hierarchy. As already demonstrated in the case of Phase Change Memories (Sec. 1.2.1) new emerging memories showing access latency between DRAMs and Hard Disks are expected to bridge completely the access latency gap (Fig. 1.1(b)). The ultimate target for Von-Neumann based computing would be replacing DRAMs using nonvolatile memories with the same bandwidths (1 GB/s for read and write), compatibility with high-speed wired interface schemes (DDR), endurance of 10<sup>15</sup> cycles and exhibiting capacity of TBs [5]. Table 1.1 shows in more details several figures of merit for different kind of memories that we reported in Fig. 1.1(c).

Figure 1.1: a) Memory capacity trend of different nonvolatile memory technologies. b) Comparison of different nonvolatile memory technology as a function of write and read bandwidth demonstrated at chip level. DDR, DDR2 and DDR3 are the high-speed interface scheme required for different DRAMs generation [1]. c) Access latency in terms of processor cycles for a 4 GHz processor [5]. Hybrid solutions Phase Change Memories + DRAM ( two macro in a single package) have been introduced by Micron.

# 1.2 Overview of next generation of nonvolatile Random Access Memories (RAM)

As shown in Fig. 1.1(c) and Tab. 1.1 Flash and PCM do not fulfill all the requirements to compete with DRAMs. The main limitations are the latency for NAND and the write bandwidth for NOR and PCM. In addition the endurance is limited to 10<sup>5</sup> cycles for NOR, 10<sup>4</sup> cycles for NAND (considering the 22 nm technological node), and 10<sup>9</sup> for PCM, whereas DRAM requires 10<sup>15</sup>. The high voltage needed for the operation of NOR and NAND memories is also a strong limitation for future integration with advanced CMOS logic in embedded systems thus making even more difficult an improvement in the bandwidth if the nonvolatile memory is used off-chip (i.e. with a serial interface)

(Sec. 1.3.2). As a result, other memories candidates are currently under investigation to provide lower latencies, higher bandwidths and compatibility with advanced (beyond 28 nm high-k MOSFETs) CMOS. This research paves the way for non volatility at several levels of the memory hierarchy and therefore provides a new abstraction on the memory systems. Integration of nonvolatile, byte addressable memories, supporting in-place writing is especially required for System on Chip (SoC) and could revolutionize consolidated architectures such as Field Programmable gate Array (FPGA) both in memory block and distributed memory cells at the interconnection level of CMOS logic. Advanced architectural studies have indicated that FPGA can be greatly improved by emerging memories distributed above the logic, as we will discuss in Sec. 1.9. Because a large number of novel hybrid (logic and SCM) architecture rely on different emerging non volatile memories, a brief survey of such technologies is presented in the next subsections.

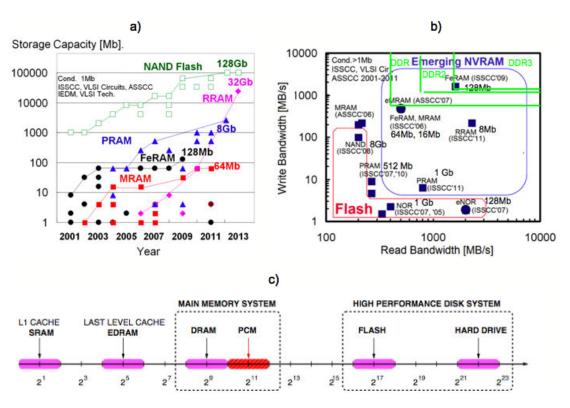

#### 1.2.1 Phase Change RAM

In Phase Change memory (PCM) the memory element is an alloy of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>,  $Ge_xTe_{1-x}$ , C doped  $Ge_xTe_{1-x}$  or N doped  $Ge_xTe_{1-x}$ . PCM utilizes the large resistivity difference between crystalline (low resistivity) and amorphous (high resistivity) phases of the phase change material. Set and reset state of PCM refers to low and high-resistance state, respectively. As fabricated, the phase change material is in the crystalline state. To reset the PCM cell into the amorphous phase, the programming region is first melted and then quenched rapidly by applying a large electrical current pulse for a short time period (Fig. 1.2 left). This operation generates a region of amorphous, highly resistive material in the PCM cell. To set the PCM cell into the crystalline phase, a current pulse is applied to annual the programming region at a temperature between the crystallization temperature and the melting temperature for a time period long enough to crystallize (Fig. 1.2 left) [6]. Fig. 1.2 shows the current voltage I-V curve for the PCM. The set and reset states have two orders of magnitudes resistance difference for voltages below the threshold switching  $V_{\rm th}$ . If a voltage higher than  $V_{\rm th}$  is applied for longer than the crystallization time it leads to memory switching to low resistance state. When the PCM is in the reset state the resistance of the PCM is too high to conduct enough current to provide Joule heating to crystallize the PCM cell. In fact it is the electronic threshold switching effect that lower the resistance of the phase change

Figure 1.2: (Left) Temperature-time and voltage-time diagram to describe set and reset operations and consequences on the lattice structure of GST material. (Right) Current-Voltage characteristics of the cell. The electronic switching corresponds to the decrease of the voltage in the amorphous state and the current increase that leads to the crystallization of the amorphous region. In the inset: schematic of the PCM structure and TEM of the integrated structure.

material and enables set programming. Reset programming consumes the largest power since the cell needs to reach the melting temperature. Reset current is also determined by material properties (doping) or stoichiometry, but still is in the order of mA or hundreds of μA. Endurance of 10<sup>9</sup> and a projected data retention of 10 years at 85 °C have been reported [7]. PCM are fabricated with 20 nm technology with a density of 8 Gb showing 40 MB/s write bandwidth [8]. A nonvolatile 6T-SRAM was proposed in [9].

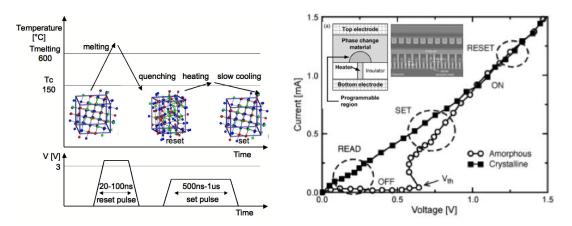

#### 1.2.2 Ferroelectric RAM

In Ferroelectric RAM (FeRAM) the memory element consists of a ferro-electric material embedded between metallic electrodes made of Pt, Ir, or oxides of transition metals such as  $RuO_2$  and  $IrO_2$ . The typical active ferroelectric materials are lead zirconate titanate ( $PbZr_zTi_{1-x}O_3$ ) and strontium bismuth tantalite ( $SrBi_2Ta_2O_9$ ) that shows two stable states of polarization corresponding to the two stable configuration of ions within the unit cell of the crystal lattice. This polarization does not vanish when the external field is removed (Fig. 1.3). Attainable cell sizes in 1T-1C configuration are in the range of 4-15  $F^2$ . The main attractiveness of this technology is that the read and programming pulses can be less than 50 ns and it is possible to get endurance typically

**Figure 1.3:** Schematic structure of FeRAM cell with capacitors connected in parallel (chain FeRAM) and TEM cross section of the integrated structure. Polarization-Voltage curve (P-V) that shows two stable states of remnant polarization  $(25\,\mu\,\mathrm{C\,cm^{-2}})$  used to store the information [13], [10].

about 10<sup>12</sup> cycles. Dynamic energy can be minimized till 200 fJ/bit and 1.6GB/s read/write bandwidth has been reported [10], [11]. Main limitations of FeRAM are related to the the read operation that is destructive, the scalability and the high thermal budget (600 °C - 700 °C) due to the crystallization temperature of these materials. 4 Mb embedded FeRAMs (e-FeRAMs) produced using a 180 nm process with a 1.8 V requirement have become widely deployed in IC cards and RFID tags for improving traceability and security. 16 Kb e-FeRAM for energy harvesting applications has been also developed, showing 82μA/MHz dynamic consumption (for comparison SuperFlash memories have 70μA/MHz dynamic consumption during read operation). The largest FeRAM chip was fabricated in 130 nm technology with a density of 128 Mb, and 75 ns read/write cycle [11]. A 512-byte nonvolatile SRAM using 250 nm double metal layer CMOS process with ferroelectric capacitors is described in [12].

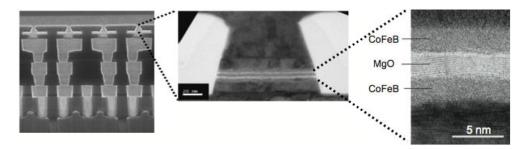

#### 1.2.3 Spin Transfer Torque RAM

In Spin Transfer Torque RAM the memory element is a magnetic tunnel junction (MTJ) that consists of two magnetic electrodes embedding an insulating MgO tunnel barrier (Fig. 1.4). The resistance of these magnetic tunnel junctions depends on the relative orientation of the magnetic moments in the two magnetic electrodes interfacing with the tunnel barrier. When the magnetic moments of the two magnetic layers are antiparallel, the resistance of the tunnel junction is significantly higher than when they are in parallel. A trilayer known as synthetic antiferromagnetic layer is used as reference to fix the direction of the magnetic moment. Hence, the magnetic moment orientation

Figure 1.4: TEM cross section of the integrated MRAM structure [15].

**Figure 1.5:** Spin transfer Torque Magnetization switching. From the left: Anti-Parallel to Parallel switching, and parallel to antiparallel switching. Example of current-induced switching. Quasi-static V-I curve show the existence of two available resistance states. The free layer of the MTJ can be switched parallel or antiparallel to the pinned layer depending on the direction of the current [15],[16].

of the storage layer will give rise to two states with distinctively different resistance values, thereby, the two states in binary bit [14]. Typical memory cells consist of two transistors connected in parallel with the MTJ to provide the current necessary for programming. The free layer of the MTJ can be switched parallel or antiparallel to the pinned layer depending on the direction of the current (Fig. 1.5). The injected current pulse is typically 200 μA in amplitude and 5 ns in duration, corresponding to a switching energy on the order of pJ [14]. The switching current density is of the order of 1 M A cm<sup>-2</sup>. The reported endurance is 10<sup>15</sup>. STT-RAM suffers of poor CMOS compatibility and active layers roughness that can increase cell to cell variability. The largest STT-RAM chip was fabricated in 54 nm technology with a density of 64 Mb, employing a 2T-1MTJ cell; programming and read speeds of 20 ns were achieved [17]. Multi-Context Look-Up Table [18] and nonvolatile Flip-Flop [19] in FPGA have been proposed using TAS (Thermally Assisted Magnetic) and STT-RAM.

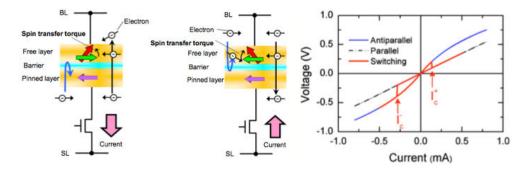

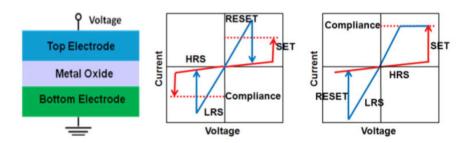

**Figure 1.6:** Schematic of MIM structure for metal oxide ReRAM and schematic DC I-V characteristics showing unipolar and bipolar behavior [20].

**Figure 1.7:** (Left) TEM of the integrated ReRAM. Both the bottom electrode and the top electrode have been scaled to 10 nm. Switching current vs operational speed.

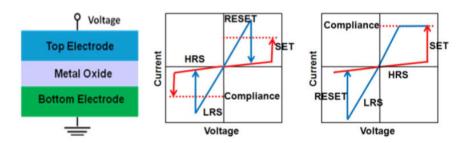

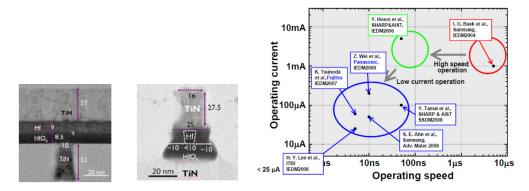

#### 1.2.4 Resistive RAM

In ReRAM memory elements are typically transition metal oxides embedded between two metal electrodes. The memory effect relies on the reversible transitions from high (reset) to low (set) resistive states upon the application of an electric field on the structure. Thermochemical and/or electrochemical reactions are responsible of the switching mechanism, which can be triggered by the amplitude of the applied electric field (unipolar switching mode) or by the polarity of the applied field (bipolar switching mode). In particular, in bipolar mode, set process can only occur at one polarity and reset can only occur at the reverse polarity (Fig. 1.6). The switching behavior is not only dependent on the oxide materials but it is also dependent on the choice of metal electrodes and the physics at the interfaces. Typical transition metal oxides are  $TaO_x$ ,  $HfO_x$  and  $AlO_x$  that exploit the lattice sub-stoichiometry in oxygens atoms, hence the mobility of oxygen vacancies. In particular, it was observed that the low resistive state

**Table 1.2:** Comparison of metrics of largest chip demonstrated for various memory technologies with focus on evolution of ReRAM in 3 years. Note that the highest density has been achieved in ReRAM where the memory stack is 1D-1R where D is a bipolar diode to avoid sneak current.

| Metric                         | FeRAM                     | STT-RAM          | PCM        | ReRAM              | ReRAM                                | ReRAM                  |

|--------------------------------|---------------------------|------------------|------------|--------------------|--------------------------------------|------------------------|

| Year                           | 2009                      | 2010             | 2009       | 2010               | 2012                                 | 2013                   |

| Technology Node [nm]           | 130                       | 54               | 45         | 130                | 180                                  | 24                     |

| Active Stack                   | ${\rm SRO\text{-}PZT/Ir}$ | CoFeB-MgO        | GST        | ${ m MeO}_x$ 1D-1R | ${ m TaO}_x/{ m Ta}_2{ m O}_5$ 1D-1R | $\mathrm{MeO}_x$ 1D-1R |

| Half-Pitch, F [nm]             | 225                       | 54               | 52         | 200                | N.A.                                 | N.A.                   |

| Memory Area [μm <sup>2</sup> ] | 0.252                     | 0.041            | 0.015      | 0.168              | 0.144                                | N.A.                   |

| Cell Size                      | $5F^2$                    | $14F^2$          | $5.5F^{2}$ | $4.2F^{2}$         | N.A.                                 | N.A.                   |

| Chip Size                      | 128Mb                     | 64Mb             | 1Gb        | 64Mb               | 8Mb                                  | 32Gb                   |

| Write Speed                    | 83 ns                     | 15 ns            | 100-500ns  | 1-10ms             | N.A.                                 | 230us                  |

| Read Speed                     | 43ns                      | $20 \mathrm{ns}$ | 85  ns     | $100 \mathrm{ms}$  | $25 \mathrm{ns}$                     | 40us                   |

| Vcc [V]                        | 1.9                       | 1.8              | 1.8        | 3-4                | N.A.                                 | N.A.                   |

| Reference                      | [11]                      | [17]             | [7]        | [26]               | [27]                                 | [23]                   |

can be ascribed to a oxygen poor phase in the insulator (es. Magneli phase in TiO<sub>2</sub>) that leads to d-orbitals overlap and hence metallic conduction. In this case the memory effect is classified as a valence change in the oxide and the ReRAM is usually called OxRRAM (Oxide Resistive RAM). Moreover, recently, has been shown that the oxygen vacancies concentration in the insulator can be controlled by an interfacial layer such as Ti or Zr greatly enhancing the performance of the ReRAM. In particular a switching speed of 10 ns and endurance of  $10^{10}$  was reported in [21] using Ti/HfO<sub>x</sub>. Hf/HfO<sub>x</sub> based ReRAM has been demonstrated to be scalable to 10nm (Fig. 1.7) [22]. The largest chip shows a density of 32 Gb and it was fabricated in 24 nm technology [23]. Tab. 1.2 provides a comparison of the fabricated memory arrays that represents a metric to define the grade of maturity of the different technologies. In this manuscript we focus on Electrochemical Metallization Cells, also called Conductive Bridge or Programmable Metallization Cells that is a topology of bipolar ReRAM. The most frequently studied Conductive Bridge RAM (CBRAM) uses Ag or Cu as electrochemically active metals and amorphous selenides and sulfide as well as various oxides, acting as electrolytes [24]. Tab. 1.3 shows the main characteristics of fabricated arrays based on 1T-1CBRAM (1T-1R) architectures. The first 6T-NVSRAM based on Ag/Zn<sub>0.4</sub>Cd<sub>0.6</sub>S CBRAM device was fabricated in 2006 [25].

Table 1.3: Characteristics of fabricated array with CBRAM technology.

| Company                                                    | NEC/JSTA                              | Quimonda            | Sony                           |  |

|------------------------------------------------------------|---------------------------------------|---------------------|--------------------------------|--|

| Tested array size                                          | 1kbit                                 | 2Mbit               | 4kbit                          |  |

| Technology Node [nm]                                       | 250                                   | 90                  | 180                            |  |

| Active Stack                                               | $\mathrm{Cu}/\mathrm{Cu}_2\mathrm{S}$ | Ag/GeSe or GeS      | $\mathrm{CuTe}/\mathrm{GdO}_x$ |  |

| Memory structure                                           | 1T-1R                                 | 1T-1R               | 1T-1R                          |  |

| $\overline{\text{Programming HRS} \rightarrow \text{LRS}}$ | 1 V, 5-32 us                          | 0.6 V, 10 uA, 50 ns | 3 V, 110 uA, 5 ns              |  |

| Erasing LRS $\rightarrow$ HRS                              | 1.1 V, 5-32 us                        | 0.2 V, 20 uA, 50 ns | 1.7 V, 125 uA, 1 ns            |  |

| Retention                                                  | 3 months                              | 10 years            | 10 years                       |  |

| Resistance Ratio                                           | 10                                    | $10^{6}$            | $10^{4}$                       |  |

| Operating temperature                                      | NA                                    | 110 °C              | 130 °C                         |  |

| Endurance                                                  | $10^{4}$                              | $10^{6}$            | $10^{7}$                       |  |

| Reference                                                  | [28]                                  | [29]                | [30]                           |  |

#### 1.3 Embedded nonvolatile memories

To meet the increasing demand for higher performance and lower power consumption in many different system applications, it is often required to have a large amount of embedded memory to support the need of data bandwidth in a system. The varieties of embedded memory in a given system range from static to dynamic, volatile to nonvolatile, one or many times programmable. Among various NVM technologies, floating-gate-based 1Tr-NOR flash has been the early technology choice for embedded logic applications. Along with the technology scaling several memories cells have been extensively explored, including alternative materials for the storage layers, different architectures and different programming mechanism.

#### 1.3.1 Mask-programmable ROM

For defined programs and data, which have no need of code-updating after manufacturing, embedded read-only-memory (ROM) provide a cost-effective and reliable solution for on-chip non volatile storage due to its small macro area, high reliability (data retention time) and process that does not require high voltage (HV) devices. There are three types of embedded mask-programmed read-only memories (ROM): NOR-ROM, NAND-ROM and flat-cell ROM. NOR-ROMs commonly appear in high-speed, small-capacity applications. NAND-ROM has the advantages of a small cell area, low power consumption, and a

small stand-by current. The flat-cell ROM is a popular solution for-low cost non high speed mid-capacity (1Mb - 32Mb) embedded applications due to its ultra-small cell area, and a logic compatible flat cell manufacturing process [31].

#### 1.3.2 Electrically programmable FLASH

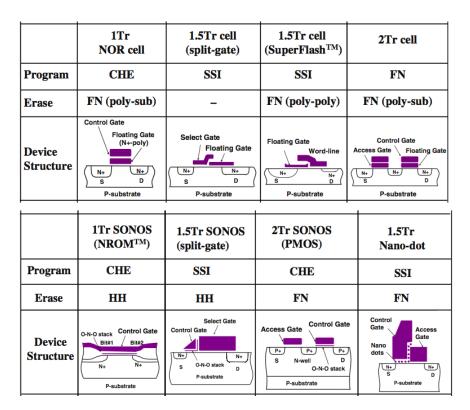

Electrically re-programmable, embedded non volatile memory technologies usually deviate from discrete memory technologies such as NOR and NAND flash memories, because of specific requirements like CMOS process full compatibility, low access time (up to 20 ns for automotive) for in place code execution, minimum area and power consumption. Moreover, the major constraint for embedded nonvolatile memory is minimum additional cost, including fewer process steps to the base CMOS logic [4]. The 1Tr-NOR cell structure has been widely used also for on chip code storage because of random access and reading latency of 70 ns with up to 10<sup>5</sup> times of program/erase covering different markets with different requirements from automotive to smart cards. The memory cell consists of a floating gate structure, which stores charge in the floating polysilicon gate to alter the threshold voltage of n-channel memory transistor. Nevertheless, the 1Tr-NOR floating-gate flash technology suffers from scalability issues beyond the 40 nm technological node. Innovations at the device level led to the introduction of Split gate memories 20 years ago. Fig. 1.8 shows different geometry for such memories compared to the 1Tr-NOR cell. Due to the process simplicity, high endurance (1M E/P cycles at 40 nm), and the use of low current source-side injection (SSI) (1 μA/bit and 40 pJ/cell) split-gate discrete charge-trapping cell with TG-first structure are widespread used for low power applications and in smart card. Accordingly to Silicon Storage Technology (SST), 45% of all smartcard devices uses SST SuperFlash Technology. New generations of SuperFlash are expected to be scalable beyond 40 nm and compatible with LV CMOS such as FDSOI, high-k metal gate and FinFET due to the read voltage between 0.9 V and 1.2 V allowing also high performance CMOS devices to be used for the read path.

**Figure 1.8:** Physical mechanism for program and erase and device geometry of 1Tr-NOR cell, split gates cell and Split gate memory technologies. Charge trap memories such as SONOS or nanodot based have been merged with split gate. It is presented the first generation of SuperFlash memories [4].

#### 1.4 Embedded volatile memories

#### 1.4.1 6T-Static Random Access Memories (6T-SRAM)

#### 1.4.1.1 Architecture of a 6T-SRAM

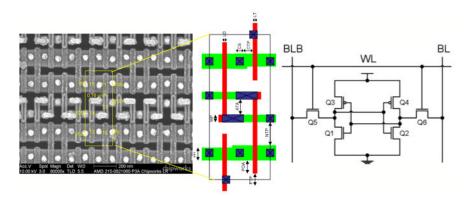

The storage element of an SRAM consists of two inverters and two access NMOS. A pair of inverters is cross-coupled such that it has the output of one inverter going into the input of the other and vice-versa. The CMOS cross-coupled inverters can hold a logical 1 or a logical 0 state as long as SRAM is powered up. SRAM elements are arranged in an array of rows and columns. Each row of bit cells shares a common word-line (WL), while each column of bit cells shares a common bit-line (BL)(Fig. 1.9). SRAM is used for the register file and caches memories of all levels from first to third in the embedded memory system, providing the highest random access speed (up to 500 GB/s) and a

**Figure 1.9:** TEM image of an array of 6T-SRAM. Layout of a 6T-SRAM cell. Schematic structure of the cell. Adapted from [32].

seamless integration with logic circuits due to its compatibility of process and operating voltage. As multiple processing cores are being integrated into one chip, the demand for integrated on-chip SRAM has become even higher to provide a sufficient data stream and to keep up with an increasing demand of memory capacity and bandwidth. In particular, the total percentage of occupied SRAM area of overall chip size is increasing and has been reached 70%. In 2008, a 128 Mb SRAM was typically implemented in an area of 100 mm<sup>2</sup> at the 45 nm process node (Fig. 1.10). In today's high-end CPUs there are more than 30 MB total of SRAMs that occupies over 70% of the total chip area.

#### 1.4.1.2 Scaling issues and power consumption

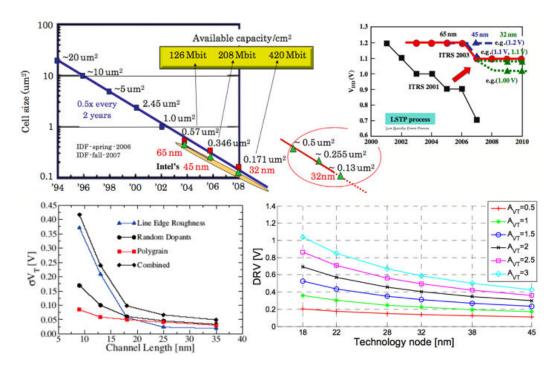

SRAM leakage has become very important with technology scaling for many reasons. In fact, since the geometry of the transistor keeps shrinking, higher leakage current in channel, gate and junction is measured. Leakage current can be limited using high-k MOSFET, FinFET or UTBB-FDSOI and/or reducing the nominal voltage. Nevertheless, the threshold voltage  $V_{\rm T}$  variability also becomes a problem (Fig. 1.10 left down). This is mostly caused by Random Dopant Fluctuations (RDF) in the channel region, but also by oxide thickness variation, Line Edge Roughness and TiN grains with different work functions. The relation between process related parameters is typically defined as the Pelgrom coefficient ( $A_{\rm VT}$ ), which is proportional to the magnitude of threshold voltage variation. Since the  $\sigma_{\rm VT}$  is also inversely proportional to the root square of the product of transistor size the SRAM becomes particularly susceptible to  $V_{\rm T}$  variability as it typically uses smallest possible transistors to increase density. As a consequence both

Figure 1.10: (Left up) SRAM memory cell scaling trend. (Right up) SRAM operating voltage scaling trend. (Left down) Standard deviation of threshold voltage variation vs channel length, for square planar bulk MOSFETs. Constant gate line edge roughness (4 nm) is assumed. (Right down) Data Retention Voltage (DRV) degradation vs. technology node for various Pelgrom coefficients  $A_{\rm VT}$  values. Adapted from [32].

the nominal voltage scaling and the Data Retention Voltage (DRV) scaling are limited by stability constraints (Fig. 1.10 right down). Stability is measured in terms of the Signal to Noise Margin. Obviously, SRAM power savings are particularly important for battery-operated mobile applications. Scaling of the supply voltage greatly minimizes active and leakage power. Hence, highly energy-constrained systems, where performance requirements are secondary, benefit greatly from SRAMs that provide a DRV at the lowest possible voltage, particularly down to 0.3 V (Fig. 1.10). Moreover portable applications have relaxed workloads for the vast majority time, but can provide bursts of high performance right after the power up thus techniques such as Dynamic Voltage Scaling and ultra-dynamic voltage scaling are employed.

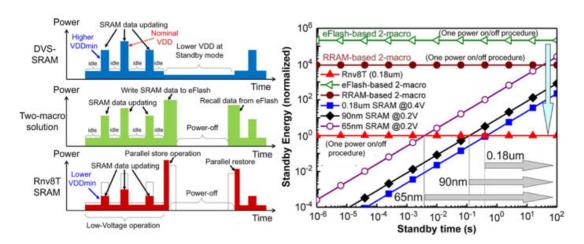

# 1.5 Embedded nonvolatile SRAM (NV-SRAM) for mobile applications

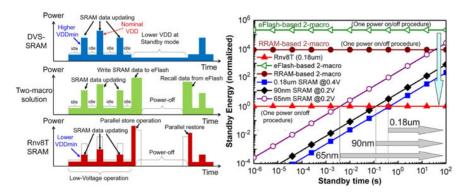

Many portable chips employ power management techniques such as dynamic voltage scaling (DVS) scheme or low supply voltage to reduce power consumption and extend battery lifetime [33]. These approaches reduce dynamic power and active-mode leakage current. Hence, low minimum operation nominal voltage single eNVM macros are needed for these DVS and low voltage devices. Unfortunately, many eNVM designs cannot achieve low  $V_{\rm DD}$  min due to read failure noises. In particular, the current mode sensing scheme, frequently used by embedded NVM, is not suitable for ultra low  $V_{\rm DD}$ operations. This is because the eNVM  $I_{\text{cell}}$  is small (< 1  $\mu$ A) at a low  $V_{\text{DD}}$  and the current-mode sensing scheme cannot increase the sensing margin with tradeoff in speed [31]. Additionally a large program current for channel hot electrons sets an obstacle in achieving low-power program operations. As a result eNVMs have become a bottleneck in achieving a lower  $V_{\rm DD}$  min for low voltage chips. For these reasons, serial Flash and SRAMs in a two macro approach are preferred to a single embedded NVM macro in low power mobile applications. Flash memory uses a serial interface SPI which sequentially accesses data. This solution lead to a reduction in board space, less power consumption contributing to lower overall system cost. The two macro scheme also reduces the number of NVM accesses and relaxes the endurance requirements for NVM; however, it requires long store and restore time due to serial SRAM read write and long NVM write read procedures. This results in long power off-on time thus requiring a power intensive task during the transfer operation limiting the battery life time (Fig. 1.11 left). Nonetheless, this operation implies a power gain if the stand-by operation operated at 0.2 V take an amount of time larger than 10<sup>3</sup> s as reported in Fig. 1.11 (right) for 65 nm CMOS technology. Moreover, since the DRV typically occurs in subthreshold, its value, among cells in the array, is highly affected by process variations (i.e. by the Pelgrom Coefficient, Fig. 1.10) that increase with scaling [4]. For these reasons a NV-SRAM that integrates SRAM cells and NVM devices within a single cell, forming a direct bit-to-bit connection in a 3D or vertical arrangement to achieve fast parallel data transfer and fast power on/off speed has been proposed. Various types of NVM devices, such as SONOS [34], FeRAM [12], MRAM [35], and ReRAM [33], have been employed in NV-SRAM macro so far, but the use of ReRAM is the most promising. In particular, a 16Kb HfO<sub>2</sub>

**Figure 1.11:** (Left) Power consumption of DVS-SRAM, two macro solution, and NV-SRAM (Rnv8TSRAM) during active and stand-by modes. (Right) Comparison of standby mode energy consumption [33].

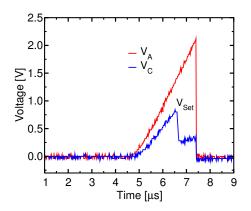

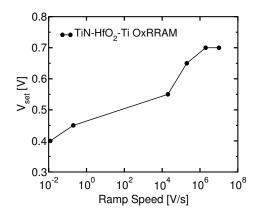

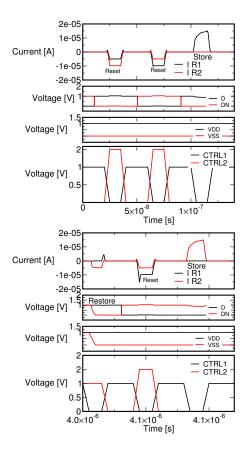

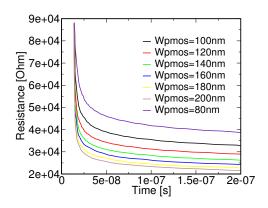

based OxRRAM chip demonstrated that power off-on procedure (including store and restore operations) contribute to power gain, if the corresponding stand-by operation take an amount of time larger than 2 ms. This feature mainly depends on the switching energy to set/reset the non volatile device and hence on the inherent logic (i.e the transistors in the latch). The HfO<sub>2</sub> based OxRRAM used in this NV-SRAM shows  $25 \,\mu\text{A}$  set/reset current, a set time of 1 ns at 3 V with a resistance ratio  $R_{\text{off}}/R_{\text{on}}$  of only 5 and a switching energy of 0.1 p J [33].

# 1.6 Field Programmable Gate Array (FPGA)

A Field Programmable Gate Array (FPGA) consists of programmable logic resources embedded in an array of programmable interconnections. The programmable logic resources can be programmed to implement any logic function, while the interconnects provide the flexibility to connect any signal in the design to any logic resource. The memory technologies for the logic and interconnect resources can be: static random access memory (SRAM), flash or antifuse. SRAM-based FPGAs offer reconfigurability at the expense of being volatile, while antifuse are One Time Programmable (OTP) devices. Flash-based FPGAs provide an intermediate alternative by providing reconfigurability as well as non volatility at the cost of scalability issues [36].

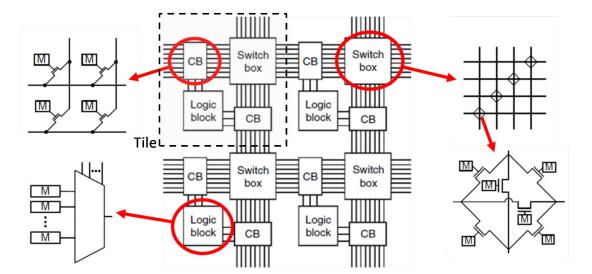

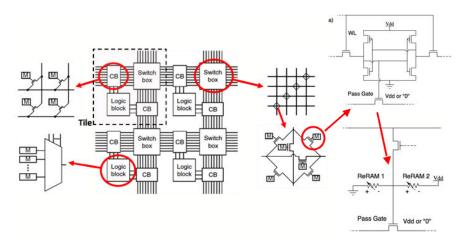

Figure 1.12: Structure of an island-type FPGA to show the periodic fabric. 6T-SRAM (M) controls both pass gates in Connection Blocks (CB) and Switching Blocks to define the general routing. Look up tables implemented with memories and multiplexer are used to store the result of a defined function.

FPGAs circuits are composed of switching blocks (SB), connection blocks (CB), logic blocks (LB) and embedded memories (Block memory). Every LB is formed by a group of basic logic elements (BLE). The most simple BLE includes a Look-up table (LUT) a D flip-flop (register) and a multiplexer.

A look-up table implements a truth table, that can be considered a function generator: in particular the truth table for a K-input logic function is stored in an array of dimension  $2^k \times 1$  constituted by 6T-SRAM cells or by Flash cells or antifuse cells. Considering the truth table of the logic function f = ab+c; if this logic function is implemented using a three-input LUT, then the SRAM would have a 0 stored at address 000, a 1 at 001 and so on, as specified by the truth table; clearly specific inputs are used to select the corresponding memory cell to define the output. During the run time the LUT outputs the result of the function; the D flip-flop saves the result temporarily and synchronizes it with the global clock.

The conventional structure of a D Flip-Flop includes two elements: Master and slave, which are both clock-controlled Latch. The master part is used to write the information in Flip-Flop and the slave part is used to output the information toward a multiplexer.

To build large logic structures, FPGAs use vertical and horizontal routing signals

in a matrix arrangement that are paired with switch boxes at intersections to support FPGA element interconnection. Switch boxes are located at the intersection of rows and columns. A switch box is used to route between the inputs/outputs of a logic block to the general on-chip routing network. The switch box is also responsible for passing or stopping signals from wire segment to wire segment. The wire segments can be short (span a couple of logic blocks) or long (run the length of the chip). All interconnections on FPGAs are active: pass transistors behave as switches thus the configuration memory controlling the pass transistors is distributed over the chip. Hence, every time a signal crosses a switch it suffers of the RC delay. This adds up quickly on long routes. Thus in FPGA there is a fundamental trade off in the amount of flexibility, speed, area and power consumption.

#### 1.7 6T-SRAM based FPGA

In 6T-SRAM based FPGA, 6T-SRAM cells are used as distributed configuration bits. Since 6T-SRAMs can be reprogrammed many times  $(10^{15})$  this architecture gives the highest grade of flexibility among FPGA types, at the cost of volatility. In fact, SRAM based FPGAs have to be configured every time the system is powered up. Configuration is the process of downloading configuration data into an FPGA using an external, usually on board, source such as a flash memory device.

The configuration bitstream is loaded at every power-up into the device through a configuration interface that links the external nonvolatile device with the FPGA. Modern FPGAs such as Xilinx 7 series offers both serial and parallel configurations. The highest throughput and speed is achieved with a parallel scheme, while the serial interface reduces the number of pins of the flash device and surface on the board. The Master Byte Peripheral Interface (BPI) flash configuration mode with a 16x data bus is widespread used as a parallel interface.

For this programming solution, the user configures the FPGA with a bitstream that serves as a bridge between the JTAG bus and the parallel NOR flash bus interface. This solution is referred to as indirect programming because the flash is not directly programmed but is programmed through the FPGA itself. This programming scheme is also used by ALTERA [37]. Using a synchronous read of the NOR flash at 100MHz and an external oscillator at 80MHz the configuration time for a 16Mb bitstream loaded

from a NOR Flash Memory to the FPGA is 126 ms [38]. This time is quite high for application that requires instantly on capabilities.

The maximum FLASH NOR density used by Xilinx in 7 series is 1Gb while ALTERA provides also external NAND Flash memories to achieve very high capacity (up to 16Gb).

At the board level (i.e not integrated on the FPGA architecture) emerging technologies have been introduced: Xilinx Nexys3 development board uses both 16 MB Parallel and Quad-mode SPI PCM.

#### 1.7.1 Power consumption in 6T-SRAM based FPGA

As the technology is scaled down, the oxide thickness  $t_{ox}$  in MOSFET is also shrunk. The scaling down of  $t_{ox}$  results in an exponential increase in the gate oxide leakage current. Moreover, to maintain the switching speed improvement of the scaled CMOS devices, the threshold voltage  $V_{\rm T}$  of the devices is reduced to keep a constant device overdrive.

Decreasing  $V_T$  results in an exponential increase in the subthreshold leakage current. As a result of the continuous scaling of  $t_{ox}$  and  $V_{th}$ , the contribution of the total leakage power to the total chip power dissipation is increasing even if the nominal voltage is decreasing.

The average leakage power dissipation of a typical 90-nm SRAM based FPGA at 25°C and 85°C, was calculated to be  $4.25\,\mu\,\mathrm{W}$  and  $18.9\,\mu\,\mathrm{W}$  respectively [36], for a utilization of a single CLB of the 75%. Hence, the leakage power dissipation for a 1000-CLB FPGA would be in the range of  $4.2\,\mathrm{mW}$ . If these FPGAs have to be used in a mobile application, which has a typical leakage current of  $300\,\mu\mathrm{A}$  then the maximum number of CLBs that can be used would be 86 CLBs for the 25°C and only 20 CLBs at 85°C.

Furthermore in [36], it was reported that for a 50% CLB utilization, 56% of the leakage power was consumed in the unused part of the FPGA. The consumption in the unused part of the FPGA is a recurrent problem in such type of architecture, that is the cost of flexibility. In fact almost 40% of the FPGA consumes stand-by leakage current without delivering useful output. Hence solutions to suppress leakage currents are strongly required.

Moreover, FPGAs used in wireless applications can go into idle mode for long periods of time [36]. In such designs, even the utilized resources need to be forced into a low-power (standby) mode during their idle periods to save leakage power. One of the most popular techniques used in leakage power reduction is multi-threshold CMOS (MTCMOS) [36]. In an MTCMOS implementation, a high- $V_T$  MOSFET called the sleep transistor connects the pull-down network using low- $V_T$  devices of a circuit to the ground. When the sleep transistor is turned OFF, the circuit subthreshold leakage current is limited to that of the sleep transistor, which is significantly low. Hence, the circuit benefits from the high performance of the low- $V_T$  pull-down network when the sleep transistor is turned ON, while limiting the circuit sub-threshold leakage current when the sleep transistor is turned OFF. This approach is utilized for CLBs but can not be used for the configuration bits in the programmable interconnect.

Moreover as reported in [39], 38% of the total leakage power in  $1.2\,\mathrm{V}$  SRAM-based FPGAs built in 90 nm CMOS process is due to the configuration bits distributed in the FPGA and continuously read during FPGA run time. Obviously, inside the routing resources the SRAM cells are designed using high- $\mathrm{V_T}$  to minimize the leakage that can vary between 10 and 100 pA for a nominal voltage of  $1.2\,\mathrm{V}$  on every single 6T-SRAM, thus there is a consistent research on the minimization of leakage at the device level and/or at the architecture level.

For example, at the device level the introduction of low power FinFET technology at the 16 nm technology node is foreseen by Xilinx for the 2014. FinFET, that replaces high-k 28nm CMOS technology in 6 series Xilinx, should enable a consistent diffusion in the mobile market, such as portable ultrasound equipment consuming less than 2 watts. Power consumption can be ascribed to five main components: Static power (leakage), Dynamic Power (frequency dependent), Power-up (inrush power), Configuration power, sleep mode power and can be calculated as:

$$P_{tot} = P_{logic,dyn} + P_{mem,dyn} + P_{net,dyn} + P_{clk,dyn} =$$

$$= P_{logic,dyn} + P_{mem,dyn} + \beta V_{DD}^2 f_{net} \sum_{allnets} C_{net} + C_{clk} V_{DD}^2 f_{clk} + I_{leak} V_{DD}$$

(1.1)

where  $P_{\text{logic,dyn}}$  is the dynamic energy consumed in the logic circuits (including the non configurable blocks),  $P_{\text{mem,dyn}}$  in the memory elements,  $P_{\text{net,dyn}}$  in the interconnection wires and  $P_{\text{clk,dyn}}$  in the clock network. The ratio between  $P_{\text{logic,dyn}}$ ,  $P_{\text{mem,dyn}}$ ,

$P_{\text{net,dyn}}$ ,  $P_{\text{clk,dyn}}$  is estimated to be 0.3:0.15:0.4:0.15 using Xilinx X-Power Tool [40]. Hence, the reduction of  $P_{\text{net,dyn}}$  should be targeted with the shrinking of the FPGA architecture by using new emerging integration schemes (such as 3D) that uses new emerging memories fully compatible with CMOS process flow.

The advantage in using 3D integration is the reduction of  $C_{net}$  and  $C_{clk}$  because memory can be stacked in the third dimension, thus achieving a smaller die area reducing the power consumption or improving the circuit speed at the same power. For example, in monolithical stacking, electronic components and their connections are lithographically built in layers on a single wafer.

The predicted advantage in using emerging memories is still a reduction of  $C_{net}$  and  $C_{clk}$  but also the suppression of the static power when the circuit is IDLE, with data kept in the SRAMs applying the data retention voltage (strongly dependent on the technological node and Pelgrom coefficient). Keep the information in volatile SRAM/DRAM is essential to have a fast loading in the CPU of the last context saved in the memory. Thus, providing a massively parallel and fast bit transfer from nonvolatile memories to the logic, every IDLE operation can be avoided and substituted with a power off thus potentially reducing the power consumption. We used the term potentially because also the contribution of static power consumption during circuit activity should be analyzed and is strongly dependent on the architecture implemented for the configuration bits as will be explained in Sec. 1.9.

## 1.8 FPGA in mobile applications

In section 1.7.1 we have claimed that historically FPGA are not suitable for mobile applications, because of the very large power consumption and area. In fact, aggressive mobile applications require an on-chip nonvolatile memories with ideally zero stand-by current, minimum area and scalable with the same trend as the MOSFETs. Moreover a sufficient bandwidth to support execute in place operation thus avoiding shadowing the context in to DRAMs and enough storage capacity is also required. In the last years, one solution for mobile applications was provided by antifuse FPGA. Unlike SRAM-based devices, which are programmed by the user himself, antifuse-based devices are programmed directly by the foundry. In the 2T architecture used in Antifuse based FPGA the circuit is in high resistive state to begin with and is programmed by

applying electrical stress that creates a low resistance conductive path. These FPGAs are nonvolatile, do not require external Flash and are radiation tolerant. State of the art ultra power 40 nm FPGA, proposed by Lattice Semiconductor (SiliconBlue), consumes 42 µW in stand-by at the nominal voltage of 1.2 V. Dissipation is mainly due to the 640 logic cells (i.e. BLE 4 input LUT and Flip-Flop) and 32Kb of volatile RAM [41]. A One Time Programmable (OTP) based memory is used inside this FPGA. OTP antifuse non volatile memories are scalable till 20 nm, show densities up to 32 Mb and depending on the capacity and the size of the boot code multiple programming cycles can be obtained. In fact, though Antifuse is an OTP, it can emulate a Multiple Time Programmable MTP for a few cycles of endurance. In fact, 1Mb memory can be chosen if 128Kb of code may need to be updated up to 8 times in the field [42]. The area of an OTP memory is  $0.8 \,\mathrm{mm^2}$  for 1 Mb density. State of the art OTP memories are slower than SRAM, DRAM, or even plain old ROM, but they are usually fast enough to allow firmware to execute in place (XIP), without copying the code into DRAM and in some cases even skip the SRAM based L2 Cache. Memory array connects to the system over a 32-bit parallel interface that runs synchronously with the on-chip bus, so it's four times faster than quad serial flash memory or serial EEPROM, giving 40 ns as random access time. Besides the low endurance, the OTP requires an internal charge pumping thus increasing the area consumption.

Flash-based FPGAs are similar to their SRAM counterparts in that their configuration cells are connected together in a long shift-register-style chain. These devices can be configured off line using a device programmer or by the user. State of the art Flash based FPGA are commercialized by Microsemi. In IGLOO nano FPGA a 130 nm, 7 metal layers, Flash-based CMOS process is used. This FPGA consumes only 5 µW in stand-by at the nominal voltage of 1.2 V with 10k LUT and FF [43]. Microsemi flash-based IGLOO nano allows 1us instant on. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. Others solutions are instead optimized to operate reactively or periodically. Rapid stopping and starting of the FPGA fabric and related IOs while preserving the state of the FPGA fabric is possible with Flash-based FPGA. In State of the art technologies 100 us are requested to enter in or exit from the sleep mode, moreover only 1 mW in sleep mode and 10 mW static power dissipation during operation of 50 K LUT and FF are

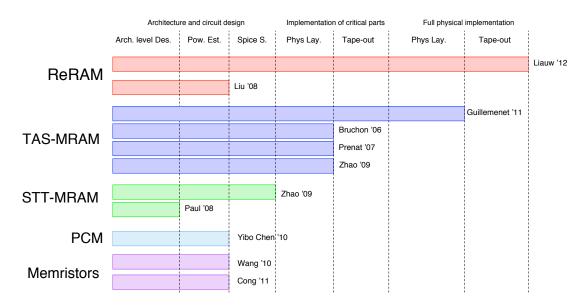

**Figure 1.13:** Grade of maturity in the process flow for many hybrid NVM FPGA with different technologies (adapted from [46]).

achieved. The main concerns related to the integration of Flash on chip are related both to the Flash cells that require high quality tunnel oxide, interpoly dielectric and two polisilicon layers (control gate and floating gate) that require additional thermal budget. Moreover high voltage transistors are required. Hybrid technology: SRAM and Flash have also been fabricated. State of the art Lattice XP2 FPGA offers instant-on and non volatility of Flash and the reconfigurability of SRAM in one chip [44]. Densities from 5K to 40K with 4-input Look-up Tables (LUTs) and instant on (1 ms) are achieved. Update logic configuration while equipment continues to operate is possible, thus giving the flexibility to load a new bitstream when the processor is running. This FPGA consumes  $102\,\mu$ W in stand-by at the nominal voltage of  $1.2\,\text{V}$ . Usually the Flash architecture is a NOR but also NAND is available [45].

## 1.9 Hybrid architectures: FPGA and ReRAM

The improvement of FPGA performances by using nonvolatile emerging memories is gaining importance in recent years and can be considered one of the key features of this thesis. The possibility of integrating memory and logic in a distributed way without silicon area overhead will give rise to disruptive hybrid architectures both inside the

#### 1. INTRODUCTION

FPGA BLE (such as: nonvolatile Flip-Flop [47] [18] or nonvolatile Look-up-Table) and/or in the routing resources (SBs or CBs). By stacking emerging memories with CMOS devices, new routing switches can be achieved to reduce FPGA area, remove external Flash, thus reducing board area and obtain instantly-on capability. As a consequence we expect to reduce the power consumption related to the in-rush and SRAM reconfiguration after power up, and dynamic power consumption due to the area shrinking (Sec. 1.7.1). In [48] it is estimated that a 3D-FPGA with the configuration memory stacked on top of FPGA logic and routing can achieve 57% smaller area than a baseline 2D-FPGA in 65nm CMOS technology. It is shown that the size of the configuration memory cell plays a key role in the degree of performance improvement achieved by a monolithically stacked 3-D FPGA. For a memory cell that is <0.7 the area of an SRAM cell, a 3D-FPGA can achieve 3.2 times higher logic density, 1.7 times lower critical path delay, and 1.7 times lower total dynamic power consumption than the baseline 2-D FPGA at the 65-nm technology node. The size of the configuration memory is determined by the design rules of the specific process design kit and usually is larger than the physical dimensions of the plug or the via between metal lines (Fig. 4.9 left). Fig. 1.13 shows the grade of maturity of hybrid FPGA architectures. A full physical implementation was demonstrated in [49], using a novel architecture to replace 6T-SRAM based configuration cells that will be explained in Sec. 1.9.2.

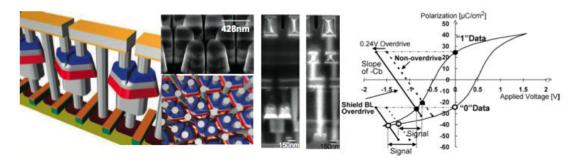

#### 1.9.1 ReRAM in switching blocks: 2T-1ReRAM architecture

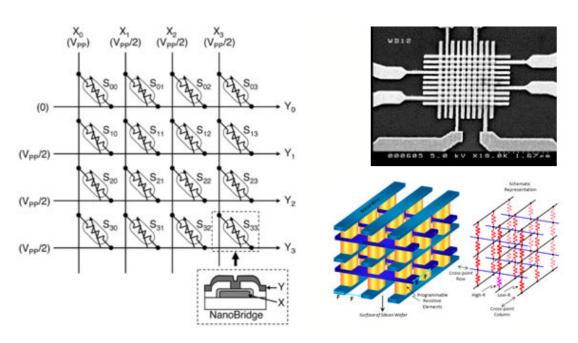

As described in Sec. 1.6 currently used CMOS routing switch consist of a pass transistor controlled by a 6T-SRAM cell to provide the routing function. The 2T-1R switch utilizes a ReRAM cell in the signal path removing both the 6T-SRAM and the pass gate. The main advantage of this solution is the area gain, from  $120F^2$  to  $4F^2$  and the reduced RC if the ReRAM resistance in the low resistive state is below the on resistance of the pass gate  $(1 \text{ k}\Omega)$ . Nonetheless, speed gain saturation is obtained since repeater buffers for driving interconnect circuit have on-resistance of order of  $1 \text{ k}\Omega$  thus limiting the delay reduction [50]. The architecture that has been introduced using the 2T-1R structure is called crossbar. This architecture is composed of a bistable memory element (typically a ReRAM, Sec 1.2.4) embedded by two sets of parallel conductive interconnects crossing perpendicularly (Fig. 1.14). The crossbar architecture is programmed by applying voltage pulses to horizontal and vertical lines. In Fig. 1.14

switch  $S_{00}$  can be programmed to be on by applying  $V_{PP}$  to  $X_0$ , grounding  $Y_0$  and applying  $V_{\rm PP}/2$  to the other lines, where  $V_{\rm PP}$  is the programming pulse for the ReRAM and has to be greater than the threshold to have the switching for a defined pulse width.  $V_{\rm PP}/2$  is less than the threshold. Since the voltage difference between the two terminals of  $S_{00}$  would become  $V_{PP}$ ,  $S_{00}$  will be turned on. With respect to all the other switches, since the voltage difference for them would be  $V_{\rm PP}/2$  or zero their states will not change [28]. ReRAMs that do not show high non linearity between the off and the on state can be used to implement such architecture if the crossbar does not exceed a specific density (i.e the power consumption due to the leakage in the off path is acceptable). For instance a 32×32 crossbar has been fabricated leading to a 72% reduction in chip area [51]. Moreover, the programming conditions used to switch the ReRAM must be carefully chosen, because the amount of current that can flow after the programming time and before the end of the pulse can lead to an important power consumption. The choice of the programming conditions is even more difficult because the time required to program ReRAM devices usually follows a statistical distribution, thus the pulse width should cover the worst case with consequences on the power consumption ([28] and Sec. 2.3). Finally, it is worth to note that with this solution the programming current and the signal trasmission current share the same path. Thus, during the programming stage, the programming voltage propagates to the other circuits connected to the routing switch, which might cause degradations and failures [52]. Some studies [53], [54] propose also the use of crossbar arrays for high density storage applications without integrated bipolar diode. In this case several constraints relies on the switching device that must exhibits  $R_{\rm on}$  higher than M $\Omega$ , non linearity, and a sufficient  $R_{\rm off}/R_{\rm on}$  ratio.

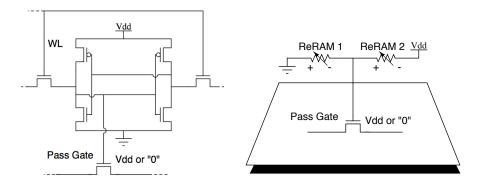

#### 1.9.2 ReRAM in switching and logic blocks: 1T-2ReRAM architecture

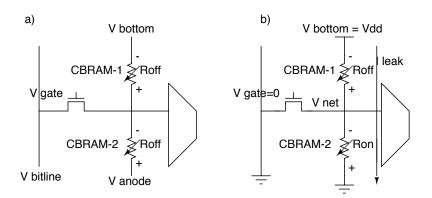

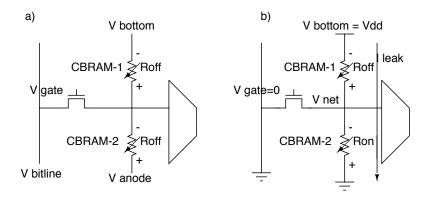

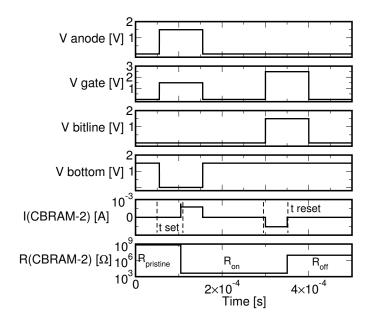

In [47], [49], [55] the 6T-SRAM cell is replaced by a structure consisting of one transistor and two ReRAM cells in a voltage divider configuration (1T-2R NVE) to control the pass gate or to store the data in a Look-Up Table (Fig. 1.15). Compared to the 6T-SRAM routing switch, 1T-2R NVE switch leads to a density enhancement, since the two ReRAM cells can be easily integrated between two metal levels in a standard CMOS process flow. In [49] it was demonstrated that a 3D-FPGA with stacked configuration memory, based on ReRAM technology, can achieve up to 40% smaller die area and

**Figure 1.14:** (Left) Crossbar switch [28]. (Right) TEM image and schematic of a 48nm  $\times$  48nm crossbar architecture.

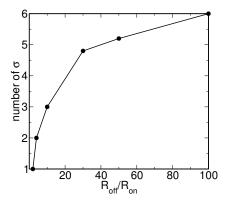

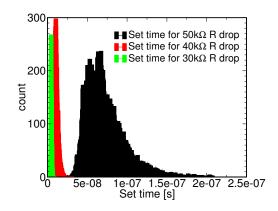

up to 28% lower energy delay product than a baseline 2D-FPGA. Smaller area also allows a reduction of the interconnection capacitance thus reducing the dynamic power consumption and enabling same operational speeds at lower power [56]. Although the 1T-2R NVE solution eliminates stand-by power consumption, the leakage current through the ReRAM during run time (i.e. in continuous read operation) depends on the resistance of the high resistive state. Maximizing the high resistive state is essential to reduce the static power consumption during FPGA run time. Hence, materials engineering and/or specific programming conditions (compatible with logic) are required to provide a competitive solution with respect to SRAM based FPGA. In particular in [49] an optimized ReRAM stack composed of nitrogen-doped  $AlO_x$  was adopted showing sub-μA programming currents, 10 years retention at 125 °C, 10<sup>5</sup> switching cycles, and an  $R_{\rm off}$  of  $1{\rm G}\Omega$  (Fig. 4.13). Our research to satisfy the aggressive requirement on  $R_{\rm off}$ will be discussed in Chap. 3. In 6T-SRAM leakage current strongly depend on  $V_{\rm th}$ , the oxide thickness, and the feature size and vary in the range of pAs [57], [58]. This implies that an  $R_{\rm off}$  value higher than  $10^{12}\,\Omega$  at a read voltage of 1 V should be targeted to reduce the power consumption during FPGA run time.

**Figure 1.15:** Configuration memory on a pass gate to establish connectivity between Logic blocks. (Left) 6T-SRAM based. (Right) 1T-2R based with Nonvolatile Voltage divider Element (NVE) using bipolar ReRAMs.

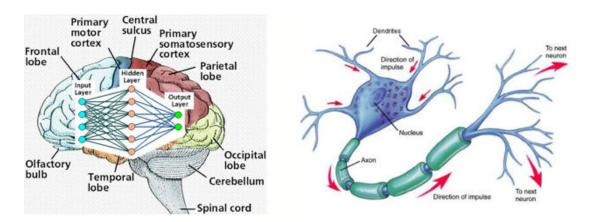

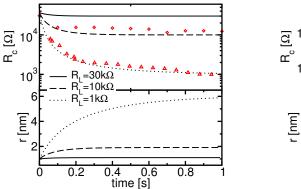

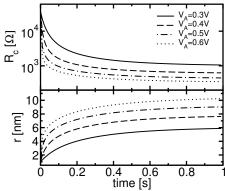

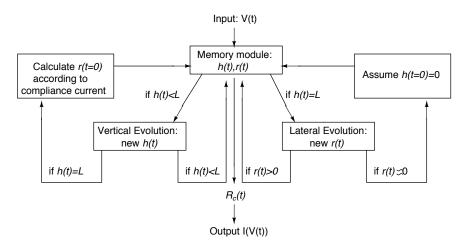

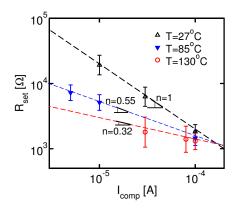

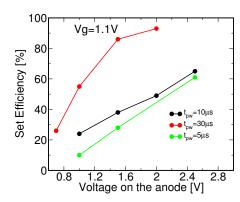

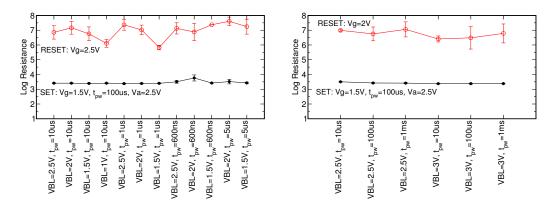

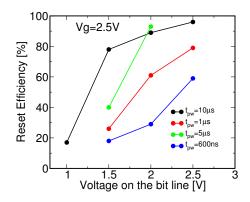

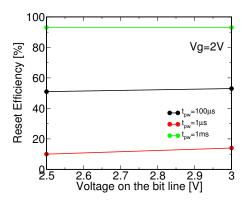

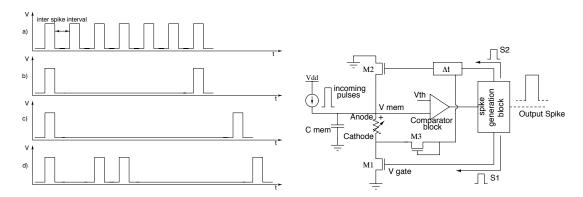

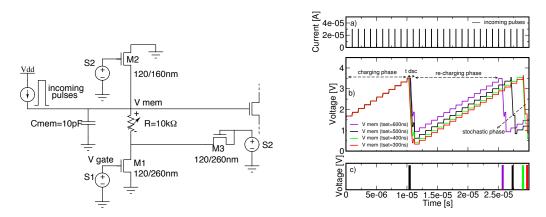

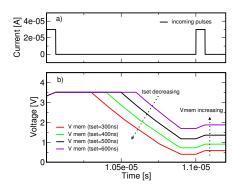

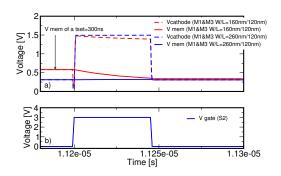

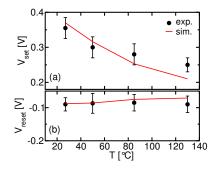

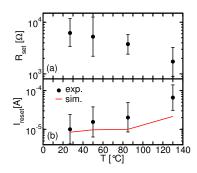

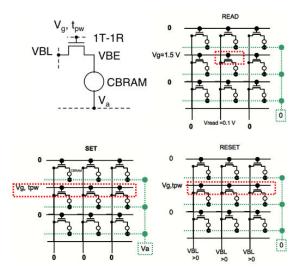

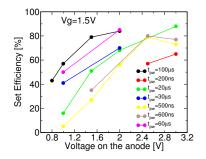

#### 1.10 Main concepts on stochastic neural networks