## Caractérisation, mécanismes et applications mémoire des transistors avancés sur SOI

Sungjae Chang

#### ► To cite this version:

Sungjae Chang. Caractérisation, mécanismes et applications mémoire des transistors avancés sur SOI. Autre. Université de Grenoble, 2013. Français. NNT: 2013GRENT056. tel-00951428

## HAL Id: tel-00951428 https://theses.hal.science/tel-00951428

Submitted on 24 Feb 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

## THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Nanoélectronique et Nanotechnologies

Arrêté ministériel : 7 août 2006

Présentée par

## Sungjae CHANG

Thèse dirigée par **Sorin CRISTOLOVEANU** et codirigée par **Maryline BAWEDIN**

préparée au sein du Laboratoire IMEP-LAHC dans l'École Doctorale EEATS

# Caractérisation, mécanismes et applications mémoire des transistors avancés sur SOI

(Characterization, mechanisms and memory applications of advanced SOI MOSFETs)

Thèse soutenue publiquement le **28 Octobre 2013**, devant le jury composé de :

Olivier BONNAUD Professeur, Université de Rennes (Président, Rapporteur) Jean-Luc AUTRAN Professeur, Université de Aix-Marseille (Rapporteur) Jean FOMPEYRINE Directeur du Laboratoire, IBM Zurich (Membre) Thomas ERNST Ingénieur de Recherche, CEA-LETI (Membre) Maryline BAWEDIN Maître de Conférences, Université de Montpellier II (Membre) Sorin CRISTOLOVEANU Directeur de Recherche CNRS, Grenoble INP (Membre)

Characterization, Mechanisms and Memory Applications of Advanced SOI MOSFETs

### **General Introduction**

For several decades, the goal of the semiconductor industry was to scale down the transistor size in order to increase integration density. But, the era of planar bulk-silicon CMOS is over. According to the International Technology Roadmap for Semiconductors (ITRS), there are two options for the next generations of CMOS circuits: fully depleted (FD) SOI (strongly supported in Grenoble by STMicroelectronics, Soitec, LETI and our laboratory) and FinFETs. These transistors will continue the miniaturization trends while also answering the requirement for low-power operation in portable electronic devices and embedded systems. The association of the legendary players (Si and SiO<sub>2</sub>) with alternative semiconductors and dielectrics is equally envisioned for enriching the device functionality. A transistor can do more than just switching on and off.

In this context, the initial topic of this thesis was to explore innovative single-transistor memory devices fabricated with FDSOI and FinFET technologies. Our results on nonvolatile and volatile data retention are exposed in Chapters 4 and 5, respectively. We show how the transistor can store the charge and evolve into multi-bit flash memory and capacitorless DRAM. A novel concept of unified memory is demonstrated by advantageously combining these two memory modes.

The key mechanism enabling memory functions is the inter-channel coupling, mitigated by floating-body, short-channel and transport effects. For achieving our objectives, the PhD work has started with a detailed investigation of coupling and associated effects in state-ofthe-art MOSFETs (Chapter 2). Our results in section 2.1 reveal the operation of FDSOI transistors by focusing on the impact of ultrathin SOI films (down to 5 nm thickness), backgate biasing and low temperature. A similar study was conducted for FinFETs. In Section 2.2, we describe the role of the fin width and channel length. It is demonstrated that the 3D coupling mechanisms are different in triple-gate and double-gate FinFETs, the latter devices being more amenable to back-gate biasing schemes.

Since ZnO TFTs operate very much like SOI MOSFETs, we have attempted to apply the same methodology to these emerging devices as well. We have faced modeling and parameter extraction issues that were solved as described in Section 2.3.

It is less notorious that the inter-channel coupling does affect the carrier mobility behavior. For obtaining an accurate picture, our approach aimed at using the most indisputable technique for mobility evaluation which is the geometric magnetoresistance. As this topic revealed to be very interesting and intriguing, we have developed the method for the characterization of FinFETs. The experimental data shown in Chapter 3 points on the failure of the 'universal mobility' law in both FDSOI and FinFETs.

Our work combines systematic measurements, numerical simulations and physics based models extending from the transistor to the memory device.

## **Table of Content**

#### **General Introduction**

#### **Chapter 1: General Introduction**

- 1.1. Context of the Work

- 1.2. Silicon on Insulator Technology

- 1.2.1. Motivations of SOI transistor

- 1.2.2. Classical classification of SOI devices

- 1.3. Impact of Miniaturization on Transistor Performance

- 1.3.1. Series resistance effects

- 1.3.2. Velocity saturation

- 1.3.3. Short-channel effects

- 1.4. Advanced Device Architecture and Technology

- 1.4.1. High-K/Metal gate stack

- 1.4.2. Strain technology

- 1.4.3. Planar fully-depleted (FD) SOI transistor

- 1.4.4. 3-Dimensional fully-depleted (FD) SOI transistor

- 1.5. Conclusion

#### **Chapter 2: Advanced Devices and Typical Effects**

- 2.1. Typical Properties in FD SOI MOSFETs

- 2.1.1. Introduction

- 2.1.2. Parameter extraction techniques and typical properties

- 2.1.3. Si film and BOX thickness effects

- 2.1.4. Coupling effect

- 2.1.5. Temperature-dependent properties

- 2.1.6. Conclusion

- 2.2. Coupling Effects in Double-Gate FinFETs

- 2.2.1. Introduction

- 2.2.2. Typical properties

- 2.2.3. Coupling effects

- 2.2.4. Conclusion

#### 2.3. Mobility Behavior and Models for Nanocrystalline ZnO TFTs

- 2.3.1. Introduction

- 2.3.2. ZnO TFT overview

- 2.3.3. Typical properties of our ZnO TFTs

- 2.3.4. Parameter extraction methods

- 2.3.5. Temperature-dependent characteristics

- 2.3.6. Conclusion

## Chapter 3: Magnetoresistance Measurements and Unusual Mobility Behavior in FD SOI MOSFETs

- 3.1. Introduction

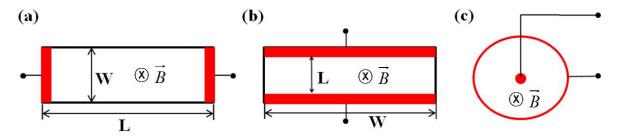

- 3.2. Theory of Magnetoresistance Mobility

- 3.3. Magnetoresistance Mobility in Planar FD SOI MOSFETs

- 3.3.1. Front-channel mobility

- 3.3.2. Back-channel mobility

- 3.4. Magnetoresistance Mobility in FD SOI Triple-gate FinFETs

- 3.4.1. Front-channel mobility

- 3.4.2. Back-channel mobility

- 3.5. Magnetoresistance Mobility in FD SOI Double-gate FinFETs

- 3.6. Conclusion

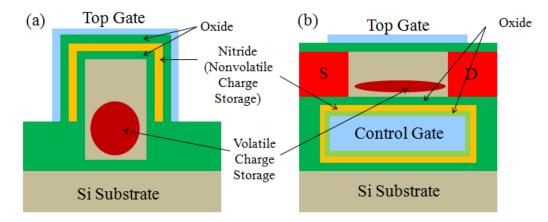

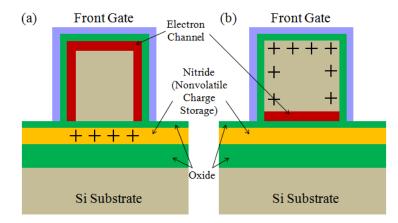

# Chapter 4: Remote Carrier Trapping in ONO FinFETs for Innovative Flash Memory

- 4.1. Introduction

- 4.2. Nonvolatile Memory

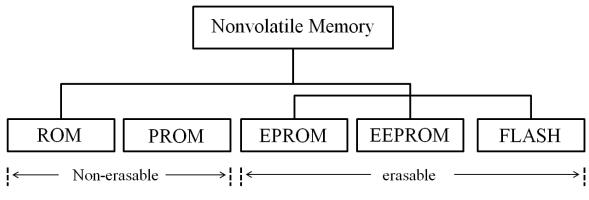

- 4.2.1. Classification of nonvolatile memory

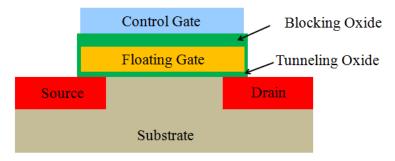

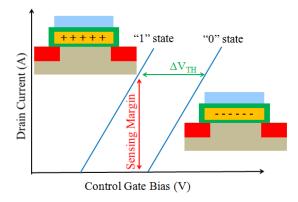

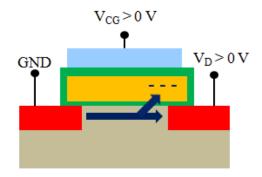

- 4.2.2. Flash memory cell

- 4.2.3. Future evolution of flash memory cell

- 4.2.4. Alternative nonvolatile memory

- 4.3. Charge Trapping in Si<sub>3</sub>N<sub>4</sub> Buried Layer

- 4.4. Nonvolatile Memory Effects

- 4.4.1. Nonvolatile memory effects induced by back-gate bias stress

- 4.4.2. Nonvolatile memory effects induced by drain bias stress

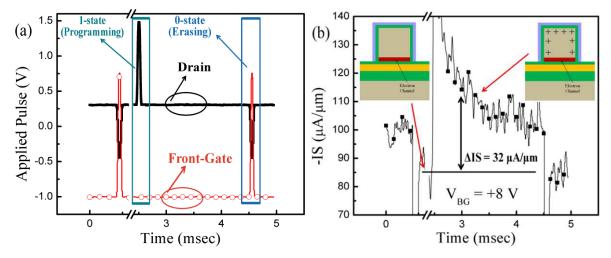

- 4.4.3. Drain current hysteresis in dynamic mode

- 4.5. Conclusion

#### **Chapter 5: FinFETs with ONO BOX for Multi-Bit Unified Memory**

- 5.1. Introduction

- 5.2. Volatile Memory

- 5.2.1. Conventional volatile memory

- 5.2.2. Capacitorless 1T-DRAM

- 5.2.3. Unified RAM (URAM)

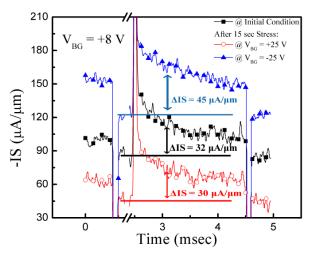

- 5.3. Volatile Operation as a Capacitorless 1T-DRAM

- 5.3.1. Multi-bit volatile operation combined with back-gate biasing

- 5.3.2. Multi-bit volatile operation combined with drain biasing

- 5.4. Conclusion

#### Conclusion

#### References

#### **Publications**

#### Résumé du Travail de la Thèse en Français

#### Acknowledgement

Chapter 1: General Introduction

# Chapter 1

# **General Introduction**

#### 1.1. Context of the Work

The number of circuit components on a microchip has sharply increased and the performance of a unit transistor has improved substantially thanks to the successful shrinking of bulk-Si MOSFETs (metal-oxide-semiconductor field effect transistors) since J. Kilby invented the concept of an integrated circuit (IC) in 1958. The scaling of the CMOS technology has followed "Moore's Law": In 1965, G. Moore anticipated that the IC device packing density will double every 18 months [1]. Moreover, C. G. Hwang suggested a new model for the memory industry: a two fold increase per year in memory density [2]. For the last forty years, silicon-based transistor has tracked these laws without any major change of the basic planar MOSFET structure. This architecture has been scaled down to gate length of  $L_G \approx 20$  nm by involving more complicate and precise fabrication process.

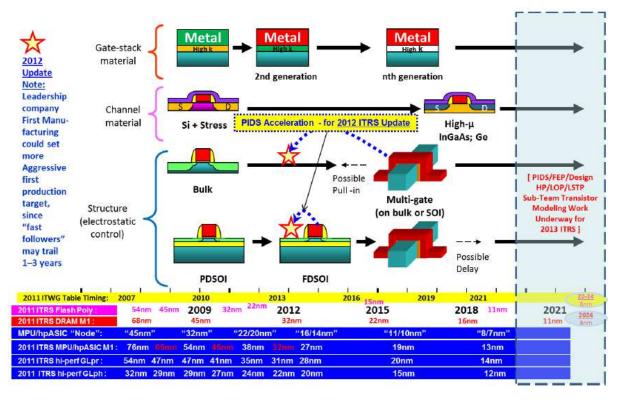

Recently, however, such scaling has been slowed down because the conventional CMOS process has researched critical limits. For example, the complex doping profiles cause reliability, yield and cost issues. The unavoidable randomness of dopant atoms produces variations in device properties. Indeed, in a conventional bulk-Si CMOS technology, there is no additional methodology to enhance performance beyond the 22 nm technology node. Therefore, many technical solutions have been proposed to optimize the existing structures or to introduce new architectures for further scaling the transistor. According to the ITRS transistor architecture roadmap shown in Fig. 1-1 [3], two main candidates are considered in order to enable continued CMOS scaling: (i) the planar fully depleted (FD) SOI MOSFET with a thin buried oxide (BOX), thin silicon film ( $T_{si}$ ) and heavily doped ground plane (GP) [4]; (ii) the (bulk-Si or SOI FD) FinFET with simplified 3D processing [5, 6]. Both structures provide high device performance and improved gate control.

Planar FD SOI MOSFET has evolved from the initial partially depleted SOI MOSFET technology. The fabrication process of the SOI device is rather similar to that of the conventional bulk-Si MOSFETs. Nevertheless, it offers excellent device performance. The device scalability and undesired parasitic effects are mainly governed by the thickness of silicon film and buried oxide. The GP (or substrate) bias  $V_{BG}$  can be an additional option to modulate the front-channel properties. Recently, A. Khakifirooz *et al.* [7] reported outstanding results in ultra-thin film ( $T_{si} = 3.5$  nm) and short (down to 18 nm) device: good gate control, low off-state current ( $I_{OFF}$ ) with reasonable on-state current ( $I_{ON}$ ) and threshold voltage  $V_{TH}$  tuning by back-gate bias  $V_{BG}$ . Also, C. Fenouillet-Beranger *et al.* [8] described

more viable characteristics of FD SOI device with thin BOX ( $T_{BOX} = 20$  nm). Obviously, these recently developed nanoscale SOI MOSFETs imply short-term feasibility of the SOI planar device in CMOS applications.

Fig. 1-1: ITRS transistor architecture roadmap. "Equivalent Scaling" process technologies Timing, MPU/Highperformance ASIC Half Pitch and Gate Length Trends, and Industry "Nodes".

FinFET is more revolutionary and has more potential than planar FD SOI MOSFET from a long-term perspective. This novel structure was invented in 1991 by folding the planar MOSFET [5] and was further developed after 2000. This 3-D architecture requires etching process to define the fin but the overall fabrication sequence is not far from that of the planar MOSFETs. Basically, the FinFET has two lateral gates (*i.e.*, double-gate (DG) device). A third gate can also be switched on at the top of the fin. By co-operation of the three gates, good electrostatic control is achieved. Actually, Intel Corporation announced that FinFETs, or so-called triple-gate transistor [9, 10], are already adopted for their 22 nm technology node. Despite Intel uses bulk-Si substrate, scaling FinFETs down to 10 nm will probably demand SOI substrate. Recent works on FD SOI FinFET architecture reported promising performance for next generation CMOS circuits.

This thesis is dedicated to theoretical and experimental researches of several advanced

SOI FD MOSFETs. Electrical characterization, modeling and simulation were carried out in order to investigate the device properties, physical mechanisms and appropriate applications.

The first chapter will briefly cover SOI technology, short-channel effects (SCEs) and the technologies to improve device performance. The advanced planar FD SOI and FinFET architectures will also be introduced.

In the second chapter, the properties of several advanced FD SOI devices will be investigated and discussed. In planar FD SOI device, the impact of temperature, back-gate bias and Si film thickness on device performance will be presented through systematic measurement results. Next, the characteristics of advanced SOI FinFETs will be shown via measurement and 3-dimensional simulation results. Especially, coupling effect will be reported for a various range of fin width in vertical DG and triple-gate FinFETs. Particular mobility behavior in ZnO thin film transistor (TFT), which operates similarly to an SOI MOSFET, will also be shown through low-temperature measurements. Simple mobility models and parameter extraction techniques will be introduced.

In the third chapter, mobility behavior will be addressed by way of low-temperature geometrical magnetoresistance measurement in advanced planar FD SOI and FinFET. Unusual mobility behavior is demonstrated to be induced by the inter-action between frontand back-gate based on the variation of the inversion charge centroid.

In the forth chapter, flash memory application will be explored in FinFETs fabricated on alternative SOI wafers with ONO BOX. In the first part, the basic device characteristics will be introduced. Then, appropriate charge injection mechanisms will be reported for a various range of the fin width, gate length and temperature. The impact of bias condition on the charge injection efficiency will also be discussed.

In the final chapter, we will describe the capacitorless DRAM application with the same device used as in chapter 4. Therefore, we will see that two different memory functions, volatile and nonvolatile, can be performed in a single transistor. Above all things, multi-bit volatile memory is demonstrated by advantageously combining the nonvolatile and volatile memory modes. Experimental results reveal the impact of the geometrical parameter and bias condition on the volatile memory sensing margin.

#### 1.2. Silicon on Insulator Technology

In a conventional bulk wafer, the thickness of active area (~ 10-100 nm) used for

fabrication and operation of the transistors is very small compared to the total wafer thickness (~ 800  $\mu$ m). Unfortunately, the unused part of wafer, which serves as mechanical support, causes parasitic effects, degrading device performance. On the other hands, silicon-on-insulator (SOI) technology consists of a single crystalline Si film (active area) separated by SiO<sub>2</sub> layer or buried oxide (BOX) from the bulk substrate, reducing parasitic capacitance and leading to faster transistor switching [11, 12]. Beyond these benefits, there are many other motivations for utilizing SOI technology.

#### 1.2.1. Motivations for SOI transistor

Historically, there have been several reasons for developing and using SOI technology. In the 1970s and 1980s, radiation hardness was the main motivation for choosing SOI substrate. The impact of ionizing radiation on device performance is minimized by the thin active Si film. For example, the majority of charges generated by an alpha particle encroaching on a Si substrate would be stopped by the buried oxide, hence reducing the current surge in the active film [11].

Recently, ultra large scale integration circuits (ULSIC) contain hundreds of millions of single transistors. In SOI technology, a single transistor is isolated from each other and from the silicon substrate. On one hand, the thin silicon film used as active area is protected by the vertical isolation from parasitic effects induced by bulky substrate: leakage currents, latch-up effects and radiation-induced photocurrents. On the other hand, the lateral isolation enables the separation of transistors by completing simple trench or well formation. Therefore, the entire technology and circuit design are significantly simplified and more compact chips can be obtained.

In addition, many semiconductor companies use SOI wafers in order to obtain high performance and low power consumption. Source and drain regions extend down to the buried oxide (BOX), achieving reduced junction capacitance and lower leakage current. As a result, SOI CMOS circuits offer improved speed and lower power dissipation in standby and operating modes.

The main advantage of SOI technology is the superior ability for the device scaling down. Unlike for the bulk technology, the SOI film and BOX thickness are tunable elements for device shrinking. Ultra-thin film SOI devices are less susceptible to SCEs originated from charge sharing between gate and junctions due to the limited extension of drain and source regions. The drain-to-body field which causes drain-induced barrier lowering (DIBL) effect is also controlled by the thin silicon film. In parallel, SOI structure can be easily combined with innovative device, especially multi-gate transistor, to achieve better immunity against the SCEs.

#### 1.2.2. Classical classification of SOI devices

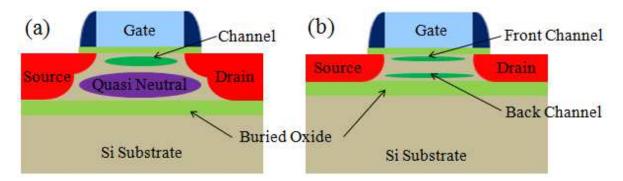

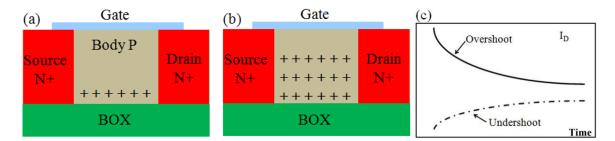

According to the Si film thickness, the depletion region covers partially or completely the whole transistor body giving the names of partially-depleted (PD, Fig. 1-2a) and fully-depleted (FD, Fig. 1-2b) SOI MOSFETs, respectively.

#### (a) Partially-depleted (PD) SOI MOSFETs

In PD SOI MOSFETs, a neutral region exists in the transistor body as the film is not completely depleted. Therefore, coupling effects (modulation of the electrical properties of one channel by the applied bias at the opposite gate) disappear but floating-body effects arise. The kink effect is generated by collecting majority carriers in the neutral body. As a result, the body potential is increased, the threshold voltage is decreased and excess current is exhibited. The floating body also causes transient variations of body potential, threshold voltage and current. Current undershoot is generated when the gate is changed from strong to weak inversion: the drain current increases with time as the majority carriers are generated allowing the depletion depth to shrink when the gate voltage is raised. A reciprocal phenomenon can occur when the channel is activated. The majority carriers are expelled from the increasing depletion region and collected in the body. Thus, drain current overshoot occurs and then gradually decreases with time by electron-hole recombination [13].

#### (b) Fully-depleted (FD) SOI MOSFETs

In FD SOI MOSFETs, the Si film thickness is thinner than the maximum depth of the depletion region defined as  $X_{dmax} = X_d(\phi_s = 2\phi_F) = \sqrt{4\varepsilon_{si}\phi_F/qN_d}$ . This means that the depletion charge is constant and cannot enlarge with increasing gate bias. For this reason, FD SOI exhibits an excellent coupling between the gate bias and the inversion charge that improves the drain current and subthreshold swing. It is possible to obtain two inversion channels, one at the front interface and the other at the back interface.

FD devices exhibit several unique characteristics:

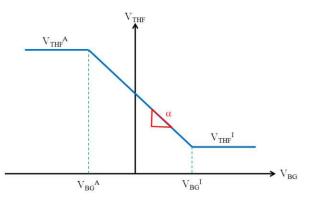

- (i) When the opposite gate bias increases, the threshold voltage decreases between two plateaus corresponding to accumulation and inversion of the opposite channel (Fig. 2-14) [14].

- (ii) The contribution of both front- and back-interface traps is reflected in the subthreshold slope. In case of front-channel, when the back-channel lies in depletion regime, the threshold slope becomes a maximum (60 mV/decade of current) [15].

- (iii) The transconductance curve has a plateau when the opposite channel is inverted (Fig. 2-22a) [16].

- (iv) The mobility and series resistance depend on the opposite gate bias due to the modulation of the effective vertical electric field [16].

Fig. 1-2: Cross-section of the conventional (a) partially-depleted (PD) and (b) fully-depleted (FD) planar SOI transistors.

Both PD and FD SOI MOSFETs have their own advantages for various applications. In this thesis, we will focus on the characterization of several different types of advanced FD SOI MOSFETs. Also, their applications to memory devices will be discussed. The unique properties described above will be documented with measurement and simulation results in the following chapters.

#### 1.3. Impact of Miniaturization on Transistor Performance

In an electronic circuit, there are two essential factors to be considered: one is the switching speed and the other is the power consumption. The switching time  $\tau$  (or intrinsic delay) of a transistor is defined as:

$$\tau = \frac{V_{DD}C_{ox}}{I_{ON}} \tag{1.1}$$

where  $V_{DD}$  is supply bias,  $C_{ox}$  is oxide capacitance and  $I_{ON}$  is onset current corresponding to the applied  $V_{DD}$ .

The static power is defined as:

$$P_{S} = I_{OFF} V_{DD} \tag{1.2}$$

where  $I_{OFF}$  is current for  $V_G = 0$  V.

The  $I_{OFF}$  current should be as low as possible in order to minimize the static power. On the other hand, it is essential to keep a high  $I_{ON}$  current to achieve a switching speed as short as possible. There are three methods to enhance  $I_{ON}$  current while short switching time is maintained:

- (i) Increase supply bias  $V_{DD}$ ,

- (ii) Reduce oxide thickness in order to increase oxide capacitance  $C_{ox}$ ,

- (iii) Reduce channel length L<sub>G</sub>.

The first approach is not suitable because of power dissipation. The reduction of channel length will successfully improve  $\tau$  and I<sub>ON</sub>. Moreover, integration density increases as the size of transistor is reduced. However, channel length scaling yields several undesired effects and requires modification of transistor features according to the scaling rules.

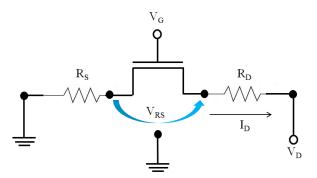

#### 1.3.1. Series resistance effects

In a transistor, the total resistance is expressed as a sum of channel resistance, reduced with gate length, and source and drain series resistance ( $R_S$  and  $R_D$ ) as shown in Fig. 1-3. In long channel device, the potential drop due to series resistance is relatively small and negligible compared with the drain bias  $V_D$ . However, the series resistance becomes no longer negligible in short device. In the ohmic regime, the effective voltage between source and drain ( $V_{RS}$ ) is lower than the applied  $V_D$ . Therefore, the action of the series resistance should be considered when a short channel device is characterized.

$$V_{RS} = V_D - (R_S + R_D)I_D$$

(1.3)

Fig. 1-3: Equivalent circuit showing the influence of series resistance on MOSFET.

#### 1.3.2. Velocity saturation

In a transistor, electron transport is governed by electric field E and carrier scattering with the lattice, impurity atoms, surface and other carriers. At low electric field, the drift velocity is described as [17]:

$$v_d = \mu E \quad (cm/s) \tag{1.4}$$

where  $\mu$  is carrier mobility. The drift velocity is proportional to the electric field.

However, at high field, this linear relationship does not hold due to the energy dependence of scattering relaxation time. The field dependent drift velocity is written as [18]:

$$v_d = \frac{\mu E}{1 + E/E_c} \quad for \quad E < E_c \tag{1.5}$$

$$v_d = v_{sat} \quad for \quad E > E_C \tag{1.6}$$

where the critical field  $E_C$  is approximately 10<sup>4</sup> V/cm for Si. Carrier velocity is saturated to  $v_{sat}$  when E is above  $E_C$ .

According to this consideration, the appropriate short-channel current model is:

$$v_d = v_{sat} = \mu E_C \quad for \quad E > E_C \tag{1.7}$$

$$V_{Dsat} = LE_C = Lv_{sat} / \mu \tag{1.8}$$

.. \_

Therefore, the conventional drain current equation in nonlinear region:

$$I_{D} = \mu C_{ox} \frac{W}{L} \left[ (V_{G} - V_{TH}) V_{D} - \frac{V_{D}^{2}}{2} \right]$$

(1.9)

is modified as:

$$I_{Dsat} = v_{sat} C_{ox} W \left[ (V_G - V_{TH}) - \frac{V_{Dsat}}{2} \right]$$

(1.10)

#### 1.3.3. Short-channel effects

With the scaling down of transistors, parasitic effects which can be neglected for long channel become significant elements. These unintended effects which limit the miniaturization and performance of devices are commonly named as short-channel effects (SCEs).

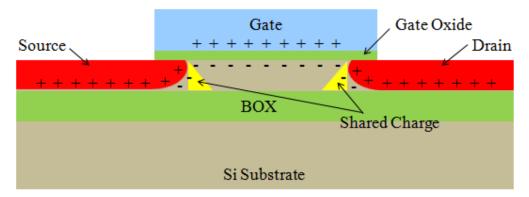

#### (a) Charge sharing

In a long channel device, the semiconductor channel is completely under the control of the gate. However, as the transistor is scaled down, source and drain junctions become closer to each other, causing a fraction of the depletion charge in the channel to lose control of gate electrode. In other words, the gate and source-drain biases share control of the charge density below the gate. Fig. 1-4 shows the shared depletion charge regions, with approximately triangular shape, near source and drain. This phenomenon is explained by the charge-sharing model [19].

Fig. 1-4: Cross-section of SOI MOSFET along the length showing depletion charge sharing between the gate, source and drain.

This charge sharing effect has strong impact on subthreshold characteristics and

threshold voltage. Once, the width of S/D depletion regions becomes non negligible compared with the channel length, the depletion charge controlled by the gate is reduced. As a result,  $V_{TH}$  becomes lower (threshold voltage roll-off) [19].

#### (b) Hot carrier effect

If carriers gain high kinetic energy due to the electric field, their energy is partially transferred to the lattice through collisions with acoustic and optic phonons. When a strong electric field is applied, the carriers can gain more energy than they can transfer to the lattice. This can be described by using a Maxwell distribution as  $T_P > T_r$ , where  $T_P$  and  $T_r$  are the carrier and lattice temperature. Therefore, the carriers become "hot" thanks to the applied electric field [20]. In short device, when an electron travels from the source to the drain along the channel, it gains kinetic energy in the pinch-off region and becomes a hot carrier [17].

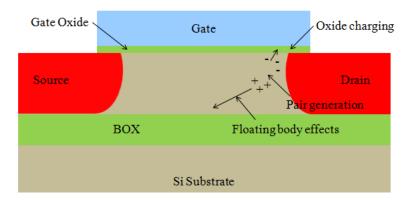

Fig. 1-5: Cross-section of SOI MOSFET along the length showing hot carrier generation (impact ionization) and its effects (floating body effects, gate oxide degradation and fixed oxide charge).

Several undesired effects induced by hot-carrier are summarized in Fig. 1-5. One of the major results of hot carrier effect is the generation of electron-hole pairs by impact ionization. This phenomenon occurs when carriers obtain enough energy to ionize atoms. In SOI MOSFETs, generated hole are stored in the body while electrons move to the drain, inducing floating body effect. Some of the hot carriers can go through the gate oxide and be collected as gate current. More importantly, some of these electrons can be trapped in the gate oxide and become fixed oxide charge. Thereby, the flat-band voltage and threshold voltage are changed and quality of the gate oxide is degraded [17].

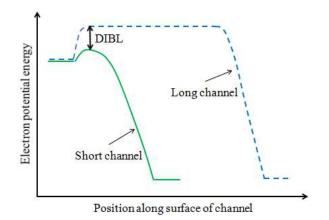

#### (c) Drain induced barrier lowering (DIBL)

Fig. 1-6 shows a more detrimental SCE which is DIBL. When the drain bias is raised,

#### Chapter 1: General Introduction

the conduction band edge (which reflects the electron energies in n-channel MOSFETs) in the drain is pulled down and the drain-channel depletion width expands. For a long channel device, the drain bias does not impact the source-to-channel potential barrier, which corresponds to the built-in potential of the source-channel p-n junction [21]. However, for a short device, as the drain bias is increased, the source-channel potential barrier is lowered due to DIBL [17]. DIBL is mainly caused by the lowering of the source-junction potential barrier below the built-in potential. This effect depends not only on the channel length and drain bias but also on the source/drain junction depth and channel doping.

Fig. 1-6: Potential distribution along the channel for a long channel and short channel MOSFET showing draininduced barrier lowering.

This phenomenon limits the maximum operation voltage of a device [22]. In order to avoid this problem, the source/drain junctions must be sufficiently shallow as the channel length is reduced. Therefore, a channel doping and/or a localized implant near source and drain known as halo (or pocket) implant [23] can be processed to reduce DIBL. It will decrease the source/drain depletion widths and prevent their interaction.

#### (d) Punchthrough effect

In short device, two depletion regions can be overlapped when the depletion region around the drain extends to the source (Fig. 1-7) [24]. This effect depends on the applied drain bias and junction depth [21]. Punchthrough occurs when drain bias impacts the formation of inversion layer, leading rapid increase of drain current and loss of gate control.

Fig. 1-7: Cross-section of SOI MOSFET along the length showing the punch-through effect.

#### 1.4. Advanced Device Architecture and Technology

To overcome SCEs and improve the device performance, advanced MOSFET techniques have been studied. Thinner gate oxide and heavily doped channel were required for good gate control with decreasing gate length. However, they cause the degradation of the device reliability and mobility. Therefore, high-k/metal gate stack has been proposed to replace conventional SiO<sub>2</sub> gate dielectric. Strain techniques, new materials (Ge or III-V) and alternative substrate orientations offer enhanced carrier mobility and drain current without resulting in parasitic effects. Also, novel architectures have been introduced such as ultra-thin body and buried insulator (UTBB) SOI and multi-gate MOSFETs to obtain good gate control of SCEs.

#### 1.4.1. High-K/Metal gate stack

When the SiO<sub>2</sub> used as gate insulator reaches its physical limit thickness (~ 1 nm), gate leakage current due to the quantum mechanical tunneling causes serious problems, increasing power consumption and degrading device reliability [25]. Therefore, replacement of the gate insulator from conventional SiO<sub>2</sub> to higher permittivity (high-k) dielectric material (Al<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub> and HfO<sub>2</sub>) is essential and unavoidable [26-28]. By adopting high-k material, the physical thickness of gate insulator can be increased while electrical thickness is maintained. According to quantum mechanics, the tunneling probability exponentially decreases as the barrier thickness increases [29]. Thereby, gate leakage can be reduced without degradation of gate control. However, dipoles in the high-k dielectric vibrate and generate vibration in the lattice of Si channel [29]. Thus, phonon scattering at its surface is large, becoming source of mobility degradation. To avoid this mobility reduction, an integrated combination of  $SiO_2$  and high-k material has been proposed. Very thin  $SiO_2$  layer located between Si body and high-k dielectric layer reduces carrier mobility deterioration [30].

In parallel, many researches have been performed to use metal gates. In metal gate electrode, the sheet resistance lowering problem is improved. The dipole vibration in high-k dielectric is also screened due to the significant increase of electrons. Metal electrode also allows an opportunity for modulating the threshold voltage of MOSFETs according to the work function engineering.

For these reasons, Intel has been using hafnium based gate insulator from 45 nm technology node [31]. Comparing to 65 nm node  $SiO_2$ /poly-Si stack, the gate leakage of 45 nm node was reduced 25 times in NMOS and 1000 times in PMOS.

#### 1.4.2. Strain technology

Strain engineering is a key method to increase the carrier mobility and driving current. There are two approaches to obtain strain in the conducting channel of a MOSFET: strained substrate and process-induced strain.

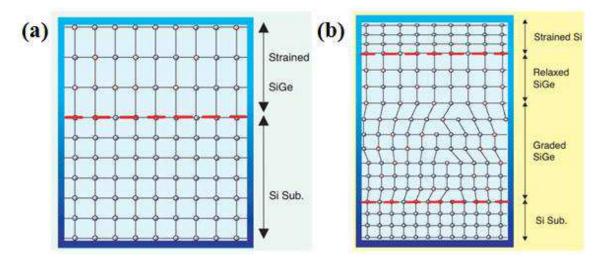

#### (a) Strained substrate

The concept of this technology is to obtain a compressive/tensile strained substrate by growing a thin film with larger/smaller lattice constant, e.g.  $Si_{1-x}Ge_x/Si$ , on a substrate with smaller/larger lattice constant, e.g.  $Si/Si_{1-x}Ge_x$ .

- (i) Strained-SOI (SSOI) substrate: The strained-Si layer is obtained by epitaxial grown Si films on relaxed SiGe virtual substrates as shown in Fig. 1-8b. After smart-cut process, only the strained Si film subsists on the BOX. Enhanced electron and hole mobility are achieved [32].

- (ii) SiGe-on-insulator (SGOI) substrate: Thin  $Si_{1-x}Ge_x$  film layer can be obtained by the condensation technique (Fig. 1-8a) [32, 33]. Improved hole mobility is obtained while electron mobility is degraded with increasing Ge concentration. A strained-Si/SiGe dual channel architectures has been proposed by Lee at al [34] for both electron and hole mobility enhancement.

Fig. 1-8: Typical substrate strain technology [32]. A schematic diagram of lattice arrangement of (a) strained Si<sub>1-x</sub>Ge<sub>x</sub> grown on Si and (b) strained Si layer on the virtual Si<sub>1-x</sub>Ge<sub>x</sub> substrate.

#### (b) Process-induced strain

Process-induced strain is simple and low cost as an existing process can be used, offering a similar carrier mobility enhancement, as the strained substrate technology [35].

- (i) Normally, silicon nitride film is deposited on a transistor for the contact-etch stop layer (CESL). This layer produces a high level of local stress. While tensile strain offers modest electron mobility enhancement, compressive strain provides outstanding hole mobility [36].

- (ii) Selective epitaxial SiGe layer deposited for raised source/drain structure compresses the Si channel and improves hole mobility. Higher strain and hole mobility are achieved with increasing Ge concentration [37]. SiC source and drain can be used for N-channels.

#### 1.4.3. Planar fully-depleted (FD) SOI transistor

As mentioned earlier, the planar FD SOI MOSFET is a good candidate for future nanoscale CMOS. FD planar MOSFETs have been fabricated on SOI wafer using UNIBOND or Smart-Cut<sup>TM</sup> technology. Unlike for the bulk technology, channel doping and pocket implantation are not essential in SOI transistor. Instead, thin Si film and thin BOX are required in order to reduce SCEs. SiO<sub>2</sub>/high-k (normally SiO<sub>2</sub>/HfO<sub>2</sub>) dielectric architecture processed by atomic layer chemical vapor deposition (ALCVD) or plasma enhanced

chemical vapor deposition (PECVD) is employed for good gate control and high mobility. Gate stack is completed by atomic layer deposition (ALD) for metal gate formation. A silicon-nitride spacer is then formed to protect the metal gate and isolate the gate stack from the subsequent formation of raised source/drain (S/D). A selective epitaxial growth is used for optimization of the S/D architecture and reduction of series resistance.

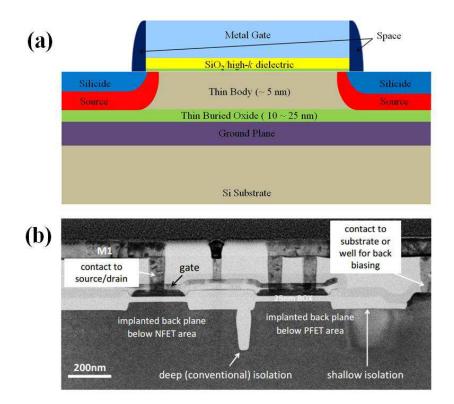

Fig. 1-9: State-of-the-art planar FD SOI MOSFETs. (a) Cross-section and (b) TEM image of advanced FD SOI device [38].

To reduce SCEs, tilted LDD implantation can be carried out prior to spacer formation and S/D implantation. Stressed-SiN CESL can also be stacked by CVD on top of the device to boost the device performance. High doped layer (ground plane) under BOX offers an opportunity to regulate front-channel properties and control SCEs. Fig. 1-9 shows the crosssection and TEM image of an advanced FD SOI transistor fabricated with state-of-the-art technology.

#### 1.4.4. 3-Dimensional fully-depleted (FD) SOI transistor

Novel transistor architectures, particularly multi-gate structure, have been proposed [39] in order to achieve simultaneously high-channel performance and integration density.

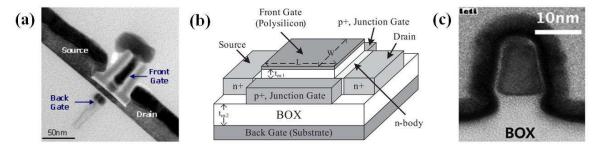

Among them, planar double-gate (DG) MOSFET shown in Fig. 1-10a offers superior performance in terms of subthreshold swing and SCEs [39]. Four-gate architecture (Fig. 1-10b) exhibits enhanced functionality by independently biasing the four gates and immunity to radiations SCEs (Fig. 1-10b) [40]. However, the industrial development of these types of structures faces problems of misalignment between the gates and lower integration density than in vertical devices. Recently, junctionless transistor (JLT) has been attracting attention due to its simple fabrication process (Fig. 1-10c) [41, 42]. JLT requires high doping of the entire transistor. That causes carrier mobility degradation and requires to pay much attention to uniform doping of whole wafer, leading technological issues for industrial application [43].

Fig. 1-10: 3-dimensional transistor architectures based on SOI technology. (a) Planar double-gate MOSFET [39], (b) four-gate MOSFET [40] and (c) junctionless transistor [41].

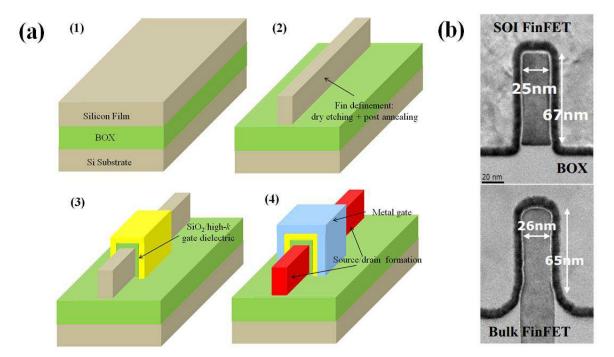

To the end, FinFET architecture is the most promising candidate for the next generation transistor. In FinFETs, the three sides (one top and two lateral) of silicon body are surrounded by the front-gate. The two lateral-gates are perfectly self-aligned and their enhanced control of the channel allows further scale down the gate length. A third channel at the top of the fin accentuates the gate control. FinFET can be fabricated not only on bulk wafer (bulk FinFET) but also on SOI substrate (SOI FinFET).

Bulk FinFETs are divided as junction-isolated or material-isolated according to the transistor isolation technique [44]. In junction-isolated FinFETs (the bottom of Fig. 1-11b), the etching of the fin is followed by an oxide deposition which should fill high aspect ratio trench without defects. Careful polishing and recess etching are then fulfilled to determine fin height. The field oxide provides isolation among the sidewalls of each fin. However, the transistors are still connected underneath the oxide. Therefore, a high dose angled implant at the bottom of the fin should be performed to create dopant junction and complete the isolation. On the other hand, the material-isolated FinFET is accomplished by the local oxidation which substitutes the high dopant implantation of the junction-isolated FinFETs.

Material-isolated technique demands more complicated and precise process steps.

By contrast, the SOI FinFET can more easily be fabricated. The BOX acts as etch stop layer and provides perfect isolation. Therefore, no additional isolation steps are required. The fin height is definitely defined by the silicon film thickness. As for planar SOI devices, the bottom interface of the body is contacted with the buried insulator and the back-channel can be activated by the back-gate biasing.

Except for the fin formation, FinFETs can basically be fabricated according to the conventional CMOS fabrication process. As we can see in Fig. 1-11a, the state-of-the-art CMOS fabrication technology, described in the previous section (1.4.3), can be adopted for FinFET processing.

Fig. 1-11: (a) SOI FinFET fabrication flow: (1) SOI wafer is used as starting material. (2) Fin definition by dry etching and post-annealing to smooth fin side wall and reduce defects. (3) Gate insulator  $(SiO_2/high-k)$  deposition. (4) Gate metal deposition and source/drain formation. (b) TEM images of SOI and junction-isolated bulk FinFETs

#### 1.5. Conclusion

The aim of this chapter was to review recent trend and related issues of Si-based MOSFETs. The device scaling down, the most critical issue, causes undesired effects: short-channel effects and performance limitation. In order to attenuate short-channel effects and acquire high-performance, several technical approaches have been proposed such as high-

k/metal gate architecture and strained-Si technology. In parallel, SOI technology was also introduced. Compared with bulk-Si technology, fully-depleted SOI offers higher performance, better scaling capability and diverse architecture thanks to its unique features. Novel device architectures have been studied based on SOI technology. FD SOI Planar MOSFETs and FinFETs are very promising candidates for beyond 22 nm technology node due to their benefits: (i) thin body and BOX; strong immunity to SCEs, (ii) undoped body; high carrier mobility, (iii) back-gate biasing; front-channel property modulation and (iv) FinFETs with excellent gate control. These advantages will be further investigated, based on our detailed measurements, in the following chapters.

Chapter 2: Advanced Devices and Typical Effects

Chapter 2:

# **Advanced Devices and Typical Effects**

In this chapter, we present characterization and modeling results for three families of devices: planar FD SOI, FinFETs with double and triple-gate, and ZnO TFTs. We will focus on the intergate couling, transport and short-channel mechanisms.

#### 2.1. Typical Properties in FD SOI MOSFETs

#### 2.1.1. Introduction

SOI technology and its advantages were briefly introduced in the previous chapter. Very good gate control and high performance are obtained with the thin Si film and BOX. The typical properties of state-of-the-art MOSFET will be reported in this section by comparing our experimental results with theoretical models.

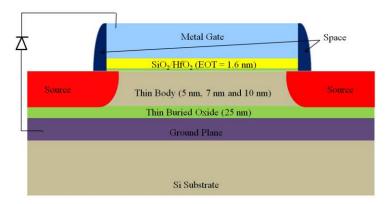

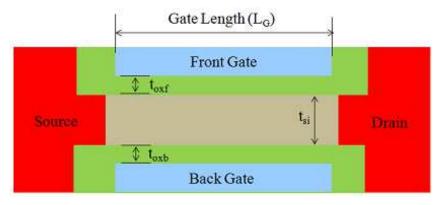

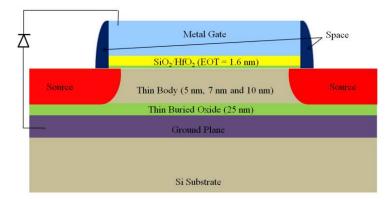

The structure of the planar devices fabricated at LETI and STMicroelectronics is shown in Fig. 2-1. The thickness of the buried insulator is  $T_{BOX} = 25$  nm. Devices with different Si film thicknesses  $T_{si}$  (5 nm, 7 nm and 10 nm) and gate lengths  $L_G$  down to 30 nm were prepared to investigate the effect of the silicon film thickness on SCEs, mobility and coupling. SiO<sub>2</sub> and HfO<sub>2</sub> layers were deposited for front-gate insulators. The effective oxide thickness (EOT) was determined to be  $T_{EOT} = 1.6$  nm. A ground plane (GP) was formed below the BOX in order to modulate the front-channel properties by GP bias. All devices have metal gate, undoped body and operate in fully-depleted mode. There is a protection diode between GP and front-gate. The turn-on voltage of this diode is around 0.8 V which prevents the application of higher bias.

Fig. 2-1: Cross-section of the ultra-thin film SOI MOSFETs studied in Chapter 2.1.

#### 2.1.2. Parameter extraction techniques and typical properties

Most of our measurements were performed at wafer level using a cryostat prober, connected HP 4155A semiconductor analyzer. The extracted electrical parameters (threshold voltage, carrier mobility, subthreshold swing and so on) from the experimental results reveal device performance. However, due to the device scaling down, undesired effects are generated and involved in the parameter extraction. In order to eliminate parasitic effects and find out precise device properties, several parameter extraction techniques have been evaluated [45-48].

#### (a) Linear extrapolation method

The first order approximation of the drain current in strong inversion and ohmic regime (at low drain bias) is expressed as:

$$I_{D} = \mu_{eff} C_{ox} \frac{W}{L} (V_{G} - V_{TH}) V_{D}$$

(2.1)

where  $I_D$  is drain current, W and L are gate width and length,  $C_{ox}$  is gate capacitance,  $V_D$  and  $V_G$  are drain and gate bias and  $V_{TH}$  is threshold voltage.

The effective mobility  $\mu_{eff}$  in strong inversion regime is defined as:

$$\mu_{eff} = \frac{\mu_0}{1 + \theta(V_G - V_{TH})}$$

(2.2)

where  $\mu_0$  is the low-field mobility and  $\theta$  is the mobility degradation factor at high vertical field. At a constant V<sub>D</sub>, based on Eq. (2.1), the drain current variation with V<sub>G</sub> is sub-linear because the effective mobility is degraded at high electric field.

The transconductance is defined as the derivative of Eq. (2.1) with respect to V<sub>G</sub>:

$$g_m = \frac{\partial I_D}{\partial V_G} = \frac{W}{L} C_{ox} \frac{\mu_0}{\left[1 + \theta (V_G - V_{TH})\right]^2} V_D$$

(2.3)

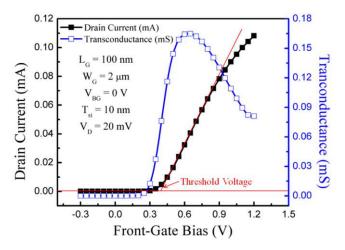

The linear extrapolation method is very simple for the extraction of the threshold voltage, using a straight line fit to the drain curve as shown in Fig. 2-2. The intercept point with X-axis indicates the threshold voltage. The slope of the line yields the mobility. However, this method is sensitive to the mobility degradation and series resistance.

Fig. 2-2: Experimental drain current and transconductance curves as a function of front-gate bias showing the linear extrapolation method for threshold voltage. N-channel SOI MOSFET with  $L_G = 100$  nm and  $T_{si} = 10$  nm.

#### (b) Transconductance method

The *field-effect* mobility  $\mu_{FE}$ , can be determined from the transconductance, defined by Eq. (2.3) [45]:

$$g_m = \frac{W}{L} \mu_{FE} C_{ox} V_D \tag{2.4}$$

The maximum *field-effect* mobility becomes:

$$\mu_{FE,\max} = \frac{Lg_{m,\max}}{WC_{av}V_{D}}$$

(2.5)

The *field-effect* mobility is strongly affected by  $\theta$  factor and does not have physical meaning but is useful for circuit design.

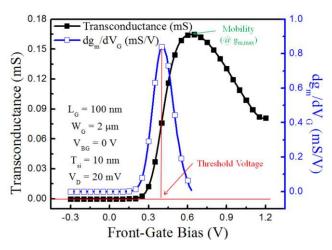

Fig. 2-3: Experimental transconductance and second derivative of drain current as a function of front-gate bias showing the extraction of *field-effect* mobility and threshold voltage.

Threshold voltage can be determined from the second derivative of current  $(d^2I_D/d^2V_G = dg_m/dV_G)$  at low drain voltage [45]. As we can see in Fig. 2-3, the gate voltage at the maximum value of the second derivative curve yields the threshold voltage. The maximum point is related to the threshold band-bending at  $\phi_s = 2\phi_F$ . This method is not affected by series resistance and mobility degradation.

#### (c) Y-function method

Y-function technique was proposed by Ghibaudo [46]. This method eliminates the mobility degradation factor  $\theta$  by dividing the current I<sub>D</sub> with  $\sqrt{g_m}$ , as defined by Eqs. (2.2) and (2.3):

$$Y = \frac{I_D}{\sqrt{g_m}} = \sqrt{\frac{W}{L} C_{ox} V_D \mu_0} (V_G - V_{TH})$$

(2.6)

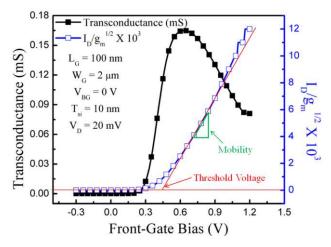

Eq. (2.6) is linear as a function of  $V_G$ . The low-field mobility is extracted from the slope of the Y-function, whereas the intercept point with X-axis represents the threshold voltage as shown in Fig. 2-4.

Fig. 2-4: Experimental transconductance and Y-function curves versus front-gate bias showing Y-function parameter extraction method.

The mobility degradation factor  $\theta$  can be calculated from Eq. (2.1):

$$\theta = \frac{\mu_0 C_{ox} W V_D}{I_D L (V_G - V_{TH})} - \frac{1}{V_G - V_{TH}}$$

(2.7)

This well known method efficiently removes the impact of series resistance. However, the effect of surface roughness at high field is emphasized in advanced MOSFETs. A second

attenuation factor  $\theta_2$  needs to be included in the current equation. Therefore, Y(V<sub>G</sub>) curve may become super-linear like in Fig. 2-4.

#### (d) McLarty method

In this parameter extraction method [47], drain current is expressed as [49, 50]:

$$I_{D} = \frac{W}{L} C_{ox} \mu_{0} \frac{(V_{G} - V_{TH}) V_{D}}{1 + \theta_{1} (V_{G} - V_{TH}) + \theta_{2} (V_{G} - V_{TH})^{2}}$$

(2.8)

where  $\theta_1$  and  $\theta_2$  are the mobility degradation factors related to series resistance and surface roughness scattering.

Inverting Eq. (2.8) and taking the first and second derivatives results in the following two equations:

$$\frac{\partial}{\partial V_G} \left( \frac{1}{I_D} \right) = \frac{1}{A} \left( \theta_2 - \frac{1}{\left( V_G - V_{TH} \right)^2} \right)$$

(2.9)

and

$$\frac{\partial^2}{\partial V_G^2} \left( \frac{1}{I_D} \right) = \frac{1}{A} \frac{2}{\left( V_G - V_{TH} \right)^3}$$

(2.10)

where  $A = C_{ox} \mu_0 V_D W/L$ .

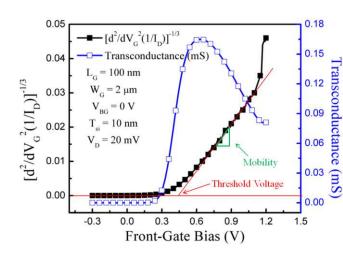

Fig. 2-5: Linear line from Eq. (2.11) and transconductance as a function of front-gate bias showing threshold voltage and carrier mobility extraction by McLarty method.

Threshold voltage and mobility can be obtained by plotting the following function versus  $V_G$ :

$$\left(\frac{\partial^2}{\partial V_G^2} \left(\frac{1}{I_D}\right)\right)^{-1/3} = \left(\frac{2}{A}\right)^{-1/3} (V_G - V_{TH})$$

(2.11)

In Fig. 2-5, threshold voltage is the intercept point with X-axis and the linear line (Eq. (2.11)) and mobility is calculated from the slope of the linear line. According to the second derivation of  $1/I_D$ , this method allows erasing the effect of series resistance  $\theta_1$  and surface roughness  $\theta_2$ .

(e) Split C-V method

The mobile channel charge density measurement technique is named as the split C-V technique. The capacitance  $C_{GC}$  is measured between the gate and source-drain. This method was introduced by Koomen *et al.* [51] for the interface trap charge density and the substrate doping measurement. It was adapted to carrier mobility measurement [48] and to SOI.

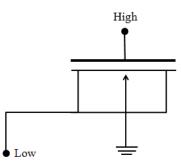

As illustrated in Fig. 2-6,  $C_{GC}$  measurement is carried out using LCR meter. A small a.c. signal is applied at the gate electrode using the high cable. The source and drain are linked together and connected to the low-cable of the LCR meter. The substrate is grounded.

Fig. 2-6: Split C-V measurement arrangement.

From the capacitor measurement, the inversion charge Q<sub>i</sub> is calculated by integration:

$$Q_{i}(V_{G}) = \int_{V_{G,acc}}^{V_{G}} C_{GC}(V) dV$$

(2.12)

In order to obtain the effective mobility, Eq. (2.12) should be combined with the drain current measurement:

$$\mu_{eff} = \frac{LI_D}{WV_D Q_i} \tag{2.13}$$

The effective mobility extracted by split C-V method depends on lattice scattering,

surface scattering and ionized impurity scattering. In our work, we mainly used the Y-function and replaced the split-CV with the magnetoresistance method developed in chapter 3.

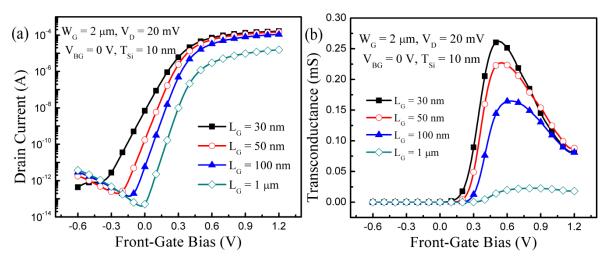

Electrical characteristics were investigated in ultra-thin body ( $T_{Si} = 10$  nm) SOI MOSFETs. In Fig. 2-7,  $I_D(V_{FG})$  curves were measured for different gate lengths. In long channel device ( $L_G = 1 \mu m$ ), excellent subthreshold swing (SS = 64 mV/dec) and high ON/OFF ratio (> 10<sup>8</sup>) were achieved, reflecting good gate control and interface quality. Reasonable threshold voltage ( $V_{THF} = 0.52$  V) and high mobility (330 cm<sup>2</sup>/Vs) were also extracted by Y-function method [46]. Gate length dependence of extracted parameters is shown in Fig. 2-8.

Fig. 2-7: Typical channel effects of ultra-thin body SOI MOSFETs. (a) Drain current and (b) transconductance curves as a function of front-gate bias for various gate lengths.

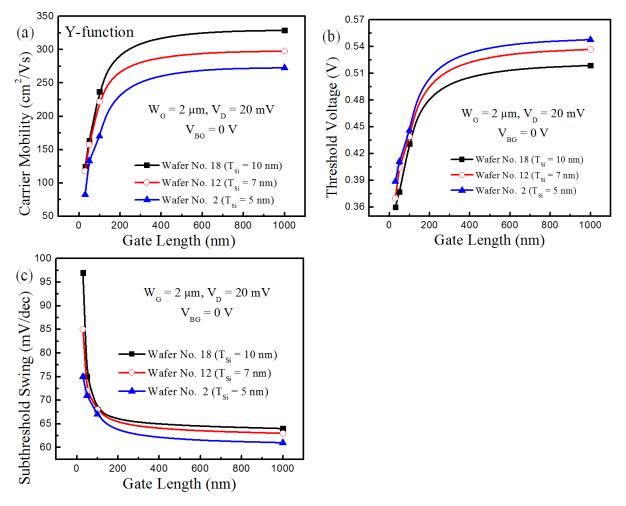

Fig. 2-8: Gate length dependence in ultra-thin body SOI MOSFETs. (a) Low-field mobility (extracted by Y-function), *field-effect* mobility (from  $g_m$  peak value), (b) threshold voltage (extracted by Y-function) and subthreshold swing as a function of gate length.

Ordinary short-channel effects were obtained. In short device, carrier mobility

decreases presumably due to the process-induced neutral defects [36]. The maximum *field*-*effect* mobility extracted from  $g_m$  peak value includes series resistance effect and is lower than the low-field mobility extracted by Y-function. However, their variation trend with channel length is identical. Threshold voltage (extracted by Y-function) roll-off and subthreshold swing (given by the Log  $I_D(V_{FG})$  curves in subthreshold regime) were degraded by the charge sharing effect [19] in shorter devices.

#### 2.1.3. Si film and BOX thickness effects

As described in Chapter 1, SCEs are the main sources of device performance degradation. The SCEs directly depend on the S/D junction depth as well as the depletion region extending into the substrate. Unlike for bulk-technology, in SOI devices, the SCEs can be effectively controlled by the reduction of silicon film and BOX thickness.

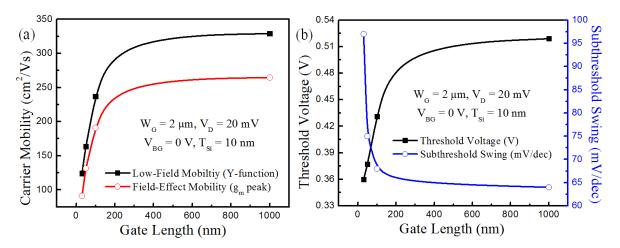

#### (a) Effect of buried oxide thickness

In long channel device with thick BOX ( $T_{BOX} = 100 \text{ nm} \sim 200 \text{ nm}$ ), the transverse electric field in the BOX is overwhelmed by the fringing field from the source/drain (Fig. 2-9a) [52]. This field induces an increase of the potential at the Si/BOX interface and, by coupling, a drop of threshold voltage [53]. This phenomenon, named drain-induced vertical substrate biasing (DIVSB), leads a loss of gate control and accentuates the DIBL effect in short devices.

Fig. 2-9: (a) Numerical simulated equipotential contours and electric-field vectors showing the fringing field in the BOX of an  $L_G = 0.2 \ \mu m$  FD SOI MOSFETs:  $T_{si} = 100 \ nm$ ,  $T_{BOX} = 350 \ nm$  and  $V_D = 50 \ mV$ . [52] (b) Vertical potential profile with conventional and GP configuration in thick ( $T_{BOX} = 350 \ nm$ ) and thin ( $T_{BOX} = 50 \ nm$ ) BOX;  $T_{si} = 20 \ nm$  [54].

In 2002, Ernst *et al.* discovered, analyzed and modeled the DIVSB [54]. The direct way to inhibit the fringing field effect is to thin down the BOX and use a ground plane (GP): the

potential peak is attenuated by GP and this advantage is remarkably enhanced in a thinner BOX (Fig. 2-9b). For nanoscale CMOS beyond the 22 nm node,  $T_{BOX} < 25$  nm is required for good control of SCEs [55, 56]. Such BOX thinning has recently been realized in SOI wafer technology [57]. This BOX combined with GP more successfully restrains the depletion region extension down to the BOX. [8, 54]

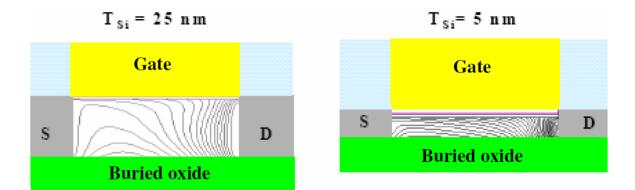

### (b) Effect of silicon film thickness

Thin film is the main condition to control SCEs in SOI device. There are very few publications so far on MOSFETs with 5 nm film thickness [8, 57]. In Fig. 2-10, the electric field in the body of the FD SOI device is governed by the silicon film thickness [58]. The potential lines are more flat in 5 nm thick body showing enhanced gate electrostatic control compared to the 25 nm thick body. An ultra-thin film physically confines the depletion region and S/D junctions depth. For excellent control of SCEs, the film thickness should be about 25 % of the channel length.

Fig. 2-10: Simulation of body potential for 25 nm and 5 nm thick SOI film at  $V_G = V_D = 1$  V [58].

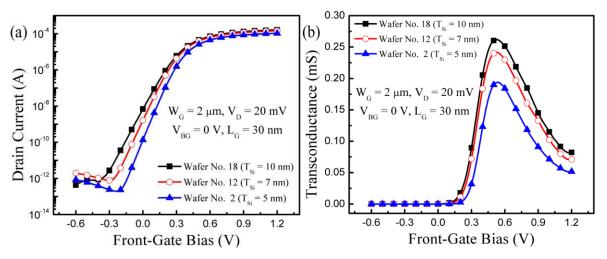

We have investigated the impact of silicon film thickness on the device performance. Fig. 2-11 shows good drain current behavior for various Si film thicknesses (5 nm, 7 nm and 10 nm) in short-length ( $L_G = 30$  nm) FD SOI MOSFETs. Better subthreshold swing is obtained in thinner devices (Fig. 2-11a). On the other hand, the transconductance peak value is reduced in thinner film, suggesting mobility degradation (Fig. 2-11b) or series resistance increases.

Fig. 2-11: Silicon film thickness dependence. (a) Drain current and (b) transconductance curves versus frontgate bias at different silicon film thickness device.

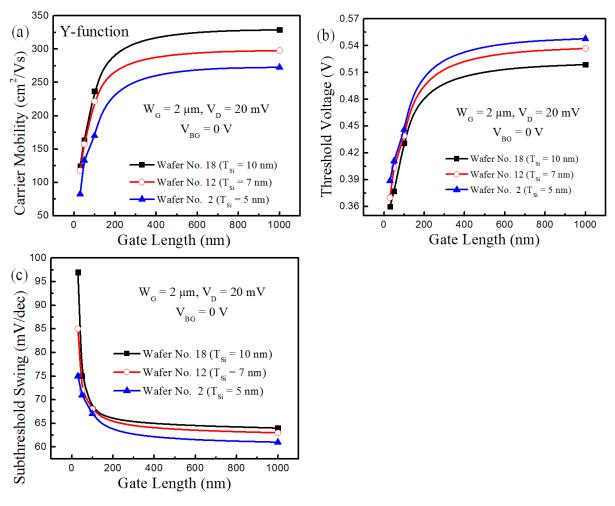

In order to compare the effect of Si film thickness on device performance and immunity to SCEs, the carrier mobility, threshold voltage and subthreshold swing were extracted for a range of gate length and thickness (Fig. 2-12). In thinner device, carrier mobility is lower by about 15 %. Note that the *field-effect* mobility shows the same tendency. In ultra-thin films, the inversion layer expends on the whole thickness of the silicon film (volume inversion) and carrier mobility is limited by phonon confinement and scattering [59]. This can explain the carrier mobility lowering. However, other reports have shown that the carrier mobility in long MOSFETs with optimized source and drain is constant in the thickness range 4-10 nm [60]. In our short channel devices, the mobility may decrease due to the defects induced by the implantation of source and drain and also by the occurring of semiballistic transport.

The threshold voltage dependence on film thickness (Fig. 2-12b) comes from quantum mechanical effects. In thinner film, quantum confinement leads to band splitting, raising the conduction band level. [61, 62]. Therefore, more energy for band-bending is necessary to get a desired inversion charge density. As a result, threshold voltage is increased with decreasing body thickness.

The degradation of the subthreshold swing in short channel (Fig. 2-12c) is much less in 5 nm film due to better gate control. When silicon film thickness reduces from 10 nm to 5 nm, the subthreshold swing is very close to the theoretical limit of 60 mV/dec that is achievable only in (perfect) FD transistors.

Fig. 2-12: Impact of silicon film thickness on device characteristics. (a) Carrier mobility, (b) threshold voltage and (c) subthreshold swing as a function of gate length for various thickness devices. Carrier mobility and threshold voltage were extracted by Y-function technique.

# 2.1.4. Coupling effect

Compared with bulk technology, there is a very particular but typical phenomenon in FD SOI devices, named "interface coupling". The back-gate bias can shift the front-gate threshold voltage and vice versa [4, 63]. Coupling effect reduces the sensitivity of threshold voltage to the thin silicon film [64] and is applicable to dynamic threshold voltage modulation [65, 66] to reduce power consumption: high  $V_{TH}$  in off state (smaller leakage current) and low  $V_{TH}$  in on state (increased drive current).

In conventional n-channel MOSFETs on bulk Si, threshold voltage  $V_{TH}$  is generally expressed as [67]:

$$V_{TH} = V_{FB} + 2\phi_B + \frac{Q_b(N_B)}{C_{ox}}$$

(2.14)

where  $V_{FB}$  is the flat-band voltage governed by the gate-body work function  $\Phi_M$  difference,  $\phi_B$  and  $Q_b$  (dependent on the doping density  $N_B$ ) are the Fermi potential and the body depletion charge density at the threshold condition and  $C_{ox}$  defined as  $\varepsilon_{ox}/t_{ox}$  is the gate-oxide capacitance per unit area.

To examine the charge coupling, we first describe the depletion approximation for intrinsic-UTB device. Oxide and interface charges are neglected and, for the sake of clarity, symmetrical DG (SDG) nMOSFET is considered as shown in Fig. 2-13. According to the Gauss's law, in weak inversion regime, front-gate bias  $V_{FG}$  of an SDG nMOSFET is expressed as:

$$V_{FG} - \Phi_M = \phi_{sf} - \frac{Q_b + Q_i}{2C_{oxf}}$$

(2.15)

where  $\phi_{sf}$  is the front-surface potential,  $C_{oxf}$  is front-gate oxide capacitance (= $\epsilon_{ox}/T_{oxf}$ ),  $Q_b$  is the depletion charge density (=-qt<sub>si</sub>N<sub>B</sub>) defined by the film theickness,  $Q_i$  is the inversioncharge density and the factor 2 in the last term comes from the symmetry of the SDG device. When the body is intrinsic,  $|Q_b| >> |Q_i|$  is clearly invalid. However,  $|Q_i|/C_{oxf} << |\phi_{sf}|$  since typically  $|Q_i| < q10^{11}$  C/cm<sup>2</sup> for subthreshold conditions. Therefore, the influence of subthreshold (or weak-inversion) charge density on  $\phi_{sf}$  in Eq. (2.15) can be neglected irrespective of N<sub>B</sub>. Finally, the charge-sheet approximation is unnecessary for subthreshold analysis.

Fig. 2-13: Schematic of the symmetrical double-gate (SDG).

In weakly inverted intrinsic UTB device ( $N_B = 0$ ), gate-to-gate coupling is well documented. The well known model of Lim and Fossum [14] was derived from depletion approximation and by solving the Poisson equation with Gauss's law.

$$V_{FG} - V_{FBf} = \left(1 + \frac{C_b}{C_{oxf}}\right) \phi_{sf} - \frac{C_b}{C_{oxf}} \phi_{sb}, \qquad (2.16)$$

$$V_{BG} - V_{FBb} = \left(1 + \frac{C_b}{C_{oxb}}\right) \phi_{sb} - \frac{C_b}{C_{oxb}} \phi_{sf}$$

(2.17)

where  $\phi_{sb}$  is the back-surface potential and C<sub>b</sub> is the capacitance of the body (= $\varepsilon_{si}/T_{si}$ ): the subscripts f and b refer to front and back gates.

From Eqs. (2.16), (2.17) and  $\phi_{sf} = 2\phi_B$  (for the nMOSFET), the front-channel threshold voltage (V<sub>THF</sub>) when the back-surface lies in depletion regime is expressed as:

$$V_{THF} = V_{FBF} + \alpha V_{FBB} + (1+\alpha)2\phi_B - \alpha V_{BG}$$

(2.18)

where

$$\alpha = \frac{C_{oxb}C_b}{C_{oxf}(C_{oxb} + C_b)}$$

(2.19)

$\alpha$  is front-channel coupling coefficient. Therefore, V<sub>TH</sub> depends on the front- and back-gate biases (V<sub>FG</sub>, V<sub>BG</sub>), flat-band voltages (V<sub>FBF</sub>, V<sub>FBB</sub>), oxide thicknesses (T<sub>oxf</sub>, T<sub>oxb</sub>) and silicon film thickness (T<sub>si</sub>). Notice that when the back-surface is accumulated or inverted, free carriers efficiently block the vertical electric field induced by V<sub>BG</sub>, pinning  $\phi_{sb}$  and V<sub>THF</sub> is independent of V<sub>BG</sub>. In Fig. 2-14, V<sub>THF</sub>(V<sub>BG</sub>) is qualitatively shown, where V<sub>BG</sub><sup>A</sup> and V<sub>BG</sub><sup>I</sup> are the back-surface accumulation and inversion onset voltages, derived from Eq. (2.17), with  $\phi_{sf} = 2\phi_B$  and  $\phi_{sb} = 0$  or  $\phi_{sb} = 2\phi_B$ .

Fig. 2-14: Front-channel threshold voltage versus back-gate bias in SOI nMOSFET [67]. When the back-surface is depleted,  $V_{THF}(V_{BG})$  varies linearly with slope  $\alpha$  (Eq. (2.19)).

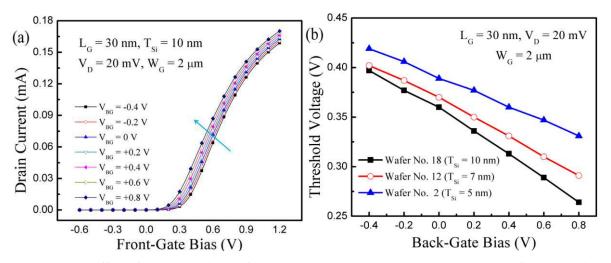

We have explored the coupling effect in our ultra-thin film MOSFETs. In Fig. 2-15,

drain current was measured at different back-gate bias (applied at the GP). The body potential is raised when the back-gate bias is increased. As a result, the front-channel threshold voltage linearly decreases with  $V_{BG}$  (Fig. 2-15b) and the drain current is enlarged (Fig. 2-15a).

Our results show that coupling effect depends on the Si film thickness. In thinner film, threshold voltage variation decreases, meaning less coupling effects. This will be further discussed with low-temperature measurement in Fig. 2-18 which provides additional insight.

Fig. 2-15: The effect of back-gate bias on front-channel properties. (a) Drain current versus front-gate bias at different back-gate bias. (b) Front-channel threshold voltage versus back-gate bias for various Si film thicknesses.

# 2.1.5. Temperature-dependent properties

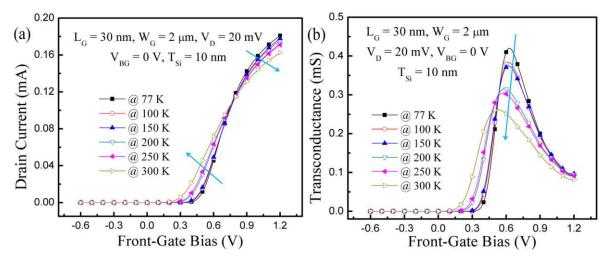

Fig. 2-16: Temperature dependence of typical device characteristics. (a) Drain current and (b) transconductance curves versus front-gate bias for a wide range of temperature.

Typical device characteristics were studied (Fig. 2-16) for a wide range of temperature (from 77 K to 300 K). At low temperature, front-channel threshold voltage is increased due to

the variation of the Fermi level. Higher drain current level and transconductance peak at low temperature mirror enhanced mobility. The overall trend of the device behavior is the same for different Si film devices.

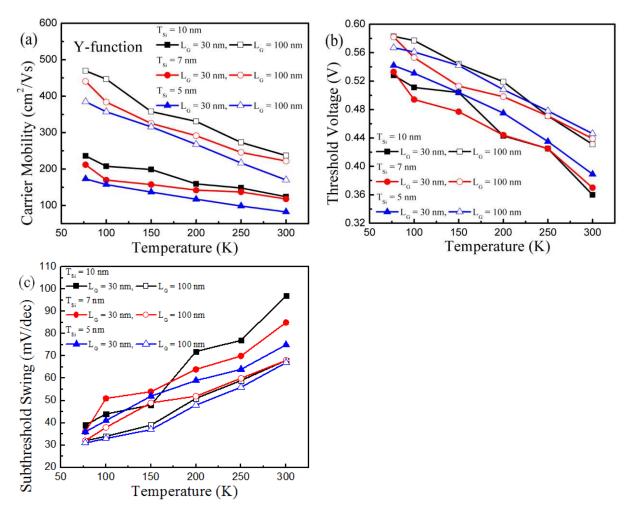

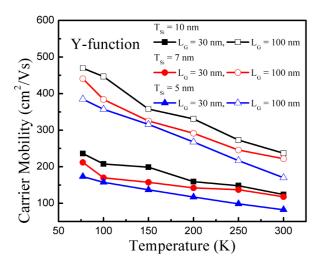

The device properties were quantified by extracting the main parameters to evaluate the influence of temperature and physical mechanisms (Fig. 2-17). The effect of Si film thickness was already discussed and obeys the same trends as in Fig. 2-12. At higher temperature, carrier mobility is reduced due to increased phonon scattering [68, 69]. Front-channel threshold voltage decreases ( $\Delta V_{THF}/\Delta T \approx 0.7 \text{ mV/K}$ ) at higher temperature. This rate of change is much smaller than in bulk MOSFETs and promotes FD SOI for operation in a wide temperature range.

The threshold voltage is expressed by the linear combination of the flat-band voltage  $V_{FB}$ , the Fermi potential  $2\phi_B$  and the potential drop in the depletion region (Eq. (2.14)). In FD MOSFETs, the latter term is temperature independent, the main contribution arising from the Fermi level variation:  $2\phi_B \times (1 + qD_{it}/C_{ox})$ . While increasing the temperature, the Fermi surface potential approximated by  $2\phi_B = 2(kT/q) \cdot \ln(N_a/N_i)$ , decreases rather linearly with temperature because the intrinsic carrier density N<sub>i</sub> exponentially increases.

At low temperature, subthreshold swing is decreases more or less linearly according to [17]:

$$SS = \ln 10 \left( \frac{kT}{q} \right) \left[ 1 + \frac{(C_{si} + C_{Dit})}{C_{ox}} \right]$$

(2.20)

where k is Boltzmann constant, T is absolute temperature, q is electron charge,  $C_{si}$ ,  $C_{Dit}$  and  $C_{ox}$  are capacitances of silicon body, interface traps and gate oxide. In Eq. (2.20), kT/q reduces with temperature while the bracket term is constant, except when  $D_{it}$  increases. In our devices, the variation of  $D_{it}$  is basically masked by the high oxide capacitance. Notice that subthreshold swing variation is almost similar in 50 nm and 100 nm length device. This means that short channel effects do not occur above 50 nm gate length device.

We can extract interface trap density from the SS(T) [70]. Subthreshold swing is proportional to the temperature (Eq. (2.20)). Therefore, the expected value at 77K is around 25 mV/dec with  $L_G = 100$  nm and  $T_{si} = 5$  nm. However, extracted value from the measurement is 32 mV/dec which yields an interface trap density of  $5.7 \cdot 10^{12}$  cm<sup>2</sup>eV<sup>-1</sup>. Interface trap density can also be extracted with Eq. (2.20) by using extracted SS value (SS = 68 mV/dec @  $L_G = 100$  nm,  $T_{si} = 5$  nm and T = 300 K). The extracted value is  $4.6 \cdot 10^{12}$   $cm^2 eV^{-1}$ . The two extracted interface trap densities are almost the same. These values are reasonable but their interpretation requires caution. Eq. (2.20) is an approximation which does not account for the influence of traps at the film-BOX interface. The effective  $D_{it}$  values include the back traps, however, their discrimination is very difficult.

Fig. 2-17: Device characteristics for a wide range of temperature. (a) Mobility, (b) threshold voltage and (c) subthreshold swing as a function of temperature for various thickness of Si film.  $W_G = 2 \mu m$ ,  $V_D = 20 mV$  and  $V_{BG} = 0 V$ .

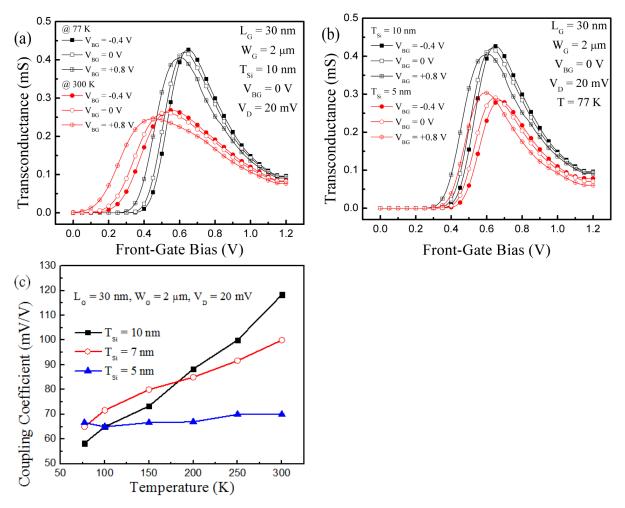

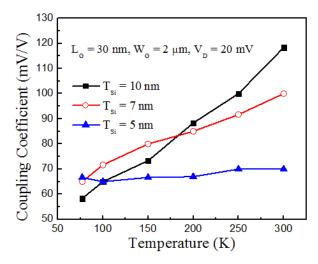

We observed an unexpected effect in ultra-thin film device. Coupling effect appears to depend on temperature (Fig. 2-18). Actually, the coupling is a result of the competition between front-gate, back-gate and SCEs. In Fig. 2-18a, the lateral variation of transconductance curve is reduced at low temperature. Fig. 2-18b shows lower transconductance peak in thinner film device at 77 K like for the results obtained at room temperature. However, the lateral shift of transconductance is slightly larger in thinner device, which apparently contradicts the result of Fig. 2-15b.

Fig. 2-18: Impact of temperature and film thickness on coupling effects in short device ( $L_G = 30$  nm). Transconductance versus front-gate bias at (a) different temperature (T = 77 K and 300 K @  $T_{si} = 10$  nm) and (b) different film thickness ( $T_{si} = 5$  nm and 10 nm @ 77 K). (c) Coupling coefficient as a function of temperature for various Si film thicknesses.

Fig. 2-18c shows the coupling coefficient defined as  $\alpha = -\Delta V_{THF}/\Delta V_{BG}$  in order to quantify the coupling effect variation with temperature. First, at 77 K, coupling coefficient is a little larger in thinner device whereas it is much smaller at 300 K. The coupling effect normally increases with body capacitance (Eq. (2.19)). Therefore, the effective body capacitance and coupling effect increase in thinner device. At higher temperature, the SCEs become more noticeable on the device operation [71, 72] and enhance coupling effect [73]. Therefore, coupling effect increases in short MOSFETs with increasing temperature. On the other hand, the rate of change of coupling coefficient  $\Delta \alpha / \Delta C_b$  is smaller in thinner device than in thicker one. Fig. 2-18c confirms that, in 5 nm film, coupling coefficient is almost constant for a wide range of temperature. The reason is that SCEs are clearly diminished in thinner film as shown in Fig. 2-12c. Thereby, the enlargement of coupling effect with increasing

temperature is prevented by the thinner film. As a result, at higher temperature, coupling effect is larger in thicker film and short device (Fig. 2-15b and Fig. 2-18c).

# 2.1.6. Conclusion

In this section, the properties of advanced ultra-thin FD SOI MOSFET were investigated for a wide range of temperature. Thanks to the state-of-the art MOSFET technology, high carrier mobility was achieved. Threshold voltage and SCEs are strongly dependent on Si film thickness: in thinner film, threshold voltage increases via quantum confinement, and SCEs are suppressed as the S/D junction depth and depletion region decrease. These results are very promising for beyond 22 nm technology node application.

Unlike for the conventional SOI MOSFETs, the competition between SCEs and Si film thickness causes unusual coupling effect. Coupling effect in short MOSFETs increases at higher temperature, more or less according to the Si film thickness. But, in devices thinner than 5-6 nm, the coupling tends to become practically insensitive to temperature. This implies that the same back-biasing scheme can be maintained for operation in a wide range of temperatures.

# 2.2. Coupling Effects in Double-Gate FinFETs

## 2.2.1. Introduction

Low power consumption and co-integration of various functionalities are the mainstream in today's VLSI circuit and system design due to the increasing demand for portable electronics and embedded system manufacturing. The size of the transistor has to be reduced as described in Chapter 1. However, as the channel length is reduced, the control of the current by the gate is jeopardized and increases the off-state leakage and power consumption. Dynamic threshold voltage modulation (*i.e.*, high  $V_{TH}$  in OFF state and low  $V_{TH}$  in ON state) is attractive to reduce the consumption and integrate different functions on the same chip [4, 74, 75]. In FD SOI technology, the back-gate bias and/or the non-volatile charge stored in ONO buried insulator can be used for threshold voltage modulation [4, 76].

Ultra-Thin Body and Buried Insulator (UTBB) and multiple-gate transistors are competing for CMOS downscaling [70, 77]. SOI FinFET is the most probable winnner thanks to its simple fabrication and enhanced electrostatic control [77-79].

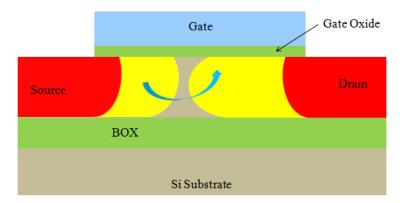

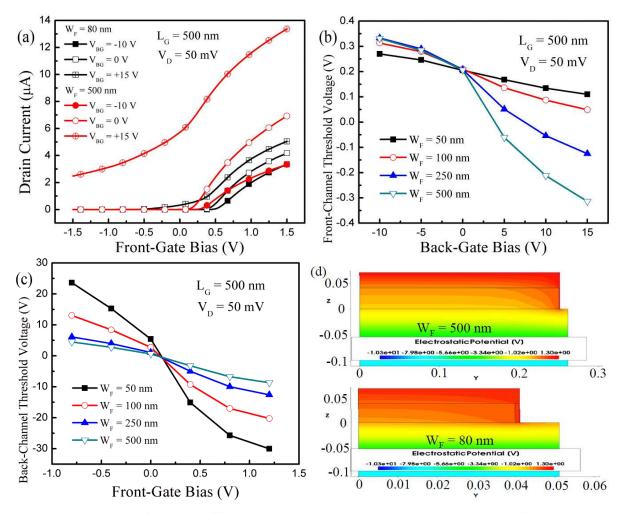

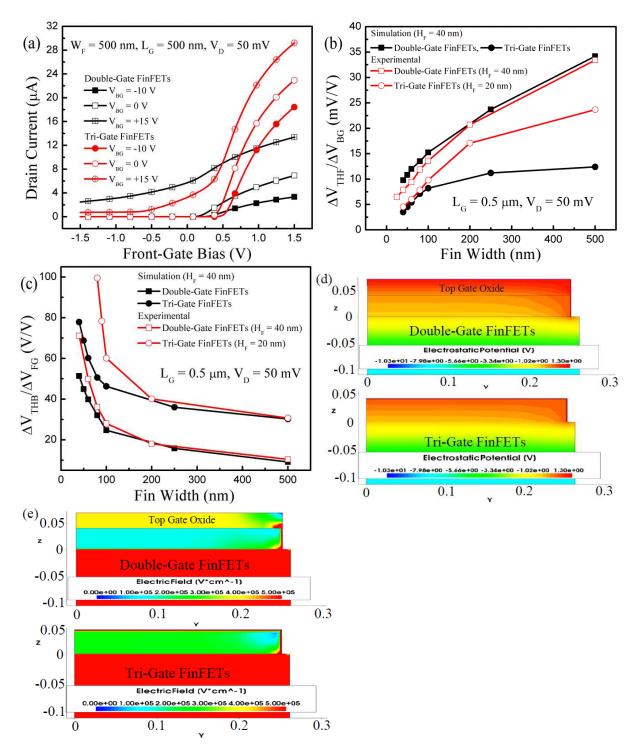

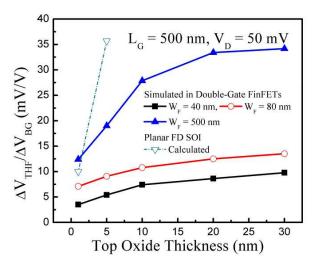

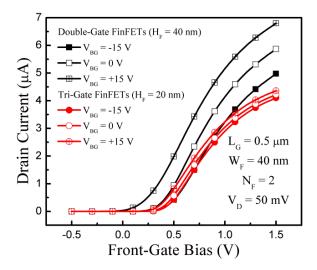

We have seen that, in fully-depleted SOI MOSFETs, the front- or back-channel threshold voltage can be modified by using the opposite gate. The question is whether this back-biasing scheme also works in FinFETs. In FD SOI FinFETs, especially with narrow fin width, we have to consider the influence of the 'lateral' electric field between the two lateral gates on the 'vertical' substrate-to-channel coupling effect. We compared two different types of SOI FinFETs. Using experimental and 3D simulation results:

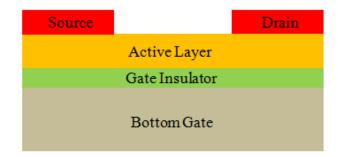

- (i) Vertical DG FinFET: top-channel activation is suppressed by thick insulating layers at the top of the fin and only the two lateral-channels are activated by the frontgate biasing.

- (ii) Triple-gate FinFET: top and lateral-channels are equally activated by applying frontgate bias.

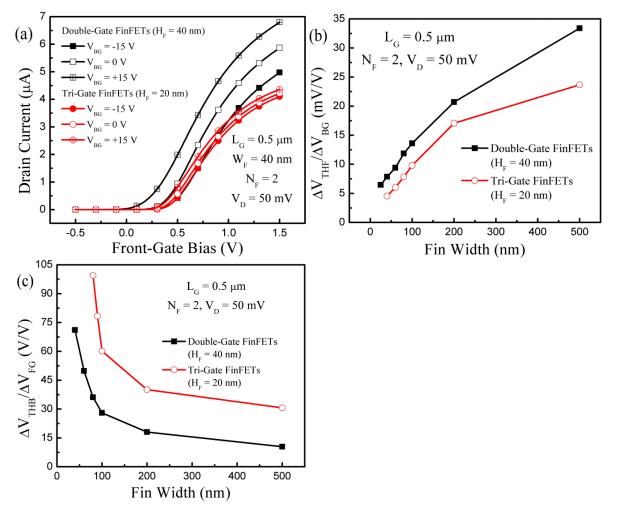

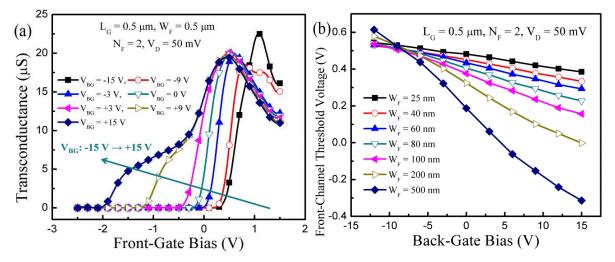

Since coupling in triple-gate FinFETs have been documented [80], we focus on the coupling effect between lateral-gates (also referred to as 'front' gate) and back-gate in DG FinFETs. We highlight the enhanced front-channel threshold voltage variation by the back-gate bias which can be applicable for dynamic threshold voltage modulation in vertical DG FinFET. Triple-gate FinFETs are used to benchmark the two device structures. The effect of the fin width on the coupling effects is further investigated.

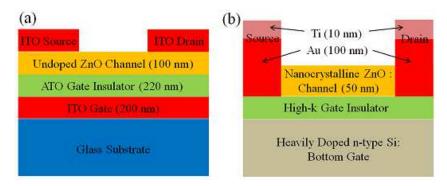

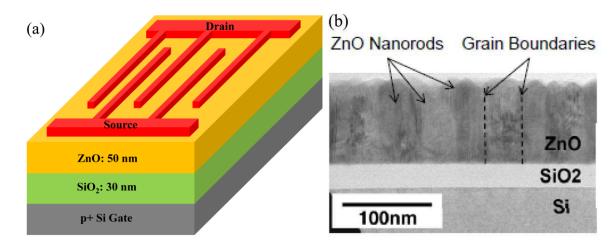

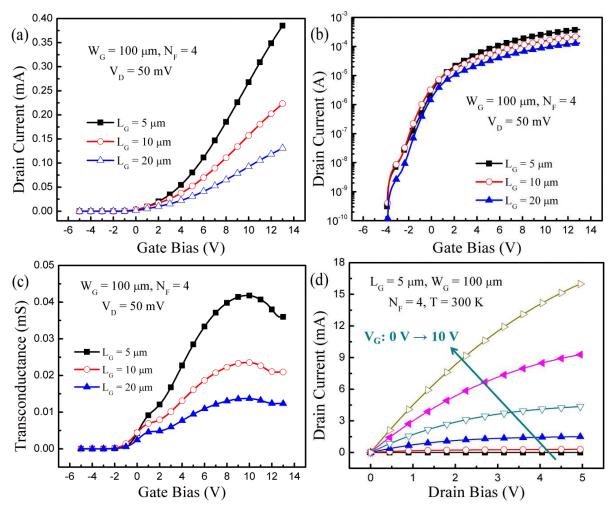

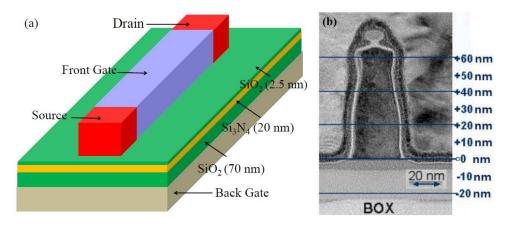

# 2.2.2. Typical properties

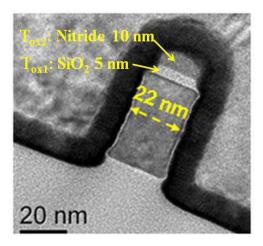

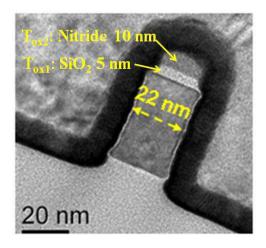

SOI wafers fabricated with the Smart-Cut<sup>TM</sup> technology were used as starting material. The thickness of the buried SiO<sub>2</sub> insulator (BOX) is  $T_{BOX} = 140$  nm. The silicon film thinned down to 40 nm defined the fin height H<sub>F</sub>. SiO<sub>2</sub> (1 nm) and HfO<sub>2</sub> (2.5 nm) layers were stacked for lateral-gate insulators. The effective oxide thickness (EOT) was determined to be  $T_{ox} = 1.4$  nm. At the top of the fin, thicker SiO<sub>2</sub> (5 nm) and nitride (10 nm) layers were deposited to prevent the top-channel conduction. The two lateral-gates are controlled by the same bias. Vertical DG FinFETs with different fin width  $W_F$  (down to 25 nm) and gate length L<sub>G</sub> (down to 40 nm) were manufactured to investigate the geometrical issues. The width we will be referring to is the designed value. The real fin width after process completion is 20-25 nm narrower. The triple-gate FinFETs used for comparison have H<sub>F</sub> = 20 nm silicon body height. Even though the vertical DG FinFETs are taller than the triple-gate FinFETs, they show enhanced sensitivity to the back-gate biasing, as discussed in section 2.2.3. All devices have undoped body, TiN metal gate and operate in fully-depleted mode. Fig. 2-19 shows the cross-section of the vertical DG FinFET fabricated at Sematech (USA).

Fig. 2-19: TEM cross-section of vertical double-gate FinFET fabricated on SOI wafer.

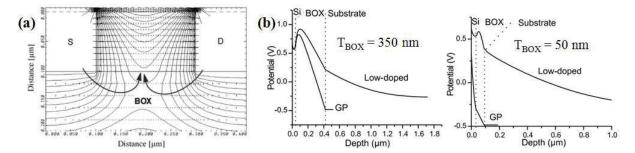

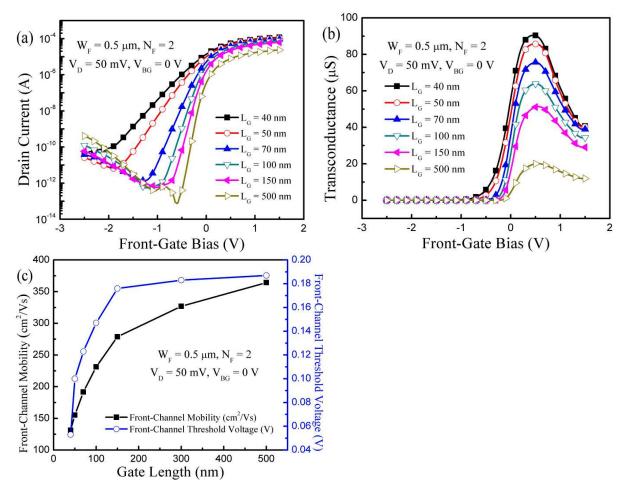

The electrical transport properties depend on the device geometry and fin size ( $L_G$ ,  $W_F$ ). The effect of the gate length on the drain current  $I_D(V_{FG})$  and transconductance  $g_m(V_{FG})$  characteristics is depicted in Fig. 2-20. The  $I_D(V_{FG})$  curves prove that an excellent gate control is achieved: (i) high ON/OFF current ratio (> 10<sup>8</sup>) and (ii) low subthreshold swing (SS = 70 mV/dec at  $L_G = 0.5 \mu m$ ). The front-channel threshold voltage  $V_{THF}$  value ( $V_{THF} = 0.17 \text{ V} @ L_G = 0.5 \mu m$ ) was extracted from the Y-function [46]. In shorter devices, the drain

current level and the transconductance peak value increase steadily which implies that the series resistance effects are not overwhelming and remain reasonable. The electron mobility, extracted from the transconductance peak [45], reaches relatively high value (~  $350 \text{ cm}^2/\text{Vs}$ ). These results reveal promising electrical properties of vertical DG FinFETs.

Fig. 2-20: Front-channel characteristics of vertical DG FinFETs. (a) Drain current and (b) transconductance as a function of the front-gate bias for different gate lengths. (c) Front-channel mobility and threshold voltage versus gate length.

In Fig. 2-20, we also observe the regular effects of shorter channel lengths: (i) subthreshold swing increase, (ii)  $V_{THF}$  roll-off and (iii) carrier mobility degradation. The mobility behavior is explained by the process-induced neutral defects located near the source and drain terminals which overlap in very short channels [36]. Only below 50 nm gate length, the threshold voltage and the subthreshold swing are significantly degraded due to the charge sharing effect [19]. Notice that, with narrower fin width, lower subthreshold swing (SS = 65 mV/dec @ W<sub>F</sub> = 50 nm, L<sub>G</sub> = 0.5 µm) and reduced short-channel effects are obtained. Indeed, the transversal component of the electric field is enhanced, improving the overall control of

the lateral-gates on the body. Back-channel characteristics were also assessed. Thanks to the good body/BOX interface quality [81], even higher mobility (~ 420 cm<sup>2</sup>/Vs) than in the front channel was achieved. The extracted back-channel threshold voltage  $V_{THB}$  is around 1 V for  $L_G = 0.5 \ \mu m$ .

## 2.2.3. Coupling effects

#### (a) 3-Dimensional coupling model

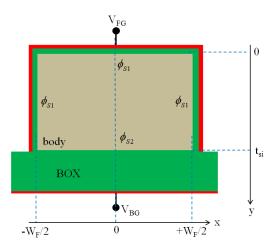

In 2007, Akarvardar *at al.* in our group reported a two-dimensional coupling model to consider the influence of the fin width and back-gate on coupling effects in triple-gate SOI FinFETs [82]. The cross-section of a triple-gate FinFET, showing the axes and symbol conventions, is given in Fig. 2-21.

A parabolic potential variation between the two lateral gates was assumed:

$$\phi(x, y) = a(y)x^{2} + b(y)x + c(y)$$

(2.21)

where  $\phi(x, y)$  is the 2-D body potential in undoped body. The 2-D Poisson's equation is solved for full depetion and negligible body doping:

$$\frac{\partial^2(x,y)}{\partial x^2} + \frac{\partial^2 \phi(x,y)}{\partial y^2} = 0$$

(2.22)

A constant surface potential is considered on the three sides:

$$\phi(\pm W_F / 2, y) = \phi(x, 0) = \phi_{S1}(y) \tag{2.23}$$

Corner effects, quantum-mechanical effects, substrate depletion (under the BOX) and drain bias effect are neglected.  $\phi_{s_2}$  is the extremum of the back-surface potential at  $\phi(x, T_{s_i})$  at the fin-BOX interface.

The solution of Eq. (2.22) using Eqs. (2.21) and (2.23) is given by

$$\phi(x, y) = \phi_{SI} + \frac{f(y)}{f(T_{si})} \left( 1 - \frac{4x^2}{W_F^2} \right) (\phi_{S2} - \phi_{SI})$$

(2.24)

where f(y) is defined as

$$f(y) = \sinh\left(2\sqrt{2}\frac{y}{W_F}\right)$$

(2.25)

Fig. 2-21: Cross-section of the triple-gate SOI FinFETs (perpendicular to current flow direction) showing the boundary conditions and axes used in modeling.

The derivation of the threshold voltage from the potential model is straightforward. Like for the Lim and Fossum's model (Chapter 2.1.4) [14],  $\phi_{s_1}$  and  $\phi_{s_2}$  are first related to V<sub>FG</sub> and V<sub>BG</sub> as follows:

$$V_{FG} - V_{FBf} = \phi_{SI} + A \frac{C_w}{C_{oxf}} (\phi_{SI} - \phi_{S2}), \qquad (2.26)$$

$$V_{BG} - V_{FBb} = \phi_{S2} + B \frac{C_w}{C_{oxb}} (\phi_{S2} - \phi_{S1})$$

(2.27)

where

$$A = \frac{2\sqrt{2}}{\sinh\left(2\sqrt{2}\frac{T_{Si}}{W_F}\right)}, \quad B = \frac{2\sqrt{2}}{\tanh\left(2\sqrt{2}\frac{T_{Si}}{W_F}\right)} \text{ and } C_w = \frac{\varepsilon_{Si}}{W_F}$$

Eqs. (2.26) and (2.27) are basic relations to describe the coupling effects between the front gate and substrate in a triple-gate FinFETs. The front- and back-channel threshold voltage can be obtained by replacing  $V_{FG}/V_{BG}$  with  $V_{THF}/V_{THB}$  and  $\phi_s = \phi_F + \phi_T$  (where  $\phi_T$  is band-bending at threshold voltage and (x,y)=(0,0)).

When the back-channel is depleted,  $\phi_{s_2}$  varies with V<sub>BG</sub> in Eq. (2.27). Therefore, front-channel threshold voltage becomes:

$$V_{THF} - V_{FBF} = \alpha (V_{BG} - V_{FBB}) + \left(1 + A \frac{C_w}{C_{oxf}} - \alpha B \frac{C_w}{C_{ox}b}\right) (\phi_F + \phi_T)$$

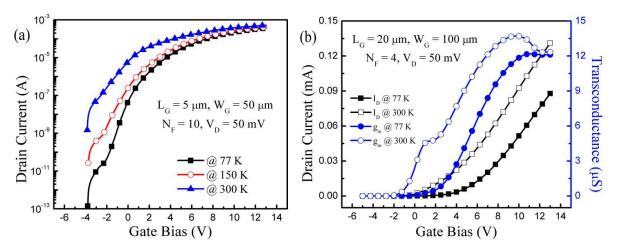

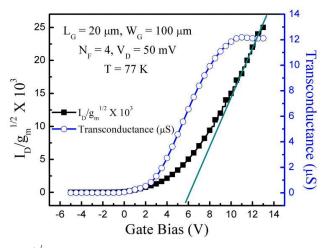

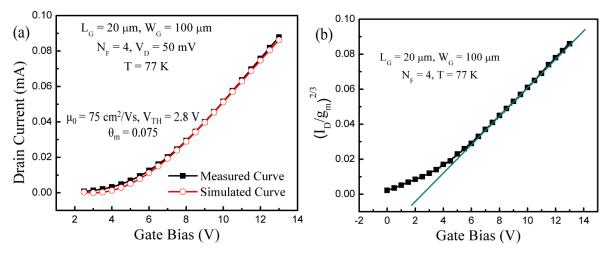

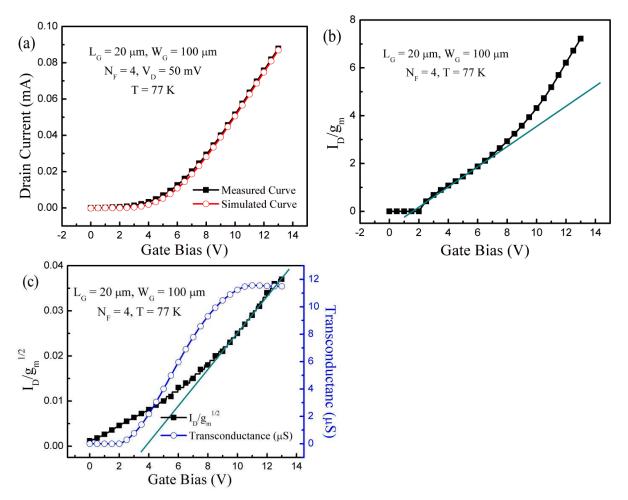

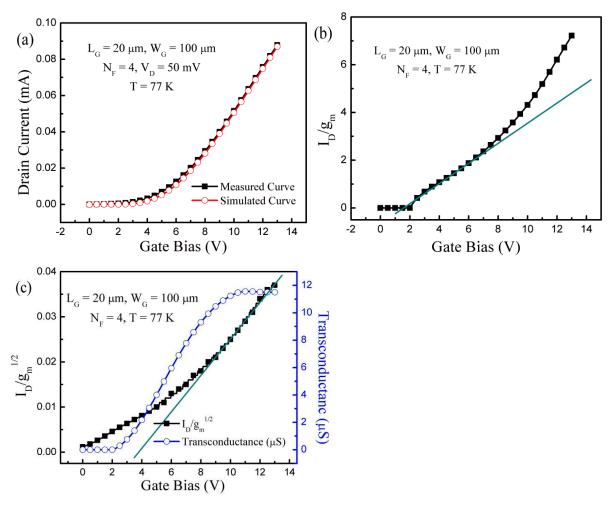

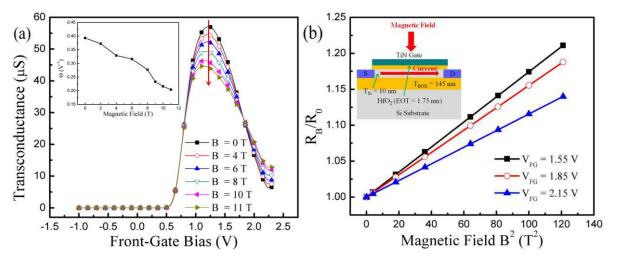

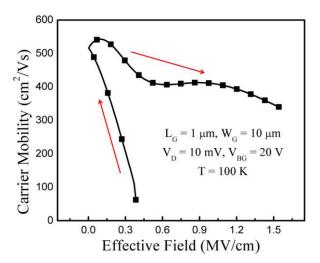

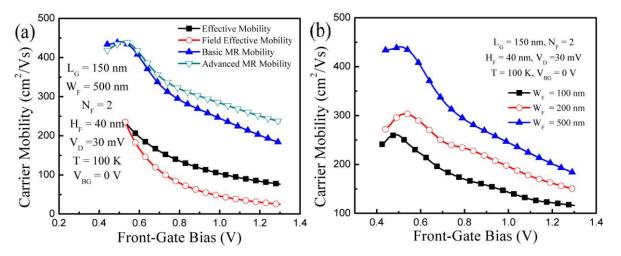

(2.28)

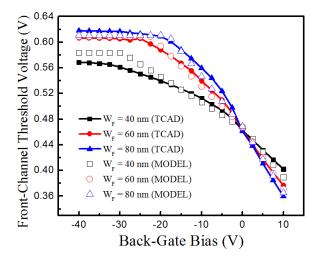

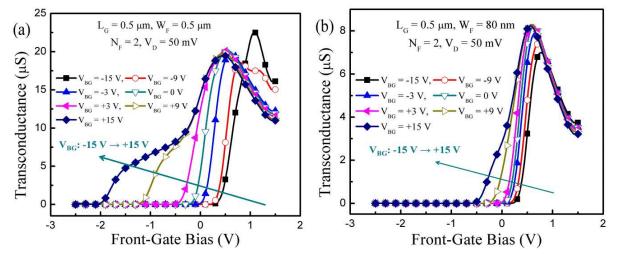

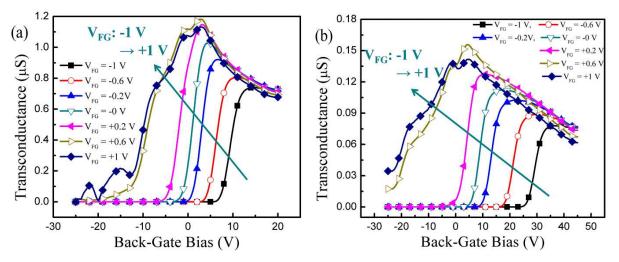

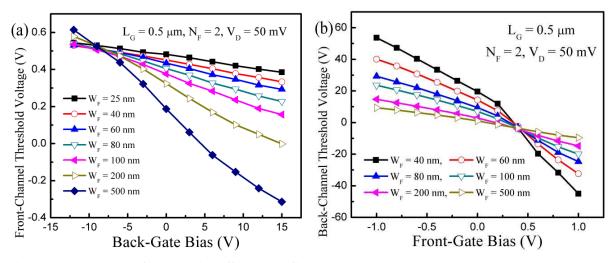

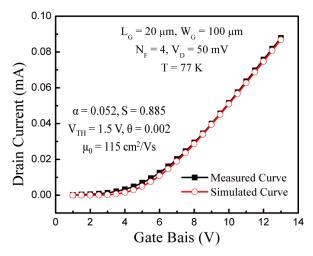

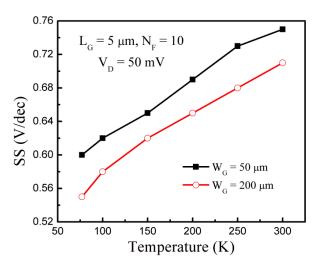

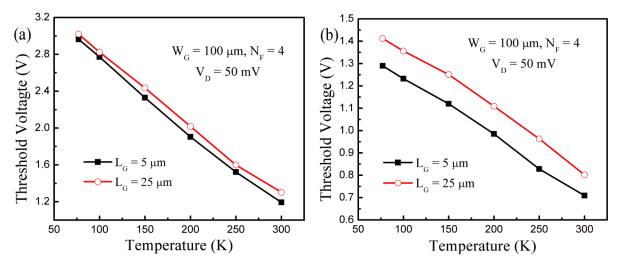

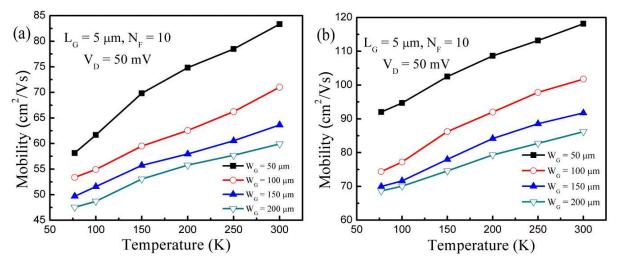

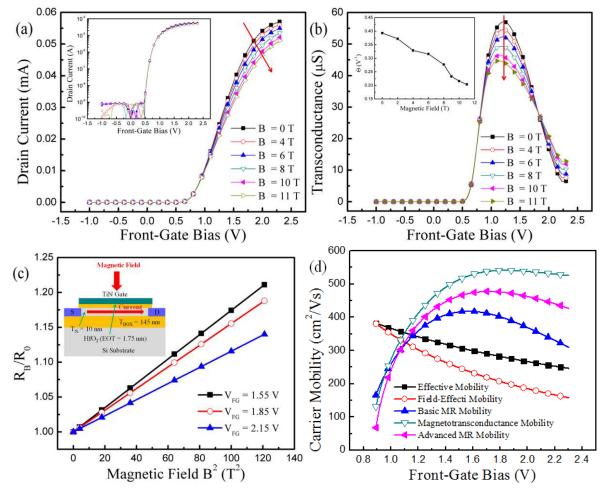

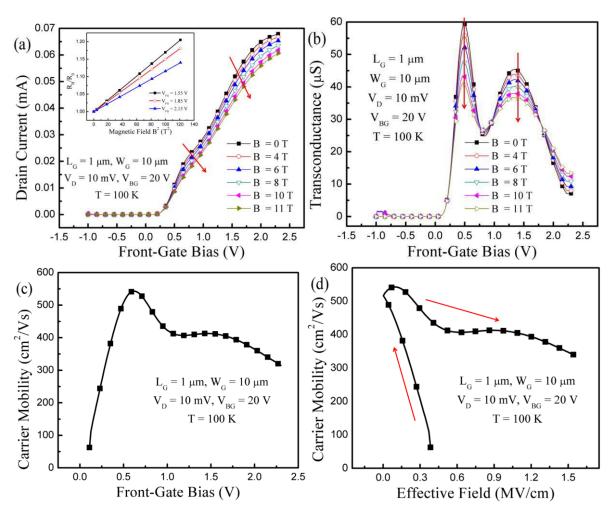

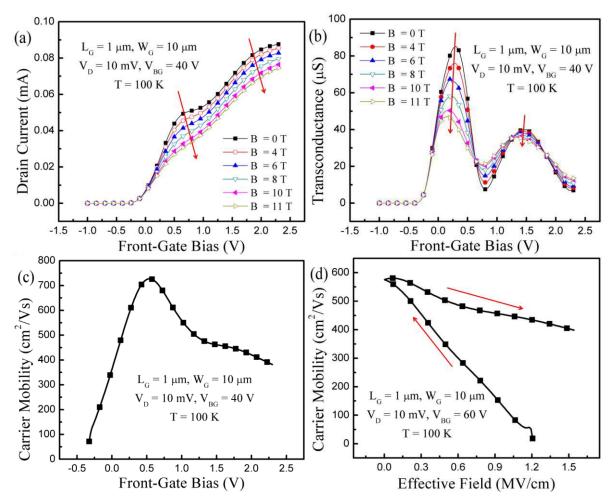

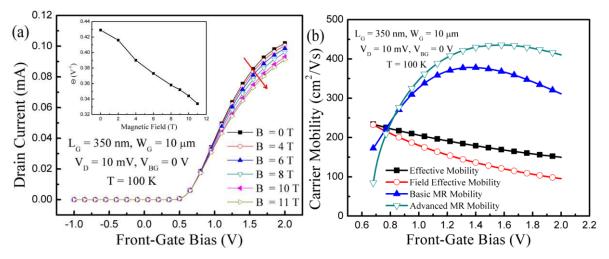

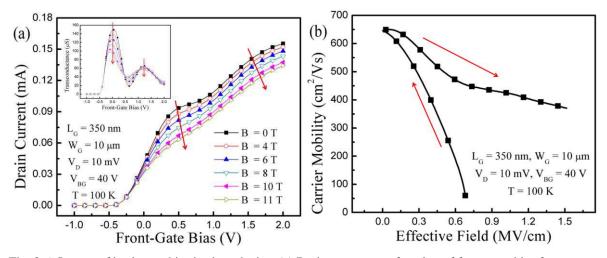

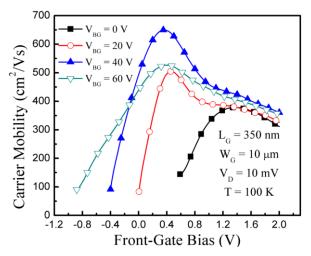

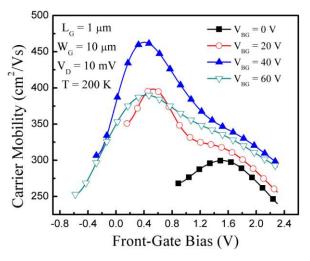

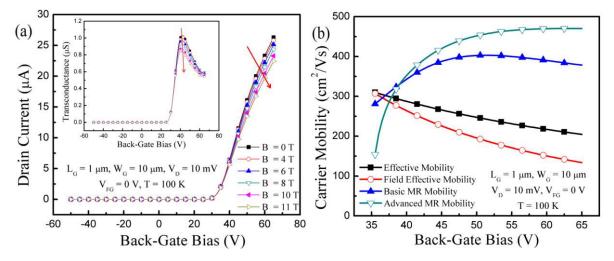

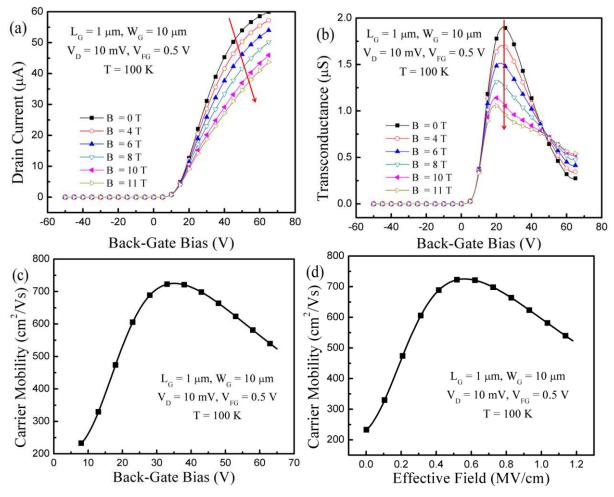

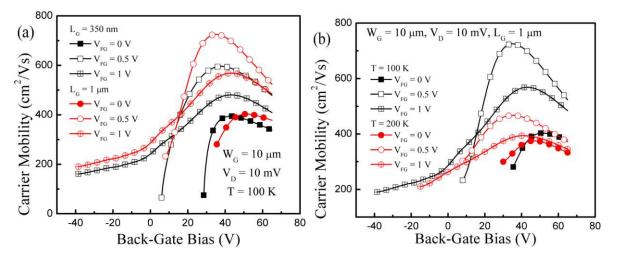

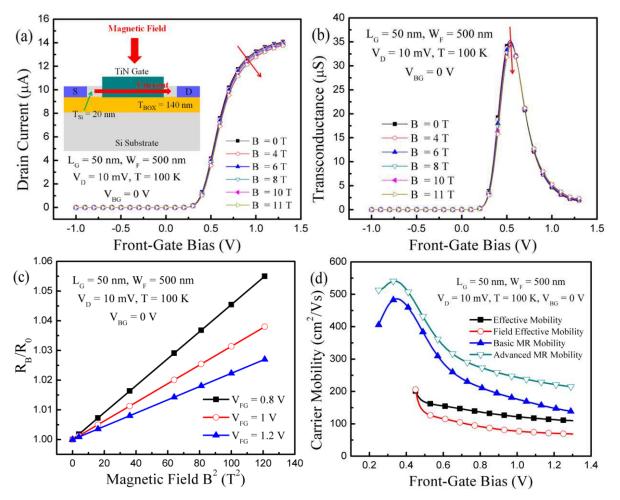

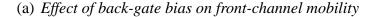

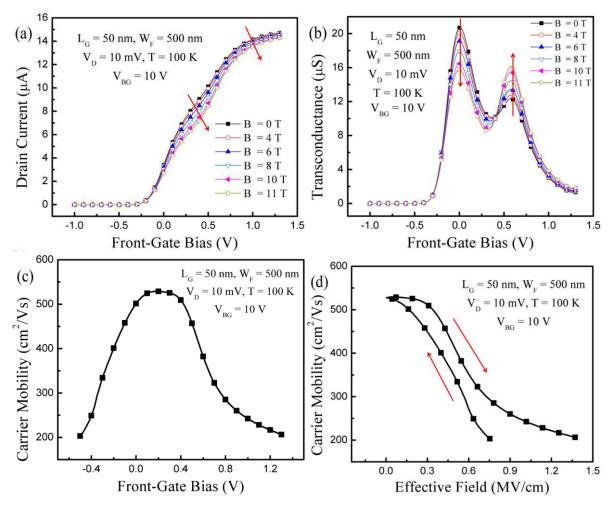

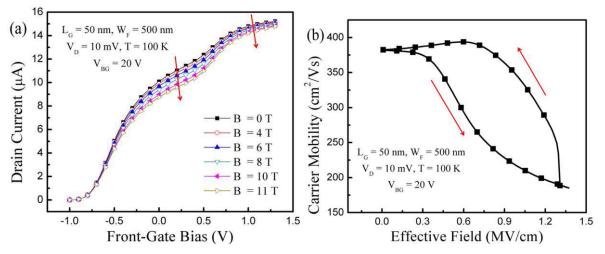

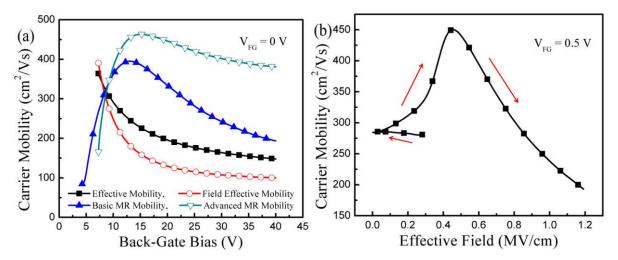

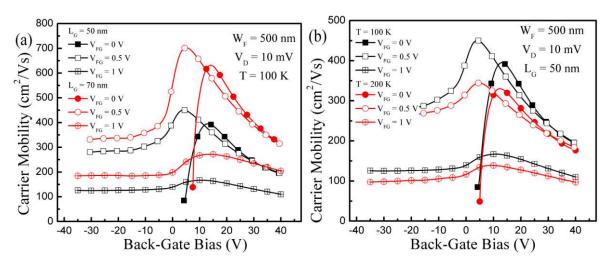

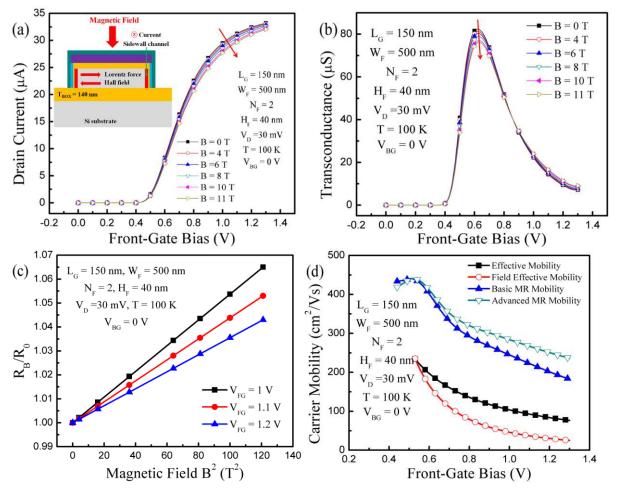

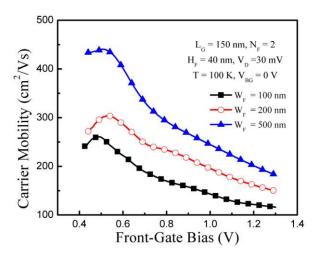

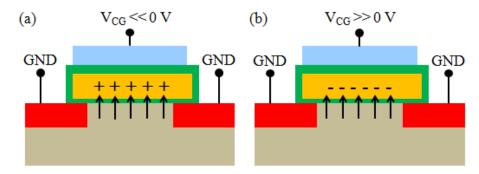

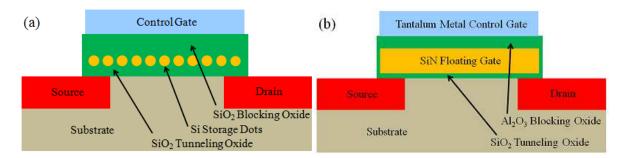

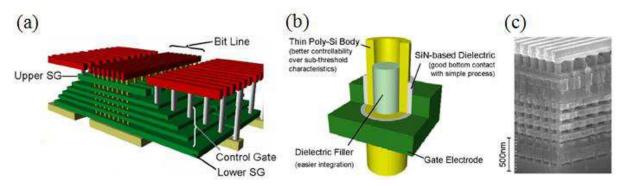

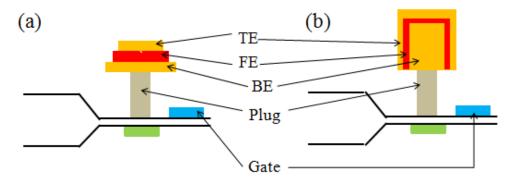

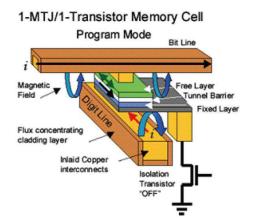

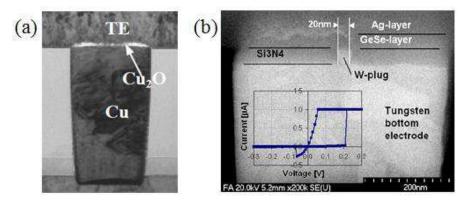

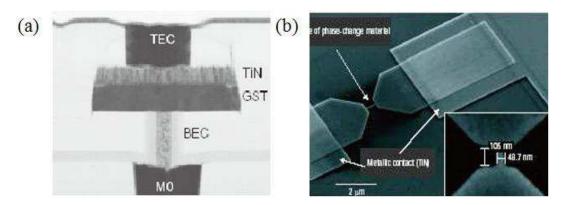

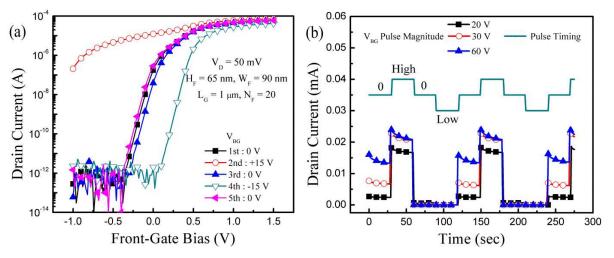

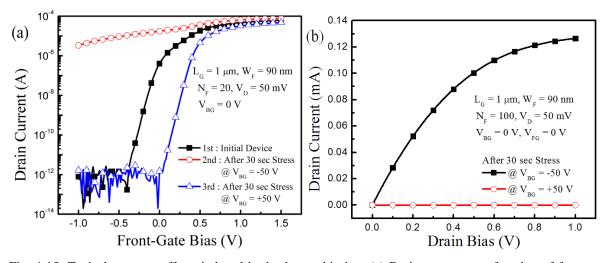

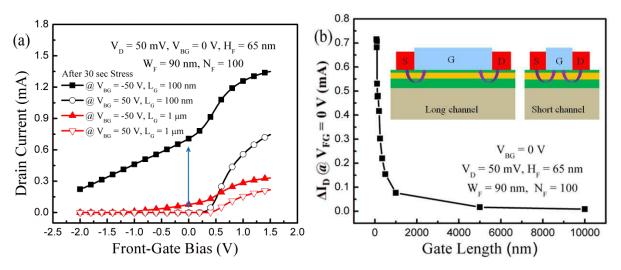

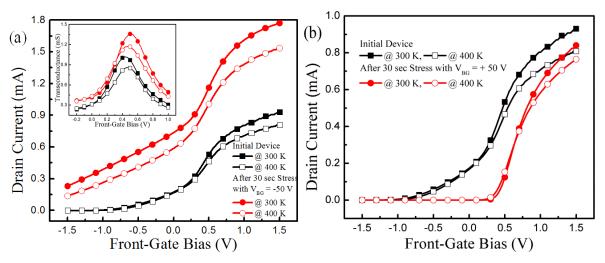

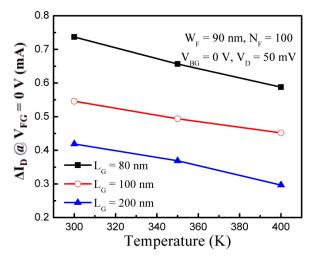

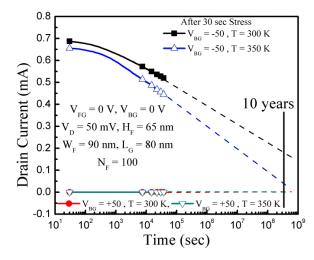

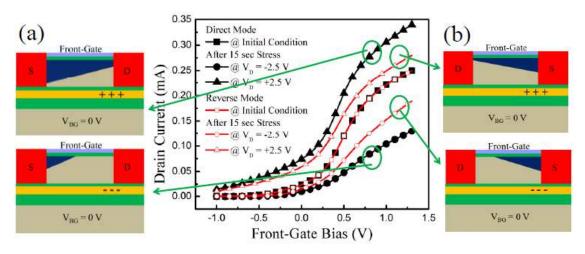

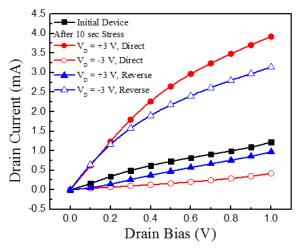

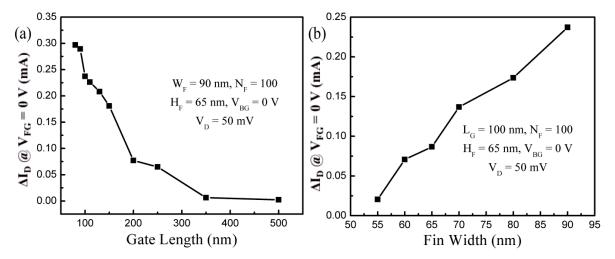

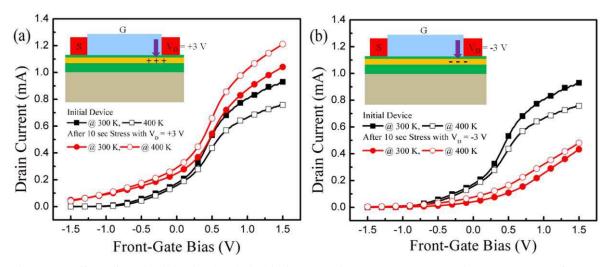

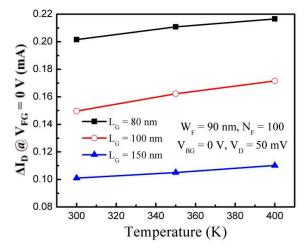

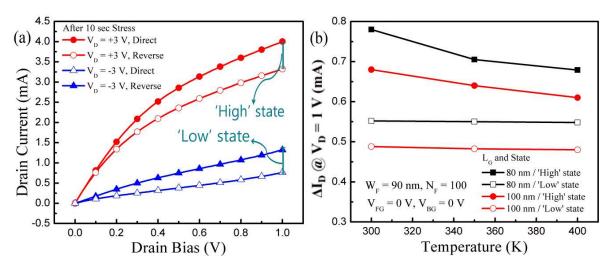

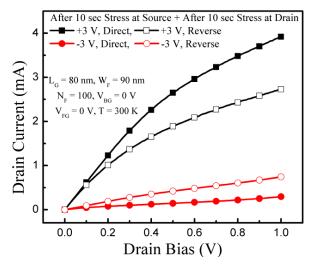

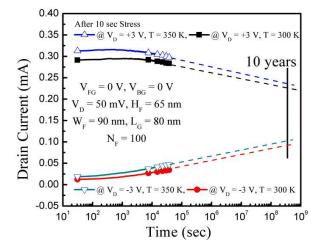

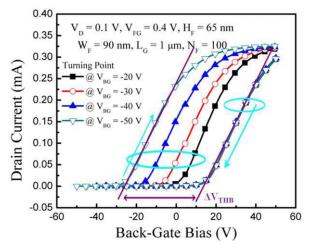

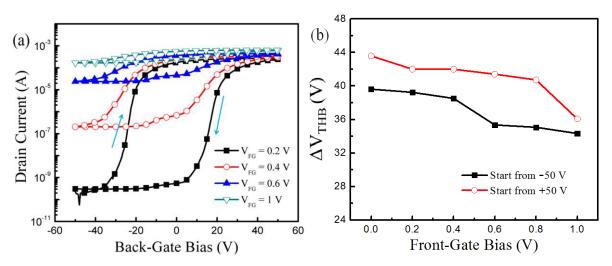

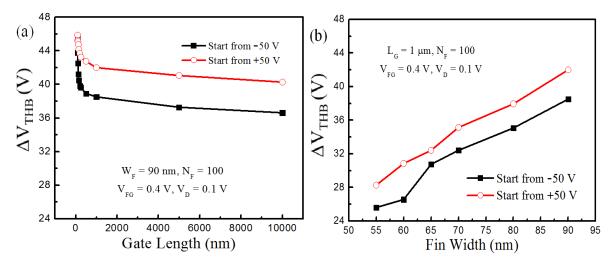

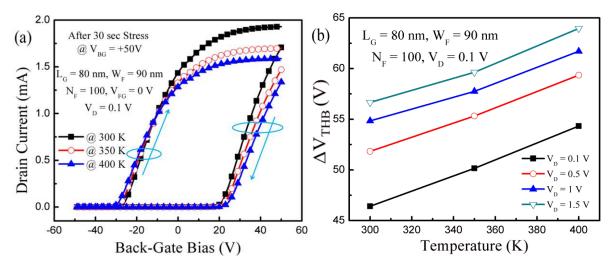

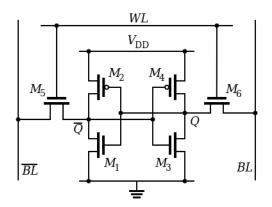

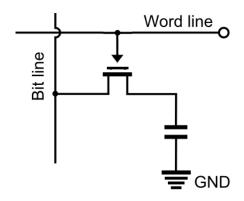

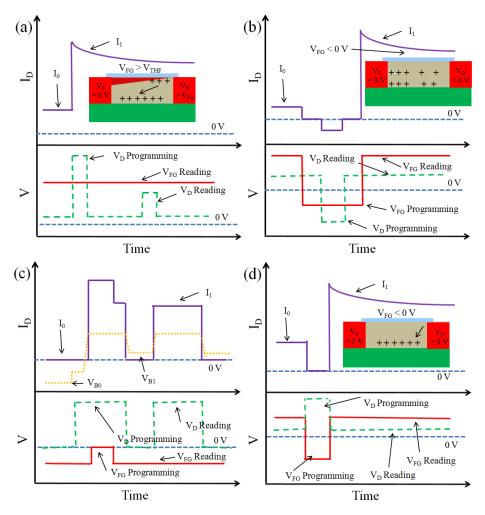

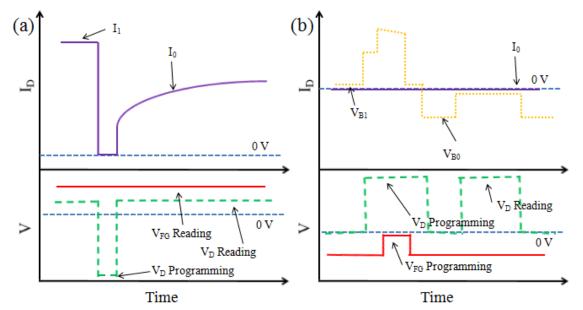

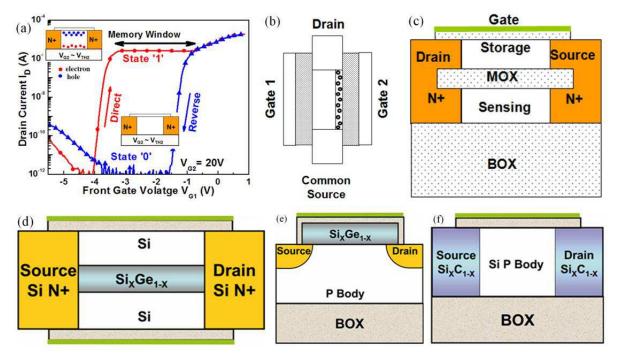

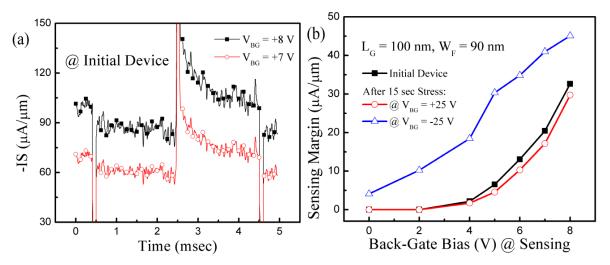

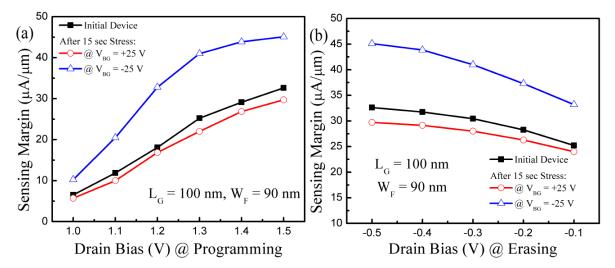

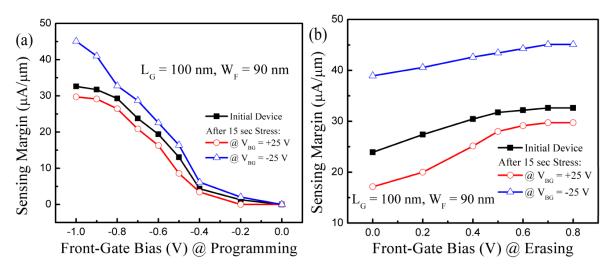

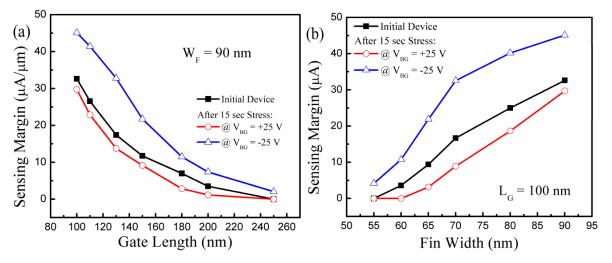

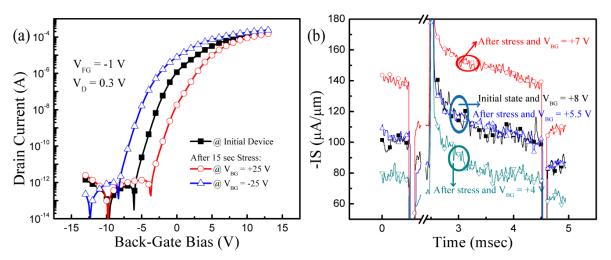

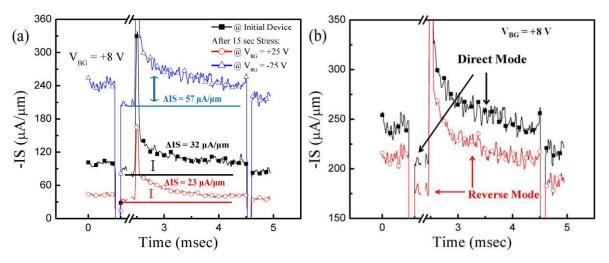

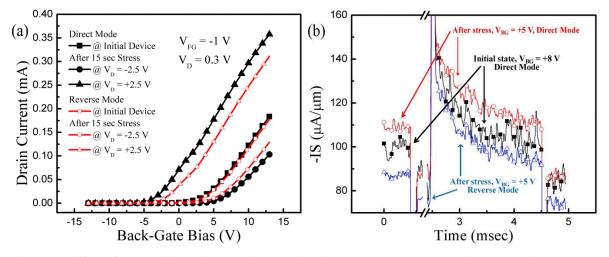

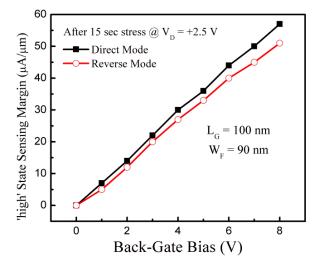

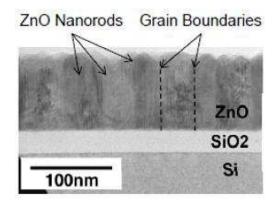

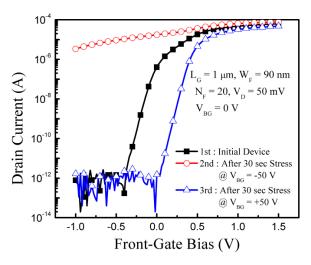

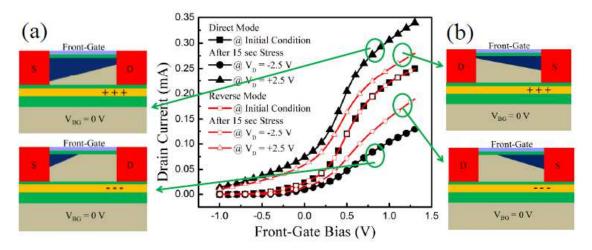

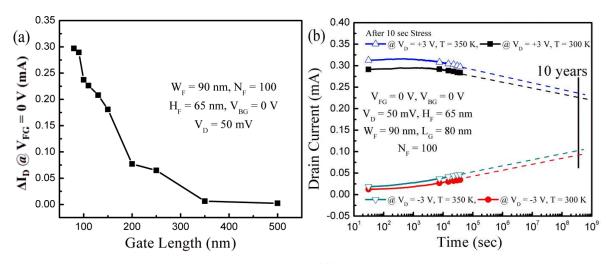

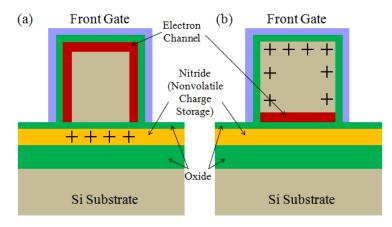

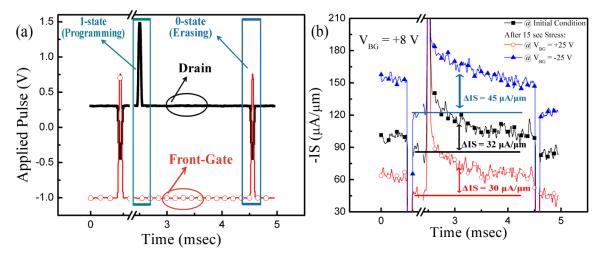

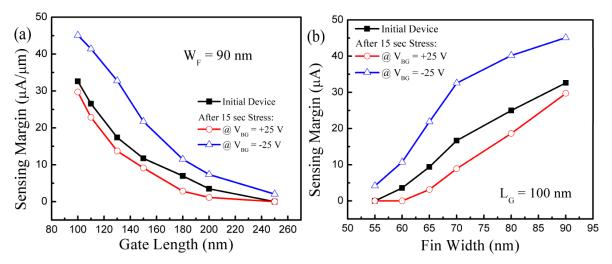

where