Propriétés électriques et modélisation des dispositifs MOS avanvés: dispositif FD-SOI, transistors sans jonctions (JLT) et transistor à couche mince à semi-conducteur d'oxyde amorphe. Electrical properties and modeling of advanced MOS devices: FD-SOI device, Junctionless Transistor, and Amorphous-Oxide-Semiconductor Thin Film Transistor

So Jeong Park

#### ▶ To cite this version:

So Jeong Park. Propriétés électriques et modélisation des dispositifs MOS avanvés: dispositif FD-SOI, transistors sans jonctions (JLT) et transistor à couche mince à semi-conducteur d'oxyde amorphe. Electrical properties and modeling of advanced MOS devices: FD-SOI device, Junctionless Transistor, and Amorphous-Oxide-Semiconductor Thin Film Transistor. Autre. Université de Grenoble; 239 -Korea University, 2013. Français. NNT: 2013GRENT075. tel-00954637

## HAL Id: tel-00954637 https://theses.hal.science/tel-00954637

Submitted on 3 Mar 2014

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITÉ DE GRENOBLE

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Nano Electronique et Nano Technologies (NENT)

Arrêté ministériel : 7 août 2006

Et de

#### **DOCTEUR DE KOREA UNIVERSITY**

Spécialité : Nano Electronique

Présentée par

# So Jeong PARK

Thèse dirigée par Laurent MONTÈS et Gérard GHIBAUDO codirigée par Gyu-Tae KIM

préparée au sein du Laboratoire IMEP-LAHC dans l'École Doctorale EEATS et de Nano Device Laboratory Korea University

Propriétés électriques et modélisation des dispositifs MOS avancés: FD-SOI dispositif, transistors sans jonctions (JLT) et transistor à couche mince semi-conducteur oxyde amorphe

Thèse soutenue publiquement le **23 Octobre 2013**, devant le jury composé de :

**Mme. Mireille MOUIS**

DR CNRS Alpes-IMEP/INPG, Président

M. Moongyu JANG

DR ETRI, Rapporteur

M. Jong Tae PARK

DR Incheon National University, Rapporteur

M. Gyu-Tae KIM

DR Korea University, Co-directeur de thèse

M. Laurent MONTÈS

MCF CNRS Alpes-IMEP/INPG, Co-directeur de thèse

M. Gérard GHIBAUDO

DR CNRS Alpes-IMEP/INPG, Directeur de thèse

# Dissertation for the Degree of Doctor of Philosophy

# Electrical properties and modeling of Advanced MOS devices: FD-SOI Tri-gate device, Junctionless Transistor, and Amorphous-Oxide-Semiconductor Thin Film Transistor

Presented by

So Jeong Park

School of Electrical Engineering

**Graduate School**

Korea University

February 2014

金 奎 兌 教授指導 博 士 學 位 論 文

# Electrical properties and modeling of Advanced MOS devices:

FD-SOI Tri-gate device, Junctionless Transistor, and Amorphous-Oxide-Semiconductor Thin Film Transistor

이 論文을 工學博士 學位論文으로 提出함.

2014 年 2 月

高麗大學校 大學院 電子電氣工學科

朴炤貞

차 炤 貞의 工學 博士學位論文 審査를 完了함.

# 2014 年 2 月

| 委員 | 長 | 7 THEY     | _hm       |

|----|---|------------|-----------|

| 委  | 員 | 科级港        | <b>建</b>  |

| 委  | 員 | 01 27 86   | _ fifferd |

| 委  | 員 | G. GHBAUDO | Entitul   |

| 委  | 員 | L. MONTES  | (印) 】     |

Dissertation for the degree of Doctor of Philosophy

# Electrical properties and modeling of Advanced MOS devices: FD-SOI Tri-gate device, Junctionless Transistor, and Amorphous-Oxide-Semiconductor Thin Film Transistor

#### By So Jeong PARK

October 2013

International co-supervising program between Korea University and Grenoble INP

#### **Thesis Advisors:**

## **Gyu-Tae KIM**

School of Electrical Engineering, Korea University, Seoul 136-701, Republic of Korea

# Laurent MONTÈS and Gérard GHIBAUDO

IMEP-LAHC, Grenoble INP-MINATEC, 3 Parvis Louis Néel, 38016 Grenoble, France

# **Contents**

| ABSTRACT                                                       |    |  |

|----------------------------------------------------------------|----|--|

| INTRODUCTIONCHAPTER 1 THEORETICAL BACKGROUND                   |    |  |

| CHAPTER 1 THEORETICAL BACKGROUND                               | 18 |  |

| 1 DOWN SCALING OF MOSFET                                       | 19 |  |

| 1.1 General down-scaling rules of MOSFET                       | 19 |  |

| 1.2 Scaling effects on device performance                      | 20 |  |

| 2 MOBILITY                                                     | 23 |  |

| 2.1 Conductivity mobility                                      | 24 |  |

| 2.2 Effective mobility                                         | 25 |  |

| 3 DOMINANT SCATTERING EFFECTS IN MOSFET                        | 26 |  |

| 4 THE EFFECT OF TEMPERATURE ON ELECTRICAL CHARACTERISTICS IN   |    |  |

| MOSFET                                                         | 28 |  |

| 4.1 Variation of threshold voltage with temperature            | 28 |  |

| 4.2 Variation of subthreshold slope with temperature           | 30 |  |

| 4.3 Variation of carrier concentration with temperature        | 30 |  |

| 5 THE SERIES RESISTANCE AND THE VARIATION OF CHANNEL LENGTH IN |    |  |

| MOSFET                                                         | 31 |  |

| 6 THE SUBSTRATE BIAS EFFECT ON ELECTRICAL CHARACTERISTICS IN   |    |  |

| MOSFET                                                         | 32 |  |

| 7 CONDUCTION IN AMORPHOUS OXIDE SEMICONDUCTOR THIN FILM        |    |  |

| TRANSISTOR (AOS TET)                                           | 34 |  |

| CHAPTER 2 EXPERIMENTAL BACKGROUND                                   | 37   |

|---------------------------------------------------------------------|------|

| 1 MEASUREMENT TECHNIQUE TO AVOID ERRORS                             | 38   |

| 1.1 The limit of voltmeter                                          | 38   |

| 1.2 The guarding technique                                          | 38   |

| 2 ELECTRICAL CHARACTERIZATION AND ANALYSIS                          | 40   |

| 2.1 Y-function                                                      | 40   |

| 2.2 The split C-V method                                            | 41   |

| 2.3 Defining the threshold voltage                                  | 42   |

| 2.4 Defining the series resistance and the effective channel length | 42   |

| 2.4.1 TLM method                                                    | 42   |

| 2.4.2 Four-probe method                                             | 43   |

| 2.5 Defining the trap density                                       | 44   |

| 2.5.1 Trap density from subthreshold swing                          | 44   |

| 2.5.2 Trap density from 1/f noise                                   | 44   |

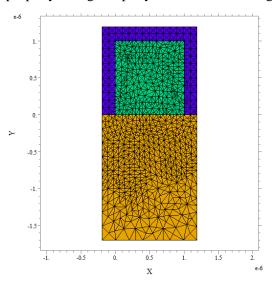

| 2.6 2-D numerical simulations                                       | 46   |

| CHAPTER 3 SIDEWALL MOBILITY AND SERIES RESISTANCE IN MUL            | TI-  |

| CHANNEL TRI-GATE MOSFET                                             | 48   |

| 1 INTRODUCTION                                                      | 49   |

| 2 EXPERIMETAL DETAILS                                               | 49   |

| 3 RESULTS AND DISCUSSION                                            | 51   |

| 3.1 Sidewall mobility in multi-channel tri-gate MOSFET              | 51   |

| 3.2 Series Resistance in multi-channel tri-gate MOSFET              | 58   |

| 4 CONCLUSION                                                        | 63   |

| CHAPTER 4 IMPACT OF CHANNEL WIDTH ON BACK BIASING EFFEC             | T IN |

| TRI-GATE MOSFET                                                                                                                                                        | 66    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1 INTRODUCTION                                                                                                                                                         | 67    |

| 2 EXPERIMETAL DETAILS                                                                                                                                                  | 67    |

| 1 INTRODUCTION                                                                                                                                                         | 69    |

| 3.1 Back biasing effect on I-V characteristics and gate-to-channel capacitance                                                                                         | 69    |

| 3.2 2-D numerical simulation of the back biasing effect in tri-gate MOSFET                                                                                             | TAILS |

| 3.1 Back biasing effect on I-V characteristics and gate-to-channel capacitance 3.2 2-D numerical simulation of the back biasing effect in tri-gate MOSFET 4 CONCLUSION |       |

| CHAPTER 5 BACK BIASING EFFECTS IN TRI-GATE JUNCTIONLESS                                                                                                                |       |

| TRANSISTORS                                                                                                                                                            | 81    |

| 1 INTRODUCTION                                                                                                                                                         | 82    |

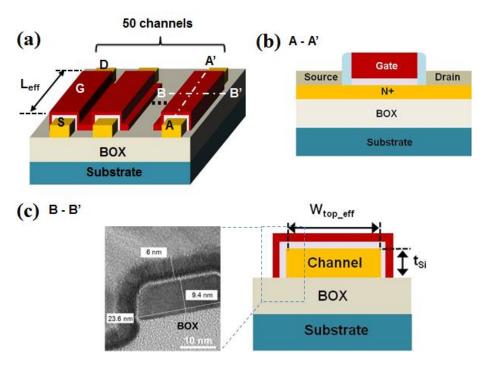

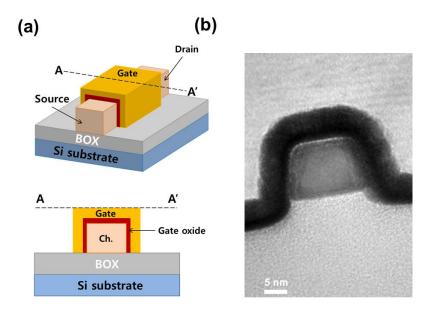

| 2 EXPERIMETAL DETAILS                                                                                                                                                  | 83    |

| 3 RESULTS AND DISCUSSION                                                                                                                                               | 83    |

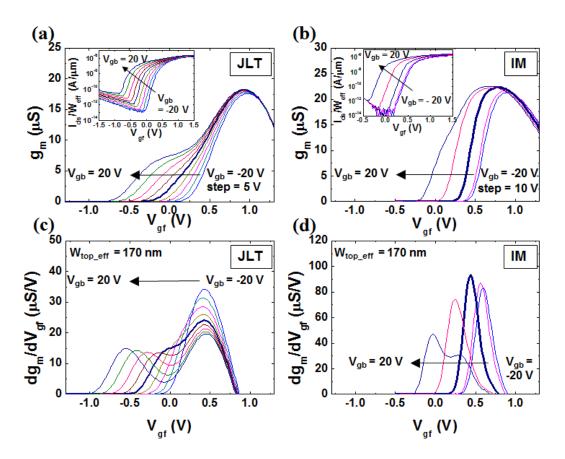

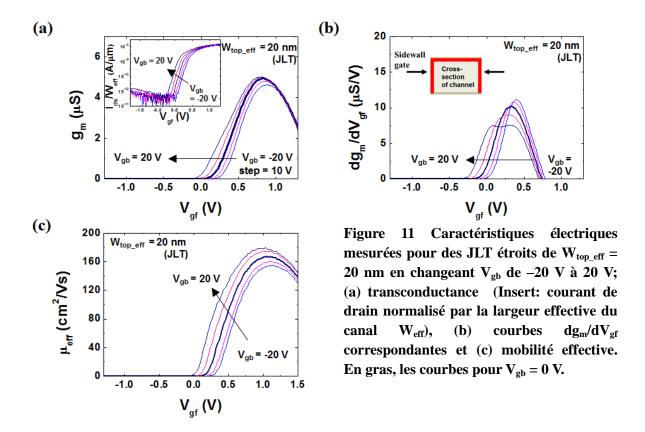

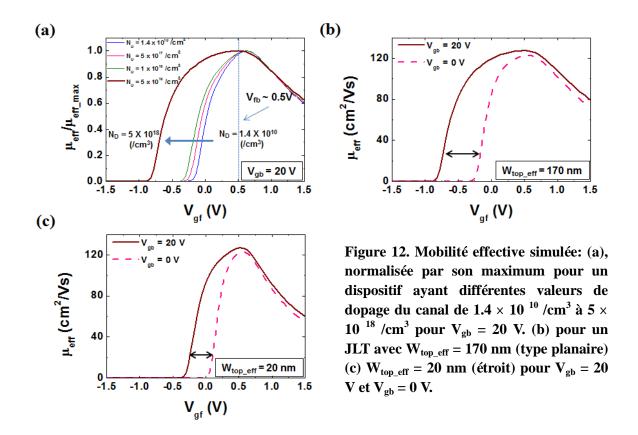

| 3.1 The back bias effect on JLTs                                                                                                                                       | 83    |

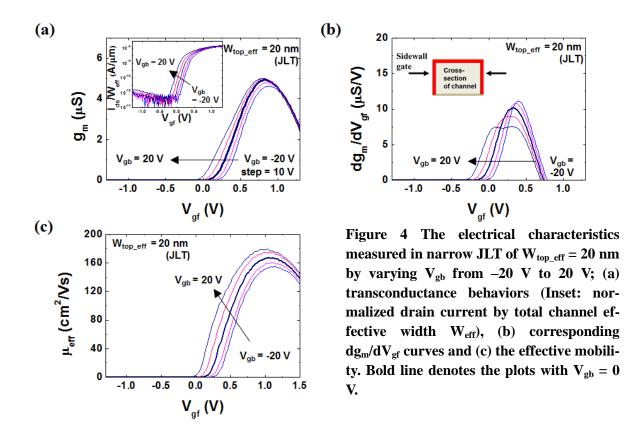

| 3.2 The back bias effect on narrow JLTs                                                                                                                                | 85    |

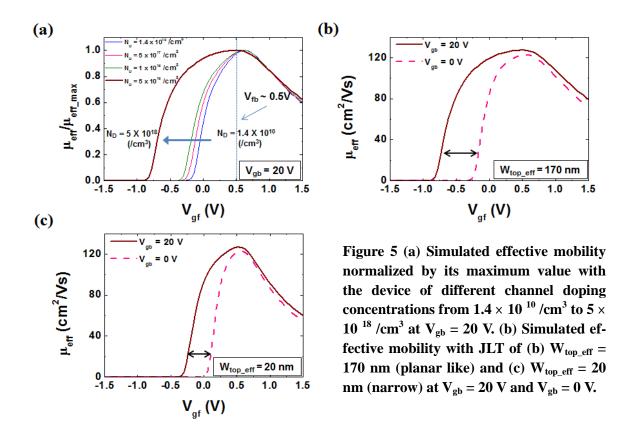

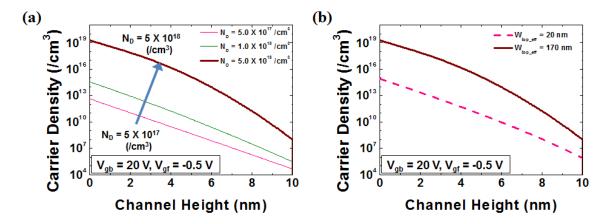

| 3.3 2-D numerical simulation results of the back bias effect                                                                                                           | 86    |

| 4 CONCLUSION                                                                                                                                                           | 88    |

| CHAPTER 6 STATIC ELECTRICAL CHARACTERIZATION AND LOW                                                                                                                   |       |

| FREQUENCY NOISE OF A-INHFZNO THIN FILM TRANSISTORS                                                                                                                     | 92    |

| 1 INTRODUCTION                                                                                                                                                         | 93    |

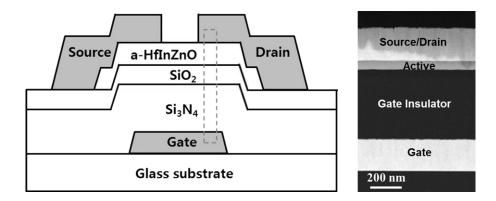

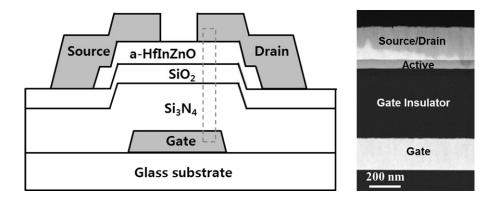

| 2 EXPERIMETAL DETAILS                                                                                                                                                  | 93    |

| 3 RESULTS AND DISCUSSION                                                                                                                                               | 94    |

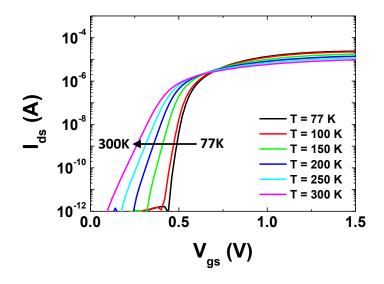

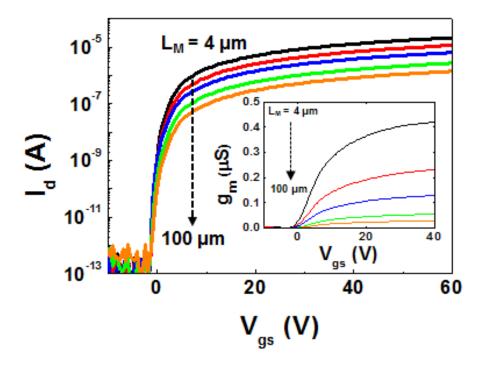

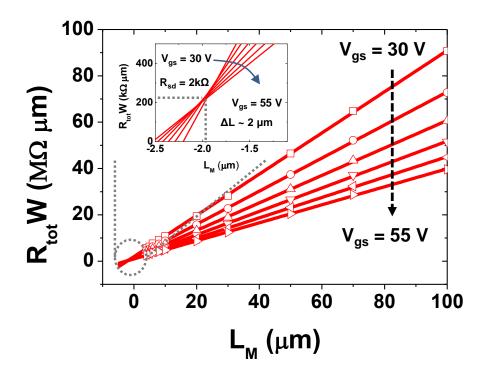

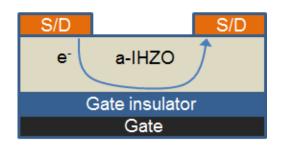

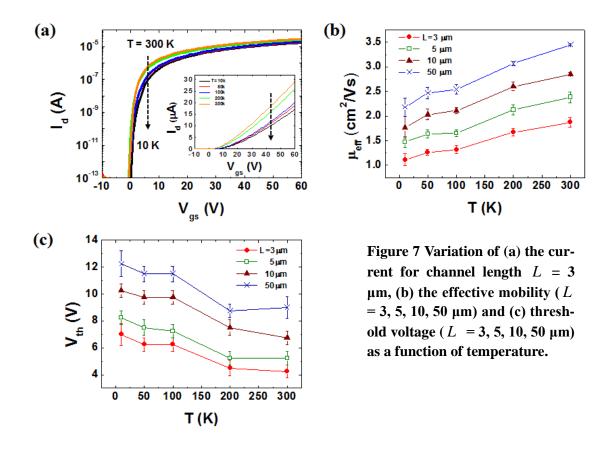

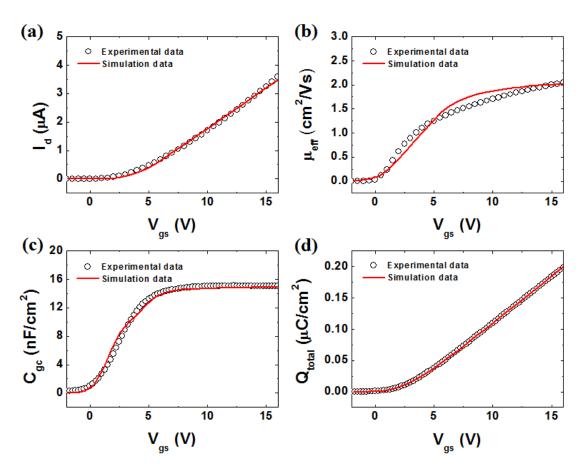

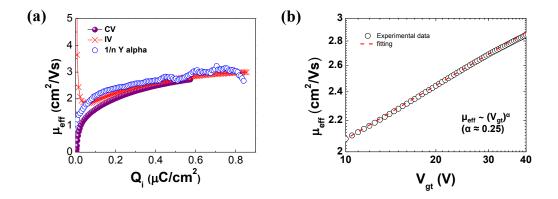

| 3.1 Static characteristics at room and low temperatures                                                                                                                | 94    |

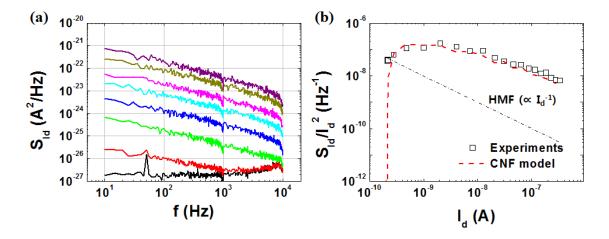

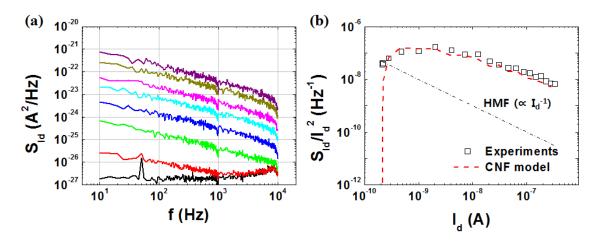

| 3.2 LF Noise characteristics                                                                                                                                           | 101   |

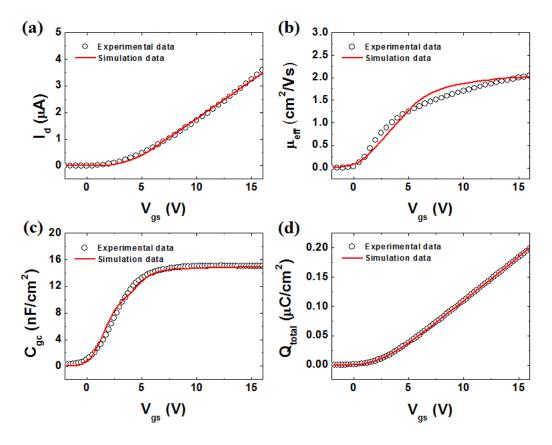

| 3.3 Numerical simulation                                                                                                                                               | 102   |

| 4 CONCLUSION                                            | 105   |

|---------------------------------------------------------|-------|

| CONCLUSIONS & PERSPECTIVE                               | 109   |

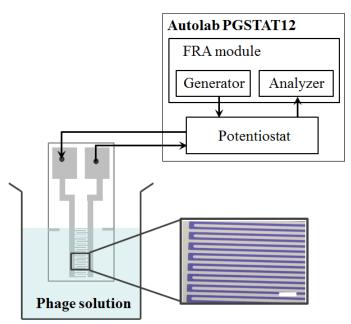

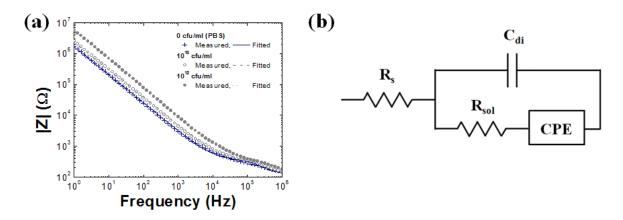

| APPENDIX 1: IMPEDANCE STUDY WITH BACTERIOPHAGE SOLUTION | N 112 |

| APPENDIX 2: PREAMP FOR SIMPLE MEASUREMENT               | 117   |

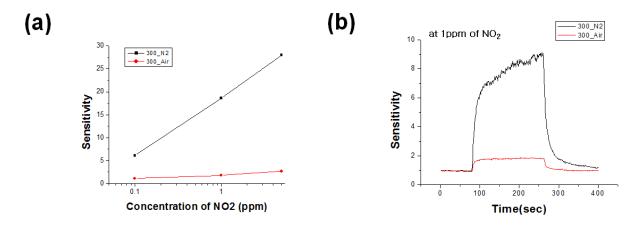

| APPENDIX 3: ZNO NANOROD GAS SENSORS                     | 120   |

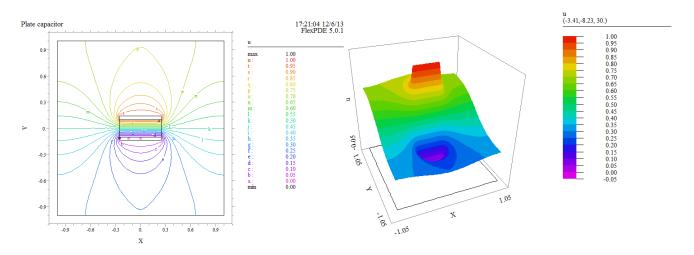

| APPENDIX 4: EXAMPLE OF FLEX-PDE SIMULATION SCRIPT       | 123   |

| PUBLICATION LIST                                        | 125   |

| 국문초록                                                    | 128   |

| RÉ SUMÉ FRANÇ AIS                                       | 131   |

# **ABSTRACT**

Novel advanced metal-oxide semiconductor (MOS) devices such as fully-depleted-silicon-oninsulator (FD-SOI) Tri-gate transistor, junctionless transistor, and amorphous-oxide-semiconductor thin film transistor were developed for continuing down-scaling trend and extending the functionality of CMOS technology, for example, the transparency and the flexibility. In this dissertation, the electrical characteristics and modeling of these advanced MOS devices are presented and they are analyzed. For the theoretical basis, at first, the scaling effect in MOS devices was briefly covered. With downscaling trends, CMOS devices technology has scaling effects such as short channel effects and narrow channel effects. While the device scale is shrunk, the general scaling rule can be applied to keep the device performance. And mobility, the important parameter to characterize the device can be defined as conductivity mobility and the mobility in metal-oxide semiconductor field effect transistor (MOSFET). The effective mobility in MOSFET is affected by several scattering mechanisms, which mainly consist of lattice scattering, ionized impurity scattering, and surface roughness scattering. Accordingly, the effect of dominant scattering effects is shown as device operation influenced by temperature and the effective field. Besides, the performance of the device is varied by the series resistance and the substrate bias. At last, the conduction in amorphous oxide semiconductor thin film transistor incorporating the band-tail states was introduced.

For the measurement of the electrical characteristics of MOSFET, the proper measurement equipment should be utilized. It is worth to note that several kinds of voltmeter have different measurement limit each other. The practical tips for precise measurements such as the guarding technique are also important to avoid possible measurement errors. The electrical parameters can be extracted by the characterization methods such as Y-function and C-V measurement technique. In addition, there are extraction methods for electrical parameter, for example, the threshold voltage, the series resistance and trap density. 2-dimensional (2-D) numerical simulation is also indispensable tool for the proper physical interpretation of electrical characteristics in MOSFET.

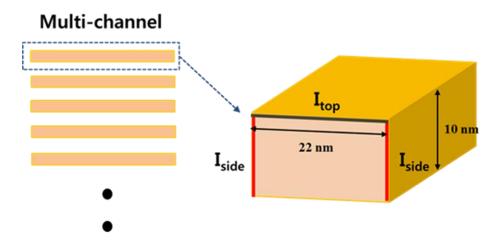

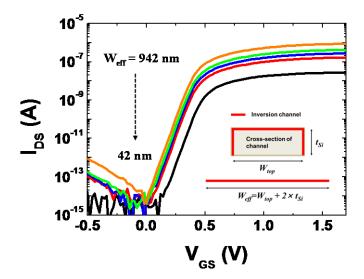

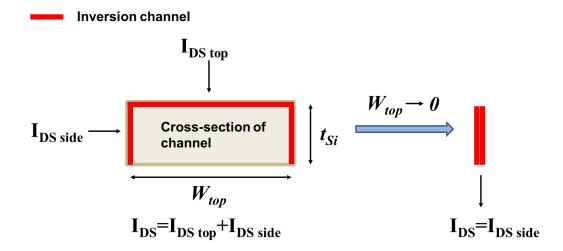

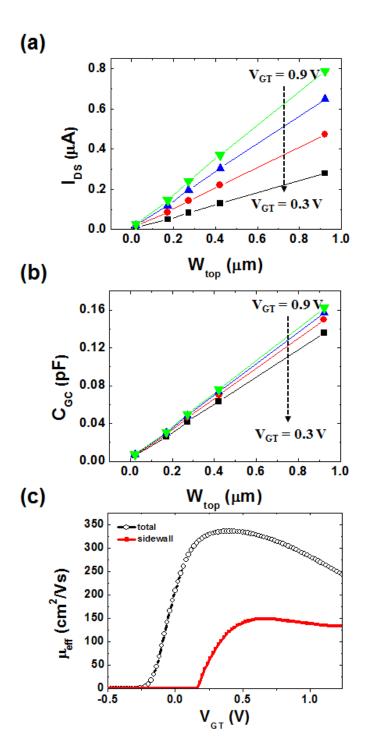

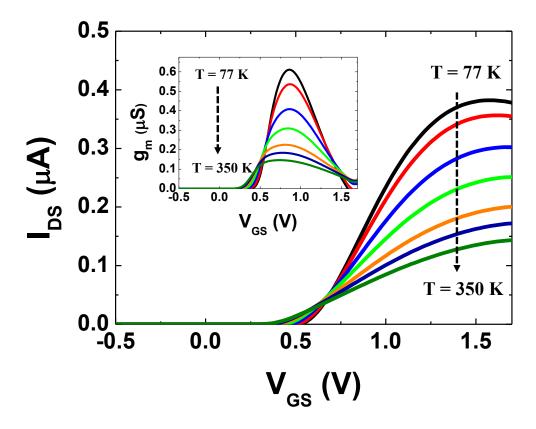

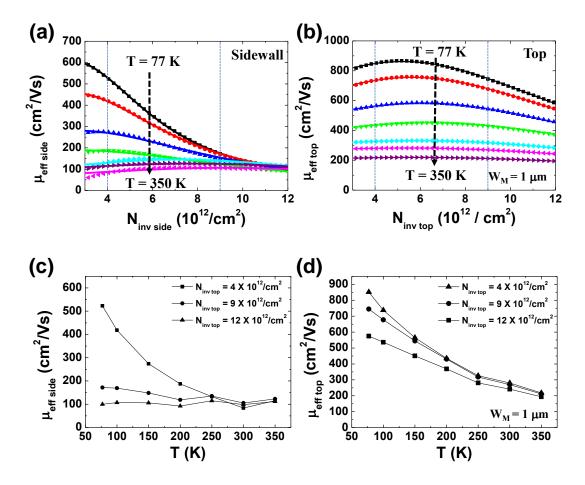

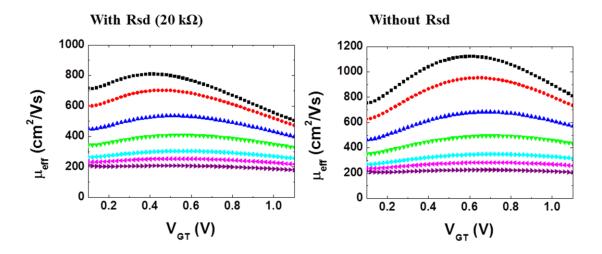

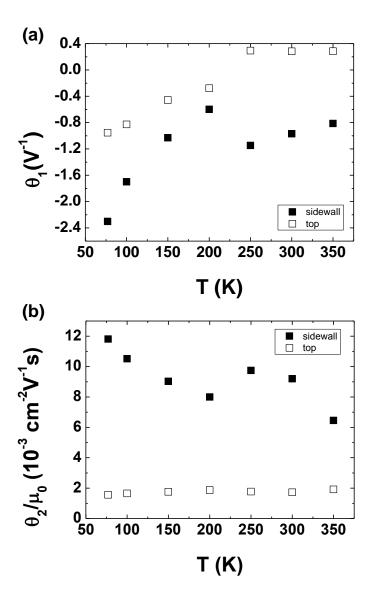

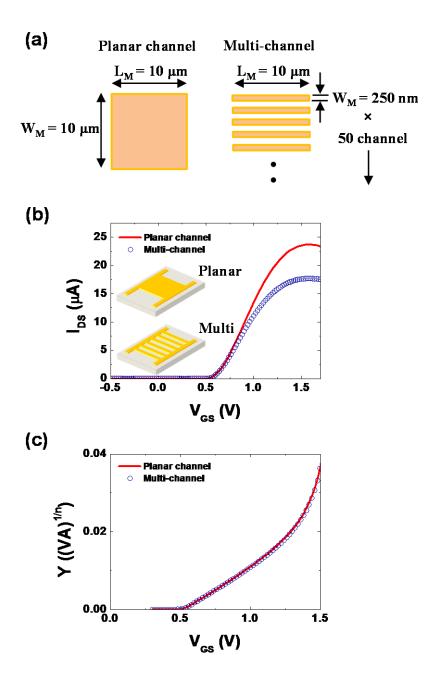

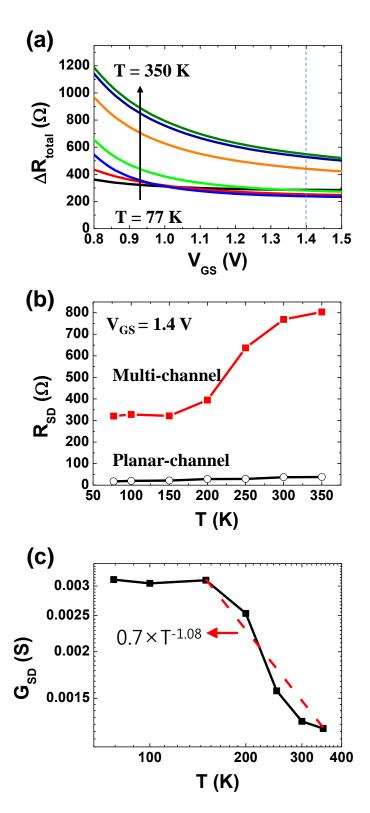

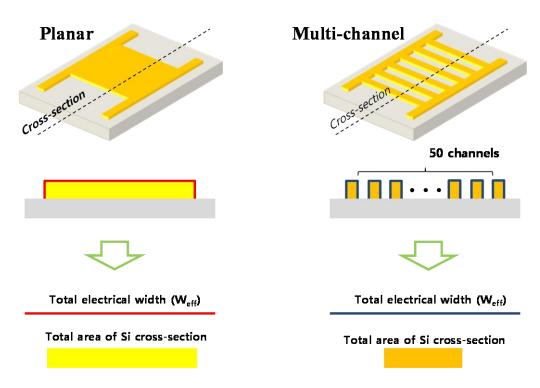

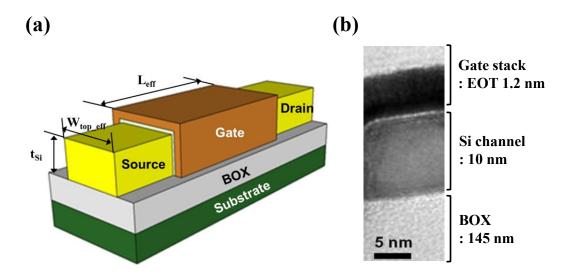

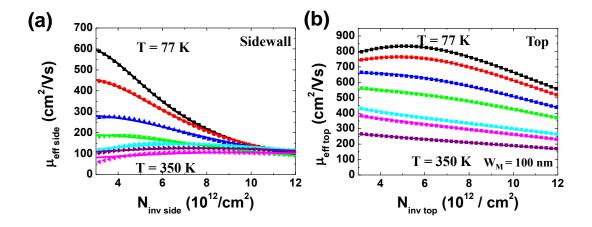

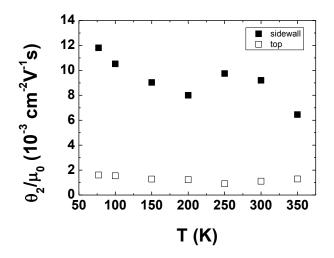

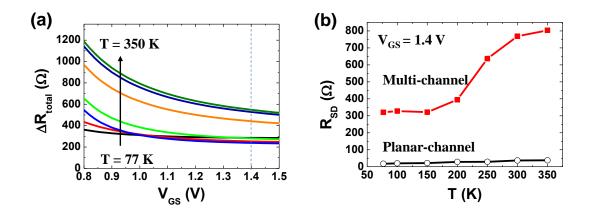

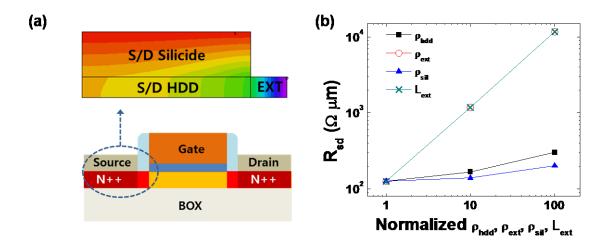

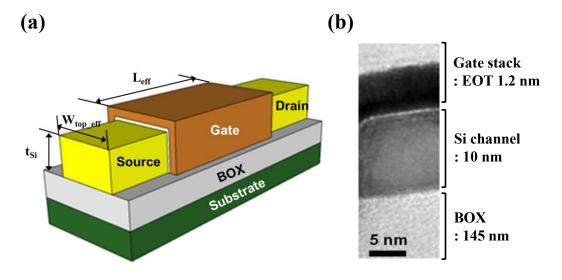

The sidewall mobility trends with temperature in multi-channel tri-gate MOSFET showed that the sidewall conduction is dominantly governed by surface roughness scattering. The degree of surface roughness scattering was evaluated with modified mobility degradation factor. With these extracted parameters, it was noted that the effect of surface roughness scattering can be higher in inversion-mode nanowire-like transistor than that of FinFET. The series resistance of multi-channel tri-gate MOSFET was also compared to planar device having same channel length and channel width of multi-channel device. The higher series resistance was observed in multi-channel tri-gate MOSFET. It was identified, through low temperature measurement and 2-D numerical simulation, that it could be attributed to the variation of doping concentration in the source/drain extension region in the device.

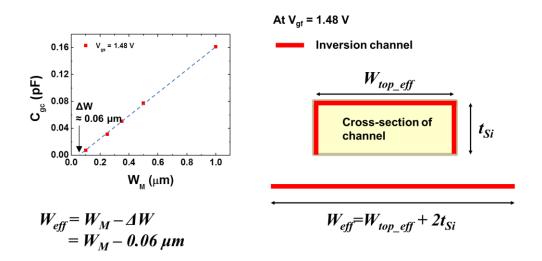

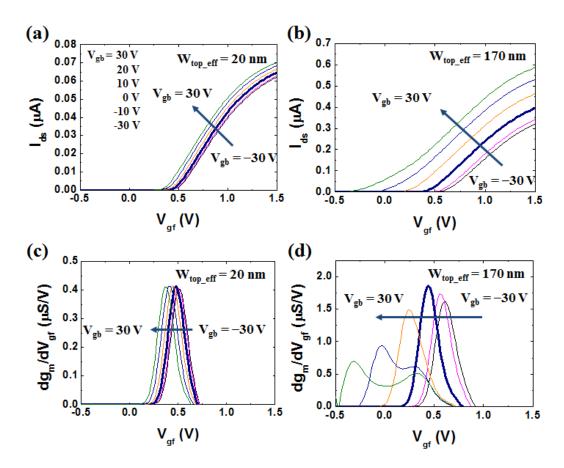

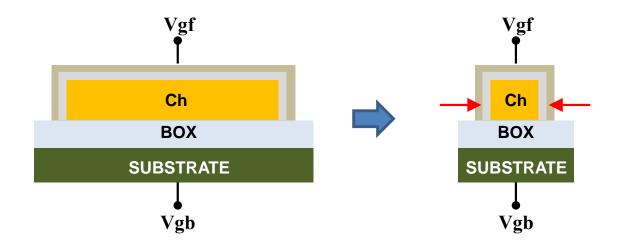

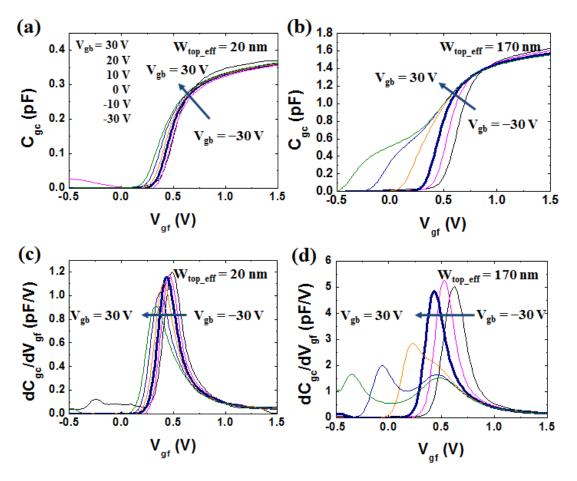

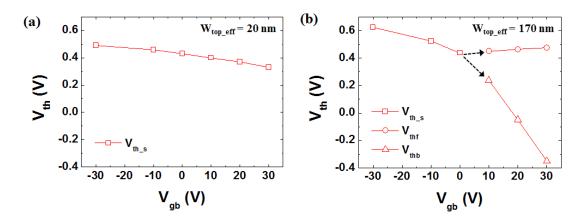

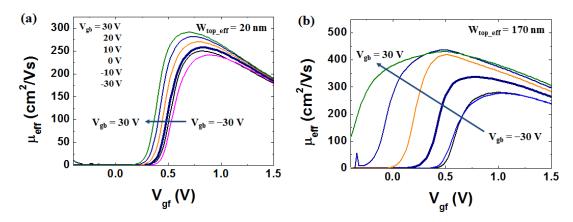

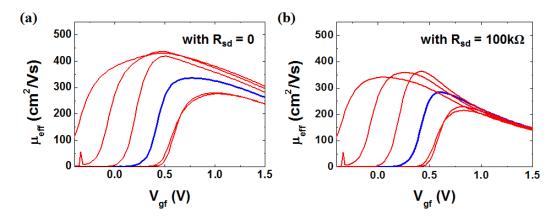

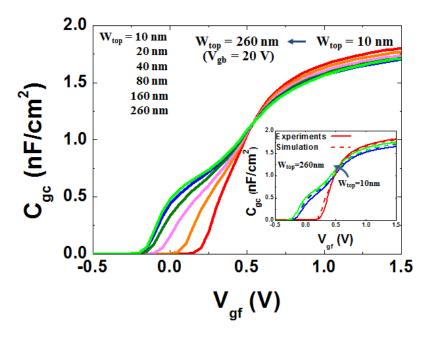

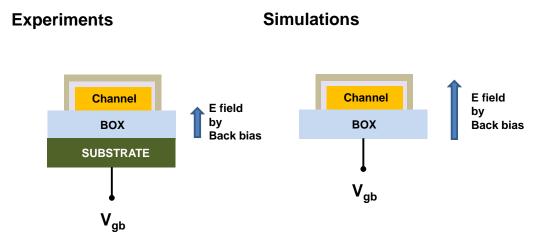

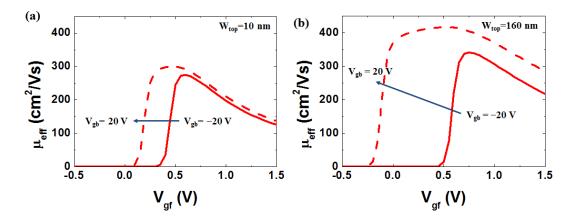

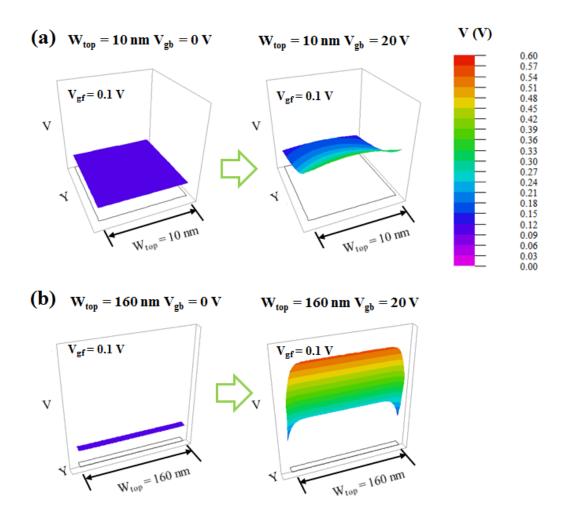

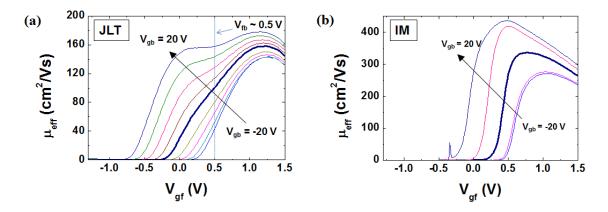

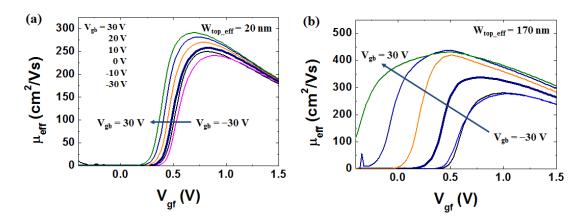

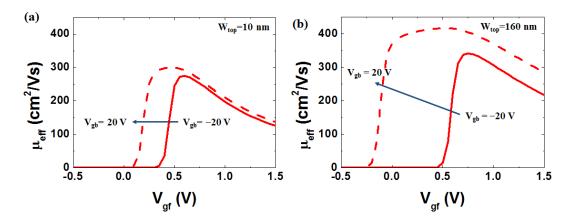

The impact of channel width on back biasing effect in n-type tri-gate MOSFET on SOI material was also investigated. The suppressed back bias effects was shown in narrow device ( $W_{top\_eff} = 20$  nm) due to higher control of front gate on overall channel, compared to the planar device ( $W_{top\_eff} = 170$  nm). The variation of effective mobility in both devices was analyzed with different channel interface of the front channel and the back channel. In addition, 2-D numerical simulation of the the gate-to-channel capacitance and the effective mobility successfully reconstructed the experimental observation. The model for the effective mobility was inherited from two kinds of mobility degradations, i.e. different mobility attenuation along lateral and vertical directions of channel and additional mobility degradation in narrow device due to the effect of sidewall mobility.

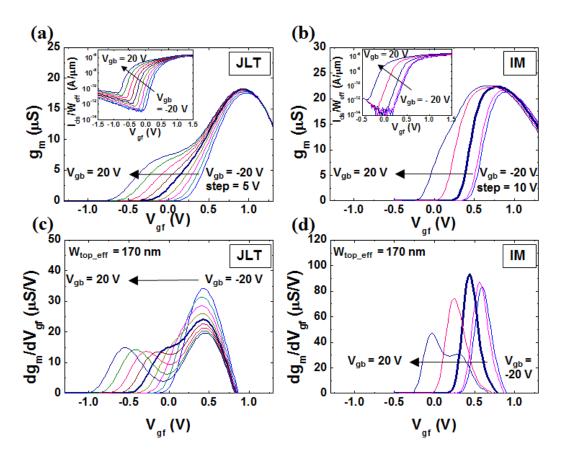

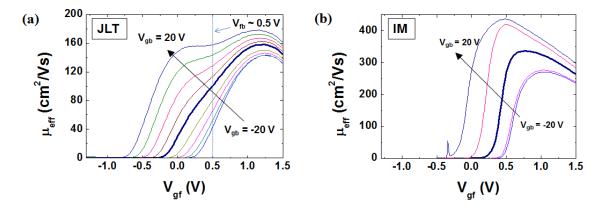

With comparison to inversion-mode (IM) transistors, the back bias effect on tri-gate junctionless transistors (JLTs) also has been investigated using experimental results and 2-D numerical simulations.

Owing to the different conduction mechanisms, the planar JLT shows more sensitive variation on the performance by back biasing than that of planar IM transistors. However, the back biasing effect is significantly suppressed in nanowire-like JLTs, like in extremely narrow IM transistors, due to the small portion of bulk neutral channel and strong sidewall gate controls.

Finally, the characterization method was comprehensively applied to a-InHfZnO (IHZO) thin film transistor (TFT). The series resistance and the variation of channel length were extracted from the transfer curve. And mobility values extracted with different methods such as split C-V method and modified Y-function were compared. The static characteristic evaluated as a function of temperature shows the degenerate behavior of a-IHZO TFT inversion layer. Using subthreshold slope and noise characteristics, the trap information in a-IHZO TFT was also obtained. Based on experimental results, a numerical model for a-IHZO TFT was proposed, including band-tail states conduction and interface traps. The simulated electrical characteristics were well-consistent to the experimental observations.

For the practical applications of novel devices, the electrical characterization and proper modeling are essential. These attempts shown in the dissertation will provides physical understanding for conduction of these novel devices.

Keywords: advanced MOS transistors, multi-channel tri-gate MOSFET, junctionless transistor, side-wall mobility, surface roughness scattering, series resistance, electrostatic coupling, channel width variation, back bias effect, 2-D numerical simulation, a-InHfZnO, thin film transistor (TFT), DC characteristics, electrical parameter extraction, low frequency noise (LFN), numerical simulation.

## INTRODUCTION

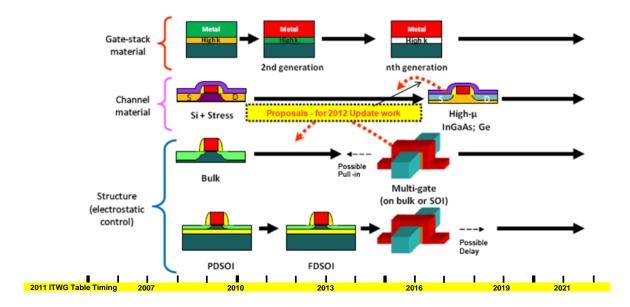

The most important trend of CMOS technology is to decrease the minimum feature size and cost-perfunction. According to the ITRS roadmap, the minimum feature size of MOSFET in 2026 is predicted as 6 nm [1]. The CMOS scaling consists of two approaches, geometrical scaling and equivalent scal-Geometrical scaling reduces the physical feature size according to Moore's law, inspiring semiconductor industry. The equivalent scaling improves the performance of the devices and is increasingly important from nowadays and new design/processing or software solutions are needed for the scaling. As the size of device is shrunk extensively, more efforts to maintain the performance of devices is dedicated against short channel effects, dopant-induced fluctuation in threshold voltage, etc [2-4]. For example, high-k gate dielectric has been used to scale down the equivalent oxide thickness (EOT) with keeping tolerable gate leakage current. Metal gate electrodes are employed in the CMOS device of recent generation for efficient gate control to channel since even degenerately doped polysilicon gate reduces metal-oxide-semiconductor capacitance with its depletion layer [5]. Higher-k dielectric and appropriate metal gates are required for further scaling as shown in Fig. 1. In addition, metal gate provides low gate resistance and efficient heat sink which is for power aspect. To improve the channel carrier low-field mobility, strained silicon is also used as a channel material [6, 7] and higher mobility materials, for example, SiGe, Ge, and III-V compound semiconductor will be used. (Fig. 1) Instead of thick body partially-depleted-silicon-on-insulator (PD-SOI) or bulk MOSFET, ultra-thin body fully-

Figure 1 2011 ITRS "Equivalent Scaling" Process Technologies Timing [1]

#### INTRODUCTION

depleted-silicon-on-insulator (FD-SOI) and multiple-gate MOSFET are expected as potential device to eliminate the variation threshold voltage corresponding to increased doping concentration.

On the other hand, various channel material, device architecture and technologies are required to meet the need of ultra-low power consumption and new functionality. For example, thin film transistor (TFT) is a promising device for flexible and transparent electronic circuit. The active channel material is deposited at low temperature (< 600 °C), thus glass substrate and flexible substrate can be used and the channel material is amorphous. TFT can be widely used for large-area transparent and flexible display [8, 9] which are challenging with conventional semiconductor processing. For these applications, TFT is feasible device type since the required device performance such as response speed and the driving current is not quite critical while it is not used for integrated circuits owing to its low channel mobility.

For the realization of these advanced devices, it is required to investigate their electrical properties compared to classical transistor and to optimize their performance. To perform this task, physical parameters of these new devices should be evaluated based on analysis method of classical silicon devices which has been enormously investigated during previous decades. The development of their device model and the investigation of special mechanisms governing their electrostatics accompanying with special electrical properties and non-conventional effects should be carried

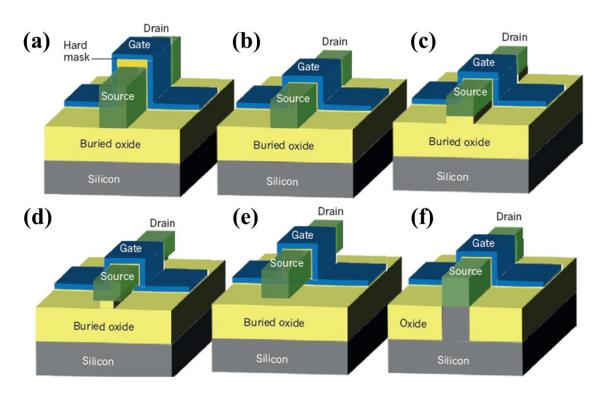

Figure 2 Multigate MOSFETs (a) SOI FinFET (b) SOI triple-gate MOSFET (c) SOI  $\Pi$ -gate MOSFET (d) SOI  $\Omega$ -gate MOSFET (e) SOI gate-all-around MOSFET (f) A bulk tri-gate MOSFET [10]

out.

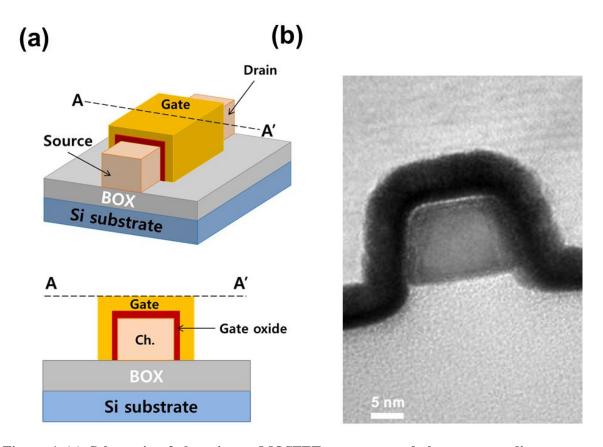

Fully-depleted silicon-on-insulator (FD-SOI) Trigate device is one of the new potential structures for continuing scaling down CMOS technology [10]. Indeed, FD-SOI structure eliminates punch-though effect with the shallow source/drain region and it can be free from the high channel doping problem [11]. It is very difficult to control the concentration of channel doping in extremely small device and spatial random dopant fluctuation seriously degrades the device reliability. Low channel doping concentration of FD-SOI device also enables to achieve enhanced channel mobility. Furthermore, the parasitic capacitance between interconnect metal lines and substrate is reduced owing to the buried oxide and the switching speed is enhanced. The reduction of parasitic devices, called as latch-up phenomenon in CMOS ICs is another benefit of using FD-SOI structure. With FD-SOI structure, the implementation of multi-gate structure can also be interesting to enhance device performance. Multi-gate MOSFET shows the best subthreshold swing and significant reduction of off-state current [12, 13]. It shows better control of short channel effects [14] since the influence by drain field on the channel is reduced [15]. As shown in Fig. 2, the multi gate MOSFET includes FinFET, tri-gate MOSFET, Π-gate MOSFET, Ω-gate MOSFET, gate-all-around MOSFET, and a bulk tri-gate MOSFET. In recent device simulation studies, it was shown that the gate-all-around device with gate length of 3 nm could work well without significant short channel effects [16]. In addition, multi-gate device, having large channel width, can be used to drive higher current than single gate device. For double gate SOI device, threshold voltage is low, compared to the bulk single gate SOI device and DIBL effect is reduced [17]. FinFET also shows many advantages such as increased drive current, reduced short channel effect and shorter access time for memory applications [18].

In 2011, among multigate structure, Trigate MOSFET was introduced to the mass industrial production by announcement, Intel will use tri-gate structure for 22-nm technology. Trigate means that a single gate electrode folded to cover three sides of transistor [19]. The gate is a common gate, thus, three gates are electrically connected and apply the same gate bias. A Trigate MOSFET shows improved gate electrostatic control to the channel and this effectively reduces short channel effects [20, 21]. It provides strong gate control over not only at the top surface channel but also on two sidewall channels (lateral channels) [22, 23]. Due to their gate control property, they have less stringent requirements for the silicon channel dimensions and larger driving current per unit area of the silicon wafer can be achieved [21, 24]. Especially, the introduction of metal gate on the trigate structure enhances the oncurrent and eliminates the leakage current as well as inverter delay. In narrow trigate transistors, it was shown that the device has the immunity against substrate effects caused by drain-induced virtual substrate biasing and hot carrier-induced charge build-up in the buried oxide [25]

On the other hand, the formation of ultra-shallow junctions with abrupt high channel doping concentration gradients is still very difficult as the device size becomes extremely small. The junctionless

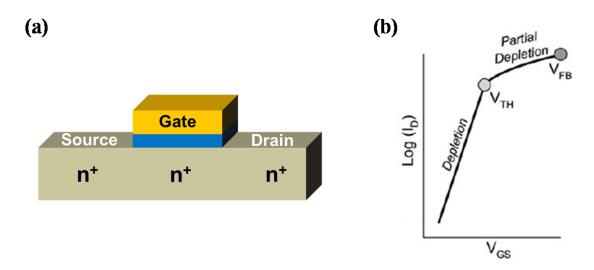

transistor (JLT) can be free from this difficulty since it doesn't have junctions or doping concentration gradient corresponding to junction (Fig. 3). In addition, JLTs using silicon nanowires are compatible with CMOS process.

Figure 3 (a) Longitudinal cross-section schematic of a junctionless transistor, showing the doping profiles and (b) Drain current (log scale) versus gate voltage in a heavily-doped junctionless transistor [18]

The junctionless transistor is a "normally on" device, however, the difference of the work function between the gate electrode and the channel silicon make the flatband voltage  $V_{FB}$  and the threshold voltage  $V_{TH}$  shifted. Below threshold, JLT is fully depleted and the carrier concentration of a part of channel of JLT reaches initial doping concentration  $N_D$  at its threshold voltage. As increasing the gate voltage the region where carrier concentration is same with  $N_D$  becomes larger in cross-section of the channel. Finally when the channel cross section is full with region of carrier concentration  $n=N_D$ , the gate bias corresponds to the flat band voltage. The conduction mechanism in JLT was presented in Fig. 3(b).

The fabrication of JLTs is very simple since only one doping concentration is needed from source region to drain region. The subthreshold slope of JLTs are excellent, exhibiting 64 mV/decade at room temperature and very close value to the ideal value of subthreshold slope in the temperature range of 225-475 K [26]. Different from the general concerning, the mobility is not seriously degraded by high doping concentration in JLTs since the electric field in the channel is almost zero, allowing bulk mobility values [27]. The carrier mobility of JLT is lower than that of IM device at room temperature owing to the mobility dominantly governed by ionized impurity scattering. However, the decrease of mobility in JLT is less than 7 % when the temperature is increased up to 200 °C while it was about 36 % with IM device [28]. Furthermore, high  $I_{on}/I_{off}$  ratio, lower DIBL and reduced short-channel ef-

fects were reported in nanowire-like JLTs [29,30]. It can be expected that the variation of the threshold voltages of JLTs is below 35 mV with recent technology controlling channel thickness below 0.2 nm since the variation of threshold voltage is not severe when the channel thickness of JLT is small enough [31]. The variation of L<sub>eff</sub> caused by gradient of doping concentration at junction boundary is not observed in JLT.

However, JLTs are more sensitive than undoped IM devices to doping fluctuation due to its high doping concentration [32]. Moreover, Rios et al reported that JLT devices show degraded gate control and short-channel behaviours and increased off current while they exhibit better mobility at moderate doping concentration [33]. There is also a theoretical approach showing significant variation of threshold voltage in JLTs due to the dopant fluctuation when  $L_g = 20$  nm [34].

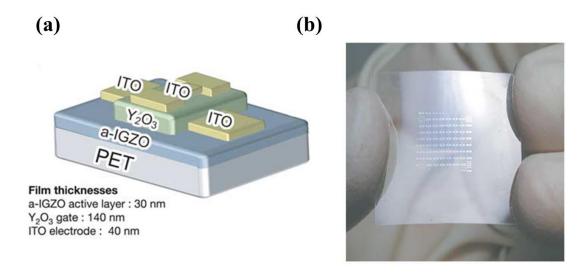

Another candidate for advanced MOS device technology, transparent amorphous oxide semiconductor (AOS) based TFTs have gotten great interest for the applications in flexible displays, flat-panel displays, optical sensor, solar cells, transparent and/or flexible electronic devices since they can be fabricated on plastic substrates at relatively low temperature [9, 35]. They also can be used for the highly uniform and large-area displays with low cost [36]. Among the AOS TFT, a-InGaZnO (a-IGZO) TFT has been intensively studied because it exhibits high mobility, a good on/off ratio and sufficient electrical stability [37]. It is mostly used for the application of switching/driving devices in active-matrix liquid crystal display (AMLCD) and active-matrix organic light emitting diode display (AMOLED) back planes due to its excellent electrical properties, compared to a-Si TFT [9].

The scaling effects on electrical properties of a-IGZO TFTs were investigated by Cho et al [38]. They examined the threshold voltage shift, subthreshold swing degradation and the field-effect mobility in scaled-down devices owing to short-channel effect and contact resistance. Stability issue in AOS TFTs

Figure 4 (a) Schematic of a IGZO TFT fabricated on a plastic sheet, PET. (c) A photograph of transparent a-IGZO TFT on flexible sheet [36].

#### INTRODUCTION

has also been intensively studied by researchers. In many research results, the variation of threshold voltage in AOS TFT after electrical stress comes from charge trapping/detrapping at, or close to, channel/insulator interface [39-41]. It takes times, from few minutes to few hours, to recover the original properties of AOS TFT [42, 43] and, in some cases, heating treatment is required for the recovery. It is reported that using passivation layer improves the stability of AOS TFT [44, 45]. For what concerns the dielectric layer, high-k material increases the gate capacitance, leading to low subthreshold swing though high trap density. But most of high-k dielectric has issues of high leakage current, low breakdown voltage and rough surface [46, 47]. Park et al reported that the introduction of Hf to channel materials enables to fabricate highly stable and high performance TFT devices. Concerning the reliability of AOS TFT, the investigation of interface states is also important. Low frequency noise measurements in AOS TFTs have provided meaningful trap information in AOS TFTs [48-50]

The objective of this thesis lies on the development of the advanced semiconductor device models and the characterization of the conduction mechanisms in these devices. This thesis covers three kinds of devices: inversion-mode trigate FD-SOI MOSFET, Junctionless transistor and AOS TFT. In chapter 1, the trend of device technology and effects corresponding to scaling are briefly introduced with theoretical background of the thesis. And some measurement precautions and electrical characterization methods, needed to study the electrical conduction in devices are followed in chapter 2.

In Chapter 3, the sidewall mobility and the series resistance in multi-channel tri-gate MOSFET are discussed via low temperature characteristics and examined by 2-D numerical simulation.

The impact of channel width on back biasing effect in multi-channel tri-gate MOSFET and the analysis of mobility behavior corresponding to interface quality are presented in chapter 4.

The back bias effect on tri-gate junctionless transistors (JLTs) using experimental results and 2-D numerical simulations are described in chapter 5.

In chapter 6, electrical characterization of amorphous InHfZnO (a-IHZO) TFTs through static characteristic, low frequency noise characteristic and 2-D numerical simulation are summarized.

# References

- [1] "ITRS Roadmap. http://www.itrs.net."

- [2] J. P. Colinge, "Fully-depleted SOI CMOS for analog applications," *IEEE Transactions on Electron Device*, vol. 45, pp. 1010-1016, 1998.

- [3] O. Faynot, S. Cristoloveanu, A. Auberton-Herve, and C. Raynaud, "Performance and potential of ultrathin accumulation-mode SIMOX MOSFET's," *IEEE Transactions on Electron Devices*, vol. 42, pp. 713-719, 1995.

- [4] S. Pidin, T. Mori, K. Inoue, S. Fukuta, N. Itoh, E. Mutoh, *et al.*, "A novel strain enhanced CMOS architecture using selectively deposited high tensile and high compressive silicon nitride films," in *Electron Devices Meeting*, 2004. *IEDM Technical Digest. IEEE International*, 2004, pp. 213-216.

- [5] B. Ricco, R. Versari, and D. Esseni, "Characterization of polysilicon-gate depletion in MOS structures," *IEEE Electron Device Letters*, vol. 17, pp. 103-105, 1996.

- [6] K.-W. Ang, J. Lin, C.-H. Tung, N. Balasubramanian, G. S. Samudra, and Y.-C. Yeo, "Strained n-MOSFET With Embedded Source/Drain Stressors and Strain-Transfer Structure (STS) for Enhanced Transistor Performance," *IEEE Transactions on Electron Devices*, vol. 55, pp. 850-857, 2008.

- [7] G. Néau, F. Martinez, M. Valenza, J. Vildeuil, E. Vincent, F. Boeuf, *et al.*, "Impact of strained-channel n-MOSFETs with a SiGe virtual substrate on dielectric interface quality evaluated by low frequency noise measurements," *Microelectronics Reliability*, vol. 47, pp. 567-572, 2007.

- [8] H. Yabuta, M. Sano, K. Abe, T. Aiba, T. Den, H. Kumomi, *et al.*, "High-mobility thin-film transistor with amorphous InGaZnO channel fabricated by room temperature rf-magnetron sputtering," *Applied physics letters*, vol. 89, p. 112123, 2006.

- [9] J. C. Park, S. Kim, S. Kim, C. Kim, I. Song, Y. Park, *et al.*, "Highly Stable Transparent Amorphous Oxide Semiconductor Thin-Film Transistors Having Double-Stacked Active Layers," *Advanced Materials*, vol. 22, pp. 5512-5516, 2010.

- [10] I. Ferain, C. A. Colinge, and J.-P. Colinge, "Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors," *Nature*, vol. 479, pp. 310-316, 2011.

- [11] S. Dimitrijev, *Understanding semiconductor devices*: Oxford university press, 2000.

- [12] V. Subramanian, B. Parvais, J. Borremans, A. Mercha, D. Linten, P. Wambacq, *et al.*, "Planar bulk MOSFETs versus FinFETs: An analog/RF perspective," *IEEE transactions on electron devices*, vol. 53, pp. 3071-3079, 2006.

- [13] M. C. Lemme, T. Mollenhauer, W. Henschel, T. Wahlbrink, M. Baus, O. Winkler, et al.,

- "Subthreshold behavior of triple-gate MOSFETs on SOI material," *Solid-State Electronics*, vol. 48, pp. 529-534, 2004.

- [14] T. Sekigawa, "Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate," *Solid-State Electron*, vol. 27, p. 827, 1984.

- [15] B. Agrawal, V. De, J. Pimbley, and J. Meindl, "Short channel models and scaling limits of SOI and bulk MOSFETs," *IEEE Journal of Solid-State Circuits*, vol. 29, pp. 122-125, 1994.

- [16] L. Ansari, B. Feldman, G. Fagas, J.-P. Colinge, and J. C. Greer, "Simulation of junctionless Si nanowire transistors with 3 nm gate length," *Applied Physics Letters*, vol. 97, p. 062105, 2010.

- [17] H.-S. Wong, D. J. Frank, and P. M. Solomon, "Device design considerations for double-gate, ground-plane, and single-gated ultra-thin SOI MOSFET's at the 25 nm channel length generation," in *Electron Devices Meeting*, 1998. IEDM'98. Technical Digest., International, 1998, pp. 407-410.

- [18] A. Nazarov, Semiconductor-on-insulator materials for nanoelectronics applications: Springerverlag Berlin Heidelberg, 2011.

- [19] J.-P. Colinge, FinFETs and other multi-gate transistors: Springer, 2007.

- [20] J.-P. Colinge, "Multiple-gate soi mosfets," *Solid-State Electronics*, vol. 48, pp. 897-905, 2004.

- [21] E. Landgraf, W. Rösner, M. Städele, L. Dreeskornfeld, J. Hartwich, F. Hofmann, *et al.*, "Influence of crystal orientation and body doping on trigate transistor performance," *Solid-state electronics*, vol. 50, pp. 38-43, 2006.

- [22] R. Ritzenthaler, S. Cristoloveanu, O. Faynot, C. Jahan, A. Kuriyama, L. Brevard, *et al.*, "Lateral coupling and immunity to substrate effect in ΩFET devices," *Solid-state electronics*, vol. 50, pp. 558-565, 2006.

- [23] B. Doyle, B. Boyanov, S. Datta, M. Doczy, S. Hareland, B. Jin, *et al.*, "Tri-gate fully-depleted CMOS transistors: Fabrication, design and layout," in *VLSI Technology*, 2003. *Digest of Technical Papers*. 2003 Symposium on, pp. 133-134, 2003.

- [24] R. Chau, B. Doyle, J. Kavalieros, D. Barlage, A. Murthy, M. Doczy, *et al.*, "Advanced depleted-substrate transistors: single-gate, double-gate and tri-gate," *SOLID STATE DEVICES AND MATERIALS*, pp. 68-69, 2002.

- [25] K. Akarvardar, A. Mercha, S. Cristoloveanu, P. Gentil, E. Simoen, V. Subramanian, *et al.*, "A two-dimensional model for interface coupling in triple-gate transistors," *IEEE Transactions on Electron Devices*, vol. 54, pp. 767-775, 2007.

- [26] J.-P. Colinge, C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, *et al.*, "Nanowire transistors without junctions," *Nature nanotechnology*, vol. 5, pp. 225-229, 2010.

- [27] J.-P. Colinge, C.-W. Lee, I. Ferain, N. D. Akhavan, R. Yan, P. Razavi, *et al.*, "Reduced electric field in junctionless transistors," *Applied Physics Letters*, vol. 96, pp. 073510-

- 073510-3, 2010.

- [28] C.-W. Lee, A. Borne, I. Ferain, A. Afzalian, R. Yan, N. Dehdashti Akhavan, *et al.*, "High-temperature performance of silicon junctionless MOSFETs," *IEEE Transactions on Electron Devices*, vol. 57, pp. 620-625, 2010.

- [29] C.-H. Park, M.-D. Ko, K.-H. Kim, R.-H. Baek, C.-W. Sohn, C. K. Baek, *et al.*, "Electrical characteristics of 20-nm junctionless Si nanowire transistors," *Solid-State Electronics*, vol. 73, pp. 7-10, 2012.

- [30] C.-W. Lee, I. Ferain, A. Afzalian, R. Yan, N. D. Akhavan, P. Razavi, *et al.*, "Performance estimation of junctionless multigate transistors," *Solid-State Electronics*, vol. 54, pp. 97-103, 2010.

- [31] J. Colinge, A. Kranti, R. Yan, C. Lee, I. Ferain, R. Yu, *et al.*, "Junctionless nanowire transistor (JNT): Properties and design guidelines," *Solid-State Electronics*, vol. 65, pp. 33-37, 2011.

- [32] G. Ghibaudo, "Evaluation of variability performance of junctionless and conventional Trigate transistors," *Solid-State Electronics*, vol. 75, pp. 13-15, 2012.

- [33] R. Rios, A. Cappellani, M. Armstrong, A. Budrevich, H. Gomez, R. Pai, *et al.*, "Comparison of Junctionless and Conventional Trigate Transistors With Lg Down to 26 nm," *IEEE electron device letters*, vol. 32, pp. 1170-1172, 2011.

- [34] A. Gnudi, S. Reggiani, E. Gnani, and G. Baccarani, "Analysis of threshold voltage variability due to random dopant fluctuations in junctionless FETs," *IEEE Electron Device Letters*, vol. 33, pp. 336-338, 2012.

- [35] M. Kim, J. H. Jeong, H. J. Lee, T. K. Ahn, H. S. Shin, J.-S. Park, *et al.*, "High mobility bottom gate InGaZnO thin film transistors with SiOx etch stopper," *Applied Physics Letters*, vol. 90, p. 2114, 2007.

- [36] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, pp. 488-492, 2004.

- [37] T. Kamiya, K. Nomura, and H. Hosono, "Electronic structures above mobility edges in crystalline and amorphous In-Ga-Zn-O: percolation conduction examined by analytical model," *Journal of Display Technology*, vol. 5, pp. 462-467, 2009.

- [38] E. N. Cho, J. H. Kang, and I. Yun, "Contact resistance dependent scaling-down behavior of amorphous InGaZnO thin-film transistors," *Current Applied Physics*, vol. 11, pp. 1015-1019, 2011.

- [39] J.-M. Lee, I.-T. Cho, J.-H. Lee, and H.-I. Kwon, "Bias-stress-induced stretched-exponential time dependence of threshold voltage shift in InGaZnO thin film transistors," *Applied Physics Letters*, vol. 93, pp. 093504-093504-3, 2008.

- [40] E. N. Cho, J. H. Kang, C. E. Kim, P. Moon, and I. Yun, "Analysis of bias stress instability in amorphous InGaZnO thin-film transistors," *IEEE Transactions on Device and Materials Reliability*, vol. 11, pp. 112-117, 2011.

- [41] K. Hoshino, D. Hong, H. Q. Chiang, and J. F. Wager, "Constant-voltage-bias stress testing of a-IGZO thin-film transistors," *IEEE Transactions on Electron Devices*, vol. 56, pp. 1365-1370, 2009.

- [42] P. Gorrn, P. Holzer, T. Riedl, W. Kowalsky, J. Wang, T. Weimann, *et al.*, "Stability of transparent zinc tin oxide transistors under bias stress," *Applied Physics Letters*, vol. 90, pp. 063502-063502-3, 2007.

- [43] R. Cross and M. De Souza, "Investigating the stability of zinc oxide thin film transistors," *Applied Physics Letters*, vol. 89, pp. 263513-263513-3, 2006.

- [44] J. K. Jeong, H. Won Yang, J. H. Jeong, Y.-G. Mo, and H. D. Kim, "Origin of threshold voltage instability in indium-gallium-zinc oxide thin film transistors," *Applied Physics Letters*, vol. 93, pp. 123508-123508-3, 2008.

- [45] D. H. Levy, D. Freeman, S. F. Nelson, P. J. Cowdery-Corvan, and L. M. Irving, "Stable ZnO thin film transistors by fast open air atomic layer deposition," *Applied Physics Letters*, vol. 92, pp. 192101-192101-3, 2008.

- [46] J. Robertson, "Electronic structure and band offsets of high-dielectric-constant gate oxides," *MRS bulletin*, vol. 27, pp. 217-221, 2002.

- [47] G. D. Wilk, R. M. Wallace, and J. Anthony, "High-κ gate dielectrics: Current status and materials properties considerations," *Journal of applied physics*, vol. 89, pp. 5243-5275, 2001.

- [48] H.-S. Choi, S. Jeon, H. Kim, J. Shin, C. Kim, and U.-I. Chung, "Verification of Interface State Properties of a-InGaZnO Thin-Film Transistors With SiNx and SiO2 Gate Dielectrics by Low-Frequency Noise Measurements," *IEEE Electron Device Letters*, vol. 32, pp. 1083-1085, 2011.

- [49] C. G. Theodorou, A. Tsormpatzoglou, C. A. Dimitriadis, S. A. Khan, M. K. Hatalis, J. Jomaah, *et al.*, "Origin of Low-Frequency Noise in the Low Drain Current Range of Bottom-Gate Amorphous IGZO Thin-Film Transistors," *IEEE Electron Device Letters*, vol. 32, pp. 898-900, 2011.

- [50] S. Jeon, S. I. Kim, S. Park, I. Song, J. Park, S. Kim, *et al.*, "Low-Frequency Noise Performance of a Bilayer InZnO–InGaZnO Thin-Film Transistor for Analog Device Applications," *IEEE Electron Device Letters*, vol. 31, pp. 1128-1130, 2010.

#### **CHAPTER 1**

- 1 THE SCALING OF MOSFET

- 1.1 GENERAL DOWN-SCALING RULES OF MOSFET

- 1.2 Scaling effects on device performance

- 2 MOBILITY

- 2.1 Conductivity mobility

- 2.2 Effective mobility

- **3 DOMINANT SCATTERING EFFECTS IN MOSFET**

- 4 THE EFFECT OF TEMPERATURE ON ELECTRICAL CHARACTERISTICS IN MOSFET

- 4.1 Variation of threshold voltage with temperature

- 4.2 Variation of subthreshold slope with temperature

- 4.3 Variation of carrier concentration with temperature

- 5 THE SERIES RESISTANCE AND THE VARIATION OF CHANNEL LENGTH IN MOSFET

- **6 THE SUBSTRATE BIAS EFFECT ON ELECTRICAL CHARACTERISTICS IN MOSFET**

- 7 CONDUCTION IN AMORPHOUS OXIDE SEMICONDUCTOR THIN FILM TRANSISTOR (AOS TFT)

# THEORETICAL BACKGROUND

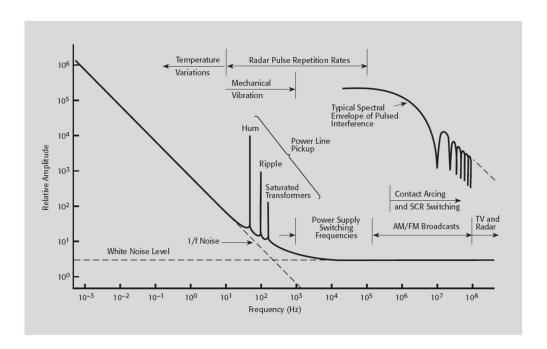

In this chapter, the general scaling rule in MOSFET to maintain the performance of the device is introduced. However, practically, the effect of scaling on the operation of the device such as short channel effect or narrow channel effect is common in I-V characteristics of MOSFET. Carrier mobility, an important parameter to evaluate the device performance can be determined from several concepts. The effective mobility in MOSFET is influenced by the scattering mechanisms which mainly consist of lattice scattering, ionized impurity scattering, and surface roughness scattering. The device operation is also affected by temperature, series resistance, and substrate bias. At last, the conduction mechanism in amorphous oxide semiconductor thin film transistor is described.

#### 1 DOWN SCALING OF MOSFET

#### 1.1 General down-scaling rules of MOSFET

As the channel length of MOSFET is decreased, proper adjustment of other device parameters is needed to maintain the device performance. When the channel length is reduced, depletion widths of source and drain region meet each other and electrons are pulled by drain field from the source, which is called as punch-through effect. To prevent this effect, higher channel doping is required. For P-type substrate ( $N_D \ll N_A$ ), the depletion layer width at source/drain is given as [1];

$$w_d \approx w_p \approx \sqrt{\frac{2\varepsilon_s(V_{bi} + V_R)}{qN_A}}$$

(1.1)

where  $w_p$  is the depletion layer (m) of p-type silicon,  $\varepsilon_s$  is the dielectric permittivity (F/m) of the semiconductor,  $V_{bi}$  is the built-in potential,  $V_R$  is a reverse-biased voltage. However, introducing more dopants to the channel increases the threshold voltage  $V_T$  because of higher body factor  $\gamma$  (V<sup>1/2</sup>),

$$V_T = V_{FB} + 2\phi_F + \gamma \sqrt{2\phi_F + V_{SB}}$$

(1.2a)

$$\gamma = \frac{\sqrt{2\varepsilon_s q N_D}}{C_{ax}} \tag{1.2b}$$

$V_{\it FB}$  is the flat-band voltage,  $\phi_{\it F}$  is the Fermi potential,  $V_{\it SB}$  is source-to-bulk voltage and  $C_{\it ox}$

| Channel length L                                   | L/S                  |

|----------------------------------------------------|----------------------|

| Channel width W                                    | W/S                  |

| Gate-oxide thickness $t_{ox}$                      | $t_{ox}/S$           |

| Substrate doping $N_{A,D}$                         | $N_{A,D} \times S^2$ |

| Drain current $I_D \propto W/(Lt_{ox})$            | $I_D \times S$       |

| Input capacitance $C_{in} \propto WL/t_{ox}$       | $C_{in}/S$           |

| Maximum switching frequency $f \propto I_D/C_{in}$ | $f \times S^2$       |

| Cell area $A \propto WL$                           | $A/S^2$              |

Table 1 Down scaling rules of MOSFET when the gate length is reduced by S times.

is the gate-oxide capacitance (F/m<sup>2</sup>). In order to keep reasonable threshold voltage value, the thickness of the gate oxide should be reduced. Accordingly, the input capacitance is increased and it is fixed by reduced channel width. The down scaling rules when the gate length is reduced by S times are summarized in Table 1.

#### 1.2 Scaling effects on device performance

For a given current density, the channel mobility of short channel device is related to the drift velocity for given electric fields E as;

$$v_d = -\mu_n E$$

(for electrons) (1.3a)

$$v_d = \mu_p E \text{ (for holes)}$$

(1.3b)

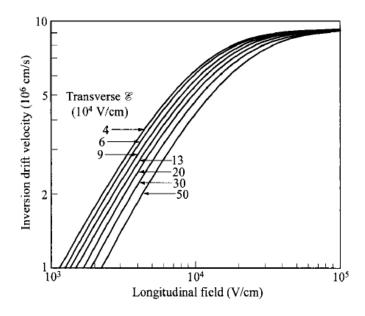

At low electric fields, the drift velocity has linear relation with the electric field as shown in Eq. (1.3a) and Eq. (1.3b). However, when the electric field is high, the drift velocity trend saturated to a constant value, deviating from the linear relation. It occurs before the pinch-off condition. In extremely short devices, the saturated velocity severely limits the drain current.

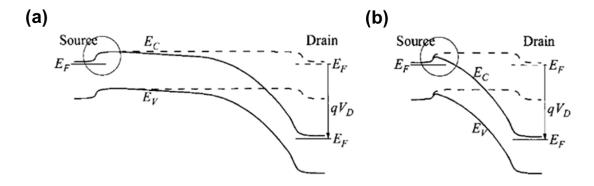

Drain induced barrier lowering (DIBL), the one of the short channel effects, is the origin of punchthrough effect. As shown in Fig 2, it causes the barrier at source end to reduce by high drain bias and

Figure 1 Inversion drift velocity versus longitudinal field for various transverse fields. [2]

Figure 2 The energy-band diagram from source to drain at  $V_D > 0$  V for (a) long channel and (b) short channel in transistor. Dashed line for  $V_D = 0$  V [3].

the substantial increase of the drain current [3]. With punch-through effect, DIBL is presented by the reduction of threshold voltage and the increase of off-state current with drain voltage. For short channel devices, the subthreshold drain current increases with drain voltage while subthreshold swing is increased as a result of threshold voltage shift. On the other hand, the subthreshold drain current is not changed with drain voltage in long channel device [4]. For extreme case of DIBL, the device doesn't turn-off.

The narrow width effect (NWE) is another scaling related effect. It corresponds to an increase of the threshold voltage when the channel width is below 1µm in device using LOCal Oxidation of Silicon isolation. When the channel width is comparable to the edge effect region, the wider depletion region

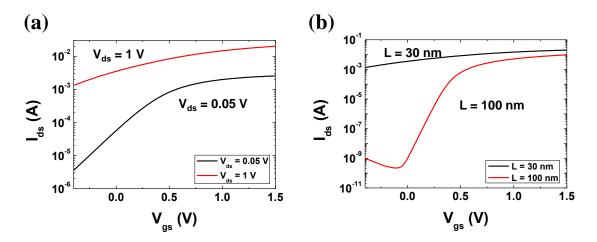

Figure 3 Drain characteristics of MOSFETs showing DIBL effects. (a) Transfer curves with L = 30 nm at  $V_{ds}$  = 0.05 V and  $V_{ds}$  = 1 V. (b) Transfer curves with L = 30 nm and L = 100 nm at  $V_{ds}$  = 1 V.

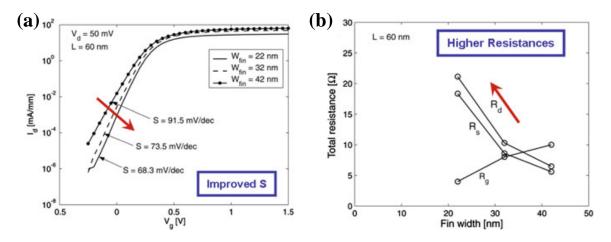

Figure 4 (a) transfer characteristic (b) extracted access resistances of 60 nm-gate length Fin-FET for different fin widths ( $W_{\text{fin}}$ ) [5]

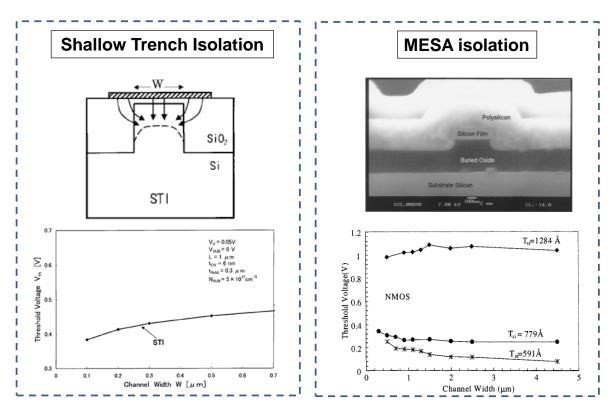

Figure 5 Variation of the threshold voltage with various channel widths for shallow trench isolation and MESA isolation. [6, 7]

by the gate voltage is observed. As a result, the depletion charge by gate voltage is increased and the threshold voltage is increased in very narrow devices. According to the isolation method, the variation of threshold voltage with channel widths exhibits different trend. As shown in Fig. 5, with shallow

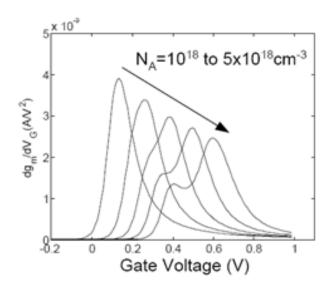

trench isolation, the threshold voltage decreases with narrow channel width due to the gate fringing field [6]. In contrast, the thin channel device using MESA isolation shows increased threshold voltage with narrow channel configuration which eliminates effects of positive oxide fixed charge in BOX [7]. In SOI device, the narrow channel width is useful for better controllability for short channel effect. FinFET with narrow channel width exhibits limited DIBL and improved transport properties with small variation of threshold voltage [5, 8]. For gate-all-around nanowire devices, the subthreshold swing was reduced with using very narrow nanowire [9]. However, as the channel width is reduced, series resistance increases, which causes the decrease of drain current [10]. In multi-gate FETs, the device with heavily doped channel may present corner effect. As gate voltage is increased, the top corner of channel reaches inversion before top and sidewall surface channel is formed due to the overlap of electric field from top gate and sidewall gate. Figure 6 shows the derivative of transconductance curves for multi-gate FET with various channel doping concentrations from  $10^{18}$  to  $5 \times 10^{19}$  cm<sup>-3</sup>. The corner effect is illustrated by the derivative of transconductance curve having two humps when channel doping is high, corresponding to channel formation at top corner and surface. However, the corner effect is eliminated in a device with low channel doping concentration [11].

Figure 6 The derivative of transconductance in  $\Omega$ -FET with various channel doping concentrations from  $10^{18}$  to  $5 \times 10^{19}$  cm<sup>-3</sup> [11].

#### 2 MOBILITY

Carrier mobility is a macroscopic transport property characterizing semiconductor materials as well as device performance. Mobility can be affected by microscopic properties such as the effective mass and the degree of carrier scattering. For multiple scattering mechanisms, the net mobility  $\mu$  is derived from the various mobilities, by Mathiessens's rule;

$$\frac{1}{\mu} = \frac{1}{\mu_1} + \frac{1}{\mu_2} + \dots \tag{1.4}$$

There are several kinds of mobility according to the definition method such as the conductivity mobility, Hall mobility, and effective mobility in MOSFET.

#### 2.1 Conductivity mobility

The conductivity mobility is determined by measuring carrier concentration and the conductivity. For n-type semiconductor, the relationship between the conductivity  $\sigma$  (S/cm) and the conductivity mobility  $\mu_n$  (cm<sup>2</sup>/Vs) given by:[12]

$$\sigma = qn\mu_n \tag{1.5}$$

where, q is the electron charge, n is the electron concentration (/cm<sup>3</sup>).

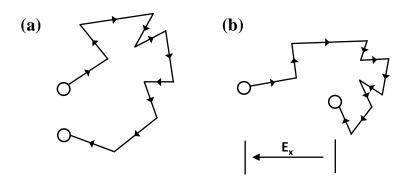

The conductivity mobility comes from the drift of group of carriers by external electric field E. For example, when the external field in x-direction  $E_x$  is applied to a group of carriers, the group of carriers is forced by  $-qE_x$  to move in x-direction. The average velocity of the group of carrier is called average particle drift velocity  $< v_x >$ .

Figure 7 Drift of an electron as a result of thermal motion. (a) When there is no electric field, the electron randomly moves but ends up with no net displacement; (b) when an electric field is applied, the electron drifts opposite to the direction of the field and has a net displacement (and therefore a drift velocity).

The conductivity mobility  $\mu_n$  is defined as the proportionality constant of the drift velocity to the electric field  $E_x$ . The net motion of the group of carriers is accelerated by the external field, however, there are many scattering sites such as crystal defects, vacancies, dislocations, impurities in a solid. Thus, the velocity of electrons is saturated with a constant electric field  $E_x$ .

$$\langle v_{x} \rangle = \frac{\langle p_{x} \rangle}{m_{n}} = -\frac{qt}{m_{n}} E_{x} = -\mu_{n} E_{x}$$

(1.6)

where,  $\langle p_{\chi} \rangle$  is the average momentum per electron, t is the mean free time, and  $m_n^*$  is the effective mass of electron.

From the drift, the current density  $J_x$  is defined by:

$$J_{\chi} = -qn < v_{\chi} > \tag{1.7}$$

where -q is the charge of electron and  $n < v_x > 1$  is the number of electrons crossing a unit area per unit time [13].

And the current density is expected to be proportional to the applied electric field with Ohm's law as;

$$J_{\chi} = \sigma E_{\chi} \tag{1.8}$$

Applying Eq (1.6) and (1.7) to Eq. (1.8), the relation between the conductivity mobility and the conductivity shown in Eq. (1.5) is established.

#### 2.2 Effective mobility

When the carrier flow is limited in the inversion layer the mobility is low, compared to the bulk mobility due to the interface effect and thin thickness of the inversion layer.

The effective mobility  $\mu_{eff}$  is obtained at low drain voltage as:

$$\mu_{eff} = \frac{I_d L}{WQ_n V_d} \quad (1.9)$$

where  $I_d$  is the drain current and  $Q_n$  is the channel charge density (C/m<sup>2</sup>), and  $V_d$  is the drain voltage.

There are two ways to obtain the channel charge density  $Q_n$ . The channel charge density  $Q_n$  can be approximated by just multiplying the effective oxide capacitance per unit area  $C_{ox}$  (F/m<sup>2</sup>) with over-drive gate voltage at strong inversion  $V_{gt} (= V_{gs} - V_{th})$  as:

$$Q_n = C_{OX} V_{gt} \qquad (1.10)$$

It is simple but there are difficulties to obtain the exact value of  $C_{ox}$  and the threshold voltage  $V_{th}$ . Another way is to obtain  $Q_n$  directly from the measurement of gate-to-channel capacitance.

$$Q_n = \int_{-\infty}^{V_{gs}} C_{gs} dV_{gs}$$

(1.11)

where  $C_{gs}$  is the gate-to-channel capacitance per unit area. Usually, it provides better results, compared to the previous one [12].

As described in (Eq 1.6), the mobility is proportionality constant of velocity to electric field. When the field is low, the velocity is linearly increased with electric field and the mobility is constant. How-

ever, at high field, the velocity is saturated to constant value. When the electric field is between these two regimes, the effective mobility is given as;

$$\mu_{eff} = \frac{\mu_0}{\left[1 + (E/E_C)^n\right]^{1/n}} \tag{1.12}$$

where  $\mu_0$  is the low field mobility and  $E_C$  is the critical field. n is 2 for electrons and 1 for holes in silicon [3, 14]. The effective mobility is higher with lower channel doping concentration owing to reduced normal field and low threshold voltage.

The effective mobility  $\mu_{eff}$  includes mobility degradation by the several scattering mechanisms such as phonon scattering, ionized impurity scattering and surface roughness scattering. The scattering effect is varied by the transverse field by gate bias and it can be presented in MOSFET by empirical relation as [15];

$$\mu_{eff} = \frac{\mu_0}{1 + \theta_1 (V_{GS} - V_T) + \theta_2 (V_{GS} - V_T)^2}$$

(1.13)

Figure 8 Electron mobility in silicon as a function of impurity concentration

$\theta_1$ ,  $\theta_2$  are mobility degradation factors which are affected by gate oxide thickness and doping concentration. While classical effective channel mobility is presented by only first-order mobility degradation factor  $\theta_1$ , recent MOSFETs have been scaled down and the second-order mobility  $\theta_2$  degradation factor is required since the drain current is significantly degraded at high field. It is known that this degradation is due to surface roughness scattering [16].

#### 3 DOMINANT SCATTERING EFFECTS IN MOSFET

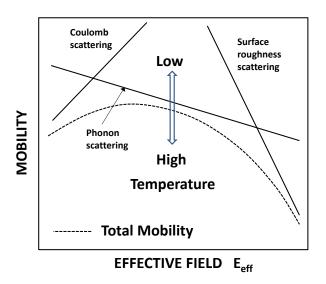

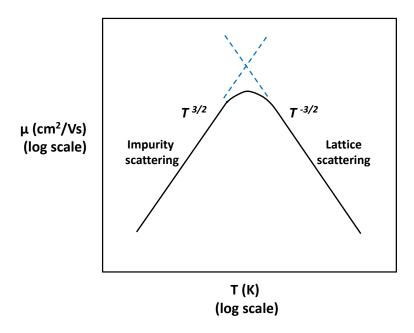

There are several scattering mechanisms which influence the mobility of MOSFET. They are phonon scattering (lattice scattering), Coulomb scattering (Ionized impurity scattering), and surface roughness scattering. Depending on the temperature and the effective electric field or the carrier concentration, different scattering mechanism governs the mobility behavior of MOSFET. The universal mobility

Figure 9 Schematic diagram of effective mobility as a function of the effective field  $E_{\text{eff}}$  with three scattering mechanisms, Phonon scattering, Coulomb scattering, and Surface roughness scattering

Figure 10 Approximate temperature dependence of mobility with both lattice and impurity scattering

behavior according to these scattering mechanisms depends on the effective field as shown in Fig. 9 [17].

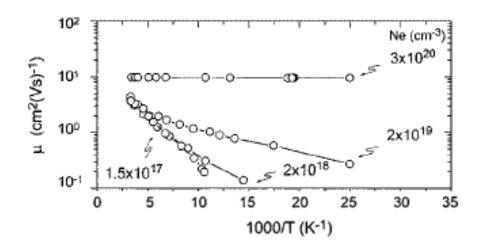

At given temperature, crystalline lattice is vibrating with thermal energy. These vibrations are represented by particle called as "phonon". When a carrier moves in vibrating crystal lattice, this carrier is scattered by this vibration. As temperature increases, more vibration occurred and the mobility is reduced since the scattering rate increases. The mobility limited by phonon scattering is decreased with temperature ( $\mu \sim T^{3/2}$  in silicon) [3].

One of important scattering mechanisms for carrier transport is ionized impurity scattering. When temperature is low, lattice scattering is less important due to reduced lattice vibration, thus, ionized impurity scattering becomes the dominant scattering mechanism. In contrast with the effect of lattice scattering, the mobility increases with temperature (Fig. 10) since a carrier which moves fast with higher thermal energy less interacts with a charged ion than one moving slowly. The mobility approximately depends on the temperature as  $T^{3/2}$  in silicon, owing to ionized impurity scattering. When the concentration of ionized impurities is high, the mobility limited by impurity scattering is shown at higher temperatures.

Phonon scattering always involves the mobility behavior and, especially, it dominantly affects the effective mobility at room temperature. When the carrier concentration is not high, Coulomb scattering is important for the determination of the effective mobility while the surface roughness scattering become important with high carrier concentration. Surface roughness scattering strongly affects the mobility behavior when the transistor is in strong inversion regime.

Surface roughness in the MOS structure is related to the random fluctuation of surface, which is represented by atomic step, between oxide insulator and channel silicon. The fluctuation creates the dipoles at the interface, inducing electrical potentials. It is expected the surface roughness always exists at the interface between insulator and channel due to the misfit of the lattice spacing and the existence of interfacial stress due to the difference in thermal expansion coefficient.

### 4 THE EFFECT OF TEMPERATURE ON ELECTRICAL CHARACTERISTICS I N MOSFET

#### 4.1 Variation of threshold voltage with temperature

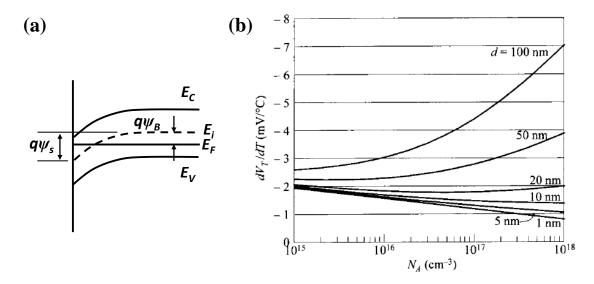

The threshold voltage in MOSFET is defined as the sum of the flat band voltage, the surface potential of  $2\psi_B$ , and the voltage drop across the oxide (Fig. 11(a));

$$V_{th} = V_{fb} + 2\psi_B + \frac{\sqrt{2\varepsilon_s q N_A(2\psi_B)}}{C_{ox}}$$

(1.14)

Figure 11 (a) Energy-band diagram and (b) the derivative of the threshold voltage with temperature as a function of the oxide thickness d with various doping concentration [3].

$$= \phi_{ms} - \frac{Q_f}{C_{ox}} + 2\psi_B + \frac{\sqrt{2\varepsilon_s q N_A(2\psi_B)}}{C_{ox}}$$

where  $V_{fb}$  is the flat-band voltage,  $\psi_B$  the Fermi potential,  $\varepsilon_s$  is the dielectric permittivity of the semiconductor,  $N_A$  is the substrate doping level (/m³),  $C_{ox}$  is the gate oxide capacitance (F/m²),  $Q_f$  is the fixed oxide charges (C/m²), and  $\phi_{ms}$  is the work function difference between the gate material and the semiconductor. Because  $\phi_{ms}$ ,  $Q_f$  and  $C_{ox}$  are independent of temperature, the derivative of threshold voltage with temperature is given as;

$$\frac{dV_{th}}{dT} = \frac{d\psi_B}{dT} \left( 2 + \frac{1}{C_{ox}} \sqrt{\frac{\varepsilon_s q N_A}{\psi_B}} \right)$$

(1.15)

And  $\psi_B$  is given as;

$$\psi_B = \frac{kT}{q} \ln \left( \frac{N_A}{n_i} \right) \tag{1.16}$$

Since,  $n_i (= \sqrt{N_C N_V} \exp(-E_g / 2kT))$  is also is a function of temperature.

$$\frac{d\psi_B}{dT} \approx \frac{1}{T} \left( \psi_B - \frac{E_{g0}}{2q} \right) \tag{1.17}$$

Adopting above equation to the equation of derivative of threshold voltage,

$$\frac{dV_{th}}{dT} \approx \left(\frac{1}{T} \left(\psi_B - \frac{E_{g0}}{2q}\right)\right) \left(2 + \frac{1}{C_{ox}} \sqrt{\frac{\varepsilon_s q N_A}{\psi_B}}\right) \tag{1.18}$$

The derivation of threshold voltage with temperature change is shown with various doping concentration as a function of the oxide thickness d (Fig. 11(b)). It is worthwhile to note that the derivation of threshold voltage is influenced by oxide thickness as well as doping concentration in MOSFET.

#### 4.2 Variation of subthreshold slope with temperature

The subthreshold swing of MOSFET, SS shows the explicit temperature dependence as shown in Fig. 12. The subthreshold slop is expressed by

$$SS = (\ln 10) \left( \frac{kT}{q} \right) \left( \frac{C_{ox} + C_D}{C_{ox}} \right) \qquad [V/\text{decade}]$$

(1.19)

where  $C_D$  is the depletion-layer capacitance.

Figure 12 Subthreshold characteristics with various temperature for FD-SOI MOSFET of L = 10  $\mu$ m and W = 10 $\mu$ m.

#### 4.3 Variation of carrier concentration with temperature

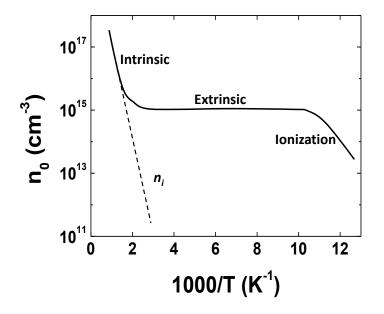

Figure 13 shows the temperature dependence of the carrier concentration. When the temperature is very low (large 1/T), most dopants are frozen out and can't donate electron or holes to conduction band or valence band. As temperature increases, dopants are fully ionized and carrier concentration in the medium temperature range is remained constant, determined by carriers which are provided by

dopants. Beyond this temperature range, the intrinsic carrier concentration become dominant in the determination of carrier concentration, thus it is increased with temperature [13].

Figure 13 Temperature dependence of the carrier concentration

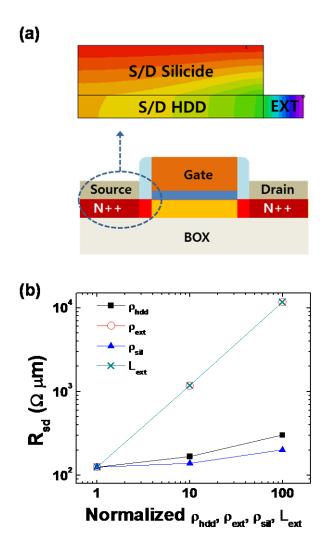

# 5 THE SERIES RESISTANCE AND THE VARIATION OF CHANNEL LENGTH IN MOSFET

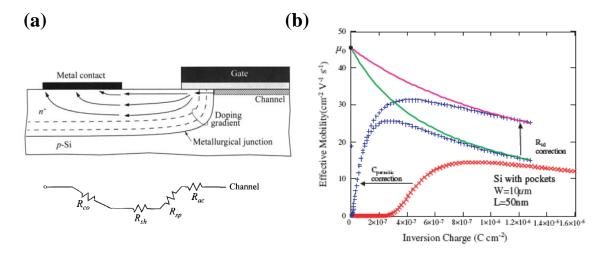

The series resistance is the sum of the source resistance and the drain resistance, including the contact resistance in source/drain  $R_{co}$ , the sheet resistance of source/drain  $R_{sh}$ , the spreading resistance between source/drain and channel  $R_{sp}$  and accumulation-layer resistance  $R_{ac}$  [3, 18].

Figure 14 (a) Series resistance in MOSFET [3], (b) the correction of the effective mobility with the series resistance correction [19]

The effect of series resistance on electrical property of MOSFET is important in the performance of device. At first, the series resistance causes the reduced drain current due to the voltage drop in series resistance. It leads to the degradation of the speed of the device. The effective mobility is also degraded by the series resistance and it can be corrected by the extraction of the series resistance as shown in Fig. 14 [19].

The channel length might deviate from mask-defined channel length owing to the imperfection of the fabrication process, such as over-or underexposed photoresist/polysilicon/metal. Besides, the channel length can be different from the distance between the ends of source and drain electrodes since source/drain junctions are spread during high temperature annealing process and the channel length is extended to the LDD region with high gate voltage [12, 13].

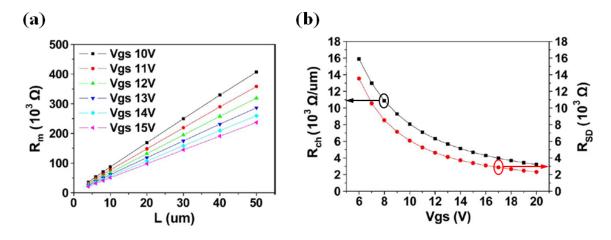

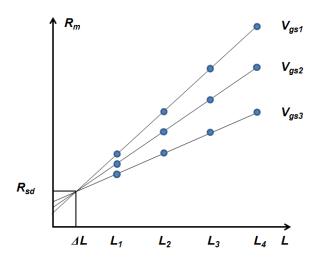

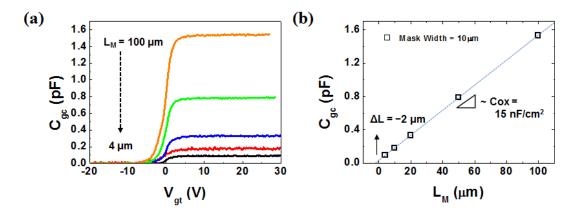

In amorphous oxide semiconductor transistors, the increase of channel length is often observed (Fig. 15). Some portion of carriers in AOS TFT is collected/injected at some distance apart from the edge of source/drain electrodes because an insulating layer is formed at electrode edge during the fabrication process [20, 21].

Figure 15 (a) Total resistance  $R_m$  as a function of channel length L for TFTs (W = 50  $\mu$ m, L = 4, 6, 8, 10, 20, 30, 40, 50  $\mu$ m). (b) Channel resistance  $R_{ch}$  and series resistance  $R_{SD}$  at source/drain contacts with various gate voltage Vgs. [20]

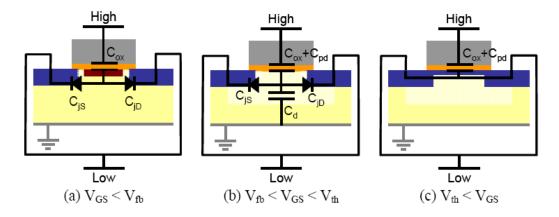

## 6 THE SUBSTRATE BIAS EFFECT ON ELECTRICAL CHARACTERISTICS IN MOSFET

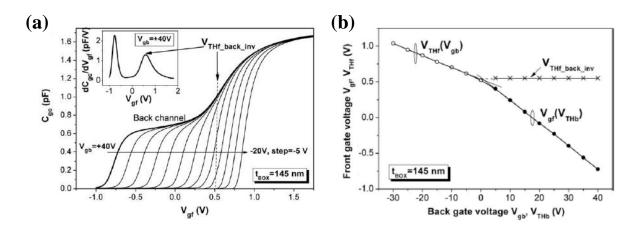

In FD-SOI MOSFET, the substrate biasing effects on transport properties and gate tunnelling currents have received a lot of interest since it has a possibility to change the carrier concentration distribution and electric field distribution in the silicon film. In addition, the bias applied to the substrate

Figure 16 (a) Gate-to-channel capacitance  $C_{gc}$  as a function of the front-gate voltage  $V_{gf}$  at different back-bias voltages  $V_{gb}$  from 40 V to -20 V with step -5 V, (b) front-channel threshold voltage and back-channel threshold voltage versus back gate bias [22]

modulates the intrinsic gate-to-channel capacitance and the front gate threshold voltage due to the interface coupling as shown in Fig. 16 [22]. Ritzenthaler et al., also reported that the short channel effect such as DIBL could be variable with substrate bias [23]. The substrate biasing effect which is presented as the polarization of the substrate is important in the operation of the transistor and it should be concerned in the practical use of SOI devices.

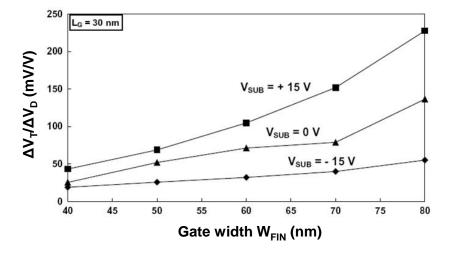

Figure 17 Threshold voltage lowering  $\Delta V_T/\Delta V_D$  in  $\Omega FET$  with gate length  $L_G=30$  nm by DIBL as a function of gate width  $W_{FIN}$  for various substrate bias ( $V_{SUB}=-15$ , 0, and +15 V) [23].

## 7 CONDUCTION IN AMORPHOUS OXIDE SEMICONDUCTOR THIN FILM TR ANSISTOR (AOS TFT)

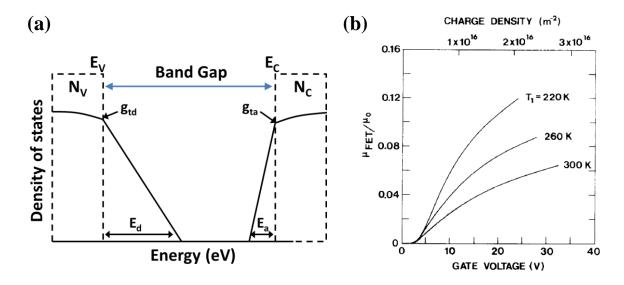

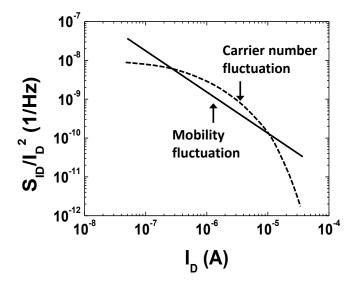

Generally, the density of states (DOS) in a-Si:H is adopted for explaining the conduction mechanism of AOS TFT. Different from the silicon, there are states in the band gap of AOS and these states consist of band-tail states and deep-gap states [24]. Similar to a-Si, some portion of carrier is localized in band-tail states and localized carriers in band-tail states decrease at higher gate voltage. Delocalized carriers can contribute to the drain current and increase the effective mobility in AOS TFT [25, 26] The band-tail states are given as a function of energy E (Fig. 18):

$$g_{CBa} = g_{ta} \exp[(E - E_C)/E_a]$$

(1.20a)

$$g_{VBd} = g_{td} \exp[(E_V - E)/E_d]$$

(1.20b)

Where  $g_{ta}$  the densities of acceptor-like tail states at  $E = E_C$ , and  $g_{td}$  the densities of donor-like tail states at  $E = E_V$ .

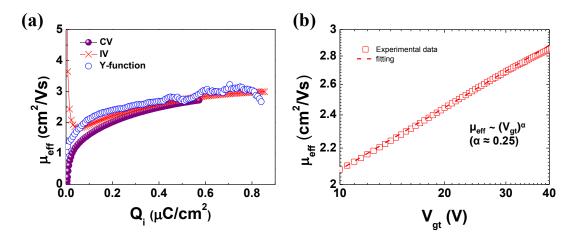

AOS TFT shows gate voltage dependent mobility as;

$$\mu_{eff} = K(V_{gs} - V_{th})^{\alpha} \qquad (1.21)$$

where K is the constant which is related to the material and  $\alpha$  is the exponent which shows the degree of dependence on the gate voltage [24].

Figure 18 (a) The density of states model of AOS TFT and (b) gate-dependent mobility of AOS TFT, ratio of field-effect to band mobility versus the gate voltage for varying temperature T [26].

## References

- [1] S. Dimitrijev, *Understanding semiconductor devices*: Oxford university press, 2000.

- [2] J. Cooper and D. Nelson, "High-field drift velocity of electrons at the Si–SiO 2 interface as determined by a time-of-flight technique," *Journal of Applied Physics*, vol. 54, pp. 1445-1456, 1983.

- [3] S. M. Sze and K. K. Ng, *Physics of semiconductor devices*: Wiley-interscience, 2006.

- [4] N. Tarr, D. Walkey, M. Rowlandson, S. Hewitt, and T. MacElwee, "Short-channel effects on MOSFET subthreshold swing," *Solid-state electronics*, vol. 38, pp. 697-701, 1995.

- [5] A. Nazarov, Semiconductor-on-insulator materials for nanoelectronics applications: Springerverlag Berlin Heidelberg, 2011.

- [6] N. Shigyo and T. Hiraoka, "A review of narrow-channel effects for STI MOSFET's: A difference between surface-and buried-channel cases," *Solid-State Electronics*, vol. 43, pp. 2061-2066, 1999.

- [7] H. Wang, M. Chan, Y. Wang, and P. K. Ko, "The behavior of narrow-width SOI MOSFETs with MESA isolation," *IEEE Transactions on Electron Devices*, vol. 47, pp. 593-600, 2000.

- [8] C. Dupré, A. Hubert, S. Becu, M. Jublot, V. Maffini-Alvaro, C. Vizioz, *et al.*, "15nm-diameter 3D stacked nanowires with independent gates operation: ΦFET," in *Electron Devices Meeting*, 2008. *IEDM 2008. IEEE International*, 2008, pp. 1-4.

- [9] M. Luisier and G. Klimeck, "Atomistic full-band design study of InAs band-to-band tunneling field-effect transistors," *IEEE Electron Device Letters*, vol. 30, pp. 602-604, 2009.

- [10] A. Dixit, A. Kottantharayil, N. Collaert, M. Goodwin, M. Jurczak, and K. De Meyer, "Analysis of the parasitic S/D resistance in multiple-gate FETs," *IEEE Transactions on Electron Devices*, vol. 52, pp. 1132-1140, 2005.

- [11] J.-P. Colinge, "Multiple-gate soi mosfets," *Solid-State Electronics*, vol. 48, pp. 897-905, 2004.

- [12] D. K. Schroder, *Semiconductor material and device characterization*: Wiley-interscience, 2006.

- [13] B. G. Streetman and S. Banerjee, *Solid state electronic devices* vol. 4: Prentice Hall New Jersey, 2000.

- [14] M.-S. Liang, J. Y. Choi, P.-K. Ko, and C. Hu, "Inversion-layer capacitance and mobility of very thin gate-oxide MOSFET's," *IEEE Transactions on Electron Devices*, vol. 33, pp. 409-413, 1986.

- [15] T. C. Ong, P. K. Ko, and C. Hu, "50-Å gate-Oxide MOSFET's at 77 K," *IEEE Transactions on Electron Devices*, vol. 34, pp. 2129-2135, 1987.

- [16] K. Rais, G. Ghibaudo, and F. Balestra, "Surface roughness mobility model for silicon MOS

- transistors," physica status solidi (a), vol. 146, pp. 853-858, 1994.

- [17] A. Takagi, K. Nomura, H. Ohta, H. Yanagi, T. Kamiya, M. Hirano, *et al.*, "Carrier transport and electronic structure in amorphous oxide semiconductor, a-InGaZnO4," *Thin Solid Films*, vol. 486, pp. 38-41, 2005.

- [18] K. K. Ng and W. T. Lynch, "Analysis of the gate-voltage-dependent series resistance of MOSFET's," *IEEE Transactions on Electron Devices*, vol. 33, pp. 965-972, 1986.

- [19] K. Romanjek, F. Andrieu, T. Ernst, and G. Ghibaudo, "Characterization of the effective mobility by split C(V) technique in sub 0.1 μm Si and SiGe PMOSFETs," *Solid-State Electronics*, vol. 49, pp. 721-726, 2005.

- [20] J. Park, C. Kim, S. Kim, I. Song, S. Kim, D. Kang, *et al.*, "Source/drain series-resistance effects in amorphous gallium–indium zinc-oxide thin film transistors," *IEEE Electron Device Letters*, vol. 29, pp. 879-881, 2008.

- [21] J. Kanicki, F. Libsch, J. Griffith, and R. Polastre, "Performance of thin hydrogenated amorphous silicon thin-film transistors," *Journal of applied physics*, vol. 69, pp. 2339-2345, 1991.

- [22] T. Rudenko, V. Kilchytska, N. Collaert, M. Jurczak, A. Nazarov, and D. Flandre, "Carrier mobility in undoped triple-gate FinFET structures and limitations of its description in terms of top and sidewall channel mobilities," *IEEE Transactions on Electron Devices*, vol. 55, pp. 3532-3541, 2008.

- [23] R. Ritzenthaler, S. Cristoloveanu, O. Faynot, C. Jahan, A. Kuriyama, L. Brevard, *et al.*, "Lateral coupling and immunity to substrate effect in ΩFET devices," *Solid-State Electronics*, vol. 50, pp. 558-565, 2006.

- [24] T.-C. Fung, C.-S. Chuang, C. Chen, K. Abe, R. Cottle, M. Townsend, *et al.*, "Two-dimensional numerical simulation of radio frequency sputter amorphous In–Ga–Zn–O thin-film transistors," *Journal of Applied Physics*, vol. 106, pp. 084511-084511-10, 2009.

- [25] R. Hoffman, B. J. Norris, and J. Wager, "ZnO-based transparent thin-film transistors," *Applied Physics Letters*, vol. 82, pp. 733-735, 2003.

- [26] M. Shur and M. Hack, "Physics of amorphous silicon based alloy field-effect transistors," *Journal of applied physics*, vol. 55, pp. 3831-3842, 1984

## **CHAPTER 2**

#### **1 MEASUREMENT TECHNIQUE TO AVOID ERRORS**

- 1.1 The limit of voltmeter

- 1.2 The guarding technique

#### **2 ELECTRICAL CHARACTERIZATION AND ANLYSIS**

- 2.1 Y-function

- 2.2 The Split C-V measurements

- 2.3 Defining threshold voltage

- 2.4 Defining the series resistance and the effective channel length

- 2.5 Defining the trap density

- 2.6 2-D numerical simulations

## **EXPERIMENTAL BACKGROUND**

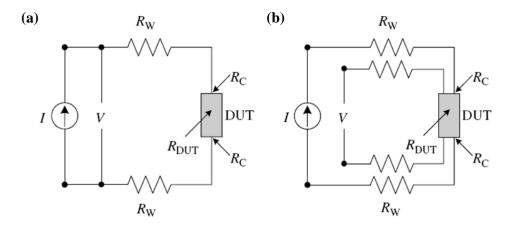

To observe previous theoretical phenomena, experimental precautions and experimental methods are worth to note. In this chapter, the consideration in the measurement tips such as the limit of voltmeter and guarding technique to avoid possible experimental error and the experimental parameter characterization method such as Y-function and C-V measurement technique will be covered. The extraction method of electrical parameters such as threshold voltage, the series resistance and trap density is also discussed. For the analysis of electrical characteristics of the MOSFETs with proper model, 2-dimensional (2-D) numerical simulation is also important tool to investigate the conduction in MOSFET.

#### 1 MEASUREMENT TECHNIQUE TO AVOID ERRORS

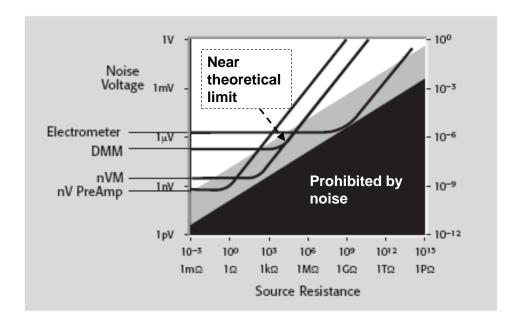

#### 1.1 The limit of voltmeter

When DC voltage measurement is performed, the measurement accuracy is limited by the noise voltage which is created by the resistances in circuit and the source resistance. For Digital multimeter (DMM), the measurement of 1  $\mu$ V with source resistance 1  $\Omega$  is possible, however, the measurement of 1 $\mu$ V with source resistance of 1k $\Omega$  is not practical since this measurement condition is below the theoretical limit of DMM. In this case, nanovoltmeter (nVM) can be used. The voltmeter can't measure the source resistance which is much larger than its input resistance because it induces input loading errors [1].

Figure 1 Limit of measurement equipment; Digital Multimeter(DMM), Nanovoltmeter (nVM), Nanovolt Preamplifier (nV PreAmp), and Electrometer [1]

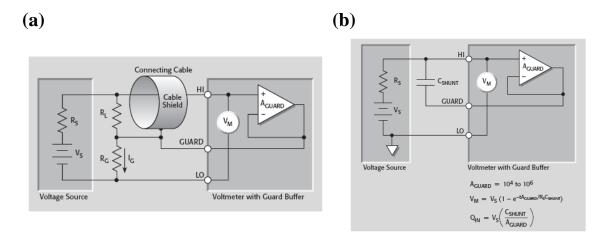

#### 1.2 The guarding technique

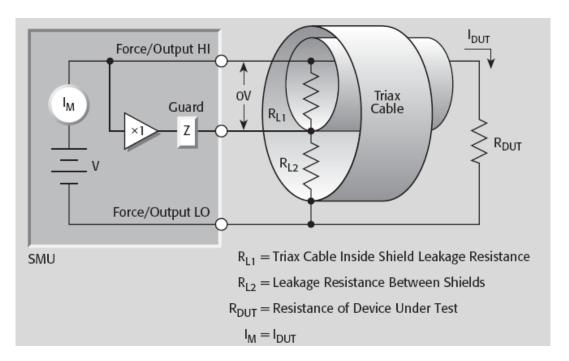

With guarded configuration, the cable leakage current can be reduced. As cable shield is connected to the output of guard buffer instead of low terminal of voltmeter, the voltage difference between high terminal voltmeter and cable shield become very small (Fig. 2(a)). Hence, the current flowing through

Figure 2 (a) Guarding leakage resistance and (b) Shunt Capacitance [1]

the cable leakage resistance is negligible. Another important advantage of guarding is reducing the effect of shunt capacitance (Fig. 2(b)). As open-loop gain of guard buffer  $A_{GUARD}$  is  $10^4$  to  $10^6$ , the charging time of shunt capacitance is significantly reduced.

When the coaxial cable is used, the leakage current through the cable leakage resistance can be created due to the voltage difference between Force/Output HI terminal and Force/Output LO terminal. The leakage current can be a serious problem in the low current measurement. In contrast, the usage of triaxial cables (Fig. 3) eliminates the leakage current because voltage difference between

Figure 3 Current measurement with guarding the leakage resistance with the triaxial cable [1]

Force/Output HI and inside shield of the triaxial cable, connected to the guard terminal of SMU, becomes almost zero.

#### 2 ELECTRICAL CHARACTERIZATION AND ANALYSIS

#### 2.1 Y-function

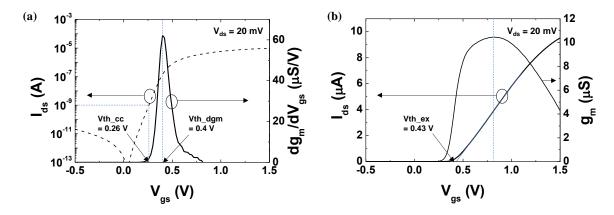

Y function method is developed to avoid the effect of series resistance and mobility degradation on the threshold voltage and the low-field mobility [2]. Y function is defined as;

$$Y = \left(\frac{I_d^2}{g_m}\right)^{\frac{1}{n}} \qquad [(A V)^{1/n}]$$

(2.1)

n is 2 for 200 - 300 K and is 3 for 4.2 - 40 K for silicon MOSFET [3]. The drain current  $I_d$  in a strong inversion regime of MOSFET is presented as;

$$I_d = \frac{WC_{ox}}{L} \frac{\mu_0}{[1 + \theta(V_g - V_{th})]} (V_g - V_{th}) V_d \quad (2.2)$$

where  $\theta$  is the mobility degradation factor.

Then, the transconductance  $g_m$  is defined as;

$$g_m = \frac{WC_{ox}}{L} \frac{\mu_0}{\left[1 + \theta(V_g - V_{th})\right]^2} V_d$$

(2.3)

With applying equations to Y function at room temperature, Y function is again presented as;

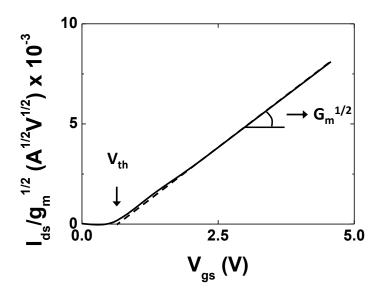

Figure 4 Y function of MOSFET characteristic

$$Y = \left(\frac{W}{L}C_{ox}\mu_0 V_d\right)^{1/2} (V_g - V_{th}) = G_m^{1/2} (V_g - V_{th})$$

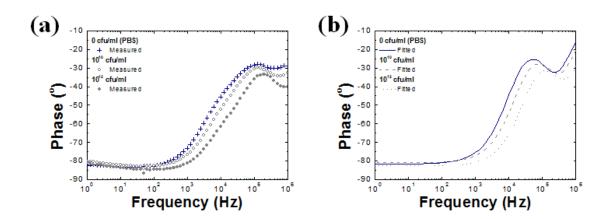

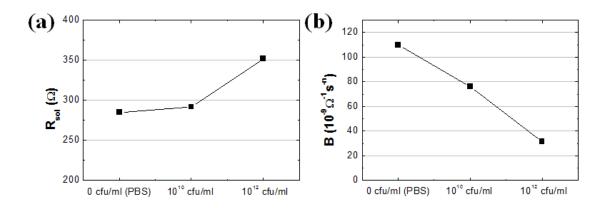

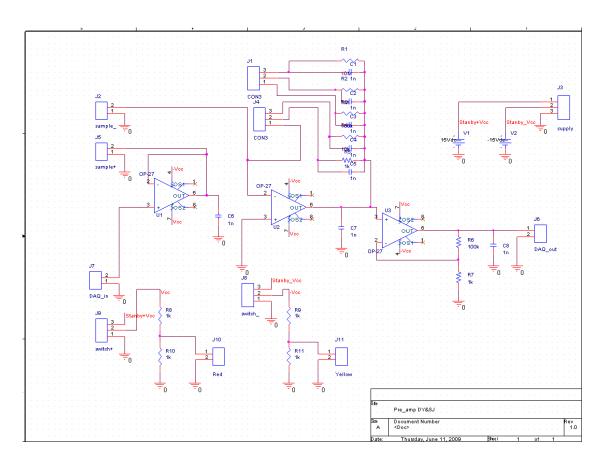

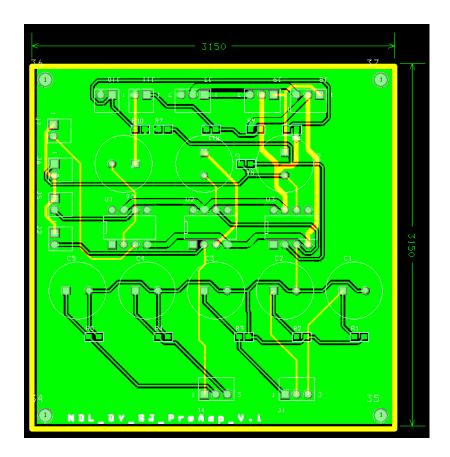

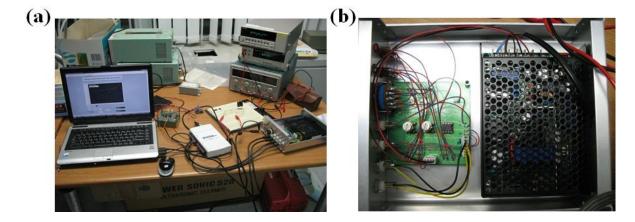

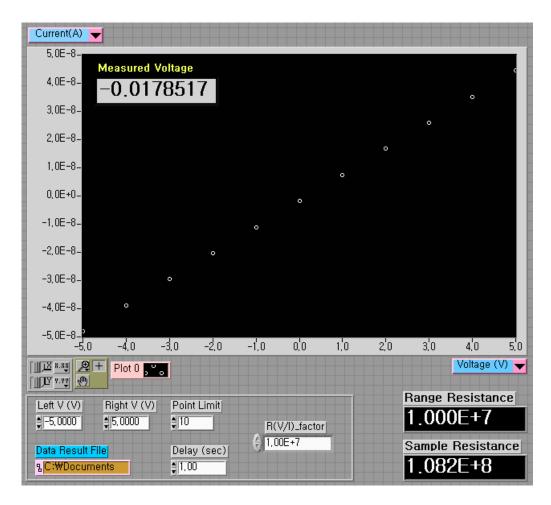

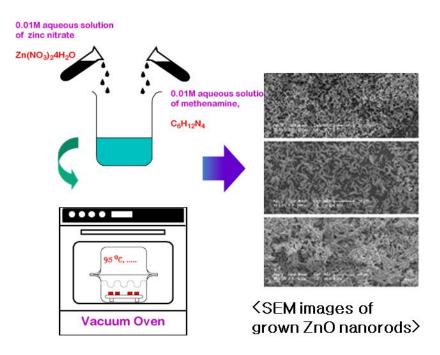

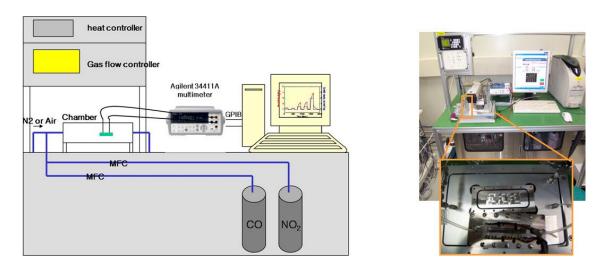

(2.4)