## Développement d'un outil de prédiction du comportement d'un circuit intégré sous impact laser en technologie CMOS

Catherine Godlewski

#### ▶ To cite this version:

Catherine Godlewski. Développement d'un outil de prédiction du comportement d'un circuit intégré sous impact laser en technologie CMOS. Autre. Université Sciences et Technologies - Bordeaux I, 2013. Français. NNT: 2013BOR15209. tel-00958998

### HAL Id: tel-00958998 https://theses.hal.science/tel-00958998

Submitted on 13 Mar 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre:

# THÈSE

#### PRÉSENTÉE A

### L'UNIVERSITÉ BORDEAUX 1

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUE ET DE L'INGENIEUR

#### Par Catherine GODLEWSKI

POUR OBTENIR LE GRADE DE

**DOCTEUR**

SPÉCIALITÉ : **ELECTRONIQUE**

# Développement d'un outil de prédiction du comportement d'un circuit intégré sous impact laser en technologie CMOS

Directeur de recherche: Pascal FOUILLAT

Soutenue le : 09 Décembre 2013

Devant la commission d'examen formée de :

M. RENOVELL, Michel Directeur de recherche CNRS Rapporteur et Président du Jury M. PORTAL, Jean-Michel Professeur Université Marseille Rapporteur M. FOUILLAT, Pascal Professeur Université Bordeaux 1 Directeur de recherche M. POUGET, Vincent Charger de recherche IMS-CNRS Co-directeur de recherche M. LEWIS, Dean Professeur Université Bordeaux 1 Co-directeur de recherche M. LISART, Mathieu Ingénieur STMicroelectronics Examinateur

# Résumé de la thèse

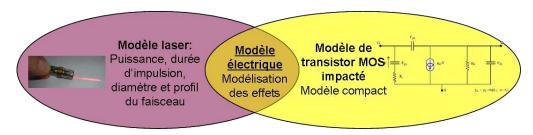

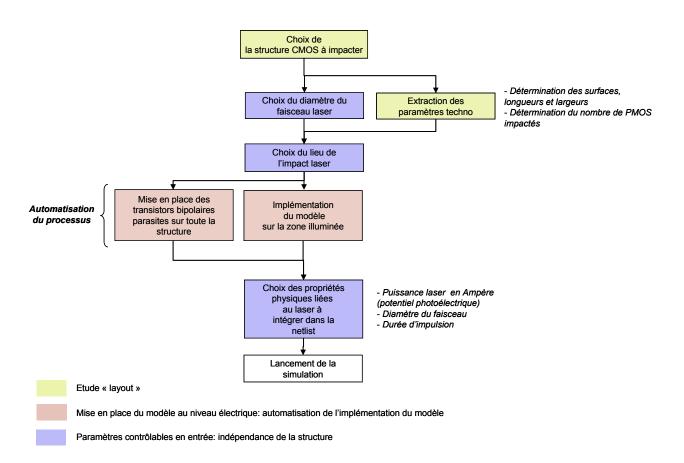

Ce travail porte sur l'analyse et l'étude du comportement de circuits intégrés en technologie CMOS soumis à un impact laser. **Une méthodologie d'implémentation d'un impact laser** a été développée et améliorée. Ainsi, elle est applicable à n'importe quelle description électrique d'un circuit CMOS, qu'il soit digital ou analogique. Ce procédé est conçu pour permettre aux concepteurs de circuits intégrés pouvant être soumis à des attaques laser, de tester leur circuit en simulation avant leur fabrication et de démontrer leur robustesse.

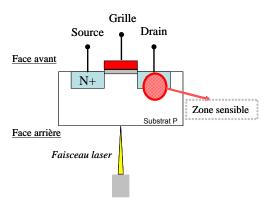

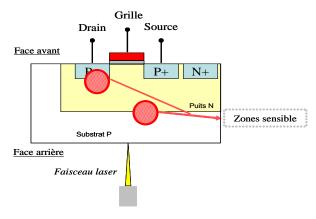

Notre étude s'est focalisée sur le développement d'un **outil de simulation intégrant un modèle électrique de l'impact laser sur les transistors MOS** afin de reproduire de façon qualitative le comportement du circuit face à un impact laser (attaque semi-invasive en face arrière du circuit), et ce quelques soient ses propriétés physiques.

Une première partie d'état de l'art est consacrée à la synthèse des différentes attaques sur circuits sécurisées que l'on peut rencontrer dans le domaine de la microélectronique, telles que les attaques semi-invasives, non invasives ou invasives par exemple. Une seconde partie théorique dédiée à l'interaction laser-silicium au niveau physique nous permet d'étudier les différents acteurs mis en jeu (propriétés physiques du laser – puissance, diamètre et profil du faisceau), avant de les importer comme paramètres dans le domaine électrique.

Cette étude se poursuit alors par l'élaboration d'un modèle électrique et d'une méthodologie de simulation dont le but est de permettre de reproduire le comportement de n'importe quel circuit impacté par un laser. Le flot de modélisation passe ainsi en revue l'ensemble des paramètres contrôlables en entrée, qu'il s'agisse des propriétés physiques du laser, traduites dans le domaine électrique, ou encore de la réalité géométrique du circuit impacté, quel que soit sa complexité. Par ailleurs, la flexibilité de cette approche permet de s'adapter à toute évolution du modèle de l'impact laser en lui-même. Il est ainsi possible de simuler un impact intégrant ou non tout ou partie des phénomènes parasites déclenchés par le photocourant. Enfin, il couvre aussi bien des analyses de comportement dans le domaine statique, que dans celui temporel, où la durée d'impulsion du laser prend toute son importance.

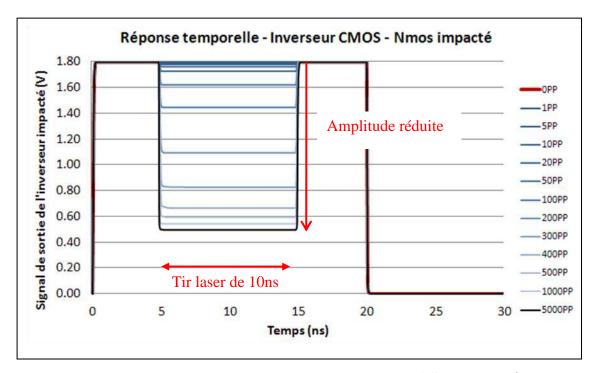

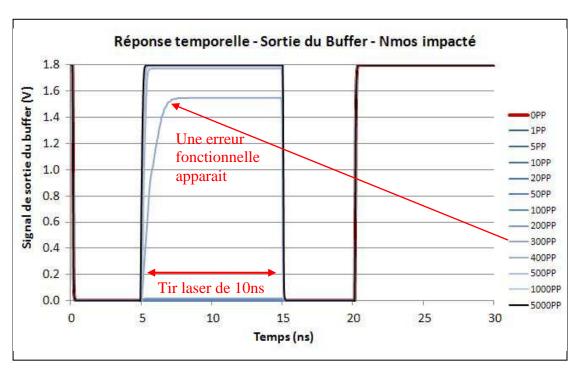

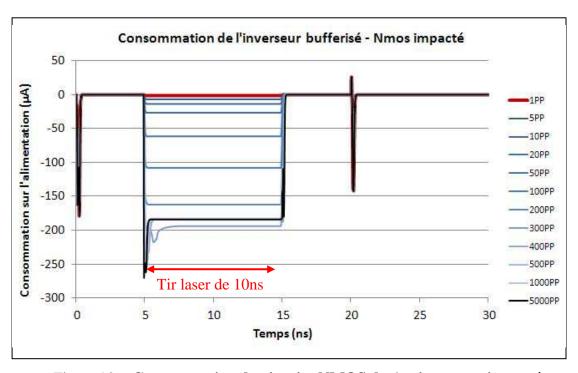

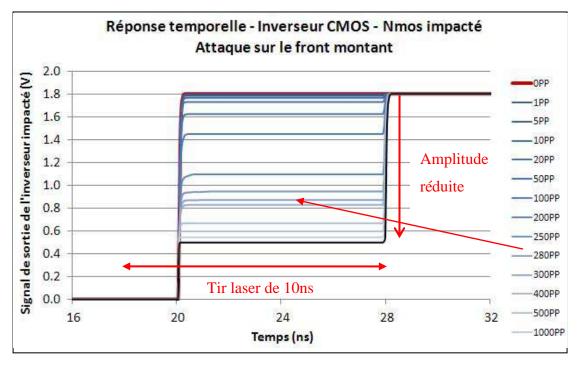

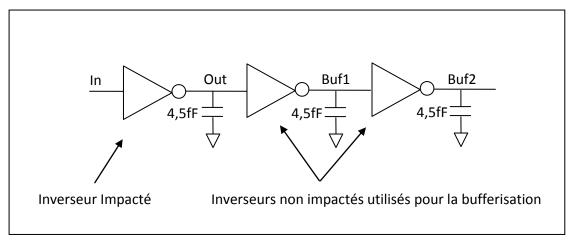

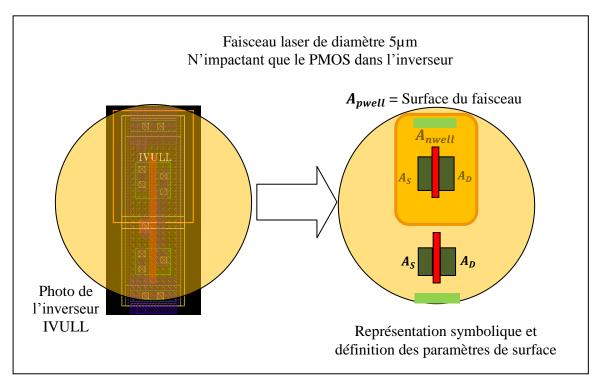

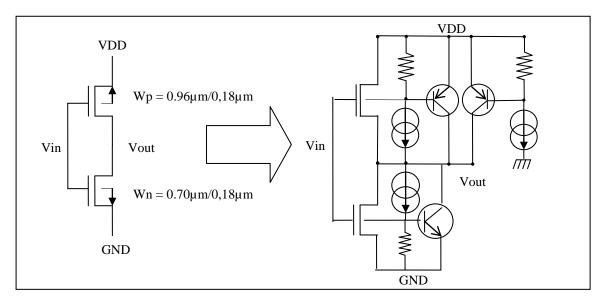

Afin de démontrer la cohérence de cette méthodologie face à nos attentes théoriques, le comportement de transistors NMOS, PMOS et un inverseur CMOS ont été étudiés au niveau simulation. Cette étude préliminaire nous a permis de calibrer et de valider notre modèle et sa méthodologie d'utilisation avec la théorie attendue : création d'un photocourant proportionnel au potentiel appliqué sur la jonction de drain et couplé au potentiel photoélectrique ainsi qu'à la surface impactée, déclenchement des bipolaires parasites latéraux, etc.... L'analyse sur un inverseur CMOS bufferisé ou non nous donne encore plus d'informations quant aux analyses dynamiques ou statiques : un impact sur un état statique (0 ou 1) ne peut entraîner que des fautes fonctionnelles, alors qu'un impact sur une transition ralentit ou accélère le signal en sortie, au risque de générer une faute fonctionnelle.

Enfin, l'étude de différents circuits complexes sur silicium face à plusieurs types de faisceau laser nous a permis de confronter notre méthodologie à la mesure. Une chaîne d'inverseurs, une bascule de type D, et un circuit de verrouillage ont ainsi été impactés. Les résultats observés en simulation sont cohérents avec la mesure, notamment du point de vue comportemental et fonctionnel. Bien plus, cet outil de prédiction macroscopique nous permet d'analyser dans le détail les mécanismes sous-jacents à la création de fautes observées, afin de comprendre les faiblesses du circuit ou celles de son implémentation layout. Des parades peuvent alors être testées.

Ce travail final valide ainsi l'outil développé ainsi que sa méthodologie d'implémentation : ce « flot d'intégration » pourrait permettre aux concepteurs d'anticiper ou prédire le comportement d'un circuit face à un impact laser, afin de trouver des solutions de contremesures et de rendre ainsi plus robustes leurs circuits face aux attaques laser.

MOTS CLÉS: Interaction laser-silicium, laser, modélisation électrique, flot d'intégration, méthodologie, fautes fonctionnelles, fautes comportementales, CMOS, prédiction du comportement, photocourant, potentiel photoélectrique

À ma famille, et à Nicolas.

Sans eux, je ne serai pas ce que je suis aujourd'hui.

# Remerciements

Les travaux présentés dans ce manuscrit s'inscrivent dans le cadre d'une convention CIFRE entre la société STMicroelectronics et le laboratoire IMS à Bordeaux, de 2006 à 2009 puis de 2009 à 2013.

Tout d'abord, je tiens à remercier grandement Monsieur Pascal Fouillat ainsi que Monsieur Vincent Pouget de m'avoir accordé leur confiance tout au long de ce projet. Ce travail de longue haleine n'aurait jamais abouti sans leur soutien.

Je remercie tout particulièrement Monsieur Mathieu Lisart, mon tuteur industriel au sein de la division SmartCard de la société STMicroelectronics, de m'avoir encadré, et soutenu pendant ces trois années. Ses conseils et son expertise m'ont permis d'arriver à ces résultats scientifiques.

J'exprime toute ma gratitude à Monsieur Jean-Michel Portal et Monsieur Michel Renovell qui ont pris le temps de lire le manuscrit et d'en faire chacun un rapport complet et détaillé. Je suis touchée et honorée qu'ils aient accepté d'examiner ce travail en qualité de rapporteurs de mon manuscrit de thèse.

Ma respectueuse reconnaissance s'adresse également à Monsieur Dean Lewis, Directeur de l'Université de Bordeaux I, qui m'a accordé le privilège de prendre part à mon jury de soutenance de thèse.

Je suis sincèrement reconnaissante envers Monsieur Sami Ajram, Docteur et Directeur de la société SL3J Systems d'avoir cru en moi ; et de m'avoir donné les armes techniques nécessaires pour défendre mes idées.

Que l'ensemble des membres de la division SmartCards ainsi que le personnel de la société STMicroelectronics trouvent ici ma gratitude pour leur support et leur sympathie. Plus particulièrement, un grand merci à Monsieur Bruno Nicolas pour m'avoir épaulé techniquement lors des expérimentations.

Enfin, je souhaite partager ce cri de victoire avec celui qui partage ma vie aujourd'hui. Son soutien moral et technique m'aura permit de conclure ce projet de longue haleine.

# TABLE DES MATIÈRES

| RESUME DE LA THE     | SE                                                                  | 2  |

|----------------------|---------------------------------------------------------------------|----|

| REMERCIEMENTS        |                                                                     | 6  |

| TABLE DES MATIÈR     | ES                                                                  | 8  |

| INTRODUCTION GEN     | NERALE                                                              | 14 |

| CHAPITRE I : CONTI   | EXTE ET ETAT DE L'ART                                               | 16 |

| 1 Contexte           |                                                                     | 16 |

| 1.1 Applications     | sécurisées et circuits intégrés                                     | 16 |

| 1.2 Test et attaqu   | es sur les circuits et systèmes sécurisés                           | 18 |

|                      | rsique sur carte à puce                                             |    |

| 1.2.1.1 Attaqı       | ue invasive ou intrusive                                            | 19 |

| 1.2.1.2 Attaqı       | ue non-invasive ou non-intrusive                                    | 19 |

| 1.2.1.3 Attaqu       | ue semi-invasive                                                    | 20 |

| 1.2.2 Attaque log    | ique sur carte à puce                                               | 21 |

| 1.2.3 Résumé sch     | ématique des différentes attaques                                   | 21 |

| 1.2.4 Les moyens     | de protection contre les attaques recensées                         | 22 |

| 1.2.4.1 Protect      | ction contre les attaques invasives                                 | 22 |

| 1.2.4.2 Protect      | ction contre les attaques non invasives                             | 23 |

| 1.2.4.3 Protect      | ction contre les attaques semi-invasives                            | 24 |

| 2 État de l'art de l | 'interaction laser silicium                                         | 27 |

| 2.1 Les principes    | de test par injection laser                                         | 27 |

| 2.1.1 Les différen   | tes stimulations                                                    | 28 |

| 2.1.1.1 Les te       | chniques OBIC et LIVA                                               | 28 |

| 2.1.1.2 Les te       | chniques OBIRCH, TIVA et SEI                                        | 30 |

| 2.1.1.3 La tec       | hnique « XIVA »                                                     | 31 |

| 2.2 Interaction las  | ser semi-conducteur en régime photoélectrique                       | 31 |

| 2.2.1 Mécanismes     | s physiques mis en jeu lors d'une interaction laser semi-conducteur | 32 |

| 2.2.1.1 Cas de       | es lasers continus                                                  | 32 |

| 2.2.1.2 Cas de       | es lasers impulsionnels                                             | 38 |

| 2.2.2 Limite du m    | odèle physique appliqué au silicium                                 | 42 |

| 2.3 Des mécanism     | nes à la modélisation électrique : ordres de grandeur utilisés      | 42 |

| 2.2.1 La diamètra    | du faisagan lasar                                                   | 12 |

| 2.     | 3.2 Le             | e profil du faisceau                                             | 44          |

|--------|--------------------|------------------------------------------------------------------|-------------|

| 2.     | 3.3 La             | a durée d'impulsion                                              | 44          |

| 2.     | 3.4 La             | a longueur d'onde                                                | 45          |

| 2.     | 3.5 La             | a puissance laser                                                | 45          |

| 3 C    | onclusi            | on                                                               | 47          |

| СНАРІТ | RE II :            | : METHODOLOGIE DE MODELISATION                                   | 48          |

| 1 M    | Iodélisa           | ation au niveau électrique : concepts                            | 48          |

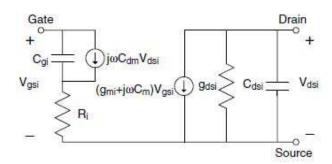

| 1.1    | Mod                | èle compact ou modèle de transistors MOS impacté                 | 49          |

| 1.2    | Le la              | aser                                                             | 50          |

| 1.3    | L'im               | npact laser semi-conducteur                                      | 51          |

| 2 M    | Iodélisa           | ntion électrique de l'interaction photoélectrique laser semi-co  | nducteur 52 |

| 2.1    | Intro              | duction à la modélisation                                        | 52          |

| 2.2    | Etat               | de l'art des modèles existants                                   | 52          |

| 2.3    | Limi               | tations des modèles existants                                    | 55          |

| 2.4    | Nou                | veau modèle électrique du premier ordre                          | 56          |

| 2.     | 4.1 In             | troduction aux éléments parasites au sein des structures CMOS    | 56          |

|        | 2.4.1.1            | Exemples de stress induisant l'intervention d'éléments parasites | 57          |

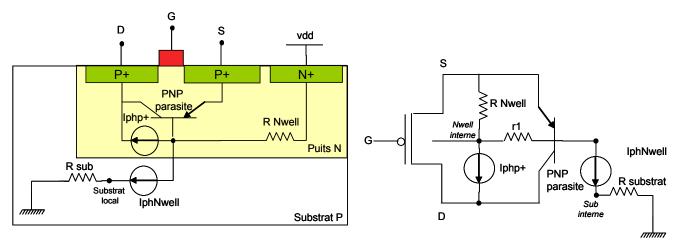

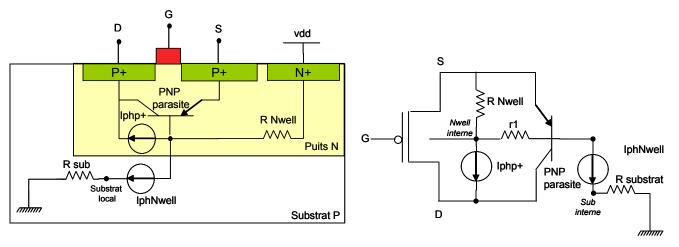

| 2.     | 4.2 Le             | es phénomènes parasites amorcés via l'impact laser               | 58          |

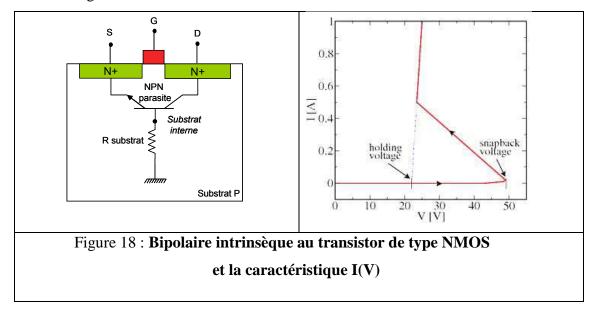

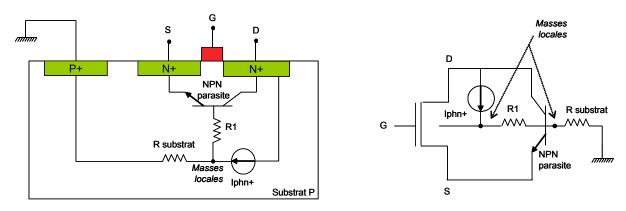

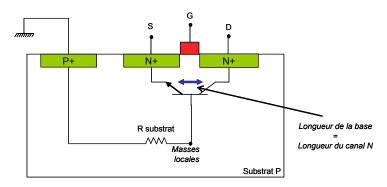

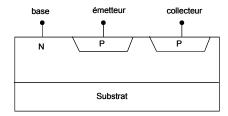

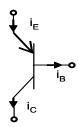

|        | 2.4.2.1            | Mécanisme d'amorçage du transistor latéral parasite              | 58          |

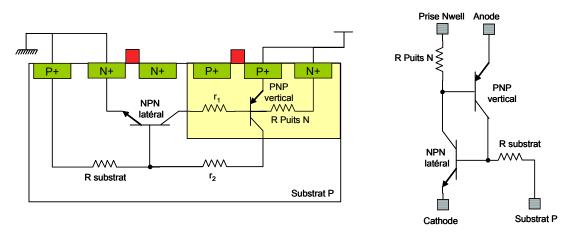

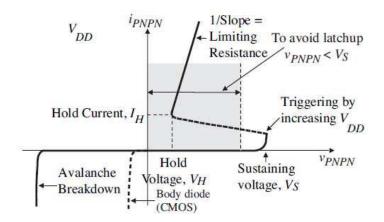

|        | 2.4.2.2            | Phénomène de SEL (Single Event Latchup )                         | 60          |

| 2.     | 4.3 Pa             | aramètres des bipolaires parasites au niveau du modèle           | 63          |

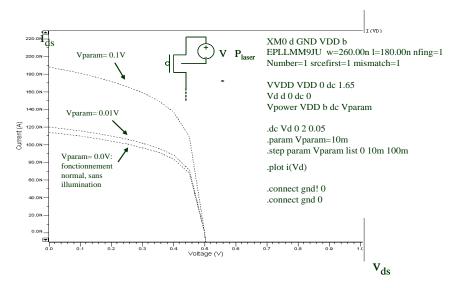

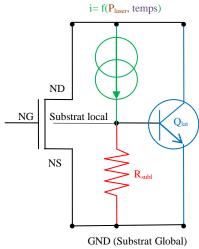

| 2.5    |                    | cription du modèle complet et application                        |             |

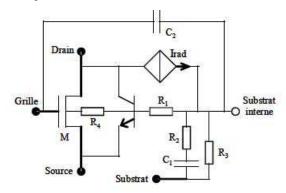

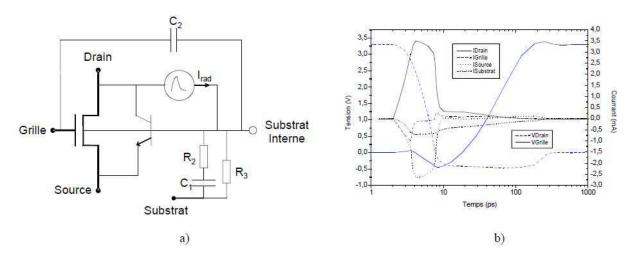

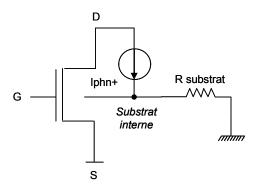

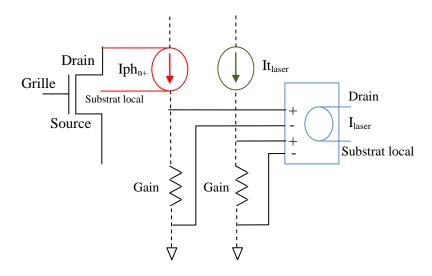

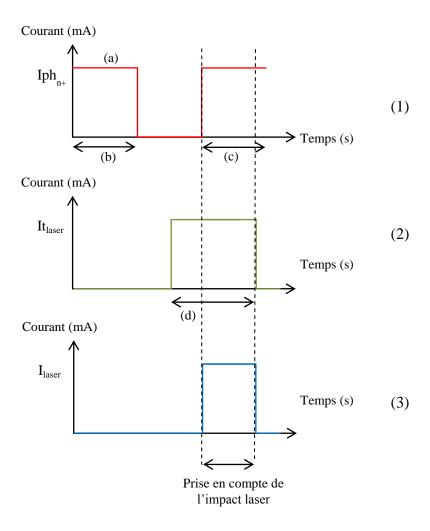

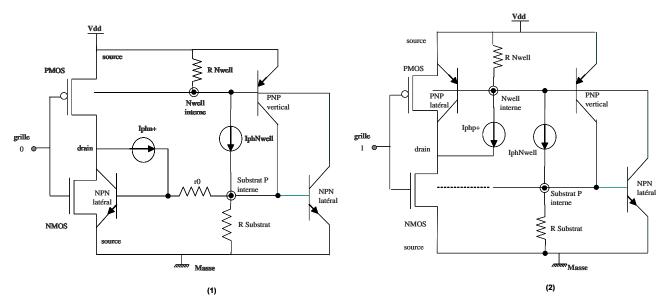

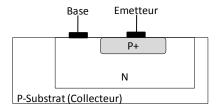

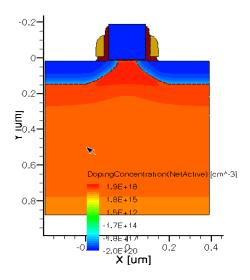

| 2.     | 5.1 Le             | e modèle du transistor NMOS                                      | 64          |

|        | 2.5.1.1            | Modèle du photocourant                                           |             |

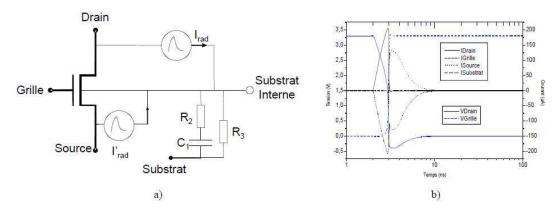

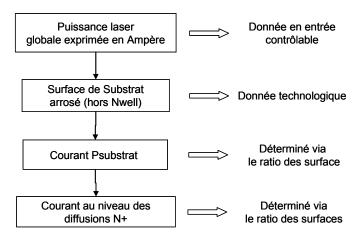

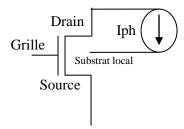

| 2.     |                    | e modèle du transistor PMOS                                      |             |

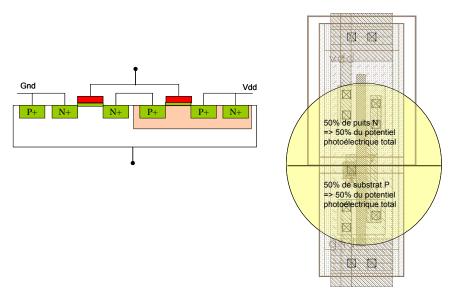

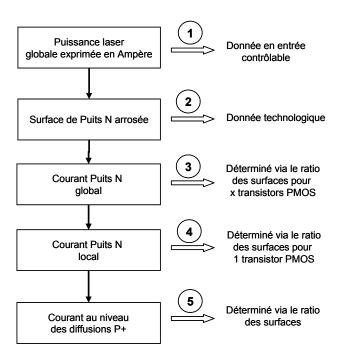

|        | 2.5.2.1            | Modèle des photocourants                                         |             |

|        | 2.5.2.2            | Méthodologie de répartition des photocourants                    |             |

| 2      | 2.5.2.3            | Eléments parasites et modèle du transistor PMOS                  |             |

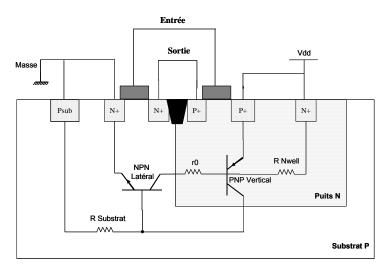

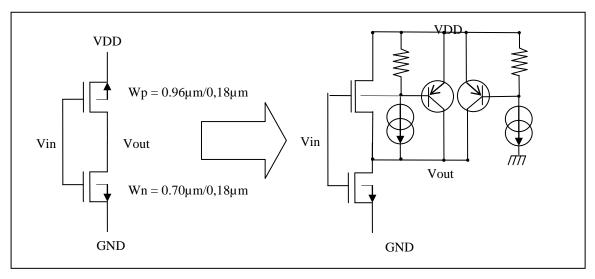

| 2.     |                    | odèle de l'inverseur                                             |             |

|        | 2.5.3.1<br>2.5.3.2 | Eléments parasites                                               |             |

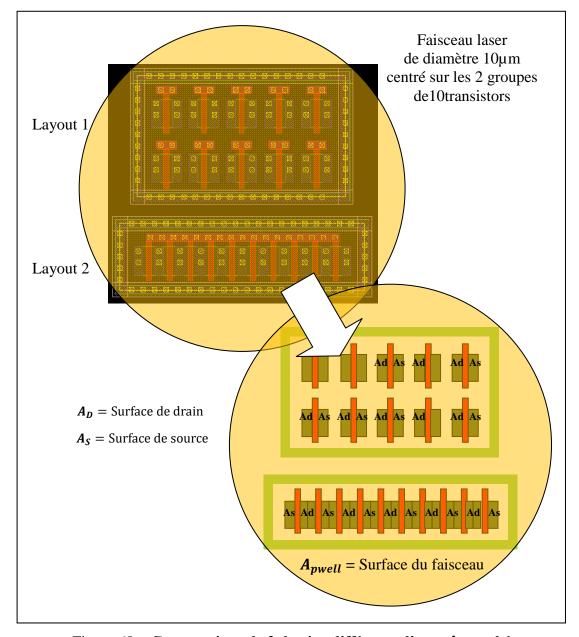

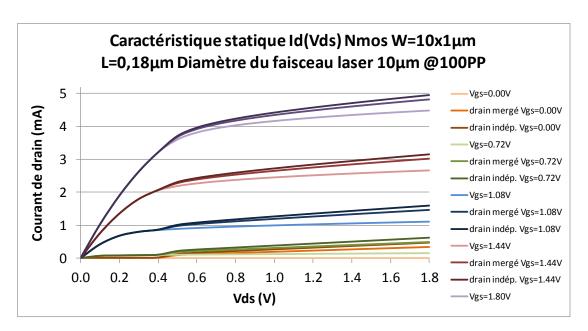

| 2      |                    | énéralisation à n transistors                                    |             |

|        |                    | on                                                               |             |

| 3 C    | onciusi            | UII                                                              |             |

| CHAPIT | RE III             | : COHERENCE DU MODELE & OUTIL DE PREDICTIO                       | N 92        |

| 1 S    | tructur            | es simples illuminées – Validation de la cohérence du modèle     | 92          |

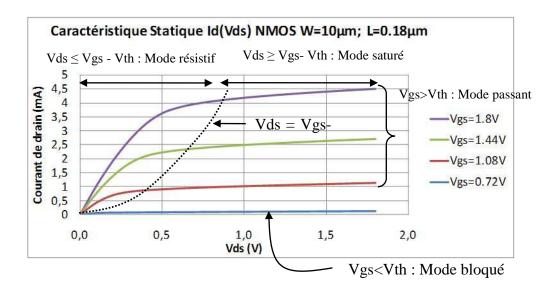

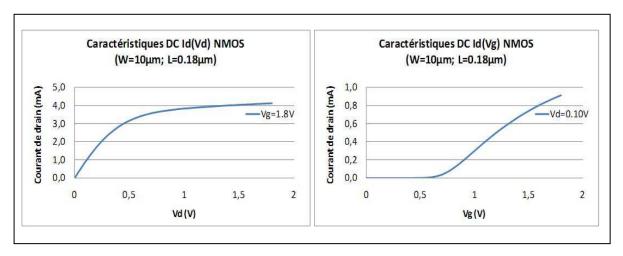

| 1.1    |                    | aportement d'un transistor NMOS impacté par notre modèle laser   |             |

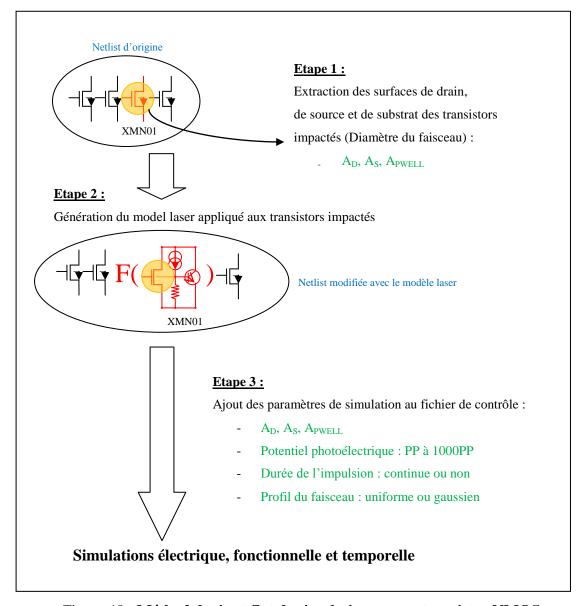

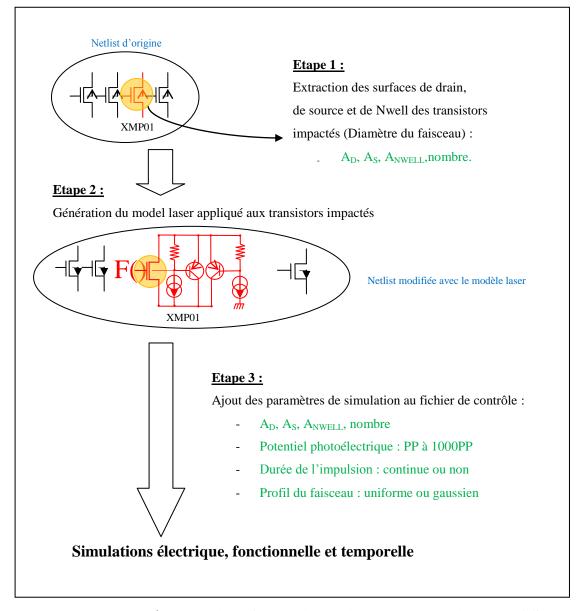

| 1.1.1  | Métho    | dologie et flot de simulation sur un transistor NMOS                      | 95  |

|--------|----------|---------------------------------------------------------------------------|-----|

| 1.1    | .1.1     | Contexte                                                                  | 95  |

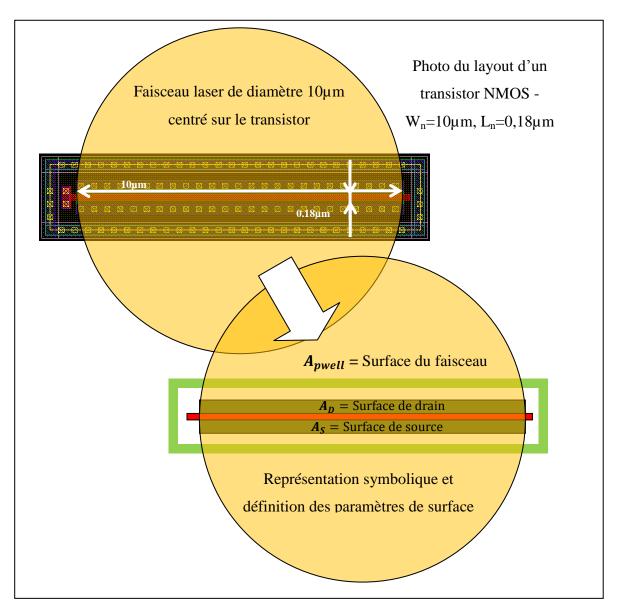

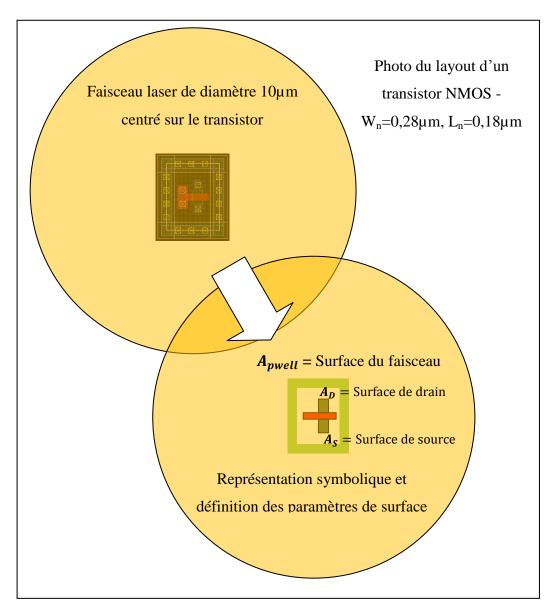

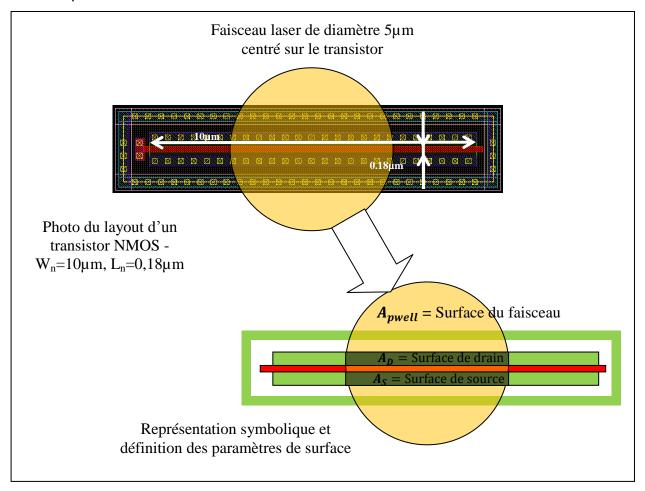

| 1.1    | .1.2     | Extraction géométrique du layout des transistors impactés                 | 96  |

| 1.1    | .1.3     | Programme et génération de la netlist électrique à simuler                | 98  |

| 1.1    | .1.4     | Fichier de contrôle et paramètres d'entrées du laser                      | 99  |

| 1.1.2  | Cohére   | ence des résultats de simulation sur le transistor NMOS                   | 101 |

| 1.1    | .2.1     | Attentes théoriques                                                       | 102 |

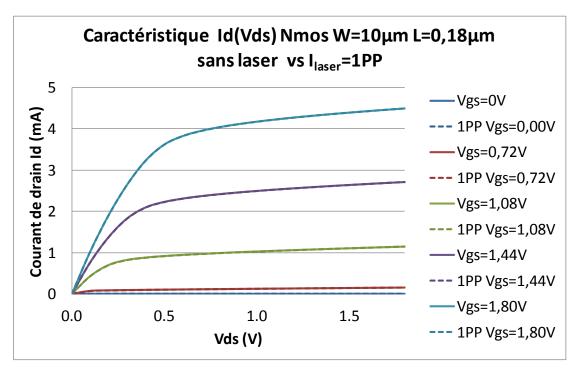

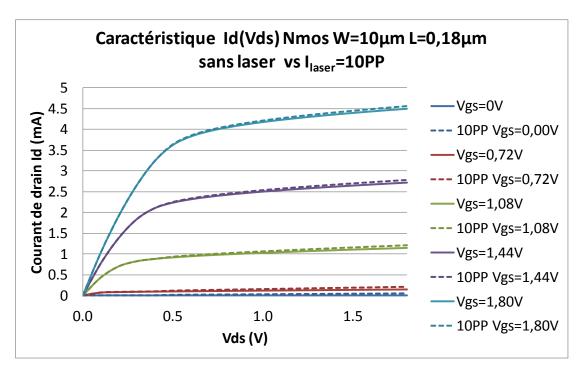

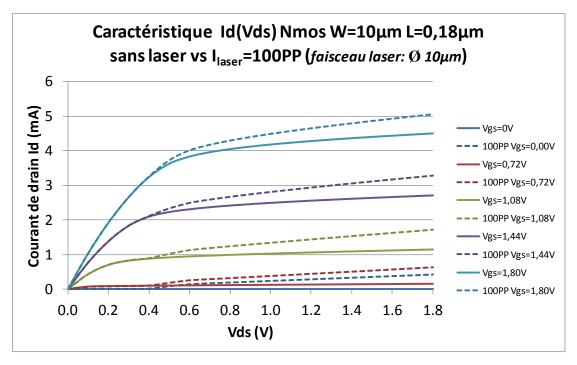

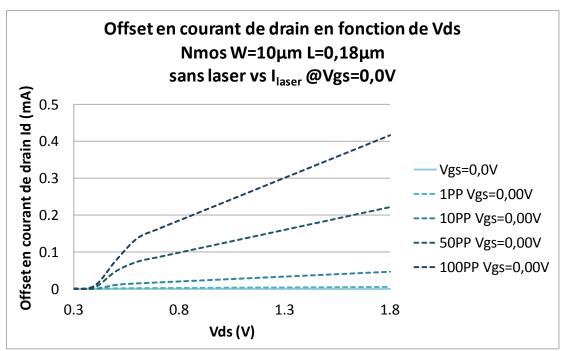

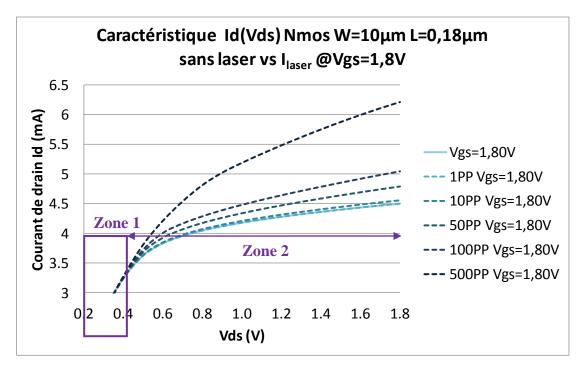

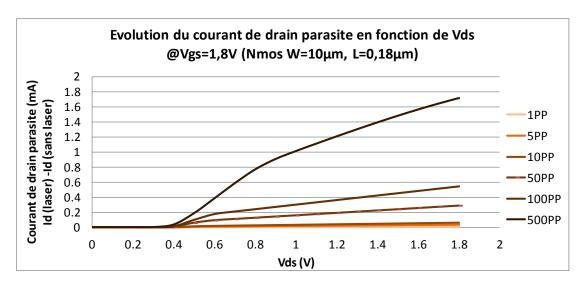

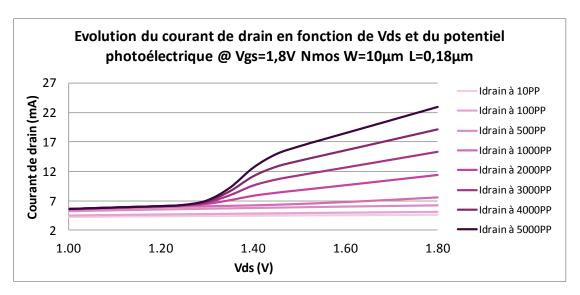

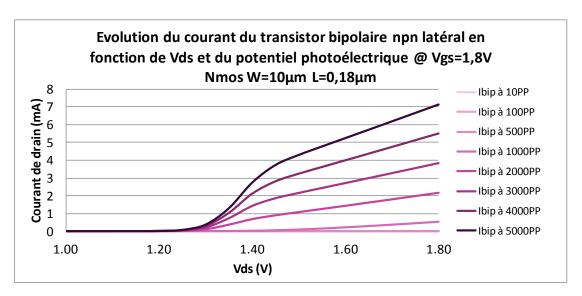

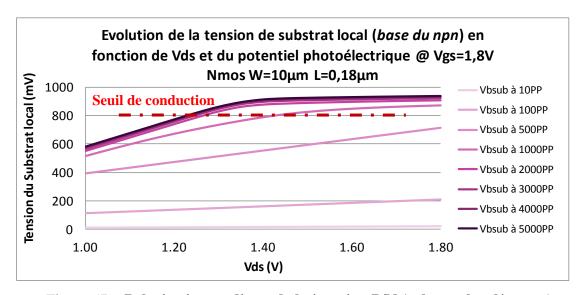

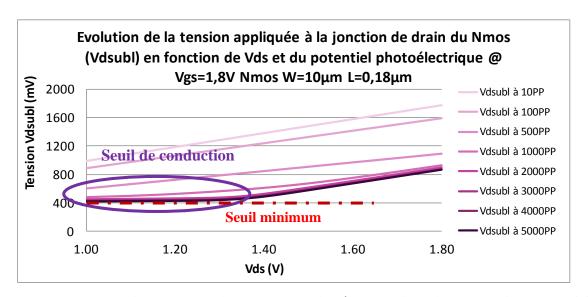

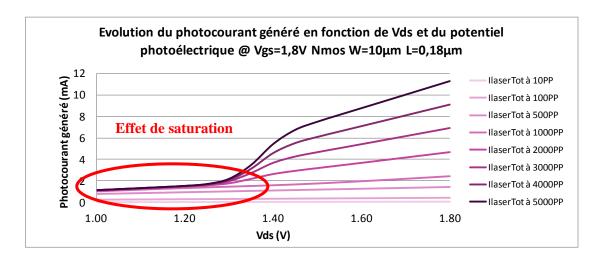

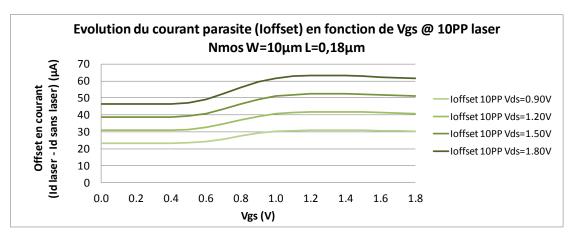

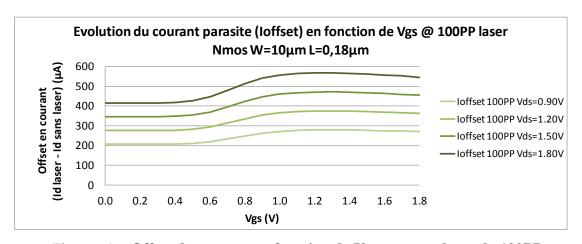

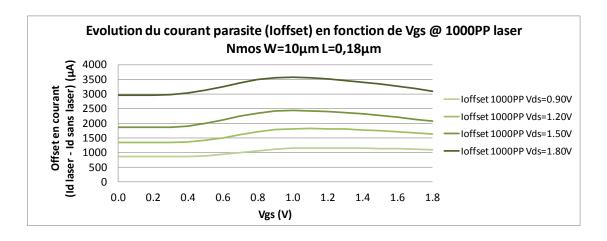

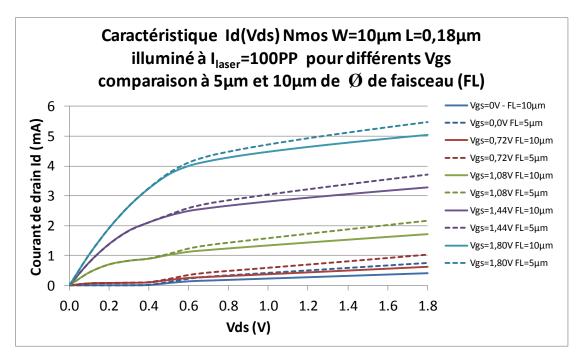

| 1.1    | .2.2     | Résultats pour un transistor NMOS constitué d'un doigt de 10μm/0,18μm     | 102 |

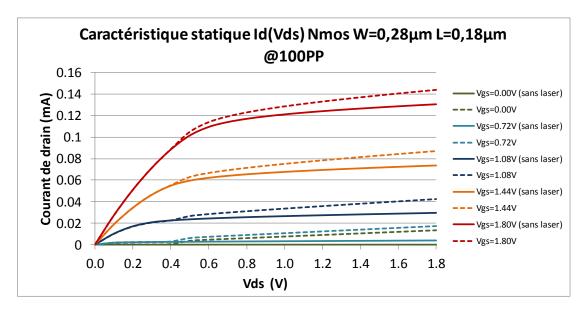

| 1.1    | .2.3     | Résultats pour un transistor NMOS constitué d'un doigt de 0,28μm/0,18μm   | 113 |

| 1.1    | .2.4     | Variation de la dimension du faisceau                                     | 117 |

| 1.1    | .2.5     | Influence du layout dans l'extraction des paramètres et simplification    | 120 |

| 1.1.3  | Valida   | tion de la cohérence du modèle sur le transistor NMOS                     | 123 |

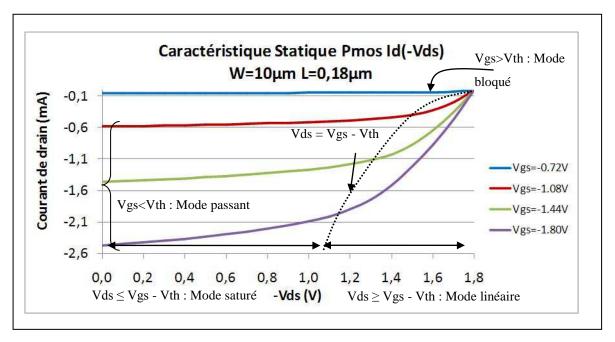

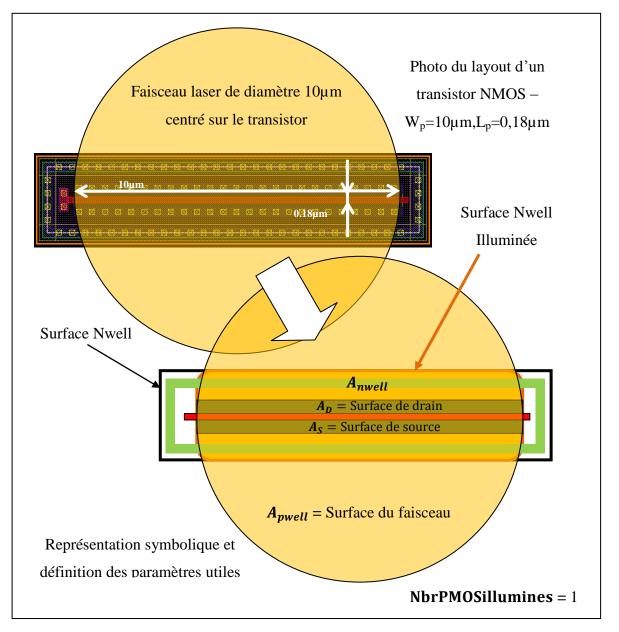

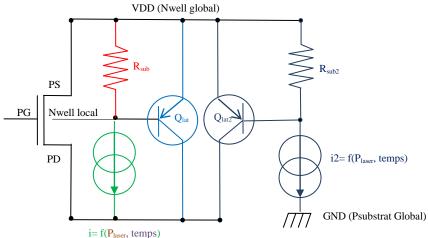

| 1.2    | Comport  | tement d'un transistor PMOS impacté par notre modèle laser                | 123 |

| 1.2.1  | Métho    | dologie et flot de simulation sur un transistor PMOS                      | 125 |

| 1.2    | .1.1     | Contexte                                                                  | 125 |

| 1.2    | .1.2     | Extraction géométrique du layout des transistors impactés                 | 125 |

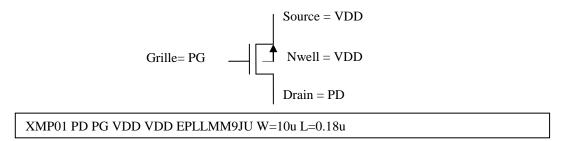

| 1.2    | .1.3     | Programme et génération de la netlist à simuler                           | 127 |

| 1.2    | .1.4     | Fichier de contrôle et paramètres d'entrée du laser                       | 129 |

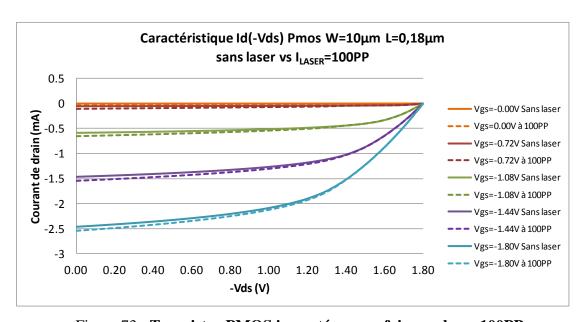

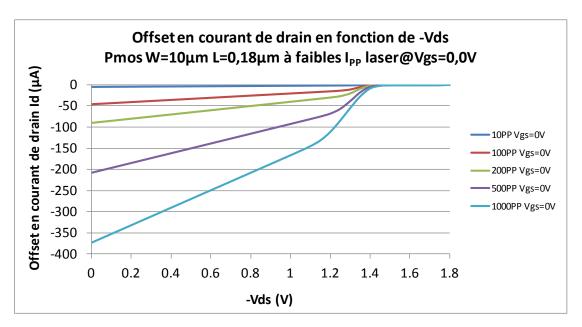

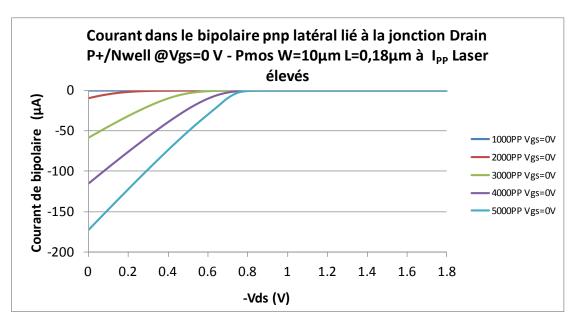

| 1.2.2  | Cohére   | ence des résultats de simulation sur le transistor PMOS                   | 130 |

| 1.2.3  | Valida   | tion de la cohérence du modèle sur le transistor PMOS                     | 136 |

| 1.3    | Conclusi | on sur la validité du modèle sur des structures simples                   | 137 |

| 2 L'in | verseur  | - Prédiction par la simulation des comportements possibles                | 138 |

| 2.1    | Rappels  | théoriques sur les caractéristiques statiques et dynamiques d'un inverseu | r   |

| CMOS   |          |                                                                           |     |

| 2.1.1  |          | se statique                                                               | 139 |

| 2.1.2  | •        | se dynamique                                                              |     |

| 2.2    | ·        | tement d'un inverseur dont seul le NMOS est impacté                       |     |

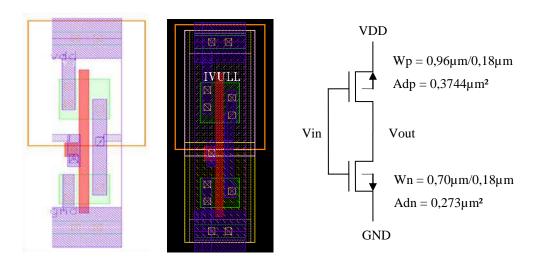

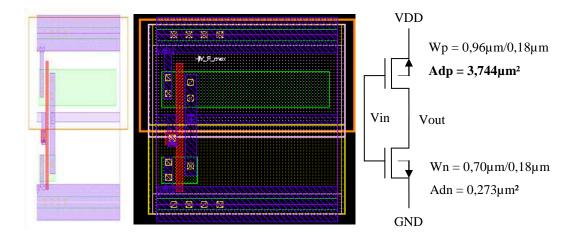

| 2.2.1  | •        | tion géométrique du layout des transistors impactés                       |     |

| 2.2.2  |          | na équivalent et netlist électrique à simuler                             |     |

| 2.2.3  |          | quences de l'impact laser sur les caractéristiques statiques              |     |

| 2.2.4  |          | quences de l'impact laser sur les caractéristiques dynamiques             |     |

|        |          | Impact laser sur un niveau stable à « 1 »                                 |     |

|        |          | Impact laser sur un niveau stable à « 0 »                                 |     |

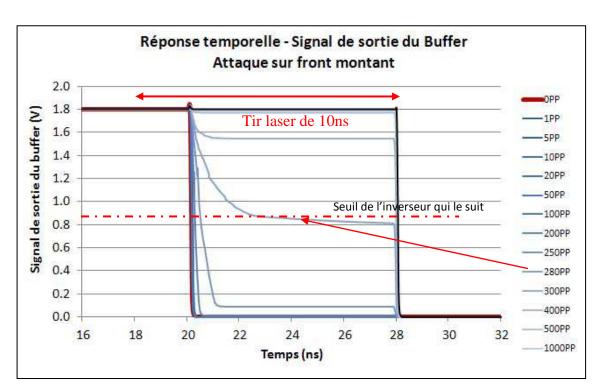

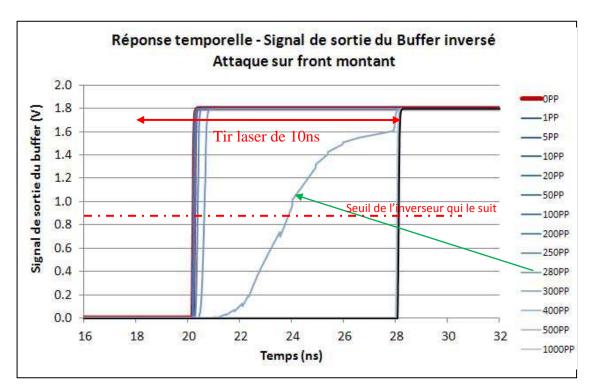

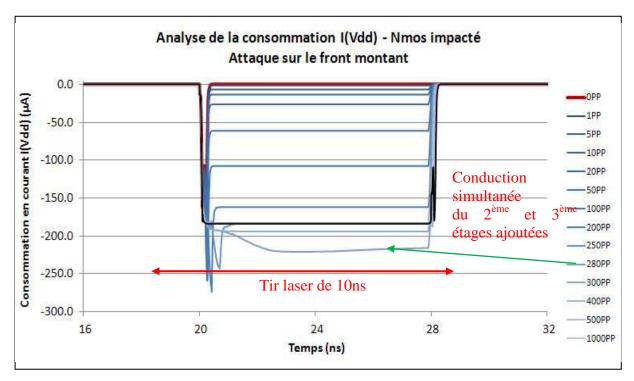

|        |          | Impact laser durant une transition montante de « 0 » vers « 1 »           |     |

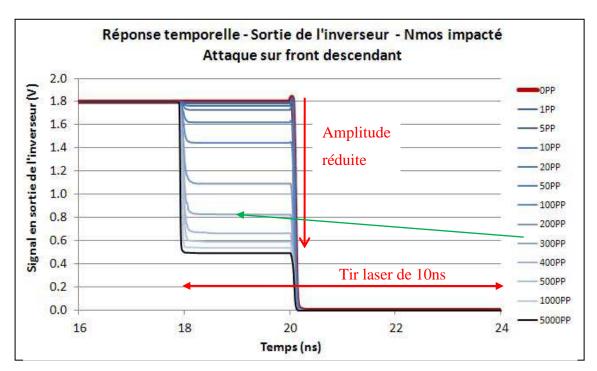

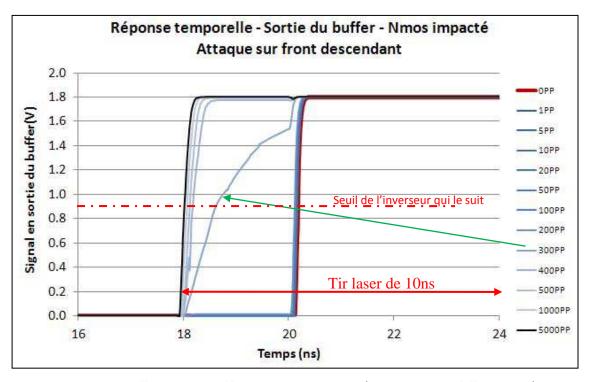

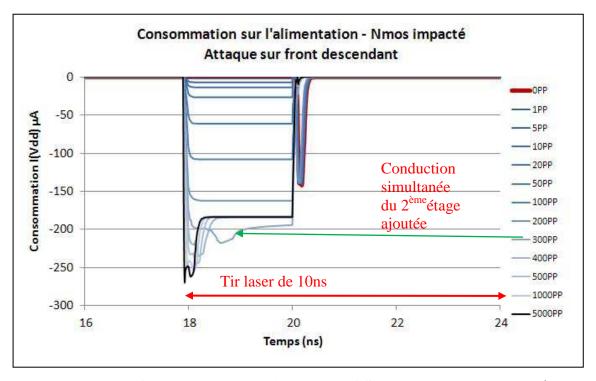

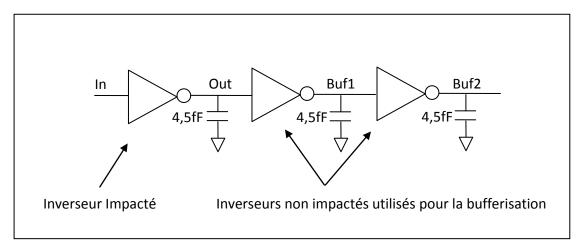

|        |          | Impact laser durant une transition descendante de « 1 » vers « 0 »        |     |

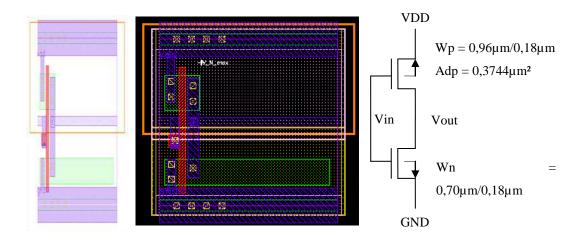

|        |          | tement d'un inverseur dont seul le PMOS est impacté                       |     |

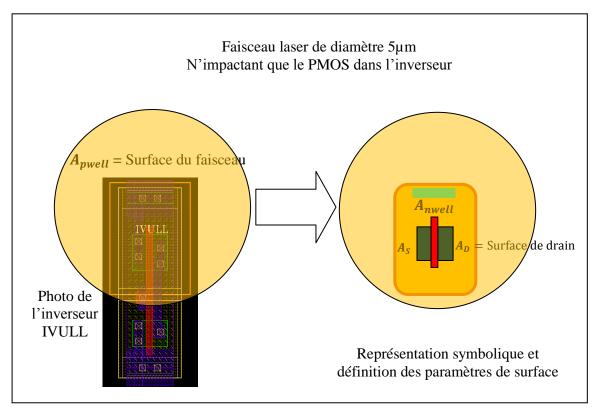

| 2.3.1  | -        | tion géométrique du layout des transistors impactés                       |     |

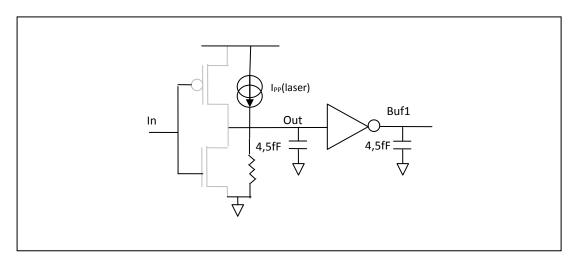

| 2.3.2  |          | na équivalent et Netlist électrique à simuler                             |     |

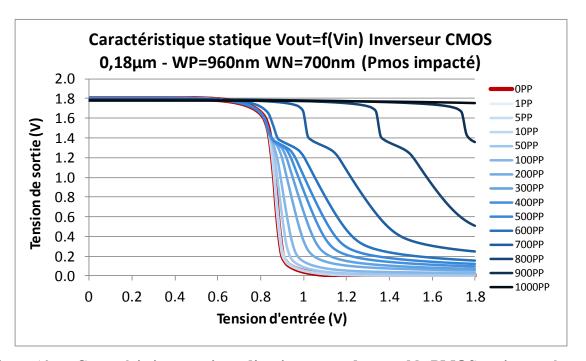

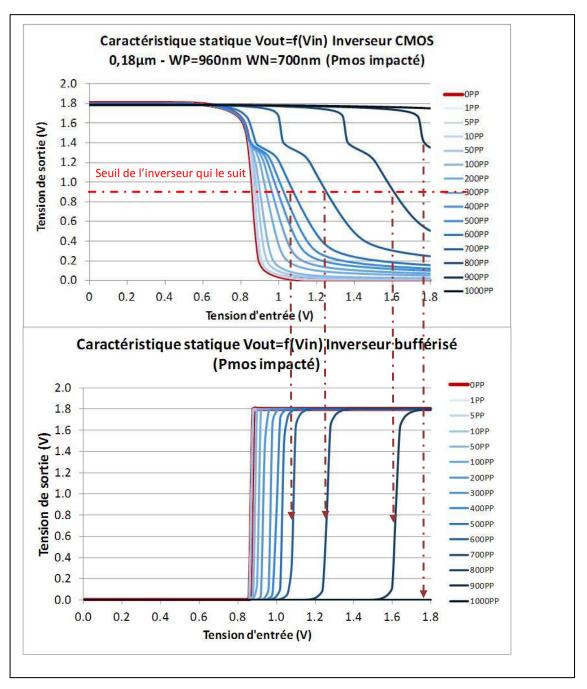

| 2.3.3  |          | quences de l'impact laser sur les caractéristiques statiques              |     |

|     | 2.3.4   | Conséquences de l'impact laser sur les caractéristiques dynamiques     | 167 |

|-----|---------|------------------------------------------------------------------------|-----|

|     | 2.3.    | 4.1 Impact laser sur un niveau stable à « 0 »                          | 167 |

|     | 2.3.    | 4.2 Impact laser sur un niveau stable à « 1 »                          | 169 |

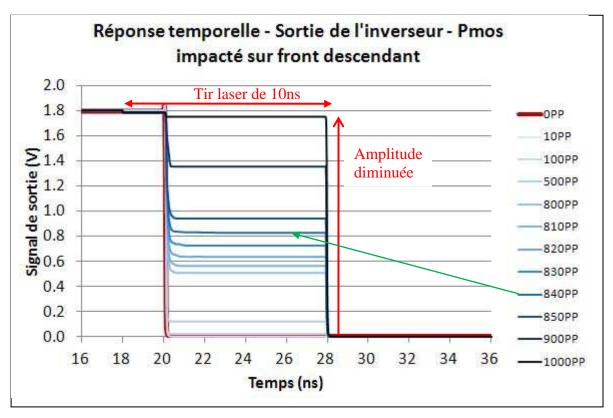

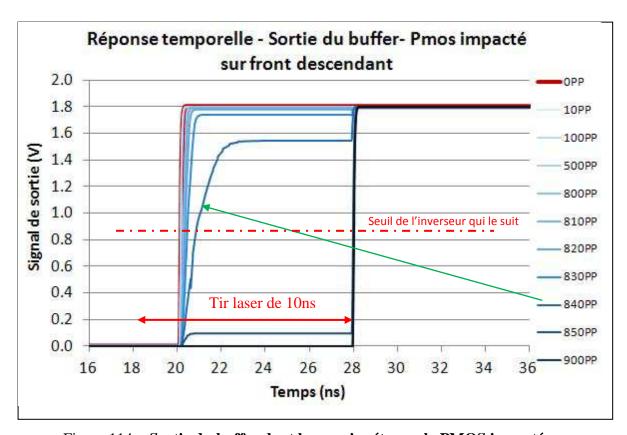

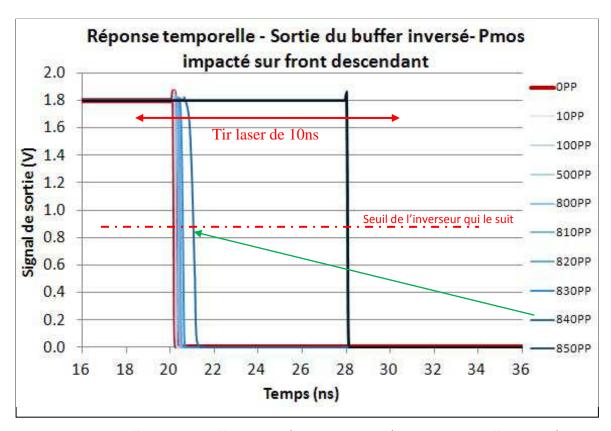

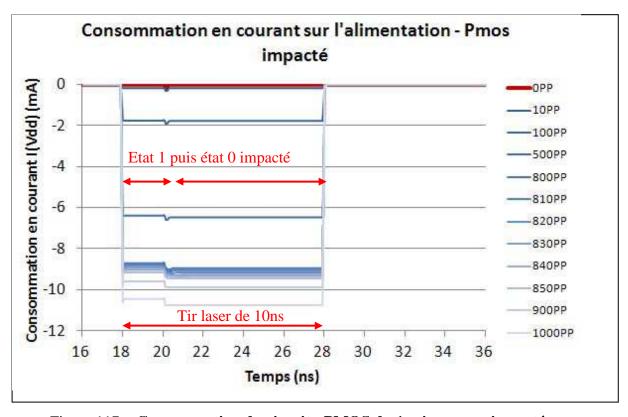

|     | 2.3.    | 4.3 Impact laser durant une transition descendante de « 1 » vers « 0»  | 169 |

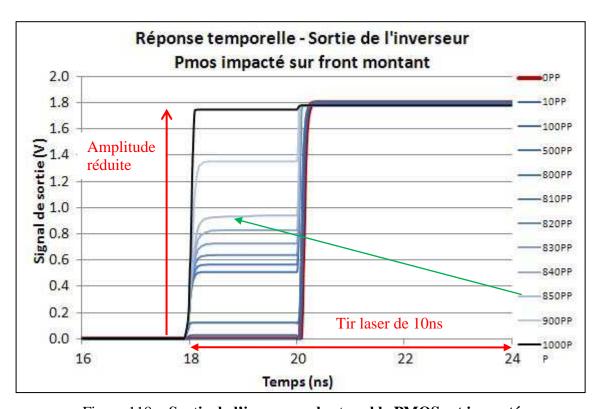

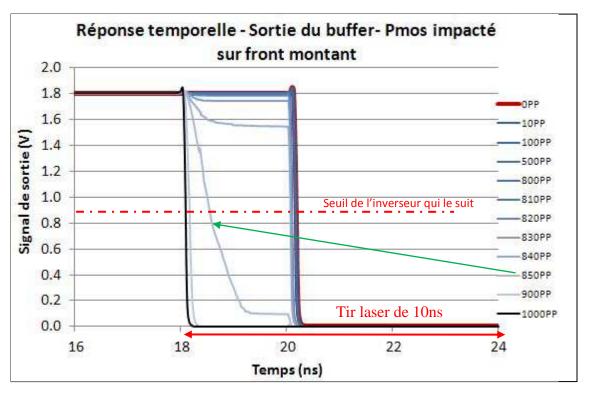

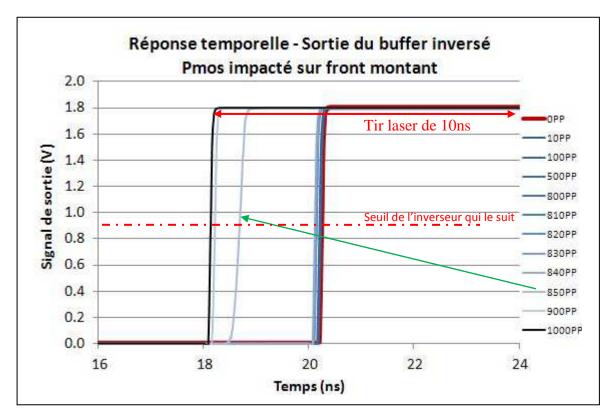

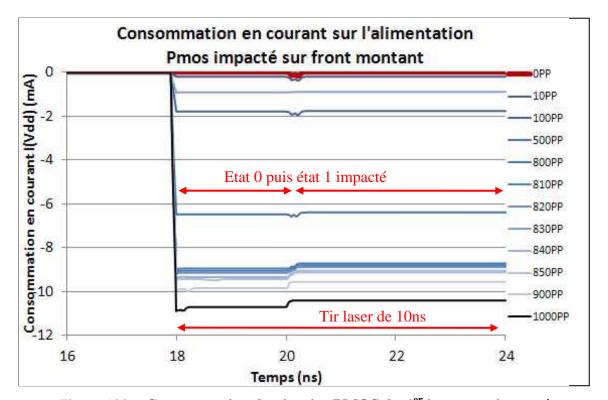

|     | 2.3.    | 4.4 Impact laser durant une transition montante de « 0 » vers « 1 »    | 174 |

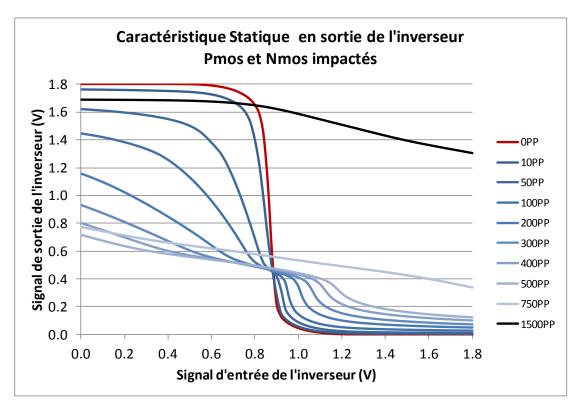

|     | 2.4     | Comportement d'un inverseur dont le NMOS et le PMOS sont impactés      | 178 |

|     | 2.4.1   | Extraction géométrique du layout des transistors impactés              | 179 |

|     | 2.4.2   | Schéma équivalent et Netlist électrique à simuler                      | 179 |

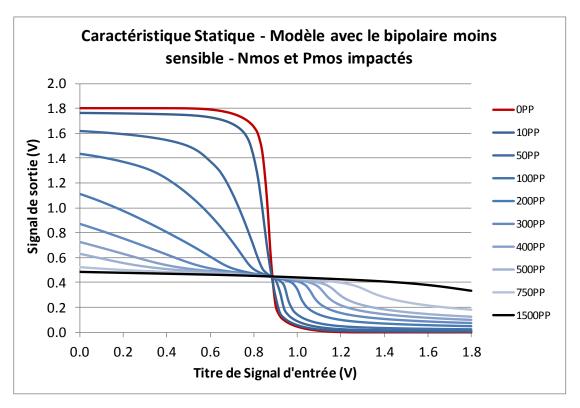

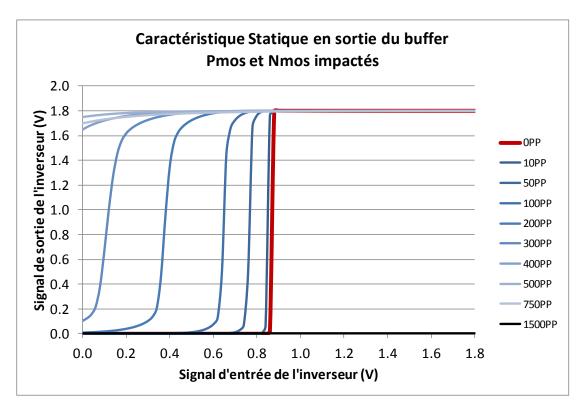

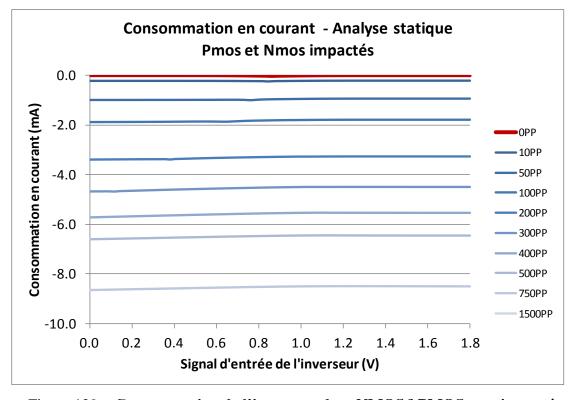

|     | 2.4.3   | Conséquences de l'impact laser sur les caractéristiques statiques      | 180 |

|     | 2.4.4   | Conséquences de l'impact laser sur les caractéristiques dynamiques     | 184 |

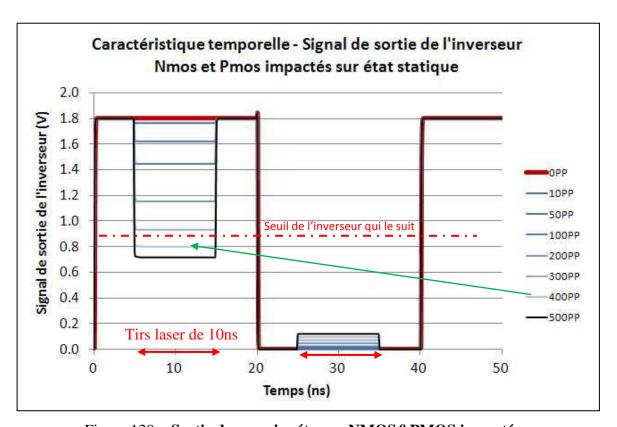

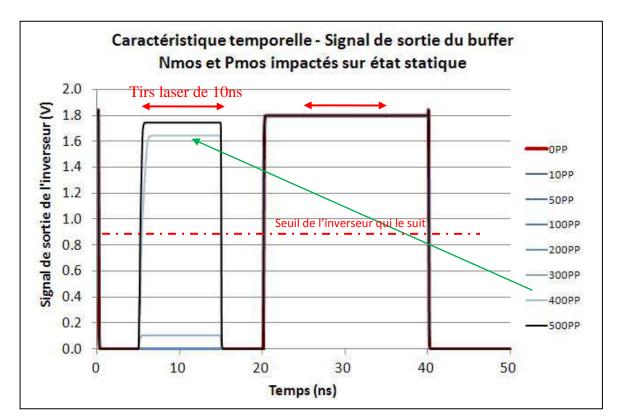

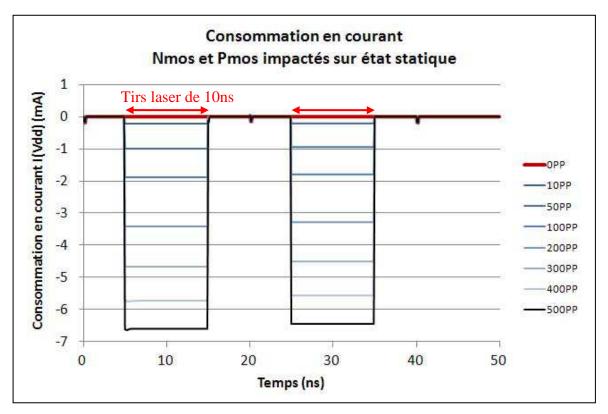

|     | 2.4.    | 4.1 Impact laser sur un niveau stable à « 0 » et à « 1 »               | 184 |

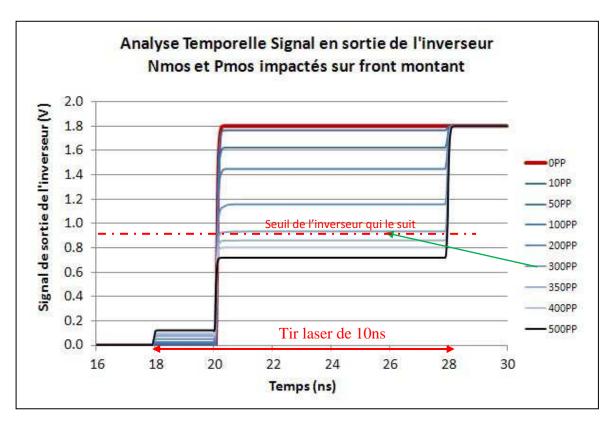

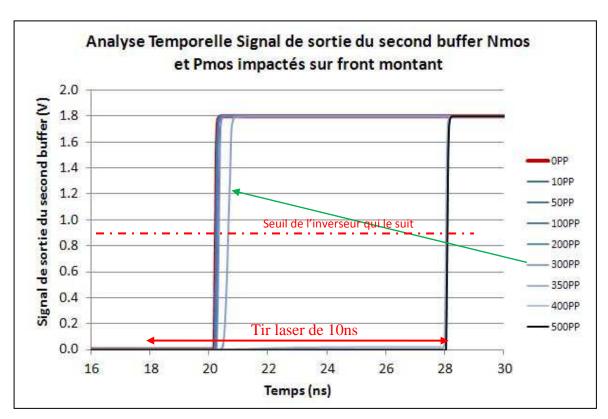

|     | 2.4.    | 4.2 Impact laser durant une transition montante de « 0 » vers « 1 »    | 186 |

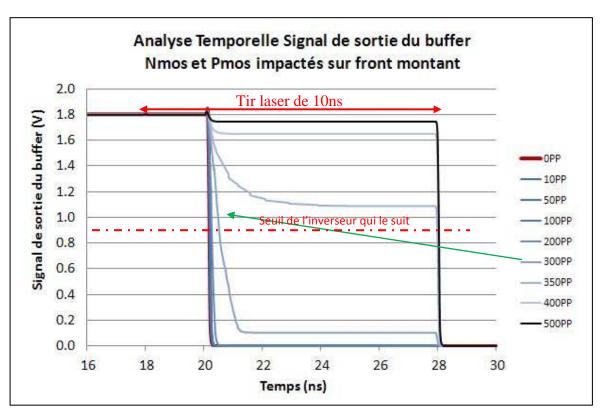

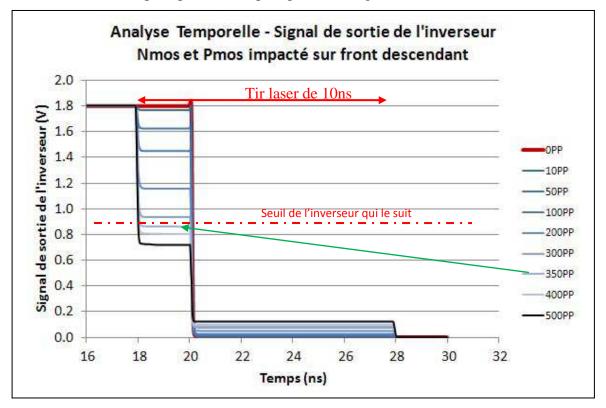

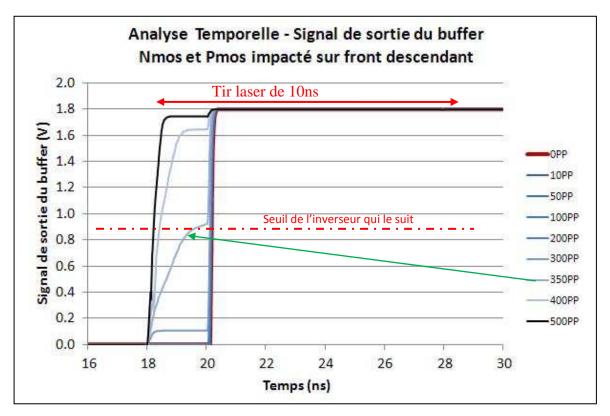

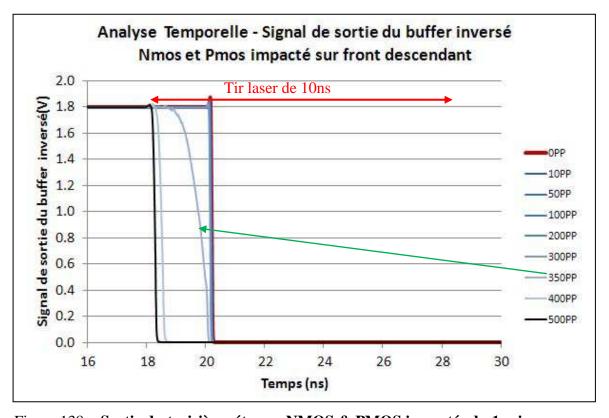

|     | 2.4.    | 4.3 Impact laser durant une transition descendante de « 1 » vers « 0 » | 188 |

|     | 2.5     | Prédiction du comportement d'un inverseur impacté                      | 191 |

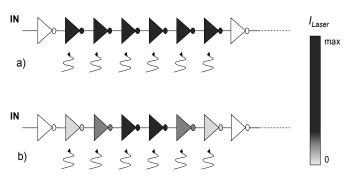

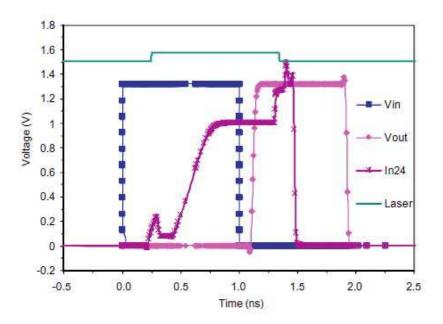

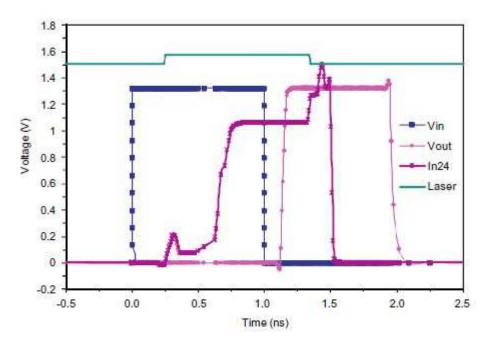

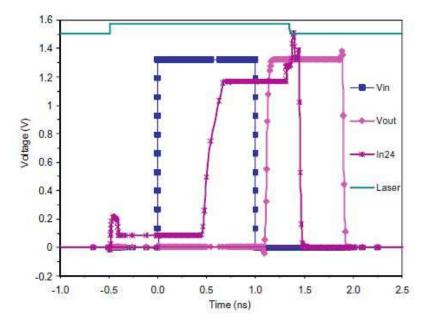

| 3   | Influ   | ence du profil du faisceau laser sur une chaîne d'inverseur [GOD09]    | 192 |

|     | 3.1     | nfluence of laser intensity distribution                               | 192 |

|     | 3.2     | Simulation results                                                     | 193 |

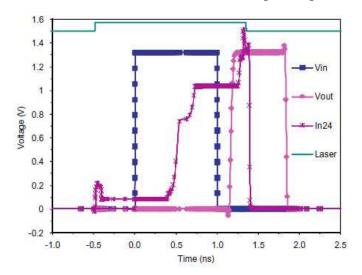

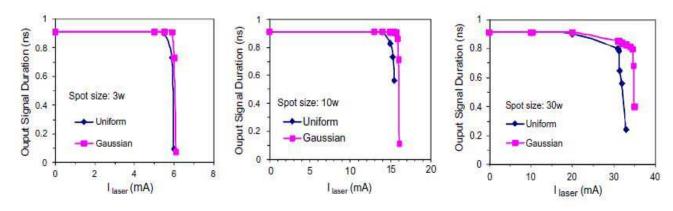

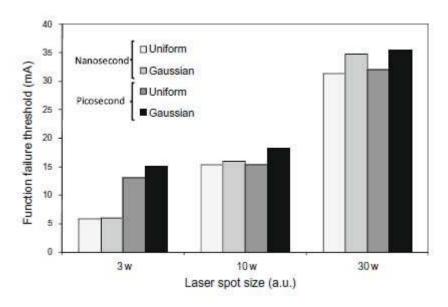

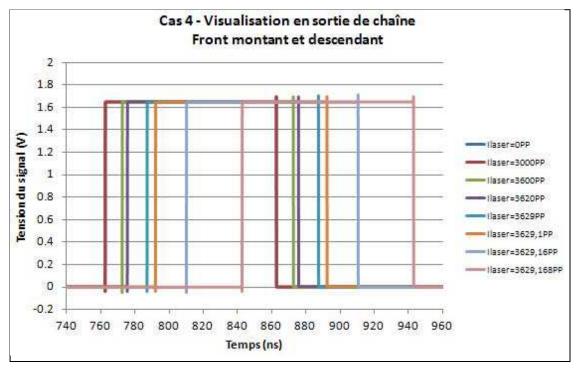

|     | 3.2.1   | Nanosecond pulses                                                      | 194 |

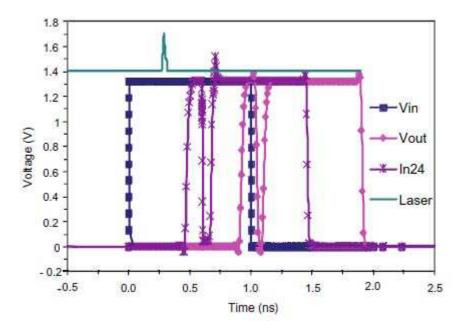

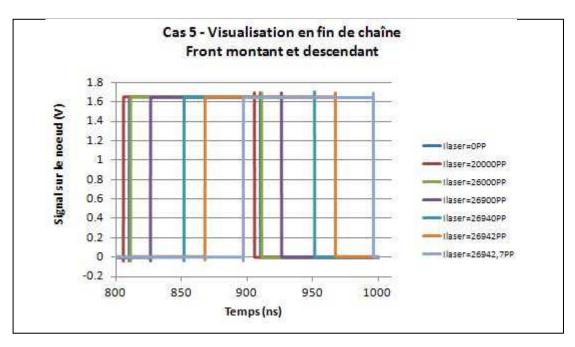

|     | 3.2.2   | Picosecond pulses                                                      | 197 |

| 4   | Conc    | lusion                                                                 | 199 |

| CII | A DIEDE | W. COMPRONELENON DU MODELE AUX MEGURES                                 | 200 |

| СН  | APIIKE  | IV: CONFRONTATION DU MODELE AUX MESURES                                | 200 |

| 1   | Intro   | ductionduction                                                         | 200 |

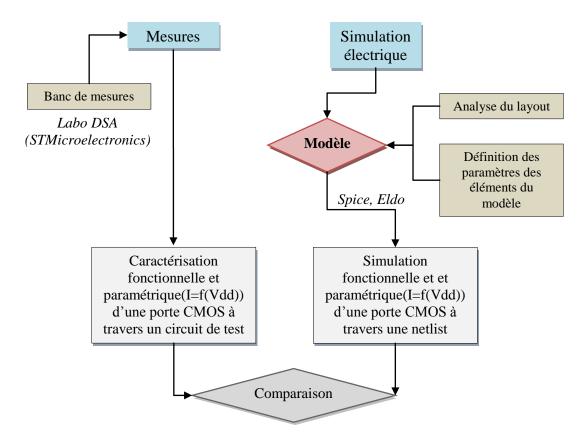

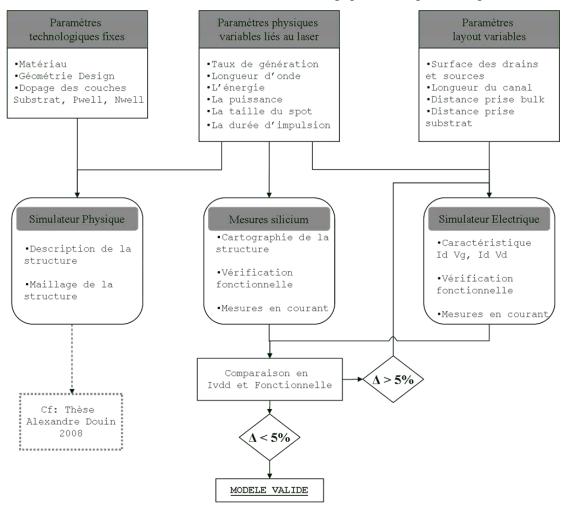

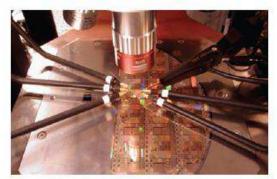

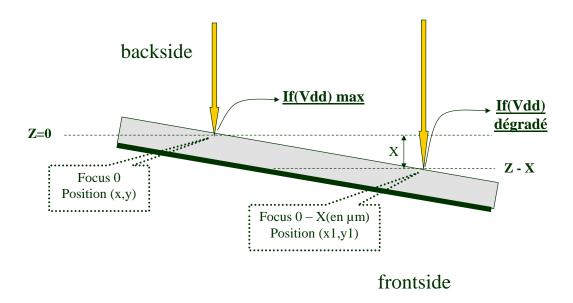

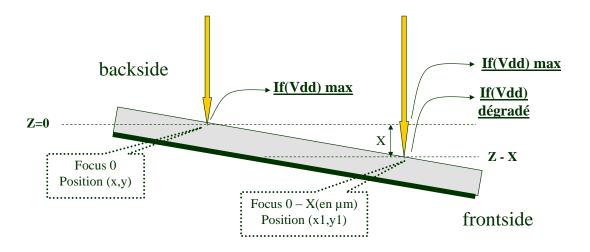

| 2   | Princ   | ipe et méthodologie de corrélation                                     | 202 |

| 3   |         | e sur des chaînes d'inverseur CMOS                                     |     |

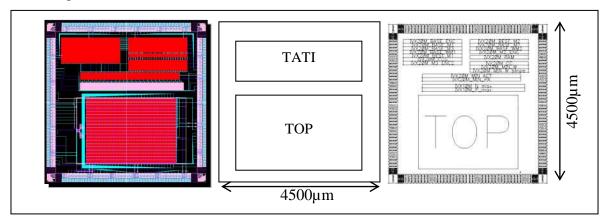

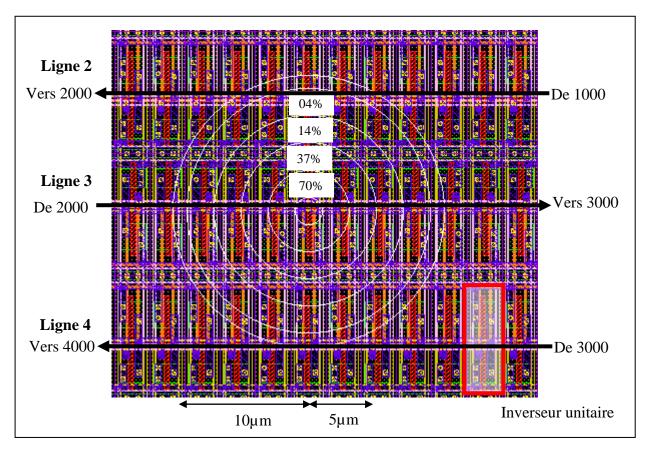

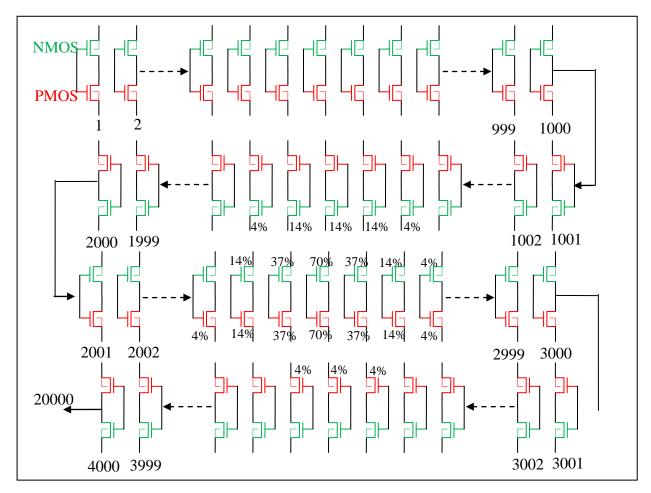

|     |         | Présentation de la puce de test                                        |     |

|     |         | Présentation des chaînes d'inverseurs                                  |     |

|     | 3.2.1   | Description de la chaîne BASE_ENC                                      |     |

|     | 3.2.2   | Description de la chaîne MAX_P                                         |     |

|     | 3.2.3   | Description de la chaîne MAX_N                                         |     |

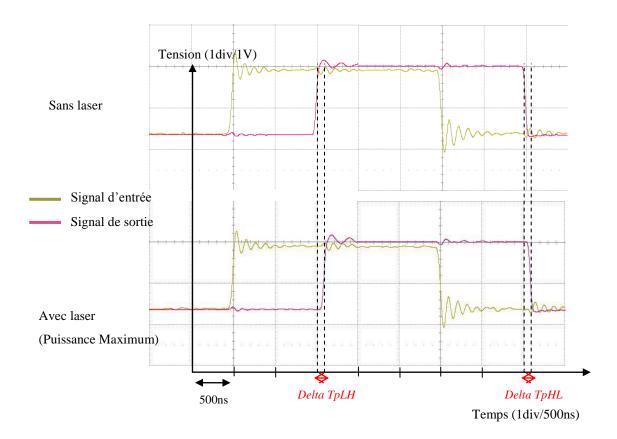

|     |         | Résultats de mesure                                                    |     |

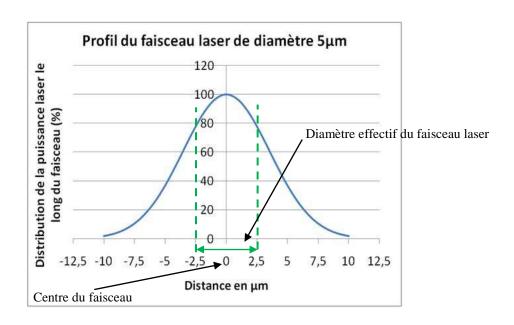

|     | 3.3.1   | Etude avec le laser de diamètre 5µm                                    |     |

|     | 3.3.    | ·                                                                      |     |

|     | 3.3.2   | Etude avec le laser de diamètre 70µm                                   |     |

|     | 3.3.    | ·                                                                      |     |

|     | 3.3.    | -                                                                      |     |

|     |         | • —                                                                    | 210 |

|     | 3.3.    | 2.3 Résultats de mesure pour la chaîne MAX_N                           |     |

|     | 3.4.1 | Etude avec le laser de diamètre 5µm                            | 213 |

|-----|-------|----------------------------------------------------------------|-----|

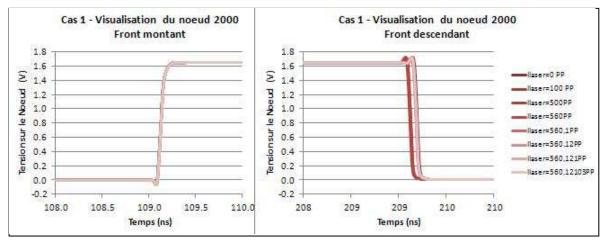

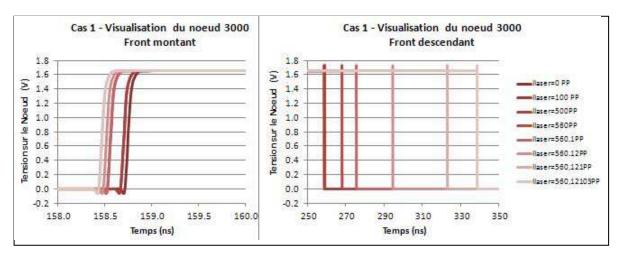

|     | 3.4   | 4.1.1 La simulation de la chaîne BASE_ENC                      | 214 |

|     | 3.4   | 4.1.2 Conclusion                                               | 221 |

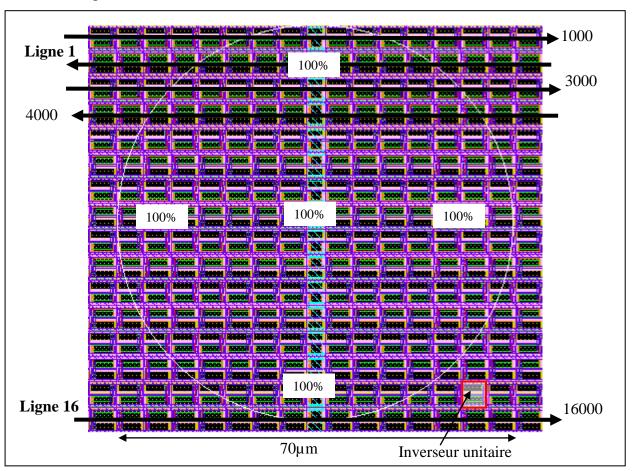

|     | 3.4.2 | Etude avec le laser de diamètre 70μm                           | 221 |

|     | 3.4   | 4.2.1 La chaîne BASE_ENC                                       | 222 |

|     | 3.4   | 4.2.2 La chaîne MAX_N                                          | 223 |

|     | 3.4   | 4.2.3 La chaîne MAX_P                                          | 225 |

|     | 3.5   | Synthèse des résultats et conclusion                           | 226 |

| 4   | Etuc  | de sur des éléments mémoires                                   | 228 |

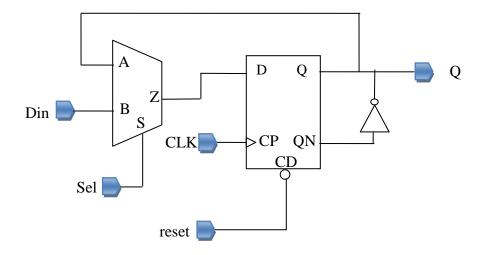

|     | 4.1   | Bascule de type Flip-Flop                                      | 228 |

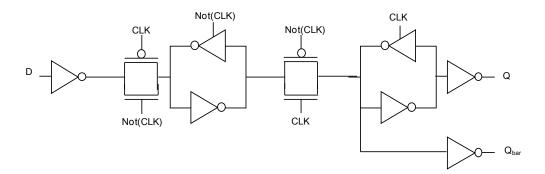

|     | 4.1.1 | Principe de fonctionnement de la bascule Flip-Flop             | 228 |

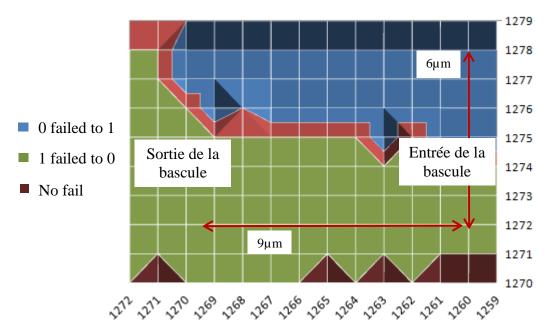

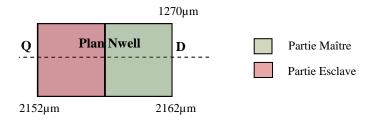

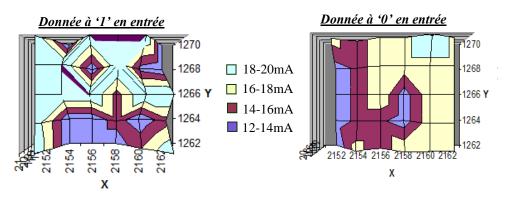

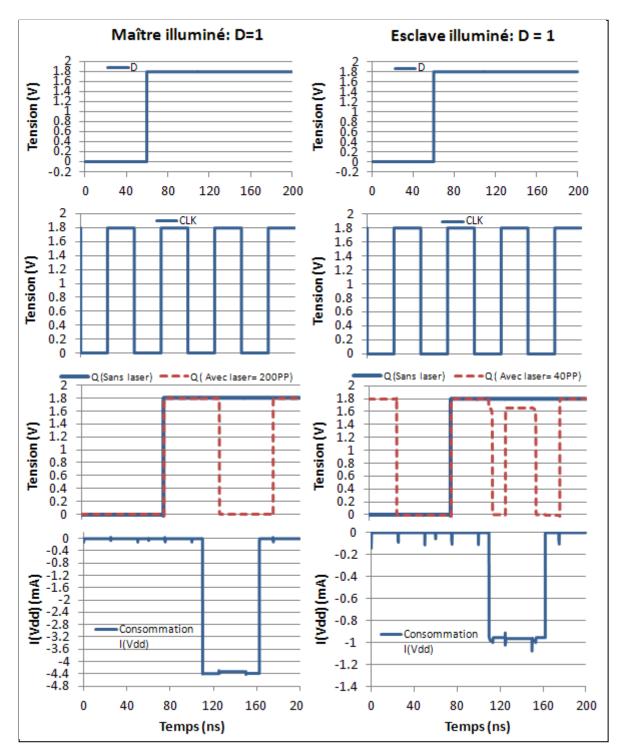

|     | 4.1.2 | Impact laser et résultats de mesures                           | 229 |

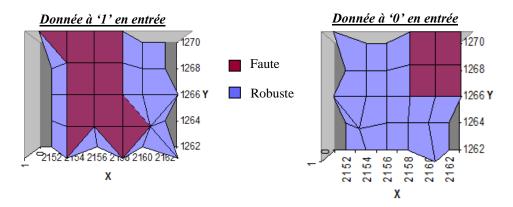

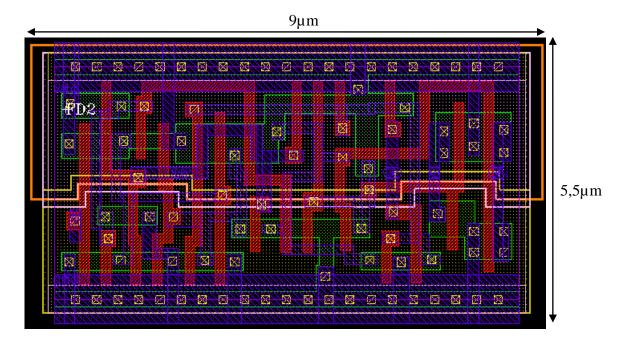

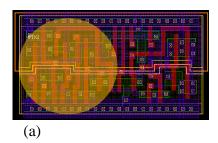

|     | 4.1.3 | Schématique et layout                                          | 233 |

|     | 4.1.4 | Etude de l'impact laser sur la géométrie                       | 235 |

|     | 4.1.5 | Résultats en simulation vs mesures                             | 236 |

|     | 4.1.6 | Conclusion                                                     | 239 |

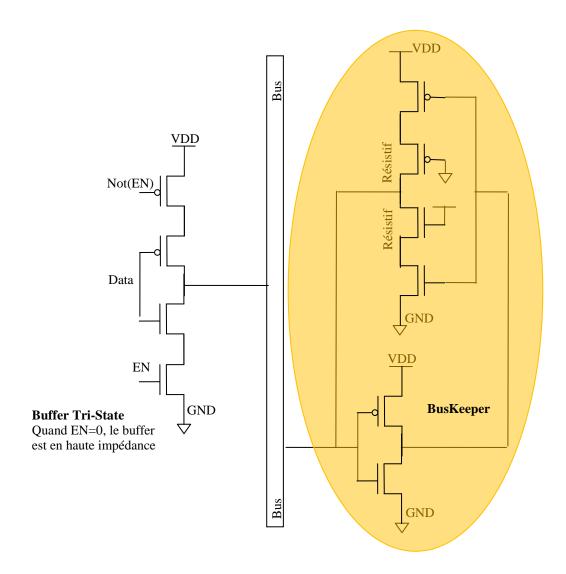

|     | 4.2   | BusKeeper                                                      | 240 |

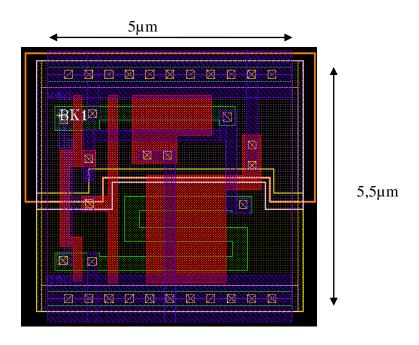

|     | 4.2.1 | Schématique et layout                                          | 240 |

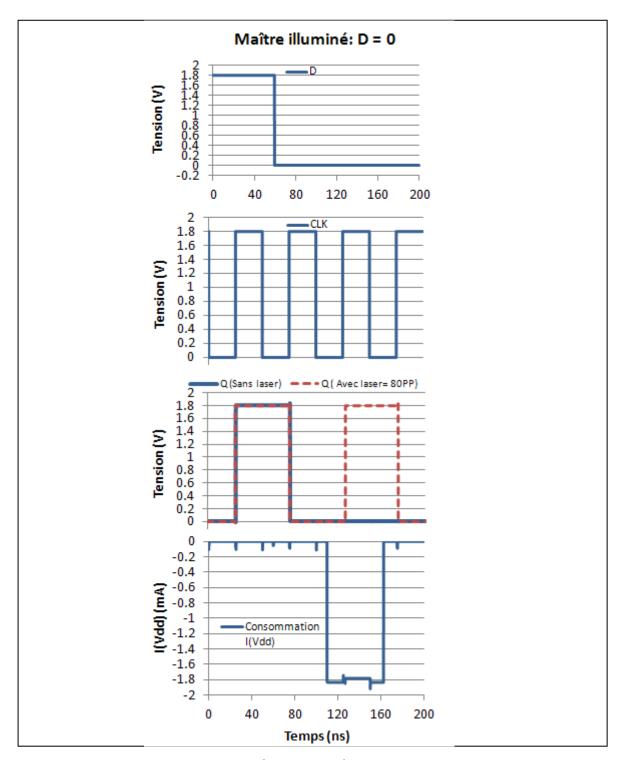

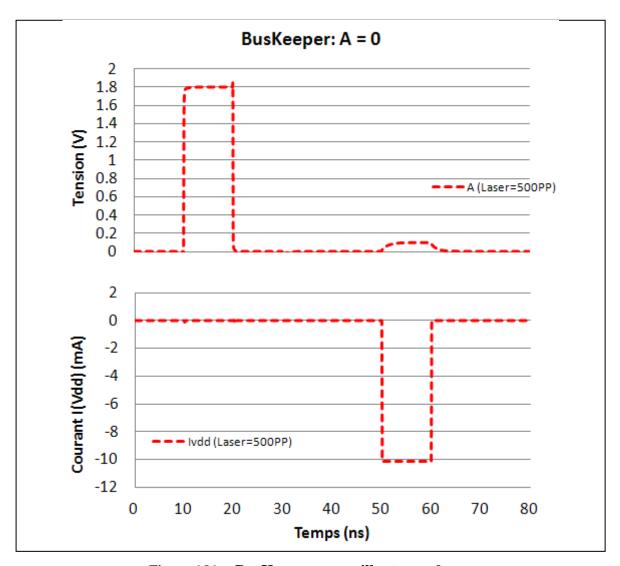

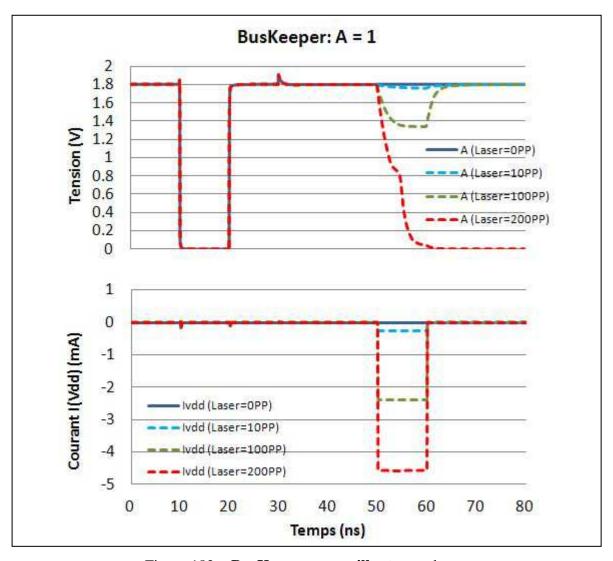

|     | 4.2.2 | Comportement d'un BusKeeper sous impact laser                  | 242 |

|     | 4.    | 2.2.1 Résultats de mesure                                      | 242 |

|     | 4.    | 2.2.2 Résultats de simulation                                  |     |

|     | 4.2.3 | Confrontation et analyse                                       | 245 |

| CO  | NCLUS | SION GENERALE                                                  | 247 |

| REF | FEREN | ICES BIBLIOGRAPHIQUES                                          | 249 |

| ANI | NEXES | j                                                              | 256 |

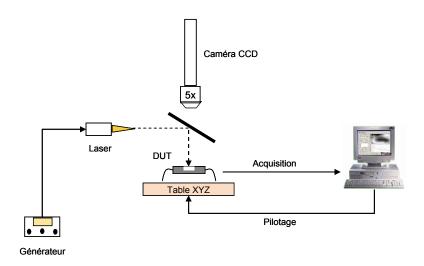

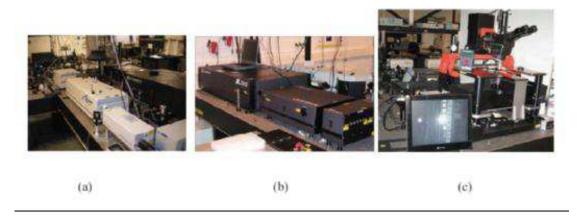

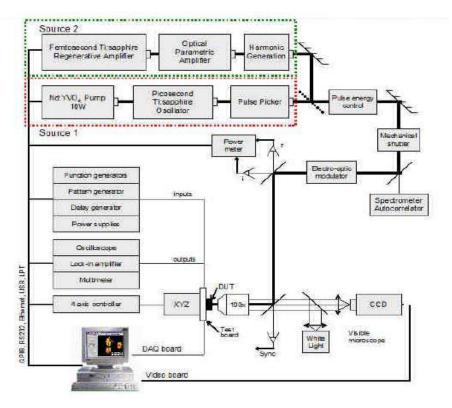

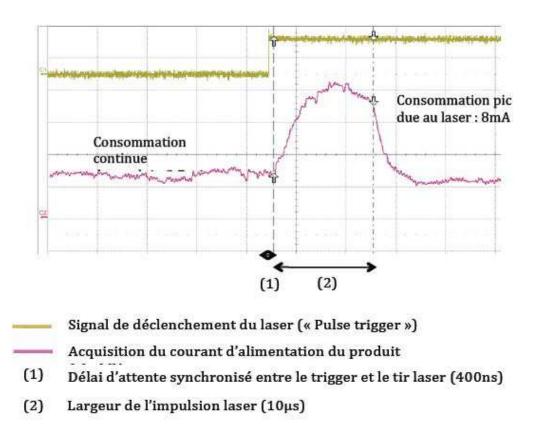

| 1   | Les   | bancs de test                                                  | 256 |

|     | 1.1   | Laboratoire DSA STMicroelectronics Rousset                     | 256 |

|     | 1.2   | Plateforme Atlas Laboratoire IMS Bordeaux I [DOU08]            | 260 |

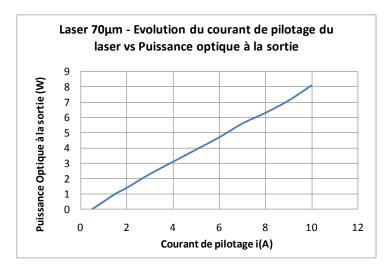

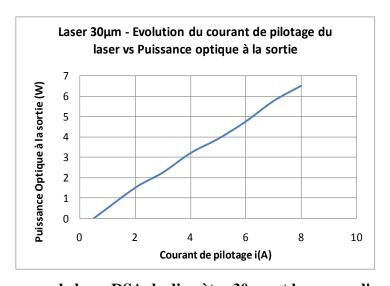

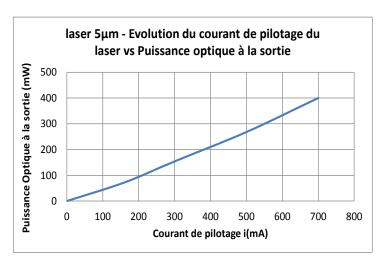

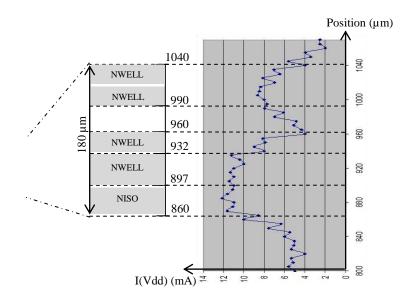

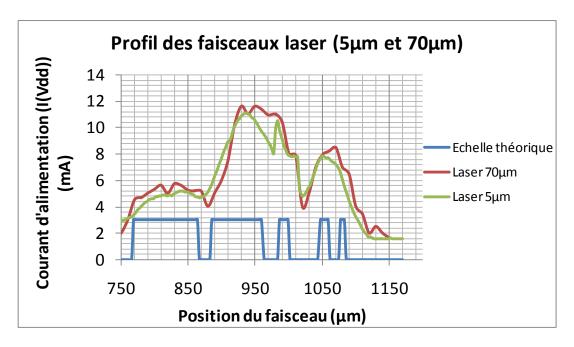

| 2   | Etuc  | de des faisceaux lasers 5µm et 70µm et Cartographie en courant | 264 |

| 3   | Etuc  | de de la planéité d'un circuit intégré                         | 267 |

| 4   | Etuc  | de des caractéristiques des transistors bipolaires             | 270 |

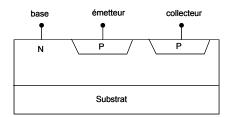

| 2   | 4.1   | Bipolaire NPN                                                  |     |

|     | 4.2   | Bipolaire PNP                                                  |     |

| 5   |       | modèle électrique développé sous ELDO Mentor Graphics          |     |

| 3   | 5.1   |                                                                |     |

|     |       | Script Perl utilisé pour l'implémentation du modèle            |     |

|     | 5.2   | Exemple de netlist de simulation impactée par le laser         | 282 |

| TABLE DES | S FIGURES                             | 286 |

|-----------|---------------------------------------|-----|

| 5.2.2     | Impact sur un transistor de type PMOS | 284 |

| 5.2.1     | Impact sur un transistor de type NMOS | 282 |

# Introduction générale

Alors que les circuits micro-électroniques font maintenant partie de notre vie de tous les jours, alors que notre quotidien repose de plus en plus sur leur fiabilité, il est devenu inimaginable de ne pas prendre en compte durant leur conception des mesures nous permettant de garantir leur bon fonctionnement. Prédire le comportement du silicium est devenu essentiel, d'autant plus que les coûts conséquents d'une erreur ou d'une faiblesse découvertes a posteriori, peuvent devenir dramatiques, tant au point de vue industriel (coût de fabrication, impact sur l'image...) que du point de vue utilisateur (mal fonction sans conséquence des biens de consommation, défaillances plus critiques (électronique embarquée dans l'automobile, dans l'aviation, la sureté nucléaire...). Des outils se développent et se perfectionnent pour simuler et prédire le comportement électrique en fonctionnement de circuits intégrés de plus en plus complexes, pour évaluer leur durée de vie lorsque soumis à des stresses en tension, en courant, en température, pour déterminer leur susceptibilité ou leur robustesse à des contraintes CEM...

Ce besoin de prédiction est encore plus marqué aujourd'hui dans le domaine de la conception de produits sécurisés tels que les circuits intégrés destinés aux cartes à puces, où la moindre fuite ou signature peut devenir une faille dans la sécurité du produit.

Cette thèse s'est principalement scindée en deux parties :

- L'analyse et l'étude du comportement des circuits intégrés soumis à un impact laser.

- Le développement d'un outil de simulation intégrant un modèle électrique de l'impact laser sur les transistors CMOS afin de reproduire de façon qualitative le comportement du circuit face à un impact laser, et ce quelque soit ses propriétés physiques.

Ainsi, pour permettre aux concepteurs de circuits intégrés pouvant être soumis à des attaques laser, de démontrer la robustesse de leur circuit et de les tester en simulation avant leur fabrication, nous avons mis en place, basé sur un modèle électrique, développé et amélioré durant cette thèse, une méthodologie d'implémentation d'un impact laser au sein de n'importe quelle description électrique d'un circuit, qu'il soit digital ou analogique.

De par le contexte même dans lequel cette thèse a été suivie, le premier chapitre est consacré dans un premier temps, aux circuits sécurisés, ainsi qu'aux différentes attaques que l'on peut rencontrer dans le domaine de la microélectronique. Par la suite, une partie théorique est dédiée à l'interaction laser-silicium au niveau physique, afin d'en explorer tous les aspects qui nous ont permis de mettre en place le cœur même de cette thèse.

Le second chapitre, quant à lui, s'oriente vers la méthodologie de modélisation et d'implémentation de la simulation d'un impact laser au sein d'un circuit intégré. Les différentes interactions mises en jeu lors d'un impact laser-silicium y sont présentées, et reproduites au niveau électrique.

Le chapitre suivant, utilisant la méthodologie préalablement développée, permet de démontrer la cohérence de ce modèle face à nos attentes théoriques. De simples structures élémentaires serviront de support à cette analyse, des transistors NMOS et PMOS à l'inverseur CMOS.

Le dernier chapitre va beaucoup plus loin puisqu'il va nous permettre de confronter notre méthodologie à la mesure. Il montrera comment l'outil que nous avons développé peut permettre d'anticiper le comportement d'un circuit face à un impact laser, et donc permettre aux concepteurs de tester en avance de phase leurs systèmes afin de trouver des solutions de contremesures et de rendre plus robustes leurs circuits face aux attaques laser.

# **Chapitre I : Contexte**

# et état de l'art

### 1 Contexte

#### 1.1 Applications sécurisées et circuits intégrés

Aujourd'hui, les circuits intégrés font partie intégrante de notre société. Ils sont devenus au fil du temps, quasiment indispensables. Ainsi, utilisés dans les cartes à puce, ils ont progressivement remplacé la carte magnétique. L'aspect sécuritaire est arrivé petit à petit sur le marché afin de sauvegarder et protéger certains contenus sensibles contre de possibles piratages [TUA07][REN04].

Ces systèmes sécurisés se retrouvent sous l'appellation de carte à puce ou « smartcard » en anglais. Ils sont généralement utilisés comme moyen d'identification personnelle tel que la carte d'identité, le badge d'entrée, la carte d'assurance maladie, ou encore la carte SIM des téléphones portables, ou bien alors comme carte de paiement (carte bancaire, porte-monnaie électronique), ou enfin comme moyens de preuve d'abonnement à des services prépayés (carte de transport...)

Cette sécurité peut être décrite de plusieurs façons, dépendant de l'application visée. La principale contrainte de sécurité est la confidentialité des données sensibles: le but est de garantir que les données protégées ne soient lisibles que par un certain nombre d'individus bien définis; pour toutes autres personnes, elles doivent demeurer inaccessibles ou inintelligibles. De même, le besoin d'échange de données confidentielles entre deux personnes, pose le problème de l'authenticité des données ou de leur provenance réelle. Ceci nécessite des mécanismes de signature de documents fiables. Cette signature a pour but d'authentifier à la fois les messages et leur auteur, de telle sorte qu'un vol de signature puisse être détecté ou décelé. Les exemples les plus courants de ce type d'applications se retrouvent dans les domaines de la banque, du contrôle d'accès et de la télévision à la demande.

Les cartes à puce embarquent un système complet capable de réaliser les transactions nécessaires pour nous authentifier et transmettre les données confidentielles nécessaires à l'application associée [WIT02].

D'un point de vue historique, le premier circuit sécurisé n'était au début qu'une simple puce mémoire qui pouvait stocker une valeur.

Au rythme des capacités nouvelles, offertes avec l'évolution des technologies silicium, de nouvelles fonctionnalités et solutions sécurisées sont embarquées, ajoutant à la complexité des applications carte à puce [SCH99].

Elles se composent principalement:

- d'un processeur qui effectue les calculs et gère l'accès aux différentes ressources grâce à un logiciel interne dédié à son fonctionnement

- d'une zone mémoire qui stocke un maximum d'informations personnelles. Les cartes actuelles ont une capacité pouvant atteindre plusieurs mégaoctets.

- d'un bloc qui est dédié au codage des informations. Pour éviter les problèmes de sécurité, l'organisme émetteur de la carte va la personnaliser lui-même. Pour une carte bancaire, il entre dans la puce puis code les références bancaires du propriétaire ainsi que son identité et ses coordonnées.

- d'un système électronique, une interface qui permet de lire et d'écrire des données ainsi que de contrôler l'alimentation du dispositif, par contact ou ondes radiofréquences.

Le circuit intégré contient aussi des parties analogiques et des capteurs pour protéger la puce d'éventuelles attaques, et à plus haut niveau, comporte du logiciel embarqué, basé sur des « systèmes d'exploitation » sécurisés (Secure OS), des machines virtuelles, des pare-feux (firewalls), et autres applications spécifiques.

La puce peut être accessible :

- soit par contact avec des électrodes de cuivre : l'interface entre les contacts ou électrodes de la puce et ceux du lecteur est le circuit imprimé doré très mince appelé micromodule. Il est divisé en huit parties, chacune ayant un rôle précis permettant l'échange des données entre la puce et le lecteur. La puce est quant à elle sous ces contacts ; elle est donc cachée.

- soit sans contact : par radio fréquence à courte ou moyenne portée, via une antenne interne dont les spires sont moulées dans l'épaisseur de la carte.

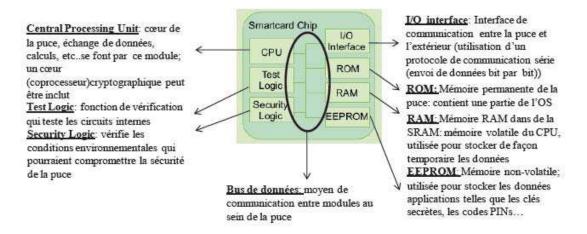

Figure 1 : Architecture de base d'une carte à puce actuelle

Au regard de l'augmentation incessante des applications ayant recours à la carte à puce, il est devenu primordiale pour les développeurs d'inventer et concevoir des produits sécurisés de plus en plus robustes face à l'augmentation des attaques de pirates (hackers) ayant pour but de connaître et voler les données confidentielles stockées sur chacune de ces puces.

Dans la suite de ce chapitre, nous ferons un état de l'art des différents types d'attaques recensés actuellement.

#### 1.2 Test et attaques sur les circuits et systèmes sécurisés

Dans ce sous-chapitre, nous dissocierons les notions d'attaque et de tests. Alors que l'attaque a pour but d'accéder sans autorisation à des données confidentielles, le test lui, a pour but de l'anticiper, afin de mettre en place des solutions de protection dites contremesures. L'objectif principal de cette section est de connaître tous les types d'attaques existants aujourd'hui. L'intérêt de connaître cette classification est d'avoir une meilleure vision des moyens qui doivent être mis en œuvre pour s'immuniser contre ces attaques.

Dans l'état de l'art actuel, plusieurs classifications des attaques contre les cartes à puce ont été proposées. Dans cette thèse, nous en retiendrons une qui est souvent référencée dans les publications ou les thèses. Cette classification propose deux grandes familles d'attaques : les attaques physiques et les attaques logicielles. A la fin de cette section, nous mettrons en avant, pour chacune des attaques citées, leurs différents moyens de contremesures qui ont été testés et prouvés.

#### 1.2.1 Attaque physique sur carte à puce

Par définition, on appelle attaque physique, toute attaque menée sur la puce en tant que composant matériel électronique. Ces attaques supposent une connaissance approfondie de l'architecture d'une carte à puce. Les attaques physiques sont rangées en trois souscatégories :

- Invasives ou intrusives

- Non invasives ou non-intrusives

- Semi-invasives

#### 1.2.1.1 Attaque invasive ou intrusive

Le premier type d'attaque dite invasive a pour résultat final de détruire la puce. Ce sont des attaques menées directement sur le composant électronique. Elles supposent de posséder un matériel lourd et spécifique. En général, elles ne permettent pas de pouvoir réutiliser la puce. Ce sont des attaques de type « analyse de construction » (Reverse Engineering) visant à démonter la puce pièce par pièce, à étudier sa structure interne, afin d'en comprendre l'architecture, d'en déduire le fonctionnement, voire d'en faire une copie par reconstruction. En effet, cette attaque doit permettre de définir la localisation précise de tous les transistors et interconnexions de la puce. Concrètement, la technique par « effeuillage » permet d'éliminer une par une dans l'ordre inverse toutes les couches du processus de fabrication qui sont ainsi cartographiées. Finalement, toutes les informations collectées sont rassemblées et permettent de reconstruire entièrement le dessin des masques de fabrication (layout) ou de créer des listes d'interconnexions (netlist) pour la simulation.

#### 1.2.1.2 Attaque non-invasive ou non-intrusive

Le second type d'attaque dite non-invasive, ne va s'intéresser qu'à des paramètres externes à la puce liés à son fonctionnement. Ces attaques étant moins coûteuses que la première, sont donc plus répandues. Elles sont de même plus pernicieuses car elles n'altèrent en rien le fonctionnement de la carte et ne permettent donc pas à son détenteur de soupçonner l'existence même de l'attaque. De façon plus explicite, les attaques non-invasives exploitent les canaux cachés du microprocesseur. Dans ce type d'attaque, on va mesurer un paramètre physique extérieur de la puce pendant son activité. L'intégrité physique de la puce n'est donc pas touchée. Ce paramètre physique peut-être le temps de calcul, le courant (consommation de

la puce) ou le champ électromagnétique émis par la puce. Ces attaques sont typiquement des attaques à clair connu, c'est-à-dire que l'attaquant va soumettre au chiffrement de la puce un ensemble de messages bien choisis. Pendant que la puce chiffrera ces messages, l'attaquant relèvera les données du paramètre physique mesuré. Une fois ces paramètres récupérés, l'attaquant par analyse directe des données ou par analyse statistique pourra en déduire des données sur la clé [HAG03].

Dans ces attaques, on retrouve la « Timing Attack », qui exploite le temps d'exécution d'une puce, la SPA (Simple Power Analysis) et la DPA (Differential Power Analysis) qui mesurent le courant consommé par la puce pendant son activité, et enfin la SEMA (Simple Electro Magnetic Analysis) et la DEMA (Differential Electro Magnetic Analysis) qui exploitent le rayonnement électromagnétique dû à l'effet produit par le courant passant dans les circuits de la puce. Dans les attaques SPA et SEMA, l'analyse des données est directe alors qu'elle est statistique pour les DPA et DEMA [BAR04].

#### 1.2.1.3 Attaque semi-invasive

La dernière sous-catégorie d'attaque représente les attaques semi-invasives. C'est une nouvelle classe d'attaques publiées pour la première fois en 2002 quand furent introduites les attaques par perturbation lumineuse [SKO03]. L'attaque que propose Skorobogatov utilise un simple flash d'appareil photo pour modifier la valeur d'une cellule mémoire.

Ce type d'attaque oblige l'attaquant, dans la majorité des cas, à enlever la puce de son boitier plastique. Contrairement aux attaques invasives, la couche de passivation reste intacte puisque ces attaques ne nécessitent pas de contacts physiques directs sur la puce.

L'attaque la plus connue est « l'attaque par injection de fautes ». Elle consiste à générer de façon intentionnelle des fautes dans le circuit en cours de fonctionnement et à comparer les résultats normaux avec les résultats fautés. Ces fautes peuvent être générées par plusieurs éléments : les flashs lumineux, qui permettent de modifier une partie du système, (Ces attaques ciblent principalement les technologies EPROM, EEPROM ou Flash) et les faisceaux laser. Dans les deux cas, des micro-courants sont créés par effet photoélectrique, ce qui permet de modifier le contenu des cellules mémoires irradiées. Le faisceau laser, plus sophistiqué, permet grâce à son pouvoir de focalisation très élevé, d'atteindre des zones beaucoup mieux ciblées dans des circuits de très haute densité (SRAM). L'attaquant peut ainsi obtenir un certain nombre de données confidentielles par analyse de la réponse électrique du circuit à ce type d'excitation [LEV04].

#### 1.2.2 Attaque logique sur carte à puce

Ce type d'attaque exploite les failles algorithmiques permettant à l'attaquant de contourner les protections mises en place. Il existe deux grandes familles d'attaques logicielles :

- La première concerne le code PIN. En théorie, le code PIN ne peut être tenté que 3 fois après quoi la carte se bloque. Pour que ce dispositif de sécurité fonctionne correctement il faut disposer d'un compteur que l'on incrémente avant la demande de code PIN. Si tel n'est pas le cas, cela signifie que la carte demande le code PIN, teste s'il est correct ou non et incrémente ensuite le compteur. La faille exploitable dans le deuxième cas est que l'attaquant peut tenter son code PIN, attendre la réponse de la carte et la retirer juste avant l'incrémentation s'il est erroné, permettant ainsi à l'attaquant de tenter éventuellement les 10000 codes possibles (10000 s'il n'a pas de chance). Ce type d'attaque n'est évidemment pas possible chez un commerçant mais devient tout-à-fait réalisable dans certains automates revendeurs de cassettes vidéo ou même aux billetteries automatiques si la carte n'est pas avalée comme dans un distributeur automatique de billets.

- La deuxième attaque logique présentée ici est celle de la datation. Il existe des attaques dites de « re-jeu » qui consistent à exécuter plusieurs fois la même action par une application qui ne l'a a priori autorisée qu'une seule fois. Prenons l'exemple d'un individu qui cherche à effectuer un virement d'un compte A vers un compte B. Si un attaquant intercepte un message électronique permettant de créditer son propre compte il peut a priori renvoyer ce message n fois à la banque de la victime pour récupérer son argent. La faille exploitée est liée au problème de la datation et à la mise en place d'un compteur permettant de ne réaliser qu'une et une seule fois le virement.

#### 1.2.3 Résumé schématique des différentes attaques

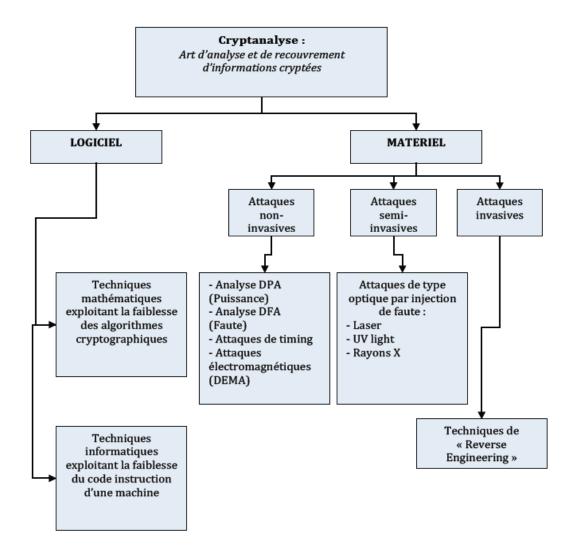

Un schéma recensant les différentes attaques énoncées ci-dessous est proposé par l'auteur de ce manuscrit afin d'avoir une meilleure visibilité du contexte :

Figure 2 : Classification proposée des différents types d'attaques possibles pouvant déstabiliser la sécurité d'une carte à puce

Afin de pouvoir sécuriser les produits ou les cartes à puce face aux attaques énoncées précédemment, plusieurs moyens de contremesure ont été développés.

#### 1.2.4 Les moyens de protection contre les attaques recensées

#### 1.2.4.1 Protection contre les attaques invasives

Pour se prémunir des attaques invasives, la solution consiste à détecter l'attaque pour bloquer dans un premier temps l'activité de la puce puis dans un deuxième temps envisager le suicide logique de la puce après cette attaque afin qu'aucune donnée ne soit transmise. Deux solutions sont principalement adoptées aujourd'hui : l'une physique et l'autre logique. Une

solution physique consiste à placer la puce sous des couches de métal sur lesquels on place des détecteurs d'activité anormale. Ceux-ci sont sensibles à la température, aux UV, aux rayons X et communique à la puce toute opération suspecte. C'est alors que la puce se bloquera voire provoquera sa mort logique. Une solution logique pour éviter les attaques invasives est d'introduire régulièrement dans les calculs des contrôles d'intégrité permettant de s'assurer que les données n'aient pas été modifiées par l'extérieur. Cette technique est également utilisée pour se prémunir des attaques par injection de fautes (DFA).

#### 1.2.4.2 Protection contre les attaques non invasives

Les attaques non-invasives consistent essentiellement à déterminer l'activité de la puce pour en déduire des informations secrètes. Cela passe par l'analyse de paramètres physiques, tels que le temps d'exécution, le courant, le champ magnétique, qui s'avèrent être de réels canaux d'informations. Les contre-mesures à ce type d'attaques vont donc consister soit à brouiller l'information qui passe par ces canaux, soit à atténuer ou éliminer le signal émis. Pour brouiller l'information l'encarteur possède plusieurs techniques qui dans leur résultat se ressemblent :

#### • le chiffrement interne des bus et des mémoires :

Chiffrer les bus et les mémoires signifie que les données ne transitent jamais en clair même à l'intérieur de la puce. Par conséquent, toute attaque par analyse d'activité sera vaine dans la mesure où l'attaquant ne récupèrera que des données chiffrées. Il existe une technique dans le même esprit que cette dernière qui consiste à appliquer pseudo-aléatoirement un masque binaire permettant de chiffrer ces mêmes données. L'idée est de se rapprocher du principe du « One Time Pad », sans la contrainte d'échange de clés grandes, en générant du « pseudo-aléa » à partir d'une clé courte.

#### • la génération d'activité aléatoire :

Générer de l'activité aléatoire, c'est introduire des opérations leurres et aléatoires que la puce effectuera en parallèle pour induire l'attaquant en erreur. Ce brouillage est donc algorithmique. En pratique, la puce effectue des calculs aléatoires en parallèle et cache donc les opérations réellement effectuées dans le cadre cryptographique.

Reste enfin les techniques qui visent à atténuer le signal émis par la puce dans ces canaux parallèles: celles-ci reposent sur le hardware et l'encarteur va pour cela essentiellement chercher à minimiser la consommation de la puce, de sorte que les attaques par analyse de courant ou de champs magnétique soient plus difficilement réalisables. L'encarteur peut également réduire la taille des composants et dispose des couches de métal pour protéger la puce.

#### 1.2.4.3 Protection contre les attaques semi-invasives

Les protections contre les attaques semi-invasives sont de nature très diverses. Elles ont pour objectif soit de détecter l'attaque, soit de la rendre inefficace, et peuvent être mises place à le l'application. en tous niveaux entre matériel et Les applications matérielles sont au nombre de trois grands groupes : certaines visent à rendre inefficace les différentes méthodes d'injection ou d'induction de fautes au sein du circuit, d'autres essaient de détecter ou de corriger les fautes logiques ou temporelles induites par l'attaque, et les dernières sont basées sur des modifications de l'algorithme afin de rendre l'analyse plus complexe [KOM99].

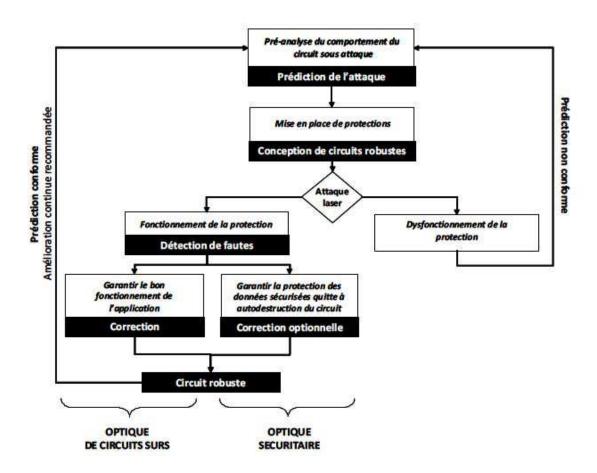

Le schéma suivant montre un flot possible utilisé par les concepteurs pour se protéger contre les attaques semi-invasives. Il dissocie l'optique des circuits sûrs de l'optique sécuritaire. En ce qui concerne la première dissociation, les concepteurs veulent garantir le bon fonctionnement global du circuit sous attaque laser. Un bloc de détection est mis en place pour détecter la faute induite par l'injection laser, et permet de corriger l'erreur afin de ne pas perturber le bon déroulement logique du circuit. En revanche, en terme sécuritaire, la correction de l'erreur est optionnelle puisque l'objectif premier est de ne pas permettre au pirate d'extraire des informations confidentielles du circuit, quitte à effacer totalement les données critiques, et ce afin de préserver l'intégrité des données ; la réinitialisation complète de l'unité de calcul ou du système complet est aussi envisagée.

Figure 3 : Flot utilisé par les concepteurs en vue d'une protection contre les attaques semiinvasives

Une des premières solutions pour se protéger des attaques semi invasives ou attaques par fautes est tout d'abord de s'assurer que les techniques d'injection de ces fautes sont inefficaces ou plus difficiles à mettre en place. Ces techniques essayent de protéger le circuit dans son intégralité. Elles se répartissent en deux catégories de protection: actives ou passives.

- Les protections actives ont pour but de savoir qu'une attaque est en cours.

- Ce sont des protections dynamiques. En général, elles sont basées sur des capteurs positionnés au sein du circuit permettant de détecter toute modification anormale du fonctionnement du système. Des bornes/limites sont prédéfinies lors de la conception d'un circuit robuste. Si une modification anormale s'opère (cela peut être un changement de température, ou encore la modification de l'intégrité des signaux de contrôle et d'alimentation), et que les paramètres de référence sortent des bornes définies au

- préalable, alors une attaque est détectée et un signal est envoyé à un bloc décisionnel (bloc de correction) pour appliquer la réaction adéquate.

- Les protections passives ont pour but de rendre l'injection de fautes plus difficile sans pour autant savoir qu'une attaque est en cours.

- Ce sont plutôt des protections dites statiques. Elles sont principalement basées sur la mise en place de boucliers tout autour du circuit, permettant l'atténuation de l'effet de tous les moyens d'induction optiques ou électromagnétiques.

Malgré ces deux types de protections, il est possible de contourner le problème en attaquant en face arrière (dans le cas d'une protection passive) ou bien en utilisant des moyens d'injection plus puissants et précis afin de contourner et d'éviter des détecteurs de lumière et générer des fautes (dans le cas d'une protection active). Afin de se protéger des attaques semi-invasives, une contre mesure efficace a été mise au point [KAR02]: la redondance. Elle s'inspire des techniques largement utilisées dans le spatial ou l'avionique pour durcir les circuits intégrés aux phénomènes de radiation ionisante, ou tout simplement pour prévenir une défaillance du système électronique. Celle-ci peut-être de trois types: matérielle, temporelle ou d'information, ou toute combinaison de ces trois types. En plus de ces techniques, il est possible de réaliser des calculs de vérification tels que le chiffrement d'une donnée puis du déchiffrement du résultat pour détecter les injections de fautes.

## 2 État de l'art de l'interaction laser silicium

Le laser peut être utilisé comme un moyen d'attaque semi-invasif sur les cartes à puce [SKO03] [WIL03]. C'est un outil permettant d'injecter des fautes au sein du circuit. Il est de même ipso facto utilisé pour tester les circuits par injection de fautes.

Nous verrons donc dans la partie suivante, comment les propriétés physiques du laser peuvent influer sur les propriétés du circuit intégré, et nous détaillerons les différentes méthodes de test utilisées dans la recherche et l'industrie.

#### 2.1 Les principes de test par injection laser

Avec une puissance de plusieurs centaines de mW, le balayage par laser sur circuit intégré, peut stimuler une altération du signal électrique aussi bien par effet photo-thermique, que par effet photoélectrique localisés au sein du chemin du signal.

Etant donné que le comportement du circuit électrique peut être altéré de multiples façons, plusieurs techniques ont été développées, basées sur le principe de la stimulation laser. Le tableau suivant donne une vue globale des différentes abréviations communes utilisées dans les stimulations laser des circuits statiques et dynamiques.

L'effet de stimulation sur un signal électrique qui peut être lu/vu/extrait via les terminaux du circuit intégré, se traduit par un de changement de résistivité, ou par la génération d'une tension thermoélectrique, ou encore par la génération d'un photocourant [DOU05].

| longueur d'onde | Effet                                             | Technique                                      | Analyse du circuit                                             |  |

|-----------------|---------------------------------------------------|------------------------------------------------|----------------------------------------------------------------|--|

|                 | TLS Thermal Laser Stimulation                     | OBIRCH Optical Beam Induced Resistivity Change | Identification des zones à forte                               |  |

|                 |                                                   | TIVA Thermally Induced Voltage Alteration      | résistance                                                     |  |

| 1300 nm         |                                                   | RIL<br>Resistive Interconnect Localization     | Vecteurs de test: Identification                               |  |

|                 |                                                   | SDL<br>Soft Defect Localizations               | des zones à haute sen sibilité<br>pass-fail (Variation Shmoo)  |  |

|                 |                                                   | SEI<br>Seebeck (Thermoelectric) Effect Imaging | Identification des interfaces<br>materielles sensibles         |  |

|                 | PLS Photoelectric Laser Stimulation, TLS parasite | OBIC Optical Beam Induced Current              |                                                                |  |

|                 |                                                   | LIVA<br>Light Induced Voltage Alteration       | Localisation des jonctions PN –<br>Région de charges d'espace. |  |

| 1064 nm         |                                                   | LADA Laser Assisted Device Alteration          | Lecture des signaux sensible<br>des états logiques             |  |

|                 |                                                   | Dynamic LS                                     | Train de signaux au sein du IC:                                |  |

|                 |                                                   | OBIRCH, SEI                                    | Variation de délai comme effe<br>parasite                      |  |

Figure 4 : Tableau recensant les différentes techniques de test utilisées actuellement [DOU08]

Dans la partie suivante, nous allons détailler les différentes stimulations existantes (photoélectrique et photo-thermique). Nous reprendrons la classification du tableau ci-dessus.

#### 2.1.1 Les différentes stimulations

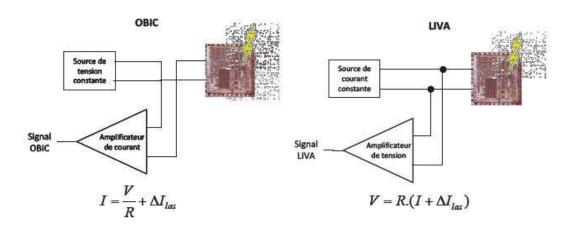

#### 2.1.1.1 Les techniques OBIC et LIVA

OBIC (« Optical Beam Induced Current) et LIVA (Light Induced Voltage Alteration) sont des techniques dites de stimulation photoélectrique laser. La première est une technique d'analyse semi-conducteur qui utilise un faisceau laser continu afin d'induire un photocourant au sein des zones actives du composant, lequel sera analysé pour générer des images représentant les propriétés du composant. La technique OBIC scanne à l'aide d'un faisceau laser continu la surface du composant[ESS07]. Dans le cas le plus général de « l'absorption un photon » (Single Photon Absorption ou SPA), un photon d'énergie supérieure au bandgap du semi-conducteur (1.2 eV pour le silicium) fait passer un électron de la bande de valence vers la bande de conduction où il peut se déplacer sous l'influence des champs électriques appliqués au composant. La création de porteurs liée à l'excitation du faisceau sur le semi-conducteur induit donc un photocourant qui peut être collecté et utilisé pour de l'imagerie.

Les variations de courant induites par le faisceau laser pendant le balayage (scanning) sont converties en variations de contraste pour former une image OBIC.

Une des limitations de cette technique OBIC est de transmettre une lumière quasiuniforme sur la surface avant du composant. Cette transmission non-uniforme de lumière est causée par la présence de plusieurs niveaux de métallisation. Une solution est de réaliser une image OBIC par illumination de la face arrière du circuit intégré pour atteindre les zones actives du composant à travers le substrat.

Figure 5 : Image OBIC d'une jonction PN [DOU08]

La figure ci-dessus représente une image OBIC d'une jonction PN avec un centre de recombinaison bloquant la formation d'un photocourant et révélant donc un défaut structurel. La résolution spatiale d'une image OBIC en face arrière du composant est cependant limitée par le compromis entre la capacité à transmettre les photons (faisceau laser) à travers le substrat et en même temps, à permettre au faisceau d'être absorbé par le semi-conducteur afin de générer des paires électrons-trous conduisant à un photocourant mesurable. L'échelle de longueur d'onde ne permet pas une résolution assez précise pour l'analyse des circuits intégrés comprenant des éléments submicroniques [DOU08].

Cette limitation du « single-photon » dans l'analyse OBIC en face arrière a été comblée par la maitrise de la technique de « l'absorption deux photons » ou « two-photon absorption » (TPA), laquelle implique deux photons arrivant en même temps sur le semiconducteur afin de libérer l'électron de la bande de valence. Ces deux photons doivent avoir des énergies plus faibles que le Bandgap du semi-conducteur mais supérieure à la moitié du Bandgap, et surtout être générés simultanément, ce qui nécessitent une puissante du faisceau nettement supérieure pour accroitre la probabilité d'occurrence du phénomène [BRI07][GODO04][RAM03].

« L'absorption deux photons » est une forme non linéaire de l'absorption standard, avec une génération de porteurs dépendant du carré de l'intensité lumineuse.

La technique LIVA est de même une technique d'analyse utilisant le laser comme source pour induire des changements de tension dans le composant, durant le balayage du faisceau laser sur la surface. Le circuit sous test est polarisé en mode statique par une source de courant constante. L'objectif est donc de mesurer les variations de tension aux bornes de la source de courant constante pendant le balayage du faisceau sur le circuit intégré

Figure 6 : Représentation électrique des techniques OBIC et LIVA proposée par [DOU08]

Ces deux techniques sont principalement utilisées aujourd'hui dans l'analyse des défauts.

#### 2.1.1.2 Les techniques OBIRCH, TIVA et SEI

Ces techniques sont basées sur la stimulation thermique par laser. Ces techniques d'imagerie utilisent un faisceau laser pour produire une variation thermique au sein du circuit intégré.

En ce qui concerne la technique OBIRCH, la stimulation laser révèle des différences de caractéristiques thermiques lorsque les éléments conducteurs impactés contiennent des défauts. L'échauffement local d'une surface défectueuse comme une ligne de métal provoque un changement de résistance qui peut être détecté en contrôlant le courant d'entrée. Quand ce changement de courant est détecté, la position du laser est repérée sur l'image du circuit. Nous ne nous étendrons pas sur les autres techniques TIVA et SEI dans ce manuscrit.

#### 2.1.1.3 La technique « XIVA »

Une nouvelle technique combinant la technique OBIC, LIVA, SEI ainsi que TIVA a été développée et décrite par [FAL01] en 2001. Il s'agit de la technique XIVA utilisée pour la location de défauts : Le circuit sous test est polarisé en mode statique par une source de tension constante, tout en maintenant la détection de courant de façon constante. La tension de polarisation est dans cette configuration, un signal à basse fréquence, alors que la détection de courant constant est un signal à haute fréquence. Le signal « XIVA » apparaît lorsque le laser scanne une zone avec défauts.

అఅఅ

De ces techniques optiques lasers vus précédemment découlent deux types de mécanismes de stimulation laser : la stimulation laser thermique et la stimulation laser photoélectrique.

La première est basée sur l'échauffement localisé d'éléments conducteurs du circuit sous test. Elle va induire des mécanismes modifiant les paramètres électriques du circuit. (Variation de résistance d'une piste métallique ou création d'une force électromotrice au niveau d'une piste coupée.)

La seconde, utilisée tout au long de cette thèse est la stimulation laser photoélectrique. Elle consiste à générer des paires électrons-trous à proximité des zones actives du circuit. Ces charges sont collectées créant ainsi un photocourant dans le circuit. Ce photocourant permet de relever des informations par mesure directe, ou en mesurant son effet sur le circuit. Ces effets peuvent être de type logique, ou paramétrique. (Influence sur l'état logique du circuit ou bien influence sur le courant de consommation du circuit).

#### 2.2 Interaction laser semi-conducteur en régime photoélectrique

Cette partie constitue une approche théorique de l'interaction laser semi-conducteur. Il est nécessaire d'étudier les phénomènes physiques mis en jeu lors de l'interaction laser silicium, en régime photoélectrique. Les principaux acteurs physiques agissants lors d'une interaction laser-silicium sont décrits ci-après.

# 2.2.1 Mécanismes physiques mis en jeu lors d'une interaction laser semi-conducteur

La stimulation photoélectrique laser est accessible avec des lasers continus (mode statique) comme impulsionnels. Afin d'étendre au maximum notre domaine de connaissance, nous détaillons les lasers continus et les lasers impulsionnels induisant donc des courants transitoires dans le circuit sous test.

Quelles que soient les applications utilisées avec des lasers, la base des phénomènes physiques mis en jeu est l'interaction du rayonnement électromagnétique du laser avec la matière. Nous allons dans cette partie expliciter les mécanismes qui régissent l'interaction laser-matière et la façon dont l'énergie apportée est absorbée.

#### 2.2.1.1 Cas des lasers continus

Nous allons rapidement rappeler le formalisme complexe utilisé pour modéliser la propagation d'une onde plane (faisceau à profil uniforme) dans un milieu absorbant. Le cas du faisceau gaussien sera abordé.

#### • Le rayonnement électromagnétique

Les mécanismes d'interaction diffèrent selon la gamme de fréquence du rayonnement électromagnétique considéré. En effet, le spectre des fréquences s'étend des rayonnements de très faibles énergies ou très basses fréquences (ondes radio), à ceux de très fortes énergies (haute fréquence) (rayons gamma), en passant par les micro-ondes, l'infrarouge, le visible, l'ultraviolet et les rayons X.

Les rayonnements émis par les lasers vont généralement de l'infrarouge à l'ultraviolet.

L'énergie du photon dépend de sa fréquence,  $\nu$  (Hz), et donc de sa longueur d'onde,  $\lambda$  (nm). Le quantum d'énergie,  $E_p$ , s'exprimant à l'aide de la constante de Planck h, et de la célérité de la lumière, c, est donné par :

$$E_p = h. \nu = \frac{h. c}{\lambda}$$

Avech.  $c = 1,2398.10^3$

Dans l'infrarouge (IR), l'énergie d'un photon varie entre 3.10<sup>-3</sup>eV et 1eV environ.

#### • Propagation d'une onde plane dans un milieu

Une onde électromagnétique est qualifiée de plane lorsque ses coordonnées spatiales ne dépendent que d'un seul paramètre. Selon la théorie établie de Maxwell, une onde électromagnétique est caractérisée par son champ électrique E et son champ magnétique. Lorsque l'onde se propage selon l'axe z, dans un milieu d'indice complexe  $n^*$ , la résolution des équations de Maxwell donne l'expression suivante du champ électrique :

$$\vec{E} = \vec{E}_0 \cdot exp \left[ i \cdot \omega \cdot \left( t - \frac{n^*}{c} \cdot z \right) \right]$$

avec

$\omega$ : la pulsation ( $\omega = \frac{2.\pi.c}{\lambda}$ )

c : la vitesse de propagation de l'onde électromagnétique

$\lambda$ : la longueur d'onde

t: le temps.

L'indice de réfraction complexe  $n^* = n - ik$  (n est l'indice de réfraction et k le coefficient d'extinction) est relié à la permittivité électrique,  $\epsilon$ , la perméabilité magnétique,  $\mu$ , et la conductivité électrique,  $\sigma$ , du milieu, de la façon suivante :

$$(n^*)^2 = n^2 - k^2 - ink = \varepsilon' - i\varepsilon'' = \mu. \varepsilon. c_0^2 - i. \sigma. \mu. \frac{c_0}{\omega}$$

Le coefficient d'extinction ou d'atténuation d'un milieu, permet de mesurer la perte d'énergie d'un rayonnement traversant ce dernier. Analogue au coefficient d'absorption, il prend aussi en compte, en plus de l'absorbance, les effets dus à la diffusion et la luminescence. [IUPAC97]

Lorsqu'un faisceau d'énergie électromagnétique, d'intensité (flux d'énergie),  $I_0$ , pénètre dans le milieu, la variation de l'intensité transmise, I(z), en fonction de la distance z, dépend du coefficient d'absorption  $\alpha$  du milieu. L'intensité décroît selon la loi de Beer-Lambert :

$$I(z) = I_0 \cdot \exp(-\alpha z)$$

Avec

$$\alpha = 2. \omega. \frac{k}{c}$$

#### • Taux d'absorption

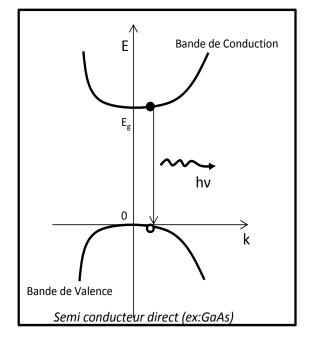

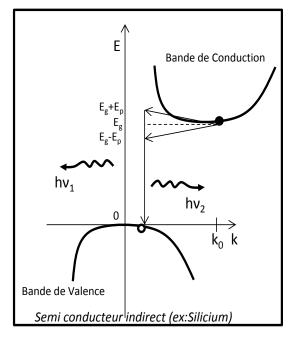

Les semi-conducteurs peuvent être classifiés sous deux types : matériau à gap direct et matériau à gap indirect.

Les diagrammes des bandes d'énergie pour les deux types de matériau sont illustrés ci-après :

- (a) Transition d'un électron en gap direct

- (b) Transition d'un électron en gap indirect, Ep étant l'énergie du phonon

Figure 7 : Diagramme d'état dans l'espace d'un semi-conducteur à gap direct (a) et indirect (b)

Dans le cas d'un gap direct, le point le plus bas dans la bande de conduction apparaît à la même valeur de k (vecteur d'onde) comme étant le plus haut point de la bande de valence. Une transition optique directe est dessinées verticalement avec un changement non significatif de k (vecteur d'onde), dû au fait que le photon absorbé a un très faible vecteur d'onde.

Par exemple, si l'on considère le matériau GaAs qui a un Bandgap direct, où le minimum de la bande de conduction est au-dessus du maximum de la bande de valence, aucun phonon n'est nécessaire pour la conservation du moment quand un électron transite du minimum de la bande de conduction vers le maximum de la bande de valence (par recombinaison avec un trou), et quand un photon ayant pour énergie  $E_g$  est émis. La fréquence seuil v pour une absorption directe détermine l'énergie de Bandgap (E = hv)

En revanche, le silicium ayant un Bandgap indirect, un phonon est nécessaire pour la conservation du moment, dans le but de permettre la transition radiative d'un électron, du minimum de la bande de conduction vers le maximum de la bande de Valence. Cela est dû au fait que les bords de la bande de conduction sont largement séparés dans l'espace k. L'énergie seuil pour ce type de procédé est plus élevée que le réel Bandgap. Un phonon doit être « consommé » ou crée quand un photon avec une énergie approximativement égale à Eg est émis. L'énergie du photon a pour valeur égale à :

$$E = hv = \frac{h. c}{\lambda} = E_g \pm E_p$$

L'énergie d'un photon peut-être transférée vers un électron de la bande de valence d'un semiconducteur, électron qui peut être porté vers la bande de conduction, quand l'énergie du photon est supérieure à l'énergie de Bandgap  $E_g$ (=1.12 eV pour le silicium).

Durant ce procédé de transition, le photon est absorbé et une paire électron-trou est générée. Cependant, les photons ayant une énergie inférieurs à  $E_{\rm g}$ , ne seront pas absorbés, et le semi-conducteur devient « transparent » pour des faisceaux lumineux auant une longueur d'onde égale à :

$$\lambda_c = \frac{h.\,c_0}{E_a}$$

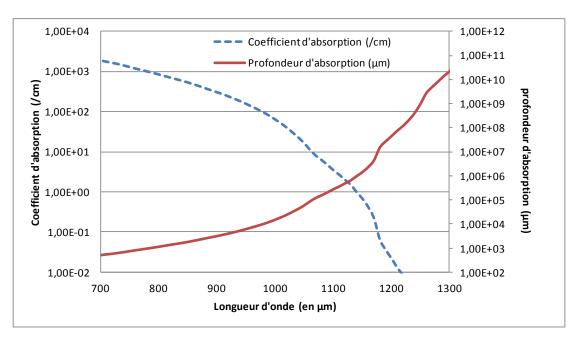

La notion de coefficient d'absorption communément appelé  $\alpha$  est très importante ; en effet, l'absorption des photons produit des paires de porteurs et génère ainsi un photocourant, dont la valeur dépend de ce coefficient. Il détermine aussi la profondeur de pénétration  $\frac{1}{\alpha}$  du faisceau lumineux au sein du semi-conducteur, suivant la loi de Lambert-Beer :

$$I(\bar{y}) = I_0 \exp(-\alpha \bar{y})$$

Avec  $\bar{y}$  étant la longueur du trajet optique,  $I_0$  l'intensité de la lumière incidente et I l'intensité de la lumière sortante.

La courbe suivante représente la variation du coefficient d'absorption du silicium ainsi que la profondeur d'absorption dans le matériau, en fonction de la longueur d'onde du faisceau lumineux.

Figure 8 : Coefficient d'absorption et de la profondeur de pénétration en fonction de la longueur d'onde [GRE95]

#### • Taux de génération

L'absorption inter-bandes se traduit dans les équations de continuité du semiconducteur par un taux de génération de paires électron-trou. D'après [POU00], le taux de génération en un point du milieu est égal aux taux de disparition des photons en ce point. Dans le cas d'une onde plane, le taux de disparition des photons est égal à l'opposé de la variation du flux de photons.

Donc le taux de génération peut s'exprimer avec l'équation suivante :

$$G_{op}(z) = \alpha. \Phi_{op}(z) = \frac{\alpha}{E_{\gamma}}. I_{op}(z)$$

avec $\Phi_{op}$  le flux de photons associé à l'onde électromagnétique,  $E_{\gamma} = \overline{h}.\omega$  l'énergie d'un photon de l'onde à la pulsation  $\omega$ , et  $I_{op}$  l'intensité de l'onde plane.

#### • Faisceau gaussien

Le rayonnement issu d'un laser peut être considéré comme gaussien. Pourquoi considérer des ondes gaussiennes plutôt que planes ou sphériques ? Car ces ondes simples obligent à considérer le phénomène de diffraction [ROU95] en raison de leur extension infinie

dans les directions transverses à la propagation. Ce phénomène peut s'avérer incompatible avec l'effet laser d'où la prise en compte d'un effet gaussien.

Cette onde, comme l'onde plane, est solution de l'équation d'onde. Elle a pour expression la formule suivante :

$$E(r,z) = A(z) \cdot \exp\left(-i \cdot \frac{k \cdot r^2}{2 \cdot R(z)}\right) \cdot \exp\left(\frac{-r}{2 \cdot w^2(z)}\right)$$

2eme facteur non homogène

A(z) représente l'amplitude complexe du champ suivant l'axe des z. Dans cette expression, les variations du champ E suivant la coordonnée radiale r sont contenues dans les termes en exponentiel.

- Le terme en  $\exp\left(\frac{-r}{2.w^2(z)}\right)$  justifie le caractère gaussien du faisceau. Pour une distance fixée z, l'amplitude du champ diminue d'un facteur  $\frac{1}{e^2}$  à une distance r=w(z) de l'axe optique. Le rayon w(z) est donc une mesure de l'extension radiale du faisceau.

- Le faisceau gaussien est ici caractérisé par des fronts d'ondes de rayon de courbure R(z).

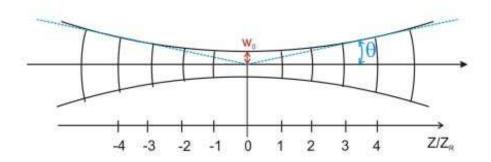

Figure 9 : Représentation d'un faisceau gaussien

Si on se base sur la figure ci-dessus, pour z nul, on peut définir un rayon de ceinture ou col de faisceau  $w_0$  qui représente la valeur minimale du rayon w(z). Ce paramètre est primordial, puisqu'il permet d'exprimer les caractéristiques suivantes du rayon de courbure du front d'onde du faisceau. Sa valeur est une fonction de la position tel que:

$$R(z) = z. \left[ 1 + \left( \frac{z_R}{z} \right)^2 \right]$$

Si on pose :  $z_R = \frac{\pi . w_0^2}{\lambda}$ , on peut écrire

$$R(z) = z \cdot \left[ 1 + \left( \frac{\pi \cdot w_0^2}{\lambda \cdot z} \right)^2 \right]$$

De même le rayon w(z) peut s'écrire :

$$w(z) = w_0. \sqrt{1 + \left(\frac{\lambda. z}{\pi. w_0^2}\right)^2}$$

La longueur de Rayleigh  $z_R$ représente donc une mesure de la divergence du faisceau. En effet, plus cette grandeur sera petite, plus le faisceau sera divergent. Cette divergence, comme il est montré sur la figure, peut se mesurer par le comportement asymptotique du rayon w(Z).

Lorsque Z>>Z<sub>R</sub>, le rayon s'approche d'une ligne droite et devient : $w(z) = w_0 \cdot \frac{z}{z_R}$

Ainsi, la divergence du faisceau est donnée par :  $\tan \theta \ll \theta = \frac{w_0}{z_R} = \frac{\lambda}{\pi \cdot w_0}$

Enfin, un modèle de l'intensité du faisceau gaussien dans le silicium, d'après [ALD03] est donné par :

$$I_2(r,z) = I_0 \cdot \frac{w_0^2}{w_{si}(z)^2} \cdot \exp\left(-\frac{2r^2}{w_{si}(z)^2}\right) \cdot \exp\left(-\alpha z\right)$$

Maintenant, il reste à établir la distribution spatiale du taux de génération de paires électrontrou induit par le faisceau gaussien. D'après [ALD03], en admettant que la présence de porteurs libres se traduit par une diminution globale de l'efficacité de photo-génération  $\eta$ , on obtient l'expression du taux de génération gaussien :

$$G(r,z) = \eta \cdot \alpha \cdot \frac{I_0}{E_v} \cdot \frac{w_0^2}{w_{si}(z)^2} \cdot \exp\left(-\frac{2r^2}{w_{si}(z)^2}\right) \cdot \exp\left(-\alpha z\right)$$

#### 2.2.1.2 Cas des lasers impulsionnels

La stimulation photoélectrique pour un laser impulsionnel est basée sur la création de photo-courants transitoires, dans le circuit intégré. Ils sont issus de la génération de paires électrons-trous induites par le faisceau laser dans le semi-conducteur.

#### • Taux de génération

Cette génération de porteurs excédentaires se caractérise par un taux de génération G qui peut être modélisé de la façon suivante en paires.cm<sup>-3</sup>.s<sup>-1</sup>:

$$G(r,t,z) = \frac{2 \cdot \alpha \cdot E_0}{E_{ph} \cdot \pi^{3/2} \cdot w_0^2 \cdot \tau} \cdot \exp\left(-\frac{2r^2}{w_0^2}\right) \cdot \exp\left(\frac{-(t-t_i)^2}{\tau^2}\right) \cdot \exp\left(-\alpha z\right)$$

où  $\alpha$  est le coefficient d'absorption,  $E_{ph}$  l'énergie du photon,  $w_0$ le rayon au col du faisceau,  $E_0$  l'énergie par impulsion,  $\tau$  la durée de l'impulsion laser, et  $t_i$  l'instant d'arrivée de l'impulsion.

#### Coefficient d'absorption

La longueur d'onde est l'un des paramètres les plus importants dans l'expression du taux de génération puisqu'on le retrouve dans plusieurs termes.

On le retrouve aussi de façon implicite dans le coefficient d'absorption  $\alpha$ . La longueur d'onde définit le processus d'absorption. Les photons sont absorbés au cours de leur propagation dans le silicium selon au moins deux processus dont l'absorption un photon et l'absorption deux photons.

#### • Energie du laser

L'énergie *E0*, quant à elle, traduit la quantité de paires électron/trou générée dans le silicium. Il est important de générer suffisamment de paires pour perturber le fonctionnement du circuit mais de ne pas en générer trop dans le cas où il existe un risque de détérioration du circuit, par échauffement essentiellement. Cela se fait par le contrôle de l'énergie laser transmise au circuit. Pour les diodes laser il suffit de contrôler le courant d'alimentation pour ajuster l'énergie. Les autres types de sources laser (laser déclenché et laser à blocage de modes), ce sera notre cas, délivrent une énergie constante. Dans ce cas le réglage doit se faire par l'insertion de composants optiques sur le trajet du faisceau.

#### • Taille du faisceau laser

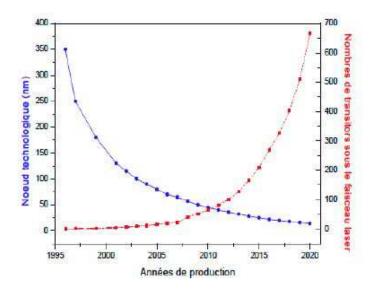

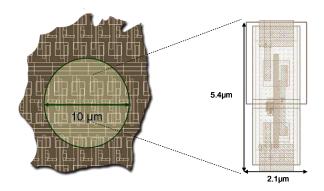

Le faisceau laser est considéré comme une onde gaussienne. Par conséquent, la structure radiale du taux de génération est du même type. Afin de réduire au maximum la taille du faisceau laser, on le focalise par le biais d'objectifs adaptés à la gamme de longueurs d'onde que délivre le laser. On définit le col du faisceau w0 au point de focalisation comme étant la demi largeur de la gaussienne à  $\frac{1}{e^2}$  et la taille du spot comme le double de celui-ci. La taille minimaleque l'on puisse obtenir par l'expérimentation est approximativement de 1 $\mu$ m.Il est important de comparer cette taille de spot laser par rapport à celle des structures actuelles et futures. En effet, comme le montre la figure ci-après, il y a quelques années le faisceau

laser n'affectait qu'un seul transistor à la fois. Aujourd'hui, le laser perturbe plusieurs transistors à la fois et ce nombre va augmenter dans les années à venir de façon critique au même rythme que l'évolution des nœuds technologiques [ITRS].

Figure 10 : Evolution dans le temps du nombre de transistors impactés par le laser pour une technologie donnée[ITRS][DOU08]

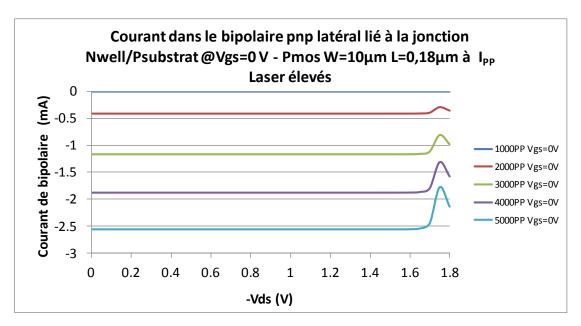

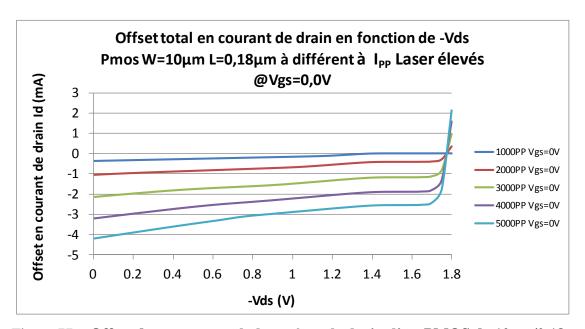

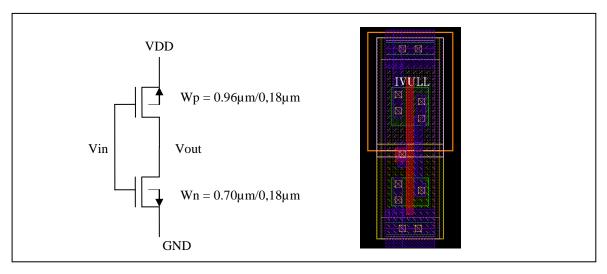

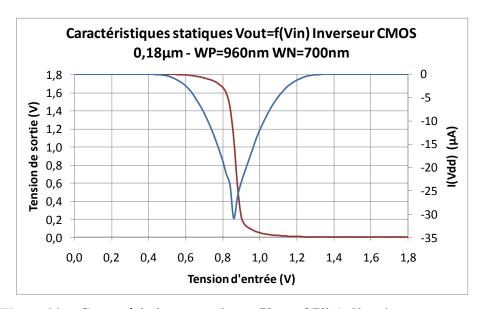

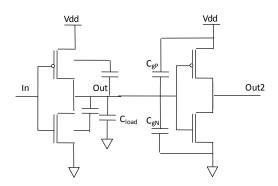

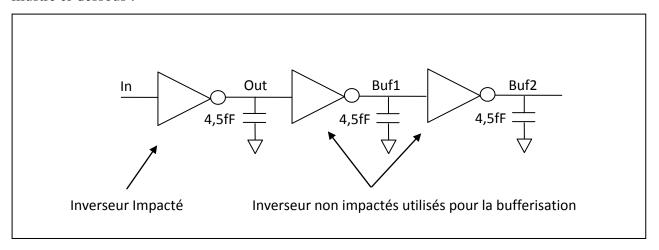

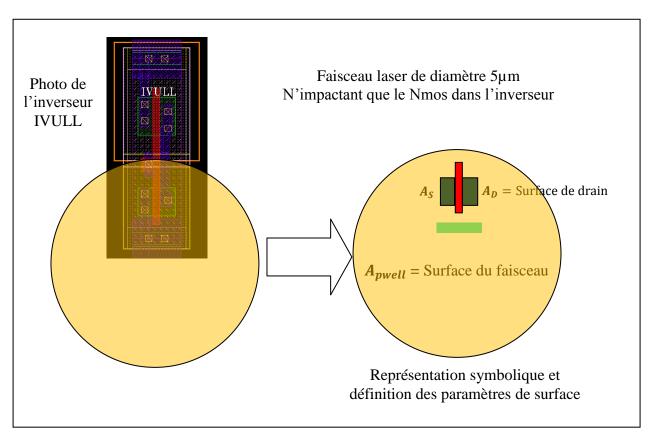

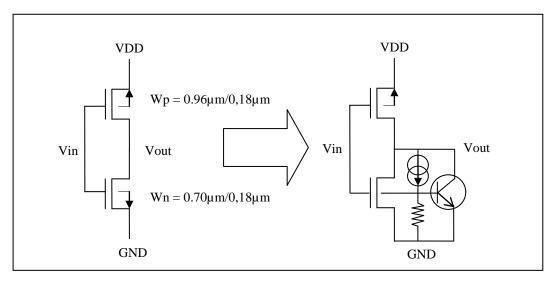

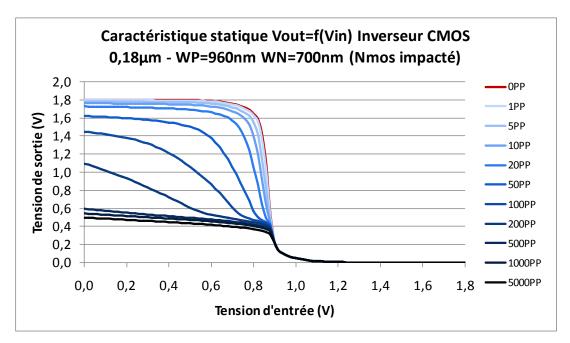

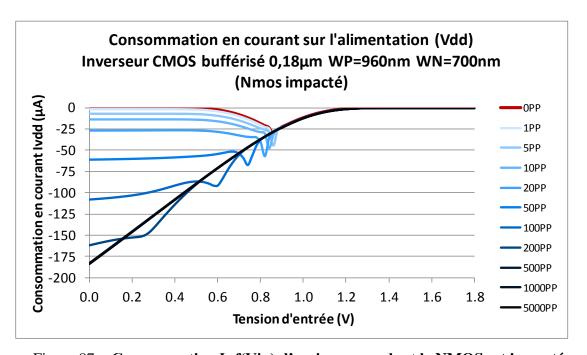

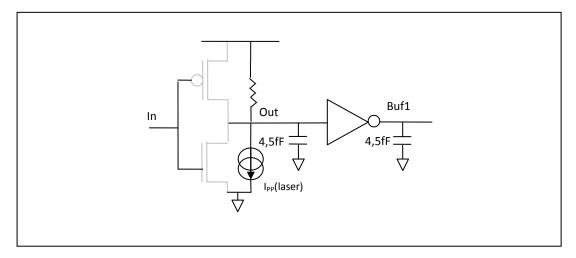

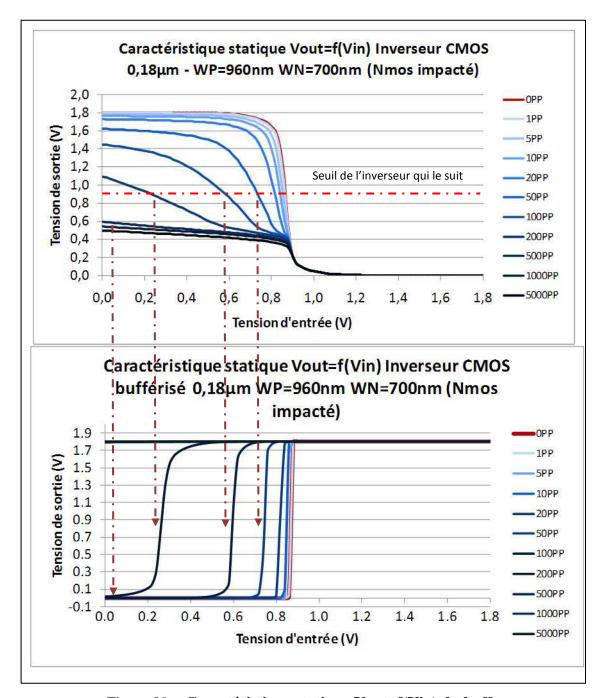

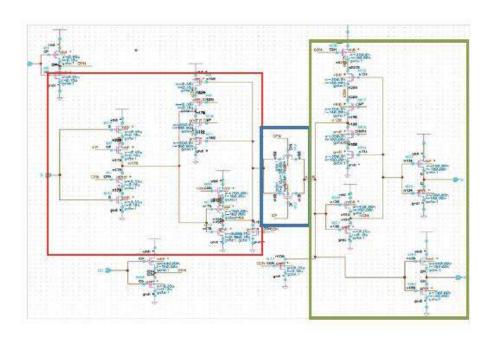

#### • Durée d'impulsion