## Crypto-processor – architecture, programming and evaluation of the security

Lubos Gaspar

#### ▶ To cite this version:

Lubos Gaspar. Crypto-processor – architecture, programming and evaluation of the security. Other [cond-mat.other]. Université Jean Monnet - Saint-Etienne, 2012. English. NNT: 2012STET4023. tel-00978472

### HAL Id: tel-00978472 https://theses.hal.science/tel-00978472v1

Submitted on 14 Apr 2014  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

pour obtenir le grade de docteur de Université Jean Monnet

DISCIPLINE : IMAGE, VISION, SIGNAL ÉQUIPE : Systèmes Embarques Sécurisés

## Crypto-processeur – architecture, programmation et évaluation de la sécurité

Lubos GASPAR

La thèse a été soutenue le 16 Novembre, 2012 avec le jury suivant

- Ingrid VERBAUWHEDE Lionel TORRES François-Xavier STANDAERT Tim GÜNEYSU Yannick TEGLIA Lilian BOSSUET Viktor FISCHER Florent BERNARD

- KUL, Belgium Rapporteur LIRMM, France Rapporteur UCL, Belgium Examinateur RUB, Germany Examinateur STM, France Examinateur LaHC, France Examinateur LaHC, France Directeur de thèse LaHC, France Codirecteur de thèse

## PHD THESIS

presented to obtain the doctor degree of Jean Monnet University

SPECIALITY: IMAGE, VISION, SIGNAL GROUP: SECURE EMBEDDED SYSTEMS

## Crypto-processor – architecture, programming and evaluation of the security

Lubos GASPAR

- Ingrid VERBAUWHEDE Lionel TORRES François-Xavier STANDAERT Tim GÜNEYSU Yannick TEGLIA Lilian BOSSUET Viktor FISCHER Florent BERNARD

- KUL, Belgium Reviewer LIRMM, France Reviewer UCL, Belgium Member RUB, Germany Member STM, France Member LaHC, France Member LaHC, France Supervisor LaHC, France Joint Supervisor

### Résumé

Les architectures des processeurs et coprocesseurs cryptographiques se montrent fréquemment vulnérables aux différents types d'attaques; en particulier, celles qui ciblent une révélation des clés chiffrées. Il est bien connu qu'une manipulation des clés confidentielles comme des données standards par un processeur peut être considérée comme une menace. Ceci a lieu par exemple lors d'un changement du code logiciel (malintentionné ou involontaire) qui peut provoquer que la clé confidentielle sorte en clair de la zone sécurisée. En conséquence, la sécurité de tout le système serait irréparablement ménacée. L'objectif que nous nous sommes fixé dans le travail présenté, etait la recherche d'architectures matérielles reconfigurables qui peuvent fournir une sécurité élevée des clés confidentielles pendant leur génération, leur enregistrement et leur échanges en implantant des modes cryptographiques de clés symétriques et des protocoles.

La première partie de ce travail est destinée à introduire les connaissances de base de la cryptographie appliquée ainsi que de l'élécronique pour assurer une bonne compréhenension des chapitres suivants.

Deuxièmement, nous présentons un état de l'art des menaces sur la confidentialité des clés secrètes dans le cas où ces dernières sont stockées et traitées dans un système embarqué. Pour lutter contre les menaces mentionnées, nous proposons alors de nouvelles règles au niveau du design de l'architecture qui peuvent augmenter la résistance des processeurs et coprocesseurs cryptographiques contre les attaques logicielles. Ces règles prévoient une séparation des registres dédiés à l'enregistrement de clés et ceux dédiés à l'enregistrement de données : nous proposons de diviser le système en zones : de données, du chiffreur et des clés et à isoler ces zones les unes des autres au niveau du protocole, du système, de l'architecture et au niveau physique.

Ensuite, nous presentons un nouveau crypto-processeur intitulé HCrypt, qui intègre ces règles de séparation et qui assure ainsi une gestion sécurisée des clés. Mises à part les instructions relatives à la gestion sécurisée de clés, quelques instructions supplémentaires sont dédiées à une réalisation simple des modes de chiffrement et des protocoles cryptographiques.

Dans les chapitres suivants, nous explicitons le fait que les règles de séparation suggérées, peuvent également être étendues à l'architecture d'un processeur généraliste et coprocesseur. Nous proposons ainsi un crypto-coprocesseur sécurisé qui est en mesure d'être utilisé en relation avec d'autres processeurs généralistes. Afin de démontrer sa flexibilité, le crypto-coprocesseur est interconnecté avec les processeurs soft-cores de NIOS II, de MicroBlaze et de Cortex M1.

Par la suite, la résistance du crypto-processeur par rapport aux attaques DPA est testée. Sur la base de ces analyses, l'architecture du processeur HCrypt est modifiée afin de simplifier sa protection contre les attaques par canaux cachés (SCA) et les attaques par injection de fautes (FIA). Nous expliquons aussi le fait qu'une réorganisation des blocs au niveau macroarchitecture du processeur HCrypt, augmente la résistance du nouveau processeur HCrypt2 par rapport aux attaques de type DPA et FIA.

Nous étudions ensuite les possibilités pour pouvoir reconfigurer dynamiquement les parties sélectionnées de l'architecture du processeur – crypto-coprocesseur. La reconfiguration dynamique peut être très utile lorsque l'algorithme de chiffrement ou ses implantations doivent être changés en raison de l'apparition d'une vulnérabilité. Finalement, la dernière partie de ces travaux de thèse, est déstinée à l'exécution des tests de fonctionnalité et des optimisations stricts des deux versions du crypto-processeur HCrypt.

### Abstract

Architectures of cryptographic processors and coprocessors are often vulnerable to different kinds of attacks, especially those targeting the disclosure of encryption keys. It is well known that manipulating confidential keys by the processor as ordinary data can represent a threat: a change in the program code (malicious or unintentional) can cause the unencrypted confidential key to leave the security area. This way, the security of the whole system would be irrecoverably compromised. The aim of our work was to search for flexible and reconfigurable hardware architectures, which can provide high security of confidential keys during their generation, storage and exchange while implementing common symmetric key cryptographic modes and protocols.

In the first part of the manuscript, we introduce the bases of applied cryptography and of reconfigurable computing that are necessary for better understanding of the work.

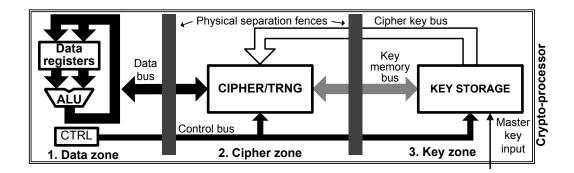

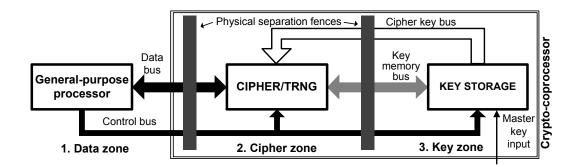

Second, we present threats to security of confidential keys when stored and processed within an embedded system. To counteract these threats, novel design rules increasing robustness of cryptographic processors and coprocessors against software attacks are presented. The rules suggest separating registers dedicated to key storage from those dedicated to data storage: we propose to partition the system into the data, cipher and key zone and to isolate the zones from each other at protocol, system, architectural and physical levels.

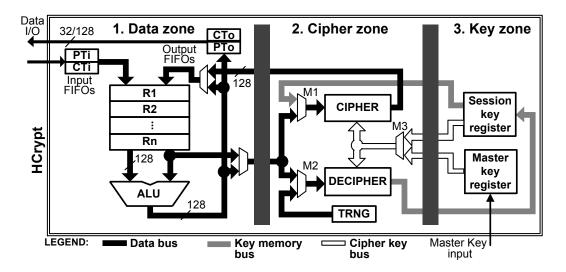

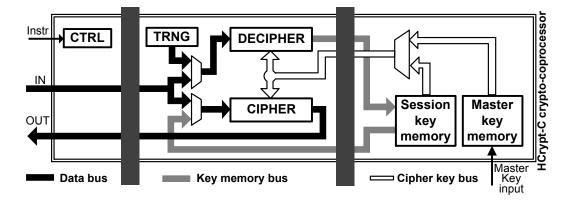

Next, we present a novel HCrypt crypto-processor complying with the separation rules and thus ensuring secure key management. Besides instructions dedicated to secure key management, some additional instructions are dedicated to easy realization of block cipher modes and cryptographic protocols in general.

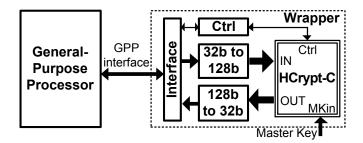

In the next part of the manuscript, we show that the proposed separation principles can be extended also to a processor-coprocessor architecture. We propose a secure crypto-coprocessor, which can be used in conjunction with any general-purpose processor. To demonstrate its flexibility, the crypto-coprocessor is interconnected with the NIOS II, MicroBlaze and Cortex M1 soft-core processors.

In the following part of the work, we examine the resistance of the HCrypt cryptoprocessor to differential power analysis (DPA) attacks. Following this analysis, we modify the architecture of the HCrypt processor in order to simplify its protection against side channel attacks (SCA) and fault injection attacks (FIA). We show that by rearranging blocks of the HCrypt processor at macroarchitecture level, the new HCrypt2 processor becomes natively more robust to DPA and FIA.

Next, we study possibilities of dynamically reconfiguring selected parts of the processor - crypto-coprocessor architecture. The dynamic reconfiguration feature can be very useful when the cipher algorithm or its implementation must be changed in response to appearance of some vulnerability.

Finally, the last part of the manuscript is dedicated to thorough testing and optimizations of both versions of the HCrypt crypto-processor.

Architectures of crypto-processors and crypto-coprocessors are often vulnerable to software attacks targeting the disclosure of encryption keys.

The thesis introduces separation rules enabling crypto-processor/coprocessors to support secure key management. Separation rules are implemented on novel HCrypt crypto-processor resistant to software attacks targetting the disclosure of encryption keys.

### Acknowledgements

First and foremost, I would like to thank Diana, the most beautiful discovery I have made, for her unconditional love, encouragement, patience, help and for reminding me that there is much more to life than study. I dedicate this dissertation also to my parents Vladimir, Emilia and my brother Vladimir who have given me their unequivocal support throughout, as always, for which my mere expression of thanks likewise does not suffice.

I am very grateful to the dissertation reviewers Lionel Torres and Ingrid Verbauwhede for their time spent on reading the thesis and their valuable comments, and also to all dissertation committee members for their valuable effort and time: Florent Bernard, Lilian Bossuet, Viktor Fischer, Tim Güneysu, François-Xavier Standaert, Yannick Teglia, Lionel Torres and Ingrid Verbauwhede.

This thesis would not have been possible without help, guidance, support and patience of my principal supervisor, professor Viktor Fischer. He is the one who has given me many invaluable advices on both an academic and a personal level, dedicated a great portion of his time to reading and correcting all my works, and enabled me to meet many great people in cryptography research domain. For all this and much more, I am greatly indebted to him. Thank you sir, dakujem!

Many thanks go to my second supervisor, Florent Bernard, for his good advice, friendship and help on the administration battlefield. I am especially grateful to all other colleagues in the Secure Embedded Systems group for making my days much brighter, for creating pleasant working environment in the laboratory, and for helping me to improve my French: Alain Aubert, Pierre Bayon, Nathalie Bochard, Lilian Bossuet, Pierre-Louis Cayrel, Karim Cherkaoui, Robert Fouquet, Patrick Haddad, Abdourhamane Idrissa, Tania Richmond and Boyan Valtchanov. I also thank the research and staff members of the Laboratoire Hubert Curien in Saint-Etienne.

This work, in the frame of the project SecReSoC (ARPEGE 2009 program, ANR-09-SEGI-013), would not have been possible without the support of the ANR (French National Research Agency). I thank also to the SecReSoC team members: Benoît Badrignans, Lyonel Barthe, Pascal Benoit, Pascal Cotret, Jean-Luc Danger, Florian Devic, Viktor Fischer, Guy Gogniat, Houssem Maghrebi and Lionel Torres.

I thank Tim Güneysu for inviting me to Bochum, for fruitful discussions and many good advices. I would like to acknowledge all the members of the EMSEC and Hardware security groups.

I acknowledge Marek Repka from Slovak Technical University of Bratislava for excellent cooperation and many passionate discussions producing interesting scientific results.

I could not have obtained excellent practical knowledge in complex PCB designs without guidance and support of Micronic company in Trebejov, Slovakia.

This way I would also like to express my sincere gratitude to Milos Drutarovsky from Technical University of Kosice in Slovakia for introducing me into the great world of cryptography, microprocessors, and FPGAs during my master studies.

Last but by no means least, I would like to thank to all my friends in Saint-Etienne for all those great unforgettable moments we had during many different social events, sports activities and trips. Thank you Ali, Alius, Anton, Christina, Claire-Marie, Fanny, Hassan, Iseline, Johanns, Johari, Katka, Laura, Lina, Maggie, Mathias, Max, Merike, Monika, Montse, Noelia, Omar, Rosaura, Sandra, Sergey, Silvia, Sona, Tomek, Tristan, Zdenka and many others!

## Contents

| R           | ésum  | é                                              | v        |  |  |

|-------------|-------|------------------------------------------------|----------|--|--|

| Abstract vi |       |                                                |          |  |  |

| A           | cknov | wledgements                                    | ix       |  |  |

| Li          | st of | Figures                                        | xv       |  |  |

| Li          | st of | Tables x                                       | vii      |  |  |

| G           | lossa | ry x                                           | ix       |  |  |

| 1           | Intr  | oduction                                       | 1        |  |  |

|             | 1.1   | Flexible Security and Hardware Implementations | 1        |  |  |

|             | 1.2   | Objectives of the Thesis                       | 2        |  |  |

|             | 1.3   | Contribution                                   | 2        |  |  |

|             | 1.4   | Thesis Preview                                 | 3        |  |  |

| <b>2</b>    | The   | eoretical and Technological Background         | <b>5</b> |  |  |

|             | 2.1   | Secure Communications                          | 6        |  |  |

|             | 2.2   | Symmetric Key Cryptography                     | 7        |  |  |

|             |       | 2.2.1 Block Ciphers                            | 7        |  |  |

|             |       | 2.2.2 Stream Ciphers                           | 16       |  |  |

|             | 2.3   | Hash Functions                                 | 17       |  |  |

|             |       | 2.3.1 MD5 Hash Function                        | 18       |  |  |

|             | 2.4   |                                                | 18       |  |  |

|             |       |                                                | 20       |  |  |

|             |       |                                                | 21       |  |  |

|             |       |                                                | 21       |  |  |

|             | 2.5   | Key Management                                 | 22       |  |  |

|             |       |                                                | 24       |  |  |

|             |       | 1 0                                            | 26       |  |  |

|             |       |                                                | 26       |  |  |

|             |       |                                                | 27       |  |  |

|             | 2.6   |                                                | 29       |  |  |

|             |       |                                                | 29       |  |  |

|             |       |                                                | 30       |  |  |

|             |       |                                                | 31       |  |  |

|             |       | 2.6.4 Technology Limits                        | 32       |  |  |

|             |       |                                                | 32       |  |  |

|             | 2.7   | Partial Hardware Reconfiguration and Security  | 33       |  |  |

|             |       |                                                |          |  |  |

|   |     | 2.7.1   | Partial Reconfiguration                                                  | 33 |

|---|-----|---------|--------------------------------------------------------------------------|----|

|   |     | 2.7.2   | Security Aspects of the Partial Reconfiguration                          | 34 |

| 3 | Cry | pto-pr  | cocessor with Secure Key Management                                      | 37 |

|   | 3.1 | Crypt   | o-processors - State of the Art                                          | 38 |

|   |     | 3.1.1   | Security Issues of the Cryptographic Software Implementations            | 39 |

|   |     | 3.1.2   | Cryptographic Hardware Architectures and their Security                  | 40 |

|   | 3.2 | New I   | Rules for Securing Key Management                                        | 43 |

|   |     | 3.2.1   | Separation at Protocol Level                                             | 44 |

|   |     | 3.2.2   | Separation at System Level                                               | 45 |

|   |     | 3.2.3   | Separation at Architectural Level                                        | 45 |

|   |     | 3.2.4   | Separation at Physical Level                                             | 46 |

|   | 3.3 | Crypt   | o-processor Design                                                       | 47 |

|   |     | 3.3.1   | Hardware Architecture                                                    | 48 |

|   |     | 3.3.2   | Implementation of HCrypt in FPGA                                         | 50 |

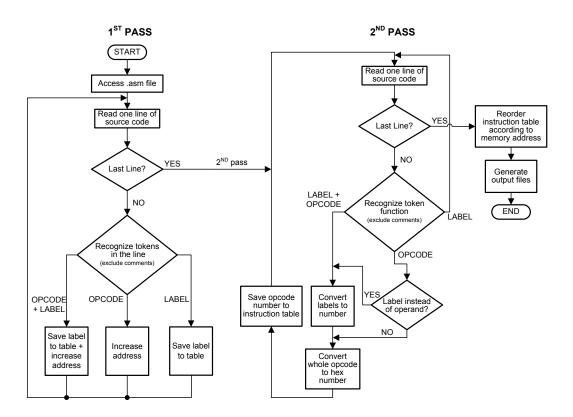

|   |     | 3.3.3   | Programming Means                                                        | 51 |

|   |     | 3.3.4   | Communication Protocol                                                   | 56 |

|   | 3.4 | Imple   | mentation Results                                                        | 58 |

|   |     | 3.4.1   | Cost Evaluation                                                          | 58 |

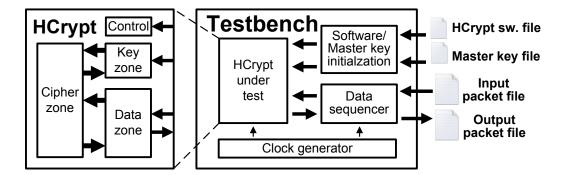

|   |     | 3.4.2   | Simulation                                                               | 58 |

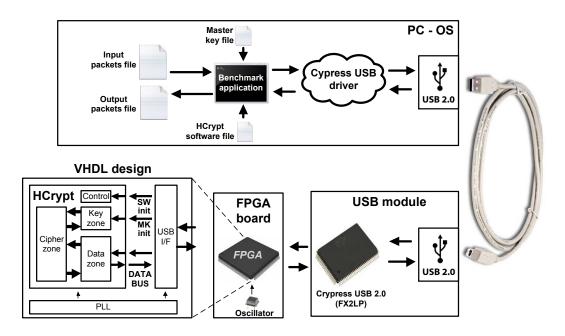

|   |     | 3.4.3   | Hardware Tests and Benchmarks                                            | 60 |

|   | 3.5 | Discus  | ssion                                                                    | 62 |

|   | 3.6 | Concl   | usions                                                                   | 62 |

| 4 | Cry | pto-co  | processor with Secure Key Management                                     | 65 |

|   | 4.1 | Crypt   | o-coprocessors - State of the Art                                        | 66 |

|   | 4.2 | New I   | Rules for Securing Key Management                                        | 67 |

|   |     | 4.2.1   | Separation at Protocol Level                                             | 67 |

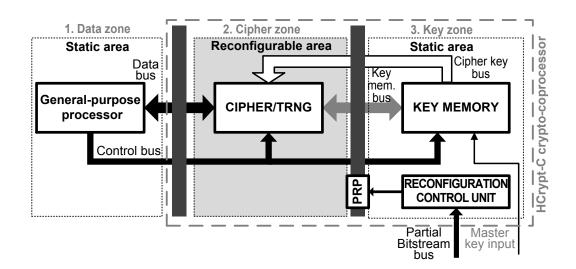

|   |     | 4.2.2   | Separation at System Level                                               | 68 |

|   |     | 4.2.3   | Separation at Architectural Level                                        | 68 |

|   |     | 4.2.4   | Separation at Physical Level                                             | 69 |

|   | 4.3 | Exten   | sion of Separation Rules to Crypto-coprocessors                          | 69 |

|   | 4.4 | Interfa | aces between GPP and the HCrypt-C Crypto-coprocessor                     | 70 |

|   |     | 4.4.1   | Internal Processor Bus                                                   | 70 |

|   |     | 4.4.2   | Dedicated Coprocessor Bus                                                | 71 |

|   |     | 4.4.3   | Peripheral Bus                                                           | 71 |

|   | 4.5 | Design  | n of the Crypto-coprocessor/Processor Pairs                              | 71 |

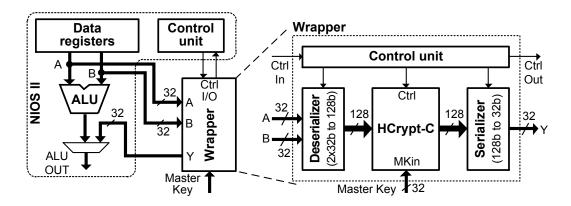

|   |     | 4.5.1   | Altera NIOS II GPP with HCrypt-C Crypto-coprocessor                      | 72 |

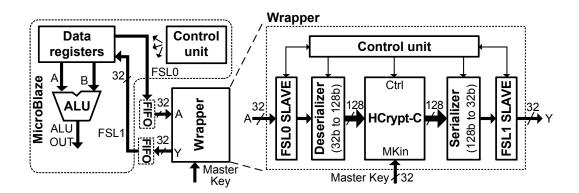

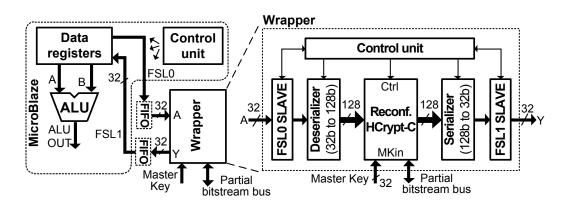

|   |     | 4.5.2   | Xilinx MicroBlaze GPP with HCrypt-C Crypto-coprocessor $% \mathcal{A}$ . | 73 |

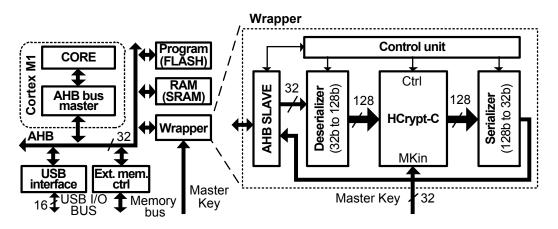

|   |     | 4.5.3   | ARM Cortex M1 GPP with HCrypt-C Crypto-coprocessor                       | 77 |

|   | 4.6 | Imple   | mentation Results                                                        | 79 |

|   |     | 4.6.1   | Cost Evaluation                                                          | 79 |

|   |     | 4.6.2   | Hardware Tests and Benchmarks                                            | 81 |

|   | 4.7 | Discus  | ssion                                                                    | 82 |

|                                                             | 4.8   | Conclu  | usions                                                       | 83  |

|-------------------------------------------------------------|-------|---------|--------------------------------------------------------------|-----|

| 5 Protecting Crypto-processors Against SCA at Macroarchitec |       |         |                                                              |     |

|                                                             | Lev   |         |                                                              | 85  |

|                                                             | 5.1   |         | Channel Attacks                                              | 86  |

|                                                             |       | 5.1.1   | Power Analysis Attacks                                       | 86  |

|                                                             |       | 5.1.2   | Countermeasures                                              | 88  |

|                                                             | 5.2   |         | o-processor with Zero-cost Countermeasures against SCA       |     |

|                                                             |       | 5.2.1   | Introduction                                                 | 90  |

|                                                             |       | 5.2.2   | Design of SCA and FIA Resistant HCrypt Version               |     |

|                                                             |       | 5.2.3   | Evaluation of the HCrypt2 Security Against SCA and FIA       |     |

|                                                             |       | 5.2.4   | Implementation Results                                       |     |

|                                                             |       | 5.2.5   | Discussion                                                   |     |

|                                                             | 5.3   | Conclu  | usions                                                       | 109 |

| 6                                                           | Par   | tial Re | econfiguration of Crypto-processors                          | 111 |

|                                                             | 6.1   | FPGA    | A Reconfiguration and Security Aspects                       | 112 |

|                                                             |       | 6.1.1   | FPGA Bitstream Protection                                    | 112 |

|                                                             |       | 6.1.2   | IP Bitstream Security in Partially Reconfigurable System     | 114 |

|                                                             | 6.2   | Separa  | ation Rules Involving Partial Reconfiguration                | 116 |

|                                                             |       | 6.2.1   | Total Reconfiguration Versus Partial Reconfiguration of the  |     |

|                                                             |       |         | Device                                                       | 117 |

|                                                             |       | 6.2.2   | Validation of the Principle of HCrypt-C Partial Reconfigura- |     |

|                                                             |       |         | tion in SRAM FPGAs                                           | 118 |

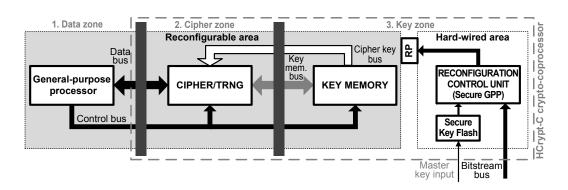

|                                                             |       | 6.2.3   | Reconfiguration of HCrypt-C Crypto-coprocessor in FPGAs      |     |

|                                                             |       |         | Containing Hardwired GPPs                                    |     |

|                                                             | 6.3   |         | n of the Reconfigurable HCrypt-C                             |     |

|                                                             |       | 6.3.1   | Reconfigurable Cipher Zone Modules                           |     |

|                                                             |       | 6.3.2   | Reconfiguration Control Unit                                 |     |

|                                                             | 6.4   |         | mentation Results                                            |     |

|                                                             |       | 6.4.1   | Cost Evaluation                                              |     |

|                                                             | 6.5   |         | ssion                                                        |     |

|                                                             | 6.6   | Conclu  | usions                                                       | 128 |

| 7                                                           | Sun   | nmary   | of Contributions and Conclusions                             | 131 |

|                                                             | 7.1   | Summ    | nary of Contributions                                        | 131 |

|                                                             | 7.2   | Conclu  | usions                                                       | 132 |

|                                                             | 7.3   | Perspe  | ectives                                                      | 133 |

| Li                                                          | st of | Publi   | cations                                                      | 135 |

| Bi                                                          | bliog | graphy  |                                                              | 137 |

| Appen | dix A: Introduction                                                                                          | 153 |

|-------|--------------------------------------------------------------------------------------------------------------|-----|

| A.1   | Sécurité Flexible Implémentations Matérielles                                                                | 153 |

| A.2   | Objectifs de la Thèse                                                                                        | 154 |

| A.3   | Contribution                                                                                                 | 155 |

| A.4   | Structure de la Thèse                                                                                        | 155 |

| Appen | dix B: Aperçu des Contributions et Conclusions                                                               | 157 |

| B.1   | Aperçu des Contributions                                                                                     | 157 |

| B.2   | Conclusions                                                                                                  | 158 |

| B.3   | Perspectives                                                                                                 | 160 |

| Appen | dix C: Résumé de Thèse                                                                                       | 161 |

| C.1   | Chapitre 1 : Introduction                                                                                    | 161 |

|       | C.1.1 Objectifs de la thèse                                                                                  | 161 |

|       | C.1.2 Contribution $\ldots$ | 162 |

| C.2   | Chapitre 2 : Approche Théorique et Technologique                                                             | 162 |

| C.3   | Chapitre 3 : Crypto-processeur avec une Gestion Sécurisée des Clés $% \mathcal{S}$ .                         | 163 |

| C.4   | Chapitre 4 : Crypto-coprocesseur avec une Gestion Sécurisée des Clés                                         | 164 |

| C.5   | Chapitre 5 : Protection des Crypto-processeurs contre les SCA au                                             |     |

|       | niveau Macroarchitecture                                                                                     | 164 |

| C.6   | Chapitre 6 : Reconfiguration Partielle des Crypto-processeurs $\ldots$ .                                     | 165 |

| C.7   | Chapitre 7 : Résumé de la Contribution et des Conclusions                                                    | 166 |

|       | C.7.1 Aperçu des Contributions                                                                               | 166 |

|       | C.7.2 Perspectives                                                                                           | 166 |

# List of Figures

| 2.1  | Structure of the Data Encryption Standard cipher (DES) 9                                    |

|------|---------------------------------------------------------------------------------------------|

| 2.2  | Structure of the Advanced Encryption Standard (AES) cipher with                             |

|      | 128-bit key: Encryption (A), Decryption (B), Key expansion (C) with                         |

|      | Function (D)                                                                                |

| 2.3  | Division of input/output data blocks and internal state array 11                            |

| 2.4  | ShiftRows transformation performing left rotation of rows by one,                           |

|      | two or three bytes                                                                          |

| 2.5  | InvShiftRows transformation performing right rotation of rows by<br>one, two or three bytes |

| 2.6  | Electronic Code Book encryption block cipher mode of operation 13                           |

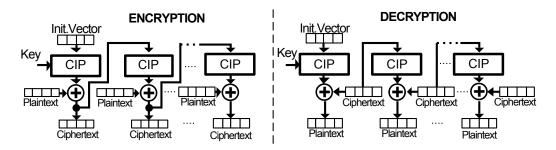

| 2.7  | Cipher Block Chaining encryption block cipher mode of operation 14                          |

| 2.8  | Cipher Feedback encryption block cipher mode of operation 14                                |

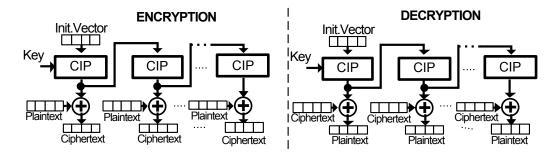

| 2.9  | Output Feedback encryption block cipher mode of operation 15                                |

| 2.10 | Counter encryption block cipher mode of operation                                           |

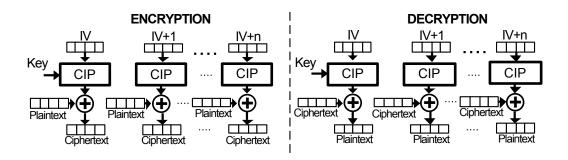

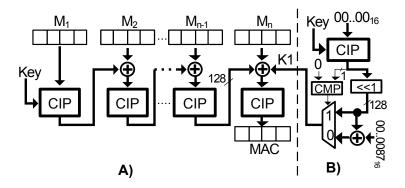

| 2.11 |                                                                                             |

|      | computation of the K1 (part B)                                                              |

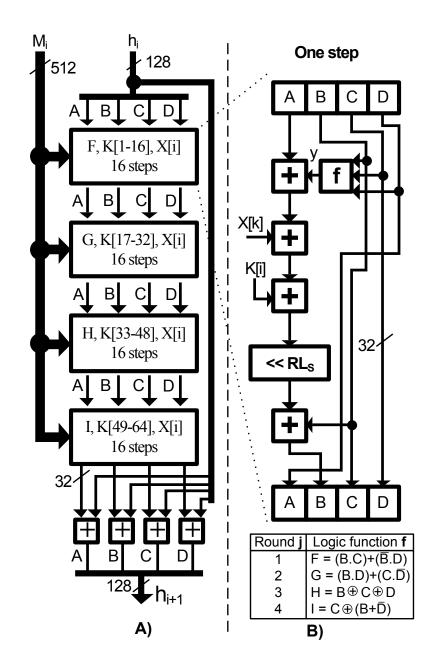

| 2.12 | MD5 hash function structure (part A) and architecture of one step                           |

|      | (part B)                                                                                    |

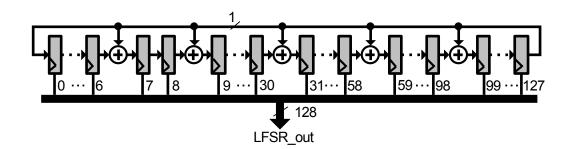

| 2.13 | A 128-bit Galois Linear Feedback Shift Register capable of generating                       |

|      | maximal length sequences                                                                    |

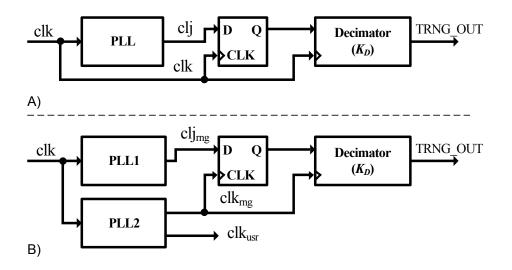

| 2.14 | TRNG based on one (part A) or two PLLs (part B) 23                                          |

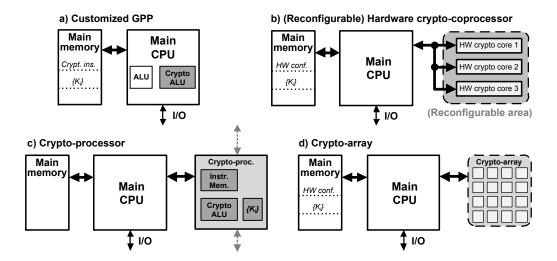

| 3.1  | Four different types of the hardware cryptographic engines 41                               |

| 3.2  | Separation of key storage and data storage at system level for crypto-                      |

|      | processor                                                                                   |

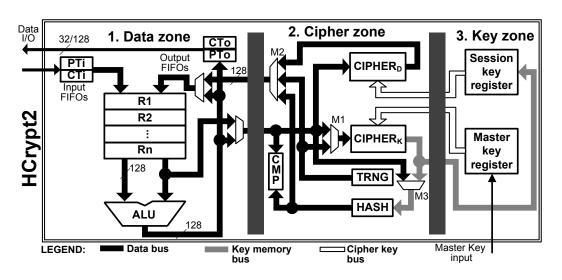

| 3.3  | HCrypt architecture divided into data, cipher and key zones 48                              |

| 3.4  | FlexASM two-pass compilation flow chart 54                                                  |

| 3.5  | Authenticated key update Communication protocol between two de-                             |

|      | vices                                                                                       |

| 3.6  | Structure of the packet supported by HCrypt 58                                              |

| 3.7  | HCrypt simulation procedure 59                                                              |

| 3.8  | HCrypt hardware test setup                                                                  |

| 4.1  | Separation of key storage and data storage at system level for crypto-                      |

|      | coprocessor                                                                                 |

| 4.2  | Cryptographic system containing the HCrypt-C crypto-coprocessor                             |

|      | interconnected with the GPP through the wrapper block 70                                    |

| 4.3  | HCrypt-C crypto-coprocessor implementation                                                  |

| 4.4  | NIOS II interconnected with the HCrypt-C crypto-coprocessor wrap-                           |

|      | per via the internal processor bus                                                          |

| 4.5 | MicroBlaze interconnected to the HCrypt-C crypto-coprocessor wrap-                    |

|-----|---------------------------------------------------------------------------------------|

|     | per via a dedicated processor bus (i.e. FSL)                                          |

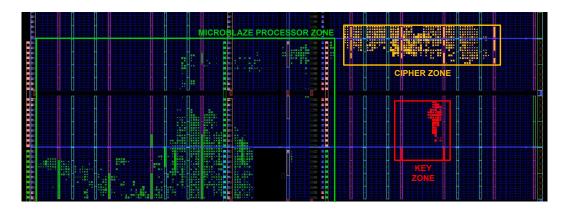

| 4.6 | Floorplan of MicroBlaze divided into processor, cipher and key zones                  |

|     | placed in isolated physical blocks (cipher and key zones are part of                  |

|     | HCrypt-C)                                                                             |

| 4.7 | Cortex M1 interconnected to HCrypt-C wrapper via peripheral bus . 78                  |

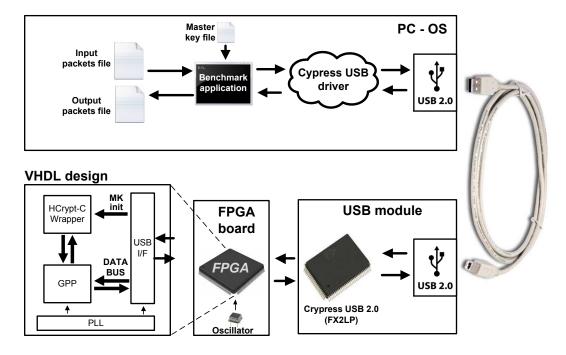

| 4.8 | General-Purpose Processor system hardware test setup                                  |

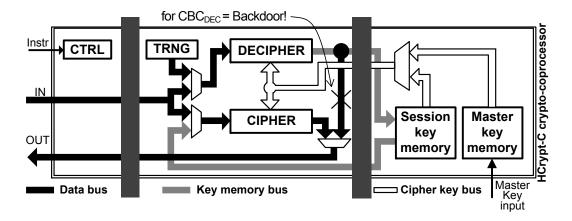

| 4.9 | Security module with CBC decryption mode backdoor                                     |

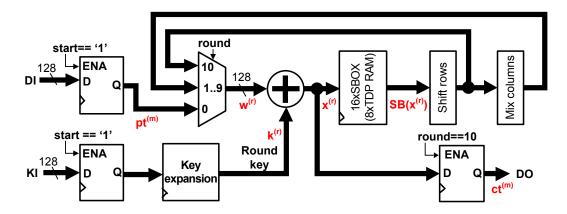

| 5.1 | Architecture of the AES cipher with the 128-bit folded datapath 93                    |

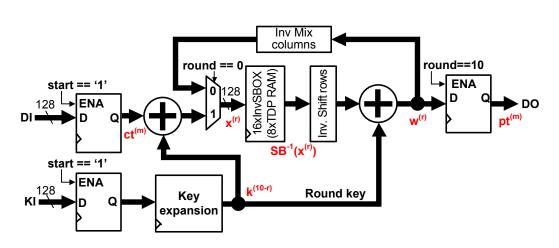

| 5.2 | Architecture of the AES decipher with the 128-bit folded data<br>path $\therefore$ 96 |

| 5.3 | HCrypt2 with parallel cipher-cipher architecture 100                                  |

| 5.4 | HCrypt2 communication protocol between two devices 104                                |

| 6.1 | Separation rules including partial reconfiguration capability with re-                |

|     | configuration of the cipher zone only 117                                             |

| 6.2 | Separation rules including partial reconfiguration capability with re-                |

|     | configuration of the processor, cipher and key zone 118                               |

| 6.3 | ${\it MicroBlaze\ interconnected\ to\ Reconfigurable\ HCrypt-C\ crypto-coprocessor}$  |

|     | extension via the FSL bus wrapper                                                     |

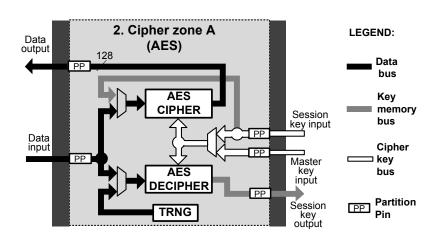

| 6.4 | Reconfigurable cipher zone containing the AES cipher, decipher and                    |

|     | TRNG (AES reconfigurable module)                                                      |

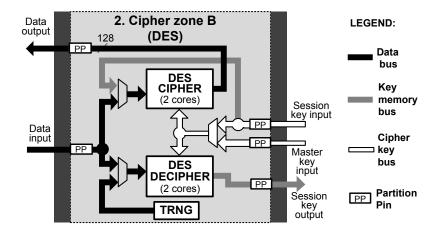

| 6.5 | Reconfigurable cipher zone containing the DES cipher unit, decipher                   |

|     | unit and TRNG (DES reconfigurable module)                                             |

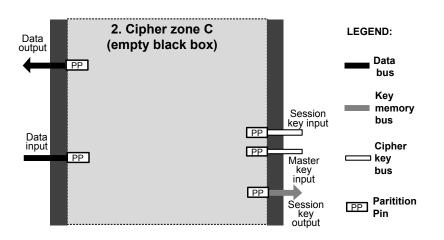

| 6.6 | Empty reconfigurable cipher zone containing only partition pins (empty                |

|     | black-box reconfigurable module)                                                      |

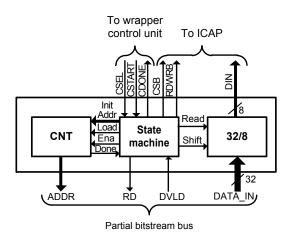

| 6.7 | Architecture of the Reconfiguration Control Unit                                      |

| 6.8 | Hardware test setup of the Secure General-Purpose Processor with                      |

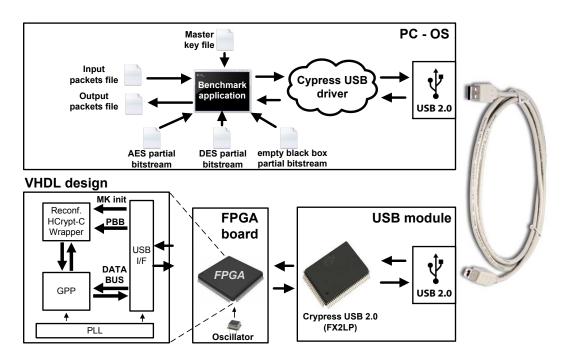

|     | reconfigurable HCrypt-C crypto-coprocessor                                            |

|     |                                                                                       |

# List of Tables

| 2.1          | The comparison of basic block cipher modes of operation providing confidentiality [1] and authenticity [2]             | 13              |

|--------------|------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.2          | Configuration of a TRNG based on two PLLs for Xilinx Virtex-6<br>FPGAs                                                 | 23              |

| 2.3          | Basic key establishment protocols and their properties as classified in [3]                                            | 23<br>28        |

| 3.1          | Overview and performance of some GPPs customized for implemen-<br>tation of cryptographic algorithms                   | 42              |

| 3.2          | Summary of characteristics of customized GPPs                                                                          | 42              |

| 3.3          | Overview and performance of some crypto-processors                                                                     | 43              |

| 3.4          | Summary of characteristics of selected crypto-processors                                                               | 44              |

| 3.5          | The dedicated instruction set                                                                                          | 52              |

| 3.6          | Block encryption modes                                                                                                 | 53              |

| 3.7          | Instruction set definition file example                                                                                | 55              |

| 3.8          | Utilization of resources in XC6VLX240T                                                                                 | 59              |

| 3.9          | Number of clock cycles required for the packet processing $\ldots$ .                                                   | 60              |

| 3.10         | Dependence of maximum throughputs on number of 128-bit data                                                            |                 |

|              | blocks in the packet                                                                                                   | 60              |

| 4.1          | Different implementations of crypto-coprocessors                                                                       | 67              |

| 4.2          | Summary of crypto-coprocessors' characteristics                                                                        | 68              |

| 4.3          | HCrypt-C crypto-coprocessor instructions in NIOS II                                                                    | 74              |

| 4.4          | Simplified CFB deciphering block mode example on NIOS II                                                               | 75              |

| 4.5          | Simplified CFB deciphering block mode example on MicroBlaze                                                            | 76              |

| 4.6          | Simplified CFB deciphering block mode example on Cortex M1                                                             | 80              |

| 4.7          | Utilization of FPGA resources by tree processors with the HCrypt-C                                                     |                 |

|              | crypto-coprocessor containing the AES cipher                                                                           | 81              |

| F 1          | Derver en derie ette der en en AEC einden en dele inder                                                                | 00              |

| $5.1 \\ 5.2$ | Power analysis attacks on an AES cipher and decipher Possibilities of physical attacks on the HCrypt1 crypto-processor | $\frac{98}{99}$ |

| 5.2<br>5.3   | The modifications of the HCrypt1 instruction set                                                                       |                 |

| 5.3<br>5.4   | Possibilities of physical attacks on the HCrypt2 crypto-processor                                                      |                 |

| 5.5          | Implementation results of HCrypt1 and HCrypt2 in Xilinx Virtex-6.                                                      | 105             |

| 5.6          | Number of clock cycles required for the packet processing                                                              | 106             |

| 5.7          | Dependence of maximum throughputs on number of 128-bit data                                                            | 100             |

|              | blocks in the packet                                                                                                   | 107             |

|              | -                                                                                                                      |                 |

| 6.1          | Utilization of Reconfigurable MicroBlaze and compared FPGA re-                                                         |                 |

|              | sources by tree processors with the HCrypt-C crypto-coprocessor con-                                                   |                 |

|              | taining the AES cipher                                                                                                 | 124             |

121

| 6.2 | Comparison of three versions of the reconfigurable module (RM) in                    |     |

|-----|--------------------------------------------------------------------------------------|-----|

|     | an extended MicroBlaze system                                                        | 124 |

| 6.3 | The maximum data throughput comparison of three static system                        |     |

|     | featuring AES cipher zone and reconfigurable MicroBlaze system fea-                  |     |

|     | turing AES, DES and empty black-box reconfigurable cipher zones .                    | 126 |

| 6.4 | ICAP throughput (left) and comparison of three reconfigurable mod-                   |     |

|     | ule sizes and configuration time length (right) $\ldots \ldots \ldots \ldots \ldots$ | 127 |

|     |                                                                                      |     |

# Glossary

| ADD:     | Addition                                            |

|----------|-----------------------------------------------------|

| AES:     | Advanced Encryption Standard                        |

| AES-NI:  | Advanced Encryption Standard - New Instructions     |

| AHB:     | Advanced High-performance Bus                       |

| ALM:     | Adaptive Logic Module (In Altera Stratix-II)        |

| ALU:     | Arithmetic Logic Unit                               |

| AMK:     | Authentication Master Key                           |

| ANSI:    | American National Standards Institute               |

| APB:     | Advanced Peripheral Bus                             |

| ASIC:    | Application Specific Integrated Circuit             |

| BB:      | Bitstream Bus                                       |

| BRAM:    | Block RAM (in Xilinx Virtex)                        |

| CBC:     | Cipher Block Chaining                               |

| CBC-MAC: | Cipher Block Chaining - Message Authentication Code |

| CC:      | Common Criteria                                     |

| CCM:     | Counter mode with CBC-MAC                           |

| CDONE:   | Configuration Done flag                             |

| CFB:     | Cipher FeedBack mode                                |

| CIP:     | Cipher                                              |

| CLB:     | Configurable Logic Block (in Xilinx Virtex)         |

| CLK:     | Clock signal                                        |

| CMT:     | Clock Management Tile (in Xilinx Virtex)            |

| CLR:     | Clear                                               |

| CMAC:    | Cipher Block Chaining Message Authentication Code   |

| CMOS:    | Complementary Metal Oxid Semiconductor              |

| CMP:     | Compare                                             |

| CPA:     | Correlation Power Analysis                          |

| CPU:     | Central Processing Unit                             |

| CSEL:    | Configuration Select                                |

| CSK:     | Ciphered Session Key                                |

| CSP:     | Critical Security Parameter                         |

| CSTART:  | Configuration Start                                 |

| CT:      | Ciphertext                                          |

| CTI:     | Ciphertext Input                                    |

| CTO:     | Ciphertext Output                                   |

| CTR:     | Counter mode                                        |

| CTRL:    | Control                                             |

| DCM:     | Digital Clock Manager (in Xilinx Virtex)            |

|          |                                                     |

| DEC:      | Decrement                                                 |

|-----------|-----------------------------------------------------------|

| Decip:    | Decipher                                                  |

| DES:      | Data Encryption Standard                                  |

| DFA:      | Differential Fault Analysis                               |

| DFF:      | D Flip-Flop                                               |

| DH:       | Diffie-Hellmann                                           |

| DI:       | Data Input                                                |

| DLL:      | Delay-Locked Loop (in Xilinx FPGAs)                       |

| DO:       | Data Output                                               |

| DPA:      | Differential Power Analysis                               |

| DPRAM:    | Dual Port RAM                                             |

| DRM:      | Digital Rights Management                                 |

| DRNG:     | Deterministic Random Number Generator                     |

| DRP:      | Dual-Rail Precharge logic                                 |

| DSP:      | Digital Signal Processing                                 |

| DVLD:     | Data Valid flag                                           |

| EAL:      | Evaluation Assurance Level (in CC)                        |

| ECB:      | Electronic Code Book                                      |

| ECC:      | Elliptic Curve Cryptography                               |

| EM:       | Encryption Modes                                          |

| EMA:      | Electromagnetic Analysis                                  |

| ENA:      | Enable signal                                             |

| FF:       | Flip-Flop                                                 |

| FIA:      | Fault Injection Attacks                                   |

| FIFO:     | First In First Out                                        |

| FIPS:     | Federal Information Processing Standard                   |

| FP:       | Fingerprint (in communication protocol)                   |

| FPGA:     | Field Programmable Gate Arrays                            |

| FSL:      | Fast Simplex Link                                         |

| GCD:      | Greatest Common Divisor                                   |

| GCM:      | Galois/Counter Mode and GMAC                              |

| GPP:      | General-Purpose Processor                                 |

| HCrypt:   | Hubert Curien Crypto-processor                            |

| HCrypt-C: | Hubert Curien Crypto-coprocessor                          |

| HD:       | Hamming Distance                                          |

| HMAC:     | Keyed-Hashing MAC                                         |

| HRNG:     | Hybrid Random Number Generator                            |

| HW:       | Hamming weight (in SCA)                                   |

| IAP:      | In-Application Programmability (in Microsemi SmartFusion) |

| ICAP:     | Internal Configuration Access Port (in Xilinx Virtex)     |

| ID:       | Identification Code                                       |

| I/F:      | Interface                                                 |

| INC:      | Increment                                                 |

| I/O:      | $\operatorname{Input}/\operatorname{Output}$              |

| IP:         | Intellectual Property (in general)                  |

|-------------|-----------------------------------------------------|

| IV:         | Initialization Vector                               |

| IVT:        | Isolation Verification Tool                         |

| JTAG:       | Joint Test Action Group                             |

| KI:         | Key Input                                           |

| KO:         | Key Output                                          |

| LAB:        | Logic Block Array (In Altera Stratix-II)            |

| LFSR:       | Linear Feedback Shift Register                      |

| LUT:        | Look-Up Table                                       |

| MAC:        | Message Authentication Code                         |

| MC:         | Mix Columns (in AES)                                |

| MCCP:       | Multi-Core Crypto-Processor                         |

| MD5:        | Message Digest algorithm 5                          |

| MIM:        | Man In the Middle                                   |

| MK:         | Master Key                                          |

| MMCM:       | Mixed-Mode Clock Management                         |

| MPSoC:      | Multi-Processor System on Chip                      |

| NIST:       | U.S. National Institute of Standards and Technology |

| NSA:        | U.S. National Security Agency                       |

| OFB:        | Output FeedBack                                     |

| PBB:        | Partial Bitstream Bus                               |

| PC:         | Personal Computer                                   |

| PC1:        | Permutation Choice 1 (in DES)                       |

| <b>PC2:</b> | Permutation Choice 2 (in DES)                       |

| PIP:        | Programmable Interconnect Points                    |

| PK:         | Public Key                                          |

| PLL:        | Phase Locked Loop                                   |

| PM:         | Personalization Module                              |

| PP:         | Partition Pin                                       |

| PR:         | Partial Reconfiguration                             |

| PRNG:       | Pseudo-Random Number Generator                      |

| PRP:        | Partial Reconfiguration Port                        |

| PSK:        | Protected Session Key                               |

| PT:         | Plaintext                                           |

| PTI:        | Plaintext Input                                     |

| PTO:        | Plaintext Output                                    |

| RAM:        | Random Access Memory                                |

| RC:         | Resistor-Capacitor oscillator                       |

| Rcon:       | Remote Constant (in AES)                            |

| RCU:        | Reconfiguration Control Unit                        |

| RD:         | Read                                                |

| RK:         | Round Key                                           |

| RM:         | Reconfigurable Module                               |

| ROL:        | Rotation to Left                                    |

| ROM:    | Read-Only Memory                    |

|---------|-------------------------------------|

| RP:     | Reconfiguration Port                |

| RSA:    | Rivest Shamir Adleman algorithm     |

| SB:     | SubBytes operation (in AES)         |

| SCA:    | Side-Channel Attack                 |

| SCC:    | Single Chip Crypto                  |

| SHA:    | Secure Hash Algorithm               |

| SK:     | Session Key (in general)            |

| SKF:    | Secure Key Flash                    |

| SL:     | Shift to Left (in DES)              |

| SoC:    | System on Chip                      |

| SPA:    | Simple Power Analysis               |

| SPP:    | Specific-Purpose Processor          |

| SR:     | Shift Rows (in AES)                 |

| SRAM:   | Static RAM                          |

| STS:    | Station-to-Station protocol         |

| TBM:    | Trusted Bus Macro                   |

| TDEA:   | Triple Data Encryption Algorithm    |

| TDPRAM: | True Dual Port RAM                  |

| TE:     | Trusted Entity                      |

| TERO:   | Transition Effect Ring Oscillator   |

| TOE:    | Target Of Evaluation (in CC)        |

| TPM:    | Trusted Platform Module             |

| TRNG:   | True Random Number Generator        |

| USB:    | Universal Serial Bus                |

| VHDL:   | VHSIC Hardware Description Language |

| VHSIC:  | Very-High-Speed Integrated Circuit  |

| WR:     | Write                               |

| VLIW:   | Very Long Instruction Word          |

| XOR:    | Exclusive OR                        |

#### 1.1 Flexible Security and Hardware Implementations

Nowadays, demands of data security are increasing, especially after introduction of wireless communications to the masses. Technologies like WIFI, Bluetooth, UMTS,... are all widely used. Moreover, usage of portable devices is skyrocketing. Particularly, in this lucrative market sector combination of reconfigurable, low power logic solution with embedded crypto-processor (hardware accelerator) and random number generator are extremely attractive. Furthermore, if being able to guarantee security on physical implementation level (concept of the black/red zone separation) as well as other countermeasure techniques, these solutions can surpass ordinary consumer electronics application to be used in avionics, automotive and military applications featuring higher security needs.

Hardware cryptographic systems must fulfill contradictory requirements: fast parallel structures implementing computationally extensive cryptographic functions must coexist with complex sequential structures used to implement cryptographic algorithms such as cipher modes, key management operations and cryptographic protocols. Implementation of cryptographic algorithms and protocols in hardware necessitates employing many complex state machines that make the logic vulnerable. Furthermore, upgrades of hardwired logic can become complicated, long and expensive. On the other hand, security of the system itself and protection of confidential data is often underestimated.

The most common solution consists in the use of a general-purpose processor employing one or more cryptographic coprocessors. This solution permits to implement sequential algorithms (that evolve very frequently as a consequence of attacks and/or evolution of standards) by the processor program, while the tasks that can be executed in parallel are implemented in the coprocessor placed inside the same logic device. However, this solution brings some difficulties concerning the system security: first, the general-purpose processor manipulates the keys as ordinary data and modification (intentional or unintentional) of the program memory contents can enable reading the keys in clear outside the system; second, the use of generalpurpose processors does not permit to isolate efficiently the red (unprotected) and black (protected) communication zones inside the device.

One problem concerning the use of a general-purpose processor in cryptographic applications is related to the speed limitation caused by the bus width: data and bus size (usually 32 bits) limits considerably the performance of the system. Another problem related to the use of general-purpose processors in cryptographic systems and their speed concerns the complexity of the instruction set: processors aimed at cryptographic applications (completed by cryptographic coprocessors) do not need a complex instruction set that is necessary in general-purpose processors and optimization (minimization) of the instruction set could increase the speed of the system. The design of dedicated processors with dedicated instruction set is especially interesting in the case of emerging application areas based on Multi-Processor System-on-Chip (MPSoC).

#### 1.2 Objectives of the Thesis

In order to fulfill aforementioned, often contradictory, requirements on the cryptographic system, French National Research Agency (ANR) founded the Secured Reconfigurable System on Chip project (SecReSoC) proposed by the Secure Embedded Systems research team of the Hubert Curien Laboratory. The aim of SecReSoC was to examine security aspects of MPSoC, and to demonstrate the final MPSoC system implemented in a Field Programmable Gate Array (FPGA). The work presented in this thesis is done in the framework of the SecReSoC project, and its objectives were defined as follows:

- 1. Propose a new architecture of the crypto-processor that includes cipher block as an independent module and that allows secure separation of data and key registers.

- 2. Optimize the architecture of the Arithmetic Logic Unit (ALU) for operations used by cryptographic protocols and cipher modes.

- 3. Propose an instruction set providing separate data and key processing.

- 4. Propose at least one version of the cipher core including countermeasures against side-channel attacks.

- 5. Propose some efficient solution enabling easy adaptation of the assembler to the modification/evolution of the instruction set.

- 6. Integrate all elements necessary for secure programming and reconfiguration into the structure of the crypto-processor.

- 7. Evaluate the security level of the proposed crypto-processor.

#### 1.3 Contribution

The thesis not only achieves all aforementioned objectives, but also proposes novel principles, design rules and architectures enabling secure key management on cryptographic processors or even general-purpose processors (extended with secure cryptographic coprocessors). The developed cryptographic processors (further just cryptoprocessors) and cryptographic coprocessors (further just crypto-coprocessors) can be directly used in practice. A part of the research work is also dedicated to countermeasures against side-channel attacks and protection of a totally or partially reconfigurable system. This work does not propose partial solutions, but its outcome is a fully functional and tested HCrypt cryptographic processor and HCrypt-C cryptographic coprocessor in many variations focused on a specific objective.

Every specific problem in this research work is preceded by an extensive study of the state-of-the-art work which is summarized in every chapter of this thesis.

#### 1.4 Thesis Preview

The manuscript describes the work progress during the thesis in chronological order. Chap. 3–6 constitute the core of the research work.

The objective of Chap. 2 is to introduce the theoretical background which is essential for further understanding of the thesis. First, basic cryptography objectives for secure communications are listed. Next, most important symmetric key cryptographic algorithms (i.e. DES, AES, block cipher modes, etc.) are described, followed by hash functions and random number generators. Subsequently, key management, assumed participating parties and all involved security threats are presented. Consequently, important key establishment schemes are briefly introduced and compared. The second part of Chap. 2 is dedicated to FPGAs and corresponding advanced design flows.

Chap. 3 starts by summarizing the state-of-the-art related to cryptographic processors. Security issues of cryptographic software implementations are discussed first, followed by overview on cryptographic hardware architectures. Further, novel separation rules for secure key management are presented. These rules are implemented on original HCrypt crypto-processor. Subsequently, its hardware and software design, and communication protocol is described, followed by simulations, and hardware tests. Finally, HCrypt properties and implementation results are discussed.

Chap. 4 is oriented on cryptographic coprocessors with secure key management. After introducing the work that has been conducted in the study of cryptocoprocessors, slight modifications of separation rules for crypto-coprocessors are proposed. These separation rules are applied on the HCrypt-C crypto-coprocessor. Subsequently, most common interface topologies for interconnection of a coprocessor to a general-purpose processor are described. Next, three different general-purpose processors are extended by HCrypt-C and their design and results are given.

Side-channel analysis attack (SCA) threat is considered in Chap. 5. After introducing state-of-the-art in hardware attacks, an extensive security analysis of the AES cipher and HCrypt is given. The HCrypt security analysis uncovers security vulnerabilities when considering SCA, and so the HCrypt2 crypto-processor is designed. HCrypt2 implements new countermeasures (zero-cost countermeasures). The HCrypt2 security analysis confirms increased robustness to SCA. HCrypt2 design and results are presented and evaluated. Chap. 6 contemplates an FPGA-specific advanced technique – partial reconfiguration flow. First, reasons for using this technique are discussed. Next, the work that has been done in the field of partially reconfigurable system is presented. Subsequently, separation rules in conjunction with partial reconfiguration are given. A total and partial reconfiguration of an FPGA and corresponding security implications are discussed. Finally, a partially reconfigurable HCrypt-C crypto-coprocessor is described and tested using three different partial configurations.

Finally, Chap. 7 summarizes all important contributions, proposals and conclusions. It also presents new challenges and perspectives that can be a subject of future studies.

# Chapter 2 Theoretical and Technological Background

#### Contents

| 2.1 | Secu           | re Communications                                           | 6         |

|-----|----------------|-------------------------------------------------------------|-----------|

| 2.2 | $\mathbf{Sym}$ | metric Key Cryptography                                     | 7         |

|     | 2.2.1          | Block Ciphers                                               | 7         |

|     | 2.2.2          | Stream Ciphers                                              | 16        |

| 2.3 | Hasl           | h Functions                                                 | <b>17</b> |

|     | 2.3.1          | MD5 Hash Function                                           | 18        |

| 2.4 | $\mathbf{Gen}$ | eration of Random Numbers                                   | <b>18</b> |

|     | 2.4.1          | Hardware Random Number Generators                           | 20        |

|     | 2.4.2          | LFSR-based PRNG                                             | 21        |

|     | 2.4.3          | PLL-based TRNG                                              | 21        |

| 2.5 | Key            | Management                                                  | <b>22</b> |

|     | 2.5.1          | Security Levels and Key Management                          | 24        |

|     | 2.5.2          | Participating Parties                                       | 26        |

|     | 2.5.3          | Threat Model                                                | 26        |

|     | 2.5.4          | Key Establishment Protocols                                 | 27        |

| 2.6 | Imp            | lementation of Cryptographic Hardware in FPGAs              | 29        |

|     | 2.6.1          | Field-Programmable Gate Arrays (FPGAs)                      | 29        |

|     | 2.6.2          | Development of Hardware Functions for FPGAs $\ . \ . \ .$ . | 30        |

|     | 2.6.3          | FPGA Classes and Families                                   | 31        |

|     | 2.6.4          | Technology Limits                                           | 32        |

|     | 2.6.5          | Isolation Design Flow in Xilinx FPGAs                       | 32        |

| 2.7 | Part           | ial Hardware Reconfiguration and Security                   | 33        |

|     | 2.7.1          | Partial Reconfiguration                                     | 33        |

|     | 2.7.2          | Security Aspects of the Partial Reconfiguration             | 34        |

This chapter introduces basic knowledge concerning cryptography for secure communications, FPGA technology and advanced design flows. It is necessary for better understanding of the following parts of the manuscript.

#### 2.1 Secure Communications

In general, secure communication can be achieved by two methods: 1) steganography 2) cryptography. Steganography exploits different methods for hiding a secret message inside an insecure message. The secret message can be hidden in digital data like images, videos, music, etc. On the contrary, cryptography does not try to hide the secret message (plaintext) from the attacker, but rather to transform it to a meaningless message (ciphertext) using a key. This transformation is performed by a cipher. Only the owner of the key can transform the ciphertext message back to its plaintext version. The attacker, however, may have knowledge of the ciphering algorithm and try to recover the confidential key or the plaintext using cryptanalysis. For this reason, security should not be based on the confidentiality of the ciphering algorithm, but only on the confidentiality of the key. This Kerckhoffs's principle has a practical reason, because it is easier to change the confidential key than to redesign the ciphering algorithm in case of their disclosure.

Different objectives have been defined for cryptography [4], [5], [6]. The following are the four cryptography objectives defined by Menezes et al. [3]:

- 1. Confidentiality is a service used to keep the content of information from all but those authorized to have it. Secrecy is a term synonymous with confidentiality and privacy. There are numerous approaches to providing confidentiality, ranging from physical protection to mathematical algorithms which render data unintelligible.

- 2. Data integrity is a service which addresses the unauthorized alteration of data. To assure data integrity, one must have the ability to detect data manipulation by unauthorized parties. Data manipulation includes such things as insertion, deletion, and substitution.

- **3.** Authentication is a service related to identification. This function applies to both entities and information itself. Two parties entering into a communication should identify each other. Information delivered over a channel should be authenticated as to origin, date of origin, data content, time sent, etc. For these reasons this aspect of cryptography is usually subdivided into two major classes: entity authentication and data origin authentication. Data origin authentication implicitly provides data integrity (for if a message is modified, the source has changed).

- 4. Non-repudiation is a service which prevents an entity from denying previous commitments or actions. When disputes arise due to an entity denying that certain actions were taken, a means to resolve the situation is necessary. For example, one entity may authorize the purchase of property by another entity and later deny such authorization was granted. A procedure involving a trusted third party is needed to resolve the dispute.

This work is focused especially on secure key management in logic devices. The confidential keys are essential piece of information for many cryptographic primitives and algorithms for fulfilling the described four objectives of cryptography. Next, we describe the cryptographic primitives, algorithms and protocols that are necessary for better understanding of this work.

#### 2.2 Symmetric Key Cryptography

The symmetric key cryptography utilizes the same key for both encryption and decryption. Contrary to the symmetric key cryptography, the asymmetric key cryptography is based on two different keys. One key is confidential and is called private and the second is freely distributed and is called public. This work concerns only the symmetric key cryptography and so the asymmetric key cryptography will not be further considered.

The use of the symmetric key cryptography in military dates back to the Roman empire when the emperor Julius Caesar used a special cipher for his private correspondence. The Caesar cipher is very simple. Each letter in the message has to be substituted by another letter shifted in the alphabet by 3 letters.

Before the digital era, the cryptographic algorithms operated on letters. The digital era allowed to encode any piece of information by a set of bits, and so the ciphering started to be performed on bits. The ciphers that operate on an infinitely long bit sequence are called stream ciphers. The opposite are the block ciphers which operate on a constant number of bits (blocks).

#### 2.2.1 Block Ciphers

Block ciphers can be divided into two classes: substitution ciphers and transposition ciphers.

The substitution ciphers replace the symbols by other symbols using some algorithm or substitution tables. Substitution tables may be defined by the ciphering algorithm or calculated from the key. The Caesar cipher is a typical substitution cipher. The transposition ciphers are rather based on changing the order of symbols in the block (symbol permutations) according to some key-dependent algorithm. Substitution or transpositions ciphers do not provide sufficient security. However, if the two are combined together they can provide a very high level of security.

Two important properties of the block ciphers are confusion and diffusion. Confusion makes the relationship between the plaintext and ciphertext as complex as possible. The substitution operation significantly increases confusion. To achieve high confusion, the substitution transformation should be non-linear. A unit performing substitution is called S-box. Diffusion, however, spreads or rearranges the plaintext bits over the ciphertext. This way any redundancy in the plaintext can be effectively spread out (diffused) over the ciphertext. Diffusion can be increased by transposition operation. Operations used in modern ciphers can be categorized as those increasing confusion or diffusion.

Next, some modern standardized ciphering algorithms will presented.

#### 2.2.1.1 Data Encryption Standard (DES)

The Data Encryption Standard (DES) was developed in the 1970s by IBM in cooperation with the National Security Agency (NSA) of the USA and published as the Federal Information Processing Standard 46 (FIPS-46) [7]. DES is based on another cipher developed by Horst Feistel. For this reason, DES is based on the so called Feistel scheme.

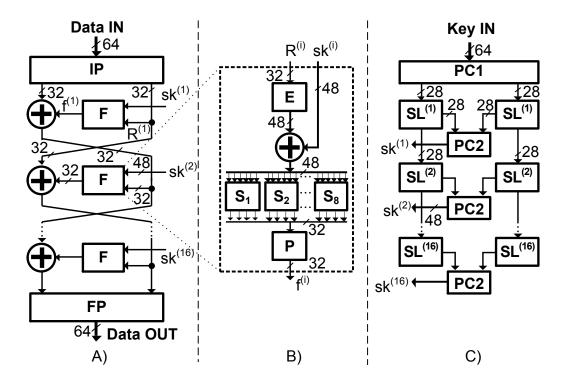

DES is a block cipher which uses a 56-bit long symmetric key and operates on 64-bit data blocks. The transformation of a plaintext block to a ciphertext block is performed in 16 rounds. The structure of the DES cipher is depicted in Fig. 2.1. First, a 64-bit data block is transformed into two 32-bit state words by Initial Permutation (IP). The less significant 32-bit word (right word) passes directly to the next round to the left word position. The more significant 32-bit word (left word) is XOR-ed with the output of the F-function (see the part B in Fig. 2.1) and the result passes into the next round to the right word position. This algorithm is repeated for every round except the last round where the two words are not swapped. Finally, the last two 32-bit words in the last round are transformed into the ciphertext by the Final Permutation (FP).

The structure of the F-function is illustrated in the part B in Fig. 2.1. The F-function loads a 48-bit subkey (SK) and a 32-bit right state word (R). In order to match two bus widths, the 32-bit state word is expanded into 48-bits by the Expansion permutation (E) by duplicating half of the bits. The expanded value is added with the subkey and the resulting 48-bit word enters the substitution part. The substitution function is represented by eight different parallel substitution blocks (S-boxes). Each S-box substitutes six bits with four bits. The resulting substituted values form a 32-bit word which is subsequently transformed by the Permutation (P) to form an output of the F-function. S-boxes together with E and P permutations contribute to high confusion and diffusion, respectively.

48-bit subkeys are generated by the key expansion function (see the part C in Fig. 2.1). Although a 64-bit secret key word enters the key expansion function, 8 bits are removed by the Permutation Choice 1 (PC1) forming a 56-bit secret key divided into two 28-bit halves. These halves are further processes separately. Each half is shifted to left (SL) by one or two bits (depends on the round). The two shifted words are processed by the Permutation Choice 2 (PC2) generating a 48-bit subkey.

The DES deciphering operation uses the same round structure. The only difference is that subkeys are used in reversed order, i.e., subkeys  $sk^{(16)}$ ,  $sk^{(15)}$ , ...,  $sk^{(2)}$ ,  $sk^{(1)}$  are used in rounds 1, 2, ..., 15, 16, respectively. More details about DES cipher can be found in the FIPS-46 standard [7].

#### 2.2.1.2 Triple DES

DES was proved to be vulnerable and feasible attacks were demonstrated in 90-ties. For this reason, the FIPS-46 standard was expanded with a so called Triple Data Encryption Algorithm (TDEA).

Figure 2.1: Structure of the Data Encryption Standard cipher (DES)

TDEA uses three DES ciphers connected in series. The ciphertext (CT) can be obtained from plaintext (PT) as follows:  $CT = E_{K_3}(D_{K_2}(E_{K_1}(PT)))$ . The decryption can be performed as follows:  $PT = D_{K_1}(E_{K_2}(D_{K_3}(CT)))$ . E represents a DES encryption operation while D represents a DES decryption operation.  $K_1, K_2$ and  $K_3$  represent three 56-bit secret keys which can be either independent (TDEA option 1),  $K_1 = K_3$  are independent from  $K_2$  (TDEA option 2), or all three keys are identical (TDEA option 3).

The TDEA option 1 is the strongest because the effective key length reaches 168 bits, followed by options 2 and 3. Unfortunately, TDEA operates with 48 rounds (three ciphers per 16 rounds) which can significantly decrease performance if a pipeline implementation is not possible.

#### 2.2.1.3 Advanced Encryption Standard (AES)

Although the TDEA was not broken and was accepted as a standard in FIPS-46-3 [7], successful attacks on DES initiated a search for a new encryption standard. The Rijndael cipher was selected in a competition for Advanced Encryption Standard (AES) and standardized in 2001 as Federal Information Processing Standard 197 (FIPS-197) [8]. Nowadays, only AES is considered as sufficiently secure and recommended for data protection.

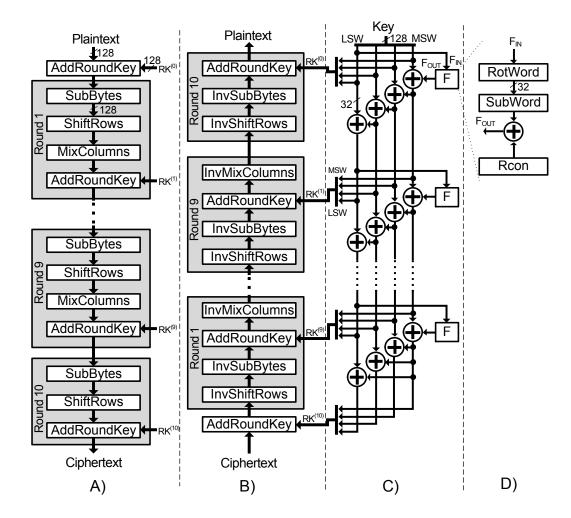

The structure of AES with a 128-bit key is depicted in Fig. 2.2 (for details on longer key versions see FIPS-197[8]). The ciphering is carried out in 11 rounds.

Data enters the cipher in 128-bit blocks. Each block is divided into 16 bytes  $(in_0, in_1, \ldots, in_{15})$ . The internal state of the cipher can be described by a matrix consisting of four rows and four columns as shown in Fig. 2.3. Four bytes of each column form a 32-bit word. The resulting data are organized 128-bit blocks.

The encryption algorithm uses four main operations that are applied on the state array: SubBytes, ShiftRows, MixColumns and AddRoundKey. The SubBytes transformation substitutes each byte in the state array with a different byte according to a substitution table (S-box tables can be found in the standard [8]). ShiftRows performs byte transposition of the state array as illustrated in Fig. 2.4. The Mix-Columns transformation operates on 32-bit words in columns ( $w_0, w_1, w_2, w_3$ ). Mix-Columns performs a modular multiplication of a state word, expressed in a polynomial form s(x), with a constant polynomial  $a(x) = \{03_{16}\}x^3 + \{01_{16}\}x^2 + \{01_{16}\}x + \{02_{16}\}$ . More details on the modular multiplication can be found in [8]. The AddRoundKey operation is very simple, because it performs only bit-wise XOR operation between state bits and round key bits.