# Intégration 3D de nanofils Si-SiGe pour la réalisation de transistors verticaux 3D à canal nanofil

Guillaume Rosaz

# ▶ To cite this version:

Guillaume Rosaz. Intégration 3D de nanofils Si-SiGe pour la réalisation de transistors verticaux 3D à canal nanofil. Autre. Université de Grenoble, 2012. Français. NNT: 2012GRENT108. tel-00981971

# HAL Id: tel-00981971 https://theses.hal.science/tel-00981971

Submitted on 23 Apr 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité: NANO ELECTRONIQUE ET NANO TECHNOLOGIES

Arrêté ministériel : 7 août 2006

Présentée par

# **Guillaume ROSAZ**

Thèse dirigée par **Thierry BARON** coencadrée par **Bassem SALEM** et **Nicolas PAUC**

préparée au sein du Laboratoire des Technologies de la Microélectronique (CNRS) et du Laboratoire Silicium, Nanoélectronique, Photonique et Structures (CEA-INAC-SP2M)

dans l'École Doctorale EEATS

# Intégration 3D de nanofils Si et SiGe pour la réalisation de transistors verticaux à canal nanofil.

Thèse soutenue publiquement le **11 décembre 2012** devant le jury composé de :

Dr, Gérard, GHIBAUDO

Directeur de recherche, IMEP/LAHC, Grenoble, Président

Pr, Jean-Luc, AUTRAN

Professeur, IM2NP, Marseille, Rapporteur

Dr, Emmanuel, DUBOIS

Directeur de recherche, IEMN, Villeneuve d'Ascq, Rapporteur

Dr, Guilhem, LARRIEU

Chargé de recherche, LAAS, Toulouse, Examinateur

Dr. Jean-Louis, LECLERCQ

Chargé de recherche, Ecole centrale de Lyon, Examinateur

Dr, Thierry, BARON

Directeur de recherche, LTM, Grenoble, Directeur de thèse

Dr, Bassem, SALEM

Chargé de recherche, LTM, Grenoble, Encadrant de thèse

Dr, Nicolas, PAUC

Ingénieur CEA, INAC/SiNaPS, Grenoble, Co-encadrant de thèse

« Anything that can go wrong, will go wrong » Edward A. Murphy Jr.

# Remerciements

Voici la fin de trois années mémorables passées au sein du LTM et de SiNaPS. Que de monde rencontré en trois ans. Si vous lisez ces quelques lignes vous en faites certainement partie. D'avance je m'excuse auprès de celles et ceux que j'aurais pu oublier dans ce petit billet.

Il est avant tout quatre personnes que je souhaiterais remercier pour m'avoir accompagné durant ce travail. Grâce à eux ma thèse se sera déroulé dans des conditions que l'on peut qualifier d'optimales.

Thierry BARON: Quelle était la probabilité d'avoir un directeur de thèse issu de ma Savoie natale et qui plus est originaire d'un village voisin? Tu as a été un incroyable directeur de thèse, toujours présent et accessible. J'ai grandement apprécié ta franchise, ton honnêteté et ta rigueur scientifique. Tu as très souvent mis la main à la pâte pour la préparation de mes échantillons parfois à des horaires plus que matinaux et pour cela je te remercie infiniment. Tu as su te rendre disponible malgré ton emploi du temps plus que chargé et cela a été un véritable plaisir de pouvoir travailler ensemble. Bonne continuation pour les futures thématiques de recherche et encore merci.

Nicolas PAUC: Un encadrant de thèse exceptionnel. Il est rare de pouvoir travailler avec des gens ayant une rigueur et un niveau scientifique comme les tiens. Tu m'as toujours soutenu dans mes initiatives et poussé à obtenir le meilleur de moi-même. Je te remercie d'avoir toujours cru en moi notamment de m'avoir soutenu malgré les débuts difficiles du fait de la complexité de la thématique. Merci pour tout et bonne continuation en espérant pouvoir collaborer avec toi dans le futur, on ne sait jamais...

Bassem SALEM: C'est officiel ton premier thésard a fini, je laisse donc la place aux suivant(e)s. J'aurais passé trois excellentes années sous ta supervision. Tu as été un encadrant hors-pair. J'ai pris énormément de plaisir à travailler avec toi. Tu as toujours tout fait pour que je puisse avoir accès au matériel nécessaire au bon déroulement de ce projet et cela a porté ses fruits. Je ne compte plus temps que nous avons passé à la PTA pour développer notre procédé d'intégration de nanofils. J'ai hâte de pouvoir reprendre une de nos discussions autour d'une shisha à St Bruno à refaire le monde mais également à discuter de nos recherches. J'ai vraiment apprécié le fait que tu m'ais toujours poussé vers l'avant notamment en ce qui concerne la publication d'articles...(au passage bon courage à Virginie, la pression va être forte :) ). Malgré le temps nécessaire à l'obtention des premiers résultats sur le 3D tu n'as jamais désespéré et tu m'as toujours fait confiance et soutenu dans mes propositions d'amélioration des procédés de fabrication. Merci pour tout en espérant pouvoir retravailler ensemble dans le futur.

Pascal GENTILE: Tu as investi beaucoup de temps dans le perfectionnement des recettes de croissance de nanofils verticaux malgré les nombreux autres projets auxquels tu étais lié. Grâce à toi j'ai pu disposer d'une base solide pour élaborer mes transistors. Je tiens véritablement à te remercier pour avoir investi autant d'énergie dans ce projet complexe et d'avoir permis d'en faire une belle réussite.

Je remercie également vivement tous les membres du jury Gérard GHIBAUDO, Jean-Luc AUTRAN, Emmanuel DUBOIS, Guilhem LARRIEU et Jean-Louis LECLERCQ qui ont accepté de prendre part à l'évaluation

de ce travail de thèse. Merci à eux pour leurs commentaires constructifs et pour le temps passé à la lecture du manuscript.

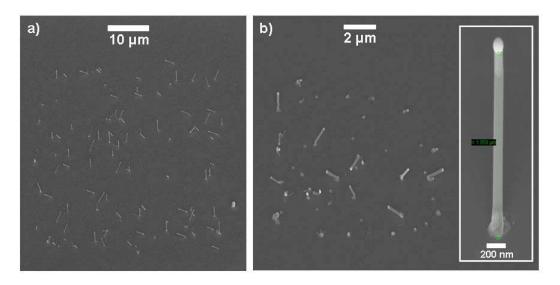

Il y a également ces thésard(e)s sans qui ce travail n'aurait jamais pu aboutir. Je pense en particulier à Alexis POTIE, Priyanka PERIWAL, Ludovic DUPRE, Fabrice OEHLER, Florian DALLUHIN. Florian et Fabrice ont dépoussiéré la difficile problématique de la croissance des nanofils. Alexis, Ludovic et Priyanka ont été mes fournisseurs officiels de nanofils et sans eux je n'aurais jamais pu mener à bien ce projet. Merci à vous pour avoir réalisé tout le travail amont indispensable à l'aboutissement de cette thèse. Je vous souhaite bien évidemment, pour ceux qui ont encore un peu de chemin à faire avant la soutenance, de vous épanouir durant la fin de votre thèse.

Je n'oublie pas non plus le personnel de la PTA sans qui je n'aurais jamais pu réaliser ce travail. Je pense particulièrement à : Jean-Luc THOMASSIN, Thibault HACCART, Helge HAAS, Marlène TERRIER, Marie PANNABIERE, Christophe LEMONIAS, Delphine CONSTANTIN, Perrine CAGNEAUX, (JB je ne t'oublies pas mais tu auras droit à quelques lignes un peu plus loin)... A vous tous un grand merci!!!

Un grand merci également à Malou, Sylvaine CETRA, Stéphanie BERGER et Leila CHAPPE pour avoir géré tous les aspects administratifs, commandes et autres procédures dont la lourde mécanique m'échappe encore. Vous facilitez la vie des thésards et de tous les autres membres du LTM avec une remarquable efficacité. Encore merci.

Je tenais également à remercier Jean-Baptiste JAGER. Je ne remercierai jamais assez d'avoir toujours tout mis en œuvre pour maintenir cette STS en état de marche, ceux qui connaissent la bête savent que c'est une rude tâche. Cela aura été un grand plaisir de discuter process et de partager le café à SiNaPS. Je te souhaite le meilleur pour la suite de ta carrière au CEA.

Merci aussi à Éric DELAMADELAINE qui trouvent sans cesse des idées originales pour améliorer les équipements de faciliter ainsi la vie des thésards de SiNaPS.

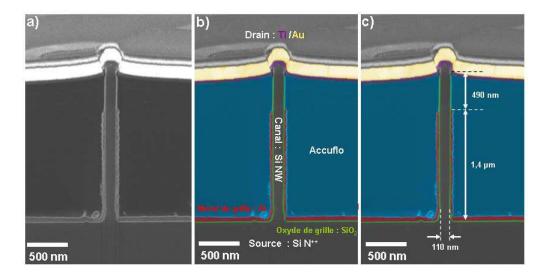

Je souhaite aussi adresser mes remerciements à Sylvain DAVID et Laurence LATU-ROMAIN pour avoir réalisé les coupes FIB et observations TEM sur mes échantillons. Ces manips, très lourdes techniquement, m'auront permis d'avoir accès à des informations menant à une meilleur compréhension de mes dispositifs. Merci beaucoup à vous deux.

Un grand merci à Quentin BALG (Benoît à la Guillaume pour les intimes) pour m'avoir fait découvrir ce superbe logiciel qu'est Blender et m'avoir ainsi permis de m'affranchir de cette horreur de powerpoint... merci également à toi pour ta constante bonne humeur. Bon courage pour la fin de thèse et à très bientôt je l'espère pour pouvoir déguster à nouveau tes bières maison.

Thanks a lot to Amit SOLANKI. Your advices about devices fabrication and characterization were really useful to me. I wish you the best for your career.

Je remercie bien évidemment Olivier JOUBERT et Emmanuel HADJI pour m'avoir accueilli au sein de leurs laboratoires afin de réaliser cette thèse.

Je tiens évidemment à remercier l'ensemble du LTM et de SiNaPS. Tout d'abord les thésard(e)s, Claude RENAUT, Cédric MANNEQUIN, Salomé TALLEGAS, Thérèse GORISSE, Pierre DELCROIX, Amit SOLANKI, Romain HURAND, Olivier DEMICHEL, Maelig OLLIVIER, John POINTET, Laurent AZARNOUCHE, Sébastien AVERTIN, Thomas BERTAUD, Emmanuel GOURVEST, Paul BODART, Romuald BLANC mais également les permanents, post-docs et autres de chaque labo: Martin KOGELSCHATZ, Marc ZELSMANN, Erwine PARGON, Gilles CUNGE, Emmanuel PICARD, Denis BUTTARD et tous ceux que j'ai pu croiser au sein des deux laboratoires pendant ces deux années.

Enfin il est des personnes que je ne saurais oublier. Tout d'abord mes parents, Gilles et Alix. Sans vous bien

évidemment rien de tout cela n'aurait été possible. Vous m'avez soutenu tout le long de mes études tant dans les bons que les mauvais moments. Je vous serai toujours reconnaissant.

Mes deux grands decapadiots de frangins, Yannick et Jean-Baptiste. Merci à vous deux de m'avoir également soutenu et supporté. Merci aussi de m'avoir changé les idées grâce à nos sorties grimpe, ski et rando.

Enfin un grand merci à Brunilde qui m'aura apporté son soutien pendant les deux dernières années de thèse. Merci à toi pour ta patience et je sais que cela n'aura pas toujours été facile. Merci également de m'avoir supporté et aidé lorsque le stress était au maximum pendant les confs ou même la veille de la soutenance.

# Introduction générale

La miniaturisation des transistors a permis depuis plus de cinquante ans d'augmenter considérablement les performances des circuits intégrés en intégrant de plus en plus de transistors au sein d'une même puce. Mais à l'heure actuelle, au-delà des performances, le grand public a des demandes très spécifiques qui se sont révélées avec le marché des smartphones. Ainsi les clients veulent pouvoir disposer d'un appareil portable permettant de téléphoner, enregistrer de la vidéo, prendre des photos ou même transmettre des données via des réseaux sans fils. Atteindre un tel niveau de fonctionnalités avec un seul appareil n'a été rendu possible qu'avec l'avènement des Systèmes-sur-Puces (SoC). Ces SoC sont en fait des micropuces rassemblant une très grande variété de composants tel que du numérique, de l'analogique, de la RF et même des capteurs. Pour réaliser ces puces chaque sous partie est réalisée indépendamment puis le tout est assemblé par collage et interconnecté. Cela pour la simple raison qu'il est à l'heure actuelle impossible de réaliser directement les étapes technologiques sur la même puce. En effet, la fabrication des circuits commence par le front-end, la région qui contient les transistors de haute performance. Ces transistors sont réalisés sur un substrat cristallin de silicium afin d'avoir des propriétés électroniques maximales. Ensuite vient le niveau du back-end qui consiste en un empilement de lignes métalliques destinées à interconnecter tous ces transistors. Les étapes back-end ne doivent en aucun cas nuire au fonctionnement des transistors du front-end et pour cela une limite thermique appelée "budget thermique" a été fixée à 450°C, température au delà de laquelle les métaux utilisés pour les contacts des transistors risquent de diffuser et ainsi de modifier leur comportement. L'obtention d'un cristal de silicium n'étant pas possible en dessous de 450°C, l'empilement de composant nécessite donc de fabriquer plusieurs puces à part et ensuite à les assembler.

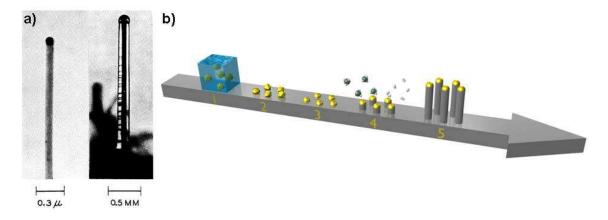

Nous proposons dans cette thèse d'utiliser une approche dite de croissance Vapeur-Liquide-Solide (VLS) permettant de synthétiser un monocristal à partir d'un catalyseur métallique et à basse température (<450°C). Cette croissance permet de fabriquer des structures tridimensionnelles appelées nanofils dont le diamètre est inférieur à 100 nm et la longueur pouvant atteindre plusieurs centaines de micromètres. L'idée ici est de démontrer qu'il est possible d'utiliser ces nanofils comme canaux de conduction dans des transistors à effet de champ tout en respectant le budget thermique imposé dans le back-end. Cela permettrait donc à terme de pouvoir directement réaliser des composants actifs dans les étapes back-end sans avoir à procéder à des étapes de collage de puces.

# Abstract

For the last fifty years the integrated circuits (ICs) performances have been increased thanks to the transistors' size miniaturization leading to a higher density of these components on every single chip. Nowadays the customers have specific queries beyond the performances which have been revealed with the smartphones market. They want a phone allowing communications, recording videos, having a camera and even able to transmit datas through wireless networks. Reaching such a level of functionnalities in a single device hase only been possible with the development of the Systems-on-Chip (SoC). These SoC are microchip wich concentrate a wide variety of components such as digital, analogical, RF and even sensors. In order to fabricate these chips every under parts are built independently and then assembled by bonding and interconnected. The reason of such a complicated way of fabrication is hat it is impossible to directly achieve all the technological steps on the same chip. Indeed, ICs fabrication starts with the front-end part which contains the high performance transistors. These transistors are elaborated on acristalline silicon substrate in order to have optimum electrical properties. Then comes the back-end level which is made of a stack of multiple metallic line dedicated to the transistors interconnections. The back-end steps have to preserve the electrical properties of front-end transistors and for this a thermal limite defined as "thermal budget" has been set to 450°C. Above this temperature the metals used to realize the transistors contacts may diffuse and modify their behaviour. The synthesis of a silicon cristal being impossible below 450°C the components stacking requires to build multiple dyes and to assemble them together in a final step.

We propose in this thesis to use an approach called the Vapor-Liquid-Solid (VLS) mechanism allowing to synthesize a monocristal using a metal catalyst at low temperature (<450°C). This process allows to grow tridimensionnal nanostructures called nanowires whose diameter is below 100 nm and length can reach few hundred of micrometers. The idea is to demonstrate the possibility to use these nanowires as conduction channel in field-effect transistors while respecting the back-end thermal budget. This could lead to a direct fabrication of active components in the back-end steps without any bonding requirement.

# Table des matières

| 1 | $\mathbf{D}\mathbf{u}$ | MOSI   | ET aux nanofils                                                                          | . 1 |

|---|------------------------|--------|------------------------------------------------------------------------------------------|-----|

|   | 1.1                    | Introd | ${ m ction}$                                                                             | 11  |

|   | 1.2                    | Le tra | sistor à effet de champ                                                                  | 11  |

|   |                        | 1.2.1  | Historique                                                                               | 11  |

|   |                        | 1.2.2  | Structure d'un transistor à effet de champ                                               | 12  |

|   |                        |        | 1.2.2.1 Capacité MOS idéale                                                              | 12  |

|   |                        |        | 1.2.2.2 Capacité MOS réelle                                                              | 13  |

|   |                        |        | 1.2.2.3 Le MOSFET                                                                        | 14  |

|   | 1.3                    | Archit | cture d'un circuit intégré                                                               | 18  |

|   |                        | 1.3.1  | Le Front End: zone active                                                                | 19  |

|   |                        | 1.3.2  | Le Back End : zone froide                                                                | 19  |

|   | 1.4                    | Accro  | sement des performances des IC's                                                         | 20  |

|   |                        | 1.4.1  | Approche "More Moore"                                                                    | 21  |

|   |                        | 1.4.2  | Approche "More-Than-Moore"                                                               | 22  |

|   |                        |        | 1.4.2.1 Collage                                                                          | 23  |

|   |                        |        | 1.4.2.2 L'élaboration directe                                                            | 24  |

|   | 1.5                    | Un tra | nsistor dans le back end : le SBFET (Schottky barrier field-effect transistor)           | 25  |

|   |                        | 1.5.1  | La barrière Schottky : électrostatique                                                   | 25  |

|   |                        | 1.5.2  | Mécanismes de transport dans un contact Métal/Semi-conducteur                            | 27  |

|   |                        |        | 1.5.2.1 Émission thermo-ionique                                                          | 28  |

|   |                        |        | 1.5.2.2 Théorie de la diffusion                                                          | 29  |

|   |                        |        | 1.5.2.3 Théorie de l'émission thermoionique-diffusion                                    | 29  |

|   |                        |        | 1.5.2.4 Émission par effet de champ et émission thermo-ionique assistée par champ . $$ 3 | 30  |

|   |                        | 1.5.3  | Intérêt du SBFET                                                                         | 31  |

|   | 1.6                    | Les na | ofils semi-conducteurs                                                                   | 32  |

|   |                        | 1.6.1  | Définition                                                                               | 32  |

|   |                        | 1.6.2  | Élaboration                                                                              | 32  |

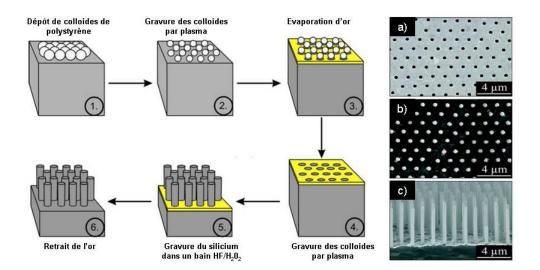

|   |                        |        | 1.6.2.1 Approche descendante                                                             | 33  |

|   |                        |        | 1.6.2.2 Approche ascendante                                                              | 34  |

|   |     |         | 1.6.2.3    | L'épitaxie par jets moléculaires                           | 35 |

|---|-----|---------|------------|------------------------------------------------------------|----|

|   |     |         | 1.6.2.4    | Le dépôt chimique en phase vapeur                          | 36 |

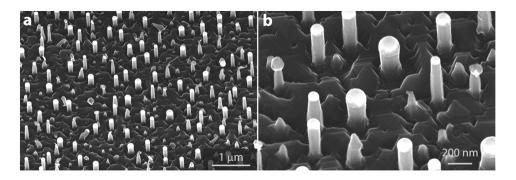

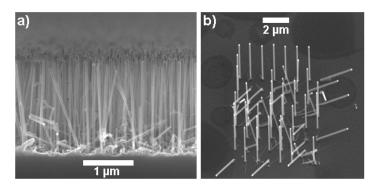

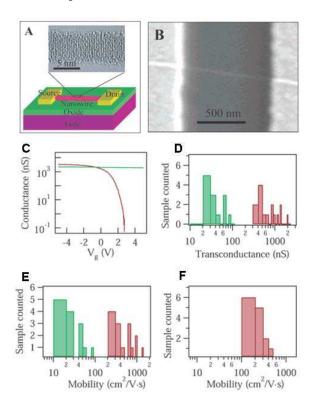

|   |     | 1.6.3   | Disposit   | ifs à nanofils                                             | 37 |

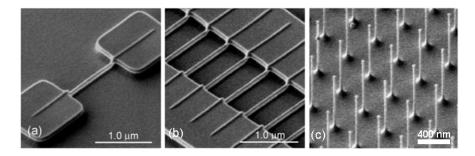

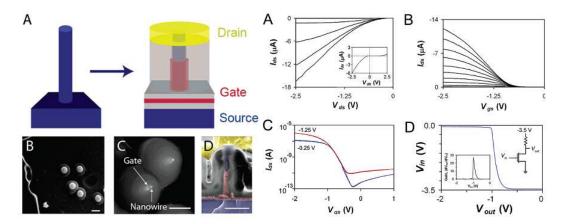

|   |     |         | 1.6.3.1    | Transistors planaires                                      | 37 |

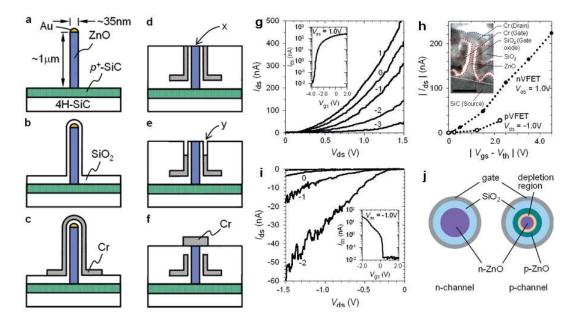

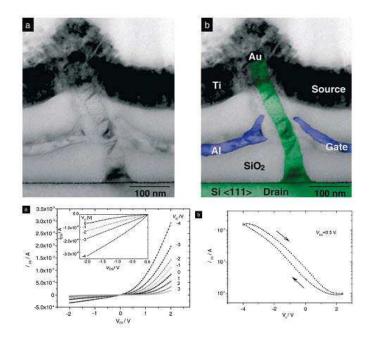

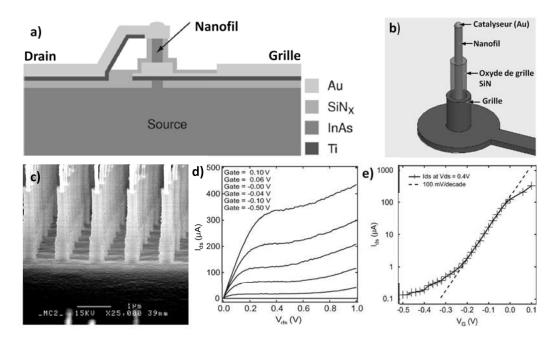

|   |     |         | 1.6.3.2    | Transistors verticaux                                      | 38 |

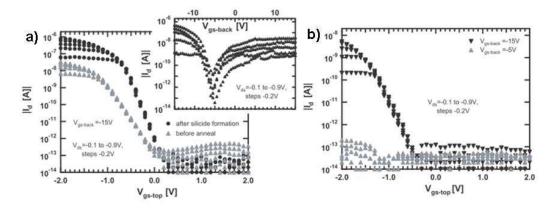

|   |     |         | 1.6.3.3    | Siliciuration des contacts                                 | 41 |

|   |     |         | 1.6.3.4    | État de l'art de la siliciuration des nanofils de silicium | 42 |

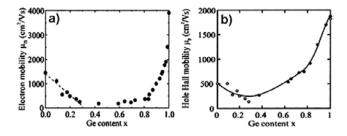

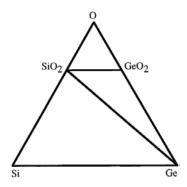

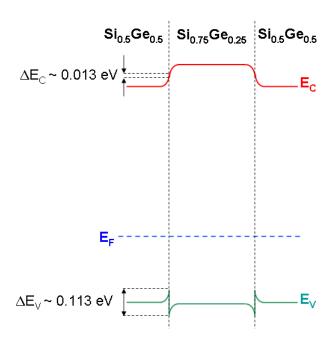

|   |     | 1.6.4   | L'alliage  | $e  Si_x Ge_{1-x}$                                         | 44 |

|   |     |         | 1.6.4.1    | Propriétés et intérêt                                      | 44 |

|   |     |         | 1.6.4.2    | État de l'art                                              | 45 |

|   | 1.7 | Object  | tifs de la | thèse                                                      | 47 |

|   |     | 1.7.1   | Objectif   | s principaux                                               | 48 |

|   |     |         | 1.7.1.1    | Évaluation des performances des nanofils                   | 48 |

|   |     |         | 1.7.1.2    | Choix du métal de contact                                  | 49 |

|   |     |         | 1.7.1.3    | Choix du diélectrique de grille                            | 49 |

|   |     |         | 1.7.1.4    | Intégration 3D                                             | 49 |

|   | 1.8 | Conclu  | ısion      |                                                            | 50 |

| 2 | Pro | priétés | s électric | ques des nanofils Si                                       | 51 |

|   | 2.1 | Introd  | uction     |                                                            | 51 |

|   | 2.2 | Élabor  | ation des  | s nanofils                                                 | 52 |

|   |     | 2.2.1   | Le réact   | eur                                                        | 52 |

|   |     | 2.2.2   | Substrat   | s et catalyseur                                            | 52 |

|   |     |         | 2.2.2.1    | Catalyseur colloidal                                       | 53 |

|   |     |         | 2.2.2.2    | Catalyseur couche mince                                    | 53 |

|   |     | 2.2.3   | Croissan   | ıce                                                        | 53 |

|   |     |         | 2.2.3.1    | Nanofils Si:                                               | 53 |

|   |     |         | 2.2.3.2    | Nanofils SiGe:                                             | 54 |

|   |     |         | 2.2.3.3    | Remarques                                                  | 54 |

|   | 2.3 | Réalis  | ation de t | ransistors à nanofils                                      | 54 |

|   |     | 2.3.1   | Disposit   | ifs planaires à grille arrière                             | 54 |

|   |     |         | 2.3.1.1    | Dispersion des fils:                                       | 54 |

|   |     |         | 2.3.1.2    | Réalisation des contacts Source/Drain :                    | 55 |

|   |     | 2.3.2   | Disposit   | ifs planaires à double grille                              | 56 |

|   |     |         | 2.3.2.1    | Grille avant non enrobante                                 | 56 |

|   |     |         | 2.3.2.2    | Grille avant enrobante                                     | 56 |

|   | 2.4 | Extrac  | ction des  | paramètres                                                 | 57 |

|   |     | 2.4.1   | Rapport    | des courants                                               | 57 |

|   |     |         |            |                                                            |    |

|   |     |         | 2.4.1.1    | Méthode simple                                                                | 58  |

|---|-----|---------|------------|-------------------------------------------------------------------------------|-----|

|   |     |         | 2.4.1.2    | Méthode classique                                                             | 58  |

|   |     |         | 2.4.1.3    | Méthode de Chau [1]                                                           | 58  |

|   |     | 2.4.2   | Normali    | sation des courants                                                           | 59  |

|   |     | 2.4.3   | Capacite   | é de grille                                                                   | 59  |

|   |     |         | 2.4.3.1    | Modèle de la capacité cylindrique                                             | 59  |

|   |     |         | 2.4.3.2    | Modèle "cylindre-sur-plan"                                                    | 60  |

|   |     | 2.4.4   | Tension    | Seuil                                                                         | 60  |

|   |     | 2.4.5   | Pente so   | ous le seuil                                                                  | 61  |

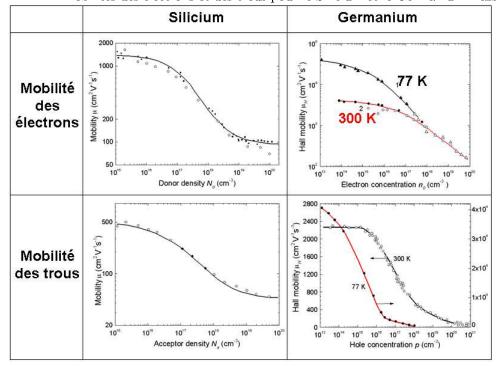

|   |     | 2.4.6   | Mobilité   | des porteurs                                                                  | 62  |

|   |     |         | 2.4.6.1    | Abaques                                                                       | 62  |

|   |     |         | 2.4.6.2    | Estimation des mobilités dans les nanofils                                    | 63  |

|   |     | 2.4.7   | Conclus    | ion                                                                           | 63  |

|   | 2.5 | Transi  | stors plar | naires à grille arrière à nanofils Si                                         | 63  |

|   |     | 2.5.1   | Introduc   | tion                                                                          | 63  |

|   |     | 2.5.2   | Nanofils   | Silicium bruts de croissance                                                  | 63  |

|   |     |         | 2.5.2.1    | Résistances d'accès et dopage résiduel                                        | 64  |

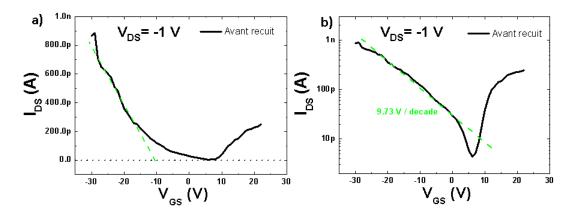

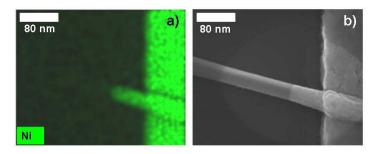

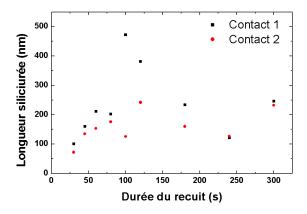

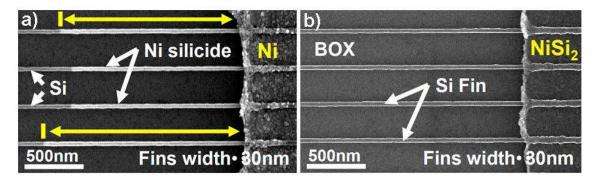

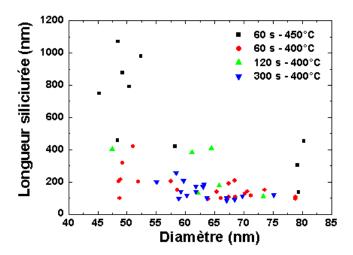

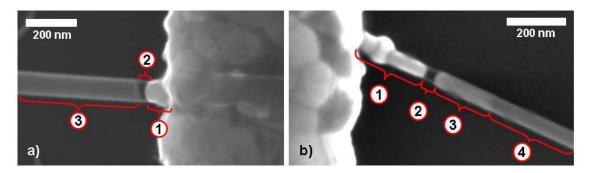

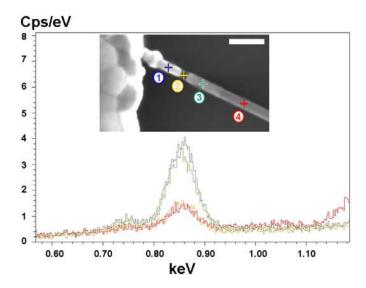

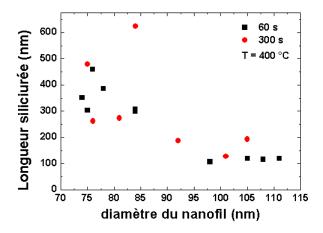

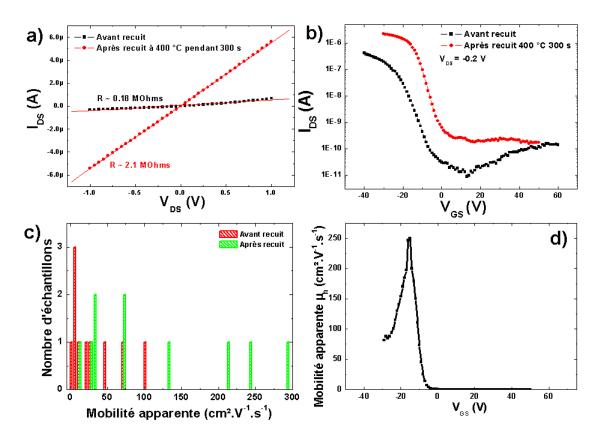

|   |     |         | 2.5.2.2    | Cinétique de la siliciuration                                                 | 67  |

|   |     |         | 2.5.2.3    | Impact de la siliciuration sur les performances électriques des transistors à |     |

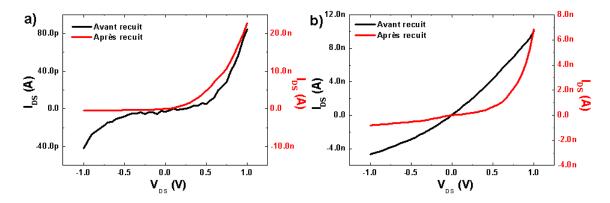

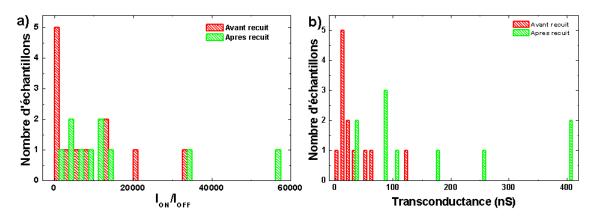

|   |     |         |            | nanofil Si                                                                    | 70  |

|   |     |         | 2.5.2.4    | Hauteur de barrière des contacts                                              | 72  |

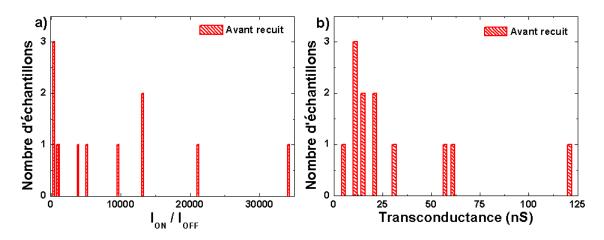

|   |     |         | 2.5.2.5    | Grandeurs caractéristiques des transistors à nanofils Si                      | 76  |

|   |     |         | 2.5.2.6    | Comportement hystérétique des nanofils Si                                     | 78  |

|   |     | 2.5.3   | Nanofils   | de Si oxydés                                                                  | 83  |

|   |     |         | 2.5.3.1    | Introduction                                                                  | 83  |

|   |     |         | 2.5.3.2    | Comportement sous champ                                                       | 83  |

|   |     |         | 2.5.3.3    | Inversion de dopage                                                           | 85  |

|   |     |         | 2.5.3.4    | Influence de l'atmosphère du recuit                                           | 89  |

|   | 2.6 | Transi  | stors plar | naires à double grille à nanofil Si                                           | 91  |

|   | 2.7 | Conclu  | usion      |                                                                               | 93  |

| 3 | Pro | priétés | s électric | ques des nanofils $Si_{0.7}Ge_{0.3}$                                          | 95  |

|   | 3.1 | Introd  | uction     |                                                                               | 95  |

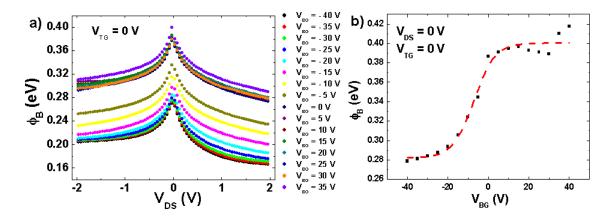

|   | 3.2 | Transi  | stors plar | naires à grille arrière à nanofil SiGe                                        | 95  |

|   |     | 3.2.1   | Nanofils   | $Si_{0.7}Ge_{0.3}$ bruts de croissance                                        | 95  |

|   |     |         | 3.2.1.1    | Dopage résiduel                                                               | 95  |

|   |     |         | 3.2.1.2    | Siliciuration - cinétique                                                     | 97  |

|   |     |         | 3.2.1.3    |                                                                               | 100 |

|   |     |         |            | <del>-</del>                                                                  |     |

|   |     | 3.2.2  | Nanofils $Si_{0.7}Ge_{0.3}$ oxydés                                                                                                                                             |

|---|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     |        | 3.2.2.1 Caractérisation électrique                                                                                                                                             |

|   |     |        | 3.2.2.2 Siliciuration - cinétique                                                                                                                                              |

|   |     |        | 3.2.2.3 Siliciuration - impact sur les performances électriques                                                                                                                |

|   | 3.3 | SiGe - | Transistors planaires à double grille                                                                                                                                          |

|   | 3.4 | Mode   | de fonctionnement des transistors à nanofils                                                                                                                                   |

|   | 3.5 | Concl  | ısion                                                                                                                                                                          |

|   | 3.6 | Concl  | ısion générale sur l'intégration planaire                                                                                                                                      |

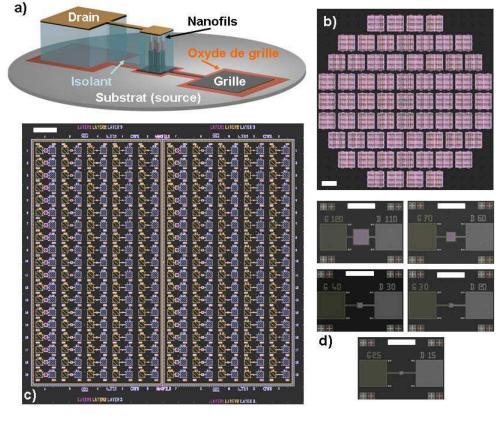

| 4 | Pro | cédé d | e fabrication et caractérisation électrique de transistors verticaux 115                                                                                                       |

|   | 4.1 | Introd | uction                                                                                                                                                                         |

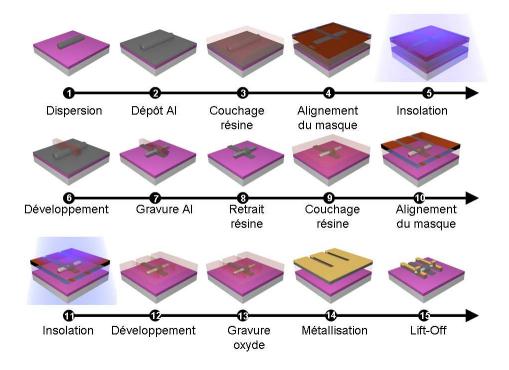

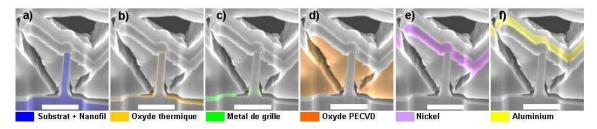

|   | 4.2 | Procé  | dé de fabrication                                                                                                                                                              |

|   |     | 4.2.1  | Design des masques                                                                                                                                                             |

|   |     | 4.2.2  | Localisation du catalyseur                                                                                                                                                     |

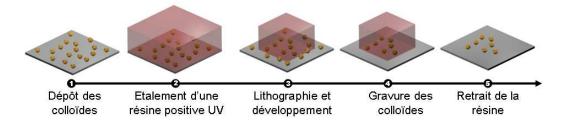

|   |     |        | 4.2.2.1 Lithographie optique :                                                                                                                                                 |

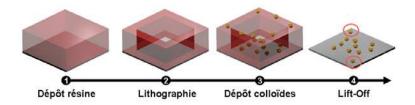

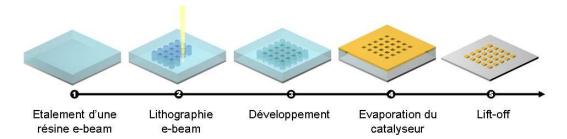

|   |     |        | 4.2.2.2 Lithographie électronique                                                                                                                                              |

|   |     | 4.2.3  | Croissance                                                                                                                                                                     |

|   |     | 4.2.4  | Retrait du catalyseur                                                                                                                                                          |

|   |     | 4.2.5  | Oxyde de grille                                                                                                                                                                |

|   |     |        | 4.2.5.1 L'oxydation thermique                                                                                                                                                  |

|   |     |        | 4.2.5.2 Oxydes déposés                                                                                                                                                         |

|   |     | 4.2.6  | Dépôt du métal de grille                                                                                                                                                       |

|   |     | 4.2.7  | Définition du pad et contrôle de la hauteur de grille                                                                                                                          |

|   |     | 4.2.8  | Isolation Grille-Drain                                                                                                                                                         |

|   |     | 4.2.9  | Reprise de contacts                                                                                                                                                            |

|   |     |        | 4.2.9.1 Drain                                                                                                                                                                  |

|   |     |        | 4.2.9.2 Grille                                                                                                                                                                 |

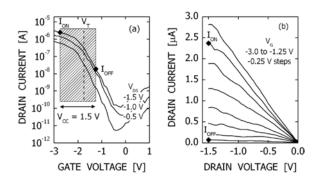

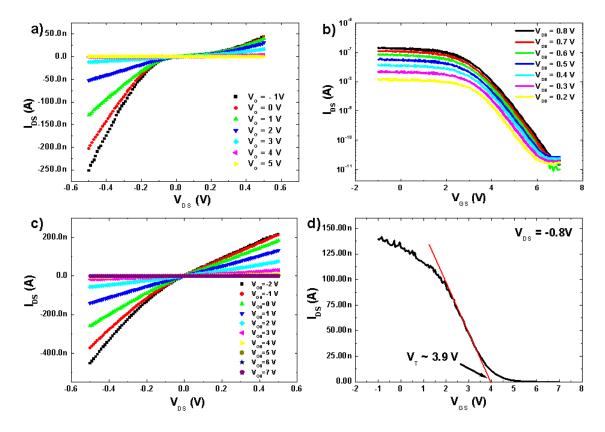

|   | 4.3 | Carac  | térisation électrique des transistors à nanofils verticaux $\dots \dots \dots$ |

|   |     | 4.3.1  | Introduction                                                                                                                                                                   |

|   |     | 4.3.2  | Nanofils Si                                                                                                                                                                    |

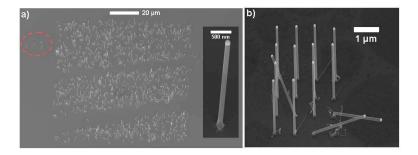

|   |     |        | 4.3.2.1 Effets de la localisation du catalyseur                                                                                                                                |

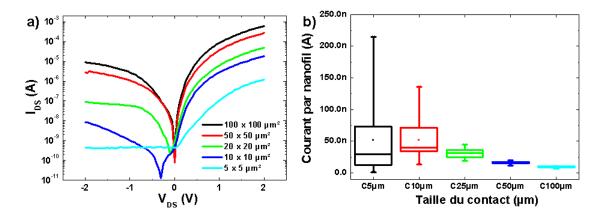

|   |     |        | 4.3.2.2 Localisation contrôlée et propriétés électriques                                                                                                                       |

|   |     | 4.3.3  | Bilan - transistors Si                                                                                                                                                         |

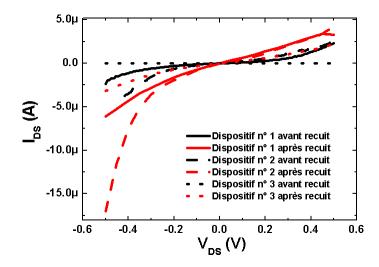

|   |     | 4.3.4  | Nanofils $Si_{0,7}Ge_{0,3}$                                                                                                                                                    |

|   |     | 4.3.5  | Durée de vie des dispositifs                                                                                                                                                   |

|   |     | 4.3.6  | Reproductibilité des procédés                                                                                                                                                  |

|   |     | 4.3.7  | Bilan - transistors SiGe                                                                                                                                                       |

|   | 4.4 | Concl  | ısion de l'intégration verticale                                                                                                                                               |

| 5 | Con  | clusio  | n Généra     | le                                                    | 140   |

|---|------|---------|--------------|-------------------------------------------------------|-------|

| 6 | Pers | specti  | ves d'inté   | gration back-end                                      | 143   |

|   | 6.1  | Introd  | uction       |                                                       | . 143 |

|   | 6.2  | Croiss  | ance des n   | anofils                                               | . 143 |

|   | 6.3  | Isolati | on des con   | tacts de grille et de drain                           | . 144 |

|   |      | 6.3.1   | Dépôt du     | ı diélectrique                                        | . 144 |

|   |      | 6.3.2   | Polissage    | mécano-chimique                                       | . 145 |

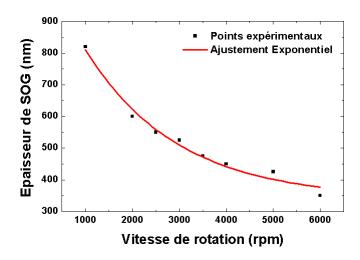

|   |      |         | 6.3.2.1      | Présentation de l'équipement                          | . 145 |

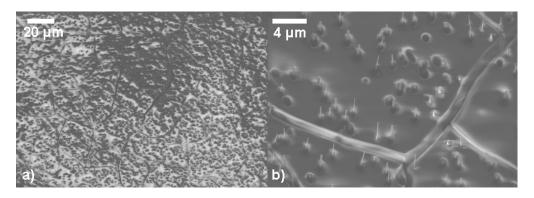

|   |      |         | 6.3.2.2      | Calibration des vitesses de gravure                   | . 145 |

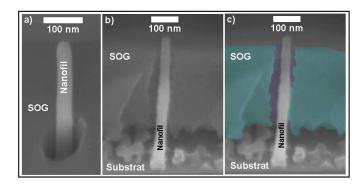

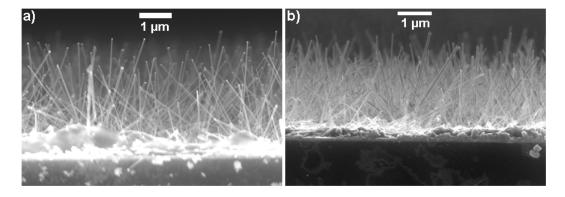

|   |      |         | 6.3.2.3      | Polissage de nanofils                                 | . 146 |

|   |      |         | 6.3.2.4      | Reprise de contact après CMP                          | . 148 |

|   | 6.4  | Bilan   | de la plana  | arisation                                             | . 150 |

|   | 6.5  | Vers l  | a compatib   | oilité back-end                                       | . 150 |

|   |      | 6.5.1   | Croissand    | e de nanofils sur TiN                                 | . 151 |

|   |      |         | 6.5.1.1      | Or démouillé                                          | . 151 |

|   |      |         | 6.5.1.2      | Croissance localisée                                  | . 152 |

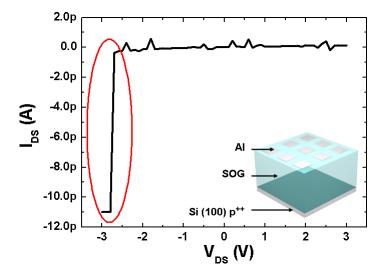

|   |      | 6.5.2   | Caractéri    | stiques électriques de fils SiGe crus sur TiN         | . 152 |

|   | 6.6  | Bilan   | de la comp   | patibilité back-end                                   | . 154 |

|   | 6.7  | Comp    | atibilité du | $_1$ catalyseur                                       | . 154 |

|   |      | 6.7.1   | Introduct    | ${f ion}$                                             | . 154 |

|   |      | 6.7.2   | Les alteri   | natives à l'or                                        | . 155 |

|   |      |         | 6.7.2.1      | Platine, palladium, cobalt et nickel                  | . 155 |

|   |      |         | 6.7.2.2      | Le cuivre                                             | . 155 |

|   |      | 6.7.3   | Influence    | de l'or sur le comportement électronique des nanofils | . 155 |

|   | 6.8  | Concl   | usion        |                                                       | . 156 |

|   | 6.9  | Perspe  | ectives gén  | érales                                                | . 157 |

|   |      | 6.9.1   | Intégration  | on sur substrat métallique                            | . 157 |

|   |      | 6.9.2   | Vers les t   | ransistors à effet tunnel                             | . 158 |

|   | 6.10 | Concl   | usion        |                                                       | . 158 |

# Chapitre 1

# Du MOSFET aux nanofils

# 1.1 Introduction

Nous allons dans ce chapitre introduire les notions de base nécessaires à la compréhension du manuscrit. Dans un premier temps nous situerons le contexte de l'étude au sein du domaine de la microélectronique. Pour cela nous rappellerons le principe de fonctionnement d'un transistor à effet de champ et détaillerons la structure des circuits intégrés actuels. Nous parlerons ensuite de l'intérêt des nanofils semi-conducteurs dans la microélectronique et expliquerons les différentes méthodes d'élaboration de ces objets. Nous présenterons en détails les objectifs de ce projet en terme d'intégration de nanostructures.

# 1.2 Le transistor à effet de champ

# 1.2.1 Historique

Le transistor à effet de champ est l'élément de base des circuits intégrés et microprocesseurs actuels. Son principe de fonctionnement a été proposé dès les années 30 par J. E. Lilienfeld et O. Heil [2, 3].

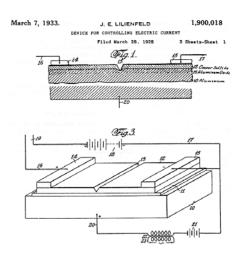

FIGURE 1.1 – Images extraites du brevet déposé par Lilienfeld en 1933 concernant la réalisation d'un "dispositif pour le contrôle d'un courant électrique".

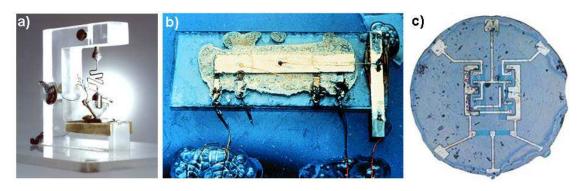

Courant 1947 J. Bardeen, W. Brattain et R. Schokley ont démontré pour la première fois la possibilité de réaliser un transistor bipolaire à partir d'un substrat de germanium fig 1.2 a) ce qui leur valu le prix Nobel de physique en 1956 pour leurs travaux sur les semi-conducteurs et la découverte de l'effet transistor. Ceci marqua le début de l'ère de la microélectronique. Quelques années après, en 1959, le premier transistor planaire était réalisé par R. Noyce. En 1958 l'entreprise Texas Instrument réalise le premier circuit intégré sur germanium comportant alors deux transistors fig 1.2 b). En 1960 J. R. Ligenza et W. G. Spitzer [4] réalisèrent le premier dispositif présentant de bonnes performances et utilisant le système Si/SiO2 au lieu du germanium. Un an plus tard était réalisé le premier circuit intégré planaire sur silicium au sein de la compagnie Fairschild Semiconductors fig 1.2 c). Afin de mieux comprendre le fonctionnement de ces composants nous allons nous intéresser maintenant à la physique de ces dispositifs. Nous ne nous intéresserons cependant qu'au transistor à effet de champ afin de se limiter aux structures ayant un intérêt pour cette étude.

FIGURE 1.2 – a) Premier transistor réalisé au laboratoire Bell b) Premier circuit intégré sur substrat germanium réalisé par Texas Instruments c) Premier circuit intégré planaire sur silicium réalisé par Fairschild semiconductors.

## 1.2.2 Structure d'un transistor à effet de champ

#### 1.2.2.1 Capacité MOS idéale

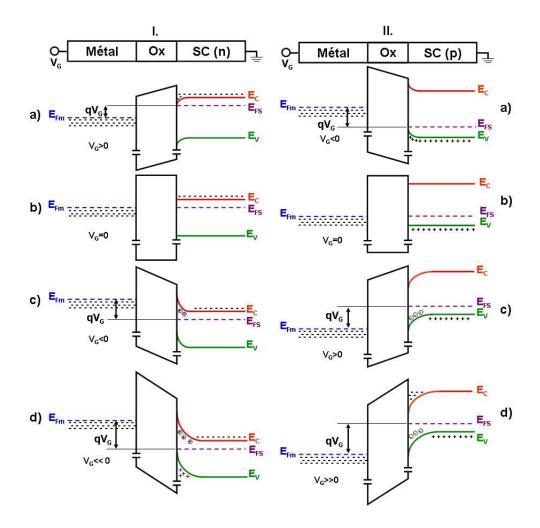

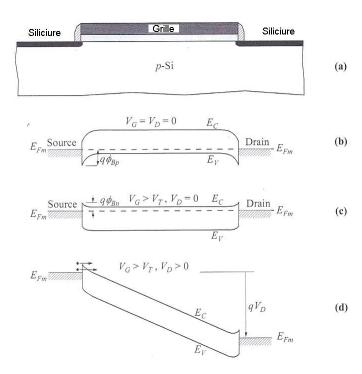

Avant de décrire le transistor nous allons nous pencher sur un de ses constituants de base qu'est la capacité MOS (Metal-Oxide-Semiconductor). Comme son nom l'indique, une capacité MOS est un empilement de trois couches à savoir, un semi-conducteur, un oxyde et un métal. Le semi-conducteur peut être dopé p ou n. L'électrode métallique est polarisée à une tension  $V_G$  pendant que le substrat est maintenu à la masse. Différents régimes apparaissent alors en fonction de  $V_G$  qui sont représentés sur la figure 1.3. Les trois modes sont l'accumulation quand  $V_G > 0$  V pour un substrat n et  $V_G < 0$  V pour un substrat p, la désertion quand  $V_G < 0$  V pour un substrat n et  $V_G > 0$  V pour un substrat p et enfin l'inversion quand  $V_G < 0$  V pour un substrat n et  $V_G > 0$  V pour un substrat p. Il existe une tension  $V_G = V_{FB}$  pour laquelle le diagramme de bandes ne présente aucune courbure, ici cette tension est considérée comme nulle car les niveaux de Fermi dans le métal et le semi-conducteur sont alignés . On appelle  $V_{FB}$  la tension de bandes plates. En pratique cette configuration est rare et on a  $V_{FB} = \Phi_m - \Phi_s$  avec  $\Phi_m \neq \Phi_s$ ,  $\Phi_m$  étant le travail de sortie du métal et  $\Phi_s$  celui du semi-conducteur.

FIGURE 1.3 – Diagrammes de bandes de capacités MOS I.) type n et II.) type p . a) régime d'accumulation b) régime de bandes plates c) régime de désertion c) régime d'inversion.

## 1.2.2.2 Capacité MOS réelle

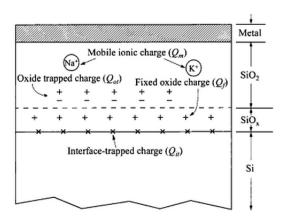

Nous venons de voir le principe de fonctionnement d'une capacité MOS idéale. En réalité, lorsqu'un oxyde est formé à la surface du silicium par oxydation thermique, l'interruption de la périodicité du réseau à la surface du cristal, la présence d'espèces extrinsèques au silicium mais également la présence d'états de liaison non présents dans le massif induisent des états pièges à l'interface  $Si/SiO_2$  dans le gap même du silicium. La charge de ces pièges a été démontrée par Schokley et Pearson [5]. Il a été mesuré que la densité de ces pièges peut être très élevée [6], de l'ordre de la densité d'atomes de surface ( $\approx 10^{15} atomes.cm^{-2}$ ) et qu'il est possible de les neutraliser à l'aide de recuits sous hydrogène à basse température ( $\sim 450$  °C) jusqu'à atteindre une densité d'environ  $10^{10}$  cm<sup>-2</sup> ce qui correspond à un piège pour  $10^5$  atomes de surface. Ces états, formant un continuum dans la bande interdite du semi-conducteur, peuvent échanger rapidement une charge avec le semi-conducteur sous-jacent et sont par nature amphotère, c'est-à-dire qu'ils peuvent aussi bien accepter qu'émettre un électron. Ils jouent donc un rôle important dans l'état d'équilibre du semi-conducteur pour un dopage donné et une polarisation de grille donnée en raison de la courbure de bandes induite par le transfert de charges en surface. A l'interface, seuls les états inclus entre le quasi niveau de Fermi et le niveau de Fermi du matériau intrinsèque seront peuplés par les porteurs majoritaires du semi-conducteur. Nous allons voir

dans la suite de ce manuscrit comment ces états pièges influencent le comportement des capacités MOS. Il sera en effet important de prendre en compte ces effets lors de la caractérisation de transistors.

Comme les états d'interface sont distribués tout le long du gap, leur distribution s'exprime comme :

$$D_{it} = \frac{1}{q} \frac{dQ_{it}}{dE} \tag{1.1}$$

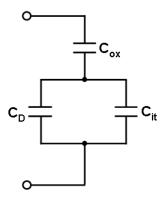

, où Dit représente la densité d'état d'interface par unité de surface et d'énergie de bande interdite, q la charge élémentaire de l'électron et  $Q_{it}$  la charge piégée à l'interface, en coulomb par unité de surface. Durant cette étude, toutes les caractéristiques électriques seront réalisées en statique aussi la capacité MOS peut être résumée par le circuit équivalent 1.4.  $C_{ox}$  représente la capacité de l'oxyde,  $C_D$  la capacité de déplétion et  $C_{it}$  la capacité liée aux états d'interface.

FIGURE 1.4 – Circuit équivalent d'une capacité MOS à basse fréquence en tenant compte des pièges à l'interface  $\mathrm{Si}/SiO_2$

Nous verrons par la suite comment ces états d'interface impactent sur le comportement électrique des transistors, mais avant tout nous allons détailler la structure d'un transistor à effet de champ et expliquer son mode de fonctionnement.

#### 1.2.2.3 Le MOSFET

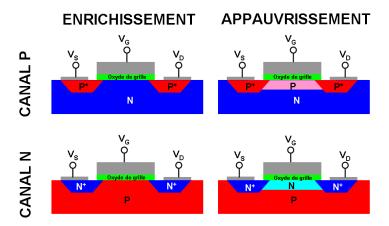

Le MOSFET ou transistor à effet de champ (Metal-Oxide-Semiconductor Field-Effect Transistor) est constitué de trois électrodes. La première est la grille destinée à contrôler le potentiel à l'interface métal semi-conducteur et donc le type et la densité de porteurs du semi-conducteur et donc du canal. On retrouve ainsi la structure présentée précédemment de la capacité MOS. A cela s'ajoutent deux contacts nommés source et drain placés de part et d'autre de la capacité destinés à jouer le rôle de réservoirs de charges et ainsi à permettre le passage d'un courant. Selon le type de porteurs utilisés dans le canal nous avons soit un NMOS (canal d'électrons) soit un PMOS (canal de trous). De plus ces transistors peuvent être dans l'état ouvert ou fermé pour une polarisation de grille nulle selon qu'ils fonctionnent respectivement en appauvrissement ou enrichissement comme présenté en figure 1.5.

FIGURE 1.5 – Représentation schématique des différentes familles de transistors à effet de champ.

Le MOSFET peut donc se résumer à un interrupteur électrostatique, la grille ayant le rôle de commutateur. Afin de mieux comprendre le comportement de ce dispositif intéressons nous à sa caractéristique courant-tension.

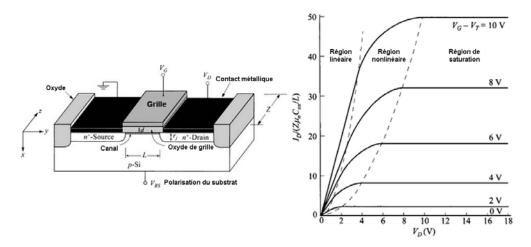

FIGURE 1.6 – Schéma d'un N-MOS à enrichissement et sa caractéristique  $I_{DS} - V_{DS}$  pour différentes tensions de grille d'après [7].

La caractéristique  $I_{DS} - V_{DS}$  d'un MOSFET présente, quelle que soit la tension de grille, trois régions distinctes. Une région linéaire, une non-linéaire et enfin une région de saturation. Nous allons décrire brièvement chacune d'entre elles.

**Région linéaire** Pour les petites tensions  $V_{DS}$  le courant de drain s'exprime comme :

$$I_{DS} = \frac{Z}{L} \mu_n C_{ox} \left( V_G - V_T - \frac{V_D}{2} \right) V_D \tag{1.2}$$

Avec  $V_T$  la tension seuil, un des plus importants paramètres, donnée par :

$$V_T = V_{FB} + 2\Psi_B + \frac{\sqrt{2\varepsilon_s q N_A 2\Psi_B}}{C_{ox}}$$

$$\tag{1.3}$$

Avec, Z la largeur du canal du transistor, L sa longueur,  $\mu_n$  la mobilité des électrons,  $C_{ox}$ est la capacité de l'oxyde de grille,  $V_G$  la tension de grille,  $V_D$  la tension de drain,  $\Psi_B$  l'écart entre le niveau de Fermi intrinsèque et le niveau de Fermi soit  $|E_F - E_i|/q$ ,  $\varepsilon_s$  est la permittivité relative du semi-conducteur,  $N_A$  est la densité de trous libres.

Nous discuterons plus en détails de la tension seuil par la suite. Lorsque la charge d'inversion devient nulle côté drain on parle alors de pincement du canal. Ce pincement est dû au fait que la différence de potentiel entre la grille et le semi-conducteur diminue fortement pour de fortes polarisations source-drain. Le courant et la tension de drain en ce point de fonctionnement sont désignés par  $I_{DS_{SAT}}$  et  $V_{DS_{SAT}}$  respectivement.

**Région de saturation** Au delà du pincement du canal, le courant est indépendant de  $V_D$  et on obtient ainsi une saturation. Le courant de saturation s'exprime alors comme :

$$I_{DS_{SAT}} = \frac{Z}{2\left(1 + \frac{\sqrt{\varepsilon_s q N_A}}{2\sqrt{\Psi_B} C_{ox}}\right) L} \mu_n C_{ox} \left(V_G - V_T\right)^2$$

(1.4)

Enfin la dernière région de fonctionnement qui est la zone intermédiaire entre le comportement linéaire et de saturation, la région non-linéaire peut être décrite comme suit.

Région non-linéaire Elle se situe entre les deux cas extrêmes et peut être décrite par :

$$I_{DS} = \frac{Z}{L} \mu_n C_{ox} \left( V_G - V_T - \frac{V_D}{2} \left( 1 + \frac{\sqrt{\varepsilon_s q N_A}}{2\sqrt{\Psi_B} C_{ox}} \right) \right) V_D$$

(1.5)

Cet ensemble d'équations permet de décrire le comportement des MOSFETs d'une manière approximée mais relativement juste. Comme nous l'avons précisé précédemment, la tension seuil du transistor est un paramètre très important. Nous allons donc aborder ce point afin d'éclaircir la relation qui existe entre le courant de drain et la tension de grille.

Tension seuil Nous avons introduit la notion de tension seuil avec l'équation 1.2.2.3. Nous avions supposé que le travail de sortie du métal et le niveau de Fermi du semi-conducteur étaient alignés par commodité entraînant ainsi un alignement des bandes pour une tension de grille nulle. En pratique ceci n'est que très rarement le cas en raison non seulement de la différence entre  $\phi_m$  et  $\phi_s$  mais également à cause des charges fixes  $Q_f$  piégées dans l'oxyde. Aussi l'équation 1.2.2.3 devient :

$$V_T = V_{FB} + 2\Psi_B + \frac{\sqrt{2\varepsilon_s q N_A 2\Psi_B}}{C_{ox}} = \left(\phi_{ms} - \frac{Q_f}{C_{ox}}\right) + 2\Psi_B + \frac{\sqrt{4\varepsilon_s q N_A \Psi_B}}{C_{ox}}$$

(1.6)

Qualitativement,  $V_T$  est la tension de grille au delà de l'état de bande plate qui commence à introduire une couche de charge d'inversion et est donnée par la somme des tensions à travers le semi-conducteur et l'oxyde de grille. Le terme en racine est la charge totale de la couche de déplétion au point d'inversion. Comme la tension seuil représente la tension au delà de laquelle le canal est considéré comme ouvert il est extrêmement important d'avoir accès à cette valeur.

Cette tension est mesurée en traçant le courant de drain en fonction de la tension de grille en échelle linéaire. Une extrapolation de la région linéaire sur l'axe des abscisses permet de déterminer sa valeur. La figure 1.7 b) montre le courant de drain tracé en échelle logarithmique en fonction de la tension de grille. Dans cette

échelle, une zone linéaire apparait avant la tension seuil. Elle va également nous permettre d'extraire des données importantes concernant le comportement des transistors.

FIGURE 1.7 – Courbes  $I_{DS} - V_{GS}$  typiques d'un transistor avec a) la représentation en échelle linéaire du courant  $I_{DS}$  permettant le calcul de  $V_T$ . b) la représentation en échelle logarithmique du courant  $I_{DS}$  mettant en avant la pente sous le seuil. (d'après [7])

**Région sous le seuil** La région sous le seuil désigne tout simplement le domaine pour lequel la tension de grille est inférieure à  $V_T$ . Ainsi la surface du semi-conducteur est en inversion, le courant de drain correspondant est désigné comme courant sous le seuil. Cette région est particulièrement intéressante pour les applications faibles tensions et faible puissance car elle traduit l'abrupté avec laquelle le courant de drain varie en fonction de la tension de grille. Dans cette région de fonctionnement, le courant de drain prend l'expression suivante :

$$I_{DS} = \frac{Z\mu_n}{L} \left(\frac{kT}{q}\right)^2 \sqrt{\frac{q\varepsilon_s N_A}{2\Psi_s}} \left(\frac{n_i}{N_A}\right) exp\left(\frac{q\Psi_s}{kT}\right) \left[1 - exp\left(-\frac{qV_{DS}}{kT}\right)\right]$$

(1.7)

Cette équation montre que dans la région sous le seuil, lorsque  $V_{DS}$  est plus grand qu'environ 3kT/q alors le courant est indépendant de  $V_{DS}$ . On peut finalement relier  $I_{DS}$  à la tension de grille  $V_G$  à l'aide de la relation :

$$V_G - V_{FB} = \Psi_s + \frac{\sqrt{2\varepsilon_s \Psi_s q N_A}}{C_{ox}}$$

(1.8)

Nous venons de dire que la région sous le seuil nous permettait de qualifier l'abrupté de la variation du courant en fonction de la tension de grille. Le paramètre qui nous permet de quantifier ce phénomène est l'inverse de la pente sous le seuil défini comme la variation de tension de grille nécessaire pour induire une changement du courant de drain d'un ordre de grandeur. D'après l'équation 1.2.2.3 on peut écrire que :

$$\frac{dV_G}{d\Psi_s} = 1 + \frac{1}{C_{ox}} \sqrt{\frac{\varepsilon_s q N_A}{2\Psi s}} = \frac{C_{ox} + C_D}{C_{ox}}$$

(1.9)

Par définition l'inverse de la pente sous le seuil est obtenu comme suit :

$$S \equiv (ln10) \frac{dV_G}{d(lnI_D)} = (ln10) \frac{dV_G}{d\left(\frac{q\Psi_s}{kT}\right)} = (ln10) \left(\frac{kT}{q}\right) \left(\frac{C_{ox} + C_D}{C_{ox}}\right)$$

(1.10)

La limite théorique de cet inverse de la pente sous le seuil est obtenu pour  $C_D = 0F$  et vaut donc 60 mV/décade. Comme nous l'avons expliqué précédemment, l'oxydation thermique engendre des pièges à l'interface  $Si/SiO_2$ . Il est possible d'en tenir compte dans l'expression de l'inverse de la pente sous le seuil en modifiant simplement l'expression de la capacité comme suit :

$$S = (ln10) \left(\frac{kT}{q}\right) \left(\frac{C_{ox} + C_D + C_{it}}{C_{ox}}\right)$$

(1.11)

avec  $C_{it}$  la capacité associée aux pièges d'interface. Cette expression permet ainsi à partir d'une simple mesure I(V) statique de remonter à la valeur de  $D_{it}$ comme nous le montrerons plus tard.

Depuis les années 60 le design des transistors, les matériaux ainsi que les procédés de fabrication ont considérablement évolué afin d'améliorer leurs performances. Nous verrons également comment l'architecture complète des circuits intégrés a été optimisée afin de permettre aux puces de gagner en rapidité et en volume de calcul. Nous verrons par la suite qu'une variante du MOSFET prometteuse pour les applications basse consommation peut être obtenue par l'utilisation non plus de silicium dopé comme contacts de source et de drain mais d'un alliage métallique.

Nous venons de présenter la brique de base qu'est le transistor ainsi que son principe de fonctionnement. Nous allons désormais nous intéresser à l'architecture globale d'un circuit intégré pour pouvoir situer plus précisément le contexte de notre étude.

# 1.3 Architecture d'un circuit intégré

Avant de réfléchir aux différents moyens permettant d'augmenter les performances des circuits intégrés nous allons nous concentrer sur leur structure interne. Le but ici est de montrer l'empilement interne.

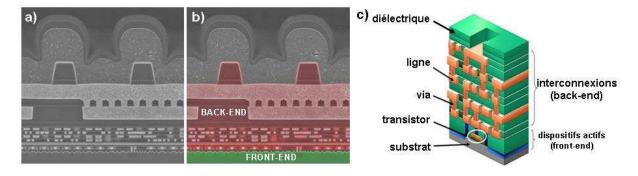

De manière générale nous distinguerons deux grandes zones dans la structure d'un circuit intégré. Le front-end et le back-end comme représenté sur le schéma 1.8 b) et c).

FIGURE 1.8 – a) et b) Images MEB originale et colorisée d'une coupe d'un circuit intégré A5 d'Apple utilisé dans l'iPad2 avec mise en évidence des deux parties majeures. c) Schéma illustrant la structure générale d'un circuit intégré.

# 1.3.1 Le Front End : zone active

Cette partie front end contient les transistors qui seront utilisés pour réaliser les opérations logiques des processeurs. Il s'agit tout simplement du substrat en silicium sur lequel ont été réalisés les MOSFETs avancés. C'est ici que l'on trouve les transistors les plus rapides et les plus performants. Aucune contrainte thermique n'existe en tant que telle lors de la réalisation de ces transistors. C'est sur cette zone que sont engagés les plus gros moyens pour augmenter les performances des circuits intégrés. Le leader du marché actuel est le fabricant Intel qui est à l'heure actuel le seul à utiliser une architecture multigrille pour les transistors du front-end comme présenté sur la figure 1.9.

FIGURE 1.9 – Évolution de l'architecture des transistors utilisés dans les microprocesseurs Intel depuis 2003.

Une fois ces transistors réalisés il faut pouvoir les contacter et les mettre en réseau de façon à accomplir des opérations de logique. Pour cela la première étape consiste à les isoler puis à réaliser des trous (Vias) qui sont ensuite remplis de métal. Les étapes d'après constituent la partie back-end

# 1.3.2 Le Back End : zone froide

La partie back end contient toutes les interconnexions destinées à relier les transistors entre eux. Le back end est en fait un empilement de diélectriques dans lesquels sont noyés des lignes ou des vias métalliques destinés à transporter les signaux électriques. Le back end ne contient donc aucun composant actif, seulement des lignes métalliques. La réalisation de ces étapes est très fortement contrainte. En effet il est impératif de réaliser les interconnexions sans porter de dommages aux transistors du front-end. Pour cela une notion importante est celle de budget thermique. Ceci représente la température maximum à ne pas dépasser sous peine par exemple de propager les siliciures des contacts des transistors et donc de rendre les canaux métalliques. L'ordre de grandeur de ce budget thermique pour les circuits intégrés actuels est d'environ 450 °C. Ainsi toute opération effectuée sur une plaque de silicium contenant une partie front-end ne doit pas dépasser cette température sous peine de détériorer les performances électriques des dispositifs préalablement réalisés.

Maintenant que nous avons introduit les notions importantes concernant la réalisation de circuits intégrés nous allons nous intéresser aux méthodes adoptées depuis environ cinquante ans pour améliorer au maximum leurs performances.

# 1.4 Accroissement des performances des IC's.

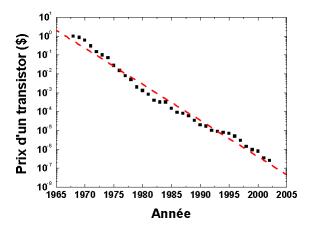

La recherche de performances accrues, c'est-à-dire de processeurs qui calculent plus vite et qui peuvent traiter un plus grand nombre de données en un temps donné est l'objectif principal de la microélectronique. Le second objectif est d'être capable de produire un nombre de puces toujours plus grand pour un cout toujours plus faible. Il est d'usage d'évaluer le prix d'un circuit en le rapportant au nombre de transistors. Ainsi le graphique (1.10) montre l'évolution du cout d'un transistor au cours du temps. On constate que sur une période de quarante ans le prix unitaire du MOSFET a été divisé par un facteur  $10^7$ .

FIGURE 1.10 – Évolution du prix des transistors des années 1960 à 2000.

Cette réduction drastique n'a pu être effectuée qu'à l'aide d'innovations technologiques majeures. D'une part le nombre de transistors sur une puce n'a cessé de croitre en cherchant sans cesse à diminuer leur taille, c'est l'approche "more-Moore". De l'autre le nombre de fonctionnalités qu'offrent les circuits intégrés a également explosé en adoptant cette fois-ci l'approche "more-than-Moore". Ces deux approches s'affrontent et se complètent. Elles s'affrontent sur la stratégie utilisée pour améliorer les puces mais se complètent sur les applications que chacune vise. Elles sont communément représentées comme sur la figure 1.11.

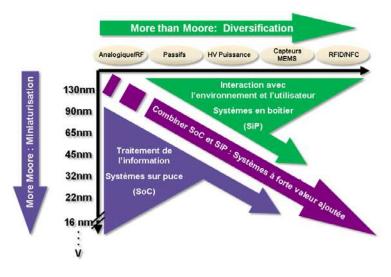

Figure 1.11 – Comparatif entre l'approche "more-Moore" et "more-than-Moore".[8]

L'approche "more Moore" est à la poursuite de la miniaturisation des composants tandis que la "more than

Moore" recherche sans cesse l'ajout de nouvelles fonctions

Nous allons maintenant définir chaque approche ainsi que les méthodes qu'elles emploient pour atteindre leurs objectifs. Dans ce contexte nous poserons les limites et guiderons notre réflexion vers de nouvelles alternatives d'amélioration des circuits intégrés.

# 1.4.1 Approche "More Moore"

En 1965, Gordon Moore, qui était à l'époque ingénieur chez Fairschild semiconductor et qui fonda plus tard Intel, constate que le nombre de transistors sur une puce doublait chaque année à cout constant et prévoyait que cette augmentation continue. En 1975 il réévalua cette conjecture et prédit que le nombre de transistors sur une plaque de silicium doublerait tous les deux ans. De 1971 à 2001 cette loi empirique s'avéra redoutablement exacte car ce nombre doublait effectivement toutes les 1,96 années. Cette conjecture prit rapidement le nom de loi de Moore. On désigne donc dans une approche "More Moore" le fait de vouloir coller au maximum avec cette loi et donc d'augmenter la densité surfacique de transistors disponibles dans le front-end. La meilleure façon de parvenir à cet objectif est tout simplement de diminuer les dimensions des transistors. C'est ce que l'on appelle le "scaling" du transistor. Il s'agit de diminuer les dimensions générales de chaque partie des transistors tout en respectant des lois de mise à l'échelle afin d'éviter certain désagréments technologiques. En effet toute diminution de la taille du transistor ne doit pas être lui être dommageable et préserver les propriétés de transport observées à la génération précédente si l'on souhaite diminuer la taille des dispositifs on souhaite également qu'ils se comportent comme leur canal était long. Un canal trop court par rapport aux longueurs de déplétion de la source et du drain pourrait annuler toute création de canal. Aussi y-a-t-il des lois à respecter quant aux proportions à adopter comme récapitulé dans le tableau (1.1).

Table 1.1 – Mise à l'échelle d'un MOSFET.[7]

| Paramètre | Champ constant | Tensions constante | Réalité        | Limitation              |

|-----------|----------------|--------------------|----------------|-------------------------|

| L         | $1/\kappa$     | $1/\kappa$         | $1/\kappa$     |                         |

| E         | 1              | >1                 | >1             |                         |

| d         | $1/\kappa$     | $1/\kappa'$        | $> 1/\kappa$   | Effet tunnel, défauts   |

| $r_j$     | $1/\kappa$     | $> 1/\kappa$       | $> 1/\kappa$   | Résistance              |

| $V_T$     | $1/\kappa$     | 1                  | $\gg 1/\kappa$ | Courant OFF             |

| $V_D$     | $1/\kappa$     | 1                  | $\gg 1/\kappa$ | Système global et $V_T$ |

| $N_A$     | κ              | $\kappa$           | < κ            | Claquage de la jonction |

Dans des conditions idéales de champ électrique constant les paramètres sont mis à l'échelle avec le même facteur. En réalité les facteurs de mise à l'échelle sont limités par d'autres raisons et donc faussés. On a  $1 < \kappa' < \kappa$

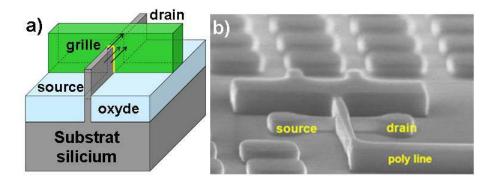

Ces optimisations agressives ne sont possibles qu'à l'aide de très lourds moyens technologiques. A l'heure actuelle le plus petit transistor fabriqué l'est par la société Intel et correspond au nœud 22 nm. Ce dernier a nécessité de développer une nouvelle stratégie quant à la géométrie même des transistors. La grille n'est plus planaire mais en forme de  $\pi$  comme présenté sur les figures 1.12 a) et b).

FIGURE 1.12 – a) schéma de principe et b) image MEB d'un transistor à grille en Pi. [9]

De cette manière le contrôle électrostatique du canal est bien meilleur pour une même surface apparente du transistor. Il est également évident de se dire que cette réduction perpétuelle de taille du transistor verra un jour sa limite arriver, la physique ne permettant évidenment pas de descendre en deçà de l'échelle atomique en terme de réalisations technologiques. Afin de palier à cet inévitable obstacle une nouvelle stratégie s'est mise en place. Le "More than Moore"

# 1.4.2 Approche "More-Than-Moore"

L'idée est la suivante. L'augmentation de la densité surfacique des transistors est très complexe et vise uniquement l'amélioration de la rapidité des microprocesseurs. Aujourd'hui le grand public recherche sans cesse des appareils permettant d'effectuer de nombreuses taches comme de la télécommunication sans fil, du stockage de masse ou même de la prise de vue. Il faut donc trouver une approche permettant non pas d'augmenter la rapidité des microprocesseurs mais le nombre de fonctionnalités qu'il proposent. Pour cela il faut réussir à réunir dans un espace confiné, afin d'avoir un appareil le plus portable possible, un très grand nombre d'outils technologiques. Deux grandes familles technologiques se sont alors développées afin de viser ces objectifs.

- 1. Les "System-on-chip" ou systèmes sur puce (SoC). Ce sont des puces qui condensent en leur sein tous les éléments d'un ordinateur complexe. Elles contiennent souvent des fonctions numériques, analogiques, mixtes et radio-fréquence. Leur principal domaine d'application est celui des systèmes embarqués. Il peut cependant s'avérer extrêmement compliqué de condenser sur une seule puce toutes les fonctionnalités nécessaires et l'on utilise alors un autre type d'intégration.

- 2. Les "System-in-Package" ou systèmes en boitier (SiP). Ce type d'intégration est différent car il s'agit ici de superposer différentes puces réunissant chacune des fonctionnalités bien précises. Dans ce cas les puces sont interconnectées soit à l'aide de fils soit par des méthodes plus complexes que nous allons expliquer par la suite.

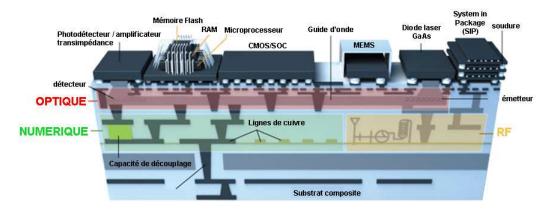

FIGURE 1.13 – Schéma représentant une puce combinant de nombreux composants aux fonctionnalités variées et faisant appel à différentes méthodes de miniaturisation.[10]

Quelle que soit l'approche utilisée ces demandes technologiques requièrent le développement de procédés complexes d'intégration 3D. Il n'est en effet pas si anodin de chercher à empiler un si grand nombre de dispositifs les uns sur les autres. Nous allons présenter dans la suite les méthodes utilisées notamment pour réaliser des SOC qui sont à terme les systèmes les plus prometteurs du fait de leur forte compacité, de leur cout de fabrication et de leur mise en boitier moins complexe que les SiP.

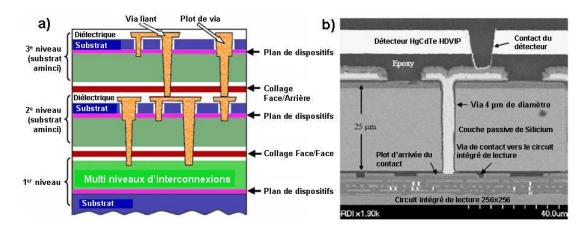

#### 1.4.2.1 Collage

La technique de collage est la suivante. Deux puces sont réalisées de façon standard puis sont superposées et contactées l'une avec l'autre à l'aide de vias traversant ou TSV (Through Silicon Vias). Cette technologie permet d'avoir des transistors de qualité front-end empilés les uns sur les autres et ainsi donc d'augmenter la quantité de dispositifs disponibles en utilisant la dimension verticale. Un exemple est donné dans la figure 1.14 où un détecteur infrarouge et un circuit intégré de lecture ont été élaborés à part puis collés et contactés à l'aide de TSV en cuivre[11]. Cette technologie permet d'empiler un grand nombre de puces sans limite mais présente quelques inconvénients avec notamment la difficulté de contrôler l'alignement des deux puces juxtaposées. Il faut également tenir compte du fait que ce genre d'approche monopolise plusieurs lignes de fabrications en salle blanche pour au final n'obtenir qu'un seul dispositif, ceci posant alors le problème du rendement. De plus l'empilement de nombreuses puce soulève la problématique complexe de l'évacuation de la chaleur générée lors du fonctionnement. Il est en effet difficile de refroidir de telles puces et cela en limite le nombre pouvant être empilées.

FIGURE 1.14 – a) Schéma de principe du collage de puces avec représentation de trois niveaux de dispositifs. b) image MEB d'une coupe d'un détecteur Infrarouge couplé à un circuit intégré de lecture par collage de puces d'après [11].

La technique de collage de puces est donc très prometteuse et largement développée à l'heure actuelle afin de réaliser de l'intégration 3D. Ce mode de fabrication permet d'obtenir des transistors de hautes qualités superposés les uns sur les autres mais nécessite de lourds moyens de production. Nous allons désormais nous intéresser à une toute autre méthode. Ne serait-il pas possible de réaliser directement dans les étapes back-end des transistors? quelles seraient les limites d'une telle approche?

#### 1.4.2.2 L'élaboration directe

Dans le but de fabriquer des SOC l'idéal serait de pouvoir réaliser les différents niveaux les uns sur les autres sans avoir à faire de report de puce, c'est-à-dire en élaborant directement les niveaux supérieurs sur la puce de base. La difficulté réside dans le fait de pouvoir notamment élaborer des composants actifs comme le transistor à des températures suffisamment basses pour éviter la destruction du front-end tout en garantissant de bonnes caractéristiques électriques. A l'heure actuelle les dispositifs réalisés utilisent une couche de silicium polycristallin comme par exemple les SRAM réalisées par Samsung (figure 1.15) avec un empilement sur trois niveaux de six transistors [12].

Figure 1.15 – Image TEM d'un empilement sur trois niveaux de transistors dédiés à la réalisation d'une SRAM par Samsung.[12]

En effet, comme il n'est pas possible de dépasser 450 °C il est impossible en utilisant les méthodes traditionnelles de dépôt de synthétiser un monocristal. L'utilisation d'un poly-cristal conduit donc à des propriétés électriques dégradées. Le but serait de pouvoir élaborer un monocristal avec le respect des conditions thermiques du back-end afin d'utiliser ce matériau comme canal de conduction d'un transistor. Il serait ainsi possible d'élaborer des SOC sans procédé de collage tout en garantissant de bonnes performances des dispositifs élaborés à basse température.

Quel type de transistors pourrait convenir, du point de vue des procédés technologiques, avec les étapes du back-end? Le MOSFET pose de nombreuses problématiques dont une de taille. Les contacts de source et de drain sont des poches de dopage réalisées par implantation ionique suivie de recuits à haute température afin d'activer les dopants. Ces étapes sont simplement impossibles à réaliser sous peine de détruire les dispositifs du front-end. Afin de palier à ce problème une autre structure est proposée : le transistor à effet de champ à barrière Schottky (SBFET).

# 1.5 Un transistor dans le back end : le SBFET (Schottky barrier field-effect transistor)

Le SBFET ou Transistor à Effet de Champ à Barrières Schottky (Schottky Barrier Field-Effect transistor) est une évolution du MOSFET standard dédiée principalement aux applications basse consommation. La différence notable réside dans la nature des contacts de source et de drain. Ainsi, au lieu d'une jonction p-n, le SBFET utilise une barrière Schottky comme contacts de source et de drain. Avant d'expliquer l'intérêt d'une telle structure penchons nous sur la physique du transport électronique au niveau d'une barrière Schottky.

# 1.5.1 La barrière Schottky : électrostatique

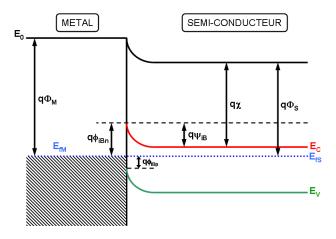

Considérons un métal M et un semi-conducteur S mis en vis à vis, possédant pour le premier un travail de sortie  $q\Phi_M$  et le deuxième une affinité électronique  $q\chi$ . Dans le cas d'un semi-conducteur ou d'un isolant l'affinité électronique représente le travail à fournir à un électron situé en bord de bande de conduction pour l'extraire dans le vide sans vitesse initiale. Par conséquent, et étant donné que  $\Phi_M$  et  $\chi$  sont généralement différents (généralement  $\Phi_M > \chi$  pour le silicium et la plupart des métaux), une barrière de potentiel s'établit lors de la mise en contact des deux matériaux s'opposant au passage des électrons du métal au semi-conducteur. Idéalement la hauteur de barrière  $\phi_{iBn}$  peut être déterminée par :

$$q\phi_{iBn} = q\left(\Phi_M - \chi\right) \tag{1.12}$$

. Le niveau de Fermi du semi-conducteur isolé n'étant généralement pas aligné avec celui du métal isolé, nous pouvons définir pour le semi-conducteur un travail de sortie  $\Phi_S$  comme étant la différence d'énergie entre le niveau du vide et le niveau de Fermi, autrement dit la somme de l'affinité électronique et de la différence d'énergie entre la bande de conduction et le niveau de Fermi. A l'issue de la mise en contact des deux matériaux, l'équilibre thermodynamique est atteint et donne lieu à l'alignement des deux niveaux de Fermi, induisant un transfert de charges entre le métal et le semi-conducteur. Ceci a pour conséquence de courber les bandes de valence et de conduction du semi-conducteur à l'interface M/S. En effet la densité d'états étant considérablement plus grande dans le métal que dans le semi-conducteur, seules les premières couches atomiques du métal seront concernées par le rééquilibrage des charges satisfaisant à la condition d'équilibre, contrairement au semi-conducteur qui sera affecté sur des distances bien plus grandes. Si l'alignement des

niveaux de Fermi repousse les porteurs majoritaires du semi-conducteur loin de l'interface, ce qui est le cas pour  $\Phi_S^n < \Phi_M$ , alors le contact est redresseur. En effet dans cette configuration les bords de bande de conduction s'éloignent de plus en plus du niveau de Fermi au fur et à mesure que l'on se rapproche de l'interface, induisant par là-même du fait de la statistique de Boltzmann une désertion progressive de porteurs majoritaires peuplant les états de conduction et responsables du transport électronique. Si au contraire la courbure de bande à l'interface favorise énergétiquement la présence des porteurs majoritaires, ce qui est le cas pour  $\Phi_S^n > \Phi_M$ , alors le contact sera ohmique. La figure 1.16 montre l'exemple d'un semi-conducteur de type n formant une jonction Schottky de type redresseur.

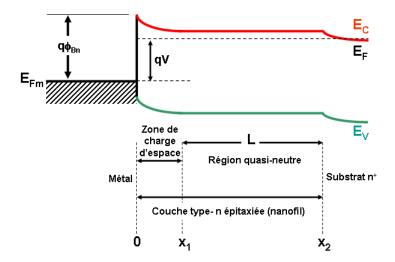

$\label{eq:figure 1.16-Schema} Figure \ 1.16-Schema \ d'un \ contact \ Schottky \ idéal \ métal/semi-conducteur \ pour \ un \ semi-conducteur \ de \ type \ n$

La chute de potentiel  $\Psi_{iB}$  dans le semi-conducteur est donnée par :

$$\Psi_{iB} = -\mid \Phi_M - \Phi_S \mid \tag{1.13}$$

La région dans laquelle la distribution de la charge est modifiée par rapport au semi-conducteur massif est appelée la région de déplétion ou zone de charge d'espace. Le profil du potentiel électrique peut être calculé simplement en résolvant l'équation de Poisson à une dimension, perpendiculairement à l'interface M/S, connaissant la distribution de la charge totale :

$$\rho = q\left(N_d - N_a + p - n\right) \tag{1.14}$$

avec  $N_d$  et  $N_a$  concentrations  $(cm^{-3})$  des dopants donneurs et accepteurs respectivement, supposés tous ionisés, dans le semi-conducteur massif supposé de type n , p est la concentration de trous libres et n la concentration d'électrons libres. En appliquant le théorème de Gauss et en considérant  $N_a$  et p comme négligeables nous trouvons que la largeur de déplétion W est définie comme :

$$W_D = \sqrt{\frac{2\varepsilon_S}{qN_d} \left(\Psi_{bi} - \frac{kT}{q}\right)} \tag{1.15}$$

Lorsqu'une tension est appliquée le potentiel et la largeur de déplétion sont modifiés. Appliquer une tension positive (négative) sur le métal augmente le nombre de porteurs à la surface du semi-conducteur et ainsi diminue en valeur absolue (augmente) le potentiel électrostatique et la courbure des bandes.

Expérimentalement les équations (1.12) et (1.13) ne prédisent pas correctement la hauteur de barrière et la courbure des bandes. Ceci s'explique par la présence d'états d'interfaces responsables de la modification de la barrière comme expliqué pour la première fois par Bardeen en 1947. Les états de surface induisent une couche chargée à l'interface responsable d'une variation du potentiel de surface du semi-conducteur par rapport au niveau de Fermi du métal, modifiant par là même la hauteur de barrière vue par les électrons désirant traverser l'interface. Si la densité de charges d'interface est grande, alors la barrière à franchir pour les électrons devient indépendante du travail de sortie du métal et est fixée par la densité de charges piégées en surface et par le taux de dopage du semi-conducteur. Dans ce cas, on parle de "Fermi-level pinning" ou littéralement "l'accrochage du niveau de Fermi".

Le modèle de Bardeen a été proposé en considérant la présence une couche interfaciale entre le métal et le semi-conducteur et a été par la suite revu afin d'expliquer ces états d'interface sans cette couche. Il y a principalement deux idées permettant d'expliquer ces états d'interface : les états induits dans le gap par le métal (ou MIGS pour metal induced gap states) et les défauts d'interface. Dans le premier cas les états d'interface sont provoqués par la queue de la fonction d'onde des électrons du métal qui s'étend au travers de l'interface. Dans le second cas l'interruption du potentiel périodique des deux matériaux conduit à des états défauts s'étendant au travers de l'interface métal/semi-conducteur. Ces modèles ont été discutés en détails par Rhoderick. Bien que les résultats expérimentaux concordent avec ces équations l'origine de ces états d'interfaces n'est pas clairement comprise. En 2000 Tung proposa que le Fermi level pinning était dû aux liaisons chimiques entre le métal et le semi-conducteur[13].

Malgré les difficultés à avoir un modèle physique précis quant à l'origine exacte de la formation de ces états d'interface, la hauteur de barrière peut être déterminée expérimentalement selon les méthodes que nous présenterons par la suite. Nous distinguerons par la suite les barrières vues par les électrons n- et par les trous p-. Aussi nous désignerons par  $\phi_{Bn}$  la barrière associée aux électrons et par  $\phi_{Bp}$  la barrière associée aux trous. Idéalement la somme des deux barrières est égale au gap du semi-conducteur,  $(E_G = \phi_{Bn} + \phi_{Bp})$ .

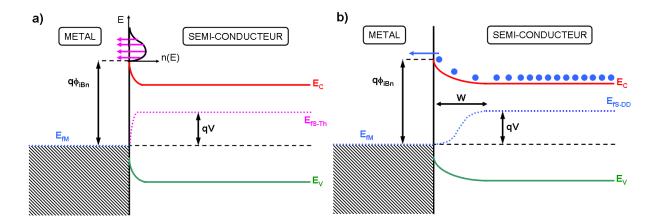

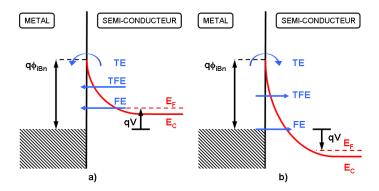

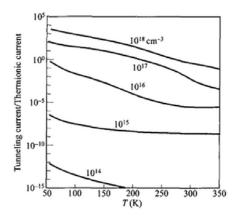

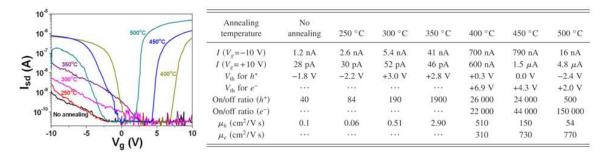

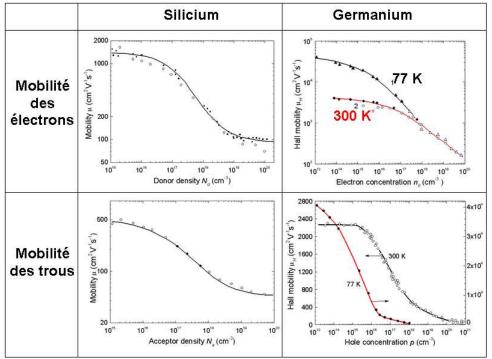

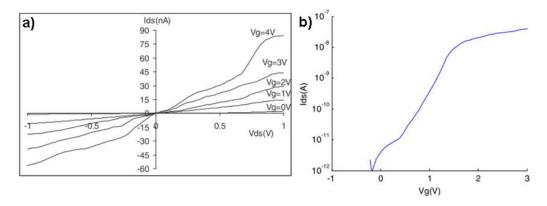

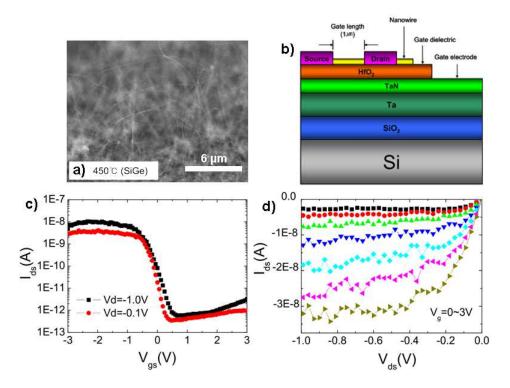

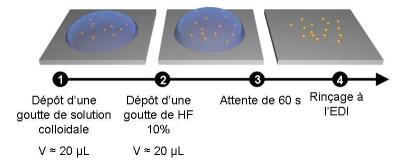

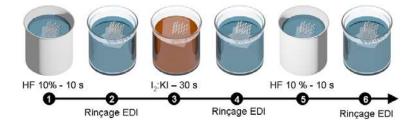

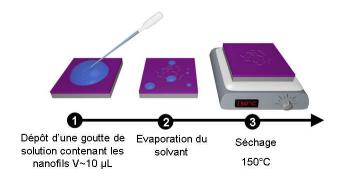

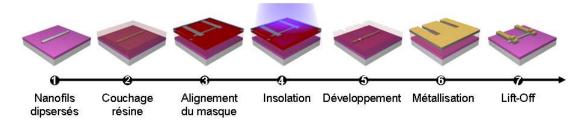

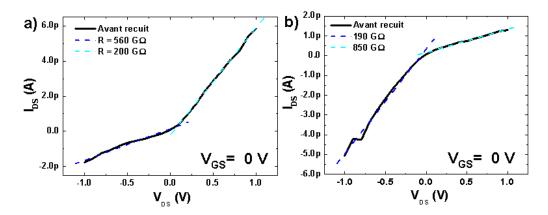

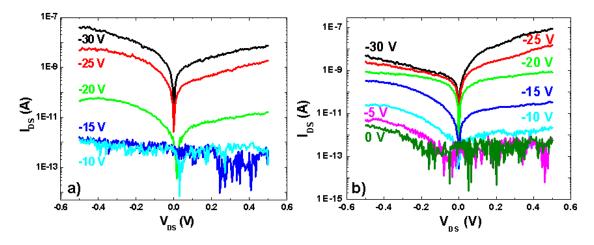

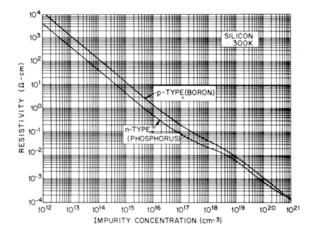

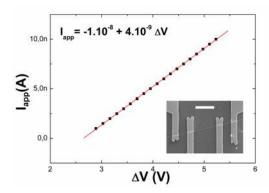

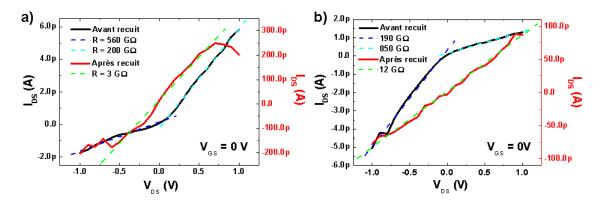

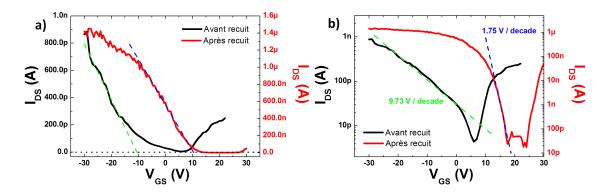

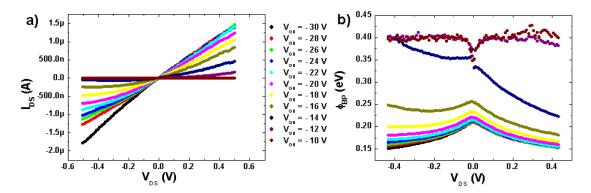

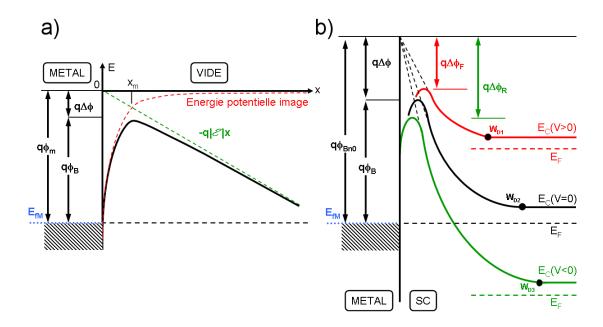

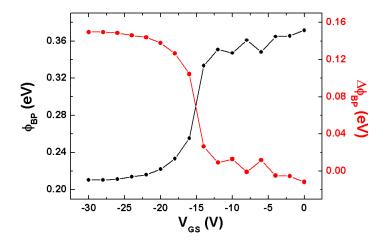

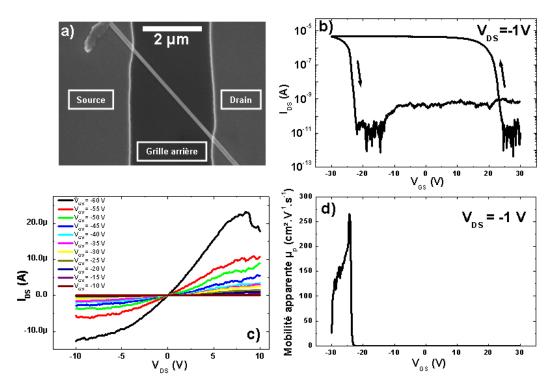

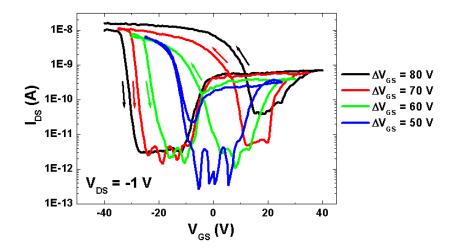

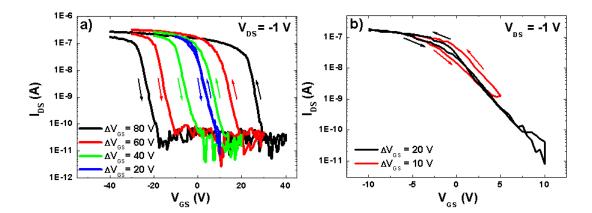

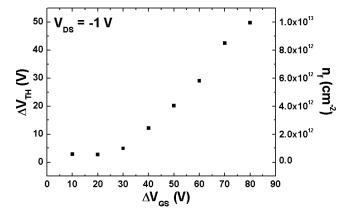

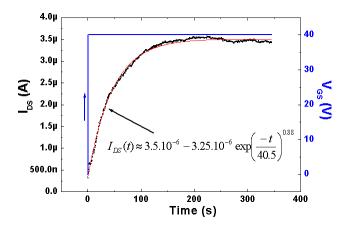

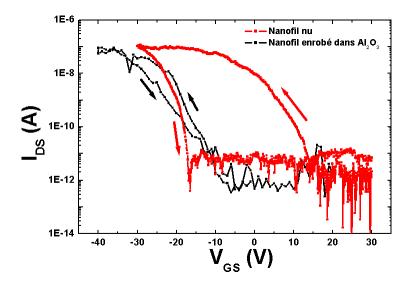

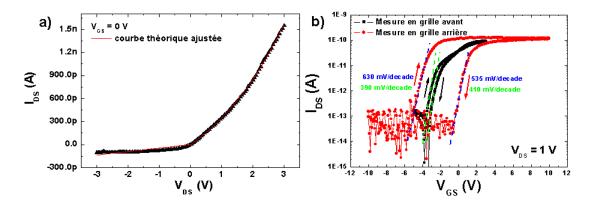

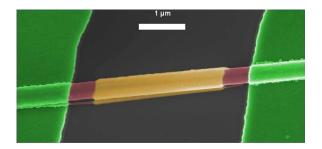

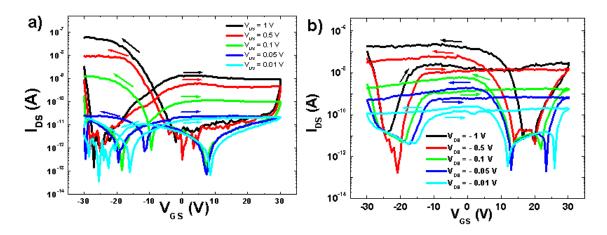

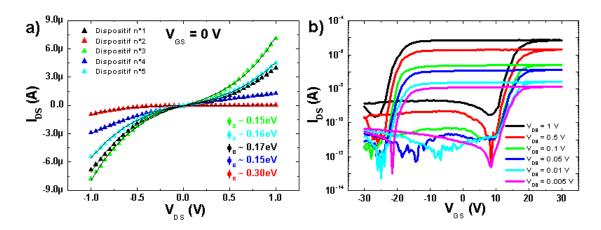

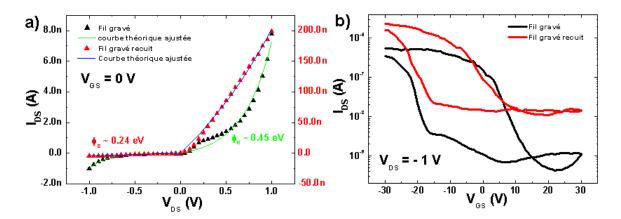

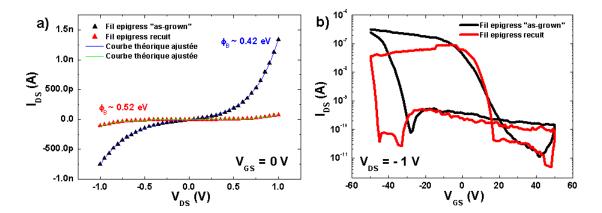

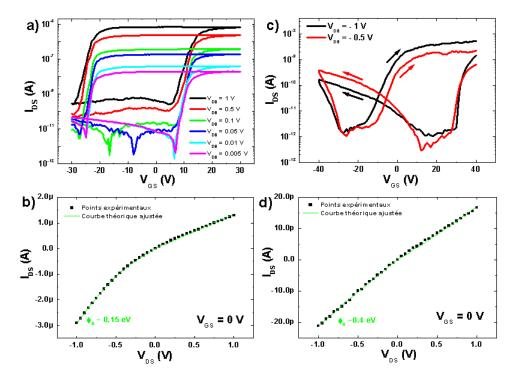

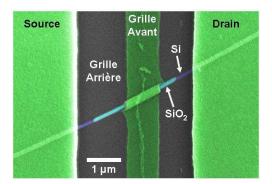

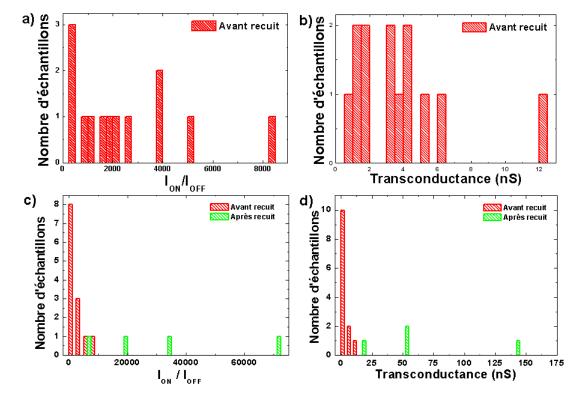

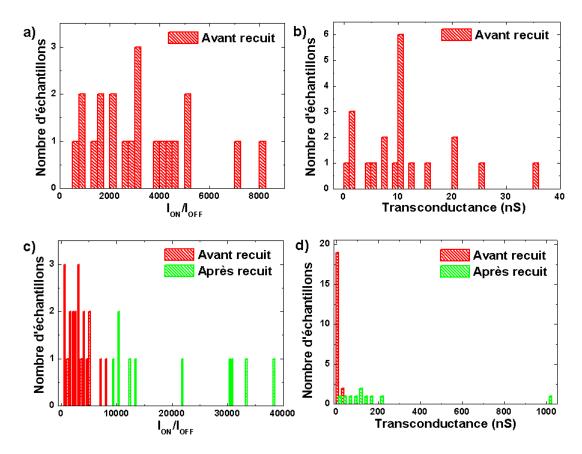

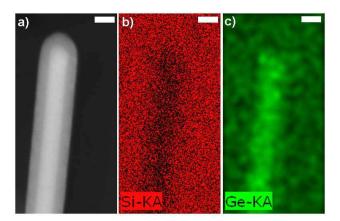

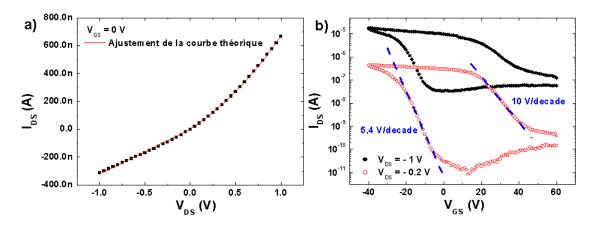

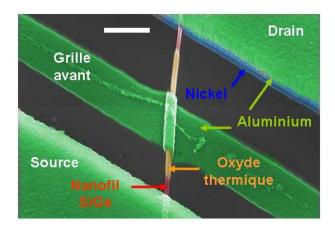

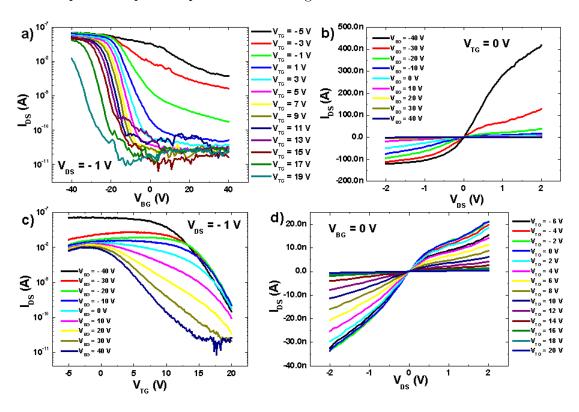

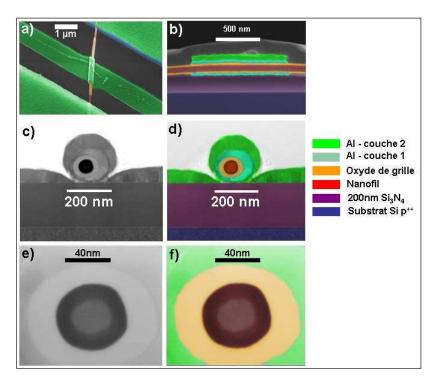

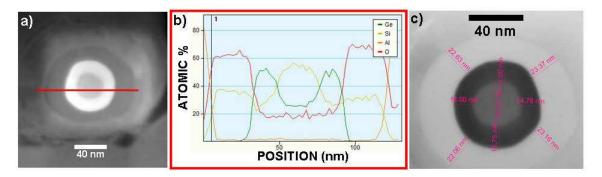

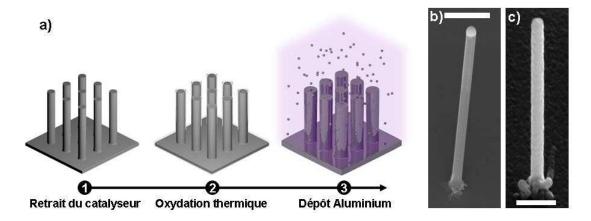

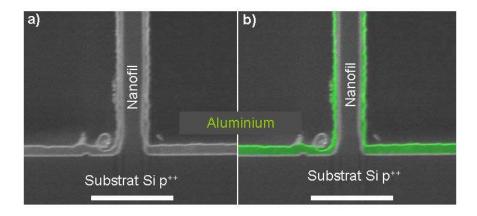

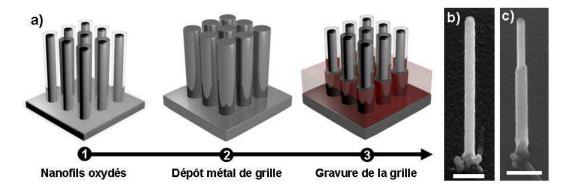

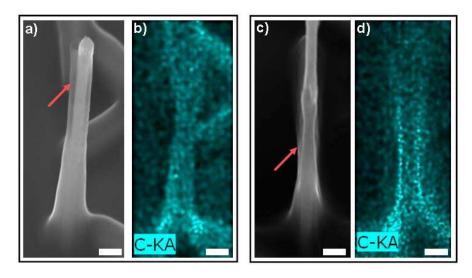

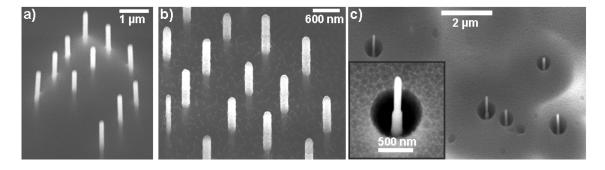

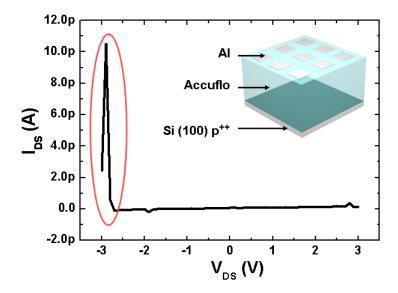

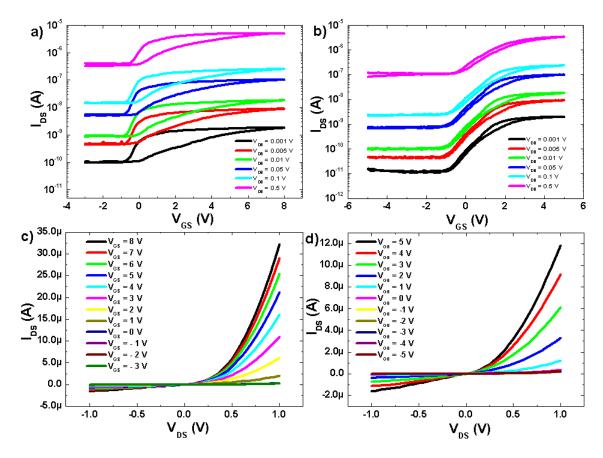

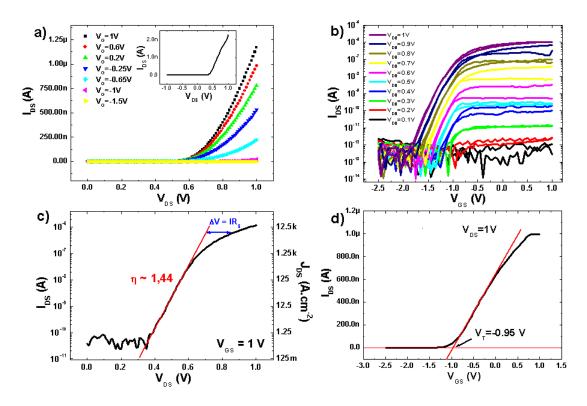

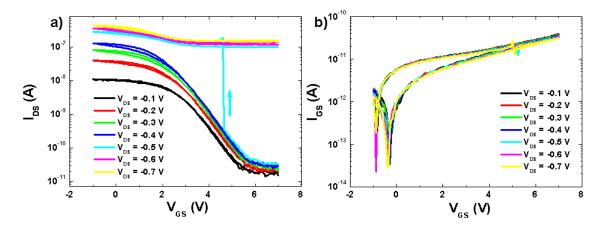

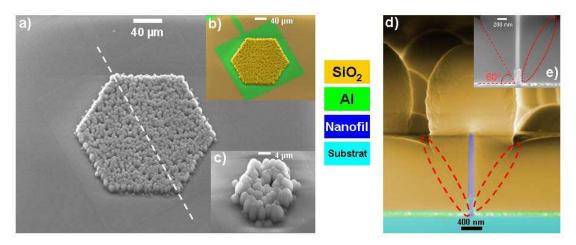

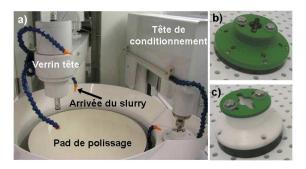

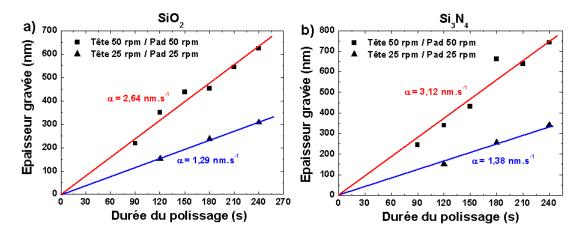

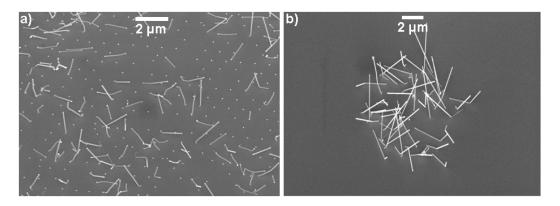

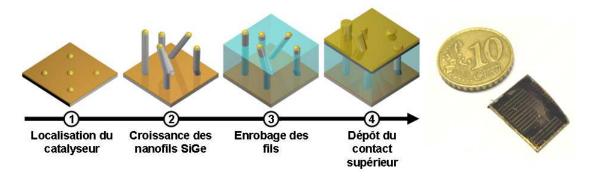

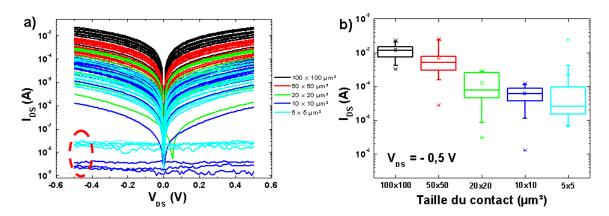

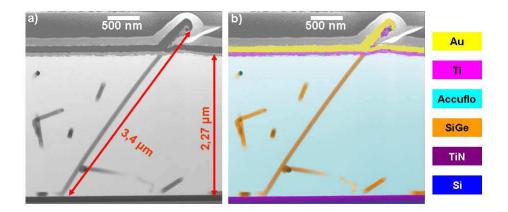

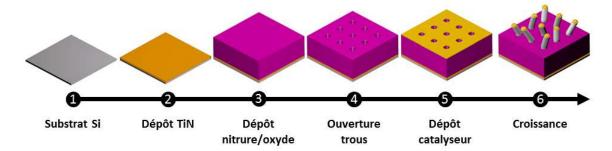

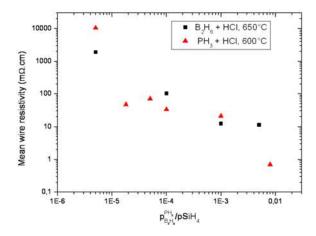

#### 1.5.2 Mécanismes de transport dans un contact Métal/Semi-conducteur