# Linearization of a Transmitter using an IC Digital/Analog Cartesian Feedback in CMOS 65nm for Advanced Communication Standards

Nicolas Delaunay

#### ▶ To cite this version:

Nicolas Delaunay. Linearization of a Transmitter using an IC Digital/Analog Cartesian Feedback in CMOS 65nm for Advanced Communication Standards. Electronics. Université Sciences et Technologies - Bordeaux I, 2012. English. NNT: . tel-00991923

### HAL Id: tel-00991923 https://theses.hal.science/tel-00991923

Submitted on 3 Dec 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Public Domain

No d'ordre:

### THÈSE

présentée à

### L'Université Bordeaux 1

Ecole Doctorale des Sciences Physiques et de l'Ingénieur

#### par Nicolas Delaunay

Pour obtenir le grade de

#### Docteur

SPÉCIALITÉ : ÉLECTRONIQUE

Linearization of a Transmitter using an IC Digital/Analog Cartesian Feedback in CMOS 65nm for Advanced Communication Standards

Version du : 19 octobre 2012

Après avis de :

M. Jean-Louis Cazaux Professeur Thales Alenia Space Rapporteur

M. Jean-Michel Nebus Professeur XLIM de Limoges Rapporteur

#### Devant la commission d'examen formée de :

| M.            | Didier Belot         | Ingénieur             | STMicroelectronics, Grenoble | Tuteur industriel     |

|---------------|----------------------|-----------------------|------------------------------|-----------------------|

| Mlle          | Nathalie Deltimple   | Maître de Conférences | IPB ENSEIRB-MATMECA          | Co-directeur de Thèse |

| M.            | Eric Kerhervé        | Professeur            | IPB ENSEIRB-MATMECA          | Directeur de Thèse    |

| M.            | Vincent Knopik       | Ingénieur             | STEricsson                   | Examinateurs          |

| M.            | Philippe Torregrossa | Ingénieur             | Agilent                      | Examinateurs          |

| $\mathbf{M}.$ | Dominique Dallet     | Professeur            | IPB ENSEIRB-MATMECA          | Examinateurs          |

Citation

- Auteur

# Remerciements

A faire plus tard

| 1 | Line | earizat | n of a Transmitter                                                 | <b>17</b> |

|---|------|---------|--------------------------------------------------------------------|-----------|

|   | 1.1  | Mobile  | Communication Standards                                            | 18        |

|   | 1.2  | Transı  | tter Architectures                                                 | 21        |

|   |      | 1.2.1   | Heterodyne transmitter architecture                                | 21        |

|   |      | 1.2.2   | Direct conversion transmitter architecture                         | 22        |

|   |      | 1.2.3   | Low-IF transmitter architecture                                    | 23        |

|   |      | 1.2.4   | Offset-PLL transmitter architecture                                | 24        |

|   |      | 1.2.5   | Summary of transmitter architectures                               | 25        |

|   | 1.3  | Nonlin  | ar Behavior of a RF Transmitter                                    | 26        |

|   |      | 1.3.1   | AM/AM and AM/PM conversion                                         | 26        |

|   |      | 1.3.2   | Carrier to Intermodulation ratio (C/In)                            | 28        |

|   |      | 1.3.3   | Adjacent Channel Power Ratio (ACPR)                                | 29        |

|   |      | 1.3.4   | Noise Power Ratio (NPR)                                            | 30        |

|   |      | 1.3.5   | Error Vector Magnitude (EVM)                                       | 31        |

|   | 1.4  | Linear  | ation Techniques                                                   | 32        |

|   |      | 1.4.1   | Tradeoffs between linearity and efficiency                         | 32        |

|   |      |         | .4.1.1 Classes of power amplifier                                  | 32        |

|   |      |         | .4.1.2 Efficiency                                                  | 33        |

|   |      |         | .4.1.3 Nonlinearity                                                | 34        |

|   |      | 1.4.2   | Power back-off                                                     | 38        |

|   |      | 1.4.3   | Efficiency improvement                                             | 38        |

|   |      |         | .4.3.1 Envelope Tracking (ET)                                      | 38        |

|   |      |         | .4.3.2 Envelope Elimination and Restoration (EER)                  | 39        |

|   |      |         | .4.3.3 LInear amplification with Nonlinear Components(LINC) / Com- |           |

|   |      |         | bined Analogue Locked Loop Universal Modulator (CALLUM) .          | 40        |

|   |      |         | .4.3.4 Doherty technique                                           | 42        |

|   |      | 1 4 4   | inearity improvement                                               | 45        |

|   |     |          | 1.4.4.1 Predistortion / Postdistortion                                  | 45 |

|---|-----|----------|-------------------------------------------------------------------------|----|

|   |     |          | 1.4.4.2 Adaptive predistortion                                          | 47 |

|   |     |          | 1.4.4.3 Feedforward                                                     | 47 |

|   |     |          | 1.4.4.4 Polar Feedback                                                  | 49 |

|   |     |          | 1.4.4.5 Cartesian Feedback                                              | 50 |

|   | 1.5 | Concl    | usion                                                                   | 51 |

| 2 | Ana | alysis a | and Specifications of the Cartesian Feedback Loop                       | 53 |

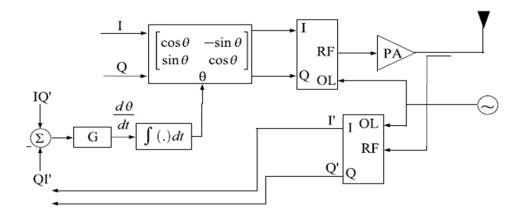

|   | 2.1 | Digita   | l/Analog Partitioning Architecture of the Transmitter                   | 54 |

|   | 2.2 | Mathe    | ematical Analysis of the Cartesian Feedback Loop                        | 56 |

|   |     | 2.2.1    | Stability study                                                         | 56 |

|   |     |          | 2.2.1.1 Modeling of the Cartesian Feedback                              | 56 |

|   |     |          | 2.2.1.2 Influence of phase shifting on the stability                    | 58 |

|   |     |          | 2.2.1.3 Graphical criteria of the stability                             | 59 |

|   |     | 2.2.2    | Noise study                                                             | 60 |

|   |     | 2.2.3    | Linearity                                                               | 61 |

|   |     | 2.2.4    | Bandwidth of the loop                                                   | 63 |

|   |     | 2.2.5    | LO pulling on Zero-IF architecture                                      | 64 |

|   |     | 2.2.6    | DC offset                                                               | 65 |

|   | 2.3 | Digita   | l Part                                                                  | 65 |

|   |     | 2.3.1    | Context and constraints                                                 | 65 |

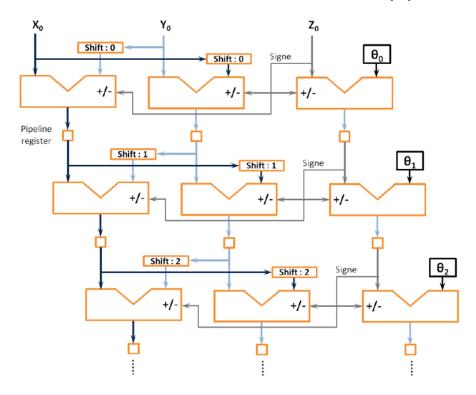

|   |     | 2.3.2    | CORDIC implementation                                                   | 66 |

|   |     |          | 2.3.2.1 CORDIC algorithm                                                | 67 |

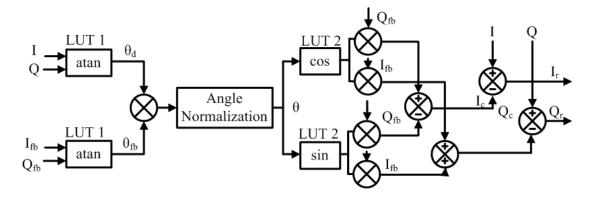

|   |     |          | 2.3.2.2 Normalization of the angle $\theta$                             | 71 |

|   |     |          | 2.3.2.3 Subtraction                                                     | 71 |

|   |     | 2.3.3    | LUTs implementation                                                     | 72 |

|   |     |          | 2.3.3.1 LUTs optimization                                               | 72 |

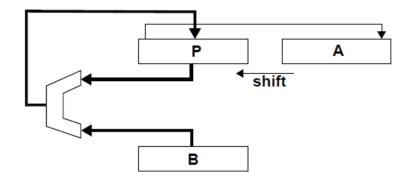

|   |     |          | 2.3.3.2 The Restoring Division Algorithm (RDA) divider                  | 72 |

|   |     |          | 2.3.3.3 Conclusion of the digital part                                  | 73 |

|   | 2.4 | Integr   | ation of the Cartesian Feedback on Silicon                              | 74 |

|   | 2.5 | Syster   | n Level Behavior                                                        | 76 |

|   |     | 2.5.1    | System Level Behavior of the Cartesian Feedback According to the State- |    |

|   |     |          |                                                                         | 77 |

|   |     | 2.5.2    | System Level Behavior of the Cartesian Feedback Using a Power Amplifier |    |

|   |     |          | in BiCMOS7RF technology                                                 | 78 |

|    |       | 2.5.3   | System Level Behavior of the Cartesian Feedback Using a Power Amplifier |     |

|----|-------|---------|-------------------------------------------------------------------------|-----|

|    |       |         | in 65nm CMOS technology                                                 | 81  |

|    | 2.6   | Conclu  | asion                                                                   | 84  |

| 3  | A F   | ully In | ntegrated Transmitter Using a Digital/Analog Cartesian Feedback         | 87  |

|    | 3.1   | A Digi  | ital Solution for the Phase Alignment and Subtraction                   | 89  |

|    |       | 3.1.1   | Synthesis and Implementation on a 65nm CMOS technology                  | 89  |

|    |       |         | 3.1.1.1 Synthesis with Relaxed Constraints                              | 90  |

|    |       |         | 3.1.1.2 Incremental Synthesis                                           | 92  |

|    |       |         | 3.1.1.3 Synthesis with Severe Constraints                               | 92  |

|    |       | 3.1.2   | Place & Route (mapping) of the digital part                             | 93  |

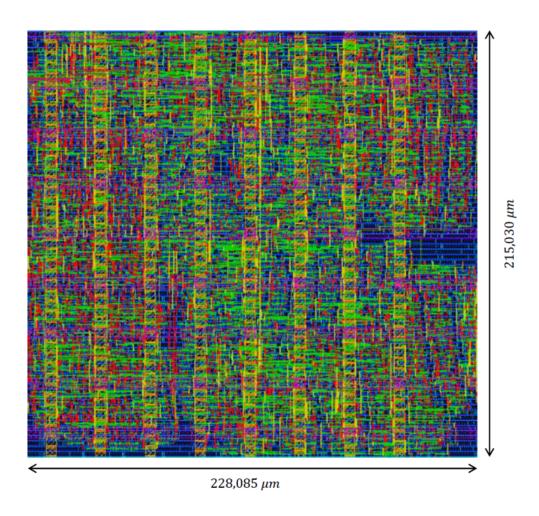

|    |       | 3.1.3   | Die Area of the Digital Part                                            | 93  |

|    |       | 3.1.4   | Conclusion of the Digital Part                                          | 94  |

|    | 3.2   | Details | s of the Analog Circuit on CMOS 65nm from STMicroelectronics            | 95  |

|    |       | 3.2.1   | Digital-to-Analog Converter (DAC)                                       | 95  |

|    |       | 3.2.2   | Active Filter                                                           | 97  |

|    |       | 3.2.3   | Active Up-Conversion Mixer                                              | 100 |

|    |       | 3.2.4   | Power Amplifier (PA)                                                    | 102 |

|    |       | 3.2.5   | Attenuator                                                              | 105 |

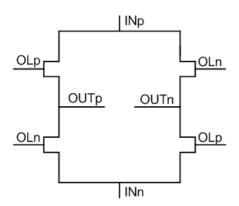

|    |       | 3.2.6   | Passive down-conversion mixer                                           | 108 |

|    |       | 3.2.7   | Analog-to-Digital converter (ADC)                                       | 109 |

|    |       | 3.2.8   | Circuit assembly                                                        | 111 |

|    | 3.3   | Linear  | rization Results                                                        | 114 |

|    |       | 3.3.1   | Methodology of Co-Simulations Experiments                               | 114 |

|    |       | 3.3.2   | Co-simulation results                                                   | 117 |

|    | 3.4   | Compa   | arison with the State-of-the-Art                                        | 120 |

| Co | onclu | sion    |                                                                         | 123 |

| Bi | bliog | graphy  |                                                                         | 129 |

# List of Figures

| 1.1  | Heterodyne transmitter architecture                                           | 21 |

|------|-------------------------------------------------------------------------------|----|

| 1.2  | Direct conversion transmitter architecture                                    | 22 |

| 1.3  | Low-IF transmitter architecture                                               | 24 |

| 1.4  | Offset-PLL transmitter architecture                                           | 24 |

| 1.5  | AM/AM and AM/PM conversion                                                    | 27 |

| 1.6  | Output power and efficiency of a PA versus input power                        | 28 |

| 1.7  | Signal with two carriers in timed (a) and frequency (b) domains $\dots \dots$ | 28 |

| 1.8  | Carrier to Intermodulation ratio                                              | 29 |

| 1.9  | Adjacent Channel Power Ratio spectrum                                         | 30 |

| 1.10 | Noise Power Ratio                                                             | 31 |

| 1.11 | Error Vector Magnitude                                                        | 31 |

| 1.12 | Definition of the compression point                                           | 35 |

| 1.13 | Input and output spectrum of a nonlinear amplifier after compression          | 36 |

| 1.14 | Definition of the third order intermodulation product                         | 37 |

| 1.15 | Discrete Envelope Tracking                                                    | 38 |

| 1.16 | Continuous Envelope Tracking                                                  | 39 |

| 1.17 | Envelope Elimination and Restoration                                          | 40 |

| 1.18 | Principle of LINC technique                                                   | 41 |

| 1.19 | CALLUM technique                                                              | 42 |

| 1.20 | Doherty technique                                                             | 43 |

| 1.21 | Evolution of the efficiency for a two stage Doherty amplifier                 | 44 |

| 1.22 | Predistortion technique                                                       | 45 |

| 1.23 | Signal before and after predistortion technique                               | 46 |

| 1.24 | Example of an adaptive predistortion                                          | 47 |

| 1.25 | Feedforward technique                                                         | 48 |

| 1.26 | Polar loop technique                                                          | 49 |

| 1.27 | Cartesian Feedback technique                                                  | 50 |

10 List of Figures

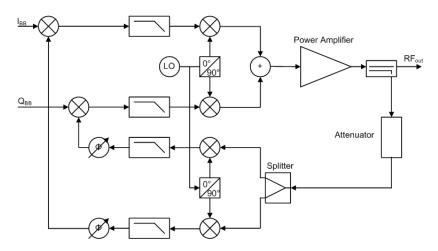

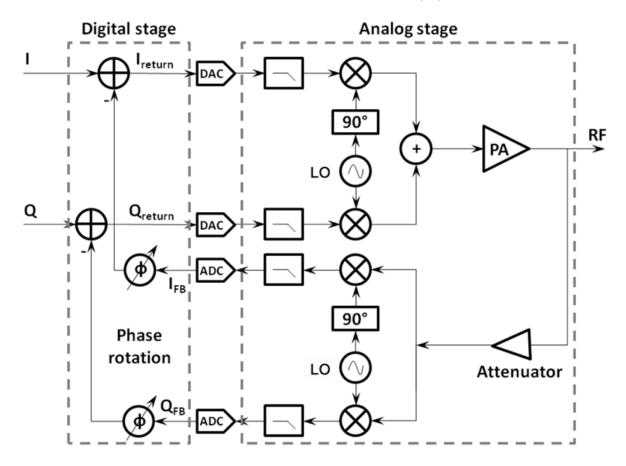

| 2.1  | Mixed architecture of the Cartesian Feedback                               | 55 |

|------|----------------------------------------------------------------------------|----|

| 2.2  | Simplified model of an open loop transmitter                               | 56 |

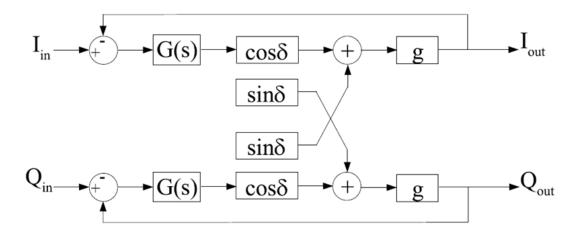

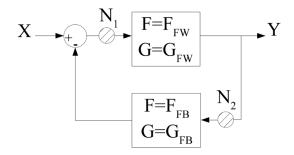

| 2.3  | MIMO model of the Cartesian Feedback                                       | 57 |

| 2.4  | Coupling of the I and Q paths by phase shifting                            | 58 |

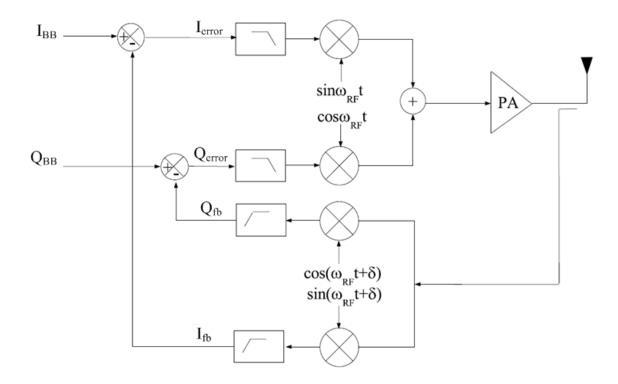

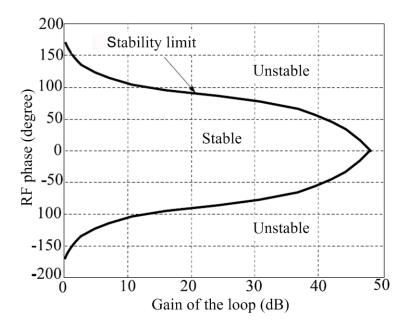

| 2.5  | Graphical criteria of the instability                                      | 60 |

| 2.6  | Noise model of the Cartesian Feedback                                      | 60 |

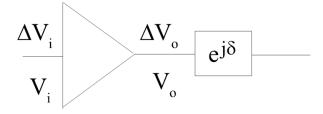

| 2.7  | Linearity model of the Cartesian Feedback                                  | 62 |

| 2.8  | Output transmitted spectrum                                                | 63 |

| 2.9  | Bandwidth of the Cartesian Feedback                                        | 64 |

| 2.10 | Pulling injection for a Zero-IF transmitter                                | 64 |

| 2.11 | LO leakage for a RF transmitter                                            | 65 |

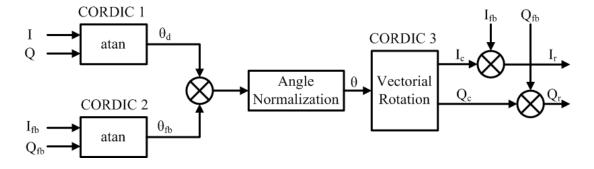

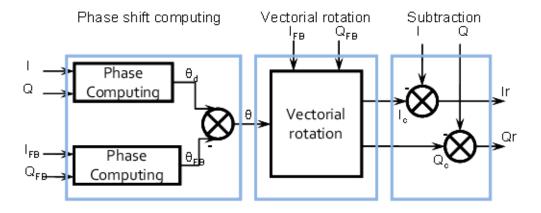

| 2.12 | Solution based on CORDIC algorithm                                         | 66 |

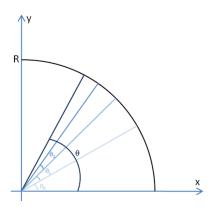

| 2.13 | Vectorial rotation by a $\theta$ angle                                     | 68 |

| 2.14 | Iterative convergence of CORDIC algorithm                                  | 68 |

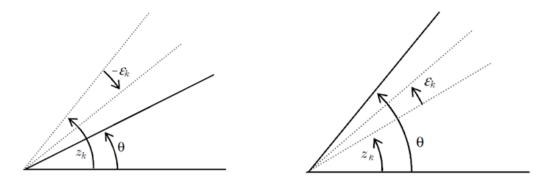

| 2.15 | Updating of $Z_k$ value                                                    | 70 |

| 2.16 | Parallel CORDIC with pipelined register                                    | 71 |

| 2.17 | Solution based on LUT                                                      | 72 |

| 2.18 | Restoring division algorithm                                               | 73 |

| 2.19 | Automatic phase correction using a Cartesian Feedback                      | 74 |

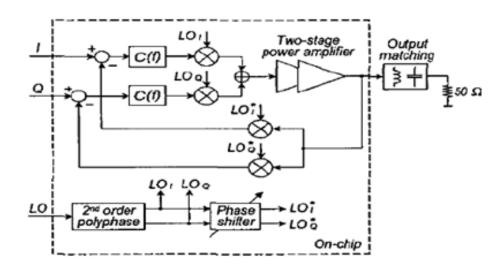

| 2.20 | Heterodyne transmitter using Cartesian Feedback loop for W-CDMA standard ′ | 75 |

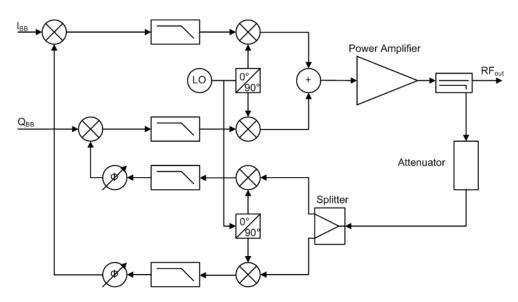

| 2.21 | Cartesian Feedback technique                                               | 77 |

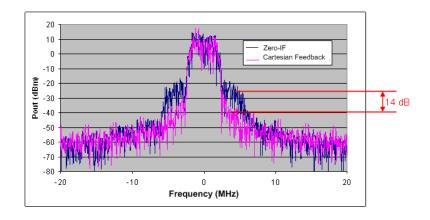

| 2.22 | Spectrum with and without linearization                                    | 78 |

| 2.23 | Schematic of the BiCMOS7RF power amplifier                                 | 79 |

| 2.24 | Layout of (a) the power amplifier and its (b) IPD associated               | 79 |

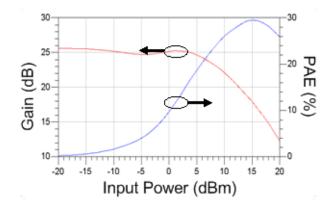

| 2.25 | Gain and efficiency of the PA according to the input power                 | 80 |

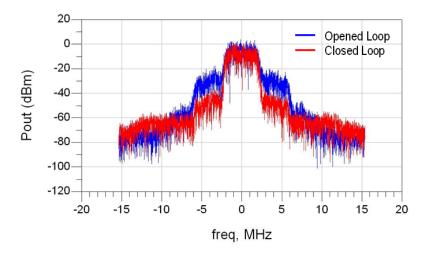

| 2.26 | Spectrum with and without CFB                                              | 80 |

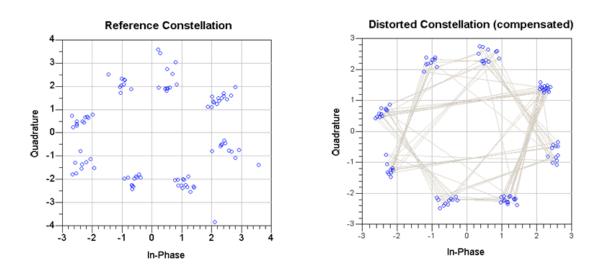

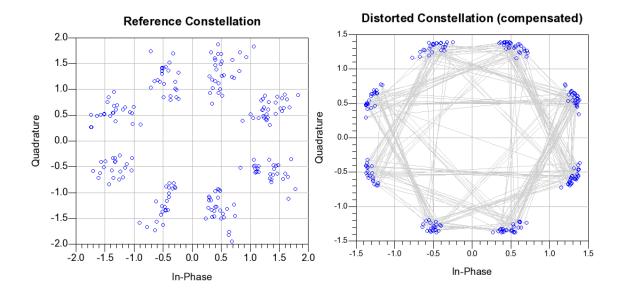

| 2.27 | Input and output constellation of the power amplifier                      | 81 |

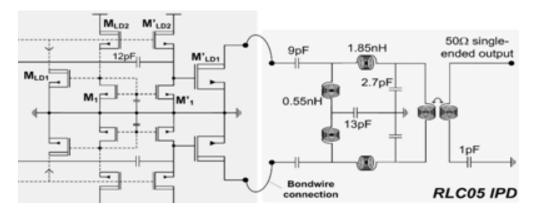

| 2.28 | Schematic of the 65nm CMOS power amplifier                                 | 82 |

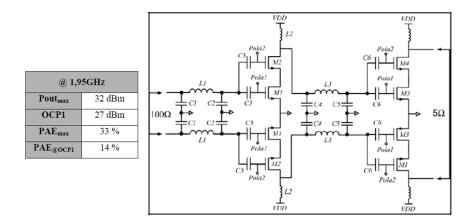

| 2.29 | SFFDS structure and PA performance associated                              | 82 |

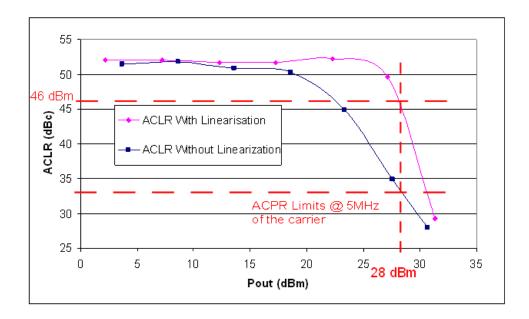

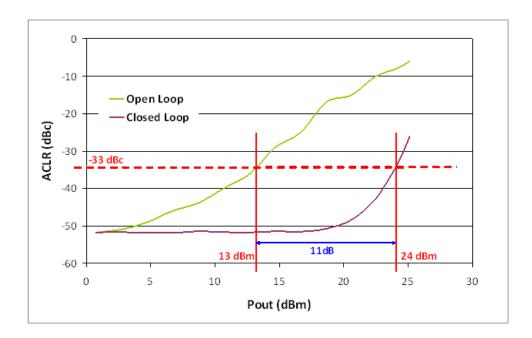

| 2.30 | ACLR improvement with and without Cartesian Feedback                       | 84 |

| 3.1  | Synoptic of the Digital Part                                               | 89 |

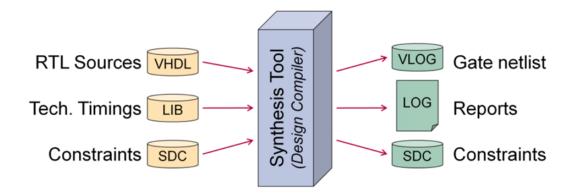

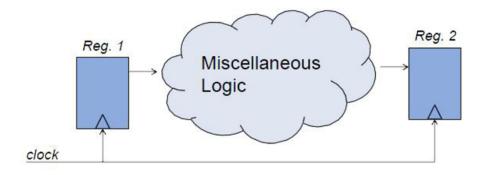

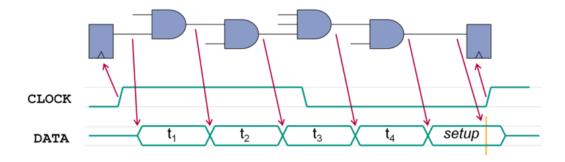

| 3.2  | Graphical Illustration of the Synthesis Tool                               | 90 |

| 3.3  | Register Level Descriptions                                                | 90 |

| 3.4  | Time-Driving Step                                                          | 91 |

| 3.5  | Die Area of the Mixed CORDIC Solution                                      | 94 |

List of Figures 11

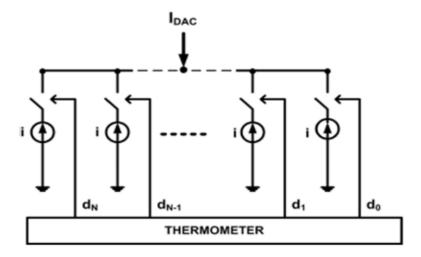

| 3.6  | General Unit-Element Current Steering DAC               |

|------|---------------------------------------------------------|

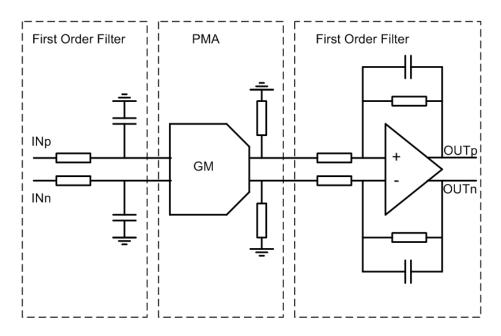

| 3.7  | Architecture of the Active Filter                       |

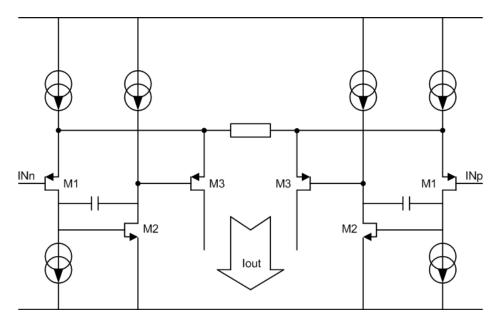

| 3.8  | Schematic of the PMA                                    |

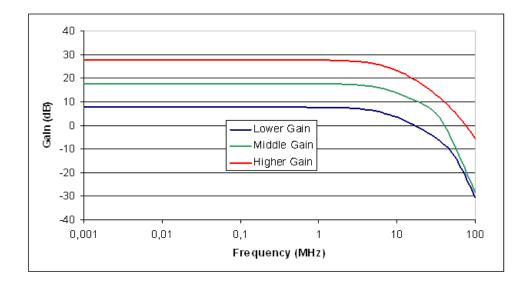

| 3.9  | Gain of the Filter According the PMA's Functioning Mode |

| 3.10 | Die Area of the Active Filter                           |

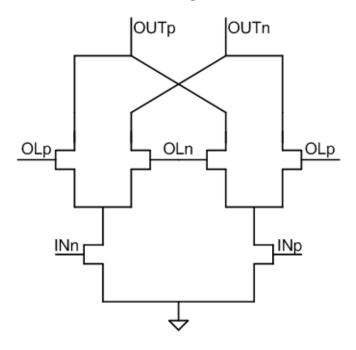

| 3.11 | Schematic of the Gilbert Cell                           |

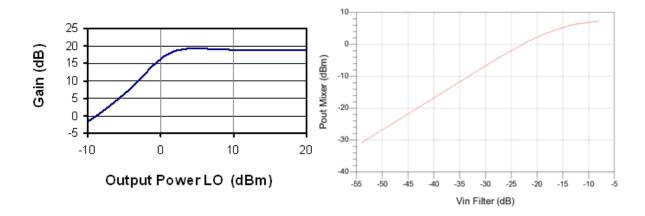

| 3.12 | Gain Conversion and Linearity of the Active Mixer       |

| 3.13 | Die Area of the Up-Conversion Mixer                     |

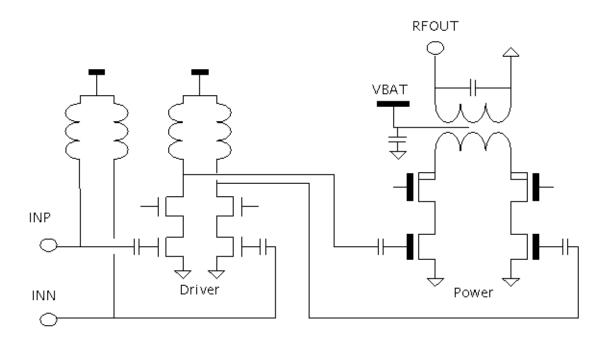

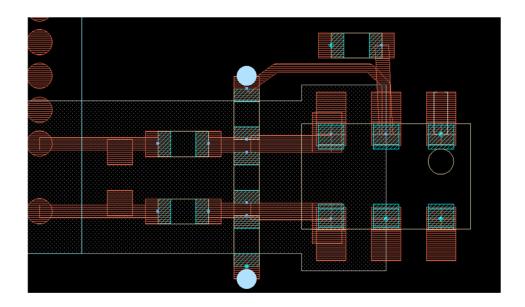

| 3.14 | Topology of the Power Amplifier                         |

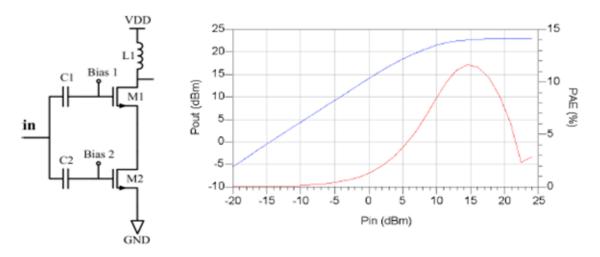

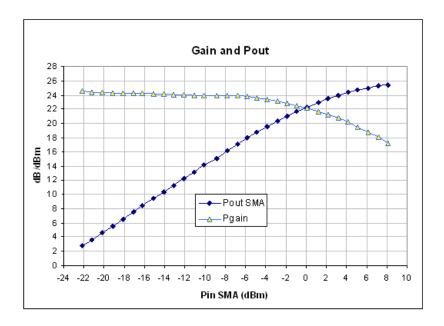

| 3.15 | Gain and Output Power of the Power Amplifier            |

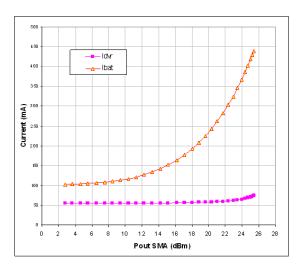

| 3.16 | Current Consumption of the PA                           |

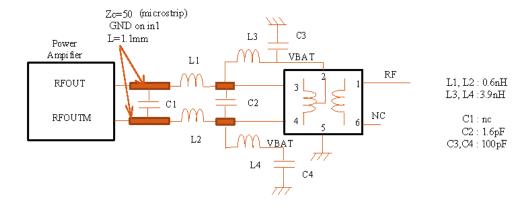

| 3.17 | Schematic of PCB for the Output of the PA               |

| 3.18 | Realization of the PCB on ADS                           |

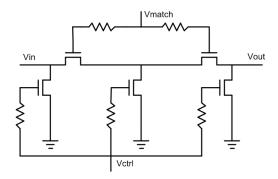

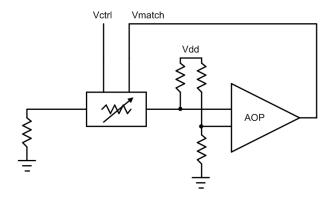

| 3.19 | Schematic of the Designed Attenuator                    |

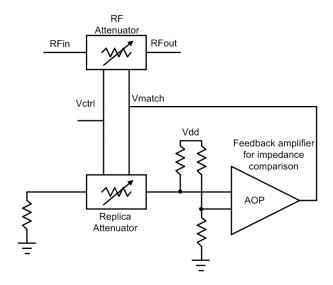

| 3.20 | Feedback Loop for Impedance Matching                    |

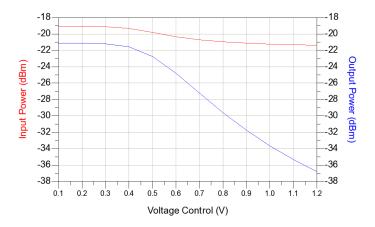

| 3.21 | Input and Output Signal Variation of the Attenuator     |

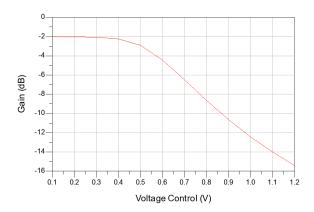

| 3.22 | Gain According Voltage Control of the Attenuator        |

| 3.23 | Whole Topology of the Attenuator                        |

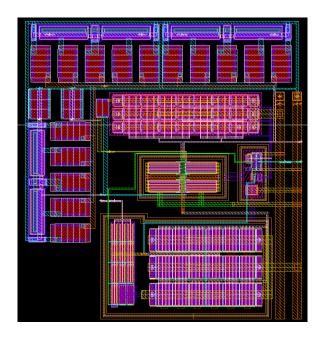

| 3.24 | Die Area of the Attenuator                              |

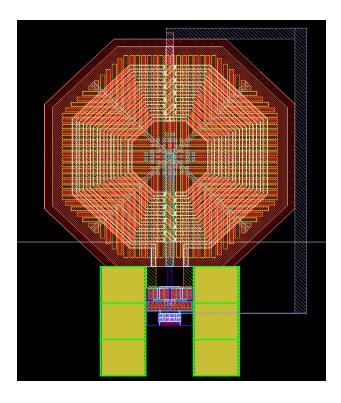

| 3.25 | Topology of the Passive Mixer                           |

| 3.26 | Die Area of the Down-Mixer                              |

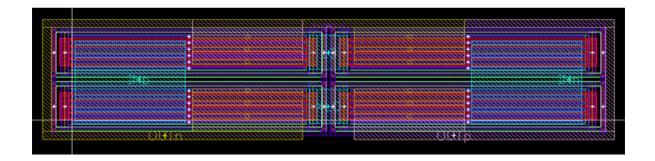

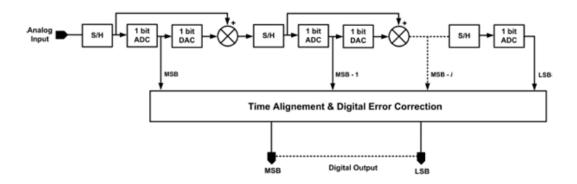

| 3.27 | Classical architecture of a pipelined converter         |

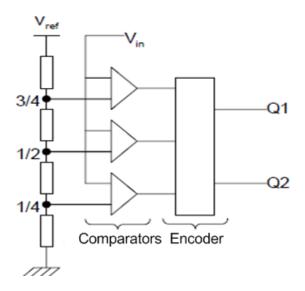

| 3.28 | Flash Converter                                         |

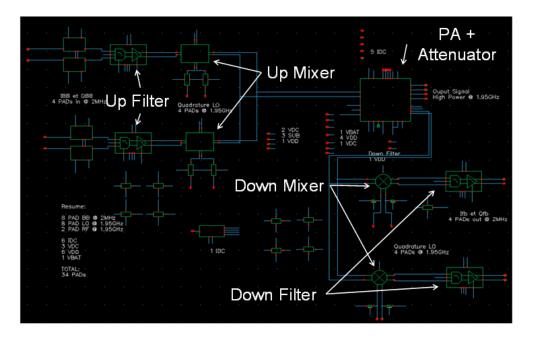

| 3.29 | Whole Schematic of the Analog Transmitter               |

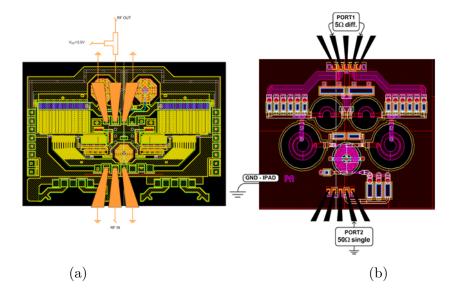

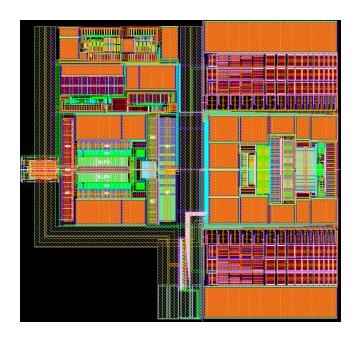

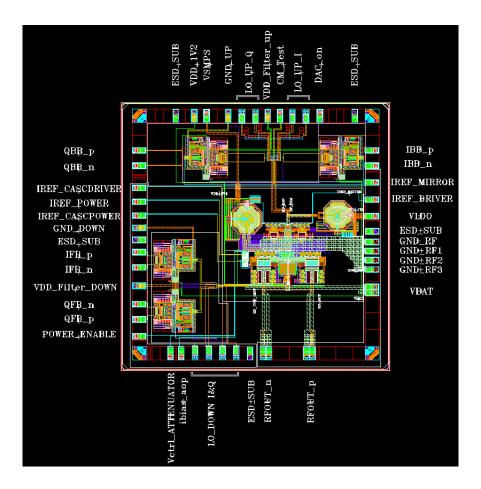

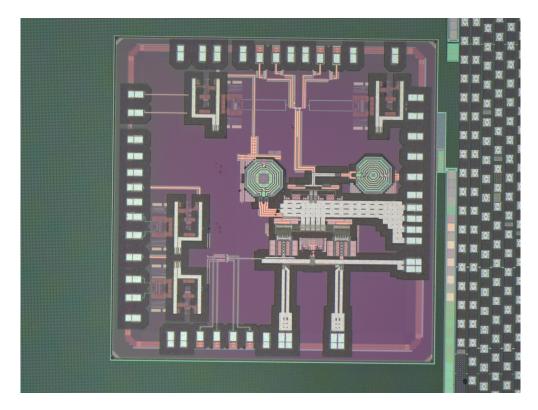

| 3.30 | Die Area of the Analog Transmitter                      |

| 3.31 | Photography of the IC Cartesian Feedback                |

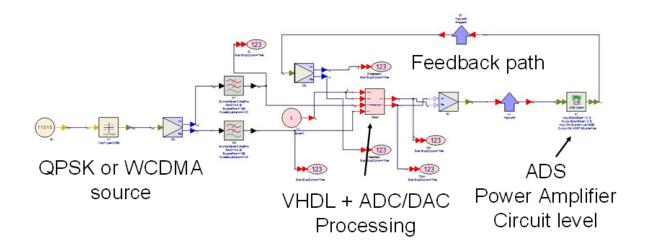

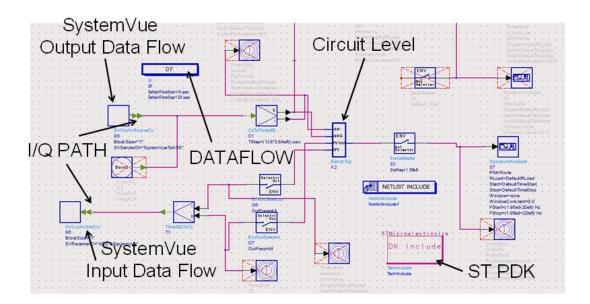

| 3.32 | Whole Co-Simulation Overview                            |

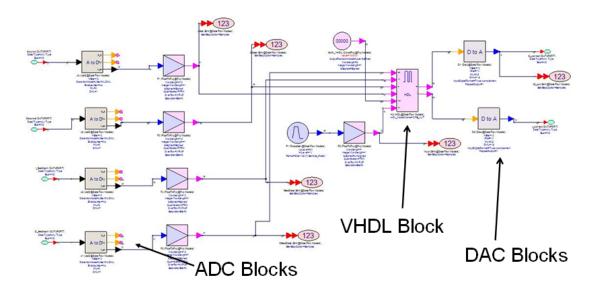

| 3.33 | Simulation's Bench of the Digital Part                  |

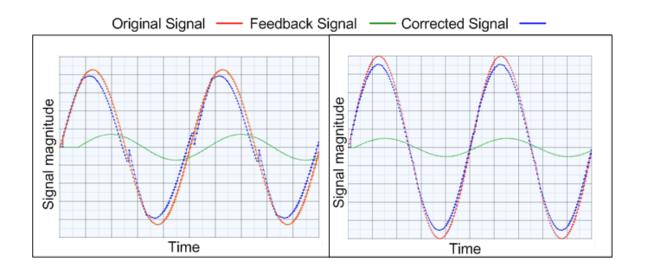

| 3.34 | Digital Signals Simulated with SystemVue                |

| 3.35 | Simulation's Bench of the Analog Part                   |

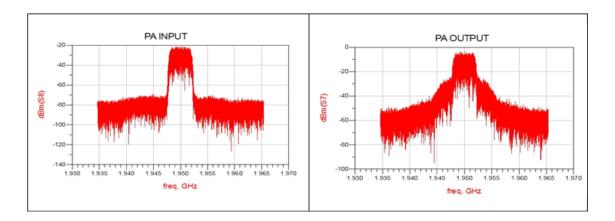

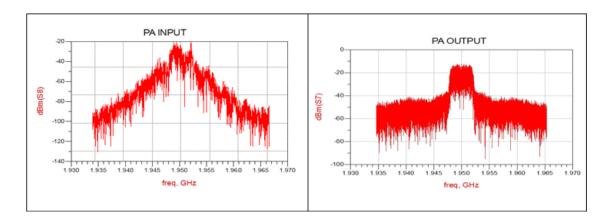

| 3.36 | Input and Output Spectrum without Linearization         |

| 3.37 | Input and Output Spectrum with Linearization            |

| 3.38 | ACLR Improvement with and without Cartesian Feedback    |

| 3.39 | Input and Output Constellations of the Power Amplifier  |

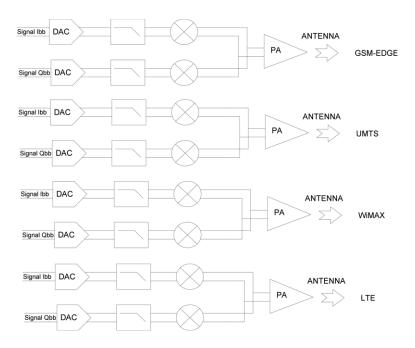

| 3.40 | Parallel Transmitter Integrated on a Mobile             |

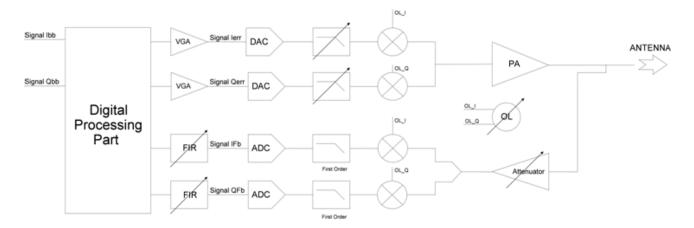

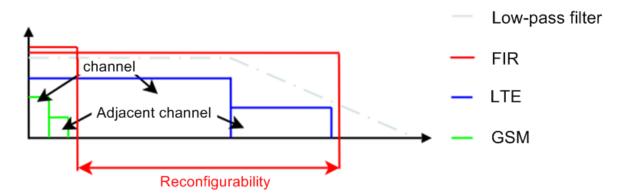

| 3.41 | Architecture of the Multi-Standard Cartesian Feedback | 125 |

|------|-------------------------------------------------------|-----|

| 3.42 | Principle functioning FIR on the new architecture     | 126 |

## List of Tables

| 1.1  | Standard evolution for mobile phone communications                | 19  |

|------|-------------------------------------------------------------------|-----|

| 1.2  | Comparison of transmitter architectures                           | 25  |

| 1.3  | Doherty amplifier principle                                       | 44  |

| 1.4  | Comparison of linearization techniques                            | 52  |

| 2.1  | Parameters of each block making the Cartesian Feedback            | 77  |

| 2.2  | Power on the adjacent channel with and without Cartesian Feedback | 78  |

| 2.3  | Parameters of each block making the Cartesian Feedback            | 83  |

| 3.1  | Results of the Relaxed Constraints Synthesis                      | 91  |

| 3.2  | Results of the Incremental Synthesis                              | 92  |

| 3.3  | Results of the Severe Constraints Synthesis                       | 92  |

| 3.4  | DAC Measured Performances                                         | 96  |

| 3.5  | Simulated Performances of the Attenuator                          | 108 |

| 3.6  | Measured Performances of the ADC                                  | 111 |

| 3.7  | Consumption of each building block of the direct path             | 113 |

| 3.8  | Consumption of each building block of the feedback path           | 113 |

| 3.9  | Comparison with the Literature                                    | 121 |

| 3.10 | Specifications of Main Communications Standard                    | 125 |

List of Tables

### Introduction

Since the first generation of mobile phones, a lot of functions, standards and tools have been integrated on handsets. Twenty years ago, consumers could use their phone only to call and to send messages. Nowadays, internet access, radio, cameras, games and music are included and available as options for each personal mobile phone.

All of these new services make the cost of production for a cellular phone more expensive. Despite that, industry has to find a solution to maintain their products the most attractive as possible including the large range of integrated functions.

Thus, compromises have to be made in order to integrate increasing numbers of chips on a mobile phone. In fact, new standards impose specifications that make the design challenging in terms of linearity, the output power, or even the power injected on the adjacent channel. These specifications make the transmitter less efficient, or less linear. A lower efficiency will increase the power consumption of the chip, and a lower linearity will lead to a lower data rate.

In the context of interaction with other standards, the aim of this thesis is to design and implement a chipset able to improve the linearity of a transmitter for third generation mobile phones, using both digital and analog technologies. For this purpose, the study will focus on the improvement of the linearity, keeping the consumption and the die area of the circuit as small as possible. We will prove that linearization on an integrated circuit is possible with almost the same consumption and die area occupation compared to a classic transmitter. Most importantly, even if a large literature about linearization techniques can be found, only a few show the entire integration in a single technology, as we will show.

The first chapter will present the different architectures used for a transmitter and various linearization techniques with their advantages and drawbacks. Some metrics are also presented in order to evaluate these architectures. The goal of this part is to choose a linearization technique associated to a transmitter in order to fit with our application and constraints.

16 List of Tables

The second chapter will explain the complete system, digital and analog parts, with theoretical studies. We will start by detailing the constraints and precautions that must be taken into account by the designer to study the instability and the noise generated by the transmitter. We will describe how two algorithms back signal corrections. Then, in the last part we will show system level simulations of the Cartesian feedback using, first, an ideal power amplifier (PA) of ADS, second, a PA in BiCMOS technology, and third and finally, a PA in CMOS technology that will be used for the final integrated circuit.

Finally, the third and last chapter shows the digital synthesis in CMOS technology of the two algorithms previously mentioned, considering all steps, from the VHDL code until the layout of the digital part. We will describe and simulate each analog building block of the Cartesian Feedback, and some of them will have their performance measured.

Each chapter will be working towards the goal of this study, demonstrated in the final part: to make an integrated circuit, with its complete solution and simulations.

#### Chapter

1

# Linearization of a Transmitter

| 1.1 | Mob   | ile Communication Standards                                                   | 18  |

|-----|-------|-------------------------------------------------------------------------------|-----|

| 1.2 | Tran  | smitter Architectures                                                         | 21  |

|     | 1.2.1 | Heterodyne transmitter architecture                                           | 21  |

|     | 1.2.2 | Direct conversion transmitter architecture                                    | 22  |

|     | 1.2.3 | Low-IF transmitter architecture                                               | 23  |

|     | 1.2.4 | Offset-PLL transmitter architecture                                           | 24  |

|     | 1.2.5 | Summary of transmitter architectures                                          | 25  |

| 1.3 | Non   | linear Behavior of a RF Transmitter                                           | 26  |

|     | 1.3.1 | AM/AM and AM/PM conversion                                                    | 26  |

|     | 1.3.2 | Carrier to Intermodulation ratio (C/In) $\ \ldots \ \ldots \ \ldots \ \ldots$ | 28  |

|     | 1.3.3 | Adjacent Channel Power Ratio (ACPR) $\ . \ . \ . \ . \ . \ . \ . \ .$         | 29  |

|     | 1.3.4 | Noise Power Ratio (NPR)                                                       | 30  |

|     | 1.3.5 | Error Vector Magnitude (EVM) $\dots \dots \dots \dots \dots \dots$            | 31  |

| 1.4 | Line  | arization Techniques                                                          | 32  |

|     | 1.4.1 | Tradeoffs between linearity and efficiency $\ldots \ldots \ldots \ldots$      | 32  |

|     | 1.4.2 | Power back-off                                                                | 38  |

|     | 1.4.3 | Efficiency improvement                                                        | 38  |

|     | 1.4.4 | Linearity improvement                                                         | 45  |

| 1 5 | Com   | aluaian                                                                       | E 1 |

Wireless communication standards are continually becoming more sophisticated because of the increasing data rate. It remains a delicate operation to transmit data at a high rate without creating distortions through the antenna with a transmitter. That is why the choice of the transmitter architecture is very important for the quality of the communication, a choice that is directly linked to the modulation or the standard used. In the case of the W-CDMA standard, a modulation with non-constant envelope is employed, the HPSK (Hyper Phase Shift Keying) modulation.

It generates a signal varying in phase and amplitude. It is used to reduce the peak-to-average ratio of the signal avoiding the zero crossings and the zero degree phase transitions. As a consequence, special care has to be taken to avoid any distortions on the main signal, which creates unwanted information on the adjacent channel reducing the data rate of the communication.

In this chapter, different transmitter architectures are studied in order to choose the one which will fit better with the integration of radio-frequency components for our application, and also, that will reduce most of the die area and consumption of the whole solution. To improve performance of this transmitter and keep the minimum consumption and die area at the same time, a linearization technique has been chosen among many techniques that we will see below.

#### 1.1 Mobile Communication Standards

Cellular communications have evolved for thirty years in terms of the modulation employed. The first generation used an analog modulation whereas the second generation used a digital modulation. For the next generations of standards, the modulation became more complex with the transmission of images or data. Indeed, from the first generation in Japan (with the standard called DoCoMo) to the third generation of cellular technology, wireless standards have had to handle internet access and other services, such as video streaming, making more complex the modulation employed.

The widespread use of mobile phones all over the world requires good management of the spectrum to avoid interferences. With added economic issues, the establishment of new standards is essential in defining the specifications for manufacturers and operators.

|                       | NMT<br>[1]     | GSM/<br>DCS [2] | GPRS/<br>EDGE[3] | UMTS<br>[4]     | HSDPA/<br>HSUPA[4]          | HSPA+<br>[5]                      | LTE-<br>Advanced<br>[6]           |

|-----------------------|----------------|-----------------|------------------|-----------------|-----------------------------|-----------------------------------|-----------------------------------|

| Generation            | 1G             | 2G              | 2.5/2.75G        | 3G              | 3.5/3.75G<br>or<br>3G+/3G++ | Evolution 3G++                    | 4G                                |

| Approximate<br>Years  | 1981           | 1993            | 2001/03          | 2004            | 2007/08                     | 2008/09                           | 2009/10                           |

| Frequency bands (Hz)  | 0.45G-<br>0.9G | 0.9/1.8G        | 0.9G             | 1.92G/<br>1.98G | 1.92G/<br>1.98G             | 1.92G/<br>1.98G                   | $2.57{ m G}\ / \ 2.62{ m G}$      |

| Carriers Spacing (Hz) | 12.5/<br>25k   | 200k            | 200k             | 5M              | 5M                          | 5M                                | 15k<br>(sub-<br>carrier)          |

| Access<br>Methodology | -              | F/TDMA          | F/TDMA           | W-<br>CDMA      | W-CDMA                      | MIMO<br>CDMA                      | OFDMA/<br>SC-FDMA                 |

| Modulation            | FM             | GMSK            | 8PSK             | HPSK/<br>QPSK   | QPSK/<br>16QAM              | $rac{	ext{QPSK}/}{16	ext{QAM}/}$ | $rac{	ext{QPSK}/}{16	ext{QAM}/}$ |

| Data Rates (bps)      | -              | 270k            | 812.5k           | 0.8-2M          | 14M                         | 28M                               | 100M                              |

Table 1.1: Standard evolution for mobile phone communications

In Table 1.1, a non-exhaustive list of main standards is given from the first generation of mobile until the fourth generation in Europe. This comparison table shows main features that are more relevant for our study (frequency bands, modulation used, carrier spacing, access methodology).

#### From 1G to 4G:

In the 1970s/1980s, the first analog wireless terminals started to appear in cars and in the business world. These mobiles had almost the size of a suitcase and did not cover a lot of territory.

This generation did not guarantee the confidentiality of communications and became saturated using a modulation technique similar to the FM radio. The development of this first generation was limited by the analog modulation used, short spectral resources, low battery life and cost of mobile terminals.

Thus, the second generation became digital in order to increase the capacity and the data rate of wireless communications. This generation insured a better sound quality and confidentiality and reduced the size of terminals. At the beginning of the 1990s, the GSM standard for wireless communication (Global System for Mobile Communication) was adopted in Europe. Since this

date, the GSM operates around the world except for Japan, South America and North America (which have another standard).

In 2001, an important evolution of the GSM Standard was the GPRS (General Packet Radio Service, more commonly called 2.5G). Concretely, the GPRS standard is an improvement of the GSM; the voice information remained on the GSM network, whereas data used the GPRS standard for a lighter internet access, as an e-mail without an attachment. The GPRS standard allowed a more comfortable connection with the WAP (internet access); however users of mobile phones were not convinced regarding the price and a limited internet connection.

Right after the GPRS, the GSM standard was developed towards the EDGE standard (Enhanced Data rate for GSM Evolution, also called 2.75G). Compared to the GPRS standard, the EDGE is able to send and receive data faster between a mobile phone and a base station. It can be considered as a complement of the future standard UMTS (Universal Mobile Telecommunication System), or a direct competitor of the 3G for a less expensive cost.

The UMTS standard exploits a new protocol of communication, called W-CDMA (Wide-Code Division Multiple Access), and new frequencies between 1900 and 2200MHz. This standard made it possible to reach high data rates for multimedia applications. Moreover, the standard made it possible to send parallel data with a higher data rate, comparing to the GSM and the GPRS. It is not a radical change compared to the second generation but it changed significantly the use of a mobile phone: high speed wireless internet, videophone and video streaming in the mobile. In theory, the UMTS can reach 2Mbps from a fixed location and 384kbps from a moving point.

After many delays of the development of the 3G, its deployment has finally started in Europe at 2004. The UMTS/W-CDMA standard has been selected in Europe by the 3GPP Association (Third Generation Partnership Project) grouping main telecommunications companies. It required each interested operator to purchase a license issued by its state, and, in parallel, to develop the infrastructure for the GSM/GPRS network. In France in 2004, according to an analysis of users of the 2G by the Telecommunications Regulatory Authority (Autorité de Régulation des Télécommunications - ART) more than 70% of French people had a mobile phone.

The worldwide industry of telecommunication is currently developing the fourth generation of mobile phones called LTE-Advanced (Long Term Evolution). This new generation will probably

use the OFDM technology (Orthogonal Frequency Division Multiplexing) reaching data rates up to 300Mbps. In order to prepare this generation, specialists developed the evolution of UMTS, called HSDPA (High Speed Downlink Package Access) and HSUPA (High Speed Uplink Package Access). The evolution of the UMTS offered a data rate of 14Mbps and the deployment in Europe began in 2006.

#### 1.2 Transmitter Architectures

Transmitters are mainly composed of converters, filters, mixers, local oscillators and a power amplifier. Their goal is to modulate and up-convert the baseband signal into a higher frequency. The resulting signal is then strengthened by the power amplifier before driving the antenna [7]. A band-pass filter (or a multiplexer) is used to filter the desired channel and send it through the antenna. Nevertheless, it is complicated to determine the architecture of the transmitter without taking into account the architecture of the receiver. Indeed, unwanted frequencies and noise that are generated by transmitter are injected into the receiver. Ideally, the transmitter and the receiver architectures should be considered at the same time, in order to optimize performance, die area and consumption of the RF circuit.

In this section, main architectures are evaluated. Among the most classic ones, we can find architectures based on a simple or on a double mixing frequency, as homodyne or heterodyne, or otherwise, transmitters based on a PLL (Phase-Locked Loop).

#### 1.2.1 Heterodyne transmitter architecture

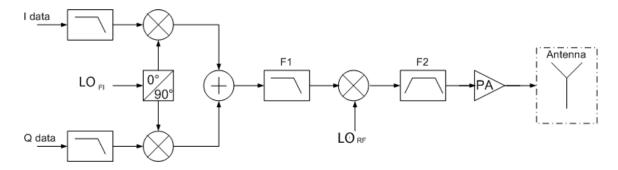

The heterodyne transmitter architecture is described in Figure 1.1.

Figure 1.1: Heterodyne transmitter architecture

Analog baseband signals I and Q are up-converted to an intermediate frequency  $(f_{IF})$  by two mixers in quadrature. The signal is then sent to a low-pass filter (F1) which deletes harmonics

coming from the  $f_{IF}$  frequency. In order to avoid any other distortion coming from the baseband domain, it remains important to realize this operation before to transpose the baseband signal to another frequency  $(f_{IF} + f_{RF})$  given by the mixer M2  $(LO_{RF})$ .

The mixer M2 will produce two inter-modulations tones at  $f_{IF} + f_{RF}$  and  $f_{IF} - f_{RF}$  frequencies. As the frequency  $f_{IF} - f_{RF}$  is a non-desired tone, a band-pass filter (F2) has to be used to remove it. The resulting signal is finally amplified and transmitted through the antenna.

This architecture works with constant and non-constant envelop modulations and the modulation of signals is made at a low  $f_{IF}$  frequency (which is about a few MHz). This architecture, thanks to its two stages of frequency conversion, obtains good results in terms of sensitivity, selectivity and linearity according to the modulation used; however, it uses two local oscillators which increase the power consumption of the transmitter.

Moreover, as the  $f_{IF}-f_{RF}$  tone has the same power as the  $f_{IF}+f_{RF}$  tone, the band-pass filter of the second stage of conversion has to reject the signal of ~40dB at least. This filter has to work at high frequency, which complicates the result of getting a good quality factor. In general, an external filter is used as a SAW filter (Surface Acoustic Wave). This filter adds area and cost that made this kind of architecture very expensive.

#### 1.2.2 Direct conversion transmitter architecture

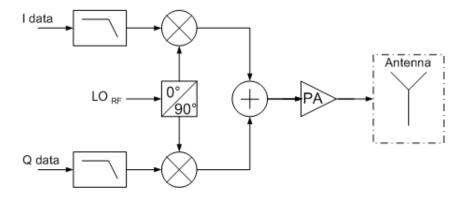

The direct conversion transmitter architecture, also called homodyne or Zero-IF (Zero-Intermediate Frequency, meaning without intermediate frequency), uses a single stage of frequency conversion as shown in Figure 1.2.

Figure 1.2: Direct conversion transmitter architecture

Like the heterodyne architecture, analog baseband signals are modulated and up-converted to

RF frequency by mixers on quadrature, a PLL with a LO working at the RF frequency. In this case, the frequency of the resulting signal is directly transposed to the frequency of the standard.

This architecture takes less area than the heterodyne architecture because it uses fewer components reducing thereby the consumption. Moreover, the image rejection on the main channel is realized dynamically by summing the output of mixers (Cf. Equation 1.1).

$$(\cos \omega_{BB}t * \cos \omega_{RF}t) + (\sin \omega_{BB}t * \sin \omega_{RF}t) = \cos(\omega_{RF}t - \omega_{BB}t)$$

(1.1)

As a consequence, we do not need the band-pass filter of the intermediate stage and release some constraints of the external filter. (Trigonometric functions removed automatically the  $\omega_{BF}t + \omega_{BB}t$  term).

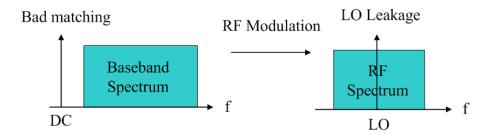

Such architecture is compatible with a complex I/Q modulation as HPSK, but has some draw-backs concerning the mismatch in phase and amplitude between I and Q. The major issue is to realize a good quadrature generation at the RF frequency. If a weak quadrature takes place, we will have a bad rejection of the image frequency [8].

One of the major drawbacks for the direct conversion transmitter is the pulling phenomenon [9] [10]. In other words, when two oscillating components are close to each other, they are oscillating at the same frequency due to the coupling phenomena. In the case of the Zero-IF frequency, the local oscillator and the PA works at frequencies very close to each other and can be coupled by the substrate. The RF signal at the output of the amplifier is much greater than the output power of the LO, so the working frequency of the LO will be shifted into the RF frequency. The isolation needed remains hard to quantify without considering the receiver associated with the Zero-IF transmitter [11].

Moreover, the direct conversion is sensitive to DC parasites. Indeed, parasites are mixed with the main signal for the receiver. In W-CDMA the baseband signal is spread around 3.84MHz. A high pass filter with a cut-off frequency lower or equal to 10 kHz can removed all of these DC parasites keeping the integrity of the W-CDMA signal.

#### 1.2.3 Low-IF transmitter architecture

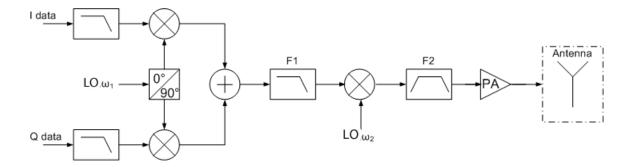

The pulling phenomenon disappears if we use two LO frequencies (frequencies of  $LO_{\omega 1}$  and  $LO_{\omega 2}$ ). The Figure 1.3 shows the architecture of the low-IF frequency.

Figure 1.3: Low-IF transmitter architecture

The low-IF transmitter architecture is based on the same principle of a heterodyne transmitter, except that the  $LO_{\omega_1}$  frequency is obtained by mixing and filtering two lower frequencies. By consequence, the first mixing stage in the IF frequency can be realized on the digital circuit. This method has the same advantages as the direct conversion transmitter, except that this transmitter is not sensitive for the pulling if the IF frequency is not too low.

Furthermore, an incorrect choice of LO frequencies produces harmonics at the output. A low-pass filter which follows the VCO (Voltage-Controlled Oscillator) has to be very selective in order to keep a good quality of the output signal.

#### 1.2.4 Offset-PLL transmitter architecture

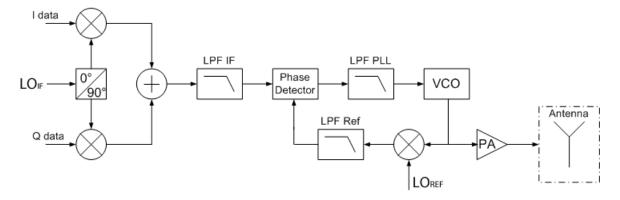

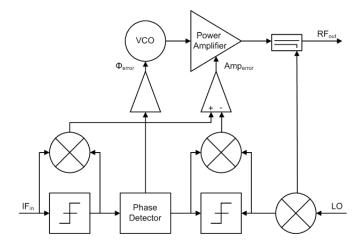

This technique was developed to answer the strong constraints of the GSM standard for the noise in the reception band. The architecture of the Offset-PLL transmitter [7] is presented in Figure 1.4.

Figure 1.4: Offset-PLL transmitter architecture

The offset-PLL transmitter [12] has the objective to mix the signal from the local oscillator

with the output signal from the VCO (Voltage Control Oscillator). The resulting signal is then injected into a phase comparator to generate an error signal which, after being filtered, controls the VCO. This will work at the RF frequency. A current offset generator is needed to obtain a fast locking of the loop. Indeed, the output current of the phase comparator does not allow the locking of the loop in a reasonable time. The time-locked can be improved by 26% [13]. Nonetheless, without adjustment of the current, the loop will become unstable.

The offset-PLL transmitter has a good IC integration because it does not use mixers to convert the baseband frequency to the RF frequency, neither external filter. Moreover, it does not consume a lot of power, which makes a very attractive solution for the cost reduction. On the other side, this solution works with constant envelop modulation and does not fit with our modulation which is the HPSK. This architecture also has the drawback of suffering from the pulling, so a good isolation between the VCO and the PA has to be realized.

#### 1.2.5 Summary of transmitter architectures

For the wireless communication in the context of mobile devices with the W-CDMA standard, it is very important to get a good integration level on the Silicon area and a low consumption of our chip, as both reduce the cost of production. Furthermore, the architecture has to work with constant and non-constant envelope modulation considering the modulation of the W-CDMA used.

| The Table 1.2 makes a | comparison of these | last transmitters | according to these criteria |    |

|-----------------------|---------------------|-------------------|-----------------------------|----|

| The Table 1.2 makes a | comparison of these | last transmitters | according to these criteri  | а. |

| Architecture | Integration | Consumption | Modulation        |

|--------------|-------------|-------------|-------------------|

| Heterodyne   | Low         | Medium      | All               |

| Homodyne     | Good        | Low         | All               |

| Low-IF       | Medium      | Medium      | All               |

| Offset-PLL   | Good        | Low         | Constant envelope |

Table 1.2: Comparison of transmitter architectures

Despite serious issues imposed by the Zero-IF architecture explained at the topic 1.2.2 and according to the previous table, this transmitter is the most appropriated to reduce consumption and die area for W-CDMA communications. These criteria remain our first objective and it is for this reason that the Cartesian Feedback has been implemented on a Zero-IF transmitter.

#### 1.3 Nonlinear Behavior of a RF Transmitter

To understand an RF transmitter, we must have the previous knowledge that it is composed of RF transistors.

In 1948[14], W. Shockley describes for the first time the principle of the bipolar junction transistor. However, it is only at the end of the 1950s that the first transistor able to amplify signals up to 1GHz was developed.

The term Radio Frequency (RF) refers to the electromagnetic waves with frequencies ranging from Gigahertz or higher. Until the 1980s, most applications for RF transistors were used only by the military. Since then, the appearance of wireless communication systems (Wi-Fi, Bluetooth and WLAN) for the costumers has completely changed the sales for mobile phones.

The conception of RF transmitters starts with the choice of the type of transistor depending of the targeted application. For our study, which is to improve the linearity of the transmitter, we opted for the characterization of a transmitter (e.g. power amplifier), using nonlinear model of transistor. This part shows the nonlinear behavior of a transistor (or components using transistors) and the metrics to measure it.

Furthermore, each of the RF transmitter architectures can be evaluated according to its integration on the Silicon area, as well as the power consumption or the modulation used. Therefore, in order to validate the RF transmitter some specifications are given by the standard communication.

#### 1.3.1 AM/AM and AM/PM conversion

The power amplifier is a very important component of a transmitter and defines the consumption and the linearity of the whole system. The behavior of the PA acts also directly on the receiver and can increase the bit error rate (BER) of the transceiver.

An ideal power amplifier has a linear response. In other words, the output signal is proportional to the input signal.

$$V_{out}(t) = a_0 + a_1 \cdot V_{in}(t) \tag{1.2}$$

Where  $a_1$  is the voltage gain of the power amplifier.

For a low input voltage, the functioning of the power amplifier can be assimilated to an ideal power amplifier. However, for strong input voltage, the output signals suffer from distortions due to amplitude (AM/AM) and phase (AM/PM) conversions. Current sources are the first elements able to cause amplitude variation of the output signal according to the input signal. Moreover, nonlinear behavior gives an additional shifting of the output signal, which is also linked with the input signal from the power amplifier.

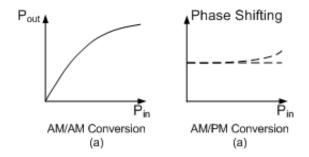

The Figure 1.5 shows these conversions:

Figure 1.5: AM/AM and AM/PM conversion

Let's consider an input sinusoidal signal with an amplitude and phase modulation

$$V_{in} = A(t) \cdot \cos\left[\omega_0 \cdot t + \phi(t)\right] \tag{1.3}$$

At the output of the power amplifier, we obtained

$$V_{out} = A'(t) \cdot \cos \left[\omega_0 \cdot t + \phi(t) + \phi'(t)\right]$$

(1.4)

With

$$A'(t) = F_{NL}[A(t)]$$

$$(1.5)$$

And

$$\phi'(t) = G_{NL}[A(t)] \tag{1.6}$$

Where  $F_{NL}$  and  $G_{NL}$  are nonlinear functions.

The deflection of AM/AM and AM/PM curves, for strong input level power, permits to understand the nonlinear behavior of the power amplifier.

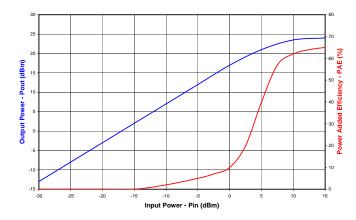

However the efficiency  $\eta$  is defined as the ratio between the output power (in Watts) and the power supply consumed (in Watts). It will be maximal when the amplifier is used with high level signal (Cf. Figure 1.6). Thus, a nonlinear function and generation of spurious tones are produced when we will try to improve the saturation power or the efficiency of the power amplifier.

Figure 1.6: Output power and efficiency of a PA versus input power

#### 1.3.2 Carrier to Intermodulation ratio (C/In)

The analysis with two carriers is a simple method to evaluate the linearity of an amplifier and to show, at the same time, amplitude and phase distortions of the amplifier. This method focuses on the variation of the envelope's signal, using the amplifier over its entire dynamic range. It is a very severe test for the amplifier because the envelope ranges from zero to a maximum level, as shown in Figure 1.7(a).

Figure 1.7: Signal with two carriers in timed (a) and frequency (b) domains

Two signals at the frequency  $f_1$  and  $f_2$ , with the same amplitude and non-modulated with  $\Delta f = f_2 - f_1$ , are applied at the input of the amplifier. On the time domain, a signal with two carriers is represented in Figure 1.7 (a). The equivalent spectrum is given in Figure 1.7 (b).

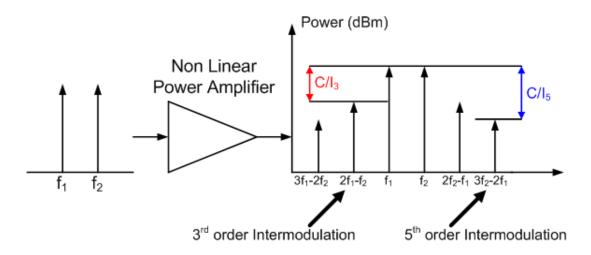

As shown in the previous part, such signal going through the nonlinear amplifier will generate intermodulation products.

Figure 1.8: Carrier to Intermodulation ratio

The  $3^{rd}$  order ratio C/I (Carrier to Intermodulation ratio) is defined as being the difference between the power in dBm, of the carrier  $f_1$  or  $f_2$ , and the intermodulation tone respectively at  $2 \cdot f_1 - f_2$  or  $2 \cdot f_2 - f_1$  frequency (Cf. Figure 1.8). In general, we define the  $n^{th}$  order ratio C/I as the difference between the power of the carrier  $f_1$  or  $f_2$  and the intermodulation tone at  $p \cdot f_1 + q \cdot f_2$  with p + q = n.

#### 1.3.3 Adjacent Channel Power Ratio (ACPR)

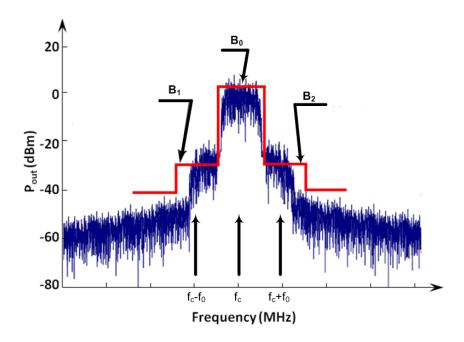

The ACPR measures the power level at the output of the power amplifier, between the adjacent channel and the main channel. It uses a modulated signal of the same type as the one that must be amplified for standard chosen. It is defined as the ratio between the average powers (in Watts) contained in a frequency band  $B_1$  and  $B_2$  to an offset  $f_0$  of the carrier frequency  $f_c$  of the channel, and the average power (in Watts) contained in the frequency band  $B_0$  around the carrier frequency  $f_c$  of the standard. It leads to the following expression:

The concept of this measure is shown in Figure 1.9. Its expression is the following:

$$ACPR_{dB} = \left(\frac{2. \int_{B_0} P(f) . df}{\int_{B_1} P(f) . df + \int_{B_2} P(f) . df}\right)$$

(1.7)

The output power according to the frequency is shown in Figure 1.9.

Figure 1.9: Adjacent Channel Power Ratio spectrum

Frequency bands  $B_0$ ,  $B_1$  and  $B_2$  and the offset  $f_0$  depend on the chosen standard of communication.

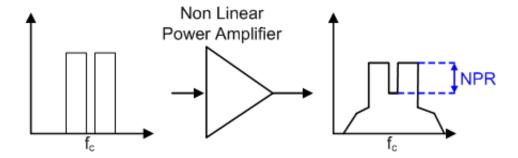

#### 1.3.4 Noise Power Ratio (NPR)

The NPR is a power measurement of distortions on the channel caused by nonlinearities of the power amplifier. It can be evaluated by removing a frequency band of the input signal of the channel, and measuring the output level of distortion in the frequency space left free (SLF).

The NPR is defined as the ratio between the maximum power of the signal on the channel and the power of distortions, where both are expressed in Watts. Figure 1.10 illustrates the measure of the NPR on the modulated signal after the power amplifier.

$$NPR(dB) = 10 * \log \left( \frac{\int_{SLF} P(f) . df}{\int_{Carriers} P(f) . df} . \frac{BW_{Carriers}}{BW_{SLF}} \right)$$

(1.8)

Figure 1.10: Noise Power Ratio

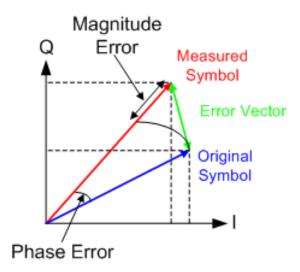

#### 1.3.5 Error Vector Magnitude (EVM)

The EVM represents the difference between the effective demodulated signal after the transmission or amplification, and the signal as it should be if the system was perfectly linear. This measurement gives the information about the error of the phase and amplitude of the received signal [15]. Figure 1.11 represents the EVM definition for a modulated signal by two signals in quadrature I and Q.

Figure 1.11: Error Vector Magnitude

The EVM represents the module of the error vector as followed:

$$Magnitude \ Error = \sqrt{I_{Measured}^2 + Q_{Measured}^2} - \sqrt{I_{Original}^2 + Q_{Original}^2}$$

$$Phase \ Error = \arctan\left(\frac{Q_{measured}}{I_{Measured}}\right) - \arctan\left(\frac{Q_{Original}}{I_{Original}}\right)$$

$$(1.9)$$

$$EVM = \sqrt{(I_{Measured} - I_{Original})^2 + (Q_{Measured} - Q_{Original})^2}$$

(1.11)

This criterion is generally used for signal processing to characterize the whole system of a couple modulator/demodulator. It helps to quantify the effect of the additive noise on the distortion of the transmitted signal's constellation.

#### 1.4 Linearization Techniques

The HPSK modulation has a good spectral efficiency, but the power efficiency remains poor with linear power amplifiers. For mobile applications, a low efficiency increases the consumption of the transmitter, decreasing the life time of mobile phone battery.

To obtain, for the same device, a good linearity and spectral efficiency, we use linearization techniques such as EER (Envelope Elimination Restoration), Feed-forward, Polar loop or Cartesian Feedback. On the other hand, a good linearity for components like an RF modulator or a power amplifier can be obtained with overconsumption. A linearization technique offers the possibility to use nonlinear components in order to reduce the consumption of the transmitter.

We have two categories of linearization techniques: those which improve the linearity of the transmitter and those which improve the efficiency of the whole system.

#### 1.4.1 Tradeoffs between linearity and efficiency

The challenge for the design of a power amplifier can be simplified by a system of two variables in which we have to reach an output power imposed by the wireless communication standard while optimizing its efficiency. This must be done with respect to the given linearity constraints. Nevertheless, a compromise has to be made between the maximum output power and the efficiency of the power amplifier. According to specifications given by the standard, we must distinguish among many topologies of power amplifiers.

#### 1.4.1.1 Classes of power amplifier

In literature, classes of power amplifiers can be divided into two categories [16]:

- The first class is defined by the polarization given to the transistor and is called the "linear class". They are designated by: Classes A, B, C, and AB.

- The other class is the commutation class because transistors work like switches. It is called the "highly efficient class". They are designated by: Classes D, E, F and S.

Linear class of power amplifier:

For power amplifiers taken from the linear class, the transistor behavior can be assimilated as a current source. The output power is proportional to the input power. The gain is constant on a wide band of power. This kind of class is well known and is required when a complex modulation is used (non-constant envelop, i.e. HPSK) in order to preserve the information contained into the envelope.

Commutation class of power amplifier:

For power amplifiers of the commutation class, the transistor works like a switch with the output non-proportional to the input. This kind of power amplifiers is really efficient for constant envelope modulation (like GMSK used for the GSM standard). The consumption of the circuit is considerably reduced and the efficiency remains very high. Indeed, in theory, when the level of the input voltage of the transistor is high, the current is equal to zero and reciprocally. This advantage increases the time-to-talk of batteries implanted into a mobile device.

The most important parameters able to define performances of a power amplifier are the efficiency and the nonlinearities. The values of these parameters are linked to the classes of the chosen power amplifier. So it is important to define their characteristics to understand how to correct or improve them.

#### 1.4.1.2 Efficiency

The efficiency of a power amplifier can be evaluated as a drain efficiency (if the transistor is a field-effect transistor, otherwise, it is a collector efficiency for a bipolar junction transistor), a power added efficiency (PAE), or a whole efficiency.

The drain efficiency is defined as the ratio between the fundamental output power  $(P_{out})$  and the power delivered by the continuous alimentation  $(P_{DC})$ .

$$\eta_{DE} = \frac{P_{out}}{P_{DC}} \tag{1.12}$$

The power added efficiency of a power amplifier is defined by the Equation 1.13. It represents the ability of a transistor to transform the energy delivered by continuous alimentation in a microwave energy. This efficiency can be calculated as the ratio between the added sine wave power of the power amplifier and the supply voltage applied to it. The added sine wave power is defined as the difference between the input power  $(P_{in})$  and the output power  $(P_{out})$  of the power amplifier.

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \tag{1.13}$$

Finally, the whole efficiency represents the ratio between the energy available at the output of the power amplifier and the energy provided to the amplifier in order to insure the output power.

This efficiency is defined by the Equation:

$$\eta = \frac{P_{out}}{P_{DC} + P_{in}} \tag{1.14}$$

#### 1.4.1.3 Nonlinearity

Power amplifiers suffer from nonlinearities, or distortions, when a certain level of the input signal is applied.

The amplitude distortions are divided in two categories:

- distortions making a compression effect on the power of the signal (compression point at 1dB); and

- distortions due to interferences between two signals which have frequencies close to the fundamental frequency.

The combination of the different frequencies creates intermodulation products. Distortions due to interferences have impacts only on the receiver. These two types of nonlinearity are described in the following section.

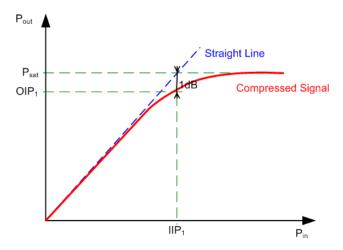

#### Compression Point at 1dB:

The sinusoidal signal at the input of the power amplifier is defined by the Equation 1.15

$$V_{in} = A.\cos\left(\omega t\right) \tag{1.15}$$

Where A is the maximum amplitude of the input signal and  $\omega$  is the operating frequency.

Considering the output voltage as a temporal function of the input voltage, it is possible to express this voltage in polynomial form until the  $3^{rd}$  order nonlinearities term. The expression of the output voltage will be:

$$V_{out} = a_1 V_{in} + a_2 V_{in}^2 + a_3 V_{in}^3 (1.16)$$

After the development of the Equation 1.16, the expression of the fundamental will be:

$$a_1 A \left[ 1 + \frac{3}{4} \frac{a_3}{a_1} A^2 \right]$$

The coefficient  $a_1A$  represents the linear gain of the system. If  $a_3 > 0$ , the power amplifier works on the linear region, but if  $a_3 < 0$ , the power amplifier suffers of the compression phenomenon at the fundamental frequency. The output power of the amplifier is often given at 1dB of compression, meaning that the gain is 1dB under the linear zone. The compression point is described in Figure 1.12.

Figure 1.12: Definition of the compression point

Where OCP1 is the first order Output Compression Point and ICP1 is the first order Input Compression Point.

Evaluating the 1dB compression point is not enough to quantify the nonlinearity of a power amplifier used on a communication system. For this reason, we must also study the intermodulation products in order to evaluate distortions of the same function. The knowledge of the 1dB compression point is important to determine the back-off level to take into account when complex modulation is brought into play (as the OFDM modulation).

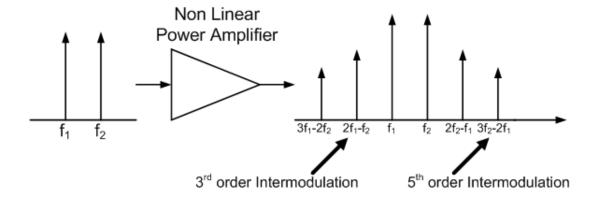

#### $Intermodulation\ products:$

Intermodulation products represent a combination of fundamental frequencies. Spurious signals

can disturb the wireless communication system if they are within the bandwidth of the system.

In order to characterize intermodulation products, we must consider the input signal  $(V_{in})$  - Cf. Equation 1.17 - composed of two sinusoidal signals with the same amplitude A but with different frequencies  $(f_1 \text{ and } f_2)$ .

$$V_{in} = V \left[ \cos \left( \omega_1 t \right) + \cos \left( \omega_2 t \right) \right] \tag{1.17}$$

The output signal of the power amplifier is then defined in Equation 1.18.

$$V_{out} = a_1 V \left[\cos(\omega_1 t) + \cos(\omega_2 t)\right] + a_2 V^2 \left[\cos(\omega_1 t) + \cos(\omega_2 t)\right]^2 + a_3 V \left[\cos(\omega_1 t) + \cos(\omega_2 t)\right]^3$$

(1.18)

The output signal  $V_{out}$  has term in  $n\omega_1 \pm m\omega_2$ , n and m being integers. The order of the intermodulation products is defined by the relation:

$$i = |n| + |m| \tag{1.19}$$

Second order intermodulation products are thus represented by tones at frequencies  $f_1 + f_2$  and  $f_2 - f_1$ , and these of the third order by frequencies  $2f_1 + f_2$ ,  $2f_1 - f_2$ ,  $2f_2 + f_1$ , and  $2f_2 - f_1$ .

Some of intermodulation products with an odd order (i being an odd number) are, as represented in Figure 1.13, within the operating bandwidth of the system, perturbing the transmitted signal.

Figure 1.13: Input and output spectrum of a nonlinear amplifier after compression

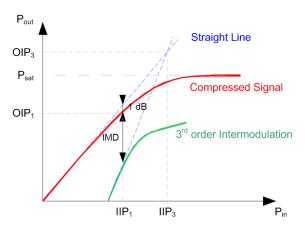

The third order intermodulation product is represented in Figure 1.14.

Figure 1.14: Definition of the third order intermodulation product

In this graphic, we can deduce the third order interception point (IP3) at the input (IIP3) and at the output (OIP3). This point can be determined by calculating the intersection between the linear line of the fundamental power and the line of the third order products intermodulation.

The Figure 1.14 represents also intermodulation products, called IMD (InterModulation Distortion) and is expressed in dBc. This distortion is defined by the Equation 1.20 knowing that the power of the fundamental is defined at the 1dB compression point:

$$IMD_3 = P_{2\omega_2 - \omega_1} - P_{\omega_1}(dBc) \tag{1.20}$$

The process is similar to determine  $i^{th}$  order intermodulation distortions. This time, it can be calculated by the Equation 1.21.

$$IMD_i = P_{m\omega_2 - n\omega_1} - P_{\omega_1} \tag{1.21}$$

Where m, n, and i are integers numbers and linked by this expression: i = m + n.

Third and fifth intermodulation products are, in most of cases, within the bandwidth of the system and have sufficient power in order to have an influence on the output signal of the power amplifier.

The knowledge of the third and fifth intermodulation products is valuable for communication system using a complex modulation, as the HPSK for the UMTS Standard.

### 1.4.2 Power back-off

The easiest way to improve the linearity of a power amplifier is to use it in a Class A operation, reducing the power level needed by the amplifier (back-off) until that the desired level of linearity is reached. For a Class A power amplifier,  $3^{rd}$  order intermodulation products increases according to a factor of 3 (Cf. Figure 1.14), and those of  $5^{th}$  order by a factor 5. A back-off of the input power can significantly reduce the intermodulation products, and especially if these intermodulation products have a high order.

An alternative of using a Class A power amplifier is employing a Class AB power amplifier, where the polarization level is typically about 10 to 50% of the Class A level. The linearity in this case depends largely on the characteristics of the RF component technology. Some technologies, such as the LDMOS, have also very good linearity performances for a Class AB [17].

The drawback of these very simple methods is the low efficiency and the need to have a power amplifier oversized for the application. Therefore, other methods are applied to increase the linearity without deteriorate the whole efficiency of the system.

### 1.4.3 Efficiency improvement

### 1.4.3.1 Envelope Tracking (ET)

Envelope tracking has an objective to keep the linearity of the power amplifier, and at the same time, increase the efficiency. The principle of this topology is to modify the biasing according to the envelope of the input signal. The envelope tracking system imposes the envelope signal at the drain of the power amplifier, and the PA is consequently working in a high efficiency region.

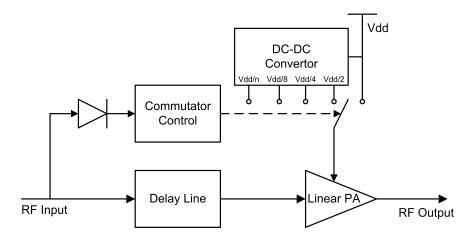

Figure 1.15: Discrete Envelope Tracking

The control of the polarization can be seen as a discrete (Cf. Figure 1.15) or continuous (Cf. Figure 1.16) DC-DC converter. In the first case when the envelope of the signal is greater or lower than a certain value, the polarization voltage can take a value previously fixed. In the other case, the ET works on the biasing, which makes a continuous adjustment of the amplitude according to the envelope signal in real time.

Figure 1.16: Continuous Envelope Tracking

The efficiency reached by the discrete or continuous ET is greater than the efficiency of a power amplifier with a fixed polarization. The current consumption of DC-DC converters and others control components reduce performances in the case of low signal envelope. It is a discrete control, easier to implement and taking less area than a converter can be used, but it does not reach an improvement like continuous correction. Moreover, the generation of different DC signals remains complex for an integrated solution. Nevertheless, dynamic biasing offers full use of the linearity performance of a Class A, while improving significantly the maximum efficiency, which is an attractive solution.

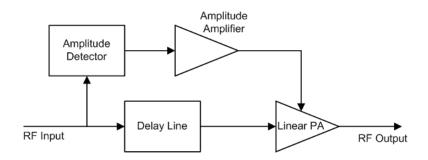

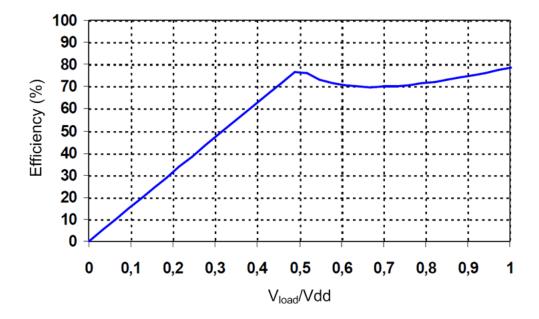

### 1.4.3.2 Envelope Elimination and Restoration (EER)

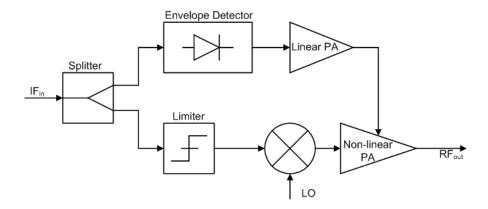

The Envelope Elimination and Restoration (EER) in Figure 1.17 has been developed by Leonard E. Khan in 1952 [18]. The goal of this technique is to amplify a non-constant envelope modulation with a nonlinear power amplifier. The input modulated signal at an intermediate frequency (IF) is decomposed in phase and amplitude through an envelope detector and a limiter. The constant envelope signal in amplitude is up-converted to the RF frequency in the mixer. The resulting signal is then amplified by the nonlinear power amplifier in saturation mode. The envelope of the signal is sent back modulating the voltage supply of the PA by the phase of the input signal.

Figure 1.17: Envelope Elimination and Restoration

The advantage of the EER is to improve the linearity and the efficiency of the power amplifier. This technique remains a complex solution to implement for two reasons. First, it requires controlling perfectly the envelope power amplifier linearity. Secondly, the phase alignment between envelope and phase signals has to be guaranteed. Linearization performance of the EER is linked to the bandwidth of the envelope, but also the phase shifting between the envelope modulation and the phase modulation. It is therefore crucial to control the variation of delay in both paths of the architecture, as well in temperature and for the process used for a good recombination of the output signal. In recent application of the EER [19], the DSP (Digital Signal Processor) splits the signal in phase and amplitude. This solution does not fit with the criteria of a system integrated on a single technology without using external devices.

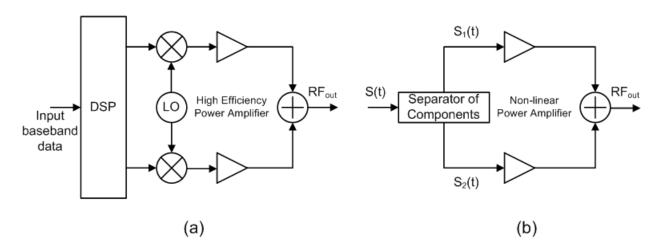

## 1.4.3.3 LInear amplification with Nonlinear Components(LINC) / Combined Analogue Locked Loop Universal Modulator (CALLUM)

This technique uses the property of the decomposition of a non-constant envelope signal into two constant envelope signals, thereby splitting the input signal into two distinct parts. Each of these parts is separately amplified on the nonlinear region and they permit to get a high efficiency and a high output power before a recombination at the output (Cf. Figure 1.18(b)) [20, 21].

The LINC technique may use a DSP to generate two baseband signals modulated in phase and with constant amplitude envelope (Cf. Figure 1.18(a))

Thus an input signal  $s(t) = a(t) \cos [2.\pi f_c t + \phi(t)]$

Figure 1.18: Principle of LINC technique

This signal can be described by two signals  $s_1(t)$  and  $s_2(t)$  with a constant amplitude such as:

$$s_1(t) = a_{max} \cdot \cos\left[2.\pi \cdot f_c \cdot t + \phi(t) + \alpha(t)\right] \tag{1.22}$$

And

$$s_2(t) = a_{max} \cdot \cos \left[ 2.\pi \cdot f_c \cdot t + \phi(t) - \alpha(t) \right]$$

(1.23)

With

$$2.s(t) = s_1(t) + s_2(t) \tag{1.24}$$

And

$$\alpha(t) = \cos^{-1}\left(\frac{a(t)}{a_{max}}\right) \tag{1.25}$$

These two signals are separately amplified by high efficiency power amplifiers, and then recombined to make an amplified copy of the input signal. Any nonlinear behavior appearing in the signal will be found in phase opposition and equal amplitude before the summation. Each nonlinear part will be canceled after summing. This method can use amplifiers in high efficiency commutation to approach an efficiency of 100%.

The two most important difficulties of the method are: to adjust both paths in phase and amplitude in order to obtain the elimination of any intermodulation; and to work with identical power amplifiers [22, 23, 24].

The CALLUM is a feedback technique with the objective to cancel problems in phase and gain of the LINC [25].

Figure 1.19: CALLUM technique

A Cartesian decomposition on the feedback path is used with the CALLUM method. The output signal is demodulated into two quadrature signals. These signals are compared in baseband domain with the two input signals and used to generate error signals. The main issue of this method is the stability of the system. For this reason, this method can be used only for straight bandwidth modulation.

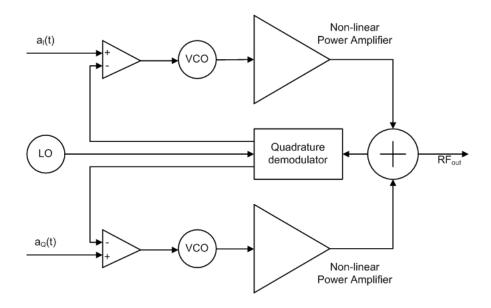

### 1.4.3.4 Doherty technique

Performances of the power amplifier are mainly determined by the load impedance at the output of the transistor [26]. The Doherty technique allows the load impedance to be modified according to the input power thanks to the combination of two power amplifiers: a main and an auxiliary; and also with two lines  $\lambda/4$  which  $Z_C$  and  $Z_{Cin}$  represent the impedance of these lines. (Cf. Figure 1.20)

Figure 1.20: Doherty technique

The  $\lambda/4$  line placed at the output of the main power amplifier realizes the impedance transformation needed to maintain the efficiency over an important variation of the output power. This line will, however, add a phase shift of 90°.

The second  $\lambda/4$  line allows compensation of this phase shift between signals from power amplifiers. Thereby, the in-phase recombination of the output signal is possible.

The functioning of the Doherty technique is as follows:

- For low input power, only the main power amplifier delivers an output signal. The auxiliary power amplifier is turned off.

- For an intermediate power level, the auxiliary power amplifier begins to deliver output power, while the main power amplifier starts to saturate. The fact that the auxiliary power amplifier is turned-on leads to the modification of the load impedance presented by the main amplifier.

- For strong power level, both amplifiers are saturated.

Assuming the same size of the two power amplifiers and the characteristic impedance of the  $\lambda/4$  line  $Z_C = 2.R_{load}$ , load impedances of power amplifiers will vary according to the input power as follows:

- For a low power level, the auxiliary power amplifier is clamped. So its drain current is then equal to zero. In this case, the impedance at the output of the main power amplifier is equal to  $4.R_{load}$ , and the one that is seen at the auxiliary is equal to an open circuit.

- For a high power level, both power amplifiers are saturated and its drain currents are equal. Both amplifiers will have the same load impedance equal to  $2.R_{load}$ .

The transition power  $P_{\alpha}$  is the output power from which the auxiliary amplifier begins to operate. The Table 1.3 summarizes the Doherty amplifier principle:

| Power level                      | Main power amplifier mode  | Auxiliary power amplifier Mode |  |

|----------------------------------|----------------------------|--------------------------------|--|

| Power $< P_{\alpha}$             | Current sources controlled | Turned off                     |  |

| $P_{\alpha}$ < Power < $P_{Max}$ | Saturated                  | Current sources controlled     |  |

| Power = $P_{Max}$                | Saturated                  | Saturated                      |  |

Table 1.3: Doherty amplifier principle

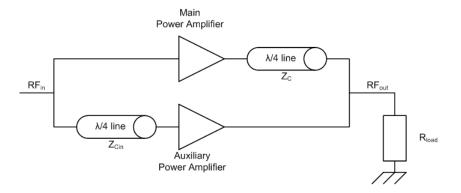

The Figure 1.21 represents the evolution of the efficiency, in cases where the main and the auxiliary power amplifier have the same size, versus the ratio between the load voltage and the voltage supply (Vload/Vdd).

Figure 1.21: Evolution of the efficiency for a two stage Doherty amplifier

The efficiency is evolving linearly to the point corresponding to the transition power  $P_{\alpha}$ . Then, it decreases when the auxiliary power amplifier starts to operate. After that, it increases again

until it reaches the maximum efficiency at the maximum power.

The size of the auxiliary power amplifier depends on the curve variation of the efficiency according to the power level. It imposes different shapes and moves the transition point. The choice of this stage size is related to the application and the shape of the signal to amplify.

This technique can also be realized with several auxiliary power amplifiers. As a consequence, different levels of transition can be obtained, being able to achieve and to maintain a strong efficiency over a wide dynamic output power [27].

The operation class of the auxiliary power amplifier has a strong influence on the power added efficiency of the whole amplifier [27]. An adjustment of the polarization of the auxiliary amplifier is then needed for each output power. A possible solution is to use a variable variation of the auxiliary power amplifier according to the power level available at the input of the amplifier [28].

### 1.4.4 Linearity improvement

### 1.4.4.1 Predistortion / Postdistortion

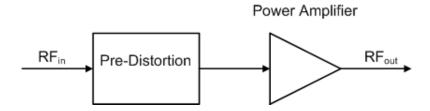

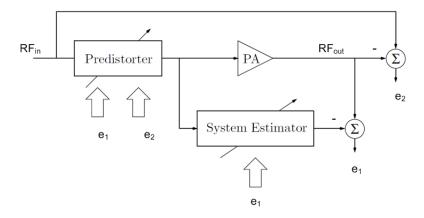

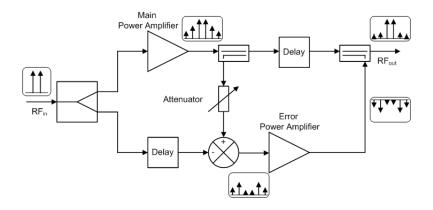

Predistortion technique deals with the RF signal before the power amplifier (Cf. Figure 1.22), and inversely to the postdistortion technique, which deals with the signal after the power amplifier. They can be used for wideband systems and for multi-carriers as amplifiers used for satellite communication.

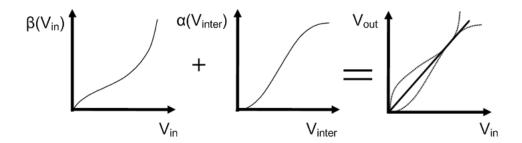

Figure 1.22: Predistortion technique

This approach involves the creation of a complementary function of distortion according to those of the power amplifier. The resulting system from the serialization of the predistortion (or post-distortion) will present few or no distortion at the output.

In the ideal case, the predistortion component generates a distorted signal which is the opposite of those created by the power amplifier (Cf. Figure 1.23). When this generator and the amplifier are cascaded together, distortion is cancelled [29].

Figure 1.23: Signal before and after predistortion technique

The difficulty of this technique is the realization of a circuit able to provide a precise inverse distortion in phase and amplitude of the distortions given by the power amplifier. Meanwhile, due to the relative simplicity of implementation, this technique is interesting for power amplifiers used for mobile system when the size, the cost and a low consumption are the most important parameters.

Different systems are based on a predistortion of the input signal and can be divided into three categories:

- High Frequency (HF) Predistortion: the component of predistortion works at the frequency of the carrier

- Intermediate frequency (IF) Predistortion: the component of predistortion works at an intermediate frequency, allowing the design of a single predistortion for different carrier frequencies. Simply varying the frequency of the local oscillator for the element of predistortion can be used with multiple carriers.

- Baseband Predistortion: before the appearance of DSP, this approach did not give a lot of advantages compared to an IF predistortion. It now becomes a very powerful tool. Predistortion characteristics are saved on a DSP in order to correct the baseband signal.

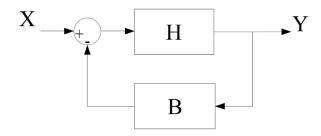

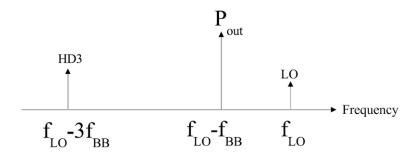

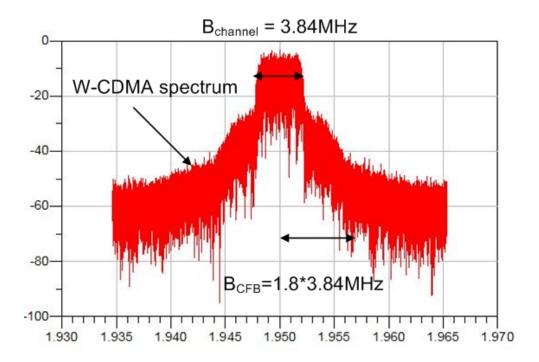

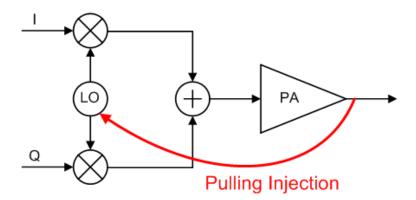

There is no feedback on this technique as the system works as an open loop. This means that the distortion has to be known in advance and performances of this technique can be sensitive to variation due to the process variation, temperature, aging etc.