# Compiling for a multithreaded dataflow architecture: algorithms, tools, and experience

Feng Li

### ▶ To cite this version:

Feng Li. Compiling for a multithreaded dataflow architecture : algorithms, tools, and experience. Other [cs.OH]. Université Pierre et Marie Curie - Paris VI, 2014. English. NNT : 2014PA066102 . tel-00992753v2

## HAL Id: tel-00992753 https://theses.hal.science/tel-00992753v2

Submitted on 10 Sep 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Université Pierre et Marie Curie École Doctorale Informatique, Télécommunications et Électronique

# Compiling for a multithreaded dataflow architecture: algorithms, tools, and experience

# par Feng LI

Thèse de doctorat d'Informatique

# Dirigée par Albert COHEN

Présentée et soutenue publiquement le 20 mai, 2014

Devant un **jury** composé de:

,

,

,

,

,

,

| Président   |

|-------------|

| Rapporteur  |

| Rapporteur  |

| Examinateur |

| Examinateur |

| Examinateur |

|             |

I would like to dedicate this thesis to my mother Shuxia Li, for her love

## Acknowledgements

I would like to thank my supervisor Albert Cohen, there's nothing more exciting than working with him. Albert, you are an extraordinary person, full of ideas and motivation. The discussions with you always enlightens me, helps me. I am so lucky to have you as my supervisor when I first come to research as a PhD student. I would also like to thank Dr. Antoniu Pop, I still enjoy the time we were working together, helped a lot during my thesis, as a good colleague, and a friend.

I am grateful to my thesis reviewers: Prof. Guang Gao and Dr. Fabrice Rastello. Thanks for your time carefully reading the thesis, and providing the useful feedbacks. For the revised version of the thesis, I would also like to thank Dr. Stéphane Zuckerman, he gives very useful suggestions and comments.

I would like to thank all the members in our PARKAS team. Prof. Marc Pouzet, Prof. Jean Vuillemin, and Dr. Francesco Zappa Nardelli invite lots of talks in our group, bring in new ideas and inspirations. Tobias Grosser, Jun Inoue, Riyadh Baghdadi, I still enjoy the time we discussing together, climbing together and flying to conferences. Boubacar Diouf, Jean-Yves Vet, Louis Mandel, Adrien Guatto, Timothy Bourke, Cédric Pasteur, Léonard Gérard, Guillaume Baudart, Robin Morisset, Nhat Minh Lê, you guys are wonderful people to work with!

Special thanks to my friends, Wenshuang Chen and Shunfeng Hu, always like your cooking! Also my friends Shengjia Wang, Ke Song, Yuan Liu, enjoy our beer time, the moments we discuss and implement a new idea.

### Abstract

Across the wide range of multiprocessor architectures, all seem to share one common problem: they are hard to program. It is a general belief that parallelism is a software problem, and that perhaps we need more sophisticated compilation techniques to partition the application into concurrent threads. Many experts also make the point that the underlining architecture plays an equally important role: there needs to be a fundamental change in processor architecture before one may expect significant progress in the programmability of multiprocessors.

Our approach favors a convergence of these viewpoints. The convergence of dataflow and von Neumann architecture promises latency tolerance, the exploitation of a high degree of parallelism, and light thread switching cost. Multithreaded dataflow architectures require a high degree of parallelism to tolerate latency. On the other hand, it is error-prone for programmers to partition the program into large number of fine grain threads. To reconcile these facts, we aim to advance the state of the art in automatic thread partitioning, in combination with programming language support for coarse-grain, functionally deterministic concurrency.

This thesis presents a general thread partitioning algorithm for transforming sequential code into a parallel data-flow program targeting a multithreaded dataflow architecture. Our algorithm operates on the program dependence graph and on the static single assignment form, extracting task, pipeline, and data parallelism from arbitrary control flow, and coarsening its granularity using a generalized form of typed fusion. We design a new intermediate representation to ease code generation for an explicit token match dataflow execution model. We also implement a GCC-based prototype. We also evaluate coarse-grain dataflow extensions of OpenMP in the context of a large-scale 1024-core, simulated multithreaded dataflow architecture. These extension and simulated architecture allow the exploration of innovative memory models for dataflow computing. We evaluate these tools and models on realistic applications.

# Contents

| Lis | st of | Figures                                                           | ix  |

|-----|-------|-------------------------------------------------------------------|-----|

| No  | omer  | nclature                                                          | xii |

| 1   | Intr  | oduction                                                          | 1   |

|     | 1.1   | Hybrid Dataflow for Latency Tolerance                             | 2   |

|     |       | 1.1.1 Convergence of dataflow and von Neumann                     | 2   |

|     |       | 1.1.2 Latency Tolerance                                           | 3   |

|     |       | 1.1.3 TSTAR Multithreaded Dataflow Architecture                   | 5   |

|     | 1.2   | Task Granularity                                                  | 7   |

|     | 1.3   | Motivation                                                        | ç   |

|     | 1.4   | Dissertation Outline                                              | 10  |

| 2   | Pro   | blem Statement                                                    | 12  |

|     | 2.1   | Explicit token matching shifts the challenges in hardware design  |     |

|     |       | to compilation                                                    | 13  |

|     | 2.2   | The complex data structure should be handled in an efficient way  | 14  |

|     | 2.3   | Related Work                                                      | 15  |

|     |       | 2.3.1 Compiling imperative programs to data-flow threads $\ldots$ | 15  |

|     |       | 2.3.2 SSA as an intermediate representation for data-flow com-    |     |

|     |       | pilation  .  .  .  .  .  .  .  .  .                               | 16  |

|     |       | 2.3.3 Decoupled software pipelining                               | 16  |

|     |       | 2.3.4 EARTH thread partitioning                                   | 17  |

|          |                | 2.3.5  | Formalization of the thread partitioning cost model $\ . \ . \ .$ | 18        |

|----------|----------------|--------|-------------------------------------------------------------------|-----------|

| 3        | Thr            | ead Pa | artitioning I: Advances in PS-DSWP                                | 19        |

|          | 3.1            | Introd | luction                                                           | 19        |

|          |                | 3.1.1  | Decoupled software pipelining                                     | 20        |

|          |                | 3.1.2  | Loop distribution                                                 | 21        |

|          | 3.2            | Obser  | vations                                                           | 21        |

|          |                | 3.2.1  | Replacing loops and barriers with a task pipeline $\ldots$ .      | 21        |

|          |                | 3.2.2  | Extending loop distribution to PS-DSWP $\ldots$                   | 22        |

|          |                | 3.2.3  | Motivating example                                                | 23        |

|          | 3.3            | Partit | ioning Algorithm                                                  | 30        |

|          |                | 3.3.1  | Definitions                                                       | 31        |

|          |                | 3.3.2  | The algorithm                                                     | 32        |

|          | 3.4            | Code   | Generation                                                        | 36        |

|          |                | 3.4.1  | Decoupling dependences across tasks belonging to different        |           |

|          |                |        | treegions                                                         | 36        |

|          |                | 3.4.2  | SSA representation                                                | 37        |

|          | 3.5            | Summ   | nary                                                              | 40        |

| <b>4</b> | TST            | far d  | Dataflow Architecture                                             | <b>42</b> |

|          | 4.1            | Datafl | low Execution Model                                               | 42        |

|          |                | 4.1.1  | Introduction                                                      | 42        |

|          |                | 4.1.2  | Past Data-Flow Architectures                                      | 43        |

|          | 4.2            | TSTA   | R Dataflow Execution Model                                        | 47        |

|          |                | 4.2.1  | TSTAR Multithreading Model                                        | 47        |

|          |                | 4.2.2  | TSTAR Memory Model                                                | 48        |

|          |                | 4.2.3  | TSTAR Synchronization                                             | 50        |

|          |                | 4.2.4  | TSTAR Dataflow Instruction Set                                    | 52        |

|          | 4.3            | TSTA   | R Architecture                                                    | 55        |

|          |                | 4.3.1  | Thread Scheduling Unit                                            | 56        |

| <b>5</b> | $\mathbf{Thr}$ | ead P  | artitioning II: Transform Imperative C Program to                 | )         |

|          |                |        | Program                                                           | 61        |

|          | 5.1            | Revisi | t TSTAR Dataflow Execution Model                                  | 62        |

#### CONTENTS

|   | 5.2 | Partit  | ioning Algorithms                                                                                   | 65  |

|---|-----|---------|-----------------------------------------------------------------------------------------------------|-----|

|   |     | 5.2.1   | Loop Unswitching                                                                                    | 66  |

|   |     | 5.2.2   | Build Program Dependence Graph under SSA                                                            | 67  |

|   |     | 5.2.3   | Merging Strongly Connected Components                                                               | 69  |

|   |     | 5.2.4   | Typed Fusion                                                                                        | 69  |

|   |     | 5.2.5   | Data Flow Program Dependence Graph                                                                  | 71  |

|   | 5.3 | Modul   | lar Code Generation                                                                                 | 74  |

|   | 5.4 | Impler  | mentation $\ldots$ | 76  |

|   | 5.5 | Exper   | imental Validation                                                                                  | 78  |

|   | 5.6 | Summ    | ary                                                                                                 | 82  |

| 6 | Har | ndling  | Complex Data Structures                                                                             | 83  |

|   | 6.1 | Stream  | ning Conversion of Memory Dependences (SCMD)                                                        | 84  |

|   |     | 6.1.1   | Motivating Example                                                                                  | 84  |

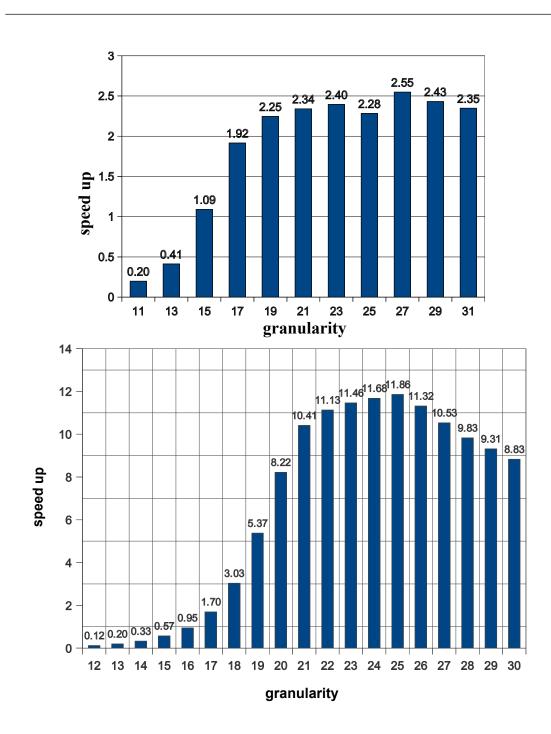

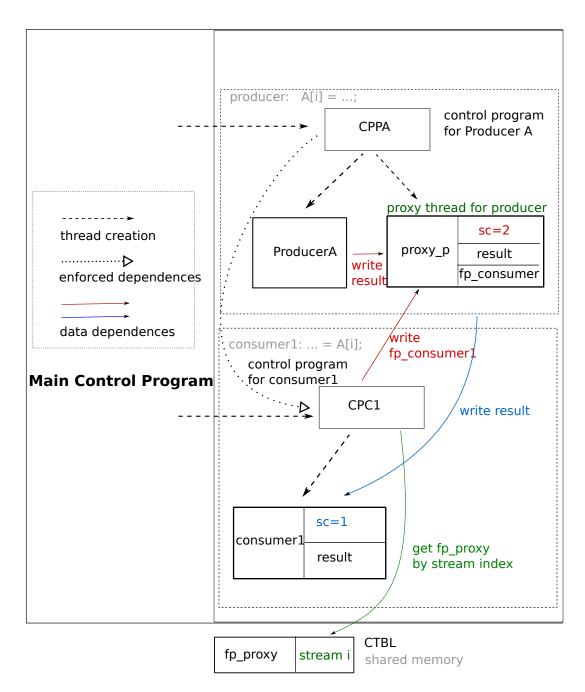

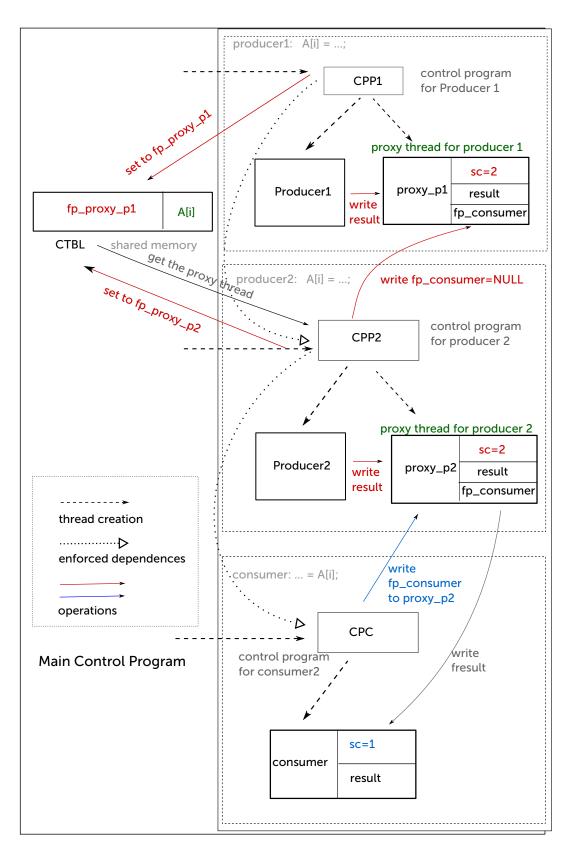

|   |     | 6.1.2   | Single Producer Single Consumer                                                                     | 86  |

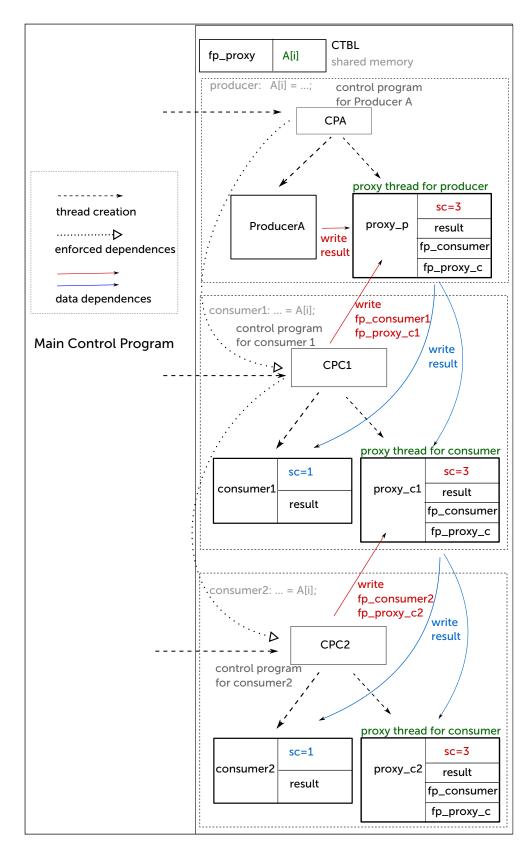

|   |     | 6.1.3   | Single Producer Multiple Consumers                                                                  | 87  |

|   |     | 6.1.4   | Multiple Producers Single Consumer                                                                  | 91  |

|   |     | 6.1.5   | Generated Code for Motivating Example                                                               | 92  |

|   |     | 6.1.6   | Discussion                                                                                          | 96  |

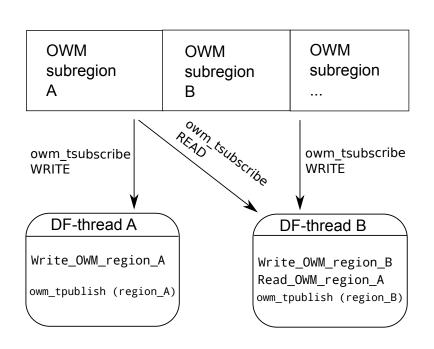

|   | 6.2 |         | r Writable Memory                                                                                   | 96  |

|   |     | 6.2.1   | OWM Protocol                                                                                        | 97  |

|   |     | 6.2.2   | OWM Extension to TSTAR                                                                              | 99  |

|   |     | 6.2.3   | Expressiveness                                                                                      | 101 |

|   |     | 6.2.4   | Case Study: Matrix Multiplication                                                                   |     |

|   |     | 6.2.5   | Conclusion and perspective about OWM                                                                |     |

|   | 6.3 | Summ    | ary                                                                                                 | 105 |

| 7 | Sim | ulation | n on Many Nodes                                                                                     | 106 |

|   | 7.1 | Introd  | uction                                                                                              | 107 |

|   | 7.2 | -       | ble Nodes Dataflow Simulation                                                                       | 108 |

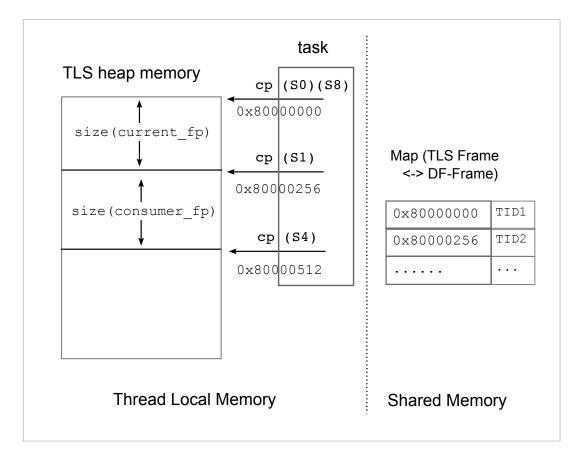

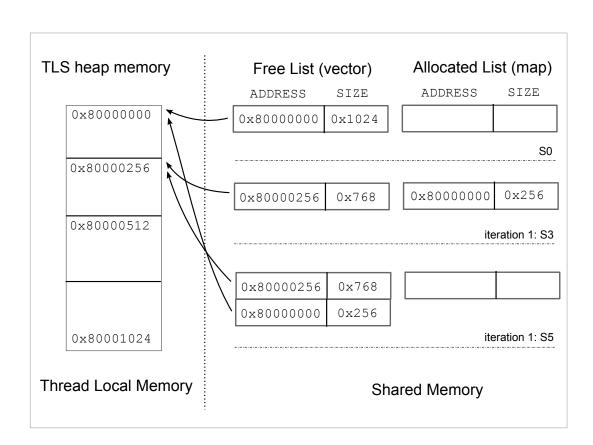

|   | 7.3 | Resou   | rce Usage Optimization                                                                              | 110 |

|   |     | 7.3.1   | Memory Usage Optimization                                                                           | 110 |

|   |     | 7.3.2   | Throttling                                                                                          | 115 |

#### CONTENTS

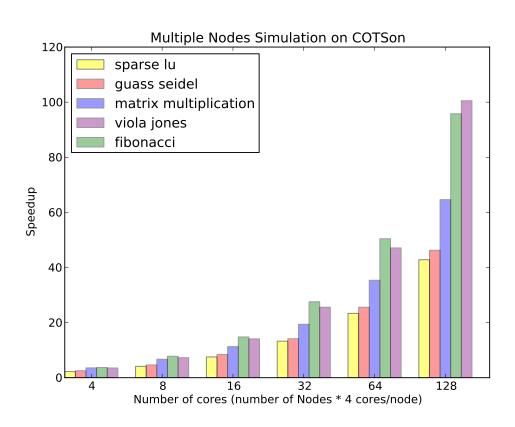

|    | 7.4   | Experimen  | ital V | alidat | ion .   |      | <br> | <br> | <br>• | ••• |       | <br>117 |

|----|-------|------------|--------|--------|---------|------|------|------|-------|-----|-------|---------|

|    |       | 7.4.1 Exp  | perim  | ental  | Settin  | gs . | <br> | <br> | <br>• |     |       | <br>117 |

|    |       | 7.4.2 Exp  | perim  | ental  | Result  |      | <br> | <br> |       |     | <br>• | <br>118 |

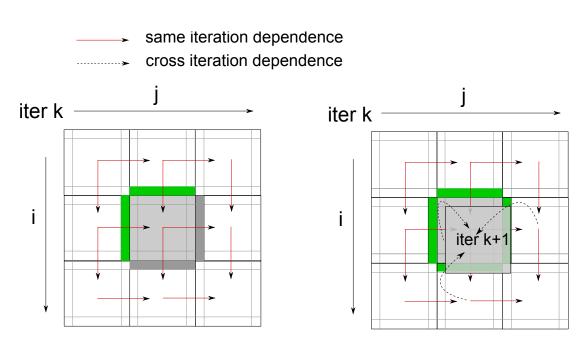

|    |       | 7.4        | .2.1   | Gau    | ss Seid | el . | <br> | <br> |       |     | <br>• | <br>121 |

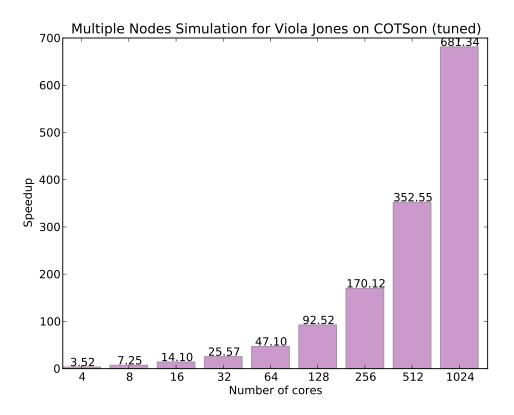

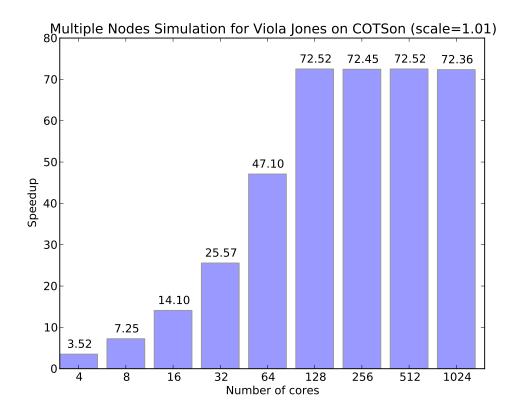

|    |       | 7.4        | .2.2   | Viola  | a Jones | s    | <br> | <br> |       |     | <br>• | <br>124 |

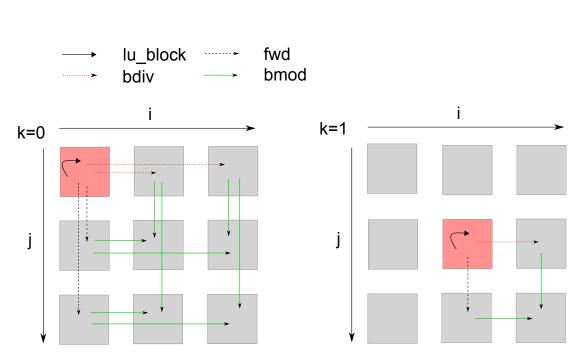

|    |       | 7.4        | .2.3   | Spar   | se LU   |      | <br> | <br> |       |     |       | <br>126 |

|    | 7.5   | Summary    | •••    |        |         |      | <br> | <br> |       |     |       | <br>129 |

| 8  | Con   | clusions a | nd F   | utur   | e Wor   | k    |      |      |       |     |       | 131     |

|    | 8.1   | Contributi | ons    |        |         |      | <br> | <br> |       |     |       | <br>131 |

|    | 8.2   | Future Wo  | ork.   |        |         |      | <br> | <br> | <br>• |     | <br>• | <br>132 |

| Pe | erson | al Publica | tions  | 5      |         |      |      |      |       |     |       | 136     |

| Re | efere | nces       |        |        |         |      |      |      |       |     |       | 138     |

# List of Figures

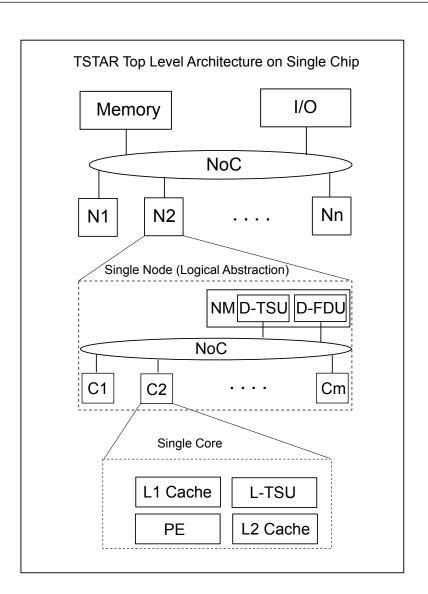

| 1.1  | TStar High level Architecture                                        | 6  |

|------|----------------------------------------------------------------------|----|

| 1.2  | The Parallelism-Overhead Trade-off (from Sarkar)                     | 8  |

| 2.1  | General strategy for thread partitioning                             | 13 |

| 3.1  | Barriers inserted after loop distribution.                           | 21 |

| 3.2  | Pipelining inserted between distributed loops. Initialize the stream |    |

|      | (left), producer and consumer thread (right)                         | 22 |

| 3.3  | Uncounted nested loop before partitioning                            | 24 |

| 3.4  | Uncounted nested loop in SSA form                                    | 25 |

| 3.5  | Loops after partitioning and annotated with OpenMP stream ex-        |    |

|      | tension                                                              | 26 |

| 3.6  | Pipelining and parallelization framework                             | 27 |

| 3.7  | Definition and use edges in the presence of control flow             | 28 |

| 3.8  | Control dependence graph of Figure 3.3. Express the definition of    |    |

|      | treegion                                                             | 30 |

| 3.9  | Split conditional statements to expose finer grained pipelining      | 32 |

| 3.10 | Algorithm for marking the irreducible edges                          | 33 |

| 3.11 | Structured typed fusion algorithm.                                   | 35 |

| 3.12 | Before partitioning (left), and After partitioning (right). Loop     |    |

|      | with control dependences.                                            | 36 |

| 3.13 | Normal form of code (left) and using streams (right)                 | 37 |

| 3.14 | Normal form of code (left) and SSA form of the code (right)          | 37 |

| 3.15 | Apply our algorithm to generate the parallel code. Producer thread   |    |

|      | (left) and consumer thread (right).                                  | 39 |

#### LIST OF FIGURES

| 3.16 | Multiple producers with applied our algorithm, the generated code.        | 40 |

|------|---------------------------------------------------------------------------|----|

| 4.1  | Firing rule example.                                                      | 43 |

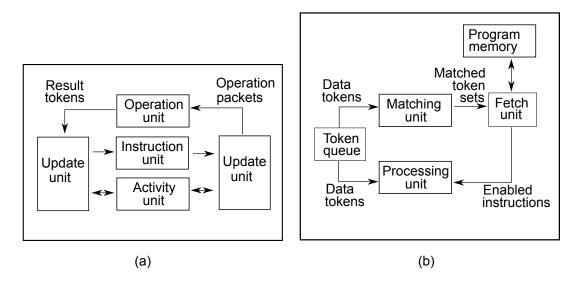

| 4.2  | The basic organization of the static (a) and dynamic (b) model.           | 44 |

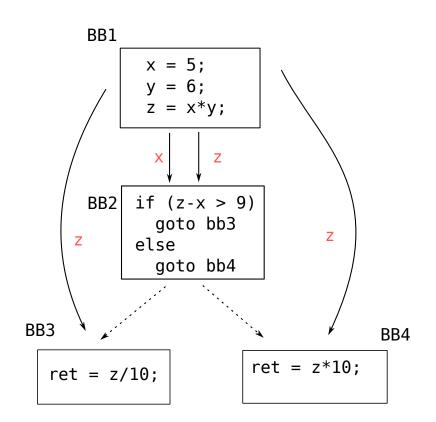

| 4.3  | Program dependence graph of an illustrative example                       | 50 |

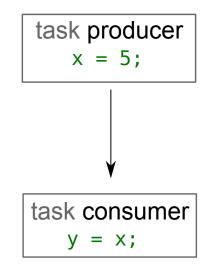

| 4.4  | Producer consumer relationship                                            | 53 |

| 4.5  | Producer consumer code                                                    | 54 |

| 4.6  | TSTAR Highlevel Architecture                                              | 57 |

| 4.7  | Overview of the Thread Scheduling Unit (TSU)                              | 58 |

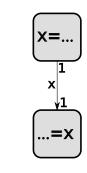

| 5.1  | Explicit Matching Operation.                                              | 62 |

| 5.2  | Program Dependence Graph for explicit token matching compila-             |    |

|      | tion example.                                                             | 64 |

| 5.3  | Running example (left) and after unswitching (right)                      | 66 |

| 5.4  | SSA form before unswitching (left) and after (right).                     | 67 |

| 5.5  | SSA representation after loop unswitching                                 | 68 |

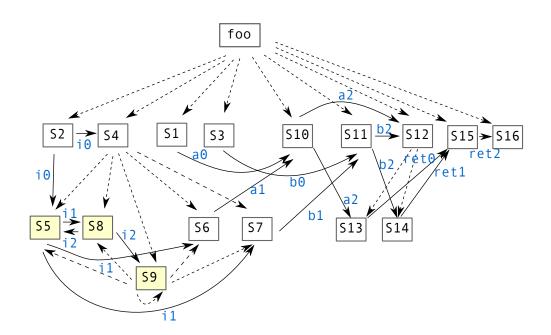

| 5.6  | SSA-PDG for the code example in Figure 5.5                                | 68 |

| 5.7  | SSA PDG after merging the SCC                                             | 69 |

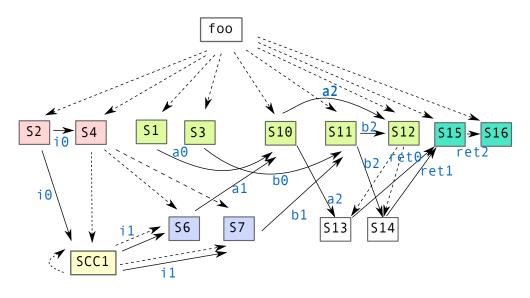

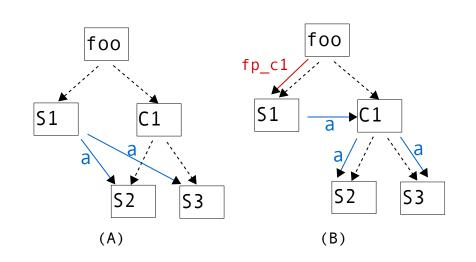

| 5.8  | (A) SSA-PDG after typed fusion. (B) Data Flow Program Depen-              |    |

|      | dence Graph                                                               | 71 |

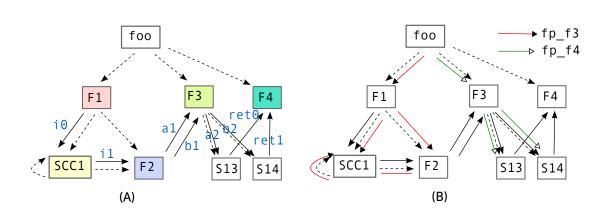

| 5.9  | Splitting data dependences: (A) the original SSA-PDG and (B)              |    |

|      | the generated DF-PDG                                                      | 73 |

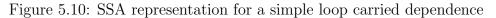

| 5.10 | SSA representation for a simple loop carried dependence $\ldots$ .        | 74 |

| 5.11 | Corresponding SSA-PDG (left) and a partial DF-PDG (right) for             |    |

|      | code in $5.10.$                                                           | 74 |

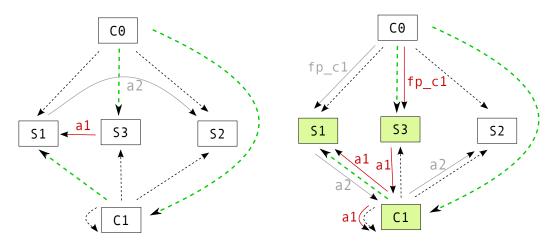

| 5.12 | Caller and callee, threaded version                                       | 76 |

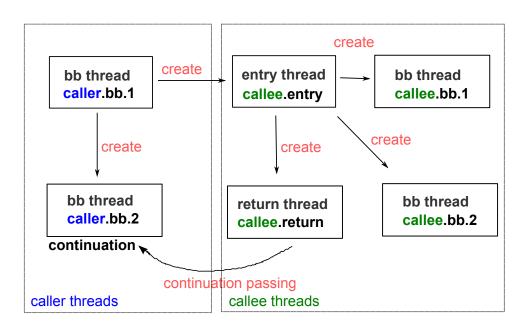

| 5.13 | Implementation within GCC.                                                | 77 |

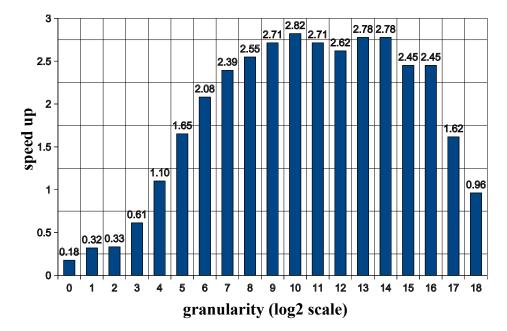

| 5.14 | Merge Sort running on 4 cores                                             | 80 |

| 5.15 | Computing the $42^{\text{th}}$ Fibonacci number on 4 cores (above) and 24 |    |

|      | cores (below)                                                             | 81 |

| 6.1  | Non-linear access for array A within a loop.                              | 84 |

| 6.2  | Decouple computation and memory accesses with loop distribution.          | 85 |

| 6.3  | Single producer single consumer                                           | 88 |

#### LIST OF FIGURES

| 6.4        | Single producer multiple consumers                               | 90  |

|------------|------------------------------------------------------------------|-----|

| 6.5        | Multiple producers and single consumer                           | 93  |

| 6.6        | Generated code for control program using SCMD                    | 94  |

| 6.7        | Generated code for control program using SCMD                    | 95  |

| 6.8        | Owner Writable Memory                                            | 100 |

| 6.9        | Pipeline using OpenStream.                                       | 101 |

| 6.10       | OpenStream cache example                                         | 102 |

| 6.11       | First phase: Matrix allocation and initialization                | 103 |

| 6.12       | Second phase: Matrix multiplication                              | 104 |

| 6.13       | Third phase: Output the results.                                 | 104 |

| <b>H</b> 1 |                                                                  | 107 |

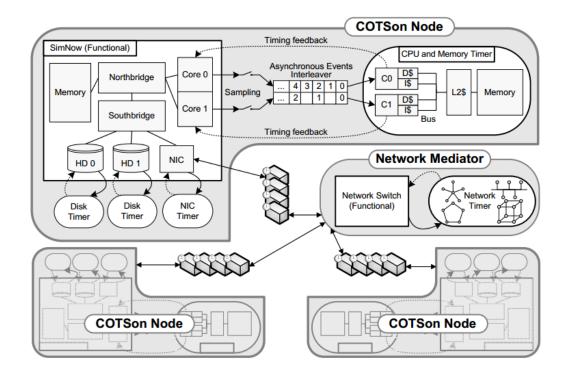

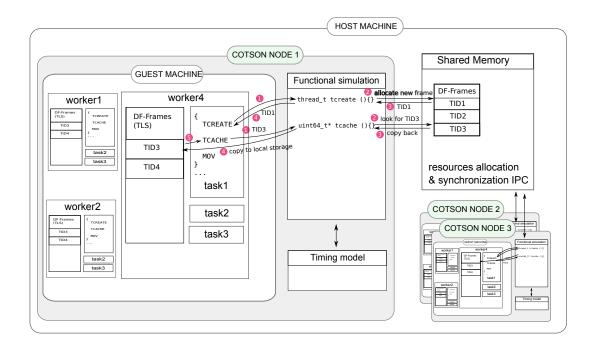

| 7.1        | COTSon Architecture.                                             | 107 |

| 7.2        | Multiple nodes simulation on COTSon                              | 108 |

| 7.3        | Code example for simple frame memory allocator                   | 111 |

| 7.4        | Simple frame memory allocator                                    | 112 |

| 7.5        | Code example for simple frame memory allocator                   | 113 |

| 7.6        | Host Space TLS Frame Memory Allocator                            | 114 |

| 7.7        | Excessive parallelism.                                           | 116 |

| 7.8        | Simulation Results                                               | 119 |

| 7.9        | Simulation Results                                               | 120 |

| 7.10       | Simulation Results                                               | 121 |

| 7.11       | Dependence of gauss seidel: A. same iteration dependences (left) |     |

|            | B. cross iteration dependences (right)                           | 122 |

| 7.12       | Gauss seidel implementation with OpenStream. $\ldots$            | 123 |

| 7.13       | Gauss seidel implementation with OWM support                     | 124 |

| 7.14       | Gauss seidel implementation with OWM support (final task)        | 124 |

| 7.15       | Viola Jones OpenStream kernel                                    | 125 |

| 7.16       | Cascade data structure.                                          | 126 |

| 7.17       | Dynamic OWM memory allocation                                    | 127 |

| 7.18       | Dependence patterns of sparse lu: A. $k = 0$ B. $k = 1$          | 128 |

|            | Sparse lu OpenStream implementation for bdiv dependences         | 128 |

| 7.20       | Sparse lu OpenStream implementation for bdiv dependences (with   |     |

|            | OWM support).                                                    | 129 |

|            |                                                                  |     |

8.1 High level overview of the compilation and simulation architecture. 134

# Chapter 1

# Introduction

The design complexity and power constraints of large monolithic processors forced the industry to develop Chip-Multiprocessor (CMP) architectures. Across the diverge range of multiprocessor architectures, all seems to share one common problem: they are hard to program. The application writer has to take detailed architecture specific measures to improve the performance, and the resulting code are hard to read, maintain or debug, and not even to mention performance portability.

It is a general belief that the difficulties of parallel programming is a software problem. Perhaps we need more sophisticated compilers, to partition the applications into tasks that can run in parallel and to coordinate or synchronize them to implement a given functional semantics. Or perhaps we need more abstract parallel programming languages, allowing the programmer to write applications or port legacy code in a productive way, and then rely on static and dynamic algorithms to exploit the target architecture

It is also argued that the design and programming interface of a multiprocessor architecture plays an equally important role. It may very well be that the conventional cache-coherent multiprocessors derived from the von Neumann model are not suitable for the scalable and productive exploitation of parallelism. Following this school of thought, there is a need for a fundamental change in processor architecture before we can expect significant progress in the use of multiprocessors.

This thesis presents a general thread partitioning algorithm for transform-

ing sequential code into a parallel data-flow program targeting a multithreaded dataflow architecture. Our algorithm operates on the program dependence graph and on the static single assignment form, extracting task, pipeline, and data parallelism from arbitrary control flow, and coarsening its granularity using a generalized form of typed fusion. We design a new intermediate representation to ease code generation for an explicit token match dataflow execution model. We also implement a GCC-based prototype. We also evaluate coarse-grain dataflow extensions of OpenMP in the context of a large-scale 1024-core, simulated multithreaded dataflow architecture. These extension and simulated architecture allow the exploration of innovative memory models for dataflow computing. We evaluate these tools and models on realistic applications.

## 1.1 Hybrid Dataflow for Latency Tolerance

The early study starts from dataflow architectures. By contrast with von Neumann architecture, the execution of an instruction in dataflow model is driven by the availability of data. In 1975, Dennis and Misunas proposed the static dataflow architecture Dennis & Misunas [1979], due to the limitation with iterative constructs and reentrancy Arvind & Culler [1986b], the dynamic, or tagged-token dataflow architecture was proposed by Watson and Gurd Watson & Gurd [1979], which exposes additional parallelism by allowing multiple instances of reentrant code, the main disadvantage of the dynamic model is the extra overhead in matching tags on tokens.

#### 1.1.1 Convergence of dataflow and von Neumann

The limit of the static dataflow model and the large cost of dynamic dataflow execution of individual instructions led to the convergence of dataflow and von Neumann models. The hybrid architecture considered in this thesis moves from fine-grained parallelism towards coarse-grained execution model, which combines the power of the dataflow model for exploiting parallelism with the efficiency of the control-flow model. Two key features supporting this shift are low-cost sequential scheduling of instructions and the use of registers to temporarily hold the results of instructions in a single thread.

Sequential instruction scheduling takes advantage of the fact that any dataflow program displays some level of sequential execution. For example, in the case where the output of one node goes to the next node, the dependences between two nodes could never executed in parallel. Therefore, there is little point to scheduling them to different processors. Sequential scheduling enables a coarser grain of parallelism compared to one instruction per task in pure dataflow model, allows to use of a simple control-flow sequencing within the grain. This comes from the fact that the data-driven sequencing is unnecessarily general and at a cost of overhead required to match tokens. Combining sequential scheduling with instruction-level context switching also gives another perspective of dataflow architectures: multithreading. In multithreaded architectures, a thread is defined as a sequence of statically ordered instructions, where once the first instruction is fired, the remaining will execute without interruption.

Multiple flavors of hybrid architectures exist: one approach essentially follows the von Neumann architecture with a few dataflow additions (large-grain dataflow architecture), another approach extends a dataflow architecture with some von Neumann additions (multithreaded dataflow architecture) Papadopoulos & Traub [1991]; Lee & Hurson [1994]; Iannucci [1988]; Nikhil [1989]; Nikhil *et al.* [1992]; Culler *et al.* [1991].

#### 1.1.2 Latency Tolerance

The term *von Neumann bottleneck* was coined by John Backus in his 1977 ACM Turing Award lecture. According to Backus:

Surely there must be a less primitive way of making big changes in the store than by pushing vast numbers of words back and forth through the von Neumann bottleneck. Not only is this tube a literal bottleneck for the data traffic of a problem, but, more importantly, it is an intellectual bottleneck that has kept us tied to word-at-a-time thinking instead of encouraging us to think in terms of the larger conceptual units of the task at hand. Thus programming is basically planning and detailing the enormous traffic of words through the von Neumann bottleneck, and much of that traffic concerns not significant data itself, but where to find it Backus [1978]

The shared bus between the program memory and data memory leads to the von Neumann bottleneck, the limited communication bandwidth between the CPU and memory limits the effective processing speed when the CPU is required to perform minimal processing on large amount of data - which is also referred as the memory wall. The memory wall is the growing disparity of speed between CPU and memory outside the CPU chip. Because of the memory wall, enhancing the CPU alone cannot guarantee improvements on system performance. From 1986 to 2000, CPU speed improved at an annual of 55 percent while memory speed only improved at 10 percent. More over, when memory is physically distributed, the latency of the network and network interface is added to that of accessing the local memory on the node. Given these trends, it was expected that memory latency would become an overwhelming bottleneck in computing performance.

As the rapid progress of the multiprocessor speed, two main issues has to be addressed: *latency* and *synchronization*. Latency appears in various forms in multiprocessor, from a few cycles at the instruction level such as pipeline bubbles caused by branch instructions, to tens of cycles cause by cache misses (memory latency), up to hundreds of cycles caused by inter-processor communication, or even worse, thousands of cycles caused by the IO. Synchronization is equally important to enforce the ordering of instruction executions according to their data dependencies, in order to ensure deterministic behavior.

There are basically two ways of fighting latency, reducing and tolerating. For instance, as a hardware approach, we might replace the disk with a new storage media, as fast as RAM to reduce the IO latency, or we could apply the software approach, removing some of the inter-process communications by apply compiler optimizations, or apply the branch prediction at instruction level to remove the pipeline bubbles. However, no matter how advanced the technology is, we could not eliminate all latencies. The latencies caused by communication and synchronization are inherent in parallel applications. Tolerating therefore maybe the only available option under this circumstances.

Prefetching and multithreading are two ways of tolerating latencies. Prefetching is a mechanism that loads data into the cache or local memory before it is actually used, anticipating it will be used in the near future. Thus prefetching is very effective if the latency length can be predicted at compile time. By contrast, multithreading is more general and flexible in coping with unpredicted latencies.

In a multithreaded dataflow architecture (or multithreading with dataflow origin), a program is partitioned into multiple threads, each thread is the unit of execution and scheduled to run dynamically. Within a thread, instructions are issued to executed sequentially as on a von Neumann architecture. Among threads, they are scheduled to run when the firing rule is satisfied. A strict firing rule allows a thread to execute only when all its inputs are available. During the execution of a thread, if there is a long latency operation, the processor can switch to another ready thread and do other useful work. If there is enough parallelism in application and a multithreaded machine can do fast thread switching, latencies caused by long latency operations can be overlapped with the execution of useful instructions from other threads. Thus latencies are effectively covered on such a multithreading machine.

A key open question for multithreaded dataflow architecture is how best to partition the programs into threads and what degree of granularity is best.

#### 1.1.3 TSTAR Multithreaded Dataflow Architecture

TSTAR is a multithreaded dataflow architecture we target on, where in the interthread level, threads are executed in a multithreading environment, scheduled according to the dataflow model to better exploit parallelism, while in the intrathread level, each thread is compiled into sequential von Neumann processor.

TSTAR execution model is a feed-forward dataflow execution model with explicit token matching, where the producers write directly to their consumers. This model origins from several inputs of our partners in the TERAFLUX project<sup>1</sup> DDM execution model from Arandi & Evripidou Arandi & Evripidou [2011]; T\* instruction set from Portero et al. Portero et al. [2011]. We will present the TSTAR execution model in detail in chapter 4.

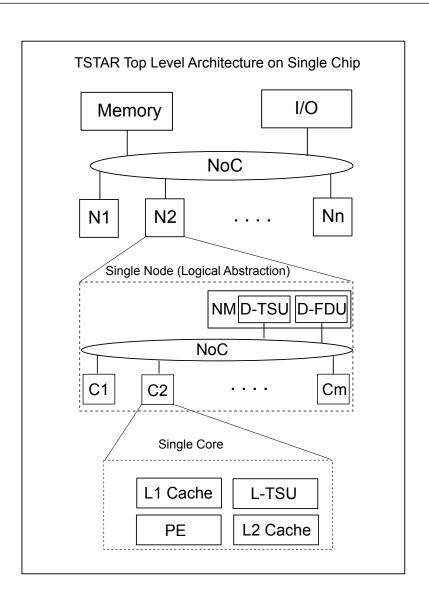

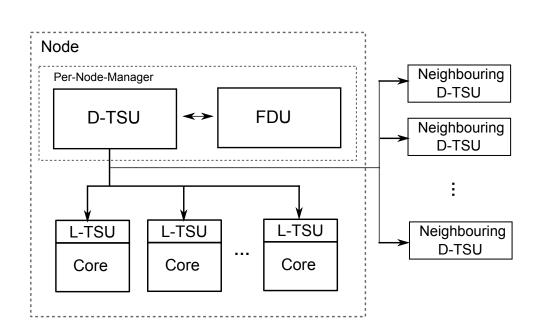

Figure 1.1 shows the TSTAR top level architecture. C2 is the single core which contains a processing element (x86-64 ISA with TStar extensions) along

<sup>&</sup>lt;sup>1</sup>http://www.teraflux.eu

with its L1 cache. Each core also includes a partition of the L2 cache. In order to support the dataflow execution of threads, each core includes a hardware module that handles the scheduling of threads - the Local Thread Scheduling Unit (L-TSU). In addition to cores, the nodes also contain a hardware module to coordinate the scheduling of the data-flow threads among the cores - the Distributed Thread Scheduling Unit (D-TSU), as well as a hardware module that monitors the performance and faults of the cores - the Distributed Fault Detection Unit (D-FDU).Each core is identified with a unique id, the Core ID (CID), and each group of cores belongs to a node whose id is the Node ID (NID). Nodes are connected via an inter-node network, the Network on Chip (NoC). Cores within a node are connected via the NoC.

### **1.2** Task Granularity

An important issue in multiprocessor performance is the granularity of the program execution. The granularity of a parallel program can be defined as the average size of a sequential unit of computation in the program, with no interprocessor synchronization or communications. For a given machine with multiprocessors, there is a fundamental trade-off between the granularity (amount of parallelism) and the overhead of synchronization. It is desirable for a multiprocessor to have small granularity, so that it can exploit larger amount of parallelism. It is also desirable for a parallel program to have larger granularity, so that the synchronization and communication overhead could be relatively small compared to the actual workloads.

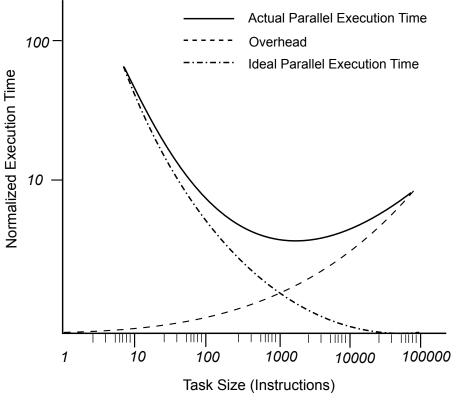

Sarkar Sarkar [1989] articulates this trade-off as the competing contributions of the ideal parallel execution time, the amount of time required to execute the program in the absence of the overhead, with the overhead factor, the extra work required to schedule and coordinate the tasks. The ideal parallel execution time is multiplied by the overhead factor to yield actual parallel execution time, the amount of time required to complete the problem for a given task granularity in the presence of scheduling overhead.

Figure 1.2 (from Sarkar) illustrates the general characteristic of the parallelismoverhead trade-off for a typical program running on a machine with ten proces-

Figure 1.1: TStar High level Architecture.

sors. This plot is suggestive of what was experienced running various programs on contemporary multiprocessors, but it does not express the data from a specific machine or application. The normalized execution time is the ratio n/s where n is the number of processors and s is the actual speedup relative to a single processor. The normalized ideal parallel execution time increases from 1 to nas the task granularity increases from a single instruction, to 100,000 when the entire program executes as a single task. The task overhead factor is given by (g + o)/g where g is the task size in the instructions and the o is the per-task overhead, in this case 1000 instructions.

10 processors, 100000 Instructions, Overhead = 1000 Instructions/Task

Figure 1.2: The Parallelism-Overhead Trade-off (from Sarkar)

It shows for a given multiprocessor, there is a minimum program granularity value below which the performance degrades significantly. Although the overhead shows in this figure is relatively long (1000 instructions/task), but we believe as the construct of the multiprocessor evolves, the overhead will decrease accordingly. There is always a trade-off between the number of parallelism and the task switching overhead. Within our multithreaded dataflow architecture, we assume a relatively low task overhead, by means of one to ten instructions per task. The hardware support largely reduce the synchronization and communication overhead. So we assume task overhead is not a first order issue, and the objective for thread partitioning is to expose the maximum amount of parallelism, and coarsen the granularity stays as an optimization pass in the procedure.

## 1.3 Motivation

There are three fundamental problems to be solved when compiling a program for parallel execution on a multiprocessor:

- Identifying parallelism in the program.

- Partitioning the program into sequential tasks.

- Scheduling the tasks on processors.

The problem of identifying or expressing parallelism belongs to the domain of programming language. Scheduling the tasks on processors is managed by a dedicated Thread Scheduling Unit (TSU) in the TSTAR multithreaded dataflow architecture. Partitioning the program into sequential tasks and targeting on TSTAR architecture is a main focus in this dissertation.

Multithreaded dataflow architectures require high-degree of TLP to tolerate latency. It is error-prone to ask programmers to partition the program to a large number of fine grain threads. On the other hand, porting the legacy code takes a large amount of work. Therefore, it is essential to have compiler support for multithreaded dataflow architectures so that they can be partitioned efficiently and widely accepted.

Automatic program parallelization techniques plus programmer efforts (e.g. annotations) can be applied to identify potential TLP. In our target architecture, threads are non-preemptive: once a thread starts its execution, it cannot be interrupted. In the non-preemptive model, thread start and end points are decided at compile time. It is the compiler's job to perform thread partitioning and optimize the partitioned code at compile time. Because of this, a compiler targeting multithreaded dataflow architecture faces real challenges when automatically partitioning threads:

- It must partition the program correctly with respect to the dependences constraints.

- It should perform optimizations on threads partitioned to make them execute efficiently.

• It should handle the complex data structures (like arrays) in an efficient way.

Thread partitioning is a challenging task in developing a compiler for multithreaded dataflow architectures. Measuring the performance metrics on the multithreaded dataflow architecture plays an equally important role. Before the real hardware processor is built, we need a flexible methodology to analyze the behavior of the proposed architecture. By performing simulations and analyzing the results with a full-system simulator, we can gain a thorough understanding how the proposed architecture behaves, how to improve it, and validate the results before it goes into the production cycle.

We will try to address all the issues mentioned above in this dissertation.

## **1.4** Dissertation Outline

The rest of the dissertation is organized as follows.

In chapter 2 we present the problem statement when compiling for a multithreaded dataflow architecture.

As a preliminary research on thread partitioning, chapter 3 presents a thread partitioning algorithm. The algorithm extends loop transformations and Parallel Stage Decoupled Software Pipelining (PS-DSWP). Section 3.1 presents the related work in PS-DSWP and loop distribution. Section 3.2 presents our observations with extending loop distribution to PS-DSWP and a motivating example. Section 3.3 presents our thread partitioning algorithms based on SSA and treegion representation. After deciding the partition point between the original treegions, Section 3.4 explains the code generation challenges in presence of multiple producers and consumers.

Chapter 4 presents a general view of the TSTAR dataflow architecture. Section 4.1 gives an overview of the dataflow execution model. Section 4.2 further explains the TSTAR execution model from different aspects (multithreading model, memory model and synchronization), and section 4.3 gives an overview of the TSTAR architecture.

Chapter 5 presents a general algorithm for thread partitioning targets on

the TSTAR architecture, which transform sequential imperative programs into parallel data-flow programs. The algorithm operates on a program dependence graph in SSA form, extracting task, pipeline and data parallelism from arbitrary control flow, and coarsening its granularity using a generalized form of typed fusion. A prototype is implemented in GCC, and we give the evaluation results in the final section.

Chapter 6 complements chapter 5. In this chapter, we studies the method of handling complex data structure (such as arrays) in thread partitioning. Streaming Conversion of Memory Dependences (SCMD) connects independent writes and reads to the same memory location with stream dynamically. Owner Writable Memory model (OWM) is proposed to reduce the communication overheads when operating on complex data structures.

Chapter 7 presents the simulation infrastructure and benchmarks written with OWM memory model to validate the approach.

We conclude and draw some perspectives in chapter 8.

# Chapter 2

# **Problem Statement**

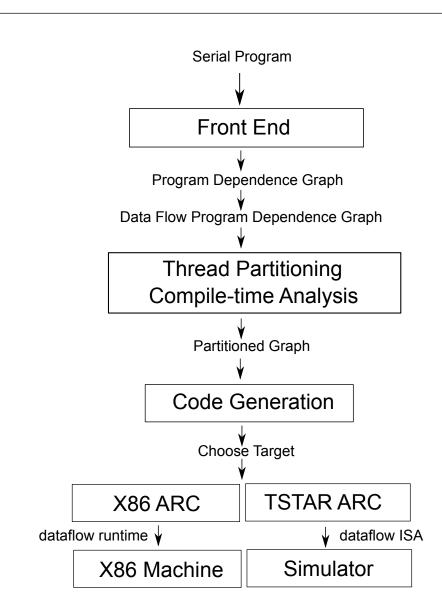

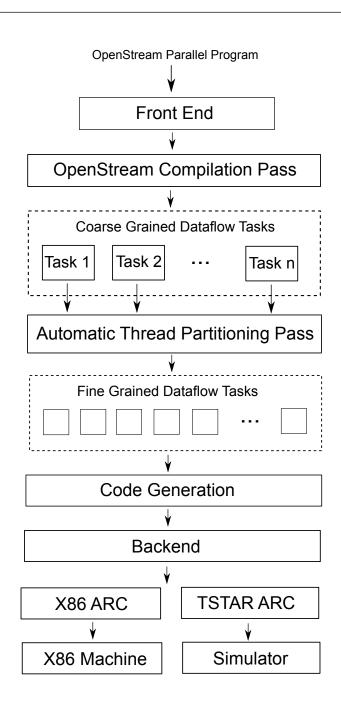

Figure 2.1 shows a general strategy for automatic thread partitioning. A serial program is translated to intermediate representations (Program Dependence Graph and Data Flow Program Dependence Graph). The IR is an input to the compile time analysis phase of the partitioning system. The output produced by compile-time analysis is a partition of the program graph into subgraphs which represent tasks. Finally, the code generation phase generate code for both x86 and TSTAR dataflow architectures.

Depending on the target, the compilation strategy diverges after thread partitioning. If the target is x86 architecture, the TSTAR backend in the compiler is disabled, the generated code will be linked to x86 dataflow runtime library. If target on TSTAR dataflow architecture, the backend will translate the dataflow builtin functions to dataflow ISA, so that it could be simulated on the full-system simulator.

Thread partitioning is a challenging task in developing a compiler for a multithreaded dataflow machine. Besides the points we discussed in previous chapter, we stress a few more points in this section.

Figure 2.1: General strategy for thread partitioning.

# 2.1 Explicit token matching shifts the challenges in hardware design to compilation

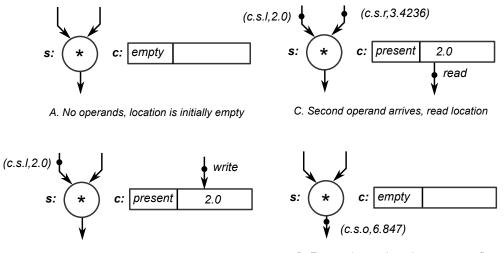

In the non-preemptive thread model, each thread runs to completion once started. The data and control dependences need to be resolved and satisfied at partitioning stage. Unlike tagged-token dataflow machines, the tokens are stored separately in the *Frame Memory*, and use an explicit token matching strategy in TSTAR execution model.

Tagged-token dataflow machines are implemented through a sophisticated matching hardware, which dynamically schedules operations with available operands Arvind & Culler [1986b] Memo & Culler [1983]. When a token arrives at a processor, the tag it carries is checked against the tags present in the token-store. If a matching token is found, it is extracted and the corresponding instruction is enabled for execution; otherwise, the incoming token is added to the store. This allows for a simple non-blocking processor pipeline that can overlap instructions from closely related or completely unrelated computations. However, the matching operation involves considerable complexity on the critical path of instruction scheduling Gajski *et al.* [1982].

The more subtle problem with the matching paradigm is that a failure to find a match implicitly allocates resources within the token store. Thus in mapping computations to processors places an unspecified commitment on the token storage hardware, if this resource becomes overcommited, the program may deadlock.

Explicit Token Matching shifts the complications from the hardware design of token-matching system to the compiler. The compiler has to match the producers and consumers explicitly. In TSTAR execution model, as producer data flow threads communicate by writing directly in the data flow frame of their consumers, it is necessary that, along all data dependence edges of the program dependence graph, the producer nodes know the data flow frame of the consumer nodes. It becomes more complicates when the producer and consumer are created by separate control programs, which means there needs to be a way to communicate such information. We address this issue in chapter 5.

# 2.2 The complex data structure should be handled in an efficient way

There are two basic approaches to represent data structures such as arrays: direct and indirect access schemes Gaudiot & Wei [1989]. The direct access scheme treats each structure element as individual data tokens. The dataflow functionality principle implies that all operations are side-effect free. The direct access scheme is compatible with the dataflow principle. However, absence of side effect also means the token carries vectors, arrays or other complex data structures results in a new data structure, which will greatly increase the communication overhead in practice.

On the other hand, in an indirect access scheme, data structures are stored in special memory units and their elements are access through "read" and "write" operations. Literature has shown that storing the data structures and representing them by indirect access incurs less overhead that the direct access scheme in transmitting data, reconstructing the resultant array, and randomly accessing array elements.

However, the indirect access approach is not free of charge. When the array elements are stored in a separate storage, to preserve the functionality principle of dataflow, a write to a single element in the array might result in copying the entire array. If the array elements are stored in a virtual memory that is global addressable to all nodes, the consistent view of the virtual memory to related threads becomes a demanding task. We address this problem in Chapter 6.

### 2.3 Related Work

#### 2.3.1 Compiling imperative programs to data-flow threads

The problem of compiling imperative programs for data-flow execution has been widely studied. Beck et al. Beck et al. [1989] propose a method for translating control flow to data flow, and show that data-flow graphs can serve as an executable intermediate representation in parallelizing compilers. Ottenstein et al. Ottenstein et al. [1990] study such a translation using the Program Dependence Web, an intermediate representation based on gated-SSA Tu & Padua [1995] that can directly be interpreted in either control-, data-, or demand-driven models of execution. Programs are transformed to the MIT dataflow program graph Arvind & Nikhil [1990], targeting the Monsoon architecture.

Najjar et al. evaluated multiple techniques for extracting thread-level dataflow Najjar *et al.* [1994]. These papers target a token-based, instruction-level data-flow model, analogous to the simulation of hardware circuits. In contrast, our data-flow model does not require tokens or associative maps, shifting the effort of explicitly assign the consumer threads to their producers to the compiler. The comparison between our approach and the token-based solution is further discussed in chapter 5. In addition, thread-level data-flow requires additional efforts to coarsen the grain of concurrency, handling the dynamic creation of threads, and managing their activation records (data-flow frames).

# 2.3.2 SSA as an intermediate representation for data-flow compilation

The static single assignment form (SSA) is formally equivalent to a well-behaved subset of the continuation-passing style (CPS) Appel [1998]; Kelsey [1995] model, which is used in compilers for functional languages such as Scheme, ML and Haskell. The data-flow model has been tied closely to functional languages, since the edges in a data-flow graph can be seen both as encoding dependence information as well as continuation in a parallel model of execution. The SSA representation builds a bridge between imperative languages and the data-flow execution model. Our algorithm uses the properties of the SSA to streamline the conversion of general control flow into thread-level data-flow.

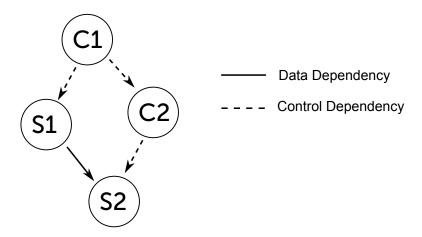

#### 2.3.3 Decoupled software pipelining

Closely related to our work, and in particular to our analysis framework, is the *decoupled software pipelining* (DSWP) technique Ottoni *et al.* [2005]. It partitions loops into long-running threads that communicate via inter-core queues, following the execution model of Kahn process networks Kahn [1974]. DSWP builds a Program Dependence Graph (PDG) Ferrante *et al.* [1987], combining control and data dependences (scalar and memory). In contrast to DOALL and DOACROSS Cytron [1986] methods which partition the iteration space into threads, DSWP partitions the loop body into several stages connected with pipelining to achieve parallelism. It exposes parallelism in cases where DOACROSS is limited by loop-carried dependences on the critical path, it handles uncounted loops, complex control flow and irregular pointer-based memory accesses. Parallel-

Stage Decoupled Software Pipelining (PS-DSWP) Raman *et al.* [2008] is an extension to combine pipeline parallelism with some stages executed in a DOALL, data-parallel fashion. For example, when there are no dependences between loop iterations of a DSWP stage, the incoming data can be distributed over multiple data-parallel worker threads dedicated to this stage, while the outgoing data can be merged to proceed with downstream pipeline stages.

These techniques have a few caveats however. They offer limited support for decoupling along backward control and data dependences. They provide a complex yet somewhat conservative code generation method to decouple dependences between source and target statements governed by different control flow.

### 2.3.4 EARTH thread partitioning

Another thread partitioning method closely related to our work is used in EARTH architecture compilation technique Tang *et al.* [1997]. The thread partitioning method operates on the Program Dependence Flow Graph (PDFG). A PDFG graph could be built based on the Program Structure Tree (PST) representation. A PST tree of a program is a hierarchical representation of the control structure of the program (similar to the control dependence graph we used in the thesis). In the PST representation, all the nodes control dependent on the same node belongs to the same region. The PDFG is built upon PST by introducing data dependences inside each basic region. The cross region data dependences is promoted up to the same region level.

Our thread partitioning method presents in Chapter 5 differs in several aspects:

• In the EARTH partitioning method, the promotion of cross region dependences creates extra overhead upon each promotion — the outer regions needs to create continuations to wait for the data passing from the inner region. When the destination region get the data passing from the source, it still needs to pass the data down to the lower region where the actual dependence happens.

Our method, instead of dependence promotion, we reserve the point to point cross region dependence, passing the consumer's thread information to its producer by building and analyzing the DataFlow Program Dependence Graph (DF-PDG). A detailed algorithm is described in Chapter 5.2.5.

• Our method operates on the SSA-PDG form. There are two main reasons for relying on a SSA-based representation of the PDG: 1. SSA is formally equivalent to a well-behaved subset of the continuation-passing style model. By making the reaching definitions unique for each use, effectively converting the scalar flow into a functional program. 2. Reducing the complexity of analyzing def-use chains from  $O(N^2)$  to O(N), as the number of def-use edges can become very large, sometimes quadratic in the number of nodes.

#### 2.3.5 Formalization of the thread partitioning cost model

Sarkar Sarkar [1989] has formally defined the macro-dataflow model and developed the cost model of the partitioning method targeting this dataflow architecture, shows that the problem of determining the optimal partition, with the smallest execution time is NP-complete in the strong sense. Tang Tang & Gao [1999] Tang *et al.* [1997] has formalized the EARTH dataflow execution model and developed the cost model for this architecture, shows the thread partitioning problem is NP complete.

The TSTAR dataflow architecture is similar to EARTH. The formalization is not our focus in this thesis since it has already been proven. Thus, in this thesis, we provide a simple heuristic algorithm for coarsening the granularity of the dataflow threads.

# Chapter 3

# Thread Partitioning I: Advances in PS-DSWP

As a preliminary research on thread partitioning, we presents a thread partitioning algorithm in this chapter. The algorithm extends loops distribution with pipelining to Parallel Stage Decouple Software Pipelining (PS-DSWP). By assertting a synchronous concurrency hypothesis, the data and control dependences can be decoupled naturally with only minor changes to existing algorithms that have been proposed for loop distribution and loop fusion.

Section 3.1 presents the related works in PS-DSWP and loop distribution. Section 3.2 presents our observations with extending loop distribution to PS-DSWP and a motivating example. Section 3.3 presents our thread partitioning algorithms based on SSA and treegion representation. After deciding the partition point between the original treegions, Section 3.4 explains the code generation challenges in presence of multiple producers and consumers.

### 3.1 Introduction

The most closely related work to this chapter is decoupled software pipelining and loop distribution. We recall the state-of-the-art in both and present the original finding at the source of this work: by extending loop distribution with pipelining and asserting a synchronous concurrency hypothesis, arbitrary data and control dependences can be decoupled very naturally with only minor changes to existing algorithms that have been proposed for loop distribution Kennedy & McKinley [1990].

#### 3.1.1 Decoupled software pipelining

Decoupled Software Pipelining (DSWP) Ottoni *et al.* [2005] is one approach to automatically extract threads from loops. It partitions loops into long-running threads that communicate via inter-core queues. DSWP builds a Program Dependence Graph (PDG) Ferrante *et al.* [1987], combining control and data dependences (scalar and memory). Then DSWP introduces a load-balancing heuristic to partition the graph according to the number of cores, making sure no recurrence spans across multiple partitions. In contrast to DOALL and DOACROSS Cytron [1986] methods which partition the iteration space into threads, DSWP partitions the loop body into several stages connected with pipelining to achieve parallelism. It exposes parallelism in cases where DOACROSS is limited by loopcarried dependences on the critical path. And generally speaking, DSWP partitioning algorithms handles uncounted loops, complex control flow and irregular pointer-based memory accesses.

Parallel-Stage Decoupled Software Pipelining Raman *et al.* [2008] (PS-DSWP) is an extension to combine pipeline parallelism with some stages executed in a DOALL, data-parallel fashion. For example, when there are no dependences between loop iterations of a DSWP stage, the incoming data can be distributed over multiple data-parallel worker threads dedicated to this stage, while the outgoing data can be merged to proceed with downstream pipeline stages.

These techniques have a few caveats however. They offer limited support for decoupling along backward control and data dependences. They provide a complex code generation method to decouple dependences among source and target statements governed by different control flow, but despite its complexity, this method remains somewhat conservative.

By building the PDG, DSWP also incurs a higher algorithmic complexity than typical SSA-based optimizations. Indeed, although traditional loop pipelining for ILP focuses on innermost loops of limited size, DSWP is aimed at processing large control flow graphs after aggressive inter-procedural analysis optimization. In addition, the loops in DSWP are handled by the standard algorithm as ordinary control flow, missing potential benefits of treating them as a special case. To address these caveats, we turned our analysis to the state of the art in loop distribution.

### 3.1.2 Loop distribution

Loop distribution is a fundamental transformation in program restructuring systems designed to extract data parallelism for vector or SIMD architectures Kennedy & McKinley [1990].

In its simplest form, loop distribution consists of breaking up a single loop into two or more consecutive loops. When aligning loop distribution to the strongly connected components of the data-dependence graph, one or more of the resulting loops expose iterations that can be run in parallel, exposing data parallelism. Barriers are inserted after the parallel loops to enforce precedence constraints with the rest of the program. An example is presented in Figure 3.1.

```

for (i = 1; i < N; i++) {

S1 A[i] = B[i] + 1;

S2 C[i] = A[i-1] + 1;

}

for (i = 1; i < N; i++)

S1 A[i] = B[i] + 1;

</pre>

for (i = 1; i < N; i++)

S2 C[i] = A[i-1] + 1

</pre>

```

#### Figure 3.1: Barriers inserted after loop distribution.

## 3.2 Observations

It is quite intuitive that the typical synchronization barriers in between distributed data-parallel loops can be weakened, resulting into data-parallel pipelines. We aim to provide a comprehensive treatment of this transformation, generalizing PS-DSWP in the process.

### 3.2.1 Replacing loops and barriers with a task pipeline

In the previous example, we could remove the barriers between two distributed loops with pipelining so that the two loops could run in parallel.

```

/* Initialize the stream,

inserting a delay. */

void INIT_STREAM() {

produce(stream, A[0]);

}

```

```

/* Decoupled producer and

consumer. */

for (i = 1; i < N; i++) {

S1 A[i] = B[i] + 1;

produce(stream, A[i]);

}

for (i = 1; i < N; i++) {

tmp = consume(stream);

S2 C[i] = tmp + 1;

}

```

Figure 3.2: Pipelining inserted between distributed loops. Initialize the stream (left), producer and consumer thread (right).

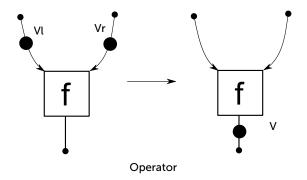

Figure 3.2 shows that pipelined execution is possible: the INIT\_STREAM function inserts one delay into a communication stream; the produce/consume primitives implement a FIFO, enforcing the precedence constraint of the data dependence on array A and communicating the value in case the hardware needs this information.

When distributing loops, scalar and array expansion (privatization) is generally required to eliminate memory-based dependences. The conversion to a task pipeline avoids this complication through the usage of communication streams. This transformation can be seen as an optimized version of scalar/array expansion in bounded memory and with improved locality Pop *et al.* [2009].

### 3.2.2 Extending loop distribution to PS-DSWP

The similarity between DSWP and distributed loops with data-parallel pipelines is striking. First, both of them partition the loop into multiple threads. Second, both of them avoid partitioning the loop iteration space: they partition the instructions of the loop body instead. But four arguments push in favor of refining DSWP in terms of loop distribution.

- 1. Loop distribution leverages the natural loop structure, where the granularity of thread partitioning can be easily controlled. Moreover, it is useful to have a loop control node to which to attach information about the iteration of the loop, including closed forms of induction variables; this node can also be used to represent the loop in additional transformations.

- 2. Using a combination of loop distribution and fusion, then replacing barriers with pipelining leads to an incremental path in compiler construction. This path leverages existing intermediate representations and loop nest optimizers, while DSWP relies on new algorithms and a program dependence graph.

- 3. Considering the handling of control dependences, a robust and general algorithm already exists for loop distribution. McKinley and Kennedy's technique handles arbitrary control flow Kennedy & McKinley [1990] and provides a comprehensive solution. The same methods could be applied for DSWP, transforming control dependences into data dependences, and storing boolean predicates into stream. After restructuring the code, updating the control dependence graph and data dependence graph, the code generation algorithm for PDGs Baxter & Bauer [1989]; Ferrante & Mace [1985]; Ferrante et al. [1988] can be used to generate parallel code. This solution would handle all cases where the current DSWP algorithm fails to clone a control condition.

- 4. Since loop distribution does not partition the iteration space, it can also be applied to uncounted loops. Unfortunately, the termination condition needs to be propagated to downstream loops. This problem disappears through the usage of a conventional communication stream when building task pipelines.

From this high-level analysis, it appears possible to extend loop distribution with pipelining to implement PS-DSWP and handle arbitrary control dependences. Yet the method still seems rather complex, especially the if-conversion of control dependences and the code generation step from the PDG. We go one step further and propose a new algorithm adapted from loop distribution but avoiding these complexities.

### 3.2.3 Motivating example

Our method makes one more assumption to reduce complexity and limit risks of overhead. It amounts to enforcing the synchronous hypothesis on all communicating tasks in the partition Halbwachs *et al.* [1991]. A sufficient condition is to check if the source and target of any decoupled dependence is dependent on the same control node.

Consider the example in Figure 3.3. S1 and S7 implement the loop control condition and induction variable, respectively. S2, S3 and S6 are control dependent on S1. S3 is a conditional node, S4, S5 and L1 are control dependent on it. In the inner loop, L2 and L3 are control dependent on L1. When we apply DSWP to the outer loop, the control dependences originating from S1 must be if-converted by creating several streams (the number of streams depends on the number of partitions). When decoupling along the control dependence originating from S3, a copy of the conditional node must be created as well as another stream.

```

S1 while (p != NULL) {

S2

x = p - value;

S3

if(c1) {

S4

x = p - value/2;

S5

ip = p->inner_loop;

L1

while (ip) {

L2

do_something(ip);

L3

ip = ip->next;

}

}

S6

\ldots = x;

p = p - next;

S7

}

```

Figure 3.3: Uncounted nested loop before partitioning.

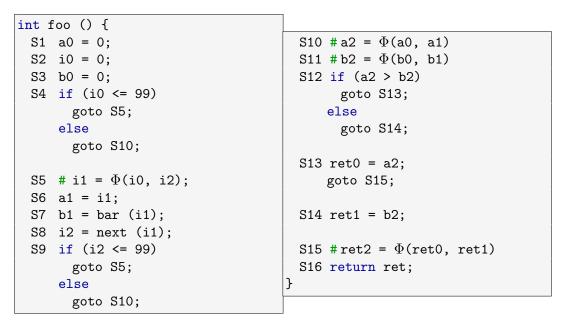

Figure 3.4 shows the conversion to SSA form. Just like GCC, we use a loopclosed SSA form distinguishing between  $loop-\Phi$  and  $cond-\Phi$  nodes. The latter

```

S1 while (p1 = \Phi^{loop}(p0, p2)) {

S2

x1 = p1->value;

S3

if(c1) {

S4

x2 = p1 - value/2;

ip1 = p1->inner_loop;

S5

while (ip2 = \Phi^{\text{loop}}(\text{ip1, ip3})) {

L1

L2

do_something(ip2);

L3

ip3 = ip2->next;

}

}

x3 = \Phi_{c1}^{cond}(x1, x2);

S6

= x3;

S7

p2 = p1 - next;

}

```

Figure 3.4: Uncounted nested loop in SSA form.

take an additional condition argument, appearing as a subscript, to explicit the selection condition. The partitioning technique will build a stream to communicate this condition from its definition site to the cond- $\Phi$  node's task.

We build on the concept of *treegion*, a single-entry multiple-exit control-flow region induced by a sub-tree of the control dependence graph. In the following, we assume the control flow is structured, which guarantees that the control dependence graph forms a tree. Every sub-tree can be partitioned into concurrent tasks according to the control dependences originating from its root. Any data dependence connecting a pair of such tasks induces communication over a dedicated stream. We call taskM\_N the N-th task at level M of the control flow tree.

In Figure 3.4, after building the control dependence tree, one may partition it into 3 tasks (task1\_1, task1\_2 and task1\_3) at the root level, and for task1\_2, one may further partition this task into inner nested tasks task2\_1 and task2\_2. One may then check for data parallelism in the inner loops; if they do not carry any dependence, one may isolate them in additional data-parallel tasks, such as task3\_1 in this example.

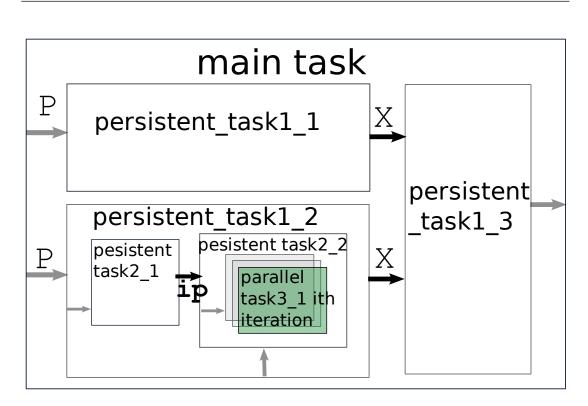

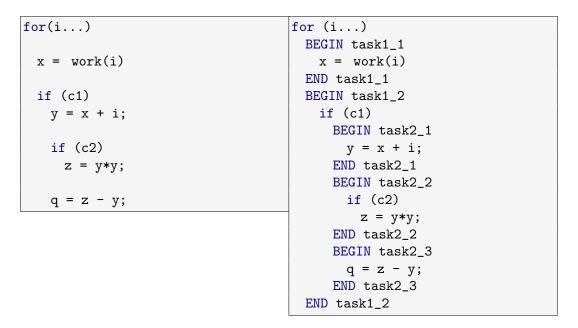

Figure 3.5 shows the task and stream-annotated code using an OpenMP syntax. Figure 3.6 shows the nested pipelining and data parallelization corresponding

```

//task0-0(main task)

S1 while (p1 = \Phi^{loop}(p0, p2)) {

//persistent-task1-1

#pragma task firstprivate (p1) output(x1)

{

S2

x1 = p1->value;

}

//persistent-task1-2

#pragma task output(c1, x2)

{

if(c1) {

S3

//persistent-task2-1

#pragma task firstprivate (p1) output(ip1) lastprivate(x2)

{

S4

x2 = p1 \rightarrow value/2;

S5

ip1 = p1->inner_loop;

}

//persistent-task2-2

#pragma task input(ip1)

{

while (ip2 = \Phi^{\text{loop}}(\text{ip1, ip3})) {

L1

//parallel - task3-1

#pragma omp task firstprivate (ip2)

{

L2

do_something(ip2);

}

L3

ip3 = ip2->next;

}

}

}

}

//persistent-task1-3

#pragma task input(c1, x1, x2)

{

x3 = \Phi_{c1}^{cond}(x1, x2);

S6

... = x3;

}

p2 = p1 \rightarrow next;

S7

}

```

Figure 3.5: Loops after partitioning and annotated with OpenMP stream extension.

Figure 3.6: Pipelining and parallelization framework.

to the partitioned code. The main task will be executed first, and a pipeline will be created for the main task and its inner tasks three task1\_1, task1\_2 and task1\_3. Among these, the same variable x used to be defined in the control flow regions of both task1\_1 and task1\_2, to be used in task1\_3. This output dependence must be eliminated prior to partitioning into tasks, so that task1\_1 and task1\_2 could be decoupled, while task1\_3 may decide which value to use internally.

Nested tasks are introduced to provide fine grained parallelism. It is of course possible to adapt the partition and the number of nesting levels according to the load balancing and synchronization overhead. The generated code will be well structured, and simple top-down heuristics can be used.

In the execution model of OpenMP 3.0, a task instance is created whenever the execution flow of a thread encounters a task construct; no ordering of tasks can be assumed. Such an execution model is well suited for unbalanced loads, but the overhead of creating tasks is significantly more expensive than synchronizing persistent tasks. To improve performance, we use the persistent task model for pipelining, in which a single instance will handle the full iteration space, consuming data on the input stream and producing on the output stream Pop & Cohen [2011a]. In Figure 3.6, all the tasks except task3\_1 use the persistent model to reduce the overhead of task creation; task3\_1 is an ordinary task following the execution model of OpenMP 3.0 (instances will be spawned every time the control flow encounters the task directive). All these tasks will be scheduled by the OpenMP runtime.

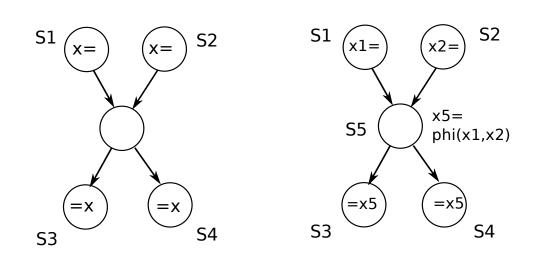

One problem with the partitioning algorithms is the fact that the def-use edges (scalar dependences) can become very large, sometimes quadratic with respect to the number of nodes Kennedy & Allen [2002]. Figure 3.7 (left) presents an example that illustrates this problem, Statements S1, S2 define the variable x. These definitions all reach the uses in the statements S3, S4 by passing through S5. Because each definition could reach every use, the number of definition-use edges is proportional to the square of the number of statements. These dependences constitute the majority of the edges in a PDG. SSA provide a solution to this problem. In SSA form, each assignment creates a different variable name and at point where control flow joins, a special operation is inserted to merge different incarnations of the same variable. The merge nodes are inserted just at the place where control flow joins. Figure 3.7 (right) is the original program under SSA form. A merge node ( $\Phi$ ) is inserted at S5, and killed the definition of S1 and S2. We could see here, in the SSA form, we could reduce the definition-use edges from quadratic to linear.

The systematic elimination of output dependences is also facilitated by the SSA form, with a  $\Phi$  node in task3\_1. Notice that the conditional expression from which this  $\Phi$  node selects one or another input also needs to be communicated through a data stream.

When modifying loop distribution to rely on tasks and pipelining rather than barriers, it is not necessary to distribute the loop control node and one may run it all in the master task, which in turn will activate tasks for the inner partitions. The statements inside each partition form a treegion whose root is the statement that is dependent on the loop control node. With pipelining inserted, distributed loops could be connected with pipelining when there are data dependences.

One concern here is that loop distribution with task pipelines may not pro-

Figure 3.7: Definition and use edges in the presence of control flow.

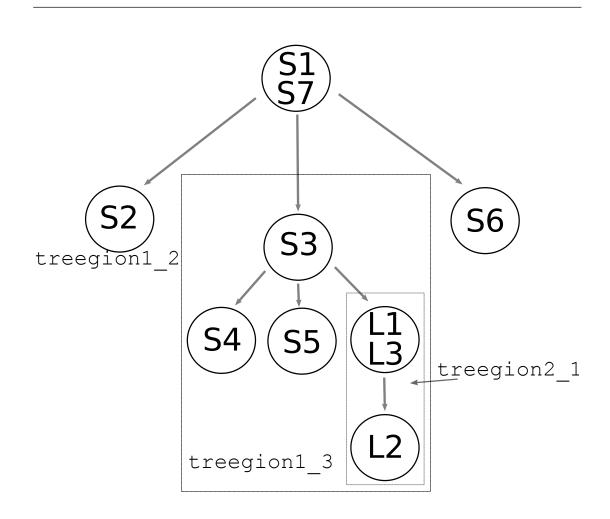

vide expressiveness to extract pipeline parallelism. This is not a problem however, since we may apply the same method to every conditional statement rooted treegion, with some special care to the nested tasks, we could get fine grained parallelism without explicitly decoupling the control dependences. Considering again the example in Figure 3.3, its control dependence tree is given in Figure 3.8. The root treegion includes all the nodes in the control dependence graph, treegion1\_2 represents the treegion at conditional level 1 and its root is node 2, treegion1\_3 is at conditional level 1 and includes nodes (S3,S4,S5,L1,L2,L3). treegion2\_1 is in conditional level 2 and its root is node (L1), which is the loop control node of the inner loop.

So following our approach, we may start from the treegion at conditional level 0, which is the whole loop, an implicit task will be created as the master task. For the treegions at level 1, we could create them as sub-tasks running at the context of the main task. If there are data dependences between the treegions at the same level and without recurrence, we will connect them with communication streams. If there is a dependence from the master task to one inner task, the value from the enclosing context can be forwarded to the inner task like in a firstprivate clause of OpenMP. Dependences from an inner task to the master task are also supported, although lastprivate is not natively sup-

Figure 3.8: Control dependence graph of Figure 3.3. Express the definition of treegion.

ported for OpenMP3.0 tasks, it is a necessary component of our streaming task representation. lastprivate(x) is associated with a synchronization point at the end of the task and makes the value of x available to the enclosing context. The same algorithms could be recursively applied to the treegion at the next inner level. e.g. For treegion1\_3 at level 1, the sub treegion at level 2 is treegion2\_4, treegion2\_5 and treegion2\_1, we could create sub-tasks by merging treegion2\_4 and treegion2\_5 as one sub-task and treegion2\_1 (which is also the inner loop) as one sub-task, or just for part of them. To reveal data parallelism, we can reuse the typed fusion algorithm introduced by McKinley

and Kennedy Kennedy & Mckinley [1993]: it is possible to fuse communicating data-parallel nodes to increase the synchronization grain or improve the load balancing. In this example, the loop in node L2 does not carry any dependence, and we need to decouple it from its enclosing task to expose data-parallelism.

# 3.3 Partitioning Algorithm

In this section, we present our partitioning algorithm, based on the SSA and treegion representations. We define our model and the important constructs that will be used by our algorithm, then we present and describe our algorithm.

### 3.3.1 Definitions

In this work, we are only targeting natural structured loops Böhm & Jacopini [1966]. Such loops are single-entry single-exit CFG sub-graphs with one entry block and possibly several back edges leading to the header from inside of the loop. break and continue statements can be preprocessed to comply with this restriction, but we plan to lift it altogether in the future.

**Treegion** The canonical definition of a treegion is a non-linear, single-entry multiple-exit region of code containing basic blocks that constitute a sub-graph of the CFG. We alter this definition to bear on the Control-Dependence Graph (CDG) instead, so we will be looking at single-entry multiple-exit sub-graphs of the CDG.

**Loop Control Node** In the representation we employ later, we will use the loop control node to represent the loop. The loop control node include statements which will evaluate the loop control expression and determines the next iteration.

Although control dependences in loops can be handled by the standard algorithm by converting them to a control flow graph, there are advantages in treating them as a special case with coalescing them in a single node (loop control node): not only the backward dependence is removed by building the loop control node so that the control dependence graph will form a tree, but also, this node can be used to represent the loop in all sort of transformations.

**Conditional Level** The control dependence graph of the structured code is a tree after building the loop control node. The root of the tree is the loop control node at the loop's outermost level. We define the conditional level for every node in the control dependence graph as the depth of the node in the tree. The root of the tree with depth 0 has conditional level 0.