### Optimised space vector modulation for variable speed drives

Hamid Khan

### ▶ To cite this version:

Hamid Khan. Optimised space vector modulation for variable speed drives. Other. Université Blaise Pascal - Clermont-Ferrand II, 2012. English. NNT: 2012CLF22288. tel-00999475

### HAL Id: tel-00999475 https://theses.hal.science/tel-00999475

Submitted on 3 Jun2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **UNIVERSITE BLAISE PASCAL - CLERMONT II**

ECOLE DOCTORALE SCIENCES POUR L'INGENIEUR DE CLERMONT-FERRAND

## Thèse

Présentée par

## HAMID KHAN

pour obtenir le grade de

# DOCTEUR D'UNIVERSITÉ

### **SPECIALITE** : ÉLECTRONIQUE DE PUISSANCE

**Optimised Space Vector Modulation for Variable Speed Drives**

Soutenue publiquement le 6 Novembre 2012 devant le jury :

Pr. Bernard DAVAT Pr. Patrick Chi Kwong LUK Pr. Guy FRIEDRICH Dr. François BADIN Pr. Khalil EL KHAMLICHI DRISSI Dr. El Hadj MILIANI Pr. Jean Marie KAUFFMANN Président Rapporteur Rapporteur Examinateur Directeur de thèse Encadrant industriel Invité

## Résumé

Le travail effectué au cours de cette thèse consiste à étudier et développer des techniques innovantes de modulation de largueurs d'impulsions (MLI) qui visent à optimiser les chaînes de traction électriques embarquées dans des véhicules hybrides ou électriques. La MLI joue un rôle stratégique au cœur des variateurs de vitesse, elle influe sur le comportement général de la chaîne de traction et sur sa performance. La MLI présente des degrés de liberté qui peuvent contribuer avantageusement à redimensionner les composants du variateur tels que le circuit de refroidissement, le filtre EMI et le condensateur du bus continu.

Les véhicules hybrides constituent une étape naturelle dans la transition énergétique entre les véhicules thermiques et les véhicules électriques.

Notre étude contribue à l'optimisation des variateurs de vitesse en général et ceux au cœur des véhicules hybrides ou électriques en particulier. Notre apport consiste à proposer une MLI performante afin de rendre le variateur plus léger et plus compacte tout en garantissant les fonctionnalités traditionnelles. La compétitivité de ces variateurs et par conséquent des véhicules hybrides ou électriques devient alors accessible.

Les véhicules hybrides ou électriques utilisent généralement une machine de traction à courant alternatif en raison de nombreux avantages que celle ci présente par rapport à une machine à courant continu. La source d'alimentation au bord d'un véhicule est une batterie, il est donc nécessaire d'utiliser un onduleur pour transformer la tension continue en tension alternative à amplitude et fréquence variables. Le contrôle de cet onduleur est réalisé par des techniques de modulation de largeurs d'impulsions (MLI) ce qui permet ainsi de réguler le couple de la machine. Les techniques MLI produisent une composante basse fréquence, le fondamental qui est le signal désiré et des composantes hautes fréquences appelées harmoniques de commutation qui sont indésirables.

Dans les véhicules modernes, il y a de plus en plus de charges mécaniques pilotées par des machines électriques et des systèmes électroniques. Il est impératif d'éliminer le risque d'interférences électromagnétiques entre ces différents systèmes pour éviter le dysfonctionnement ou la défaillance. Il faut donc filtrer ces harmoniques indésirables pour qu'elles ne perturbent pas les calculateurs et autres circuits électroniques de faibles niveaux de tensions. Il existe des techniques de modulation aléatoire (RPWM) qui permettent d'étaler les harmoniques à la fréquence de commutation et ses multiples. Dans cette étude, notre choix s'est porté sur la technique de modulation vectorielle aléatoire (RSVM) qui présente plusieurs avantages par rapport à la MLI intersective. Les machines pilotées par une MLI produisent des tensions de mode commun dites « shaft voltage », qui peuvent provoquer des courants à travers les roulements de la machine, ces derniers pouvant être destructifs. Nous avons pu développer une technique MLI vectorielle basée sur un choix judicieux des vecteurs nuls pour réduire cette tension de mode commun.

La chaleur produite par les pertes dans les convertisseurs à commutation dure lors de l'ouverture et de la fermeture des interrupteurs doit être évacuée rapidement, ce qui réduit le stress thermique, évite la défaillance et augmente la durée de vie des interrupteurs. Une technique utilisée pour réduire ces pertes par commutation est la modulation discontinue (DPWM); une amélioration est apportée à cette technique dans ce travail. Cette amélioration est présentée sous forme d'une technique discontinue évolutive (EDSVM) qui s'adapte au régime du moteur pour minimiser les pertes. Grâce à cette technique une meilleure distribution du stress thermique sur les différents bras de l'onduleur est rendue possible et permet ainsi d'augmenter la durée de vie de l'onduleur.

Une autre variante de modulation est abordée dans ce travail; cette technique utilise des vecteurs non adjacent et un placement dynamique des pulses permettant ainsi de réduire le stress électrique sur le condensateur du bus continu et de réduire le nombre de capteurs de courants requis pour la régulation du couple de la machine.

Les effets indésirables de la MLI cités ci-dessus ont été abordés séparément et des techniques de modulation dédiées ont été développées telles que : la modulation aléatoire, la modulation discontinue et la modulation discontinue évolutive. Ces techniques permettent de réduire le filtrage passif souvent encombrant et d'utiliser des condensateurs du bus continu moins volumineux. Elles permettent également de réduire les interférences électromagnétiques (EMI) et l'effort de refroidissement.

Un banc de test complet associant l'électronique de puissance à un système de contrôle performant à base de DSP a été réalisé. Toutes les validations expérimentales sont précédées par une étude théorique et validées par simulation.

**Mots clés:** Electric drives, Interférence Electromagnétique, Véhicules Hybride-Electrique, Pertes par Commutation, Modulation par largeur d'impulsion, MLI Discontinue, MLI Aléatoire, MLI Vectorielle.

## Abstract

The dissertation documents research work carried out on Pulse Width Modulation (PWM) strategies for hard switched Voltage Source Inverters (VSI) for variable speed electric drives. This research is aimed at Hybrid Electric Vehicles (HEV). PWM is at the heart of all variable speed electric drives; they have a huge influence on the overall performance of the system and may also help eventually give us an extra degree of freedom in the possibility to rethink the inverter design including the re-dimensioning of the inverter components.

HEVs tend to cost more than conventional internal combustion engine (ICE) vehicles as they have to incorporate two traction systems, which is the major discouraging factor for consumers and in turn for manufacturers. The two traction system increases the maintenance cost of the car as well. In addition the electric drives not only cost extra money but space too, which is already scarce with an ICE under the hood. An all-electric car is not yet a viable idea as the batteries have very low energy density compared with petrol or diesel and take considerable time to charge. One solution could be to use bigger battery packs but these add substantially to the price and weight of the vehicle and are not economically viable. To avoid raising the cost of such vehicles to unreasonably high amounts, autonomy has to be compromised. However hybrid vehicles are an important step forward in the transition toward all-electric cars while research on better batteries evolves. The objective of this research is to make electric drives suitable for HEVs i.e. lighter, more compact and more efficient -- requiring less maintenance and eventually at lower cost so that the advantages, such as low emissions and better fuel efficiency, would out-weigh a little extra cost for these cars.

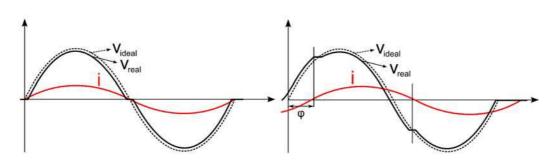

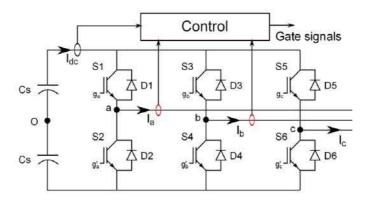

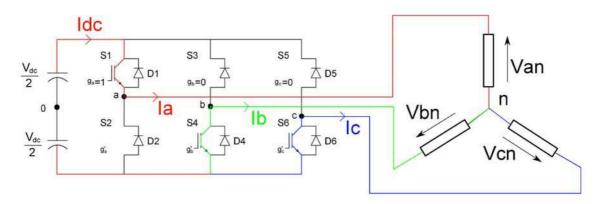

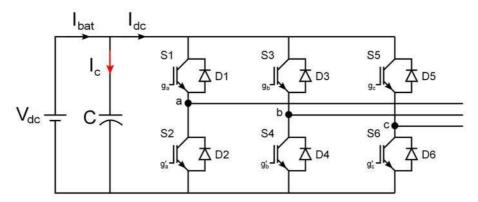

The electrical energy source in a vehicle is a battery, a DC Voltage source, and the traction motor is generally an AC motor owing to the various advantages it offers over a DC motor. Hence the need for a VSI, which is used to transform the DC voltage into AC voltage of desired amplitude and frequency. Pulse width modulation techniques are used to control VSI to ensure that the required/calculated voltage is fed to the machine, to produce the desired torque/speed. PWM techniques are essentially open loop systems where no feedback is used and the instantaneous values differ from the required voltage, however the same average values are obtained.

Pulse width modulated techniques produce a low frequency signal (desired average value of the switched voltage) also called the fundamental component, along with unwanted high frequency harmonics linked to the carrier signal frequency or the PWM period. In modern cars we see more and more mechanical loads driven by electricity

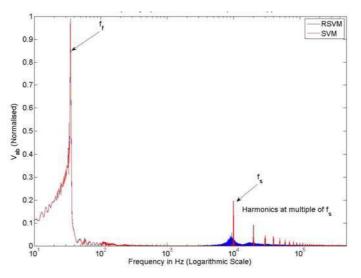

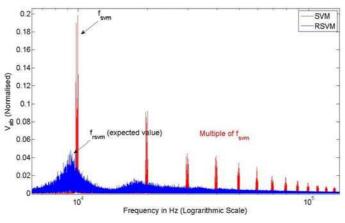

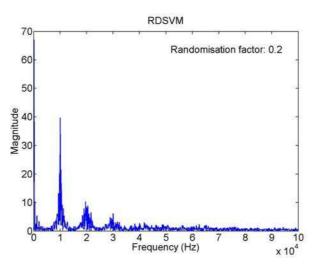

through digital processors. It is very important to eliminate the risk of electromagnetic interference between these systems to avoid failure or malfunction. Hence these unwanted harmonics have to be filtered so that they do not affect the electronic control unit or other susceptible components placed in the vicinity. Randomised modulation techniques (RPWM) are used to dither these harmonics at the switching frequency and its multiple. In this thesis a random modulator based on space vector modulation is presented which has additional advantages of SVM.

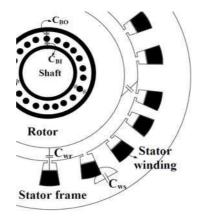

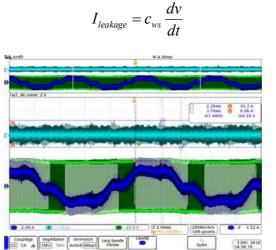

Another EMI problem linked to PWM techniques is that they produce common mode voltages in the load. For electric machines, common mode voltage produces shaft voltage which in turn provokes dielectric stress on the motor bearings, its lubricant and hence the possibility of generating bearing currents in the machine that can be fatal for the machine. To reduce the common mode voltage a space vector modulation strategy is developed based on intelligent placement of zero vectors.

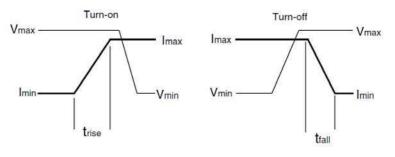

For hard switched converters, commutations or the switching of the power switches produce losses that heat up the switches and have to be evacuated rapidly as thermal stress reduces the component life and makes it prone to failure. The higher the switching losses the higher the thermal stress that the switch undergoes. The heat sink dimensions are proportional to the energy lost in the form of heat to be dissipated. So higher switching losses result in a bigger heat sink. Discontinuous modulators (DPWM) are used to reduce the switching losses. Here we have developed an improved discontinuous modulator which can adapt itself to the changing machine speed and load to minimise the switching losses. It also offers the possibility to regulate the thermal stress between the inverter legs to increase the inverter life.

A PWM technique to reduce the electric stress on the DC-Link capacitors and reduce the number of current sensors required for torque regulation is presented as well. This technique makes use of non-adjacent active vectors and dynamic pulse placement.

Each of the aforementioned side effects and its alleviation is dealt with separately and dedicated modulation strategies namely Randomized, Discontinuous Space Vector Modulation and Optimised PWM in terms of reduced ripple content of the inverter input current are developed to achieve it. These techniques will eventually result in inverters with a smaller EMI filter, a smaller heat sink, smaller DC-link capacitor i.e. a compact and cheaper inverter.

A befitting test bench is realised to calculate the real gains and check the practical feasibility of these techniques in terms of execution on embedded processor. All experimental work is systematically preceded by theoretical study where analytical expressions are developed to prove the claims made and validation by simulation tools.

**Keywords:** Electric drives, Electromagnetic Interference, Hybrid Electric Vehicles, Commutation Losses, Pulse Width Modulation, Discontinuous-PWM, Random PWM, Space Vector Modulation.

## **Acknowledgment**

I would like to thank my two institutions, LAboratoire des Sciences et Matériaux pour l'Électronique et d'Automatique, LASMEA a Blaise Pascal university laboratory and the department of electronic systems and real time at IFP Energies Nouvelles, a renowned research firm for providing me with such an excellent research opportunity to complete my industrial PhD. This research conducted in collaboration between a university and a public sector research centre provided me with a unique and technically stimulating environment, with both an academic and industrial insights. I'd like to thank my university supervisor Mr. Khalil El Khamlichi Drissi and my industrial advisor Mr. El-Hadj Miliani for sharing their vast knowledge and their valuable experience with me. I would also like to thank my former supervisor Mr. Youssef Touzani who now works for Thales Avionics, for his encouragement and support as I adjusted to life and work in France.

I'd also like to thank the head of the department Mr. Mohammed Abdellahi Ould and the director Mr. Van Bui Tran for their belief in my capacities and the financial support they provided which enabled me to present my work in international conferences. My lab-mates and my office colleagues have been a source of encouragement, entertainment and camaraderie without which it would have been difficult going.

Finally, I cannot express my gratitude to my family and friends, who never ceased to surprise and overwhelm me with their support and faith in my success as I undertook this endeavour.

## Contents

| RÉSUMÉ                                                                      | 3  |

|-----------------------------------------------------------------------------|----|

| ABSTRACT                                                                    | 5  |

| ACKNOWLEDGMENT                                                              | 7  |

| CONTENTS                                                                    | 8  |

| LIST OF FIGURES                                                             | 10 |

| LIST OF TABLES                                                              | 13 |

| LIST OF ABBREVIATIONS                                                       | 14 |

| INTRODUCTION                                                                |    |

| I. PRELIMINARIES                                                            |    |

| I.1. INTRODUCTION                                                           |    |

| I.2. LITERATURE REVIEW                                                      |    |

| I.2.1. Fundamentals of PWM                                                  | 24 |

| I.2.2. Classical Sinusoidal PWM                                             | 25 |

| I.2.3. Hysteresis Band control                                              |    |

| I.2.4. Zero Sequence voltage injection                                      |    |

| I.2.4.1. Third Harmonic Injection PWM                                       |    |

| I.2.4.2. Discontinuous PWM<br>I.2.4.2.1. DPWM1                              |    |

| 1.2.4.2.1. DPWMI1                                                           |    |

| 1.2.4.2.3. DPWM3                                                            |    |

| I.2.5. Space Vector Modulation                                              |    |

| I.2.5.1. Sector and time calculation                                        |    |

| I.2.5.2. Space Vector PWM                                                   |    |

| I.2.6. Random PWM                                                           |    |

| I.2.6.1. Random Carrier Frequency-PWM<br>I.2.6.2. Random Pulse Position PWM |    |

| I.2.6.2. Random Pulse Position PWM<br>I.2.6.3. Dual Randomization           |    |

| I.2.7. Practical aspects of PWM                                             |    |

| I.2.7.1. Dead time                                                          |    |

| I.2.7.2. Switching losses                                                   |    |

| I.2.7.3. Leakage Currents                                                   |    |

| I.3. ELECTROMAGNETIC INTERFERENCE                                           |    |

| I.3.1. Introduction                                                         |    |

| I.3.2. EMI Standards and measurements                                       |    |

| I.3.3. EMI Filters                                                          |    |

| I.4. ANALYTICAL ANALYSIS OF PWM SCHEMES                                     |    |

| I.4.1. Frequency domain analysis                                            |    |

| I.4.1.1. Power Spectrum Density                                             |    |

| I.4.2. Waveform quality                                                     |    |

| I.4.2.1. Harmonic Voltage Distortion<br>I.4.2.2. Harmonic Distortion Factor |    |

|                                                                             |    |

|        | 1.4.2.3.                          | Subcarrier harmonic analysis                       | 62  |

|--------|-----------------------------------|----------------------------------------------------|-----|

| 1.5    | 5. Sumi                           | MARY                                               | 66  |

| п.     |                                   | PMENT OF PWM SCHEMES                               | 68  |

|        |                                   |                                                    |     |

| II.'   |                                   |                                                    |     |

| 11.2   |                                   | ONTINUOUS SPACE VECTOR MODULATION                  |     |

|        |                                   | Zero Vector Placement                              |     |

|        | <i>II.2.2.</i><br><i>II.2.2.1</i> | Evolutive Discontinuous SVM                        |     |

|        | 11.2.2.1.                         | Clamping Study<br>Switching loss reduction         |     |

|        | 11.2.2.3.                         | Unbalanced load condition                          |     |

|        | 11.2.2.4.                         | Waveform quality                                   |     |

|        | II.2.2.5.                         | Simulations                                        |     |

|        |                                   | Summary                                            |     |

| 11.3   | 3. Rani                           | DOMISED SPACE VECTOR MODULATION                    | 82  |

|        | II.3.1.                           | Randomisation parameters                           | 82  |

|        | II.3.1.1.                         |                                                    |     |

|        | II.3.1.2.                         | Choice of active vectors                           |     |

|        | II.3.1.3.                         | Zero vector distribution                           |     |

|        | II.3.1.4.                         | Counter profile                                    |     |

|        |                                   | Random number generation                           |     |

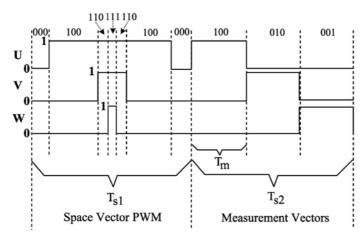

|        | <i>II.3.3.</i><br>II.3.3.1.       | Random Space Vector Modulation<br>Pulse Generation |     |

|        | II.3.3.1.<br>II.3.3.2.            | Acquisition and control sequence                   |     |

|        |                                   | Random discontinuous modulation                    |     |

|        |                                   | Simulation                                         |     |

|        | II.3.5.1.                         |                                                    |     |

|        | II.3.5.2.                         | close loop                                         |     |

|        | II.3.6.                           | Summary                                            |     |

| 11.4   | 4. PWN                            | OPTIMIZED EMBEDDED ELECTRIC DRIVES                 |     |

|        |                                   | Introduction                                       |     |

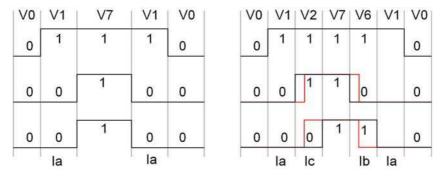

|        | II.4.2.                           | Phase current reconstruction                       |     |

|        | II.4.2.1.                         | Limitations and Boundary conditions                |     |

|        | II.4.2.2.                         | State of the art                                   |     |

|        | II.4.2.                           |                                                    |     |

|        | II.4.2.                           |                                                    |     |

|        | II.4.2.3.                         | Proposed solution<br>Simulation                    |     |

|        | II.4.2.4.<br>II.4.2.5.            | Summary                                            |     |

|        | -                                 | DC link capacitor reduction                        |     |

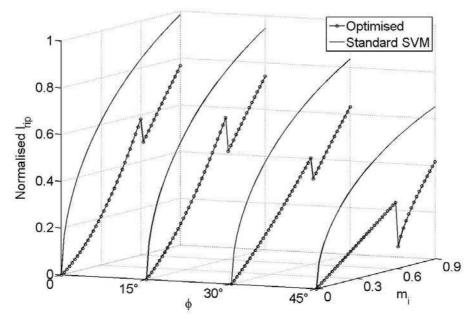

|        | II.4.3.1.                         | Ripple component of the inverter input current     | 110 |

|        | II.4.3.                           |                                                    |     |

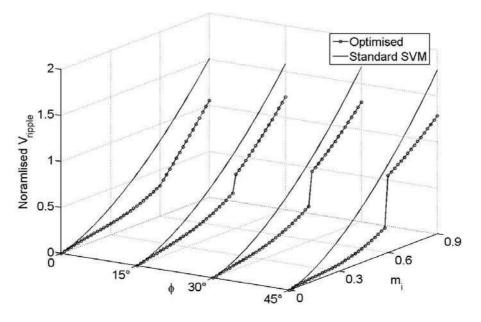

|        | II.4.3.2.                         | Ripple component of the inverter input Voltage     | 117 |

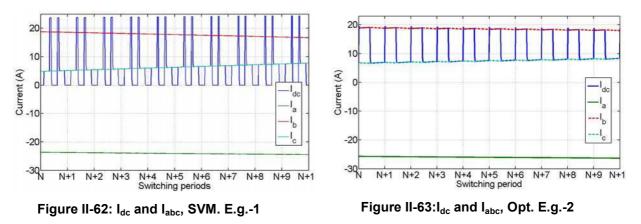

|        | II.4.3.3.                         | Simulation                                         | 120 |

|        | II.4.3.4.                         | Summary                                            | 121 |

| III.   | FXPF                              | RIMENTAL VALIDATION                                | 123 |

|        |                                   |                                                    |     |

| - III. | .1. INTRO                         | ODUCTION                                           | 123 |

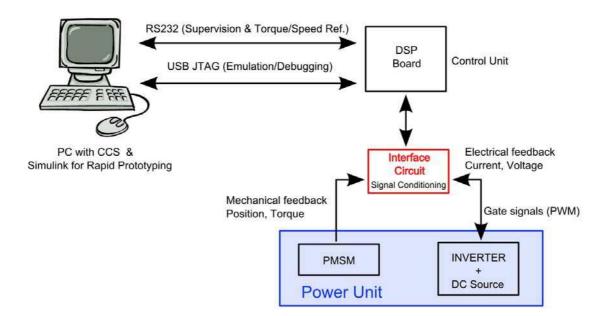

| III.   | .2. TEST                          | BENCH                                              | 124 |

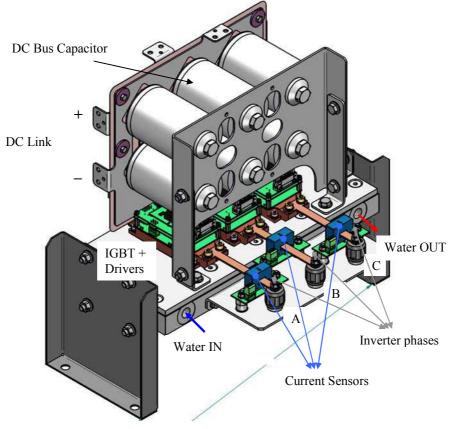

|        | III.2.1.                          | Power Unit                                         |     |

|        | III.2.1.1.                        | Power Converter VSI                                |     |

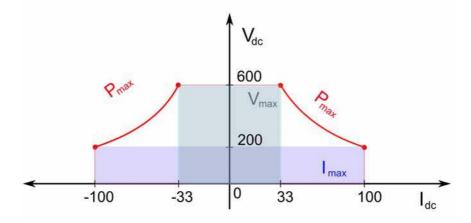

|        | III.2.1.2.                        | DC source                                          |     |

|        | III.2.1.3.                        |                                                    |     |

|        |                                   | Control unit                                       |     |

|        |                                   | Power and control Interface                        |     |

|        | III.2.3.1.<br>III.2.3.2.          | Analog signal interfacing                          |     |

|        | -                                 |                                                    |     |

|        |                                   | BENCH VALIDATION                                   |     |

|        |                                   |                                                    |     |

|        |                                   | Incremental encoder                                |     |

|        |                                   | PWM Module                                         |     |

| - 111. | .4. Perf                          | ORMANCE INDICATORS                                 | 135 |

| III.5. EXPERIMENTAL RESULTS1                                                   | 138 |

|--------------------------------------------------------------------------------|-----|

| III.5.1. Static Load1                                                          | 38  |

| III.5.1.1. Continuous Modulators1                                              |     |

| III.5.1.1.1. Sinusoidal Pulse Width Modulator1                                 | 139 |

| III.5.1.1.2. Space Vector Modulator 1                                          | 40  |

| III.5.1.2. Discontinuous Modulator1                                            |     |

| III.5.1.2.1. DPWM1 1                                                           |     |

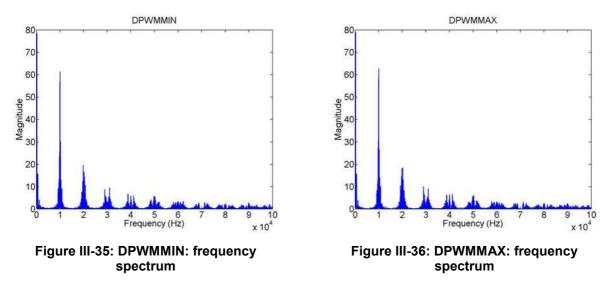

| III.5.1.2.2. DPWMMIN & DPWMMAX1                                                |     |

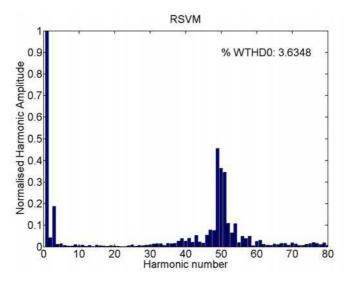

| III.5.1.3. Random modulator1                                                   |     |

| III.5.2. Dynamic Load1                                                         |     |

| III.5.2.1. Continuous Modulator1                                               |     |

| III.5.2.1.1. Sinusoidal Pulse Width Modulator1                                 |     |

| III.5.2.1.2. Space Vector Modulator                                            |     |

| III.5.2.2. Discontinuous modulator                                             |     |

| III.5.2.2.1. DPWMMIN & DPWMMAX1                                                | -   |

| III.5.2.2.2. EDSVM                                                             |     |

| III.5.2.3. Randomised modulator1<br>III.5.2.4. Random discontinuous modulator1 |     |

|                                                                                |     |

| III.6. SUMMARY1                                                                | 128 |

| IV. CONCLUSION & FUTURE WORK10                                                 | 61  |

| IV.1. CONCLUSION1                                                              | 161 |

| IV.2. SUGGESTIONS FOR FUTURE WORK1                                             |     |

| REFERENCE10                                                                    | 64  |

# **List of Figures**

| FIGURE 1. WORLD CO2 EMISSIONS BY SECTOR IN 2009 [3]                 | . 16 |

|---------------------------------------------------------------------|------|

| FIGURE 2. PARALLEL HEV DRIVETRAIN                                   |      |

| FIGURE I-1: SCHEMATIC DIAGRAM OF AN ELECTRIC DRIVE                  | 22   |

| FIGURE I-2: HALF BRIDGE                                             |      |

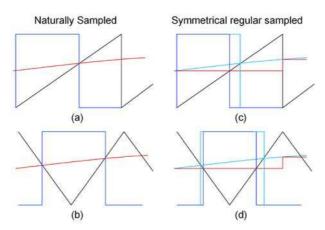

| FIGURE I-3: (A), (B): NATURALLY SAMPLED, (C), (D) REGULARLY SAMPLED | . 24 |

| FIGURE I-4: ASYMMETRICALLY SAMPLED                                  | .24  |

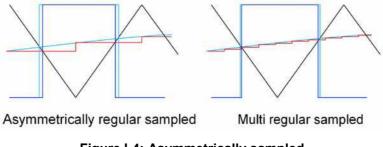

| FIGURE I-5: HYSTERESIS BAND                                         | 26   |

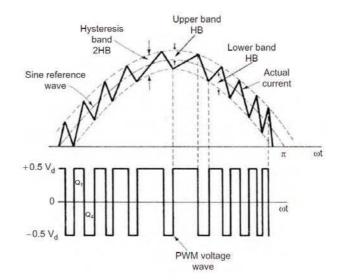

| FIGURE I-6: INVERTER FED FLOATING NEUTRAL 3-PHASE LOAD              | . 27 |

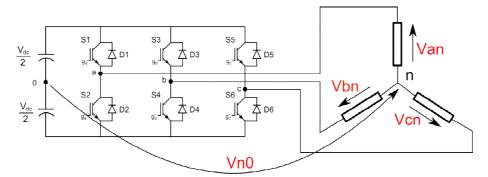

| FIGURE I-7: GENERALIZED MODULATOR: ZSS INJECTION                    | . 27 |

| FIGURE I-8: FLOATING NEUTRAL                                        |      |

| FIGURE I-9: 1/4TH THIPWM                                            |      |

| FIGURE I-10: DPWM1, MI=0.68                                         |      |

| FIGURE I-11: DPWM1, MI=0.907                                        |      |

| FIGURE I-12: DPWMMAX                                                |      |

| FIGURE I-13: DPWMMIN                                                |      |

| FIGURE I-14: DPWM3, MI=0.68                                         | 32   |

| FIGURE I-15: DPWM3, MI=0.907                                        |      |

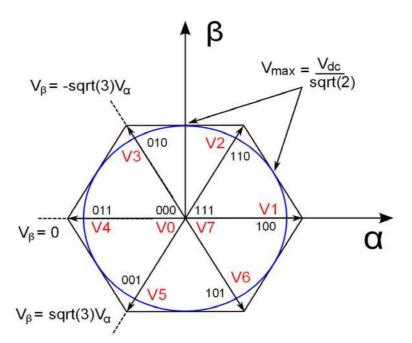

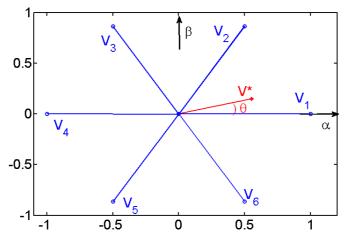

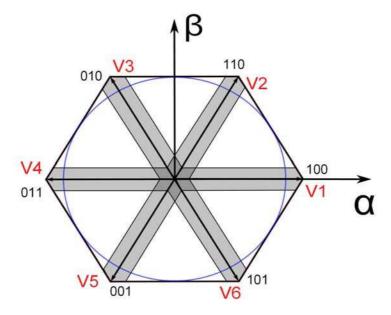

| FIGURE I-16: VOLTAGE SPACE VECTORS                                  | 33   |

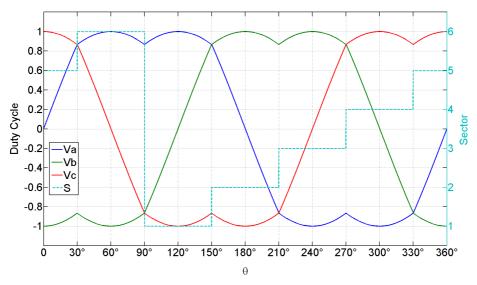

| FIGURE I-17: SVM; MODULATION FUNCTION AND CORRESPONDING SECTORS     |      |

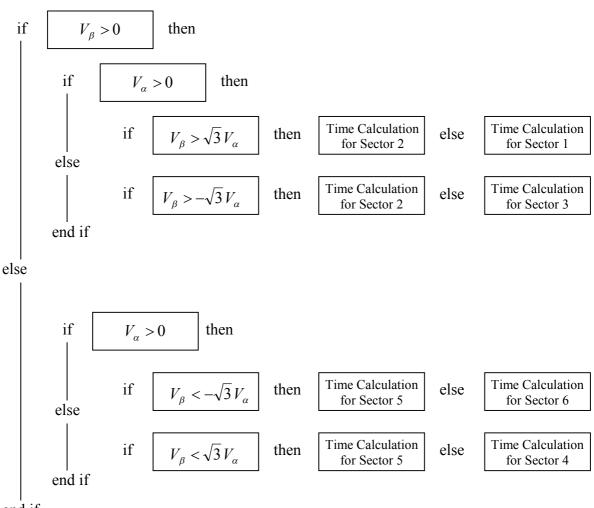

| FIGURE I-18: SVM SECTOR IDENTIFICATION                              |      |

| FIGURE I-19:TIME CALCULATION SECTOR 1                               | 37   |

| FIGURE I-20: SVPWM                                                  | 39   |

| FIGURE I-21: FREQUENCY SPECTRUM - PHASE VOLTAGE V <sub>A0</sub>     | 39   |

| FIGURE I-22: INCREASED LINEARITY OF MODULATION INDEX                | .40  |

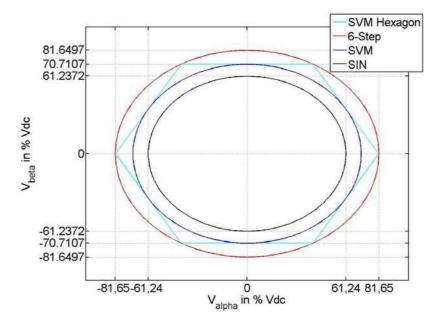

| FIGURE I-23: AMPLITUDES OF DIFFERENT MODULATION SCHEMES IN AB-PLANE | 40   |

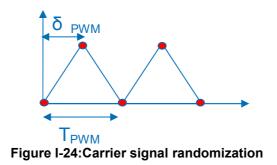

| FIGURE I-24: CARRIER SIGNAL RANDOMIZATION                           | 42   |

|                                                                                                          | 40    |

|----------------------------------------------------------------------------------------------------------|-------|

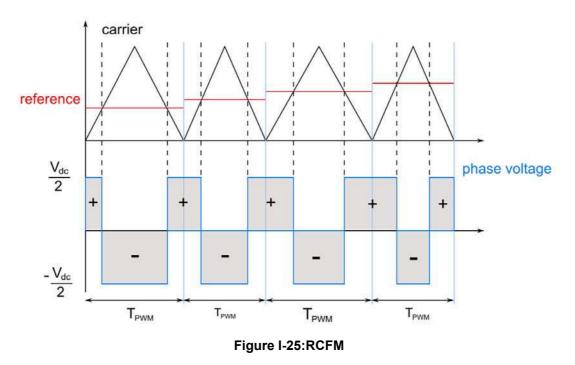

| FIGURE I-25:RCFM                                                                                         |       |

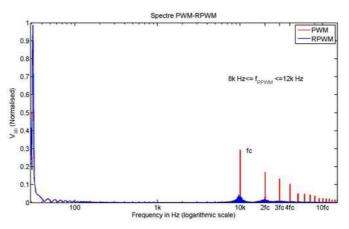

| FIGURE I-20:1 REQUENCE SPECTROM FWW-REWING                                                               |       |

| FIGURE I-28:RPPM                                                                                         |       |

| FIGURE I-29: HALF BRIDGE                                                                                 |       |

| FIGURE I-30: DEAD TIME                                                                                   |       |

| FIGURE I-31: DEAD TIME; VOLTAGE DISTORTION                                                               |       |

| FIGURE I-32: HARD SWITCHING                                                                              |       |

| FIGURE I-33: HIGH FREQUENCY MODEL OF AN ELECTRIC MOTOR                                                   |       |

| FIGURE I-34:LEAKAGE CURRENT (TOP), $I_{a}$ and $V_{a0}$                                                  |       |

| FIGURE I-35: HIGH FREQUENCY EQUIVALENT MODEL                                                             |       |

| FIGURE I-36: INVERTER FEEDING TOPOLOGIES                                                                 | . 49  |

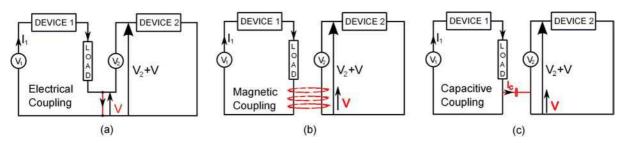

| FIGURE I-37: EMI PROPAGATION                                                                             | . 50  |

| FIGURE I-38: MODES OF COUPLING                                                                           | . 51  |

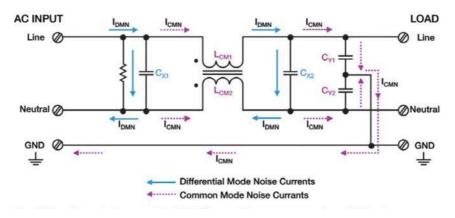

| FIGURE I-39: CONDUCTED NOISE FILTER                                                                      | . 52  |

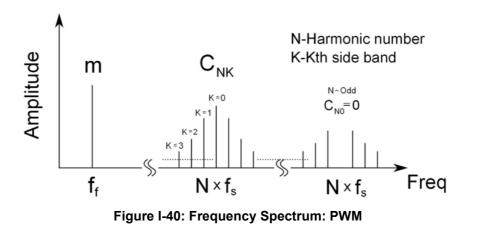

| FIGURE I-40: FREQUENCY SPECTRUM: PWM                                                                     |       |

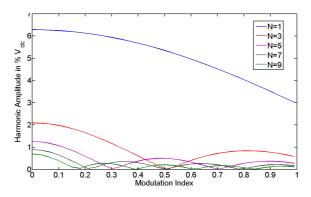

| FIGURE I-41: CARRIER HARMONIC AMPLITUDES                                                                 | . 54  |

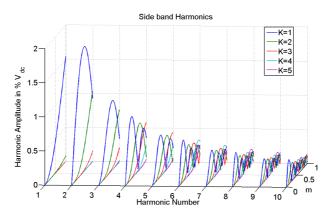

| FIGURE I-42: SIDEBAND HARMONIC AMPLITUDES                                                                |       |

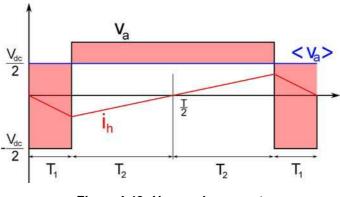

| FIGURE I-43: HARMONIC CURRENT                                                                            |       |

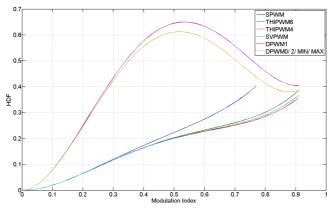

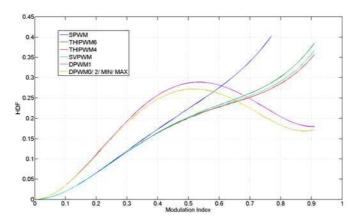

| FIGURE I-44: HDF                                                                                         |       |

| FIGURE I-45: HDF; SAME EFFECTIVE FREQUENCY                                                               |       |

| FIGURE I-46:SPACE VECTOR, ARBITRARY REFERENCE V*                                                         |       |

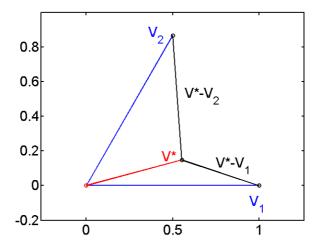

| FIGURE I-47: HARMONIC VOLTAGE VECTORS                                                                    |       |

| FIGURE I-48: SVM SWITCHING SEQUENCE                                                                      |       |

| FIGURE I-49: SVM, HARMONIC FLUX TRAJECTORIES                                                             |       |

| FIGURE I-50: SVM, HARMONIC FLUX                                                                          |       |

| FIGURE I-51: VECTOR APPLICATION SAWTOOTH CARRIER                                                         |       |

| FIGURE I-52: Λ <sub>H</sub> ; TRIANGULAR AND SAWTOOTH CARRIER                                            |       |

| FIGURE I-53: VECTOR APPLICATION DPWM                                                                     |       |

|                                                                                                          |       |

| FIGURE II-1: SVM, DSVMMAX, DSVMMIN.                                                                      |       |

| FIGURE II-2: ZERO VECTOR PLACEMENT.                                                                      |       |

| FIGURE II-3: CLAMPING ZONES<br>FIGURE II-4:INTELLIGENT SWITCHING FUNCTION – Φ=30°                        | . / 1 |

| FIGURE II-4.INTELLIGENT SWITCHING FUNCTION – Φ=30<br>FIGURE II-5: INTELLIGENT SWITCHING FUNCTION - Φ>30° |       |

| FIGURE II-5. INTELLIGENT SWITCHING FUNCTION - \$250                                                      |       |

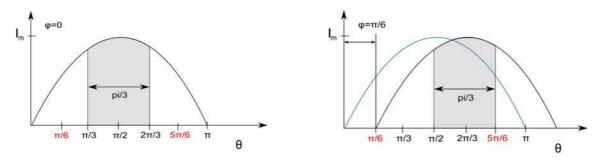

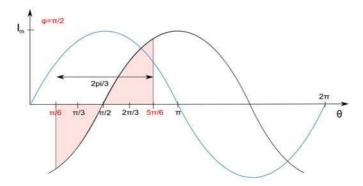

| FIGURE II-0. ALGORITHM EDSVM<br>FIGURE II-7: SWITCHING LOSS REDUCTION Φ=0°                               |       |

| FIGURE II-7. SWITCHING LOSS REDUCTION Φ=0<br>FIGURE II-8: SWITCHING LOSS REDUCTION Φ=30°                 |       |

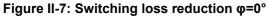

| FIGURE II-0. SWITCHING LOSS REDUCTION Φ=30°                                                              |       |

| FIGURE II-9. SWITCHING LOSS REDUCTION \$-90                                                              |       |

| FIGURE II-10: SWITCHING LOSS REDUCTION-DOWN                                                              |       |

| FIGURE II-12: HDF EDSVM                                                                                  |       |

| FIGURE II-12: HDF EDSVM; SAME EFFECTIVE FREQUENCY                                                        |       |

| FIGURE II-14: HDF EDSVM; EQUAL SWITCHING LOSSES                                                          |       |

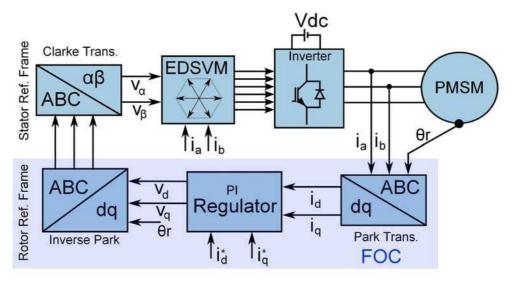

| FIGURE II-15: FOC WITH DSVM                                                                              |       |

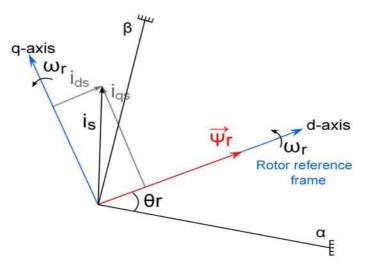

| FIGURE II-16: FOC PHASOR DIAGRAM                                                                         |       |

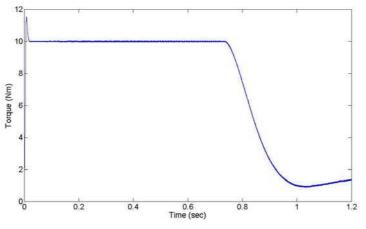

| FIGURE II-17: EDSVM TORQUE RESPONSE                                                                      |       |

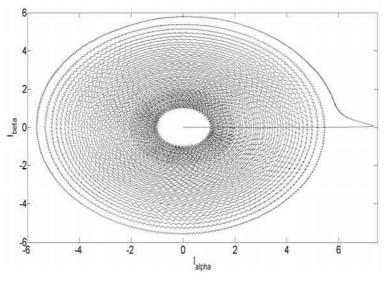

| FIGURE II-18: STATOR CURRENT EVOLUTION                                                                   |       |

| FIGURE II-19: EDSVM- IA, DA                                                                              |       |

| FIGURE II-20: RANDOM VECTOR SEQUENCE, TRIANGULAR CARRIER                                                 |       |

| FIGURE II-21: RANDOM VECTOR SEQUENCE, SAWTOOTH CARRIER                                                   |       |

| FIGURE II-22: RANDOM ACTIVE VECTOR SELECTION                                                             | . 84  |

| FIGURE II-23: COMPLEMENTARY COUNTERS                                                                     |       |

| FIGURE II-24: RANDOM ACTIVE VECTOR SELECTION; COMMUTATION SIGNALS                                        | . 86  |

| FIGURE II-25: RANDOM ZERO VECTOR DISTRIBUTION                                                            | . 87  |

| FIGURE II-26:HARMONIC FLUX, Λ <sub>H</sub> FOR D <sub>0</sub> ≠D <sub>7</sub>                            |       |

| FIGURE II-27: DIGITAL COUNTER                                                                            | . 88  |

| FIGURE II-28: PULSE GENERATOR                                                                            |       |

| FIGURE II-29: RSVM CONTINUOUS                                                                            |       |

| FIGURE II-30: RSVM: (No V7)                                                                              | . 92  |

|                                                                                                          |       |

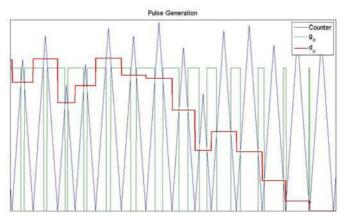

| FIGURE II-31: PULSE GENERATION                                                                       |     |

|------------------------------------------------------------------------------------------------------|-----|

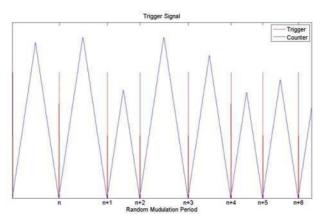

| FIGURE II-32: TRIGGERED ITERATIONS                                                                   |     |

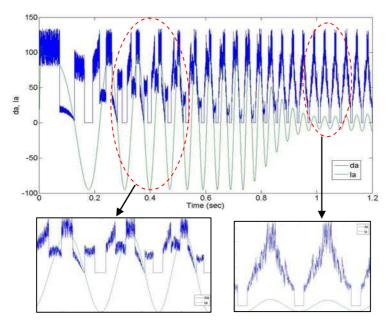

| FIGURE II-33: RDSVM – PHASE CURRENT AND MODULATION FUNCTION                                          |     |

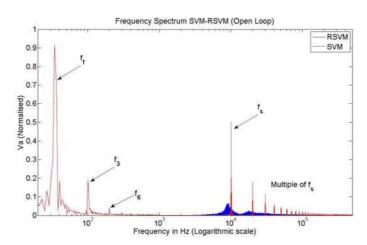

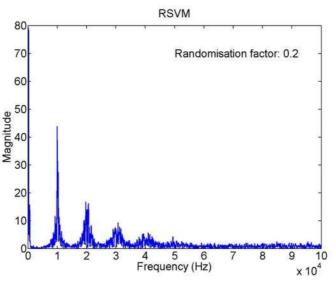

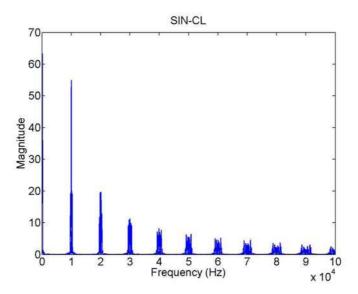

| FIGURE II-34: SVM, RSVM; FREQUENCY SPECTRUM CONTRAST                                                 |     |

| FIGURE II-35: RSVM STATOR CURRENT EVOLUTION                                                          |     |

| FIGURE II-36: FREQUENCY SPECTRUM CONTRAST (CLOSED LOOP)                                              |     |

| FIGURE II-37: SWITCHING HARMONICS (RSVM AND SVM)                                                     |     |

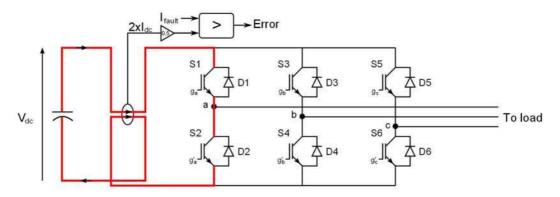

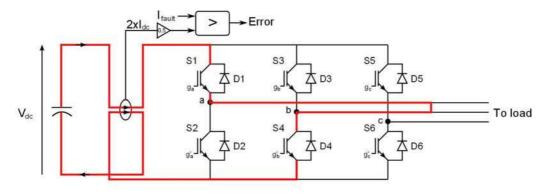

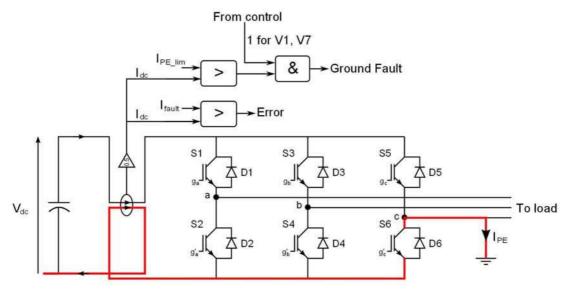

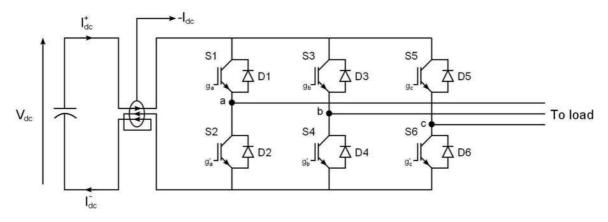

| FIGURE II-38: THREE PHASE INVERTER AND CURRENT SENSORS                                               |     |

| FIGURE II-39: CURRENT CHANNELLING                                                                    |     |

| FIGURE II-40. SPACE VECTOR REPRESENTATION                                                            |     |

| FIGURE II-41: MEASUREMENT VECTORS, [46]                                                              |     |

| FIGURE II-42: PULSE DISPLACEMENT, [48]                                                               | 101 |

| FIGURE II-43: DUTY CYCLE ALTERATION, [49]                                                            |     |

| FIGURE II-44: AVERAGE CURRENT AND HARMONIC CURRENT                                                   | 102 |

| FIGURE II-45: CURRENT RECONSTRUCTION ERROR ELIMINATION                                               | 103 |

| FIGURE II-46: FAULT DETECTION WITH ONE CURRENT SENSOR, [51]                                          |     |

| FIGURE II-47: DC LINK SHORT-CIRCUIT                                                                  | 104 |

| FIGURE II-48: PHASE SHORT-CIRCUIT                                                                    | 105 |

| FIGURE II-49: GROUND FAULT                                                                           | 105 |

| FIGURE II-50: FAULT DETECTION USING ONE CURRENT SENSOR, [50]                                         | 106 |

| FIGURE II-51: TRIANGLE AND SAWTOOTH MODULATION                                                       | 107 |

| FIGURE II-52: PHASE CURRENT DEDUCTION; HIGH M, AND SECTOR EXTREMITIES                                |     |

| FIGURE II-53: DISCONTINUOUS PWM FOR PHASE CURRENT DEDUCTION                                          |     |

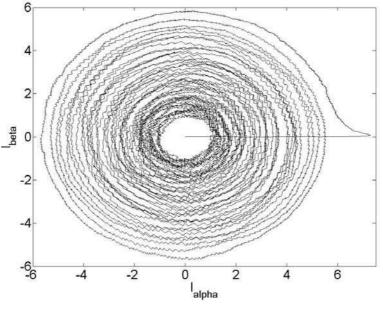

| FIGURE II-54: PHASE CURRENT IN THE AB-PLANE                                                          |     |

| FIGURE II-55: CURRENT IN THE DC-LINK                                                                 |     |

| FIGURE II-56: TWO NON-ADJACENT VECTORS – CASE1                                                       |     |

| FIGURE II-57: TWO NON-ADJACENT VECTORS – CASE2                                                       |     |

| FIGURE II-58: THREE NON-ADJACENT VECTORS                                                             |     |

| FIGURE II-59 THREE ADJACENT VECTORS                                                                  |     |

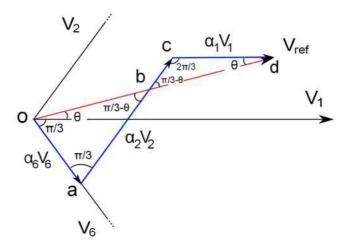

| FIGURE II-60: RMS INPUT CURRENT RIPPLE                                                               |     |

| FIGURE II-61: RMS INPUT VOLTAGE RIPPLE                                                               |     |

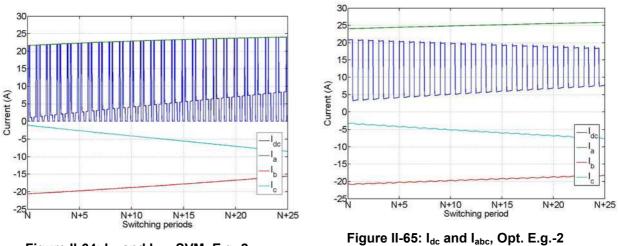

| FIGURE II-62: I <sub>DC</sub> AND I <sub>ABC</sub> , SVM. E.G1                                       |     |

| FIGURE II-62: $I_{DC}$ AND $I_{ABC}$ , SVM. E.G1<br>FIGURE II-63: $I_{DC}$ AND $I_{ABC}$ , OPT. E.G2 |     |

| FIGURE II-03. $I_{DC}$ AND $I_{ABC}$ , OPT. E.G2<br>FIGURE II-64: $I_{DC}$ AND $I_{ABC}$ , SVM. E.G2 |     |

| FIGURE II-65: $I_{DC}$ AND $I_{ABC}$ , OVT. E.G2                                                     |     |

| FIGURE II-05. 1 <sub>DC</sub> AND 1 <sub>ABC</sub> , OP1. E.G2.                                      |     |

| FIGURE III-1: TEST BENCH, SCHEMATIC DIAGRAM                                                          |     |

|                                                                                                      |     |

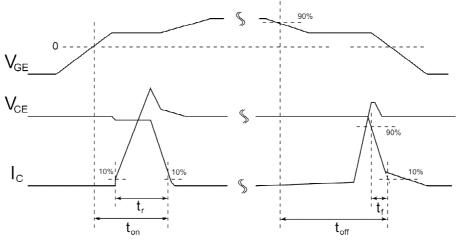

| FIGURE III-3: INVERTER MODULE<br>FIGURE III-4: IGBT SWITCHING CHARACTERISTICS                        |     |

|                                                                                                      |     |

| FIGURE III-5: DC SOURCE                                                                              |     |

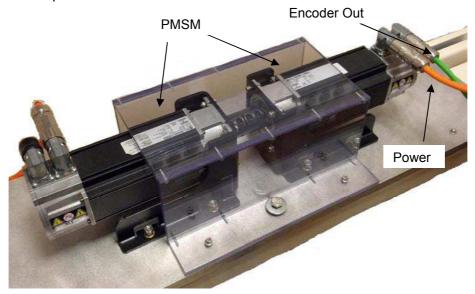

| FIGURE III-6: ELECTRIC MACHINE                                                                       |     |

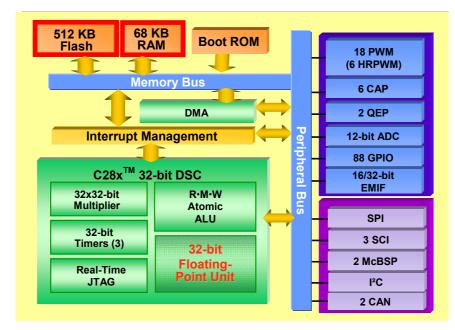

| FIGURE III-7: F28X ARCHITECTURE                                                                      |     |

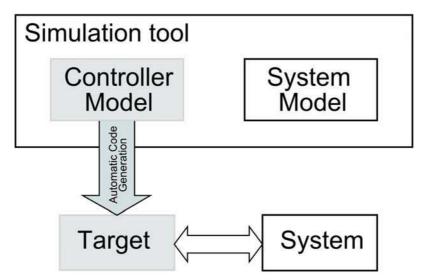

| FIGURE III-8: RAPID PROTOTYPING                                                                      |     |

| FIGURE III-9: SIMULATION IN THE LOOP                                                                 |     |

| FIGURE III-10: AUTOMATIC CODE GENERATION                                                             |     |

| FIGURE III-11: SCHEMATIC DIAGRAM OF THE INTERFACE CIRCUIT                                            |     |

| FIGURE III-12: ANALOG SIGNAL SCALING                                                                 |     |

| FIGURE III-13: ANTI-ALIASING FILTER                                                                  | -   |

| FIGURE III-14: INTERFACE BOARD                                                                       |     |

| FIGURE III-15: TEST BENCH                                                                            |     |

| FIGURE III-16: ADC CALIBRATION                                                                       |     |

| FIGURE III-17: CURRENT CALIBRATION                                                                   |     |

| FIGURE III-18: ENCODER VERIFICATION                                                                  | 135 |

| FIGURE III-19: PWM SIGNALS FROM DSP                                                                  |     |

| FIGURE III-20: WTHD0 FOR SPWM FOR DIFFERENT PULSE RATIOS                                             |     |

| FIGURE III-21: INVERTER FEEDING A STATIC LOAD                                                        |     |

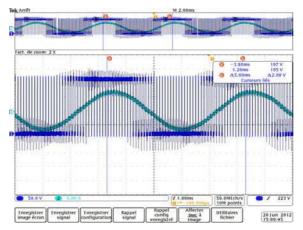

| FIGURE III-22: SPWM: PHASE VOLTAGE AND CURRENT                                                       |     |

| FIGURE III-23: SPWM: HARMONIC SPECTRUM                                                               |     |

| FIGURE III-24: SPWM: FREQUENCY SPECTRUM                                                              |     |

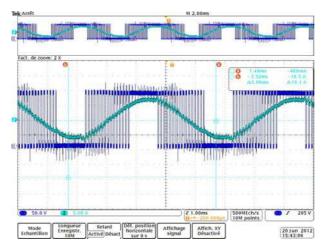

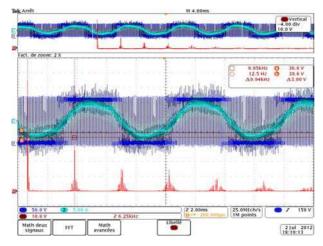

| FIGURE III-25: SVM: PHASE VOLTAGE AND CURRENT                                                        | 141 |

|                                                                                                      |     |

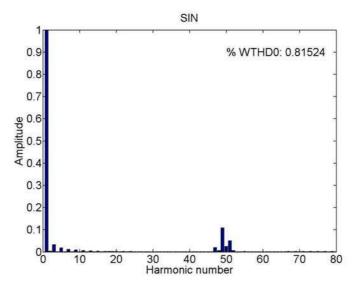

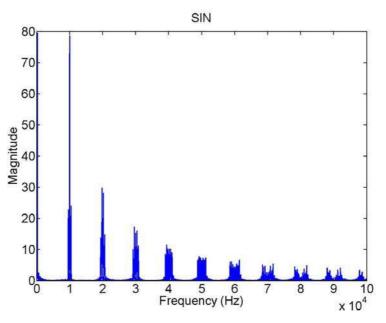

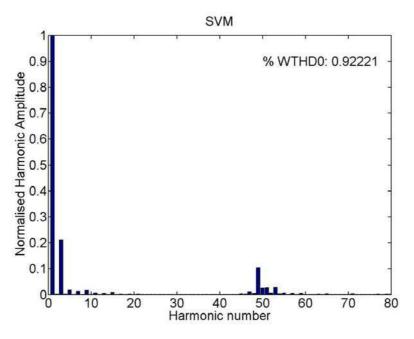

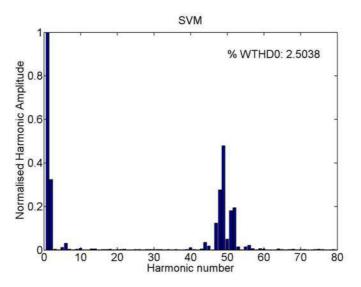

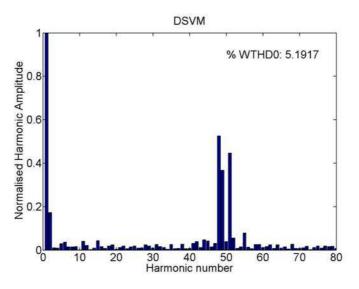

| FIGURE III-26: SVM: HARMONIC SPECTRUM                               | . 141 |

|---------------------------------------------------------------------|-------|

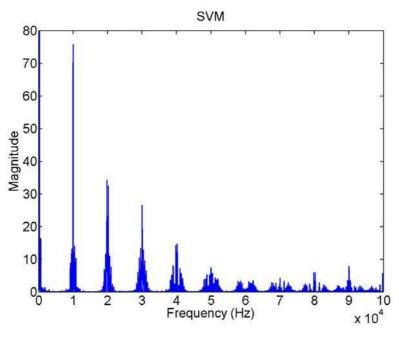

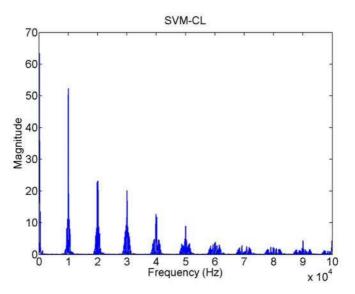

| FIGURE III-27: SVM: FREQUENCY SPECTRUM.                             |       |

| FIGURE III-28: DPWM1: PHASE VOLTAGE AND CURRENT.                    |       |

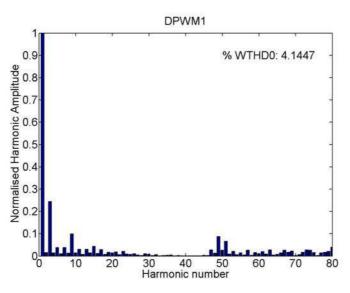

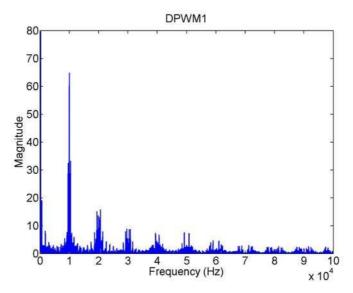

| FIGURE III-29: DPWM1: HARMONIC SPECTRUM                             |       |

| FIGURE III-30: DPWM1 SPWM: FREQUENCY SPECTRUM                       |       |

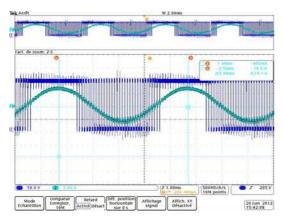

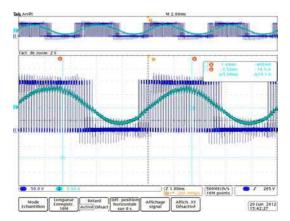

| FIGURE III-31: DPWMMAX: PHASE VOLTAGE AND CURRENT                   | . 144 |

| FIGURE III-32: DPWMMIN: PHASE VOLTAGE AND CURRENT                   | . 144 |

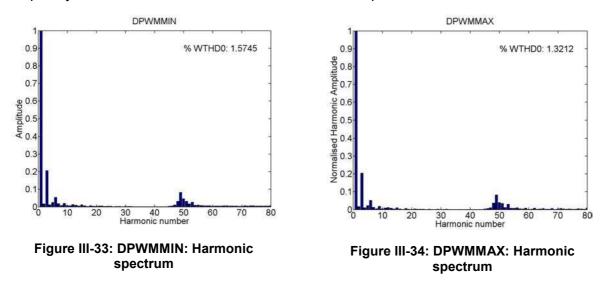

| FIGURE III-33: DPWMMIN: HARMONIC SPECTRUM                           | . 145 |

| FIGURE III-34: DPWMMAX: HARMONIC SPECTRUM                           | . 145 |

| FIGURE III-35: DPWMMIN: FREQUENCY SPECTRUM                          | . 145 |

| FIGURE III-36: DPWMMAX: FREQUENCY SPECTRUM                          | . 145 |

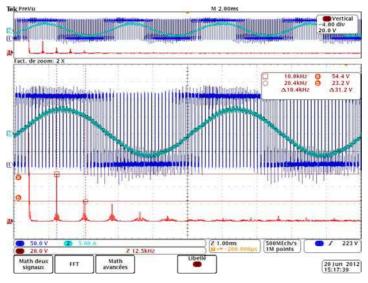

| FIGURE III-37: SVM: PHASE VOLTAGE AND CURRENT                       | . 146 |

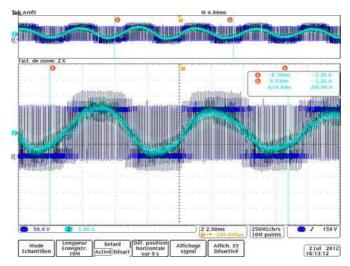

| FIGURE III-38: RSVM: PHASE VOLTAGE AND CURRENT                      | . 146 |

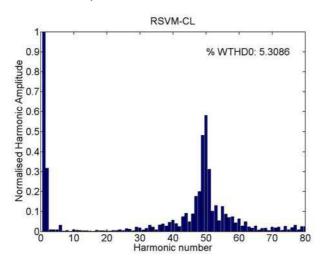

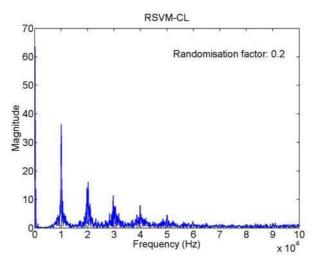

| FIGURE III-39: RSVM: HARMONIC SPECTRUM                              | . 147 |

| FIGURE III-40: DPWMMAX: FREQUENCY SPECTRUM                          | . 147 |

| FIGURE III-41: SPWM: PHASE VOLTAGE AND CURRENT                      | -     |

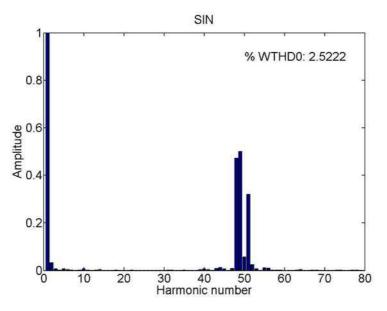

| FIGURE III-42: VECTOR CONTROLLED SPWM: HARMONIC SPECTRUM            | . 149 |

| FIGURE III-43: VECTOR CONTROLLED SPWM: FREQUENCY SPECTRUM           | . 150 |

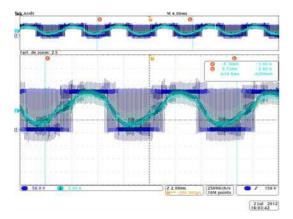

| FIGURE III-44: VECTOR CONTROLLED SVM: PHASE VOLTAGE AND CURRENT     | . 150 |

| FIGURE III-45: VECTOR CONTROLLED SVM: HARMONIC SPECTRUM             | . 151 |

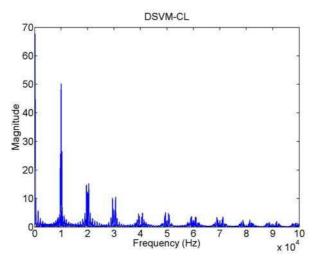

| FIGURE III-46: VECTOR CONTROLLED SVM: FREQUENCY SPECTRUM            | -     |

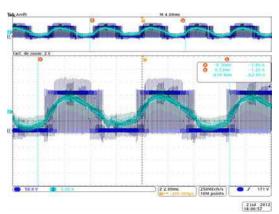

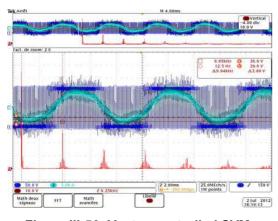

| FIGURE III-47: VECTOR CONTROLLED DSVMMAX: PHASE VOLTAGE AND CURRENT | . 152 |

| FIGURE III-48: VECTOR CONTROLLED DSVMMIN: PHASE VOLTAGE AND CURRENT | . 152 |

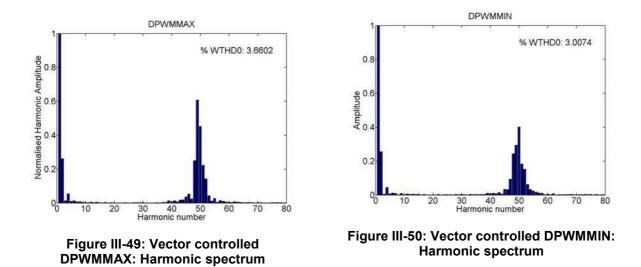

| FIGURE III-49: VECTOR CONTROLLED DPWMMAX: HARMONIC SPECTRUM         | . 153 |

| FIGURE III-50: VECTOR CONTROLLED DPWMMIN: HARMONIC SPECTRUM         | . 153 |

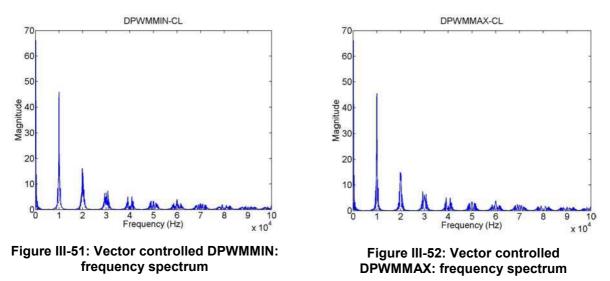

| FIGURE III-51: VECTOR CONTROLLED DPWMMIN: FREQUENCY SPECTRUM        |       |

| FIGURE III-52: VECTOR CONTROLLED DPWMMAX: FREQUENCY SPECTRUM        |       |

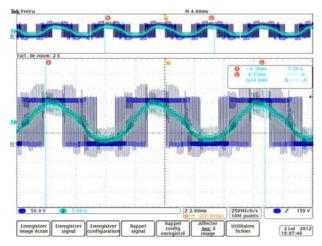

| FIGURE III-53: VECTOR CONTROLLED EDSVM: PHASE VOLTAGE AND CURRENT   | . 154 |

| FIGURE III-54: VECTOR CONTROLLED EDSVM: HARMONIC SPECTRUM           |       |

| FIGURE III-55: VECTOR CONTROLLED EDSVM: FREQUENCY SPECTRUM          |       |

| FIGURE III-56: VECTOR CONTROLLED SVM: PHASE VOLTAGE AND CURRENT     |       |

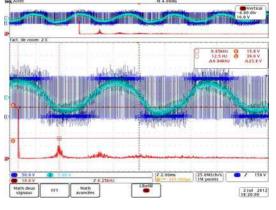

| FIGURE III-57: VECTOR CONTROLLED RSVM: PHASE VOLTAGE AND CURRENT    |       |

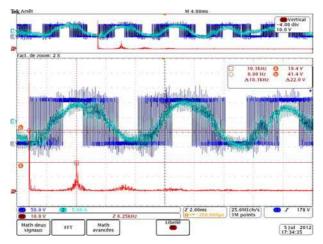

| FIGURE III-58: VECTOR CONTROLLED RSVM: HARMONIC SPECTRUM            |       |

| FIGURE III-59: VECTOR CONTROLLED RSVM: FREQUENCY SPECTRUM           |       |

| FIGURE III-60: VECTOR CONTROLLED RDSVM: PHASE VOLTAGE AND CURRENT   | -     |

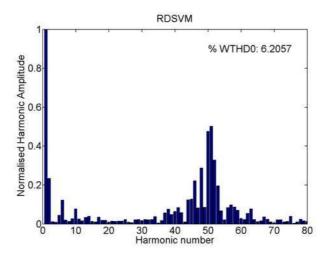

| FIGURE III-61: VECTOR CONTROLLED RSVM: HARMONIC SPECTRUM            |       |

| FIGURE III-62: VECTOR CONTROLLED RSVM: FREQUENCY SPECTRUM           | . 158 |

|                                                                     |       |

## **List of Tables**

| TABLE I-1 COMPARISON OF ELECTRICAL MACHINES                                      | 23  |

|----------------------------------------------------------------------------------|-----|

| TABLE I-2 VECTOR MAGNITUDES IN AB-PLANE                                          | 34  |

| TABLE I-3 ATTAINABLE VOLTAGE USING DIFFERENT TECHNIQUES                          | 41  |

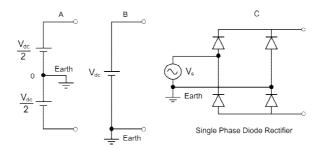

| TABLE I-4: VCM FOR A SINGLE PHASE FULL WAVE RECTIFIER                            | 49  |

| TABLE II-1: PHASE CURRENT AND SPACE VECTORS                                      | 99  |

| TABLE III-1: MACHINE CHARACTERISTICS                                             | 127 |

| TABLE III-2: EXPERIMENTAL PERFORMANCE COMPARISON OF DIFFERENT PWM STRATEGIES     | 148 |

| TABLE III-3: EXPERIMENTAL PERFORMANCE COMPARISON OF PWM STRATEGIES IN CLOSE-LOOP | 159 |

| DPWM   | Discontinuous Pulse Width Modulation  |

|--------|---------------------------------------|

| DFT    | Discrete Fourier Transformation       |

| DSP    | Digital Signal Processor              |

| DSVM   | Discontinuous Space Vector Modulation |

| DTC    | Direct Torque Control                 |

| ECU    | Electronic Control Unit               |

| EMC    | Electromagnetic Compatibility         |

| EMF    | Electromotive Force                   |

| EMI    | Electromagnetic Interference          |

| FFT    | Fast Fourier Transformation           |

| FOC    | Field Oriented Control                |

| HEV    | Hybrid Electric Vehicle               |

| ICEV   | Internal Combustion Engine Vehicle    |

| IGBT   | Insulated Gate Bipolar Transistor     |

| MOSFET | Metal Oxide Field Effect Transistor   |

| PMSM   | Permanent Magnet Synchronous Motor    |

| PSD    | Power Spectral Density                |

| PWM    | Pulse Width Modulation                |

| RCF    | Random Carrier Frequency              |

| RPP    | Random Pulse Position                 |

| RPWM   | Random Pulse Width Modulation         |

| RSVM   | Random Space Vector Modulation        |

| SVM    | Space Vector Modulation               |

| THIPWM | Third Harmonic Injection PWM          |

| THD    | Total Harmonic Distortion             |

| VSI    | Voltage Source Inverter               |

| 799    | Zero sequence signal                  |

ZSS Zero sequence signal

## **List of Notations**

- g<sub>a</sub> Upper switch Gating signal for phase 'a'

- $\langle V_a \rangle_T$  Mean phase voltage over a modulation period

- C<sub>a</sub> Clamping duration phase 'a'

- C<sub>NK</sub> Fourier coefficients

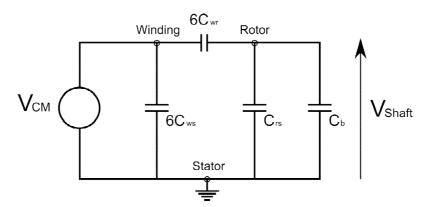

- $C_{ws}$  Parasitic capacitance between the stator windings and stator frame

- E Back EMF of the machine

- f(m<sub>i</sub>) Harmonic distortion factor

- f<sub>PWM</sub> Carrier frequency

- i<sub>h</sub> Harmonic current

- L Inductance

- m<sub>i</sub> Modulation index

- P<sub>sw</sub> Switching losses

- S(f) Power density spectrum

- u<sub>0</sub> Zero sequence voltage

- V\*<sub>a</sub> Voltage reference, phase 'a'

- V<sub>a0</sub> Phase 'a' voltage with respect to DC mid-point

- V<sub>an</sub> Phase voltage with respect to the load neutral

- V<sub>CM</sub> Common mode voltage

- V<sub>dc</sub> Inverter input voltage

- V<sub>i</sub> Space vectors (i=0,1,2,3,4,5,6,7)

- v<sub>max</sub> Maximum instantaneous value of a 3 phase system

- V<sub>n0</sub> Potential difference between load neutral and the DC mid-point

- $V_{\alpha}$ ,  $V_{\beta}$  Voltages in  $\alpha\beta$ -plane

- $\alpha_i$  Duty cycle of space vectors

- $\lambda_h$  Harmonic flux

- $\phi$  Phase angle between the phase voltage and current

## Introduction

Vehicles contribute enormously to atmospheric pollution, about 20%-35% of total atmospheric pollution [1]. An average European car produces about 4 tonnes of  $CO_2$  every year [2], [3]. These emissions can be classified further as exhaust emissions including dangerous gases such as carbon monoxide, oxides of nitrogen, hydrocarbons and particulates and evaporative emissions vapours of fuel which are released into the atmosphere without being burnt. Some of these gases contribute to the greenhouse effect which is a threat to the planet.

EVs or HEV can help to considerably reduce these emissions. Depending on the way the electricity is produced and on the type and extent of electrification of the vehicle (e.g. micro hybrid, mild hybrid, Plug in HEVs range extenders, pure electric etc.) the emissions can be reduced from 5% to 100%. Statistics for some HEVs are given in Table I. Toyota Prius is most sold HEV.

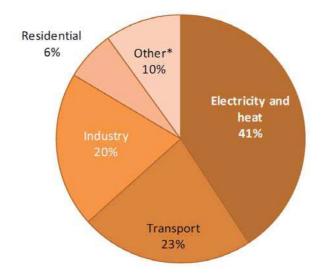

Figure 1. World CO<sub>2</sub> emissions by sector in 2009 [3]

Figure 1 shows the carbon dioxide emissions by sector for the year 2009. It is clear that transport represents the second largest chunk on the pie chart, however electricity and heat remain the biggest contributors of this greenhouse gas. Hence all the more reason to concentrate on Hybrids rather than on all-electrics, until we get this percentage down. However this doesn't apply to countries which do not use fossil fuel to generate electricity. The '*Other*' on the chart includes commercial/public services, agriculture/forestry, fishing, energy industries other than electricity and heat generation, and other emissions not specified elsewhere.

|                      | CO2 Reduction<br>(%) | Fuel consumption<br>Reduction (%) |

|----------------------|----------------------|-----------------------------------|

| Toyota Prius         | 42                   | 38                                |

| Ford Fusion Hybrid   | 36                   | 31                                |

| Lincoln MKZ Hybrid   | 36                   | 31                                |

| Honda Civic Hybrid   | 31                   | 28                                |

| Lexus HS 250h        | 30                   | 28                                |

| Mazda Tribute Hybrid | 26                   | 23                                |

| Nissan Altima Hybrid | 21                   | 19                                |

| Table I. HEV | pollution | reduction |

|--------------|-----------|-----------|

|--------------|-----------|-----------|

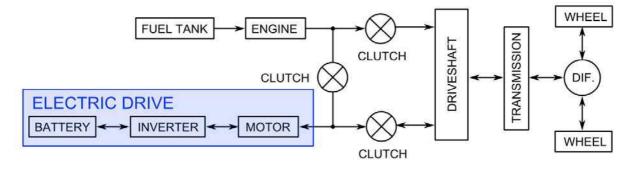

ICEVs give good performance and autonomy, taking advantage of the rich petroleum fuels. The efficiency and pollution of such vehicles is a threat to the environment and limited energy reserves. Whereas battery powered EVs have high efficiency and zero emission but very low operating range per battery charge. HEVs have the advantages of an ICEV and an EV while alleviating their drawbacks [1], [6]. Since HEVs have two energy sources and converters it could considerably increase the cost and space requirements as can be seen in Figure 2. Many types of hybrid structures are possible like series, parallel, series-parallel and complex hybrid [7]. Parallel hybrid best meets the objective of increased efficiency and low emissions. There are serious drawbacks of the series hybrid drivetrain, such as the energy conversion takes place twice and the electric traction motor needs to be rated for maximum power. Whereas for a parallel drivetrain, a complex mechanical coupling design is required with the additional complexity of regulating/blending two parallel power sources [8], [1].

Figure 2. Parallel HEV Drivetrain

Regenerative braking, or energy recuperation, is the principal means through which the kinetic energy of the vehicle is returned to electric energy storage rather than burned off as heat in the brake pads. But there are practical limits to how much and how fast regenerative braking can be applied. The machine runs in the generator mode and the inverter in rectifier mode, hence a reversible converter is required. Smooth braking is the result of a fine balance between electric motor energy recuperation and the vehicle's foundation brakes. The best brake system for a hybrid is what is known as series regenerative braking system (RBS). With series RBS the electric motor extracts braking energy without application of the service brakes, then when higher braking forces are required, or if the brake pedal is depressed faster than a prescribed threshold, the service brakes are engaged so that total braking effort is delivered. Not only are such cars energy efficient they have better performance owing to very dynamic torque response, particularly under Field Oriented Control (FOC), it is quicker than ICE response. During gear-shifting the electric motor can add torque to the driveline, thus filling in for lack of engine-supplied torque and give a better driving experience. Hybrid electric power trains require a large investment in electric motor and power electronics technology. Package space is extremely restricted so that even with a ground-up design for a hybrid there is little space to put 20 to 100 kW electric machines and the power electronics to drive them. Such machines must not only have the highest power density but they must also be robust and efficient. The power electronics must be of the highest power density both gravimetrically and volumetrically [1].

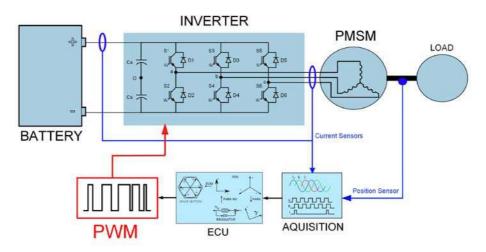

Nonetheless EVs have already penetrated the off-road vehicles where the required autonomy is not the limiting factor and is known beforehand and where low acoustic noise and clean air are a priority. Such applications include airport vehicles for passenger and ground support; recreational vehicles like golf carts and for theme parks, plant operation vehicles like forklifts and loader trucks. All of this is possible because of the technological advancements in power electronics and digital signal processors. The recent developments in the field of power solid state devices or Power Electronics has changed completely the form of electric propulsion system, it has made the use of AC machines possible. Here we'll discuss electric drives with a portable energy source, the battery for automotives. A typical modern electric drive is shown in Figure I-1. The AC motor is fed by a battery via a Voltage Source Inverter (VSI), it can be seen as the interface between the DC voltage source (battery) and the AC Motor. The inverter can convert DC Voltage in a poly phase AC voltage source of variable amplitude and frequency. They are made up of power switches that can be electronically switched on and off. These electronic signals are voltage pulses for IGBTs, which have been used in this work as they meet our power and frequency requirements. An Electronic Control Unit (ECU) calculates the duty cycle of the pulses using the information fed to it by an acquisition circuit, this is known as Pulse Width Modulation.

The research revolves around the development of modulation techniques for hard switched three phase two level inverters for variable speed drives destined for HEV to alleviate the drawbacks of the hybrid drivetrains mentioned above. Random and discontinuous modulation techniques have been developed to address the issues of EMI interference and switching losses respectively and their digital implementation has been given equal importance. Techniques to reduce DC-link capacitors are also developed.

Hard switched PWM converters have the following drawbacks:

1) Electromagnetic pollution caused by the switching harmonics and switching transients [11] may hamper the proper functioning of digital electronic circuitry used extensively in modern cars. This is normally dealt by adding bulky and voluminous L-C filters and shielding of the power converter.

2) Switching Losses [12] are not only a waste of energy but give rise to another very important concern -- evacuating this energy dissipated in the form of heat in the power switches. Thermal stress can lead to poor functioning and in extreme cases complete failure of the switch.

3) Shaft voltages may cause an electric discharge through the lubricant around the ball bearing and the stator called bearing current and destroy the motor [13].

4) Acoustic noise in power converters [14] for switching frequencies in the audible range till 22kHz can be very annoying.

To alleviate these drawbacks this work has the objective of reducing the cost and volume of the electric drivetrain by developing innovative PWM techniques to reduce the need of auxiliary components required to suppress the side effects of such systems namely EMI, DC link fluctuations and heating of the power switches and at the same time increasing the efficiency and hence an improved autonomy on battery. These auxiliaries are namely the passive filters to absorb the switching harmonics, DC stabilizing capacitors and voluminous cooling circuit.

A very important aspect of this research is the integration of EMI mitigation techniques and meeting Electromagnetic Compatibility (EMC) standards at the development stages of the electric drive rather than troubleshooting at the end, which is a costly and time-consuming process. The motivation behind the work is to reduce the cost to market of HEVs which is significantly higher than conventional cars. Innovative techniques based on the classical PWM techniques such as RPWM and DPWM exist to address the issue of unwanted harmonics linked to the switching frequency and the switching losses. These techniques are explained in the chapters to follow. Space Vector Modulation (SVM) is a relatively new PWM technique based on mathematical transformations and has some advantages over conventional techniques. Since more and more sophisticated techniques are used, such as FOC, DTC, the digital signal processors have become indispensible and this means SVM can be implemented at no extra cost. SVM has been taken as the basic modulation technique and its derivatives are developed to address the issues mentioned above.

In such electric drives, PWM methods influence heavily the behaviour of the drive. A meticulously programmed technique cannot only give improved performance but also reduce many of the unwanted secondary effects of modulated power supply. The work

presented here is on developing such PWM techniques to alleviate the problems in the drives mentioned in the previous section.

The thesis is divided into four parts, the first part puts into perspective the need for this study and an assessment of the state of the art of the field, explaining briefly the major problems that need to be addressed. Introduction to EMI is given and then an overview of some performance indicators of Pulse Width Modulators. The second part gives details of the PWM techniques developed during this PhD. The third part gives the details of the experimental setup and the experimental validations of the techniques developed in the second part. The fourth part is the conclusion and few suggestions for future works.

# **PART I**

# PRELIMINARIES

## **I.**Preliminaries

The research documented in this thesis relates to pulse-width modulation (PWM) techniques for hard-switched three phase two level power electronic inverters for variable speed drives destined for vehicle propulsion. Focus has been on two different types of modulators that introduce randomness and discontinuity to the system for reasons to be described shortly. Such modulators are generally designated as random PWM techniques in the literature to emphasize their non-deterministic properties.

### I.1. Introduction

An electric drive comprises of an inverter which interfaces the energy source to the motor/generator. In the context of vehicle propulsion system the inverter helps feeding the motor as required by the driver but also recharging the batteries during deceleration and braking. The inverter is comprised of electronically controllable switches. The PWM schemes control the state of the switches whether conducting or not. The maximum DC side voltage is about 600V hence 2 level IGBT inverters are sufficient. However to improve the signal quality one can imagine the use of multilevel inverters but for automotive applications it is not practical owing to the extra cost it will add to the overall system, i.e. extra gate drivers, extra PWM peripherals, extra processing power, extra space.

Figure I-1: Schematic diagram of an Electric Drive

Permanent Magnet Synchronous Motor (PMSM) are preferred as they are superior to the DC and induction motors in servo applications due to their high power density, efficiency, moment to current ratio and their low moment of inertia [9]. Permanent Magnet Synchronous Motors (PMSM) have been unanimously declared to be the most suitable for HEVs. Table I-1 recapitulates how different electrical machines fair on grounds mentioned above.

|               | DC | IM | PMSM | SRM |

|---------------|----|----|------|-----|

| Power Density |    | +  | ++   | 0   |

| Efficiency    |    | +  | ++   | 0   |

| Cost          | +  | +  | 0    | +   |

**Table I-1 Comparison of Electrical Machines**

The two most pertinent control schemes for AC motors are Field Oriented Control (FOC) and Direct Torque Control (DTC). The former was chosen because DTC is a method based on hysteresis comparators which require the controller to work at a very high frequency in order to confine the error in the hysteresis band which means introducing error to the system and hence torque ripple. FOC unlike DTC is based on regulators which calculate the exact value of the phase voltage to be fed to the motor. PWM techniques are used to calculate the duty cycle of the pulse to be applied to the switch to produce the required output voltage to be applied to the motor [10]. PWM techniques are at the heart of such drives, they have a huge influence on various aspects apart from the quality of the voltage produced, like the losses and electromagnetic interference.

### **I.2. Literature review**

Pulse Width Modulation is an interface between the control circuit and the inverter, where the modulator is given a value that is required at the converter terminal and it has to produce it for a given period and a given DC voltage. Modulation technique was developed by communication engineers to transmit a baseband signal by transforming it into a passband signal. The use of PWM for electric drives dates as back as the early 1960s [15].

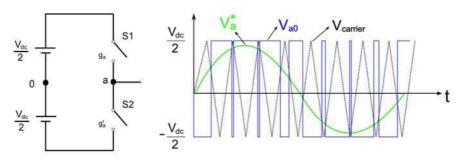

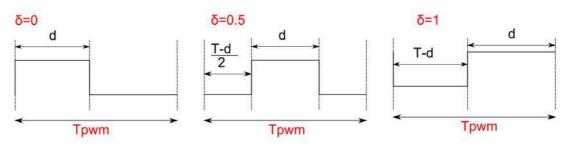

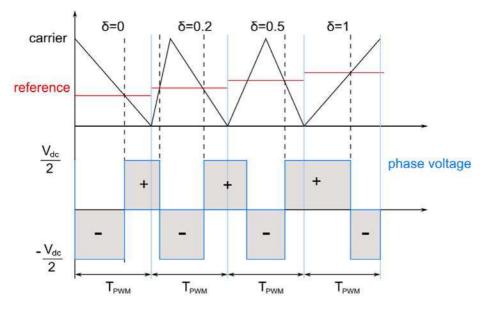

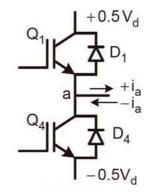

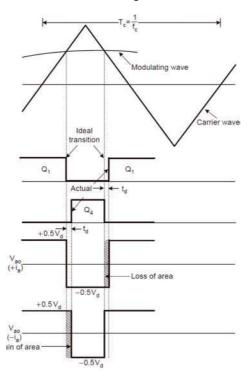

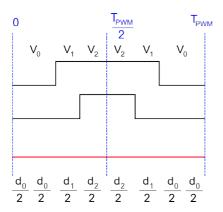

The concept is to achieve a variable voltage from a fixed DC voltage source while regulating the duty cycle of the power converter control signal. Half bridge or a converter leg configuration is shown in Figure I-2. The control signals  $g_a$  and  $g_a$ ' of the two switches S1 and S2 are complementary in nature. The voltage output ( $V_{a0}$ ) for a sinusoidal reference signal ( $V_a^*$ ) is the modulated signal generated by comparing a high frequency carrier wave with the reference signal, the switch changes state each intersection of the these two signals The voltage produced is known as Pulse Width Modulated Voltage. The average value of the modulated voltage over a carrier period is equal to the reference voltage for that carrier period this is also known as Volt-Sec match. For good results the carrier frequency should be at least 20 times higher than the fundamental frequency.

Figure I-2: Half Bridge

### I.2.1. Fundamentals of PWM

Different types of carrier signal and the frequency of the reference voltage updates schemes can be envisioned and some of the most common methods are discussed here. The two predominant carrier signals used are sawtooth, triangular and the reference voltage updates usually employed are naturally sampled, regularly sampled (symmetrical and asymmetrical).

Figure I-3: (a), (b): Naturally sampled, (c), (d) regularly sampled

The naturally sampled scheme is realized by an analog circuit and therefore the comparator is updated continuously and thus the most accurate. Whereas other techniques such as symmetrical, asymmetrical, multi-sampled schemes are digitally implemented using DSP/FPGA. In Figure I-3 and Figure I-4 the evolution the reference signal is highly exaggerated as the carrier is very high compared to the reference signal frequency for a carrier period the reference signal can be considered constant.

Figure I-4: Asymmetrically sampled

### I.2.2. Classical Sinusoidal PWM

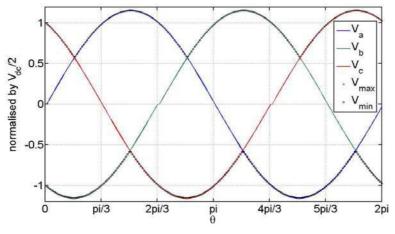

Three half bridges in parallel form a three phase inverter. For a 3-phase system given by (1.1) the voltage reference of each leg is phase delayed by 120°.

$$\begin{bmatrix} v_a^* \\ v_b^* \\ v_c^* \end{bmatrix} = A \begin{bmatrix} \sin(\theta) \\ \sin(\theta - 2\frac{\pi}{3}) \\ \sin(\theta - 4\frac{\pi}{3}) \end{bmatrix}$$

(1.1)

The most basic and straight forward PWM strategy is the Sinusoidal PWM. This method is used specially for loads with neutral tied to the ground or the DC mid-point.

$$d_{i} = \frac{T_{PWM}}{2} (1 + \frac{2v_{i}^{*}}{v_{dc}}) \times 100$$

where i \le \{a, b, c\}

(1.2)

Equation (1.2) gives the duty cycle in percentage of the modulation period ' $T_{PWM}$ ' for symmetrically sampled PWM. Since the duty cycle cannot be greater than 100, again from equation (1.3) one can deduce that the amplitude of the reference is limited to half of V<sub>dc</sub>. Hence the maximum value of A is A<sub>max</sub>=V<sub>dc</sub>/2.

Modulation Index  $(m_i)$  is given by (1.3) to evaluate the extent to which the DC input voltage is used.

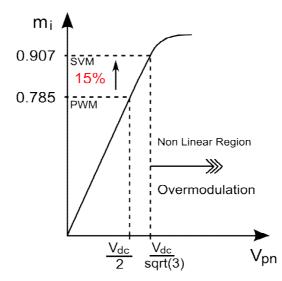

$$m_{i} = \frac{V_{fundamental-PWM}}{V_{fundamental-sixstep}}$$

(1.3)

Six step refers to square wave phase voltage were for the positive half cycle the phase is clamped to the positive terminal of the DC source and for the negative half to the negative terminal hence the voltage is not modulated and produces the maximum output voltage. This definition of  $m_i$  is chosen so because it makes sure that  $0 \le m_i \le 1$ . The fundamental component of a square wave is  $2 V_{dc} / \pi$ . So the modulation index for SPWM

is  $\frac{\pi}{4}$  or 0.785.

Frequency domain analysis of the modulated signal helps visualizing the presence of the reference signal in the square pulse train. The switching harmonics are the byproduct of the PWM, frequency domain analysis of the PWM signals are elaborated later in the thesis. These unwanted high frequency voltage causes conducted and radiated electromagnetic emissions. Passive filters are used to send back these voltages back to the source and absorb some of these unwanted signals however to reduce the filtering effort one can use Random PWM methods explained in the next section.

### I.2.3. Hysteresis Band control

Before we go further I'd like to mention a slightly different type of controller, called the hysteresis controller or a current regulator. As the name current regulator suggest this technique directly controls the current in the inverter. What distinguishes it from the other PWM techniques is that it is technique is a closed loop technique i.e. it requires a feedback. This is the most basic current control method that doesn't require current regulators. The switches are controlled to maintain the current around the desired value defined by the hysteresis band (HB). As indicated in Figure I-5, if the actual current exceeds the HB, the upper device of the half-bridge is turned off and the lower device is turned on. As the current decays and crosses the lower band, the lower device is turned off and the upper device is turned on. If the HB is reduced, the harmonic quality of the wave will improve, but the switching frequency will increase, which will in turn cause higher switching losses.

Figure I-5: Hysteresis Band

Basically, the current loop error signal generates the PWM voltage wave through a comparator with a hysteresis band. Although the technique is simple, control is very fast, and device current is directly limited, the disadvantages are a harmonically non-optimum waveform and the phase lag is frequency dependent, increases with the increase in frequency.

### I.2.4. Zero Sequence voltage injection

If the neutral point on the poly-phase load has a floating neutral i.e. not connected to the DC side midpoint 0 or the ground, the zero sequence signals (ZSS) in the phase voltages disappear from the line voltages and thus the phase currents depend only on the potential difference between the phases and the phase to neutral voltages are perfectly sinusoidal and in turn the phase currents. A 3-phase 3-wire system, i.e. neutral free to float with respect to the ground or the DC mid-point is shown in Figure I-6.

Figure I-6: Inverter fed floating neutral 3-Phase load

However certain rules must be followed while inserting ZSS into the reference voltages. In equation (1.4) the  $u_0$  is the ZSS voltage added and u<sup>\*</sup> is the original reference voltage generally sinusoidal and u<sup>\*\*</sup> is the final voltage seldom a sinusoid of different amplitude.

$$u^{**} = u^* + u_0 \tag{1.4}$$

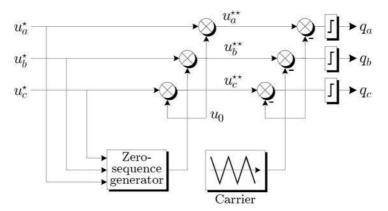

Figure I-7 shows a generalised modulator commonly abbreviated as GPWM.

Figure I-7: Generalized modulator: ZSS injection

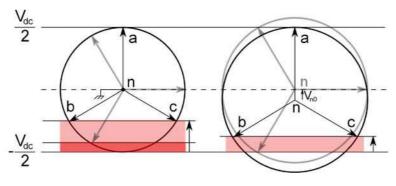

Figure I-8 helps visualize the concept of floating neutral and how one can achieve higher phase voltages injecting the right zero sequence component without creating an imbalance, in the next section we'll see what ZSS should be injected if the goal is to achieve higher phase voltages. Whatever be the zero sequence voltage injected into the system it should not make the phase voltages go beyond the maximum calculated value, beyond this value it will introduce imbalance in the system. Another very important aspect about ZSS component is the possibility of adding discontinuity to the modulator.

Figure I-8: Floating neutral

From the above figure the maximum value of the phase to neutral voltage can be calculated.

$$\begin{aligned} \left| V_{an} - V_{bn} \right| &\leq V_{DC} \\ V_{\max} \angle 240 - V_{\max} \angle 0 = V_{dc} \\ V_{\max} \cos 30^\circ + V_{\max} \cos 30^\circ + V_{\max} \cos 60^\circ - V_{\max} \cos 60^\circ = V_{dc} \\ V_{\max} &= \frac{V_{dc}}{2\cos 30^\circ} = \frac{V_{dc}}{\sqrt{3}} \end{aligned}$$

$$V_{\max} = \frac{V_{dc}}{\sqrt{3}} \tag{1.5}$$

From the above derivation it is evident that there are limits to the ZSS that can be added without creating an imbalance in the poly-phase system.

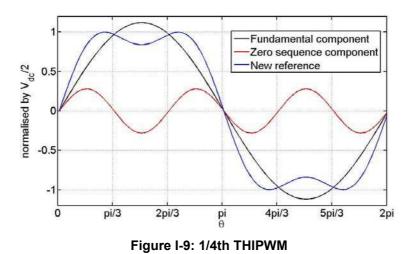

### I.2.4.1. Third Harmonic Injection PWM

Third harmonic injection PWM (THIPWM) can increase the value of the fundamental component of the phase voltage, Figure I-9 shows that after the addition of the zero sequence component the region which would have been over-modulated or un-modulated is now under linear modulation region. The optimum injection value can be calculated as following: [16].

The most prominent third harmonic injection schemes are THIPWM1/4 and THIPWM1/6 where the zero sequence voltage to be injected is given by (1.6).

$$u_{0} = A_{3} \cos(3\omega t)$$

$$A_{3} = \frac{A_{1}}{4} \text{ or } A_{3} = \frac{A_{1}}{6}$$

(1.6)

Where A1 and A3 are the amplitudes of the fundamental and the third harmonic components respectively. Injecting ¼ of the fundamental is theoretically superior in terms of harmonic distortion [17] while injecting 1/6 increases the fundamental to the maximum possible value , this can be shown in the following manner: Let Eq.(1.7) give the resultant voltage after third-harmonic injection.

$$V_a = \frac{V_{dc}}{2} \left( M_1 \cos \theta + M_3 \cos 3\theta \right)$$

(1.7)

Dividing by

$$\frac{M_1 V_{dc}}{2}$$

we get:

$v = \cos \theta + \gamma \cos 3\theta$

Where  $\gamma = \frac{M_3}{M_1}$ .

$\frac{dv}{dt} = \sin \theta + 3\gamma \sin 3\theta = 0$  (1.8)

The maxima or minima of (1.7) would lie on the values of  $\theta$  and  $\gamma$  that satisfy equation (1.8) and sin 3 $\theta$  can be written as:

$\sin 3\theta = (4\cos^2\theta - 1)\sin\theta$

Substituting it in equation (1.8) gives

$\sin\theta + 3\gamma(4\cos^2\theta - 1)\sin\theta = 0$  from where the value of  $\cos\theta$  can be calculated as:

$$\cos\theta = \sqrt{\frac{3\gamma - 1}{12\gamma}} \tag{1.9}$$

$\cos 3\theta$  can similarly be expanded to give as  $\cos 3\theta = (4\cos^2 \theta - 3)\cos \theta$  and therefore

$$\cos 3\theta = -\frac{6\gamma + 1}{6\gamma} \sqrt{\frac{3\gamma - 1}{12\gamma}}$$

Substituting these values back in (1.8) give:

$$v_{\rm max} = -\frac{3\gamma - 1}{3} \sqrt{\frac{3\gamma - 1}{3\gamma}}$$

(1.10)

Differentiating this time with .respect to  $\gamma$  and equating to 0.

$$\frac{dv_{\max}}{d\gamma} = \sqrt{1 - 1 - \frac{1}{3}\gamma} - \frac{1}{6}\frac{3\gamma - 1}{\sqrt{1 - \frac{1}{3\gamma}}}\frac{1}{3\gamma^2}$$

$$0 = \sqrt{1 - \frac{1}{3}\gamma}(1 + \frac{1}{6\gamma})$$

We get two values of  $\gamma$ .

$$\gamma = \frac{1}{3} \& \gamma = -\frac{1}{6}$$

(1.11)

The first one can be neglected and clearly produces 0 when substituted in (1.10). Hence a minimum.

With the second value of  $\gamma$  the maximum attainable fundamental component is found.

$$A_{\rm l,max} = \frac{V_{dc}}{\sqrt{3}} \tag{1.12}$$

It should be noted that the amplitude is one-sixth of the A1,max given by equation (1.12). It is the same value that was calculated earlier in this chapter hence it confirms that injecting this ZSS the maximum possible phase voltage can be achieved.

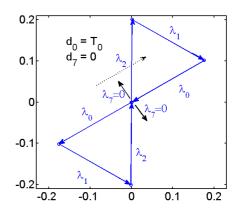

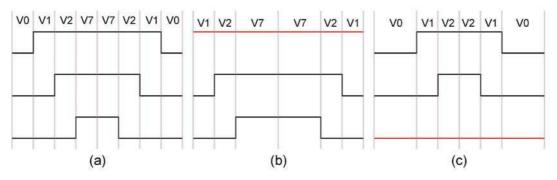

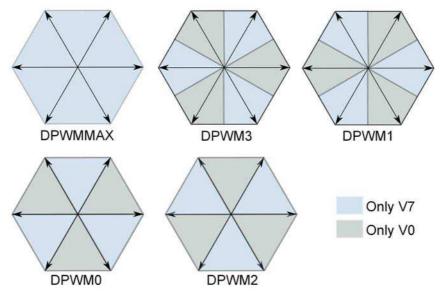

#### I.2.4.2. Discontinuous PWM

ZSS can be injected in the system not only to make better use of the DC link voltage, it can also reduce the effective switching frequency over a fundamental period avoiding commutations during a part of the fundamental period. The idea behind such techniques is clamping a phase to either side of the DC rail. To clamp phase 'i' the following condition must be met:

$$v_i = v_{\max} \vee v_{\min} \tag{1.13}$$

This condition basically assures that the line voltages will not be distorted and since line voltages dictate the current in the phases for loads with floating neutral. Respecting this condition one can imagine quite a few discontinuous techniques. The commonly found techniques in the literature are briefly covered here. All the figures in this section show three waveforms: the zero sequence signal in red, the initial voltage reference signal in black and the new resultant signal (blue) u<sup>\*\*</sup>. In this method the voltage clamping is symmetrical for the positive and negative half cycles.

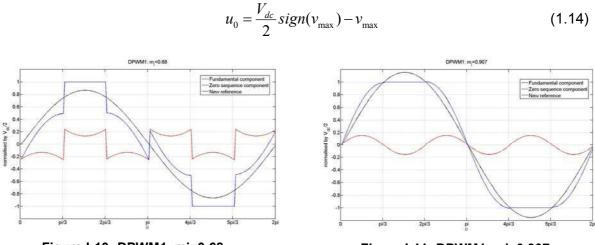

### I.2.4.2.1. DPWM1

DPWM1 is one of the most basic types of modulation scheme where the phase with the maximum absolute amplitude is clamped. The expression of the voltage to be injected in this case is given by (1.14).

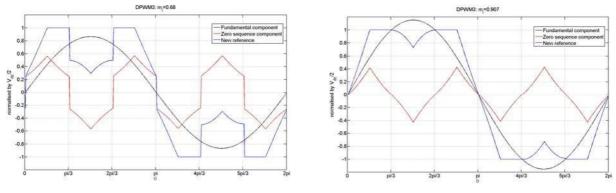

Figure I-10: DPWM1, mi=0.68

Figure I-11: DPWM1, mi=0.907

Where  $V_{max}$ = max(abs(V<sub>a</sub>, V<sub>b</sub>, V<sub>c</sub>). Figure I-10 and Figure I-11 show the DPWM1 method for two different modulation index.

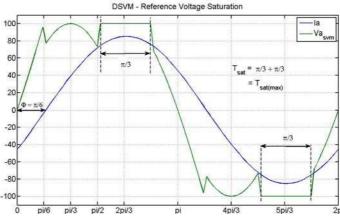

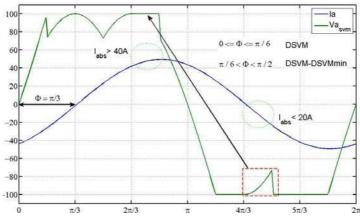

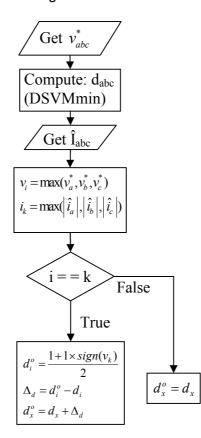

### I.2.4.2.2. DPWMMIN & DPMWMMAX

Voltage clamping for these methods is done either at maximum voltage or minimum. This method unlike DPWM1 is an unsymmetrical method where clamping is done only during one of the two half cycles for 120°. The harmonic injection law for DPWMMIN is given by (1.15):

Similarly the zero sequence component to be inserted is given by equation (1.16). Figure I-12 and Figure I-13 show the modulation functions for DPWMMAX and DPWMMIN respectively.

I: Preliminaries

$$u_0 = \frac{V_{dc}}{2} - v_{max}$$

(1.16)

#### I.2.4.2.3. DPWM3

DPWM3 has four 30° discontinuous segments as can be seen in Figure I-14 and Figure I-15, the zero sequence voltage to be injected is given by:

$$u_0 = \frac{signV_{dc} - \{(sign+1)V_{max} - (sign+1)V_{min}\}}{2}$$

(1.17)

If  $|V_a| < |V_b| < |V_c|$ , then sign=1 if  $V_a > 0$  and -1 otherwise.

Figure I-14: DPWM3, mi=0.68

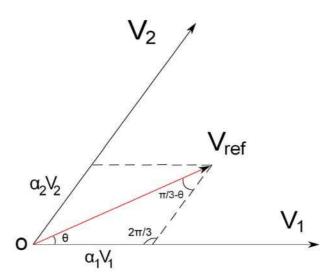

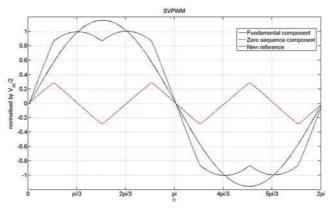

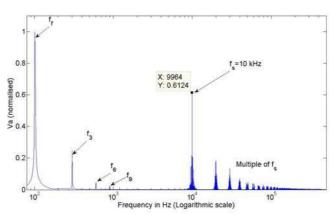

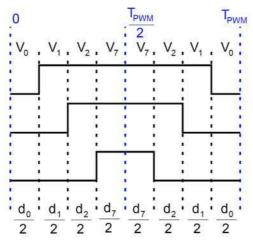

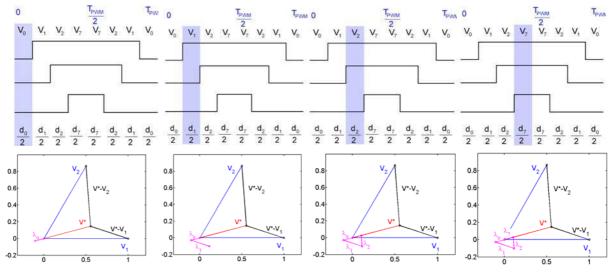

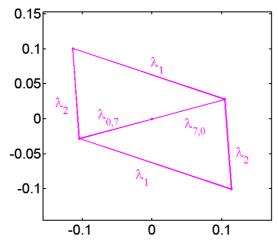

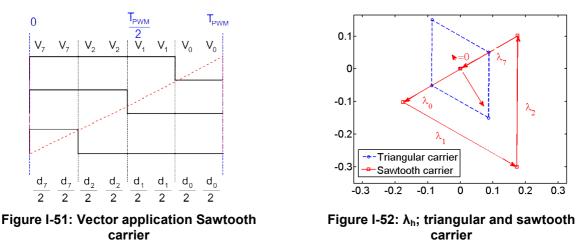

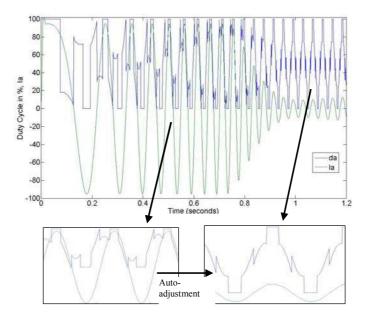

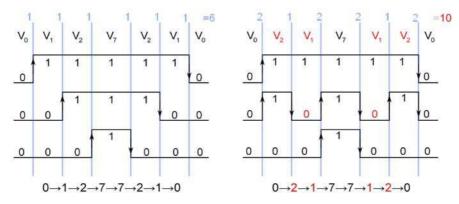

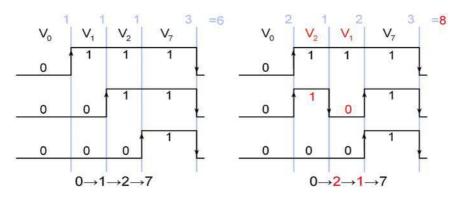

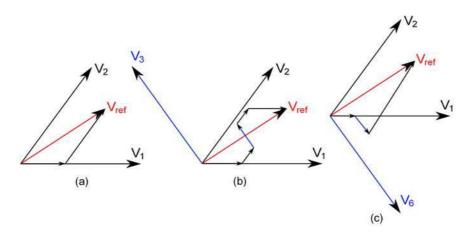

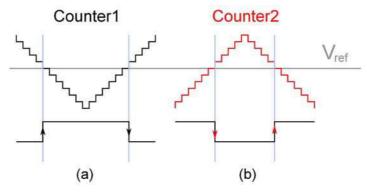

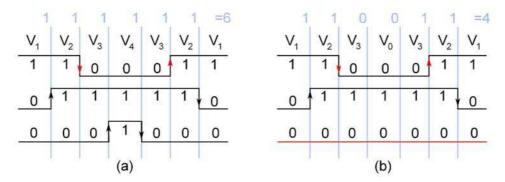

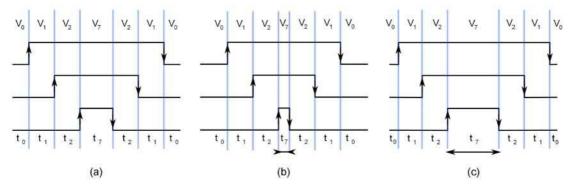

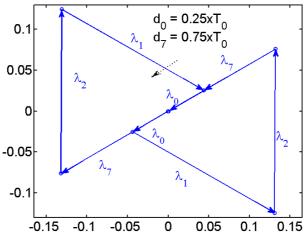

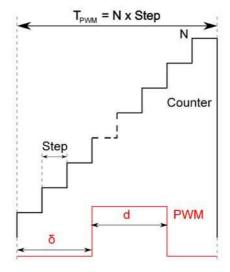

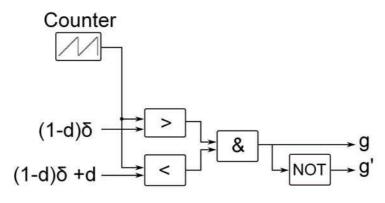

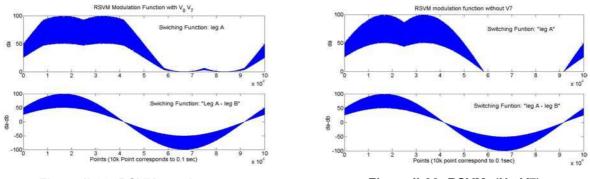

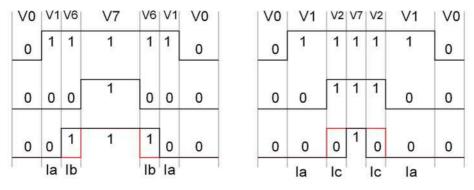

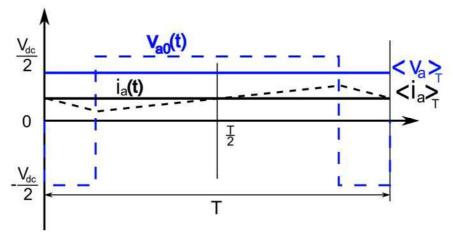

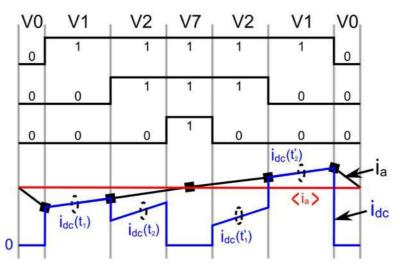

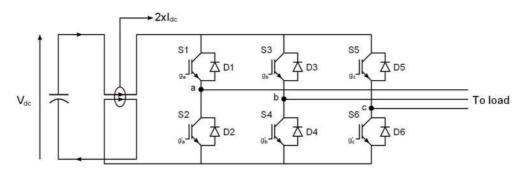

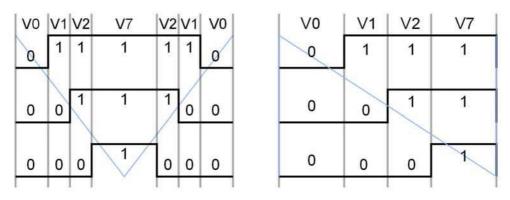

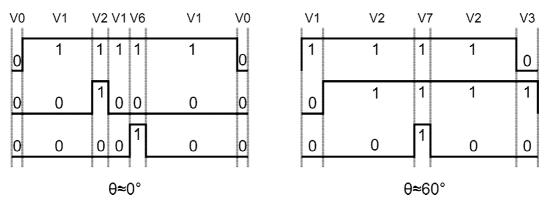

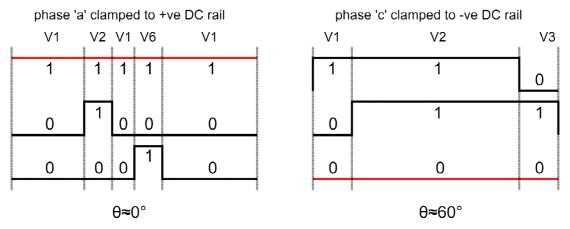

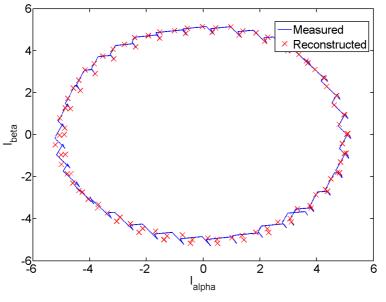

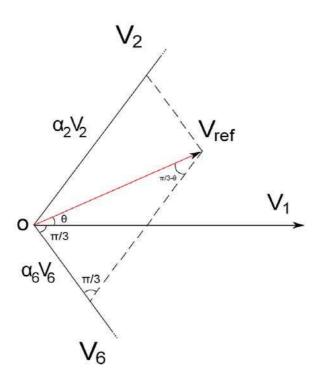

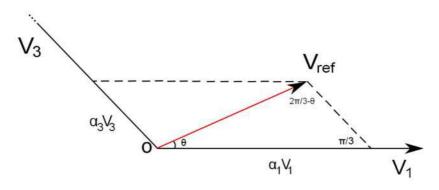

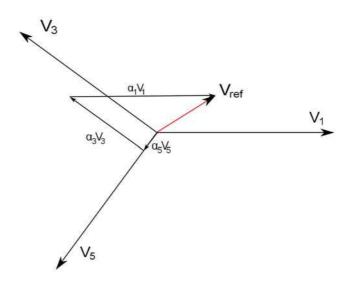

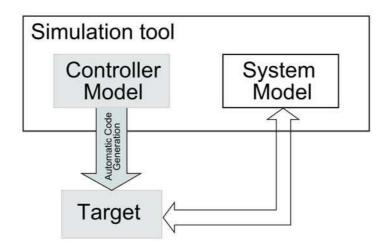

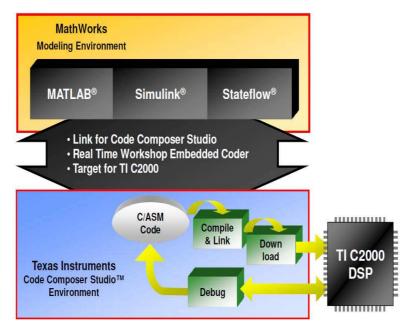

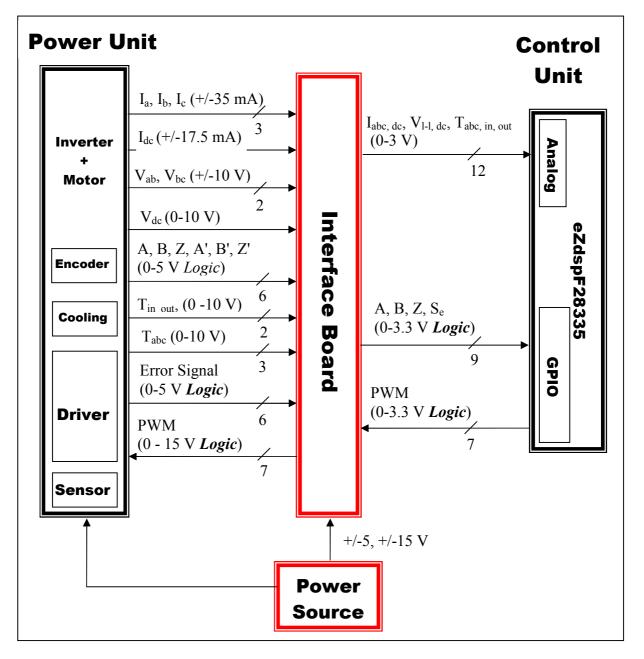

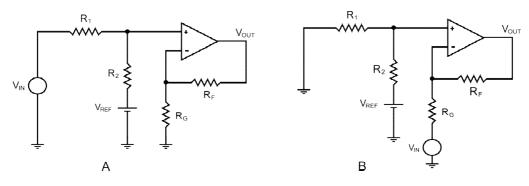

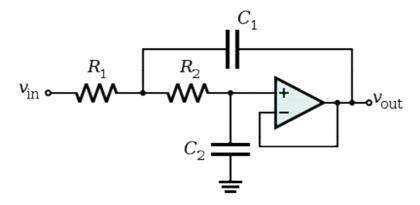

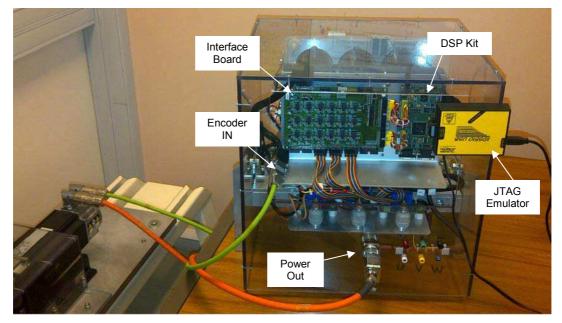

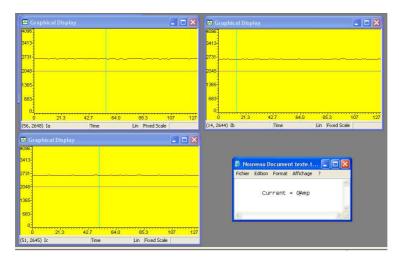

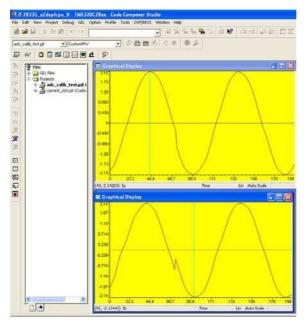

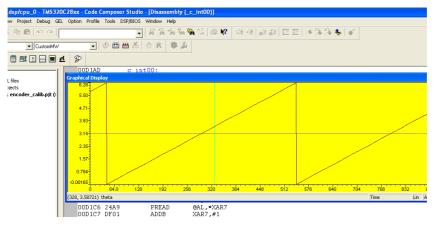

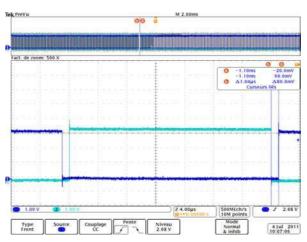

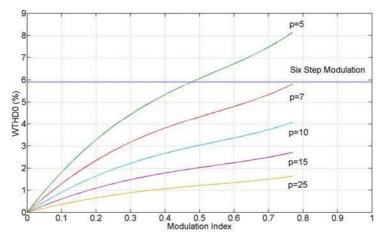

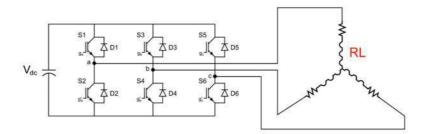

Figure I-15: DPWM3, mi=0.907