# Applications des technologies mémoires MRAM appliquées aux processeurs embarqués

Luís Vitório Cargnini

## ▶ To cite this version:

Luís Vitório Cargnini. Applications des technologies mémoires MRAM appliquées aux processeurs embarqués. Micro et nanotechnologies/Microélectronique. Université Montpellier II - Sciences et Techniques du Languedoc, 2013. Français. NNT: 2013MON20091. tel-01015187

## HAL Id: tel-01015187 https://theses.hal.science/tel-01015187

Submitted on 26 Jun 2014  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Délivré par UNIVERSITÉ MONTPELLIER 2

## Préparée au sein de l'école doctorale Information, Structures et Systèmes Et de l'unité de recherche LIRMIM

Spécialité : Systèmes Automatiques et Microélectronique

Présentée par Luís Vitório Cargnini

# Applications des technologies mémoires MRAM

Appliquées aux processeurs embarqués

#### Soutenue le 12/11/2013 devant le jury composé de

| Dr. Lionel TORRES         | Professeur, Université Montpellier 2                  | Directeur de Thèse |

|---------------------------|-------------------------------------------------------|--------------------|

| Dr. Gilles SASSATELLI     | Directeur de Recherche CNRS, LIRMM UMR CNRS 5506      | Co-Encadrant       |

| Dr. Guy Gogniat           | Professeur, Université Bretagne-Sud, Lorient          | Rapporteur         |

| Dr. Bertrand GRANADO      | Professeur, Université Pierre et Marie Curie, Paris   | Rapporteur         |

| Dr. Jacques-Olivier Klein | Professeur, Université Paris Sud 11, Paris            | Président          |

| Dr. Daniel Étiemble       | Professeur, Université Paris Sud 11, Paris            | Examinateur        |

| Dr. Guillaume Prenat      | Ingénieur-Docteur, CEA, Laboratoire SPINTEC, Grenoble | Examinateur        |

## Académie de Montpellier U n i v e r s i t é M o n t p e l l i e r II — Sciences et Techniques du Languedoc —

## Thèse

présentée au Laboratoire d'Informatique de Robotique et de Microélectronique de Montpellier pour obtenir le grade de

## Docteur de l'Université Montpellier II

| Discipline          | : | Génie Informatique, Automatique et Traitement du Signal |

|---------------------|---|---------------------------------------------------------|

| Formation Doctorale | : | Systèmes Automatiques et Microélectronique              |

| École Doctorale     | : | Information, Structures et Systèmes                     |

## MRAM APPLIED TO EMBEDDED PROCESSORS ARCHITECTURE AND MEMORY HIERARCHY

NON-VOLATILE MEMORY MRAM INTO THE MEMORY HIERARCHY

par

## Luís Vitório Cargnini

#### Jury composé de :

| Lionel Torres         | Professeur, Université Montpellier II/CNRS, Montpellier, France                          | Directeur de thèse |

|-----------------------|------------------------------------------------------------------------------------------|--------------------|

| Gilles Sassatelli     | Directeur de recherche/CNRS, Montpellier, France                                         | Co-encadrant       |

| Guy Gogniat           | Professeur, Université de Bretagne Sud, Lorient, France                                  | Rapporteur         |

| Bertrand Granado      | Professeur, Université Pierre et Marie Curie, Paris, France                              | Rapporteur         |

| Jacques-Olivier Klein | Professeur, Institut d'Électronique Fondamentale, Université Paris Sud 11, Paris, France | Président          |

| Daniel Étiemble       | Professeur, Lab. de Recherche en Informatique, Université Paris Sud 11, Paris, France    | Examinateur        |

| Guillaume Prenat      | Ingenieur, CEA Spintec, Grenoble, France                                                 | Examinateur        |

|                       |                                                                                          |                    |

#### luís vitório cargnini

#### MRAM APPLIED TO EMBEDDED PROCESSORS ARCHITECTURE AND MEMORY HIERARCHY

## MRAM APPLIED TO EMBEDDED PROCESSORS ARCHITECTURE AND MEMORY HIERARCHY

LUÍS VITÓRIO CARGNINI

Non-volatile Memory MRAM into the memory hierarchy

Ph.D. I2S

LIRMM – Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier Université de Montpellier 2

November 12, 2013 – version 7.3

Luís Vitório Cargnini: *MRAM applied to Embedded Processors architecture and Memory Hierarchy*, Non-volatile Memory MRAM into the memory hierarchy, Ph.D., ©, November 12, 2013

SUPERVISORS: Lionel Torres Gilles Sassatelli

LOCATION & TIME FRAME: Montpellier,France, November 12, 2013 To my wife, that endured, my years of Ph.D., my absences. I was lucky to have found you at our *Alma Mater* ! Thanks for all the trust, help and support you give me everyday, we finally can go home ! To my thesis baby: now, dad have time to play !

New ideas pass through three periods: 1) It can't be done. 2) It probably can be done, but it's not worth doing. 3) I knew it was a good idea all along! Arthur C. Clarke

*Ohana* means family. Family means nobody gets left behind, or forgotten.

— Lilo & Stitch

*Ad Verum Ducit* — Pontifícia Universidade Católica do Rio Grande do Sul (PUCRS) motto.

#### ABSTRACT

The Semiconductors Industry with the advent of submicronic manufacturing flows below 45nm began to face new challenges to keep evolving according with the Moore's Law. Regarding the widespread adoption of embedded systems one major constraint became power consumption of Integrated Circuit (IC). Also, memory technologies like the current standard of integrated memory technology for memory hierarchy, the SRAM, or the FLASH for non-volatile storage have extreme intricate constraints to be able to yield memory arrays at technological nodes below 45nm. One important is up until now Non-Volatile Memory weren't adopted into the memory hierarchy, due to its density and like flash the necessity of multi-voltage operation.

This thesis has the objective to work into these constraints and provide some answers. Into the thesis will be presented methods and results extracted from this methods to corroborate our goal of delineate a roadmap to adopt a new memory technology, non-volatile, low-power, low-leakage, SEU/MEU-resistant, scalable and with similar performance as the current SRAM, physically equivalent to SRAM, or even better with a area density between 4 to 8 times the area of a SRAM cell, without the necessity of multi-voltage domain like FLASH. This memory is the MRAM (Magnetic Memory), according with the ITRS one candidate to replace SRAM in the near future. MRAM instead of storing charge, they store the magnetic orientation provided by the spin-torque orientation of the free-layer alloy in the Magnetic Tunnel Junction (MTJ). Spin is a quantical state of matter, that in some metallic materials can have the orientation or its torque switched applying a polarized current in the sense of the desired field orientation.

Once the magnetic field orientation is set, using a sense amplifier, and a current flow through the MTJ, the memory cell element of MRAM, it is possible to measure the orientation given the resistance variation, higher the resistance lower the passing current, the sense will identify a logic zero, lower the resistance the SA will sense a one logic. So the information is not a charge stored, instead it is a magnetic field orientation, reason why it is not affected by SEU or MEU caused due to high energy particles. Also it is not due to voltages variations to change the memory cell content, trapping charges in a floating gate.

Regarding the MRAM, this thesis has by objective address the following aspects: MRAM applied to memory Hierarchy:

- By describing the current state of the art in MRAM design and use into memory hierarchy;

- by providing an overview of a mechanism to mitigate the latency of writing into MRAM at the cache level (Principle to composite memory bank);

- By analyzing power characteristics of a system based on MRAM on CACHE L1 and L2, using a dedicated evaluation flow

- by proposing a methodology to infer a system power consumption, and performance.

- and for last based into the memory banks analyzing a Composite Memory Bank, a simple description on how to generate a memory bank, with some compromise in power, but equivalent latency to the SRAM, that keeps similar performance.

#### PUBLICATIONS

Some ideas and figures have appeared previously in the following publications:

#### BOOK CHAPTERS

Weisheng Zhao, Lionel Torres, Luís Vitório Cargnini, Raphael Martins Brum, Yue Zhang, Yoann Guillemenet, Gilles Sassatelli, Yahya Lakys, Jacques-Olivier Klein, Daniel Etiemble, Dafiné Ravelosona, Claude Chappert, "High Performance SoC Design Using Magnetic Logic and Memory", VLSI-SoC: Advanced Research for Systems on Chip, IFIP Advances in Information and Communication Technology, Volume 379, 2012, pp 10-33, DOI: 10.1007/978-3-642-32770-4\_2, Print ISBN 978-3-642-32769-8, Online ISBN 978-3-642-32770-4, ISSN 1868-4238, Springer Berlin Heidelberg, http://link.springer.com/ chapter/10.1007%2F978-3-642-32770-4\_2

#### INTERNATIONAL CONFERENCES

Torres, L.; Brum, R.M.; Cargnini, L.V.; Sassatelli, G., "Trends on the application of emerging nonvolatile memory to processors and programmable devices," Circuits and Systems (ISCAS), 2013 IEEE International Symposium on , vol., no., pp.101,104, 19-23 May 2013, doi: 10.1109/ISCAS.2013.6571792, http://ieeexplore.ieee.org/stamp/stamp.jsp? tp=&arnumber=6571792&isnumber=6571764

Torres, L.; Brum, R.M.; Guillemenet, Y.; Sassatelli, G.; Cargnini, L.V., "Evaluation of hybrid MRAM/CMOS cells for reconfigurable computing," New Circuits and Systems Conference (NEWCAS), 2013 IEEE 11th International , vol., no., pp.1,6, 16-19 June 2013, doi: 10.1109/NEWCAS.2013.6573676, http://ieeexplore.ieee.org/stamp/stamp.jsp? tp=&arnumber=6573676&isnumber=657361

Cargnini, Luis Vitorio; Torres, Lionel; Brum, Raphael Martins; Senni, Sophiane; Sassatelli, Gilles, "Embedded memory hierarchy exploration based on magnetic RAM," Faible Tension Faible Consommation (FTFC), 2013 IEEE, vol., no., pp.1,4, 20-21 June 2013, doi: 10.1109/FTFC.2013.6577780, http://ieeexplore.ieee.org/stamp/stamp.jsp? tp=&arnumber=6577780&isnumber=6577746

Weisheng Zhao, Lionel Torres, Yoann Guillemenet, Luís Vitório Cargnini, Yahya Lakys, Jacques-Olivier Klein, Dafine Ravelosona, Gilles Sassatelli, and Claude Chappert. 2011. Design of MRAM based logic circuits and its applications. In Proceedings of the 21st edition of the great lakes symposium on Great lakes symposium on VLSI (GLSVLSI'11). ACM, New York, NY, USA, 431-436., DOI: 10.1145/1973009.1973104, http://doi.acm.org/10.1145/1973009.1973104

Zhao, W.S.; Zhang, Y.; Lakys, Y.; Klein, J-O; Etiemble, D.; Revelosona, D.; Chappert, C.; Torres, L.; Cargnini, L.V.; Brum, R. M.; Guillemenet, Y.; Sassatelli, G., "Embedded MRAM for high-speed computing," VLSI and System-on-Chip (VLSI-SoC), 2011 IEEE/I-FIP 19th International Conference on , vol., no., pp.37,42, 3-5 Oct. 2011, doi: 10.1109/VL-SISoC.2011.6081627, http://dx.doi.org/10.1109/VLSISoC.2011.6081627 Barthe, L.; Cargnini, L.V.; Benoit, P.; Torres, L., "The SecretBlaze: A Configurable and Cost-Effective Open-Source Soft-Core Processor," Parallel and Distributed Processing Workshops and Phd Forum (IPDPSW), 2011 IEEE International Symposium on , vol., no., pp.310,313, 16-20 May 2011, doi: 10.1109/IPDPS.2011.154, http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=6008911&isnumber=6008799

Barthe, L.; Cargnini, L.V.; Benoit, P.; Torres, L., "Optimizing an Open-Source Processor for FPGAs: A Case Study," Field Programmable Logic and Applications (FPL), 2011 International Conference on , vol., no., pp.551,556, 5-7 Sept. 2011, doi: 10.1109/FPL.2011.107, http://dx.doi.org/10.1109/FPL.2011.107 – Nominated the 6th best papers of FPL 2011 –

Cargnini, L.V.; Guillemenet, Y.; Torres, L.; Sassatelli, G., "Improving the Reliability of a FPGA Using Fault-Tolerance Mechanism Based on Magnetic Memory (MRAM)," Reconfigurable Computing and FPGAs (ReConFig), 2010 International Conference on , vol., no., pp.150,155, 13-15 Dec. 2010, doi: 10.1109/ReConFig.2010.10, http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5695297&isnumber=5695271

#### NATIONAL CONFERENCES

Luis Vitorio Cargnini, Raphael Martins Brum, Gilles Sassatelli, Lionel Torres, "Exploration of MRAM cache memory for embedded processors", GDR SoC-SiP, 2012, June 13-15, Paris, France

Luís Vitório Cargnini, Raphael Brum, Yoann Guillemenet, Lionel Torres, Gilles Sassatelli, "Improving the Reliability of a FPGA using Fault-Tolerance Mechanism Based on Magnetic Memory (MRAM)", GDR SoC-SiP, 2011, June 15-17, Lyon, France

#### ACKNOWLEDGMENTS

The limits of the possible can only be defined by going beyond them into the Impossible. — Arthur C. Clarke

To my advisor Professor Dr. Lionel Torres, who have gave me the chance and opportunity to work in a fascinating field as MRAM. Thank you for your time and patience, to advise me all this years.

To my co-advisor Dr. Gilles Sassatelli for his insights during my research about the best approaches to evaluate an architecture.

To the reviewers of my thesis Professor Dr. Guy Gogniat and Professor Dr. Bertrand Granado, for having the time to read my manuscript and for gently accept being part of my thesis committee.

To Professor Dr. Jacques-Olivier Klein, Professor Dr. Daniel Étiemble, and Dr. Guillaume Prenat to also accept being part of my thesis committee.

To my research network, which I worked and co-authored with them my many thanks for their insights to Jacques-Olivier Klein, Daniel Étiemble, Weisheng Zhao and Claude Chappert.

To professor Dr. Fernando Gehm Moraes (PUCRS), by his help providing me access to the Cadence Physical Synthesis and Characterization tools, so I could fulfill and enrich my research. Also, for all the help trough this years.

To Raphael Garibotti, for daily opportunity on debating, discussing, exchanging ideas regarding both researches. Also, for the help on how to conduct the Integrated Circuit experiments, aggregating ideas to my research.

To Raphael Brum, for all the help during this last years at LIRMM writing a paper with tight dead-lines or discussing about the MTJ technology base in our researches.

To Marcelo Mandelli, to have saved me in the last minute when I needed a Mac to finish one the images of my thesis.

To Agence Nationale de Recherche (ANR) through SPIN, MARS and European Union (MODERN) for funding my research.

To Lorival Regis, who promptly and efficiently provided me all the technical resources that allowed me to conduct my research.

To Cécile Lukasik , for always so kindly help and solve the administrative related issues.

To God, that gave me strength, wisdom and perseverance all this years to conclude my Ph.D..

## CONTENTS

| i  | INTR | ODUCI | FION                                                            | 1  |

|----|------|-------|-----------------------------------------------------------------|----|

| 1  | INTI | RODUC | CTION                                                           | 3  |

| ii | STAT | EOFI  | THE ART, DRAFTED METHODOLOGIES AND MATERIALS                    | 9  |

| 2  | CUR  | RENT  | STATE OF MEMORY TECHNOLOGY                                      | 11 |

|    | 2.1  | Mem   | ory Taxonomy                                                    | 17 |

|    | 2.2  |       | ory Devices                                                     | 19 |

|    |      | 2.2.1 |                                                                 | 19 |

|    |      |       | 2.2.1.1 Ferroelectric FET                                       | 19 |

|    |      |       | 2.2.1.2 Ferroelectric Polarization ReRAM                        | 19 |

|    |      | 2.2.2 | Nanoelectromechanical memory (NEMM)                             | 20 |

|    |      | 2.2.3 |                                                                 | 20 |

|    |      | 2.2.4 | Mott Memory                                                     | 21 |

|    |      | 2.2.5 | Macromolecular Memory                                           | 22 |

|    |      | 2.2.6 | Molecular Memory                                                | 22 |

|    |      |       | 2.2.6.1 Vertical Transistors                                    | 23 |

|    |      |       | 2.2.6.2 Two-terminal select devices (resistance-based memories) | 24 |

|    |      |       | 2.2.6.3 Diode-type select devices                               | 24 |

|    |      | 2.2.7 | Resistive-Switch-type select devices                            | 25 |

|    |      |       | 2.2.7.1 MIT switch                                              | 25 |

|    |      |       | 2.2.7.2 Threshold switch                                        | 25 |

|    |      |       | 2.2.7.3 MIEC switch                                             | 25 |

|    |      |       | 2.2.7.4 2 Terminal Switches                                     | 26 |

|    | 2.3  | Magr  | netic Tunneling Junction (MTJ)                                  | 27 |

|    |      | 2.3.1 | Tunnel Magnetoresistance (TMR)                                  | 29 |

|    |      | 2.3.2 | Field Induced Magnetic Switching (FIMS) MRAMs                   | 29 |

|    |      | 2.3.3 |                                                                 | 32 |

|    |      | 2.3.4 |                                                                 | 32 |

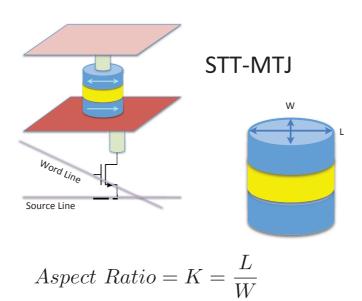

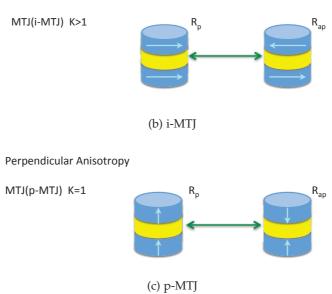

|    |      | 2.3.5 | STT based Magnetic Tunnel Junction (STT-MTJ)                    | 33 |

|    |      | 2.3.6 | Planar and Perpendicular STT                                    | 33 |

|    | 2.4  |       | ent state compared to the memory state of the art               | 36 |

|    | 2.5  |       | puter Architecture and Memory Hierarchy                         |    |

|    | -    | 2.5.1 | Working Principles of the Memory Hierarchy                      | 38 |

|    | 2.6  |       | HE Memories                                                     | 40 |

|    |      | 2.6.1 | Larger block size to reduce MISS rate                           | 41 |

|    |      | 2.6.2 | Bigger caches to reduce MISS rate                               | 41 |

|    |      | 2.6.3 | Higher associativity to reduce MISS rate                        | 41 |

|    |      | 2.6.4 | Multilevel caches to reduce MISS penalty                        | 41 |

|    |      | 2.6.5 |                                                                 | 41 |

|    |      | 2.6.6 | Avoiding address translation during indexing of the cache to    |    |

|    | a –  |       | reduce HIT time                                                 | 42 |

|    | 2.7  | MKA   | M applied into Memory Hierarchy                                 | 42 |

| iii | ANA | LYTICA  | L METHODOLOGY FLOW                                            | 47  |

|-----|-----|---------|---------------------------------------------------------------|-----|

| 3   | ANA | LYTICA  | L METHODOLOGY FLOW                                            | 49  |

|     | 3.1 | CACT    | I: Integrated Memory Simulator                                | 49  |

|     |     | 3.1.1   | CACTI background                                              | 50  |

|     |     | 3.1.2   | CACTI Thesaurus                                               | 51  |

|     |     | 3.1.3   | NUCA Modeling                                                 | 52  |

|     | 3.2 | NVSin   | 1                                                             | 52  |

|     |     | 3.2.1   | NVSim Non-Volatile Memory (NVM) Physical Mechanisms and       |     |

|     |     |         | Write Operations                                              | 53  |

|     |     | 3.2.2   | NAND Flash                                                    | 53  |

|     |     | 3.2.3   | STT-RAM                                                       | 53  |

|     |     | 3.2.4   | PCRAM                                                         | 53  |

|     |     | 3.2.5   | ReRAM                                                         | 54  |

|     |     | 3.2.6   | Charge Pump                                                   | 54  |

|     |     | 3.2.7   | Write Endurance Issue                                         | 54  |

|     |     | 3.2.8   | Retention Time Issue                                          | 55  |

|     |     | 3.2.9   | MOS-Accessed Structure Versus Cross-Point Structure           | 55  |

|     | 3.3 | Compa   | arison of NVSim to CACTI                                      | 55  |

|     | 3.4 | Reliabi | ility of the methodology base-line models                     | 56  |

|     | 3.5 | Metho   | dology to Evaluate the Intrinsic aspects of MRAM compared to  |     |

|     |     | SRAM    | memories                                                      | 57  |

|     |     | 3.5.1   | Memory models used in NVSim for analyses                      | 58  |

|     |     | 3.5.2   | Intrinsic Analyses                                            | 58  |

|     |     | 3.5.3   | Intrinsic Analyses - Results                                  | 62  |

|     |     | 3       | 3.5.3.1 Memory banks of 45nm                                  | 62  |

|     | 3.6 | Metho   | dology to Evaluate the aspects of MRAM into Memory Hierarchy  | 87  |

|     | 3.7 | Simple  | Scalar                                                        | 89  |

|     | 3.8 | Gem5    |                                                               | 90  |

|     |     | 3.8.1   | Simulation Capabilities                                       | 90  |

|     |     | 3.8.2   | ISAs                                                          | 90  |

|     |     | 3.8.3   | Execution Modes                                               | 90  |

|     |     | 3.8.4   | CPU Models                                                    | 90  |

|     |     | 3.8.5   | Interconnection Networks                                      | 91  |

|     |     | 3.8.6   | Devices                                                       | 91  |

|     |     |         |                                                               |     |

| iv  | ANA | LYSES ( | OF EMBEDDED MEMORY HIERARCHY                                  | 93  |

| 4   | ANA |         | OF EMBEDDED MEMORY HIERARCHY                                  | 95  |

|     | 4.1 | Embed   | Ided MRAM for Processor Applications                          | 96  |

|     |     | 4.1.1   | MRAM applications for the processor memory hierarchy          | 96  |

|     |     | 4.1.2   | In-Depth Analysis: Case Study CJPEG                           | 98  |

|     | 4.2 | 0       | Gem5 to evaluate the implications into memory hierarchy of L2 |     |

|     |     | CACH    | E banks of significant sizes from 2GB down to 256KB           | 102 |

|     |     | 4.2.1   | Recalibrating the Gem5 using the NVSim bank details           | 106 |

|     |     | 4.2.2   | Power Analysis based into the memory banks generated after    |     |

|     |     |         | the NVSim.                                                    | 114 |

|     | 4.3 | Benchr  | marks used for evaluations                                    | 115 |

|    | 4.4                | Comparing a Microprocessor memory hierarchy, synthesized with MRAM            |            |

|----|--------------------|-------------------------------------------------------------------------------|------------|

|    |                    | and SRAM at 28nm                                                              |            |

|    |                    | 4.4.1 OpenRISC Architecture                                                   |            |

|    |                    | 4.4.1.1 Memory Model                                                          |            |

|    |                    | 4.4.1.2 Memory Synchronize Instruction                                        | 121        |

|    |                    | 4.4.1.3 Memory Management                                                     |            |

|    |                    | 4.4.2 MRAM Characterization using Liberty                                     | 122        |

|    |                    | 4.4.3 Synthesis Results                                                       | 123        |

|    |                    | 4.4.4 MRAM and Static Random Access Memory (SRAM) synthesis                   |            |

|    |                    | results                                                                       | 124        |

|    |                    | 4.4.5 Assessments comparing the synthesis results of the two technol-<br>gies | 125        |

|    | 4.5                | The Composite Bank                                                            |            |

|    | т.)                | 4.5.1 Composite Memory banks of 45nm                                          |            |

|    |                    | +                                                                             | /          |

| V  | CON                | CLUSIONS & FUTURE INSIGHTS                                                    | 149        |

| 5  | CON                | CLUSIONS & FUTURE INSIGHTS                                                    | 151        |

|    |                    |                                                                               |            |

| vi | APP                | ENDIX                                                                         | 155        |

| Α  |                    | M TERMINOLOGY                                                                 | 157        |

|    | A.1                | Anisotropy                                                                    |            |

|    | A.2                | Magnetic anisotropy                                                           |            |

|    | A.3                | Superparamagnetism                                                            | -          |

|    | A.4                | Magnetic Permeability                                                         |            |

|    | A.5                | Isotropy                                                                      | -          |

|    | А.б                | Magnetic moment                                                               | 159        |

|    | A.7                | Magnetic moment and angular momentum                                          |            |

|    | A.8                | Exchange bias                                                                 |            |

|    | A.9                | Antiferromagnetism                                                            |            |

|    |                    | A.9.1 Measurement                                                             |            |

|    |                    | A.9.2Antiferromagnetic materials                                              |            |

| -  |                    |                                                                               |            |

| В  |                    | ROVING THE RELIABILITY OF A FPGA USING FAULT-TOLERANCE MECH-                  |            |

|    | B.1                | SM BASED ON MRAM<br>Reliability                                               | 163<br>164 |

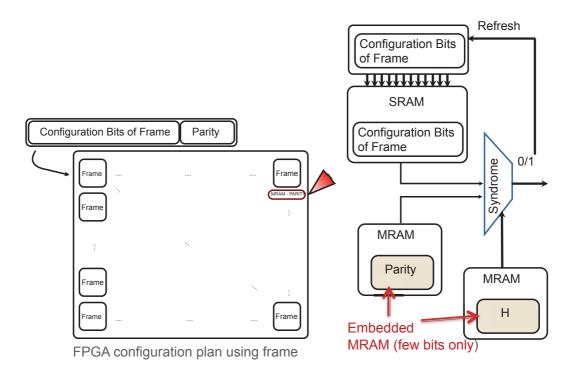

|    | в.1<br>В.2         | Mechanism to improve reliability regarding SEU events                         | 164        |

|    | в.2<br>В.3         | Scrubbing Mechanism - Refresh the configuration bits                          | 167        |

|    | в. <u>э</u><br>В.4 | General approach                                                              | 167        |

|    | в.5                | Error Detection Code                                                          | 169        |

|    | в.6                | Experimental Results                                                          |            |

|    | в.7                | Hamming results                                                               |            |

|    | в.8                | BCH Results                                                                   |            |

|    | в.9                | Assessments on MRAM applied to FPGA to improve reliability                    |            |

| С  | -                  | RINSIC ANALYSES - ADDITIONAL RESULTS                                          | 173        |

| D  |                    | TI ANALYTICAL MODELS - RELEVANT DETAILS                                       | 181        |

| 2  | D.1                | CACTI Analytical Models                                                       | 181        |

|    | D.2                | Wire Parasitics                                                               |            |

|    |                    |                                                                               |            |

|   | D.3  | Global Wires                          | 181         |

|---|------|---------------------------------------|-------------|

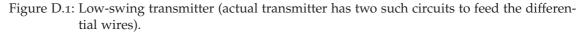

|   | D.4  | Low-swing Wires                       | 183         |

|   | D.5  | Transmitter                           | 183         |

|   | D.6  | Sense Amplifier                       | 184         |

| Е | INTR | INSIC ANALYSES - MEMORY BANKS OF 28nm | 185         |

| F | THE  | COMPOSITE BANK - ADDITIONAL RESULTS   | 205         |

|   | F.1  | LOP 45nm                              | 205         |

|   | F.2  | Composite Baank 28nm                  | 225         |

|   | F.3  | LOP 28nm                              | <b>2</b> 45 |

|   |      |                                       |             |

#### BIBLIOGRAPHY

#### LIST OF FIGURES

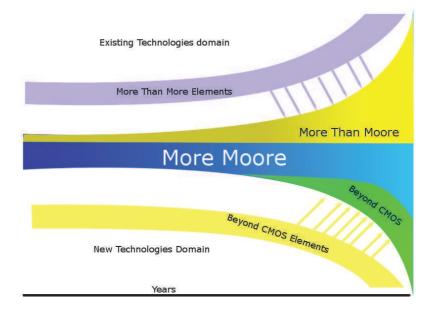

| Figure 1.1               | Relationship among More Moore, More-than-Moore, and Beyond CMOS [ITRS, 2012a]                                                                                                                                                                                                                                                                                                                                | 4        |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

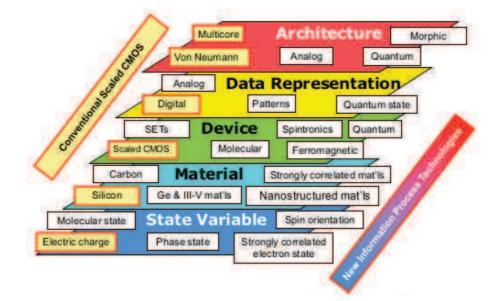

| Figure 1.2               | A Taxonomy for Emerging Research Information Processing De-<br>vices found in [ITRS, 2012a].                                                                                                                                                                                                                                                                                                                 |          |

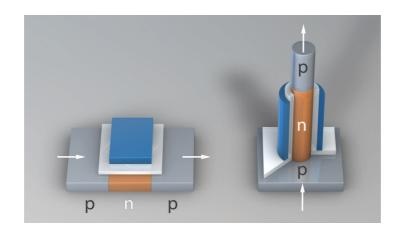

| Figure 2.1               | Physical difference between a vertical and a planar transistor, ex-                                                                                                                                                                                                                                                                                                                                          | 7        |

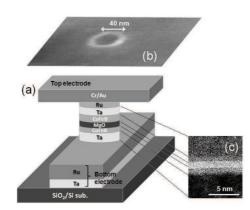

| Figure 2.2               | <ul><li>tracted from [Ou et al., 2010]</li></ul>                                                                                                                                                                                                                                                                                                                                                             | 23       |

|                          | (b) Planar MTJ, (c) Perpendicular MTJ                                                                                                                                                                                                                                                                                                                                                                        | 28       |

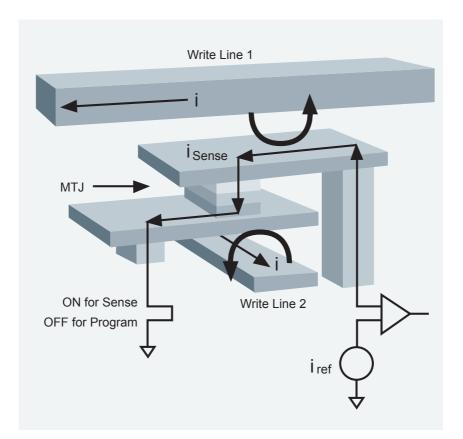

| Figure 2.3               | Schematic of a 1-transistor, 1-MTJ memory cell showing the write<br>lines above and below the bit and the read current path [Everspin<br>Technologies Inc., 2010]                                                                                                                                                                                                                                            | 30       |

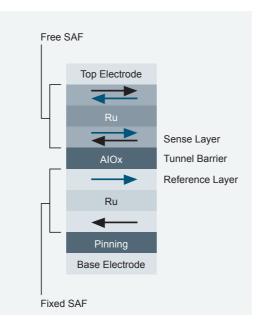

| Figure 2.4               | The magnetic tunnel junction (MTJ) material stack used for Tog-<br>gle MRAM. The Free SAF magnetic moments switch between two<br>states when the proper magnetic field sequence is applied. Elec-<br>trons tunnel across the alumina (AlOx) tunnel barrier, resulting<br>in a magnetoresistance that is sensitive to the magnetic moment<br>direction of the sense layer [Everspin Technologies Inc., 2010]. | 31       |

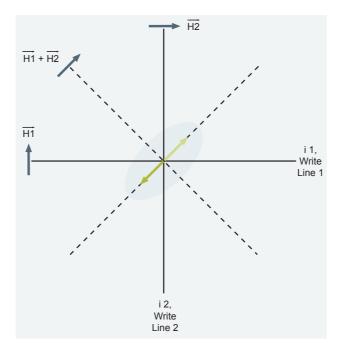

| Figure 2.5               | Schematic of a toggle Magnetic Random Access Memory (MRAM)<br>bit with the field sequence used to switch the free layer from one<br>state to the other. The fields, H1, H1+H2 and H2 are produced<br>by passing currents, i1 and i2, through the write lines [Everspin<br>Technologies Inc., 2010].                                                                                                          | 31       |

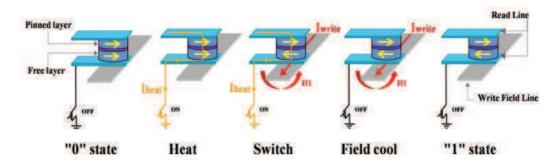

| Figure 2.6               | MTJ process to switch the electromagnetic thin-layer field and                                                                                                                                                                                                                                                                                                                                               | -        |

| <b>T</b> .               | store the logic value into the MTJ passing from the electrical layer.                                                                                                                                                                                                                                                                                                                                        | 32       |

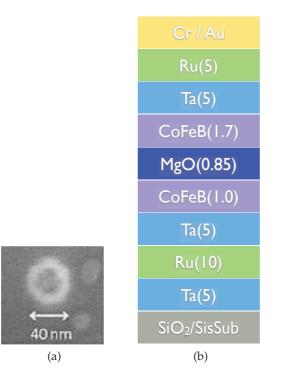

| Figure 2.7<br>Figure 2.8 | High performance perpendicular MTJ with $\phi$ 40nm Microprocessor Datapath [Hennessy and Patterson, 2007b; Patter-                                                                                                                                                                                                                                                                                          | 35       |

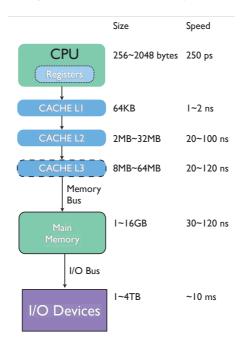

| Figure 2.9               | son and Hennessy, 2012]                                                                                                                                                                                                                                                                                                                                                                                      | 38<br>38 |

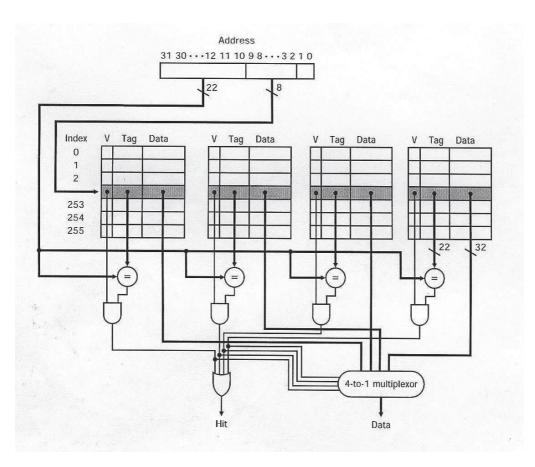

| Figure 2.10              | An example of a possible Set-Associative Cache Organization [Pat-                                                                                                                                                                                                                                                                                                                                            |          |

| Figure 2.11              | terson and Hennessy, 2012]                                                                                                                                                                                                                                                                                                                                                                                   | 39       |

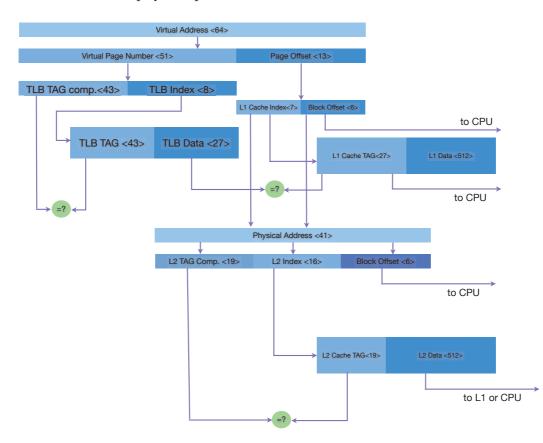

|                          | 2006]                                                                                                                                                                                                                                                                                                                                                                                                        | 42       |

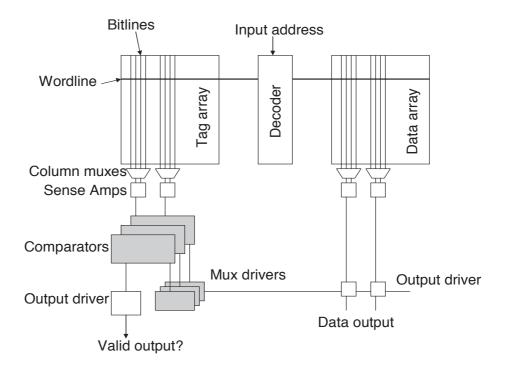

| Figure 3.1               | CACHE bank memory physical organization [Tarjan et al., 2006].                                                                                                                                                                                                                                                                                                                                               | 50       |

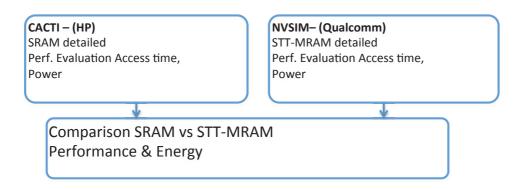

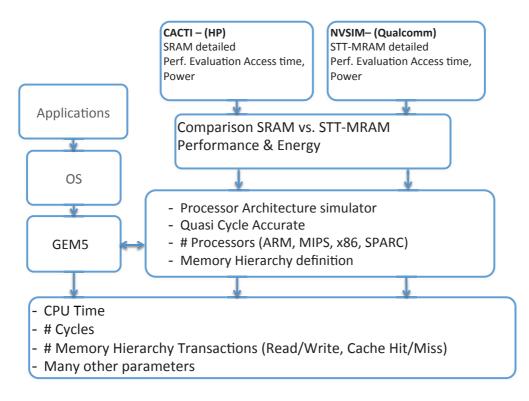

| Figure 3.2               | Evaluation Methodology depicted.                                                                                                                                                                                                                                                                                                                                                                             | 57       |

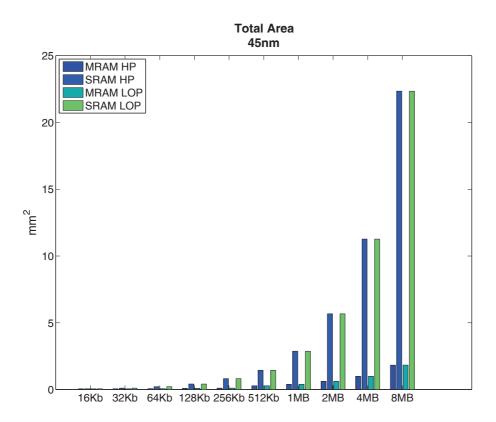

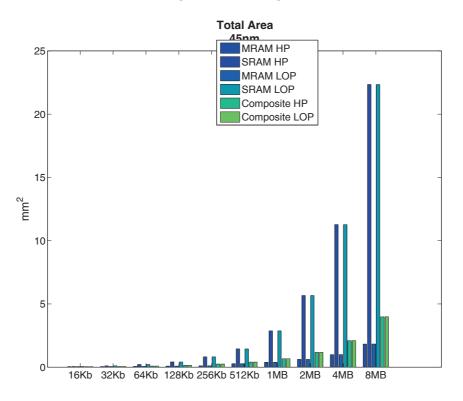

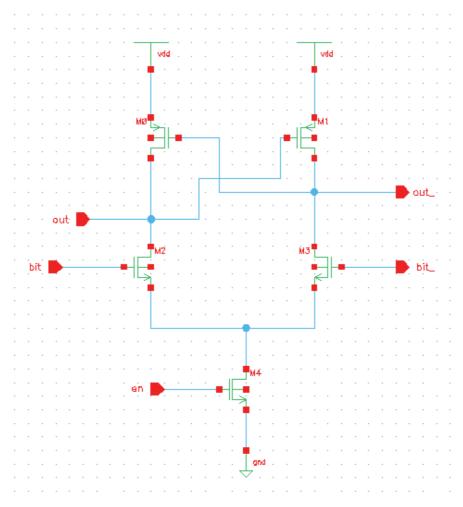

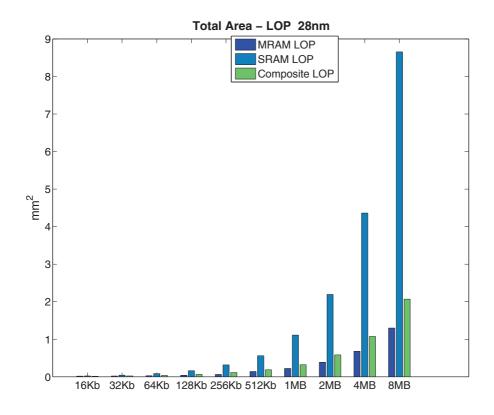

| Figure 3.3               | Total Area                                                                                                                                                                                                                                                                                                                                                                                                   | 67       |

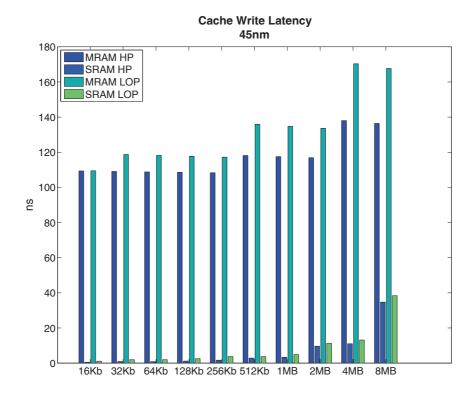

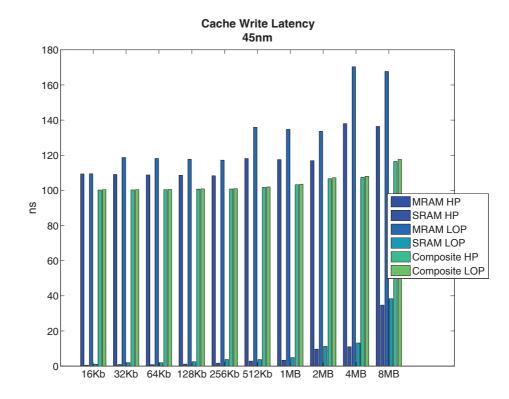

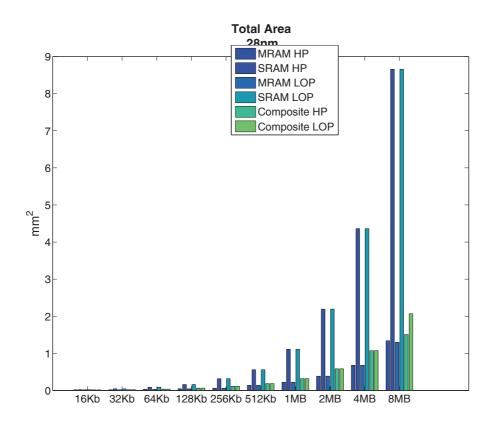

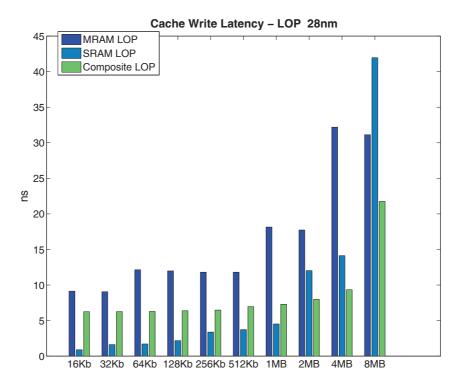

| Figure 3.4  | CACHE Total Write Latency.                                          | 68  |

|-------------|---------------------------------------------------------------------|-----|

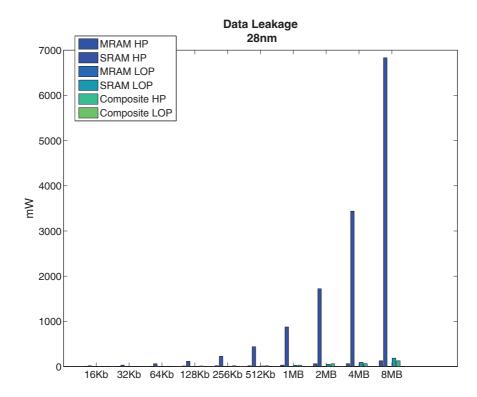

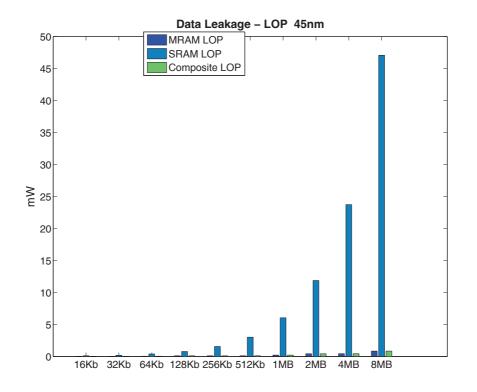

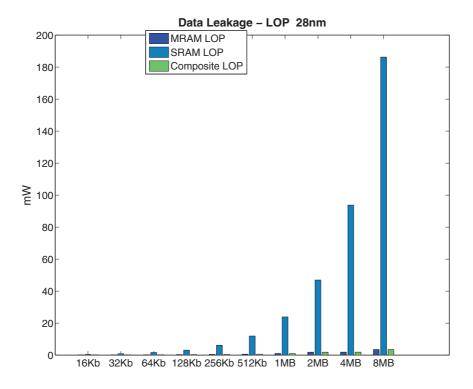

| Figure 3.5  | CACHE DATA Array Leakage Power                                      | 69  |

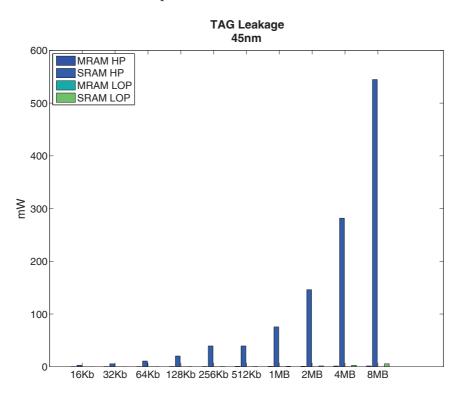

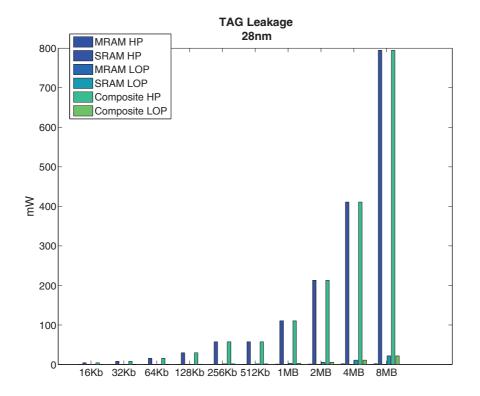

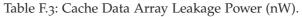

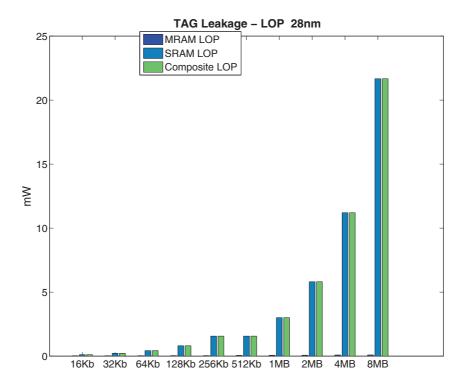

| Figure 3.6  | CACHE TAG Leakage Power.                                            | 70  |

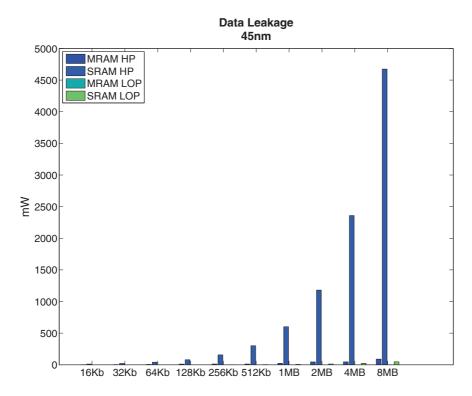

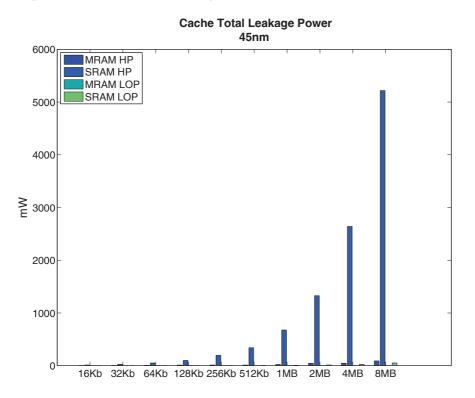

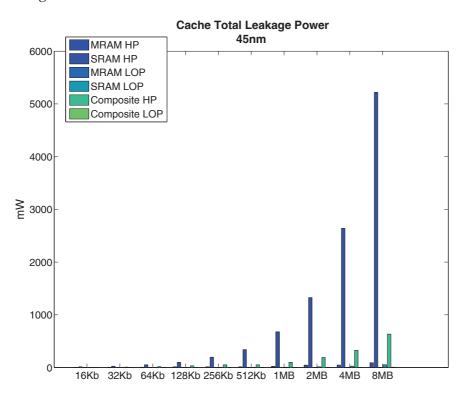

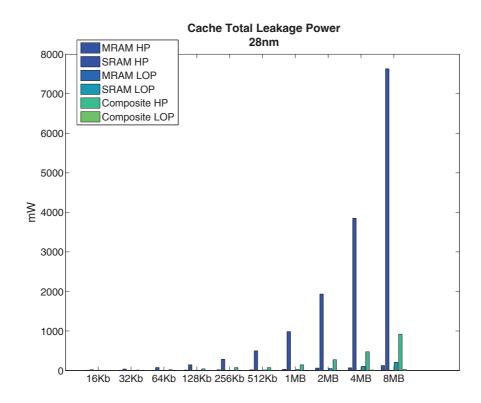

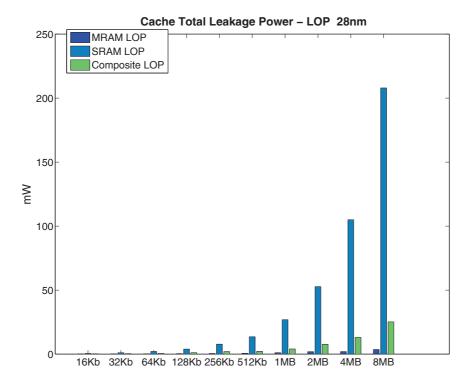

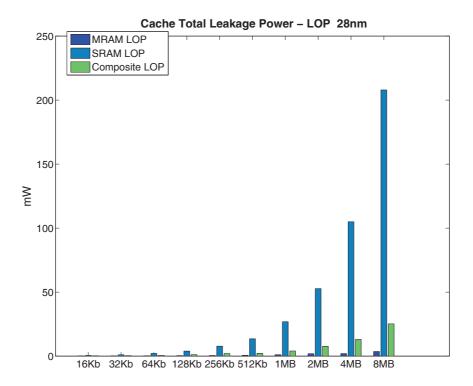

| Figure 3.7  | Leakage Power.                                                      | 71  |

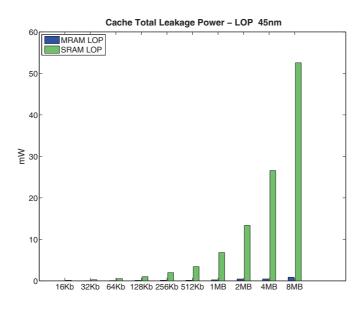

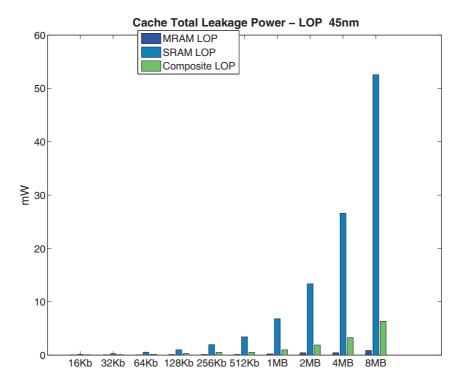

| Figure 3.8  | Low-Power (LOP) Total Leakage, observe only the Low Power           |     |

| 0           | Performance (LOP) banks observed in Figure 3.7.                     | 72  |

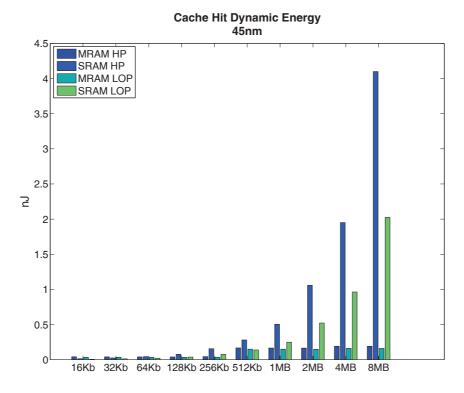

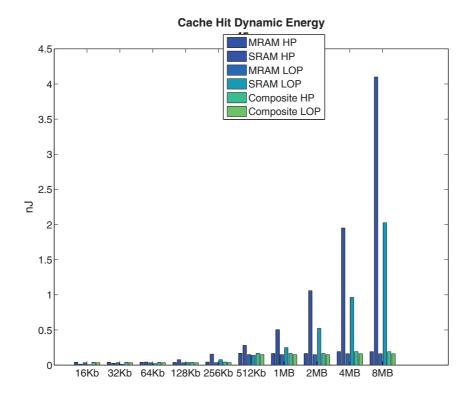

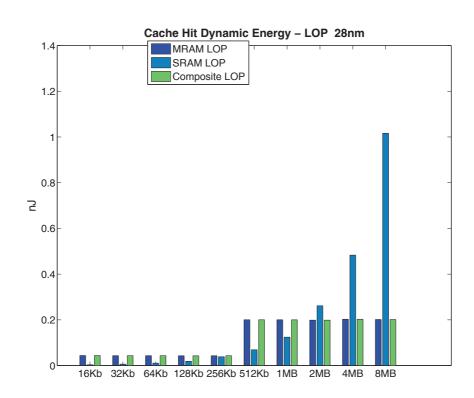

| Figure 3.9  | Hit Dynamic Energy.                                                 | 73  |

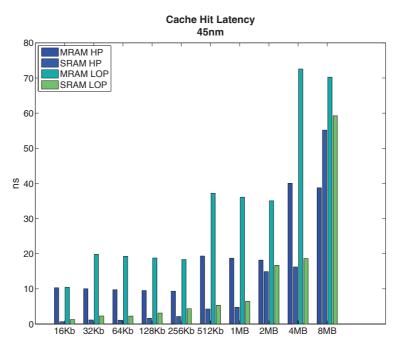

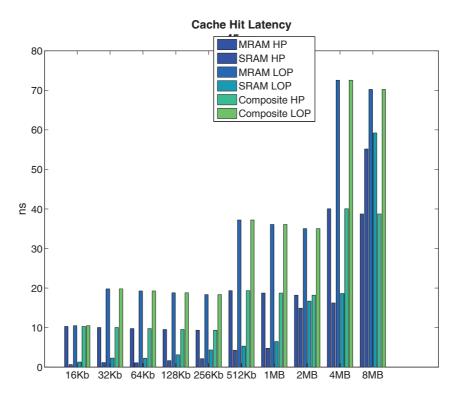

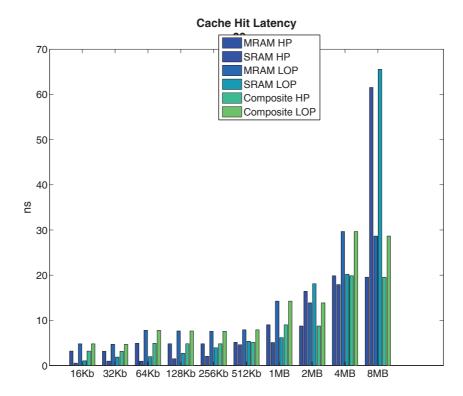

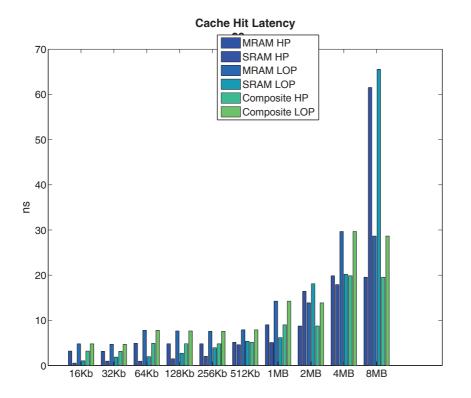

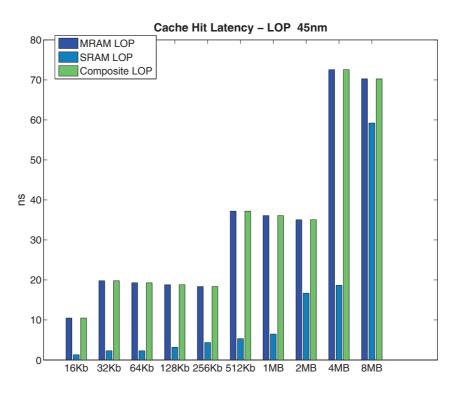

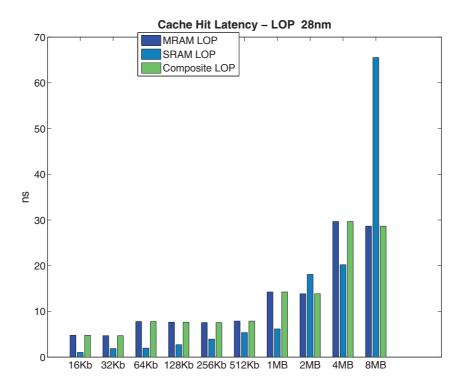

| Figure 3.10 | Hit Latency.                                                        | 74  |

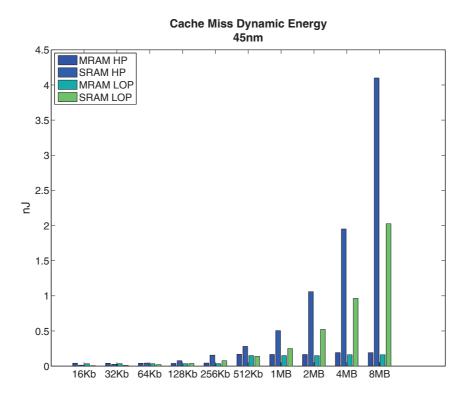

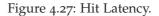

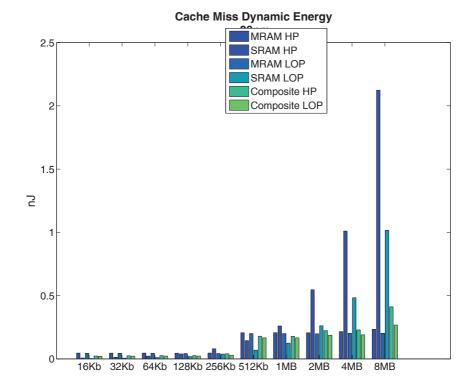

| Figure 3.11 | Miss Dynamic Energy.                                                | 75  |

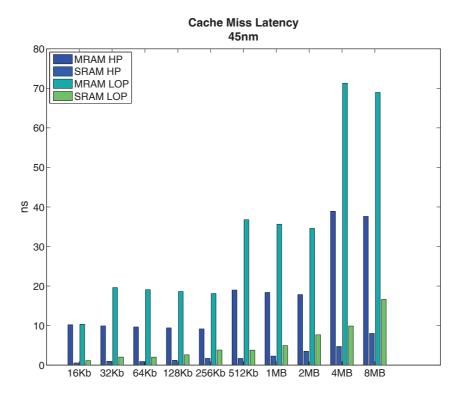

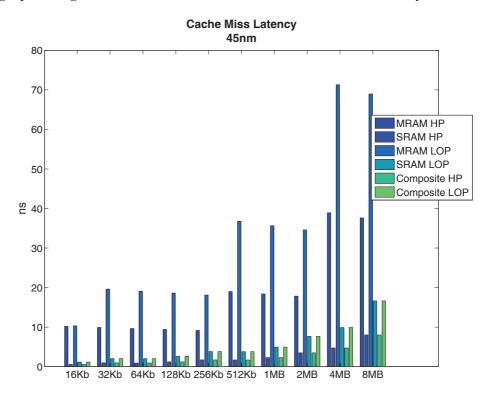

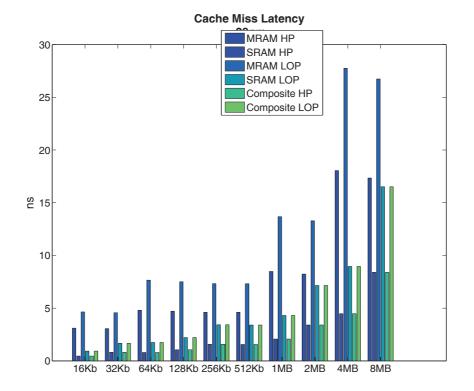

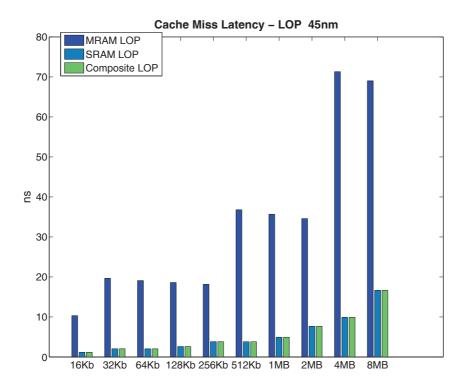

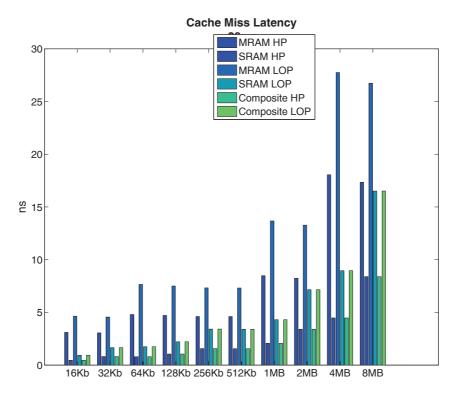

| Figure 3.12 | Miss Latency.                                                       | 76  |

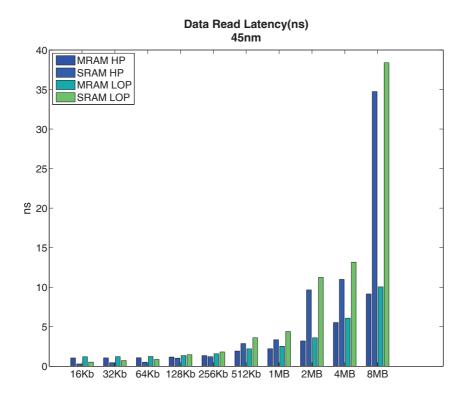

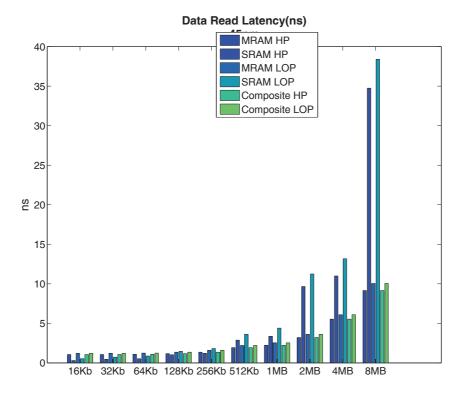

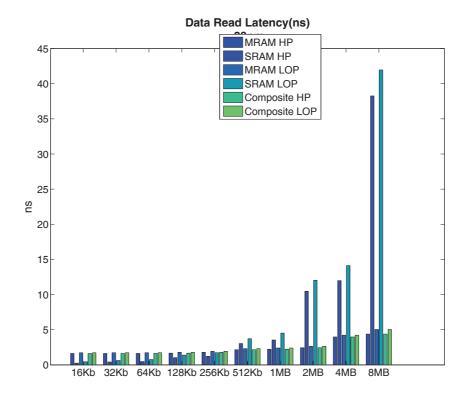

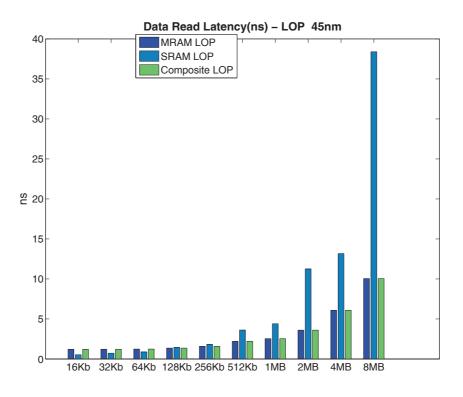

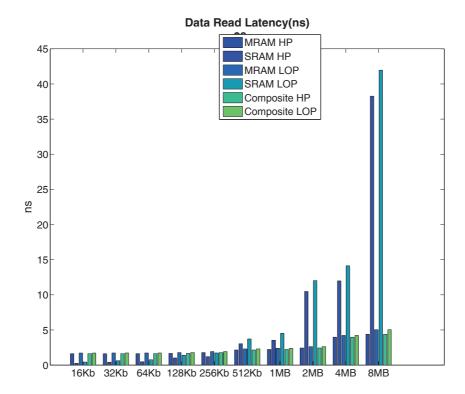

| Figure 3.13 | Data Read Latency.                                                  | 77  |

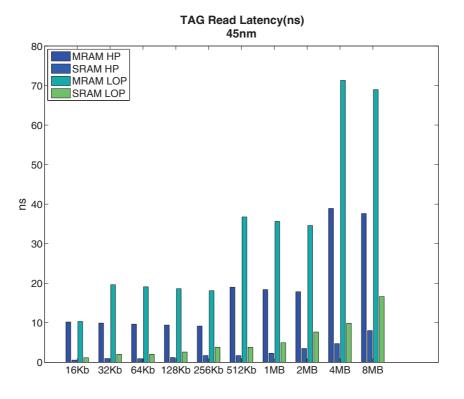

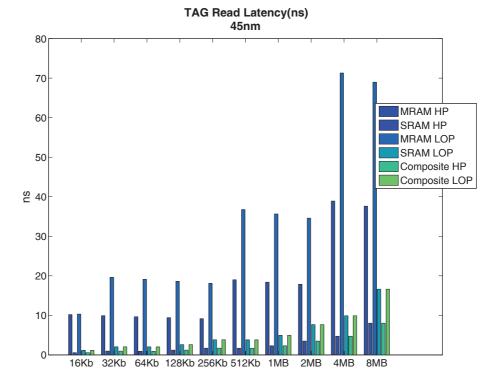

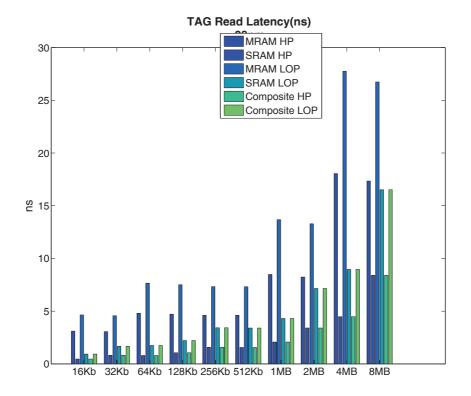

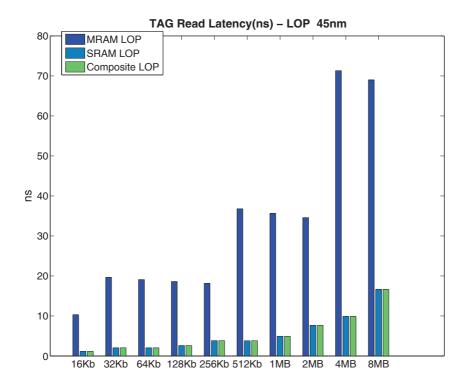

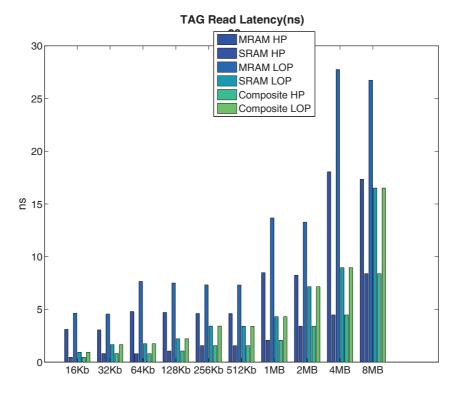

| Figure 3.14 | TAG Read Latency.                                                   | 78  |

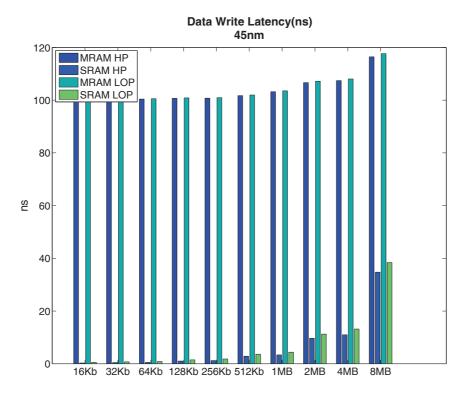

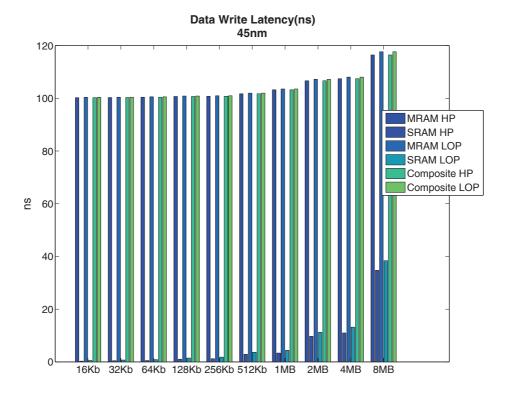

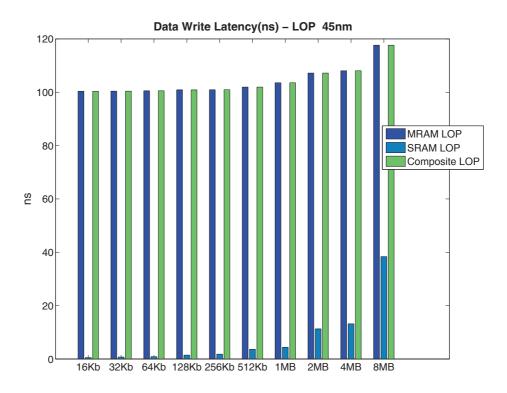

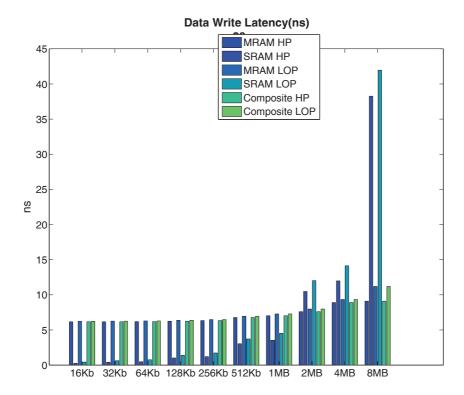

| Figure 3.15 | DATA Write Latency.                                                 | 79  |

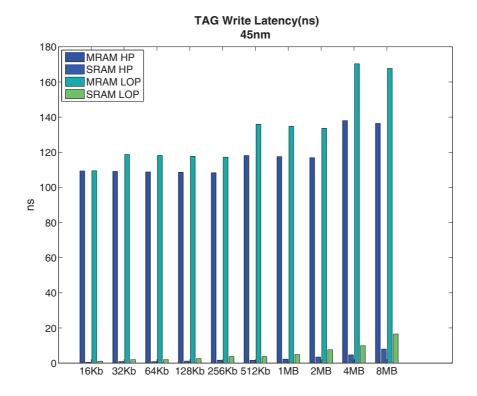

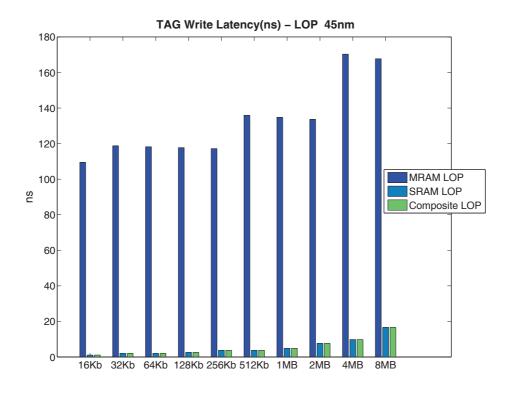

| Figure 3.16 | TAG Write Latency.                                                  | 80  |

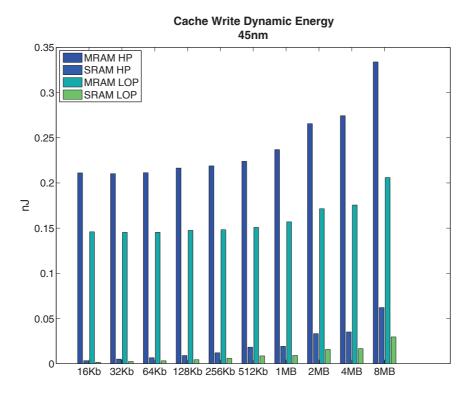

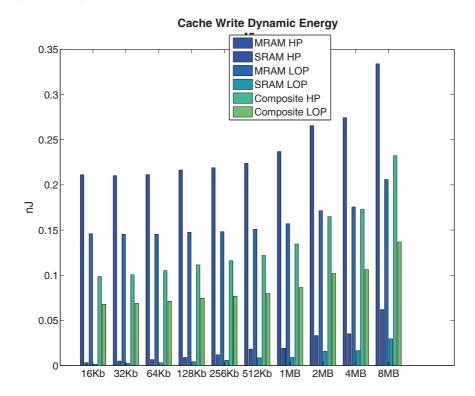

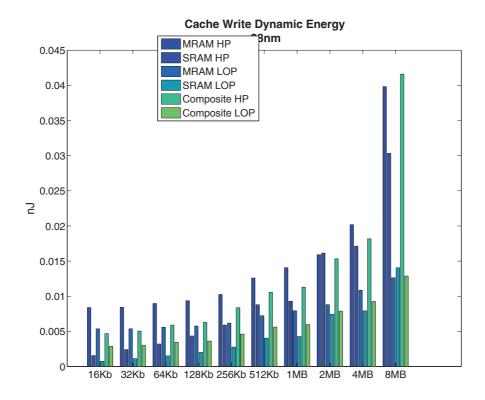

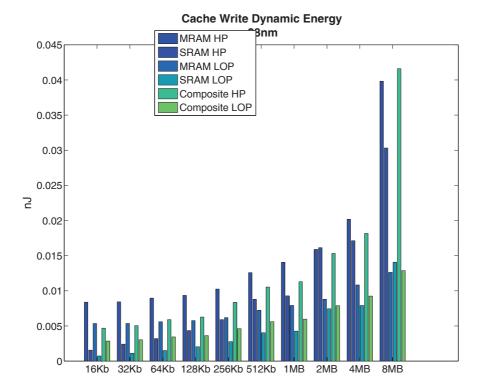

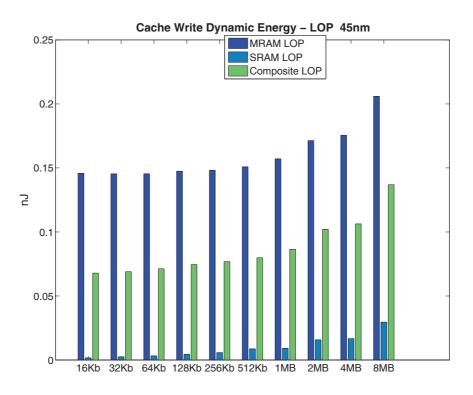

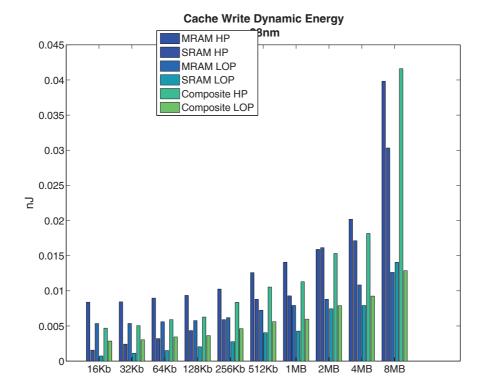

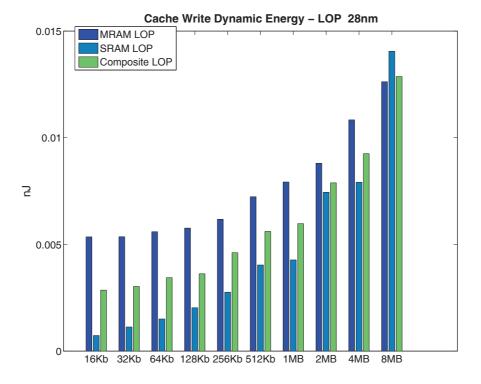

| Figure 3.17 | CACHE Write Dynamic Energy                                          | 81  |

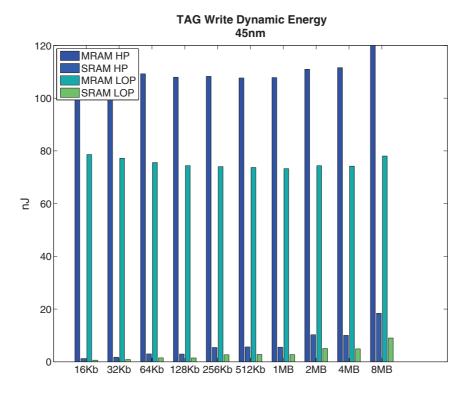

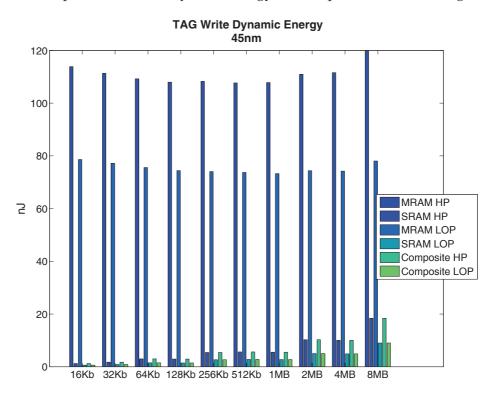

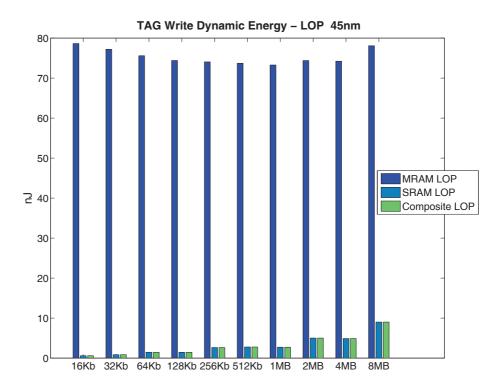

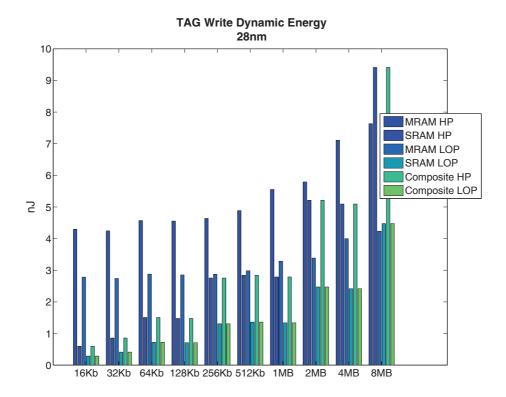

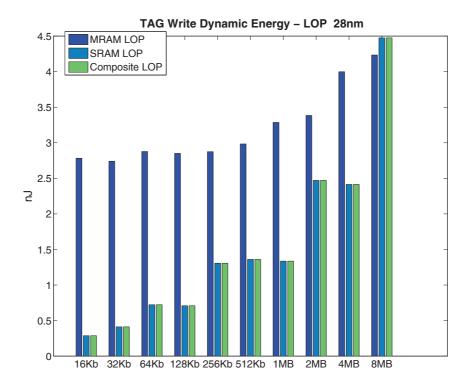

| Figure 3.18 | TAG Dynamic Energy                                                  | 82  |

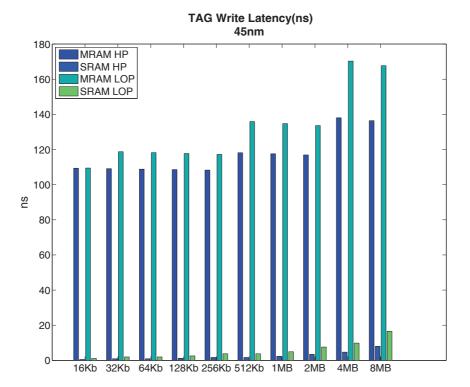

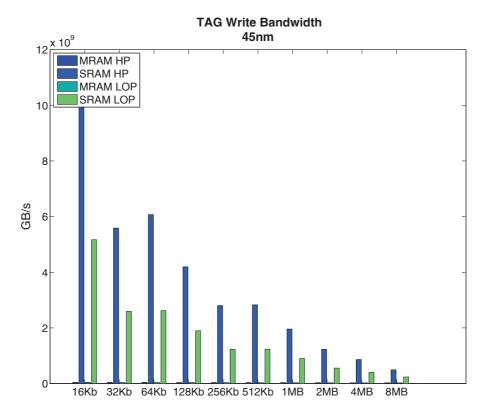

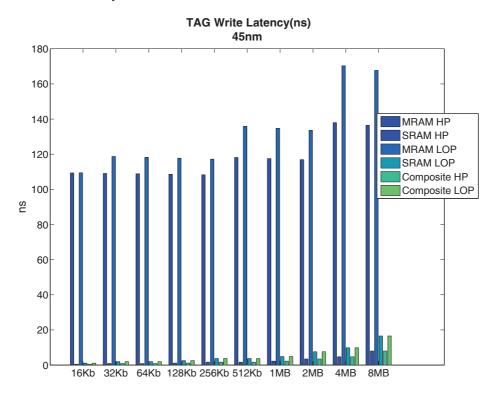

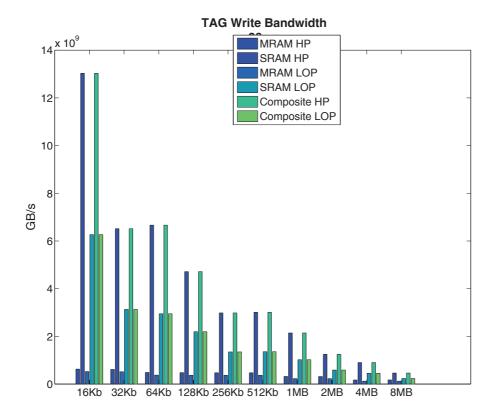

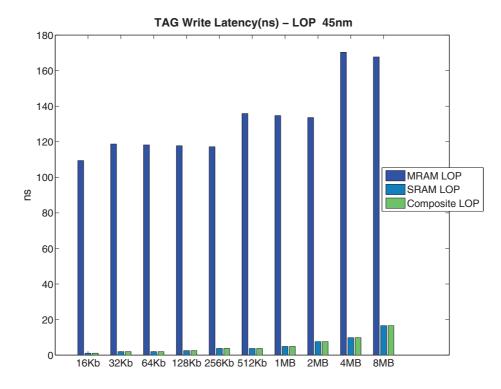

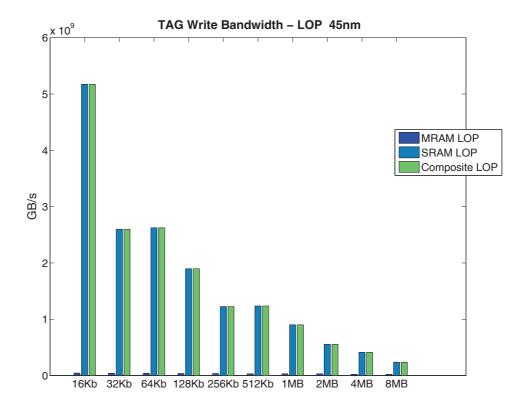

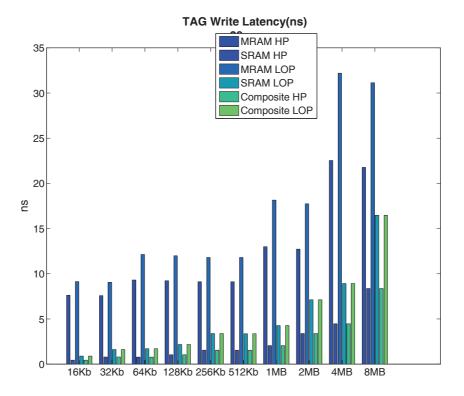

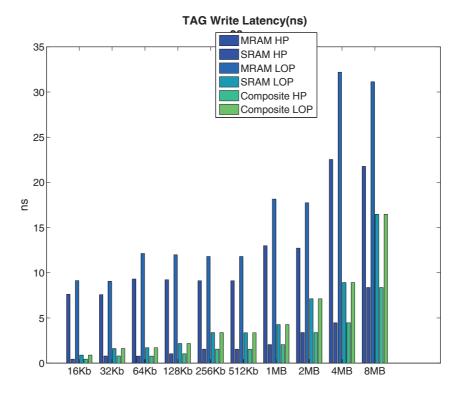

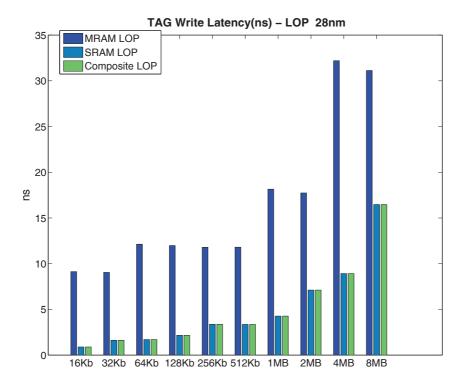

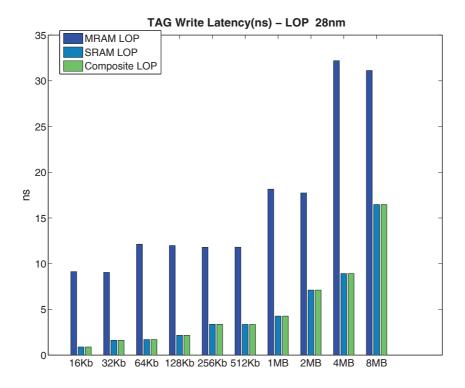

| Figure 3.19 | TAG Write Latency                                                   | 83  |

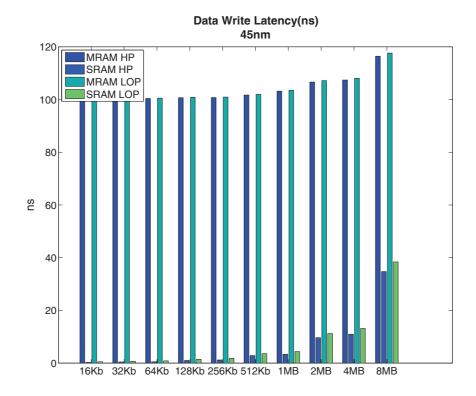

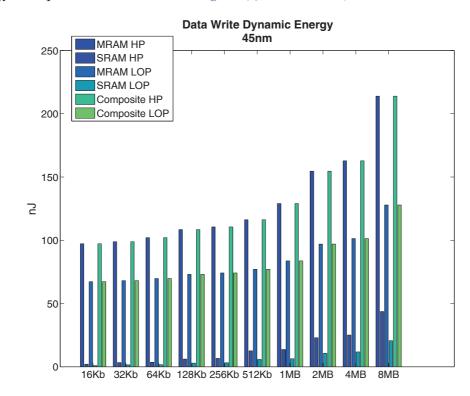

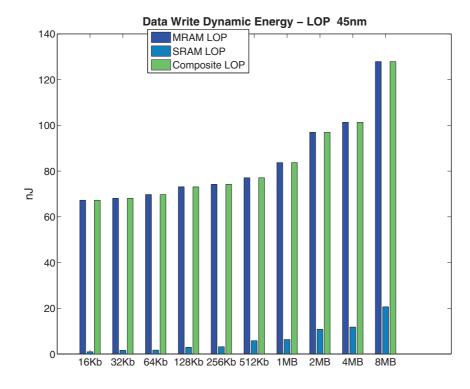

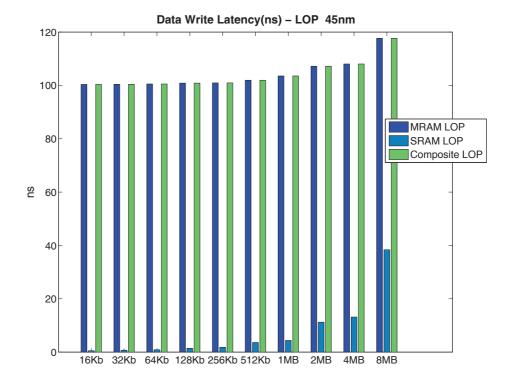

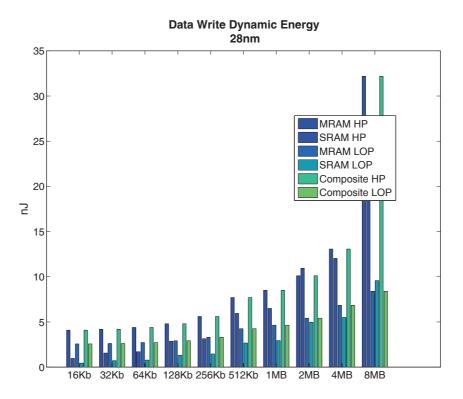

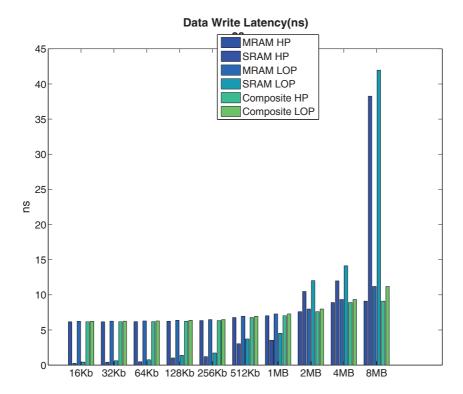

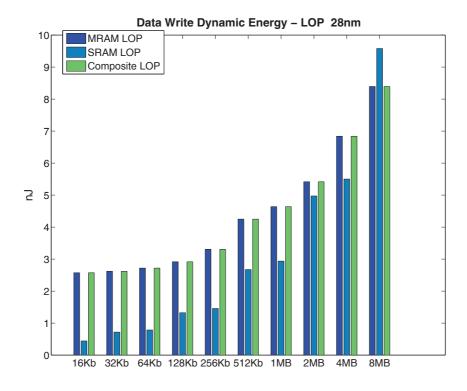

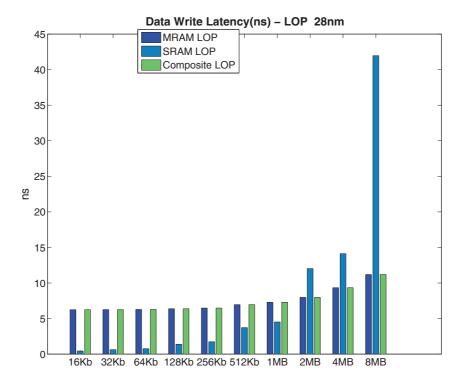

| Figure 3.20 | Data Write Latency                                                  | 84  |

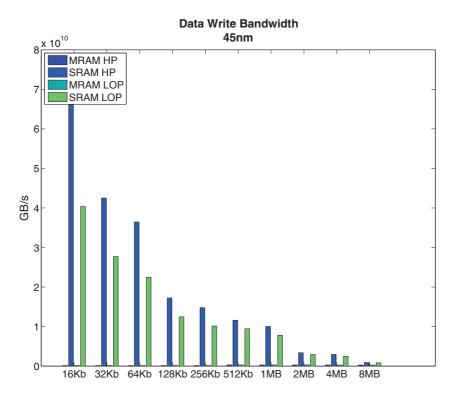

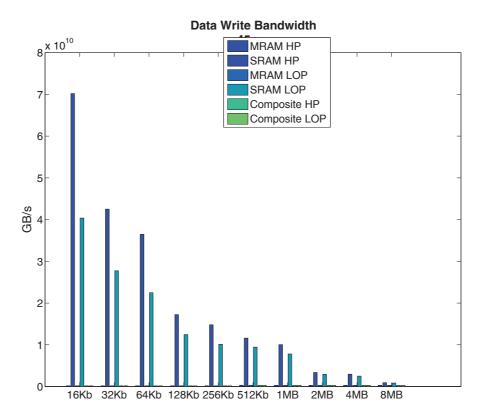

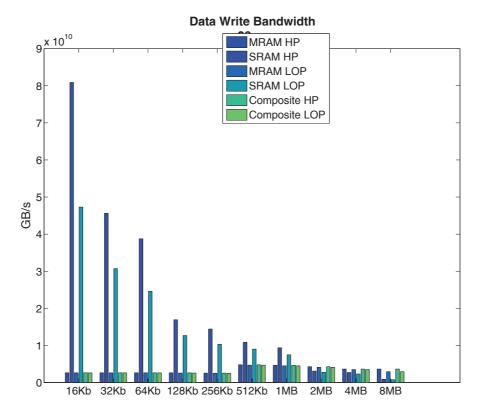

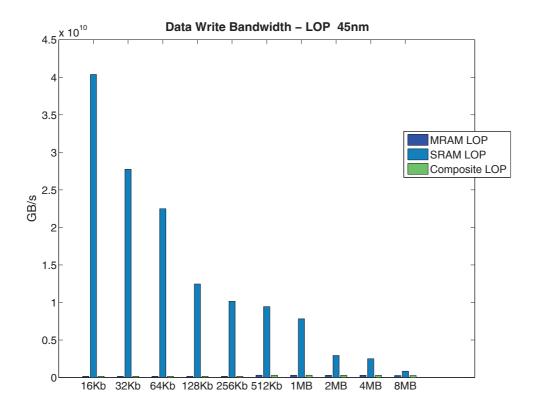

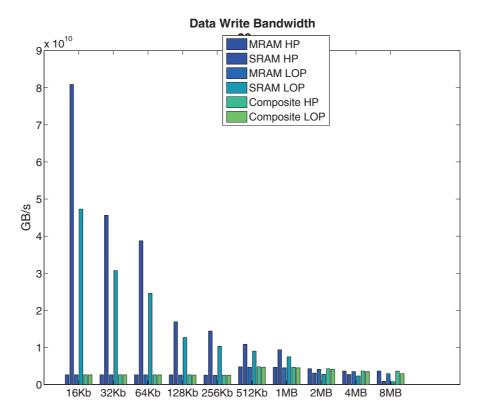

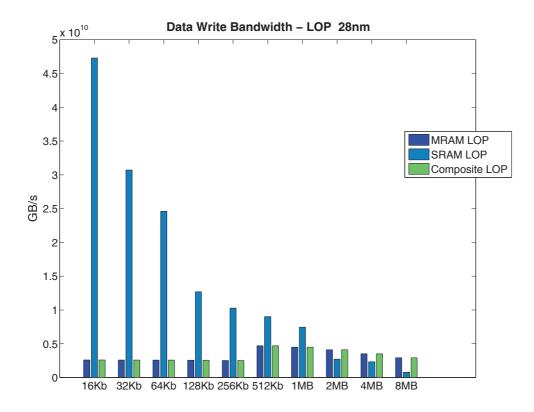

| Figure 3.21 | Write Bandwidth.                                                    | 85  |

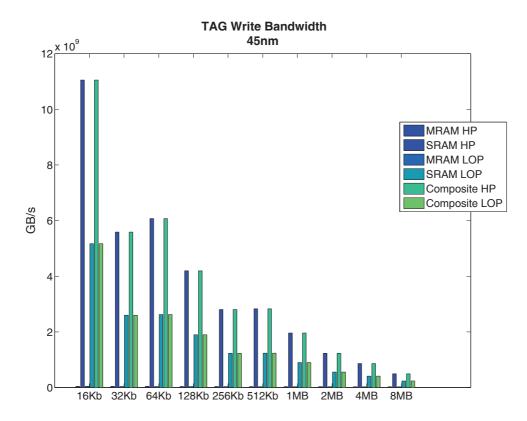

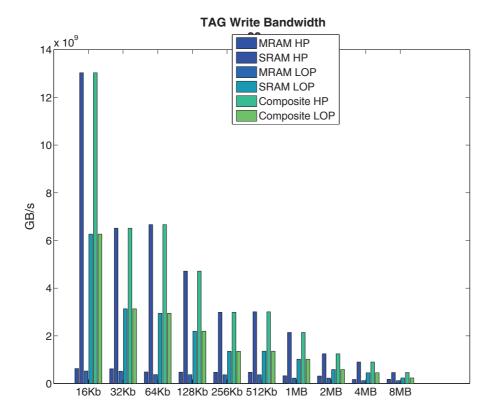

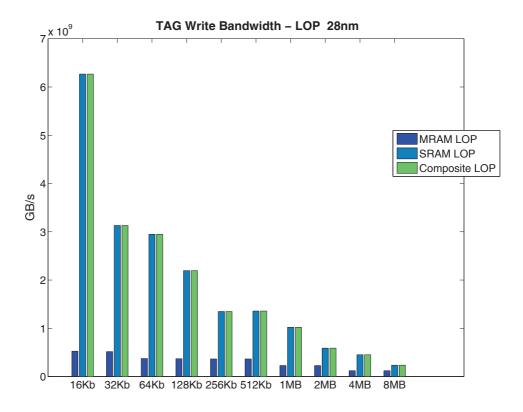

| Figure 3.22 | Write Bandwidth.                                                    | 86  |

| Figure 3.23 | Evaluation Methodology depicted.                                    | 87  |

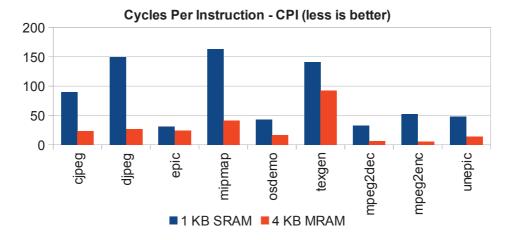

| Figure 4.1  | Overview of the processor performance using low-capacity L1         |     |

|             | caches                                                              | 98  |

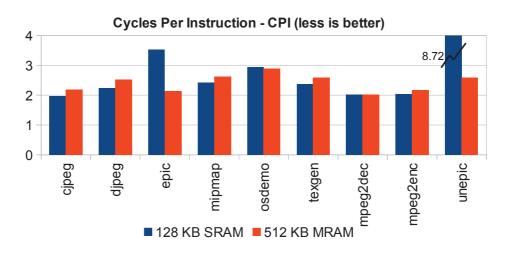

| Figure 4.2  | Overview of the processor performance using high-capacity L1        |     |

|             | caches                                                              | 98  |

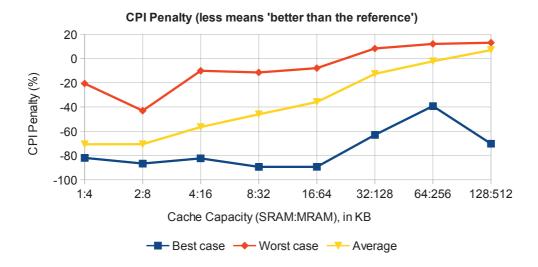

| Figure 4.3  | Overview of Cycles Per Instruction (CPI) Penalty: best-case, worst- |     |

|             | case and average of the Mediabench benchmarks' performance.         | 99  |

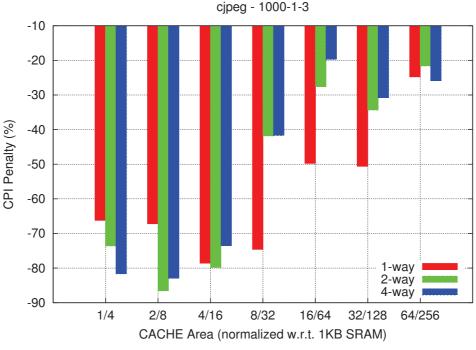

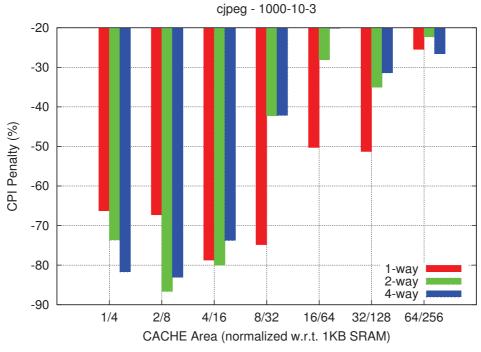

| Figure 4.4  | Simulation results for 1000 cycles and 1 cycle of delay for each    |     |

|             | subsequent word in burst mode.                                      | 100 |

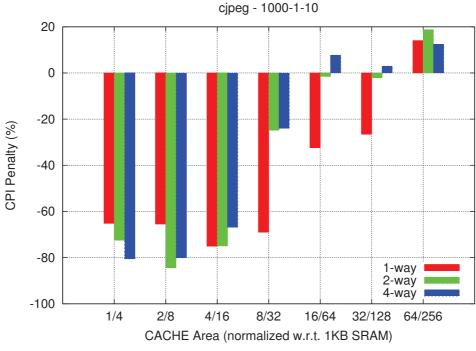

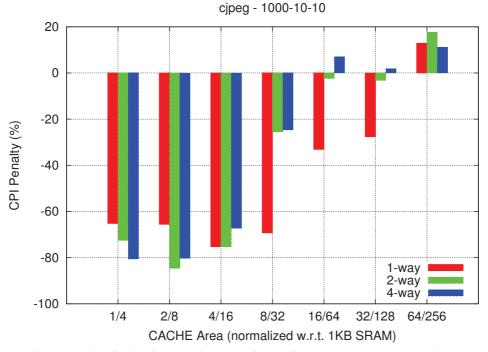

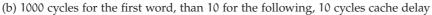

| Figure 4.5  | Simulation results for 1000 cycles and 10 cycles of delay for each  |     |

|             | subsequent word in burst mode.                                      | 101 |

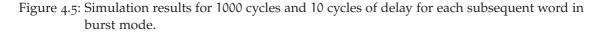

| Figure 4.6  | % Miss Latency Encoder.                                             | 103 |

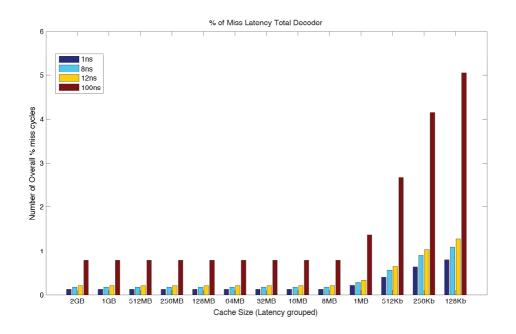

| Figure 4.7  | % Miss Latency Decoder                                              | 103 |

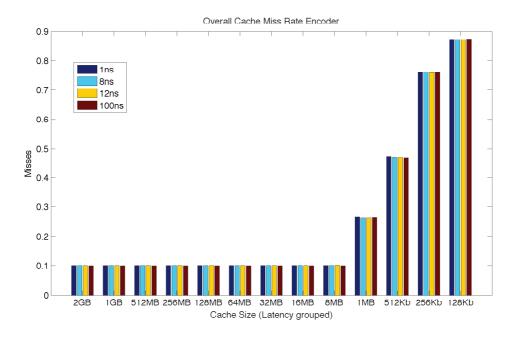

| Figure 4.8  | Overall Miss Rate Encoder.                                          | 104 |

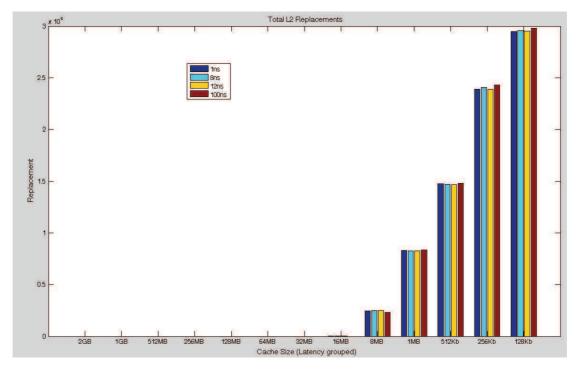

| Figure 4.9  | encoder L2 replacements.                                            | 104 |

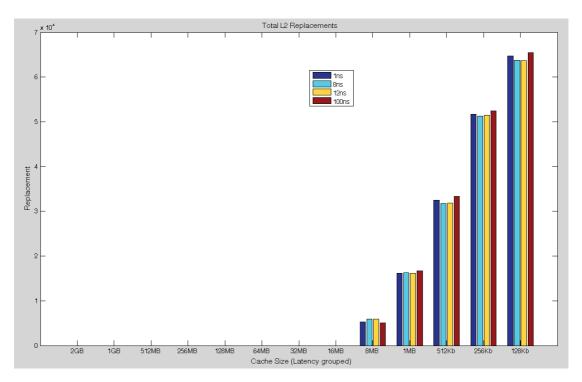

| Figure 4.10 | decoder L2 replacements.                                            | 105 |

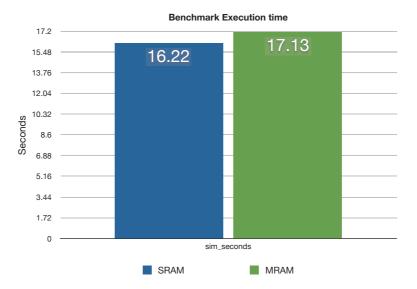

| Figure 4.11 | X.264 Execution time.                                               | 108 |

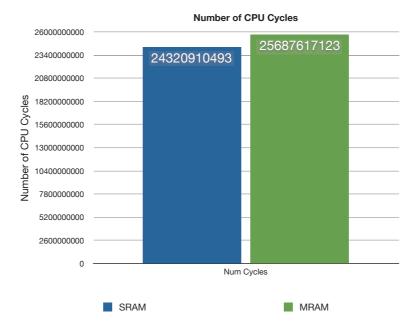

| Figure 4.12 | X.264 Clock cycles                                                  | 110 |

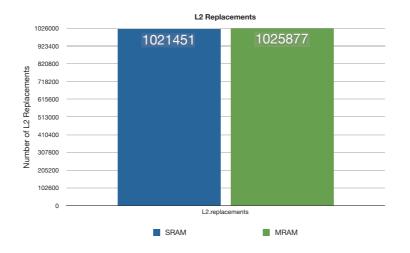

| Figure 4.13 | L2 Replacements                                                     | 111 |

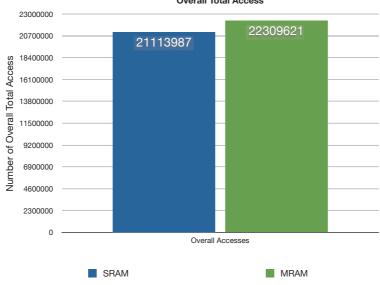

| Figure 4.14 | L2 Overall Access Total.                                            | 111 |

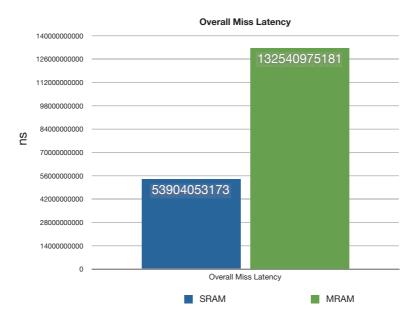

| Figure 4.15 | L2 Overall Miss Latency.                                            | 112 |

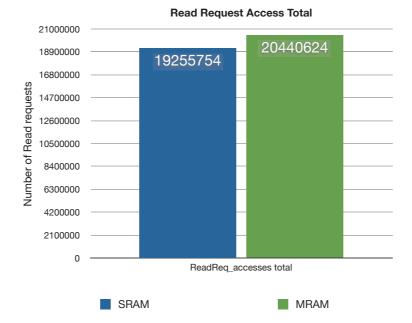

| Figure 4.16 | L2 ReadReq Access total.                                            | 112 |

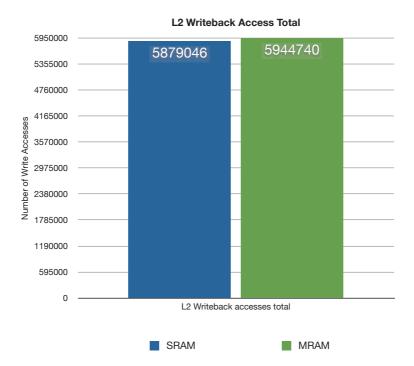

| Figure 4.17 | L2 Write Access Total.                                              | 113 |

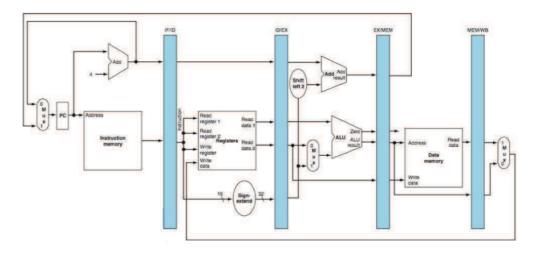

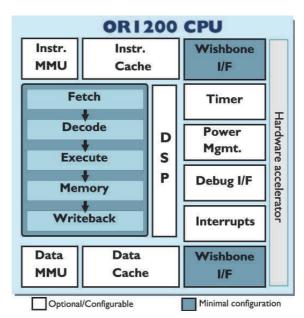

| Figure 4.18 | The OR1200 is a 32-bit scalar RISC with Harvard microarchitec-      |     |

|             | ture, 5 stage integer pipeline, virtual memory support (Memory      |     |

|             | Management Unit (MMU)) and basic Digital Signal Processing          |     |

|             | (DSP) capabilities                                                  | 119 |

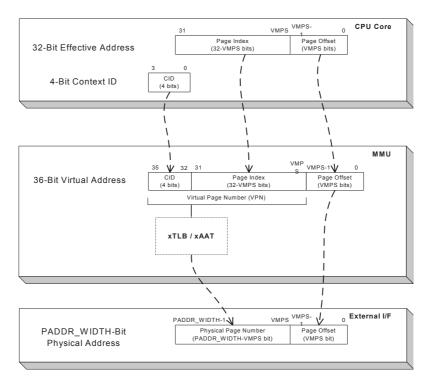

| Figure 4.19 | Translation of Effective to Physical Address. Simplified block dia-   |     |

|-------------|-----------------------------------------------------------------------|-----|

|             | gram for 32-bit processor implementations                             | 122 |

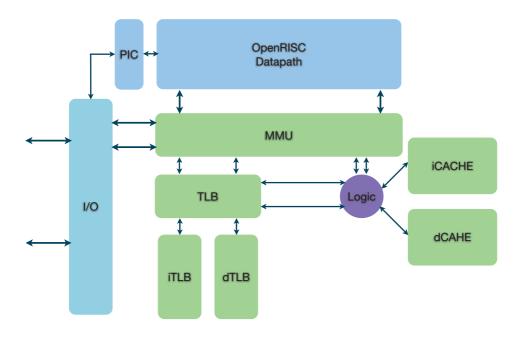

| Figure 4.20 | Synthesized OpenRISC architecture organization                        | 123 |

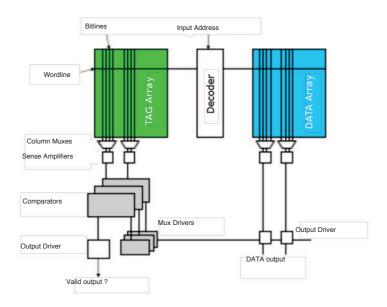

| Figure 4.21 | Composite CACHE set bank architecture, built with two heteroge-       |     |

|             | neous memory technologies. In the Figure the TAG(green matrix,        |     |

|             | left) is built using SRAM, while the DATA (blue matrix, right) is     |     |

|             | built using Spin Transfer Torque MRAM (STT-MRAM)                      | 128 |

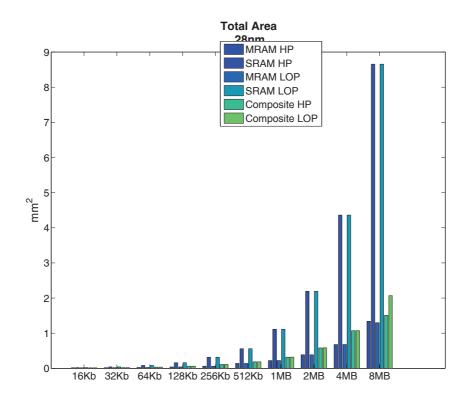

| Figure 4.22 | Total Area                                                            | 128 |

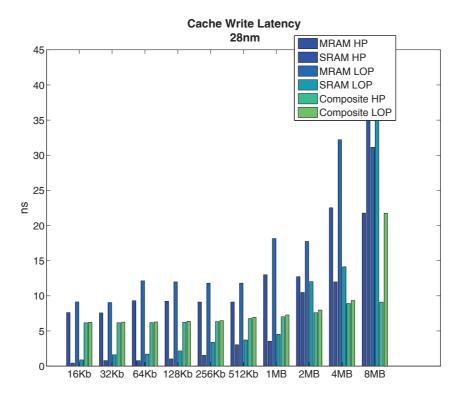

| Figure 4.23 | Total Write Latency.                                                  | 130 |

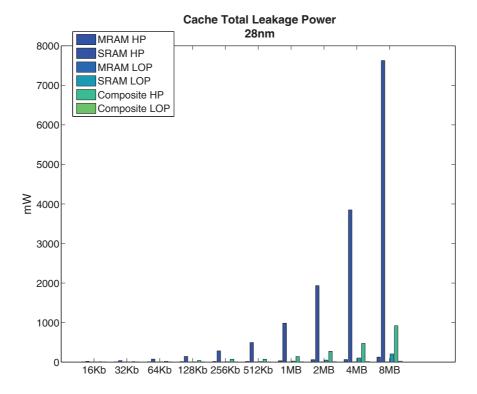

| Figure 4.24 | Composite Leakage Power.                                              | 131 |

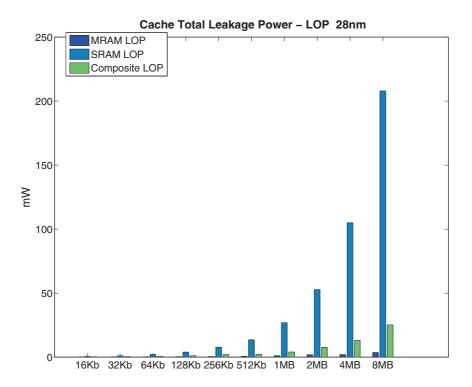

| Figure 4.25 | Low-Power (LOP) Total Leakage, magnification on the LOP banks         |     |

|             | observed in Figure 4.24                                               | 132 |

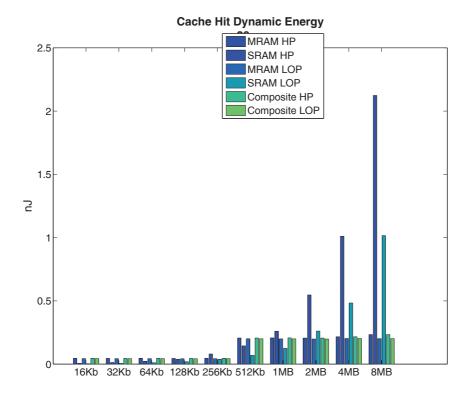

| Figure 4.26 | Hit Dynamic Energy                                                    | 133 |

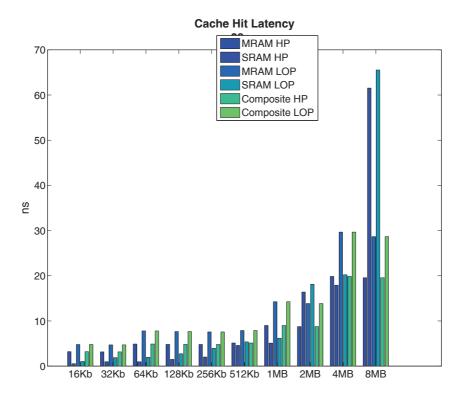

| Figure 4.27 | Hit Latency.                                                          | 134 |

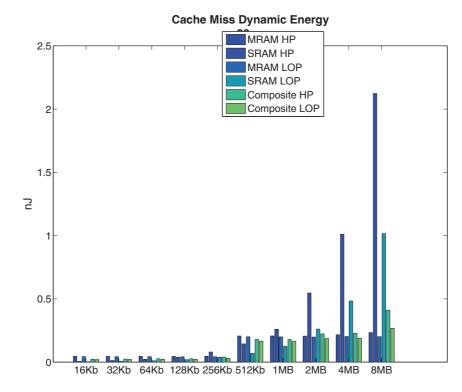

| Figure 4.28 | Miss Dynamic Energy                                                   | 135 |

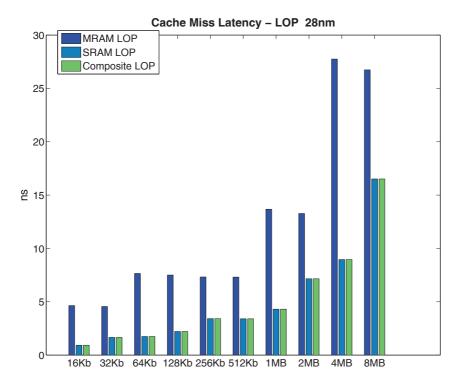

| Figure 4.29 | Miss Latency.                                                         | 136 |

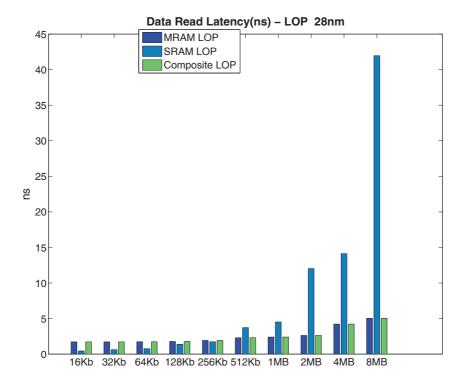

| Figure 4.30 | Data Read Latency.                                                    | 137 |

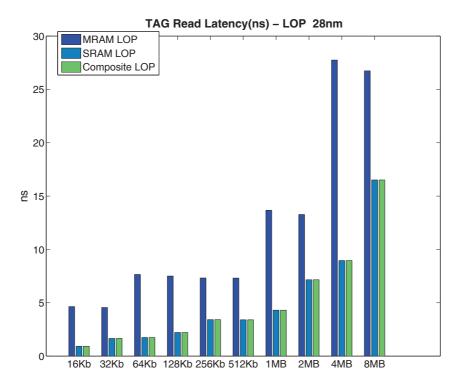

| Figure 4.31 | TAG Read Latency.                                                     | 138 |

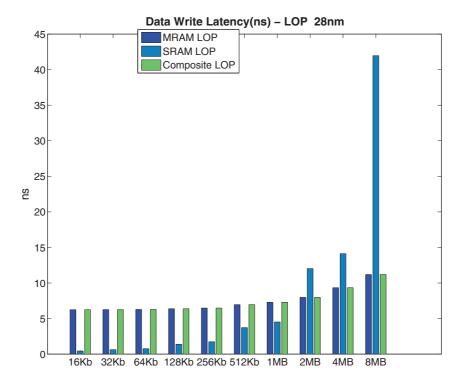

| Figure 4.32 | Data array matrix Write Latency                                       | 139 |

| Figure 4.33 | TAG Write Latency.                                                    | 141 |

| Figure 4.34 | TAG Dynamic Energy                                                    | 142 |

| Figure 4.35 | CACHE Write Dynamic Energy                                            | 143 |

| Figure 4.36 | Data Dynamic Energy                                                   | 145 |

| Figure 4.37 | Write Bandwidth.                                                      | 146 |

| Figure 4.38 | Write Bandwidth.                                                      | 147 |

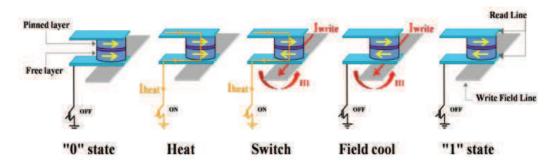

| Figure B.1  | MTJ process to switch the electromagnetic thin-layer field and        |     |

|             | store the logic value into the MTJ passing from the electrical layer. | 166 |

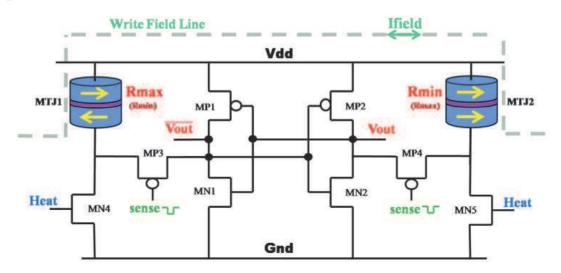

| Figure B.2  | TAS-MRAM non-volatile memory cell, with two complimentary             |     |

| -           | MTJs.                                                                 | 166 |

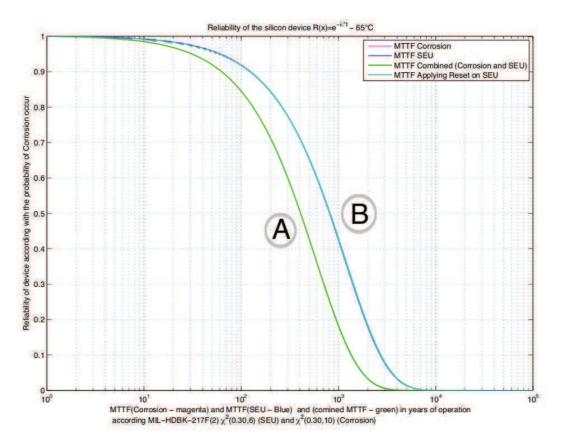

| Figure B.3  | The joint reliability of corrosion and Single Event Upset (SEU) in    |     |

|             | green (A) and in blue (B) the reliability applying the scrubbing      |     |

|             | technique, improving the reliability regarding SEU in 2x              | 168 |

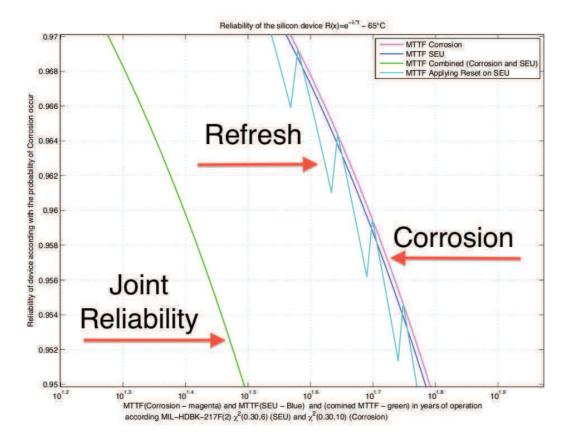

| Figure B.4  | The joint reliability of corrosion and SEU in green and in blue the   |     |

| -           | reliability applying the refresh technique, improving the reliabil-   |     |

|             | ity regarding SEU over the joint reliability distribution in 2x       | 169 |

| Figure B.5  | An overview of our general approach.                                  | 170 |

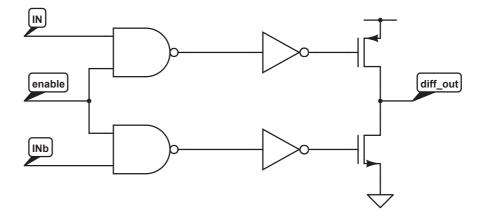

| Figure D.1  | Low-swing transmitter (actual transmitter has two such circuits to    |     |

| 0           | feed the differential wires).                                         | 182 |

| Figure D.2  | Sense Amplifier model adopted by CACTI.                               | 184 |

| Figure E.1  | Total Area.                                                           | 185 |

| Figure E.2  | Total Write Latency.                                                  | 186 |

| Figure E.3  | Total Write Dynamic Energy.                                           | 187 |

| Figure E.4  | CACHE Data Array Leakage Power.                                       | 188 |

| Figure E.5  | TAG Leakage Power.                                                    | 189 |

| Figure E.6  | Leakage Power.                                                        | 190 |

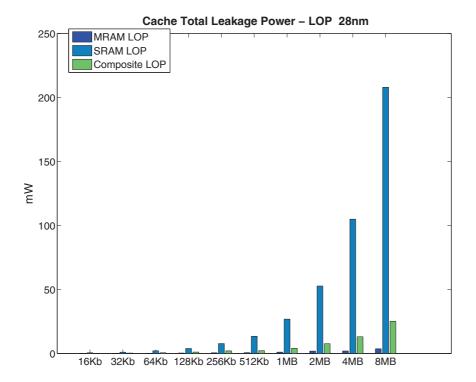

| Figure E.7  | Low-Power (LOP) Total Leakage, zoom into it to observe only the       |     |

| <u> </u>    | LOP banks observed in Figure E.6.                                     | 191 |

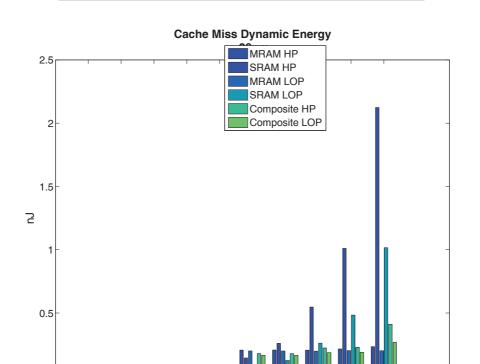

| Figure E.8  | Miss Dynamic Energy                                             | 192 |

|-------------|-----------------------------------------------------------------|-----|

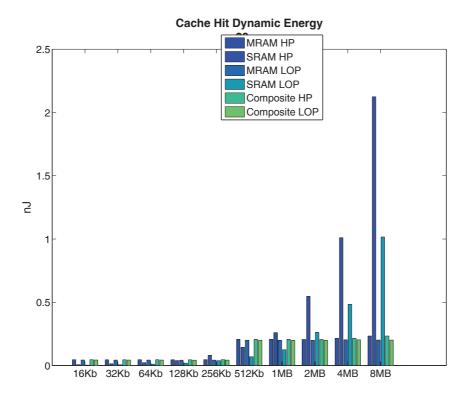

| Figure E.9  | Hit Dynamic Energy.                                             | 193 |

| Figure E.10 | Hit Latency.                                                    | 194 |

| Figure E.11 | Hit Latency.                                                    | 195 |

| Figure E.12 | Miss Dynamic Energy.                                            | 196 |

| Figure E.13 | Miss Latency                                                    | 197 |

| Figure E.14 | Data Read Latency.                                              | 198 |

| Figure E.15 | TAG Read Latency.                                               | 199 |

| Figure E.16 | Write Dynamic Energy                                            | 201 |

| Figure E.17 | Write Bandwidth.                                                | 202 |

| Figure E.18 | Write Bandwidth.                                                | 203 |

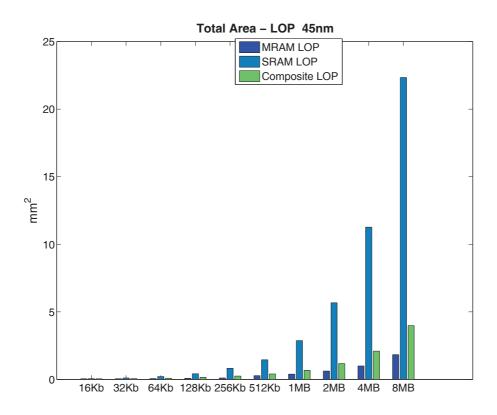

| Figure F.1  | Total Area                                                      | 205 |

| Figure F.2  | Total Write Latency.                                            | 206 |

| Figure F.3  | CACHE Data Array Leakage Power                                  | 207 |

| Figure F.4  | TAG Leakage Power.                                              | 208 |

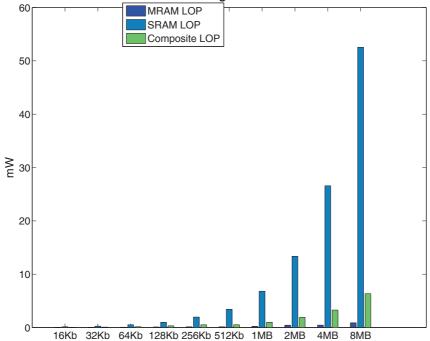

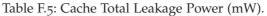

| Figure F.5  | Leakage Power.                                                  | 209 |

| Figure F.6  | Low-Power (LOP) Total Leakage, zoom into it to observe only the |     |

| -           | LOP banks observed in Figure F.5.                               | 210 |

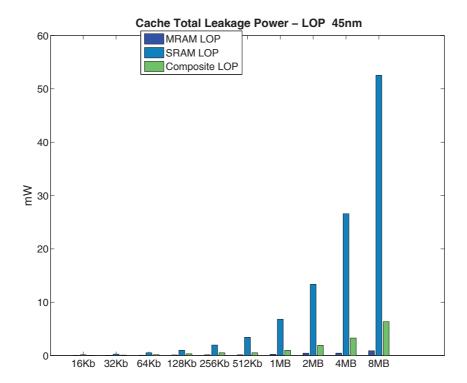

| Figure F.7  | Hit Dynamic Energy.                                             | 211 |

| Figure F.8  | Hit Latency.                                                    | 212 |

| Figure F.9  | Miss Latency.                                                   | 213 |

| Figure F.10 | DATA Read Latency.                                              | 214 |

| Figure F.11 | TAG Read Latency.                                               | 215 |

| Figure F.12 | DATA Write Latency.                                             | 216 |

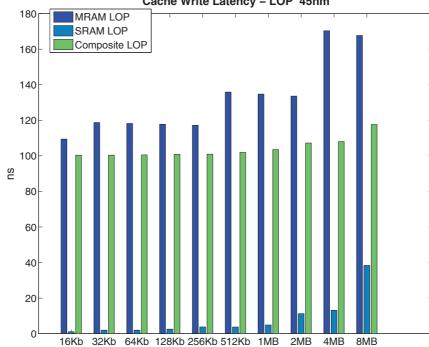

| Figure F.13 | TAG Write Latency.                                              | 217 |

| Figure F.14 | Write Dynamic Energy                                            | 218 |

| Figure F.15 | DATA Dynamic Energy                                             | 219 |

| Figure F.16 | TAG Dynamic Energy                                              | 220 |

| Figure F.17 | TAG Dynamic Energy                                              | 221 |

| Figure F.18 | DATA Write Latency                                              | 222 |

| Figure F.19 | Write Bandwidth.                                                | 223 |

| Figure F.20 | Write Bandwidth.                                                | 224 |

| Figure F.21 | Total Area                                                      | 225 |

| Figure F.22 | Total Write Latency.                                            | 226 |

| Figure F.23 | Leakage Power.                                                  | 227 |

| Figure F.24 | Low-Power (LOP) Total Leakage, close-up into only the LOP banks |     |

|             | observed in Figure F.23.                                        | 228 |

| Figure F.25 | Hit Dynamic Energy.                                             | 229 |

| Figure F.26 | Hit Latency.                                                    | 230 |

| Figure F.27 | Miss Dynamic Energy.                                            | 231 |

| Figure F.28 | Miss Latency.                                                   | 232 |

| Figure F.29 | DATA Read Latency.                                              | 233 |

| Figure F.30 | TAG Read Latency.    .                                          | 234 |

| Figure F.31 | DATA array matrix Write Latency.                                | 235 |

| Figure F.32 | TAG Write Latency.    .                                         | 236 |

| Figure F.33 | CACHE Write Dynamic Energy                                      | 237 |

| Figure F.34 | DATA Dynamic Energy                                             | 238 |

| Figure F.35 | TAG Dynamic Energy                                              | 239         |

|-------------|-----------------------------------------------------------------|-------------|

| Figure F.36 | TAG Dynamic Energy                                              | 240         |

| Figure F.37 | DATA Write Latency                                              | 241         |

| Figure F.38 | Write Bandwidth.                                                | 242         |

| Figure F.39 | Write Bandwidth.                                                | 243         |

| Figure F.40 | Total Area                                                      | <b>2</b> 45 |

| Figure F.41 | Total Write Latency.                                            | 246         |

| Figure F.42 | CACHE Data Array Leakage Power                                  | 247         |

| Figure F.43 | TAG Leakage Power.    .                                         | 248         |

| Figure F.44 | 8                                                               | 249         |

| Figure F.45 | Low-Power (LOP) Total Leakage, zoom into it to observe only the |             |

|             | LOP banks observed in Figure F.44.                              | 250         |

| Figure F.46 | CACHE Hit Dynamic Energy.                                       | 251         |

| Figure F.47 | CACHE LOP Hit Latency.                                          | 252         |

| Figure F.48 | CACHE LOP Miss Latency.                                         | 253         |

| Figure F.49 | DATA Read Latency.                                              | 254         |

| Figure F.50 | TAG Read Latency.                                               | 255         |

| Figure F.51 | DATA Write Latency.                                             | 256         |

| Figure F.52 | TAG Write Latency.                                              | 257         |

| Figure F.53 | CACHE Write Dynamic Energy                                      | 258         |

| Figure F.54 | DATA Write Dynamic Energy                                       | 259         |

| Figure F.55 | TAG Write Dynamic Energy                                        | 260         |

| Figure F.56 | TAG Write Latency                                               | 261         |

| Figure F.57 | DATA Write Latency                                              | 262         |

| Figure F.58 | DATA Write Bandwidth.                                           | 263         |

| Figure F.59 | TAG Write Bandwidth.    .                                       | 264         |

#### LIST OF TABLES

| Table 1.1 | Semiconductors Constraints and challenges as defined by ITRS in     |    |

|-----------|---------------------------------------------------------------------|----|

|           | [ITRS, 2012a]                                                       | 5  |

| Table 2.1 | Memory Taxonomy, according last assessment of ITRS [ITRS, 2012a]. 1 | 2  |

| Table 2.2 | Current Baseline and Prototypical Memory Technologies accord-       |    |

|           | ing [ITRS, 2012a]                                                   | 3  |

| Table 2.3 | Emerging Research Memory Devices—Demonstrated and Projected         |    |

|           | Parameters for the next generation of memory technologies be-       |    |

|           | yond 2020 [ITRS, 2012a]                                             | 5  |

| Table 2.4 | Potential of the Current Prototypical and Emerging Research Mem-    |    |

|           | ory Candidates for Storage Class Memory (SCM) Applications          |    |

|           | [ITRS, 2012a]                                                       | 18 |

| Table 2.5 | Labels detail for Table 2.4                                         | 18 |

| Table 2.6 | Experimental demonstrations according with [ITRS, 2012a] of ver-    |    |

|           | tical transistors in memory arrays                                  | 23 |

| Table 2.7                | Benchmark Select Device Parameters, according ITRS report [ITRS,      2012a]                                              | 4        |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------|----------|

| Table 2.8                | 2-Terminals Select Devices demonstrated experimentally [ITRS,                                                             | 4<br>26  |

| Table 2.9                | Comparison of NVM technologies [itr, 2011; Kim et al., 2011a;                                                             | 6        |

| Table 2.10               |                                                                                                                           | 7        |

| Table 3.1                | Memory Cell characterization models, employed to simulate the                                                             |          |

| Table 3.2                | Details about SRAM and MRAM memory banks, generated us-<br>ing NVSim, this table comprises the 45nm results of the memory | 8        |

| Table 3.3                | Details about SRAM and MRAM memory banks, generated us-<br>ing NVSim, this table comprises the 28nm results of the memory | 1        |

| Table 3.4                | Details about SRAM and MRAM DATA memory arrays, this table                                                                | 1        |

| 10010 3.4                |                                                                                                                           | 3        |

| Table 3.5                | Details about SRAM and MRAM DATA memory arrays, this table                                                                | 9        |

|                          |                                                                                                                           | 4        |

| Table 3.6                | Details about SRAM and MRAM TAG memory arrays, this table                                                                 |          |

|                          |                                                                                                                           | 5        |

| Table 3.7                | Details about SRAM and MRAM TAG memory arrays, this table                                                                 |          |

| $T_{-1}$                 |                                                                                                                           | 6        |

| Table 3.8                |                                                                                                                           | 7        |

| Table 3.9<br>Table 3.10  |                                                                                                                           | 8<br>9   |

| Table 3.10<br>Table 3.11 |                                                                                                                           | '9<br>'0 |

| Table 3.12               |                                                                                                                           | '1       |

| Table 3.13               |                                                                                                                           | '3       |

| Table 3.14               |                                                                                                                           | '4       |

| Table 3.15               |                                                                                                                           | '5       |

| Table 3.16               |                                                                                                                           | 6        |

| Table 3.17               | Data Read Latency (ns).                                                                                                   | 7        |

| Table 3.18               | TAG Read Latency (ns)                                                                                                     | 8        |

| Table 3.19               | DATA Write Latency (ns)                                                                                                   | '9       |

| Table 3.20               |                                                                                                                           | 0        |

| Table 3.21               |                                                                                                                           | 1        |

| Table 3.22               |                                                                                                                           | 2        |

| Table 3.23               |                                                                                                                           | 3        |

| Table 3.24               |                                                                                                                           | 4        |

| Table 3.25               |                                                                                                                           | 5        |

| Table 3.26               |                                                                                                                           | 6        |

| Table 4.1                |                                                                                                                           | 7        |

| Table 4.2                |                                                                                                                           | 7        |

| Table 4.3                | The Simulation Results of x264 encoder, for same system, only with different L2 CACHE memory bank, and Gem5 re-calibrated |          |

|                          |                                                                                                                           | קו       |

|                          | with NVSim latency details of the memory banks                                                                            | 1        |

| Table 4.4  | Memory banks characteristics                                   | 109 |

|------------|----------------------------------------------------------------|-----|

| Table 4.5  | Power Consumption estimation regarding the Leakage current.    | 114 |

| Table 4.6  | Power Consumption estimation number of WriteBack Total, and    |     |

|            | the data about the memory bank technology Table 4.4            | 114 |

| Table 4.7  | Summary of instances and area for SRAM banks                   | 124 |

| Table 4.8  | Summary of instances and area for MRAM banks                   | 124 |

| Table 4.9  | MRAM area summary, regarding logic and memory.                 | 125 |

| Table 4.10 | MRAM synthesis summary                                         | 125 |

| Table 4.11 | SRAM area summary, regarding logic and memory.                 |     |

| Table 4.12 | SRAM synthesis summary                                         | 125 |

| Table 4.13 | Total Area ( $\mu m^2$ )                                       | 129 |

| Table 4.14 | Cache Write Latency (ns)                                       | 130 |

| Table 4.15 | Cache Total Leakage Power (mW)                                 | 132 |

| Table 4.16 | Cache Hit Dynamic Energy (nJ)                                  | 133 |

| Table 4.17 | Cache Hit Latency (ns).                                        | 134 |

| Table 4.18 | Cache Miss Dynamic Energy (nJ)                                 | 135 |

| Table 4.19 | Cache Miss Latency (ns).                                       | 137 |

| Table 4.20 | Data Read Latency (ns)                                         | 138 |

| Table 4.21 | TAG Read Latency (ns)                                          | 139 |

| Table 4.22 | DATA array matrix Write Latency (ns)                           | 140 |

| Table 4.23 | TAG Write Latency (ns)                                         | 141 |

| Table 4.24 | TAG Write Dynamic Energy (nJ).                                 | 142 |

| Table 4.25 | Cache Write Dynamic Energy (nJ)                                | 144 |

| Table 4.26 | Data Write Dynamic Energy (nJ).                                | 145 |

| Table 4.27 | Write Bandwidth (GB/s)                                         | 146 |

| Table 4.28 | Write Bandwidth (GB/s)                                         | 147 |

| Table B.1  | Summary of the ECC synthesis results using CMOS ST 65nm stan-  |     |

|            | dard cell library.                                             | 171 |

| Table C.1  | Details about SRAM and MRAM memory banks, generated using      |     |

|            | the NVSim, this table comprises the 45nm results of the memory |     |

|            | banks for High Performance (HP)                                | 174 |

| Table C.2  | Details about SRAM and MRAM memory banks, generated using      |     |

|            | the NVSim, this table comprises the 28nm results of the memory |     |

|            | banks for HP                                                   | 175 |

| Table C.3  | Details about SRAM and MRAM DATA memory arrays, this table     |     |

|            | comprises the 45nm HP                                          | 176 |

| Table C.4  | Details about SRAM and MRAM DATA memory arrays, this table     |     |

|            | comprises the 28nm HP                                          | 177 |

| Table C.5  | Details about SRAM and MRAM TAG memory arrays, this table      |     |

|            | comprises the 45nm HP                                          | 178 |

| Table C.6  | Details about SRAM and MRAM TAG memory arrays, this table      |     |

| m 1 1      | comprises the 28nm HP                                          | 179 |

| Table E.1  | Total Area ( $\mu$ m <sup>2</sup> )                            | 186 |

| Table E.2  | Cache Write Latency (ns).                                      | 187 |

| Table E.3  | Cache Write Dynamic Energy (nJ)                                | 188 |

| Table E.4  | Cache Data Array Leakage Power (nW).                           | 189 |

| Table E.5  | Cache Tag Array Leakage Power (nW)                             | 190 |

| Table E.6  | Cache Total Leakage Power (mW)       | 191 |

|------------|--------------------------------------|-----|

| Table E.7  | LOP Cache Total Leakage Power (mW)   | 192 |

| Table E.8  | Cache Miss Dynamic Energy (nJ).      | 193 |

| Table E.9  | Cache Hit Dynamic Energy (nJ).       | 194 |

| Table E.10 | Cache Hit Latency (ns).              | 195 |

| Table E.11 | Cache Hit Latency (ns).              | 196 |

| Table E.12 | Cache Miss Dynamic Energy (nJ).      | 197 |

| Table E.13 | Cache Miss Latency (ns).             | 198 |

| Table E.14 | Read Latency (ns).                   | 199 |

| Table E.15 | Read Latency (ns).                   | 200 |

| Table E.16 | Cache Write Dynamic Energy (nJ)      | 201 |

| Table E.17 | Write Bandwidth (B/s)                | 202 |

| Table E.18 | Write Bandwidth (B/s)                | 204 |

| Table F.1  | Total Area ( $\mu$ m <sup>2</sup> )  | 206 |

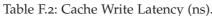

| Table F.2  | Cache Write Latency (ns).            | 207 |

| Table F.3  | Cache Data Array Leakage Power (nW). | 208 |

| Table F.4  | Cache Tag Array Leakage Power (nW).  | 209 |

| Table F.5  | Cache Total Leakage Power (mW)       | 210 |

| Table F.6  | Cache Hit Dynamic Energy (nJ).       |     |

| Table F.7  | Cache Hit Latency (ns).              |     |

| Table F.8  | Cache Miss Latency (ns).             | 213 |

| Table F.9  | DATA Read Latency (ns).              |     |

| Table F.10 | TAG Read Latency (ns).               | 215 |

| Table F.11 | Write Latency (ns).                  | 216 |

| Table F.12 | Read Latency (ns).                   | 217 |

| Table F.13 | Cache Write Dynamic Energy (nJ)      | 218 |

| Table F.14 | DATA Write Dynamic Energy (nJ).      | 219 |

| Table F.15 | TAG Write Dynamic Energy (nJ).       |     |

| Table F.16 | TAG Write Latency (ns).              | 221 |

| Table F.17 | DATA Write Latency (ns)              |     |

| Table F.18 | Write Bandwidth (B/s)                | 223 |

| Table F.19 | Write Bandwidth (GB/s)               | 224 |

| Table F.20 | Total Area ( $\mu$ m <sup>2</sup> )  | 225 |

| Table F.21 | Cache Write Latency (ns)             | 226 |

| Table F.22 | Cache Total Leakage Power (mW)       | 227 |

| Table F.23 | Cache Hit Dynamic Energy (nJ)        | 229 |

| Table F.24 | Cache Hit Latency (ns).              | 230 |

| Table F.25 | Cache Miss Dynamic Energy (nJ).      | 231 |

| Table F.26 | Cache Miss Latency (ns).             | 232 |

| Table F.27 | DATA Read Latency (ns)               | 233 |

| Table F.28 | TAG Read Latency (ns)                | 234 |

| Table F.29 | DATA array matrix Write Latency (ns) | 235 |

| Table F.30 | TAG Write Latency (ns)               | 236 |

| Table F.31 | Cache Write Dynamic Energy (nJ)      | 237 |

| Table F.32 | DATA Write Dynamic Energy (nJ).      | 238 |

| Table F.33 | TAG Write Dynamic Energy (nJ).       | 239 |

| Table F.34 | TAG Write Latency (ns).              | 240 |

| Table F.35 | DATA Write Latency (ns)               | 1 |

|------------|---------------------------------------|---|

| Table F.36 | Write Bandwidth (GB/s) 242            | 2 |

| Table F.37 | Write Bandwidth (GB/s) 244            | 4 |

| Table F.38 | Total Area ( $\mu$ m <sup>2</sup> )   | 5 |

| Table F.39 | Cache Write Latency (ns)              | 6 |

| Table F.40 | Cache Data Array Leakage Power (nW)   | 7 |

| Table F.41 | Cache Tag Array Leakage Power (nW)    | 3 |

| Table F.42 | Cache Total Leakage Power (mW)        | 9 |

| Table F.43 | Cache Hit Dynamic Energy (nJ)         | С |

| Table F.44 | Cache Hit Latency - LOP (ns)          | 2 |

| Table F.45 | Cache Miss Latency LOP (ns)           |   |

| Table F.46 | DATA Read Latency (ns)                | 4 |

| Table F.47 | TAG Read Latency (ns).         255    | 5 |

| Table F.48 | DATA Write Latency (ns)               | 6 |

| Table F.49 | TAG Read Latency (ns).         257    | 7 |

| Table F.50 | Cache Write Dynamic Energy - LOP (nJ) | 3 |

| Table F.51 | DATA Write Dynamic Energy (nJ)        | 9 |

| Table F.52 | TAG Write Dynamic Energy (nJ)         | С |

| Table F.53 | TAG Write Latency (ns)                | 1 |

| Table F.54 | DATA Write Latency (ns)               | 2 |

| Table F.55 | DATA Write Bandwidth (B/s) 265        | 3 |

| Table F.56 | TAG Write Bandwidth (GB/s)    264     | 4 |

## LIST OF ALGORITHMS

| 1 | Stretch of the automated script.                                                              | 88  |

|---|-----------------------------------------------------------------------------------------------|-----|

| 2 | Fragment of a TCL file to demonstrate how to characterize a memory library using Liberate MX. | 118 |

## ACRONYMS

| ASIC | Application Specific Integrated Circuit |

|------|-----------------------------------------|

| BCH  | Bose-Chaudhuri-Hocquenghem168           |

| CMOS | Complementary Metal Oxide Semiconductor |

| CCS  | Composite Current Source                |

| CMB   | Composite Memory Bank                                 |

|-------|-------------------------------------------------------|

| CPU   | Central Processing Unit                               |

| CNN   | Cellular Nonlinear Network                            |

| CNT   | Carbon Nano Tubes20                                   |

| CeRAM | Correlated Electron Random Access Memory 21           |

| CIMS  | Current induced magnetic switching                    |

| CPI   | Cycles Per Instructionxx                              |

| DFM   | Design For Manufacturing116                           |

| DRAM  | Dynamic Random Access Memory                          |

| DNUCA | Dynamic Non-Uniform CACHE Access 44                   |

| DSP   | Digital Signal Processingxx                           |

| EDA   | Electronic Design Automation 118                      |

| ECC   | Error Correcting Code                                 |

| FPGA  | Field Programmable Gate Arrays                        |

| FeM   | Ferromagnetic                                         |

| FLASH | Floating-gate transistor NAND or NOR4                 |

| FIMS  | Field Induced Magnetization Switching29               |

| FeFET | Ferroelectric Field Effect Transistor19               |

| FL    | Free-Layer                                            |

| GMR   | Giant Magnetoresistance                               |

| HDD   | Hard Disk Drive                                       |

| HP    | High Performance                                      |

| HPC   | High Performance Computing 117                        |

| HRS   | High Resistance State                                 |

| IC    | Integrated Circuitix                                  |

| ITRS  | International Technology Roadmap for Semiconductors11 |

| iMTJ  | in-Plane or Parallel Magnetic Tunnel Junction         |

| ISA   | Instruction Set Architecture                          |

| LOP   | Low Power Performance                                 |

| MTJ   | Magnetic Tunnel Junctionix                            |

| MRAM  | Magnetic Random Access Memoryxix                      |

| MMU   | Memory Management Unitxx                              |

| MtM   | More than Moore                                       |

| MLC   | Multi-Level Cell17                                    |

| MIEC  | Mixed Ionic and Electronic Conduction Materials25     |

| MIM   | Metal-Insulator-Metal                                 |

| MIT   | Metal Insulator Transition25                          |

| MEU     | Multiple Event Upset                   |

|---------|----------------------------------------|

| NVM     | Non-Volatile Memoryxvi                 |

| NUCA    | Non-Uniform CACHE Access               |

| NEMM    | Nanoelectromechanical Memory 20        |

| NoC     | Network-on-Chip154                     |

| PCRAM   | Phase Change Random Access Memory4     |

| PMA     | Perpendicular Magnetic Anisotropy34    |

| PLL     | Phase Locked Loop 116                  |

| PL      | Pinned Layer 33                        |

| PCM     | Phase-Change Memory                    |

| pMTJ    | Perpendicular Magnetic Tunnel Junction |

| RRAM    | Resistive Random Access Memory4        |

| ReRAM   | Redox Resistive Random Access Memory4  |

| RTL     | Register Transfer Level                |

| RL      | Reference-Layer                        |

| RISC    | Reduced Instruction Set Computing 119  |

| STT     | Spin Transfer Torque7                  |

| STT-MRA | AM Spin Transfer Torque MRAMxxi        |

| SEU     | Single Event Upsetxxi                  |

| SRAM    | Static Random Access Memoryxvii        |

| SCM     | Storage Class Memoryxxiii              |

| SSD     | Solid State Drive                      |

| SoC     | System-on-Chip40                       |

| SAF     | Synthetic Antiferromagnet              |

| SMT     | Simultaneous Multi-Threading91         |

| SMP     | Symmetric Multi-Processing 119         |

| TAS-MR  | AM Thermally Assisted Switching MRAM   |

| TMR     | Tunneling Magnetoresistance 29         |

| TLB     | Translation Lookaside Buffer42         |

| UCA     | Uniform CACHE Access                   |

| VLSI    | Very Large Scale Integration           |

| VCM     | valence change mechanism 20            |

| WORM    | Write Once Read Many 114               |

#### Part I

## INTRODUCTION

From approximately 1.8 million years ago (*Homo Ergaster* appearance) to the current state, the mankind evolved and, since the advent of the CMOS circuits, the human knowledge is shifting exponentially at the speed of the Semiconductors industry. Such is the influence of Semiconductors in the society daily life that the advent of new memory technologies will, again, create a huge impact in the society. This thesis is just a fragment of this evolutional cycle and will be another forgotten milestone in the years to come.

# 1

#### INTRODUCTION

Any sufficiently advanced technology is indistinguishable from magic. — Arthur C. Clarke