## Physical modelling of impurity diffusion and clustering phenomena in CMOS based image sensors

Zahi Essa

### ▶ To cite this version:

Zahi Essa. Physical modelling of impurity diffusion and clustering phenomena in CMOS based image sensors. Micro and nanotechnologies/Microelectronics. Université Paul Sabatier - Toulouse III, 2013. English. NNT: . tel-01020497

### HAL Id: tel-01020497 https://theses.hal.science/tel-01020497

Submitted on 8 Jul 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

### En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

### Présentée et soutenue par : Zahi ESSA

Le lundi 25 novembre 2013

### Titre:

Physical modelling of impurity diffusion and clustering phenomena in CMOS based image sensors

ED GEET: Micro et Nanosystèmes

#### Unité de recherche :

Laboratoire d'Analyse et d'Architecture des Systèmes

### Directeur(s) de Thèse:

Fuccio CRISTIANO, Directeur de Thèse au LAAS/CNRS Toulouse Pierre BOULENC, Co-encadrant à STMicroelectronics Crolles

### Rapporteurs:

Gérard GHIBAUDO, Directeur de Recherche à l'IMEP-LAHC/CNRS Grenoble Daniel ALQUIER, Professeur à l'Université de Tours

### Autre(s) membre(s) du jury:

Pierre MAGNAN, Professeur à l'ISAE Toulouse Enrico NAPOLITANI, Chercheur au CNR-IMM MATIS Padova Italie Frédéric MORANCHO, Professeur à l'Université de Toulouse Clément TAVERNIER, Manager Équipe TCAD à STMicroelectronics Crolles

#### Abstract

Over the last years, microelectronics growth was made possible thanks to the innovations occurring in CMOS (Complementary Metal Oxide Semiconductor) technology, leading to a constant improvement of device performances. These innovations have to answer the technological challenges related to devices miniaturization, as well as to their continuous diversification. In response to these challenges, modelling approaches such as TCAD (Technology Computer Aided Design) drastically reduce the technologies development time and cost. In this context, the thesis deals with TCAD models development of several physical mechanisms taking place within advanced process steps. In the first part, diffusion and activation mechanisms following high-dose dopant implantation were studied, mainly in the case of plasma implantation, a promising technique for conformal doping in image sensors and Tri-Gates transistors. In high doping conditions, the observation and modelling of large boron interstitial clusters (BICs) were carried out. In the second part, the evaluation of chemical species diffusion and transfer between materials was considered. In particular, Boron dose loss from silicon in spacer stacks and corresponding diffusion in oxide were studied. In addition, lanthanum diffusion evaluation during thermal annealing in gate stacks with high-k oxides was investigated. In the last part, the impact of the different investigated mechanisms on CMOS devices electrical behaviour was finally evaluated, resulting in the improvement of TCAD models predictability on MOS transistors performances, as well as FSI (Front Side Illumination) and BSI (Back Side Illumination) CMOS-based image sensors.

# Contents

| A  | ckno  | wledge  | ements                                                        | iii |

|----|-------|---------|---------------------------------------------------------------|-----|

| Li | st of | figure  | $\mathbf{s}$                                                  | v   |

| Li | st of | tables  | 3                                                             | xi  |

| Li | st of | abbre   | viations                                                      | 1   |

| In |       | uction  |                                                               | 5   |

|    | REI   | FEREN   | CES                                                           | 8   |

| 1  | Adv   | vanced  | CMOS technologies modelling challenges                        | 9   |

|    | 1.1   | Introd  | luction                                                       | 9   |

|    | 1.2   | A brie  | ef introduction to MOS transistor                             | 9   |

|    |       | 1.2.1   | The p-n junction                                              | 10  |

|    |       | 1.2.2   | The metal/oxide/silicon capacitance                           | 14  |

|    |       | 1.2.3   | MOS transistor and CMOS technology                            | 16  |

|    |       |         | 1.2.3.1 MOS transistor operation regimes                      | 16  |

|    |       |         | 1.2.3.2 MOS transistor miniaturization                        | 18  |

|    |       |         | 1.2.3.3 CMOS technology process                               | 20  |

|    | 1.3   | CMOS    | S image sensors                                               | 22  |

|    |       | 1.3.1   | CMOS image sensors operation regimes                          | 22  |

|    |       | 1.3.2   | CMOS image sensors features                                   | 24  |

|    |       | 1.3.3   | CMOS image sensors process                                    | 26  |

|    |       |         | 1.3.3.1 CMOS image sensors FEOL process                       | 26  |

|    |       |         | 1.3.3.2 CMOS image sensors BEOL process                       | 27  |

|    | 1.4   | Advar   | nced process techniques                                       | 28  |

|    |       | 1.4.1   | Physical mechanisms during implantation and thermal annealing | 28  |

|    |       | 1.4.2   | Implantation advanced solutions                               | 30  |

|    |       | 1.4.3   | Thermal annealing advanced solutions                          | 31  |

|    | 1.5   | Silicon | n level TCAD modelling                                        | 32  |

|    |       | 1.5.1   | State-of-the-art TCAD models                                  | 33  |

|    |       |         | 1.5.1.1 Advanced process models                               | 33  |

|    |       |         | 1.5.1.2 Junction leakage current models                       | 34  |

|    |       | 1.5.2   | Beyond state-of-the-art                                       | 35  |

|    | 1.6   | Concl   | usion                                                         | 35  |

|    | REF   | FEREN   | CES                                                           | 37  |

ii CONTENTS

| 2            | _             | plantation-induced defects and their impact on dopant diffusion and activation      |              |

|--------------|---------------|-------------------------------------------------------------------------------------|--------------|

|              | 2.1           | Introduction                                                                        | 43           |

|              | 2.2           | Plasma Immersion Ion Implantation (PIII)                                            | 43           |

|              | 2.3           | Experimental investigation and modelling of BF3 plasma implanted p+/n USJs          | 45           |

|              |               | 2.3.1 BF <sub>3</sub> PIII dedicated samples                                        | 45           |

|              |               | 2.3.2 Implantation and amorphization in BF <sub>3</sub> PIII                        | 46           |

|              |               | 2.3.3 Dopants diffusion and electrical activation in BF <sub>3</sub> PIII           | 51           |

|              | 2.4           | High boron and interstitials super-saturation and large boron-interstitial clusters | 55           |

|              |               | 2.4.1 Introduction to large BICs                                                    | 55           |

|              |               | 2.4.2 Large BICs continuum modelling in silicon                                     | 56           |

|              |               | 2.4.3 Large BICs model applied to BF <sub>3</sub> PIII                              | 65           |

|              | 2.5           | Conclusion                                                                          | 66           |

|              | REF           | FERENCES                                                                            | 69           |

| 3            | Che           | emical species diffusion in multi-materials stacks                                  | <b>7</b> 5   |

|              | 3.1           | Introduction                                                                        | 75           |

|              | 3.2           | Boron dose loss modelling in nitride/oxide/silicon stacks                           | 75           |

|              |               | 3.2.1 Introduction to boron dose loss                                               | 75           |

|              |               | 3.2.2 Dedicated boron dose loss experiments                                         | 77           |

|              |               | 3.2.3 Boron dose loss modelling                                                     | 79           |

|              |               | 3.2.3.1 Dynamics of hydrogen related species                                        | 79           |

|              |               | 3.2.3.2 Boron out-diffusion modelling                                               | 83           |

|              | 3.3           | Lanthanum diffusion in high-k stacks                                                | 88           |

|              | 0.0           | 3.3.1 Introduction to high-k stacks and the use of lanthanum                        | 91           |

|              |               | 3.3.2 Experimental investigation of lanthanum diffusion in high-k stacks            | 92           |

|              |               | 3.3.3 Lanthanum diffusion modelling in high-k stacks                                | 95           |

|              | 3.4           | Conclusion                                                                          | 102          |

|              |               | FERENCES                                                                            | $102 \\ 103$ |

|              | REI           | FERENCES                                                                            | 105          |

| 4            | $\mathbf{TC}$ | AD modelling of advanced CMOS devices                                               | 107          |

|              | 4.1           | Introduction                                                                        | 107          |

|              | 4.2           | MOS transistors modelling                                                           | 108          |

|              |               | 4.2.1 Boron dose loss in advanced bulk pMOS transistors                             | 108          |

|              |               | 4.2.2 Boron precipitation in FDSOI pMOS transistors                                 | 109          |

|              |               | 4.2.3 PIII in TriGate nMOS transistors                                              | 112          |

|              | 4.3           | FSI CMOS image sensors modelling                                                    | 114          |

|              |               | 4.3.1 Boron dose loss in TG of FSI CMOS image sensors                               | 114          |

|              |               | 4.3.2 PIII in DTIs of FSI CMOS image sensors                                        | 117          |

|              | 4.4           | BSI CMOS image sensors modelling                                                    | 121          |

|              |               | 4.4.1 Back side boron dose loss in BSI CMOS image sensors                           | 121          |

|              |               | 4.4.2 Back side LTA in BSI CMOS image sensors                                       | 122          |

|              | 4.5           | Conclusion                                                                          | 125          |

|              | REF           | FERENCES                                                                            | 126          |

| $\mathbf{C}$ | onclu         | ısion                                                                               | 129          |

# Acknowledgements

First of all, I would like to acknowledge my advisor Fuccio Cristiano for his guidance and support throughout the PhD. I thank him for his deep knowledge in the physics of implantation defects, doping and precipitation mechanisms, but also for being a constant source of inspiration and motivation. I also appreciated his enriching feedback during articles writing and international conferences, undoubtedly improving the quality of my work. Next, I would like to thank my co-supervisor Pierre Boulenc for communicating his knowledge in technological process and device simulation and more particularly in CMOS image sensors. I am grateful for his availability, encouragement and for helping me to improve my problem solving skills.

I would like to thank the committee members for their time, feedback and interesting questions. I am grateful to Dr. Gérard Ghibaudo and Prof. Daniel Alquier for their reports of my thesis manuscript. I also thank Prof. Pierre Magnan, Dr. Enrico Napolitani and Prof. Frédéric Morancho for taking part in the committee. I thank Mr. Clément Tavernier for taking part in the committee, but also for his welcome and support within STMicroelectronics Crolles TCAD team during my PhD.

This PhD work held at STMicroelectronics Crolles France and LAAS CNRS Toulouse France, would not have been possible without the contribution of several individuals within strong research collaborations. Among the research activities, the ones carried out within the European project ATE-MOX were the most significant. Therefore, I would like to acknowledge my colleagues in the project: Cloud Nyamhere, François Olivié, Elena Bedel-Pereira, Vincent Mortet and Yang Qiu from LAAS CNRS, Yohann Spiegel and Frank Torregrosa from Ion Beam Services, Christoph Zechner, Nikolas Zographos and Alexander Tsibizov from Synopsys, Alexander Burenkov, Moritz Hackenberg and Peter Pichler from Fraunhofer IISB, Giuseppe Fisicaro and Antonino La Magna from CNR IMM, Maurice Quillec and Nadjib Taleb from Probion Analysis, Karim Huet from Excico, Nick Cowern from the University of Newcastle and Artur Scheinemann from ETH. I also would like to thank collaborators for their contribution in the different treated subjects of my PhD project: Bertrand Pelletier, Pierre Morin, Ardechir Pakfar, Clément Gaumer, Mickael Gros-Jean, Didier Blavette, Huiyuan Wang, Sébastien Duguay, Evgeny Demenev, Florian Meirer, Flavien Hirigoyen and Axel Crocherie.

I would like to thank all my colleagues and friends from STMicroelectronics Crolles and LAAS CNRS Toulouse for their help and the great moments spent together during these three years. From Crolles and Grenoble area, I would like to thank Floria, Sébastien G., Benoît, Olivier N., Olivier S., Assawer, Amina, Yvan, Fabio, Fred, Denis, Marie-Anne, Papa, Vincent, Andres, Alban, Komi, Sylvain, Sébastien P., Guillaume, Alexandru, Raphaël, Corentin, Tobias and Adrien. From Toulouse, I would like to thank Nicolas, Yoan, Paul, Farès and Franck.

Finally, I would like to express my gratitude to my parents and sisters for their courage, love and support, whatever the situation is.

# List of Figures

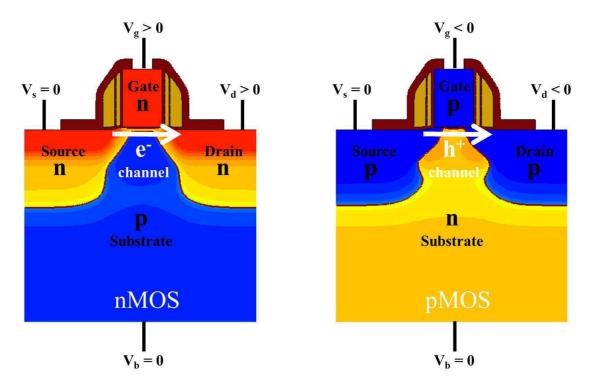

| 1.1 | nMOS and pMOS transistors two dimensional (2D) structures from TCAD simulations with silicon net doping (red: n-doping, blue: p-doping). Are also given the different terminals voltage conditions leading to a strong inversion regime (sub-section 1.2.3) with electrons and holes transfer between source and drain respectively for nMOS and                                                                                                          |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | pMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10  |

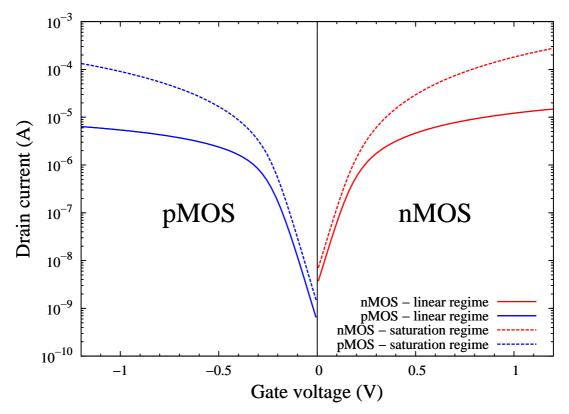

| 1.2 | nMOS and pMOS $I_d(V_g)$ characteristics in linear and saturation regimes from TCAD device simulations [21] for the transistors presented in Fig. 1.1 with a gate length                                                                                                                                                                                                                                                                                  | 1.0 |

| 1.3 | $L_g=3\mu m.$                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19  |

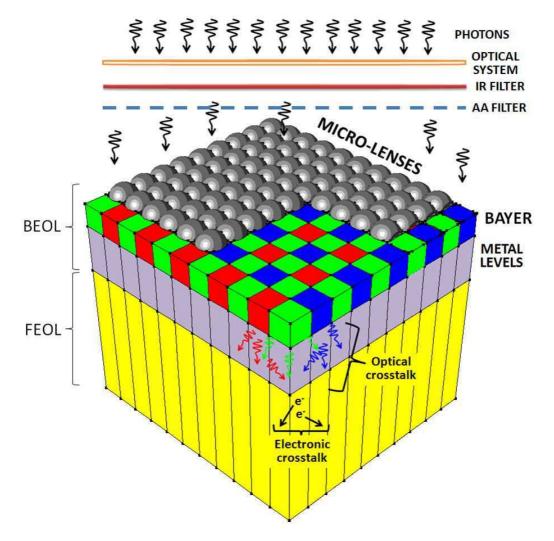

| 1.4 | part                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23  |

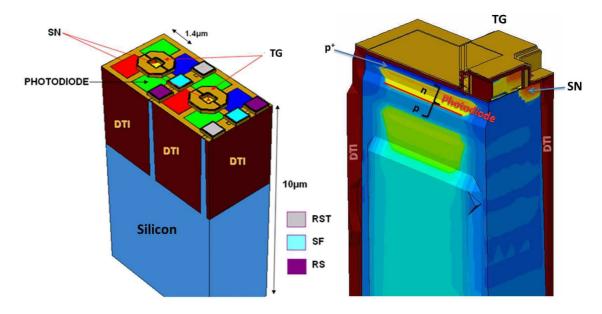

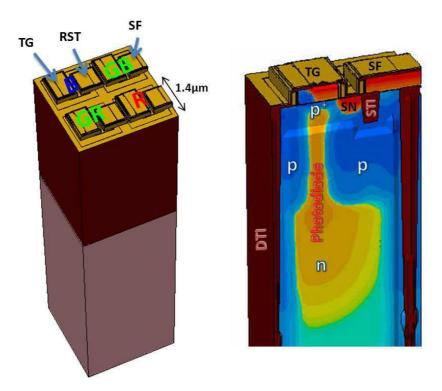

|     | in 1.3.3). Right: one pixel's doping is highlighted thanks to 3D TCAD simulations where the photodiode n-doped region can be evidenced in addition to the substrate p and surface p <sup>+</sup> pinning doping [28]                                                                                                                                                                                                                                      | 24  |

| 1.5 | Left: Bayer pattern with four pixels of 1.4 $\mu$ m pitch with a vertical photodiode manufactured at STMicroelectronics, and their main transistors including the TG, the RST and the SF, the different pixels being isolated thanks to DTIs. Right: one pixel's doping is highlighted thanks to 3D TCAD simulations [28] where the vertical photodiode n-doped region can be evidenced in addition to the vertical and surface $p^+$ pinning doping [31] | 27  |

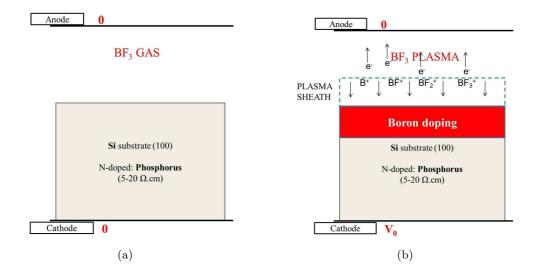

| 2.1 | PULSION <sup>®</sup> plasma doping tool characteristics: (a) at zero voltage and (b) with applied negative voltage $V_0$ at the cathode connected to the sample holder                                                                                                                                                                                                                                                                                    | 44  |

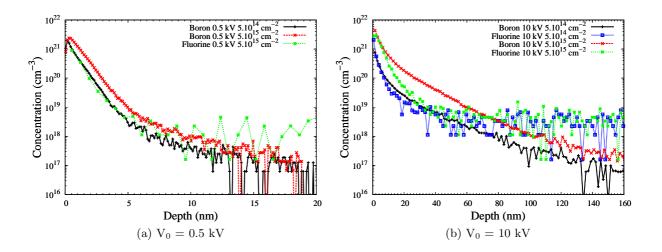

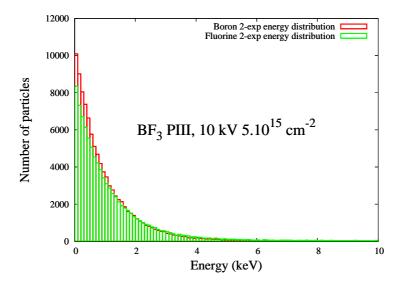

| 2.2 | SIMS as implanted profiles for (a) $0.5 \text{ kV BF}_3$ plasma acceleration voltage for boron at $5.10^{14} \text{ cm}^{-2}$ and boron and fluorine at $5.10^{15} \text{ cm}^{-2}$ and (b) for $10 \text{ kV BF}_3$ plasma acceleration voltage for boron and fluorine at $5.10^{14} \text{ and } 5.10^{15} \text{ cm}^{-2}$                                                                                                                             | 47  |

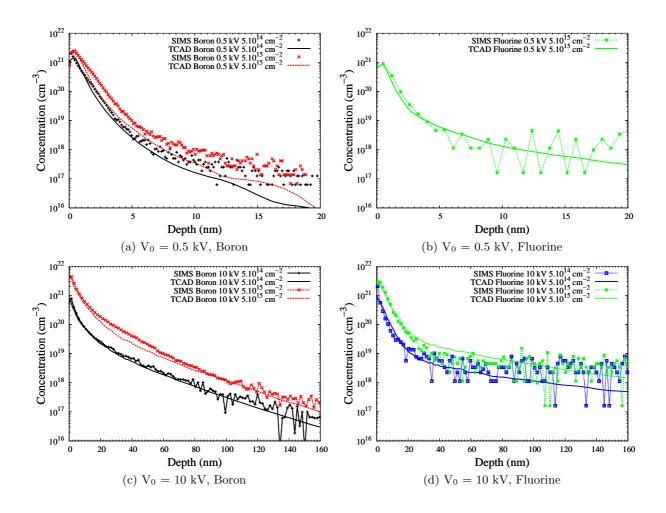

| 2.3 | SIMS versus TCAD as implanted profiles using 2-exp energy distribution of equation 2.2 with the set of parameters of table 2.2 for 0.5 kV BF <sub>3</sub> plasma acceleration voltage for (a) boron, (b) fluorine and for 10 kV BF <sub>3</sub> plasma acceleration voltage for (c) boron and                                                                                                                                                             |     |

| 2.4 | (d) fluorine                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50  |

|     | of table 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50  |

vi LIST OF FIGURES

| 2.5  | Amorphous depth from TEM measurements and TCAD simulations for the different PIII samples of table 2.1                                                                                                                                                                                                                                                                           | 51 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

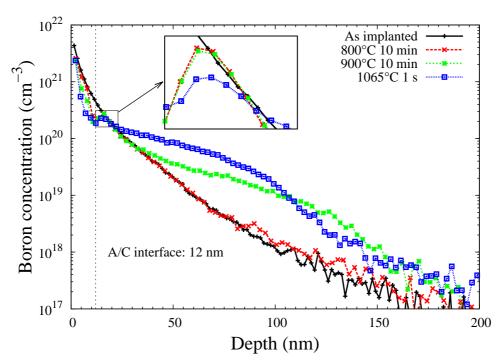

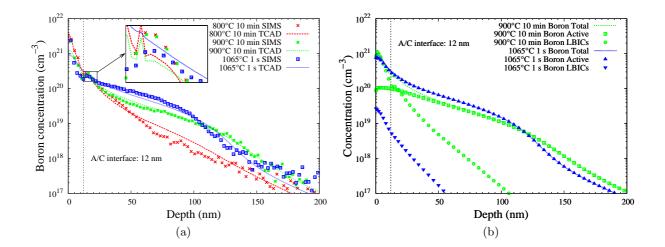

| 2.6  | Boron SIMS profiles following a BF <sub>3</sub> PIII at $10 \text{ kV } 5.10^{15} \text{ cm}^{-2}$ annealed at $800^{\circ}\text{C } 10 \text{ min}$ , $900^{\circ}\text{C } 10 \text{ min}$ and $1065^{\circ}\text{C } 1 \text{ s}$ . A boron peak below the A/C interface is observed for the different thermal anneals                                                        | 52 |

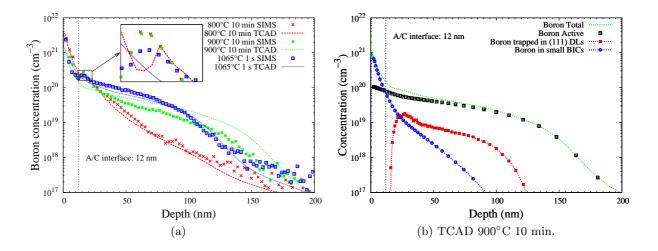

| 2.7  | (a) Boron SIMS versus TCAD profiles using state-of-the-art SProcess models [3] following a BF $_3$ PIII at 10 kV $5.10^{15}$ cm $^{-2}$ annealed at $800^{\circ}$ C 10 min, $900^{\circ}$ C 10 min and $1065^{\circ}$ C 1 s, and (b) details of boron concentration including total boron, active boron, boron in (111) DLs and small BICs for the $900^{\circ}$ C 10 min anneal | 53 |

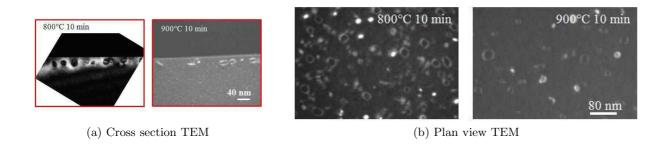

| 2.8  | TEM (a) cross-section where (001) DLs corresponding to LBICs are observed below the A/C interface and (b) plan-view images with a [400] diffracting vector $\mathbf{g}$ of the BF <sub>3</sub> PIII samples at 10 kV $5.10^{15}$ cm <sup>-2</sup> and annealed at $900^{\circ}$ C and $900^{\circ}$ C $10$ min                                                                   | 53 |

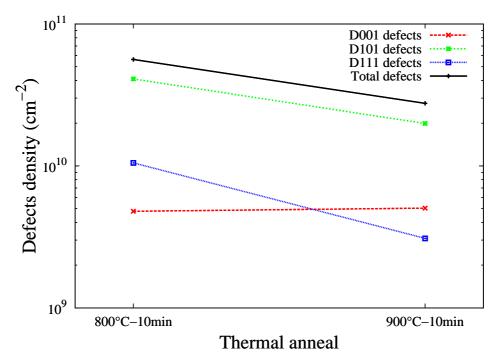

| 2.9  | Defects density measured from TEM WBDF images for BF $_3$ PIII at 10 kV 5.10 $^{15}$ cm $^{-2}$ annealed at 800°C and 900°C 10 min including D001, D101, D111 defects(table 2.3) and total EOR defects                                                                                                                                                                           | 54 |

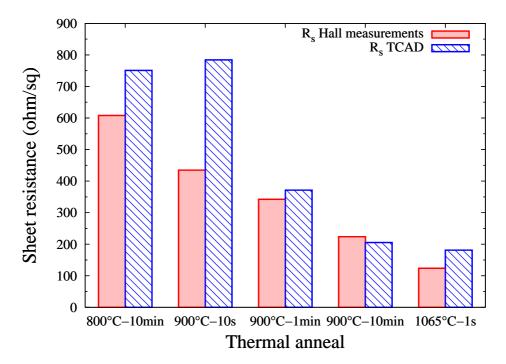

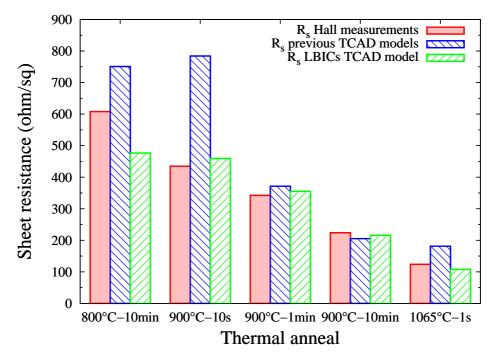

| 2.10 | $\rm p+/n~PIII~BF_3$ junctions sheet resistance extracted from Hall effect measurements for different thermal anneals of table 2.1 compared to TCAD state-of-the-art process models.                                                                                                                                                                                             | 55 |

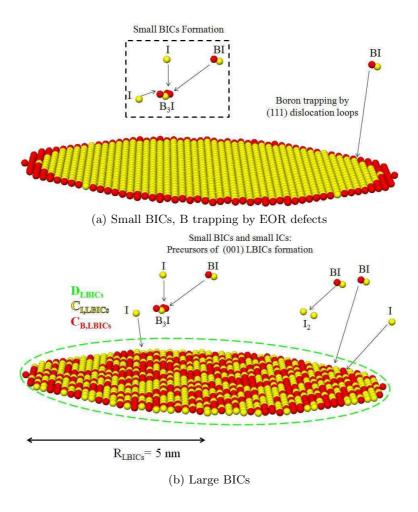

| 2.11 | Diagram showing boron interaction with silicon interstitial atoms in (a) default advanced continuum TCAD models and (b) using the LBICs model based on moments approach [51]. The atomistic view shown here is explanatory and only continuum simulations were carried out in our work.                                                                                          | 58 |

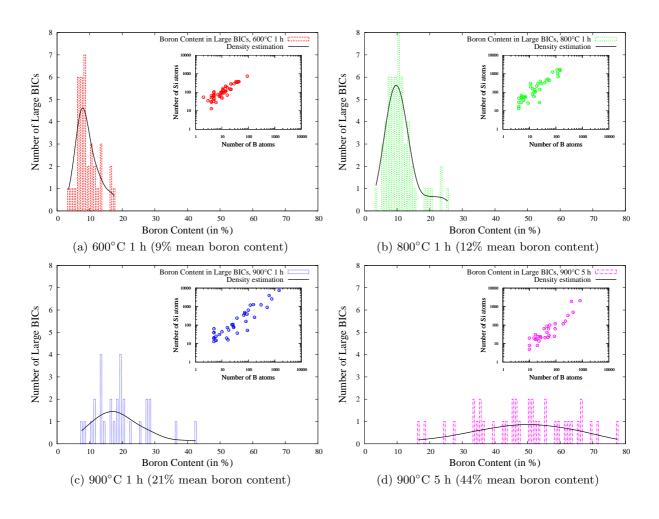

| 2.12 | Histogram distribution of boron content in the LBICs from [45] following a boron implant at 10 keV 5.10 <sup>15</sup> cm <sup>-2</sup> implant annealed at (a) 600°C 1 h, (b) 800°C 1 h, (c) 900°C 1 h and (d) 900°C 5 h                                                                                                                                                         | 63 |

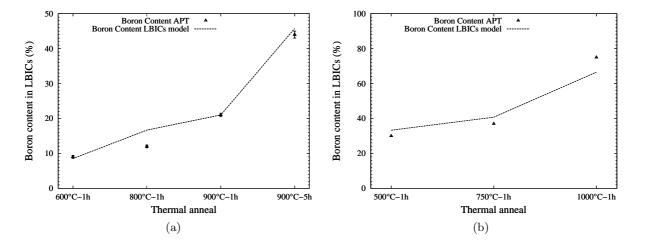

| 2.13 | Boron content in the LBICs from APT measurements and LBICs model simulations following a boron implant at (a) 10 keV $5.10^{15}$ cm <sup>-2</sup> , annealed at 600, 800 and 900°C 1 h and 900°C 5 h from Cojocaru-Mirédin et al. work [45] and (b) 27 keV $1.10^{17}$ cm <sup>-2</sup> annealed at 500, 750 and 1000°C 1 h from Blavette et al. work [46]                       | 63 |

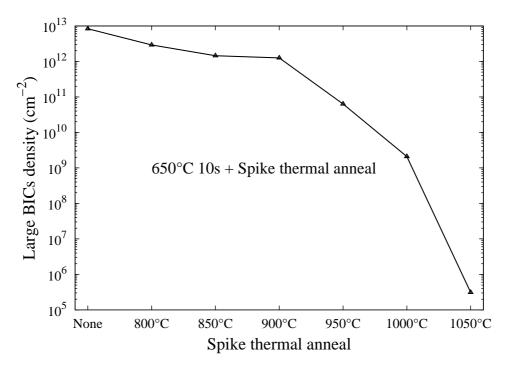

| 2.14 | LBICs density evolution using the LBICs model for a shallow boron implant at 0.5 keV 5.10 <sup>15</sup> cm <sup>-2</sup> from Cristiano et al. work [35, 63] annealed at 650°C 10 s (None) and followed by subsequent spike anneals at 800, 850, 900, 950, 1000 and 1050°C                                                                                                       | 64 |

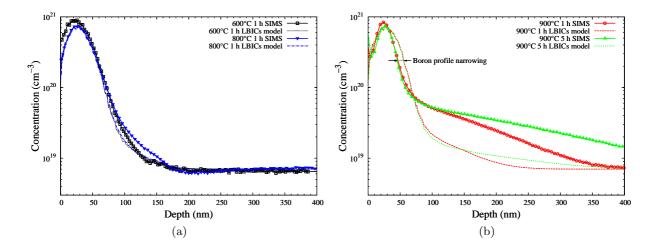

| 2.15 | Boron 10 keV 5.10 <sup>15</sup> cm <sup>-2</sup> annealed at (a) 600°C and 800°C during 1 hour and (b) 900°C during 1 and 5 hours from SIMS results [45] and using our LBICs model. Boron profile narrowing is observed experimentally in the precipitation region for the two 900°C anneals.                                                                                    | 61 |

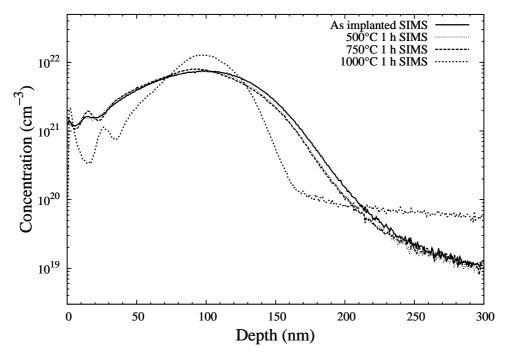

| 2.16 | Boron 27 keV 1.10 <sup>17</sup> cm <sup>-2</sup> as implanted and annealed at 500, 750 and 1000°C during one hour SIMS profiles [46]. Boron profile narrowing in the precipitation region is observed for the different thermal anneals and is very pronounced for the 1000°C anneal                                                                                             | 65 |

| 2.17 | (a) Boron SIMS versus TCAD profiles using the LBICs model following a BF <sub>3</sub> plasma implant at 10 kV 5.10 <sup>15</sup> cm <sup>-2</sup> annealed at 800°C 10 min, 900°C 10 min and 1065°C 1 and (b) boron detailed TCAD profiles at 900°C 10 min and 1065°C 1 s, including concentrations of total boron, active boron and boron in the LBICs                          | 67 |

| 2.18 | p+/n PIII BF <sub>3</sub> junctions sheet resistance extracted from Hall effect measurements for different thermal anneals of table 2.1 and compared to TCAD simulations using previous TCAD models [17] in comparison to the LBICs model [69]                                                                                                                                   | 67 |

LIST OF FIGURES vii

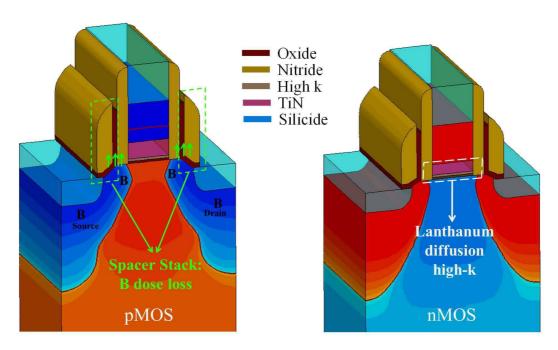

| 3.1  | Diagram of the different materials (silicon, oxide, nitride, high-k, TiN metal gate and silicide) and interfaces between materials of a pMOS transistor (left) where we show the LDD and source/drain boron (B) doped regions (green square) in silicon relatively to the position of the spacer stack and corresponding boron dose loss from silicon to be presented in section 3.2 and a nMOS transistor (right) gate stack region (white square) with the interfacial oxide, the high-k and the TiN metal gate where lanthanum diffusion will take place as it will be presented in section 3.3 | 76 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

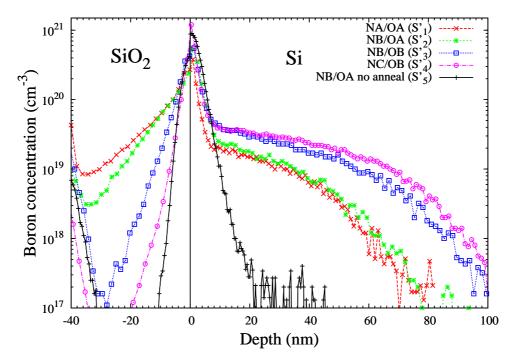

| 3.2  | Boron SIMS results for samples $S'_1$ to $S'_4$ (table 3.1) with different nitride/oxide/silicon spacer stacks annealed at $1000^{\circ}$ C 2 min, in addition to NB/OA $S'_5$ reference sample before annealing                                                                                                                                                                                                                                                                                                                                                                                   | 79 |

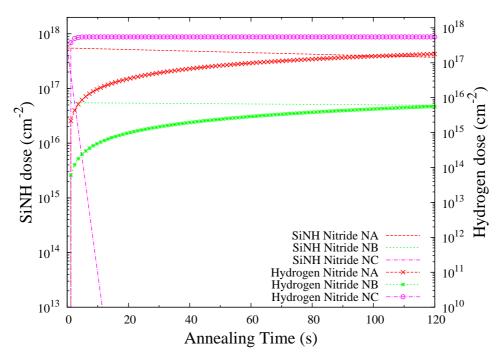

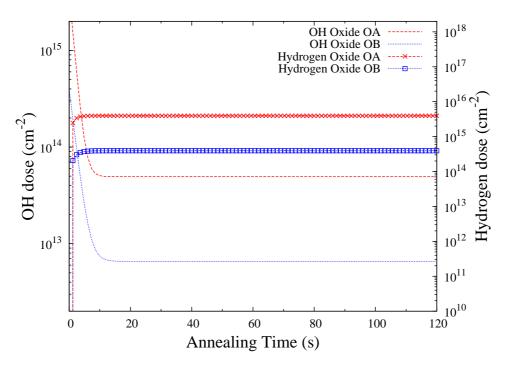

| 3.3  | Temporal evolution of SiNH bonds (lines) and hydrogen (lines + symbols) density for homogeneous isolated nitrides NA, NB and NC during the 1000°C 2 min anneal using the analytical solutions 3.14 and 3.15                                                                                                                                                                                                                                                                                                                                                                                        | 83 |

| 3.4  | Temporal evolution of OH bonds (lines) and hydrogen (lines + symbols) density for homogeneous isolated oxides OA and OB during the 1000°C 2 min anneal using the analytical solutions 3.16 and 3.17                                                                                                                                                                                                                                                                                                                                                                                                | 84 |

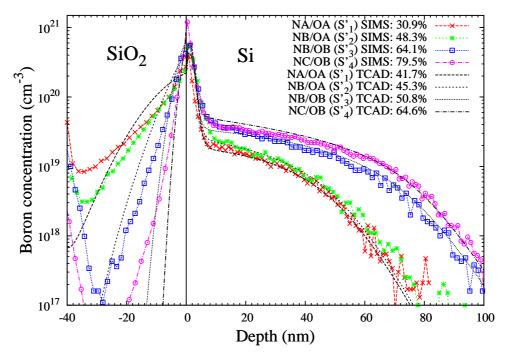

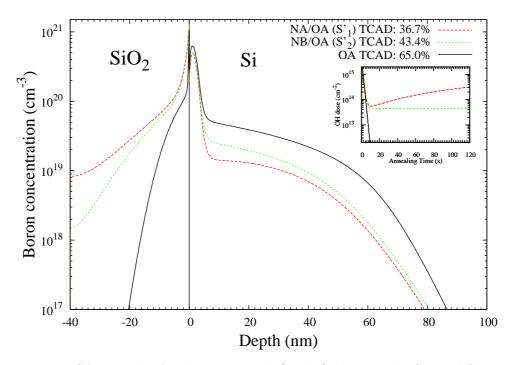

| 3.5  | Boron SIMS versus TCAD results for samples S' <sub>1</sub> to S' <sub>4</sub> (table 3.1) using equation 3.18 for boron diffusion in oxide, in association with equations 3.8, 3.9, 3.10 and 3.11 for hydrogen related species temporal evolution. Final percentage of boron dose loss in silicon after anneal is also given in the legend                                                                                                                                                                                                                                                         | 86 |

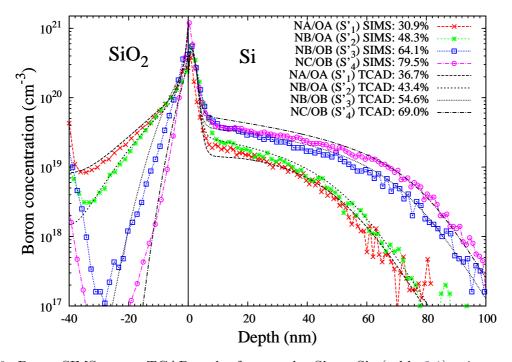

| 3.6  | Boron SIMS versus TCAD reults for samples $S'_1$ to $S'_4$ (table 3.1) using equations 3.20 and 3.21 for boron diffusion in oxide with the long hop mechanism, in association with equations 3.8, 3.9, 3.10 and 3.11 for hydrogen related species temporal evolution. Final percentage of boron dose loss in silicon after anneal is also given in the legend                                                                                                                                                                                                                                      | 87 |

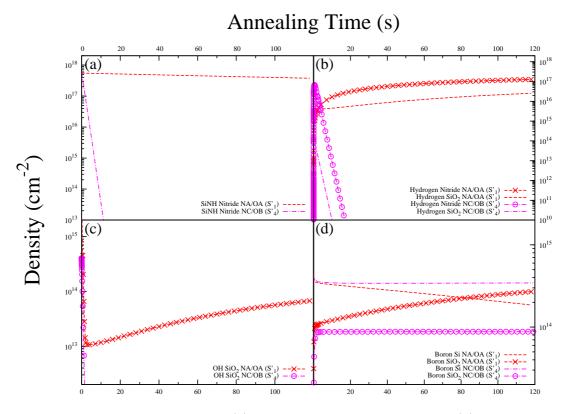

| 3.7  | TCAD temporal evolution of (a) SiNH bonds density in nitride, (b) hydrogen density in nitride and oxide, (c) OH bonds density in oxide and (d) boron density in oxide and silicon for samples S' <sub>1</sub> and S' <sub>4</sub> during the 1000°C 2 min anneal using equations 3.8, 3.9, 3.10 and 3.11 for hydrogen related species and equations 3.20 and 3.21 for boron diffusion in oxide                                                                                                                                                                                                     | 89 |

| 3.8  | Boron TCAD results for the two nitride/oxide/silicon stacks S' <sub>1</sub> and S' <sub>2</sub> , in comparison to a simple oxide(OA)/silicon stack showing the capability of the model in reproducing the capping effect of nitride on hydrogen degassing during the 1000°C 2 min thermal anneal. Final percentage of boron dose loss in silicon is also given in the legend                                                                                                                                                                                                                      | 90 |

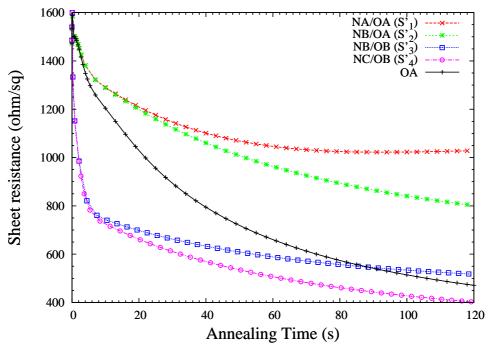

| 3.9  | TCAD temporal evolution of sheet resistance $R_s$ for samples $S'_1$ to $S'_4$ (table 3.1) and the simple oxide(OA)/silicon stack (Fig. 3.8) during the 1000°C 2 min thermal anneal.                                                                                                                                                                                                                                                                                                                                                                                                               | 90 |

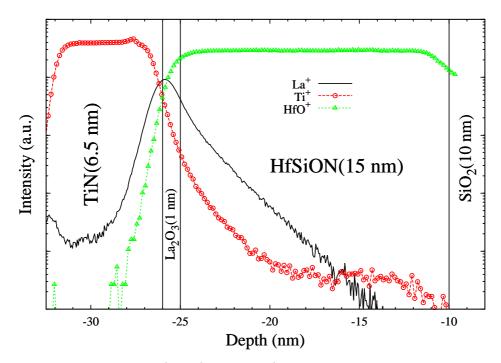

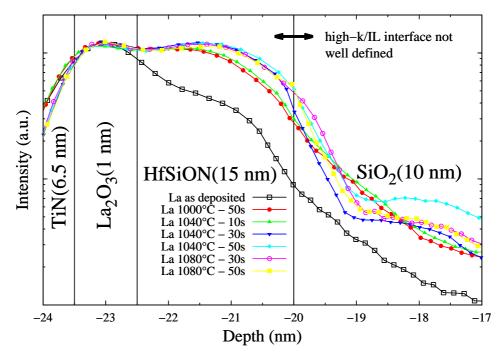

| 3.10 | SIMS profiles for La $^+$ , Ti $^+$ and HfO $^+$ in the as-deposited (non annealed) sample of table 3.5 for the HfSiON(15 nm)/SiO <sub>2</sub> (10 nm) stack                                                                                                                                                                                                                                                                                                                                                                                                                                       | 94 |

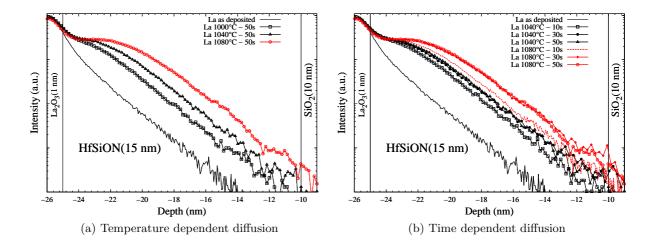

| 3.11 | La SIMS profiles for thermal anneals at (a) 1000, 1040 and 1080°C during 50 s where we can see that the La diffusion in HfSiON is thermally activated and (b) 1040 and 1080°C during 10, 30 and 50 s for each temperature where La diffusion saturation versus time is observed                                                                                                                                                                                                                                                                                                                    | 94 |

| 3.12 | La SIMS profiles for series (ii) samples (table 3.5) with a thin HfSiON (2.5 nm) high-k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 95 |

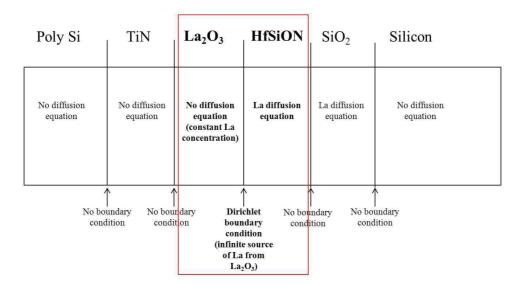

| 3.13 | Diagram of the different materials and interfaces in the ${\rm TiN/La_2O_3/HfSiON/SiO_2/Si}$ stack and their related equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 96 |

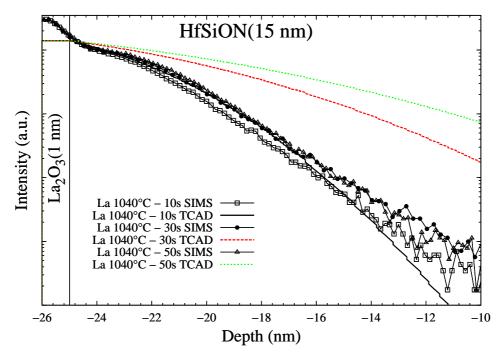

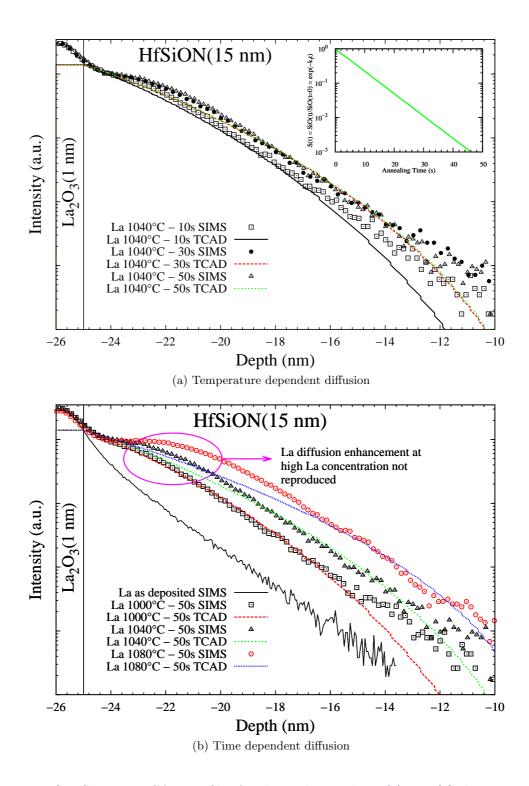

| 3.14 | La SIMS versus TCAD profiles for thermal anneal at 1040°C during 10, 30 and 50 s, using equation 3.24 where La diffusion saturation versus time of anneal is not reproduced.                                                                                                                                                                                                                                                                                                                                                                                                                       | 97 |

viii LIST OF FIGURES

| 3.15 | La SIMS versus TCAD profiles for thermal anneals at (a) 1040°C during 10, 30 and 50 s using equation 3.28 where La diffusion saturation is correctly reproduced and (b) at 1000, 1040 and 1080°C during 50 s using equation 3.28 where La thermally activated diffusion is correctly reproduced, except near the La <sub>2</sub> O <sub>3</sub> /HfSiON interface with a high La concentration                                                             | 99                                |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

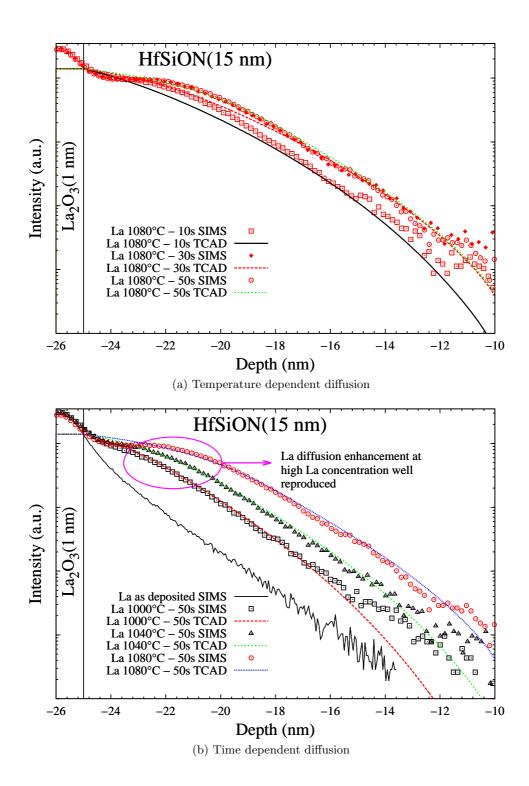

| 3.16 | La SIMS versus TCAD profiles for thermal anneals at (a) 1040°C during 10, 30 and 50 s using equation 3.29 where La diffusion saturation is correctly reproduced and (b) at 1000, 1040 and 1080°C during 50 s using equation 3.29 where La thermally activated diffusion is correctly reproduced, including near the La <sub>2</sub> O <sub>3</sub> /HfSiON interface with a high La concentration                                                          | 100                               |

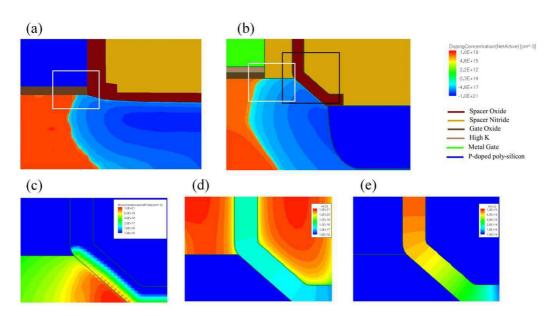

| 4.1  | 2D process simulations after a 1000°C spike anneal with a S' <sub>1</sub> (table 3.1) sample based spacer stack of (a) 45 nm and (b) 28 nm technology node pMOS transistor with the corresponding doping profiles in silicon. The boron doped LDD region is white framed. The 2D concentration profiles of boron, free hydrogen and OH bonds contained in the black framed region of the 28 nm transistor (b) are shown in (c), (d) and (e), respectively. | .108                              |

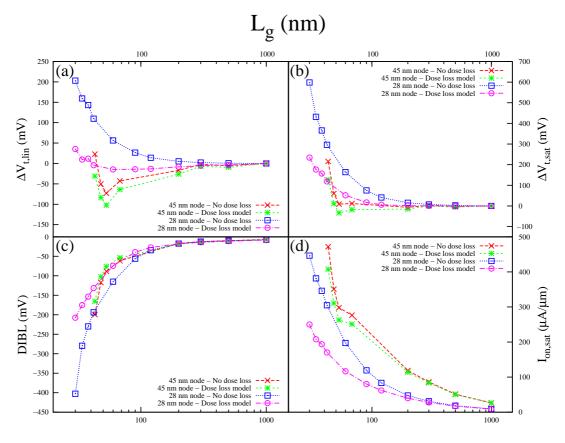

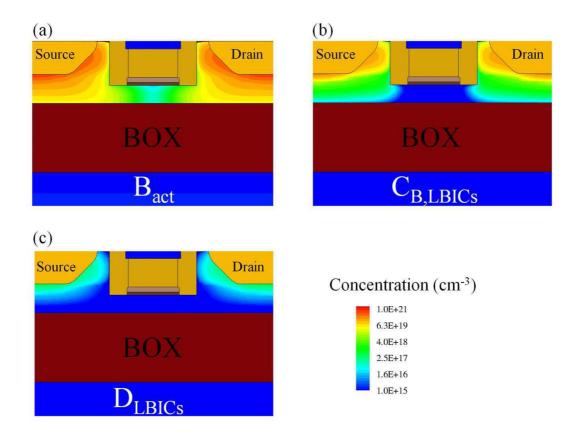

| 4.2  | 45 nm and 28 nm technology node pMOS transistors electrical characteristics versus gate length including (a) $\Delta V_{t,lin}(L_g)$ , (b) $\Delta V_{t,sat}(L_g)$ , (c) DIBL (L <sub>g</sub> ) and (d) $I_{on,sat}(L_g)$ following 2D device simulations with and without boron dose loss model                                                                                                                                                           | 109                               |

| 4.3  | 2D process simulations using large BICs continuum model on FDSOI pMOS transistor of 28 nm gate length using $BF_2$ implantation condition $C_1$ of table 4.1 including (a) boron active concentration, (b) boron in the LBICs concentration $C_{B,LBICs}$ and (c)                                                                                                                                                                                          |                                   |

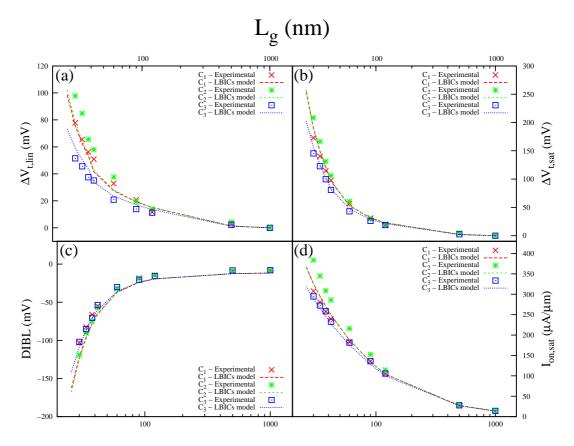

| 4.4  | LBICs density $D_{LBICs}$                                                                                                                                                                                                                                                                                                                                                                                                                                  | 111                               |

| 4.5  | LBICs continuum model developed in 2.4.2                                                                                                                                                                                                                                                                                                                                                                                                                   | 112                               |

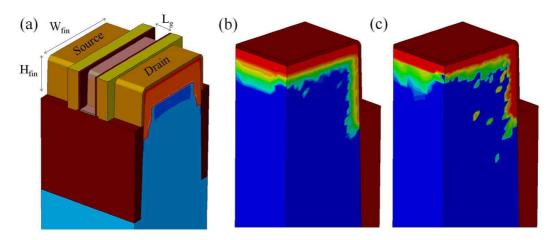

| 4.6  | conformal aspect of the implant can be noticed                                                                                                                                                                                                                                                                                                                                                                                                             | 114                               |

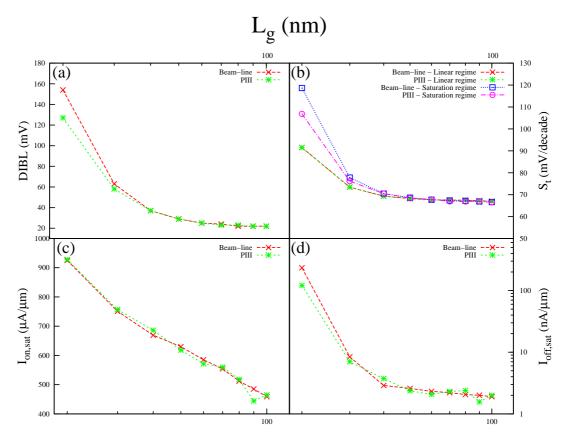

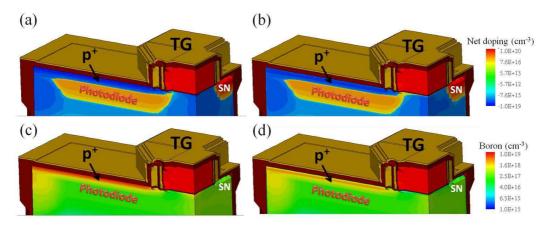

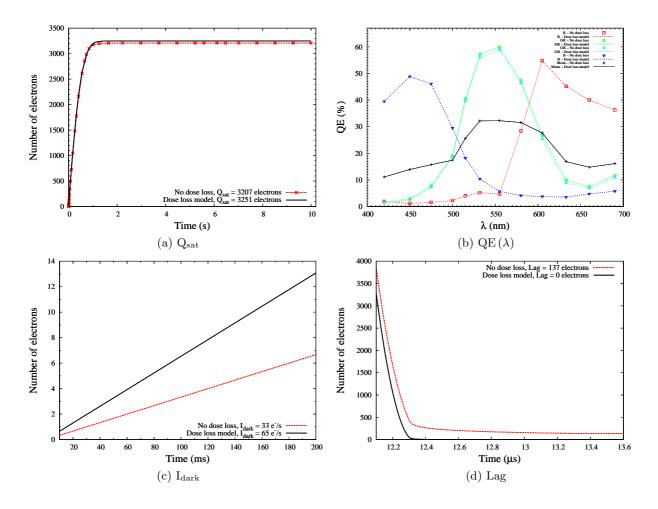

| 4.7  | and $S_{t,sat}$ ( $L_g$ ), (c) $I_{on,sat}$ ( $L_g$ ) and (d) $I_{off,sat}$ ( $L_g$ ) following 3D device simulations 3D process simulations of 1.4 $\mu m$ FSI pixels including (a) net doping concentration without and (b) with boron dose loss model. Is also shown boron concentration (c) without and (d) with boron dose loss model                                                                                                                 | <ul><li>115</li><li>117</li></ul> |

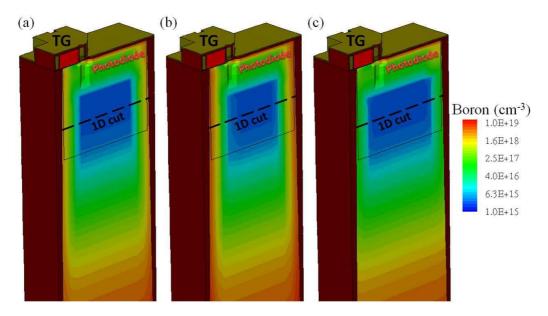

| 4.8  | Electro-optical device simulation results for 1.4 $\mu m$ FSI pixels without and with boron dose loss model of 3.2 including (b) $Q_{sat}$ , (a) $QE(\lambda)$ characteristics, (c) $I_{dark}$ and (d)                                                                                                                                                                                                                                                     |                                   |

| 4.9  | electrons lag                                                                                                                                                                                                                                                                                                                                                                                                                                              | 118                               |

|      | are shown in Fig. 4.10                                                                                                                                                                                                                                                                                                                                                                                                                                     | 119                               |

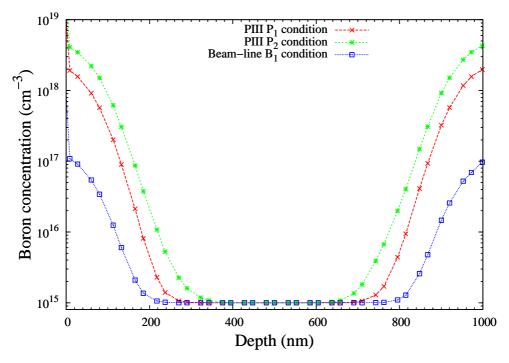

| 4.10 | Boron 1D profiles following the 1D cut of 3D simulated structures shown in Fig. 4.9 for implantation conditions PIII $P_1$ , PIII $P_2$ and beam-line implantation $B_1$                                                                                                                                                                                                                                                                                   | 120                               |

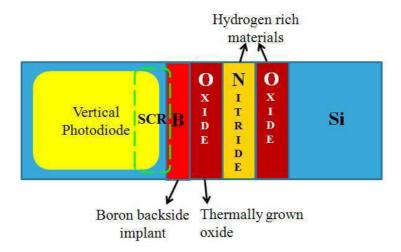

| 4.11 | Diagram presenting the 1D system of backside boron dose loss in the ONO stack. The oxide directly in contact with boron is thermally grown. Remaining nitride and oxide layers are deposited using CVD techniques. SCR of n-type vertical photodiode is also                                                                                                                                                                                               | 14(                               |

|      | presented                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 122                               |

LIST OF FIGURES ix

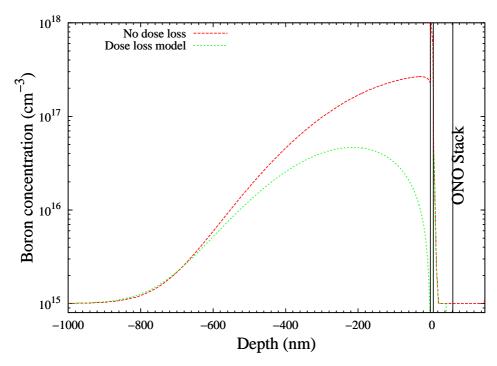

| 4.12 | Boron 1D profiles at the backside interface with the ONO stack without and with boron                                            |     |

|------|----------------------------------------------------------------------------------------------------------------------------------|-----|

|      | dose loss model                                                                                                                  | 123 |

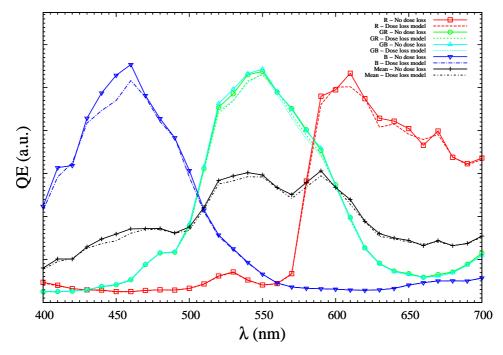

| 4.13 | $\mathrm{QE}\left(\lambda\right)$ characteristics of a 3D Bayer structure of 2 $\mu\mathrm{m}$ BSI pixels with and without       |     |

|      | backside boron dose loss in the ONO stack                                                                                        | 123 |

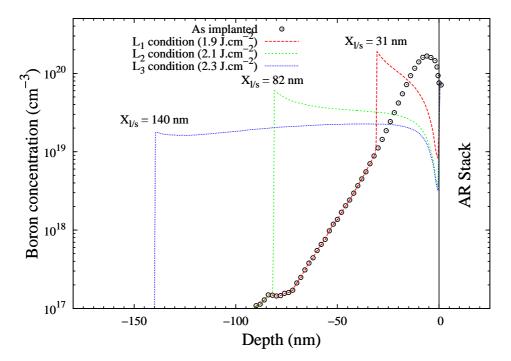

| 4.14 | Boron 1D profiles at the backside interface with the AR stack following LTA anneales                                             |     |

|      | using 1.9 (L <sub>1</sub> ), 2.1 (L <sub>2</sub> ) and 2.3 (L <sub>3</sub> ) $J.cm^{-2}$ laser energy density with corresponding |     |

|      | melt depth $X_{1/s}$                                                                                                             | 124 |

# List of Tables

| 1.1 | Summary of the different leakage current contributions in a p-n junction and corresponding activation energy [18]                                                                                                                                                                                                                                                                                                                                                     | 14       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1 | Summary of the different BF <sub>3</sub> PIII samples and corresponding experimental measure-                                                                                                                                                                                                                                                                                                                                                                         | 47       |

| 2.2 | ments presented in this chapter                                                                                                                                                                                                                                                                                                                                                                                                                                       | 47<br>49 |

| 2.3 | with $E_0$ the ion energy corresponding to the acceleration voltage $V_0$ Observed EOR defects using TEM in the PIII BF <sub>3</sub> at 10 kV $5.10^{15}$ cm <sup>-2</sup> annealed at $800^{\circ}$ C and $900^{\circ}$ C during 10 min, including defect category, Burgers vectors and defect                                                                                                                                                                       |          |

| 2.4 | nature Summary of literature experimental results used for LBICs continuum model calibration.                                                                                                                                                                                                                                                                                                                                                                         | 54<br>61 |

| 2.5 | LBICs model parameters [51] calibrated using the experimental data of 2.4                                                                                                                                                                                                                                                                                                                                                                                             | 61       |

| 3.1 | Summary of the samples used in this study. S' <sub>1</sub> to S' <sub>4</sub> are the nitride/oxide/silicon samples for boron SIMS measurements with the 1 keV 5.10 <sup>14</sup> cm <sup>-2</sup> BF <sub>2</sub> LDD implant, annealed at 1000°C during 2 min. A reference S' <sub>5</sub> similar to S' <sub>4</sub> but not annealed has also been preferred for the sake of comparison                                                                           | 78       |

| 3.2 | Summary of physical parameters of the different materials used in this study: $K(H)_{nit}$ and $D(H)_{nit}$ (equations 3.8 and 3.9) extracted from coupled stress/TDS measurements [16] for nitrides NA to NC, initial SiNH bonds concentration SiNH <sub>0</sub> and OH bonds concentration OH <sub>0</sub> extracted from FTIR measurements for nitride NA to NC and oxide OA and OB. Nitrides density $\rho$ was obtained by simple weighing. Values at 1000°C are |          |

| 3.3 | in italic                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81       |

| 3.4 | Fig. 3.2. Different values between oxides OA and OB are in italic Summary of diffusion model parameters at 1000°C for boron in both oxides OA and                                                                                                                                                                                                                                                                                                                     | 85       |

|     | OB including the long hop mechanism from equations 3.20 and 3.21                                                                                                                                                                                                                                                                                                                                                                                                      | 87       |

| 3.5 | Deposit and anneal details of the samples designed in order to study La diffusion in TiN/La <sub>2</sub> O <sub>3</sub> /HfSiON/SiO <sub>2</sub> /Si high-k stacks                                                                                                                                                                                                                                                                                                    | 93       |

| 3.6 | Summary of the different models used in this work, and their related parameters and characteristics                                                                                                                                                                                                                                                                                                                                                                   | 98       |

| 4.1 | Summary of the different BF <sub>2</sub> source/drain implantation conditions investigated experimentally on FDSOI pMOS transistors with gate lengths between 28 nm and 1 $\mu$ m                                                                                                                                                                                                                                                                                     | 110      |

| 4.2 | Electrical features including $Q_{\rm sat}$ and $I_{\rm dark}$ obtained from 3D simulations for the different                                                                                                                                                                                                                                                                                                                                                         |          |

| 4.3 | DTIs implantation conditions of 1.4 $\mu$ m FSI pixels, assuming identical interface traps. Electrical features including $Q_{sat}$ and $I_{dark}$ obtained from 3D simulations for the different                                                                                                                                                                                                                                                                     | 120      |

|     | backside boron LTA conditions of 1.1 $\mu$ m BSI pixels                                                                                                                                                                                                                                                                                                                                                                                                               | 125      |

## List of abbreviations

AA Anti Aliasing

A/C Amorphous/Crystalline

APS Active Pixel Sensor

APT Atom Probe Tomography

**AR** Anti Reflective

**BBT** Band to Band Tunnelling

**BEOL** Back End Of Line

BIC Boron Interstitial Cluster

BJT Bipolar Junction Transistor

**BOX** Buried Oxide

**BSI** Back Side Illumination

**CCD** Charged Coupled Devices

**CDF** Cumulative Distribution Function

CMOS Complementary Metal Oxide Semiconductor

CPU Central Processing UnitCVD Chemical Vapour Deposition

**DIBL** Drain Induced Barrier Lowering

**DL** Dislocation Loop

DPN Decoupled Plasma NitridationDRAM Dynamic Random Access Memory

**DTI** Deep Trench Isolation

**EOR** End Of Range

**EOT** Equivalent Oxide Thickness

**ETSOI** Extremely Thin Silicon On Insulator

**EWF** Effective Work Function

FDL Frank (or Faulted) Dislocation Loop FDSOI Fully Depleted Silicon On Insulator FDTD Finite Difference Time Domain

FEM Finite Elements Method FEOL Front End Of Line

FinFET Fin Field Effect Transistor FSI Front Side Illumination FTIR Fourier Transform Infrared

**GAA** Gate All Around

GIDL Gate Induced Drain Leakage

GR Generation Recombination

**HP** High Performance

**HRD** Hydrogen Related Defect

IC Integrated Circuit or Interstitial Cluster

IL Interfacial Layer

IR Infra Red

ITRS International Technology Roadmap for Semiconductors

**KMC** Kinetic Monte Carlo

LBIC Large Boron Interstitial Cluster

LDD Lightly Doped Drain

**LKMC** Lattice Kinetic Monte Carlo

**LP** Low Power

**LPCVD** Low Pressure Chemical Vapour Deposition

LTA Laser Thermal Anneal LPE Liquid Phase Epitaxy

MC Monte Carlo

MEMS Micro Electro Mechanical System

MG Metal Gate

MIS Metal Insulator Silicon MLA Melting Laser Anneal

MOCVD Metal Organic Chemical Vapour Deposition

MOS Metal Oxide Semiconductor

nMOS negative (type) Metal Oxide Semiconductor

**ONO** Oxide Nitride Oxide

PDE Partial Differential Equation

PDL Perfect Dislocation Loop

PECVD Plasma Enhanced Chemical Vapour Deposition

PIII Plasma Immersion Ion Implantation

PLD Peroxy Linkage Defect

pMOS positive (type) Metal Oxide Semiconductor

PVD Physical Vapour Deposition

**QE** Quantum Efficiency

**R&D** Research and Development

RS Row Select

RST Reset Transistor

RTA Rapid Thermal Anneal

RTA Rapid Thermal Processing

SCE Short Channel Effect

SF Source Follower

SCR Space Charge Region

SIMS Secondary Ion Mass Spectrometry

SN Sense Node

SOI Silicon On Insulator

SPERSolid Phase Epitaxial RegrowthSRAMStatic Random Access Memory

SRH Shockley Read Hall

STI Shallow Trench Isolation

TAT Trap Assisted Tunnelling

TCADTechnology Computer Aided DesignTDSThermal Desorption SpectroscopyTEDTransient Enhanced DiffusionTEMTransmission Electron Microscopy

TG Transfer Gate

**ToF-SIMS** Time of Flight Secondary Ion Mass Spectrometry

TTL Transistor Transistor Logic

**USJ** Ultra Shallow Junction

WBDF Weak Beam Dark Field

### Introduction

Transistors play a key role in modern electronics, and clearly modified our society thanks to innovative applications with a direct impact on our everyday's life. Metal oxide semiconductor (MOS) transistors and related electronic components shrinking size led to the birth of modern microelectronics and the definition of the famous Moore's law by Gordon E. Moore in 1965, according to which the number of transistors on integrated circuits (ICs) doubles approximately every two years [1]. Moore's prediction was more or less satisfied during the last fifty years following the miniaturization of MOS transistors thanks to continually increasing research and development efforts of the semiconductor industry. Miniaturization allowed increasing the number of components in ICs, extending their functionalities. Nowadays, complementary MOS (CMOS) technology is used in several ICs such as microprocessors, microcontrollers, memories, image sensors and others. The semiconductor industry markets are therefore constantly expanding and diversifying. ICs are currently used in several applications [2]: data processing (personal computers, laptops, servers and tablets), communications (mobile phones, smartphones ...), consumer electronics (television sets, music players, gaming consoles ...), automotive, industrial (transport...), military in addition to spatial and medical applications.

According to the International Technology Roadmap for Semiconductors (ITRS) 2011 [3], two main improvement trends are followed by the different actors of the semiconductor industry:

- Miniaturization, or integration level expressed by Moore's law related to shrinking CMOS devices with a direct consequence on cost-per-function decrease. The miniaturization in microelectronics concerns "More Moore" devices and their corresponding scaling from a technology node to another <sup>1</sup>. "More Moore" elements evolution is related to technology node reduction. Currently, the most advanced CMOS commercially available products use 22 nm technology node and R&D efforts for 14 nm node are made by the leading semiconductor companies. "More Moore" elements correspond historically to core CMOS devices such as MOS transistors used in logic circuits and other memory devices.

- Diversification, corresponding to "More than Moore" elements according to ITRS 2011 [3], which are an emerging category of devices integrating additional functionalities that do not necessarily scale according to Moore's law, but provide additional values and functions in CMOS products.

Therefore, semiconductor industry is facing both miniaturization and diversification challenges and the latter's weight is expected to expand over the next years leading to the "pure microelectronics" interaction with other scientific fields in order to maintain progress and innovation. The example of modern mobile phones known as smartphones as a final product addressed by semiconductor companies is quite interesting. Indeed in a smartphone, one can find on one side "More Moore" elements such as MOS transistors in the processors and other memory devices such as Flash and DRAM. On another side, "More than Moore" elements can be found, as the image sensors used in up to two

<sup>&</sup>lt;sup>1</sup>The term "technology node" used here is defined as the smallest half-pitch of contacted metal-lines on a given CMOS product [3]. Historically, dynamic random access memory (DRAM) device had the highest integration level among CMOS devices, and was used for "technology node" definition.

6 INTRODUCTION

camera modules in the phone. Microelectromechanical systems (MEMS) can also be found such as the accelerometer used for screen rotation. Therefore, from the particular example of smartphones, one can see that semiconductor companies have to solve both miniaturization and diversification challenges in order to stay competitive.

Among "More than Moore" elements concerned with both miniaturization and diversification issues, image sensors are also a very good example. In fact, image sensors followed the miniaturization trend which enhanced their electrical performances. In addition, their extra-functionalities would not have been possible without answering the diversification challenges.

Image sensors market is continually growing and the same trend is expected for the next years [4, 5]. Image sensors cover applications in consumer electronics such as mobile phones, cameras, in addition to security, surveillance, automotive, medical and spatial applications. Their market includes two main categories: charge coupled devices (CCD) sensors discovered in 1970 by W. S. Boyle and G. E. Smith [6], 2009 Nobel's prize [7] and CMOS image sensors based on CMOS technology, invented in 1960 by S. R. Morrison [8]. The cost-effectiveness of CMOS image sensors in comparison to CCD sensors and their easy integration in a CMOS technology scheme gave them a leading role in image sensors market. As a consequence, semiconductor companies quickly became the main actors in this field.

As for core CMOS devices, CMOS image sensors miniaturization is targeted by semiconductor companies in order to increase their electrical performances. Indeed, a CMOS image sensor is an array of pixels, each pixel containing a photo-detector and several MOS transistors in order to convert an optical image into and electrical signal. Thus, increasing the number of pixels is expected to improve the image resolution obtained by a CMOS image sensor. However, as for MOS transistors reducing pixels dimensions leads to several challenges to be solved in order to keep the required CMOS sensor performances.

In order to answer miniaturization and diversification challenges, CMOS devices processes had to continually evolve in order to meet technical requirements in terms of high performance, low operating power and low standby power [9]. Therefore, new materials, new implantation and annealing techniques were developed to answer these challenges and improve overall CMOS devices performances. The impact of such novel techniques on CMOS devices of both "More Moore" and "More Than Moore" categories has to be estimated and optimized. In addition to the direct physical effects observed during the devices fabrication, remaining undesired chemical species configurations may have a direct impact on the performances of the final CMOS devices. Therefore, in addition to the development of such new techniques, their constant evaluation has to be made to avoid devices deterioration. Several conditions have to be tested before a given process step is chosen following the design and fabrication of a great number of samples. This approach is unavoidably time and money consuming in the highly competitive semiconductor industry. In addition, multiplying experimental investigations does not necessarily lead to a better physical understanding of the benefit or drawback introduced by a new process technique. To this regard, technology modelling and simulation can be used to study the physical mechanisms involved by such techniques, therefore making this strategy the best solution to reduce advanced CMOS development cycle, both in terms of time and cost [10]. Such modelling methodologies are called Technology Computer Aided Design (TCAD) and cover: process modelling of the different manufacturing steps and device modelling of the final active devices in their operational regime (electrical, optical ...).

Over the last two decades, thanks to important European but also worldwide R&D efforts, TCAD process and device simulations were able to predict with a sufficient accuracy most of the physical mechanisms occurring in advanced CMOS technologies. With the previously calibrated TCAD models

INTRODUCTION 7

for technology nodes above 45 nm, core CMOS devices behaviour can be correctly predicted without additional model calibration or development efforts. However, the implementation of new process techniques to improve high performance and low power requirements introduced new physical mechanisms to be accounted for in TCAD simulations. These new concepts referred to both "More Moore" and "More Than Moore" applications (such as CMOS image sensors) are not sufficiently covered by TCAD. Therefore, research collaborations between industrial and academic actors have to be established for a better understanding of physical mechanisms involved in advanced CMOS processes. The PhD thesis described in this report was proposed in this context and carried out in collaboration between STMicroelectronics Crolles and LAAS CNRS Toulouse in the frame of the European project ATEMOX [11] gathering several European industrial and academic partners. The project deals with the development of new TCAD models and improvement of existing ones in order to predict the physical mechanisms involved in advanced process techniques.

In particular, the objectives of my work concern modelling of advanced CMOS devices, answering both miniaturization and diversification challenges in CMOS technologies with a main focus on derivative applications of CMOS image sensors. Therefore, TCAD models should be able to reproduce all these different aspects by improving existing models and developing new models if needed.

The main challenges to be answered by the PhD work are:

- Improving dopants implantation and diffusion modelling in high implant-dose conditions such as those achieved by the plasma immersion ion implantation technique. In such case, diffusion and electrical activation mechanisms may be strongly influenced by the concurrent dopant precipitation phenomena, which are not yet well reproduced by existing TCAD physical models.

- Improving diffusion models of chemical species in multi-materials stacks, due to their expected impact on CMOS devices electrical behaviour. Boron dose loss in nitride/oxide/silicon stacks for instance, is not well understood on both experimental and modelling parts. The dose loss effect modifies electrical characteristics of CMOS based devices and its evaluation in TCAD models becomes mandatory. A second example is lanthanum diffusion in high-k stacks during thermal annealing leading to a negative threshold voltage shift in n-type MOS transistors.

These challenges were investigated during the PhD and the outline of the research activities presented in this report, is the following:

- Chapter 1 summarizes advanced CMOS technologies modelling challenges as well as the main physical concepts that represent the background of the PhD work.

- Chapter 2 deals with implantation-induced defects and their impact on dopant diffusion and activation mechanisms. In this chapter, plasma immersion ion implantation technique will be presented and investigated experimentally and using TCAD modelling, focusing on boron precipitation models for high implantation dose conditions, and corresponding boron diffusion and electrical activation.

- Chapter 3 considers chemical species diffusion in multi-materials stacks. Two main subjects are investigated: (i) boron dose loss in nitride/oxide/silicon stacks modifying electrical characteristics of advanced CMOS devices and (ii) lanthanum diffusion in advanced high-k stacks leading to a negative threshold voltage shift in advanced n-type MOS transistors.

- Chapter 4 deals with TCAD modelling of advanced CMOS devices. The different process models developed in previous chapters will be evaluated in terms of their impact on the electrical characteristics of several advanced MOS transistors, including Bulk, FDSOI and TriGate MOS, but also on FSI and BSI advanced CMOS image sensors.

8 LIST OF TABLES

### REFERENCES

[1] G. E. Moore, "Cramming more components onto integrated circuits," *Electronics Magazine*, vol. 38, no. 8, 1965.

- [2] W. Ballhaus, A. Pagella, C. Vogel, and C. Wilmsmeier, "Faster, greener smarter: Reaching beyond the horizon in the world of semiconductors," pwc.com/technology, 2012.

- [3] See ITRS 2011 Executive Summary chapter: http://www.itrs.net.

- [4] "Image sensors market analysis and forecast (2013 2018): By applications (healthcare (endoscopy, radiology, ophthalmology), surveillance, automobile, consumer, defense, industrial)); technology (CCD, CMOS, contact IS, infrared, X-ray) and geography," marketsandmarkets.com, 2013.

- [5] "Image sensors market in U.S. will reach USD 3.7 billion in 2017: Transparency market research," www.transparencymarketresearch.com, 2013.

- [6] W. S. Boyle and G. E. Smith, "Charge Coupled Semiconductor Devices," The Bell System Technical Journal, vol. 49, pp. 587–593, Apr. 1970.

- [7] Nobel Prize in Physics 2009: http://www.nobelprize.org.

- [8] S. Morrison, "A new type of photosensitive junction device," *Solid-State Electronics*, vol. 6, no. 5, pp. 485 494, 1963.

- [9] See ITRS 2011 Front End Processes chapter: http://www.itrs.net.

- [10] See ITRS 2011 Modeling and Simulation chapter: http://www.itrs.net.

- [11] ICT Project 258547 ATEMOX <u>A</u>dvanced <u>Te</u>chnology <u>Mo</u>deling for Extra-Functionality Devices, Website: http://www.atemox.eu.

## Chapter 1

# Advanced CMOS technologies modelling challenges

### 1.1 Introduction

In this chapter, we will summarize the main concepts of the work activities of the thesis. In section 1.2, a brief introduction to MOS transistor and CMOS technology will be given. In section 1.3, image sensors based on CMOS technology will be presented. Considering miniaturization and diversification challenges of CMOS technology, silicon level TCAD modelling will be presented in section 1.5 with an identification of possible improvements of existing models and missing ones.

### 1.2 A brief introduction to MOS transistor

The first pnp point-contact germanium transistor [1] was invented in 1947 by John Bardeen, Walter Brattain and William Shockley, Nobel laureates in Physics 1956 "for their researches on semiconductors and their discovery of the transistor effect" [2]. The following discoveries in semiconductor physics and mainly the development of the first silicon npn bipolar junction transistor (BJT) by Morris Tanenbaum et al. [3] at Bell Laboratories in 1954, clearly reshaped our modern society and the role played by electronics in everyday's life. Following the silicon bipolar transistor invention, Dawon Kahng and Martin M. (John) Atalla also from Bell Laboratories used an older concept of field effect transistor developed by Julius Edgar Lilienfeld in the 1920s [4] and achieved the first field effect metal oxide semiconductor (MOS) transistor in 1959 [5]. The ease of fabrication of MOS transistors and the advances made in fabrication process techniques quickly allowed the inventors to point out the transistor's role as a key component in integrated circuits (ICs). Indeed, combining n-type (electrons conduction) and p-type (holes conduction) MOS transistors, logic functions can be developed in the frame of CMOS technology, invested by Frank Wanlass at Fairchild Semiconductor in 1963 [6]. CMOS technology quickly invaded the ICs market replacing the existing transistor-transistor logic (TTL) based on BJTs. In addition to its high noise immunity and low static power consumption, the main advantage of CMOS technology is its high density of integration.

MOS transistor is a key element in modern electronics with main applications in digital technologies. In the frame of CMOS technology [6], a combination of negative type and positive type MOS (respectively nMOS and pMOS) transistors are implemented in order to preform the different logic gates in ICs. nMOS and pMOS transistors are based respectively on the transport of negative charges (or electrons) and positive charges (or holes). In both nMOS and pMOS cases, the MOS transistor is a three-terminal device where the channel conduction between two of the contacts called source and drain is controlled by a third terminal called gate [7]. Therefore, MOS transistor can be used as a switching device, very useful for logic operations in digital circuits. Fig. 1.1 shows the structure

of both nMOS (left) and pMOS (right) transistors obtained by 2D TCAD simulations. The source and drain regions have an excess of negative and positive charges respectively for nMOS and pMOS transistors. For the sake of simplicity and in order to explain MOS operation regimes, we will concentrate on the nMOS transistor, the same explanations being valid for pMOS transistor by reverting the charges sign and applied voltages. In the case of nMOS transistor the n-type source and drain regions have an excess of electron carriers (obtained by external n doping using specific technological processes such as ion implantation to be explained in 1.2.3). Source and drain regions are formed on a p-doped silicon substrate. Therefore, substrate/source and substrate/drain interfaces form two p-n junctions or diodes. Before going further in MOS transistor understanding, p-n junctions basics are reminded in sub-section 1.2.1.

Figure 1.1: nMOS and pMOS transistors two dimensional (2D) structures from TCAD simulations with silicon net doping (red: n-doping, blue: p-doping). Are also given the different terminals voltage conditions leading to a strong inversion regime (sub-section 1.2.3) with electrons and holes transfer between source and drain respectively for nMOS and pMOS.

### 1.2.1 The p-n junction

A p-n junction is a two terminal device, considered as the fundamental element of semiconductor physics, whose mechanisms are extensively explained in reference manuals such as [7, 8]. In the periodic diamond cubic silicon crystal, energy bands of allowed energy states for electrons form in the reciprocal space, separated by energy gaps called band gaps [9]. Electrons in silicon are fermions and therefore, considering Pauli exclusion principle, follow Fermi-Dirac statistics with an energy distribution f(E) defined by:

$$f(E) = \frac{1}{1 + e^{\frac{E - \mu}{k_B T}}}$$

(1.1)

where  $k_B$  is Boltzmann's constant ( $\sim 1.38 \times 10^{-23} J.K^{-1}$ ), T is the temperature in Kelvin (K), and  $\mu$  is the total chemical potential also known as the Fermi level  $E_F$ . In a semiconductor such as silicon,

$E_F$  is located in a band gap and the energy band just below  $E_F$  is called the valence band with an energy maximum  $E_V$ , and the one just above is called the conduction band with an energy minimum  $E_C$ . The two valence and conduction bands are separated by an energy band gap  $E_g$  of approximately 1.12 eV at room temperature [10].  $E_F$  depends on temperature and external (or extrinsic) doping. At finite temperature T, and due to the Fermi-Dirac distribution 1.1, the valence band is almost full with electrons and some free energy states are available, which leads to the concept of holes (or hole carriers), corresponding to a missing electron and therefore a positive charge in the valence band. It should be noticed that a hole is not an actual particle and is only the mathematical opposite of an electron, introduced for its usefulness in semiconductor physics calculations. From the other side, the conduction band is almost empty with electrons or full with holes. In the pure crystal at finite temperature T, thanks to the thermal energy some electrons will leave the valence band to the conduction one, contributing in an electron current when an electric field is applied to the material. In an opposite manner, some holes can leave the conduction band to the valence one, leading to a hole current in the presence of an electric field.

Electrons or holes conduction in an undoped silicon (also called intrinsic silicon), is related respectively to available free electrons in the conduction band or holes in the valence band. However, in an intrinsic semiconductor, conductivity control is quite limited and can only be modified by changing the temperature or using an external energy source such as light.

Doping process in semiconductors was first introduced for germanium in 1944 [11], according to which an impurity is intentionally introduced in a pure semiconductor in order to modulate its conducting properties. Doping silicon crystal consists of replacing some crystal sites by dopant atoms, therefore called substitutional atoms. When dopants are introduced in silicon crystal, its periodicity is altered leading to the formation of allowed energy states within the band gap that are close to the valence or conduction energy band, therefore called shallow levels whose exact position depends on the used dopant atoms.