# Light software services for dynamical partial reconfiguration in FPGAs

Yan Xu

### ► To cite this version:

Yan Xu. Light software services for dynamical partial reconfiguration in FPGAs. Micro and nanotechnologies/Microelectronics. Université de Grenoble, 2014. English. NNT: 2014GRENT010. tel-01060171

### HAL Id: tel-01060171 https://theses.hal.science/tel-01060171

Submitted on 3 Sep 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE GRENOBLE

# THÈSE

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Nano-Electronique et Nano-Technologies

Arrêté ministériel : 6 Août 2006

Présentée par

Yan XU

Thèse dirigée par Frédéric Pétrot

préparée au sein Laboratoire TIMA et de l'École Doctrale EEATS

# Gestion Logicielle Légère pour la Reconfiguration Dynamique Partielle sur les FPGAs

Thèse soutenue publiquement le **13 Mars 2014**, devant le jury composé de :

M. Bertrand GRANADO

Professeur à l'UPMC, Président

M. Loïc LAGADEC

Professeur à l'ENSTA Bretagne, Rapporteur

M. Fabrice MULLER

Maître de Conférence à Polytech'Nice, Rapporteur

M. Fabrice LEMONNIER

Directeur du Lab HPC chez Thales Research and Technology, Examinateur

M. Benoit MIRAMOND

Maître de Conférences à l'ETIS, Examinateur

M. Frédéric PÉTROT

Professeur à Grenoble INP, Directeur de thèse

M. Olivier MULLER

Maître de Conférences à Grenoble INP, Co-Directeur de thèse

HOLE ISTATIS GRAIN

# Acknowledgement

This work is carried out during the years 2010-2014 at TIMA Laboratory, SLS group. It is an honour for me to finally have this chance to thank those who made this thesis possible.

My deepest gratitude goes to my advisor Mr. Olivier MULLER, who made available his support in a number of ways. Just after my arrival, Olivier provided me with a series of good quality tutorials which helped me quickly integrate into the group and set up a good working manner. During the four years, I was always appreciating the constructive and interesting discussions with him. He constantly encouraged me to develop my own ideas and to have more self-confidence. When I lost myself into certain details, his strong sense of priorities and capacity of structuring ideas prevented me many times from sticking into the mud of trivialities. I highly valued his practical writing advices for my manuscript, and his useful communication tips for my defence presentation. Especially, I am grateful for his patience and efforts for aiding me in coming out of my shell of shyness. In addition, Olivier spared his precious time to help me with all the administrative procedures, which allows me to concentrate to the research work.

I would like to express my warmest acknowledgement to Professor Frédéric PÉTROT for directing my thesis. Although we saw each other only occasionally, he guaranteed his presences at every key moment along the years when I was pursuing my doctorate. Thanks to his extensive expertise, I could obtain useful references when I urgently needed to apprehend or integrate some concepts. His rigorous scholarship and optimistic attitude always made me go out of the meeting room with a better-organized mind and a lighter heart.

Mr. Fabrice MULLER, Mr. Loïc LAGADEC, Mr. Benoit MIRAMOND, Mr. Bertrand GRANADO are thanked sincerely for accepting being the members of my jury, and in particular the two reviewers for their constructive remarks.

I owe many thanks to Xavier GUÉRIN, Damien HEDDE and Pierre-Henri HOR-REIN for their generous technical support; to Nicolas FOURNEL and Frédéric ROUSSEAU for their insightful suggestions; and to all members of the SLS group for their frank feedbacks.

The debt I owe is not only intellectual but also moral. Mr. Gang FENG, thank you for years of concern, from the recruitment at the very beginning to my last defence. Mrs. Sophie MARTINEAU, I cherish your lovely French courses in Monday afternoons, full of laughters. Hai YU, your warm reception released me a lot from the tension of being in a foreign country. Adrien PROST-BOUCLE, Florentine DUBOIS, Greicy COSTA-MARQUES, Maryam BAHMANI and Zuheng MING, your friendship is irreplaceable. I will always remember the good time we had together.

My special thank goes to Quentin MEUNIER and his family. Quentin, you are a patient listener and always turning my head to the bright side. Each step of my advance was accompanied by your persistent encouragement. The continuous tender care from your family gives me feeling of belonging in France. I really appreciated for all you people have done.

Last but not less important, I wish to send my ocean-deep feeling to my family and friends in China, where my life energy resides. Every Chinese word coming from you, through a letter or a phone call, was calming and evoking the nostalgic wave of mine. Thank you for your companion and support in distance. Mother and Father, you said nothing but gave me wings when I wished to fly. I just want you to know that, no matter how far am I, you are my roots forever.

# Contents

| 1 | Intro                                   | oductio                            | n                                      |                                                   | 1                          |  |

|---|-----------------------------------------|------------------------------------|----------------------------------------|---------------------------------------------------|----------------------------|--|

| 2 | Prok<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Task N<br>Resour<br>Comm<br>Flexib | rce Manag<br>nunicatior<br>ility Issue | ent                                               | 5<br>6<br>7<br>8<br>8<br>9 |  |

| 3 | State of the Art 1                      |                                    |                                        |                                                   |                            |  |

|   | 3.1                                     | Backg                              | round on                               | Model of Computation and Reconfigurable Circuit . | 11                         |  |

|   |                                         | 3.1.1                              |                                        | ational Model                                     | 11                         |  |

|   |                                         |                                    | 3.1.1.1                                | Streaming Model                                   | 12                         |  |

|   |                                         |                                    | 3.1.1.2                                | Kahn Process Network Model                        | 12                         |  |

|   |                                         |                                    | 3.1.1.3                                | Synchronous Data-Flow Model                       | 12                         |  |

|   |                                         |                                    | 3.1.1.4                                | Multi-Threaded Model                              | 13                         |  |

|   |                                         | 3.1.2                              | Reconfig                               | gurable Architectures                             | 14                         |  |

|   |                                         |                                    | 3.1.2.1                                | Granularity of FPGA Devices                       | 14                         |  |

|   |                                         |                                    | 3.1.2.2                                | Reconfiguration Types                             | 14                         |  |

|   |                                         |                                    | 3.1.2.3                                | Coupling FPGAs with GPPs                          | 15                         |  |

|   |                                         | 3.1.3                              |                                        | ween Computational Models and Reconfigurable Ar-  |                            |  |

|   |                                         |                                    |                                        | es                                                | 15                         |  |

|   | 3.2                                     | Integra                            |                                        | tegies                                            | 17                         |  |

|   |                                         | 3.2.1                              | -                                      | on at Task Level                                  | 17                         |  |

|   |                                         |                                    | 3.2.1.1                                | FOSFOR                                            | 17                         |  |

|   |                                         |                                    | 3.2.1.2                                | ReConfigME                                        | 18                         |  |

|   |                                         |                                    | 3.2.1.3                                | SPORE                                             | 18                         |  |

|   |                                         |                                    | 3.2.1.4                                | Flextiles                                         | 19                         |  |

|   |                                         | 3.2.2                              | -                                      | on at Process Level                               | 19                         |  |

|   |                                         |                                    | 3.2.2.1                                | BORPH                                             | 19                         |  |

|   |                                         | 3.2.3                              |                                        | on at Thread Level                                | 20                         |  |

|   |                                         |                                    | 3.2.3.1                                | HybridThread                                      | 20                         |  |

|   |                                         |                                    | 3.2.3.2                                | ReconOS                                           | 20                         |  |

|   |                                         |                                    | 3.2.3.3                                | FUSE                                              | 21                         |  |

|   |                                         |                                    | 3.2.3.4                                | SPREAD                                            | 22                         |  |

|   |                                         |                                    | 3.2.3.5                                | Virtual Memory System                             | 22                         |  |

|   |          | 3.2.4  | Integration at Instruction-Set Processor Level                                                                                          | 23       |

|---|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------|----------|

|   |          |        | 3.2.4.1 Chimaera                                                                                                                        | 23       |

|   |          |        | 3.2.4.2 XiRisc                                                                                                                          | 23       |

|   |          |        | 3.2.4.3 MOLEN                                                                                                                           | 24       |

|   |          |        | 3.2.4.4 RISPP                                                                                                                           | 24       |

|   | 3.3      | Conclu | usion                                                                                                                                   | 25       |

| 4 | <b>A</b> |        |                                                                                                                                         | 27       |

| 4 |          |        | tion Layer for Dynamic Reconfiguration                                                                                                  | 27<br>27 |

|   | 4.1      | 4.1.1  | theses on the System                                                                                                                    | 27       |

|   |          | 4.1.1  | Targeted Hardware Architecture Template                                                                                                 | 27<br>28 |

|   |          |        | 0                                                                                                                                       | 28<br>28 |

|   |          |        | 4.1.1.2 Reconfiguration Controllers                                                                                                     |          |

|   |          | 410    | 4.1.1.3 General-Purpose Processors                                                                                                      | 29       |

|   |          | 4.1.2  | Software Environment Assumptions                                                                                                        | 29       |

|   |          |        | 4.1.2.1 Explicit Partition                                                                                                              | 29       |

|   |          |        | 4.1.2.2 Cooperative Multitasking                                                                                                        | 29       |

|   |          |        | 4.1.2.3 Pre-synthesized User Library                                                                                                    | 30       |

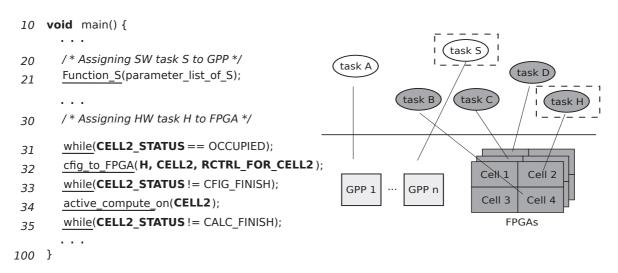

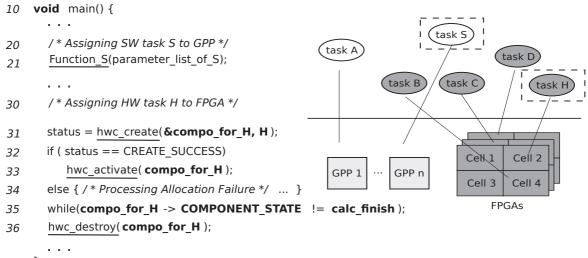

|   | 4.2      |        | tivating Example                                                                                                                        | 30       |

|   |          | 4.2.1  | Development and Maintenance of the Code                                                                                                 | 31       |

|   |          | 4.2.2  | Flexibility of the Code                                                                                                                 | 31       |

|   |          | 4.2.3  | Working in the Multi-User Context                                                                                                       | 32       |

|   |          | 4.2.4  | Motivation of our Work                                                                                                                  | 32       |

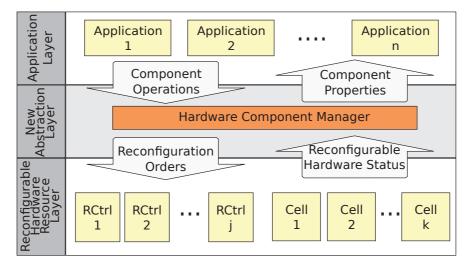

|   | 4.3      |        | sal: An Abstraction Layer Wrapping Hardware Components .                                                                                | 32       |

|   |          | 4.3.1  | Observed Interactions                                                                                                                   | 32       |

|   |          | 4.3.2  | Hardware Component: the Key Element for Interfacing with                                                                                |          |

|   |          |        | Application Layer                                                                                                                       | 33       |

|   |          |        | 4.3.2.1 Hardware Component Properties                                                                                                   | 33       |

|   |          |        | 4.3.2.2 Hardware Component Operations                                                                                                   | 35       |

|   |          | 4.3.3  | Hardware Component Manager: A Centralized Reconfig-                                                                                     |          |

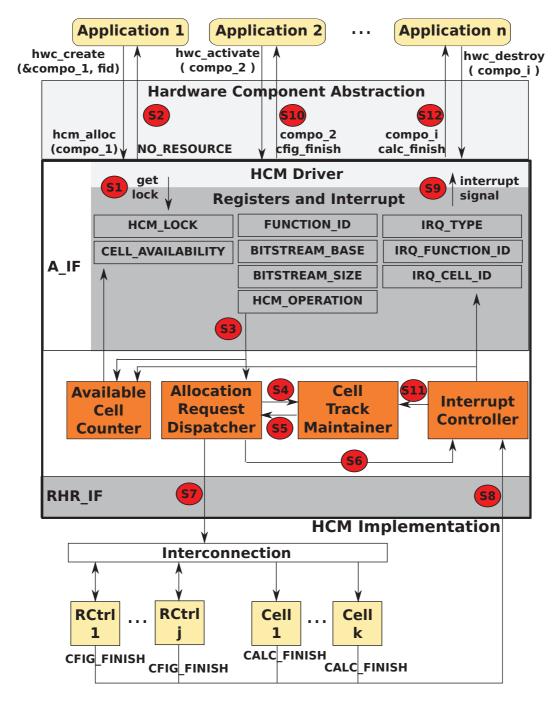

|   |          |        | urable Hardware Resource Manager                                                                                                        | 37       |

|   |          |        | 4.3.3.1 Conceptual Model of HCM                                                                                                         | 37       |

|   |          |        | 4.3.3.2 An Implementation of the HCM                                                                                                    | 39       |

|   | 4.4      | Summ   | ary of the Chapter                                                                                                                      | 41       |

| 5 | A Sc     | alable | Communication Mechanism for Dynamic Reconfiguration Plat-                                                                               |          |

| 0 | form     |        | communication meenument for Dynamic Accomigatation I hat                                                                                | 43       |

|   | 5.1      | Comm   | nunication Problems Brought by Dynamically Reconfigurable                                                                               |          |

|   |          |        | rms                                                                                                                                     | 43       |

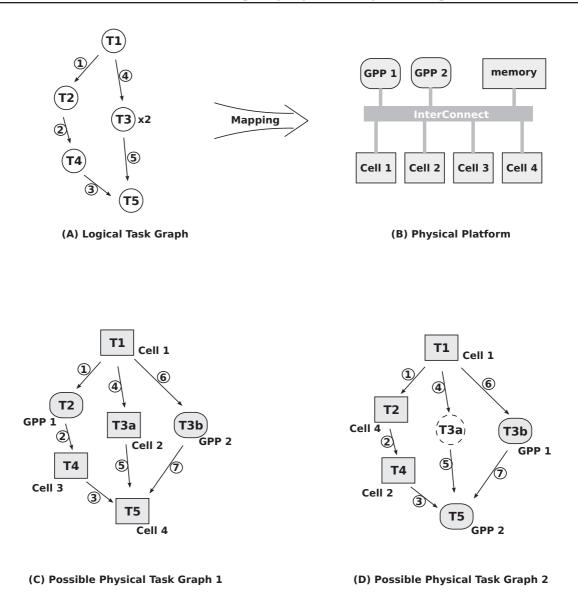

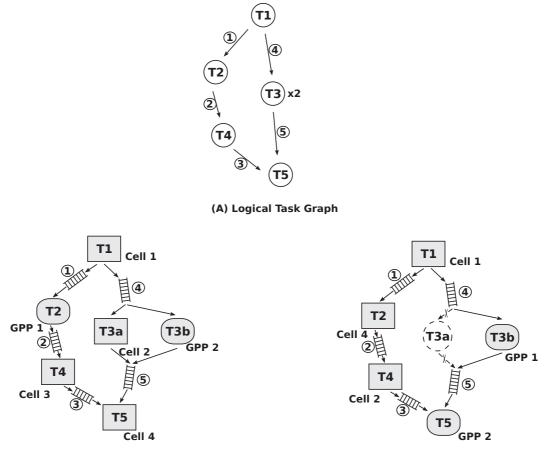

|   |          | 5.1.1  | A Motivating Example                                                                                                                    | 44       |

|   |          | 5.1.2  | Analysis of the Motivating Example                                                                                                      | 46       |

|   |          |        | 5.1.2.1 The Existence of Tasks                                                                                                          | 46       |

|   |          |        | 5.1.2.2 The Access to Tasks                                                                                                             | 47       |

|   | 5.2      | MWM    | IR Channel Analysis in a Dynamic Reconfigurable Context                                                                                 | 48       |

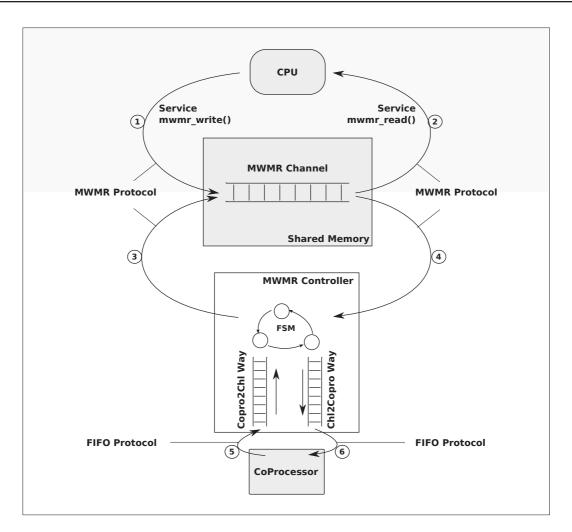

|   |          | 5.2.1  | MWMR Channel Description                                                                                                                | 48       |

|   |          | 5.2.2  | Why the MWMR Channel is Chosen                                                                                                          | 50       |

|   |          |        | 5.2.2.1 Shared Hypotheses                                                                                                               | 50       |

|   |          |        | 5.2.2.2 Useful Features                                                                                                                 | 50       |

|   |          |        | $0.2.2.2  0.001 ut t catul 0.000 \dots \dots$ | 50       |

|   | 5.3 | 5.2.3<br>Propo | 5.2.2.3 Reasonable Technical Requirements                    | 52<br>52 |

|---|-----|----------------|--------------------------------------------------------------|----------|

|   |     |                | ICM                                                          | 54       |

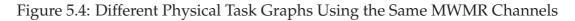

|   |     | 5.3.1          | Proposed Architecture                                        | 54       |

|   |     | 5.3.2          | Communication Services                                       | 56       |

|   |     | 5.3.3          | Use on the Motivating Example                                | 58       |

|   | 5.4 | summ           | nary of this chapter                                         | 59       |

| 6 | Exp | erimen         | lts                                                          | 61       |

|   | 6.1 | Proof-         | -of-concept Integration in an OS                             | 61       |

|   |     | 6.1.1          | The Implementation of the HCM Integration                    | 62       |

|   |     | 6.1.2          | HWC Services Description                                     | 64       |

|   |     | 6.1.3          | Experiment 1: Feature Validation on Simulator-based Test En- |          |

|   |     |                | vironment                                                    | 65       |

|   |     |                | 6.1.3.1 Test Platforms                                       | 65       |

|   |     |                | 6.1.3.2 Application                                          | 66       |

|   |     |                | 6.1.3.3 Results Analysis                                     | 67       |

|   |     | 6.1.4          | Experiment 2: Integration Cost                               | 69       |

|   |     |                | 6.1.4.1 Test Platform and Application                        | 70       |

|   |     |                | 6.1.4.2 Execution Result                                     | 70       |

|   |     | _              | 6.1.4.3 Results Analysis                                     | 72       |

|   | 6.2 |                | nunication Mechanism Validation                              | 76       |

|   |     | 6.2.1          | Experiment 3: Original MWMR Channel Migration                | 76       |

|   |     | 6.2.2          | Experiment 4: Dynamicity Management with the HCM and         |          |

|   |     | <b>C</b> 1     | Modified MWMR Channels                                       | 78       |

|   | 6.3 | Concl          | usion                                                        | 82       |

| 7 |     | clusior        |                                                              | 83       |

|   | 7.1 | Contr          | ibution                                                      | 83       |

# List of Tables

| 4.1 | Hardware Component Properties          | 34 |

|-----|----------------------------------------|----|

| 4.2 | Hardware Component Services            | 36 |

| 6.1 | Parameters of test platforms           | 66 |

| 6.2 | Basic components for test applications | 66 |

|     | Time Overhead of OS Extension Services |    |

| 6.4 | Memory Footprints of Systems           | 74 |

# List of Figures

| 1.1<br>1.2 | Evolution of Internet and cellphone users between 1980 and 2010 Evolution of the amount of data produced every year between 2005 | 1        |

|------------|----------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2        | and 2020                                                                                                                         | 2        |

| 2.1        | Schematic view of a basic dynamically reconfigurable system                                                                      | 5        |

| 2.2        | Task Graph Example                                                                                                               | 6        |

| 3.1        | The Coupling between Reconfigurable Fabrics and General Purpose<br>Processors (adapt from [HD07])                                | 16       |

| 3.2        | Gap between Computation Models and Reconfigurable Architectures                                                                  | 16       |

| 4.1        | The targeted hardware architecture template                                                                                      | 27       |

| 4.2        | Task Assignment in a GPP/FPGA Hybrid Platform                                                                                    | 31       |

| 4.3        | The Rewritten Motivated Example                                                                                                  | 36       |

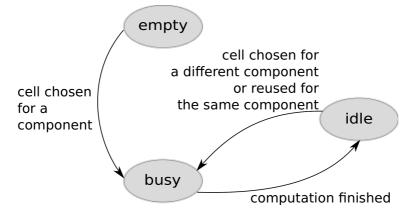

| 4.4<br>4.5 | Hardware Component Manager in SystemThe State Machine of a Cell                                                                  | 37<br>38 |

| 4.6        | Internal Structure of the HCM Implementation                                                                                     | 40       |

| 5.1        | Passive Task Model                                                                                                               | 44       |

| 5.2        | Communication Problems Caused by Dynamic Reconfigurable Plat-                                                                    |          |

|            | form                                                                                                                             | 45       |

| 5.3        | Basic Properties of a MWMR Channel                                                                                               | 49       |

| 5.4<br>5.5 | Different Physical Task Graphs Using the Same MWMR Channels<br>The Problems that MWMR Channels Left Unsolved                     | 51<br>53 |

| 5.6        | Proposed Communication Architecture                                                                                              | 55<br>55 |

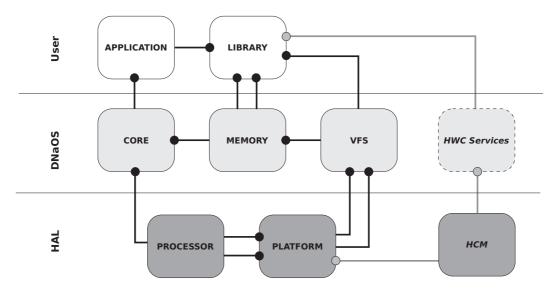

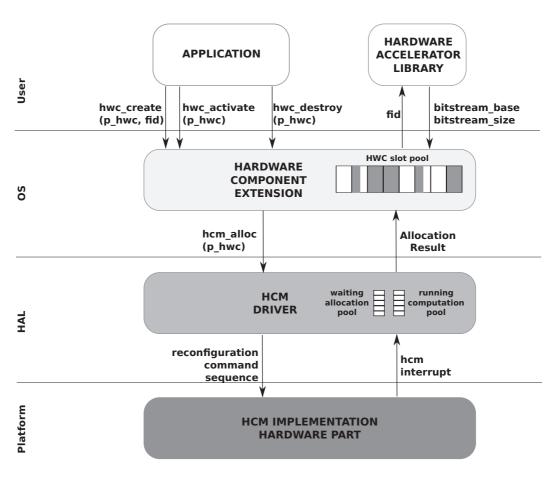

| 6.1        | Global View of Software Organization                                                                                             | 62       |

| 6.2        | One Implementation of HCM-integrated OS                                                                                          | 63       |

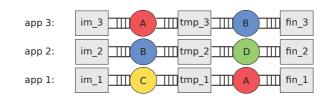

| 6.3        | Simple image processing scenario                                                                                                 | 67       |

| 6.4        | Code without HCM                                                                                                                 | 68       |

| 6.5        | Code with HCM                                                                                                                    | 69       |

| 6.6        | The Underneath Processing of Scenario in Different Platforms                                                                     | 69       |

| 6.7        | Time Consumption During the Lifetime of an HA                                                                                    | 71       |

| 6.8        | Maximum Frequency that the HCM can Reach Depending on the Cell<br>Number                                                         | 75       |

| 6.9        | HCM Resource Utilization Depending on the Cell Number                                                                            | 75       |

| 6.10       | Platform for Testing the Original MWMR channel                                                                                   | 77       |

|            | 6 6                                                                                                                              |          |

| 6.11 | MWMR Channel Validation in Various Data Producer-Consumer Pair      |    |

|------|---------------------------------------------------------------------|----|

|      | Cases                                                               | 79 |

| 6.12 | The Platform for Testing the Dynamic Communication Mechanism .      | 80 |

| 6.13 | The Platform for Testing the Dynamic Communication Mechanism .      | 80 |

| 6.14 | Underlying Cell Usage for Each Application Processing the Two First |    |

|      | Images                                                              | 81 |

# List of Used Acronyms

#### **General Acronyms**

| API      | Application Programming Interface       |

|----------|-----------------------------------------|

| ASIC     | Application Specific Integrated Circuit |

| CPU      | Central Processing Unit                 |

| DPR      | Dynamic Partial Reconfiguration         |

| DR       | Dynamic Reconfiguration                 |

| FIFO(s)  | First-in First-out queue(s)             |

| FPGA(s)  | Field Programmable Gate Array(s)        |

| GPP      | General-Purpose Processor               |

| HPC      | High Performance Computers              |

| HLS      | High-Level Synthesis                    |

| HW/SW    | Hardware/Software                       |

| MPI      | Massage Passing Interface               |

| MWMR     | Multi-Writer Multi-Reader               |

| OS       | Operating System                        |

| P-C pair | Producer-Consumer pair                  |

| SDF      | Synchronous Data Flow                   |

|          |                                         |

#### **User-Defined Acronyms**

- ARD Allocation Request Dispatcher

- CTM Cell Track Maintainer

- DRM Dynamic Resource Manager

- HCM Hardware Component Manager

- RF(s) Reconfigurable Fabric(s)

- RHR Reconfigurable Hardware Resource

# Chapter 1 Introduction

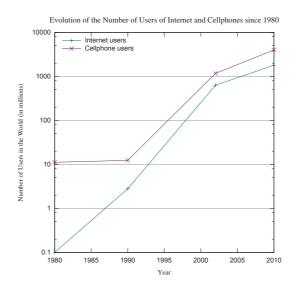

THE digital revolution, which started somewhere around 1970 and is still undergoing today, has modified deeply and in many ways the society we are living in. The number of users of electronic devices has not stopped increasing since then. As an example, figure 1.1 shows that the number of cellphone users has gone from 11.2 millions in 1980 to 4 billions in 2010, while the number of Internet users has passed from less than 100,000 in 1980 to more than 1.8 billion in 2010.

Figure 1.1: Evolution of Internet and cellphone users between 1980 and 2010

Similarly, the number of electronic devices has known an incredible growth over the last 30 years, going from 1 million in 1980 to more than 6 billions in 2012. As another example, Oracle is proud to say that more than 4 billion devices run java in the world at every java update.

Not only the digital revolution is related to the omnipresence of electronic devices, but it has also been accompanied by a fast evolution of each individual system's performance. The most famous quoted measure is the number of transistors integrated on a single chip, which has continuously doubled every 2 years since 1965, commonly known as Moore's law. One of the challenges addressed by this integration growth is the face to the always increasing computation demand. Although this demand has a lot of sources (e.g. games), one of the biggest is data processing. In fact, the amount of data produced worldwide in 2010 has reached 1.2 zettabytes ( $10^{21}$  bytes), and even if only about 5% of this data is structured – i.e. can be analyzed by a machine –, it still represents a very high computing demand [idc11]. According to the same sources, this trend is not going to stop in the near future, since the International Data Corporation foresees the world to produce more than 40 zettabytes per year in 2020, as shown on figure 1.2.

Figure 1.2: Evolution of the amount of data produced every year between 2005 and 2020

However, if Moore's law combined to the increase of the number of devices provides a support to face this demand, it still does not resolve it all as two major problems come up with the transistor integration growth.

The first one may seem paradoxical since it deals with the utilization of the transistors themselves. Around 2004, 50 years of exponential improvement in the sequential performance of processors ended [OH05]. This led manufacturers to design multicore chips, which has been the first answer to the utilization of available circuit surface. The second problem is related to the power consumption of actual and future chips, since it estimated that by 2015, 300mm<sup>2</sup> chip will consume more than 1kW [Bor07]. One part of this increase is due to what is called the *power wall*, or the trend to consume an exponentially increasing power when increasing linearly the frequency. The other part is related to Pollack's rule, which states that the performance increase of a circuit achieved via architectural improvements is roughly proportional to the square root of the increase of complexity – the latter being directly linked with power consumption. Once again, an answer is to turn towards multi- and manycore chips, so as to enhance the performance per watt ratio.

Finally, another problem related to Moore's law is the end of it; we know that

physical constraints will make technology below 1nm hardly feasible, and until a major breakthrough in technology occurs – likely the end of CMOS –, new ways to improve performance at fixed cost and power must be found.

### **Using FPGAs to Improve Performance**

A general-purpose microprocessor, by executing various software on a fixed hardware, can achieve any logical or mathematical operation that a programmer can conceive, but the performance is not always satisfactory. In contrast, Application Specific Integrated Circuits (ASICs), by dedicating hardware circuits to a particular task, can result in a smaller, cheaper, faster chip that consumes less power than a programmable processor. However, a slight change in its functionality may lead to a complete redesign and rebuilt of the circuit, which is very expensive.

In order to find the right balance, the idea of adapting hardware to the application after build time was formed in the 1960s [Est60]. However, this idea could not become a reality before long.

Field Programmable Gate Arrays (FPGAs) are circuits which were originally designed in the mid-1980's to validate Register Transfer Level (RTL) models before using them to make an ASIC chip. By configuring its behaviour with the means of a "bitstream", a FPGA can achieve any functionality in hardware. These bitstreams are created from RTL models *via* different tools. Using FPGAs is thus an alternative to RTL simulation, with the advantage of providing a very high speed compared to the former. It is, as such, a RTL emulation technique.

However, this also allows triggered a regain of interest in the idea of adapting hardware to the application after its build. Quickly enough, FPGAs became used as a part of a System-on-Chip.

With this hypothesis, circuit design now possesses an additional step in the speed vs generality trade-off: a functionality implemented by a RTL model on a FPGA is orders of magnitude faster (up to 3 can be observed in literature) than a software implementation, what also results on large power savings compared to a processor executing equivalent code. On the other side, the circuit used for it has neither to be designed, nor is definitely attached to this functionality. As such, a FPGA is a good compromise between a processor executing a piece of software and an ASIC. The drawbacks are the opposite: a RTL model is still harder to write than a high level function; besides, a RTL model on a FPGA will still run one order of magnitude slower than an ASIC backend of this model.

### **Exploiting Reconfiguration Inside FPGAs**

To even gain more in flexibility, researchers and industrials did not content themselves with integrating FPGAs in system-on-chip. In the late 1990's, a technique was proposed to allow a part of the FPGA to be reconfigured while the rest of the system is still running and computing, thus opening a new era in which the adaption of hardware to the application can even be done at runtime. This technique was called *Dynamic Partial Reconfiguration* (DPR). Dynamic reconfigurable FPGAs achieve both inherent computing efficiency and potentially infinite execution space by breaking the barriers between hardware and software. Unfortunately, compared to CPU-based solutions, FPGA-based solution suffer from low productivity. The latter is measured by the time required to arrive to a solution and indirectly by flexibility (scalability, portability and reusability).

This thesis investigates dynamic reconfigurable FPGA, and more specifically the ways to ease the life of application developers who program a system containing such FPGAs. In particular, this work will try to improve the flexibility of such systems in terms of scalability, portability and reusability.

The rest of the thesis is organized as follows: chapter 2 introduces the problematic we considered for this work; chapter 3 presents related works considering the integration of FPGAs into conventional systems-on-chip; chapter 4 details the abstraction layer proposed by the author to solve the portability problems stated earlier; chapter 5 presents the communication mechanisms used between the different parts of the systems; chapter 6 summarizes the experiments fulfilled during this thesis to validate our proposal; finally, chapter 7 concludes and discusses possible future works.

# **Chapter 2**

# **Problem Statement**

THIS chapter introduces the general context of our study, centered around dynamic reconfigurable (DR) systems, i.e. systems in which a part of the hardware can be adapted to applications at run-time, while the rest of the system keeps executing as normal.

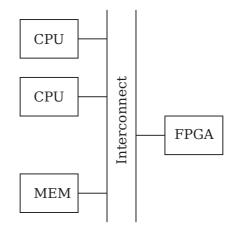

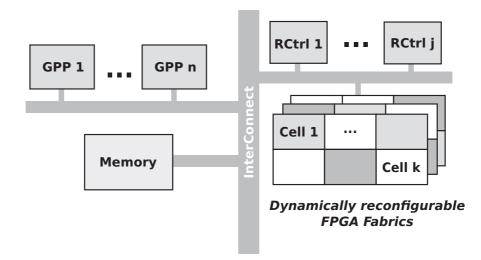

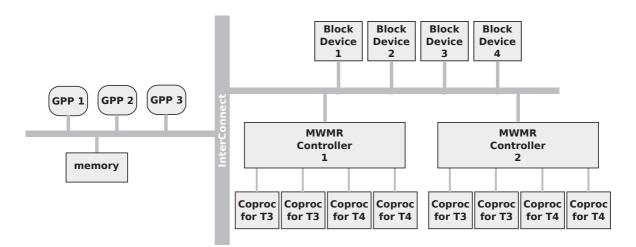

Figure 2.1 is a schematic diagram of a typical architecture employed by DR systems, in which the general purpose CPUs and reconfigurable fabrics (RF) are loosely-coupled by an interconnect.

Figure 2.1: Schematic view of a basic dynamically reconfigurable system

According to the integration strategy, the RF part can either act as individual data processors in a heterogeneous multi-processor system or peripheral data processing devices.

Depending on the scale of the DR system, the RFs can be implemented by one partial reconfigurable FPGA or several FPGAs. The number of CPUs is not limited to one neither. The CPUs can be conventional micro-processors, multi-core processors, or soft cores in FPGAs.

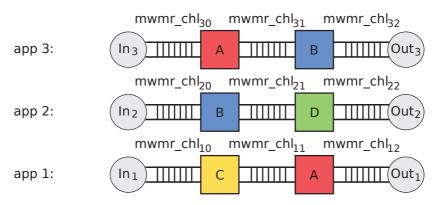

In our hypothesis, applications can be seen as communicating tasks, as shown in Figure 2.2. A task can be a data producer (T1), a data consumer (T3) or both (T2) at the same time. Tasks can be executed by CPU or be mapped to RF. We can see that the CPU/RF hybrid DR architecture provides a quite promising computational power by breaking the barrier between hardware (hardware) and software (software), but it is exactly such a mixture that makes programming somehow complicated. Taking the dynamic nature and flexibility demand into consideration, handling such systems is not an easy job.

T2

Figure 2.2: Task Graph Example

There are numerous issues in programming models, resource management, communication infrastructure to deal with, and many design choices to make before finally arriving to a solution.

### 2.1 Task Management

Noticing the possible parallelism implied by the loose coupling between the CPUs and RFs, and the potential multi-CPU, multi-FPGA context, wise application programmers would probably consider dividing their algorithms into multiple computation tasks, which can independently execute during a relatively long period of time and which can effectively communicate with each other when necessary. The tasks definition and their assignment to an execution unit have a great influence on the system's performance, thus should be treated with care.

One particularity of the hybrid DR systems is that a task can either be executed by a CPU, called a software task; or be implemented on a RF, then called a hardware task. A hardware task can be considered as the hardware accelerator of its software counterpart. Normally, an application designer knows best whether a task should be allocated to a kind of execution unit or another; therefore, when the whole system is totally predictable, the HW/SW partitioning can be done statically before the application is executed. However, there are cases in which the behavior of the application depends on information only available at run-time. Accordingly, the executing unit of a specific task must be decided based on system state at that moment. Dedicating the precious RF to a task which never runs is a waste of resource and an inefficient way of using the DR architecture. This on-demand task allocation increases the difficulty of task management, because the procedure of launching a hardware task is not the same as the one of a software one.

The hardware tasks can be prepared in advance in several ways:

- from a Register Transfer Level Hardware Description Language, such as VHDL or Verilog,

- by commercial Electronic Design Automation tools,

- or, from high level language, as C or C++, by High-Level Synthesis (HLS) tools.

Some just-in-time compile-synthesis methods are in research to provide an on-line hardware task generation. Whichever the way, the bitstreams of hardware tasks must be loaded to the FPGA before these hardware tasks actually run. They can run until all expected computations are finished, or be swapped in-and-out and complete all predefined operations in several time slices. Whether preemptive or not, there must be a way to recognize the tasks' state, i.e. that the requested hardware task is available on FPGA (first appearance or reloaded), and that the hardware tasks reach their end or the point to be swapped out.

### 2.2 Resource Management

The DR feature adds another dimension of system resource management. The FPGA is not only a spatial resource, but also temporally shared by different hardware tasks. Therefore, resource management mainly consists in managing the RFs in the platform, through a reconfiguration process, by allocating room for hardware tasks and for a given time on the RFs. Apart from this reconfiguration process, the configurations (usually called bitstreams) of hardware tasks corresponding to the RFs should also be stored somewhere in memory. The identification and transfers of these bitstreams to the RF also need to be handled. In addition, FP-GAs can be configured through several kinds of interface, such as Joint Test Action Group (JTAG) port, synchronized serial data/clock interface, or Internal Configuration Access Port (ICAP) in some self-reconfigurable FPGAs. All these reconfigurable interfaces need to be controlled and thus require the system to have this ability.

From the view of resource management, the execution of a hardware task can be considered as a request of part of the RF on the FPGA. Some of the questions to address during the lifetime of a hardware task are the following:

- How to organize RFs into zones in which we can put different hardware tasks?

- How to choose a specific zone to be reconfigured for the required hardware task from the numerous available zones?

- What to do when there are no more zones available?

- How to make a zone reusable once the hardware task on it has finished its execution?

In a multi-threaded context, several applications run independently. It is neither necessary nor possible to know the executing state of other applications. There must be a mechanism to guarantee the coexistence of hardware tasks belonging to different applications. For example, the requests sent simultaneously from different applications should not be lost; or a hardware task configured on the RF by one application should not be replaced by a request of another application even without a proper run. When in a multi-FPGA context or when an FPGA contains several configuration ports, parallelizing several reconfigurations is feasible. In that case, the distribution of reconfiguration requests to the different ports is also a problem to consider.

### 2.3 Communication Management

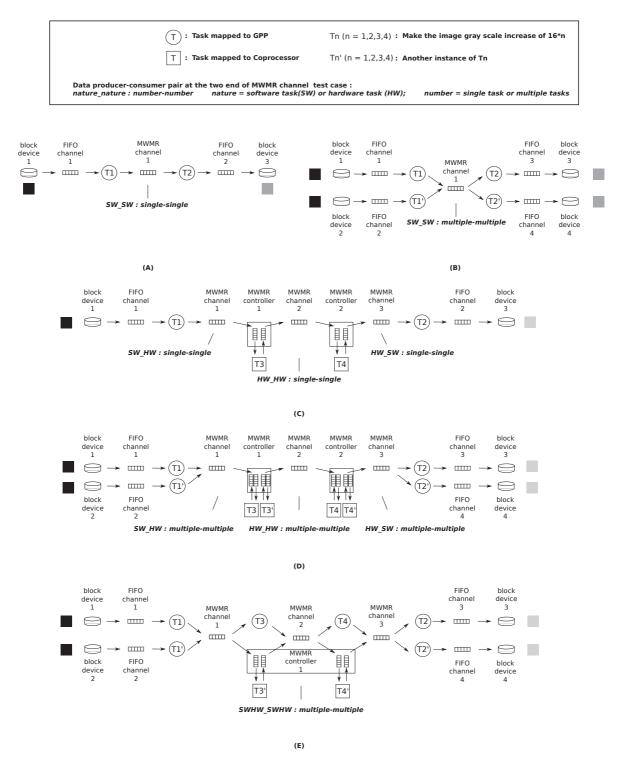

As mentioned at the beginning of this chapter, our programming model is supposed to be communicating tasks, which form the data producer-consumer (P-C) pairs (Figure 2.2). In a conventional architecture, once the task graph is settled, the communication can be managed as the data synchronization between P-C pairs. However, the communication in a DR system could be much more complicated.

Firstly, each task could either be implemented in its software version or hardware version. Consequently, a basic P-C pair evolves into four combinations: software/software, software/hardware, hardware/software and hardware/hardware. In a software version, data is usually stored in arrays, which are referred to by a pointer; while in a hardware version, data is probably stored in an unaddressable First-In First-Out (FIFO) queue on the RF. The communication mechanism should be able to cover the different natures of communicators.

Secondly, depending on the availability of resources on the RF, one task could have more than one instance. As a result, a basic P-C pair may leave as single-producer/single-consumer, or it may expand to multiple-producers/single-consumer, single-producer/multiple-consumers or multiple-producers/multiple-consumers. Thus, the number of instances of a hardware task may not be predicable. The communication mechanism should be able to cover an arbitrary number of communicators in both sides of a P-C pair, so that the computational power is not wasted due to disconnections among tasks.

Finally, since the hardware tasks need a period of time to be reconfigured on the RF and since they may be taken off from the RF, the communicators of a basic P-C pair do not always exist. The communication mechanism should also be able to guarantee that the data will not be sent to or taken from nowhere, while keeping the property that different running tasks should not break their boundaries to get information of existence of other tasks.

### 2.4 Flexibility Issues

Usability, portability and scalability are the terms we use when talking about flexibility. In the above sections, we discussed the management of tasks, reconfigurable resources and communication separately, but in practice they are often tightly connected due to FPGA architectures. In the conventional way of using FPGAs, it is the application programmer who decides which task is put on which part of FPGA, at which moment, through which reconfiguration port, from which place the bitstream of the task should be taken from in the memory, and how the ready task should be accessed.

The strong relation between the platform and the application imposes on the application programmers a deep knowledge about the underlying hardware, what asks extra efforts apart from their own job – programming to implement algorithms. The usability of DR CPU/FPGA hybrid architecture thus need to be improved.

In addition, platform information is planted into applications, what makes such applications not portable at all. A slight change of the platform, such as a damage of one part of the FPGA, requires a complete recoding of the application; not to mention the porting of an application to other FPGA devices.

Besides, such applications are not scalable: the communication graph is firmly based on task distribution and task distribution is mixed with resource management of the current platform. As a result, when resources are added to the platform, the applications cannot benefit from the potential increase in computational power without a rewrite, which is both not trivial and error prone.

To solve the flexibility issues, the only possible choice is to hide the platform details to application programmers. All the problem is to decide to which degree this hiding should occur. Is it better to achieve a virtualization, meaning the application programmers are not aware of the underlying platform at all; or just an abstraction, meaning the application programmers can get some information from and give order to the underlying platform in a much easier way. The former gives the application programmer more freedom, while the latter promises better performance gained from more control. Once decided, the other problems arising are the following:

- How to provide this hiding;

- how to separate the communication from the task distribution;

- how to separate the management of tasks and resource.

### 2.5 Summary

After discussing the different aspects of DR CPU/FPGA hybrid system, we can identify the following problems:

- 1. How are tasks allocated to different resources in a CPU/FPGA hybrid system where dynamic partitioning is allowed?

- 2. How the reconfiguration related resources (RFs, bitstreams, reconfiguration ports) are managed, so that the DR processing can be well maintained even in a multi-threaded, multi-FPGA environment?

- 3. How to design a communication mechanism which can recognize the existence of dynamically appearing communicators, no matter what the nature and number of communicators at both sides of a P-C pair?

- 4. How to ease the life of application programmers by separating the management of tasks, reconfiguration resources and communication, so that they can write more flexible applications?

# Chapter 3

# State of the Art

THIS chapter presents existing work relevant to our study. The different domains covered deal with the parallel programming models, and the reconfigurable architectures which have been proposed in the literature. The focus is made on the gap between both domains, and the attempt to integrate reconfiguration into existing programming models.

### 3.1 Background on Model of Computation and Reconfigurable Circuit

Current applications often impose conflicting requirements on computing system designers. For example, the system should be efficient to implement a specific application, while it should be generic enough in order to adapt to different applications; or the computing power is expected to greatly increase, while stricter constraints in terms of area, footprint and power consumption are placed. In order to meet such design requirements, various efforts are made in the community. In this section, we are going to review mainly in two directions: the computational model and the reconfigurable architecture.

### 3.1.1 Computational Model

To make developers more productive in describing their applications, various computational models have been proposed to abstract the hardware system, giving the developers the representations of algorithms and data structures which are easier to manipulate than underlying hardware details. One tendency of the computational model development is to explore the parallelism inside an application. To do this, the most discussed subjects are recognizing the independent computation parts and managing the communications amongst them. Some frequently used computational models are described in the following text. It is to note that research efforts also exist to bring interoperability between models [DCL13].

### 3.1.1.1 Streaming Model

Data stream is a model often used in real time data-intensive applications, such as network monitor, telecommunication data management, on-line video player, etc.

In [Mut03], the authors describe data stream as a "sequence of digitally encoded signals used to represent information in transmission, where TCS balance should be struck when input data comes at a very high rate". Here, T stands for transmitting the entire input to the program, C for computing sophisticated functions on large pieces of the input at the rate it is presented, and S for storing, capturing temporarily or archiving all of it on the long term. The authors of [BBD+02] point out the common characters of data stream models. For instances, the input data is not available for random access from disk or memory, but rather arrive as continuous data items. The system has no control over the order or the moment of the arriving data items that can be temporarily stored is relatively small. Besides, once an item in a data stream has been processed, it cannot be retrieved easily.

The parallelism in streaming application can be explored by separating the application in several step functions running at the same time, and keeping the output data rate of one step function the same as the input data rate of next step functions.

### 3.1.1.2 Kahn Process Network Model

The Kahn Process Network (KPN) is a widely accepted model for parallel programs, used for example in [APDG05] and [CDHL12]. The formal description of KPN model is firstly given in [Kah74] as a programming language. If we try to describe it in simple words, the KPN model could be seen as concurrently running processes which communicate through unidirectional FIFOs. A process in the KPN model either stays blocked by the unavailable input, or it computes and products output data. The process transmits information within an unpredictable but finite amount of time. The data writing in an output FIFO is non-blocking, which means in theory that the FIFO should acts as if it had an infinite size.

The above characteristics indicate that the KPN is suitable for modeling only the deterministic parallel programs. Here the word "deterministic" can be explained as the following: whatever the possible execution order of running processes is, the final outputs and the data history on channels of one program remain unchanged.

For applications satisfying the KPN model hypotheses, their concurrency and communications are explicitly handled. KPN Processes are only data-dependent, none of control variables are shared. In practice, the FIFO size need to be bounded by considering the data rate and possible executing time range. Some run-time monitoring mechanism might be need to notify and handle the overflow exceptions [Par95].

### 3.1.1.3 Synchronous Data-Flow Model

The Synchronous Data-Flow (SDF) model [LM87] is considered to be a natural paradigm for describing many digital signal processing applications. In the SDF

model, algorithms are described as directed graphs where the nodes represent computations and the arcs represent data paths. Any node can fire (perform its computation) whenever input data are available on its incoming arcs. When the node fires, a fixed number of data samples (or tokens) are consumed or produced on each arc respectively.

The SDF model is sometimes considered as a restriction of the KPN model. However, thanks to its static property (the fixed number of tokens on each arc), the SDF model has certain appealing characteristics. For instance, it is suitable for optimization techniques, namely minimizing bounded buffer sizes and static scheduling at compile time [BLM96].

Based on the primary SDF model, many efforts have been made to extend this model to be able to describe more generic programs, such as the following:

- the cyclo-static data flow model [BELP95], in which the rules of firing are allowed to be changed cyclically;

- The scenario-aware data flow model [TGB<sup>+</sup>06], in which the data rate and execution time can be parameterized according to the scenario occurrence captured by a stochastic approach;

- The control-operations-integrated SDF model, where the control informations are exchanged amongst processes to synchronize their execution and configuration [Bui13].

### 3.1.1.4 Multi-Threaded Model

The multi-threaded programming model brings the abstraction of *threads* to the programmer, a thread being a sequence of instruction executed in order. In this model, the threads communicate through shared memory, meaning that a thread can access to any memory location without constraint. This is why the threads come along with some synchronization primitives: at least locks, and often other abstractions like semaphores and barriers. Usually, this kind of model also comes up with some other support, e.g. memory allocation primitives.

Contrary to the previous models, multi-threaded programming lets the programmer a lot more freedom, but this freedom comes with a counterpart: the programmer has to guarantee himself the correctness of the synchronization to avoid deadlocks, while allowing enough concurrence between threads to get an effective parallelization. The latter is non-trivial at all, and this is why embedded programs are usually not written directly using this model. However, this model is well adapted to write a higher-level programming model such as the ones described above.

The most commonly known multi-threaded programming interface is the POSIX specification which provides all these basic blocks. Its most widespread implementations are Linux and BSD.

### 3.1.2 Reconfigurable Architectures

[HD07] provides an introduction to the entire range of issues relating to reconfigurable computing. In this book, various reconfigurable architectures are presented as the solution of the conflict between the increasing performance demand and the stricter constraints of area, memory footprint and energy consumption. Nowadays, the most commonly used reconfiguration device is the FPGA. The following discussion are mainly about the granularity of the FPGA device, the configuration type and the coupling with general purpose processors (GPP).

### 3.1.2.1 Granularity of FPGA Devices

FPGA can be seen as an array of logic block islands surrounded by general routing resources. The complexity and size of the logic blocks are referred to as the granularity of the blocks. The range of the granularity can vary.

[KTR08] reviews a spectrum of FPGAs. The logic blocks range from the veryfine-grained ones made of transistors, NAND gates; to medium-grained ones made of multiplexers, lookup tables; and to coarse-grained ones made of PAL-style wideinput gates, or even small processors.

The area, speed and power consumption are analyzed based on the granularity of the FPGA. In general, the fine-grained FPGAs benefit from convenient bit-level manipulations, but suffer from lower productivity, larger area, slower clock rates and higher power consumptions when complicated functions are demanded. The facts that developers have to construct functions at bit-level and that many areas are dedicated for interconnection result to a lower area-efficiency and a longer configuration time. The coarse-grained FPGAs, such as DART [DCPS02], are the other side of the story, as they are suited to implement relatively complicated operations, but very fine value operations lead to unnecessary area and speed overheads. The detailed trade-off can be found in [Ahm01].

### 3.1.2.2 Reconfiguration Types

The logic blocks and routing resources in FPGAs are controlled by reprogrammable memory locations. Boolean values held in these memory bits control whether certain wires are connected and what functionality is implemented by a particular piece of logic. A specific sequence of 1s and 0s for a particular memory locations in hardware is called a configuration, or referred to as a bitstream in the rest of the thesis. The process of loading bitstreams to the hardware memory locations is called reconfiguration. Depending on the time and influence to the system, we can divide the reconfigurations into two kinds: static ones and dynamic ones.

*Static reconfigurations* refer to the reconfigurations which can only take place during the system initiation and in which any change of configuration requires a halt of the whole system. If we limit our discussion only at the FPGA scope, the static reconfiguration examples could be the single-context FPGAs. The memory locations of such FPGAs can only be sequentially accessed, so that a large single bitstream for the whole chip has to be reloaded even when the functionality of a very small part needs to be modified.

At the opposite, *dynamic reconfiguration* means that a part of the fabric can be reconfigured while the rest of the system keeps on running. The example of dynamic reconfiguration could be multi-context FPGAs which allow background loading of inactive planes when an active plane is in execution. Another example is the partial reconfigurable FPGAs, whose memory locations can be randomly accessed, so that reconfiguration of one part of the chip and the computation of the rest are allowed to overlap in time. It is a special case of dynamic reconfiguration, called dynamic partial reconfiguration (DPR).

The main difference between static and dynamic reconfiguration is whether the functionality of a system hardware can evolve at runtime. It is not strictly bound to a special reconfigurable architecture. For instance, in a multi-FPGA system composed of single-context FPGAs, if the reconfiguration of a particular FPGA does not effect the execution of other FPGAs, the multi-FPGA system is still a dynamic reconfigurable system.

Another concept related with DPR is self-reconfiguration. It refers to a reconfigurable architecture in which the partial reconfigurations are controlled at runtime inside the FPGA device itself (either by a CPU core or by a dedicated controller).

### 3.1.2.3 Coupling FPGAs with GPPs

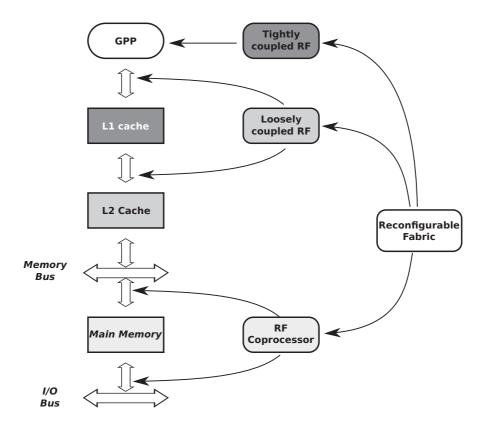

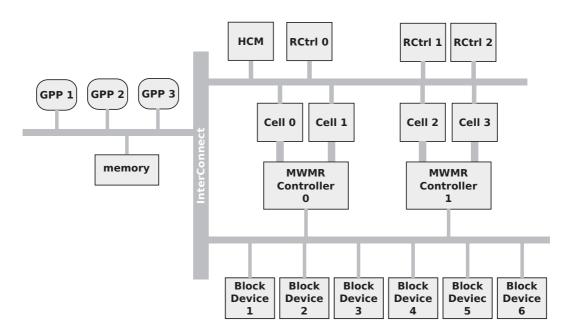

Frequently, the reconfigurable fabrics (RFs) are coupled with GPPs to set up a reconfigurable system. Such systems tend to make good use of both computation structures. High density of parallel data processing are often mapped to RFs, while certain control-intensive operations are left to GPPs. According to the position of RFs in the memory hierarchy, [HD07] summed up the coupling between RFs and GPPs as shown in Figure 3.1.

Tightly coupled RFs can be seen for example in PRISC architecture [RS94], Chimaera architecture [YMHB00], and OneChip architecture [CC01]. Garp architecture [CHW00] is an example of loosely coupled RF. The coprocessor RF can be found in the RaPiD architecture [CFF<sup>+</sup>99] and various commercial systems.

Each of the above coupling styles has its advantages and drawbacks. Normally, the tighter RFs and GPPs are coupled, the lower is the communication overhead between the two computation structures. The looser RFs and GPPs are coupled, the more complicated functions can be put on the RFs, thus greater parallelism can be achieve between the two computation structures. Before choosing an appropriate coupling style, the developer needs to carefully analyze the nature (control-intensive or data-intensive) of an application.

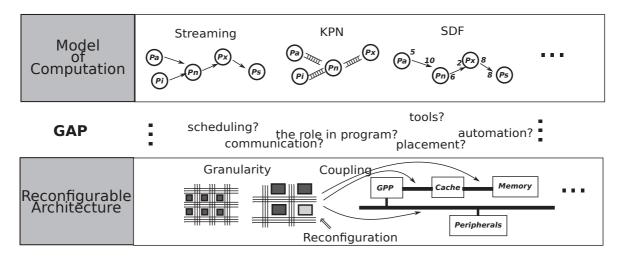

### 3.1.3 Gap Between Computational Models and Reconfigurable Architectures

As shown in Figure 3.2, we have reviewed some commonly used computational models and some key characteristics of the reconfigurable architectures in the last two subsections. However, for application programmers who probably are not experts of hardware, the link between the sea of reprogrammable arrays and their familiar models for describing algorithms is not so obvious. To be able to quickly

Figure 3.1: The Coupling between Reconfigurable Fabrics and General Purpose Processors (adapt from [HD07])

Figure 3.2: Gap between Computation Models and Reconfigurable Architectures

come to a solution, they need the appropriate design methodologies to answer the new problems introduced by reconfigurable architectures. Examples of such problems are: what is the role of RFs in an application? How do they communicate with the GPPs? Which place should a computation be mapped to? When should a computation take place? Are the programmer supposed to take care of all above aspects? Is that possible to have some automation?

There is clearly a gap between the computation models and the reconfiguration architecture, which largely influences the productivity of the application programmer. In the following two sections, we are going to review some efforts to fill the gap. The related works are organized from two angles: how the RFs are integrated in a computing system, and how these extra reconfigurable resources are managed at runtime.

### 3.2 Integration Strategies

In this section, we are going to review some works bridging the semantic gap between the algorithm and the reconfigurable hardware architecture, emphasizing how hardware implemented computations are encapsulated and notified by programming environments.

The related works are categorized into four groups according to different integration strategies. We can see that the way of integration (at task level, process level, thread level or instruction-set level) also influences the way of interactions between a hardware implemented computation and the other parts of the programming environment.

### 3.2.1 Integration at Task Level

Integrating hardware implemented computations as tasks is the integration means which is the closest to the algorithm level. Such an integration usually relies on a specific programming paradigm or a domain-specific language. The hardware implemented computations are recognized as independent tasks (they may also be named actors, nodes or components) in the programming paradigm, where the communications amongst tasks are explicitly decided in most of the cases.

To achieve a task level integration, a high-level abstraction API has to be provided to adapt to the corresponding programming model or domain-specific language. Sometimes, the high-level abstraction API may be built up on thread implementations. Some examples of task level integration are described as follows.

### 3.2.1.1 FOSFOR

The FOSFOR project[GKM<sup>+</sup>12] targets applications written via a SDF model. The author intends to propose a full development flow to reduce the programming complexity of such application on a Heterogeneous System-on-Chip architecture.

At high level, the applications are described as a graph of SDF actors which receive and send certain amount of data tokens through virtual channels. The actors description is made from the standard graphical language UML (Unified Modeling Language). Their interfaces are described using Interface Description Language (IDL3).

At implementation level, the actors are refined as threads. software threads are managed by the RTEMS Operating System (OS), which is able to run on a multiprocessor target by using its *Multi-Processor Communication Interface*; while hardware

threads are managed by a flexible hardware OS, which provides the services including fast system call, thread management, semaphores, simple memory allocation and mailbox. The virtual channels and their corresponding managers are implemented as a middleware on top of the OS, explicitly transferring the exchanged data and implicitly maintaining state coherency through software and hardware.

The preemptive states have been added in the hardware thread Finite State Machines. However, the current scheduling strategy is a Highest-Priority First algorithm sorting statically partitioned thread. The context switch and relocation of hardware threads are left as open issues. The authors also plan to develop a loadbalancing HW/SW partition mechanism and model transformation techniques to automatically generate the actors' code.

### 3.2.1.2 ReConfigME

ReConfigME [WK01, WKJ06] is a set of OS services, which are developed for allocating pure hardware implemented applications onto shared reconfigurable platforms, and for managing shared-memory data communications for each application.

All applications handled by ReConfigME must respect a data flow programming paradigm. Each application should be structured as a data flow graph, which consists of computation nodes and logic connections amongst the nodes. As inputs of ReConfigME, each node is described by an EDIF file, and a JAVA class file is provided to define how EDIF files are connected together.

The ReConfigME is responsible to place the input application, generating the corresponding bitstreams and realizing the actual configuration procedure. An application can be configured to the platform only when all of its nodes can be placed on the FPGA, or the application is put into a waiting queue. In other words, a whole application is the minimum unit to be allocated on the reconfigurable fabrics. The decision of user to load and unload an application is transferred to ReConfigME through a user command-line interface.

As for the aspect of communication, each application is assigned to a dedicated segment of on-board memory. The nodes of the application access the segment of memory through a memory controller. A remote host can send the stimulating data to and collect the final result from the memory segment through a network protocol.

The ReConfigME framework does not support dynamic reconfiguration or partial reconfiguration. When a new application is about to be added to the platform, the clock of FPGA is stopped. The bitstream of the whole FPGA is read out, merged with the bitstream of the newly-added application, then reloaded back to FPGA.

### 3.2.1.3 SPORE

Simple Parallel platfOrm for Reconfigurable Environment (SPORE) [FMG13] is a general theoretical platform which adapts a High Performance Computers (HPC) topology, with nodes composed of computing processing elements and a communication-dedicated element.

Close to OpenCL [ope11], applications in SPORE are viewing as a gathering of independent kernels communicating with each other. All the kernels have both

a software and a hardware implementation, the one eventually used is chosen at execution time depending on available resources and process criticality.

To achieve this HW/SW online codesign, the author proposed a virtualization mechanism to automatically manage kernels and their access. Sequential action sets are carried out by a kernel implementation as the way to deal with the starting and parameters setting of the kernel implementation.

Currently, SPORE has two implementations. One is software HPC platform, which use MPI [For12] for inter-node communication; the other is hardware stream dynamic platform, which is rather dataflow-oriented. Both platform are evaluated in terms of resource usage and job running time. The evaluation revealed that memory is a bottleneck issue led by the symmetric multiprocessing characteristic of their platform. The author intended to develop the third SPORE implementation, in which both the nodes and kernel implementations can have hybrid HW/SW nature.

### 3.2.1.4 Flextiles

In the Flextiles project [LMA<sup>+</sup>12], the application is described as a set of actors, that respects a dataflow model of computation. This on going project aims at providing a virtualization layer in order to mask the underlying heterogeneity of the reconfigurable architecture. Their virtualisation layer will provide self-adaptation capabilities by dynamically relocation of application tasks to software on the manycore or to hardware on the reconfigurable area. Beside the code location, the virtualization layer should also manage on the fly the storage and communication paths. To make this possible, the project also proposes a specific reconfigurable technology based on a virtual bitstream that allows dynamic relocation of accelerators just as software based on virtual binary code allows task relocation.

### 3.2.2 Integration at Process Level

### 3.2.2.1 BORPH

BORPH [hSAS<sup>+</sup>07] provides kernel support for FPGA applications by extending a standard Linux operating system. In BORPH, an instance of a program executing on the reconfigurable fabric is recognized as a hardware process, which is an active independent executing entity equivalent to the conventional software process.

A hardware process is an executing BORPH object file. Such a file is a binary file format that encapsulates, among other information, configuration for reconfigurable fabrics. In order to handle hardware processes, BORPH makes use of an extensible interface provided by the standard Linux kernel and integrates a new binary file format kernel module. The interface provides a system-call-consisted API for user defined binary file formats. The newly-added kernel module serves the requests passed by the extensible interface, such as allocating and configuring the necessary reconfigurable resources during process creation.

BORPH provides hardware processes a hybrid message passing system call interface for both accessing regular data files and to communicate with other processes in the system through UNIX's pipe construct. Besides, the <code>ioreg</code> virtual file system allows passive communication from the controlling processor to gateware designs. Because of the kernel's involvement, access to FPGA resources may be initiated by any UNIX programs: from simple shell scripts to complex compiled programs.

BORPH has been implemented for multi-FPGA platforms. The kernel/user interface of BORPH also makes it possible to employ dynamic partial reconfiguration on a FPGA.

## 3.2.3 Integration at Thread Level

There exists solutions which integrate hardware implemented computations at thread level. Such solutions have the following features in common. They all rely on a multi-threaded programming model. The computation implemented by hardware and software are handled in a unified manner, as threads share the same memory space. To achieve this, an API for hardware thread management is normally built up on the top of an OS, providing services such as scheduling, communication, synchronization, and so forth. A thread interface is usually implemented on the reconfigurable fabric for each hardware computation, providing to the OS the thread elements to manipulate. Some examples of thread level integration are described in the following.

#### 3.2.3.1 HybridThread

HybridThread [ASA<sup>+</sup>08] is a POSIX-compliant multi-threaded programming model across the HW/SW boundary. It is composed of several middleware services and an extended operating system.

The middleware services provide a unified API to create, control and schedule all threads. The executing unit of a specific thread is indicated as an attribute of the creation function. That is to say, the partition is explicitly done in the application code. Each hardware thread has a dedicated system interface called *hardware thread interface*, which allows the hardware thread to execute autonomously and in parallel by supporting system call mechanism and shared memory accesses.

In order to have a promising performance, parts of the OS concerning the hardware thread management are migrated into hardware, including a mutex manager, a CPU bypass interrupt scheduler, a thread scheduler and a thread manager.

A compiler is demanded to automatically and correctly translate the application from a standard high-level programming language to hardware threads that can be synthesized for a specific target platform. As far as we get from the literature, the HybridThread framework neither supports dynamic nor partial reconfiguration.

#### 3.2.3.2 ReconOS

ReconOS [LP07] is an execution environment built on the top of existing embedded operating systems, extending shared memory multi-threaded programming model from the software domain to reconfigurable hardware.

ReconOS employs hardware threads through a dedicated API which is similar to but different from the POSIX or eCos kernel API used by software threads. The HW/SW thread interfacing problem is addressed by using the same OS objects for thread communication and synchronization. Each hardware thread has its own software proxy thread, called delegate thread. The delegate thread is responsible to maintain the OS kernel-mapped objects used by the associated hardware thread.

Hardware thread is structured by two hardware parts: user logic and an OS interface. The user logic implements the computation demanded by the application. The OS interface provides thread supervision and control. Inside this OS interface, there are VHDL-implemented procedures which govern the system calls required by the hardware thread. These system calls are either transformed as an access to shared memory or dedicated hardware FIFO buffer, or relayed to the corresponding delegated thread to execute a software OS call on behalf of the hardware thread.

The current ReconOS prototypes hardware threads are statically configured. The support of dynamic partial reconfiguration is planned in future work by the authors [LP09].

#### 3.2.3.3 FUSE

FUSE [IS11] is a front-end user framework intending to ease the migration of software-implemented tasks to hardware. To attain this goal, the authors proposed a specific creation/destroy API and some OS support organized in two layers.

The API acts as the wrapper of corresponding POSIX thread creation/destruction functions, augmenting their abilities by supporting hardware tasks when a platform contains hardware accelerators. The user-layer OS supports, called *toplevel FUSE component*, provide a decision flow to firstly partition a task on hardware when possible and secondly to assign the task to software otherwise. Thanks to the API and top-level FUSE component, the semantic of task creation/destruction code remains identical in the application program, whatever the underlying platform is.

Although the creation of hardware tasks is encapsulated in POSIX-like thread creation function, the communication and synchronization between software and hardware are not managed at thread-level. In the FUSE framework, all tasks implemented in hardware are considered as memory-mapped I/O devices.

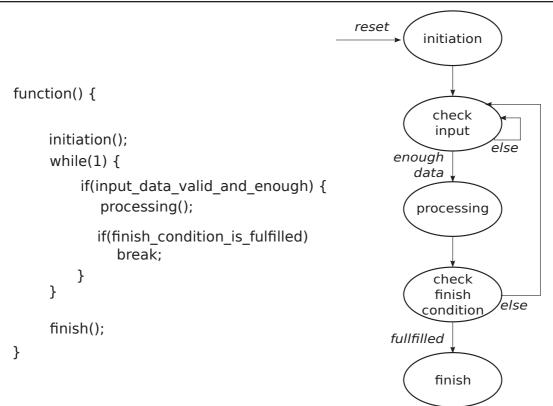

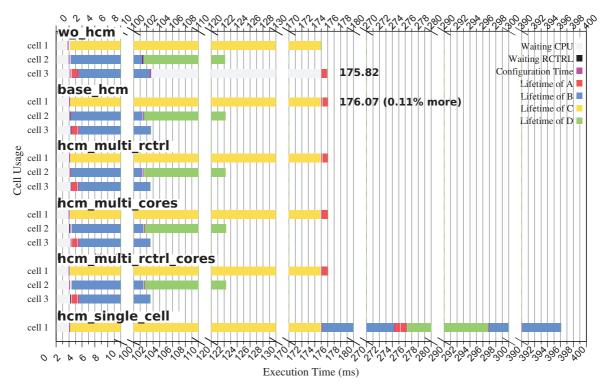

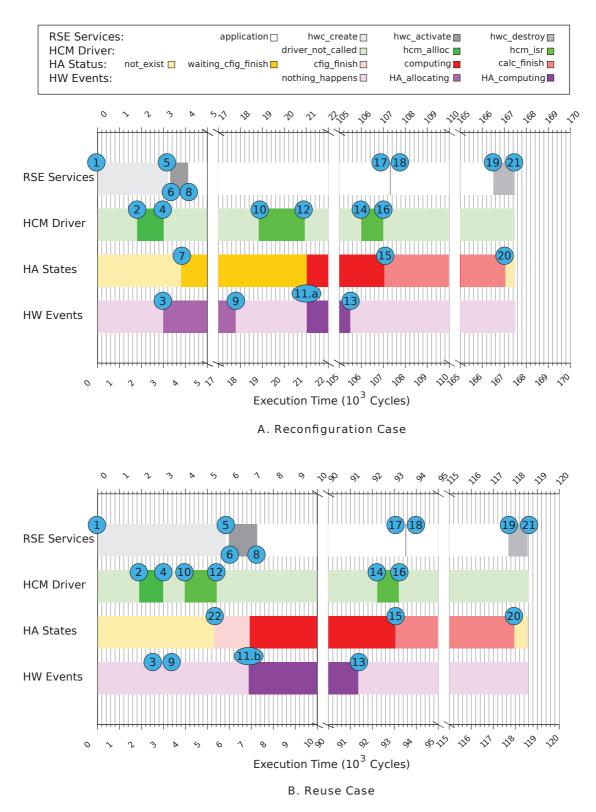

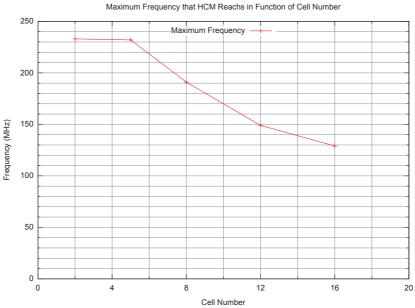

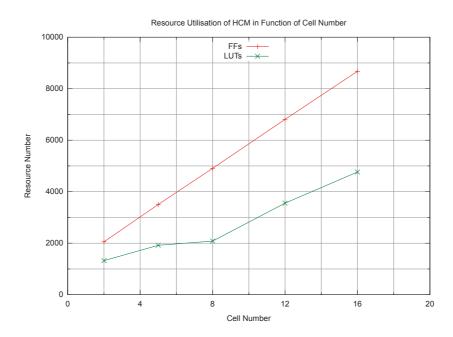

The kernel-layer OS supports, called *low-level FUSE component*, provides the typical file system services (open, close,read, write, iocrl and mmap) to give access to hardware tasks. The device drivers in the low-level FUSE component are customized for each specific hardware task. They can be dynamically loaded to kernel at runtime.