# SiC Nanowires: from growth to related devices Jihoon Choi

#### ▶ To cite this version:

Jihoon Choi. SiC Nanowires: from growth to related devices. Other. Université de Grenoble, 2013. English. NNT: 2013GRENT028. tel-01061784

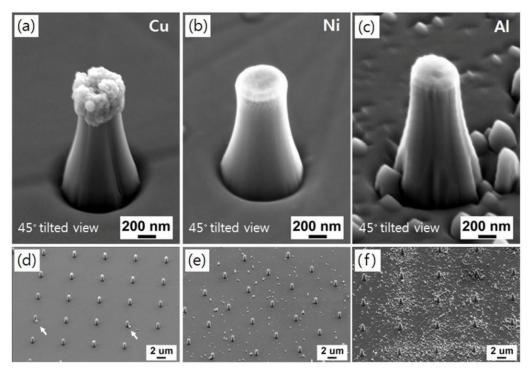

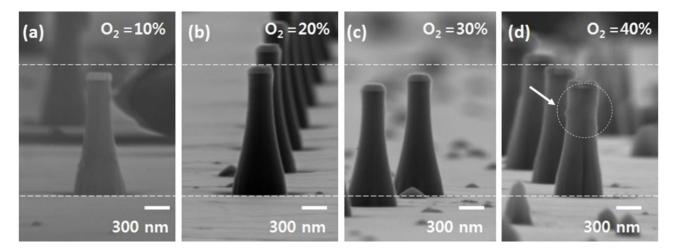

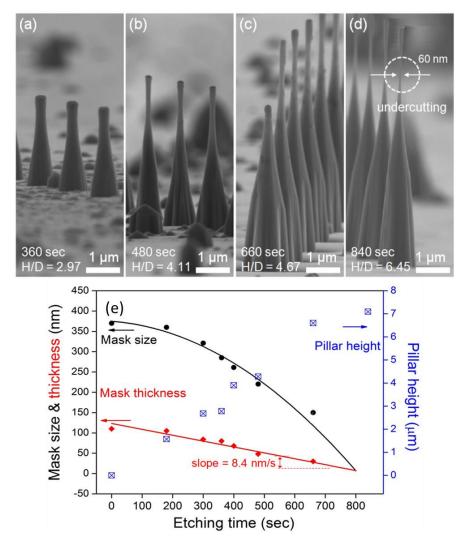

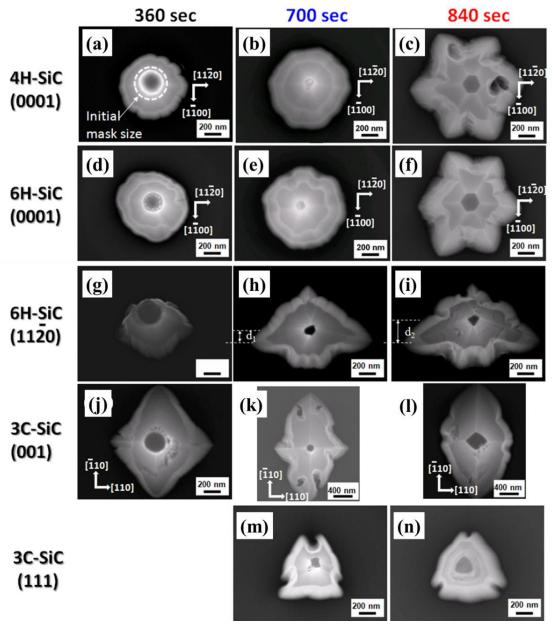

## HAL Id: tel-01061784 https://theses.hal.science/tel-01061784

Submitted on 8 Sep 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE GRENOBLE

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES (NENT)

Arrêté ministériel : 7 août 2006

Présentée par

### **Jihoon CHOI**

Thèse dirigée par **Edwige BANO** et codirigée par **Laurence LATU-ROMAIN**

préparée au sein des Laboratoires IMEP-LAHC et LTM dans l'École Doctorale EEATS

# Silicon carbide nanowires: from fabrication to related devices

Thèse soutenue publiquement le **21 Mars 2013**, devant le jury composé de :

#### M. Michel PONS

Directeur de Recherche CNRS, SiMaP (Président)

#### M. Konstantinos ZEKENTES

Directeur de Recherche, Université de Crete/institut FORTH (Rapporteur)

#### M. Giovanni ATTOLINI

Professeur, IMEM-CNR (Rapporteur)

### M. Mikhael BECHELANY

Chargé de Recherche CNRS, Université Montpellier (Examinateur)

#### **Mme. Edwige BANO**

Professeur, IMEP-LAHC (Directeur de thèse)

#### **Mme. Laurence LATU-ROMAIN**

Maître de conférences, Université Joseph Fourier, LTM (Co- directeur de thèse)

## **Acknowledgements**

Firstly, I would like to thank my two advisors, Edwige Bano and Laurence Latu-Romain for accepting me as a Ph.D. student and for their efforts in building up the research activities at Grenoble University. Without their encouragement and wisdom, it would have been so much harder to conduct this work. I have greatly appreciated to Marco Pala and Alessandro Cresti in IMEP-LAHC for providing me the initial numerical code for the simulation of FET and supervising my simulation results. Also, I would like to thank Laurent Montes for valuable discussions.

During my Ph.D study, I have collaborated with several famous researchers, Giovanni Attolini (IMEM-CNR, Italy), Anne Henry (Linköping University, Sweden), Didier Chaussende (LMGP, France), Marc Portail (CHREA, France), Dominique Planson (Ampere, INSA Lyon, France), Won-Jae Lee (Dong-Eui University, Korea) and Sang-Mo Koo (Kwang-won University, Korea). They have supported me overwhelmingly such as providing expensive SiC nanowires and SiC wafers and/or epilayers.

It has also been a pleasure to interact with my colleagues at the LTM laboratory: Maelig Ollivier, Bassem Salem, Thierry Chevolleau, Thierry Luciani, Florian Dhalluin, Guillaume Rosaz, Martin Kogelschatz, Camille Petit-Etienne, and Thierry Baron. Specifically, I have worked closely and productively with Florian Dhalluin on the etching of SiC nanostructures. I know I could not have all achieved without him.

The whole process for fabricating the nanowire device was performed in the Plateforme Technologique Amont (PTA), Grenoble. I would like to thank the technical staffs: Thibault Haccart, Jean-Luc Thomassin, Delphine Constantin, Frederic Gustavo, Christophe Lemonias and Marlene Terrier. And I would like to thank my former and current office mate in IMEP-LAHC: Louis Gerrer, William Van Den Daele, Amer El Hajj Diab, Louis Fradetal and Sharon Hsu.

I have very much appreciated Konstantinos Zekentes for his detailed reading of my thesis. I have benefited a lot from his comments and discussions. I would also like to thank my committee members; Dr. Giovanni Attolini, Dr. Konstantinos Zekentes, Dr. Michel Pons and Dr. Mikhael Bechelany, for their time and knowledge.

Life at Grenoble is unforgettable. It was very enjoyable working with my bright fellow students. I really want to send my thanks and best wishes to them: Doyoung Jang, Jeawoo Lee, Daeyoung Jeon, Sojung Park, Sungjae Jang, Minkyu Joo, Jungkyu Chae, Hee-eun Kho and Misang Ryu. Finally, I owe more than words to thank my family. This work is dedicated to them.

## Citations to published work

#### **International Journals**

- J. H. Choi, L. Latu-Romain, E. Bano, F. Dhalluin, T. Chevolleau and T. *Baron*, "Fabrication of SiC nanopillars by inductively coupled SF<sub>6</sub>/O<sub>2</sub> plasma etching", J. Phys. D: Appl. Phys. Vol. 45 (2012) p. 235204.

- J. H. Choi, L. Latu-Romain, E. Bano, A. Henry, W. J. Lee, T. Chevolleau, T. *Baron*, "Comparative study on dry etching of  $\alpha$  and  $\beta$ -SiC nano-pillars", Materials Letters Vol. 87 (2012) pp. 9–12.

## **Publications in Refereed Conference Proceedings**

- J. H. Choi, L. Latu-Romain, F. Dhalluin, T. Chevolleau, B. Salem, T. Baron, Didier Chaussende, and E. Bano, "Fabrication of SiC nanopillars by inductively coupled SF<sub>6</sub>/O<sub>2</sub> plasma", Materials Science Forum Vol. 711 (2012) pp 66-69.

- J. H. Choi, L. Latu-Romain, T. Baron, T. Chevolleau and E. Bano, "Hexagonal faceted SiC nanopillars fabricated by inductively coupled SF<sub>6</sub>/O<sub>2</sub> plasma method", Materials Science Forum Vols. 717-720 (2012) pp 893-896.

- J. H. Choi, M. Pala, L. Latu-Romain, and E. Bano, "Theoretical study of thermoelectric properties of SiC nanowires", Materials Science Forum Vols. 717-720 (2012) pp 561-564.

- J. H. Choi, L. Latu-Romain, E. Bano, A. Henry, W. J. Lee, T. Chevolleau, T. Baron, "Comparative study on dry etching of α- and β-SiC nano-pillars", will be published in Materials Science Forum, presented in ICSCRM 2012 (International Conference on Silicon Carbide and Related Materials, held in St Petersburg, September 2012).

#### **Abbreviations**

AFM Atomic Force Microscopy

ALD Atomic Layer Deposition

BTE Boltzmann Transport Equation

CNT Carbon NanoTubes

CVD Chemical Vapor Deposition

CMOS Complementary Metal-Oxide- Semiconductor

DI De-Ionized

DOS Density Of States

EBL E-Beam Lithography

EDX Energy-Dispersive X-ray spectroscopy,

EELS Electron Energy Loss Spectroscopy

FET Field Effect Transistor

GAA Gate-All Around

HRTEM High Resolution Transmission Electron Microscopy

ICP Inductively Coupled Plasma

IPA IsoPropyl Alcohol

MOSFET Metal-Oxide- Semiconductor Field-Effect Transistor

MIBK Methyl-IsoButyl-Ketone

NEMD Non Equilibrium Molecular Dynamics

MC Monte Carlo

MD Molecular Dynamics

MEMS MicroElectroMechanical Systems

NEMS NanoElectroMechanical System

NP NanoPillar NW NanoWire

NEGF Non Equilibrium Green's Function

PF Power Factor

PMMA Poly-MethylMethAcrylate PSD Power Density Spectrum

PR Photo Resist

PVT Physical Vapor Transport

QD Quantum Dot

RIE Reactive-Ion Etching

rms Root Mean Square

rpm Revolutions Per Minute

SEM Scanning Electron Microscopy

Si Silicon

SiC Silicon carbide

SOI Silicon on Insulator

S/D Source/Drain

SR Surface Roughness

TC Thermal conductance

TCR Thermal Contact Resistance

TEM Transmission Electron Microscopy

VLS Vapor–Liquid–Solid VPE Vapor Phase Epitaxy

VS Vapor–Solid

VS-FET Vertical Surround-gate Field-Effect Transistor

XRD X-Ray Diffraction

1D, 2D and 3D One-, Two and Three-Dimension

## **Physical Constants**

| Symbol            | Name                         | Value                                                                       |

|-------------------|------------------------------|-----------------------------------------------------------------------------|

| q                 | Electronic charge            | $1.602 \times 10^{-19} \mathrm{C}$                                          |

| $\epsilon_{ m o}$ | Permittivity of vacuum       | $8.854 \times 10^{-14} \text{ F/cm}$                                        |

| $k_{\mathrm{B}}$  | Boltzmann's constant         | $1.381 \times 10^{-23} \text{ J/K}$<br>$8.617 \times 10^{-5} \text{ eV/K}$  |

| h                 | Planck's constant            | $6.625 \times 10^{-34} \text{ J s}$<br>$4.135 \times 10^{-15} \text{ eV s}$ |

| $\epsilon_{ m r}$ | Relative dielectric constant | $SiO_2 = 3.9$                                                               |

## Parameters in the equation (or in the text)

| Symbol                                | Name                                           | Unit                                                  |

|---------------------------------------|------------------------------------------------|-------------------------------------------------------|

| $C_d$                                 | Depletion layer capacitance                    | [F]                                                   |

| Cox                                   | Gate coupling capacitance                      | [F]                                                   |

| D <sub>it</sub>                       | Electrically active interface states           | [cm <sup>-2</sup> ]                                   |

| Е                                     | Electric field                                 | $[V \cdot \mu m^{-1}]$                                |

| $E_{F}$                               | Fermi energy level                             | eV                                                    |

| E <sub>ON</sub>                       | Electron emission turn-on field                | $[\mathbf{V} \cdot \boldsymbol{\mu} \mathbf{m}^{-1}]$ |

| $E_{Th}$                              | Electron emission threshold field              | [V·µm <sup>-1</sup> ]                                 |

| f <sub>S/D</sub>                      | Fermi function at the Source/Drain             |                                                       |

| G                                     | Electrical conductance                         | $[\Omega^{-1}]$ or $[S]$                              |

| G <sup>&lt;</sup> , G <sup>&gt;</sup> | Lesser than or greater than Green's function   |                                                       |

| $G^A, G^R$                            | advanced or retarded Green's function          |                                                       |

| g                                     | degeneration coefficient (4 for Si, 2 for SiC) |                                                       |

| $g_{\mathrm{m}}$                      | Transconductance                               | $[\Omega^{-1}]$ or $[S]$                              |

| h                                     | Thickness of oxide                             | [nm]                                                  |

| Н                                     | Hamiltonian                                    |                                                       |

| I                        | Current                                  | [A]                                        |

|--------------------------|------------------------------------------|--------------------------------------------|

| L                        | Channel length                           | [nm]                                       |

| L <sub>m</sub>           | Correlation length of surface roughness  | [nm]                                       |

| m* or m <sub>o</sub>     | Effective mass of a carrier              |                                            |

| $m_l$                    | Longitudinal effective mass              |                                            |

| $m_t$                    | Transverse effective mass                |                                            |

| N                        | Carrier concentration                    | [cm <sup>-3</sup> ]                        |

| $N_{1D}$ , $N_{3D}$      | Linear or volume charge density          | [cm <sup>-1</sup> ] or [cm <sup>-3</sup> ] |

| R                        | Radius of nanowire                       | [nm]                                       |

| r                        | Diameter of nanowire                     | [nm]                                       |

| r=(x, y, z)              | 3D position vector                       |                                            |

| S                        | Seekbeck coefficient                     | [V·K <sup>-1</sup> ]                       |

| T                        | Temperature                              | [K]                                        |

| T(E)                     | Transmission coefficient                 |                                            |

| Usc                      | Self-consistent potential energy         | [eV]                                       |

| V                        | Voltage                                  | [V]                                        |

| Z                        | Material's thermoelectric properties     | [K <sup>-1</sup> ]                         |

| β                        | Field enhancement factor                 |                                            |

| Δm                       | Root mean square of surface roughness    | [nm]                                       |

| $\eta$ +                 | Infinitesimal positive value,            |                                            |

| К                        | Thermal conductance                      | [W·K <sup>-1</sup> ]                       |

| $K_{\rm e},~K_{ m ph}$   | Electrical or phonon thermal conductance | $[\mathbf{W} \cdot \mathbf{K}^{-1}]$       |

| $\mu_{	ext{S/D}}$        | Chemical potential at the Source/Drain   |                                            |

| $\mu_{\rm e},\mu_{ m h}$ | Electron or Hole mobility                | $[cm^2 \cdot V^{-1}s^{-1}]$                |

| ρ                        | Resistivity                              | [\O\cm]                                    |

| $\rho(r)$                | Charge distribution                      |                                            |

| $\Sigma_{	ext{S/D}}$     | Self-energy matrices at the Source/Drain |                                            |

| φ                        | Electrostatic potential                  | [V]                                        |

| Ψ                        | Electron wave function                   |                                            |

| $v_{ m d}$               | Drift velocity                           | [cm·s <sup>-1</sup> ]                      |

| ω                        | Phonon frequency                         | [cm <sup>-1</sup> ]                        |

#### **Abstract**

Low dimensional semiconductor nanostructures (such as nanowires (NWs), nanorods and nanotubes) have become the focus of intensive research for exploring new emergent phenomena at the nanoscale and probing their possible use in future electronics. Among these semiconductor NWs, Silicon Carbide (SiC) has very unique properties, such as wide bandgap, excellent thermal conductivity, high breakdown electric field, chemical and physical stability, high electron mobility and biocompatibility. These factors makes SiC a long standing candidate material to replace silicon in specific electronic device applications operating in extreme conditions or/and harsh environments.

SiC nanostructures have been studied extensively and intensively over the last decade not only for their fabrication and characterization, but also for their diverse applications. I have outlined the growth of SiC nanostructures based on different growth methods, a noteworthy feature of their characteristic properties and potential applications in the chapter one.

As-grown SiC NWs fabricated by bottom-up method present a high density of structural defects, such as stacking faults. This kind of defect is one of the factors which lead to poor electrical performance (such as weak gate effect and low mobility) of the related devices. Therefore, it is required to develop a high quality of SiC nanostructures with low density of the structural defects using an alternative method, such as top-down process.

Main objectives of this thesis are divided into three main parts.

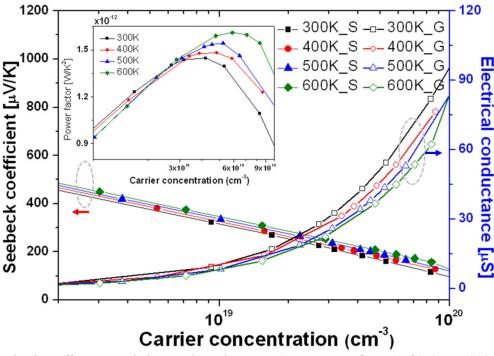

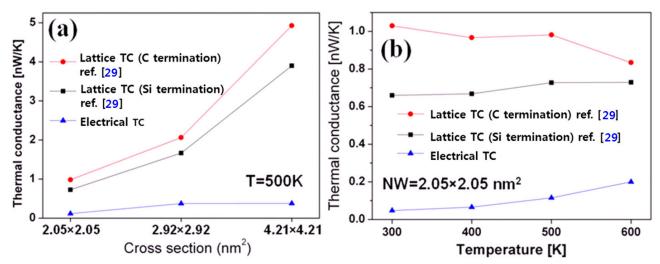

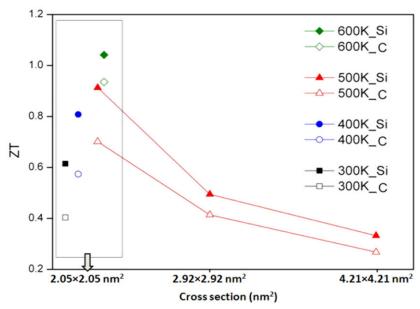

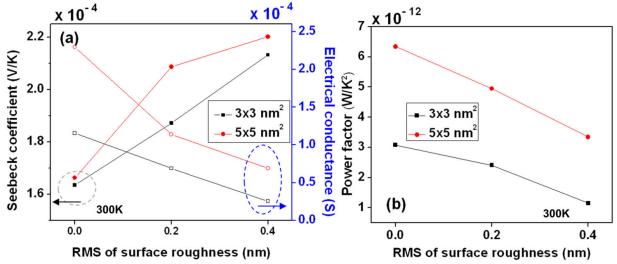

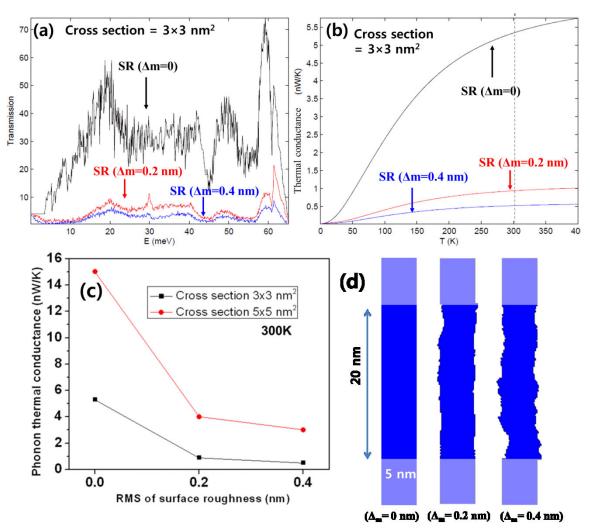

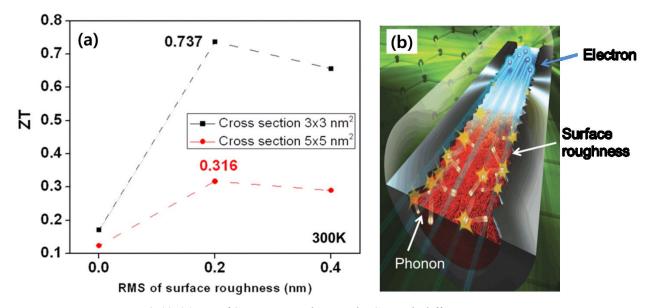

The first part of the thesis (Chapter two), we present the simulation results of the electrical transport and thermoelectric properties of SiC and Si NWs. I have investigated the thermoelectric enhancement by studying the complex interplay of the size of NWs, temperature and surface roughness. Our simulation results show that the ZT of Si terminated SiC NW  $(2.05\times2.05~\text{nm}^2)$  reaches a maximum value of 1.04 at 600K. In case of Si NW, the ZT of Si NW for the cross section  $(3\times3~\text{nm}^2)$  with the SR  $(\Delta_m=0.2~\text{nm})$  is 0.7, which is comparable to the highest experimental ZT value of Si NW (0.6).

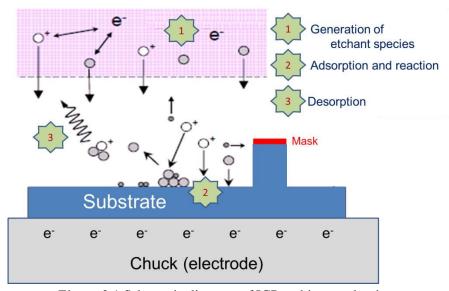

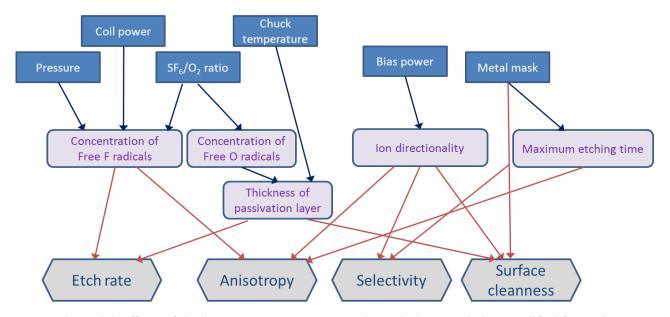

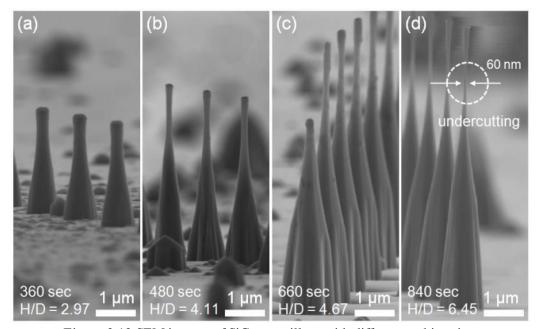

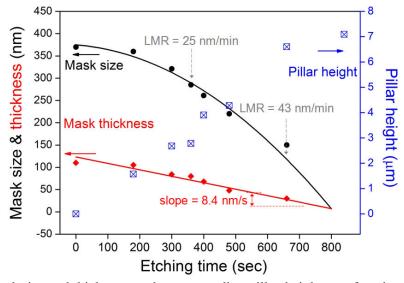

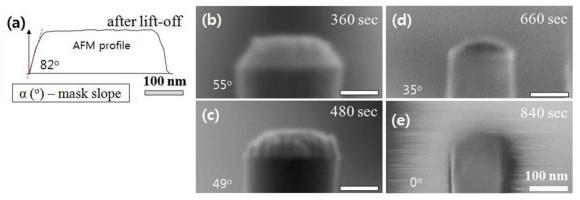

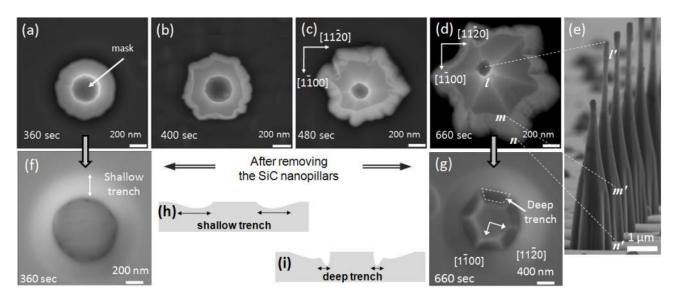

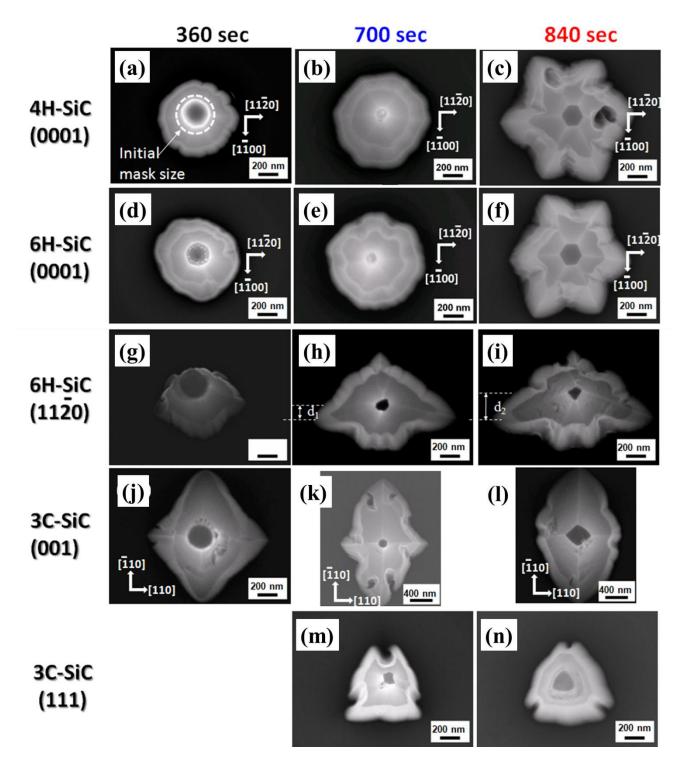

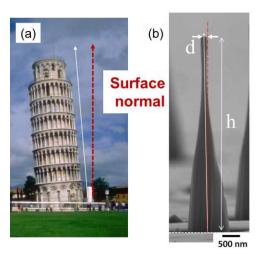

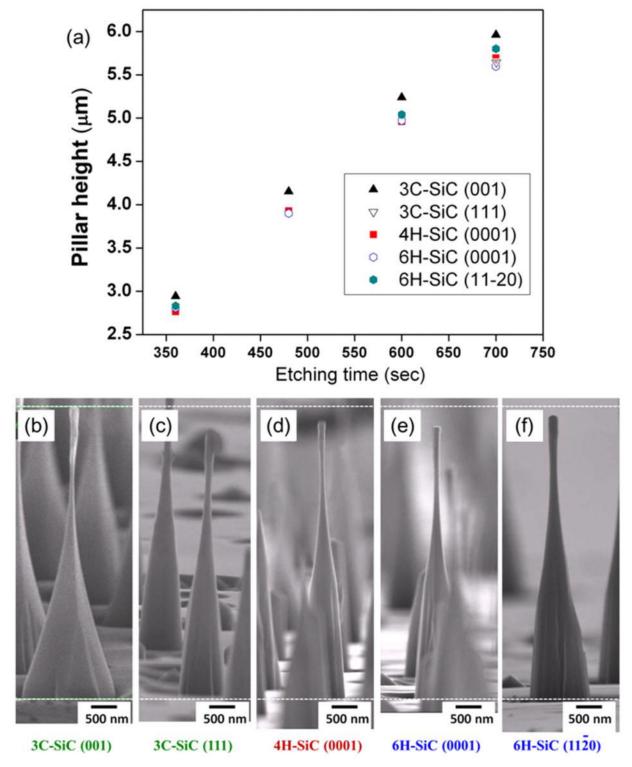

The second part of the thesis (Chapter there) is devoted to the fabrication of high quality SiC nanostructures with controlled doping level. I have developed a top-down fabrication technique for high quality nanometer scale SiC nanopillars (NPs) using inductively coupled plasma etching. The etching behavior of SiC NPs has also been studied depending on polytypes and crystallographic orientations.

Under the optimal etching conditions using a large circular mask pattern with 370 nm diameter, the obtained 4H-SiC nanopillars exhibit high anisotropy features (6.4) with a large etch depth (>7 $\mu$ m). A hexagonal, rhombus and triangle based pillar structures have been obtained using  $\alpha$ -SiC (0001), 3C-SiC (001) and 3C-SiC (111) substrates, respectively. The length of these pillars below 100 nm in diameter is around 1.0  $\mu$ m, which is long enough to reveal the electrical property of SiC nano-FETs.

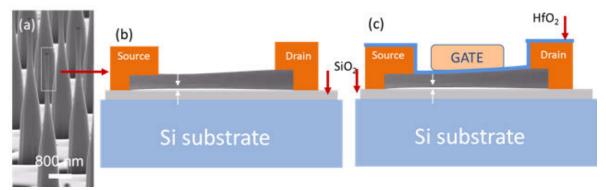

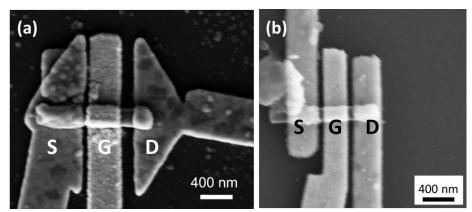

The last part of the thesis (Chapter four) is dedicated to the design and the electrical characterization of SiC nanodevices. To investigate the electrical properties of SiC nanostructures, two different kinds of SiC nanoFETs (SiC NWFET and SiC NPFET) have been fabricated by using SiC NWs and SiC NPs prepared via bottom-up method and top-down methods, respectively.

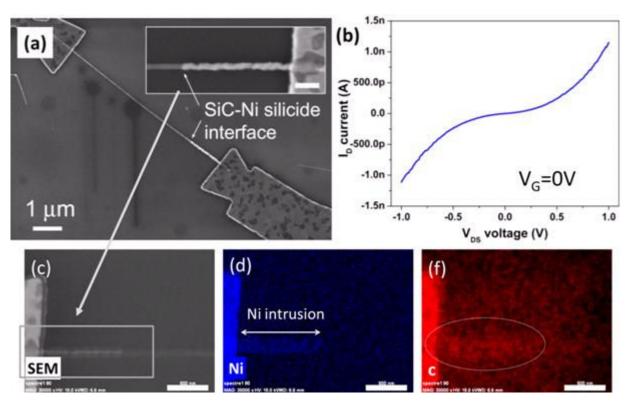

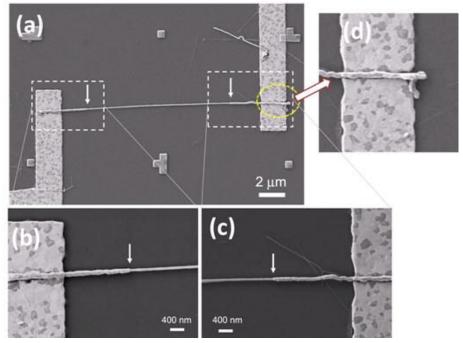

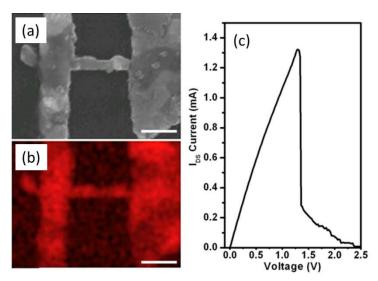

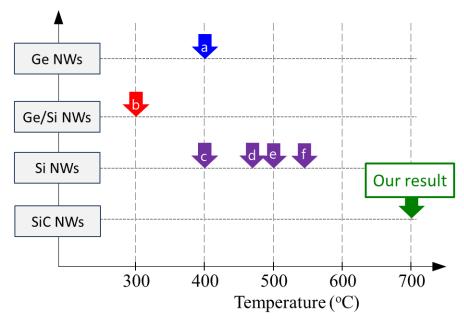

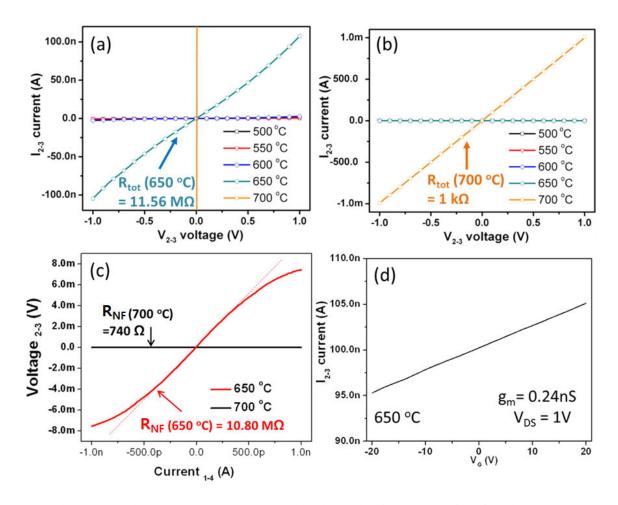

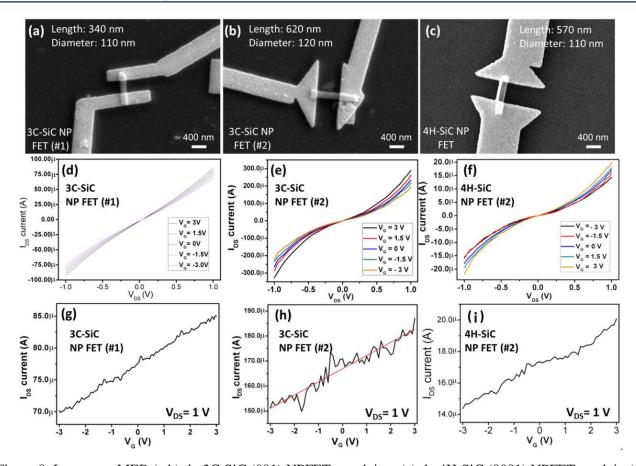

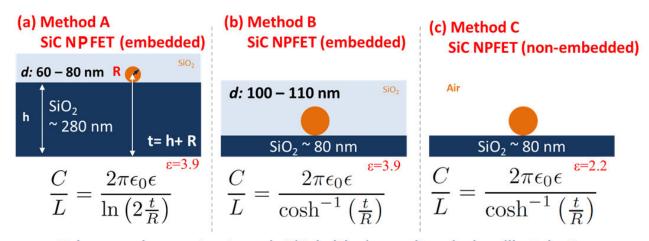

In case of SiC NWFET, low resistivity ohmic contacts (378 k $\Omega$ ) have been obtained after the annealing at 650 °C. Ni silicide intrusion into the SiC NW channel has been observed the annealing at 700 °C. This temperature is compared to one of other group IV materials. In case of SiC NPFET, two different types of NPFET (3C-SiC (001) and 4H-SiC (0001)) have been fabricated using our SiC nanopillars, obtained by top-down approach. The estimated values of the field-effect carrier mobility are 411.6 cm $^2 \cdot V^{-1}s^{-1}$  for 3C-SiC (001) NPFET (#2) and 95.2 cm $^2 \cdot V^{-1}s^{-1}$  for 4H-SiC (0001) NPFET, which is higher than the best values reported in the literature (15.9 cm $^2 \cdot V^{-1}s^{-1}$ ).

## **TABLE OF CONTENTS**

| Introduction                                                              | 1  |

|---------------------------------------------------------------------------|----|

| Chapter 1. Silicon carbide nanowires: growth, properties and applications | 3  |

| 1.1 Introduction                                                          | 4  |

| 1.2 Introduction about bulk SiC                                           | 5  |

| 1.2.1 Polytypism in SiC                                                   | 5  |

| 1.2.2 Properties of bulk SiC                                              |    |

| 1.2.3 Defects in SiC                                                      | 9  |

| 1.3 SiC nanowire growth                                                   | 10 |

| 1.3.1 Introduction: the fabrication methods of nanowires                  | 10 |

| 1.3.2 Bottom-up growth mechanisms of nanowires                            | 11 |

| 1.3.3 Fabrication of SiC nanowires                                        | 13 |

| 1.4 Properties of SiC nanowires                                           | 20 |

| 1.4.1 Mechanical properties of SiC nanowires                              | 20 |

| 1.4.2 Electrical properties of SiC nanowires                              | 21 |

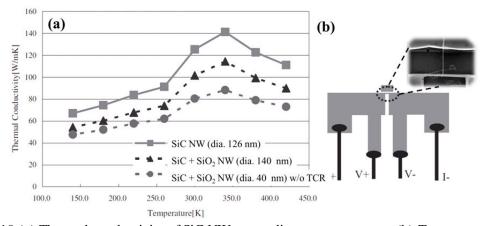

| 1.4.3 Thermal property of SiC nanowires                                   | 23 |

| 1.5 Potential applications of SiC nanowires                               | 24 |

| 1.5.1 Field emission display                                              | 24 |

| 1.5.2 SiC nanowires as fillers for composite matrix materials             | 25 |

| 1.5.3 NEMS applications                                                   | 25 |

| 1.5.4 Energy conversion devices                                           | 25 |

| 1.5.5 Catalytic nanomaterials                                             | 27 |

| 1.5.6 Nanowires for self-cleaning coating films                           | 27 |

| 1.5.7 Hydrogen storage                                                    | 28 |

| 1.5.8 Nanodevices                                                         |    |

| 1.5.9 Bio-related application                                             | 29 |

| 1.6 Conclusion                                                            | 30 |

| Chapter 2. Modeling of electrical transport in Si and SiC nanowire FET    | 37 |

| 2.1 Introduction                                                          | 38 |

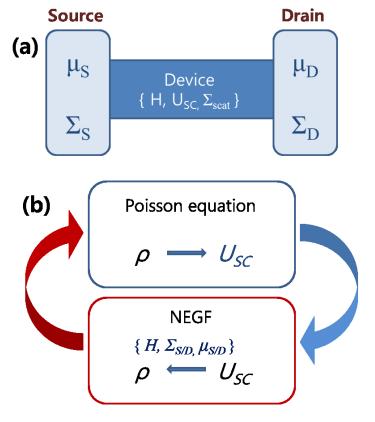

| 2.1.1 Self-consistent solution                                            | 38 |

| 2.1.2 Non equilibrium Green's Function formalism                          | 40 |

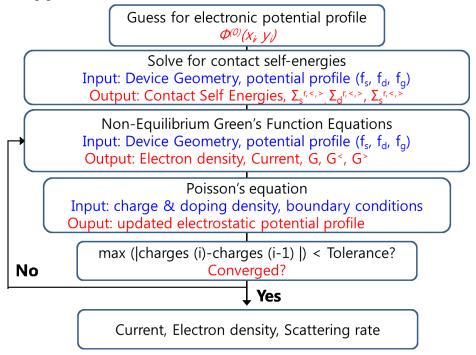

| 2.1.3 Presentation of the simulation scheme                               | 41 |

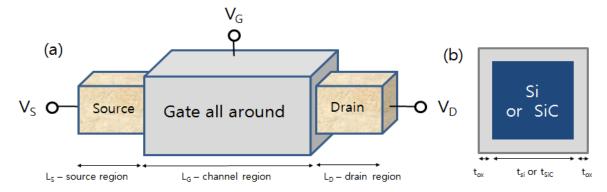

| 2.2 Electrical transport of nanowires                                     | 43 |

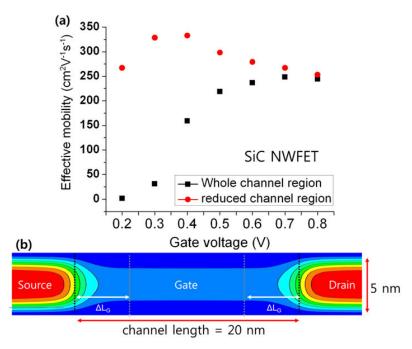

| 2.2.1 Effective mobility                                                  | 43 |

| 2.2.2 Surface roughness effect                                            | 45 |

| 2.3 Simulation of thermoelectric properties of Si and SiC nanowires       | 47 |

| 2.3.1 Theoretical background of thermoelectric properties                 | 48 |

|      | ch thesis summary (Résumé de la thèse française)                      |     |

|------|-----------------------------------------------------------------------|-----|

| Appe | endix                                                                 | 138 |

| Conc | clusion and Perspectives                                              | 135 |

| 4.4  | Conclusion                                                            | 129 |

|      | 4.3.2 Electrical property of SiC nanopillar FET                       |     |

|      | 4.3.1 Improvement of ohmic contact of SiC nanowire by Ni silicidation | 109 |

|      | 4.3.1 Electrical properties of SiC NWFET                              | 107 |

| 4.3  | Electrical characterization of SiC nanoFET                            | 107 |

|      | 4.2.2 Fabrication steps of SiC NPFET                                  |     |

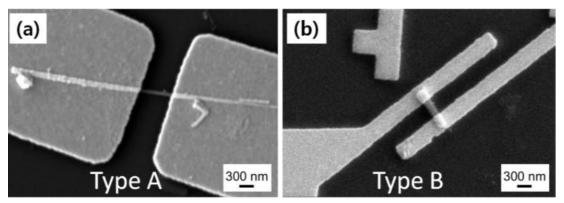

|      | 4.2.1 Fabrication steps of SiC NWFET                                  |     |

| 4.2  | Fabrication process of SiC nanowire FETs                              |     |

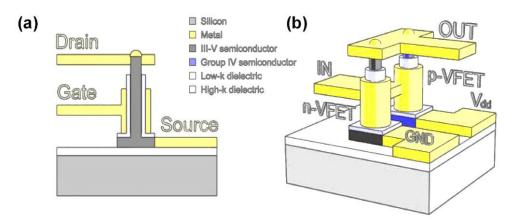

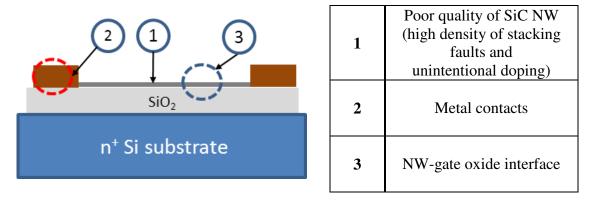

|      | 4.1.2 Issues for high performance of SiC nanowire FETs                |     |

|      | 4.1.1 Important issues for the fabrication of nanowire FETs           |     |

| 4.1  | Introduction: the state-of-the-art of nanoFET                         | 92  |

| Chap | oter 4. SiC nanoFETs                                                  | 91  |

| 3.4  | Conclusion                                                            | 86  |

|      | 3.3.7 Experiments with the Bosch process                              | 83  |

|      | 3.3.7 Fabrication of SiC FinFET like structures                       |     |

|      | 3.3.6 Dependence of polytypes and crystal orientations                |     |

|      | 3.3.5. Hexagonal shape of SiC nanopillars                             |     |

|      | 3.3.4. Etching profile evolution over etching time                    |     |

|      | 3.3.2 Effect of SF <sub>6</sub> /O <sub>2</sub> flow rate ratio       |     |

|      | 3.3.1 Effect of metal mask species                                    |     |

| 3.3  | Experimental results for the fabrication of SiC nanopillars           |     |

|      | 3.2.3 Etching phenomena                                               |     |

|      | 3.2.1 Etching mechanism of inductively coupled plasma                 |     |

| 3.2  | Dry etching of SiC                                                    |     |

|      | Introduction                                                          |     |

| _    | oter 3. Fabrication of SiC nanostructures by top-down method          |     |

|      |                                                                       |     |

| 2.4  | Conclusion                                                            |     |

|      | 2.3.2 Simulation results of thermoelectric properties of Si nanowires | E.  |

## Introduction

The main focus of this Ph.D. thesis is to develop new methodologies and design strategies for the fabrication of SiC nanostructures and SiC nanodevices.

This thesis is organized in the following manner.

- ✓ In the first chapter of this thesis, I briefly introduces the properties of bulk SiC (section 1.2), including the polytypism and defects, because the basic properties of NWs are originally based on their parent materials. And then, the current research activities is introduced to synthesize one dimensional semiconductor nanowires by covering different methods (either top-down or bottom-up techniques) in section 1.3. I summarize the current state of the research on the properties (section 1.4) and the related applications (section 1.5) of SiC nanostructure.

- ✓ Chapter two presents the device numerical simulations of SiC (and Si) nanowire based on the selfconsistent solution of the Schrödinger and Poisson equations within the NEGF formalism. The electrical transport in SiC (and Si) NWFET has been investigated in SiC (and Si) NWFET (section 2.2), including the thermoelectric properties (section 2.3).

- ✓ Chapter three contains the details of process parameters and relevant results for the fabrication of one dimensional SiC nanostructures by top-down approach using ICP etching. In addition, the dependency of polytypes and crystallographic orientations are discussed, which are responsible to control the morphology of etched SiC nanostructures. It is demonstrated that SiC nanopillars can be successfully fabricated.

- ✓ In the Chapter four, two different kinds of SiC nanoFET (SiC NWFET and SiC NPFET) have been developed to reveal the electrical property of SiC nanostructures. SiC NWFET is fabricated by using SiC NWs prepared via bottom-up method. SiC NPFET is fabricated by using SiC nanopillar demonstrated in the chapter 3. The detail device fabrication process and the electrical characterization are presented in this chapter.

- ✓ Finally, the summary of our findings is given in the conclusion together with a discussion of possible future directions.

# Chapter 1. Silicon carbide nanowires bibliography: growth, properties and applications

| 1.1 Introduction                                              | 4  |

|---------------------------------------------------------------|----|

| 1.2 Introduction about bulk SiC                               | 5  |

| 1.2.1 Polytypism in SiC                                       | 5  |

| 1.2.2 Properties of bulk SiC                                  | 7  |

| 1.2.3 Defects in SiC                                          | 9  |

| 1.3 SiC nanowires growth                                      | 10 |

| 1.3.1 Introduction: the fabrication methods of nanowires      | 10 |

| 1.3.2 Bottom-up growth mechanisms of nanowires                | 11 |

| 1.3.3 Fabrication of SiC nanowires                            | 13 |

| 1.4 Properties of SiC nanowires                               | 20 |

| 1.4.1 Mechanical properties of SiC nanowires                  | 20 |

| 1.4.2 Electrical properties of SiC nanowires                  | 21 |

| 1.4.3 Thermal property of SiC nanowires                       | 23 |

| 1.5 Potential applications of SiC nanowires                   | 24 |

| 1.5.1 Field emission display                                  | 24 |

| 1.5.2 SiC nanowires as fillers for composite matrix materials | 25 |

| 1.5.3 NEMS applications                                       | 25 |

| 1.5.4 Energy conversion devices                               | 25 |

| 1.5.5 Catalytic nanomaterials                                 | 27 |

| 1.5.6 Nanowires for self-cleaning coating films               | 27 |

| 1.5.7 Hydrogen storage                                        | 28 |

| 1.5.8 Nanodevices                                             | 28 |

| 1.5.9 Bio-related applications                                | 29 |

| 1.6 Conclusion                                                | 30 |

#### 1.1 Introduction

Nanostructured materials are a new class of materials, having dimensions in the 1 - 100 nm range. Over the past decade, one-dimensional (1D) semiconductor nanomaterials have formed a promising category for their exclusive electrical, mechanical and optical properties, and potential applications in nanotechnology, such as nanoelectronics [1], nanooptics [2] and nanosensors [3]. The novel properties of 1D nanostructures are caused by their nanoscale dimension, morphology and crystal structure. In the literature, a lot of different names of 1D nanostructures can be found to refer the differences in shape and dimensions, like nanowires, nanotubes, nanowhiskers and nanorods, as summarized in Table 1.1.

|              | Diameter (nm) | Length (µm) | Cross section | Ref.         |

|--------------|---------------|-------------|---------------|--------------|

| Nanowires    | 1 – 100       | 1-100       | Cylinder      | [ <u>4</u> ] |

| Nanotubes    | 1 – 100       | 1-100       | Hollow        | [ <u>5</u> ] |

| Nanorods     | 1 – 100       | < 2         | Cylinder      | [ <u>6</u> ] |

| Nanowhiskers | ≥ 1000        | 10 - 1000   | Cylinder      | [ <u>7</u> ] |

| Nanocables   | 1 – 100       | 1-100       | Core-shell    | [ <u>8</u> ] |

Table 1.1 Nomenclature for various one-dimensional nanostructures.

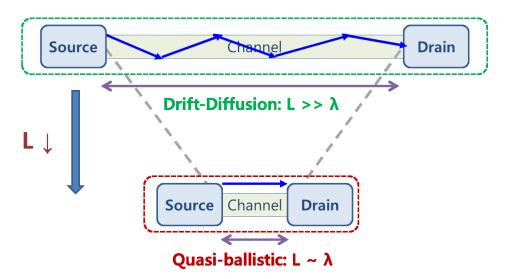

Among the 1D nanostructures, nanowires (NWs) have two quantum confined directions with a diameter between 1 and 100 nm, while still leaving one unconfined direction with a length of several microns. Due to sufficiently small dimension of NWs, it has also been proposed as promising solution for the overcoming down-scaling limitations of CMOS devices. In addition, NWs are expected to exhibit significantly different electrical properties from their bulk counterparts, such as ballistic transport, owing to quantum confinement effects along the transverse direction. The quantum confinement effect exists when the diameter (d) is such that  $d < 2R_{Bohr}$ , where  $R_{Bohr}$  is the Bohr radius. Wu et al. [9] estimated the Bohr radius of 3C-SiC to be 2.7 nm, so SiC nanostructures with sizes less than 5.4 nm have an obvious quantum confinement effect and quasiballistic transport. The other prominent feature of NWs is their higher surface-to-volume ratio than bulk counterpart, which provides higher sensitivity to the surrounding environment. Therefore, NWs are excellent candidates for sensing applications due to more reaction area per volume. These properties of NWs have stimulated new device design concept for a variety of applications in electronics [1], photonics [2] and sensors [3].

NWs can be synthesized either by a top-down or by a bottom-up approach. Much effort has been devoted to fabricate high-quality semiconductor NWs based on different techniques. There has been significant progress made in the area of the fabrication of NWs, such as dimension and morphology control, chemical composition and alignments, etc.

First, I'll briefly introduce the properties of bulk SiC in section 1.2, including the polytypism and defects, because the basic properties of NWs are originally based on their parent materials. Then I'll describe recent progress and advances in the growth of NWs in section 1.3. In the section 1.4, I'll review the important properties of the SiC NWs, in particular, electrical, mechanical, and thermal properties. Finally, I'll explore and address possible applications based on SiC NWs in section 1.5, including the simulation and the experimental results of the literature.

#### 1.2 Introduction about bulk SiC

SiC is a IV–IV compound semiconductor. The crystalline structure of SiC is composed of strong tetrahedral SP<sup>3\*</sup> bonds of carbon (C) and silicon (Si) atoms. SiC has been considered as a long standing candidate material to replace silicon in specific electronic device applications, which required high temperature, high power, high frequency and extreme environments.

The technology of single crystalline SiC growth has been developed over the past decades and has shown commercial availability of SiC substrates of ever-increasing diameter and quality. Most successful method for the growth of large SiC crystals of high quality is the physical vapor transport (PVT) method [10], also known as seeded sublimation growth.

Currently, commercial hexagonal 4H- and 6H-SiC polytypes substrate are now available at diameters up to 150 mm. It has opened the way for the fabrication of electronic devices with steadily improving performances, but the price of substrate is still relatively expensive. Increasing substrate diameter while reducing the defects is crucial for reducing the cost of SiC materials and SiC based devices. An optimistic point is that the progress in commercial growth of SiC has occurred much quicker than Si and GaAs. SiC substrates of high quality and cost-effective with ever-increasing diameter will be available within the near future.

#### 1.2.1 Polytypism in SiC

SiC exists in hundreds of different polytypes, which have the same chemical composition but different crystalline structures. The polytypes of SiC is defined by the combination of the number of stacking layers and the type of crystal symmetry in an unit cell. The popular polytypes are 3C-, 4H- and 6H-SiC, as presented in Figure 1.1. Small crystal inclusions of 2H-, 15R-SiC can be found on 4H and 6H wafers. H, C, and R stand for hexagonal, cubic, and rhombohedral, respectively.

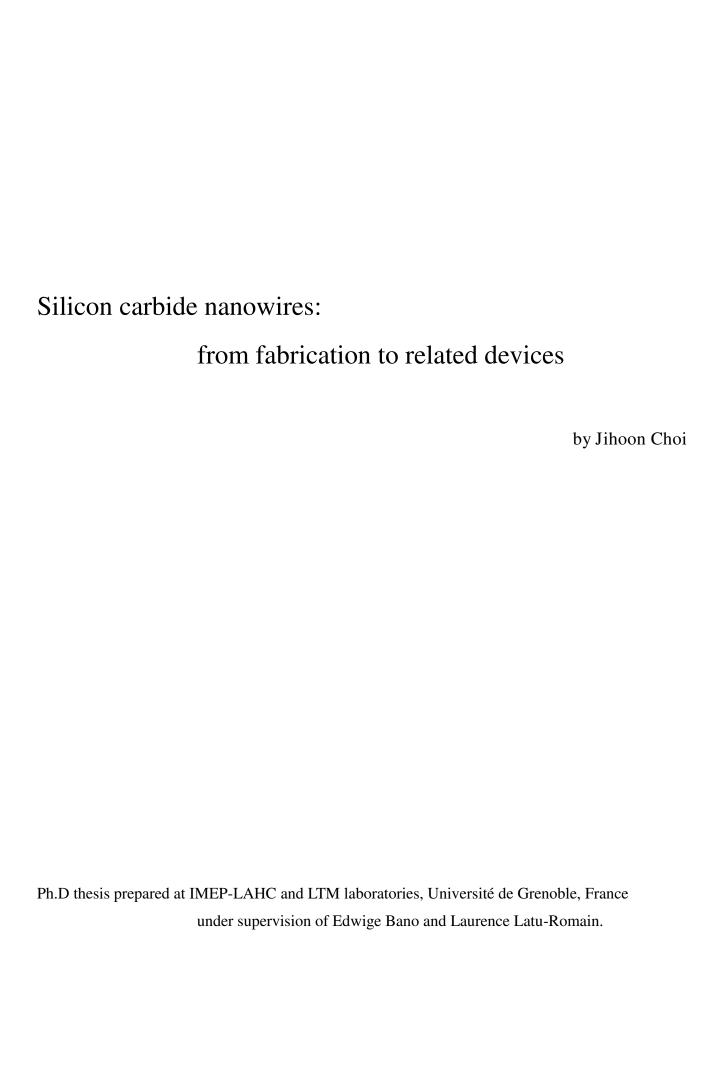

Figure 1.1 (a) Elementary Si-C tetrahedron, (b) projection of the different positions of the atoms, Stacking sequences for different SiC polytypes, (c) 3C-SiC, (d) 4H-SiC and (e) 6H-SiC, respectively [10].

The structure of SiC (the [0001] direction) is the tetrahedrally bonded carbon atoms linked to three Si atoms within the bilayer (see Figure 1.1(a)). Each SiC bilayer can be oriented into only three possible positions (A-, B- and C- cites), as shown in Figure 1.1(b), with respect to the lattice while the tetrahedral bonding is

maintained. The stacking sequence of 3C-SiC is ABCABC in Figure 1.1(c) 4H-SiC is composed of an equal number of cubic and hexagonal structures with stacking sequences of ABCB (the hexagonality is 50%) in Figure 1.1(d). 6H-SiC consists of two-thirds of cubic bonds and one-third of hexagonal bonds with stacking sequences of ABCACB (the hexagonality is 33%) in Figure 1.1(e). Generally, 4H- and 6H-SiC are called  $\alpha$ -SiC, 3C-SiC is referred to as  $\beta$ -SiC because it is the only cubic SiC crystalline structure, and corresponds to the zinc-blende structure. As is obvious from the definition, cubic structure of 3C-SiC shows zero hexagonality. The band energy gap of SiC polytypes tends to increase with increasing the degree of hexagonality.

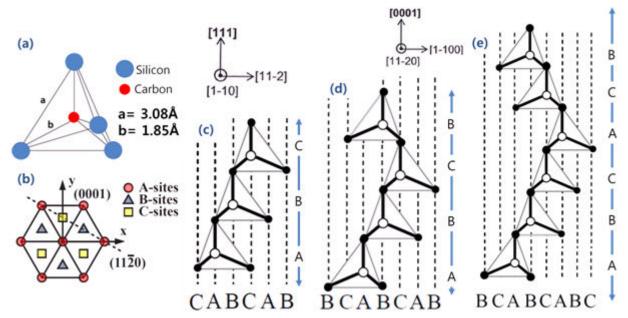

Figure 1.2 Stability diagrams of SiC polytypes [11].

The stability of the different polytypes is mainly a function of temperature and supersaturation as shown in Figure 1.2 according to Knippenberg (1963) [11]. The cubic form of SiC (3C-SiC) is believed to be more stable than the hexagonal structure (4H- and 6H-SiC) at low temperature (below 2000 °C).

#### ■ 4H- and 6H- SiC

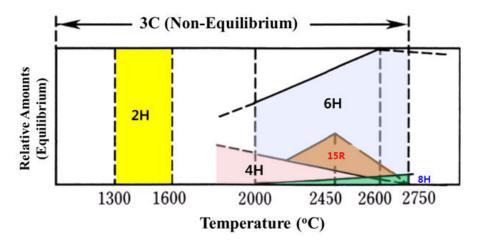

Except for the cubic polytype of SiC (3C-SiC), other polytypes of SiC are anisotropic. In particular, hexagonal structure shows a clear distinction between the different directions in the lattice, as illustrated in Figure 1.3. Therefore, electrical properties can vary not only between the polytypes, but also with the crystal orientation of polytypes.

Figure 1.3 Hexagonal lattices of (a) c-, (b) m- and (c) α-planes on 4H- or 6H-SiC substrates.

The direction parallel to the central axis in the hexagonal structure is called the crystal axis, or c-axis (blue arrow in Figure 1.3a). In commercially available wafer, the c-axis noted as the [0001] direction is either perpendicular the substrate which is a (0001) plane or slightly disoriented of about 3 to  $8^{\circ}$  to be able to favor, further and homo-epitaxy by the step controlled growth [12].

#### ■ 3C-SiC

3C-SiC is the only crystalline structure with isotropic morphology. Therefore, the electrical properties are same in different directions. The advantage of 3C-SiC is that it is able to be grown on Si substrates, therefore it can provide the large size, low price and the possibility in the future of integration of 3C-SiC devices with Si technology. However, it doesn't guarantee high quality of polytypes due to the large lattice constant (~20 %) and thermal coefficient (~8%) mismatch between Si and SiC interface. That is why the best crystalline quality of 3C-SiC is obtained on hexagonal SiC seeds [13, 14]. In comparison with 4H-SiC, the 3C-SiC shows lower hole mobility, smaller band-gap and larger electron mobility.

#### 1.2.2 Properties of bulk SiC

SiC is a material of great interest because of its intrinsic physical and chemical properties in comparison with other semiconductors, as listed in Table 1.2.

Si **GaAs** 3C-SiC 4H-SiC 6H-SiC **GaN Diamond**  $E_{\sigma}(eV)$ 1.12 1.43 2.4 3.2 3.0 3.3 5.5 Band gap type (Direct [D] or I Ι I Ι D Ι D indirect [I]) 947 ⊥c 415 ⊥c Electron mobility 1300 8500 1000 400 2200  $(\mu_e) (cm^2 \cdot V^{-1} \cdot s^{-1})$ 1141 ||c 87 ||c Saturation 2.7 velocity(v<sub>sat</sub>) 1.0 1.0 2.5 2.0 2.0 2.0  $(10^{7} \text{cm} \cdot \text{s}^{-1})$ Hole mobility (µh) 480 400 40 120 80 30 1600  $(cm^2 \cdot V^{-1} \cdot s^{-1})$ Thermal conductance 1.5 0.5 3.5 - 5.03.5-5.0 3.5-5.0 1.3 20.0  $(\mathbf{W} \cdot \mathbf{cm}^{-1} \mathbf{K}^{-1})$

Table 1.2 Comparison of SiC and other semiconductors [15].

(\(\percaperage c\): perpendicular to the c-plane, \(\percaperage c\): parallel to \(\cercaperage c\)-plane)

3.0

6.1

5.0

3.5

2.5

3.2

#### Wide bandgap

Critical field (E<sub>c</sub>)

Density (g·cm<sup>-3</sup>)

$(MV \cdot cm^{-1})$

0.25

2.3

0.3

5.3

The wide band gap of SiC (2.3 - 3.3 eV) opens up for SiC devices to be used at very high temperatures (in excess of 600 °C), because the thermal generation of electron-hole pair is low. Thanks to its wide bandgap, SiC material shows a higher than  $10^{12}$  cm<sup>-3</sup> intrinsic carrier concentration at over 1000 °C.

2.0

3.2

2.2

3.2

#### ■ High breakdown field and high saturated electron drift velocity

Thanks to its wide band gap, SiC also possesses a very high breakdown field (3 - 5 MV·cm<sup>-1</sup>). The breakdown field of SiC is about ten times higher than the one of Si. The high electric breakdown field allows the fabrication of SiC devices with a theoretical power efficiency two orders of magnitude better than Si devices. High breakdown electric field of SiC enables to fabricate the device with small size, low-resistive and high-power.

The combination of high breakdown field and high saturated electron drift velocity values allowed also publication of high performance microwave PIN diodes [16].

#### High thermal conductivity

SiC has nearly three times as high thermal conductivity (350 - 490 W·m<sup>-1</sup>K<sup>-1</sup>) compared to Si and 7 times higher than GaAs, and is superior to Cu. Therefore, SiC based devices operate at extremely high power levels, since it can dissipate heat more efficiently. If this property is coupled with low thermal expansion, SiC devices could be used for specific applications, which require thermal shock resistant environment.

Due to these properties of SiC mentioned above, SiC is expected to operate with the most advantageous benefits over conventional Si and GaAs electronics in high-power applications.

#### Chemical inertness

SiC has very high etch resistance in most acid and alkaline solutions due to its chemical inertness. Therefore, SiC has attracted much attention as a possible material for microelectromechanical systems (MEMS) operating in harsh environments (aggressive and corrosive media). In addition, the native oxide is silicon dioxide, which makes SiC directly compatible with the usual Si technology.

#### Biocompatibility

SiC is one of the semiconducting materials that possess an excellent biocompatibility and great sensing potentiality compared to Si, which is widely used for fabrication of biological systems. According to our knowledge, several reports are found in the literature, which investigates crystalline SiC biocompatibility [17, 18]. Colett and Saddow et al. [17] have investigated the biocompatibility of SiC polytypes compare with Si by culturing mammalian cells directly on substrates. SiC in all its phases shows better proliferation than Si for all mammalian cell lines studied. There are no significant differences of the cell proliferation on different SiC polytypes. They suggest that two possible explanations could be the basis of the enhanced cell proliferation observed on SiC substrates. From the contact angle images, SiC surfaces are more hydrophilic than Si surfaces and mammalian cells preferentially adhere to hydrophilic surfaces.

It is known that surfaces with a normal electrochemical potential close to the one of the cells are more biocompatible [17]. Since the electrochemical potential of carbon is comparable to that of living tissue, the higher carbon concentration of the SiC surfaces most likely justifies SiC greater biocompatibility. The results of this biocompatibility study show that SiC is indeed a better promising material for bio-applications than Si, whose cytotoxicity has been reported by several studies [17]. These results open up exciting perspectives for in a variety of medical applications (e.g. implant coating material [18]) and bio-electronic devices.

#### 1.2.3 Defects in SiC

As any real crystal, the SiC crystals and epilayer also suffer from defects. The defect density in SiC is still high compared with Si. Defects have been a major limiting factor for SiC based applications because they are often detrimental to the behavior of electrical devices. It is therefore critical to understand the impact of various kinds of defects. In this section, I'll briefly introduce the defects related with SiC materials.

#### ■ Structural defects in SiC bulk and epilayer

The most severe defect in the crystal and epilayer structure of hexagonal SiC is called micropipe, which looks like wormholes with micro-diameter-scale. The micropipes decreased the breakdown voltage and increased the leakage currents in high-field devices. The density of micropipes of commercial available SiC wafer was scaled down to around zero per cm<sup>2</sup>. Closed-core axial screw dislocation defects are similar in structure and strain properties to micropipes, but the core is solid instead of a hollow void due to smaller Burgers vector [19]. Overall dislocation densities of commercial available SiC wafer have been reduced by up to low 10<sup>4</sup> cm<sup>-2</sup> [20].

#### Defects in SiC nanostructures

Most SiC NWs are the cubic zinc-blend structure ( $\beta$ -SiC) oriented along the thermodynamically preferred [111] direction because of the low growth temperature (1000  $^{\circ}$ C) [11]. The dominant defects in SiC nanostructures, are the staking faults. A very small energy is needed to create a stacking faults (SFs) in SiC [21]. Theoretically, it has even been calculated the SFs energy in cubic SiC should be negative [22]. That is why SFs are easily created.

As-prepared SiC NWs by bottom-up methods show a high density of SFs perpendicular to the growth direction. SFs in low dimensional structures are generally thought to originate from release of thermal stress during the growth process. The imperfections of 1D SiC nanostructures strongly influence the performance of SiC NWs based devices, but it remains less explored.

In summary, I briefly presented certain kind of defects with SiC materials and studied root causes of each defect, because the defects have a strong influence on the performance of SiC devices. The removal of defects is still a main challenge for SiC material itself as well as related applications. We expect that the density of defects will be dramatically reduced in the near future with improved crystal growth processes.

#### 1.3 SiC nanowires growth

#### 1.3.1 Introduction: the fabrication methods of nanowires

There are two different approaches to the production of 1D nanostructures: top-down and bottom-up technologies. These terms were first introduced in the field of nanotechnology by the Foresight Institute in 1989.

Figure 1.4 Illustrations of (a) top-down and (b) bottom-up approach [23].

Top-down approach literally means that it transforms a bulk material into several structures until reaching the desired sizes. Whereas, a bottom-up approach assemble small particles, such as constituent atoms, into a larger structure, as shown in Figure 1.4.

#### ■ Top-down methods

Usually, the top-down approach involves the lithography and etching processes to fabricate NWs with their integrated systems on the substrate. This method can obtain highly ordered NWs with precisely controlled dimensions and location. One of the big advantages is also compatible with well-developed complementary metal-oxide-semiconductor (CMOS) fabrication technology. Planarly and vertically etched NWs can be obtained using with line and dot patterns via top-down processing, respectively.

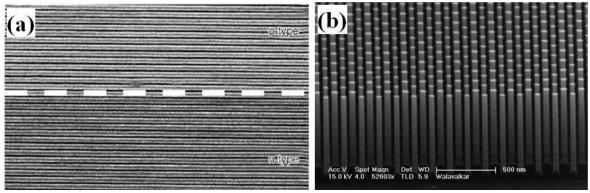

Figure 1.5 shows a planarly and a vertically etched high density of Si NWs arrays fabricated by top-down processing. Wang et al. [24] have fabricated high density of Si NWs array with top-down approach by pattering on silicon-on-insulator (SOI) substrates (34 nm Si <100> films on 250 nm oxide). The dimensions of Si NWs are 17 nm wide and 34 nm thickness with a pitch of 34 nm (Figure 1.5a). They also have modulated the doping levels of boron (p-type) and phosphorous (n-type) by optimizing the diffusion temperatures.

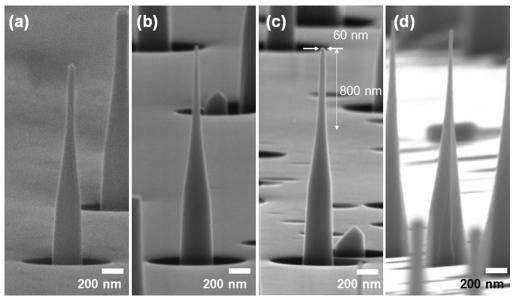

Henry et al. [25] have demonstrated vertically etched silicon nanopillars with the high-aspect-ratio using alumina dot mask patterns. Figure 1.5b shows the SEM images of alternating rows of 40 and 65 nm diameter Si naonopillars with a height of 780 nm.

Figure 1.5 (a) Planarly *etched Si NW's array with the* controlled doping profile (diameter = 17 nm, pitch distance = 34 nm) [24], (b) vertically etched Si NW's (diameter = 40, 65 nm, height = 780 nm) [25].

Although the top-down approach has been successful carried out for the fabrication of nanostructures, this approach has some drawbacks. This approach is complicated, time-consuming, and expensive. And it usually leads to additional roughness on the NWs sidewalls. In addition, it cannot produce nanomaterials with high throughput and the dimension of nanostructures has strongly limited by the resolution of lithography for the patterns.

#### Bottom-up methods

The bottom-up approach for the growth of nanostructures is more of an assembly process, which is analogous to the way that nature works. The nanostructures are built by stacking the core materials to the growth directions.

As devices approach atomic size, the bottom-up method may prove to be a suitable solution to the technological challenges, which allows smaller geometries than the limitation of lithography resolution. It also provides a convenient way to fabricate a broad range of single-crystalline nano-materials with cost-effective way. In addition, it is providing more flexibility in growing complex heterostructures, such as super lattice [26] and coaxial [8] types.

In spite of several advantages mentioned above, there are still major challenges in the fabrication of nanostructures by the bottom-up methods. For example, as-grown NWs possess the growth induced defects, such as twinning and SFs. Moreover, it is difficult to tailor the exact doping level of NWs. On the other hand, the metallic catalyst that could be used for the growth may diffuse from the tip and get incorporated into the NW as a contaminant and affect the electronic and optical properties of the NWs. In addition, this method may not fully control over the position and orientation of NWs. So, the assembling of NWs into hierarchical architectures are still major challenges for the realization of nanoscale components.

#### 1.3.2 Bottom-up growth mechanisms of nanowires

The growth is in general described by two mechanisms: vapor-liquid-solid (VLS) and vapor-solid (VS).

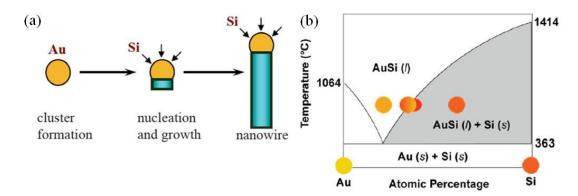

#### Vapor Liquid Solid method

The VLS mechanism discovered by Wagner and Ellis in 1964 [7] has proven to be extremely flexible and allows the controlled growth of complex nanostructures. A schematic of VLS mechanism is shown in Figure 1.6. VLS growth is promoted by the presence of a metallic particle droplet usually named as the catalyst to direct the 1D growth. So, VLS growth is often referred to as "catalyst assisted" growth. For Si NWs growth, gold is usually used as catalyst because Au and Si forms an eutectic at a very low temperature The eutectic temperature is at 363 °C in Figure 1.6(b). The catalyst forms a liquid alloy with the supplied vapor species of

the materials to be synthesized. When the liquid alloy is supersaturated, nucleation occurs, and the axial growth proceeds by precipitation at the liquid alloy/solid interface.

The diameter of NWs could be successfully controlled by tailoring the catalyst particle size due to the lateral growth confinement. In addition, VLS growth is providing more flexibility in growing complex heterostructures by modulating the supplied vapor species of the materials.

Figure 1.6 (a) Schematic of VLS growth of Si NWs,

(b) binary phase diagram for Au and Si illustrating the thermodynamics of VLS growth [27].

The presence of a metal particle at the tip of the NWs is generally considered as an evidence of the VLS growth. However, in some cases the metal particle may also be consumed during the growth or detached due to interfacial dewetting and thermal strain during the cooling process.

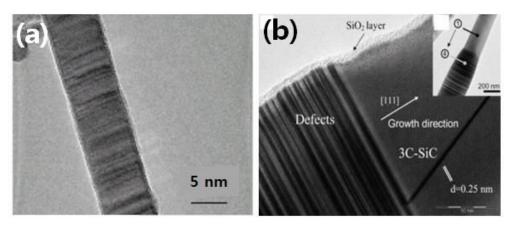

Many efforts have been done to fabricate the SiC NWs via VLS route using various catalysts; NiSi, Fe-Si, Co-Si, Fe and Ni [28, 29]. Typical SiC NWs synthesized by VLS methods show a high density of SFs along the NW (see for examples Figure 1.7a).

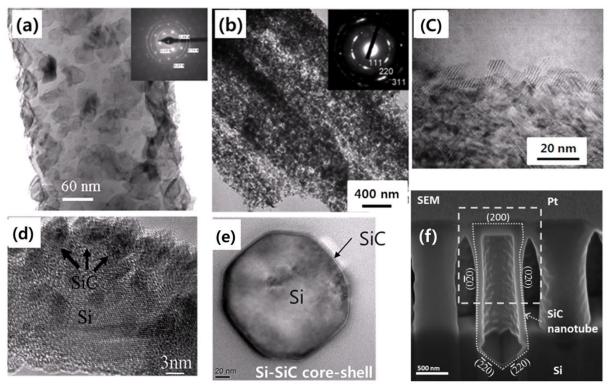

Figure 1.7 TEM images of SiC NWs synthesized by (a) VLS [29] and (b) VS [8], respectively.

#### Vapor Solid method

VS growth is a spontaneous condensation process of vapor into solid material induced by the decrease in Gibbs free energy from crystallization or the decrease in supersaturation [8]. VS growth is often referred to as "catalyst free" growth. Specifically, the growth mechanism has been associated with the radial thickening and tapering of NWs, due to direct adsorption of gas to the crystallized NWs. Considerable efforts have been done to fabricate SiC NWs by VS methods [8], but SFs are again present (Figure 1.6b).

#### 1.3.3 Fabrication of SiC nanowires

SiC nanostructures, in particular NWs, could be fabricated by the bottom-up and the top-down methods. Common technique for fabrication of SiC NWs is the bottom-up approach. Many efforts have been made to fabricate SiC NWs with controlled diameters and crystallinity by bottom-up approach. The big majority of SiC NWs studies deal with 3C-SiC NWs. This is due to the fact the cubic polytype is the most stable polytype at low temperature [11]. So, when SiC NWs are mentioned in this thesis, it'll mean 3C-SiC NWs. Otherwise, the specific polytypes of NWs will be mentioned. In this section, I'll review the literature on synthetic diversity techniques to fabricate the SiC NWs by the bottom-up methods. SiC NWs also can be prepared by conversion methods, which is exposing carbon and silicon precursor on Si NWs and CNTs, respectively. I'll also mention the recent progress of conversion methods for the fabrication of SiC NWs.

#### Top-down approach

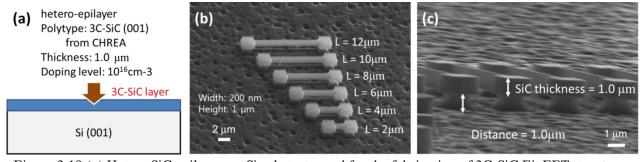

Feng et al. [30] have fabricated the SiC nanostructures with a diameter of 55 nm by etching heteroepitaxially grown 3C-SiC layers (thickness ~ 55 nm) on Si substrate. Fabricated SiC nanostructure is suitable to nanoelectromechanical system (NEMS) devices, but it is not suitable for the electrical device due to the low crystalline quality.

#### ■ Bottom-up approach

Considerable efforts have been made to fabricate SiC NWs by bottom-up approach. To date, many techniques have been developed to synthesize SiC NWs, as listed in Table 1.3

| Growth technique                               | Ref.          | Growth technique            | Ref.          |

|------------------------------------------------|---------------|-----------------------------|---------------|

| Thermal evaporation (carbon thermal reduction) | [31, 32]      | Laser ablation              | [ <u>33</u> ] |

| Arc discharge                                  | [ <u>34</u> ] | Polymer pyrolysis route     | [ <u>35</u> ] |

| Chemical vapor deposition                      | [28]          | Combustion process          | [ <u>36</u> ] |

| Microwave heating-assisted methods             | [37]          | Template-directed synthesis | [38]          |

Table 1.3 Bottom up growth methods of SiC NWs.

The vapor based techniques employed to synthesize SiC nanostructures could be categorized according to the route to generate the vapor species, such as thermal evaporation, laser ablation, polymer pyrolysis, arc discharge, combustion process, microwave methods and chemical vapor deposition.

#### Thermal evaporation (Carbon thermal reduction)

The thermal evaporation (also called carbothermal reduction) is widely employed in nanofabrication processes due to its simplicity, high yield and low cost. The technique uses powder or condensed source materials that are vaporized at an elevated temperature. The vapor phase is transported onto a substrate, and consequently produces the SiC NWs by following the VLS or VS mechanism [31, 32].

#### Laser ablation

Laser ablation is the process of vaporizing material from a solid target (such as SiC) containing the desired

elements to fabricate 1D nanostructures by irradiating it with a laser beam. The clusters of vaporized material are collected by a cold finger inside a chamber with a controllable environment. The SiC nanostructures are formed on the cold finger [33].

#### Arc discharge

Direct current arc discharge is an effective growth method for nanomaterials, which has been commonly used to synthesize carbon nanotubes (CNTs). High temperatures (3000 - 4000 K) instantaneously produced by arc plasma result in enhancement in the synthesis efficiency of nanomaterials. In a typical experiment for the growth of SiC nanostructures, the anode is a sintered graphite crucible with a hole, in which SiC powder was filled, and a pure graphite rod was used as the cathode [34]. When voltage is applied between the electrodes, an arc discharge occurs, which allows the SiC clusters in the anode to instantly evaporate. The clusters of vaporized material precipitate into SiC nanostructure on the cathode or wall of the chamber.

#### Polymer pyrolysis route

For polymer pyrolysis method, a slurry solution is prepared by introducing the activated carbon powder and catalyst into polymer (such as, 1-PS) [35]. The activated carbon acts as an absorbant to postpone the evaporation during the pyrolysis. A slurry solution or a ground fine powder is loaded in a conventional furnace and begin to pyrolyze at 1300 - 1450 °C. The silane fragments derived from decomposition of the polymer precursor provided both the Si and C sources for the growth of the SiC NWs.

#### Chemical vapor deposition

Chemical vapor deposition (CVD) method directly introduces the gas-phase sources (for Si: SiH<sub>4</sub>, SiCl<sub>4</sub>, Si(CH<sub>3</sub>)Cl and for C: CH<sub>3</sub>SiCl<sub>3</sub>,CH<sub>4</sub>, C<sub>3</sub>H<sub>8</sub>) into the reaction chamber [28]. Three different methods have been used by this group to synthesize SiC NWs using a thin Ni film deposited on Si substrate.

In the first one, 3C-SiC NW is grown on a Ni film (4 nm) deposited on the Si substrate in a Vapor Phase Epitaxy (VPE) reactor with silane (SiH<sub>4</sub>) and propane ( $C_3H_8$ ) as precursors. The synthesized NW are predominantly 3C polytype with <111> growth axis, and planar defects are characterized such as SFs lied on {111} planes, these SFs are oriented perpendicular to the growth axis.

In the second case, 3C-SiC NWs are also synthesized in a heated quartz tube using carbon tetrachloride (CCl<sub>4</sub>) as precursor. The carbon tetrachloride (CCl<sub>4</sub>) is decomposed at high temperature and formed silicon chlorides by reacting with Si substrate. Consequently, the reaction between silicon chlorides and carbon atoms produce 1D 3C-SiC NWs. As-grown SiC NWs are less than 80 nm in diameter and several tens of microns long.

Last, 3C-SiC/SiO<sub>2</sub> core/shell NWs can be obtained on the Ni-covered Si substrate (Si source) in an opentube configuration by flowing carbon oxide (carbon source). Carbon oxide served as carbon source for the growth of SiC core structures by reacting with Si species, and it also reacts with SiC core and consequently forms thin SiO<sub>2</sub> sheath on SiC NWs.

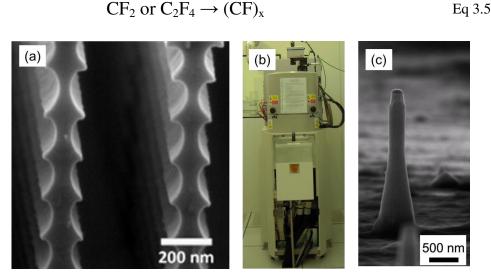

#### Combustion process

The initiation of the combustion (strong exothermic reaction) results in the fast temperature increase in the reactor, hence the pyrolysis of reactants (poly-tetrafluoroethylene - PTFE) are started. These gaseous species (Si-containing compounds and halocarbons (e. g.  $C_2F_4$ )) will be formed in the combustion zone [36]. When they move from the central reaction zone toward the colder area (low temperature zone), the freshly formed carbon atoms assemble either into hexagonal carbon clusters (which may grow into soot particles) and reacts

with Si-containing compounds, and consequently it forms SiC compounds. During this rapid SiC nucleation phase, Si and C atoms pack along its close-packed plane. Finally, it leads to the nucleation and growth of 1D SiC structures, generally with abundant SFs and of a low crystalline quality.

#### Microwave heating-assisted methods

Microwave heating is a relatively new technique for large-scale NW processing [37], which is different from existing conventional process. Microwave heating-assisted methods will only heat the target compounds (SiC) without heating the entire furnace. Therefore, this method provides a simple but effective synthesis of SiC NWs using inexpensive resources.

#### Template-directed synthesis

Template-directed method provides a straightforward route to fabricate 1D nanostructures. Channels in porous membranes, such as anodic aluminum oxide (AAO), provide a class of templates for use in the synthesis of 1D nanostructure. Different materials can be generated in situ and shaped into a nanostructure with its morphology complementary to that of the template. Template-directed synthesis provides a high-throughput, simple and cost-effective procedure. Li et al. [38] have demonstrated a large-area highly oriented SiC NW arrays in the nanopores of an AAO template via a series of chemical reactions of Si, SiO<sub>2</sub>, and C<sub>3</sub>H<sub>6</sub>.

In summary, we reviewed the literature on techniques to fabricate the SiC NWs by bottom-up methods. Among the various synthesis methods, CVD and thermal evaporation are widely used for the VLS and the VS mechanism of SiC NW, respectively, because those methods can easily control the amount of reaction species and the reaction temperature. Even though considerable efforts have been made to fabricate the SiC NWs by the bottom-up methods, as-grown SiC NWs still suffered from high density of SFs with unintentional doping.

#### Conversion methods

As it has been mentioned in the previous section, conventional SiC NWs fabricated by bottom-up methods have shown very high structural defects density with a high level of n-type unintentional doping. To minimize these kinds of problems, some research groups have tried to synthesize the SiC nanostructures by exposing carbon or silicon precursor on Si NWs or CNTs, respectively. A number of works have been carried out in order to control the diameter, length and morphology of Si NWs and CNTs with various growth methods. Therefore, well defined SiC NWs might be obtained with conversion methods by using high quality and controlled 1D material (Si NWs and CNTs).

#### Carbonization of Si nanowires

Zhang et al. [39] have first reported the exposing of carbon-containing precursor on Si NWs in 2000. After the carbonization process, they got a crystalline Si core with a sheath of MWCNT due to the fast carbon deposition. Tsakalakos et al. [40] have demonstrated in situ carburization process by flowing methane and hydrogen right after catalyst-assisted Si NWs growth. After carburization process, it shows partially carburized NWs contained distinct polycrystalline SiC nanosized grains on the Si NWs surface (Figure 1.8(a)). Even though thermodynamically the carbonization of Si wafers is favorable over a wide temperature range (from 500 up to 1360 °C), there exists a significant kinetic barrier to Si NWs carburization below ~1100 °C according to their experimental results.

Yang and coworkers [41] have achieved highly oriented SiC porous NW arrays on Si substrate via in situ carbonizing aligned Si NW porous NW arrays, which are fabricated by chemical etching methods. During the

carbonization process, the porous Si NWs react with active carbon species decomposed from  $C_2H_5OH$  to form porous SiC, as shown in Figure 1.8(b). Thanks to the porous structure of Si NWs, carbon species can easily diffuse into the whole region of Si NWs without the limitation of carbon's diffusion length in Si. Consequently, the original Si NWs were completely converted into SiC porous NWs.

Xing et al. [42] and Zhou et al. [43] have demonstrated the incorporation of carbon element into Si NWs by the implantation and ion beam deposition, respectively. These small protrusions on Si NWs induced by ion implantation and deposition are confirmed to be β-SiC precipitates by TEM, shown Figure 1.8(c) and (d).

Figure 1.8 (a-b) TEM images and corresponding SAD patterns (inset) after the carbonization of Si NWs, (a) SiC nanosized grains on Si NW [40], (b) SiC porous NWs [41], SiC nanosized grains on Si NW fabricated by (c) carbon implantation [42] and (e) ion beam deposition [43], (e) TEM image of a Si-SiC core-shell NW [44] and (f) SiC NTs [45].

Latu-Romain et al. have reported the carbonization of Si NWs at 1100 °C under methane to form 1D SiC nanostructures [44, 45]. Experimental results have shown that Si NWs can be transformed either in Si-SiC core-shell NWs [44] or in SiC NTs [45]. In the first case, the SiC shell is continuous and single crystalline (as well as the Si core); the thickness of the SiC shell is about 2 to 4 nm (Figure 1.8(e)). In the second case, 3C-SiC-NTs with faceted {200} sidewall planes are obtained with an excellent crystalline quality (Figure 1.8(f)). The external diameter of the SiC-NT is about 300 nm (nearly the same than the etched Si-NWs used) and the thickness of the sidewalls is about 40 to 100 nm. By controlling the pressure during the carburization process, out-diffusion of Si through the SiC layer can be monitored and could lead either to Si-SiC core shell NWs or to SiC-NTs.

#### Carbon nanotube-mediated growth

Since the discovery of CNTs in 1991 [5], this 1D nanostructure material becomes very attractive because of its unique mechanical, optical, electronic properties. CNT has also been used as a template (base material) for the fabrication of other 1D nanomaterials such as SiC, TiC, NbC, TaC, BN, and GaN, etc. CNTs are suitable

starting materials as precursors for reactant and provide the frame for preparation of new type or heterostructures of 1D nanomaterials. Because, it can be easily converted into a 1D heterostructures nanomaterials by filling the inside of CNTs or coating the outside surfaces of CNTs with other elements. It also can be transformed into various metal carbide nanomaterials or new type of nanotubes by spatially confined reaction or substitution reaction, which replace the carbon element of CNTs with other atoms.

Dai et al. [46] first reported SiC nanorods through a reaction between CNTs and SiO or  $SiI_2$  at high temperature (1100 – 1450 °C). Li et al. [47] have revealed the transition process from the CNTs into SiC NW via a systematic time-dependent TEM analysis. They have also investigated the chemical reaction on different morphology of CNTs (bamboo shape) [47]. The terminations of graphitic layers in the bamboo-like CNTs provide more active sites for the chemical reactions. The segmented bamboo-like structure of the CNTs causes the reaction to start on the external surface of the tubes and progressively transform the CNTs into solid NW segment by segment.

In conclusion, CNT-mediated growth for SiC NWs have successfully demonstrated via various reactions, such as filling, coating, confined reaction and substituted reaction. Even though the SiC NWs synthesized by CNT-mediated growth still possess high density of SFs along the growth direction, it is versatile way to produce a large quantity of SiC NWs with low-cost production.

#### Several points for the growth of SiC nanowires

#### Crystal orientation growth

SiC NWs have been grown on various substrates, such as Si, SiO<sub>2</sub>, graphite, poly-SiC, 4H-SiC [48] and 6H-SiC [49]. NWs generally grow in the crystal direction with minimum the total free energy. Fabricated SiC NW are 3C-SiC NWs in the most cases grown along <111> direction with SFs {111} planes due to low growth temperature. The use of monocrystalline SiC substrates with a specific orientation may offer possible controllability of hexagonal polytypes SiC NWs during the growth [48] (see discussion below). The growth habits of SiC NWs are strongly affected by the SiC substrate orientations. It has been found that 6H-SiC NWs can grow along the  $[\bar{1}102]$  direction. The polytype-controlled SiC NWs have great potential to become building blocks for electronic nanodevices, optoelectronic nanodevices with tailored electrical and optical properties.

#### Growth of 6H-SiC nanowires

The polytype control is a big issue for the growth of SiC NWs as well as SiC bulk substrate, because the various polytypes with different physical properties can provide more versatile applications of SiC NWs. Several methods have been proposed for the fabrication of 6H-SiC NWs, such as arc-discharge process [50], polymer pyrolysis route [35] and microwave methods [51].

Li et al. [50] have first reported the synthesis of cone-shaped 6H–SiC nanorods by an arc-discharge process. The 6H-SiC nanorods have the same preferential growth  $<10\overline{1}0>$  direction. They have proposed that the high enthalpy of the droplets and the Al doping in the NWs favor the formation of hexagonal 6H–SiC NWs rather than the stable cubic 3C–SiC phase. Gao et al. [35] have reported Al-doped single-crystalline 6H-SiC NWs by the catalyst-assisted pyrolysis of polymeric precursors with FeCl<sub>2</sub> as the catalyst. The 6H-SiC lattice constant decreases with increasing the Al content, which indicate that Al-doped SiC NWs formed by the substitutional solid solutions. Wei et al. [51] have synthesized by microwave method with the presence of nano-Al powders. It is interesting to find that they could not have obtained 6H–SiC NWs without the use of nano-Al powders. It seems that Al powders play a crucial role in forming 6H-SiC NWs. Wang et al. [49] have first demonstrated preferred orientation of 6H-SiC NWs on 6H-SiC substrate. 6H-SiC NWs grew in  $<10\overline{1}0>$  direction (or its equivalent ones). SiC NWs grown on (0001) plane show six growth directions with same orientation ( $\overline{1}102$ ).

#### Various morphologies of SiC nanowires

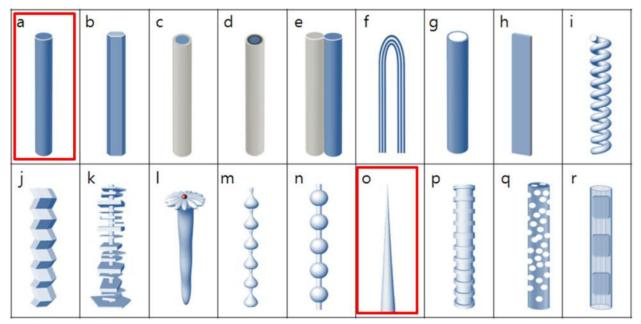

Synthesized 1D SiC structures show various morphologies in the literature. Its range includes core-shell, nanotubes, hollow, helical, flower, neck-lace, needle, bamboo and porous morphologies, as shown in Figure 1.9.

Figure 1.9 Schematic summary of various morphologies of SiC nanostructure reported in the bibliography.

(a) cylinder [28], (b) hexagonal [52],(c) core-shell [8], (d) core/multi-shell [53], (e) bi-axial [54], (f) nanotubes [55], (g) hollow [45], (h) nanobelt [56], (i) helical [57], (j) twin [58], (k) hierarchical nanoarchitectures [59], (l) flower [60], (m) beaded nanochains [61], (n) neck-lace [62], (o) needle [63], (p) bamboo [52], (q) porous [41], (r) CNT-encapsulated SiC nanocrystals [64].

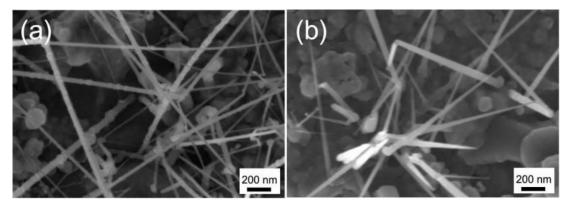

In the present thesis, SiC NWs with the morphologies of (a) cylinder and (o) needle have been investigated.

The growth kinetics and thermodynamics of 1D SiC nanostructures are complex, the morphologies of assynthesized SiC nanostructures will be significantly different even with a minor difference on the synthesis conditions. It is known that the properties of NWs, such as optical, electrical and mechanical properties, may sensitively depend on their geometrical shape. Therefore, full control of morphologies, composition and dimensions of SiC nanostructure has been a dominant theme in materials science

For example, core-shell structure might be suitable for building blocks of nanoelectronics device, since the electron density is confined to the core and the shell serves as a potential barrier. And the SiC nanotube has theoretically proven well suited to hydrogen storage. Unique morphology of SiC beaded nanochains has exhibited an excellent reinforcing property when used as filler in composite [61]. Needle, bamboo and porous SiC nanostructures have been proven to increase the field emission efficiency by enhancing the field enhancement factor.

In our study, two types of SiC NWs (cylinder and needle shapes - (Figure 1.9(a) and (o), respectively) are used for the fabrication of SiC nanodevices in chapter 4. In case of the needle-shaped SiC NW growth, the Ni catalyst is gradually evaporated or diffused into NW during the reaction, therefore the size of the nanosize metallic droplet as catalyst will decrease. Consequently, it results in a sharp end of the needle-shaped SiC NWs. The apex of a needle SiC NW could be down below 10 nm [63].

#### Doping of SiC nanowires

Doping is obviously used to tailor the electronic properties of SiC, and is one of the main reasons for the usefulness of semiconductors in electronics. It is therefore necessary to investigate how impurities incorporate into NWs. For bulk SiC and SiC thin films, doping can be realized by vapor phase co-deposition [65] and ion-implantation [66]. Ion implantation method can control the lateral control of dopant incorporation. However, doping processes of nanostructures may show completely different behaviors from that obtained in the bulk phase. For instance, several nanocrystals exhibit a lower incorporation rate of impurities than their bulk counterpart. In this case, the impurity elements are ejected from the inner sites of the nanocrystal, lying at the nanocrystal surface, there is a "self-purification" process.

Generally, SiC NWs grown by many growth technique show unintentional n-type doping (~  $10^{19}$  -  $10^{20}$  cm<sup>-3</sup>) along the NWs [29]. Among the doping methods, diffusion methods are not suitable for SiC NWs, because the diffusivities of dopants in SiC are very low due to the chemical inertness and densely packed atomic structure of SiC, and high temperatures above 1800 °C are needed for the incorporation of dopants into the SiC. However, this process might promote the graphitization of SiC NWs by Si sublimation and probably induce the SiC/CNT heterostructures.

A feasible method for the doping of SiC NWs is in situ doping during the growth by exposing the doping precursor. In most cases, as-grown SiC NWs are unintentional n-type doped  $(10^{18} - 10^{19} \text{ cm}^{-3})$  during the growth. The best value of effective carrier mobility measured on n-type SiC NWFET is 15 cm<sup>2</sup>·V<sup>-1</sup>s<sup>-1</sup> [29]. P-type doping is also investigated for modulating the electrical property of SiC NWs [67, 68]. Al doped 3C-SiC NWs have demonstrated as an outstanding building blocks for the field emitter [67] and nano Field Effect Transistor (FET) [68]. Chen and Zhang et al. [68] have reported for the first time the fabrication of p-type 3C-SiC NW FET, it exhibits a hole carrier concentration of ~  $1.7 \times 10^{17}$  cm<sup>-3</sup> and a low mobility of 6.4 cm<sup>2</sup>·V<sup>-1</sup>s<sup>-1</sup>. They also considerably improve the field emission properties of 3C-SiC NW by reducing the work function via in situ Al doping [67].

Besides the doping for modulating the electrical property, Seong et al. [69] have also demonstrated the doping of transition metal (V) in 3C-SiC NWs and characterized its magnetic semiconductor behavior at very low temperature.

## 1.4 Properties of SiC nanowires

In this section, I'll introduce the electrical, mechanical and thermal properties of SiC NWs. Our experimental results of the electrical properties of SiC NW FET will be discussed in chapter 4.

#### 1.4.1 Mechanical properties of SiC nanowires

The mechanical properties of nanostructures have aroused considerable interest due to possible stronger property than their bulk counterparts. This might be attributed to a reduction in the number of defects per unit length (compared with larger structures), which leads to mechanical failure.

For the practical applications of SiC NWs, it is important not only to understand its mechanical properties, such as toughness and hardness, but also to investigate mechanical response, such as elastic-plastic response and brittle-ductile transition, in the nano-domain [70]. Researchers have investigated the mechanical properties of various nanowire systems with different approaches, such as nano-indentation [71], atomic force microscopy (AFM) [72] and mechanical resonance by in situ TEM [54].

#### Mechanical properties of SiC nanowires

Two main approaches have been developed to characterize the mechanical properties of various NWs. The first one has measured the strength of SiC nanorods with AFM by physical bending of the SiC nanostructure, which was pinned at one end to molybdenum disulfide surfaces [72]. The bending force was measured versus displacement along free-end lengths. The measured bending strength and Young's modulus of SiC nanostructures were 53.4 and 660 GPa, respectively. Young's modulus of SiC nanostructure shows were substantially greater than those found previously for any type SiC structures (SiC whiskers and fibers), and they approaches theoretically predicted value (600 GPa) for [111] oriented bulk SiC [72].

The second method used electric-field-induced resonance for measuring the mechanical properties by the field emission microscopy (FEM) [73] and in situ TEM [54]. One end of the NW is pinned on the tip, and an oscillating voltage is applied across the ball and its counter electrode. Mechanical resonance occurs when the applied frequency matches the natural resonance frequency of NWs. Wang et al. [54] have measured the mechanical property of biaxial SiC-SiO<sub>x</sub> NWs by in situ TEM. They have proved that the effective Young's modulus (E<sub>eff</sub>) of biaxial structured SiC-SiO<sub>x</sub> NWs is the combination from SiC and SiO<sub>x</sub>. The Young's modulus determined by FEM yielded a high Young's modulus value (Y =750 GPa) [73], which is corresponding to the highest value reported in the literature for a bulk single crystal of 748 GPa.

#### Mechanical behavior of SiC nanowires

Han et al. [74] have directly observed the mechanical behavior of SiC NWs in situ TEM measurement by bending individual NWs. Instead of a crystalline fracture (or any cracks) under deformation, the SiC NW has transformed from crystalline to amorphous at the mostly strained region. Large strain plasticity of SiC NWs at temperatures close to room temperature has been observed for the first time in this study. From their experimental results, the plastic deformation process of SiC NWs is typically regarded as three stages, dislocation initiation, dislocation propagation and amorphization. Zhang et al. [70] have investigated the plastic deformation and fracture behavior of individual SiC NWs by in situ stretching equipment in a SEM. The plastically deformed region shows identical size and morphology without any necking appearance, indicating a super-plastic deformation.

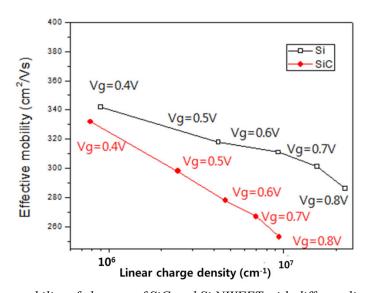

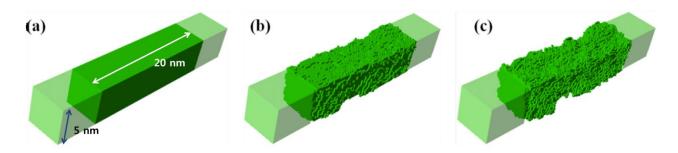

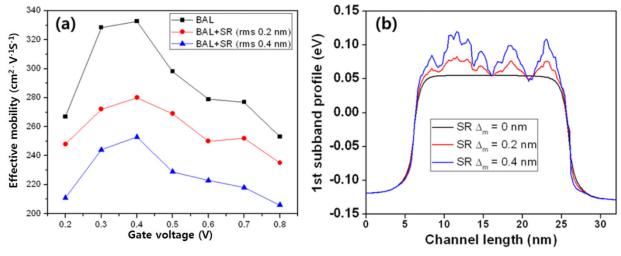

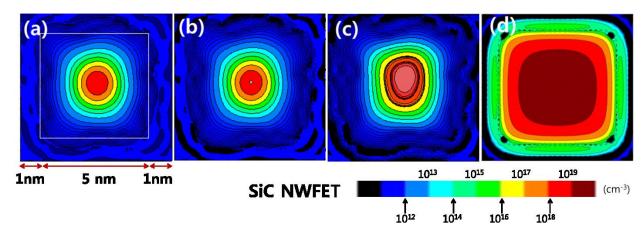

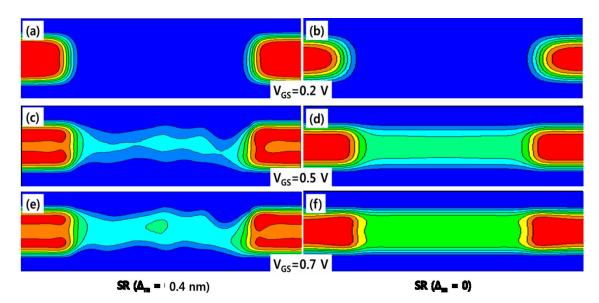

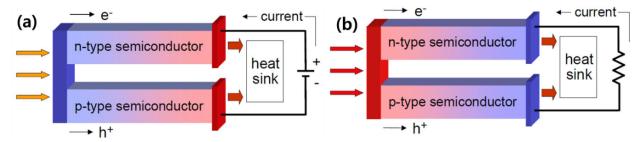

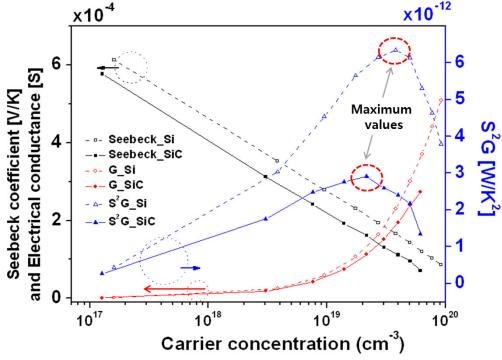

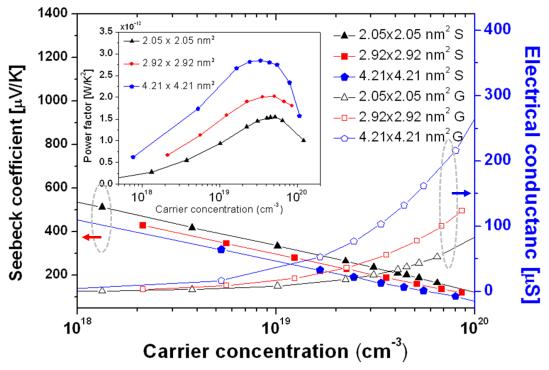

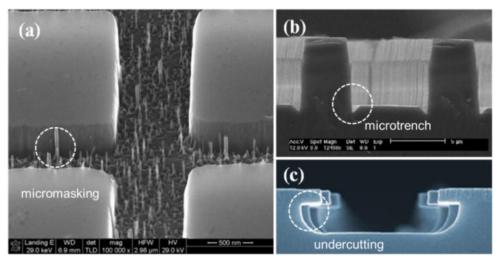

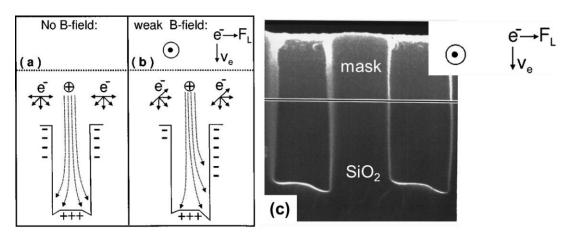

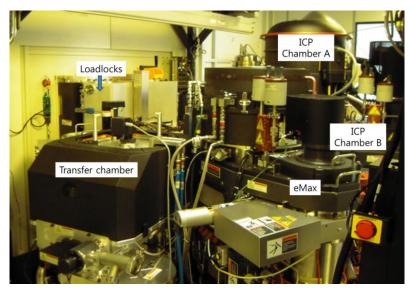

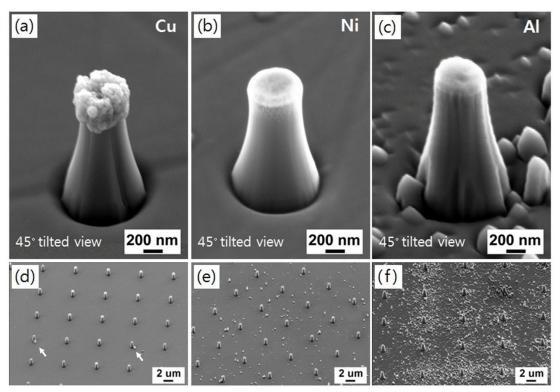

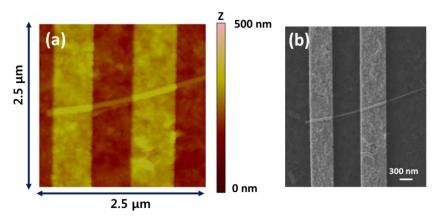

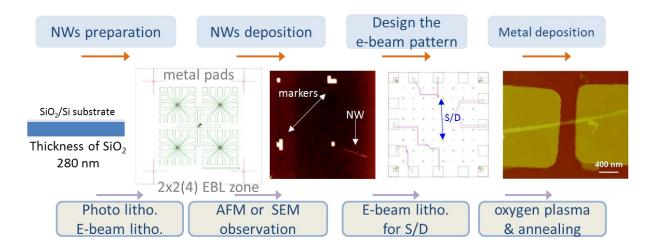

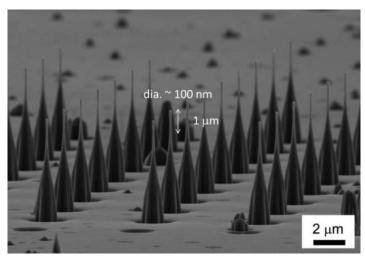

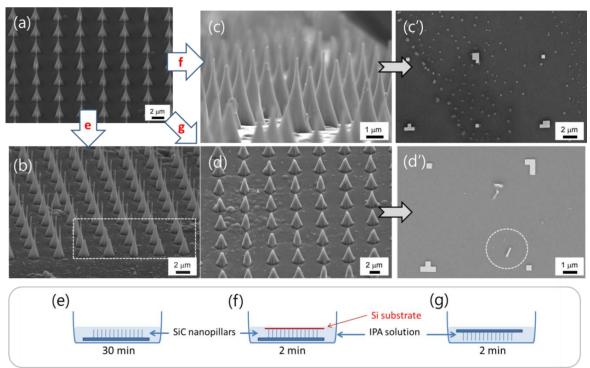

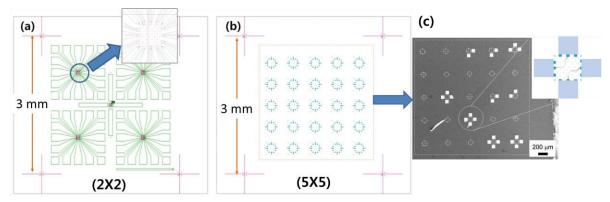

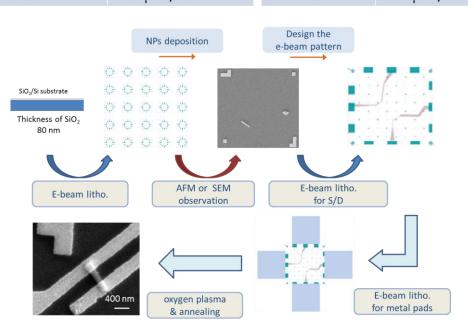

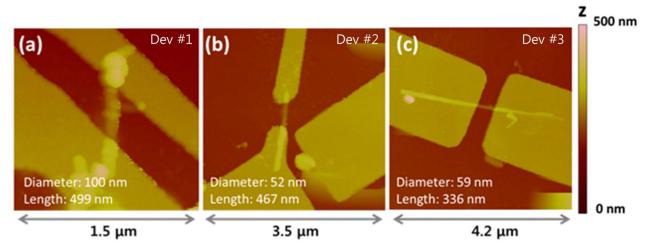

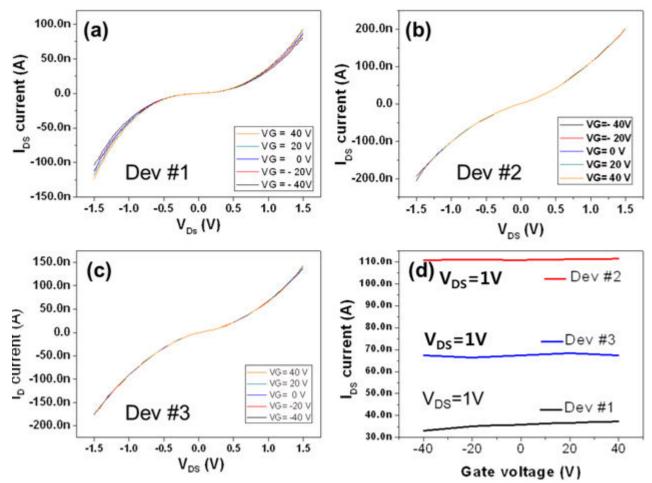

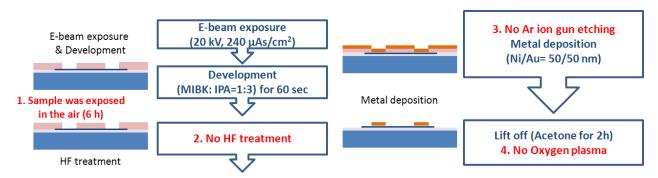

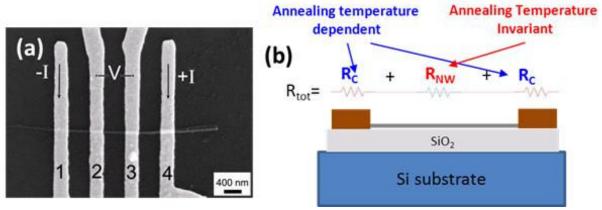

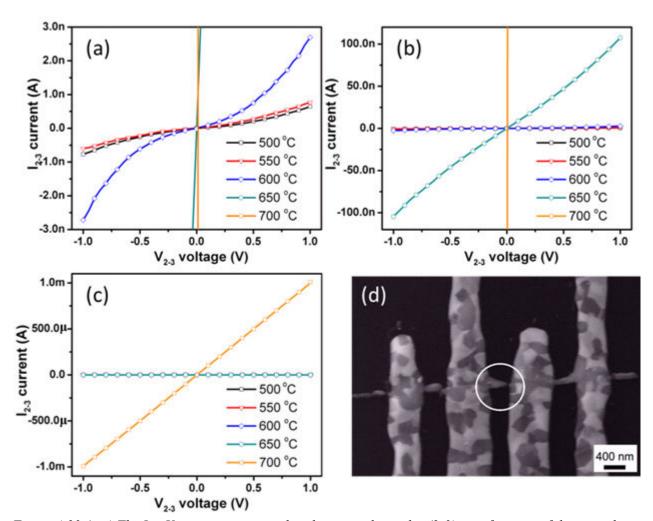

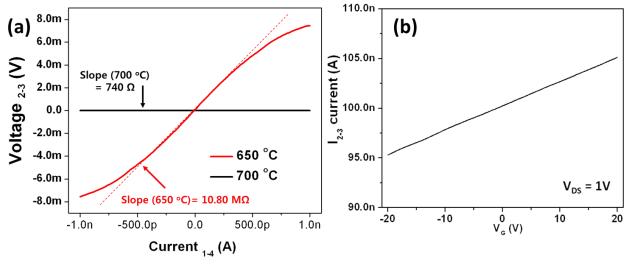

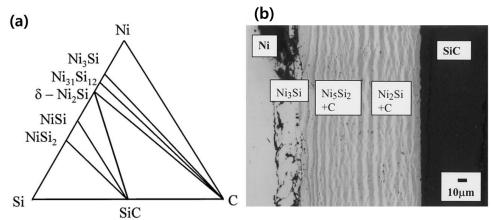

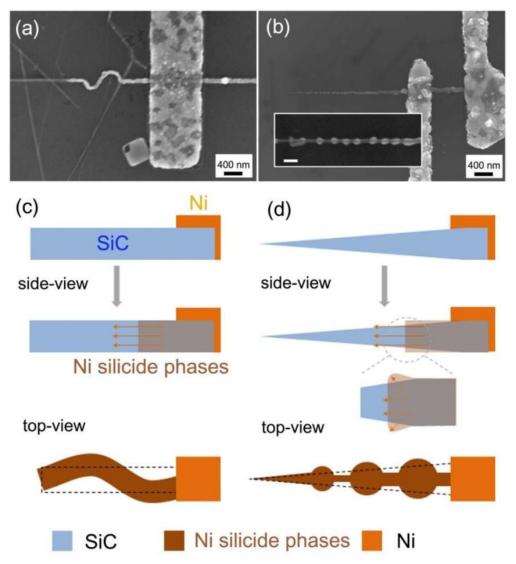

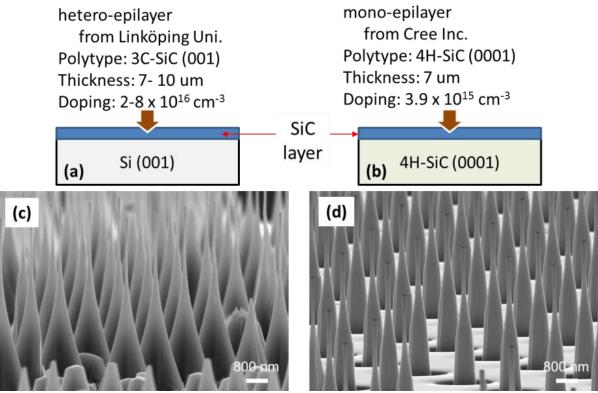

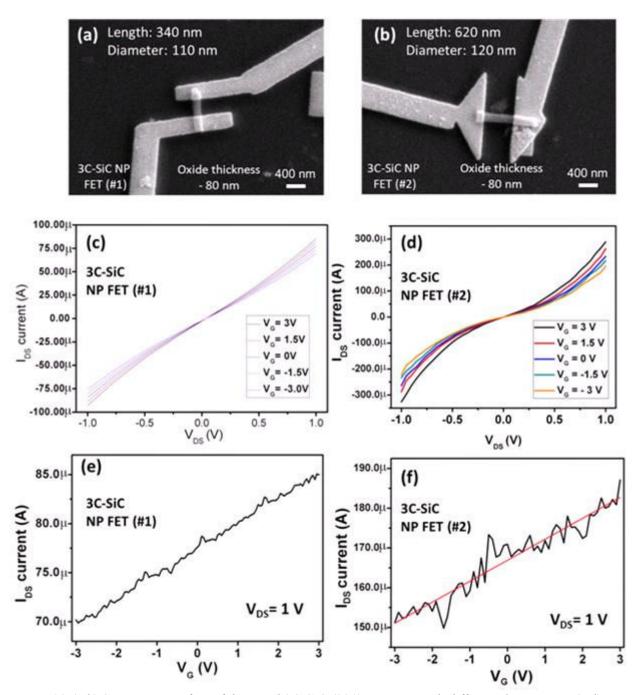

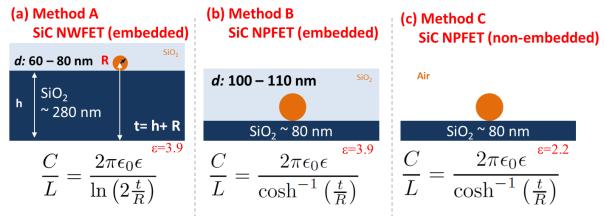

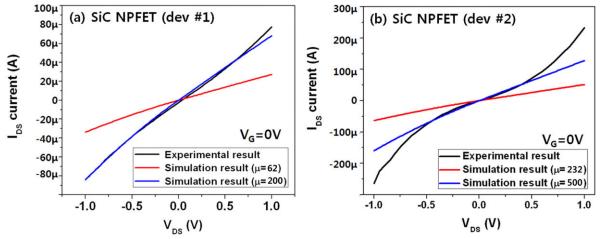

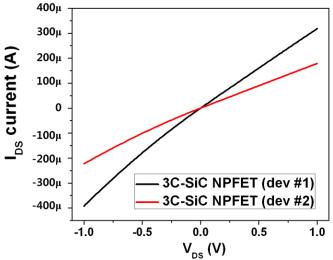

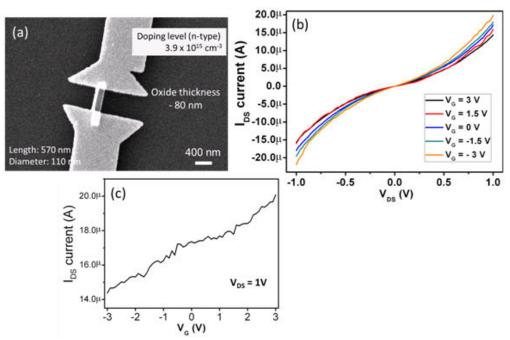

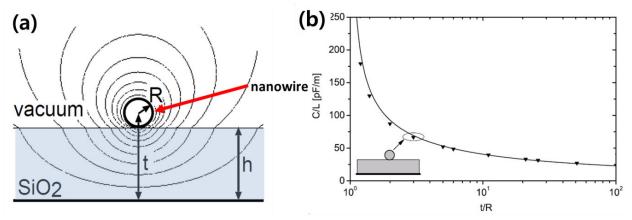

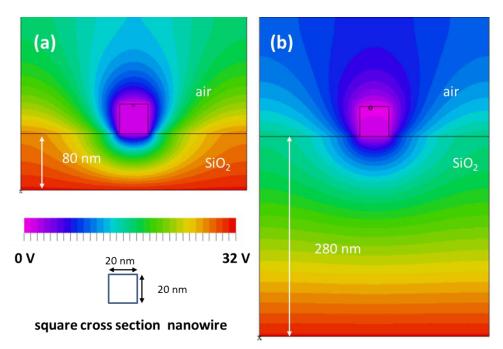

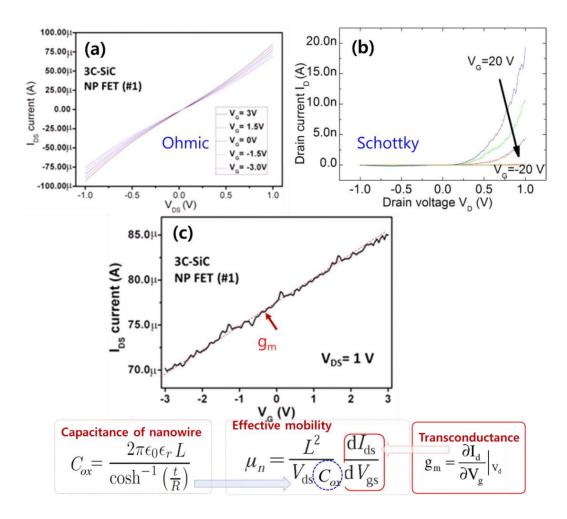

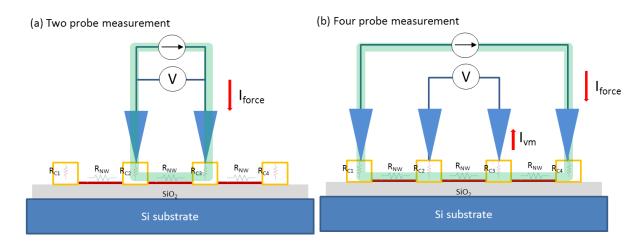

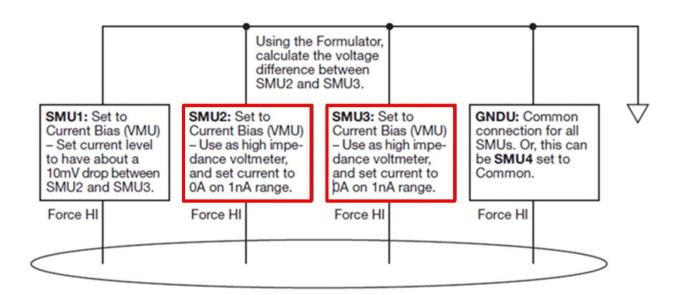

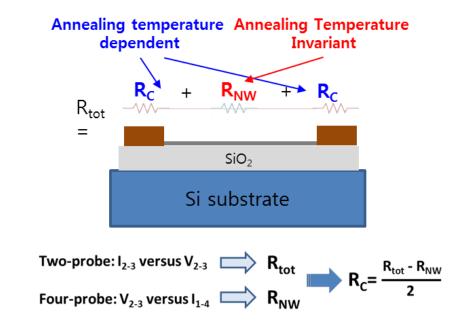

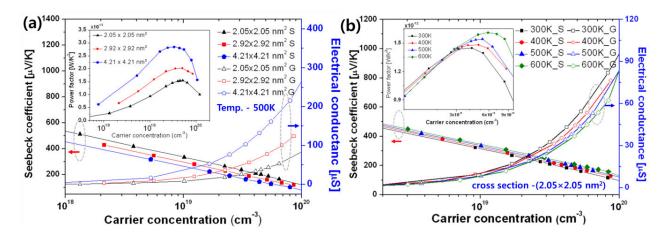

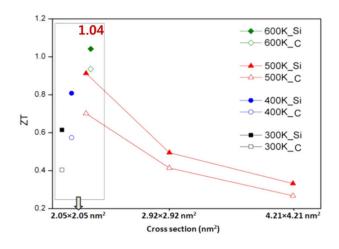

In conclusion, SiC NWs show excellent mechanical property, such as Young's modulus (660 GPa), comparable or better performance than similar size CNTs. The mechanical properties of SiC NWs have been measured by the bending of NWs with AFM tip and mechanical resonance by in situ (SEM and TEM).