## Reliability analysis of embedded Phase-Change Memories based on innovative materials

Gabriele Navarro

#### ▶ To cite this version:

Gabriele Navarro. Reliability analysis of embedded Phase-Change Memories based on innovative materials. Other. Université de Grenoble, 2013. English. NNT: 2013GRENT084. tel-01061792

## HAL Id: tel-01061792 https://theses.hal.science/tel-01061792

Submitted on 8 Sep 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITÉ DE GRENOBLE

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Nano Électroniques et Nano Technologies

Arrêté ministériel: 7 août 2006

Présentée par

#### Gabriele NAVARRO

Thèse dirigée par **Gérard GHIBAUDO** et co-encadrée par **Véronique SOUSA**

préparée au sein du CEA-LETI dans l'École Doctorale Electronique, Electrotechnique, Automatique et Traitement du Signal

## Reliability Analysis of Embedded Phase-Change Memories Based on Innovative Materials

Thèse soutenue publiquement le **16 Décembre 2013** devant le jury composé de :

#### Monsieur, Yves BRÉCHET

Prof., PR SIMAP/INP Grenoble,

Haut-Commissaire à l'Energie Atomique (France) (Président)

**Monsieur, Matthias WUTTIG**

Prof., RWTH Aachen University of Technology (Allemagne) (Rapporteur)

Monsieur, Daniele IELMINI

Prof., Politecnico di Milano (Italie) (Rapporteur)

Madame, Paola ZULIANI

Ing., STMicroelectronics Agrate (Italie) (Examinatrice)

Madame, Véronique SOUSA

Ing., CEA LETI Grenoble (France) (Co-encadrante)

Monsieur, Gérard GHIBAUDO

Prof., DR CNRS, IMEP/INP Grenoble (France) (Directeur de thèse)

## Acknowledgments

I would like to thank my supervisor, Véronique Sousa, for these three years of thoughtful, patient guidance and support and for our weekly "long" scientific discussions on Wednesday mornings at 10. Her expertise and selfless contribution to my professional development have been invaluable and will forever be part of my personal and professional life. A particular thanks also to my PhD director Gérard Ghibaudo, and to the members of my committee.

I would also like to extend my gratitude to Barbara De Salvo, for giving me the opportunity to join her laboratory, for motivating me and driving to improve myself, and to Luca Perniola for his friendship, his confidence in me and his valuable advices since the beginning of my PhD.

I wish to express my gratefulness to all the people from the Memory Laboratory (old LTMA, new LCM) and from CEA Leti that collaborated with me and helped me to realize this work. I want to thank as well the people from STMicroelectronics for their precious collaboration.

I want to thank from the bottom of my heart Erica, my family and all the friends that encouraged me and supported me during these years.

Gabriele Navarro

# Contents

| A             | cknov | ledgments                                                                                                 | 1   |

|---------------|-------|-----------------------------------------------------------------------------------------------------------|-----|

| C             | onten | s                                                                                                         | III |

| $\mathbf{A}$  | bstra | ${f t}$                                                                                                   | VII |

| $\mathbf{Li}$ | st of | Symbols                                                                                                   | XI  |

| In            | trodu | ction                                                                                                     | 1   |

| 1             | The   | Phase-Change Memory Technology                                                                            | 5   |

|               | 1.1   | Brief history of PCM technology                                                                           | 6   |

|               | 1.2   | The PCM cell                                                                                              | 7   |

|               | 1.3   | PCM applications and challenges                                                                           | 10  |

|               |       | 1.3.1 The multi-level PRAM cell                                                                           | 11  |

|               |       | 1.3.2 Automotive applications                                                                             | 11  |

|               | 1.4   | The phase-change materials                                                                                | 12  |

|               |       | 1.4.1 GeTe                                                                                                | 12  |

|               |       | $1.4.2  Ge_2Sb_2Te_5 \dots \dots$ | 13  |

|               | 1.5   | Crystallization kinetics                                                                                  | 15  |

|               |       | 1.5.1 Crystal nucleation                                                                                  | 15  |

|               |       | 1.5.2 Crystal growth                                                                                      | 16  |

|               |       | 1.5.3 Overall Crystallization Kinetics                                                                    | 16  |

|               | 1.6   | The crystalline phase                                                                                     | 18  |

|               |       | 1.6.1 Structure of the crystalline phase                                                                  | 18  |

|               |       | 1.6.2 The conduction in the crystalline phase                                                             | 19  |

|               | 1.7   | The amorphous phase                                                                                       | 20  |

|               |       | 1.7.1 Structural properties of the amorphous phase                                                        | 21  |

|               |       | 1.7.2 Band structure and conduction in the amorphous phase                                                | 22  |

|               |       | 1.7.3 The threshold switching of the amorphous phase and the ON-stat                                      |     |

|               |       | 1.7.4 The stability of the amorphous phase                                                                | 26  |

|               |       | 1.7.4.1 Structural relaxation of the amorphous phase                                                      | 27  |

|               |       | 1.7.4.2 The Kissinger analysis of the crystallization dynamics                                            | 30  |

|               | 1.8   | The liquid phase                                                                                          | 31  |

|               | 1.9   | The impact of the phase-change material volume scaling                                                    | 33  |

|               | 1.10  | Summary of the chapter                                                                                    | 3.5 |

IV Contents

| 2 | $\mathbf{The}$ | Phase   | e-Change Memory cell: structures and reliability                      | 37 |

|---|----------------|---------|-----------------------------------------------------------------------|----|

|   | 2.1            | The ele | ectro-thermal behavior of the cell and the main electrical parameters | 38 |

|   |                | 2.1.1   | The plug/phase-change material interface                              | 40 |

|   |                | 2.1.2   | The plug element                                                      | 41 |

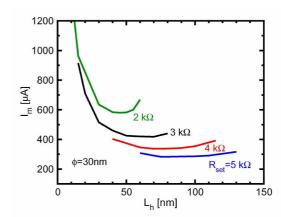

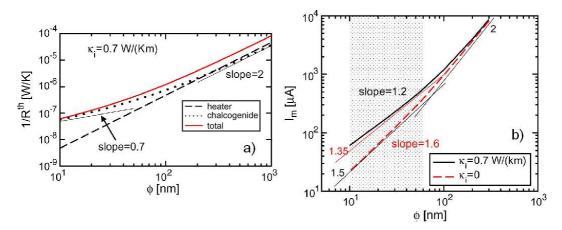

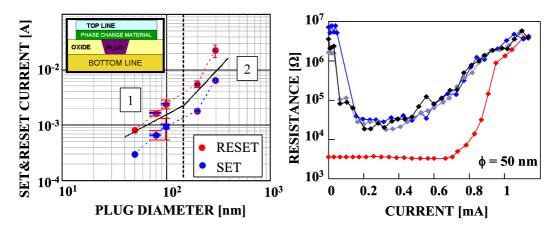

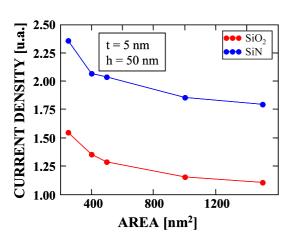

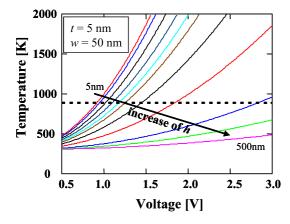

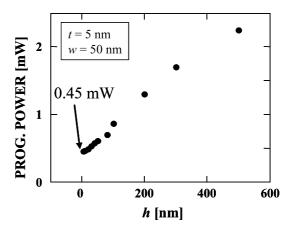

|   | 2.2            | The sh  | rink of the cell                                                      | 43 |

|   | 2.3            | The m   | ain PCM structures                                                    | 45 |

|   |                | 2.3.1   | The lance-type structure                                              | 45 |

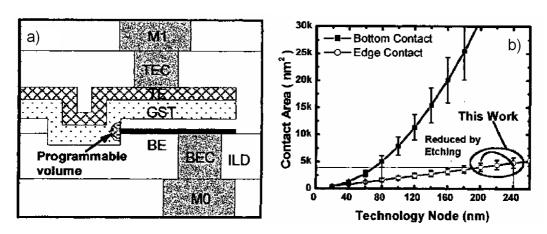

|   |                | 2.3.2   | The edge structure                                                    | 45 |

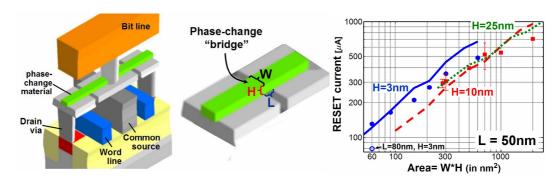

|   |                | 2.3.3   | The bridge structure                                                  | 46 |

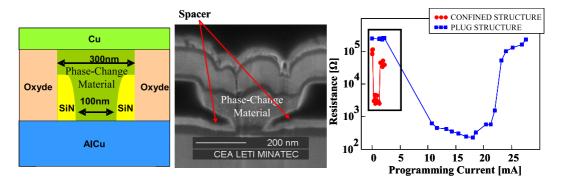

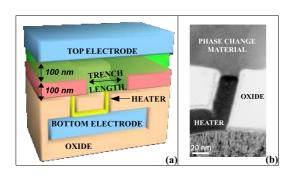

|   |                | 2.3.4   | The confined structure                                                | 47 |

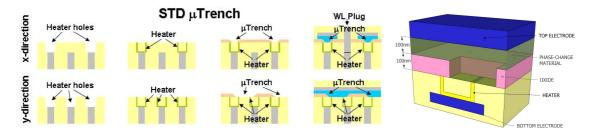

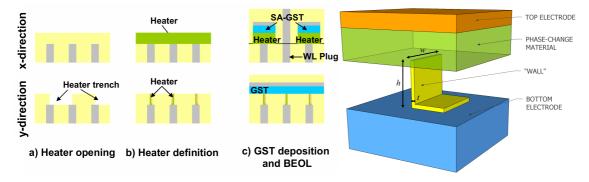

|   |                | 2.3.5   | The $\mu$ trench structure                                            | 49 |

|   |                | 2.3.6   | The "Wall" structure                                                  | 50 |

|   |                | 2.3.7   | The PCM structures: a comparison                                      | 51 |

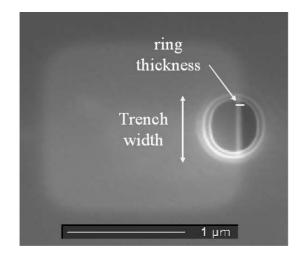

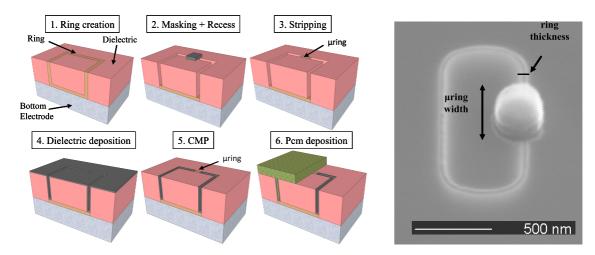

|   | 2.4            | New P   | CM concepts to scale the dimensions: the $\mu$ ring structure         | 52 |

|   | 2.5            | The ele | ectrical characterization of the PCM cell                             | 55 |

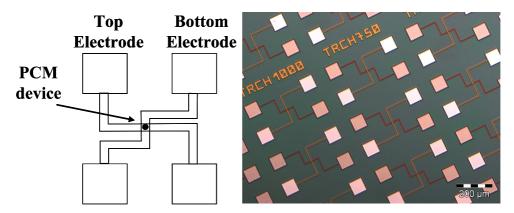

|   |                | 2.5.1   | The device                                                            | 55 |

|   |                | 2.5.2   | The equipment                                                         | 58 |

|   | 2.6            | The st  | udy of the PCM reliability                                            | 61 |

|   |                | 2.6.1   | The cycling endurance                                                 | 61 |

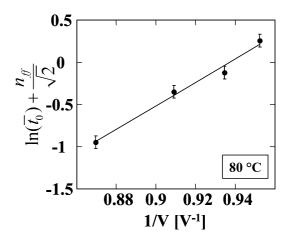

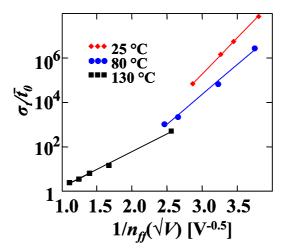

|   |                | 2.6.2   | The subthreshold switching: a statistical approach                    | 63 |

|   |                | 2.6.3   | The decrease of the threshold voltage rising the temperature          | 67 |

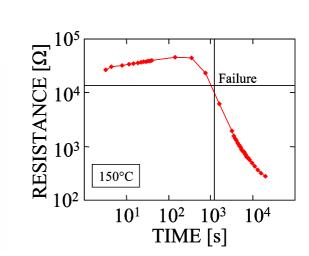

|   |                | 2.6.4   | The drift of the cell resistance                                      | 67 |

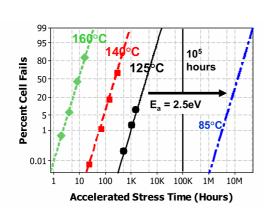

|   |                | 2.6.5   | The data retention                                                    | 68 |

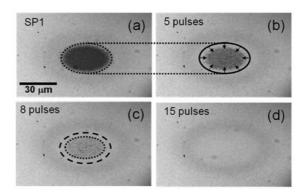

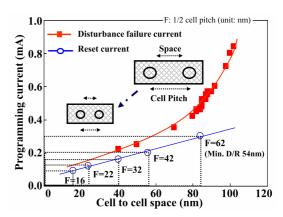

|   |                | 2.6.6   | The cell-to-cell cross-talk                                           | 70 |

|   |                | 2.6.7   | Case study: the high temperature reliability of the $\mu$ trench PCM  |    |

|   |                |         | structure                                                             | 70 |

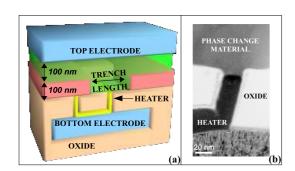

|   |                |         | 2.6.7.1 Our µtrench memory cell structure                             | 71 |

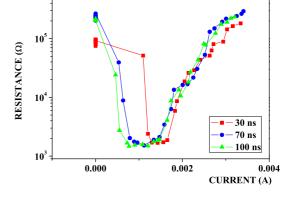

|   |                |         | 2.6.7.2 The devices and the speed analysis                            | 71 |

|   |                |         | 2.6.7.3 Dependence of the threshold voltage on temperature .          | 72 |

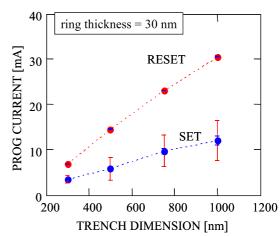

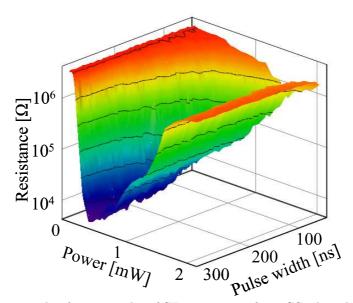

|   |                |         | 2.6.7.4 Programming curves                                            | 73 |

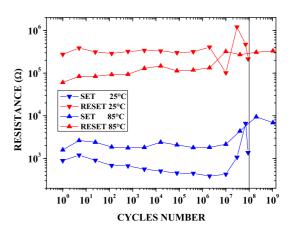

|   |                |         | 2.6.7.5 Endurance at high temperature                                 | 74 |

|   |                |         | 2.6.7.6 Resistivity drift analysis                                    | 74 |

|   |                |         | 2.6.7.7 Data retention measurements                                   | 75 |

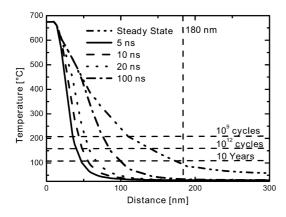

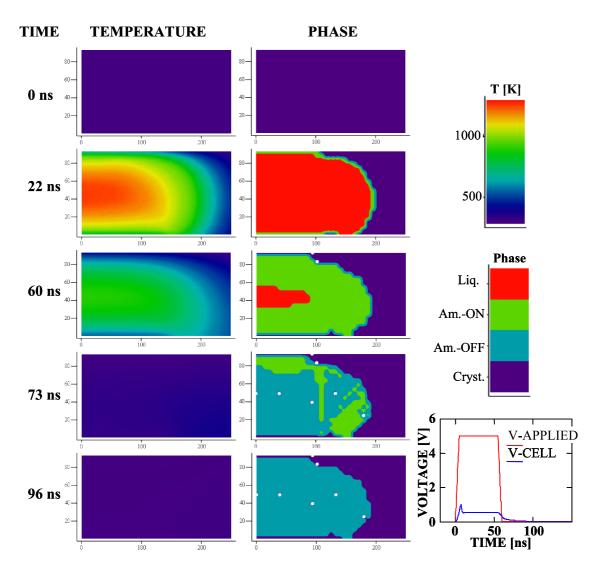

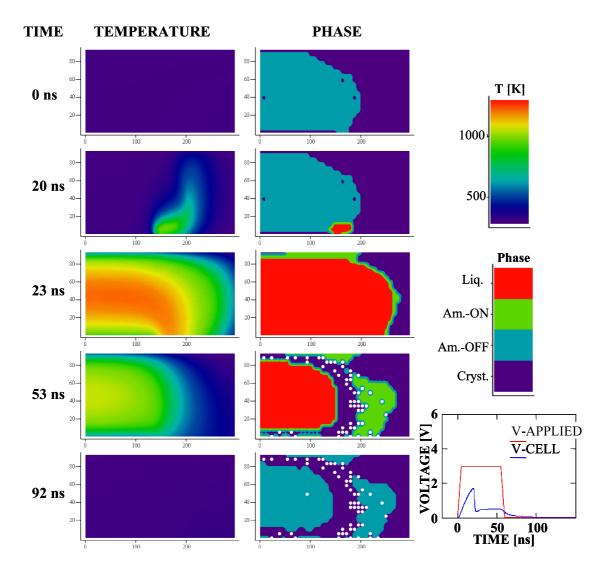

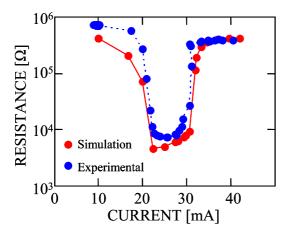

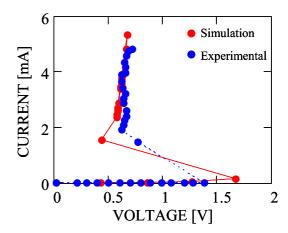

|   |                |         | 2.6.7.8 Simulation results                                            | 75 |

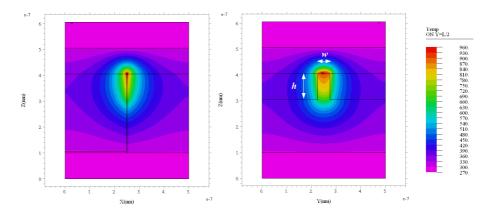

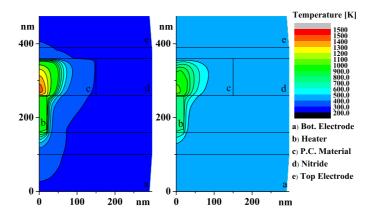

|   | 2.7            |         | mulation tool and the model                                           | 76 |

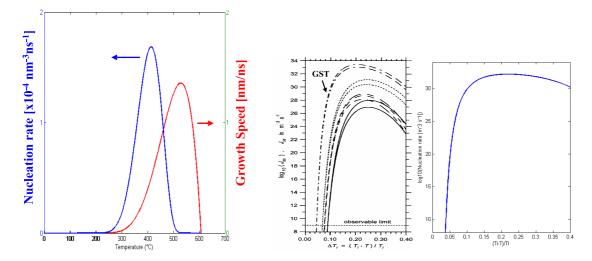

|   |                | 2.7.1   | The crystallization model                                             | 77 |

|   |                | 2.7.2   | The electrothermal solver                                             | 78 |

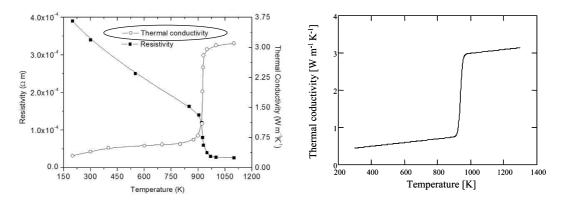

|   |                | 2.7.3   | The thermal conductivity                                              | 79 |

|   |                | 2.7.4   | The electrical conductivity                                           | 80 |

|   | 2.0            | 2.7.5   | Implementation of the electronic switch                               | 85 |

|   | 2.8            |         | mulation results                                                      | 86 |

|   |                | 2.8.1   | The simulation of the RESET pulse                                     | 86 |

|   |                | 2.8.2   | The simulation of the SET pulse                                       | 87 |

|   | 0.0            | 2.8.3   | A complete cell characteristic                                        | 89 |

|   | 2.9            | Summa   | ary of the chapter                                                    | 90 |

Contents

| 3  | The                                                  | reliab  | ility optimization of the embedded Phase-Change Memory           | 93  |  |  |

|----|------------------------------------------------------|---------|------------------------------------------------------------------|-----|--|--|

|    | 3.1 $\operatorname{Ge}_{x}\operatorname{Te}_{100-x}$ |         |                                                                  |     |  |  |

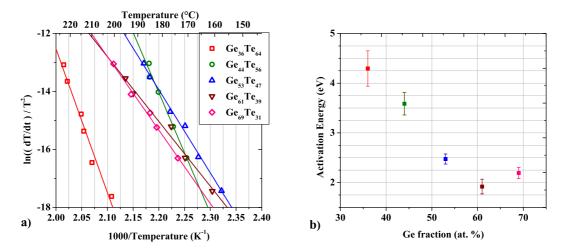

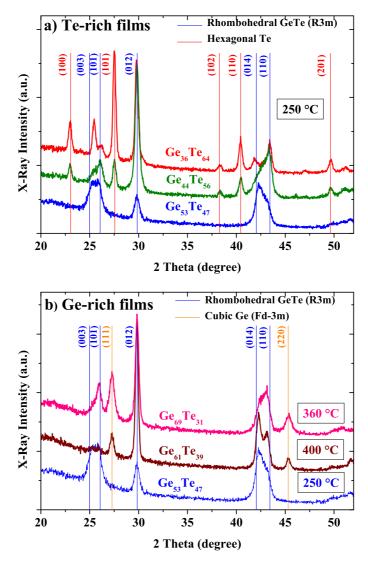

|    |                                                      | 3.1.1   | RBS, resistivity and XRD measurements                            | 94  |  |  |

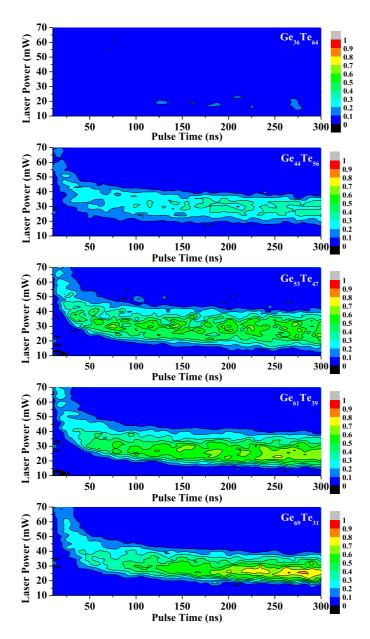

|    |                                                      | 3.1.2   | Optical characterization at the static tester                    | 97  |  |  |

|    |                                                      | 3.1.3   | Memory Device Characterization                                   | 97  |  |  |

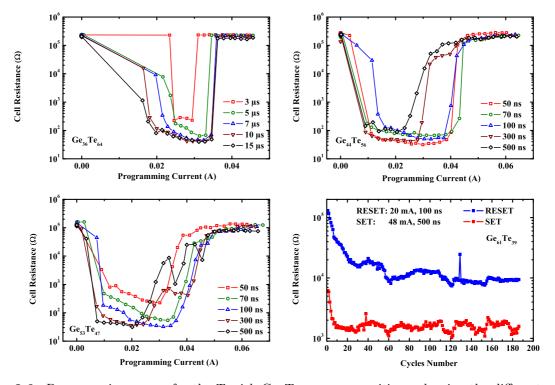

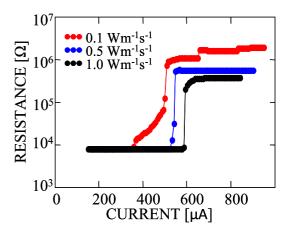

|    |                                                      | 3.1.4   | Effects of the growth speed on the RESET-SET characteristics .   | 100 |  |  |

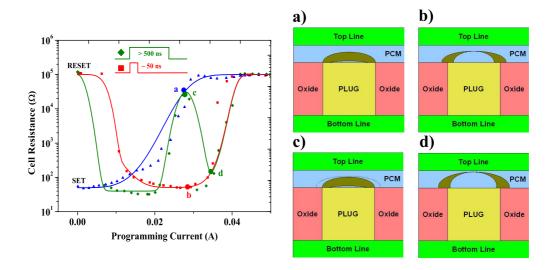

|    |                                                      | 3.1.5   | Simulation of the growth speed effects on the R-I characteristic | 102 |  |  |

|    |                                                      | 3.1.6   | Threshold voltage investigation                                  | 103 |  |  |

|    |                                                      | 3.1.7   | Endurance                                                        | 104 |  |  |

|    |                                                      | 3.1.8   | Resistivity drift in the RESET state                             | 104 |  |  |

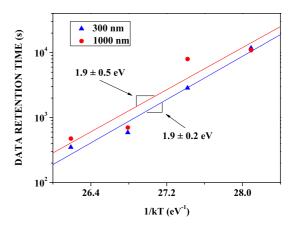

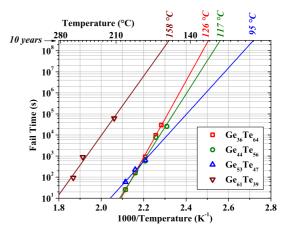

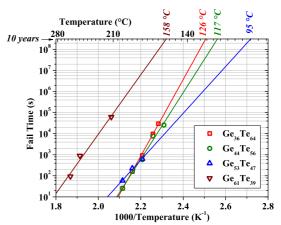

|    |                                                      | 3.1.9   | Data retention measurements                                      | 104 |  |  |

|    |                                                      | 3.1.10  | Conclusions                                                      | 105 |  |  |

|    | 3.2                                                  | _       | loped PCM                                                        | 106 |  |  |

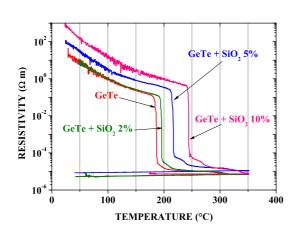

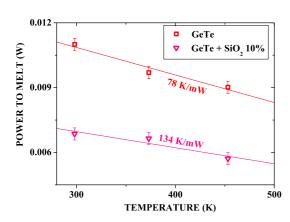

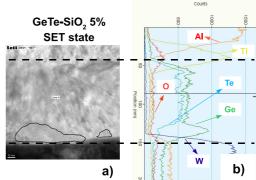

|    |                                                      | 3.2.1   | Material characterization                                        | 106 |  |  |

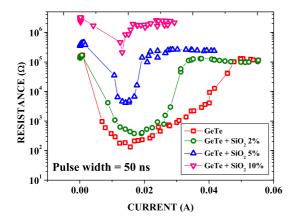

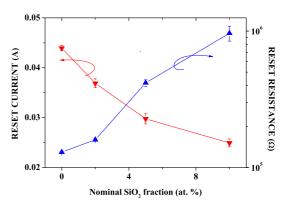

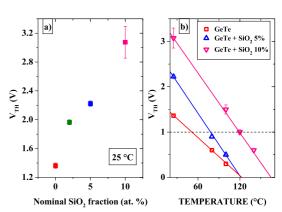

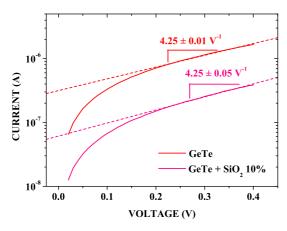

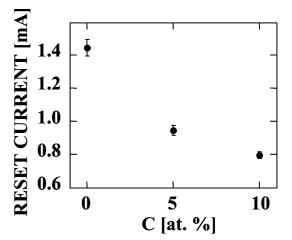

|    |                                                      | 3.2.2   | Device electrical characterization                               | 107 |  |  |

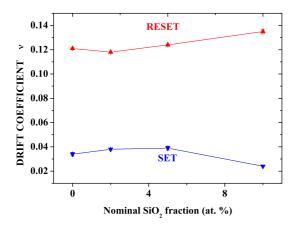

|    |                                                      | 3.2.3   | Drift of the RESET state characterization                        | 109 |  |  |

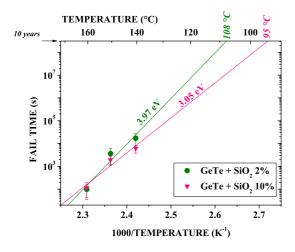

|    |                                                      | 3.2.4   | Retention properties                                             | 110 |  |  |

|    |                                                      | 3.2.5   | Threshold voltage                                                | 110 |  |  |

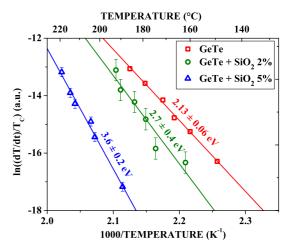

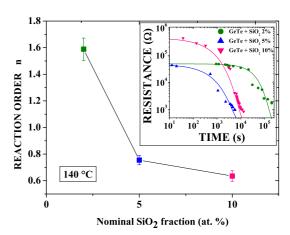

|    |                                                      | 3.2.6   | Avrami analysis                                                  | 111 |  |  |

|    |                                                      | 3.2.7   | Summary of $SiO_2$ inclusions effects                            | 112 |  |  |

|    | 3.3                                                  |         | n-doping in $Ge_2Sb_2Te_5$ -based PCM                            | 112 |  |  |

|    | 3.4                                                  | Ge enr  | riched phase-change materials                                    | 113 |  |  |

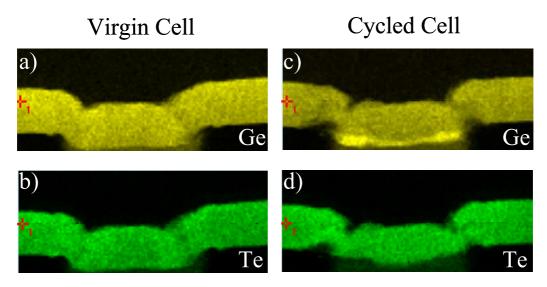

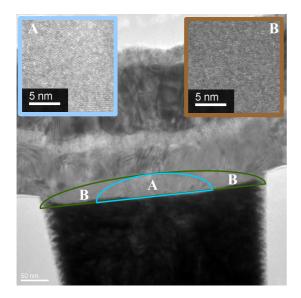

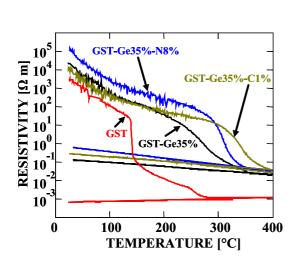

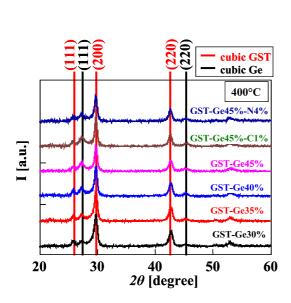

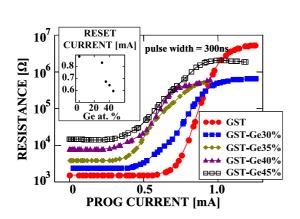

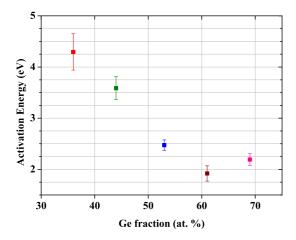

|    |                                                      | 3.4.1   | Material characterization                                        | 114 |  |  |

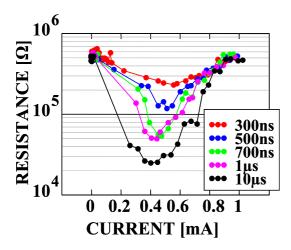

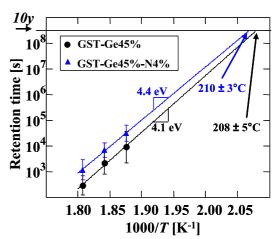

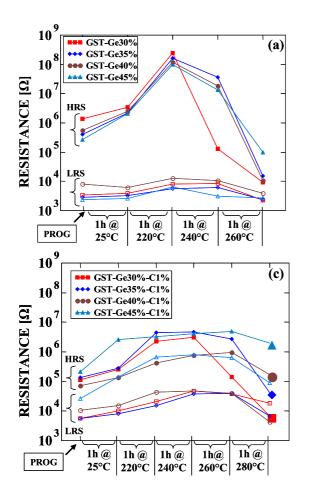

|    |                                                      | 3.4.2   | Device performance                                               | 116 |  |  |

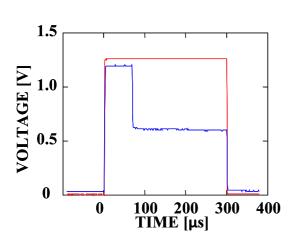

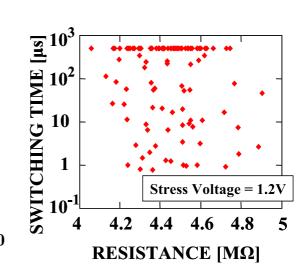

|    |                                                      | 3.4.3   | SET performance                                                  | 118 |  |  |

|    |                                                      | 3.4.4   | Conclusions                                                      | 124 |  |  |

|    | 3.5                                                  | Discus  | sions                                                            | 124 |  |  |

|    | 3.6                                                  | Summ    | ary of the chapter                                               | 125 |  |  |

| Co | onclu                                                | sions a | and perspectives                                                 | 127 |  |  |

| Re | efere                                                | nces    |                                                                  | 131 |  |  |

| A۱ | utho                                                 | r's pub | dication list                                                    | 145 |  |  |

| Re | ésum                                                 | é en fr | rançais                                                          | 147 |  |  |

## Abstract - Résumé

# <u>TITLE:</u> Reliability Analysis of Embedded Phase-Change Memories Based on Innovative Materials

#### Abstract:

Memories are getting an exponential importance in our present era, and are fundamental in the definition of all the electronic systems with which we interact in our daily life. Non-volatile memory technology (NVM), represented by Flash technology, have been able to follow till now the miniaturization trend to fulfill the increasing memory density demanded by the market. However, the scaling is becoming increasingly difficult, rising their cost per byte due to the incoming technological complexity. In this context, innovative memory technologies are becoming not just an alternative, but the only possible solution to provide higher density at lower cost, better functionality and low power consumption. Phase-Change Memory (PCM) technology is considered the leading solution for the next NVM generation, combining non-volatility, scalability, bit-alterability, high write speed and read bandwidth and high cycle life endurance. However, some reliability issues remain to overcome, in order to be a valid Flash replacement in all the possible applications. In particular, retention of data at high temperature, is one of the main requirements of industrial and automotive embedded applications.

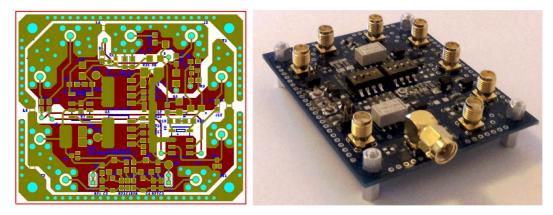

This work focuses on the study of embedded Phase-Change Memories, in order to optimize the memory device and finally propose some solutions to overcome the main bottlenecks of this technology, in particular addressing automotive applications. We designed, fabricated, and tested PCM devices based on recognized and innovative structures, analyzing their advantages and disadvantages, and evaluating the scaling impact. Our reliability analysis led to the development of a characterization setup dedicated to characterize our PCM cells with pulses in the order of nanoseconds, and to the implementation of a simulation tool based on a thermoelectrical solver and on the Level Set numerical approach, to understand the different mechanisms taking place in our cells during the programming operations.

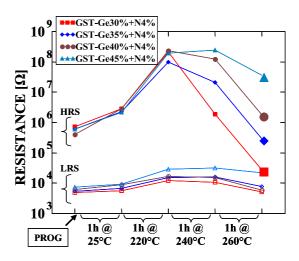

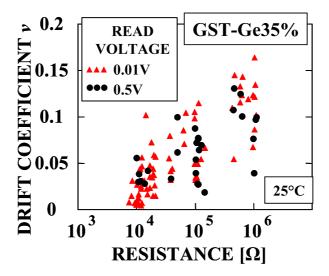

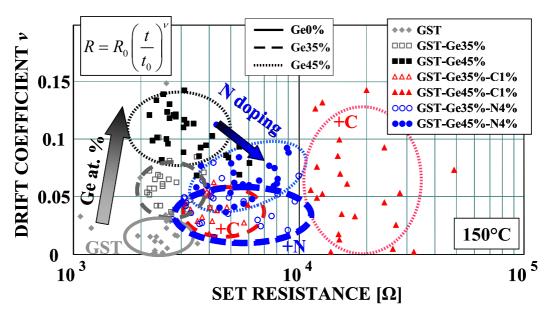

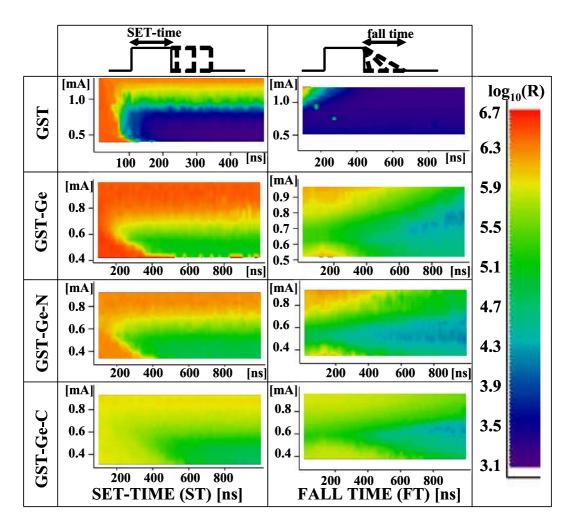

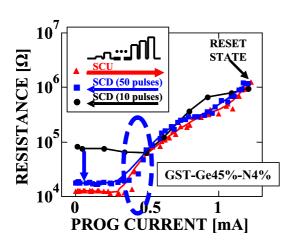

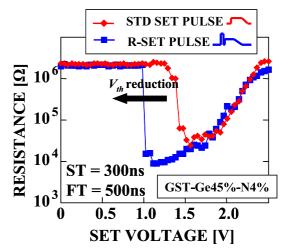

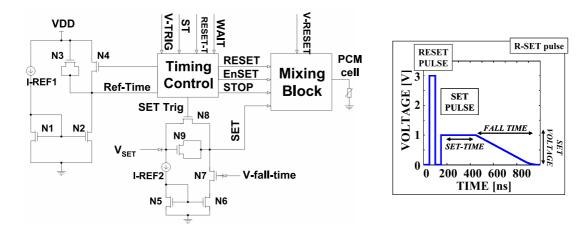

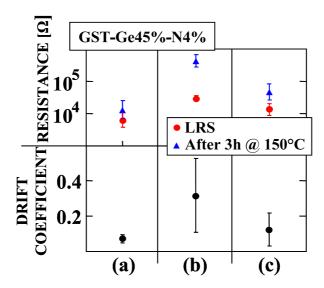

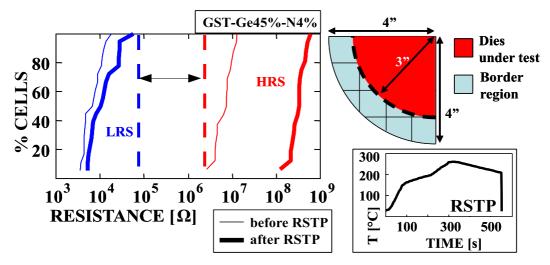

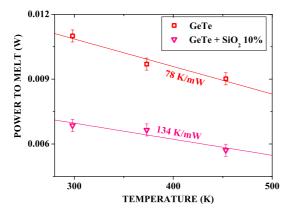

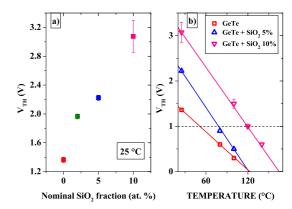

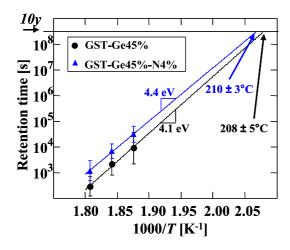

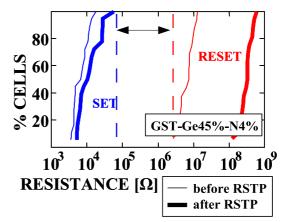

In order to fulfill embedded NVM requirements, we engineered the phase-change material integrated in the PCM device with two main approaches: the stoichiometry variation and the dopants addition. We showed and explained how the data retention in GeTe based PCM devices can be enhanced increasing Te content, and how SiO<sub>2</sub> inclusions can reduce the read voltage disturbs at high operating temperatures. Moreover, we reported the advantages on the programming power reduction of carbon doping in Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> based devices. Finally, we studied the effects of Ge enrichment in Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>, combined with N or C doping, integrated in state-of-the-art PCM cells. Through the introduction of a new programming technique, we demonstrated the possibility to improve the programming speed of these devices, characterized by data

VIII Abstract

retention performance among the best reported in the literature, and to reduce the drift phenomenon that affects the resistance state stability of PCM technology. We then proved, with these last results, the suitability of PCM for embedded applications.

#### Speciality: Nanoelectronics and Nanotechnology

**<u>Key Words:</u>** Phase-Change Memory, embedded applications, reliability, innovative materials, non-volatile memory.

Thesis work prepared at: Advanced Memory Laboratory,

CEA, LETI, MINATEC Campus, 17 rue des Martyrs, 38054 Grenoble Cedex 9, France.

# <u>TITRE</u>: Analyse de la Fiabilité de Mémoires à Changement de Phase Embarquées Basées sur des Matériaux Innovants

#### Résumé:

Les Mémoires ont de plus en plus importance à l'époque actuelle, et sont fondamentales pour la définition de tous les systèmes électroniques avec lesquels nous entrons en contact dans notre vie quotidienne. Les mémoires non-volatiles (NVM), représentées par la technologie Flash, ont pu suivre jusqu'à présent l'effort à la miniaturisation pour satisfaire la demande croissante de densité de mémoire exigée par le marché. Cependant, la réduction de la taille du dispositif de mémoire est de plus en plus difficile et la complexité technologique demandé a augmenté le coût par octet. Dans ce contexte, les technologies de mémoire innovantes deviennent non seulement une alternative, mais la seule solution possible pour fournir une densité plus élevée à moindre coût, une meilleure fonctionnalité et une faible consommation d'énergie. Les Mémoires à Changement de Phase (PCM) sont considérées comme la solution de pointe pour la future génération de mémoires non-volatiles, grâce à leur non-volatilité, scalabilité, "bit-alterability", grande vitesse de lecture et d'écriture, et cyclabilité élevée. Néanmoins, certains problèmes de fiabilité restent à surmonter afin de rendre cette technologie un remplacement valable de la technologie Flash dans toutes les applications. Plus en détail, la conservation des données à haute température, est l'une des principales exigences des applications embarquées industrielles et automobiles.

Cette thèse se concentre sur l'étude des mémoires à changement de phase pour des applications embarquées, dans le but d'optimiser le dispositif de mémoire et enfin de proposer des solutions pour surmonter les principaux obstacles de cette technologie, en abordant notamment les applications automobiles. Nous avons conçu, fabriqué et testé des dispositifs PCM basés sur des structures reconnues et innovantes, en analysant leurs avantages et inconvénients, et en évaluant l'impact de la réduction de la taille. Notre analyse de fiabilité a conduit au développement d'un système de caractérisation dédié à caractériser nos cellules PCM avec des impulsions de l'ordre de la nanoseconde, et à la mise en œuvre d'un outil de simulation basé sur un solveur thermoélectrique et sur l'approche numérique "Level Set", pour comprendre les différentes mécanismes qui ont lieu dans nos cellules pendant les opérations de programmation.

Afin de répondre aux spécifications du marché des mémoires non-volatiles embarquées, nous avons conçu le matériau à changement de phase intégré dans le dispositif PCM avec deux principales approches : la variation de la stœchiométrie et l'ajout de dopants. Nous avons démontré et expliqué comme la rétention des données dans les dispositifs PCM à base de GeTe peut être améliorée avec l'augmentation de la concentration de

Abstract

Te, et comme les inclusions de SiO<sub>2</sub> peuvent réduire les défauts causés par la tension de lecture à températures de fonctionnement élevées. En outre, nous avons présenté les avantages sur la réduction de la puissance de programmation du dopage de carbone dans les dispositifs à base de Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>. Enfin, nous avons étudié les effets de l'enrichissement en Ge dans le Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>, combiné avec le dopage N et C, intégré dans des cellules PCM à l'état de l'art. Grâce à l'introduction d'une nouvelle technique de programmation, nous avons démontré la possibilité d'augmenter la vitesse de programmation de ces dispositifs, caractérisés par des performances de rétention des données parmi les meilleurs rapportés dans la littérature, et de réduire le phénomène de la dérive de la résistance qui affecte la stabilité de l'état programmé des cellules PCM. Nous avons donc prouvé, avec ces derniers résultats, la pertinence de la technologie PCM pour les applications embarquées.

#### Spécialité : Nano Électroniques et Nano Technologies

Mots Clés: mémoires à changement de phase, applications embarquées, fiabilité, matériaux innovants, mémoires non-volatiles.

Thèse préparée au sein du : Laboratoire de Mémoires Avancées,

CEA, LETI, MINATEC Campus, 17 rue des Martyrs, 38054 Grenoble Cedex 9, France.

# List of Symbols

| Symbol              | Measure Unit                             | Designation                                                                           |

|---------------------|------------------------------------------|---------------------------------------------------------------------------------------|

| a                   | [m]                                      | Characteristic distance                                                               |

| 1                   | [ 1 m -2]                                | Fitting parameter (current density) in the equation of the                            |

| A                   | $[A m^{-2}]$                             | electrical conductivity of the amorphous phase (simulation tool)                      |

| $A_{th}$            | $[m^2]$                                  | Thermal effective area                                                                |

| $A_{PLUG}$          | $[m^2]$                                  | Surface area of the plug/phase-change material interface                              |

| B                   | [m]                                      | Fitting parameter (distance) in the equation of the electri-                          |

| $B_W$               | $[Bytess^{-1}]$                          | cal conductivity of the amorphous phase (simulation tool)<br>Memory bandwidth         |

| $C_{end}$           | [cycles]                                 | Cycling endurance                                                                     |

| $C_p$               | $[JKg^{-1}K]$                            | Heat capacity of the material (simulation tool)                                       |

| $C_P$               | [F]                                      | Parasitic capacitance                                                                 |

| $\Delta d$          | [m]                                      | Average increase of the radius of the crystalline volume                              |

| d                   | [m]                                      | Interatomic distance (simulation tool)                                                |

| $ec{E}$             | $[V m^{-1}]$                             | Electric field vector                                                                 |

| E                   | $[V m^{-1}]$                             | Electric field intensity                                                              |

| $E_0$               | $[V m^{-1}]$                             | Characteristic field<br>Activation energy of conduction in the amorphous phase        |

| $E_{am}$            | [eV]                                     | (simulation tool)                                                                     |

| $E_{cr}$            | [eV]                                     | Activation energy of the conduction in the crystalline phase                          |

|                     |                                          | (simulation tool)                                                                     |

| $E_g$               | [eV]                                     | Energy band gap                                                                       |

| $E_A \ E_B$         | $egin{array}{c} [eV] \ [eV] \end{array}$ | Activation energy of the failure process  Energy barrier of the structural relaxation |

| $E_C$               | [eV]                                     | Activation energy of the conduction                                                   |

| $E_{TH}$            | $[V m^{-1}]$                             | Threshold electric field                                                              |

| $f_{BW}$            | [Hz]                                     | Bandwidth                                                                             |

| g                   | [-]                                      | Shape factor                                                                          |

| $\Delta G_{ac}$     | [eV]                                     | Difference between the Gibbs free energy of the amorphous                             |

|                     |                                          | and crystalline phase<br>Difference between the Gibbs free energy per unit volume     |

| $\Delta G_v$        | $[eV m^{-3}]$                            | of the amorphous and crystalline phase                                                |

| $I_m$               | [A]                                      | Melting current                                                                       |

|                     | $[m^{-3} s^{-1}]$                        | Nucleation rate                                                                       |

| $I_{peak}$          | [A]                                      | Current peak                                                                          |

| $I_s$               | $[m^{-3}  s^{-1}]$                       | Stationary nucleation rate                                                            |

| $I_{CELL}$ $I_{CN}$ | [A] $[A]$                                | Current in the cell Current in the cell in the ON-state                               |

| $I_{ON} \ I_{R}$    | [A]                                      | RESET current                                                                         |

| $I_S$               | [A]                                      | SET current                                                                           |

| $I_{TH}$            | [A]                                      | Threshold current                                                                     |

|                     | =                                        |                                                                                       |

XII List of Symbols

| $ec{J}$                  | $[\Lambda_m=2]$                                                                                                        | Current density vector                                                      |

|--------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| J                        | $[A  m^{-2}] \ [A  m^{-2}]$                                                                                            | Current density vector Current density intensity                            |

| $J_R$                    | $[A m^{-1}]$                                                                                                           | RESET current density                                                       |

|                          |                                                                                                                        | SET current density                                                         |

| $J_S$                    | $\begin{bmatrix} A H t \end{bmatrix}$ $\begin{bmatrix} W m^{-1} & -1 \end{bmatrix}$                                    | v                                                                           |

| $\kappa_{th}$            | $\begin{bmatrix} W & m & S \end{bmatrix}$                                                                              | Thermal conductivity due to electron diffusion                              |

| $\kappa_{th}^{r}$        | [VV III S]                                                                                                             | Thermal conductivity due to electron diffusion                              |

| $\kappa_{th}$            | $[W \ m^{-1} s^{-1}]$                                                                                                  | Thermal conductivity of the phase-change material                           |

| $\kappa_{th}^-$          | $ [A m^{-2}] $ $ [W m^{-1} s^{-1}] $ $ [eV K^{-1}] $ | Lattice thermal conductivity                                                |

| $\stackrel{\kappa_B}{K}$ | $[ev \ K^{-1}]$                                                                                                        | Boltzmann constant Crystallization rate of the Avroni equation              |

|                          | [-]                                                                                                                    | Crystallization rate of the Avrami equation                                 |

|                          | $[J  m^{-3}]$                                                                                                          | Latent heat of melting (simulation tool)                                    |

| $L_{PLUG}$               |                                                                                                                        | Length of the plug element  Melan mass (simulation tool)                    |

|                          | $[Kg  mol^{-1}]$                                                                                                       | Molar mass (simulation tool)                                                |

| $M_C$                    | [Bytes]                                                                                                                | Memory capacity Reaction order of the crystallization process in the Avrami |

| n                        | [-]                                                                                                                    | equation                                                                    |

| $n_{ff}$                 | [-]                                                                                                                    | Form factor                                                                 |

|                          | [-]                                                                                                                    | Polarization factor                                                         |

| $\stackrel{N}{N}$        | $[m^{-3}]$                                                                                                             | Density of the possible nucleation sites (simulation tool)                  |

| $N_0$                    | [—]                                                                                                                    | Number of growing crystals                                                  |

|                          |                                                                                                                        | Number of atoms at the surface of the critical size nucleus                 |

| $O_n$                    | [-]                                                                                                                    | (simulation tool)                                                           |

| p                        | $[W m^{-3}]$                                                                                                           | Power density                                                               |

| P                        | [W]                                                                                                                    | Electrical power                                                            |

| $P_m$                    | [W]                                                                                                                    | Power to melt the phase-change material                                     |

| $P_{CELL}$               | [W]                                                                                                                    | Programming power delivered in the PCM cell                                 |

| q                        | [C]                                                                                                                    | Fundamental charge                                                          |

| $r_0$                    | [m]                                                                                                                    | Critical nucleus size                                                       |

| R                        | $[\Omega]$                                                                                                             | Resistance value                                                            |

| $R_0$                    | $[\Omega]$                                                                                                             | Resistance constant - fitting parameter                                     |

| $R_{th}$                 | $[KW^{-1}]$                                                                                                            | Thermal resistance                                                          |

| $R_{CELL}$               | $[\Omega]$                                                                                                             | Cell resistance                                                             |

| $R_{LINES}$              | $[\Omega]$                                                                                                             | Resistance of access lines                                                  |

| $R_{LOAD}$               | $[\Omega]$                                                                                                             | Pull-up load resistance                                                     |

| $R_{ON}$                 | $[\Omega]$                                                                                                             | Resistance of the cell in the ON-state                                      |

| $R_{PCM}$                | $[\Omega]$                                                                                                             | Resistive contribution of the phase-change material                         |

| $R_{PLUG}$               | $[\Omega]$                                                                                                             | Plug resistance                                                             |

| $R_{SET}$                | $[\Omega]$                                                                                                             | SET resistance of the device                                                |

| $R_{RESET}$              | $[\Omega]$                                                                                                             | RESET resistance of the device                                              |

| $S_D$                    | $[m^2]$                                                                                                                | Amorphous dome external surface                                             |

| $ar{t}$                  | [s]                                                                                                                    | Observation time                                                            |

| $ar{t_0}$                | [s]                                                                                                                    | Characteristic time                                                         |

| $t_0$                    | [s]                                                                                                                    | Time constant - fitting parameter                                           |

| $t_{cr}$                 | [s]                                                                                                                    | Crystallization time                                                        |

| $t_{fail}$               | [s]                                                                                                                    | Failure time                                                                |

| T                        | [K]                                                                                                                    | Temperature                                                                 |

| $\Delta T$               | [K]                                                                                                                    | Temperature variation                                                       |

|                          |                                                                                                                        |                                                                             |

List of Symbols XIII

| $T_a$           | [K]                                     | Ambient temperature                                                        |

|-----------------|-----------------------------------------|----------------------------------------------------------------------------|

| $T_{life}$      | [s]                                     | Life time of the cell                                                      |

| $T_m$           | [K]                                     | Melting temperature                                                        |

| $T_C^m$         | [K]                                     | Crystallization temperature                                                |

| $u_a$           | [m]                                     | Amorphous material thickness                                               |

| $U_B$           | [eV]                                    | Atomic energy barrier of the crystallization growth                        |

|                 | $[m s^{-1}]$                            | Growth speed                                                               |

| $v_g$           |                                         | •                                                                          |

| $V_0$           | [V]                                     | Characteristic voltage                                                     |

| $V_{CELL}$      | [V]                                     | Voltage drop on the PCM cell                                               |

| $V_H$           | [V]                                     | Holding voltage                                                            |

| $V_{MAX}$       | [V]                                     | Maximum voltage of the pulse generator                                     |

| $V_{PULSE}$     | [V]                                     | Voltage applied                                                            |

| $V_T H$         | [V]                                     | Threshold voltage                                                          |

| W               | [eV]                                    | Activation energy of the nucleation                                        |

| $W_0$           | [eV]                                    | Zero-field energy barrier of nucleation                                    |

| $W_{cr}$        | [eV]                                    | Activation energy of the crystallization                                   |

| $W_{ON}$        | [eV]                                    | Activation energy of the ON-state (simulation tool)                        |

| $\Delta z$      | [m]                                     | Mean distance between two traps in the lattice                             |

| $Z_e$           | [-]                                     | Zeldovich factor (simulation tool)                                         |

| $\alpha$        | [-]                                     | Crystalline fraction in the amorphous volume                               |

| $\alpha_{nucl}$ | [-]                                     | Geometrical constant dependent on the nucleus shape                        |

| $lpha_{th}$     | $[m^3 K W^{-1}]$                        | Thermal efficiency constant                                                |

| $\alpha_{wle}$  | [%]                                     | Wear leveling efficiency                                                   |

| $\gamma_m$      | [-]                                     | Material dependent constant                                                |

| /m              |                                         | Constant dependent on the critical conductivity at the                     |

| $\gamma_c$      |                                         | switching point                                                            |

| $\gamma_a$      | [Hz]                                    | Characteristic atomic frequency (simulation tool)                          |

| $\epsilon$      | $[F  m^{-1}]$                           | Dielectric permittivity                                                    |

| $\lambda$       | [m]                                     | Percolation distance (simulation tool)                                     |

| $ u_c$          | [Hz]                                    | Frequency of the atomic vibration in the crystalline phase                 |

| $ u_a$          | [Hz]                                    | Frequency of the atomic vibration in the amorphous phase                   |

| $\nu$           | [-]                                     | Drift coefficient                                                          |

| ρ               | $[\Omega m]$                            | Resistivity                                                                |

| $ ho_0$         | $[\Omega m]$                            | Resistivity constant                                                       |

| $ ho_{cr}$      | $[\Omega m]$                            | Resistivity of the crystalline phase                                       |

| $ ho_m$         | $[\Omega m]$                            | Material density (simulation tool)                                         |

| $ ho_{PLUG}$    | $[\Omega m]$                            | Resistivity of the plug element                                            |

| $\sigma$        | $[S m^{-1}]$                            | Electrical conductivity                                                    |

| $\sigma_0$      | $[S m^{-1}]$                            | Saturation conductivity                                                    |

| -               | $[J m^{-2}]$                            | Crystal-amorphous interface energy                                         |

| $\sigma_{ac}$   | · . · · · · · · · · · · · · · · · · · · | Time variability                                                           |

| $\sigma_t$      | $\begin{bmatrix} S \end{bmatrix}$       | · ·                                                                        |

| $\sigma_{ON}$   | $[S m^{-1}]$                            | Conductivity of the ON-state (simulation tool)  Threshold conductivity     |

| $\sigma_{TH}$   | $[S m^{-1}]$                            | Threshold conductivity Voltage measure resolution                          |

| $\sigma_V$      | [V]                                     | Voltage measure resolution  Dispersion of the energy barrier of nucleation |

| $\sigma_W$      | [eV]                                    | Dispersion of the energy barrier of nucleation                             |

| $\sigma_{W_0}$  | [eV]                                    | Dispersion of the zero-field energy barrier of nucleation                  |

XIV List of Symbols

| $	au_0$    | [s]     | Defect relaxation time at high temperature     |

|------------|---------|------------------------------------------------|

| $	au_i$    | [s]     | Incubation time                                |

| $	au_l$    | [s]     | Carrier life time                              |

| $	au_r$    | [s]     | Relaxation time of the material                |

| $	au_v$    | [s]     | Characteristic vibrational atomic time         |

| $	au_{SR}$ | [s]     | Defect relaxation time                         |

| $\phi$     | [m]     | Diameter of the plug in a lance-type structure |

| $\Omega$   | $[m^3]$ | Nucleus volume                                 |

# Introduction

#### Context

Memories are getting an exponential importance in our present era, and are fundamental in the definition of all the electronic systems with which we interact in our daily life. The number of digital data created and stored every day reached last year the surprising rate of 2.5 quintillion bytes per day ( $10^{18}$  bytes), with the 90% of the world's data created in the last two years alone [1]. Hence, the memory technologies have become more than a simple support technology, with the introduction of the "memorycentric" electronic concept [2]. The main example of this, is the changed measure unit along the years to describe a specific electronic application, moving from the computation power of the CPU to the memory capacity. Dynamic Random Access Memory (DRAM) but over all non-volatile memory technology (NVM), represented by Flash technology, have been able to follow till now the miniaturization trend to fulfill the increasing memory density demanded by the market. However, the scaling is becoming increasingly difficult, rising the cost per byte of Flash memories due to the incoming technological complexity. In this context, innovative memory technologies are becoming not just an alternative, but the only possible solution to provide higher density at lower cost, better functionality (bandwidth and latency) and low power consumption. Moreover, the great quest is to identify a technology able to guarantee the scaling for more consecutive technology nodes.

Different companies and research centers in recent years started the study of new possible solutions to replace standard memories. Instead of displacing and trapping electrons like in Flash memory, innovative approaches have been investigated, changing and simplifying also the philosophy of the device. A resistive NVM is based on a two-terminal device, in which an "active" material is sandwiched between two electrodes. The main idea of this structure, is to use a specific physical mechanism characteristic of the active material considered, to switch it reversibly, between two completely different resistive states. For example, in a Phase-Change Memory (PCM) a chalcogenide material (phase-change material) is used, taking advantage of the thermally induced transition from an amorphous phase to a crystalline phase. In a Resistive or Conductive Bridge RAM (RRAM or CBRAM), a metallic filament is grown and dissolved inside an insulating material. Another example is the Oxide RAM (OxRAM), in which the reversible soft-breakdown of some oxides is used. These memory devices, are among the most studied nowadays, and the possible candidates for the next NVM generation, replacing Flash and possibly also DRAM. The latter in fact, represents today the higher source of power consumption in the memory systems, requiring constant data refresh.

2 Introduction

PCM technology is considered the leading solution for the next NVM generation, revealing unique capabilities with respect to the other competing memory technologies [3, 4]. In particular it offers:

- non-volatility: DRAM requires a constant power supply to retain information, resulting in higher power consumption. PCM, being non-volatile, offers the retention of the data after power removal;

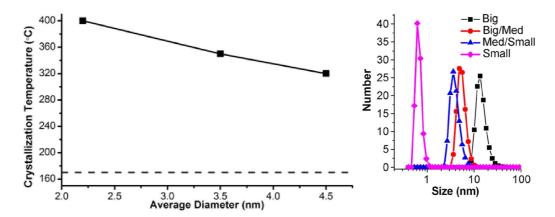

- scalability: stability of the stored phase has been demonstrated to be at least as small as 5 nm [5];

- bit-alterability: Flash technology requires regular page refreshing. PCM, like random access memories (RAM), does not require pre-erasing operations to store the information;

- write speed: the PCM write speed (on the order of 100 MB/s) is approaching today the 1 GB/s of DRAM;

- read bandwidth: Flash has long random access times on the order of tens of microseconds. PCM shows read latency of tens of nanoseconds like DRAM, enabling in-place code execution (not possible with standard Flash);

- endurance: PCM has not reached already the high endurance of 10<sup>16</sup> cycles of DRAM, but its demonstrated endurance of 10<sup>12</sup> cycles [6] makes it suitable for some DRAM replacement in infrequent or managed write applications;

- rad-hardness: radiation hardness is another important feature of PCM technology [7], required in embedded space applications or high energy physical instruments.

Even if PCM is today a recognized mature industrial technology, some reliability issues remain to overcome, in order to be a valid Flash replacement in all the possible applications. In fact, the thermal stability at high temperatures of the phase-change material integrated in a PCM device, is an intrinsic challenge of this technology. The retention of data in high temperature environments is one of the main requirements of industrial and automotive embedded applications, like microcontrollers and other integrated circuits that embed NVM. The required operations from -40 °C up to more than 150 °C, the soldering reflow process at 260 °C and the zero-defects requirement, are today the big challenges for PCM technology to finally fulfill all the requirements of the market. Moreover, the multi-level capability can open the door for higher data density.

## Thesis presentation

This work focuses on the study of embedded Phase-Change Memory, in order to optimize the memory device and finally propose some solutions to overcome the main bottlenecks of this technology, in particular addressing automotive applications and multi-level capability.

Introduction 3

In chapter 1 we present the PCM technology and the basics of the phase-change memory device. We introduce the Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> and the GeTe, as main phase-change materials that made possible the development of a PCM. We focus then on the three phases of a phase-change material: the crystalline phase, the amorphous phase and the liquid phase. The analysis of the electrical and thermal properties of the phases of a phase-change material, allows to understand the main characteristics of the final PCM cell, and the correlated reliability issues.

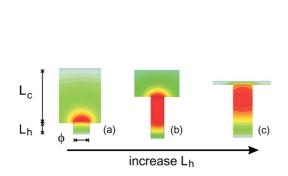

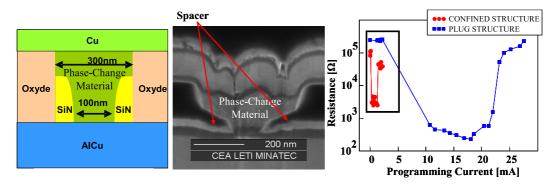

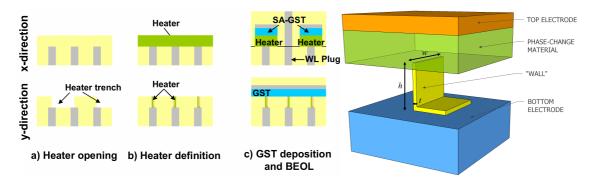

The chapter 2 presents the electrical parameters of a PCM device, and how the geometry and the scaling of the cell strongly impact the device performance. We present then some of the main PCM structures developed in the last decade, in order to scale the cell size, starting with the lance-type cell and ending with the state-of-the-art industrial "Wall" PCM. At the same time, we introduce the devices we designed, fabricated and tested, in order to perform our studies on this technology. We developed a specific characterization setup in order to perform the reliability analysis, and in the chapter we show the main issues of PCM, in particular correlated with the stability of the phase-change material at high operating temperatures. The specific case of the reliability of the PCM  $\mu$ trench technology is addressed. To conclude, we present the simulation tool we implemented, in order to understand the different mechanisms taking place in the cell during the programming operations, and to understand the dependency of the device behavior, on the phase-change material physical parameters.

In chapter 3 we describe how we engineered our phase-change materials. We show how tuning the GeTe stoichiometry, we were able to improve the data retention of the PCM device. We demonstrate that  $SiO_2$  doping in phase-change materials allows the reduction of the read-disturb problem at high temperature, and we propose the carbon doping, as possible solution for the cell power reduction. Finally, we show how we obtained data retention results among the best reported in the literature, in Ge-rich based state-of-the-art devices fabricated in the framework of the collaboration with STMicroelectronics. Through the introduction of a new programming technique, we demonstrate the possibility to improve the programming speed of these devices, and to reduce the drift phenomenon that affects the resistance state stability of PCM technology, in particular at high temperature. We then proved, with these last results, the suitability of PCM for embedded applications.

In the end, we present the general conclusions of this work, summarizing the main results obtained and proposing some perspectives for future research activities on this technology.

# Chapter 1

# The Phase-Change Memory Technology

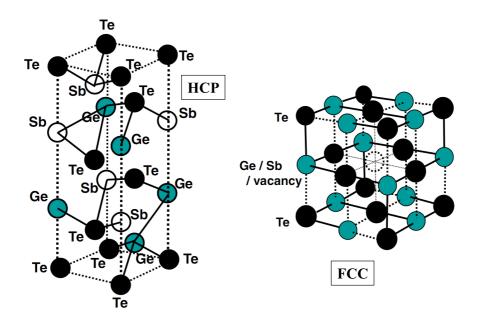

Phase-Change Memory (PCM) bases its functionality on the physical phase change of a chalcogenide material, sandwiched between two electrodes. This simple definition, revealed in the last decade the potentiality of a new technology, which has become today the most promising candidate for the next generation of non-volatile memory. The phase-change materials belong to the class of chalcogenides. The outstanding property of these materials is the reversible switching from a high resistive amorphous phase to a low resistive crystalline phase, made possible in a memory device, by the current induced Joule heating of the phase-change material.

In this chapter we introduce the principles of the PCM technology, and the range of applications in which the PCM technology can be used. We present then the GeTe and the Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>, considered as the two main phase-change materials, and studied in recent years before for optical applications, and nowadays for phase-change memory (PCM) applications. We address the phase-change theory and we analyze the three phases of a phase-change material: the crystalline phase, the amorphous phase, and the liquid phase. Their thermal and electrical properties are described, in order to understand how they impact the final behavior of the memory device.

# **United States Patent Office**

3,241,009 Patented Mar. 15, 1966

3,241,009

MULTIPLE RESISTANCE SEMICONDUCTOR

ELEMENTS

Jacob F. Dewald, Mendham, William R. Northover,

Westfield, and Arthur D. Pearson, Bernardsville, N.J.,

assignors to Bell Telephone Laboratories, Incorporated, New York, N.Y., a corporation of New York

Filed Nov. 6, 1961, Ser. No. 150,374

14 Claims. (Cl. 317—234) FIG. 3A CURRENT SOURCE What is claimed is: 1. An electrical component capable of operating in two resistance states comprising a glass body having an electronic resistivity within the range 10<sup>2</sup> to 10<sup>8</sup> ohm-cm. and having electrical means for impressing an electric signal on said body, said glass comprising means responsive to voltage signals of a minimum value for changing the resistance state of said body from a first discrete high resistance state to a second discrete low resistance state and said means being further responsive to the rate of decrease of the value of the voltage signals to revert said body to the high resistance state when the rate of decrease of the voltage signal exceeds a given rate and to maintain said body in the low resistance state when the rate of decrease of the voltage signal is less than the given J. F. DEWALD

INVENTORS: W.R. NORTHOVER

A.D. PEARSON

BY

**Fig. 1.1.** First patent on a multiple resistance device, based on a reversible switching mechanism. On the right the idea for the characterization setup and the current/voltage characteristic of the device, showing the two different programmable state (A and B) [8].

## 1.1 Brief history of PCM technology

ATTORNEY

The concept of using the amorphous to crystalline phase transition of chalcogenide materials to store information has been proposed since the early 1960's by Stanford Robert Ovshinsky, considered the father of the phase-change memory devices. His main contribution is the demonstration of the existence of the switching phenomenon, that makes possible the transition of an amorphous phase-change material from a low to a high conductive state, in different chalcogenides integrated in analytical structures. The first patent concerning "multiple resistance semiconductor elements" was filled in 1961 by Dewald, Northover and Pearson, in which they advanced the description of the modern PCM technology and that we report partially in Fig. 1.1. In their idea they evidenced the main characteristics of a PCM device. First, two possible main stationary states: a low resistance state (called LRS or SET) and a high resistance state (HRS or RESET). Second, the presence of a so called "threshold voltage" ( $V_{TH}$ ) that makes possible the electronic switching from a low to a high conductive state, in which the current-induced Joule heating of the phase-change material allows the recrystallization of the material, and then the transition from the HRS to the LRS [8].

Even if the industrial interest for PCM technology started to be concrete in 1970, when the first 256-bit memory array was developed by Neale and Nelson of Energy Conversion Devices along with Gordon Moore of Intel, a real first comprehension of

1.2 The PCM cell

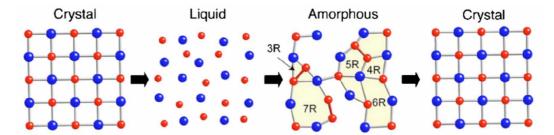

Fig. 1.2. The principle of the phase change transition. The phase-change material in the crystalline phase has to be melted to achieve the liquid phase. If the cooling rate is sufficiently high, then the material is quenched in the amorphous phase. To recover the crystalline phase, only a specific thermal profile can provide the energy necessary for the atomic reorganization [9].

the switching phenomenon has not been provided until the early 80's. Just after the first successful integrations of phase-change materials in silicon based electronics, the future of this technology started to be compromised by the limitation of the technology node: to guarantee a reliable and power-efficient device, the dimensions required a level of integration not available in that years. This explains the hibernation for about 20 years of PCM technology, just after the realization in 1978 of the first 1 kbit PCM prototype by Burroughs Corporation. Along this period, phase-change materials started their well known success in the optical applications, also thanks to the discovery of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) and its phase change properties. With the release of the first rewritable compact disc (CD-RW) in 1990, Panasonic declared the starting of the end of the magnetic tape supports for consumer applications: the first real revolution caused by the phase-change materials in the history of technology.

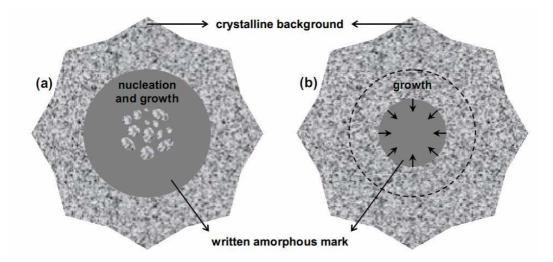

The principle of the phase transition in a PCM device, is based on the thermally-induced phase change of the material from a crystalline phase, ordered and lowly resistive, to an amorphous phase, disordered and highly resistive, passing from the liquid phase, as schematically described in Fig. 1.2 [9]. To achieve the amorphous phase, the phase-change material in the crystalline phase has to be melted (crossing the material melting temperature  $T_m$ ), through Joule heating, at high current densities, and then rapidly quenched (RESET operation). Thanks to the switching phenomenon, once reached a specific electric field threshold ( $E_{TH}$ ), the material in the amorphous phase changes abruptly its conductivity and starts to be highly conductive (what we call "ON-state" of the material). The phase-change material, once in the ON-state, is then crystallized through the Joule heating obtained thanks to the current flow (SET operation). There are many other properties of these materials that are involved in the device behavior, that we will analyze in the next sections introducing the properties of the crystalline phase, of the amorphous phase and of the liquid phase of a phase-change material.

## 1.2 The PCM cell

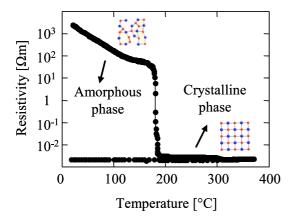

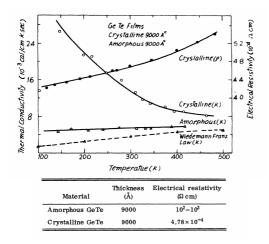

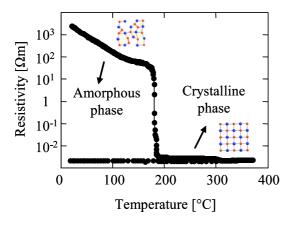

Like other resistive memories, the phase-change memory (PCM) cell is a two-terminal device. It bases its functionality on the strong difference in resistivity (up to more than 5 orders of magnitude), between the crystalline phase and the amorphous phase of the

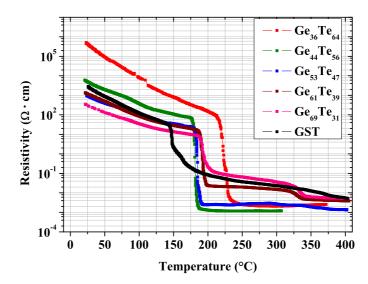

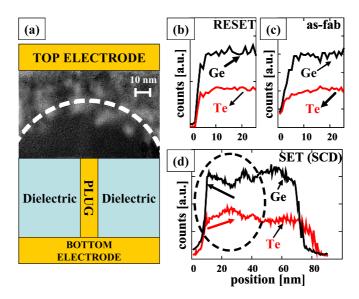

**Fig. 1.3.** Resistivity as a function of the temperature of a phase-change material. The transition from the amorphous to the crystalline phase, is highlighted by the sharp decrease of the resistivity of the material.

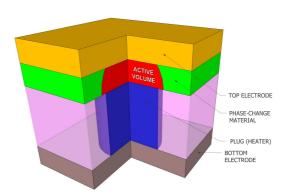

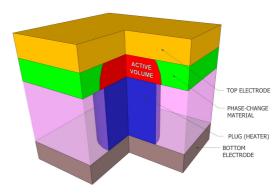

**Fig. 1.4.** General description of a PCM cell. The active volume involved in the phase transition is highlighted at the plug/phase-change material interface.

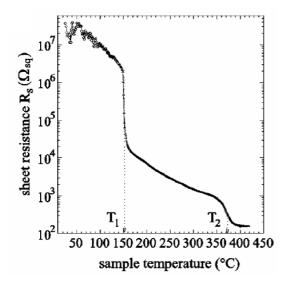

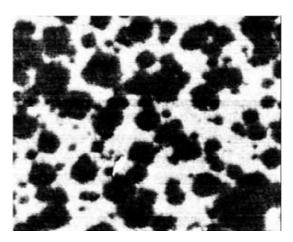

phase-change materials. In Fig. 1.3 we can see an example of this transition. The amorphous material is heated, and during the temperature increase, it experiences a decrease of the resistivity at a specific temperature, called crystallization temperature. The process of crystallization, activated and favorable at this temperature, drastically increases the conductivity of the material, finally crystallizing all the material volume. Once the material is cooled down to room temperature, the crystalline phase is preserved. The full process gives rise to the phase-change mechanism, in this case, induced by the external heating of the material.

The PCM cell, as reported in Fig. 1.4, can be basically described as consisting of:

- the bottom electrode;

- the plug conductive element (called also "heater") with the function to provide the electrical access to the phase-change material, to enable the current limitation, and to contribute to the "heating" of the phase-change material in the different phases of the programming;

- the phase-change material;

- the insulator surrounding the plug;

- the top electrode.

In the standard memory array architecture, the memory cell consists of a transistor access device (1T) and the PCM cell in series (1R). This configuration is called "1T1R". In an analytical structure in which only the PCM cell is realized in order to allow the study of the resistive element, the metal levels of the top and bottom electrodes are properly designed in order to provide the electrical access to the cell, and they are called "access lines".

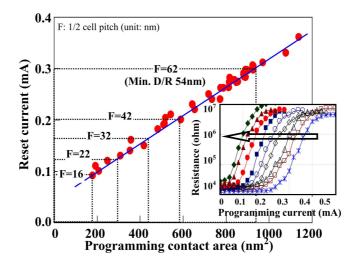

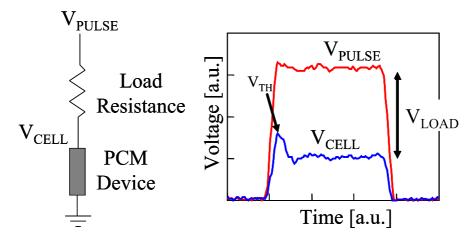

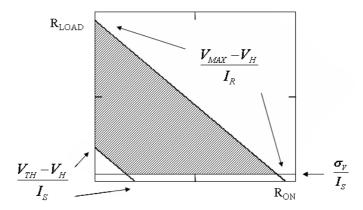

To program a PCM cell in the RESET state (or high resistance state, HRS), a RESET pulse is applied, consisting of a high current pulse able to raise the temperature above the melting point  $(T_m)$  in the active chalcogenide volume, followed by a sharp

1.2 The PCM cell

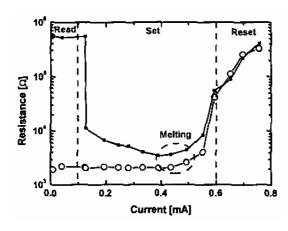

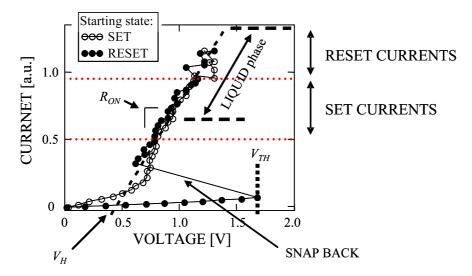

Fig. 1.5. Resistance as a function of the programming current (R-I), for a phase-change memory device starting from the SET state (open symbols), and starting from the RESET state (filled symbols). The READ, SET and RESET current ranges are highlighted [11].

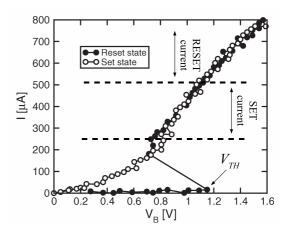

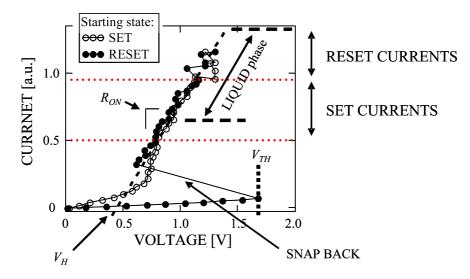

Fig. 1.6. Programming current as a function of cell voltage characteristic (I-V), typical of a PCM device. The two curves correspond respectively to a device starting from a RESET state (filled symbols), and to a device starting from a SET state (open symbols) [10].

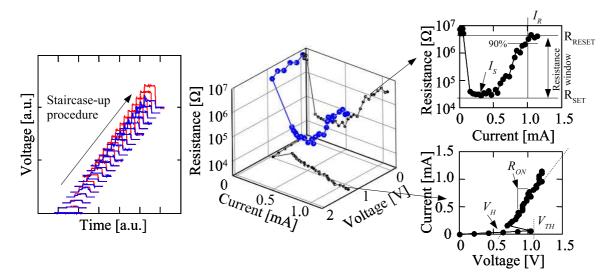

trailing edge quenching the same volume into an amorphous state (RESET operation) [10]. The RESET operation can be successful, only if a considerable volume of phase-change material is amorphized over the plug surface, in order to increase considerably the resistance of the device. To program the cell in the SET state (or low resistance state, LRS), two main strategies can be adopted:

- the application of a pulse with the same amplitude of a RESET pulse, but with a trailing edge sufficiently long to guarantee the permanence of the phase-change material in the range of temperatures favorable to the recrystallization;

- a pulse with amplitude lower than the RESET pulse, but higher than the threshold voltage, able to provide already during the pulse width, the good crystallization temperature in the active area of the phase-change material, to achieve at the end of the pulse the final SET state. In this case, the trailing edge can be as fast as in the RESET pulse.

The pulse shape becomes fundamental for the programming of the cell, since the main parameter to play on the material phase-change is the temperature. The temperature in fact, is increased in the device by the current induced Joule heating, and specific pulse shapes, correspond to specific temperature profiles in the cell.

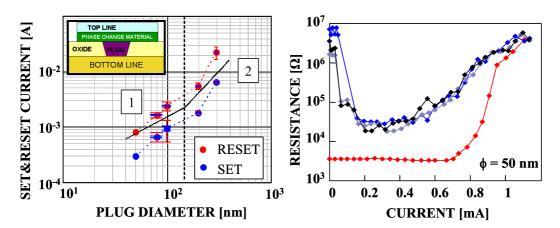

In Fig. 1.5 we report a typical resistance versus programming current characteristic of a PCM device. Each point in the graph corresponds to the final resistance of the memory, achieved after the application of a current pulse of specific intensity. Three main regions are highlighted: READ, SET and RESET. The READ operation enables the sensing of the device, and it has to avoid the disturbing or the change of the resistance state of the cell. Hence, it is performed at low current values. Increasing the programming current the temperature in the cell is risen enabling the recrystallization of the phase-change material, and lowering the final device resistance (SET). When the current intensity allows the partial melting of the phase-change material (melting

current), the rapid quenching allows the amorphisation of part of the material volume, resulting after the pulse application, in an increase of the resistance of the device (RESET). If we consider the characteristics of a device starting from a SET state, and of a device starting from a RESET state, we notice two main differences. The first, is the starting resistance, that is preserved in the READ region. The second is the different resistance achieved in the SET region. In fact, if the device starts already from a SET state, the material does not experience any phase transition till the reaching of the melting current. On the contrary, starting from an amorphous phase, the device, thanks to the crystallization mechanism, decreases its resistance, but this decrease depends as already observed, on the pulse shape (e.g. duration, fall time, etc.). As illustrated in the graph, in this case the pulses applied were not sufficiently long to recover the perfect crystallization of the phase-change material. Once reached the RESET region, the two characteristics overlap, because of the melting of the phase-change material in both cases.

The current as a function of the voltage plots of a phase-change memory (I-V), reported in Fig. 1.6, show the overlapping of the SET and of the RESET characteristics (that corresponds respectively to the device starting from the SET and the RESET state) in the SET and in the RESET range of currents. However, coming from the amorphous phase, only a long persistence in the SET current region, allows the recrystallization of the phase-change material. Moreover, the RESET I-V curve evidences the main electrical property of a PCM device: the switching phenomenon. The RESET device, once reached a critical threshold voltage  $V_{TH}$ , with a typical snap back in the I-V curve, switches to a high conductive state (ON-state), with conduction properties similar to the crystalline phase. Once in the ON-state, the heating induced by the increased current, can allow the recrystallization of the integrated phase-change material. The switching phenomenon, is the fundamental property that makes possible the phase transition in a PCM device.

## 1.3 PCM applications and challenges

Nowadays, an exponential growth of code and data is occurring in all electronic systems. The increasing memory density requirement in embedded applications of the non-volatile memory (NVM) market, made the scaling in the last years a great challenge for researchers and industries. The scaling of the Flash technology in fact, requires to overcome some major hurdles like economic limitations, increasing logic platform complexity, introduction and research of new materials (Hi-k) [12]. New memory technologies, to be competitive with Flash technology, must not only meet power needs but must demonstrate the ability to scale down for more technology nodes. In this context, PCM technology supports the promise of scalability beyond that of other memory technologies, with proven scalability down to the 5 nm node. And this is the reason why, with respect to other resistive memory technologies, it is already an industrial reality in the stand-alone market and first embedded prototypes have been presented. The range of applications in which the PCM technology can be used is wide [3]:

- ultra high-performance memory subsystems to achieve solid state drive (SSD) performance and reliability that is unachievable with Flash NAND and at power

consumption levels (and nonvolatility) that cannot be achieved with RAM;

- execution memory in embedded systems, thanks to the bit-alterability;

- wireless systems (read latencies are on the same order of magnitude as the latencies of DRAM);

- computing platforms: PCM banks, with respect to DRAM can be turned off when they are not in use to provide reduced power in idle states. They also offer endurance and write latencies that are compelling for this type of application;

Two challenges remain for this technology, to be a valid Flash replacement: the multi-level capability, and the data retention in high temperature environments, like in automotive applications.

#### 1.3.1 The multi-level PRAM cell

One possible direction to increase the effective memory density (number of bits per unit area) is the so called multi-level cell technology (MLC). It exploits the capability of a memory cell to store analog data in order to encode more than 1 bit of digital data per cell [13]. In PCM technology there are some intrinsic factors that limit this multi-level storing:

- the write noise, that increases with the lifetime and the number of cycles, and depends on fabrication variability, phase-change material stability, etc.;

- the recrystallization of the amorphous phase, seen at room temperature as a "long-term" phenomenon in standard phase-change material;

- the drift of the resistance towards higher values, even immediately after the programming ("short-term" phenomenon);

Among these factors, the drift represents the most important to be overcome to enable MLC. In recent years, because of the intrinsic nature of the phenomenon, different solutions have been proposed at system level [14], showing the capability for the PCM technology of multi level storing, at the expense of the reduced programming speed. The reduction of the resistance drift by the engineering of the phase-change material is another solution and the subject of current active research in the PCM research community.

### 1.3.2 Automotive applications

The problem of the preservation of data and code is not only a prerogative of the consumer market. The increasing number of microelectronic applications in the means of transport raised the demand for memory capability. Automotive applications have different requirements with respect to consumer and industrial applications in terms of reliability:

- from 15 years up to 30 years lifetime (for standard server the requirement is 10 years);

- effective working time  $\sim 10\%$  of standard applications;

- working temperature range from -55 °C up to 150 °C;

- zero defect requirement.

The automotive environment represents a challenging target for PCM technology, first of all because of the high temperature at which programming operations and storage have to be guaranteed. The only possible way to overcome this limit, is the engineering of the integrated phase-change material and we will see in the next chapter, how our work contributed to the research of innovative phase-change materials, in order to make PCM a valid candidate for Flash replacement, even in this challenging market.

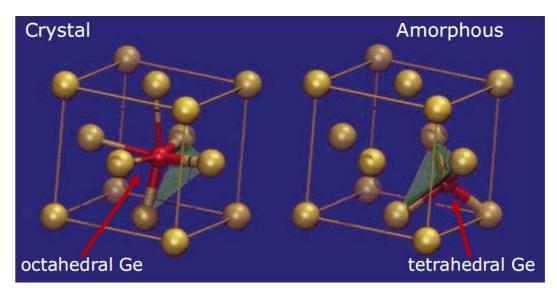

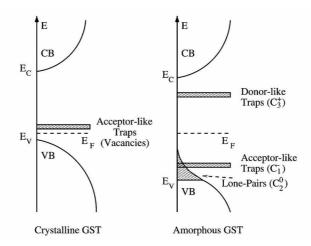

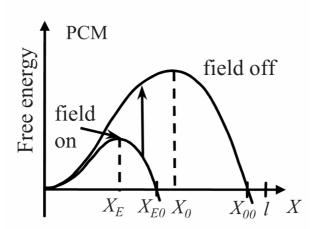

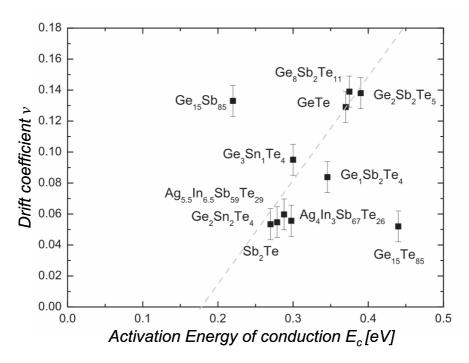

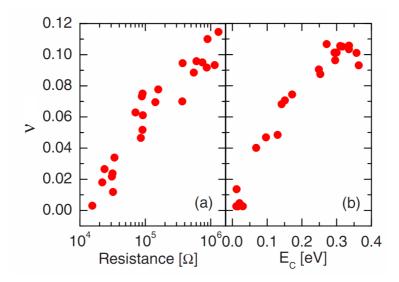

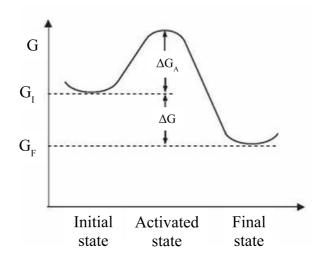

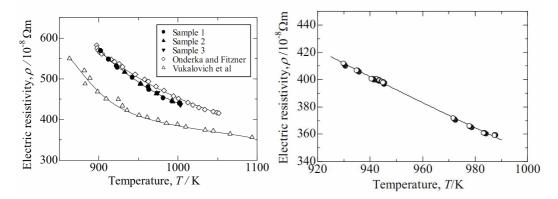

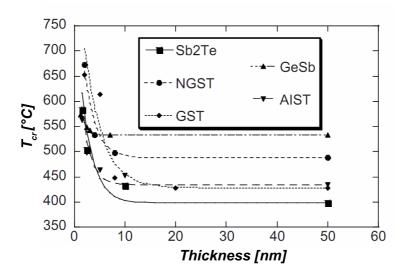

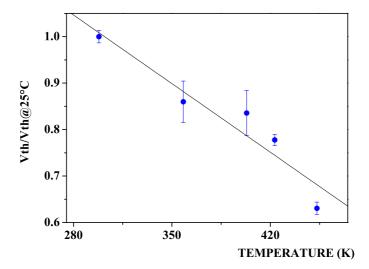

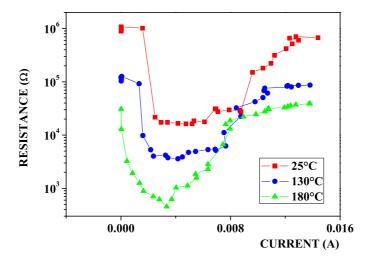

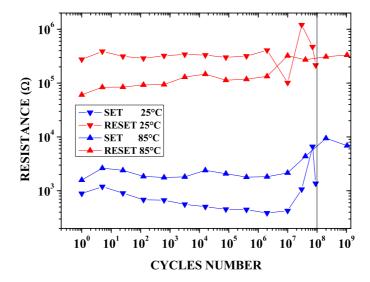

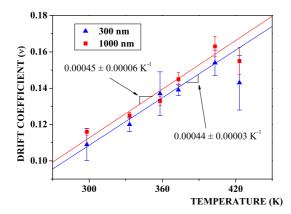

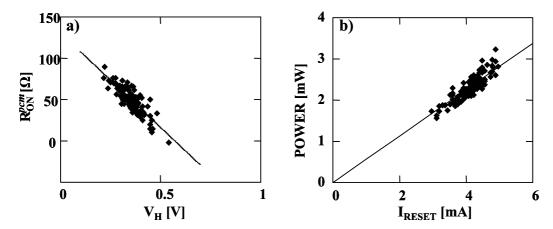

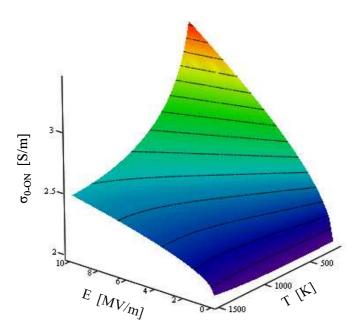

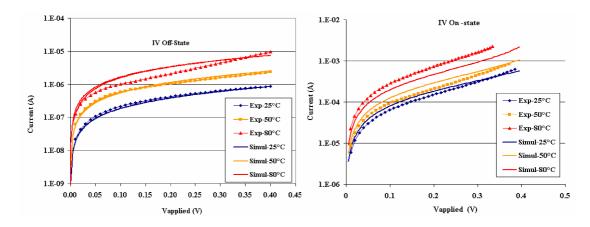

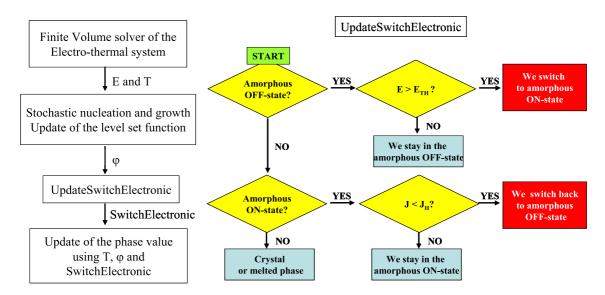

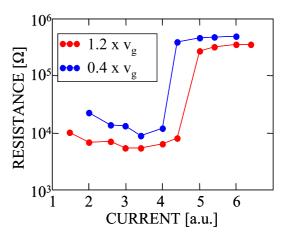

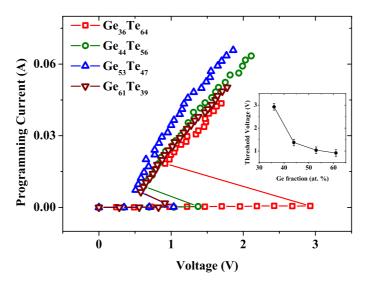

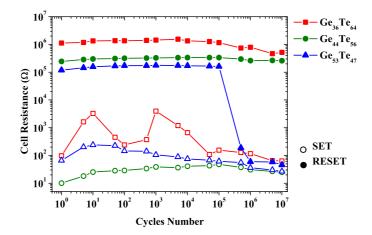

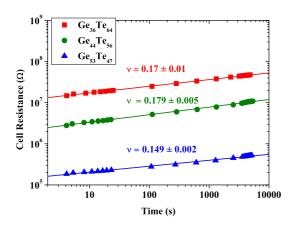

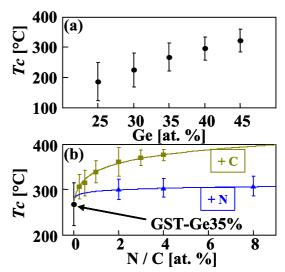

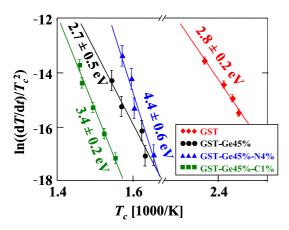

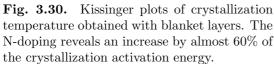

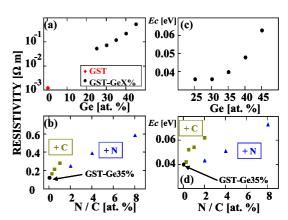

## 1.4 The phase-change materials