## Ultra-Low Power RFIC Solutions for Wireless Sensor Networks

Hassen Kraimia

#### ▶ To cite this version:

Hassen Kraimia. Ultra-Low Power RFIC Solutions for Wireless Sensor Networks. Other [cond-mat.other]. Université Sciences et Technologies - Bordeaux I, 2013. English. NNT: 2013BOR14822. tel-01066815

## HAL Id: tel-01066815 https://theses.hal.science/tel-01066815

Submitted on 22 Sep 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THESIS

with

## University of Bordeaux

Physics Science and Engineering Doctorate School

presented by

#### Hassen KRAIMIA

in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in: Electronics

## Ultra-Low Power RFIC Solutions for Wireless Sensor Networks

Discussing: 10 July 2013

Commission:

Prof. Corinne BERLANDESIEEExaminatorProf. Christian ENZSwiss Federal Institute of Technology in LausanneExaminator

A/Prof. Thierry TARIS

University of Bordeaux

Advisor

Prof. Yann DEVAL

University of Bordeaux

Advisor

Prof. Jean-Baptiste BEGUERET University of Bordeaux

A/Prof. Dominique MORCHE CEA-LETI

to my parents...

to my dear father...

# Contents

| A | bstra | ct                                             |                                                         | 1  |

|---|-------|------------------------------------------------|---------------------------------------------------------|----|

| A | cknov | wledgn                                         | nent                                                    | 3  |

| 1 | Intr  | oducti                                         | ion                                                     | 5  |

|   | 1.1   | System                                         | m Requirements                                          | 6  |

|   | 1.2   | RF Tr                                          | ransceiver Requirements                                 | 8  |

|   |       | 1.2.1                                          | Power Consumption                                       | 8  |

|   |       | 1.2.2                                          | Datarate                                                | 9  |

|   |       | 1.2.3                                          | Range                                                   | 9  |

|   |       | 1.2.4                                          | Sensitivity                                             | 10 |

|   |       | 1.2.5                                          | Turn-On Time                                            | 10 |

|   |       | 1.2.6                                          | Integration/Power Tradeoff                              | 11 |

|   | 1.3   | Challe                                         | enges                                                   | 13 |

|   |       | 1.3.1                                          | Energy Constraints                                      | 13 |

|   |       | 1.3.2                                          | Duty-cycle Control in Sensor Networks                   | 19 |

|   |       | 1.3.3                                          | Low-power Design Strategies                             | 21 |

|   | 1.4   | Thesis                                         | s organization                                          | 26 |

| 2 | Circ  | $\operatorname{cuit}  \mathbf{A}_{\mathtt{J}}$ | pproach                                                 | 27 |

|   | 2.1   | Analog                                         | g Techniques for low power/low supply voltage RF design | 27 |

|   |       | 2.1.1                                          | Circuit Configurations                                  | 28 |

|   |       | 2.1.2                                          | Transistor Biasing                                      | 32 |

|   |       |                                                |                                                         |    |

|   | 2.2  | Ultra-Low Power 2.4 GHz Down Conversion Mixer |                                                                         |     |

|---|------|-----------------------------------------------|-------------------------------------------------------------------------|-----|

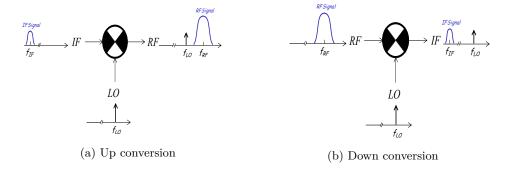

|   |      | 2.2.1                                         | CMOS Mixer Fundamentals                                                 | 39  |

|   |      | 2.2.2                                         | Topology Choice                                                         | 47  |

|   |      | 2.2.3                                         | Circuit Design                                                          | 49  |

|   |      | 2.2.4                                         | Layout and Post-layout Simulations                                      | 51  |

|   | 2.3  | Ultra-l                                       | Low Power 2.4 GHz Self-Oscillating Mixer (SOM)                          | 56  |

|   |      | 2.3.1                                         | CMOS LC Oscillators Background                                          | 56  |

|   |      | 2.3.2                                         | Self-Oscillating Mixer State-of-the-art                                 | 63  |

|   |      | 2.3.3                                         | Circuit Design                                                          | 67  |

|   |      | 2.3.4                                         | Measurement Results                                                     | 77  |

|   | 2.4  | Conclu                                        | asion                                                                   | 84  |

| 3 | Syst | tem A <sub>l</sub>                            | pproach                                                                 | 87  |

|   | 3.1  | Archit                                        | ecture Overview                                                         | 87  |

|   |      | 3.1.1                                         | Passive Detectors                                                       | 88  |

|   |      | 3.1.2                                         | Traditional Architectures                                               | 89  |

|   |      | 3.1.3                                         | Compact Front-ends                                                      | 92  |

|   | 3.2  | Modul                                         | lated Oscillator for envel<br>Ope Detection (MOOD) Architecture $\ \ .$ | 96  |

|   | 3.3  | Circui                                        | t Design                                                                | 105 |

|   |      | 3.3.1                                         | LC Oscillator                                                           | 106 |

|   |      | 3.3.2                                         | Envelope Detector                                                       | 113 |

|   |      | 3.3.3                                         | Baseband Amplifier                                                      | 119 |

|   | 3.4  | Result                                        | s                                                                       | 121 |

|   |      | 3.4.1                                         | Complete System Post-layout Simulations                                 | 121 |

|   |      | 3.4.2                                         | Measurement Results                                                     | 124 |

|   | 3.5  | Conclu                                        | asion                                                                   | 138 |

| 4 | Con  | clusio                                        | ns                                                                      | 139 |

|   | 4.1  | Perfor                                        | mance Summary                                                           | 139 |

|   | 4.2  | Future                                        | e Work                                                                  | 141 |

|   |      |                                               |                                                                         |     |

| - | Ωr | · 4 . | <br>+- |

|---|----|-------|--------|

|   |    |       |        |

Bibliography 150

# List of Figures

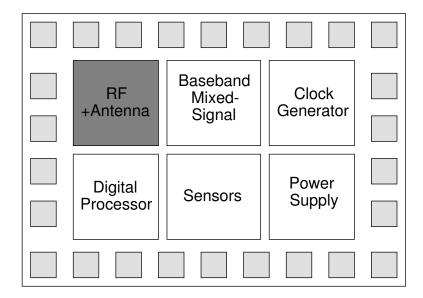

| 1.1  | Hardware blocks for wireless sensor network implementations $\dots \dots$               | 8  |

|------|-----------------------------------------------------------------------------------------|----|

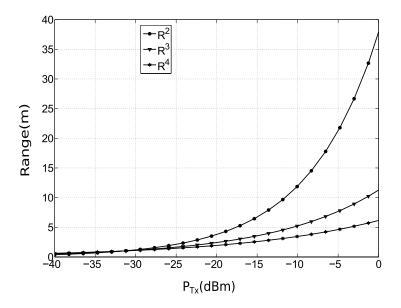

| 1.2  | Radio range for receiver with a $-70\mathrm{dBm}$ sensitivity                           | 11 |

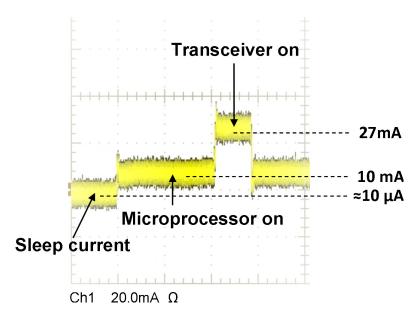

| 1.3  | Three current consumption states in a wireless sensor node $\dots$                      | 15 |

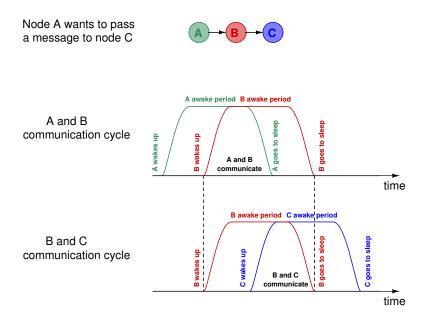

| 1.4  | Synchronizing "awake" period among nodes                                                | 18 |

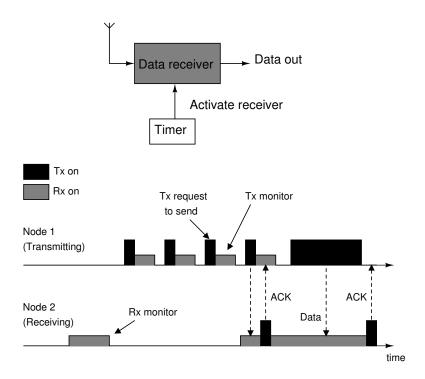

| 1.5  | Protocol-based duty-cycle control: transmitter initiated                                | 20 |

| 1.6  | Duty-cycle control with wake-up receiver                                                | 21 |

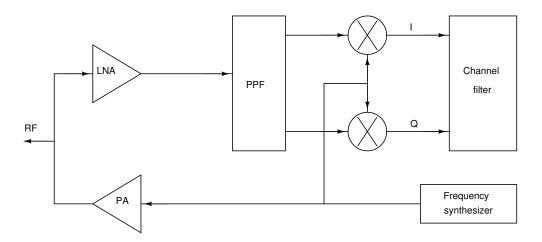

| 1.7  | Direct conversion receiver proposed in $[1]$                                            | 23 |

| 1.8  | Block diagram of the proposed transceiver in $[2]$                                      | 23 |

| 1.9  | Proposed transceiver in [3]                                                             | 24 |

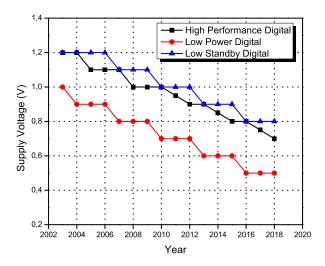

| 2.1  | ITRS projections for CMOS supply voltage scaling                                        | 29 |

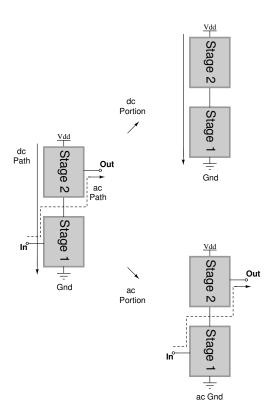

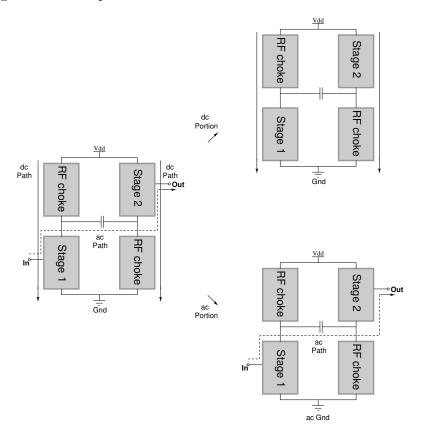

| 2.2  | A conceptual illustration of the cascode architecture                                   | 30 |

| 2.3  | A conceptual illustration of the folded cascode architecture                            | 31 |

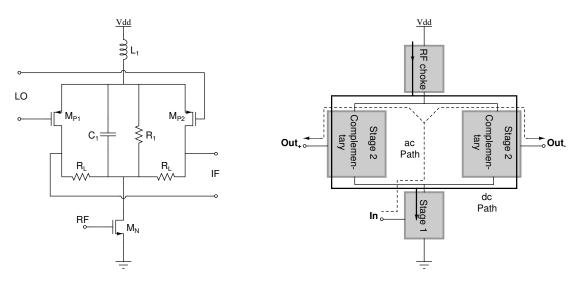

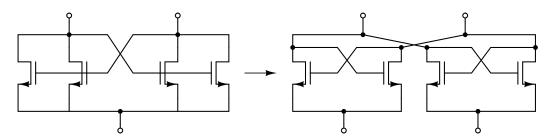

| 2.4  | The complementary current-reused mixer with a current-bleeding technique                | 32 |

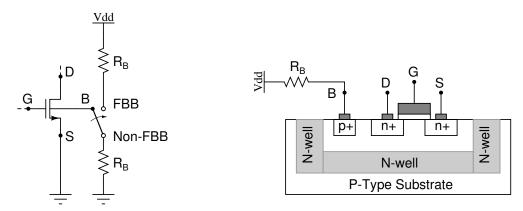

| 2.5  | Forward-body bias technique                                                             | 33 |

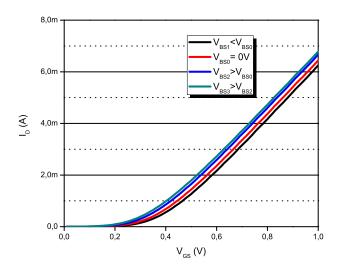

| 2.6  | Transistor drain current for different bulk-source voltages, $130\mathrm{nm}$ CMOS      |    |

|      | process                                                                                 | 34 |

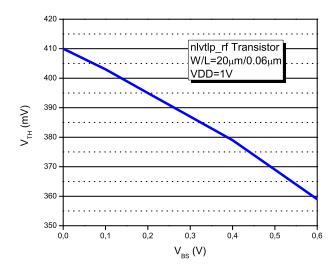

| 2.7  | Threshold voltage versus $V_{BS}$ for NMOS transistor in 65nm process                   | 34 |

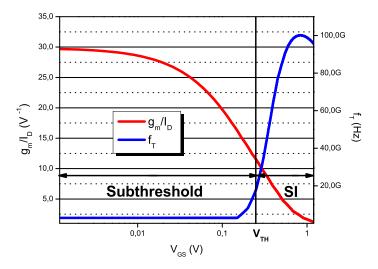

| 2.8  | $g_m/I_D$ and $f_T$ for a modern CMOS 130 nm process                                    | 35 |

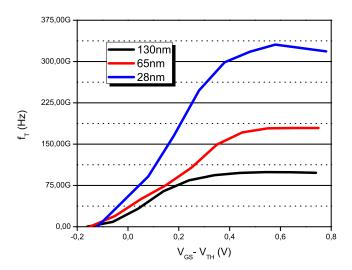

| 2.9  | Comparison of $f_T$ with technology scaling                                             | 36 |

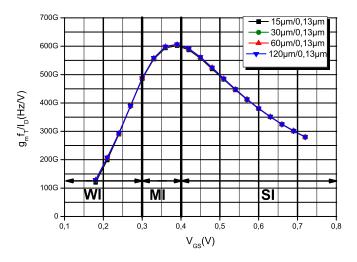

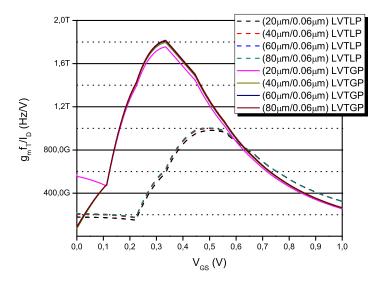

| 2.10 | $g_m f_T/I_D$ for various transistor sizes for a modern CMOS $130\mathrm{nm}$ process . | 37 |

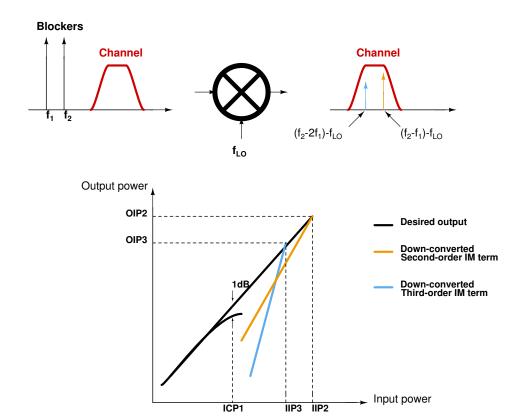

| 2.11 | Mixer principle                                                                         | 39 |

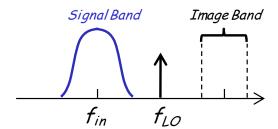

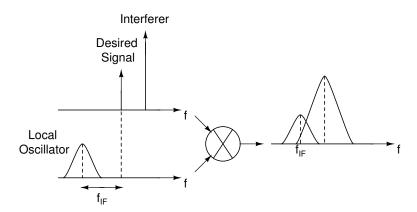

| 2.12 | Image band                                                                           | 41 |

|------|--------------------------------------------------------------------------------------|----|

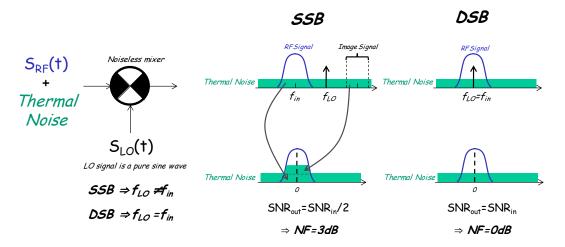

| 2.13 | SSB and DSB noise figure                                                             | 41 |

| 2.14 | Noise folding mechanism                                                              | 42 |

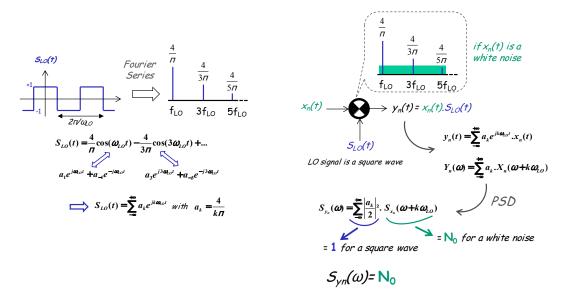

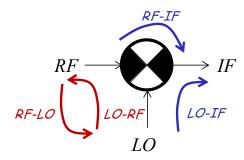

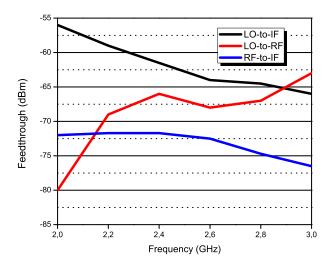

| 2.15 | Different mixer isolations                                                           | 43 |

| 2.16 | Mixer linearity mechanism                                                            | 44 |

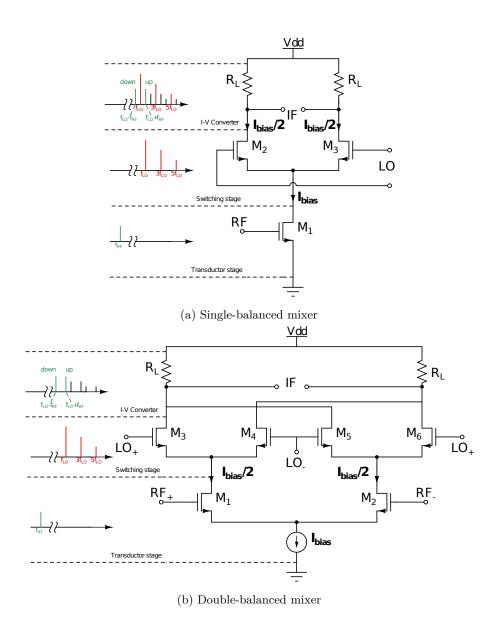

| 2.17 | Single-balanced and double-balanced mixers                                           | 46 |

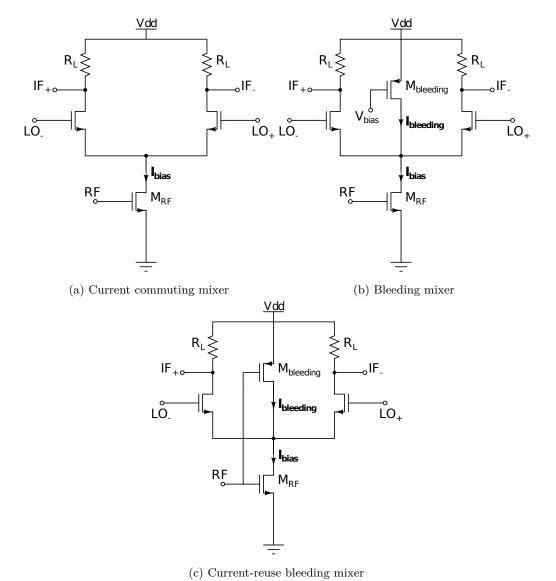

| 2.18 | Various configurations of active mixers                                              | 47 |

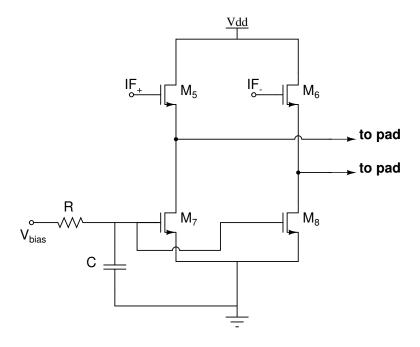

| 2.19 | Circuitry of mixer core                                                              | 49 |

| 2.20 | Schematic of the source followers                                                    | 51 |

| 2.21 | Snapshot of the mixer layout                                                         | 52 |

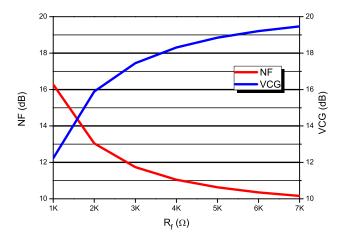

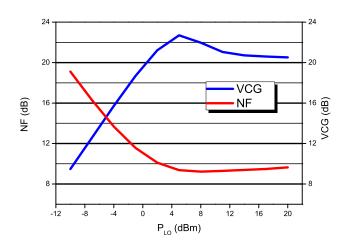

| 2.22 | Simulated voltage conversion gain and SSB noise figure versus $\mathcal{R}_f$ at     |    |

|      | $10\mathrm{MHz}$ IF. LO power is $-1\mathrm{dBm}$                                    | 53 |

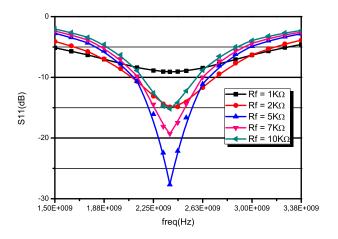

| 2.23 | Input return loss $S_{11}$ for various $R_f$                                         | 54 |

| 2.24 | Simulated voltage conversion gain and SSB noise figure versus $P_{LO}$ at            |    |

|      | $10\mathrm{MHz}$ IF                                                                  | 54 |

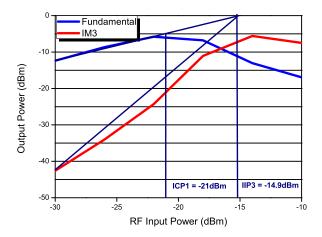

| 2.25 | IIP3 and ICP1 of Mixer at $330\mu\mathrm{W}$ power consumption                       | 55 |

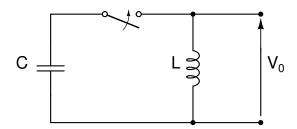

| 2.26 | Ideal inductor capacitor resonator                                                   | 57 |

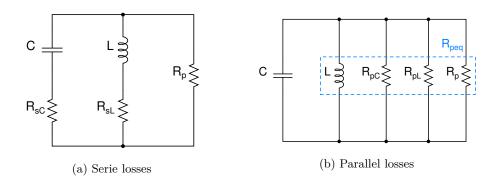

| 2.27 | Tank serie and parallel losses                                                       | 58 |

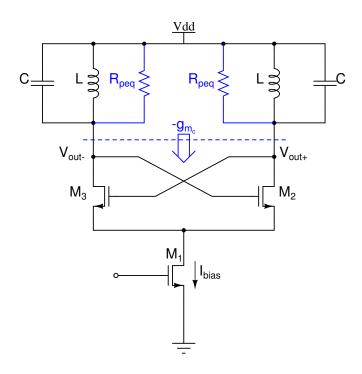

| 2.28 | Circuit schematic of negative resistance LC CMOS Oscillator $\ \ldots \ \ldots$      | 60 |

| 2.29 | Ideal and real oscillator spectrum                                                   | 62 |

| 2.30 | Effect of phase noise in a downconverting system $\dots$                             | 62 |

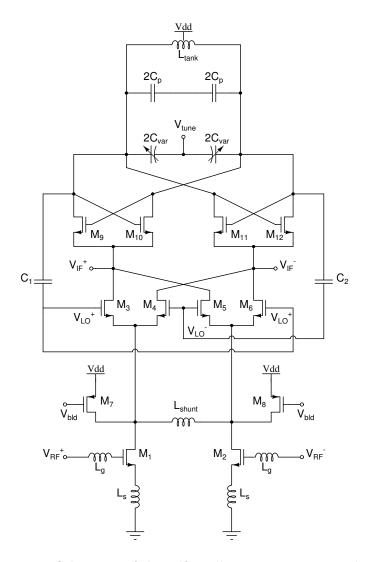

| 2.31 | Schematic of the self-oscillating mixer proposed in $[4]$                            | 64 |

| 2.32 | Low-power oscillator mixer from $[5]$                                                | 65 |

| 2.33 | Low-power oscillator mixer from $[5]$                                                | 66 |

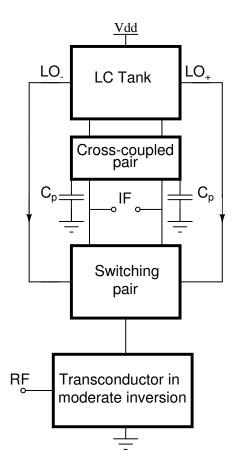

| 2.34 | Block diagram of the proposed self-oscillating mixer $\dots$                         | 67 |

| 2.35 | $g_m f_T/I_D$ versus $V_{GS}$ for LP and GP transistors                              | 68 |

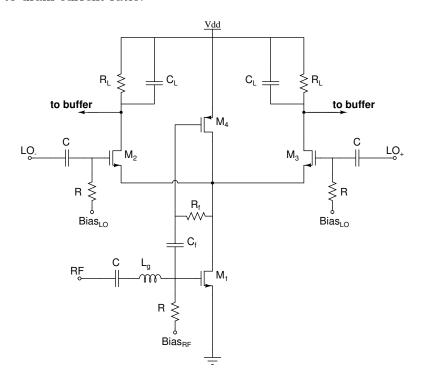

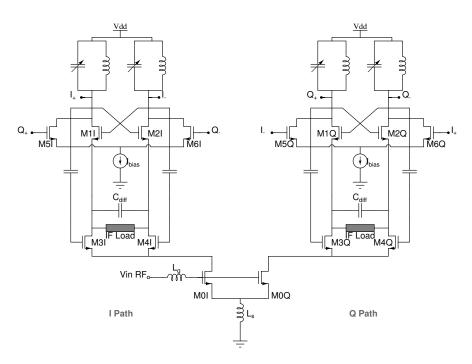

| 2.36 | Schematic of the proposed self-oscillating mixer core                                | 69 |

| 2.37 | Single-ended and differential configurations for cross-coupled pair                  | 70 |

| 2.38 | gm/ $I_D$ for a $(30\mu\text{m}/0.06\mu\text{m})$ nlvtgp transistor in 65 nm process | 71 |

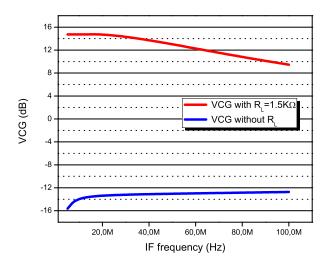

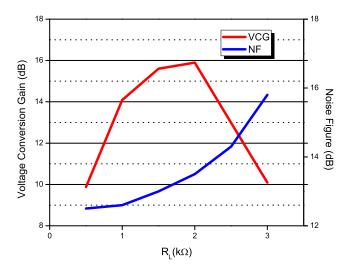

| 2.39 | Voltage conversion gain with and without $R_L$                                  | 72  |

|------|---------------------------------------------------------------------------------|-----|

| 2.40 | Voltage conversion gain and noise figure versus $R_L$                           | 73  |

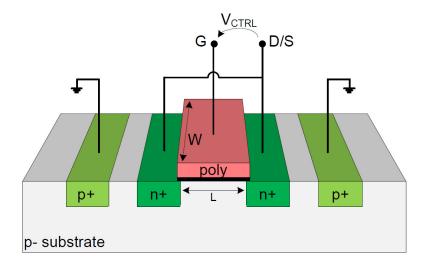

| 2.41 | Cross section of I-MOS varactor                                                 | 74  |

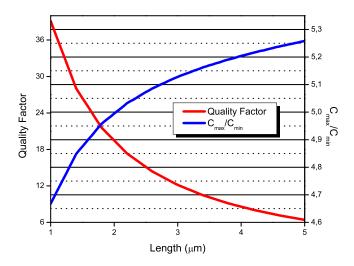

| 2.42 | Varactor quality factor and $C_{max}/C_{min}$ versus transistor length          | 75  |

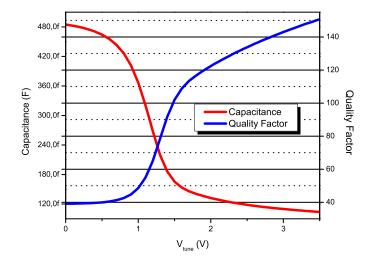

| 2.43 | Varactor quality factor and capacitance versus $V_{tune}$                       | 75  |

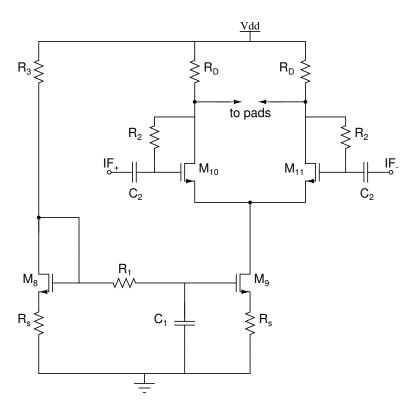

| 2.44 | Schematic of the differential common source buffer $\dots \dots \dots$          | 76  |

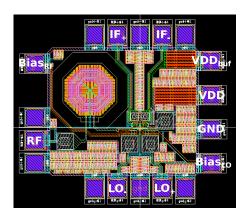

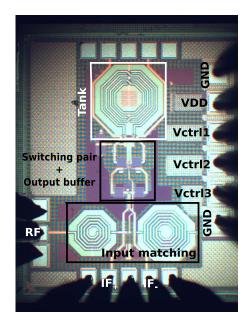

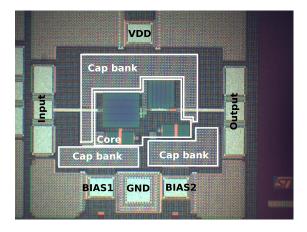

| 2.45 | SOM microphotograph                                                             | 78  |

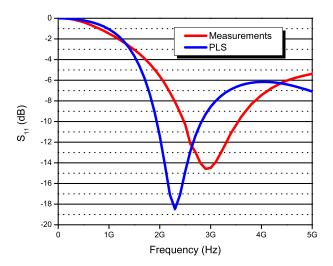

| 2.46 | Input return loss of the self-oscillating mixer                                 | 78  |

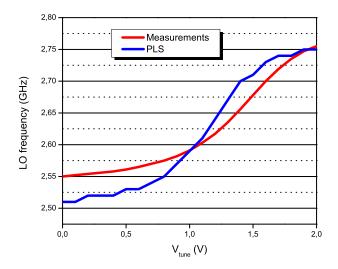

| 2.47 | Tuning range of the SOM $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 79  |

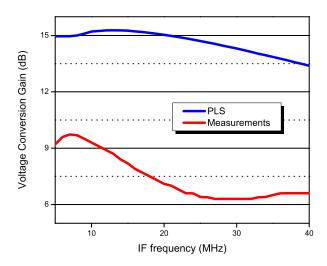

| 2.48 | Voltage conversion gain at different IF frequencies $\dots \dots \dots$ .       | 80  |

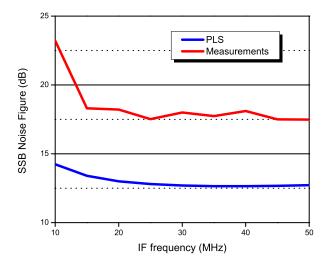

| 2.49 | Single side band noise figure at different IF frequencies                       | 80  |

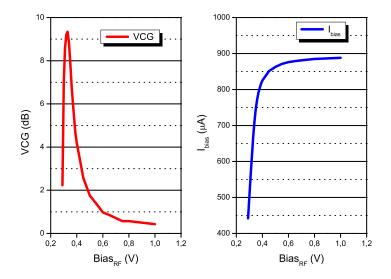

| 2.50 | Voltage conversion gain and $I_{bias}$ versus $Bias_{RF}$                       | 8   |

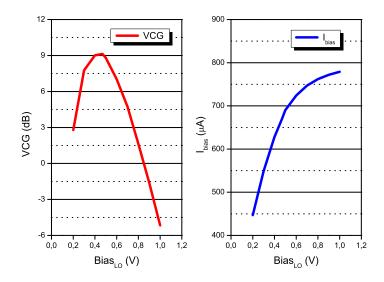

| 2.51 | Voltage conversion gain and $I_{bias}$ versus $Bias_{LO}$                       | 82  |

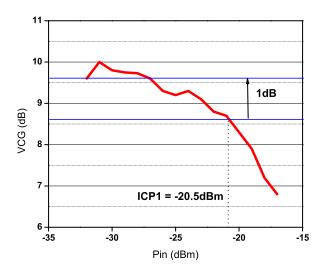

| 2.52 | Measured input compression point ICP1                                           | 83  |

| 2.53 | measured leakages of the SOM at different ports                                 | 83  |

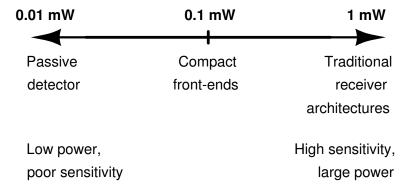

| 3.1  | Receiver design space in terms of power consumption                             | 88  |

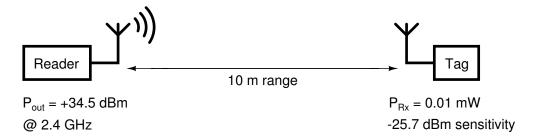

| 3.2  | RFID link operating parameters                                                  | 89  |

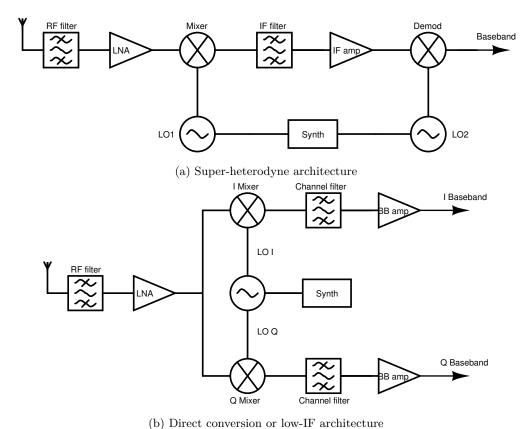

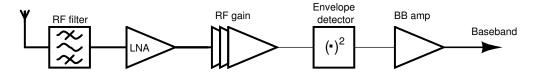

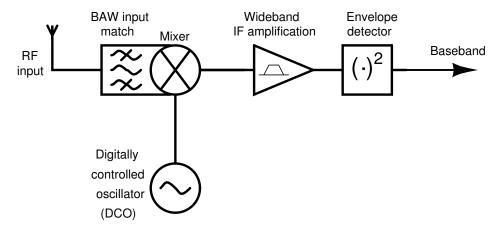

| 3.3  | Traditional receiver architectures                                              | 90  |

| 3.4  | Tuned-RF (TRF) architecture                                                     | 93  |

| 3.5  | "Uncertain-IF" architecture                                                     | 94  |

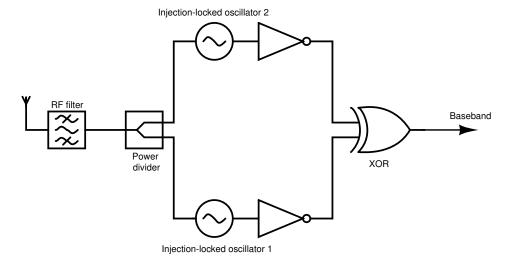

| 3.6  | BPSK demodulator in [6]                                                         | 95  |

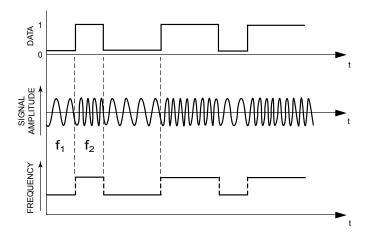

| 3.7  | FSK modulation                                                                  | 97  |

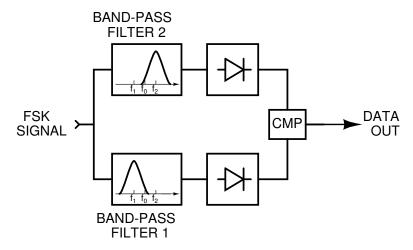

| 3.8  | Non-coherent FSK demodulator                                                    | 97  |

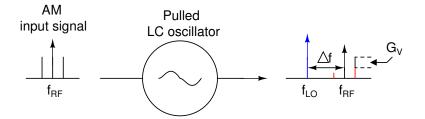

| 3.9  | Proposed FSK demodulator                                                        | 98  |

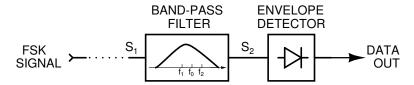

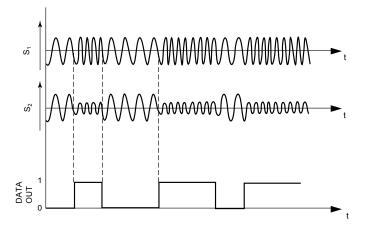

| 3.10 | Time evolution of the received signal with the proposed architecture $$ . $$ .  | 96  |

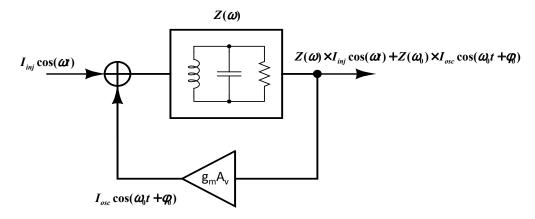

| 3.11 | Simplified behavioral model for injection pulled oscillator                     | 101 |

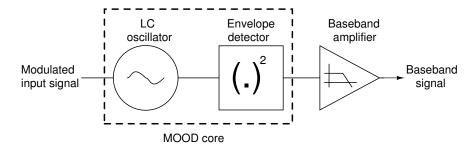

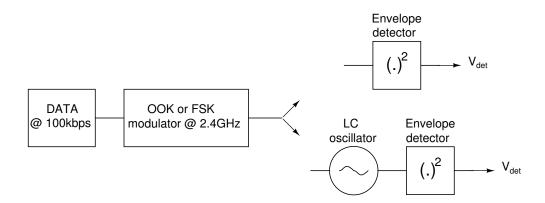

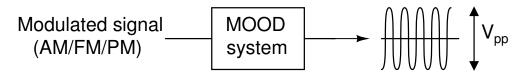

| 3.12 | Block diagram of prototype MOOD system                                          | 105 |

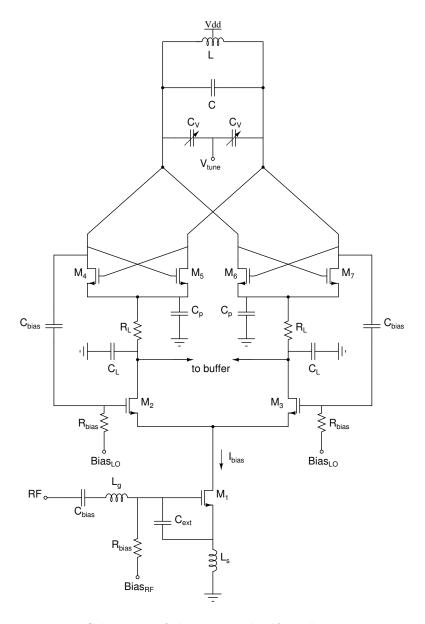

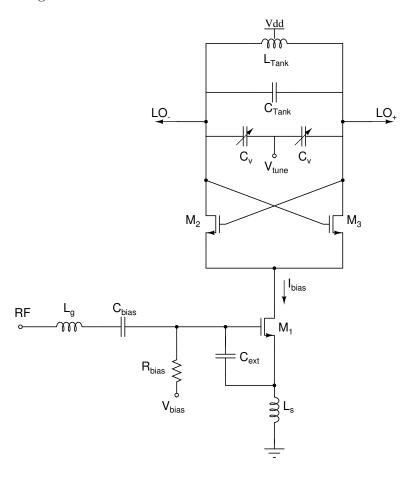

| 3.13 | Schematic of the oscillator core                                                | 107 |

|      |                                                                                 |     |

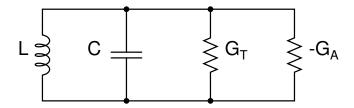

| 3.14 | Simple model of oscillator as resonant tank                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

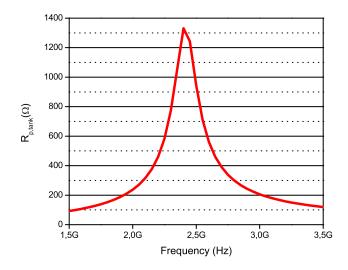

| 3.15 | Tank losses                                                                                                                                                              |

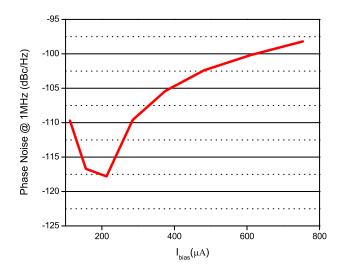

| 3.16 | Phase noise versus bias current $I_{bias}$                                                                                                                               |

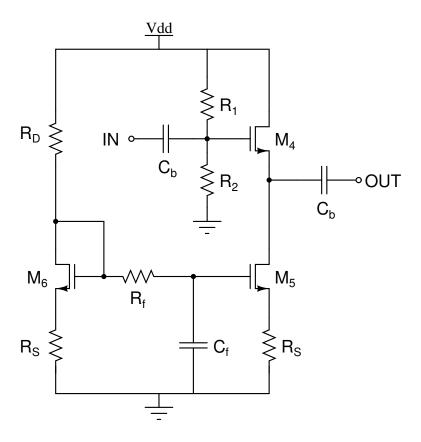

| 3.17 | Schematic of the output buffer                                                                                                                                           |

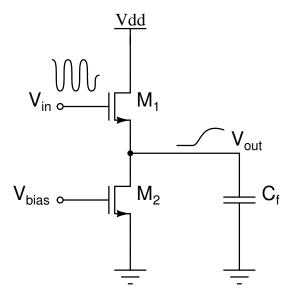

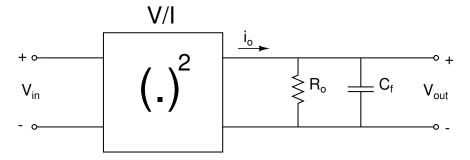

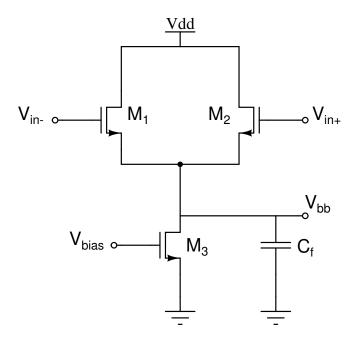

| 3.18 | Schematic of basic envelope detector circuit in CMOS $\dots \dots \dots$ |

| 3.19 | Simple model of envelope detector to calculate conversion gain $\dots \dots 115$                                                                                         |

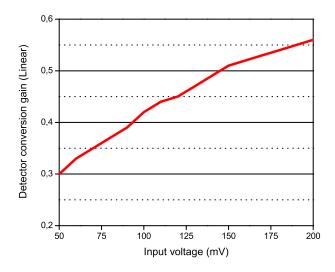

| 3.20 | Simulated conversion gain of the envelope detector $\dots \dots \dots$   |

| 3.21 | Circuitry of the differential envelope detector (Bias not shown) $\ \ldots \ \ldots \ 118$                                                                               |

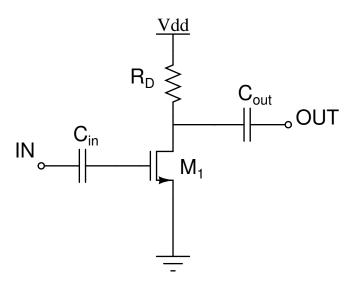

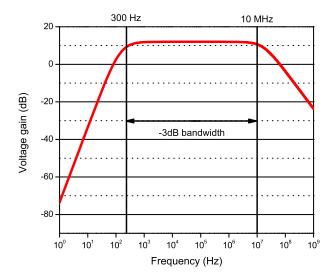

| 3.22 | Schematic of the baseband amplifier (Bias not shown) $\dots \dots \dots$ |

| 3.23 | Simulated baseband amplifier frequency response                                                                                                                          |

| 3.24 | Pulled oscillator's output spectrum in presence of AM signal $\dots \dots 121$                                                                                           |

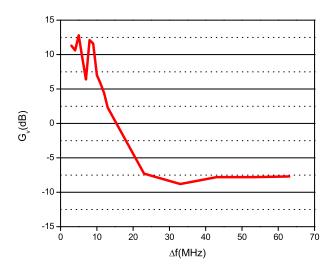

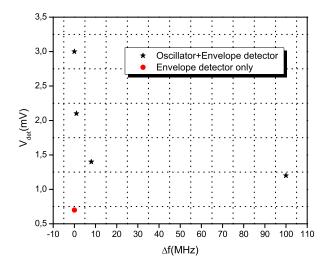

| 3.25 | Oscillator's voltage gain versus $\Delta f$                                                                                                                              |

| 3.26 | Testbench simulation for system validation $\dots \dots \dots$           |

| 3.27 | Envelope detector's output voltage in OOK setup                                                                                                                          |

| 3.28 | Die photo of the envelope detector $\dots \dots \dots$                   |

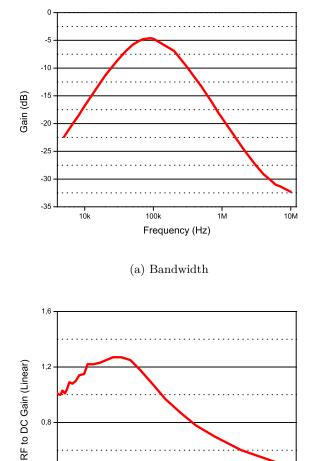

| 3.29 | Measured bandwidth and conversion gain of the envelope detector $$ 126                                                                                                   |

| 3.30 | Die photo of the LC oscillator                                                                                                                                           |

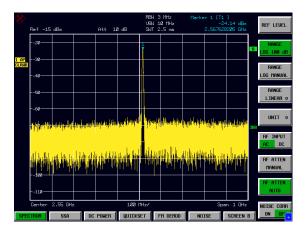

| 3.31 | Measured output spectrum                                                                                                                                                 |

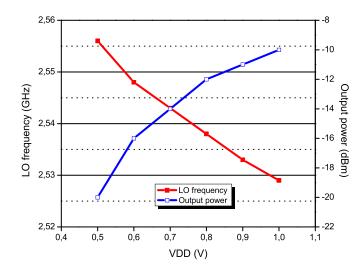

| 3.32 | Measured oscillation frequency and output power for different $V_{DD}$ 128                                                                                               |

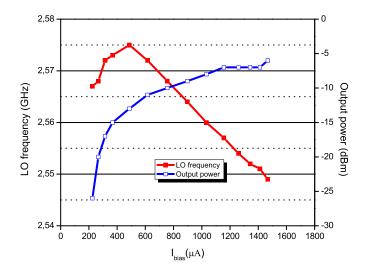

| 3.33 | Variation of oscillation frequency and output power for range of $I_{bias}$ 128                                                                                          |

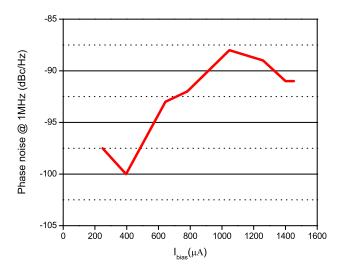

| 3.34 | Oscillator's phase noise for different bias current $\dots \dots \dots$  |

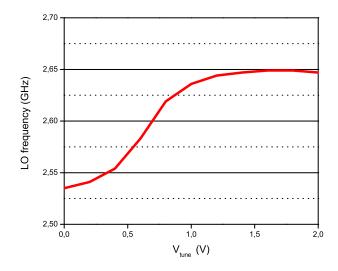

| 3.35 | Tuning range of the oscillator                                                                                                                                           |

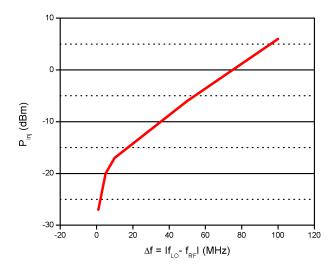

| 3.36 | Output power for different frequencies of a continuous wave 131                                                                                                          |

| 3.37 | Required injection power for different $\Delta f$                                                                                                                        |

| 3.38 | Measurement setup for system validation $\dots \dots \dots$              |

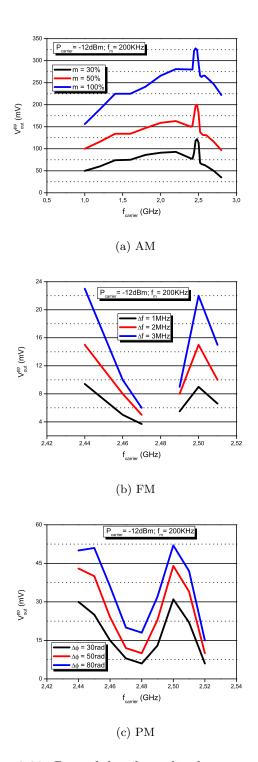

| 3.39 | Demodulated amplitude versus $f_{carrier}$                                                                                                                               |

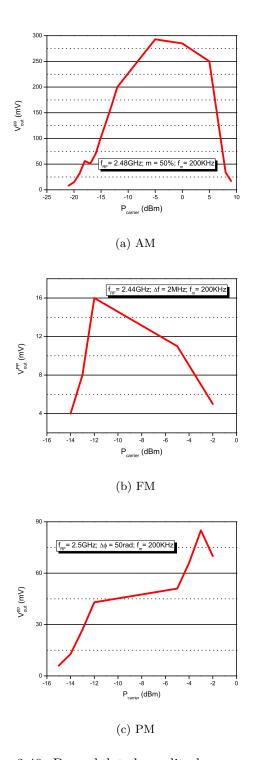

| 3.40 | Demodulated amplitude versus $P_{carrier}$                                                                                                                               |

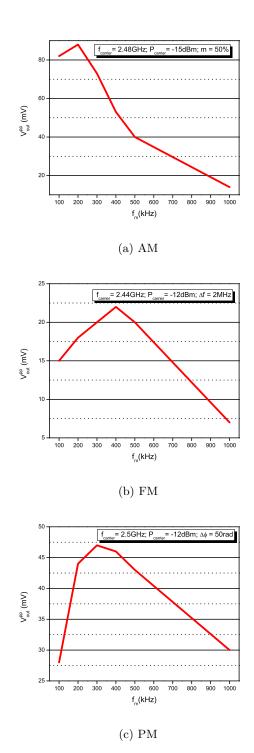

| 3.41 | Demodulated amplitude versus $f_m$                                                                                                                                       |

# List of Tables

| 1.1 | Average power density of various energy storage and scavenging devices [7] | 14  |

|-----|----------------------------------------------------------------------------|-----|

| 2.1 | Operating regions of the MOS transistor                                    | 38  |

| 2.2 | Sizes of mixer devices                                                     | 52  |

| 2.3 | Performance summary and comparison to other CMOS mixers                    | 55  |

| 2.4 | Sizes of SOM devices (core and buffer)                                     | 77  |

| 2.5 | Performance summary and comparison to other SOM                            | 84  |

|     |                                                                            |     |

| 3.1 | Sizes of Oscillator devices (Core and buffer)                              | 113 |

| 3.2 | Sizes of envelope detector devices                                         | 119 |

| 3.3 | Sizes of baseband amplifier devices                                        | 120 |

# Abstract

[EN] Since their emergence, Wireless Sensor Networks (WSN) have been growing continually becoming a key player in many applications such as military tracking, remote monitoring, bio-sensing and home automation. These networks are based on IEEE 802.15.4 standard which is dedicated to low rate wireless personal area networks (LR-WPANs) in the unlicensed radio band (868 MHz/915 MHz/2.4 GHz). Low power consumption, low cost of implementation and high level of integration are the main challenges of these systems. As radio frequency transceiver is one of the most power hungry block in wireless sensor node, power consumption of radio frequency front-end (RFFE) must be reduced. To deal with, several approaches are possible, either at circuit level by investigating operating modes of transistors and merging functionalities or at system level by searching novel demodulating architectures. This thesis explores the specific requirements and challenges for the design of a very-low power 2.4 GHz down conversion mixer operating in moderate inversion region and consuming 330 μW. A second circuit merging the local oscillator and the mixer was designed and implemented in 65 nm CMOS technology. The self-oscillating mixer (SOM) operates at a radio frequency of 2.4 GHz and consumes 600 µW from a 1 V supply. Finally, a compact demodulator implemented in 65 nm CMOS technology was proposed. It uses a novel architecture to demodulate all analog modulations while consuming just 120 µW from a 0.5 V supply and achieving a sensitivity less than  $-30\,\mathrm{dBm}$  in the case of AM modulation.

[FR] Depuis leur apparition, les réseaux de capteurs sans fil (WSN) n'ont cessé de se développer pour devenir un acteur clé dans de nombreuses applications telles que le suivi militaires, la surveillance à distance, la bio-détection ou la domotique. Ces réseaux basés principalement sur la norme IEEE 802.15.4 qui est consacrée aux réseaux sans fil personnels à faible débit et à faible portée (LR-WPAN) dans la bande de fréquences radio sans licence ISM (868 MHz/915 MHz/2.4 GHz). La faible consommation d'énergie, le faible coût de mise en œuvre et le niveau d'intégration élevé sont les principaux défis de ces systèmes. Le module radio est le bloc le plus gourmand en énergie dans un nœud capteur, sa consommation de puissance doit donc être réduite. Pour ce faire, plusieurs approches sont possibles, soit au niveau circuit en exploitant les modes de fonctionnement du transistor ou en fusionnant les fonctionnalités des blocs qui constituent un front-end radiofréquence. Soit au niveau système en examinant de nouvelles architectures de démodulation. Cette thèse explore les exigences et les défis spécifiques pour la réalisation d'un mélangeur à très faible consommation fonctionnant en zone d'inversion modérée et consommant 330 µW. Un second circuit combinant l'oscillateur local et le mélangeur a été conçu et réalisé en technologie CMOS 65 nm. Le "Self-Oscillating Mixer" (SOM) fonctionne à une fréquence radio de 2.4 GHz et consomme 600 µW sous une tension d'alimentation de 1 V. Enfin, un démodulateur compact a été réalisé en technologie CMOS 65 nm. Il utilise une nouvelle architecture pour démoduler toutes les modulations analogiques, cette approche se base sur la théorie de synchronisation des oscillateurs. Le système proposé consomme uniquement 120 µW sous une alimentation de 0.5 V et permet d'atteindre une sensibilité inférieure à  $-30\,\mathrm{dBm}$  dans le cas d'une modulation AM.

# Acknowledgment

The success of this research work would not have been possible without the support and assistance of many other individuals. First, I would like to thank my advisors, Professor Yann Deval and Associate Professor Thierry Taris, for their support and guidance throughout my time in IMS laboratory. Their vision and scientific recommendations have been both inspiring and challenging. I also thank Professor Corinne Berland and Professor Christian Enz for reading this thesis and providing helpful feedback.

I extend my deep gratitude to all members of IC design team for their valuable assistance. I also thank the former team leader Professor Jean-Baptiste Begueret for his constant support and availability.

The IMS laboratory is fortunate to employ a talented and dedicated staff. Special thanks is due to Simone Dang Van, whose tireless efforts to facilitate administrative tasks. Patrick Villesuzanne and Olivier Mazouffre keep the computer systems and tools running smoothly and play an integral role in the successful fabrication of chips.

My co-workers of the last 3 years, have been a constant source of helpful discussion and distractions. Special thanks to Paolo Lucchi, Sophie Drean, Yoann Abiven, Quentin Beraud Sudreau, Adrien Tuffery, Nejdat Demirel with whom I have shared valuable discussions and many cups of coffee.

Many thanks to the German community with which I was connected the last period of the thesis. I have shared interesting discussions, sometimes philosophical, with Mario Weiß. He was always up for practicing sport and going out. I also thank my roommate Janina Reents for positive changes she has brought with her, this was really helpful. Vielen Dank an alle. I cannot forget all the people I met in Bordeaux and with whom I

have shared many things. Thank you Brahim, Sami, Damien, Thalia, Tugdual, Thomas, Henri and Laetitia for supporting me.

Finally, I want to dedicate this modest work to my home country, Tunisia, to all the people who started the revolution at the end of 2010 and who continue to struggle for a better future. Living this event while being far away was really hard. Special thanks to all my friends there for their constant and helpful support.

Last but of course not least, I thank my parents and my family for their permanent support and especially for their sacrifices which has allowed me to continue my studies. I am really grateful to them. I dedicate this thesis to my dear father that I would have loved to share this moment with him but unfortunately life decided otherwise. He taught me how to stay strong in tough times, I love you Dad.

## Chapter 1

# Introduction

In recent years, a trend toward a world in which people will be surrounded by networked devices that are sensitive and adaptive to their needs can be foreseen. This trend has been expressed in a vision called Ambient Intelligence (AmI). It is possible to partition this world into three different classes of devices called "Watt nodes", "milli-Watt nodes" and "micro-Watt nodes" [8]. The "Watt nodes" and the "milli-Watt nodes" demand a further improvement in technology scaling to meet the low-power target. In contrast, the design of a "micro-Watt" node requires meeting the limit of miniaturization, cost reduction and power consumption. Therefore, the complexity of this task is not in the number of transistors but in the capability to optimally combine technologies, circuit and protocol innovation to obtain the utmost simplicity of the wireless node. One implementation of these "micro-Watt nodes" can be achieved through wireless sensor networks (WSN). Since their emergence, they keep on growing up, becoming a key player in most industrial applications. Thanks to their ease of implementation and very low cost, these networks are extensively used in wireless personal or body area networks (WPAN or WBAN) enabling a wide variety of compelling applications. As an example, WSN are used to survey the environment or to monitor energy consumption in residential buildings. The use of WSN enables real-time pricing and adaptive energy usage without user intervention. Several applications require low datarate, very low power consumption and a long lifetime for the battery. In this case the easier management of the wireless nodes has allowed discarding the star-mesh in favor of a more flexible peer-to-peer architecture. Within this evolving scenario, the ZigBee [9] and the other wireless sensor networks standards represent an additional step towards an even more flexible system able to reshape itself dynamically. Due to their nature, these systems do not require any base-station, since they are formed by autonomous shortrange wireless nodes, which monitor and control the environment defining the working area by their spatial distribution. Since the high density of units makes the system more flexible and relaxes the sensitivity of the single receiver, in ZigBee compliant networks the performance is exchanged with the possibility of having long-lasting and cheap devices [2]-[10]. However there is a trade-off between efficiency and cost which settles the density of nodes in a WSN. One of the most critical components making up an efficient sensor node is the wireless transceiver, which transmits and receives data packets in order to provide the communication link between distributed nodes. The goal of this research activity through MIRANDELA project is to comprehensively address the challenges in implementing ultra-low power CMOS RFIC solutions for WSN.

## 1.1 System Requirements

The implementation of wireless sensor networks involve a hardware optimization in order to make dense node deployment possible in practical scenarios, each node must be physically and economically unobtrusive. In order to make these networks a reality, the wireless node should be optimized for three metrics:

• Low cost: The utility of the network depends on high density and ubiquity, which means a large numbers of nodes. In order to make large-scale deployments

economically feasible, nodes must be very low cost.

- Small size: Embedding the components into the existing infrastructure of daily environments (walls, furniture, lighting, etc.) requires a very small form factor of the entire sensor node. Typically, node volumes less than 1 cm<sup>3</sup> (much smaller than a AA battery) are necessary. A very high level of integration is mandatory if such small dimensions are to be achieved.

- Low power: For large networks with many nodes, battery replacement is difficult, expensive, or even impossible. Nodes must be able to function for long periods, ideally up to 10 years, without running out of power.

Each of these three factors are somewhat intertwined. For example, electronic components are already so small that overall module size is limited by power supply or energy storage requirements. For this reason, reducing power consumption of the electronics is an effective way to shrink size as well. Another example is that highly integrated circuits with few external components can simultaneously reduce both size and cost. One of the most compelling reasons to reduce power consumption is to enable the use of new power supply technologies like energy harvesting [11] and low cost printable batteries [12]. These early-stage developing technologies cannot supply much power, so any means of reducing power requirements will hasten the adoption of next-generation power supplies. A successful implementation of wireless sensor networks require improvements in several disciplines: networking, low power RF and digital IC design, MEMS techniques, energy scavenging, and packaging. Figure 1.1 shows the various specialized blocks of a sensor node. In the implementation of extremely small sensor nodes, each of these blocks becomes crucial. However, among all the functions, the wireless communication component is the most power consuming one and the most challenging issue in implementing a wireless node is the integration of ultra-low power RF transceiver. Therefore, the main target of this research is to reduce the energy dedicated to communication in wireless sensor nodes. In order to reach this goal, it is important to understand the needs of RF transceivers in WSN.

Figure 1.1: Hardware blocks for wireless sensor network implementations

## 1.2 RF Transceiver Requirements

This section describes the transceiver requirements [13] that are unique to sensor node communications. It is further demonstrated, the radio requirements are very different from traditional low power transceivers (pager receivers, RFID tags, Bluetooth-specification radios, keyless-entry).

#### 1.2.1 Power Consumption

In the design of prototype sensor nodes, the wireless interface consumes the largest fraction of the power and size budget of the node. While the demands of the sensing and digital processing components cannot be ignored, their duty cycle is typically very low. A combination of advanced sleep, power down, and leakage reduction techniques allows to make their average power dissipation virtually negligible [14]. Thus, the wireless interface for sensor networks is the dominant source of power consumption. Whereas optical communication approaches offer the potential of very low power and small size, line-of-sight and directivity considerations make them less attractive [15].

#### 1.2.2 Datarate

As mentioned, the requirements of a transceiver for wireless sensor networks differ dramatically from a traditional wireless link. Thus, common performance metrics such as energy/bit and bits/s/Hz should be applied with the realization that other factors prevail. For example, a modified metric such as energy/useful-bit is relevant if all sources of power and overhead (for example: synchronization, the impact on energy storage) are included. First we will examine the typical operation mode of the sensor node. An investigation of the traffic patterns and data payloads reveal that the transceiver operation is fundamentally different than a wireless LAN or Bluetooth-specification radio. Data packets in sensor networks tend to be relatively rare and unpredictable events. In most application scenarios, each node in the network sees only a few packets/second. In addition, the packets are relatively short (typically less than 200 bits/packet). This is expected as the payloads normally represent slowly varying and highly correlated environmental data measurements. Combined, this means that the average data rate of a single node rarely exceeds 1 kbit/s.

#### 1.2.3 Range

In this discussion, we will assume that the nodes in the network are placed relatively closely (the average distance between nodes is less than or equal to  $10\,\mathrm{m}$ ). For a given sensitivity, scaling the node to larger ranges would require additional transmit power or increased coding gain (longer transmit times). As the transmitted power increases in low power transmitters, the global transmitter efficiency increases. Thus, in short-distance links, rising the transmitted power is the preferred approach over increased coding gain. As the transmitted power increases, a linear enhance in the link budget is obtained for a sub-linear increase in the transmitter power consumption. Improving the link budget through coding gain would involve linear or super-linear increases in the receive power consumption due to increased packet length and/or higher received bandwidths. Indeed, at transmitted power levels of  $-10\,\mathrm{dBm}$  and below, a majority of the transmit mode power is dissipated in the circuitry and not radiated by the antenna. However, at high

transmit levels (over  $0\,\mathrm{dBm}$ ), the active current draw of the transmitter is high. It is difficult to source high active currents with micro-scale energy scavengers and batteries. Convenient and efficient transmit power levels for sensor node applications are roughly in the range of -10 to  $3\,\mathrm{dBm}$ .

#### 1.2.4 Sensitivity

Figure 1.2 plots the theoretical range for a radio with a  $-70\,\mathrm{dBm}$  sensitivity for various RF propagation models at  $2\,\mathrm{GHz}$ . As shown, the range varies greatly depending on the radio environment. For free space (where the path loss appropriate is  $R^2$ ), a range of  $37\,\mathrm{m}$  is achieved with a  $0\,\mathrm{dBm}$  transmit power. However, in indoor environments, a higher exponent ( $R^3$  or  $R^4$ ) is more suited. In that regime, a transmit power of at least  $0\,\mathrm{dBm}$  is required for a  $10\,\mathrm{m}$  range. To add a margin for deep fading, the receiver sensitivity for a  $0\,\mathrm{dBm}$  transmit signal and a  $10\,\mathrm{m}$  range should be greater than  $-75\,\mathrm{dBm}$ . Thus, for this application, a receiver sensitivity of better than  $-75\,\mathrm{dBm}$  is imposed. Higher sensitivities will allow lower transmitted power levels, subject to the constraints in the previous section.

Figure 1.2: Radio range for receiver with a  $-70 \, dBm$  sensitivity

### 1.2.5 Turn-On Time

In an environment in which the radio is in idle or off mode most of the time, and in which data communications are rare and packets short, it is essential that the radio start up very quickly. For instance, a typical 1 Mbps Bluetooth specification radio with a 500 µs turn-on time would be poorly suited for the transmission of short packets. The on-time to send a 200 bit packet would be only 200 µs. Start-up and acquisition represent an overhead that is larger than the actual payload cost, and could easily dominate the power budget (given that channel acquisition is typically the most power-hungry operation). Thus, fast start-up and acquisition is essential to minimize this overhead. An agile radio architecture that allows for a quick and efficient channel acquisition and synchronization is desirable. Complex wireless transceivers tend to use sophisticated algorithms such as interference cancellation and large constellation modulation schemes to improve bandwidth efficiency. These techniques translate into complex and lengthy synchronization procedures and may require accurate channel estimations. Packets are spaced almost seconds apart, which is beyond the coherence time of the channel. This means that these procedures have to be repeated for every packet, resulting in major overhead unsuitable in a low-power environment. Simple modulation and communication schemes are hence the desirable solution if agility is a prime requirement.

#### 1.2.6 Integration/Power Tradeoff

Achieving the goal of a very low power/low cost RF design is complicated by a well documented power/integration (cost) tradeoff. For example, the use of high performance SiGe processes, while offering the designer high  $f_T$  operation and low bias current levels, eliminates the possibility of integration with low power digital systems. A multi-chip solution would prohibitively increase the cost and area for sensor network applications. Another common strategy for CMOS RF designers trying to reduce power consumption is to use high quality passive surface mount components [16]. This solution also prohibitively increases cost and board area, as each surface mount inductor is larger than the entire transceiver chip. Recently published "fully integrated" transceivers typically refer to a

transceiver that has simply eliminated the need for external ceramic or surface acoustic wave (SAW) filters. They still, however, require an off-chip quartz crystal and various passive components. To meet the cost and form-factor requirements of this application, a truly fully integrated transceiver is mandatory. In addition to increasing the size, off-chip passives add more complexity and cost to the board manufacturing and package design. Furthermore, these macro-fabricated components increase the manufactured performance distributions of the radio by adding completely uncorrelated component variations. One method that can be used to achieve a high level of integration is the use of a relatively high carrier frequency. Currently available simple low power radios, as used in control applications, typically operate at low carrier frequencies between 100 and 800 MHz. A high carrier frequency has the distinct advantage of reducing the required values of the passive components, making integration easier. For example, a 2.53 µH inductance is needed to tune out a 1 pF capacitor in a narrow-band system at 100 MHz, requiring a surface mount inductor. For a 2 GHz carrier frequency, the inductance needed is only 6.33 nH, which can easily be integrated on-chip using interconnect metallization layers. In addition, the critical antenna physical dimensions are linearly related to the carrier frequency. For a given antenna radiation pattern and efficiency, a higher carrier frequency allows a much smaller antenna. A quarter-wavelength monopole antenna at 100 MHz would be 0.75 m long. At 2 GHz, the size shrinks to 37.5 mm, allowing very efficient and inexpensive board-trace antenna. However, the drive to higher carrier frequencies in the interest of high integration is in direct conflict with the need for low power consumption. As the carrier frequency increases, the active devices in the RF signal path must be biased at higher cutoff frequencies, increasing the bias current and decreasing the transconductance-to-current gm/Id ratio. The result is an increased power dissipation at higher carrier frequencies. Thus, an inherent tradeoff exists between integration and power consumption that must be addressed through architectural decisions and the use of new technologies.

## 1.3 Challenges

In order to meet the RF transceiver requirements of wireless sensor networks, several challenges have emerged addressing both physical and protocol layer issues. The energy scavenging problem for example is an important technological key issue in wireless sensor networks. In fact, offering a wireless node the possibility to harvest the energy from his environment is an ideal solution to improve the lifetime of the wireless sensor and to avoid costly battery replacement. However, the power efficiency of these energy scavenging sources is sometimes limited and must be enhanced to provide necessary power to the node. Another attractive challenge is the duty-cycle control of radio communication module. This latter is most of time in idle state and large amount of energy could be saved by choosing a proper duty-cycle control.

#### 1.3.1 Energy Constraints

In order to reduce the implementation cost and to allow a flexible method of deployment, the node's battery lifetime must be enhanced. In fact, in many applications, the maintenance cost considerations render frequent replacement of the energy source deterrent. Thus, the node has to scavenge its energy from the environment. The energy storage capability is limited by the storage medium (battery or capacitor) and the size constraints. Single-time charge could work for applications with life cycles below one year, replacing the energy supply could be constraining for some applications and using energy scavenging is often a necessity. The finite power density of state-of-the-art energy sources is illustrated in Table 1.1 [7].

The average power dissipation of the node is severely constrained by the energy scavenging volume of the node. These sources can be broadly grouped into two categories: energy scavenging sources and energy storage sources. From a volume of  $1\,\mathrm{cm}^3$ , an average continuous output power of  $100\,\mu\mathrm{W}$  could be supplied by one or a combination of these power sources. If a one year lifetime were acceptable, either a lithium battery or fuel cell would suffice. However, micro fuel cell technology is still in the early

Table 1.1: Average power density of various energy storage and scavenging devices [7]

| Power Source          | Power Density $\mu W  \mathrm{cm}^{-3}$ | Lifetime  |

|-----------------------|-----------------------------------------|-----------|

| Lithium Battery       | 100                                     | 1 year    |

| Micro Fuel Cell       | 110                                     | 1 year    |

| Solar Cell            | 10-15000                                | $\propto$ |

| Vibrational Converter | 375                                     | $\propto$ |

| Air Flow              | 380                                     | $\propto$ |

| Temperature Gradients | 50                                      | $\propto$ |

stages of research, and is prohibitively complex and expensive. Another active area of research is the thin-film battery technology, which will yield large benefits for sensor node implementations. For desired node lifetimes greater than one year, however, 1 cm<sup>3</sup> does not provide ample storage for the node's 3110 J/year energy requirements. Typical node deployment scenarios would demand a 10 years lifetime (31 kJ). This is a prohibitively large amount of energy to store in a 1 cm<sup>3</sup> volume, requiring the harvesting of energy from the environment. Solar power is a proven and universal method of collecting ambient energy. For outdoor or high-light conditions, this is the obvious solution. However, in dim lighting conditions, the power output drops dramatically. In these environments, an additional energy source is needed. Vibrational converters, air flow generators, and temperature gradient generators all produce 50-400 µW cm<sup>-3</sup>, as listed in Table 1.1. Of the three, vibrational converters are the simplest and they have the most potential for wafer-scale fabrication. In conclusion, a 1 cm<sup>3</sup> sensor node can support an average power draw of 100 µW. A combination of solar or vibrational energy scavenging and battery energy storage is likely to yield the most robust and inexpensive solution. In addition to limitations on average power dissipation, the available peak current levels that can be supplied to the electronics are also limited. In fact, the current consumption form is an important metric in wireless sensor networks and it is not surprising that wireless

sensor communication components score well on power consumption and utilization of wake-up/sleep modes for duty cycling. However, power consumption is only part of the solution. Four other factors must also be addressed in order to achieve low power in wireless sensor applications [17]. These are peak current, graceful power failure, low-power mesh routing and sleep current.

#### Peak current

The plot in Figure 1.3 [17] depicts the current consumption in three typical wireless sensor node states for a commonly used wireless sensor platform. In state one, the microprocessor and transceiver are in sleep mode ( $10\,\mu\text{A}$ ). In state two, the microprocessor is switched on while the transceiver is asleep ( $10\,\text{mA}$ ). In state three, both the transceiver and the microprocessor are awake ( $27\,\text{mA}$ ). These current draws can be sustained with

Figure 1.3: Three current consumption states in a wireless sensor node

high-power batteries such as alkaline cells, but they typically exceed the tight energy budgets available with small batteries or energy harvested sources. These energy sources share an important feature; they have a hard time generating the peak current needed to awaken the electronics, even if they can cope with the average current consumption throughout the wake-up/sleep cycles. A coin cell battery, for example, has a typical maximum output power of 15 milliamps, far below the peak value that most wireless communication systems require. In addition, since most microscale energy scavenging and storage devices provide a naturally high impedance, the peak current drive capability is small (less than a few mA). Providing high drive current would require excessively large storage capacitors and complex voltage regulators. The RF datalink circuit design must address this issue by presenting a low peak active current draw.

#### Graceful power failure

When an energy source has dried out, the electronics cannot communicate and are dead. This unexpected situation can arise and must be taken into account, either as a normal event, solar cell at midnight as instance or as an exceptional condition (depleted battery). In both case, the power problem is expected to be forecasted before the energy source has completely dried out. During this last breath, the device should perform a number of actions to inform its environment of the situation, transmit some critical data and put itself in a state that allows fast recovery when the power is restored. To accommodate failing low-power energy sources such as batteries and solar cells, devices must employ a technique known as "graceful power failure". During normal operation, the devices carefully monitor the state of the power circuits. As they encounter declining power levels, they raise different levels of alarms ranging from early warning to near-death. The alarms are escalated and communicated to other parts of the system, thereby enabling the system to be placed in a state consistent with the alarm condition.

#### Low-power mesh routing

One of the most important differences between wireless sensor communication technology and other well-known wireless technologies is the ability of sensor nodes to forward messages from another one located further down in the communication chain. This technique, known as mesh routing or multi-hop networking, provides an effective and reliable means of spanning large infrastructures, beyond the range of what a single

wireless link can do. However, to forward a message received from a neighboring node, the concerned node needs to be in an awake and receiving mode when the original wireless message arrives. Unfortunately, the receiving mode requires so much power that it can drain batteries in a matter of a few days. The most straightforward solution, as specified by most industry standards, is to limit the multi-hop capability to the nodes that are permanently connected to the main power. In such a framework, low-power devices, which are assumed to be in a power-down mode most of the time, are not capable of retransmitting messages from other devices. These low-power devices, known as end-devices, are located at the end or beginning of the communication chain. This framework, which combines mains-powered mesh routing devices and low-power enddevices, works for some applications. Take, for example, an office lighting application utilizing interconnected wireless luminaires and light switches. The luminaires, which are connected to the main power source, house the mesh routing communication nodes. The switches, which are not mains powered, are a natural place for the end-devices. Many other applications do not fit well in such a framework. Think of gas detection, fire detection, access control, precision farming, battlefield monitoring, perimeter surveillance and warehouse temperature monitoring. In these applications, mains power is not readily available or even present. Running a power cable in these applications would be cost prohibitive, offsetting the benefit of wireless communication. To address this class of applications, which has been found to be more prevalent than mains-powered, multi-hop applications require a totally different framework. In this framework, known as low-power multi-hop networking or low-power routing, all of the nodes, including the mesh routing nodes, operate in low-power mode. The key to this approach, referred in the literature as "synchronized wake-up", is to coordinate receiving activity in a way that eliminates the need for the mesh routing nodes to continually operate in receive mode, thereby significantly reducing power consumption. Figure 1.4 depicts how low-power routing works when Node A wants to send a message to Node C, through Node B. All nodes in the picture are low-power nodes, sleeping most of the time. The breakthrough lies in synchronizing the sleep/wake-up cycles of the nodes to each other. Nodes wake up when

Figure 1.4: Synchronizing "awake" period among nodes

they expect a message from a neighboring node. This enables the routing nodes to operate in a nearly powerless sleeping state most of the time, thereby achieving ultra-low-power operation. Clearly, more wake-ups will occur than strictly required to carry the data, as neighboring nodes will not always have data to transmit. However, the additional power required for periodic wake-ups and synchronizations is more than offset by the power saved by eliminating the need for continuous receive mode operation.

#### sleep current

Wireless chips are usually specified according to their power consumption in receive and transmit mode. Remember, however, that in order to achieve low power, the devices must be duty cycled, moving between alternate sleep and awake states. The longer the required battery life, the longer the device sleeps between wake-up periods. Unfortunately, electronic circuits never really "sleep". Although the powered-down circuits don't yield anything meaningful from a functional standpoint, a small leakage current flows through the transistors. This leakage can amount to several tens of microamps. Sleep current is not usually considered as an important design factor, but it becomes extremely important

when designing a circuit that must live for five years or more on a battery, sleeping most of its life. If the design is not optimized for low leakage current, the majority of the power will be spent on sleeping.

#### 1.3.2 Duty-cycle Control in Sensor Networks

Several methods can be used to address the duty-cycle control issue. Most of them can be described as protocol-based. In synchronous networks, a global reference clock is maintained on each node throughout the network. With a global clock, the protocol can assign communication timeslots to each node. The drawback of this solution is that it may be difficult to maintain and distribute the clock in an ad-hoc network where nodes may be joining and leaving the network. In addition, the energy used to distribute and maintain synchronization can be significant. Another type of protocol-based duty-cycle control, which avoids a global time reference, is pseudo-asynchronous "rendezvous". Depending on the protocol, communication may be initiated by either the transmitting node or the receiving one [18]. Figure 1.5 shows an example of a transmitter-initiated protocol. A timer is used to activate the receiver periodically in order to monitor the channel for communication. If no signal is received, the node returns to sleep mode. When the transmitting node wants to initiate communication it repeatedly sends requests, or beacons, until the receiver wakes up and hears the request, at this time data can be exchanged. Although this method avoids the need for time synchronization between the two nodes, significant energy may be expended both by the receiver (monitoring) and the transmitter (beaconing). More importantly, there is an inherent trade-off between average power consumption and network latency. In order to reduce latency, the protocol must be adjusted for the receiving node to monitor the channel more often, increasing duty-cycle and average power. An alternative to protocol-based duty-cycle control is based on asynchronous wake-up. This method adds an auxiliary receiver called a wake-up receiver (WuRx) to each node. Its only job is to continuously monitor the channel for communication requests or wake-up signals. As shown in Figure 1.6, the WuRx now effectively controls the duty-cycle based on actual communication requests, taking the

Figure 1.5: Protocol-based duty-cycle control: transmitter initiated

place of the timer used in protocol-based methods. The use of a wake-up receiver breaks the trade-off between latency and average power consumption described earlier. The WuRx can respond immediately to requests and so latency is effectively eliminated. The energy that was previously dedicated to repeated beaconing on the transmit side and periodic monitoring on the receive side is replaced by the power consumption of the WuRx. Because of the continuously monitoring of the channel by the WuRx, its active power consumption must be very low. Duty-cycle control based on asynchronous wake-up is an attractive alternative to protocol-based methods for many network scenarios, particularly those with low latency requirements. However, very few published wake-up receiver implementations exist in the literature. In [19], the authors extend the battery life of a personal digital assistant (PDA) by activating it only when an incoming request is received. An IEEE 802.11b wireless LAN transceiver is used for data communications in this prototype, while the wake-up receiver is implemented with a commercial off-the-shelf receiver module consuming about 7 mW in receive mode.

Figure 1.6: Duty-cycle control with wake-up receiver

#### 1.3.3 Low-power Design Strategies

Battery life-time is an important performance metric for many wireless networks. In WSN applications for example, there is a growing need to extend the life-time of the network and, as discussed before, energy scavenging techniques and duty-cycle control help to reach this goal. However, this is one part of the solution and a deep investigation on radio communication module (cf. section 1.1) of sensor nodes is mandatory to see where we can attack the power consumption problem. A proper architectural choice is crucial to obtain good levels of performance, costs and power dissipation. Nevertheless, it is only the first step towards the design optimization, which can be reached only by proper choices down to transistor level. Within communication module's blocks, radio-frequency ones are the most promising for power and area saving since they are more expensive and

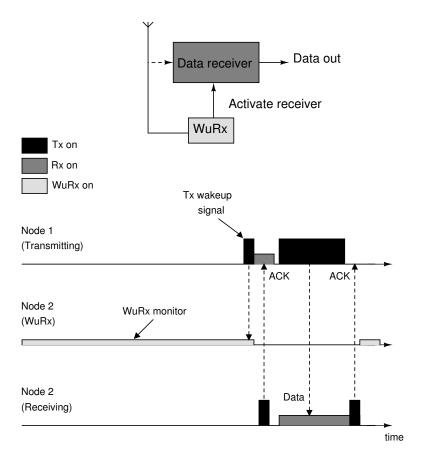

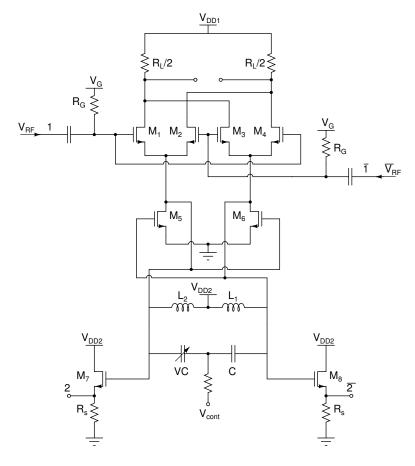

power-hungry than low-frequency parts. Therefore, much effort in optimization process is paid to RF blocks. In this section several design approaches are discussed, in order to find the most effective area and power minimizing strategies proposed in the litterature. To illustrate this purpose some selected examples from the state-of-the-art are reported and described in this section. The proposed architectures specifically highlight the tradeoff between silicon saving and the optimization of power consumption. Figure 1.7 shows a direct conversion receiver architecture proposed in [1]. Since the frequency synthesizer is the most power-hungry block in a receiver front-end, reducing its power consumption results in a large saving on the whole receiver power dissipation. Therefore, the proposed solution reduces the working frequency to save power. In a conventional direct conversion

Figure 1.7: Direct conversion receiver proposed in [1]

receiver, the RF input signal and LO frequencies are equal, which allows the translation of the input to DC. In this architecture, the generated LO frequency is halved respect to the RF signal; the frequency synthesizer is then processed by a frequency multiplier to generate the desired RF frequency for direct conversion. Thus, both voltage controlled

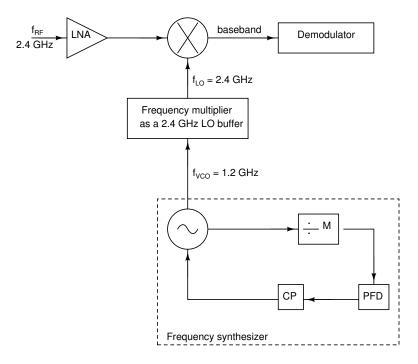

oscillator (VCO) and the frequency divider work at 1.2 GHz instead of 2.4 GHz, resulting in power saving. This is obtained at the cost of a phase noise worsening, which is anyway maintained in an acceptable range for the application. Power reduction is also obtained thanks to the buffering effect of the frequency multiplier avoiding the need to introduce power-hungry buffers. In this solution, the power optimization is obtained by increasing costs, since two integrated coils are required to generate the desired LO frequency. Another way to minimize power consumption is to reduce both, bias current and voltage supply. The approach proposed in [2] focuses mainly on voltage supply minimization. The architecture reported in Figure 1.8 is based on a passive and differential front-end in order to increase the available voltage swing and to have a good noise figure (NF) and linearity at minimum power. In order to reduce the number of inductors and therefore

Figure 1.8: Block diagram of the proposed transceiver in [2]

the silicon area, the antenna matching network is shared between the transmitter and the receiver. This network, which introduces a passive gain, replaces the traditional LNA, resulting in power saving. Quadrature generation is provided by a back-gate quadrature VCO. This technique reduces power consumption in comparison with the conventional cross-coupling quadrature generation [20]. In transmit mode, the PA and mixer are driven from the high quality factor LC tank of the VCO without buffering and the whole differential VCO output swing is amplified. This design choice helps to reduce power consumption and to improve performances. Avoiding quadrature generation at LO path

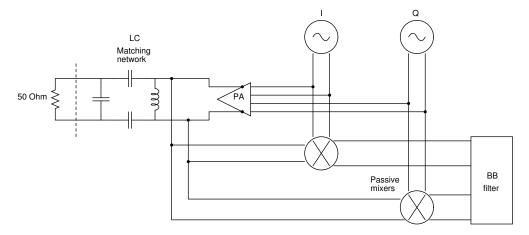

is an efficient approach to reduce at the same time power dissipation and cost. Exploiting this design technique, [3] proposes a low-IF architecture with direct VCO modulation transmitter. The block diagram of the transceiver is depicted in Figure 1.9. The proposed

Figure 1.9: Proposed transceiver in [3]

architecture utilizes a single oscillator signal and generates the quadrature signals in RF path, where the low-noise amplified signal is split into I and Q components using a passive 2 stage poly-phase-filter (PPF). The down-conversion mixer can be implemented as a passive switching device, lowering not only the power consumption but also the flicker noise in comparison with a Gilbert cell. Thus, the only power consuming element of the receiver front-end is the LNA, which has also to compensate losses introduced by the poly-phase-filter and mixer. The proposed LNA is composed by two stacked stages, sharing the bias current and boosting the gain. Concerning the transmitter, the VCO frequency modulation is performed within the loop. This allows to amplify the modulated signal without any mixing and low-pass filtering needed, which helps to reduce power consumption. In addition, the constant envelope frequency modulation allows to maximize the PA efficiency. In this design strategy, power minimization is reached by using a single VCO and generation quandrature in the RF path. This choice requires a careful design of the LNA, where power consumption can be minimized exploiting the bias sharing technique. In conclusion, even if the power and area minimization require

a careful choice of the transceiver architecture, they can be reached only by combining this choice with proper design strategies. As shown in the state of the art overview, cost minimization requires to reduce the number of integrated coils and external components. This can be obtained by e.g. sharing the matching network and the oscillator between the transmitter and the receiver. Nevertheless, the most promising solution to save power consumption seems to be bias and device sharing. A careful choice of the operating region for transistors is necessary in order to capture both RF performances and current efficiency [21]. Another promising approach to further reduce power consumption is to merge functionalities in RF building blocks [22]. This attractive way helps to maximize the power saving while maintaining a good flexibility, which can be exploited to optimize the design and reach a good trade-off between power dissipation and system performances. Since the RF transceiver requirements in WSN are quite relaxed in comparison with other wireless networks, they can be satisfied by designing mere circuits and systems. The need for complex architectures, to demodulate the RF signal, is no longer necessary and new topologies could be imagined to directly extract the useful information. One can imagine the early times of radio receivers with envelope detection module to demodulate AM signals. These systems could be implemented in wireless sensor networks thanks to their simplicity. This approach will be further detailed and discussed in chapter 3.

# 1.4 Thesis organization

This chapter proposes a brief on wireless sensor networks backgrounds. Requirements on system and radio-frequency transceivers are presented with a special focus on power consumption of radio communication module. Challenges related to energy constraints and duty-cycle control in sensor networks are discussed. The main goal of this research is to present solutions at circuit and system levels which help the design and implementation of an ultra-low power receiver for WSN. Chapter 2 introduces some design methodologies dedicated to reduce the power consumption at building block level. Two circuits a mixer and a mixer-VCO, namely Self-Oscillating Mixer (SOM), are presented to illustrate the techniques. Chapter 3 describes the design and implementation of a receiver demodulator

using a novel architecture to extract useful information from a RF signal. This system level solution is compatible with basic modulation schemes namely phase modulation, frequency modulation and amplitude modulation. Finally, Chapter 4 concludes with a brief summary of results and discussion of future research directions.

# Chapter 2

# Circuit Approach

This chapter introduces design methodologies to reduce power consumption in RF circuits. First, techniques to reduce power consumption are discussed. Since they do not correspond all the time to low voltage operation, approaches for lowering supply voltage are also proposed. In order to implement these techniques, a mixer and a self-oscillating mixer were carried out in a 130 nm and 65 nm CMOS process respectively.

# 2.1 Analog Techniques for low power/low supply voltage RF design

Standard CMOS technology has become prevalent in analog and RF circuit design mainly due to the low production cost and potential for integration with accompanying digital circuits. As outlined in chapter 1, cost and integration are two essential considerations in the design of circuits for wireless sensor networks. Thus, scaled sub-micron CMOS technology is a natural choice for implementation of these circuits. In addition, deep sub-micron CMOS opens up new frontiers in low voltage and current circuit design. In this section, design techniques are outlined to fully explore the advantages of modern CMOS devices and achieve minimal power consumption for RF circuits.

## 2.1.1 Circuit Configurations

Although CMOS scaling has been extremely beneficial for digital circuits, analog circuits have often been hindered by these advances. One of the most difficult problems is the constantly diminishing supply voltage for modern CMOS processes, causing reduced voltage headroom and dynamic range for analog and RF applications. Figure 2.1 shows projected trends in CMOS supply voltage scaling over the next 6 years, as predicted by the International Technology Roadmap for Semiconductors (ITRS) [23]. Scaling trends are shown for three different digital technology targets. The low power operation digital roadmap is the most aggressive, since supply voltage scaling is one of the main strategies for reducing power consumption in digital circuits [24]. Trends for high performance and low standby power designs lag by several generations, but are also expected to experience supply voltage scaling below 1 V in the next six years. These digital roadmaps are an important indicator for the state of future analog designs because digital performance drives technology scaling. In order to reap the cost benefits of integration, analog and RF designs must conform to the specifications of digital technologies. One common strategy for dealing with reduced voltage in analog designs is to use special analog process options or high voltage I/O devices for the analog portions of the design. Though effective, this solution raises cost and increases power usage of the analog block. It is clear that future analog and RF designs will be subjected to ever more stringent supply voltage constraints. In many cases, however, it may be feasible to embrace this trend and reduce the supply voltage as low as possible as a means of achieving minimum power consumption. For low power designs, the minimum bias current is usually determined by the required circuit performances and cannot be arbitrarily reduced. On the other hand, the supply voltage is usually set at a standard value that may not be optimal for the design. If the current levels are optimized, the technique of reducing the supply voltage may result in additional power savings. In the following, possible opportunities for low voltage RF design are discussed.

Figure 2.1: ITRS projections for CMOS supply voltage scaling

#### The Cascode and Folded Topologies

The cascode configuration is widely used in the design of CMOS RFICs thanks to its reasonable high-frequency characteristics in terms of gain, output impedance and reverse isolation. Figure 2.2 shows a simplified illustration of a cascode stage with its principles of operation in dc and ac conditions [25]. With a stacked architecture, the dc bias current is shared by the two active devices of the same type, which is advantageous as far as power consumption is concerned. However, if both of the metal-oxide-semiconductor (MOS) transistors are operating in saturation, a supply voltage of at least twice of the transistor's overdrive ( $V_{GS} - V_{TH}$ ) is required. Typically, the RF performance of a cascode stage degrades significantly as the supply voltage decreases, making it less attractive for low-voltage circuit operations. To alleviate the stringent limitations on the supply voltage, a folded cascode configuration in classical analog circuit design has been adopted by many RF designers. The idea of folded cascade is to decouple the ac and dc paths of the circuit. A simplified illustration is depicted in Figure 2.3 where a decoupling capacitor and two RF chokes are employed. As the equivalent impedance provided by the RF chokes is sufficiently large and the decoupling capacitor is considered as a short circuit at

Figure 2.2: A conceptual illustration of the cascode architecture

the frequencies of interest, the ac signal path of the folded cascode stage is identical to that of a conventional one. On the other hand, as indicated in Figure 2.3, the dc voltages and bias currents of the two stages are virtually independent. Therefore, the required supply voltage can be effectively reduced at the cost of higher current consumption while maintaining the desirable performance of the RFICs.

Figure 2.3: A conceptual illustration of the folded cascode architecture

#### Complementary Current Reuse Technique

As indicated in the previous section, the folded cascode topology trades dc power for supply voltage. To achieve low-voltage and low-power circuit operations at the same time, a complementary current-reuse technique is proposed in [26] with circuit example and design guidelines for down-conversion mixers. A conceptual illustration of a down-conversion mixer using the current-reuse technique is shown in Figure 2.4, where the

transconductance stage  $M_N$  performs the voltage-to-current conversion of the RF input signal, small-signal current is then directed to the source of the PMOS differential pair through capacitor  $C_1$ . The commutating stage  $(M_{P1}, M_{P2})$  provides frequency down-conversion since it is driven by local oscillator (LO) with sufficient swings. Resistor  $R_1$  is employed to provide a bypass current path such that large load resistance  $R_L$  can be used to boost the conversion gain without introducing excessive voltage drop.

Figure 2.4: The complementary current-reused mixer with a current-bleeding technique

#### 2.1.2 Transistor Biasing

# Forward-body Bias Technique

In the design of CMOS RFICs for low-voltage operations, the threshold voltage of the MOSFETs is considered one of the fundamental limitations for the supply voltage. For circuits in which the active devices are always on, it is desirable to have transistors with a reduced threshold voltage. For the CMOS process technology, the option of multiple threshold voltages is typically realized by adjusting the thickness of the gate oxide or the doping profile in the channel. However, this complicates the fabrication process and requires higher implementation cost. Alternatively, the threshold voltage can be manipulated by the bias voltage at the body terminal. Taking the n-channel MOSFET

as an example, the threshold voltage is given by:

$$V_{TH} = V_{TH0} + \gamma (\sqrt{|2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|})$$

(2.1)

Where  $V_{SB}$  is the source-to-body voltage,  $V_{TH0}$  is the threshold voltage for  $V_{SB} = 0$ ,  $\gamma$  is a process-dependent parameter, and  $\phi_F$  is a semiconductor parameter with a typical value in the range of 0.3-0.4 V. In a triple-well CMOS technology, the simplified cross-sectional view of a NMOS device is given in Figure 2.5 to demonstrate the forward-body bias technique (FBB). By raising the dc voltage  $V_B$  at the body terminal, the value of  $V_{SB}$  becomes negative, leading to a decrease in the effective threshold voltage and therefore a control on the transistor current as it is shown on Figure 2.6.

As forward body bias is directly applied to p-n junction between the source and the

Figure 2.5: Forward-body bias technique

body, a current-limiting resistance  $R_B$  is typically included in the series path to prevent excessive current conduction, which may cause latch-up failure in CMOS circuitry. A special care must also be taken into account regarding the applied amount of  $V_{SB}$ , since a large source to bulk voltage may trigger CMOS latch up. The FBB is limited by the subthreshold leakage current and the forward biasing of the drain-bulk junction. According to [27] and [28], the upper limit of the FBB voltage for latch-up free operation, in 65 nm CMOS technology with  $V_{DD}$  ranges from 0.9 to 1.2 V, is 0.6 V.

Figure 2.7 shows the threshold voltage versus back-gate forward bias for NMOS transistor in 65 nm CMOS process. It can be clearly seen that an increase in the back-

Figure 2.6: Transistor drain current for different bulk-source voltages,  $130\,\mathrm{nm}$  CMOS process

Figure 2.7: Threshold voltage versus  $V_{BS}$  for NMOS transistor in 65nm process

gate forward bias from  $0\,\mathrm{V}$  to  $0.6\,\mathrm{V}$  can lower the threshold voltage from  $0.41\,\mathrm{V}$  to  $0.36\,\mathrm{V}$ , which correspond to a reduction of  $12\,\%$ . Therefore, the circuit power supply voltage could be lowered by the same proportion.

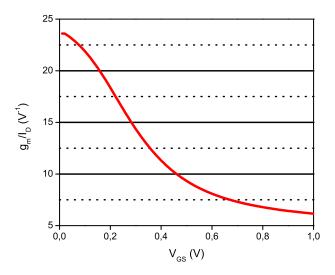

# Subthreshold Operation

The main interest in transistor effect is the transconductance operation, which converts an input AC voltage into an output AC current. Hence, the transconductance  $g_m$  is the first and most important analog parameter of a transistor. The transconductance efficiency, rating the  $g_m$  to the drain current, is a figure of merit exploited in the design of low power analog circuits. Its maximum occurs in subthreshold operation of MOS device as depicted in Figure 2.8. In RF domain, the performances of a circuit are often correlated to the maximum of the cutoff frequency,  $f_T$ , defined as:

$$f_T \approx \frac{g_m}{2\pi (C_{qs} + C_{qd})} \tag{2.2}$$

where  $g_m$  is the small-signal transconductance and  $C_{gs}$  and  $C_{gd}$  represent the gate-source and gate-drain capacitances, respectively. Figure 2.8 figures out that the  $f_T$  is maximum when the transistor operates in strong inversion region (SI), which in turn corresponds to a weak transconductance efficiency.

Figure 2.8:  $g_m/I_D$  and  $f_T$  for a modern CMOS 130 nm process

#### **Technology Scaling**