## Formal Verification of a Synchronous Data- flow Compiler: from Signal to C

van Chan Ngo

#### ▶ To cite this version:

van Chan Ngo. Formal Verification of a Synchronous Data- flow Compiler : from Signal to C. Software Engineering [cs.SE]. Université Rennes 1, 2014. English. NNT : . tel-01067477v1

### HAL Id: tel-01067477 https://theses.hal.science/tel-01067477v1

Submitted on 26 Aug 2014 (v1), last revised 23 Sep 2014 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE / UNIVERSITÉ DE RENNES 1**

sous le sceau de l'Université Européenne de Bretagne

pour le grade de

### **DOCTEUR DE L'UNIVERSITÉ DE RENNES 1**

Mention : Informatique

### École doctorale Matisse

présentée par

# Van Chan NGO

Préparée à l'unité de recherche UMR 6074 Institut National de Recherche en Informatique et en Automatique

Formal Verification of a Synchronous Dataflow Compiler : from Signal to C

#### Thèse soutenue à Rennes le 01 Juillet 2014

devant le jury composé de :

Sandrine BLAZY Professeur à l'Université de Rennes/ présidente

Jean-Paul BODEVEIX Professeur à l'Université de Toulouse / rapporteur

Laure GONNORD Maître de Conférence, Université de Lyon / rapportrice

Abdoulaye GAMATIÉ Chargé de Recherche, CNRS-LIRMM / examinateur

**Dumitru POTOP-BUTUCARU** Chargé de Recherche, INRIA Rocquencourt / *examinateur*

Jean-Pierre TALPIN Directeur de Recherche, INRIA Rennes / directeur

Directeur de Recherche, INRIA Rennes / direc de thèse

To my loving parents.

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to my advisor, Jean-Pierre Talpin. Thanks for all his support, my three years of Ph.D. have been a very useful time. I learnt much from his experience and knowledge. He has been a great advisor. He gave me the freedom of pursing my goals and interests while always providing guidance. Thank you so much Jean-Pierre.

I would like to thank the members of my Ph.D. committee, specially Jean-Paul Bodeveix and Laure Gonnord who agreed on reviewing my dissertation and gave useful and interesting comments.

I also would like to thank my colleagues Loïc Besnard, Thierry Gautier, Paul Le Guernic, Huafeng Yu, Yue Ma, Christophe Junke, Adnan Bouakaz, Sun Ke in the TEA group at INRIA, Abdoulaye Gamatié and Sandeep Shukla for their friendship and support. My special thanks to Thierry and Abdoulaye who has read and commented on every bit of my reports and this dissertation, and who has listened to every idea I had during my time at INRIA.

I also would like to thanks my friends here, in RENNES for their help and relaxed time.

Last but not least, I would like to thank my family, especially my parents, Van Tac & Ngo Ngo who have always been there for me. Only I know that this dissertation cannot be carried out without them.

### ABSTRACT

Synchronous languages such as SIGNAL, LUSTRE and ESTEREL are dedicated to designing safety-critical systems. Their compilers are large and complicated programs that may be incorrect in some contexts, which might produce silently bad compiled code when compiling source programs. The bad compiled code can invalidate the safety properties that are guaranteed on the source programs by applying formal methods. Adopting the translation validation approach, this thesis aims at formally proving the correctness of the highly optimizing and industrial SIGNAL compiler. The correctness proof represents both source program and compiled code in a common semantic framework, then formalizes a relation between the source program and its compiled code to express that the semantics of the source program are preserved in the compiled code.

Les langages synchrones tels que SIGNAL, LUSTRE et ESTEREL sont dédiés à la conception de systèmes critiques. Leurs compilateurs, qui sont de très gros programmes complexes, peuvent a priori se révéler incorrects dans certains situations, ce qui donnerait lieu alors à des résultats de compilation erronés non détectés. Ces codes fautifs peuvent invalider des propriétés de sûreté qui ont été prouvées en appliquant des méthodes formelles sur les programmes sources. En adoptant une approche de validation de la traduction, cette thèse vise à prouver formellement la correction d'un compilateur optimisé et industriel de SIGNAL. La preuve de correction représente dans un cadre sémantique commun le programme source et le code compilé, et formalise une relation entre eux pour exprimer la préservation des sémantiques du programme source dans le code compilé.

## CONTENTS

| Co  | ontent  | s                                                    | vii  |

|-----|---------|------------------------------------------------------|------|

| Lis | stings  |                                                      | xi   |

| Lis | st of I | Figures                                              | xiii |

| Lis | st of 7 | fables                                               | XV   |

| 1   | Intro   | oduction                                             | 1    |

|     | 1.1     | Correctness of compilation                           | 2    |

|     | 1.2     | Formal compiler verification                         | 5    |

|     | 1.3     | Translation validation                               | 7    |

|     | 1.4     | Contributions                                        | 9    |

|     |         | 1.4.1 Preservation of clock semantics                | 11   |

|     |         | 1.4.2 Preservation of data dependency                | 12   |

|     |         | 1.4.3 Preservation of value-equivalence of variables | 13   |

|     |         | 1.4.4 Towards a formally verified SIGNAL compiler    | 13   |

|     | 1.5     | Chapter plan                                         | 14   |

| 2   | Rela    | ted work in compiler verification                    | 16   |

|     | 2.1     | Compiler verification based on testing               | 18   |

|     | 2.2     | Compiler verification based on formal methods        | 20   |

| 3   | Sync    | chronous data-flow languages                         | 26   |

|     | 3.1     | Embedded, reactive and real-time systems             | 26   |

|     |         | 3.1.1 Reactive systems                               | 27   |

|     |         | 3.1.2 Real-time systems                              | 28   |

|     | 3.2     | Synchronous programming                              | 29   |

|   |      | 3.2.1    | Classical approaches                                        | 30  |

|---|------|----------|-------------------------------------------------------------|-----|

|   |      | 3.2.2    | The synchronous approach                                    | 31  |

|   | 3.3  | The SI   | IGNAL language                                              | 31  |

|   |      | 3.3.1    | Synchronized data flow                                      | 31  |

|   |      | 3.3.2    | An overview of the language                                 | 32  |

|   |      | 3.3.3    | Semantics of the language                                   | 36  |

| 4 | Trai | nslation | validation of transformations on clocks                     | 44  |

|   | 4.1  | The cl   | ock calculus in SIGNAL compiler                             | 45  |

|   | 4.2  | The sy   | vnchronization space $\mathbb{Z}/_3\mathbb{Z}$              | 47  |

|   |      | 4.2.1    | PDS model                                                   | 49  |

|   | 4.3  | Transl   | ation validation of PDSs                                    | 53  |

|   |      | 4.3.1    | Definition of correct transformation: PDS refinement        | 53  |

|   |      | 4.3.2    | Proving refinement by simulation                            | 56  |

|   |      | 4.3.3    | Composition of compilation phases                           | 58  |

|   |      | 4.3.4    | Implementation with SIGALI                                  | 59  |

|   | 4.4  | Transl   | ation validation of clock models                            | 63  |

|   |      | 4.4.1    | Clock model of SIGNAL program                               | 63  |

|   |      | 4.4.2    | Soundness of clock model                                    | 69  |

|   |      | 4.4.3    | Definition of correct transformation: Clock refinement      | 74  |

|   |      | 4.4.4    | Proving clock refinement by SMT                             | 76  |

|   |      | 4.4.5    | Implementation with SMT                                     | 78  |

|   |      | 4.4.6    | Detected bugs                                               | 83  |

|   | 4.5  | Discus   | ssion                                                       | 84  |

| 5 | Trai | nslation | validation of SDDG                                          | 86  |

|   | 5.1  | The da   | ata dependency analysis in SIGNAL compiler                  | 87  |

|   | 5.2  | Synch    | ronous data-flow dependency graph                           | 89  |

|   |      | 5.2.1    | Data dependency graphs                                      | 90  |

|   |      | 5.2.2    | SIGNAL program as synchronous data-flow dependency graph    | 90  |

|   | 5.3  | Transl   | ation validation of SDDG                                    | 94  |

|   |      | 5.3.1    | Definition of correct implementation: Dependency refinement | 94  |

|   |      | 5.3.2    | Adaptation to the SIGNAL compiler                           | 98  |

|   |      | 5.3.3    | Proving dependency refinement by SMT                        | 99  |

|   |      | 5.3.4    | Implementation                                              | 100 |

|   | 5.4  | Precise  | e deadlock detection for SIGNAL compiler                    | 103 |

|    |       | 5.4.1    | Deadlock detection in the SIGNAL compiler     | 103 |

|----|-------|----------|-----------------------------------------------|-----|

|    |       | 5.4.2    | A more precise deadlock detection             | 105 |

|    |       | 5.4.3    | Precise deadlock detection                    | 110 |

|    | 5.5   | Discus   | sion                                          | 113 |

| 6  | Eval  | uating   | SDVG translation validation: from SIGNAL to C | 115 |

|    | 6.1   | Code g   | generation in SIGNAL compiler                 | 116 |

|    |       | 6.1.1    | The principle                                 | 116 |

|    |       | 6.1.2    | Sequential code generation                    | 119 |

|    | 6.2   | Illustra | tive example                                  | 120 |

|    | 6.3   | Synchr   | ronous data-flow value-graph                  | 123 |

|    |       | 6.3.1    | Definition of SDVG                            | 125 |

|    |       | 6.3.2    | SDVG of SIGNAL programs                       | 130 |

|    |       | 6.3.3    | SDVG of generated C code                      | 138 |

|    | 6.4   | Sdvg     | translation validation                        | 143 |

|    |       | 6.4.1    | An introduction to graph rewriting            | 143 |

|    |       | 6.4.2    | Normalizing                                   | 148 |

|    |       | 6.4.3    | Implementation                                | 157 |

|    | 6.5   | Discus   | sion                                          | 161 |

| 7  | Con   | clusion  |                                               | 163 |

|    | 7.1   | Summa    | ary of the contribution                       | 163 |

|    | 7.2   | Future   | work                                          | 165 |

| Re | feren | ces      |                                               | 167 |

## LISTINGS

| 1.1  | Bug 15549                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Stack-machine code of $(x+2) * y \dots + y + y$ |

| 1.3  | Pseudo-code implementation of formal verified SIGNAL compiler 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1  | Bit clear test case with SUPERTEST 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1  | "Event driven"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.2  | "Sampling"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.3  | DEC in Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.1  | ALTERN in Signal         52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.2  | PDS of ALTERN         53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.3  | Compute symbolic simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.4  | Symbolic simulation implementation in SIGALI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.5  | DEC_BASIC_TRA in Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.1  | DEC_SEQ_TRA in Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.2  | CycleDependency in SIGNAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.1  | Structure of P_main.c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.2  | Structure of P_io.c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.3  | Program WHENOP in SIGNAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.4  | Synchronous Step of WHENOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.5  | Simple Program in SIGNAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.6  | SDVGMerge in SIGNAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.7  | Generated C code of SDVGMerge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.8  | Normalizing value-graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.9  | MasterClk in SIGNAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.10 | Generated C code of MasterClk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.11 | Generated C code of DEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## LIST OF FIGURES

| 1.1  | The compilation process of a synchronous compiler                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Phases of compiler design 3                                                                                                                                                     |

| 1.3  | A bird's-eye view of translation validation framework                                                                                                                           |

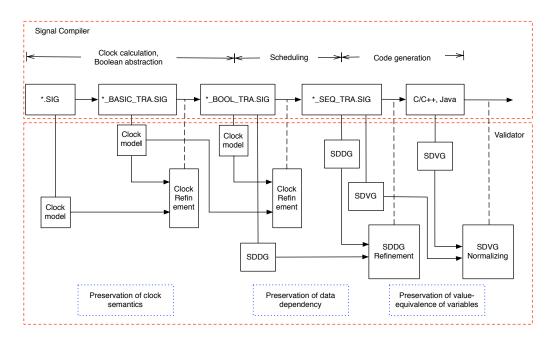

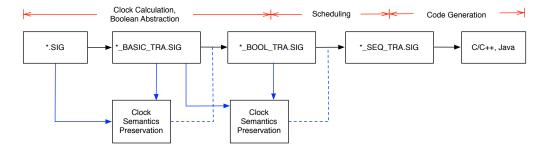

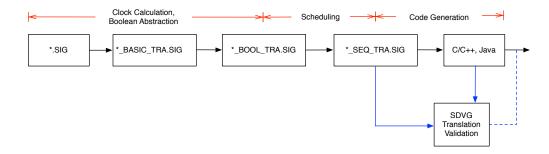

| 1.4  | The compilation process of the SIGNAL compiler                                                                                                                                  |

| 1.5  | The translation validation for the SIGNAL compiler 11                                                                                                                           |

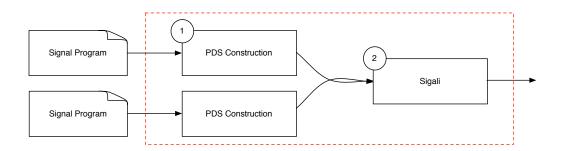

| 4.1  | A bird's-eye view of the verification process                                                                                                                                   |

| 4.2  | The PDS translation validation                                                                                                                                                  |

| 4.3  | Rule CLKREF         76                                                                                                                                                          |

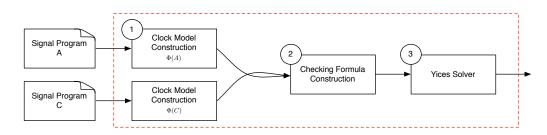

| 4.4  | The clock model translation validation                                                                                                                                          |

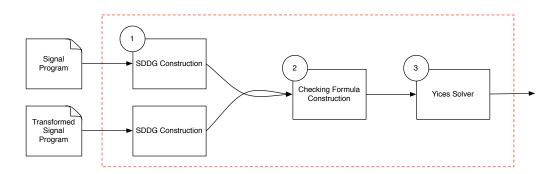

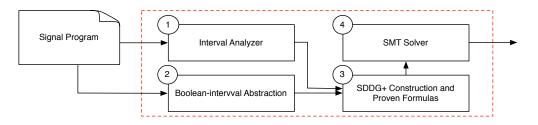

| 5.1  | Translation validation of SDDG                                                                                                                                                  |

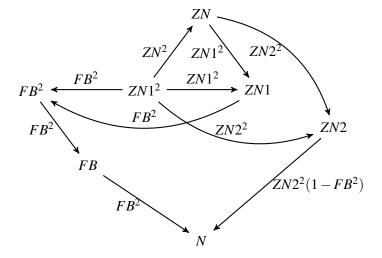

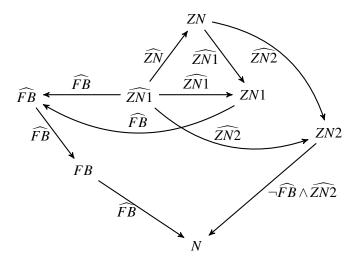

| 5.2  | The GCD of DEC                                                                                                                                                                  |

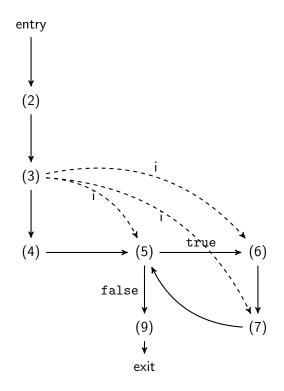

| 5.3  | CFG for Sum, with data dependency edges for i (dotted lines) 91                                                                                                                 |

| 5.4  | The SDDG of merge operator                                                                                                                                                      |

| 5.5  | The SDDG of DEC                                                                                                                                                                 |

| 5.6  | A bird's-eye view of the SDDG translation validation 101                                                                                                                        |

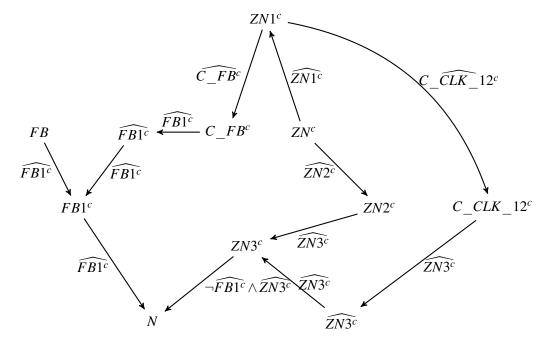

| 5.7  | The SDDG of DEC_SEQ_TRA                                                                                                                                                         |

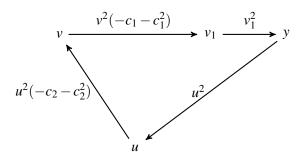

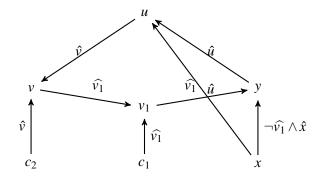

| 5.8  | Dependencies among $y, u, v$                                                                                                                                                    |

| 5.9  | The SDDG <sup>+</sup> of CycleDependency $\ldots \ldots \ldots$ |

| 5.10 | An overview of our approach                                                                                                                                                     |

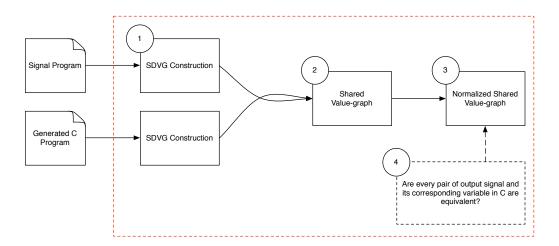

| 6.1  | A bird's-eye view of the verification process                                                                                                                                   |

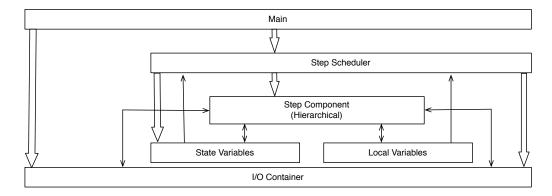

| 6.2  | Code generation: General scheme                                                                                                                                                 |

| 6.3  | The shared value-graph of WHENOP and WHENOP_step 123                                                                                                                            |

| 6.4  | The resulting transformed value-graph                                                                                                                                           |

| 6.5  | The final value-graph                                                                                                                                                           |

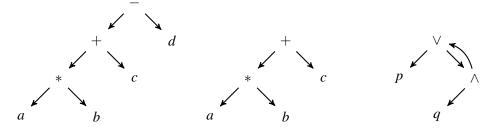

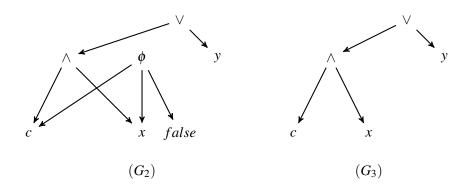

| 6.6  | The directed graphs of $a + b * c$ and $a + b, b * c \dots \dots$               |

| 6.7  | The subgraph rooted at node labeled $+$ and a root-cyclic graph $\ldots \ldots \ldots$                                                                                 | 127 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.8  | An example of homomorphism                                                                                                                                             | 128 |

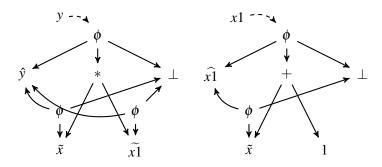

| 6.9  | The subgraphs of $y := x * x1$ and $x1 := x + 1$                                                                                                                       | 131 |

| 6.10 | The SDVG graph of $P$                                                                                                                                                  | 132 |

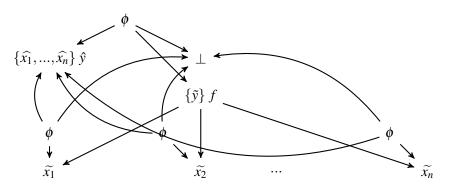

| 6.11 | The graph of $y := f(x_1,, x_n)$                                                                                                                                       | 132 |

| 6.12 | The graph of $y := (x \ge 1)$ and $c  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                 | 133 |

| 6.13 | The graph of $y := x$ \$1 init $a \dots $                        | 134 |

| 6.14 | The graph of $y := (x \$1 \text{ init } 1) + z \dots \dots$            | 134 |

| 6.15 | The graph of $y := x$ default $z$                                                                                                                                      | 135 |

| 6.16 | The graph of $y := x$ default $(z+1)$                                                                                                                                  | 135 |

| 6.17 | The graph of $y := x$ when $b \ldots \ldots$                                                     | 136 |

| 6.18 | The graph of $y := x$ when $(z \ge 1)$                                                                                                                                 | 137 |

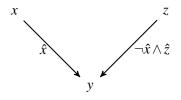

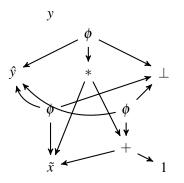

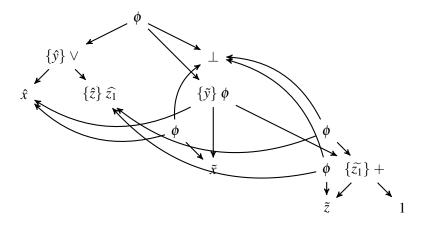

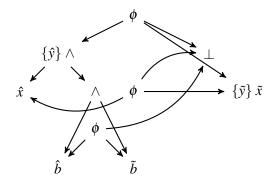

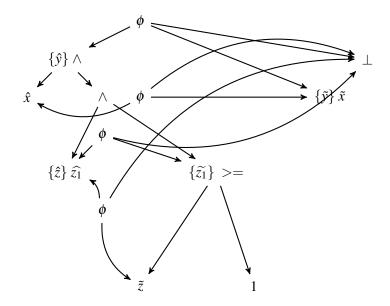

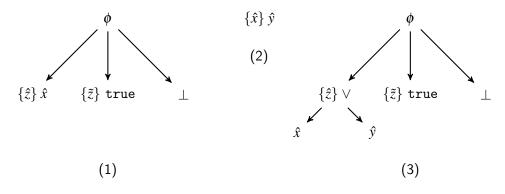

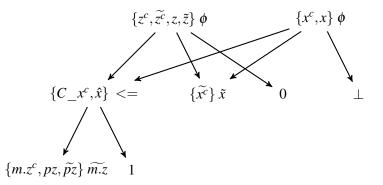

| 6.19 | The graphs of (1) $z := \hat{x}$ , (2) $x^{2} = y$ and (3) $z := x^{2} + y \dots \dots \dots \dots$                                                                    | 137 |

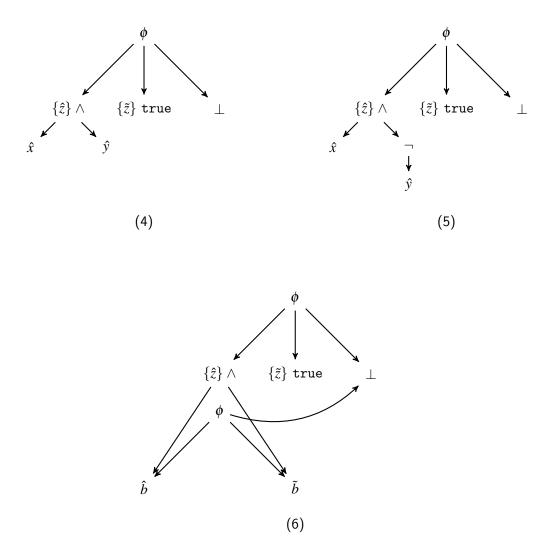

| 6.20 | The graphs of (4) $z := x^* y$ , (5) $z := x^- y$ and (6) $z :=$ when $b \ldots \ldots$                                                                                | 138 |

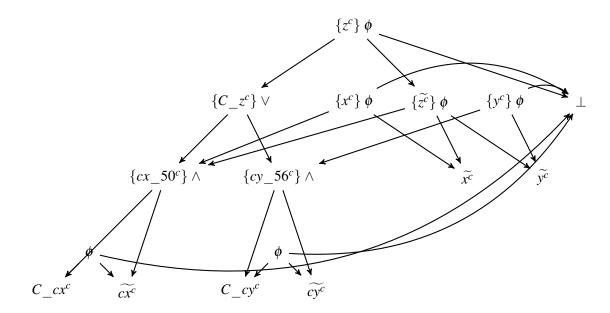

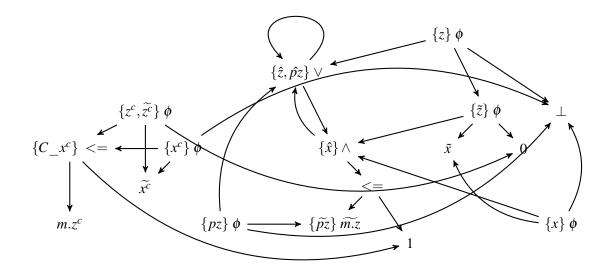

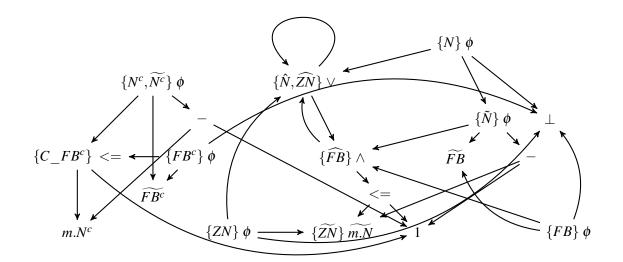

| 6.21 | The graph of SDVGMerge_step                                                                                                                                            | 141 |

| 6.22 | The graph of $N$ 's computation $\ldots \ldots \ldots$ | 142 |

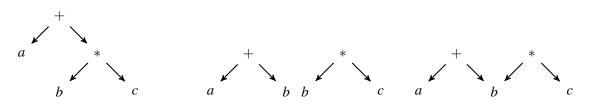

| 6.23 | The transformation of the graph of $t * (u+1)$                                                                                                                         | 144 |

| 6.24 | The transformation of graph of $t * (u + 1)$ with sharing of repeated subterms                                                                                         | 144 |

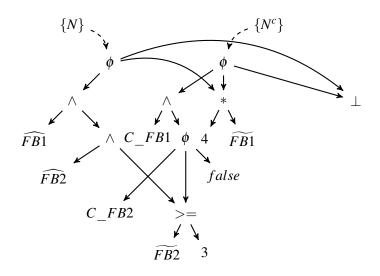

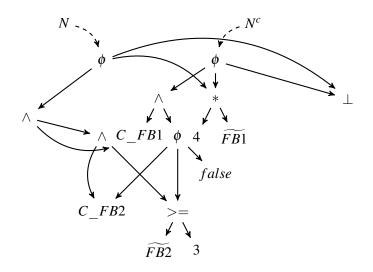

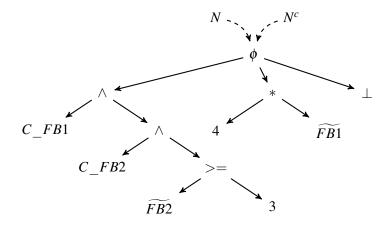

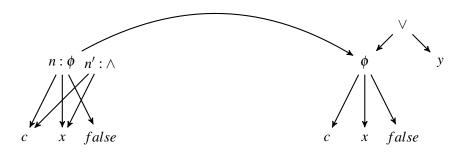

| 6.25 | The graph rule of the term rule $\phi(c, x, false) \rightarrow c \land x$                                                                                              | 146 |

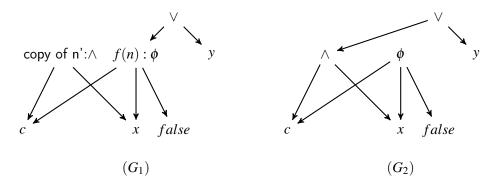

| 6.26 | An example of graph rewriting                                                                                                                                          | 147 |

| 6.27 | Graph rewriting: Build and redirection phases                                                                                                                          | 147 |

| 6.28 | Graph rewriting: Garbage collection phases                                                                                                                             | 148 |

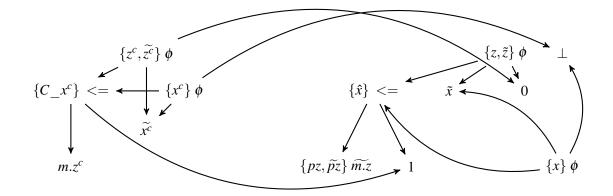

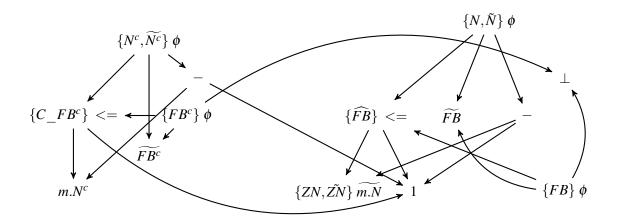

| 6.29 | The shared value-graph of MasterClk and MasterClk_step                                                                                                                 | 155 |

| 6.30 | The resulting graph of MasterClk and MasterClk_step by applying the rule                                                                                               |     |

|      | 6.38                                                                                                                                                                   | 156 |

| 6.31 | The resulting graph of MasterClk and MasterClk_step by applying the rule                                                                                               |     |

|      | 6.39                                                                                                                                                                   | 156 |

| 6.32 | The final normalized graph of MasterClk and MasterClk_step                                                                                                             | 157 |

| 6.33 | A bird's-eye view of the SDVG translation validation                                                                                                                   | 158 |

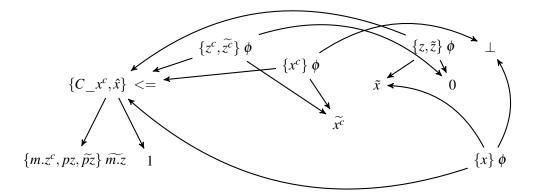

| 6.34 | The shared value-graph of DEC and DEC_step                                                                                                                             | 159 |

| 6.35 | The resulting value-graph of DEC and DEC_step                                                                                                                          | 160 |

| 6.36 | The final normalized graph of DEC and DEC_step                                                                                                                         | 161 |

## LIST OF TABLES

| 3.1 | The implicit clock relations and dependencies        | 34 |

|-----|------------------------------------------------------|----|

| 4.1 | Translation validation of PDSs: Experimental results | 64 |

| 4.2 | Clock semantics of the SIGNAL primitive operators    | 71 |

| 5.1 | The implicit dependencies and their encoding in GCD  | 88 |

| 5.2 | The dependencies of the core language                | 93 |

## CHAPTER 1

#### INTRODUCTION

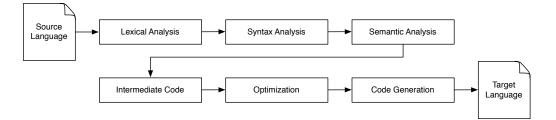

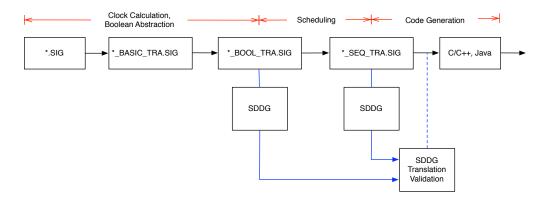

Synchronous programming languages such as SIGNAL, LUSTRE and ESTEREL propose a formal semantic framework to give high-level specification of safety-critical software in automotive and avionics systems [17, 71, 73, 81]. As other programming languages, synchronous languages are associated with a compiler. The compiler takes a source program, analyses and transforms it, performs optimizations, and finally generates executable code in a general-purpose programming language (e.g., C, C<sup>++</sup>, or JAVA). This compilation process is depicted as in Figure 1.1.

Fig. 1.1 The compilation process of a synchronous compiler