# Design of a dependable Interlock System for linear colliders

Patrice Nouvel

#### ▶ To cite this version:

Patrice Nouvel. Design of a dependable Interlock System for linear colliders. Micro and nanotechnologies/Microelectronics. Institut National Polytechnique de Toulouse - INPT, 2013. English. NNT: 2013INPT0093. tel-01068043v2

### HAL Id: tel-01068043 https://theses.hal.science/tel-01068043v2

Submitted on 21 Nov 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

#### En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

#### Délivré par :

Institut National Polytechnique de Toulouse (INP Toulouse)

#### Discipline ou spécialité :

Conception des Circuits Microélectroniques et Microsystèmes (CCMM)

#### Présentée et soutenue par :

M. PATRICE NOUVEL le mercredi 18 décembre 2013

#### Titre:

CONCEPTION D'UN SYSTEME DE VERROUILLAGE SUR DE FONCTIONNEMENT POUR LES COLLISIONNEURS LINEAIRES.

#### **Ecole doctorale:**

Génie Electrique, Electronique, Télécommunications (GEET)

#### Unité de recherche :

Laboratoire d'Analyse et d'Architecture des Systèmes (L.A.A.S.)

#### Directeur(s) de Thèse :

MME HÉLÈNE TAP -BETEILLE M. BRUNO PUCCIO

#### Rapporteurs:

M. LIONEL TORRES, UNIVERSITE MONTPELLIER 2 M. YANNICK HERVE, UNIVERSITE STRASBOURG 1

#### Membre(s) du jury :

M. JEAN ARLAT, LAAS TOULOUSE, Président Mme HÉLÈNE TAP -BETEILLE, INP TOULOUSE, Membre

#### INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE

## Abstract

Doctoral School Génie Electrique, Electronique, Télécommunications

#### DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

#### Design of a dependable Interlock System for linear colliders

by Patrice Nouvel

For high energy accelerators, the interlock system is a key part of the machine protection. The interlock principle is to inhibit the beam either on failure of critical equipment and/or on low beam quality evaluation. The dependability of such a system is the most critical parameter. This thesis presents the design of an dependable interlock system for linear collider with an application to the CLIC (Compact Linear Collider) project. This design process is based on the IEEE 1220 standard and is is divided in four steps. First, the specifications are established, with a focus on the dependability, more precisely the reliability and the availability of the system. The second step is the design proposal based on a functional analysis, the CLIC and interfaced systems architecture. Third, the feasibility study is performed, applying the concepts in an accelerator facility. Finally, the last step is the hardware verification. Its aim is to prove that the proposed design is able to reach the requirements.

#### INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE

## Resumé

Ecole Doctorale Génie Electrique, Electronique, Télécommunications

#### DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

# Conception d'un système de verrouillage sûr de fonctionnement pour les collisionneurs linéaires

par Patrice Nouvel

Pour les accélérateurs de particules à hautes énergies, le système de verrouillage est une partie clé de la protection de la machine. Le verrouillage de la machine est l'inhibition du faisceau dès lors qu'un équipement critique tombe en panne et/ou qu'un faisceau est de faible qualité. Pour un système de verrouillage, sa sûreté de fonctionnement est la caractéristique la plus importante. Cette thèse présente le développement d'un système de verrouillage pour les collisionneurs linéaires avec une application au projet CLIC (Compact Linear Collider). Son élaboration s'appuie sur la norme d'ingénierie IEEE 1220 et se décline en quatre parties. Tout d'abord, les spécifications sont établies. Une attention particulière est portée sur la sûreté de fonctionnement, plus précisément, la fiabilité et la disponibilité du système. La deuxième étape est la proposition d'un design. Celui-ci est basé sur une analyse fonctionnelle, les interfaces du système et l'architecture du CLIC. Troisièmement, une étude de faisabilité est effectuée en appliquant les concepts dans un environnement opérationnel. Finalement, la dernière étape est la vérification matérielle. Le but est de prouver que le design proposé est capable de remplir le cahier des charges établi.

# Acknowledgements

First of all, I would like to thank the rapporteurs Lionel TORRES and Yannick HERVE for their valuable advices and the time they spent to read this manuscript.

I would like to warmly thanks my thesis director, Hélène TAP, for her precious guidance which leads me successfully to the thesis defence. A big thanks to Bruno Puccio, my CERN supervisor, who gives me the opportunity to undertaken this PhD. His support, advices and availability during these 3 past years have been a key factor to the thesis success.

I would like to thank Alexey Dubrovskiy for his help for the CTF3 application.

For their help on the dependability study, I would like to thank Benjamin Todd and Sigrid Wagner. For their help on JAVA programming, Maxime Audrain, Rafal Leszko and Jean-Christophe Garnier (and for his help for Linux).

Also, I would like to thank Bernard Collignon and Chistophe Martin for their help on the test bench realisation.

I would like also to thank Andrzej Siemko, the group leader, to allow me to present my works in conferences.

A big thank to the (not yet cited) lunch (and ping pong) and machine interlock team: Ivan, Jakub, Jacek, Andrea, Stephane, Konstatinos, Javier, Daniel, Damien, Scott, Gaetan, Steffen, James, Jonathan, Cristina, Kajetan, Dawn, Alain, Jean-Louis, Jean-Phillipe, Jeremie, Pierre, Juan, Maciej, Markus, Kamil (with the hope I did not forget anybody).

In more general way, I thank my friends, who were tolerant enough to allow me talking about the PhD!

More personally, I thank my family, for their help (special mention to Jeff, who gives me regularly a place to rest myself). At last but not the least, I thank Claire for her constant support on a day basis for this challenge!

# Table of Contents

| A  | Abstract |         |                                                                | 3  |  |

|----|----------|---------|----------------------------------------------------------------|----|--|

| A  | cknov    | wledge  | ements                                                         | 5  |  |

| Li | st of    | Figure  | es                                                             | 11 |  |

| Li | st of    | Table   | ${f s}$                                                        | 15 |  |

| 1  | Ger      | ieral I | ntroduction                                                    | 1  |  |

| 2  | Con      | ıtext a | and state of the art                                           | 5  |  |

|    | 2.1      | Introd  | luction                                                        | 5  |  |

|    | 2.2      | Partic  | le Physics and CERN                                            | 5  |  |

|    |          | 2.2.1   | Challenges in particle physics                                 | 6  |  |

|    |          | 2.2.2   | European Organisation for the Nuclear Research                 | 8  |  |

|    | 2.3      | High 6  | energy linear colliders overview                               | 10 |  |

|    |          | 2.3.1   | CLIC overview                                                  | 10 |  |

|    |          | 2.3.2   | ILC overview                                                   | 14 |  |

|    |          | 2.3.3   | CLIC and ILC parameters comparison                             | 18 |  |

|    | 2.4      |         | Machine protection overview                                    | 18 |  |

|    |          | 2.4.1   | Failures type and protection strategies                        | 19 |  |

|    |          | 2.4.2   | Machine Protection Systems                                     | 20 |  |

|    | 2.5      | CLIC    | Interlock system and thesis problematic                        | 21 |  |

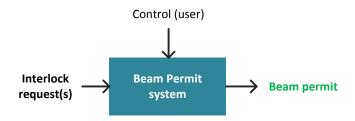

|    |          | 2.5.1   | Beam Permit                                                    | 21 |  |

|    |          | 2.5.2   | Post-pulse analysis                                            | 21 |  |

|    |          | 2.5.3   | Thesis problematic definition                                  | 22 |  |

|    | 2.6      |         | luction to interlock systems                                   | 23 |  |

|    |          | 2.6.1   | Protect the machine - Beam Interlock Function                  | 23 |  |

|    |          | 2.6.2   | High dependability requirements                                | 24 |  |

|    |          | 2.6.3   | Common design                                                  | 25 |  |

|    | 2.7      |         | ed protection systems                                          | 26 |  |

|    |          | 2.7.1   | LHC Beam Interlock System                                      | 26 |  |

|    |          | 2.7.2   | Linac Coherent Light Source Interlock System                   | 28 |  |

|    |          | 2.7.3   | Linac 4 watchdog                                               |    |  |

|    |          | 2.7.4   | Real-time and post-pulse beam quality assessment for LHC beams | 30 |  |

|    |          | 2.7.5   | Safe Machine Parameters                                        | 31 |  |

Contents 7

|   | 2.8        | Conclusion                                      | 3 |

|---|------------|-------------------------------------------------|---|

| 3 | Req        | uirements establishment 3                       | 5 |

|   | 3.1        | Introduction                                    | 5 |

|   | 3.2        | Operational scenarios and interfaces            | 6 |

|   | 3.3        | Functional requirements                         | 8 |

|   |            | 3.3.1 Main functional requirements              | 9 |

|   |            | 3.3.2 Functional suggestions                    | 0 |

|   | 3.4        | Performance requirements                        | 0 |

|   |            | 3.4.1 Response times                            | 0 |

|   |            | 3.4.2 Establishing dependability requirements 4 | 1 |

|   |            | 3.4.3 Reaching dependability requirements 4     | 6 |

|   |            | 3.4.4 Suggestions for the dependability study 4 |   |

|   | 3.5        | Interfaces and safety-critical requirements     |   |

|   |            | 3.5.1 Acquisition and control infrastructure 50 |   |

|   |            | 3.5.2 Target systems                            |   |

|   | 3.6        | Conclusion                                      |   |

|   | 5.0        | Conclusion                                      | 9 |

| 4 | Des        | ign Proposal 5                                  | 7 |

|   | 4.1        | Introduction                                    | 7 |

|   | 4.2        | Functional analysis                             | 7 |

|   |            | 4.2.1 System functional behaviour               | 8 |

|   |            | 4.2.2 Functional decomposition                  | 8 |

|   |            | 4.2.3 Functional architecture                   | 5 |

|   | 4.3        | Implementation proposal                         |   |

|   |            | 4.3.1 Subfunctions implementation               | 6 |

|   |            | 4.3.2 System implementation                     | 8 |

|   |            | 4.3.3 Hardware modules                          | 1 |

|   | 4.4        | Conclusion                                      |   |

| 5 | Dog        | ign verification 7                              | E |

| J |            | Introduction                                    |   |

|   | 5.2        |                                                 |   |

|   | 0.4        |                                                 |   |

|   |            | 1                                               |   |

|   |            | *                                               |   |

|   |            | 5.2.3 Technical description                     |   |

|   | <b>r</b> o | 5.2.4 Results and discussion                    |   |

|   | 5.3        | Hardware demonstration                          |   |

|   |            | 5.3.1 Technical discussion                      |   |

|   |            | 5.3.2 Goals                                     |   |

|   |            | 5.3.3 VHDL blocks description                   |   |

|   |            | 5.3.4 Nodes description                         |   |

|   |            | 5.3.5 Hardware and test bench description       |   |

|   |            | 5.3.6 Results and discussion                    |   |

|   | 5.4        | Conclusion                                      | 2 |

| 6 | Con        | clusion and perspectives 11                     | 5 |

Contents 8

| A            | Dependability data                                  | 117   |

|--------------|-----------------------------------------------------|-------|

| В            | CTF3 Application details                            | 119   |

|              | B.1 Technical Overview                              | . 119 |

|              | B.2 Finite state machine diagram                    | . 121 |

|              | B.3 Threshold dynamic factors                       |       |

|              | B.3.1 Maximum Value                                 | . 123 |

|              | B.3.2 Beam Length                                   | . 124 |

|              | B.3.3 Beam Charge                                   |       |

| $\mathbf{C}$ | Hardware demonstration details                      | 127   |

|              | C.1 VHDL blocks details                             | . 127 |

|              | C.2 VHDL code extracts                              | . 129 |

| D            | Research trails for the CLIC Interlock System       | 133   |

|              | D.1 Beam quality                                    | . 133 |

|              | D.2 Interlock System and beam operation             | . 133 |

|              | D.3 Interlock System and injection complex          | . 134 |

|              | D.4 Interlock System and radiation                  | . 135 |

|              | D.5 Interlock System and acquisition infrastructure | . 136 |

|              | D.6 Local rules for global analysis                 | . 139 |

| $\mathbf{E}$ | Requirements and constraints list                   | 141   |

|              | E.1 Requirements list                               | . 141 |

|              | E.2 Environment constraints list                    | . 142 |

|              | E.3 External requirements list                      | . 142 |

| F            | Conferences and workshops                           | 143   |

| Gl           | lossary and acronyms                                | 145   |

| Bi           | ibliography                                         | 149   |

# List of Figures

| Standard model particles common representation                          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CERN accelerators complex                                               | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CMS Higgs Search - collision electrons/muons at 8 TeV                   | ç                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CLIC detectors push-pull scheme [1]                                     | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Schematic overview of the CLIC layout                                   | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Illustration of two beam accelerating scheme                            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Simulation of a Higgs decay at ILC detector (courtesy to Norman Graf) . | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Schematic overview of the ILC layout [2]                                | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

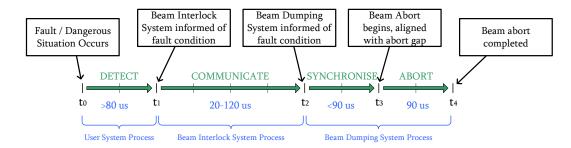

| LHC BIS response time requirement [5]                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

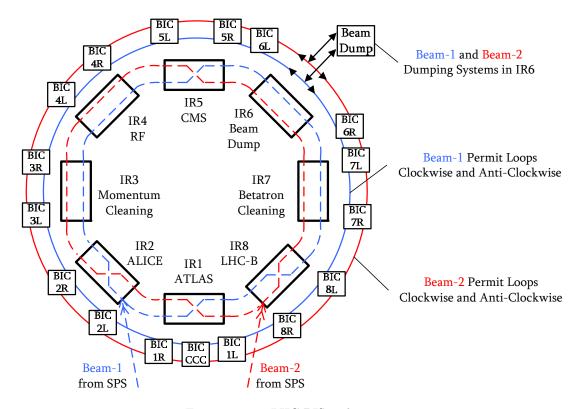

| LHC BIS architecture                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

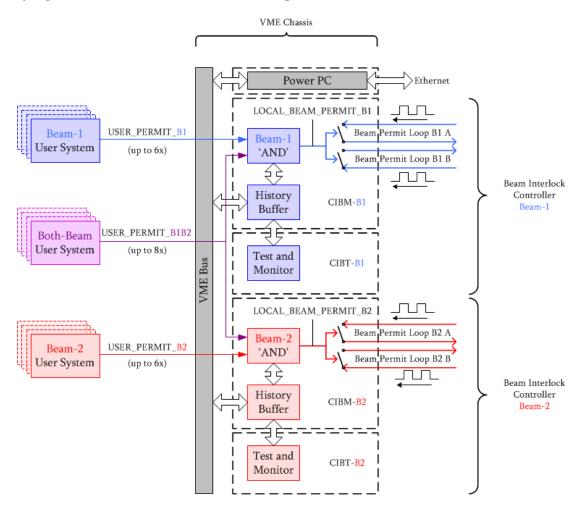

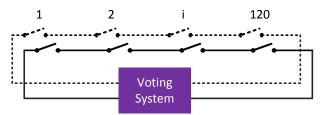

| LHC BIS Node synoptic view                                              | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

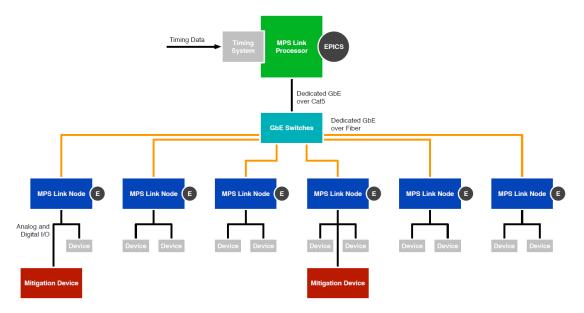

| LCLS Interlock System Architecture [6]                                  | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

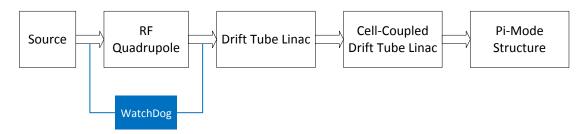

| Linac 4 Watchdog implementation example                                 | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

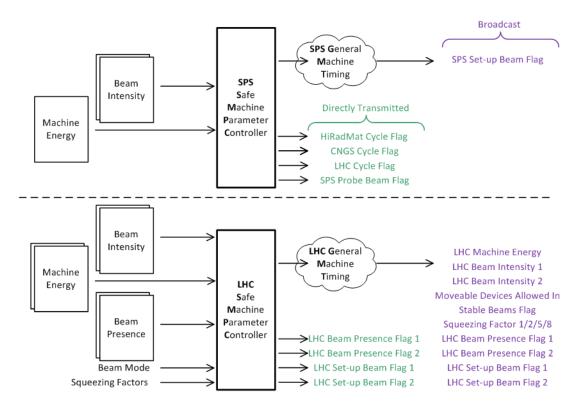

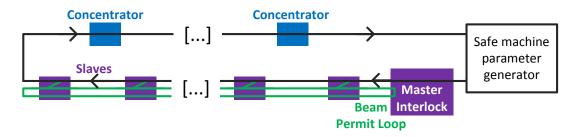

| Safe Machine Parameter Overview [7]                                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • 0 0                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

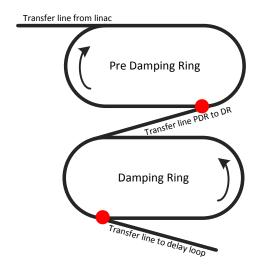

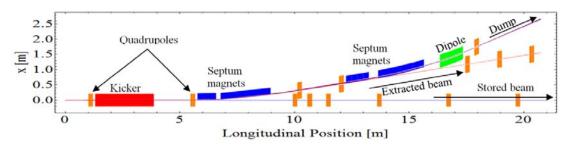

| Damping rings dump system [9]                                           | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

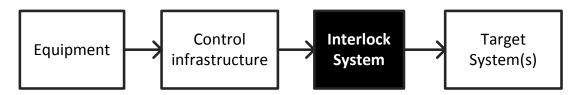

| Interlock System functional black box                                   | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ·                                                                       | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ·                                                                       | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ·                                                                       | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| - · · · · · · · · · · · · · · · · · · ·                                 | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                         | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

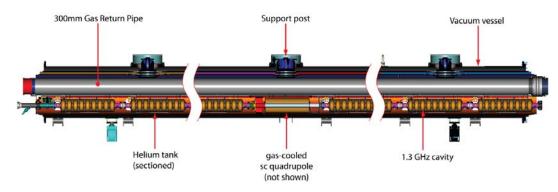

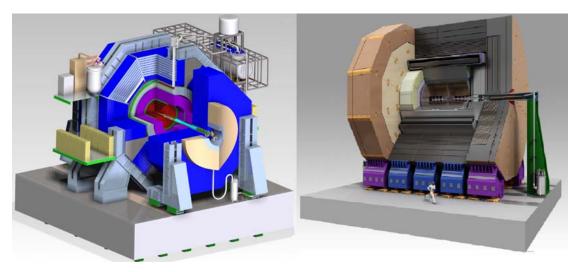

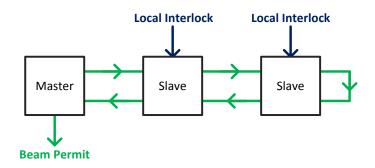

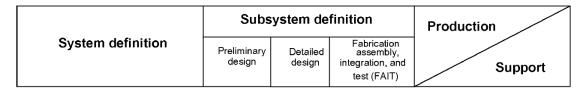

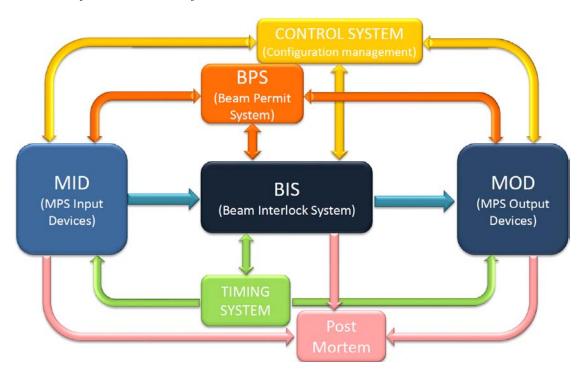

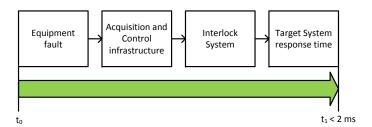

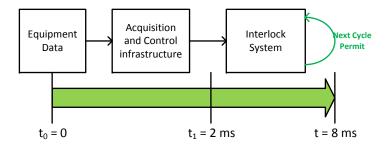

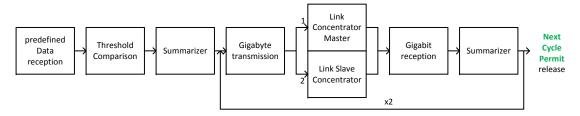

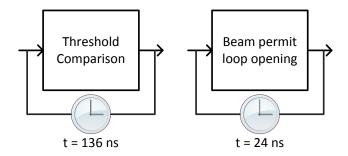

|                                                                         | CERN accelerators complex  CMS Higgs Search - collision electrons/muons at 8 TeV  CLIC detectors push-pull scheme [1]  Schematic overview of the CLIC layout  Illustration of two beam accelerating scheme  Simulation of a Higgs decay at ILC detector (courtesy to Norman Graf)  Schematic overview of the ILC layout [2]  Schematic the ILC cryomodule [2]  ILC Detectors - SiD (left) and ILD (right) [2]  Beam permit concept  Typical system life cycle [3]  Generic Interlock System overview [4]  LHC BIS response time requirement [5]  LHC BIS architecture  LHC BIS Node synoptic view  LCLS Interlock System Architecture [6]  Linac 4 Watchdog implementation example |

List of Figures 10

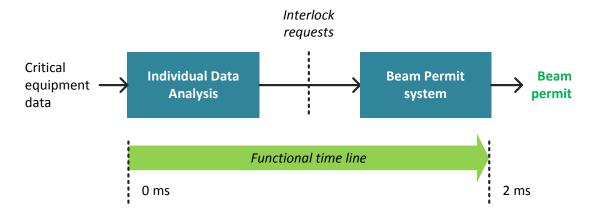

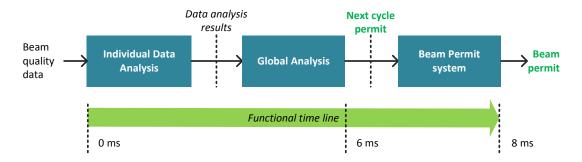

| 4.7 Functional time line and data flow - Beam quality input                | . 62  |

|----------------------------------------------------------------------------|-------|

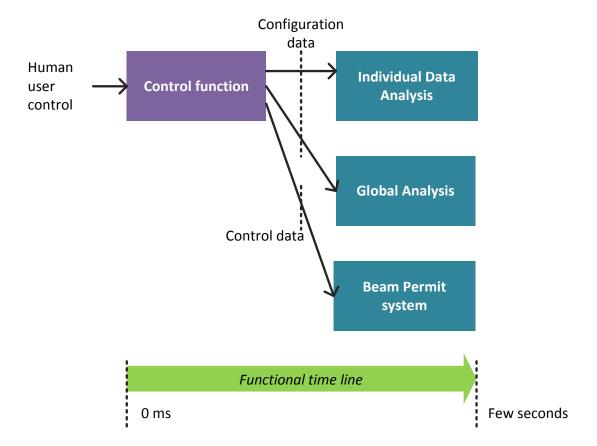

| 4.8 Functional time line and control flow                                  | . 63  |

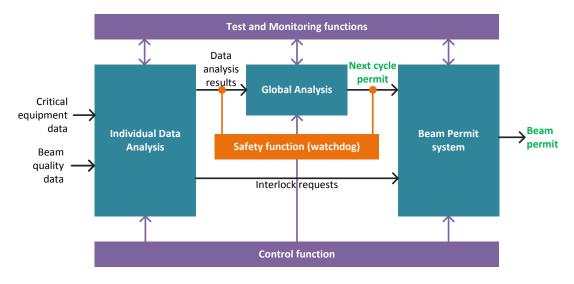

| 4.9 Functional architecture schematic                                      | . 65  |

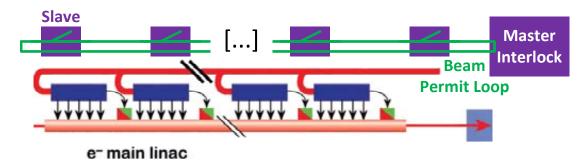

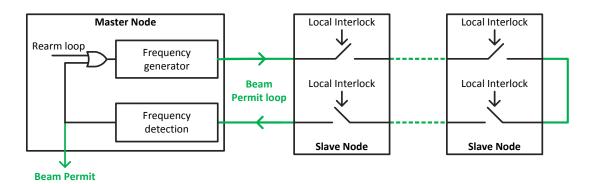

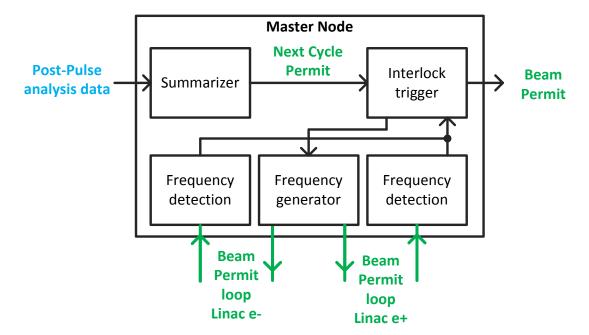

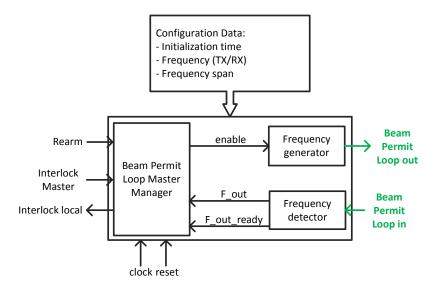

| 4.10 Beam permit loop implementation                                       | . 67  |

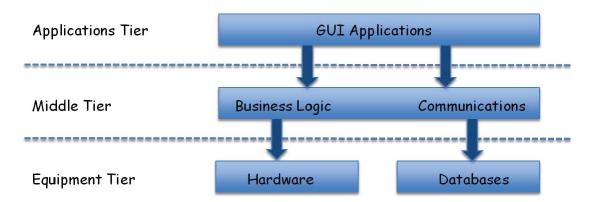

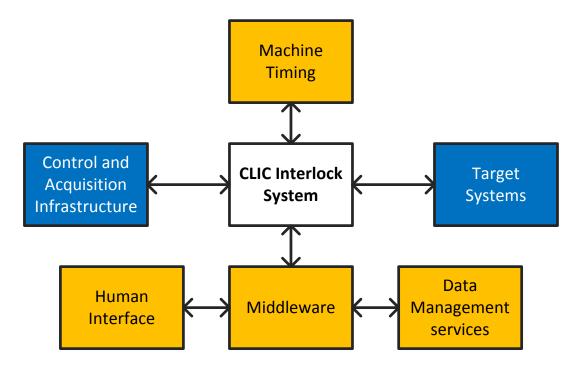

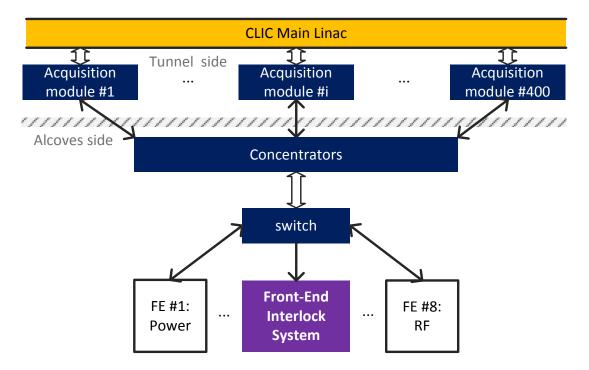

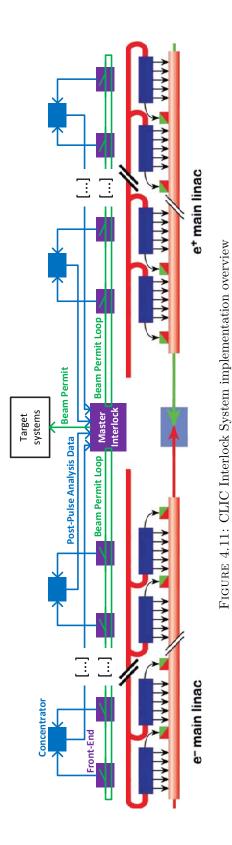

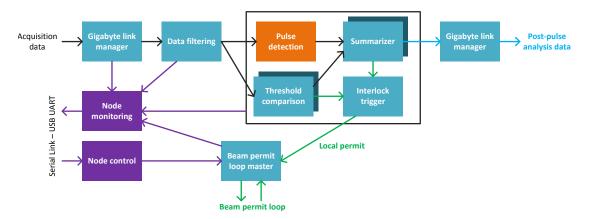

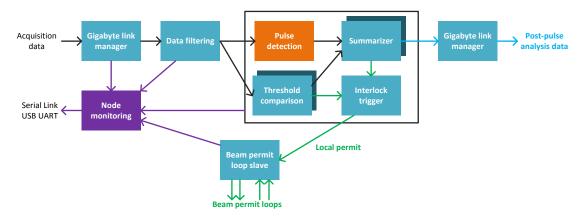

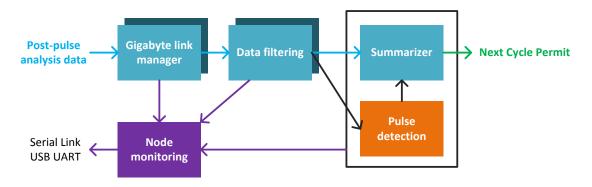

| 4.11 CLIC Interlock System implementation overview                         | . 70  |

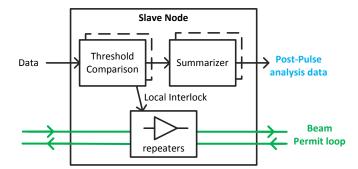

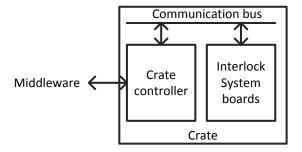

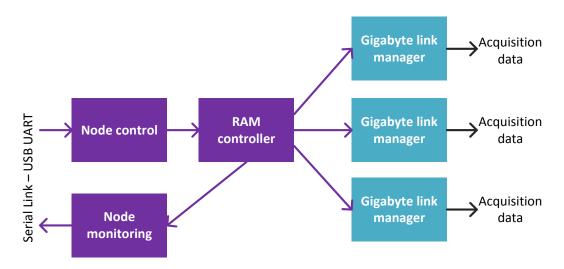

| 4.12 Slave node hardware module synoptic                                   | . 71  |

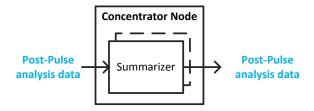

| 4.13 Concentrator node hardware module synoptic                            |       |

| 4.14 Master node hardware module synoptic                                  |       |

| 4.15 Nodes monitoring                                                      |       |

|                                                                            |       |

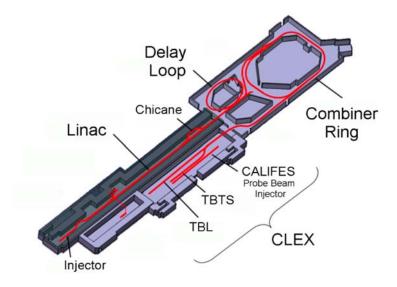

| 5.1 CTF3 general layout                                                    |       |

| 5.2 Application principle synoptic                                         |       |

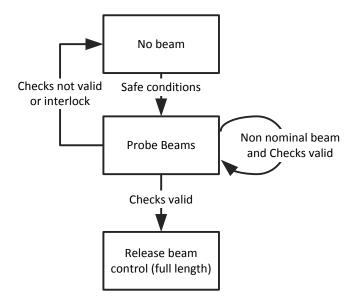

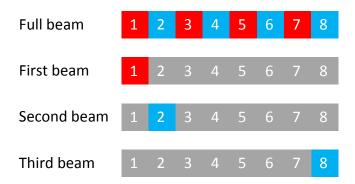

| 5.3 Application probe beams                                                |       |

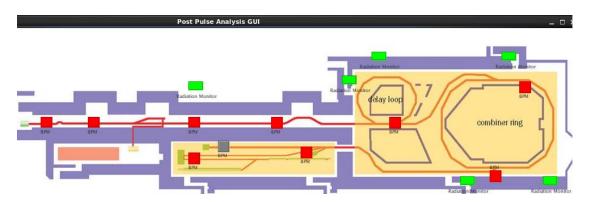

| 5.4 Application post-pulse analysis GUI                                    |       |

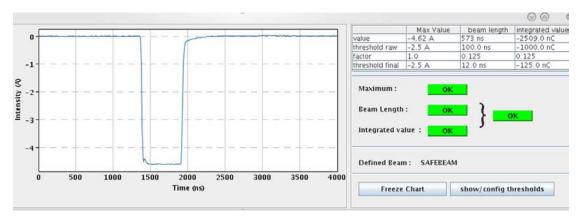

| 5.5 Application beam position monitor GUI                                  |       |

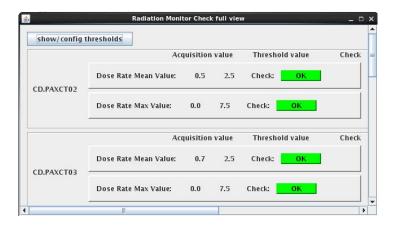

| 5.6 Application radiation monitor GUI                                      |       |

| 5.7 Application logbook - post-pulse analysis failure                      |       |

| 5.8 Application logbook - post-pulse analysis success                      |       |

| 5.9 Suggestion of the safe machine parameter integration                   | . 85  |

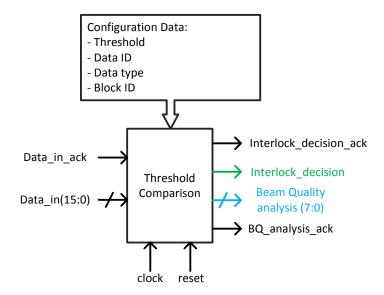

| 5.10 Threshold comparison VHDL module - synoptic                           | . 89  |

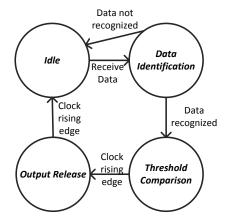

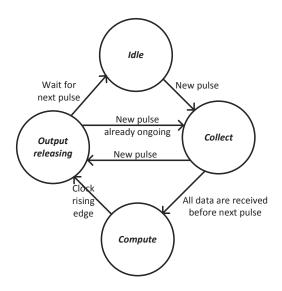

| 5.11 Threshold comparison VHDL module - state machine                      | . 89  |

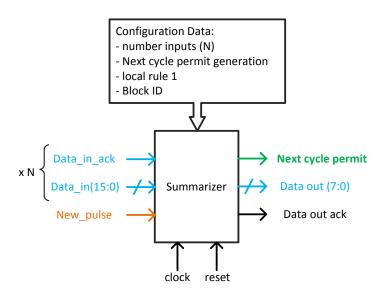

| 5.12 Summarizer VHDL module - synoptic                                     | . 90  |

| 5.13 Summarizer VHDL module - state machine                                | . 91  |

| 5.14 Beam permit loop VHDL module - master synoptic                        | . 92  |

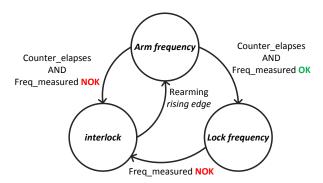

| 5.15 Beam permit loop VHDL module - master state machine                   | . 92  |

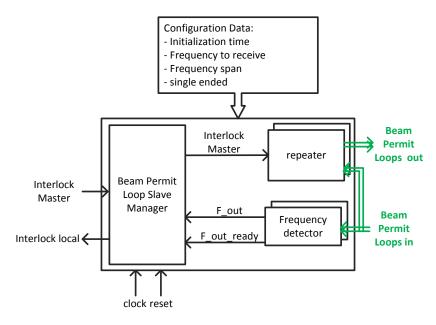

| 5.16 Beam permit loop VHDL module - slave synoptic                         | . 93  |

| 5.17 Beam permit loop VHDL module - slave state machine                    |       |

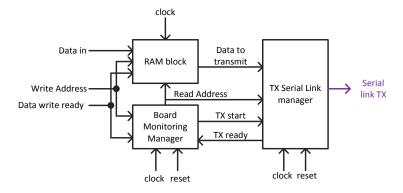

| 5.18 Board monitor VHDL module - synoptic                                  |       |

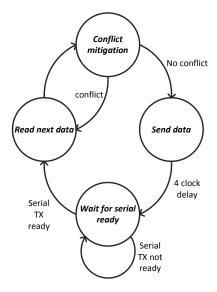

| 5.19 Board monitor VHDL module - state machine                             |       |

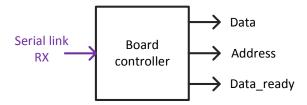

| 5.20 Board controller VHDL module - synoptic                               |       |

| 5.21 Board controller VHDL module - state machine                          |       |

| 5.22 Master node - VHDL configuration                                      | . 98  |

| 5.23 Slave node - VHDL configuration                                       |       |

| 5.24 Concentrator node - VHDL configuration                                | . 99  |

| 5.25 Test controller node - VHDL configuration                             |       |

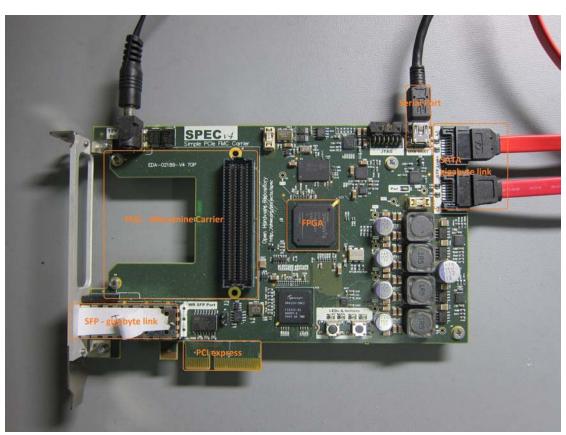

| 5.26 Simple PCI-Express FMC Carrier (SPEC) board overview                  | . 100 |

| 5.27 XM104 FMC board                                                       |       |

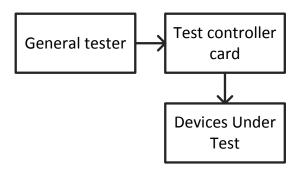

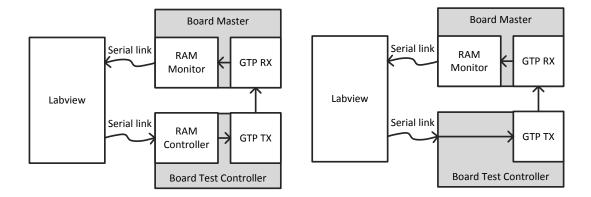

| 5.28 Test bench policy                                                     |       |

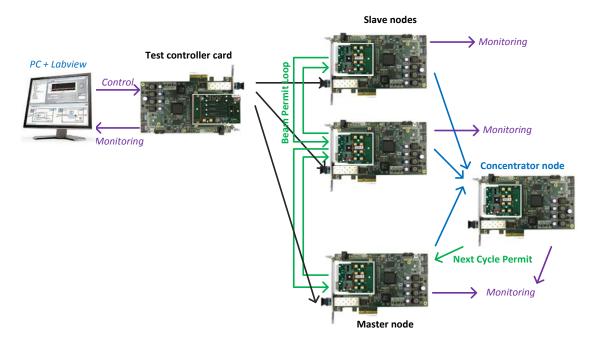

| 5.29 Test bench overview                                                   | . 102 |

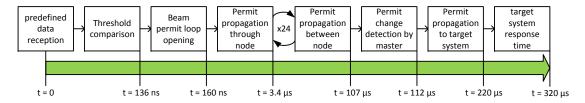

| 5.30 Machine interlocking global chain of event                            | . 103 |

| 5.31 Machine interlocking system chain of event                            | . 104 |

| 5.32 Post-pulse analysis global chain of event                             |       |

| 5.33 Post-pulse analysis system chain of event                             |       |

| 5.34 Machine interlocking response time measurements - inside FPGA         |       |

| 5.35 Machine interlocking response time measurements - fibres              | . 107 |

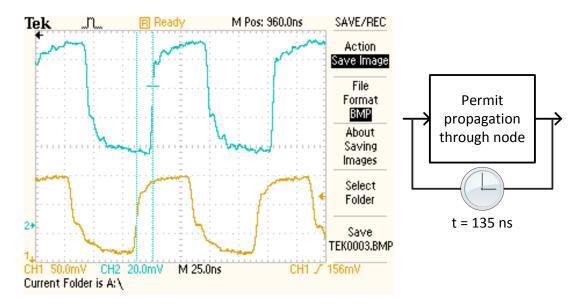

| 5.36 Machine interlocking response time measurements - nodes               | . 108 |

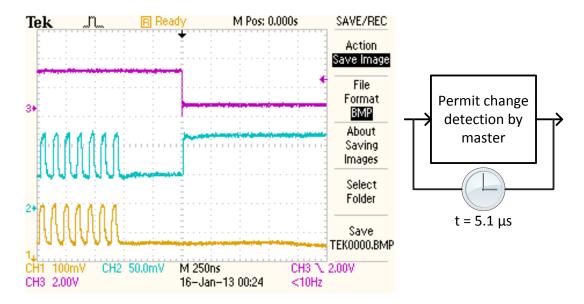

| 5.37 Machine interlocking response time measurements - frequency detection | . 108 |

List of Figures 11

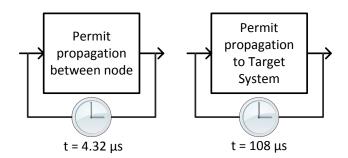

| 5.38 | Machine interlocking response time measurements - synthesis 109                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

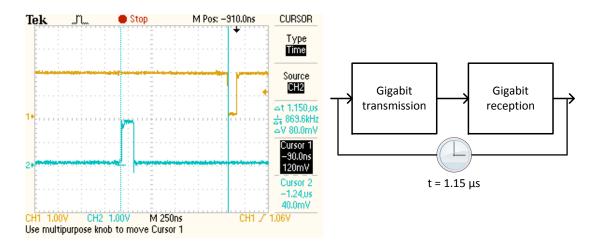

| 5.39 | Post-pulse analysis response time measurements - gigabyte link 110                                                                                             |

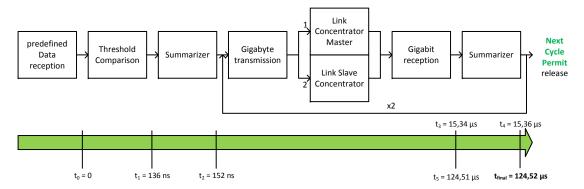

| 5.40 | Post-pulse analysis response time measurements - synthesis $\ \ldots \ \ldots \ \ldots \ 111$                                                                  |

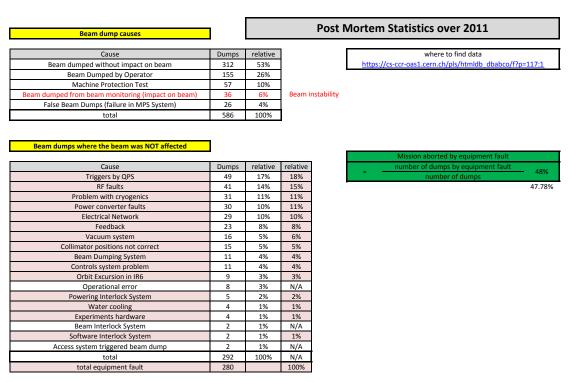

| A.1  | Post-mortem system data - 2011                                                                                                                                 |

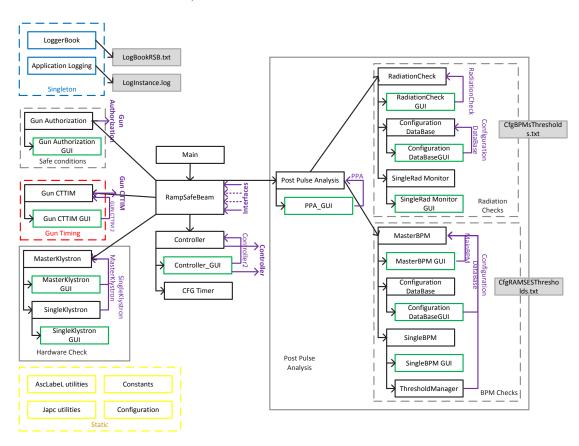

| B.1  | CTF3 Application classes overview                                                                                                                              |

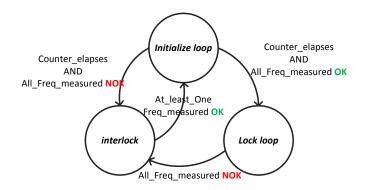

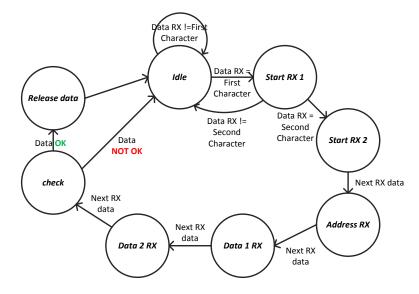

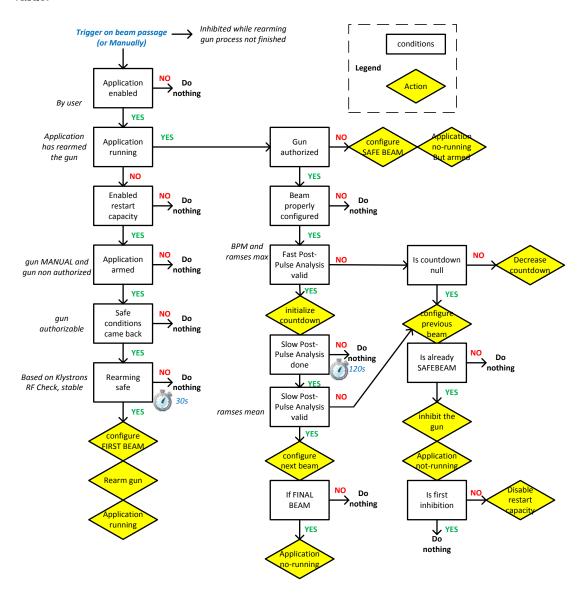

| B.2  | CTF3 Application finite state machine                                                                                                                          |

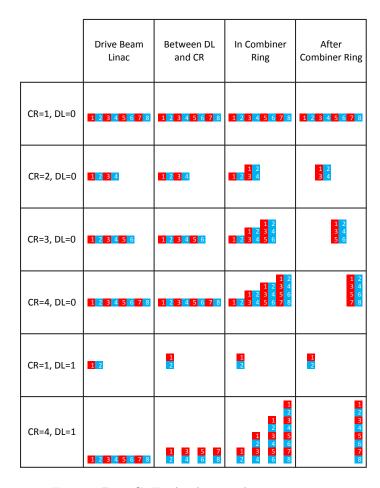

| B.3  | CTF3 Application beam operation                                                                                                                                |

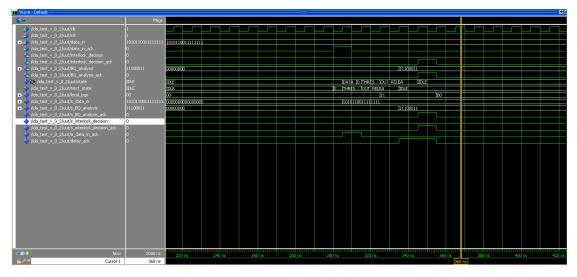

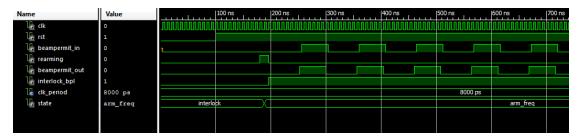

| C.1  | Threshold comparison VHDL block - Simulation                                                                                                                   |

| C.2  | Threshold comparison VHDL block - Code coverage report                                                                                                         |

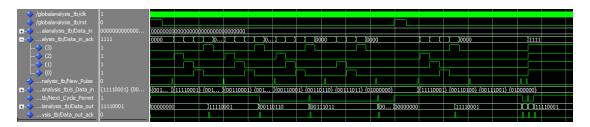

| C.3  | Summarizer VHDL block - Simulation                                                                                                                             |

| C.4  | Summarizer VHDL block - Code coverage report                                                                                                                   |

| C.5  | Beam permit loop VHDL block - Simulation master                                                                                                                |

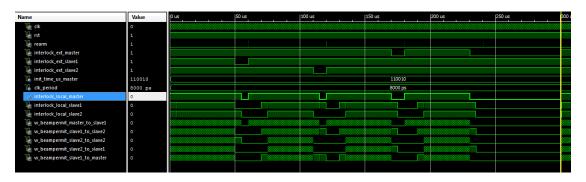

| C.6  | Beam permit loop VHDL block - Simulation complete loop 129                                                                                                     |

| C.7  | Control VHDL block - implementation                                                                                                                            |

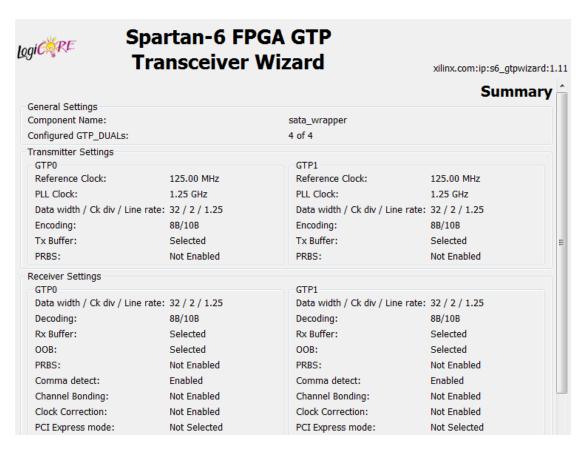

| C.8  | Gigabyte link VHDL block - wizard option                                                                                                                       |

| C.9  | VHDL block - GENERATE illustration                                                                                                                             |

| C.10 | VHDL block - Threshold comparison configuration illustration 131                                                                                               |

| C.11 | VHDL block - summarizer core function                                                                                                                          |

| C.12 | VHDL block - summarizer local rule example $\dots \dots \dots$ |

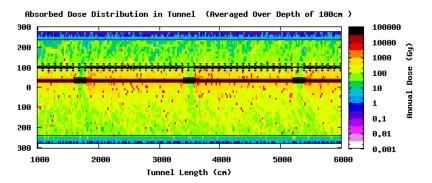

| D.1  | Radiation dose due to the main beam at 1.5 TeV                                                                                                                 |

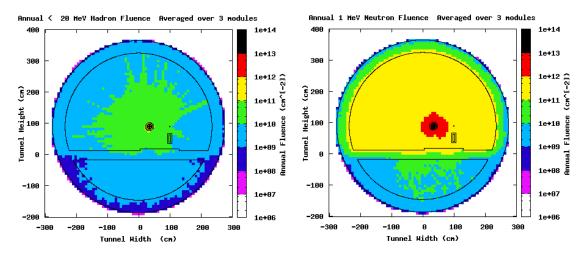

| D.2  | Hadrons and neutrons fluence due to the main beam at 1.5 TeV $136$                                                                                             |

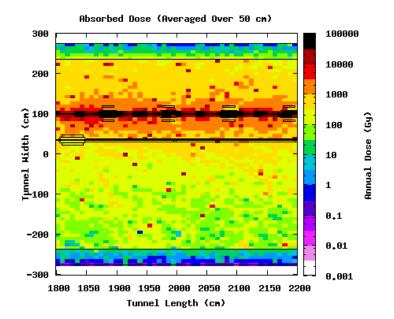

| D.3  | Radiation dose due to the drive beam at 2.4 GeV                                                                                                                |

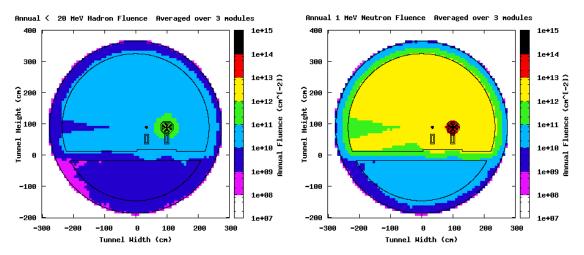

| D.4  | Hadrons and neutrons fluence due to the drive beam at 2.4 GeV 137                                                                                              |

| D.5  | CLIC acquisition crate signals list                                                                                                                            |

# List of Tables

| 2.1 | ILC and CLIC parameters comparison                                           |

|-----|------------------------------------------------------------------------------|

| 3.1 | Risks analysis synthesis                                                     |

| 3.2 | Failure modes requirements                                                   |

| 3.3 | Interlock System Dependability Attribute                                     |

| 3.4 | Redundancy scenario                                                          |

| 3.5 | Simulation Objectives                                                        |

| 3.6 | Simulation results - single node failure rates                               |

| 3.7 | Set of critical interlock channels                                           |

| 4.1 | Interlock system functional behaviour                                        |

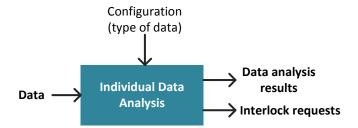

| 4.2 | Individual Data Analysis behaviour                                           |

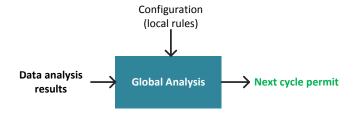

| 4.3 | Next Cycle Permit behaviour                                                  |

| 5.1 | CTF3 vacuum leak events                                                      |

| 5.2 | Measurements results                                                         |

| D.1 | Annual CLIC radiation and fluence for electronic systems in the tunnel . 135 |

| E.1 | Simulation results - single node failure rates                               |

## Chapter 1

# General Introduction

When entering in the particles accelerators field, the first thought that may arise is to realize the impressive complexity of these machines. Building these huge scientific tools requires the cooperation of many sectors: super-conductive magnets, Radio Frequency cavities, electronics (analog, numeric, microelectronic), cryogenic, vacuum, beam physics, mechanics, electric powering, etc. Building more and more powerful machines has created a need of protection and a new sector dedicated to the machine protection has been set up [10]. Indeed, the energy reached by the beam (360 MJ for the Large Hadron Collider (LHC)) and stocked in the equipment (10 GJ in LHC magnet system) are way more higher than the energy needed to melt on kilogram of copper (i.e. 700kJ) [11]. Consequently, particles accelerators can easily be damaged in case of uncontrolled energy release. The Interlock Systems are part of the machine protection. An Interlock System stops the machine when an unsafe condition occurs. The goal is to stop before the uncontrolled energy deposition.

The European Organisation for the Nuclear Research (CERN) is one of the larger particles physics laboratory. Created in 1954, many machines have been built and part of them are still in operation. However, due to physics challenges evolution, new machines are studied. Among them, CERN has taken a leading part of the Compact Linear Collider (CLIC) [12] [13] [1] study and has started a close collaboration with the International Linear Collider (ILC) project. They both aim to explore new physics revealed by current accelerators and to test predicted theories: Higgs boson [14], dark matter [15], supersymmetrie [16], beyond the standard model [17], etc.

The CLIC design faces several challenges [18]. As it is a linear machine, the acceleration cavities are used only once and require a strong gradient. Thus, a novel two beams acceleration scheme has been introduced. Its feasibility demonstration is a crucial point for the project. Another critical feasibility study is the machine protection and the beam

operation. Part of it, the CLIC Interlock System study has been undertaken in the form of a thesis, presented in this manuscript.

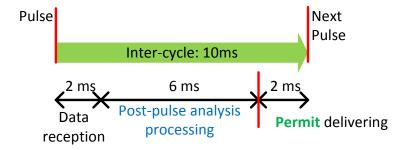

In the CLIC machine protection framework, the Interlock System concepts have been defined [19]. It is based on a beam permit system [20] and a new post-pulse analysis, dedicated to linear colliders.

The thesis works attempt to answer the following question: how to design an Interlock System for a linear collider?

From the state of the art, some works have already been done on the Interlock System design. Indeed, a thesis has been performed on the LHC Interlock System to carry on the work from prototype to a fully tested and operational system [5]. Another example is the recent method to use Programmable Logic Device (PLD) in similar systems [21]. The presented thesis works undertake the design from concepts up to the prototype, thus complementing the two previously mentioned works.

To answer the main problematic, we propose to introduce an industrial methodology inspired by a system engineering standard, and to apply it to the CLIC Interlock System project. The goal is to be transparent on each method steps, thus allowing understanding, enhancement and correction of the design. The idea behind is to be able to use this method as a basis to develop future interlock systems. A special focus is proposed to be taken for the dependability, as it is a critical quality for an Interlock System.

Chapter 2 presents the context, starting from the physics particles challenges up to the CLIC machine protection. It expands on the problematic of the thesis and performs the state of the art on interlock and selected protection systems.

In chapter 3, the conditions of use and the system interfaces are defined. The central part is the establishment of the functional and performance requirements. It is done with an Institute of Electrical and Electronics Engineers (IEEE) standard as a guideline. A part of the chapter is dedicated to reliability and availability requirements determination. It proposes a methodology to verify if a design is compliant with these requirements. The last part explains in details the critical interfaces, extract the constraints, and how the expectations from the Interlock System to these interfaced systems are produced.

Chapter 4 presents the Interlock System design proposal. It explains the functional analysis done with the help of the IEEE standard. Finally, the implementation proposal, based on the functional analysis and concepts to implement, is presented. Going further, it proposes an implementation to the hardware modules level.

In chapter 5, the design verification is explained. The feasibility study performed in CLIC Test Facility 3 (CTF3) is presented: it is studying the post-pulse analysis application

in operational environment through a JAVA software. The hardware demonstration is described from the VHDL blocks up to the whole test bench. The measurements which aim to prove the design compliance are then examined.

Finally, the chapter 6 concludes the thesis works. It is proposing the short and long term improvements that would enhance these works.

# Chapter 2

# Context and state of the art

#### 2.1 Introduction

This thesis is focused on the design process of a dependable interlock system, applied to the CLIC. Before going into the design process, there are two needs: to explain the context and to define the starting point of the thesis works.

This chapter follows a top-bottom approach. The nowadays challenges in particle physics are introduced. The involvement in this field of the CERN, where the thesis has been done, is presented. Going more specific, the interest is focused on two proposed high energy linear colliders: the CLIC and the ILC. The next step is to give an overview of the CLIC machine protection strategy. It leads to introduce the CLIC Interlock System concepts. At that point, the problematic of the thesis is set up. The two last sections are dedicated to the background on protection systems related to interlock systems. The fifth section presents the interlock systems in a generic way, synthesizing the state of the art. The last section is more specific and presents five selected protection systems which are the main design references for these thesis works.

### 2.2 Particle Physics and CERN

In order to explain the thesis subject, it is needed to introduce the particles accelerators and therefore their purposes. It starts with the standard model.

#### 2.2.1 Challenges in particle physics

The goal in physics is to understand the basic structures and laws, from infinite high scale (stars, galaxies clusters) to infinite low scale (fundamental particles) [22].

#### a. Building the standard model

The particle physics has started with the discoveries of different atoms. A great simplification has been made when it has been realized that atoms can be unified with three particles: protons, neutrons and electrons.

In the beginning of the twentieth century, new particles from cosmic rays have been discovered. There was no system to classify them. They have been organized in regard with their properties: mass, charge, spin and lifetime (time before decay in lighter particles).

To simplify this organization, new particles, so-called quarks, have been predicted. Their combination can describe the other particles. This is the birth of the standard model.

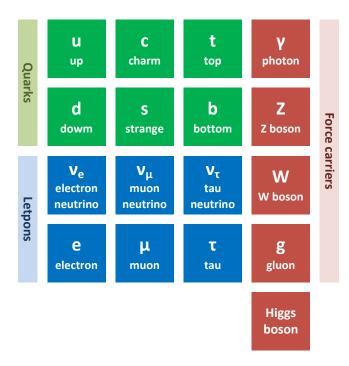

The standard model comprises fundamental particles (6 quarks and 6 leptons) and fundamental forces as represented in Figure 2.1, [17]. The forces are represented via force carriers:

- The weak force is seen through the bosons W and Z. It explains the energy production in the sun and the radioactivity.

- The electromagnetic force carrier is the photon. It is responsible for the transmission of light and magnet attraction force.

- The strong force is represented with gluons. It is responsible for nucleus cohesion.

To synthesize, the standard model is unifying the strong, weak and electromagnetic forces. It is very precise at both low and high energy. However, it remains incomplete: new particles and interaction are needed to cover some gaps.

#### b. Beyond the standard model

The standard model has several limitations [2], [17]:

- It does not explain how gravity is connected to the other fundamental forces. In other words, it does not comprise the Einstein's general theory of relativity.

- It does not explain why the fundamental particles are the quarks and leptons (and their numbers).

- It does not explain the unbalance between matter and antimatter.

FIGURE 2.1: Standard model particles common representation

- It does not explain the existence of the dark matter and dark energy.

- It does not explain the mass existence of neutrinos.

However, several models beyond the standard model have been predicted. One of them predicts a mechanism called Higgs field [14], which gives mass to fundamental particles. This hypothesis could contain particles with properties similar to dark matter. This Higgs field could be studied through its particle: the Higgs boson.

#### c. Challenges in particle physics

Hereunder are presented a selected bunch of nowadays challenges in particle physics :

**Dark matter/energy** The known matter (galaxies) is estimated to account only for 4% of the content of the universe. What remaining is dark matter and dark energy. Despite there are evidences of these phenomenons (gravitational clues), no theories have been proved until now. Some of them are related with particle physics such as the supersymmetry theory [16] or the hidden valley theory [15].

**Supersymmetry** The supersymmetry is a theoretical expansion of the standard model. It predicts a partner particle for each particle of the standard model: standard bosons would have supersymmetric fermions and the other way around. This theory

would resolve several gaps of the standard model (among them, the Higgs boson mass). It would unify the force strength at very high energy, making more understandable the state of the early universe. It would be a step closer to the grand unified theory.

Gravity and standard model Several tracks to include the gravity force to the standard model are followed. There is research for the hypothetical gravitons. Another point is to explain why the gravitation is so weak compared to the three other forces. Some hypothesis predict tiny black holes or extra dimensions that could appear during collisions. It could be a solution to this challenge.

**Compositeness** The compositeness is a theory predicting every particle of the standard model are made up of smaller unit called *preons*.

There are many other challenges that have not been described (neutrino mass, muons physics, extra dimensions, grand unifications). These particle physics challenges are studied by many institutes and laboratories around the world: for instance the Fermi National Accelerator Laboratory (FNAL) in North America, the Shanghai Institute of Applied Physics (Sinap) in Asia, the European Synchrotron Radiation Facility (ESRF) and CERN in Europe. The thesis has been undertaken at CERN.

#### 2.2.2 European Organisation for the Nuclear Research

The CERN is the world's largest particle physicist laboratory. It is made up of 20 member states. More than 600 institutes and universities use CERN facilities. About 10000 scientists working in collaboration and 2400 are employed by CERN.

The CERN's aims is the fundamental research in high energy physics. Its goal is to study fundamental structure of universe and state of the matter. The CERN intends to carry on the challenges previously mentioned.

The research tools used at CERN are particles accelerators. The principle is to accelerate particle beams (protons, leptons or ions) and make them collide together or with a fixed target. The resulting collisions are then studied by detectors.

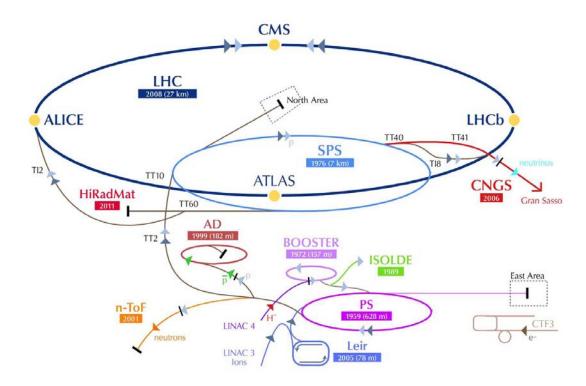

In Figure 2.2 is represented the accelerator complex at CERN. It is a chain of small accelerators (like Linac 4) pre-accelerating and bunching the beam up to large accelerators like the Super Proton Synchrotron (SPS) or the more known LHC.

FIGURE 2.2: CERN accelerators complex

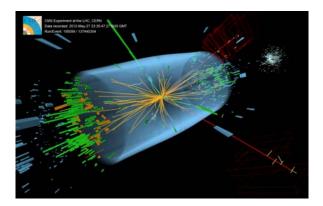

The beam collisions are studied by many experiments at different locations of the complex. In the LHC case, there are two multi-purposes detectors: ATLAS (A Toroidal LHC ApparatuS) and CMS (Compact Muon Solenoid). They both look for Higgs boson, extra dimensions and dark matter. In Figure 2.3 is represented the type of event registered with beam collisions.

FIGURE 2.3: CMS Higgs Search - collision electrons/muons at 8 TeV

There are also specialized detectors like ALICE (A Large Ion Collider Experiment), studying heavy ions for quark-gluon plasma understanding and LHCb (LHC beauty), studying matter/antimatter through the quark beauty.

Apart LHC, there are many other experiments that use beam collisions: for instance COMPASS (Common Muon and Proton Apparatus for Structure and Spectroscopy), which looks into hadrons structure to study spin property. We can cite CLOUD (Cosmics Leaving Outdoor Droplet), which studies link between cosmic rays and cloud formation.

To finish, the Antiproton Decelerator (AD) is used for many experiments to study antimatter, from earth gravitational acceleration measurement to cancer therapy suitability.

CERN is not only about high energy physics. It is pushing the technology frontier for supporting the research. The main example is the world wide web created at CERN to share physics data over the world (first website: http://info.cern.ch/).

#### 2.3 High energy linear colliders overview

The high energy lepton linear colliders are the most desirable high energy facilities after LHC era. The hadrons colliders such as the LHC are used at the energy frontier as discovery facilities. Conversely, leptons colliders are used for precision physics. Currently, two linear colliders are proposed: the ILC and the CLIC. The ILC is based on superconducting technology in the TeV range (0.5 TeV) whereas the CLIC is designed on a new two beams acceleration approach in the multi-TeV (3 TeV) range. The choice of the built machine will be based on one hand on their technological maturity and on the other hand on the requirements from physics results. Therefore, a close and fruitful collaboration is established between ILC and CLIC.

The last lepton collider at CERN was the Large Electron-Positron collider (LEP). This circular collider was energy-limited by the synchrotron radiation effect. This parasite radiation is proportional to the invert of the cubic mass of the particles. Consequently, light particles such as electrons and positrons induce bigger radiation than hadrons. Linear accelerators consequently avoid the synchrotron radiation. The main disadvantage of a linear collider is that the accelerating cavities are used only once, implying a much longer complex than a circular collider for equivalent energy.

#### 2.3.1 CLIC overview

The CLIC is an international project with collaborations with more than 30 institutes around the world. The project is currently in a research and development phase. The next step is to deliver a technical design report (projected for 2016). The main issue is to demonstrate the feasibility of this extensive project, whether in term of cost, time or

technological challenges. Therefore, a test facility named CTF3 has been built for the feasibility study.

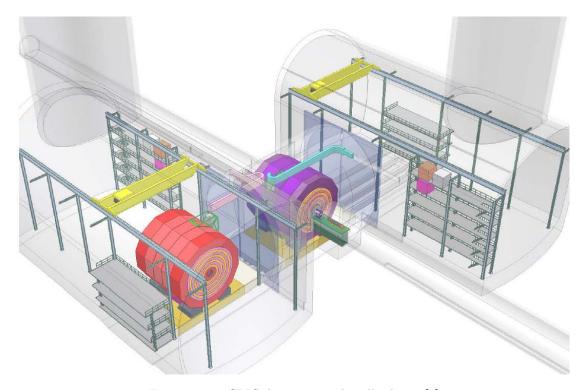

The CLIC aims to provide particles collisions at a center-of-mass energy of 3 TeV. The luminosity will be reached with powerful beam (14 MW for the main beam) and collision with extremely small dimensions (emittance of 1 nm on vertical plane). Because the accelerating structures are used only once per pulse, they are required to have a high gradient of  $100 \ MV/m$ . The CLIC project foresees to have only one interaction point (IP). At this area, a push-pull concept will allow to have two detectors in the same cavern, as similar to the ILC project (Figure 2.4).

FIGURE 2.4: CLIC detectors push-pull scheme [1]

#### a. CLIC scheme overview

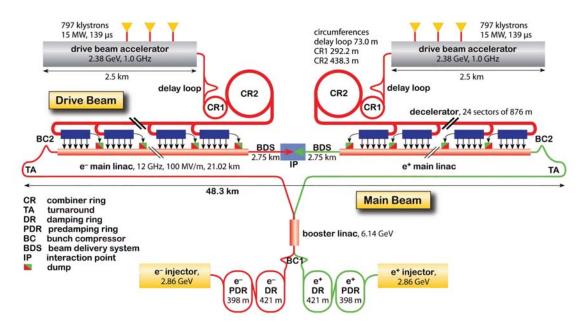

In this paragraph, a short explanation of the CLIC layout (Figure 2.5) is given.

Main beam complex: The injection complex is the source of particles. It generates 2.4 GeV electrons and positrons. The positrons are generated by shooting some electrons into a hybrid target.

The damping ring aims to reduce drastically the beam emittance. It has to generate the smallest emittance than ever achieved, 500 nm horizontally and 5 nm vertically.

FIGURE 2.5: Schematic overview of the CLIC layout

The Ring To the Main Linac (RTML) aims to prepare the beam to the main linac injection. It is made up of a booster linac, which accelerates the beam at 9 GeV, a transfer line of 21 km, the turnaround, decreasing the emittance through synchrotron radiation and finally the bunch-compressor, delivering the beam to the main linac.

The main linac is a 21 km long accelerator where the main beam energy is increased from 9 GeV to 1.5 TeV. The beam delivery system aims to guide safely the 15 MW beam to the interaction point. At this point, a pair of detectors will be set. The post-collision beam will be then dumped by the beam dumping system.

**Drive beam complex:** The drive beam complex can be divided in three parts. The first part is where the electron trains are generated and then accelerated up to 2.38 GeV.

The second part is the compression stage. The beam will be compressed through a delay loop and two combiner rings, leading to the beam peak current of 100 A.

The third part is the decelerator stage. The drive beam is made up of 24 trains (after the combiner rings) and each one will go to one of the 24 deceleration areas (blue rectangles in Figure 2.5). At that point, the energy will be extracted from the drive beam to the main beam through several Power Extraction and Transfer Structure (PETS).

#### b. Feasibility Issue

Before validating the CLIC project, some critical points must be demonstrated as feasible. These feasibility issues [18] are listed hereafter.

The first challenge is the drive beam generation. This beam has to be generated with a 100 A stable intensity, with a 12 GHz bunch generation and a frequency multiplication factor of 24.

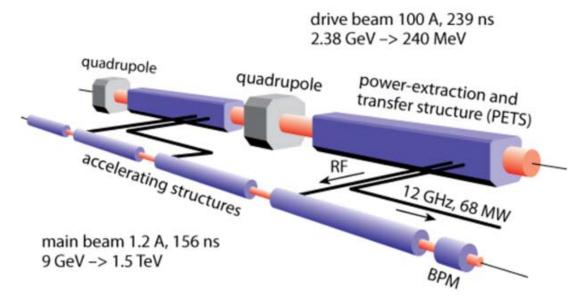

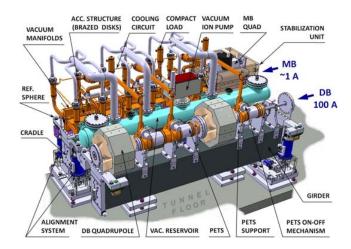

The second point is the drive beam Radio Frequency (RF) generation, more precisely, the PETS development. Its principle is to transmit RF power from a low-energy high-intensity beam (drive beam) to a low-intensity high-energy beam (main beam) which will be involved in collisions. This concept is represented in Figure 2.6.

FIGURE 2.6: Illustration of two beam accelerating scheme

The third challenge is the high gradient of accelerating structures (100 MV/m). This parameter must be reached with a RF efficiency of 27% and a breakdown rate lower than  $3.10^{-7}.m^{-1}$ .

As said before, one of the CLIC novel approaches is the two beams acceleration scheme. This concept has to be demonstrated in compact module, including all technical subsystems such as RF and vacuum. It has to send the RF energy from the drive beam to the main beam with a pulse length of 170 ns. This operation involves a high beam to beam stability (accuracy of 0.07 ps).

A fifth point is the ultra low beam emittance. This parameter is a mandatory condition for high luminosity. The CLIC system has to be able to generate ultra low emittance and to preserve it to reach the expected beam size at the interaction point. Another challenge is the alignment and the stabilization system. The CLIC needs a 15  $\mu$ m alignment accuracy, and a vertical displacement lower than 1.5 nm above 1 Hz vibrations.

At least but not the last, the feasibility of the machine operation and the machine protection has to be demonstrated.

#### c. CLIC operational scenario

The safe operation of the CLIC requires testing each system before starting physics experiments. Thence, an operational scenario has been proposed [19]. It allows to test gradually and safely each system of the two beams trajectory. A beam is considered safe when its energy is under the yield limit in copper (62 J/g).

Main Beam operational scenario The nominal main beam is above safe condition by 4 orders of magnitude. In order to ramp up safely the beam, the strategy is to reduce its luminosity. A first decrease can be done by reducing the number of bunches. A second cut is realizable by reducing the current per bunch. Finally, the last reduction comes from the beam size growing (emittance).

The operational scenario consists to send a safe beam. Then, the aim is to cancel progressively the luminosity reduction explained above as long as the protection systems allow it, to finally reach the nominal main beam.

**Drive Beam operational scenario** The drive beam is above the safe condition by a factor of 100. A safe drive beam can be generated by reducing the charge density (less particles).

The operational scenario is to increase the charge density step by step as long as the protection systems allow it.

#### 2.3.2 ILC overview

The ILC is a worldwide international collaboration of 300 institutes. Its global design effort, mandated by the International Committee for Future Accelerators (ICFA)), has led to deliver the *reference* design report in 2007. At that point, high risk challenges have been identified and the research and development on them has led to release the *technical* design report in June 2013.

The ILC is a electron-positron collider of 31 km length. It is based on 15000 SuperConductive Radio Frequency (SCRF) cavities expected to deliver an accelerating gradient of 31.5 MV/m. The particles are accelerated with two linacs to have a collision energy of 0.5 TeV. It is foreseen to have a staged construction, thus starting the collision energy at 0.3 TeV and extensible up to 1 TeV. The collision events will be recorded with two detectors at the interaction region. The *push-pull* mode will be used.

#### a. Physics goals

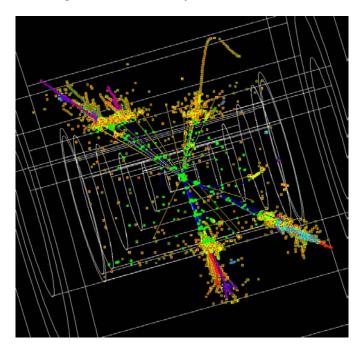

The purpose of the ILC is to take up several physics challenges. First of it, the study of the Higgs boson and associated particles will start at 125 GeV, the collision energy where it must appear (Figure 2.7). The high precision measurements of the rates of the decay of the Higgs boson will be achieved because lepton colliders have less background events than hadron colliders. Moreover, this study will be completed at others energy (250 and 500 GeV) and by the determination of the Higgs boson self-interaction. One of the question of interest is to determine if the Higgs field is the only one to create mass or if there are additional particles which may contribute.

FIGURE 2.7: Simulation of a Higgs decay at ILC detector (courtesy to Norman Graf)

The second challenge that would be undertaken by the ILC is the study of the Supersymmetry. Regarding this theory, it is needed to have a matter-type Higgs particles. The ILC will search for them and measure their properties (quantum numbers and couplings).

A third major challenge to be noticed is the study of new interactions for pair production. It will be focused on W boson and top quark. Moreover the mass of the top quark will be precisely measured. Indeed, this quark is the heaviest fundamental particle in the standard model and may help to understand the Higgs field.

#### b. ILC scheme overview

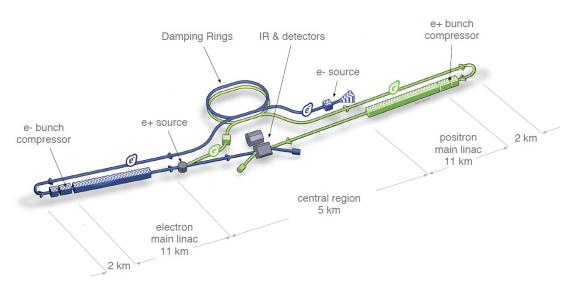

In this paragraph, a short overview of the ILC layout (Figure 2.8) will be explained. From the particle sources Interaction Region, the ILC machine is divided in several parts.

FIGURE 2.8: Schematic overview of the ILC layout [2]

The electrons are generated with a laser/photocathode interaction in a DC gun. Some structures are then bunching and pre-accelerating the particles.

The positrons are generated with the electron beam. The accelerated beam is sent to undulators which generate photons. These photons are then sent to a titanium-alloy target, thus generating electron-positron pairs. A capture system extract the positrons which are then bunched and pre-accelerated.