### Développement d'une méthodologie de caractérisation et de modélisation de l'impact des décharges électrostatiques sur les systèmes électroniques

Nicolas Monnereau

### ▶ To cite this version:

Nicolas Monnereau. Développement d'une méthodologie de caractérisation et de modélisation de l'impact des décharges électrostatiques sur les systèmes électroniques. Energie électrique. Université Paul Sabatier - Toulouse III, 2011. Français. NNT: . tel-01068707

### HAL Id: tel-01068707 https://theses.hal.science/tel-01068707v1

Submitted on 26 Sep 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

#### En vue de l'obtention du

### DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

### Présentée et soutenue par : Nicolas MONNEREAU

le mercredi 7 décembre 2011

Titre:

Développement d'une méthodologie de caractérisation et de modélisation de l'impact des décharges électrostatiques sur les systèmes électroniques

### École doctorale et discipline ou spécialité :

ED GEET : Génie Electrique

Unité de recherche :

LAAS-CNRS

Directeur(s) de Thèse:

Fabrice CAIGNET

Jury:

Rapporteurs:

Dean LEWIS, , James ROUDET

**Examinateurs:**

Jean-Luc LEVANT, Etienne SICARD, Jean-Guy TARTARIN

Membres invités:

Frédéric LAFON, Patrice BESSE

# Laboratoire d'Analyse et d'Architecture des Systèmes du CNRS

# Développement d'une méthodologie de caractérisation et de modélisation de l'impact des décharges électrostatiques sur les systèmes électroniques

Nicolas MONNEREAU

le 7 décembre 2011

Université de Toulouse

### Directeur de thèse :

Dr. F. CAIGNET

### Jury

Pr. D. LEWIS, Rapporteur

Pr. J.ROUDET, Rapporteur

Pr. JG. TARTARIN, Examinateur

Pr. E. SICARD, Examinateur

Dr JL. LEVANT, Examinateur

Dr P. BESSE, Invité

Dr F. LAFON, Invité

### Remerciements

Les travaux présentés dans ce mémoire ont été réalisés au sein du groupe « Intégration de Système de Gestion de l'Energie » (ISGE) du Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS) du CNRS de Toulouse, en partenariat avec les entreprises Freescale basé à Toulouse et Valéo basé à Créteil. Ceux-ci ont été financés par l'Agence Nationale de la Recherche (ANR) dans le cadre du programme nationnale "Véhicules pour les Transports Terrestres" (VTT), pour le projet "Système Electronique Automobile Robuste aux ESD" (E-SAFE).

À l'issue de cette thèse, je souhaite tout d'abord remercier les directeurs successifs du LAAS, Messieurs Raja CHATILA, Jean-Louis SANCHEZ et Jean ARLAT, pour m'avoir accueilli au sein du Laboratoire. Je tiens aussi, à remercier Madame Marise BAFLEUR, directrice du groupe ISGE, pour m'avoir donné les moyens de mener à bien cette étude.

Je tiens tout particulièrement à exprimer ma reconnaissance à mon directeur de thèse, Monsieur Fabrice CAIGNET, Maître de conférences à l'Université Paul Sabatier, pour avoir su me guider, pendant ces années, avec beaucoup d'attention et de gentillesse. Ses qualités scientifiques et humaines, sa disponibilité et sa patience ont contribué à l'aboutissement de cette thèse. Je tiens également à lui exprimer ma profonde reconnaissance pour le temps qu'il a consacré pour finir ce travail dans de bonnes conditions. Je lui adresse par ces quelques mots, ma plus profonde gratitude.

J'adresse également toute ma reconnaissance à Monsieur David TREMOUILLES, chargé de recherche au CNRS, qui m'a initié aux décharges électrostatiques en tant qu'encadrant de stage de Master 2 et qui a fortement contribué à mes travaux de thèse. Pour le remercier de tous les conseils et l'aide qu'il m'a apporté au cours de ces années, je lui dédie la référence 42 de mon manuscrit.

Je souhaiterais aussi remercier Monsieur Nicolas Nohlier, Professeur de l'Université Paul Sabatier, pour avoir été toujours prêt à discuter avec moi, pour ses conseils, ses compétances et ses grandes qualités humaines qui ont contribué à l'avancement de ce travail. Je le remercie également pour les séances de vols de modélisme et d'ULM que nous avons partagées.

Je tiens également à remercier Messieurs Dean LEWIS et James ROUDET, qui ont accepté la tâche d'être rapporteur de mes travaux de thèse. Je remercie également les membres du jury, Messieurs Jean Guy TARTARIN, Etienne SICARD, Jean Luc LE-

VANT, Patrice BESSE et Fréderic LAFON pour leurs commentaires constructifs et pour avoir apporté un regard neuf sur mes travaux.

Je voudrais aussi remercier tous mes collègues, amis du laboratoire pour leur bonne humeur durant mes trois années de thèse et qui ont réussi (ou pas) à me supporter : Ben, Laurent, Jérome, Manu, Christophe, Jean Guy, Emilie, Aude, Bertrand, Toufik, Monsieur Adnan, Houssam, Sandra, Mariane, Thomas, Partice, Jean Philipe, Alain, Jean Luc, Patrick, Karine, Claude ................................... liste non exhaustive à compléter au besoin.

Enfin, c'est avec une profonde émotion que je remercie mes proches et ma famille pour le soutien et la confiance qu'ils m'ont toujours accordés.

## Table des matières

| n                                                                     | trodu | iction § | générale   |                                                             | 13 |

|-----------------------------------------------------------------------|-------|----------|------------|-------------------------------------------------------------|----|

| l Les décharges électrostatiques : état de l'art des moyens de contrô |       |          |            |                                                             | ı  |

|                                                                       | com   | posant   | t aux sys  | tèmes                                                       | 17 |

|                                                                       | 1.1   | Origin   | ne des déc | charges électrostatiques et leurs impacts                   | 17 |

|                                                                       |       | 1.1.1    | Mécanis    | smes de génération de charges électriques                   | 17 |

|                                                                       |       | 1.1.2    | Générat    | cions des décharges électrostatiques                        | 19 |

|                                                                       |       | 1.1.3    | Impact     | sur l'électronique                                          | 20 |

|                                                                       | 1.2   | Aspec    | t compos   | ant:                                                        | 22 |

|                                                                       |       | 1.2.1    | Zone El    | PA (Electrostatic discharge Protected Areas)                | 22 |

|                                                                       |       | 1.2.2    | Modèles    | s de décharges et testeurs industriels                      | 23 |

|                                                                       |       |          | 1.2.2.1    | Modèle et testeur HBM (Human Body Model)                    | 23 |

|                                                                       |       |          | 1.2.2.2    | Modèle et testeur MM (Machine Model)                        | 25 |

|                                                                       |       |          | 1.2.2.3    | Modèle et testeur CDM (Charged Device Model)                | 26 |

|                                                                       |       |          | 1.2.2.4    | Modèle non standardisé CBM (Charged Board Model)            | 27 |

|                                                                       |       | 1.2.3    | Protecti   | ions intégrées dans les circuits                            | 28 |

|                                                                       |       |          | 1.2.3.1    | Principe de fonctionnement d'une structure de protection    | 28 |

|                                                                       |       |          | 1.2.3.2    | Les structures de protection typiques :                     | 30 |

|                                                                       |       |          | 1.2.3.3    | Réseaux de protections ESD d'un circuit                     | 35 |

|                                                                       |       |          | 1.2.3.4    | Les outils de caractérisation et d'optimisation des protec- |    |

|                                                                       |       |          |            | tions                                                       | 38 |

|                                                                       | 1.3   | Aspec    | t système  | 9:                                                          | 41 |

|                                                                       |       | 1.3.1    | Modèles    | s de décharge et testeurs industriels                       | 43 |

|                                                                       |       |          | 1.3.1.1    | Modèle standard IEC 61000-4-2                               | 43 |

|                                                                       |       |          | 1.3.1.2    | Modèle standard ISO 10605                                   | 46 |

|                                                                       |       |          | 1.3.1.3    | Modèle CDE (Cable Discharge Event)                          | 47 |

|                                                                       |       |          | 1.3.1.4    | Modèle HMM (Human Metal Model)                              | 48 |

|                                                                       |       | 1.3.2    | Les pro    | tections externes                                           | 50 |

|                                                                       |       | 1.3.3    | Les pro    | blématiques des ESD au niveau système et les besoins in-    |    |

|                                                                       |       |          | dustriel   | S                                                           | 51 |

|                                                                       | 1 4   | Concl    | usion      |                                                             | 53 |

| Mét  | éthodologie de modélisation d'un système soumis à des décharges électro- |             |                                                          |    |  |

|------|--------------------------------------------------------------------------|-------------|----------------------------------------------------------|----|--|

| stat | iques                                                                    |             |                                                          | 55 |  |

| 2.1  | Introd                                                                   | luction .   |                                                          | 55 |  |

| 2.2  | Princi                                                                   | pe de mo    | délisation                                               | 55 |  |

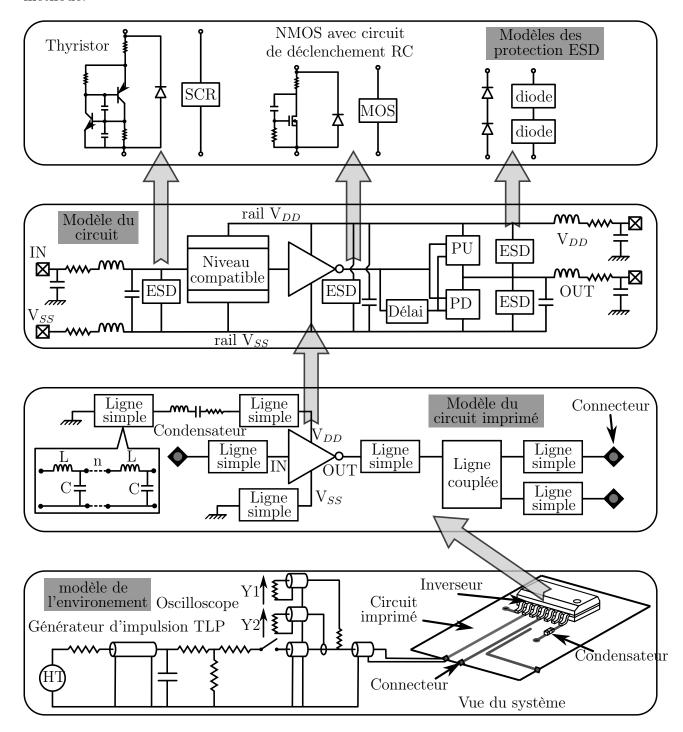

| 2.3  | Modé                                                                     | lisation di | u circuit                                                | 57 |  |

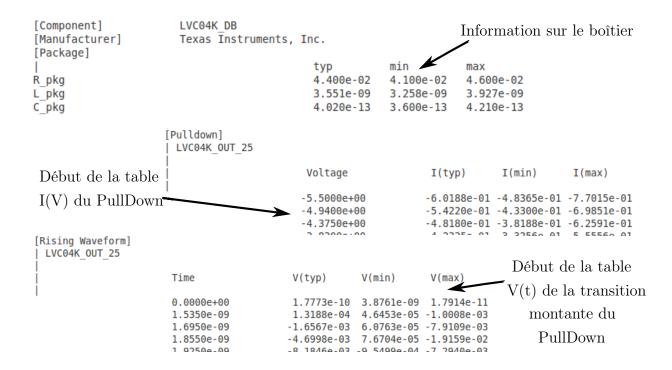

|      | 2.3.1                                                                    | Informa     | tions disponibles pour la modélisation du circuit :      | 57 |  |

|      | 2.3.2                                                                    | Descript    | tion des modèles IBIS                                    | 58 |  |

|      |                                                                          | 2.3.2.1     | Principe des modèles IBIS                                | 58 |  |

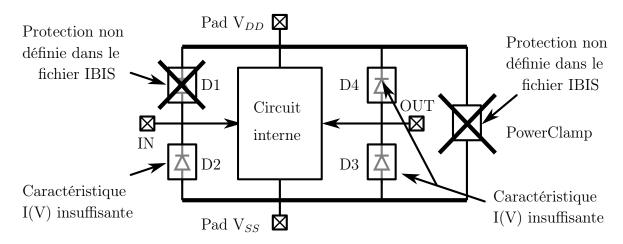

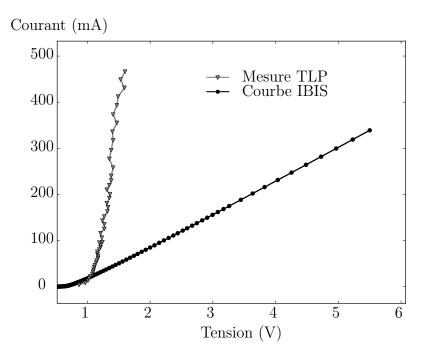

|      |                                                                          | 2.3.2.2     | Lacunes pour les simulations ESD                         | 60 |  |

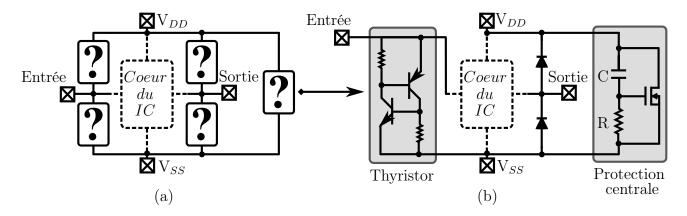

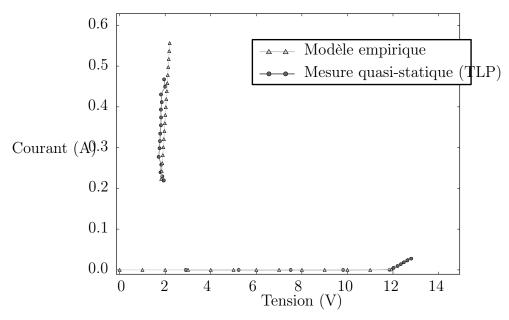

|      | 2.3.3                                                                    | Modélis     | ation des protections ESD                                | 61 |  |

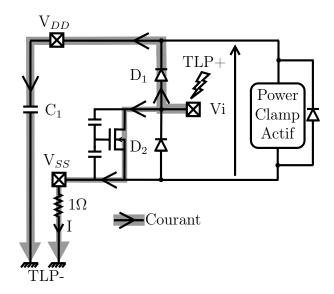

|      |                                                                          | 2.3.3.1     | Extraction d'informations à partir de mesures            | 62 |  |

|      |                                                                          | 2.3.3.2     | Modélisation des protections basée sur le fonctionnement |    |  |

|      |                                                                          |             | empirique                                                | 64 |  |

|      |                                                                          | 2.3.3.3     | Modélisation des protections basée sur le comportement . | 70 |  |

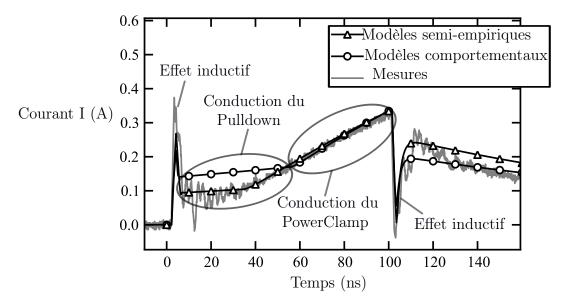

|      |                                                                          | 2.3.3.4     | Vérification des modèles :                               | 76 |  |

|      |                                                                          | 2.3.3.5     | Comparaison des modèles                                  | 77 |  |

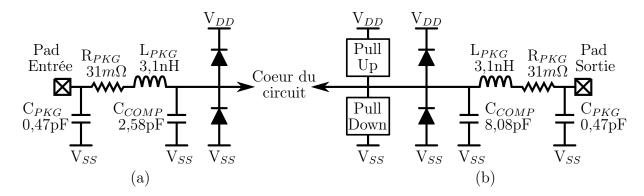

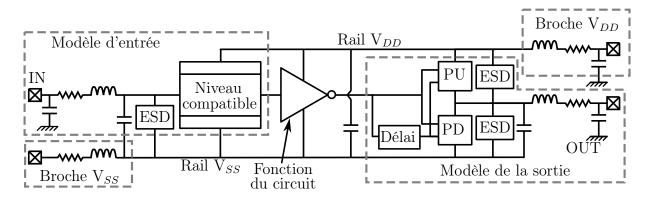

|      | 2.3.4                                                                    | Modélis     | ation de la fonctionnalité à partir des modèles IBIS     | 78 |  |

|      |                                                                          | 2.3.4.1     | Modélisation de l'étage d'entrée                         | 78 |  |

|      |                                                                          | 2.3.4.2     | Modélisation de l'étage d'une sortie deux états          | 79 |  |

|      |                                                                          | 2.3.4.3     | Modélisation de la fonction                              | 82 |  |

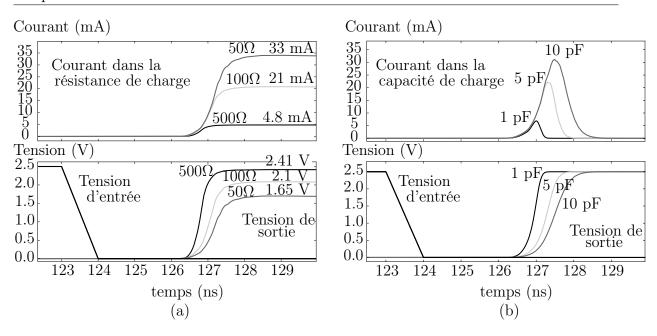

|      | 2.3.5                                                                    | Validati    | on de la partie fonctionnelle                            | 83 |  |

|      |                                                                          | 2.3.5.1     | Commutation de la sortie :                               | 83 |  |

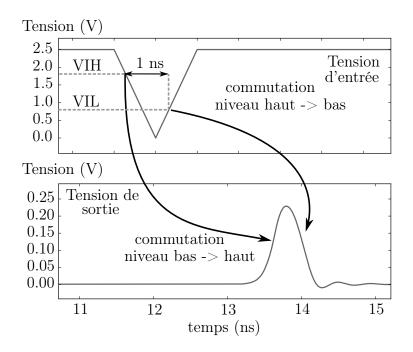

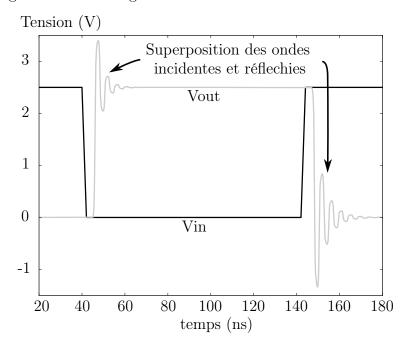

|      |                                                                          | 2.3.5.2     | Simulation d'un évènement rapide sur l'entrée :          | 84 |  |

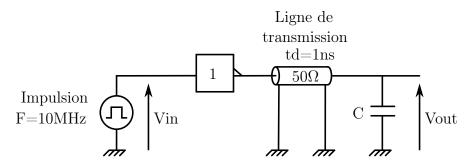

|      |                                                                          | 2.3.5.3     | Simulation de l'intégrité du signal :                    | 85 |  |

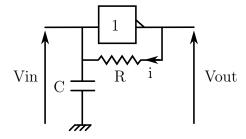

|      |                                                                          | 2.3.5.4     | Simulation d'un oscillateur astable :                    | 86 |  |

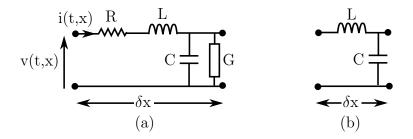

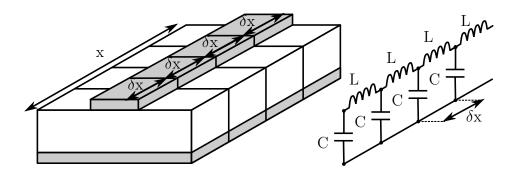

| 2.4  | Modé                                                                     | lisation di | u circuit imprimé                                        | 87 |  |

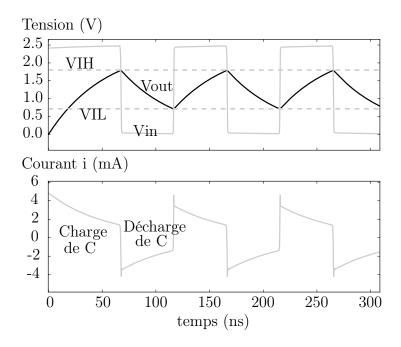

|      | 2.4.1                                                                    | Modélis     | ation de la ligne microruban                             | 87 |  |

|      |                                                                          | 2.4.1.1     | Ligne microruban simple :                                | 87 |  |

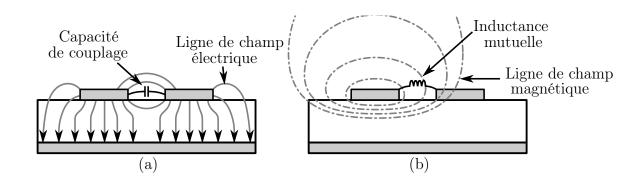

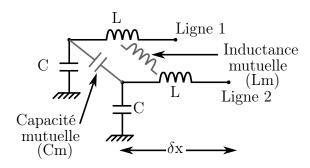

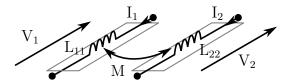

|      |                                                                          | 2.4.1.2     | Modélisation de lignes couplées                          | 90 |  |

|      | 2.4.2                                                                    | Assembl     | lage pour la modélisation complète du PCB                | 92 |  |

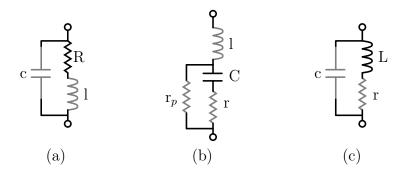

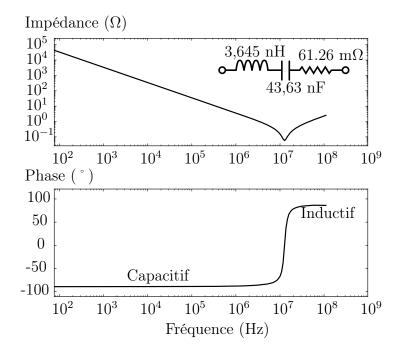

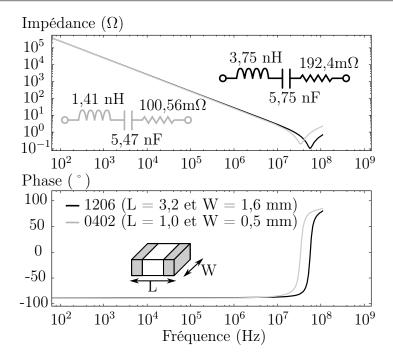

|      | 2.4.3                                                                    | Modélis     | ation des éléments passifs                               | 92 |  |

| 2.5  | Modé                                                                     | lisation de | e l'environnement de test                                | 94 |  |

|      | 2.5.1                                                                    | Connect     | cique entre le système et les appareils de mesure        | 94 |  |

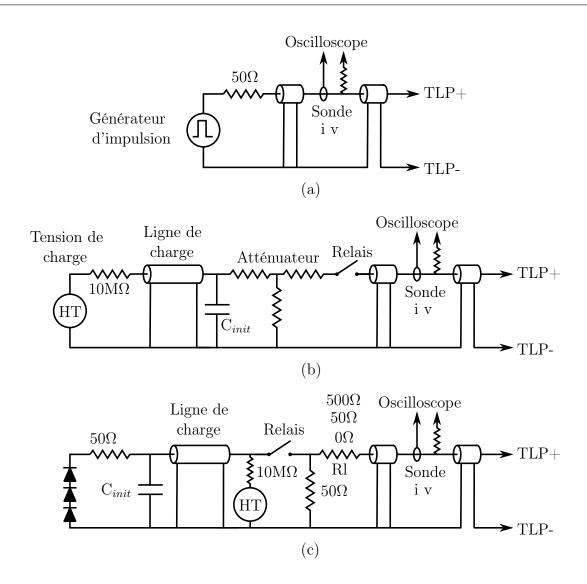

|      | 2.5.2                                                                    | Modélis     | ation des générateurs ESD                                | 94 |  |

|      |                                                                          | 2.5.2.1     | Pistolet ESD                                             |    |  |

|      |                                                                          | 2.5.2.2     | Générateur TLP                                           | 96 |  |

| 2.6  | Modé                                                                     | lisation di | u système complet                                        | 98 |  |

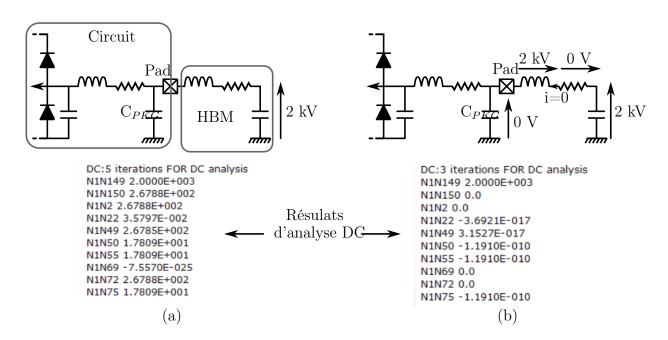

|   | 2.7 | Préca                | écautions et difficultés à prendre en compte dans le montage de la simu- |                                                              |      |  |

|---|-----|----------------------|--------------------------------------------------------------------------|--------------------------------------------------------------|------|--|

|   |     | lation               |                                                                          |                                                              | 100  |  |

|   |     | 2.7.1                | Réglage                                                                  | du pas de calcul                                             | 100  |  |

|   |     | 2.7.2                | Initialis                                                                | ation DC                                                     | 101  |  |

|   |     | 2.7.3                | Masse d                                                                  | e référence                                                  | 102  |  |

|   | 2.8 | Concl                | usion                                                                    |                                                              | 102  |  |

| 3 | Tec | hniques              | s de mes                                                                 | ure et d'injection                                           | 105  |  |

|   | 3.1 | Introd               | luction .                                                                |                                                              | 105  |  |

|   | 3.2 | Techniques de mesure |                                                                          |                                                              |      |  |

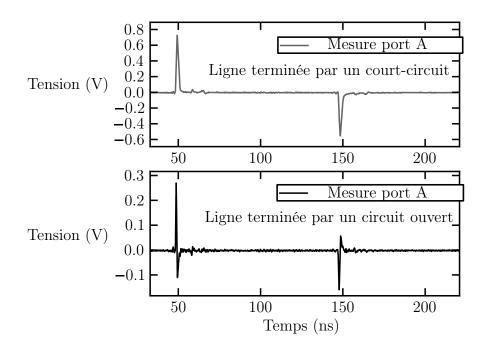

|   |     | 3.2.1                | Réflectr                                                                 | ométrie (TDR : Time Domain Reflectrometry)                   | 105  |  |

|   |     |                      | 3.2.1.1                                                                  | Théorie:                                                     | 105  |  |

|   |     |                      | 3.2.1.2                                                                  | Application de la méthode TDR aux évènements ESD :           | 109  |  |

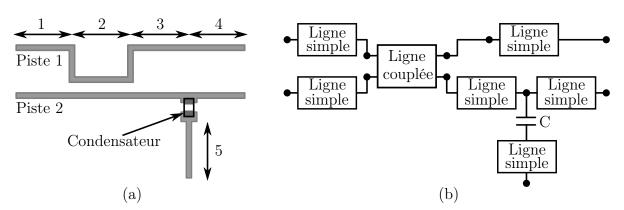

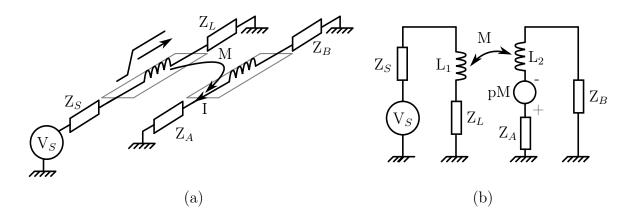

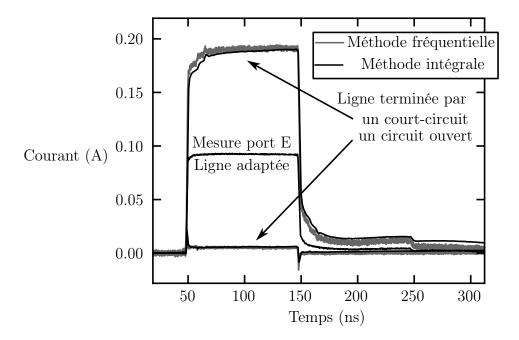

|   |     | 3.2.2                | Mesure                                                                   | du courant par diaphonie entre deux pistes proches           | 112  |  |

|   |     |                      | 3.2.2.1                                                                  | Théorie                                                      | 112  |  |

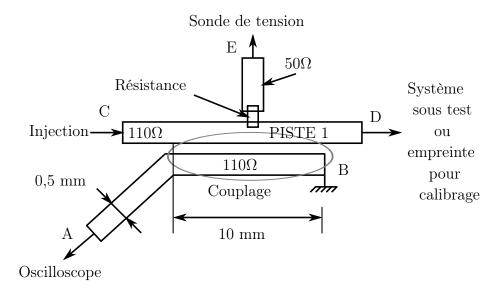

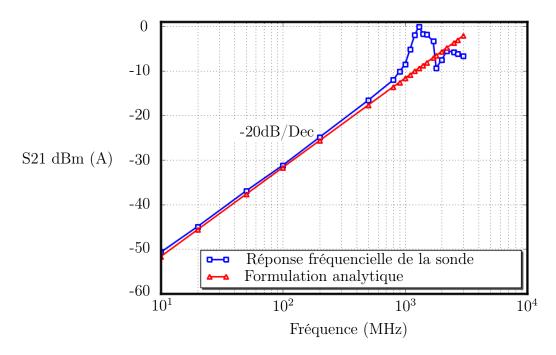

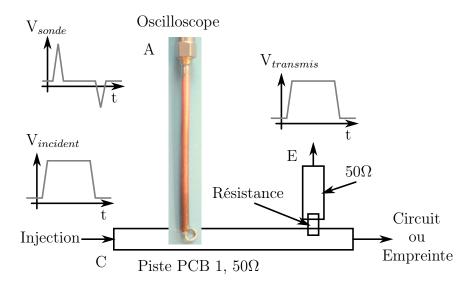

|   |     |                      | 3.2.2.2                                                                  | Motif du système de mesure                                   | 114  |  |

|   |     |                      | 3.2.2.3                                                                  | Détermination du courant                                     | 115  |  |

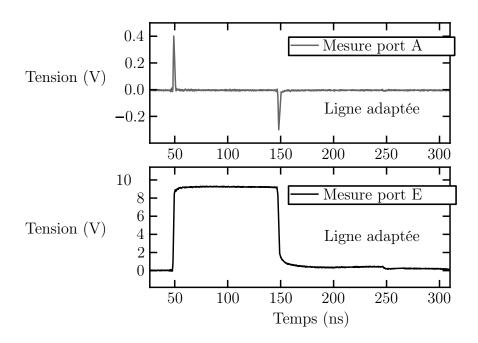

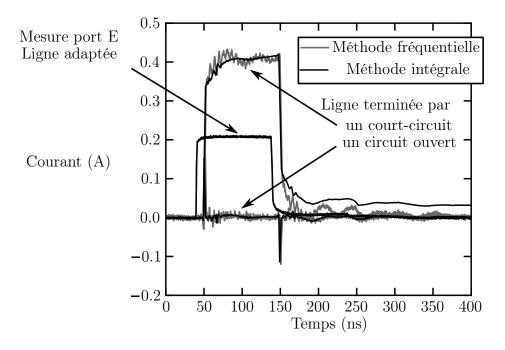

|   |     |                      | 3.2.2.4                                                                  | Expérimentation des méthodes de reconstitution du cou-       |      |  |

|   |     |                      |                                                                          | rant:                                                        | 117  |  |

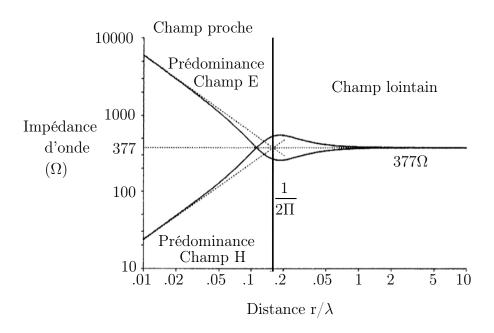

|   |     | 3.2.3                | Mesure                                                                   | du courant avec des sondes de champ proche                   | 120  |  |

|   |     |                      | 3.2.3.1                                                                  | Condition de champ proche et de champ lointain               | 120  |  |

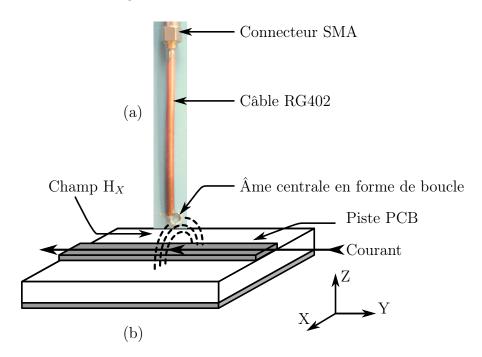

|   |     |                      | 3.2.3.2                                                                  | Construction et fonctionnement de la sonde de champ ma-      |      |  |

|   |     |                      |                                                                          | gnétique                                                     | 122  |  |

|   |     |                      | 3.2.3.3                                                                  | Expérimentation avec la sonde de champ                       | 124  |  |

|   |     | 3.2.4                | Mesure                                                                   | de courant par la méthode de $1\Omega$                       | 125  |  |

|   |     | 3.2.5                | Compar                                                                   | aison des méthodes 1 $\Omega$ et champ proche                | 128  |  |

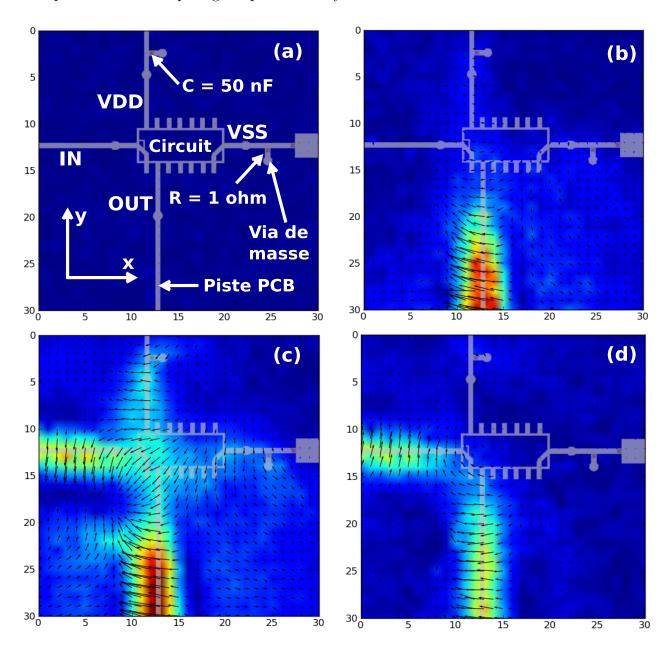

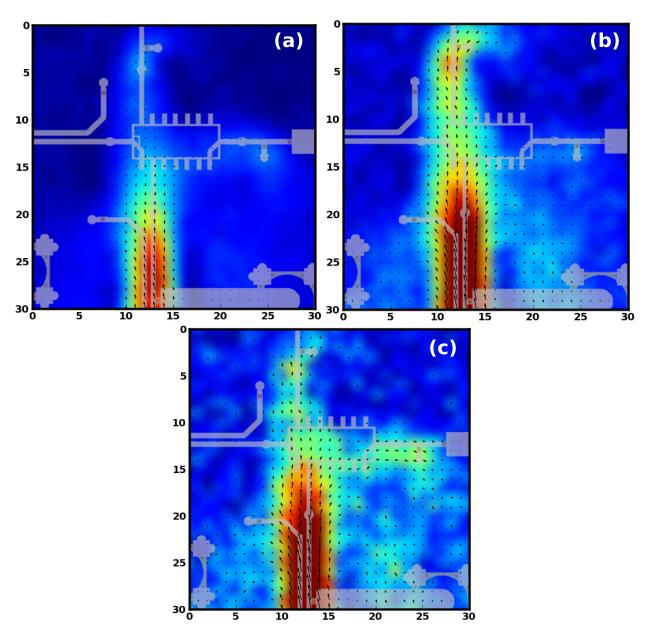

|   |     | 3.2.6                | Cartogr                                                                  | aphie de la répartition du courant dans un circuit imprimé . | 129  |  |

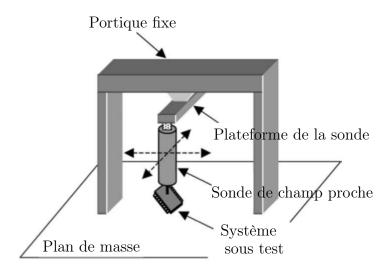

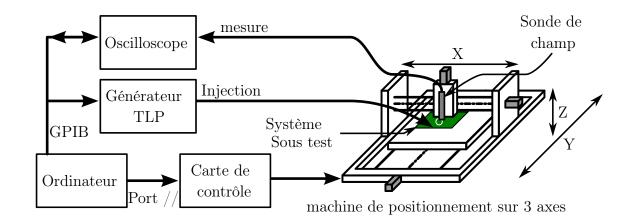

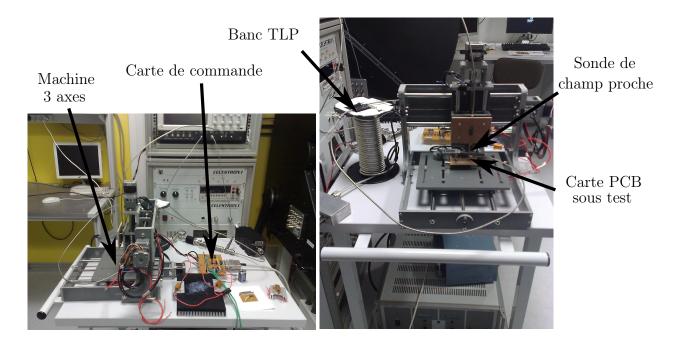

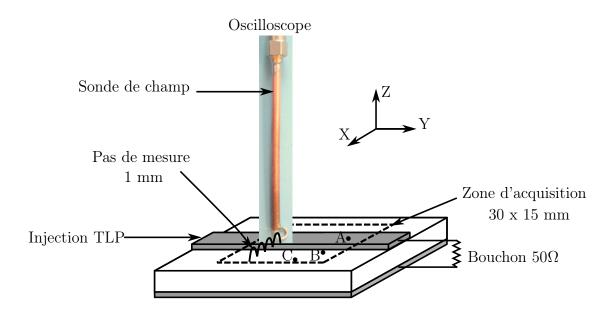

|   |     |                      | 3.2.6.1                                                                  | Développement du banc de mesure de scan en champ proche :    | :130 |  |

|   |     |                      | 3.2.6.2                                                                  | Expérimentation : cartographie du champ magnétique           | 131  |  |

|   |     |                      | 3.2.6.3                                                                  | Détermination de la répartition du courant dans le PCB .     | 135  |  |

|   | 3.3 | Techn                | iques d'in                                                               | ijections                                                    | 136  |  |

|   |     | 3.3.1                | Introdu                                                                  | ction                                                        | 136  |  |

|   |     | 3.3.2                |                                                                          | n en mode conduit et rayonné :                               |      |  |

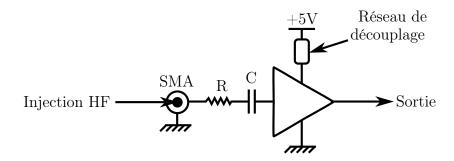

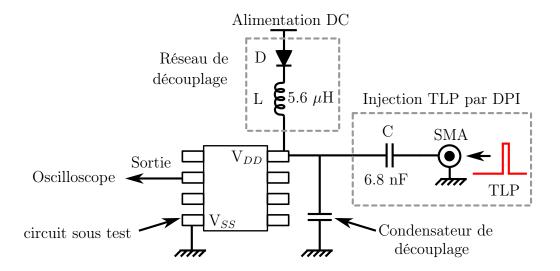

|   |     |                      | 3.3.2.1                                                                  | Méthode d'injection directe (DPI : Direct Power Injection) : | :137 |  |

|   |     |                      | 3.3.2.2                                                                  | Méthode d'injection rayonnée                                 | 138  |  |

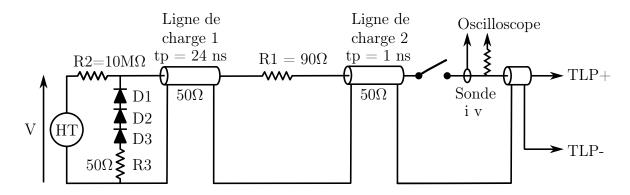

|   |     | 3.3.3                | Concept                                                                  | tion d'un banc d'injection TLP double impulsion :            |      |  |

|   |     |                      | 3.3.3.1                                                                  | Réalisation du banc TLP2P :                                  |      |  |

|   |     |                      | 3.3.3.2                                                                  | Ajustement des délais :                                      |      |  |

|   |     |                      |                                                                          |                                                              |      |  |

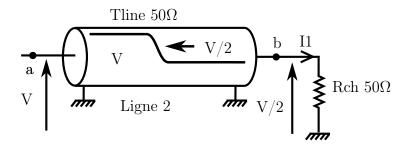

|    |       |         | 3.3.3.3     | Ajustement de l'amplitude des courants :                      | . 139 |

|----|-------|---------|-------------|---------------------------------------------------------------|-------|

|    |       |         | 3.3.3.4     | Analyse du fonctionnement du banc :                           | . 141 |

|    |       |         | 3.3.3.5     | Expérimentation du banc d'injection :                         | . 143 |

|    |       |         | 3.3.3.6     | Utilisation du banc :                                         | . 143 |

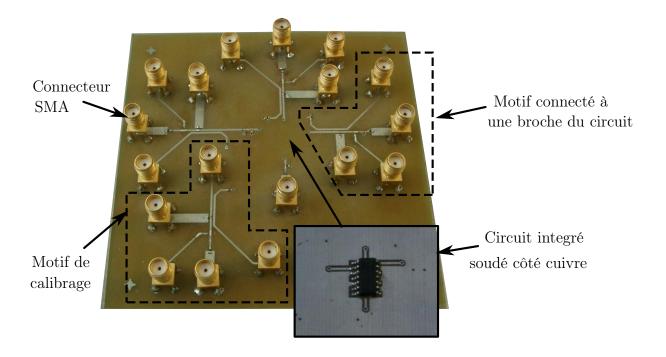

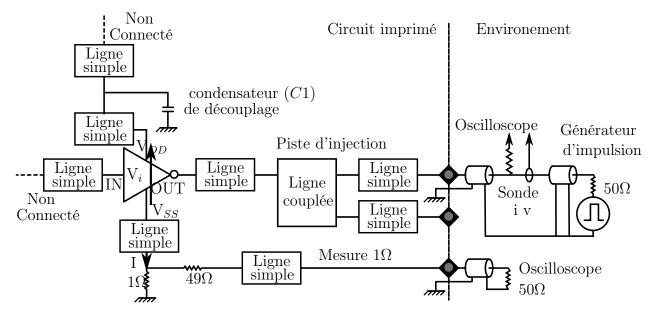

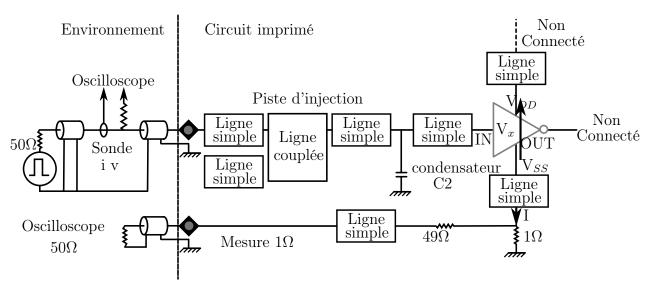

|    | 3.4   | Motif   | d'injection | on et de mesure universels :                                  | . 146 |

|    | 3.5   | Concl   | usion       |                                                               | . 147 |

| 4  | Vali  | dation  | des mét     | hodologies de modélisation et de caractérisation              | 149   |

|    | 4.1   | Introd  | luction .   |                                                               | . 149 |

|    | 4.2   | Étude   | de la pro   | opagation d'une ESD sur une carte non alimentée               | . 150 |

|    |       | 4.2.1   | Présenta    | ation du cas d'étude                                          | . 150 |

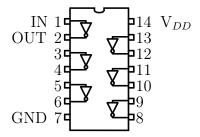

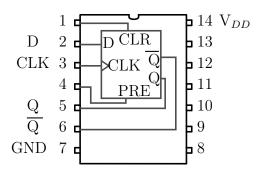

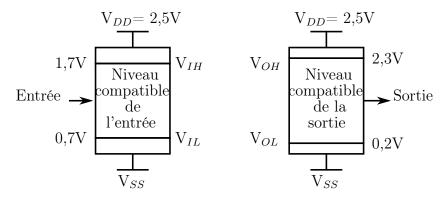

|    |       |         | 4.2.1.1     | Description rapide du circuit                                 | . 150 |

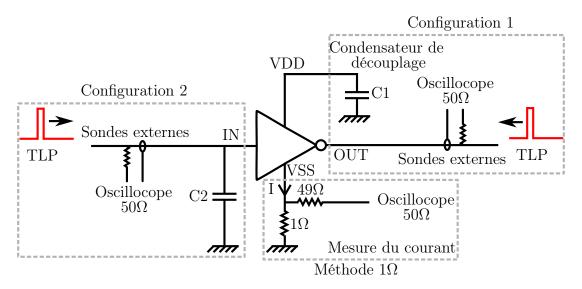

|    |       |         | 4.2.1.2     | Configurations de test                                        | . 150 |

|    |       | 4.2.2   | Analyse     | des résultats de simulation et de mesure                      | . 151 |

|    |       |         | 4.2.2.1     | Modélisation du circuit                                       | . 151 |

|    |       |         | 4.2.2.2     | Configuration de test n°1 $\dots \dots \dots \dots \dots$     |       |

|    |       |         | 4.2.2.3     | Configuration de test n°2                                     | . 163 |

|    |       |         | 4.2.2.4     | Conclusion de la configuration                                | . 169 |

|    | 4.3   | Étude   | de la sus   | sceptibilité d'une carte en fonctionnement                    | . 169 |

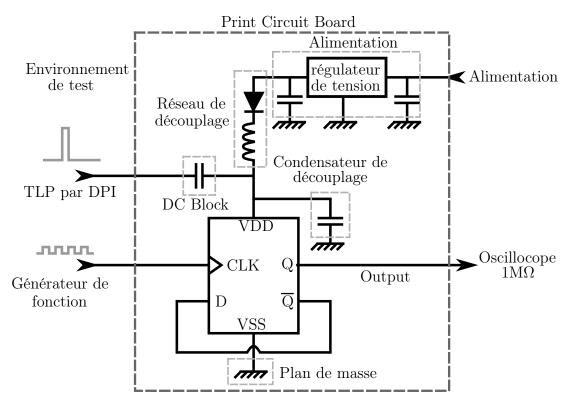

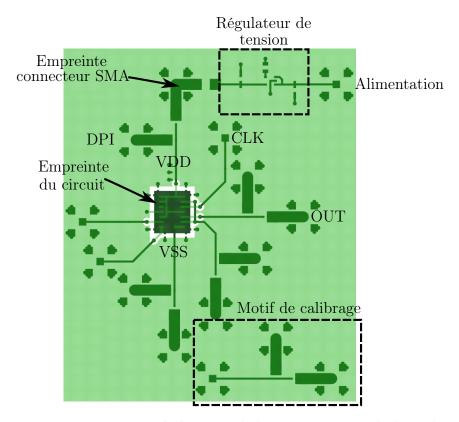

|    |       | 4.3.1   | Présenta    | ation du cas d'étude                                          | . 169 |

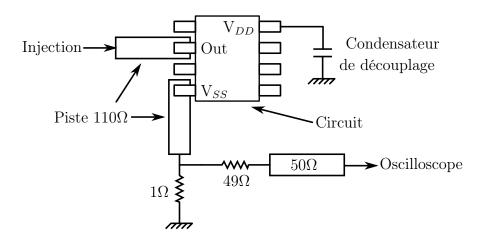

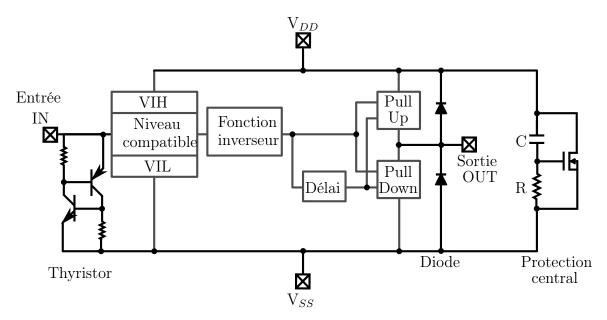

|    |       |         | 4.3.1.1     | Description du circuit                                        | . 169 |

|    |       |         | 4.3.1.2     | Configuration de test                                         | . 170 |

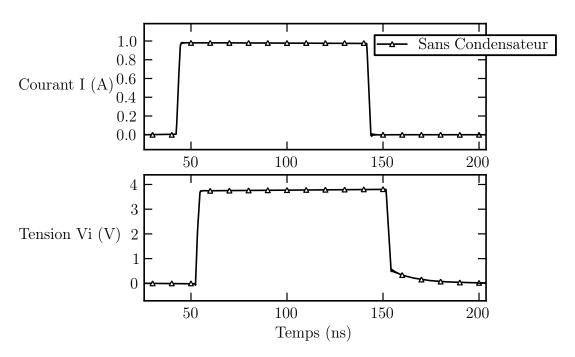

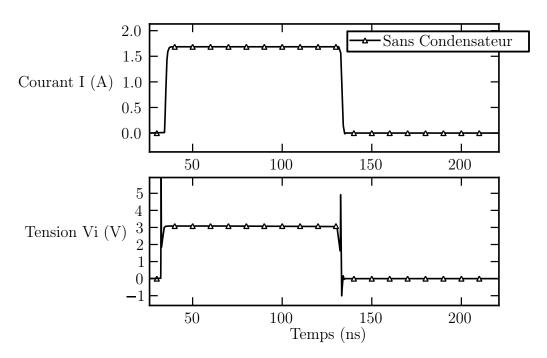

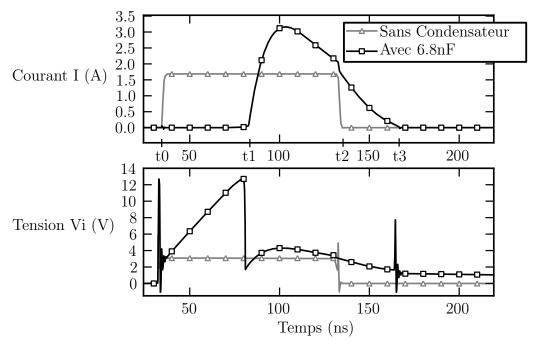

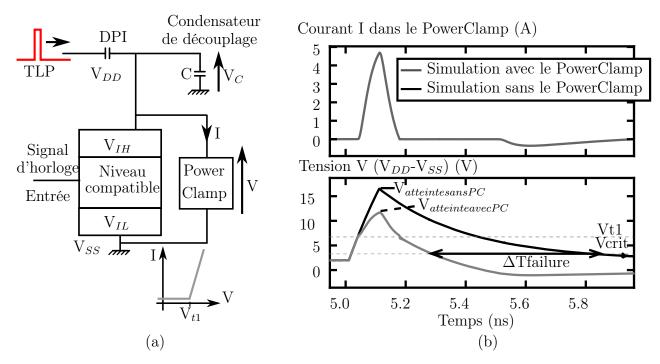

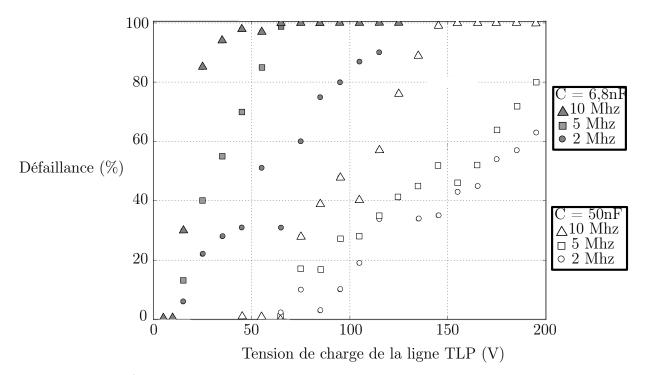

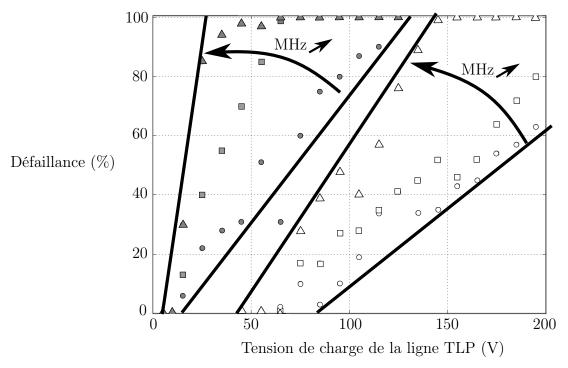

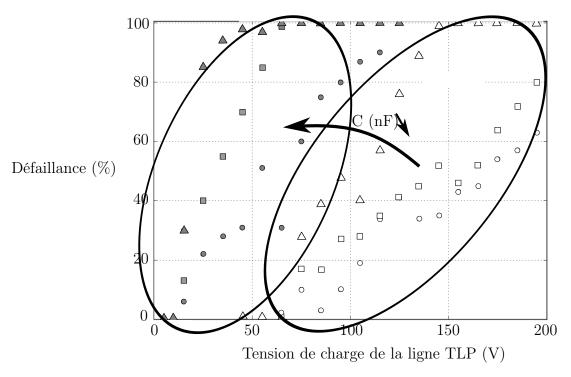

|    |       | 4.3.2   | Analyse     | des résultats de simulation et de mesure                      | . 173 |

|    |       |         | 4.3.2.1     | Reproduction des défaillances                                 | . 173 |

|    |       |         | 4.3.2.2     | Investigation de la probabilité de générer des erreurs        | . 178 |

|    |       | 4.3.3   | Conclus     | ion du cas d'étude n°2                                        | . 183 |

|    | 4.4   | Cas d   | 'étude n°   | B: Étude d'une application automobile                         | . 184 |

|    |       | 4.4.1   | Introdu     | ction:                                                        | . 184 |

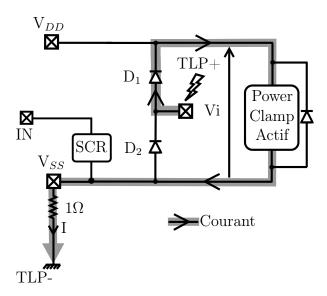

|    |       | 4.4.2   | Présenta    | ation du cas d'étude                                          | . 184 |

|    |       |         | 4.4.2.1     | Description du circuit LIN                                    | . 184 |

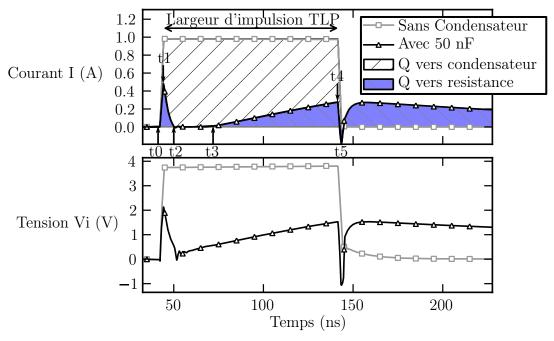

|    |       | 4.4.3   | Analyse     | des résultats de simulation et de mesure                      | . 188 |

|    |       |         | 4.4.3.1     | Injection TLP 50 $\Omega$                                     | . 189 |

|    |       |         | 4.4.3.2     | Étude du système soumis à un générateur non 50 $\Omega$ (pis- | -     |

|    |       |         |             | tolet ESD)                                                    | . 193 |

|    |       | 4.4.4   | Conclus     | ion du cas d'étude                                            | . 197 |

|    | 4.5   | Concl   | usion .     |                                                               | . 198 |

| Co | onclu | sion gé | nérale      |                                                               | 199   |

| Bibliographie          | 203 |

|------------------------|-----|

| Liste des publications | 217 |

| Annexes                | 219 |

### Introduction générale

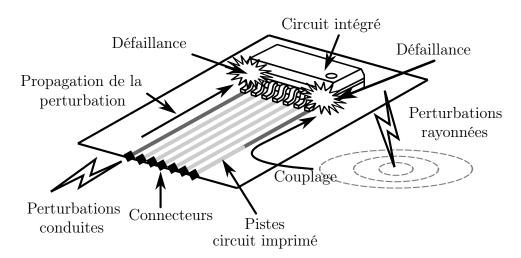

Les décharges électrostatiques, ou en anglais "ElectroStatic Discharges" (ESD), sont des phénomènes naturels et inévitables. Que ce soit durant leurs étapes de fabrication, ou pendant leurs utilisations, tout produit électronique va subir inexorablement ces agressions pouvant induire des défaillances fonctionnelles et/ou des défaillances destructives.

Durant les phases de fabrication et d'assemblage, les décharges peuvent détruire les circuits intégrés. Afin de préserver la puce, de nombreuses précautions sont prises en compte pour limiter les décharges et leurs effets. L'impact du phénomène peut être atténué en contrôlant la génération des charges électriques dans les zones où évolue le circuit (zone de fabrication, zone de test). De plus, des protections sont intégrées directement sur la puce dans le but de protéger la partie active en détectant et détournant les ESD. Enfin, les circuits sont testés suivant différents standards qui seront détaillés [1, 2, 3] pour vérifier leur robustesse et garantir que ceux-ci peuvent "survivre" à leurs fabrications.

Les produits électroniques ou systèmes, comme par exemple un module embarqué dans une automobile, ne sont pas confrontés à la même problématique que les circuits intégrés seuls. Il est important de voir que, contrairement aux circuits, les systèmes n'évoluent plus dans un milieu contrôlé. Les décharges sont plus rudes. Les composants embarqués doivent donc supporter des niveaux de stress plus importants pour ne pas être détruits. Dans le cas où les protections intégrées sur les puces ne sont pas suffisantes pour assurer la robustesse, le concepteur du système doit le prévoir et trouver des méthodes pour réduire l'amplitude de la décharge sur la carte électronique.

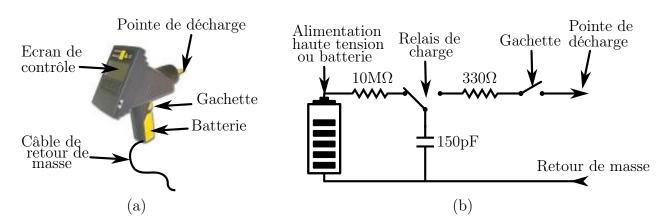

D'un autre coté, lorsque le système est en fonctionnement, des défaillances de type fonctionnelles peuvent survenir impliquant par exemple des problèmes de "Reset" du système [4, 5]. Ceci est particulièrement critique pour les applications où la sécurité de l'utilisateur est primordiale comme dans le domaine de l'automobile. Pour vérifier l'immunité des systèmes vis à vis des ESD, des tests sont aujourd'hui effectués dans l'industrie suivant les standards IEC 61000-4-2 [6] et ISO 10605 [7] pour l'automobile.

La problématique au niveau du système est qu'il n'existe que très peu d'outil, très peu de méthode, permettant d'analyser ou de prédire le comportement du système lorsqu'une défaillance du produit est révélée par les tests standards. Les concepteurs du système remanient le produit jusqu'à ce que celui-ci remplisse les exigences du standard, sans avoir suffisamment de méthodes d'investigation pour comprendre ce qui se passe durant

la décharge. Ceci peut conduire à de nombreuses itérations avant de trouver une solution qui n'est pas forcément la plus efficace et la plus économique.

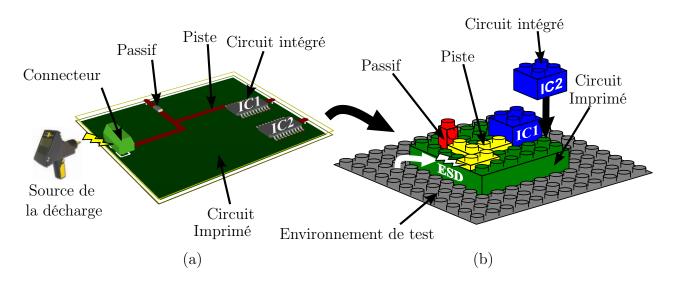

Pour répondre à cette problématique, les travaux de ma thèse sont orientés sur le développement de méthodes de modélisation et de caractérisation permettant d'analyser un système et de comprendre les modes de propagation et de défaillance lorsque survient une décharge électrostatique. Le système électronique considéré dans ce document se limitera à la carte électronique ou PCB (Printed Circuit Board) intégrant les composants actifs et passifs.

En ce qui concerne la modélisation, nous avons développé une méthodologie comportementale hiérarchique. Cette méthode est destinée à analyser la propagation du courant de décharge dans un système, depuis un générateur ESD, jusqu'aux phénomènes internes pouvant induire des défaillances à l'intérieur du circuit. En parallèle, nous avons développé des méthodes de caractérisation qui permettent d'une part, de visualiser les courants et tensions circulant dans le système, mais aussi de réaliser des corrélations avec les simulations de nos modèles. Toutes ces méthodes ont été validées au fur et à mesure de leur développement sur différents cas d'étude. Nous avons choisi de séparer et présenter l'état de l'art, la modélisation, les techniques de caractérisations et les cas d'études selon le plan suivant :

Le chapitre 1 fait une synthèse de l'état de l'art des décharges électrostatiques et des moyens de contrôles utilisés pour s'en prémunir. Dans un premier temps, les mécanismes de génération de charges électriques qui conduisent aux phénomènes des décharges électrostatiques et leurs impacts sur l'électronique sont détaillés de manière générale. Ensuite, nous avons voulu mettre en évidence les différences entre « l'aspect ESD composant » et « l'aspect ESD système » afin de mieux cerner la problématique actuelle des ESD. Ainsi, pour chacun de ces aspects, nous présenterons les différents modèles industriels, les testeurs associés et les protections servant à supprimer ou minimiser les effets des décharges. Enfin, nous aborderons la problématique et les besoins industriels concernant le niveau système.

Le deuxième chapitre décrit une méthodologie de modélisation comportementale destinée à l'analyse de la propagation de la décharge dans le système (sur la carte électronique et dans le circuit intégré), et à la prédiction de son impact. Après avoir énoncer le principe de cette méthodologie, nous présenterons la modélisation des puces Nous verrons que les informations fournies par le fabricant de semi-conducteur sont très insuffisantes d'un point vue ESD. Nous avons choisi de modéliser le circuit sur la base d'un modèle existant appelé IBIS (Input/output Buffer Information Specification), développé à l'origine pour effectuer des simulations d'intégrité du signal. Nous présenterons les différentes investiga-

tions réalisées auprès de ce modèle que nous avons adapté à la prédiction des phénomènes ESD. Dans la suite du chapitre, nous détaillerons comment nous avons modélisé le circuit imprimé, notamment les lignes PCB. Pour cela, nous avons repris les travaux de la thèse de Nicolas Lacrampe [8]. Nous détaillerons aussi la modélisation de l'environnement de test, à savoir, les générateurs de décharges et les câbles. Enfin, nous expliquerons comment tous ces modèles sont assemblés pour former le système complet.

Le troisième chapitre se concentre sur la présentation des différentes techniques développées au cours de la thèse permettant l'injection des ESD et la mesure des signaux se propageant dans le système. Dans un premier temps, nous présenterons les différentes techniques de mesure du courant et/ou de tension basées sur la réflectrométrie temporelle. D'autres méthodes de mesures ont été développées, comme l'utilisation de pistes PCB couplées, de sondes de champs proche et d'une méthode appelée "1  $\Omega$ ". Nous développerons particulièrement une technique de cartographie par les champs proches permettant d'obtenir la répartition des champs magnétiques et du courant dans un système. La deuxième partie du chapitre est consacrée à la description des techniques d'injection direct es utilisant des générateurs d'impulsion, basés sur des lignes de transmission, ainsi qu'à l'injection indirecte pour effectuer le test de systèmes alimentés en fonctionnement. Enfin, nous présenterons un motif universel reprenant les différentes méthodes proposées dans le chapitre et permettant la réalisation d'une carte de test dédiée à la caractérisation ESD d'un circuit monté dans un système.

Dans le quatrième chapitre, afin de valider les techniques de caractérisations et la méthode de modélisation développées au cours de la thèse, nous avons étudié trois cas d'étude. Nous présenterons dans un premier temps un cas d'étude réalisé pour analyser la propagation du courant dans un système non alimenté. Ensuite, nous avons réalisé une deuxième étude permettant, cette fois-ci, d'étudier la susceptibilité d'un système en fonctionnement. Dans le cadre de la collaboration avec les industriels Freescale et Valéo (Projet ANR VTT E-SAFE : ESD safe automotive Electronic products), nous avons étudié un cas d'étude réel basé autour d'un circuit intégré LIN (Local Interconnect Network) dont les contraintes CEM (Compatibilité ElectroMagnétique) imposent l'ajout d'une capacité sur une des broches directement connectée à l'extérieur.

L'objectif final de la thèse est de prouver que des simulations uniquement comportementales suffisent pour comprendre ce qui se passe dans le système durant une décharge ESD, mais aussi permettent de prédire les défaillances de type robustesse et susceptibilité, au niveau du système.

# 1 Les décharges électrostatiques : état de l'art des moyens de contrôle, du composant aux systèmes

Ce chapitre a pour but d'introduire, les notions élémentaires des décharges électrostatiques (ESD: ElectroStatic Discharge), leurs effets dans le domaine de l'électronique et de la microélectronique, et les moyens de lutte et de test utilisés pour s'en prémunir. Dans la première partie, nous allons mettre en avant l'origine de la génération de charges électriques qui conduit aux phénomènes de décharges électrostatiques. Nous verrons comment ces phénomènes parasites engendrent des défaillances sur les systèmes électroniques qui vont de la perturbation du fonctionnement d'une carte à la destruction d'un circuit intégré. Dans la deuxième partie de ce chapitre, nous allons décrire les évènements ESD qui peuvent survenir au sein des environnements de fabrication ainsi que les tests associés (appliqués directement sur les circuits intégrés). Nous présenterons les protections ESD ajoutées pour préserver le circuit et les différents moyens de caractérisation mis en œuvre. Enfin, dans la troisième partie, nous parlerons des tests permettant de reproduire les perturbations qui surviennent sur le produit final, dans les conditions réelles de fonctionnement. Nous verrons que certains de ces tests, et notamment l'IEC 61000-4-2 sur lequel se focalise ce sujet de thèse, souffrent de nombreuses lacunes et nous définirons les besoins industriels.

# 1.1 Origine des décharges électrostatiques et leurs impacts

### 1.1.1 Mécanismes de génération de charges électriques

Avant de parler de décharges électrostatiques, il est intéressant de définir les notions de charge et le phénomène de charge électrique. L'apparition d'une charge électrique sur un corps peut être expliquée en regardant la structure atomique de la matière. Les atomes sont constitués de particules : les neutrons et protons formant le noyau et les électrons gravitant autour de ce noyau. Certaines de ces particules portent une charge

élémentaire  $\pm e$  ayant les propriétés de s'attirer dans le cas de charge e de signe contraire ou de se repousser dans le cas de charge e de même signe. Les protons portent une charge élémentaire positive tandis que les électrons portent une charge élémentaire négative. A l'état de repos, l'atome contient autant de protons que d'électrons, les charges positives sont compensées par les charges négatives, l'atome est dit électriquement neutre. Cette neutralité peut être rompue lorsque l'atome gagne ou perd un ou plusieurs électrons. Les atomes, dont le nombre d'électrons n'est plus égal à celui des protons, sont appelés "ions" positifs ou négatifs, suivant qu'ils aient perdus ou gagnés des électrons. Un corps possède une charge électrique lorsque les atomes le constituant ne sont plus en équilibre. Le corps est dit "électrisé" ou "chargé".

Il existe de nombreux phénomènes à l'origine de la génération de ces charges. Les phénomènes les plus répandus dans le monde de la microélectronique étant la génération de charge par triboélectrification, induction et conduction [9].

L'électrisation par triboélectrification correspond à la création de charges par contact puis séparation de deux objets de nature différente. Lorsque les deux objets sont frottés puis séparés, des électrons sont transférés de l'un des matériaux au détriment de l'autre. Ainsi, le matériau ayant perdu des électrons devient électropositif, tandis que l'autre devient électronégatif. La quantité de charges ainsi générée dépend de nombreux facteurs tels que la surface de contact, la vitesse de séparation et l'humidité relative [10]. D'autre part, la polarité des charges électriques générées dépend de la caractéristique des matériaux frottés. Par exemple, la peau d'un être humain a tendance à générer une charge positive tandis que le Téflon ou le silicium ont une tendance négative [11]. Un exemple couramment utilisé pour décrire le phénomène est l'humain qui marche sur une moquette. Lorsque ses chaussures frottent la moquette et se séparent de celle-ci pendant la marche, l'humain peut accumuler une charge allant de 1,5 à 35 kV suivant l'humidité relative de l'air [12].

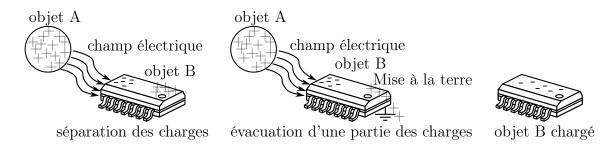

FIGURE 1.1: Illustration de la charge d'un circuit intégré par induction.

La charge par induction, ou influence, a lieu lorsqu'un objet est placé dans le champ électrique d'un autre objet [13] comme illustré par la Figure 1.1. Le champ électrique de l'objet A, électropositif, sépare les charges positives et négatives de l'objet B. Si l'objet

B est momentanément mis à la terre, une partie des charges va être évacuée. Lorsque l'objet n'est plus sous l'influence du champ électrique, il reste chargé. Ce phénomène peut avoir lieu sur les postes de travail près des transformateurs et des écrans cathodiques d'ordinateur.

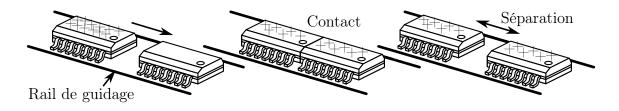

Enfin, le phénomène de conduction correspond à un transfert de charges par contact [9]. Ce genre de phénomène peut avoir lieu sur une chaîne de production où les composants circulent sur des rails de guidage. Un composant peut accumuler des charges par triboélectrification en glissant sur ces rails. Le composant chargé rentre en contact avec un autre composant et lui transfert une partie de ces charges comme illustré sur la Figure 1.2.

FIGURE 1.2: Illustration de la charge d'un circuit intégré par conduction adaptée de [9].

La répartition des charges à l'intérieur d'un même corps dépend de la nature des matériaux. Un matériau isolant aura tendance à conserver les charges localement où elles ont été générées. Par contre, pour les conducteurs, de part leur résistance plus faible, les charges vont être réparties sur toute la surface et pourront être évacuées facilement si ce dernier entre en contact avec la terre.

### 1.1.2 Générations des décharges électrostatiques.

Lorsque deux objets ou personnes ayant acquis une quantité extrême de charge électrique entrent en contact, un transfert de charge a lieu entre ces deux objets pour que ceux-ci retrouvent leur neutralité électrique. C'est la décharge électrostatique. Lorsque la différence de potentiel électrique entre les deux objets atteint le potentiel disruptif de l'air, qui est d'environ 3600 V/mm pour un air sec, un arc se forme dans l'air. Cet arc correspond à l'ionisation des molécules dans l'air permettant le passage des électrons d'un objet à l'autre. Le chemin est très peu résistif, ainsi le courant est très intense pouvant atteindre plusieurs ampères, voir quelques dizaines d'ampères, et la durée du transfert des charges est extrêmement courte, inférieure à la microseconde.

Si l'on reprend l'exemple de l'humain qui marche sur la moquette, lorsque celui-ci va saisir la poignée d'une porte, une décharge va avoir lieu permettant l'évacuation des charges accumulées par le corps dans la poignée métallique. L'être humain commence à ressentir les décharges lorsque sa tension de charge est d'environ 3, 4 kV. Il faut savoir qu'en

dessous de ce seuil de perception, un humain génère un grand nombre de décharges sans forcement les ressentir. A partir de 15 kV, les décharges commencent à être douloureuses.

Les décharges électrostatiques émettent des perturbations électromagnétiques [14, 15]. La mesure du rayonnement provoqué par la décharge d'une personne réelle dans un plan métallique a été étudiée par Jiusheng [16]. L'onde électromagnétique captée par une antenne située à proximité est très forte même pour des petites tensions de charge du corps humain (2 kV dans l'expérience de Jiusheng). A quelques centimètres, le champ électrique crête à crête atteint 100 à 1000 V/m et le champ magnétique 10 à 100 A/m. Le spectre du champ électrique est très large, au delà de 4 GHz.

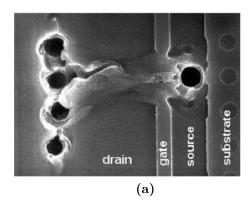

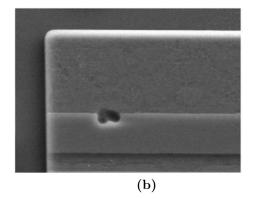

### 1.1.3 Impact sur l'électronique

Les évènements ESD surviennent des procédés de fabrication d'un wafer jusqu'à l'utilisation du composant dans les équipements électroniques, et ce, tout au long de la durée de vie du produit. Les circuits intégrés sont très vulnérables à ces décharges. Durant leurs manipulations, la décharge engendrée par un humain ou une machine dans un circuit met en jeu de fortes densités de courant et des champs électriques très intenses pouvant induire des défaillances. Les densités de courant associées aux ESD sont dissipées directement par la puce en silicium. Cette dissipation de puissance s'effectue dans de faibles volumes et a pour conséquence une augmentation de la température pouvant entraîner des dommages thermiques. Ceux-ci peuvent se traduisent par la fusion du silicium entraînant la dégradation de jonction comme illustrée 1.3a. Les champs électriques intenses, générés par les ESD, induisent des fortes tensions aux bornes des circuits. Dans le cas des technologies MOS (Metal Oxyde Semiconductor) cette forte tension peut apparaître aux bornes d'un diélectrique tel que l'oxyde de grille d'un transistor MOS. Un dépassement de la tension de claquage de l'oxyde entraîne sa rupture et crée une défaillance irréversible. Le claquage d'un oxyde de grille liée à une ESD est illustrée Figure 1.3b. Typiquement, les oxydes de grille peuvent supporter des champs électriques de 6 à 10 MV/cm avant qu'ils ne cassent [11]. Ces types de dégradation ne sont pas les seules observables, mais ce sont les plus répandues.

Avec l'évolution des technologies de la micro-électronique, la taille des transistors diminue vers les échelles nanométriques ceci, afin d'augmenter la densité d'intégration ainsi que les performances. Les nouveaux procédés de fabrication tels que les oxydes de grille ultra minces, les jonctions peu profondes, les drains fortement dopés, l'utilisation de nouveaux matériaux pour les interconnections (cuivre au lieu de l'aluminium) rendent les circuits plus sensibles [17]. L'énergie d'une décharge se trouve dissipée dans des volumes de plus en plus réduits. La finesse des oxydes de grille implique une tension de claquage moins importante. Les interconnexions sont plus fines, la dissipation d'énergie est moins efficace. Les défaillances des circuits surviennent donc pour des niveaux de tension de charge de

plus en plus faibles.

FIGURE 1.3: Exemple de défaillances liées à un stress ESD : (a) destruction thermique par fusion du silicium [18] et (b) rupture d'un isolant, ici l'oxyde de grille [18].

D'un point de vue ESD, lorsque nous parlons de robustesse des composants, nous faisons référence uniquement aux problèmes de destruction du circuit intégré engendrés par une décharge tel que nous venons de le décrire.

Après sa fabrication, le circuit intégré est soudé sur une carte électronique formant l'équipement électronique. Même si cet équipement est mis dans un boîtier, il n'est pas à l'abri des ESD. Une décharge peut survenir, durant l'utilisation ou la maintenance, directement ou par couplage sur un des connecteurs ou câbles reliant l'application au monde extérieur. Le produit électronique étant en fonctionnement, deux types de défaillances peuvent survenir :

- la robustesse : défaillance qui correspond à la perte irréversible de la fonction par destruction

- la susceptibilité : défaillance qui correspond à la perte de fonctionnalité temporaire. En terme de robustesse, les effets sont les mêmes que cités au début de cette section, les deux principaux mécanismes de destruction étant le claquage thermique et d'oxyde [19].

Pour la susceptibilité, la décharge peut perturber le fonctionnement du système : pertes de cycle d'horloge dans les communications, RESET, modification de données stockées dans des mémoires... Le RESET d'un composant électronique peut être très critique car il place le système dans un état indéterminé [5, 4]. Lorsqu'il s'agit d'un téléphone, cela n'est pas trop grave, il redémarre. Par contre, cela peut avoir de lourdes conséquences dans les applications où la sécurité de l'utilisateur est mise en jeu comme dans l'automobile. Une publication faite par Jean Rivenc [20], illustre le cas du déclenchement intempestif d'un airbag de voiture à cause d'une ESD. Un pull-over chargé est posé sur le tableau de bord de la voiture et charge par induction l'airbag qui se déclenche. Cela a entraîné le rappel de million de véhicules en Europe dans les années 1997-1998.

Comme nous pouvons le constater, ils existent deux domaines distincts dans le monde des ESD. D'une part, "l'aspect composant", s'intéressant essentiellement à la robustesse des circuits durant les phases de fabrication et d'assemblage. De l'autre, "l'aspect système", s'intéressant aussi bien à la robustesse et à la susceptibilité des systèmes électroniques vis à vis des ESD durant leur utilisation. L'aspect composant a été largement étudié, et aujourd'hui, il est relativement bien maîtrisé, même si les évolutions technologiques forcent les concepteurs de circuit à d'énormes précautions et investigations. Comme nous le verrons dans le chapitre qui suit, des normes définissent clairement les tensions que doivent supporter les composants. Cependant, les réductions technologiques poussent à réduire les marges de tensions supportées par les composants. D'un autre coté, l'explosion des nouvelles technologies expose de plus en plus de circuits à l'environnement extérieur, plus sévère. Par conséquent, l'aspect système est une problématique récente dans le sens ou, les équipementiers doivent garantir la fiabilité de leurs systèmes qui utilisent des circuits de plus en plus sensibles.

Afin d'amener le lecteur de cette thèse à la problématique que rencontre le concepteur du système vis à vis des décharges, nous avons choisi de séparer et de décrire ces deux aspects, composant et système, dans deux sections distinctes. Pour chaque aspect, nous présenterons les différentes normes et standards applicables ainsi que les moyens et méthodes de prévention existantes.

### 1.2 Aspect composant :

### 1.2.1 Zone EPA (Electrostatic discharge Protected Areas)

Afin de limiter les niveaux de décharge qui vont survenir lors de la fabrication et de l'assemblage, les composants vont évoluer dans une zone protégée appelée EPA (ESD Protected Areas). Cette zone a pour objectif de limiter la charge électrique du personnel et des machines en appliquant les précautions de base, telles que le port de bracelets antistatiques, la mise à la terre des équipements et l'utilisation d'emballages aux propriétés anti-ESD [21].

D'autres techniques avancées sont utilisées dans les laboratoires, les zones de tests et les zones de fabrication des wafers, comme que le contrôle de l'humidité et l'ionisation de l'air [9]. Ces zones "avancées" sont en conformité avec les standards ANSI S20.20 [22] et IEC 61340 [23] qui définissent les types de revêtement du sol ainsi que les chaussures portées par le personnel. L'objectif est d'optimiser la résistance du personnel par rapport à la terre, d'un point de vue électrostatique, afin d'en limiter la charge. Des méthodes de contrôle sont détaillées par cette norme [24]. L'objectif du standard est d'atteindre une tension de charge du corps humain (HBM) inférieur à 100 V [21]. Compte tenu de

l'avancement technologique et de l'augmentation de la sensibilité des composants, de plus en plus d'industriels s'orientent vers ses techniques dîtes "avancées".

Bien que de nombreuses précautions soient prises en compte, les décharges ne sont pas annulées, mais limitées. C'est pour cela que les circuits intègrent des structures visant à protéger le cœur du circuit face aux évènements ESD qui pourraient survenir dans la zone EPA. Des modèles et des testeurs ont été développés afin de vérifier la robustesse de ces structures communément appelées "protections ESD". La section suivante détaille les différents modèles de décharges existant ainsi que leurs testeurs associés. Puis la section 1.2.3 décrit les protections ESD typiquement utilisées dans les circuits et leur organisation dans ce dernier.

### 1.2.2 Modèles de décharges et testeurs industriels

Afin de reproduire les différents évènements ESD qui pourraient survenir durant les phases de fabrication et d'assemblage dans la zone EPA, des modèles de décharges ont été développés par différents comités de standardisation. Pour chacun de ces modèles, un testeur est associé, reproduisant l'évènement ESD et permettant d'évaluer la robustesse des circuits. Le but de ces tests est de vérifier que les protections ESD, qui ont été ajoutées dans les circuits, sont suffisamment efficaces pour que le composant survive et ne soit pas détruit durant sa fabrication. Cette section détaille les trois modèles standards qui sont : le HBM (en anglais : Human Body Model), le MM (Machine Model) et le CDM (Charged Device Model), et les testeurs associés. Elle décrit aussi le modèle CBM (Charged Board Model) non standardisé mais qui décrit toutefois un évènement ESD qui peut survenir en zone EPA.

### 1.2.2.1 Modèle et testeur HBM (Human Body Model)

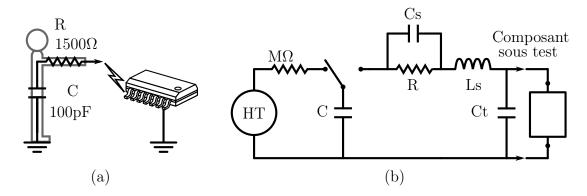

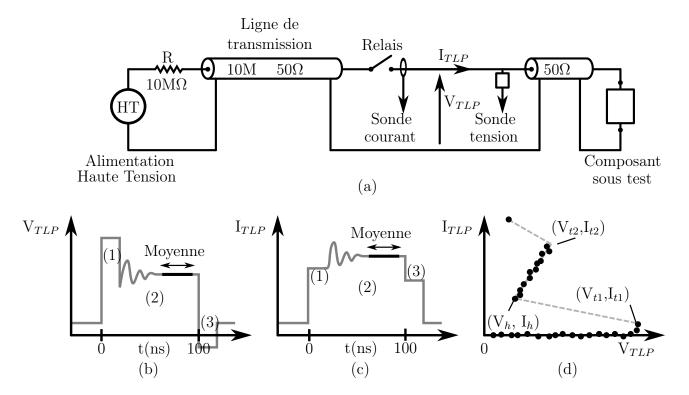

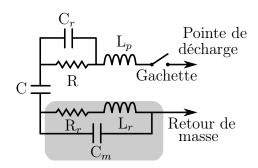

Comme nous avons vu dans la sous-section 1.1.1, le corps humain peut se charger par triboélectrification. Lorsque l'humain chargé va toucher le composant semi-conducteur, une décharge va survenir entre ses doigts et les broches du circuit. Le modèle standard HBM [25, 1, 26] est destiné à simuler cet évènement. D'un point de vue électrostatique et en première approximation, le corps humain peut être assimilé à une capacité C, de 100 pF, et une résistance R, de 1500  $\Omega$  comme illustré Figure 1.4 (a). Le schéma électrique du testeur permettant de reproduire ce modèle est donné Figure 1.4 (b). Autour des éléments modélisant le corps humain, des éléments parasites Ct et Cs sont ajoutés pour reproduire une forme de décharge réelle. Ct est la capacité parasite associée au testeur et Ls permet de régler le temps de montée. La valeur de ces éléments ainsi que la procédure de test sont détaillées dans les standards [25, 1, 26].

FIGURE 1.4: Modèle du corps humain (HBM) (a) et schéma électrique d'un testeur HBM (b).

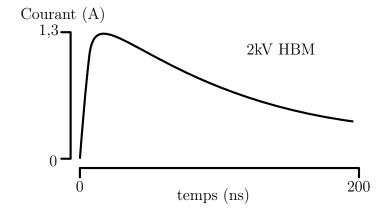

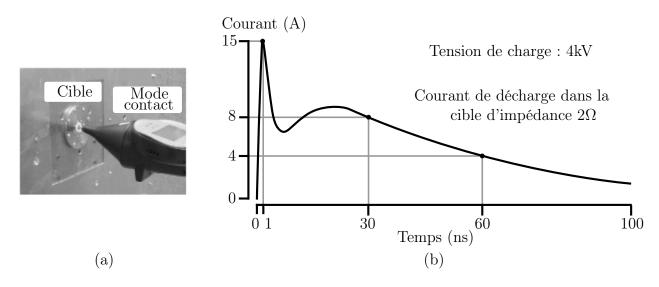

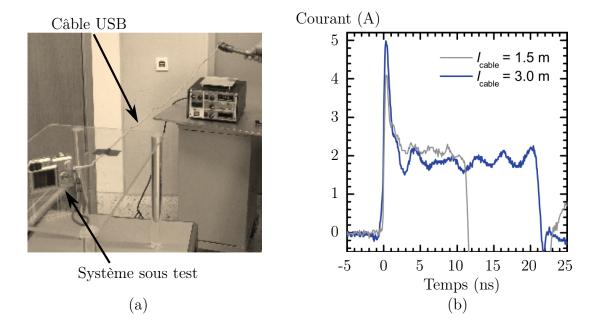

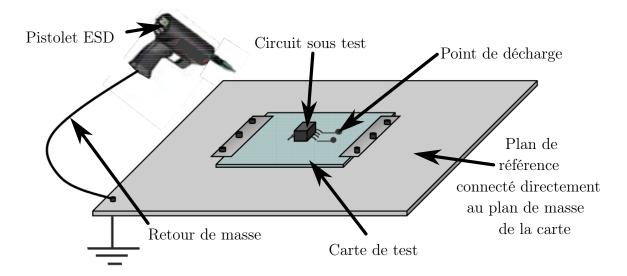

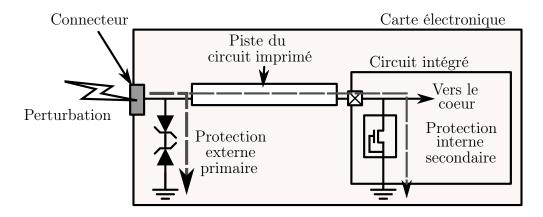

Lors des tests, la capacité C, initialement chargée à quelques kilovolts, est déchargée au travers de la résistance R dans le composant sous test à la fermeture du relais. La forme d'onde du courant résultant, obtenue dans un court-circuit, est donnée Figure 1.5. Elle est caractérisée par un temps de montée entre 2 et 10 ns et une durée de 450 ns. L'intensité de la décharge dépend de la tension de charge de la capacité C, 2 kV dans notre cas.

FIGURE 1.5: Forme d'onde du courant de décharge HBM obtenue dans un court-circuit pour une tension de pré-charge de 2 kV.

La tension de pré-charge de la capacité C est prise en compte pour donner une information sur le niveau de robustesse. Si le composant sous test supporte une décharge HBM quand la capacité C est initialement chargée à 2 kV, celui-ci est dit robuste à 2 kV HBM.

Le niveau de robustesse requis pour les circuits est fixé par le cahier des charges, rédigé par les clients des constructeurs de circuit. Cependant, la documentation "industry council" fournie par l'ESDA (ESD Association), préconise que le circuit doit garantir une robustesse de 1 kV HBM minimum pour que celui-ci ne soit pas détruit durant la fabrication [27].

### 1.2.2.2 Modèle et testeur MM (Machine Model)

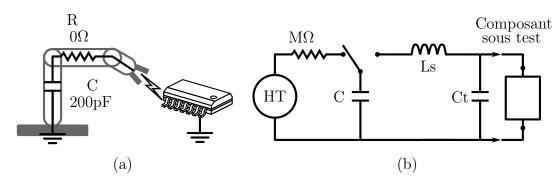

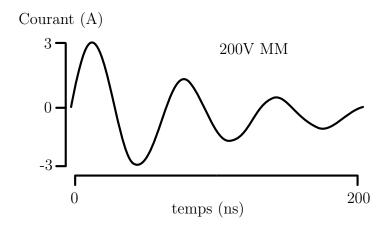

Le modèle de décharge standard MM [28, 3] est destiné à reproduire la décharge d'une machine ou d'un humain tenant un objet métallique dans la main. Il diffère du modèle HBM de part sa capacité de charge légèrement plus grande (200 pF), et de part une résistance série quasi nulle représentant l'outil métallique ou le bras manipulateur d'un robot. Ce modèle est représenté Figure 1.6 (a). Le schéma du testeur associé est représenté Figure 1.6 (b). Typiquement, la capacité C est chargée entre 10 et 500 V. Elle est ensuite déchargée dans le composant sous test à la fermeture du relais. La forme d'onde résultante, obtenue dans un court-circuit pour une tension de charge de 200 V, est donnée Figure 1.7. L'absence de résistance produit une oscillation amortie avec une fréquence de 5 à 15 MHz et des temps de montée de quelques dizaines de nanosecondes. L'inductance, Ls, et la capacité, Cs, parasites ont une forte influence sur cette forme d'onde.

FIGURE 1.6: Modèle d'une machine (MM) (a) et schéma électrique du testeur MM (b).

FIGURE 1.7: Forme d'onde du courant de décharge MM obtenue dans un court-circuit pour une tension de charge de 200 V.

Comme pour le HBM, c'est la tension de charge de la capacité C qui est prise en compte comme indication de robustesse. L' "industry council" préconise que le circuit doit être robuste à 30 V MM pour garantir que celui ne sera pas détruit durant la fabrication [27].

### 1.2.2.3 Modèle et testeur CDM (Charged Device Model)

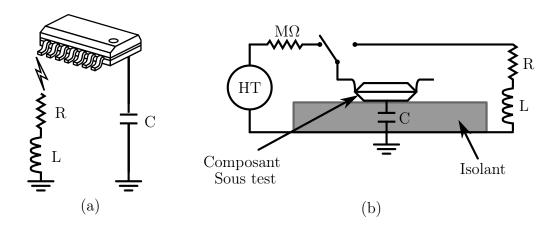

Comme nous avons pu le voir dans la première partie, un circuit peut accumuler des charges lors de sa manipulation. Le modèle CDM [2, 29] représente la décharge de ce circuit par l'une de ces broches, vers la masse (Figure 1.8 (a)). Ce modèle a été développé afin d'expliquer la rupture de certains oxydes dont l'origine ne peut pas être expliquée par les modèles HBM et MM.

FIGURE 1.8: Modèle du composant chargé (CDM) (a) et schéma représentatif d'un testeur CDM (b).

Un fois que le circuit est assemblé dans un boîtier, celui ci peut accumuler des charges par triboélectrification en glissant sur un rail de guidage. Lorsqu'une de l'une de ses broches est mise à la masse, les charges accumulées sont évacuées par la masse créant des surtensions et des chemins de courant internes pouvant détériorer les oxydes de grilles.

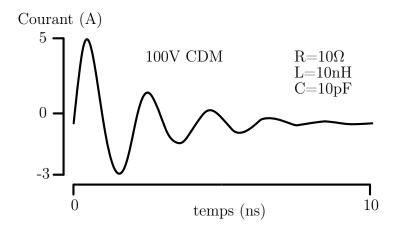

Le testeur permettant de reproduire ce modèle est représenté Figure 1.9 (b). Le circuit sous test est positionné à l'envers sur un support isolé de la terre. La capacité C, correspondant à la capacité du circuit par rapport à la terre, est chargée par une alimentation haute tension au travers d'un résistance de forte valeur. Le composant est ensuite déchargé par l'une de ses broches au travers de R et L, représentant les éléments parasites de la ligne de décharge. Le modèle de décharge CDM est difficile à reproduire car celui-ci est très sensible à ces éléments parasites ainsi qu'à la capacité associée au composant. Les valeurs typiques de la résistance et de l'inductance du modèle sont  $R=10~\Omega$  et L=10~nH. La forme de la décharge typique CDM d'un circuit chargé à 100 V dont la capacité C équivalente vaut 10 pF est illustrée Figure 1.9. La forme est caractérisée par des courants de 5 A pic avec des temps de transitions très rapides de l'ordre de 200 ps.

L'industry council préconise un niveau minimum de robustesse de 250 V CDM afin de garantir que le circuit ne sera pas détruit pendant sa fabrication [30].

FIGURE 1.9: Forme d'onde typique du courant de décharge CDM obtenue dans un courtcircuit pour une tension de charge de 100 V du composant.

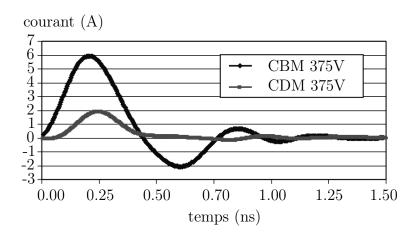

### 1.2.2.4 Modèle non standardisé CBM (Charged Board Model)

Le modèle CBM est un modèle non standardisé similaire au modèle CDM. La différence réside dans le fait que c'est le circuit imprimé qui est chargé et qui se décharge dans le composant. Les dommages CBM sont plus sévères que ceux provoqués par le HBM et le CDM [31]. En effet, les niveaux d'énergie mis en jeu sont plus importants car la capacité d'une carte est bien plus grande que celle d'un circuit intégré. Cette capacité dépend fortement de la taille du circuit imprimé [32].

Une comparaison des formes du courant obtenue avec une décharge CDM et CBM, réalisée par Andrew Olney [33], est donnée Figure 1.10.

FIGURE 1.10: Comparaison des courants de décharge CDM et CBM pour une tension de charge de 375 V, mesurée sur la broche d'un composant et sur le connecteur d'une carte [33].

La mesure est effectuée respectivement sur la broche d'un composant seul et sur le connecteur d'une carte dédiée sur laquelle est monté ce même circuit. Pour une même tension de charge, le courant pic est plus important pour le CBM. Ceci est dû au fait que les charges stockées par le circuit imprimé ajoutées à celles du composant sont plus importantes.

Bien que ce modèle de décharge ne soit pas standardisé, il représente un évènement réel de décharge qui peut survenir dans la zone EPA. Les circuits robustes vis à vis des évènements HBM, MM et CDM peuvent être endommagés par les CBM.

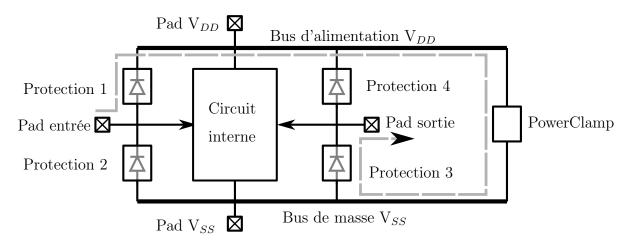

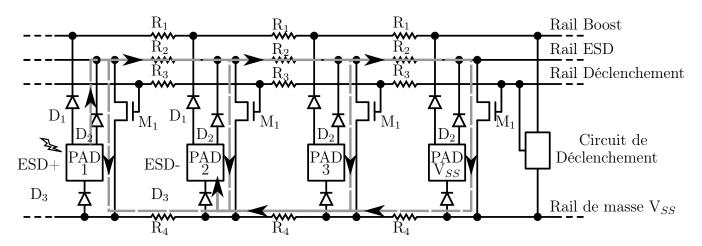

### 1.2.3 Protections intégrées dans les circuits

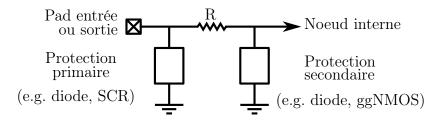

Afin de dévier les forts courants issus d'une décharge électrostatique qui pourraient survenir entre deux broches d'un circuit intégré, des protections sont ajoutées directement sur la puce. Les quatre sections suivantes détaillent respectivement, le principe de fonctionnement de ces protections, les structures typiques utilisées, comment celles-ci sont organisées dans le circuit et les outils disponibles pour leurs optimisations.

#### 1.2.3.1 Principe de fonctionnement d'une structure de protection

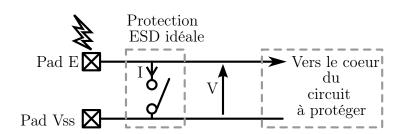

Les structures de protection doivent dévier les forts courants ESD du cœur du circuit pour éviter les dommages thermiques tels que la fusion du silicium. Elles doivent aussi limiter la tension dans le circuit à protéger pour éviter par exemple les claquages d'oxyde de grille d'un transistor MOS (voir sous-section 1.1.3). En fonctionnement normal, la protection est transparente à l'application et se réduit à un interrupteur ouvert avec une impédance infinie comme illustré Figure 1.11. En condition de stress ESD, celle-ci est déclenchée et peut être assimilée à un court circuit dont l'impédance doit être la plus faible possible afin de faire circuler un courant (I) le plus grand possible tout en limitant la tension (V) aux bornes de l'élément à protéger.

FIGURE 1.11: Schéma illustrant le principe d'une protection ESD assimilée à un interrupteur parfait.

Cette protection idéale doit répondre à certaines caractéristiques fondamentales [11] :

Robustesse : la structure doit être capable supporter elle même les énergies très fortes des ESD;

- Transparence : elle ne doit pas se déclencher durant le fonctionnement normal du circuit. Les éléments parasites apportés doivent être faibles pour minimiser la dégradation des performances des entrées et sorties. Son courant de fuite doit être le plus faible possible pour limiter la consommation du circuit;

- Rapidité : elle doit se déclencher sur les évènements transitoires des ESD, de l'ordre de la nanoseconde;

- Économique : la surface du silicium est très coûteuse. La protection doit donc consommer la surface la plus faible possible. D'autre part, les étapes technologiques de fabrications sont très coûteuses. Les protections doivent donc respecter les étapes de fabrication de la technologie pour laquelle elles sont dédiées;

- Efficacité : la tension de déclenchement doit être au dessus des tensions de fonctionnements du circuit et présenter une résistance faible pour limiter la tension.

Il est clair qu'une protection ESD ne peut pas avoir toutes ces caractéristiques. Cependant, ces critères fournissent une liste d'optimisation et de compromis qui vont être utilisés en fonction du cahier des charges.

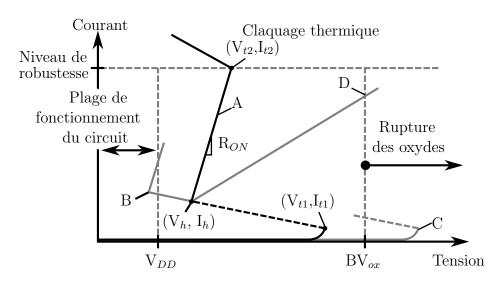

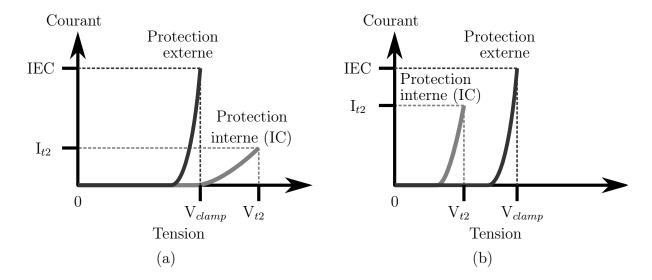

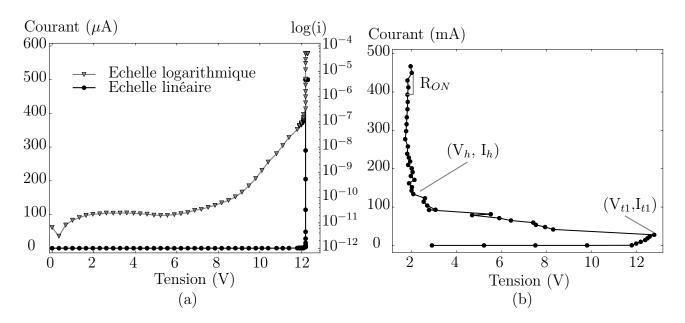

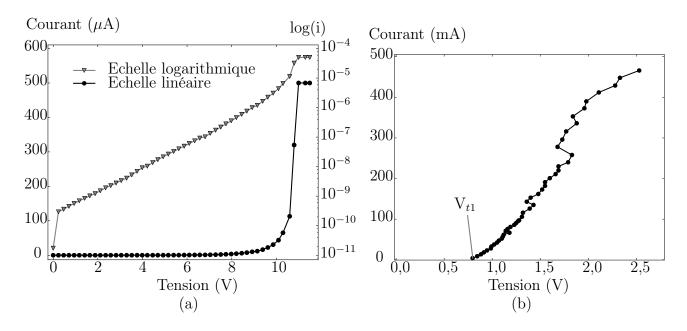

La fenêtre de conception d'une protection ESD est illustrée Figure 1.12 [34]. Elle délimite la caractéristique I(V) de la protection qui permet de visualiser les couples de tensions, courants caractéristiques typiques tels que le déclenchement  $(V_{t1}, I_{t1})$ , le maintient dans le cas de structure avec repliement  $(V_h, I_h)$ , la résistance à l'état passant,  $(R_{ON})$ et le second retournement lié au claquage thermique  $(V_{t2}, I_{t2})$ .

FIGURE 1.12: Fenêtre de conception d'une protection ESD.

Cette fenêtre de conception est délimitée par les marges de conception. Ces marges sont fixées par les valeurs maximales des tensions d'alimentation du circuit  $V_{DD}$ , la tension de destruction du circuit Bv (correspondant par exemple à la tension de claquage des oxydes,

la tension de ruptures de jonctions ou encore la tension de déclenchement d'une structure parasite) et le niveau de robustesse souhaité. La caractéristique I(V) de la protection ne doit pas sortir de ces marges comme illustré par le cas A Figure 1.12. Si la tension de déclenchement  $V_{t1}$  est trop importante (cas C) ou si la résistance à l'état passant  $R_{ON}$  est trop grande et que la tension dépasse la tension  $BV_{OX}$  avant le niveau de robustesse souhaité (cas D), on risque les claquages d'oxydes. Si la tension de repliement est inférieure à  $V_{DD}$  (cas B), la protection risque de partir en "Latchup" [35, 36], c'est à dire de continuer à faire passer du courant même après l'évènement ESD, car la tension d'alimentation maintient la protection déclenchée. Ces marges de conception tendent à se resserrer compte tenue des tendances technologiques actuelles. La diminution de la taille des transistors font que les tensions d'alimentation baissent et sont actuellement de l'ordre de 1,2 V pour les technologies CMOS 65 nm.

Enfin, il est nécessaire de définir un critère de défaillance qui indique le niveau de robustesse de la protection, c'est à dire quand celle-ci est considérée défaillante. Dans la littérature, les trois principaux critères de défaillances pour les structures de protection ESD sont :

- Le niveau du courant où survient le second retournement dont le dommage est un claquage par effet thermique [37], correspondant au point  $(V_{t2}, I_{t2})$  (Figure 1.12).

- L'augmentation du courant de fuite (appelé Idss) de la structure après le stress ESD [38].

- Un critère en température : vérification que les points chauds au cours de la décharge ne dépassent pas les températures de fusion,  $1412^{\circ}$ C pour le silicium [39]. Le niveau de courant  $I_{t2}$  pris en compte dans ce cas là, correspond au moment où le point chaud dépasse un point de fusion.

#### 1.2.3.2 Les structures de protection typiques :

Dans la littérature, de nombreuses structures de protection ont été développées pour lutter contre les ESD. Voici les structures typiques utilisées.

1.2.3.2.1 Les diodes : les diodes sont des protections statiques. Elle sont typiquement utilisées pour protéger les entrées/sorties (I/O). La diode polarisée en direct peut conduire les courants lorsque la tension appliquée à ses bornes est plus grande que la tension de seuil qui est située normalement autour de 0.5, 0.7 V. A ce niveau de tension, la résistance de la diode est très faible, de l'ordre de l'ohm. En raison de cette faible tension directe et de la faible résistance, la dissipation de puissance et donc la température interne reste basse même pour les fortes injections de courant. La diode en direct supporte des courants de l'ordre de 20 à 50 mA par micromètre [11].

En polarisation inverse, le courant est généré par effet d'avalanche. D'après O. Semenov,

la tension de déclenchement est de l'ordre de 10 à 20 V et la résistance à l'état passant est de 50 à 100 ohm. Ce mode de fonctionnement n'est pas optimisé pour la dissipation de puissance. La diode en inverse supporte des courants de l'ordre 0.5 à 2 mA par micromètre [11].

Dans le cas de jonctions fortement dopées, les diodes se déclenchement par effet Tunnel ou Zener. Ces diodes présentent une tension de déclenchement inverse plus faible qu'une diode classique, de l'ordre de 5 à 7 V et une résistance plus faible. Elles sont utilisées pour réaliser des protections entre les broches d'alimentation qui nécessitent des tensions de déclenchement plus élevées au dessus des tensions de polarisation du circuit [40].

Enfin, pour augmenter les tensions de seuil des diodes en direct et en l'occurrence pour les utiliser comme protections d'alimentation, elle peuvent être associées en série [41]. Chaque tension de seuil est alors ajoutée.

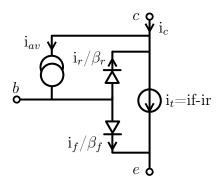

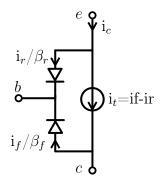

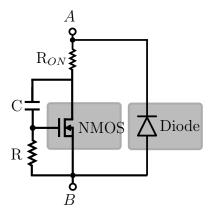

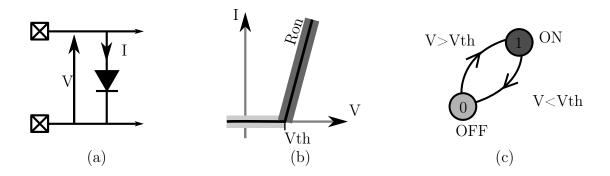

1.2.3.2.2 Le transistor NMOS les transistors MOS (Metal Oxide Semiconductor) sont couramment utilisés comme protection dans les circuits intégrés modernes. Plusieurs déclinaisons de la mise en œuvre du MOS existent faisant intervenir différents régimes de fonctionnement. Associé à un circuit de déclenchement, le MOS est utilisé dans son régime de fonctionnement normal. D'un autre coté, une structure parasite optimisée du transistor MOS (par exemple un NPN), peut être utilisée pour évacuer les courants. Le transistor n'est alors plus utilisé dans son régime de fonctionnement normal. Il existe aussi d'autres structures combinant ces deux techniques. Cette section détaille les principales structures du MOS utilisées comme protection ESD.

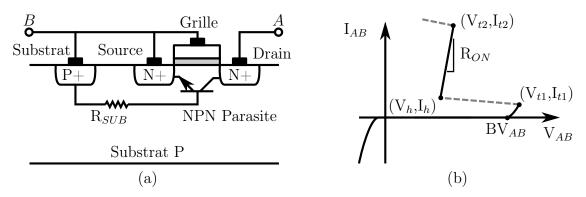

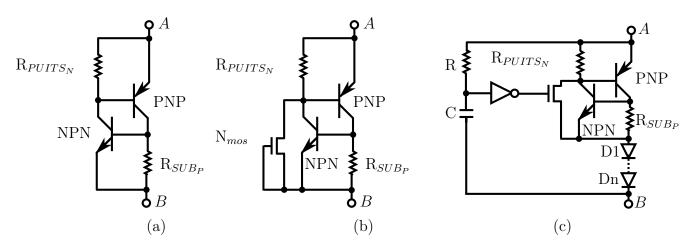

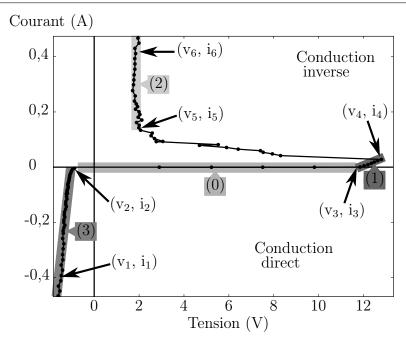

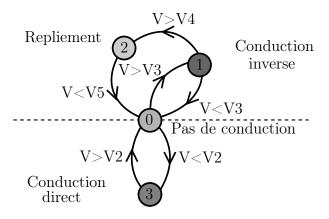

Utilisation d'un transistor bipolaire parasite : le ggNMOS (ground-gate NMOS) est un transistor MOS dont la grille et la source sont court-circuitées et reliées au substrat. Le transistor ne fonctionne pas dans son régime normal mais utilise le transistor NPN parasite pour conduire les courants de décharge [42, 43]. La coupe d'un transistor ggN-MOS est donnée Figure 1.13 (a). Lorsque cette structure est utilisée comme protection ESD, l'électrode A est connectée au plot ou "pad" d'entrée/sortie à protéger ou au bus d'alimentation et l'électrode B est connectée à la masse.

Pour expliquer son fonctionnement, il faut s'intéresser à ce qui se passe physiquement dans le semi-conducteur. Lorsque le potentiel entre les électrodes A et B augmente et atteint la tension de claquage de la jonction constitué par le Drain N+ et le Substrat P, celle-ci est polarisée en inverse par l'effet d'avalanche. Cette jonction va injecter des trous qui vont circuler au travers de la résistance  $R_{SUB}$  et créer un courant. La circulation du courant dans la résistance  $R_{SUB}$  va faire augmenter le potentiel permettant de polariser la jonction Substrat P et Source N+ en direct. Dès que la tension est suffisante, de l'ordre de 0.5 à 0.7 V, le transistor Bipolaire composé de la Source N+ du substrat P et du drain N+

se déclenche. Les électrons injectés par la source contribuent au mécanisme d'avalanche de la jonction Drain N+ Substrat P permettant la diminution de la tension de Drain nécessaire pour obtenir le courant de trou. La tension de Drain diminue jusqu'à la tension de maintient  $V_h$  (entre 3 et 5 V) et un comportement de repliement est observé comme illustré sur la caractéristique idéale Figure 1.13 (b). La représentation schématique de cette structure est donnée Figure 1.14 (a).

FIGURE 1.13: Vue en coupe du transistor Ground-Gate NMOS (ggNMOS) (a) et sa caractéristique  $I_{AB}(V_{AB})$  idéale (b).

Dans le cas où une décharge négative est appliquée sur le Drain par rapport à la Source, la conduction est effectuée par la diode de substrat formée par la jonction Substrat P / Drain N+. La conduction de courant dans ce mode de fonctionnement est favorable telle que décrite dans le paragraphe 1.2.3.2.1.

Le problème d'une telle structure est qu'elle nécessite une tension de déclenchement élevée (entre 8 et 10 V), correspondant à la tension de claquage par avalanche de la jonction Drain N+/Substrat P, ce qui est critique notamment dans les technologies MOS car cette tension est en générale supérieure aux tensions de claquage des oxydes de grille. Pour éviter ce problème, il est possible d'ajouter une structure ou circuit de déclenchement permettant de baisser le niveau de déclenchement de la protection NMOS comme décrit dans le paragraphe suivant.

**Utilisation d'un circuit de déclenchement :** il existe deux types de déclenchement : les déclenchements statiques et les déclenchements dynamiques :

Le déclenchement statique peut être effectué à l'aide de diode Zener [44] ou de diodes en série [45] et d'une résistance R comme illustré respectivement Figure 1.14 (b) et (c). Dès que la tension de seuil des diodes est atteinte, celles-ci injectent un courant dans la résistance R permettant de polariser la grille du transistor MOS.

Les circuits de déclenchement dynamiques permettent de polariser la grille en détectant les fronts rapides  $\frac{dv}{dt}$  des ESD. La technique la plus simple, et couramment utilisée, est le

couplage capacitif représentée Figure 1.14 (d). Ce type de structure s'appelle le gcNMOS [46] (en anglais : gate coupling NMOS). La capacité C correspond soit à la capacité parasite grille/drain du MOS, soit à une capacité rajoutée. Le circuit RC est optimisé de manière à ce que le potentiel sur la grille ne dépasse pas la tension de seuil du transistor NMOS durant les conditions normales d'utilisation. Par contre, sous conditions ESD, le réseau RC couple une partie des charges ESD sur la grille permettant le déclenchement. Bien sûr, il faut s'assurer que la tension délivrée sur la grille ne dépasse pas la tension de claquage de l'oxyde.

FIGURE 1.14: Représentations schématiques des structures de protections basées sur un transistor NMOS: (a) Gate-Ground NMOS (ggNMOS), (b) déclenchement statique du NMOS par une diode Zener, (c) déclenchement statique du NMOS par des diodes en séries, (d) Gate Coupled NMOS, (e) Déclenchement dynamique par un circuit RC.

Enfin, le déclenchement dynamique de la protection avec un circuit de contrôle RC est illustré Figure 1.14 (e) [47]. Le système est composé d'un circuit RC et d'un inverseur connecté sur la grille du MOS. La constante de temps du circuit RC est d'environ une microseconde pour déclencher et forcer la protection à conduire pendant toute la durée d'une décharge.

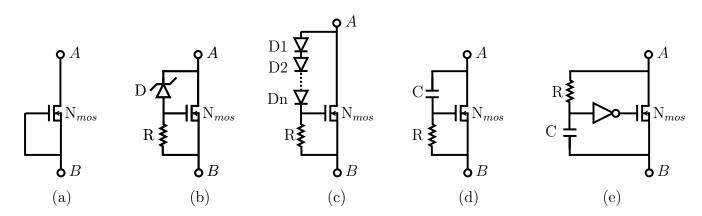

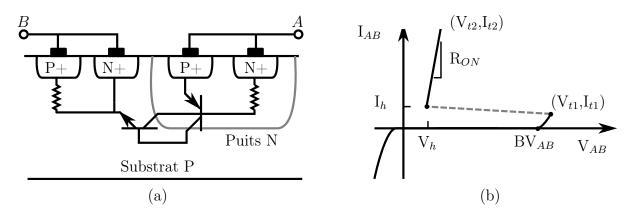

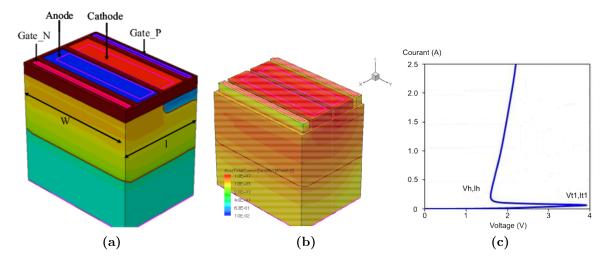

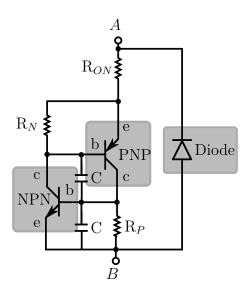

1.2.3.2.3 Thyristor l'utilisation du thyristor ou SCR (Silicon Controlled Rectifier) comme protection ESD a été introduit par Avery en 1983 [48]. La vue en coupe d'un thyristor latéral est donné Figure 1.15 (a). La structure utilise l'association de deux transistors bipolaires parasites : un NPN, constitué du puits N / Substrat P / Diffusion N+ de l'électrode B, et un PNP constitué de la Diffusion P+ de l'électrode A / Puits N / Substrat P. Les Diffusion P+ dans le substrat P et N+ dans le puits N correspondent à la prise de contact du substrat dans ces zones respectives. Lorsque cette structure est utilisée comme protection ESD, l'électrode A est connectée au plot d'entrée/sortie à protéger ou au bus d'alimentation et l'électrode B est connectée à la masse. La représentation schématique de cette structure est donnée Figure 1.16 (a). Ce type de structure présente

l'avantage de passer d'un état de forte impédance à une faible impédance de part son fort repliement à l'état passant comme illustré par la caractéristique  $I_{AB}(V_{AB})$  Figure 1.16.

D'un point de vue physique, lorsque le potentiel entre les électrodes A et B est supérieur à la tension de claquage par avalanche, la jonction composée par le contact N+ et le substrat P, va se polariser en inverse. Le courant de trous généré par l'avalanche va circuler dans la résistance du Substrat P. Le potentiel monte alors sur la base du transistor NPN. Celui-ci se déclenche et le courant de collecteur génère une chute de tension aux bornes de la résistance du puits N permettant le déclenchement du transistor PNP. Le courant du PNP crée à son tour une chute de tension dans la résistance de Substrat P permettant de maintenir le transistor NPN passant. A ce point, la structure se verrouille et il n'est plus nécessaire pour l'électrode A de maintenir le courant de trous. La tension sur cette électrode décroit jusqu'à la tension de maintient  $V_h$ . En comparaison avec le ggNMOS, la caractéristique  $I_{AB}(V_{AB})$  est similaire, cependant la tension  $V_{t1}$ du thyristor est plus importante, entre 20 et 25 V, et sa tension de repliement est plus faible de l'ordre de 1 à 2 V. La résistance à l'état passant est inférieure à l'ohm, ce qui est très favorable à la dissipation de courant.

Dans le cas ou une décharge négative est appliquée sur l'électrode A par rapport à l'électrode B, la conduction est effectuée par la diode de substrat formée par la jonction Substrat P / Puits N. La conduction de courant dans ce mode est favorable comme décrite dans le paragraphe 1.2.3.2.1.

FIGURE 1.15: Vue en coupe du thyristor latéral (a) et sa caractéristique  $I_{AB}(V_{AB})$  idéale (b).

Cette structure présente cependant deux inconvénients. Il faut veiller à ce que la tension et le courant de maintien  $(V_h,I_h)$  soient supérieurs à l'alimentation du circuit pour éviter que la structure reste enclenchée durant le fonctionnement normal (voir les marges de conceptions dans la sous-sous-section 1.2.3.1). L'autre inconvénient est, comme pour le transistor ggNMOS, qu'elle nécessite un tension  $V_{t1}$  importante pour son déclenchement, ce qui n'est pas idéal pour protéger les oxydes de grille dont la tension de rupture  $BV_{OX}$

est bien plus faible.

Pour diminuer la tension  $V_{t1}$ , un circuit de déclenchement statique constitué d'un NMOS est ajouté au SCR. Cette structure s'appelle un LVTSCR [49] (Low Voltage Trigger SCR) et sa représentation schématique est donnée Figure 1.16 (b). Le déclenchement de la structure est provoqué par le NMOS dont le fonctionnement correspond au ggNMOS décrit dans le paragraphe 1.2.3.2.2. Comme reporté dans [49], la tension de déclenchement d'un LVTSCR est cinq fois moins importante qu'un SCR standard.

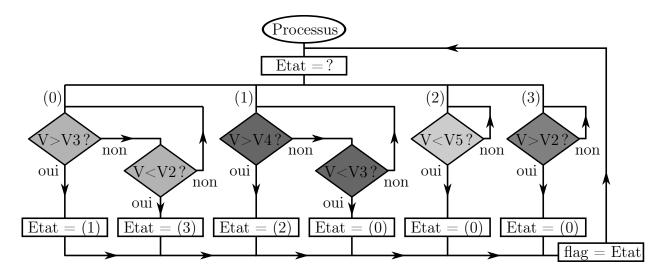

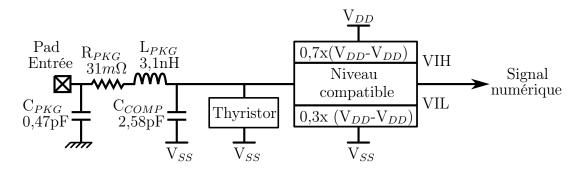

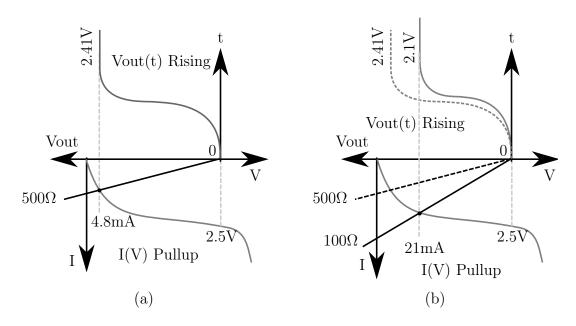

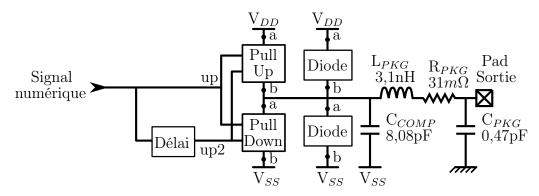

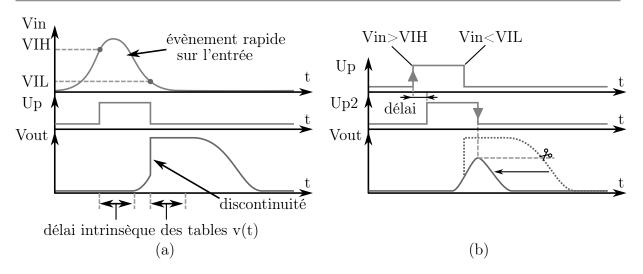

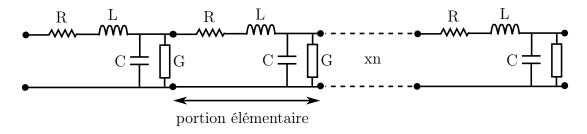

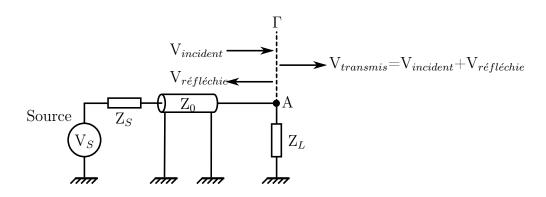

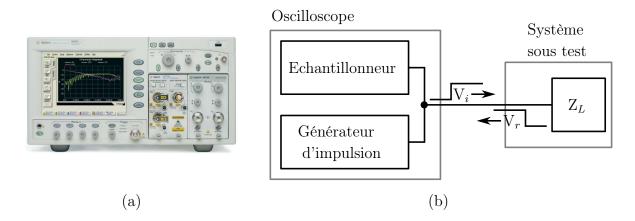

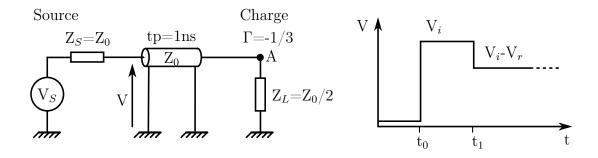

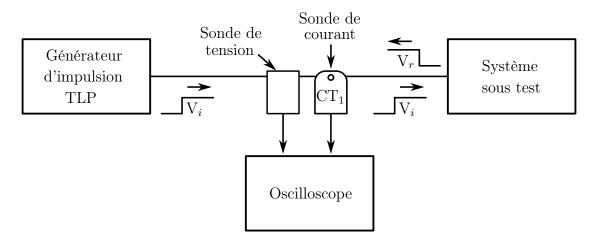

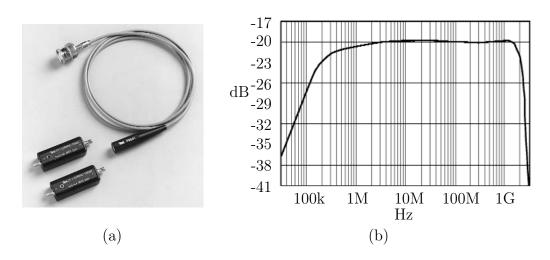

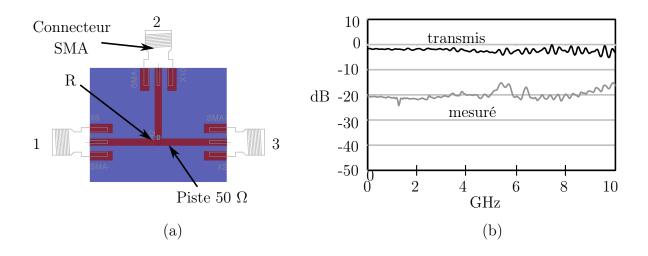

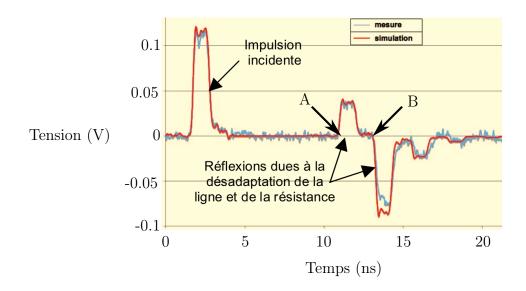

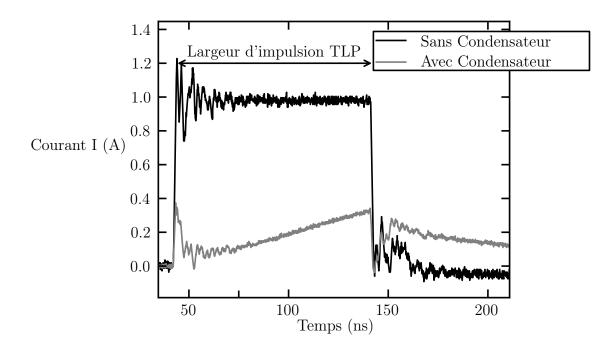

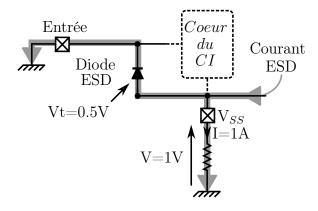

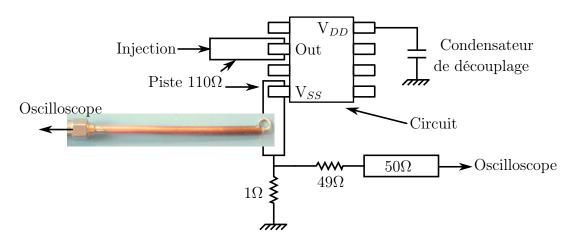

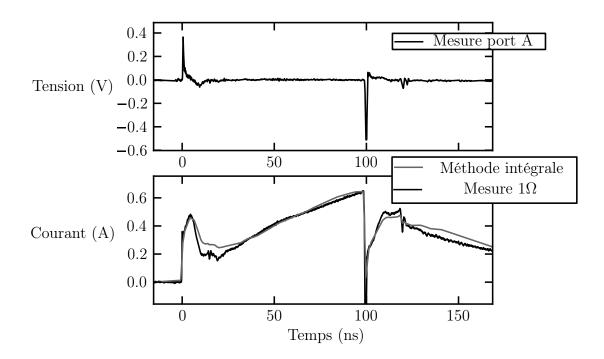

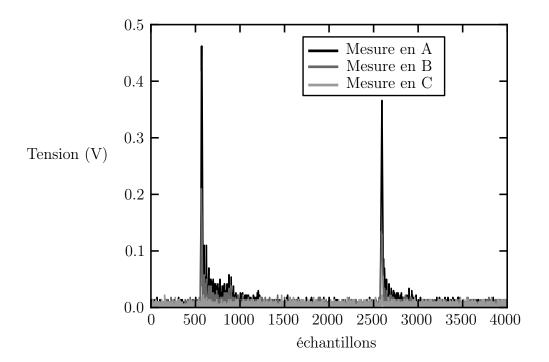

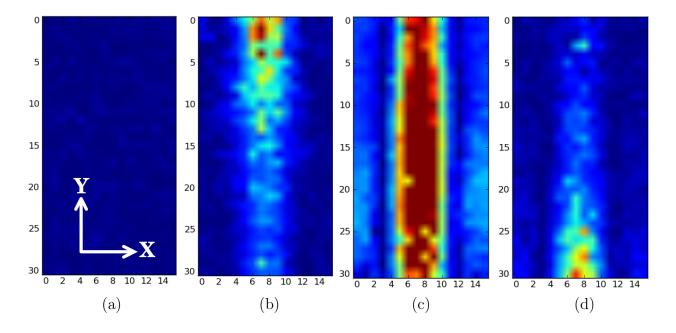

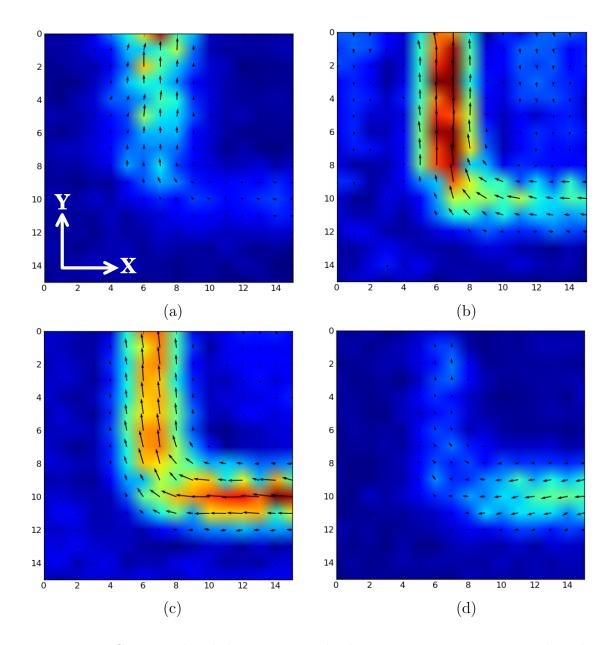

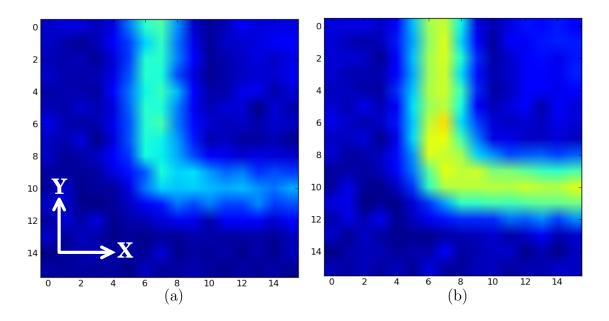

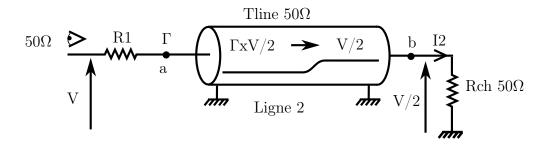

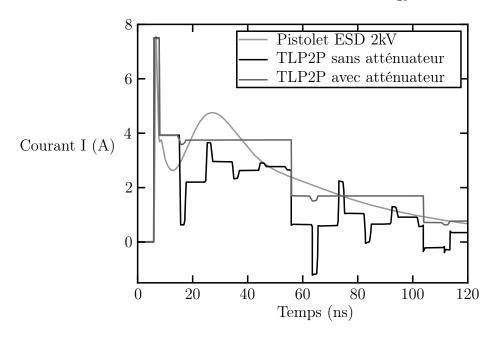

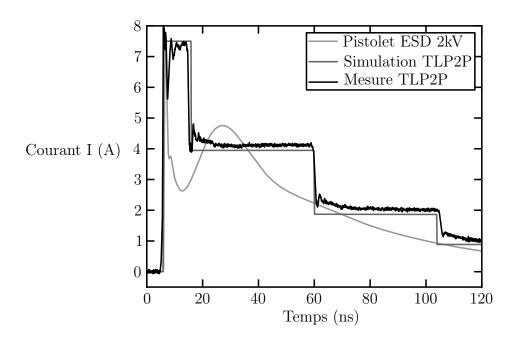

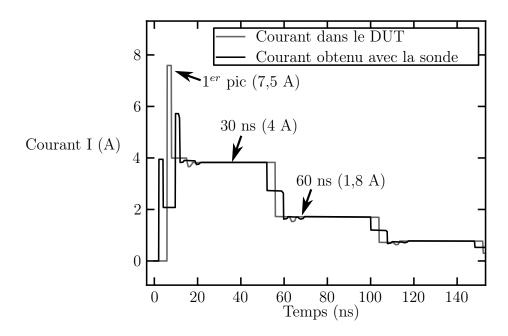

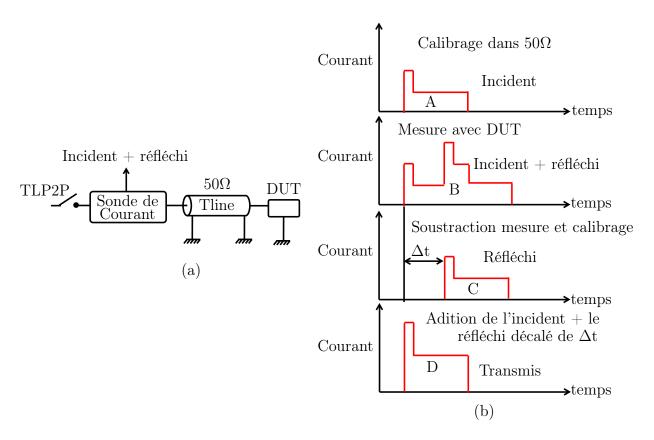

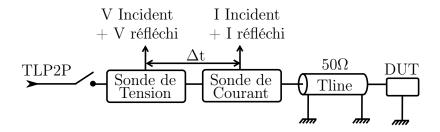

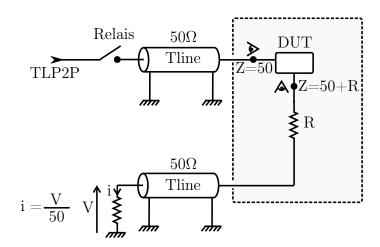

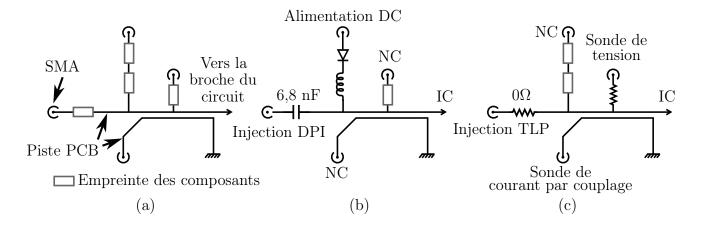

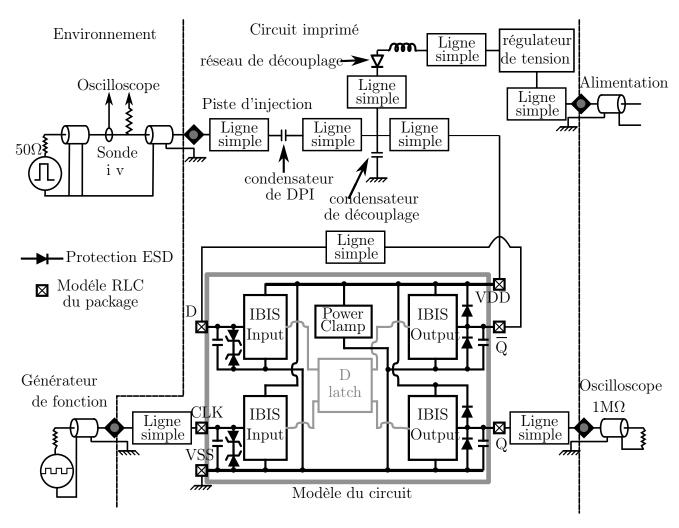

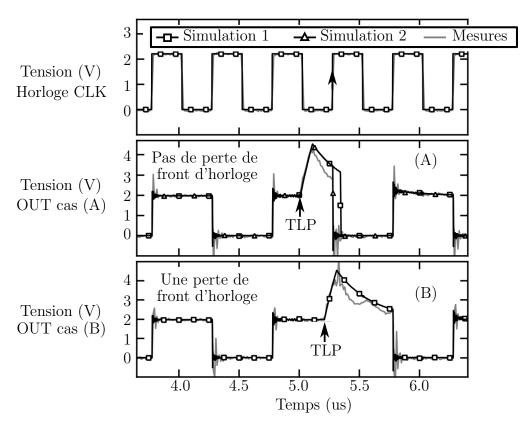

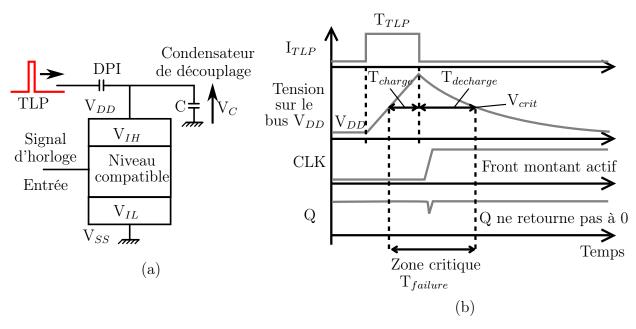

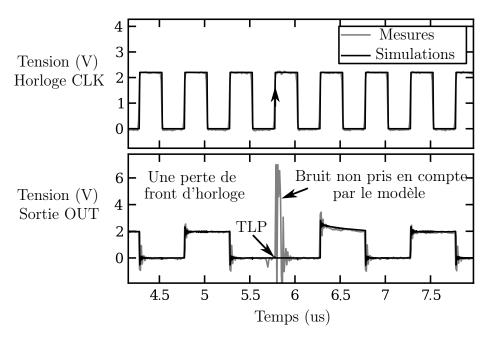

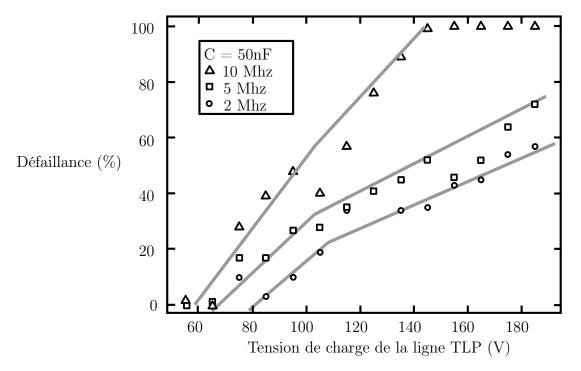

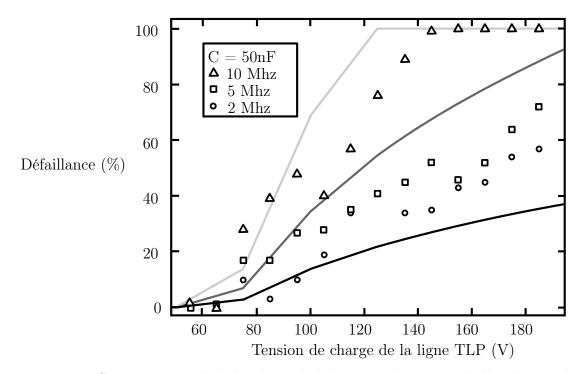

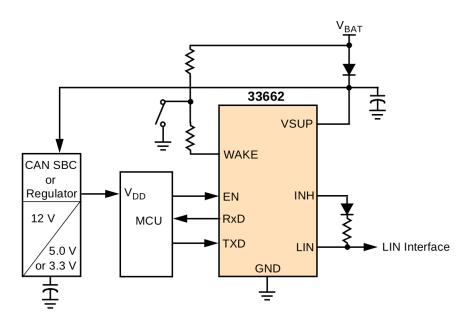

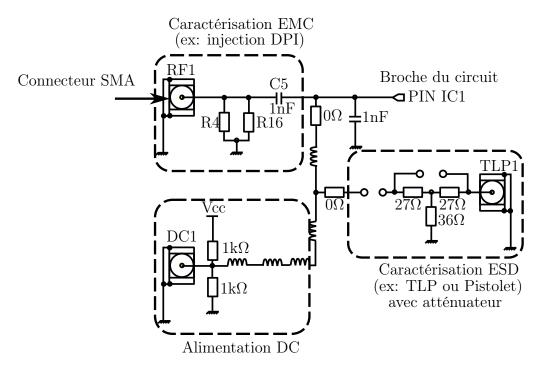

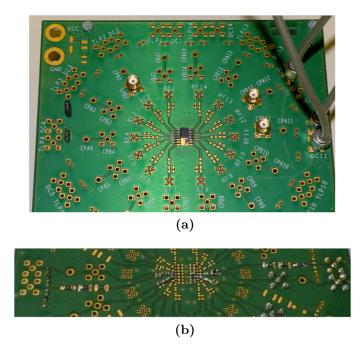

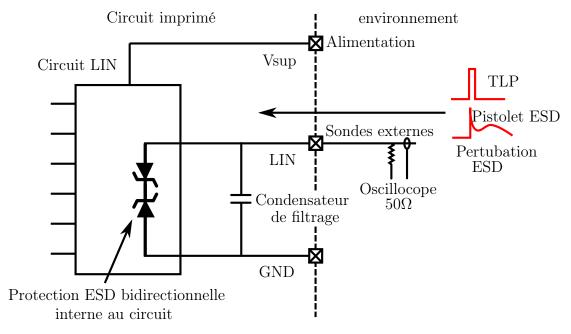

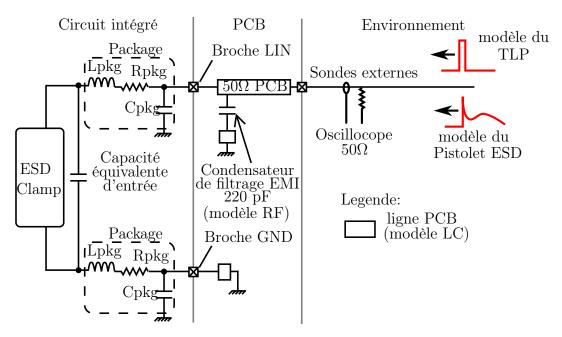

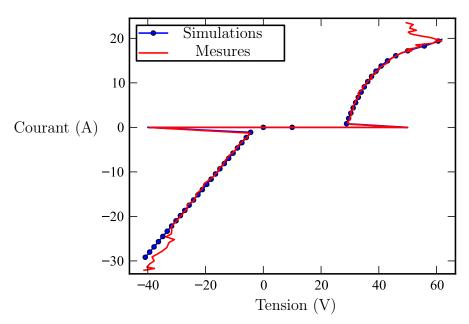

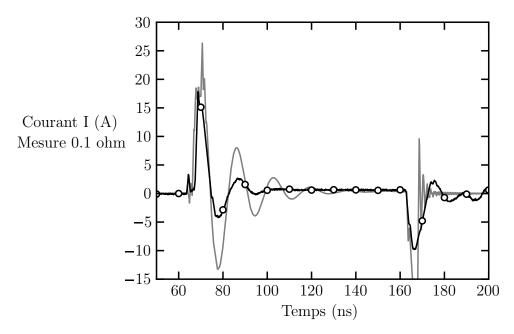

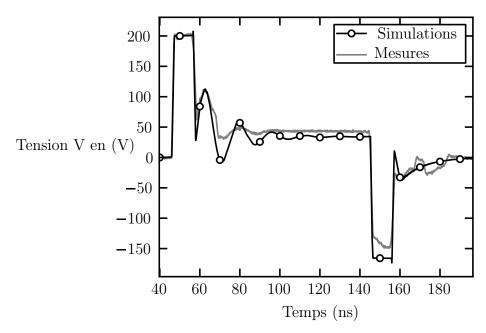

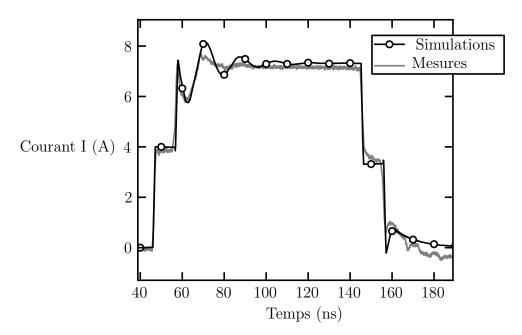

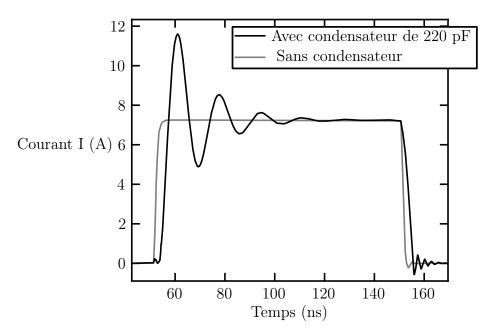

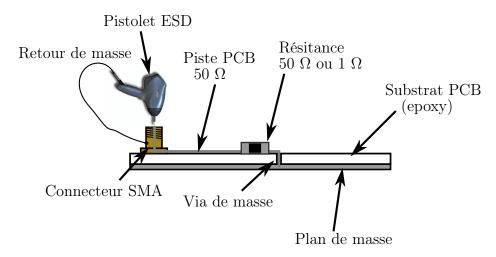

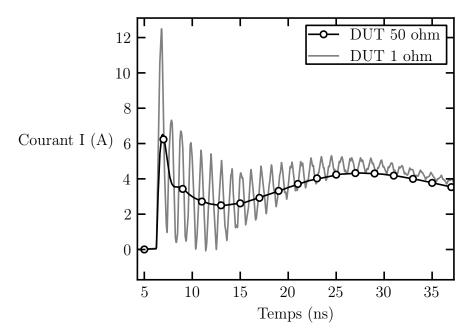

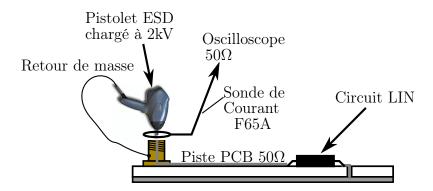

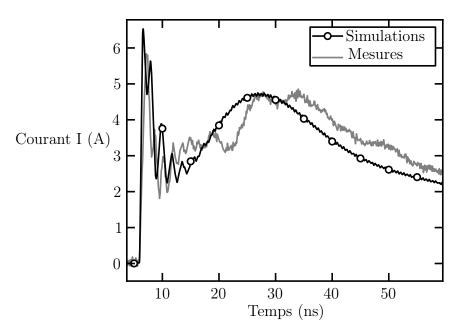

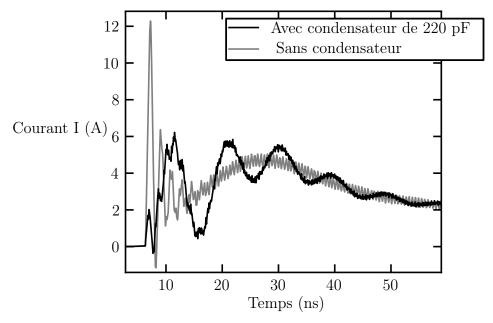

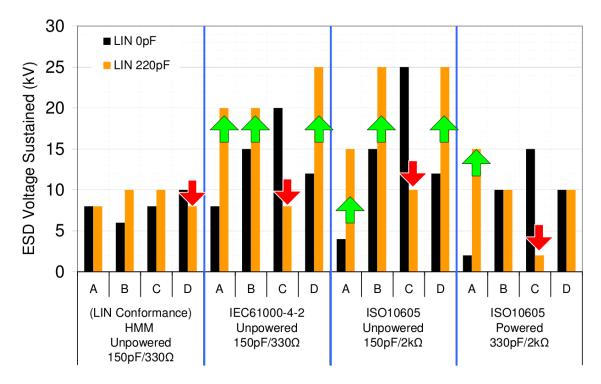

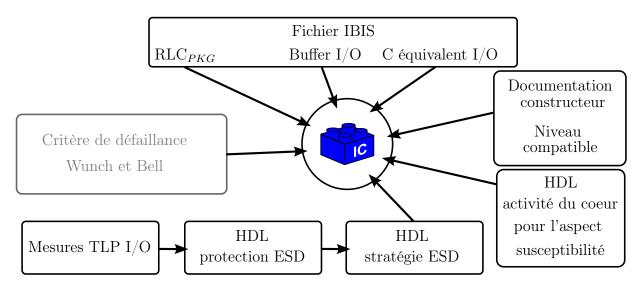

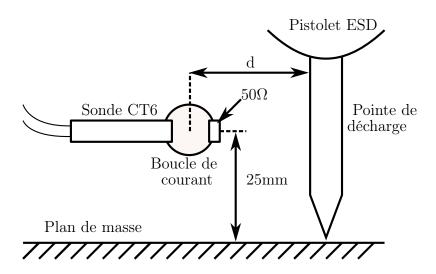

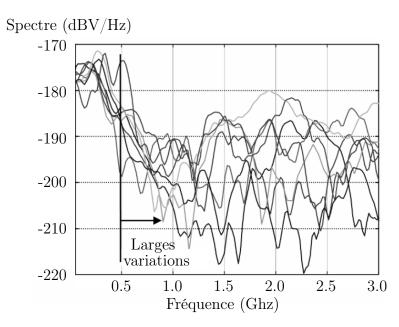

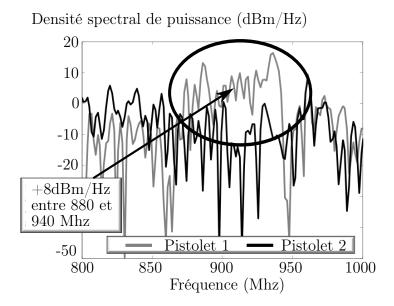

FIGURE 1.16: Représentations schématiques des structures de protections basées sur un thyristor : (a) Thyristor Latéral (LSCR), (b) Low voltage trigger SCR (LVTSCR) représentation d'après [50] et (c) LVTSCR avec des diodes séries et un circuit RC de déclenchement dynamique.