# Contributions to computer arithmetic and applications to embedded systems

Nicolas Brunie

#### ▶ To cite this version:

Nicolas Brunie. Contributions to computer arithmetic and applications to embedded systems. Other [cs.OH]. Ecole normale supérieure de lyon - ENS LYON, 2014. English. NNT: 2014ENSL0894. tel-01078204

#### HAL Id: tel-01078204 https://theses.hal.science/tel-01078204

Submitted on 28 Oct 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

en vue de l'obtention du grade de

#### Docteur de l'Université de Lyon, délivré par l'École Normale Supérieure de Lyon

**Discipline: Informatique**

#### Laboratoire de l'Informatique du Parallélisme

École Doctorale InfoMaths (ED 512)

présentée et soutenue publiquement le 16 mai 2014

par Monsieur Nicolas BRUNIE

# Contribution à l'arithmétique des ordinateurs et applications aux systèmes embarqués

Directeur de thèse : M. Florent de DINECHIN

Devant la commission d'examen formée de :

- M. Renaud AYRIGNAC, Kalray, Examinateur

- M. Laurent-Stéphane DIDIER, Université du Sud Toulon Var, Examinateur

- M. Florent de DINECHIN, INSA Lyon, Directeur

- M. David LUTZ, ARM, Rapporteur

- M. Arnaud TISSERAND, Laboratoire IRISA, Rapporteur

- M. Lionel TORRES, Université Montpellier 2, Examinateur

# Contributions to computer arithmetic in embedded systems

a hardware/software co-design story

#### **Thanks**

Ce travail n'aurait jamais pu être mené à bien sans le suivi et les conseils éclairés de mon directeur de thèse : Florent de Dinechin, et de mes encadrants à Kalray : Renaud Ayrignac et Benoît de Dinechin.

Je souhaite aussi particulièrement remercier les deux relecteurs de cette thèse : Arnaud Tisserand et David Lutz, ainsi que les autres membres de mon jury : Laurent-Stéphane Didier et Lionel Torres.

Il me serait difficile de remercier séparément toutes les personnes ayant contribué à cette thèse. J'ai eu la chance de rencontrer tant de gens passionnés et passionnants, je leur serai toujours reconnaissant. Merci à Sylvain Collange et Marius Cornea ainsi qu'à mes collègues de l'équipe Arénaire/Aric, de Kalray, du LIP et d'Intel.

| 1 | Intr | duction                                                           | 19 |

|---|------|-------------------------------------------------------------------|----|

|   | 1.1  | Embedded architectures                                            | 19 |

|   | 1.2  | Exploiting arithmetic parallelism                                 | 21 |

|   | 1.3  | Versatility versus efficiency in arithmetic                       |    |

|   | 1.4  | Outline of this thesis                                            | 23 |

|   | 1.5  |                                                                   | 24 |

|   |      | 1.5.1 Architecture of the MPPA cluster                            | 25 |

|   |      | 1.5.2 Architecture of the K1 core                                 | 25 |

| Ι | Cor  | tributions to Floating-Point Arithmetic                           | 29 |

| 2 | Con  |                                                                   | 31 |

|   | 2.1  | The IEEE-754 floating-point standard                              | 31 |

|   |      | 2.1.1 Floating-point formats                                      |    |

|   |      | 2.1.2 Rounding modes and exception                                | 32 |

|   | 2.2  | Unit in the last place                                            |    |

|   | 2.3  | State of the art of floating-point support in embedded processors | 33 |

|   |      | 2.3.1 ARM architecture                                            | 33 |

|   |      | 2.3.2 ST231                                                       | 33 |

|   |      | 2.3.3 IBM's Power architecture                                    | 34 |

|   |      | 2.3.4 Texas Instrument TMS320                                     | 34 |

|   |      | 2.3.5 Conclusion                                                  | 34 |

| 3 | Har  | 01 0                                                              | 37 |

|   | 3.1  | Introduction                                                      |    |

|   | 3.2  | Fused-Multiply and Add state of the art                           |    |

|   |      | 0 1                                                               | 39 |

|   |      | 1 1                                                               | 43 |

|   |      | 3.2.3 Exotic FMA designs                                          |    |

|   | 3.3  | Building K1's FPU: architectural study                            |    |

|   |      | 3.3.1 Mixed-precision FMA                                         |    |

|   |      | 3.3.2 2D dot-product                                              |    |

|   |      | 3.3.3 Triple-operand add                                          |    |

|   |      | 3.3.4 Conclusion on K1's first FPU structure                      |    |

|   | 3.4  | Building K1's FPU: miscellaneous contributions                    |    |

|   |      | 3.4.1 Automatic generation of bit-pattern detector                |    |

|   |      | 3.4.2 Management of subnormal numbers                             |    |

|   |      | 3.4.3 Multiplier tiling                                           | 67 |

|    | 3.5 | 3.4.4 Iterative process of extended multiplication                           | . 70  |

|----|-----|------------------------------------------------------------------------------|-------|

|    |     | 3.5.2 Summary and conclusion                                                 |       |

| 4  |     | ware Floating-Point stack                                                    | 73    |

|    | 4.1 | Implementation error                                                         |       |

|    | 4.2 | Optimized low-level floating-point primitives: division and square root      |       |

|    |     | 4.2.1 Newton-Raphson iteration                                               |       |

|    |     | 4.2.2 Binary32 iteration implementation                                      |       |

|    |     | 4.2.3 Code example and error study                                           | . 81  |

|    |     | 4.2.4 ISA extension to improve multiple rounding modes and correct exception |       |

|    |     | support                                                                      |       |

|    |     | 4.2.5 Performance result                                                     |       |

|    | 4.3 | Introduction to the development of mathematical functions                    |       |

|    |     | 4.3.1 Exponential evaluation scheme                                          |       |

|    |     | 4.3.2 Implementation and error analysis                                      |       |

|    |     | 4.3.3 Performance results and conclusion                                     | . 90  |

| 5  |     | omated code generation of mathematical functions                             | 93    |

|    | 5.1 | Introduction                                                                 |       |

|    |     | 5.1.1 State of the art                                                       |       |

|    |     | 5.1.2 Objectives and philosophy of our project                               |       |

|    | 5.2 | Arithmetic support: PythonSollya                                             |       |

|    | 5.3 | Description language                                                         |       |

|    |     | 5.3.1 Annotation system                                                      |       |

|    |     | 5.3.2 Constants, tables                                                      |       |

|    |     | 5.3.3 Polynomials                                                            |       |

|    |     | 5.3.4 Abstract type                                                          |       |

|    | 5.4 | Metalibm support libraries: miscellaneous and multi-precision                |       |

|    | 5.5 | Metalibm core: internal representation and optimization                      |       |

|    |     | 5.5.1 Format determination                                                   |       |

|    |     | 5.5.2 Operand-flavour selection and interval determination                   | . 107 |

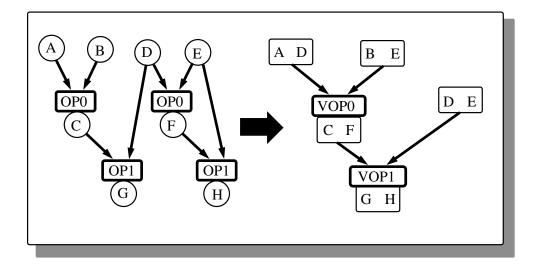

|    |     | 5.5.3 Scalar vectorizer                                                      | . 107 |

|    | 5.6 | Code and proof generation                                                    | . 108 |

|    |     | 5.6.1 Gappa script generation                                                | . 108 |

|    |     | 5.6.2 Code generation and target specific processing                         | . 109 |

|    | 5.7 | Vectorization support                                                        | . 110 |

|    |     | 5.7.1 Result blending                                                        | . 112 |

|    |     | 5.7.2 Callout extraction                                                     | . 113 |

|    |     | 5.7.3 Static vectorization implementation                                    | . 113 |

|    | 5.8 | Application: vectorized correctly rounded exponential and logarithm          | . 115 |

|    | 5.9 | Conclusion and perspectives                                                  | . 117 |

|    |     |                                                                              |       |

| II | Ar  | chitecture and application of a deeply integrated reconfigurable fabric      | 119   |

| 6  | Rec | onfigurable taxonomy and state of the art                                    | 121   |

|    | 6.1 | FPGAs                                                                        |       |

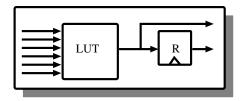

|    |     | 6.1.1 Reconfigurable Logic Cell                                              | . 122 |

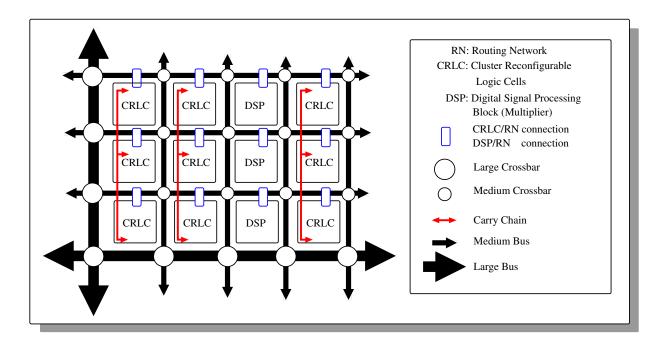

|   |      | 6.1.2   | Routing network                                                          | . 122 |

|---|------|---------|--------------------------------------------------------------------------|-------|

|   |      | 6.1.3   | Fast arithmetic support                                                  |       |

|   |      | 6.1.4   | Memory block                                                             |       |

|   |      | 6.1.5   | Conclusion: FPGA versus ASIC as computing systems                        |       |

|   | 6.2  |         | GA and the DREAM Digital Signal Processor                                |       |

|   | 6.3  |         | Project                                                                  |       |

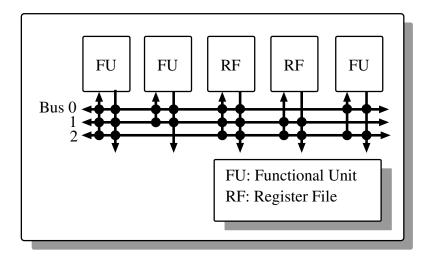

|   | 0.0  | 6.3.1   | Transport-triggered architecture                                         |       |

|   |      | 6.3.2   | TCE configurability                                                      |       |

|   |      |         |                                                                          |       |

| 7 | Dee  |         | egrated Reconfigurable Fabric                                            | 129   |

|   | 7.1  |         | all view                                                                 |       |

|   | 7.2  | Basic   | cell                                                                     | . 131 |

|   |      | 7.2.1   | Cell interfaces                                                          |       |

|   |      | 7.2.2   | Cell micro-architecture after a first round of design exploration        |       |

|   | 7.3  | Interc  | onnect network                                                           | . 133 |

|   |      | 7.3.1   | Generalized carry-chain                                                  | . 134 |

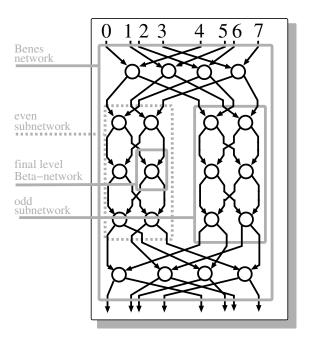

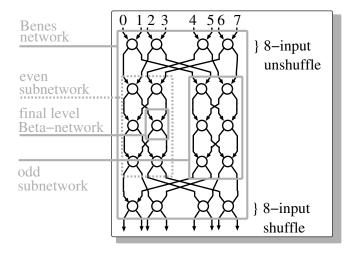

|   |      | 7.3.2   | Elementary interconnect node: $\beta$ -network                           | . 135 |

|   |      | 7.3.3   | Crossbar-based architecture                                              | . 135 |

|   |      | 7.3.4   | Permutation-based networks: introduction and advantages                  | . 136 |

|   | 7.4  | Contr   | ibution to permutation-based Benes networks                              | . 139 |

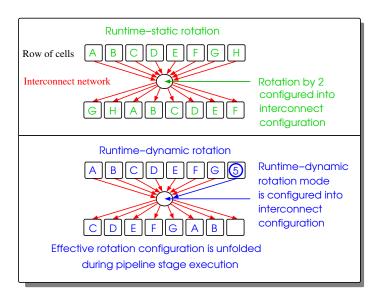

|   |      | 7.4.1   | Using the interconnect network to perform runtime-dynamic shifts and ro- | -     |

|   |      |         | tations                                                                  | . 139 |

|   |      | 7.4.2   | Benes network and rotation: state of the art                             | . 141 |

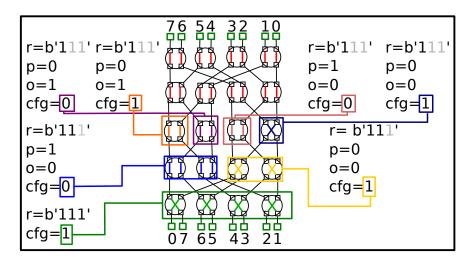

|   |      | 7.4.3   | Realizing rotation                                                       | . 141 |

|   |      | 7.4.4   | Configuration unfolding                                                  | . 143 |

|   |      | 7.4.5   | Hardware implementation and comparison                                   | . 144 |

|   |      | 7.4.6   | Generalization                                                           | . 145 |

|   | 7.5  | Concl   | usion                                                                    | . 148 |

| 0 | т    | 7       | Education I Co. Duranton                                                 | 140   |

| 8 |      |         | Triggered Co-Processor                                                   | 149   |

|   | 8.1  | _       | e master coprocessor                                                     |       |

|   |      | 8.1.1   |                                                                          |       |

|   |      | 8.1.2   | Coprocessor architecture                                                 |       |

|   |      | 8.1.3   | Instruction Set Architecture                                             |       |

|   | 8.2  | _       | ocessor integration and shared TTA                                       |       |

|   |      | 8.2.1   | Shared TTA                                                               |       |

|   |      | 8.2.2   | Input buffer                                                             |       |

|   |      | 8.2.3   | Input arbiter                                                            |       |

|   |      | 8.2.4   | Configurable master id pipeline                                          |       |

|   |      | 8.2.5   | Output FIFO                                                              |       |

|   |      | 8.2.6   | System sizing                                                            |       |

|   | 8.3  | Concl   | usion                                                                    | . 157 |

| 9 | Rece | onfiour | rable Kernel Toolchain                                                   | 159   |

| , | 9.1  | _       | RTL generation and architectural exploration                             |       |

|   | J.1  | 9.1.1   | Reconfigurable matrix parametrization                                    |       |

|   |      | 9.1.1   | Basic cell parametrization                                               |       |

|   | 9.2  |         | front-end                                                                |       |

|   | J•∠  | 9.2.1   | Intermediate representation                                              |       |

|   |      | 9.2.1   | Decomposition: technology mapping                                        |       |

|   |      | 1.4.4   | Decomposition technology mapping                                         | 100   |

|     | <ul><li>9.3</li><li>9.4</li><li>9.5</li></ul>    | RKC Backend: place and route  9.3.1 Single level placement  9.3.2 Multiple-level placement  9.3.3 Routing  DIRFsim: software emulation  Conclusion                                                                                                                                                                                                                                                                                                                   | 167<br>168<br>169<br>169                             |

|-----|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 10  | 10.1<br>10.2<br>10.3                             | Advanced Encryption Standard  10.1.1 SubBytes  10.1.2 ShiftRows  10.1.3 MixColumns  10.1.4 AddRoundKey  10.1.5 Conclusion  Hash function: SHA-1  Design exploration and results  Conclusion and future work                                                                                                                                                                                                                                                          | 172<br>173<br>173<br>173<br>173<br>174               |

| III | N                                                | IMT Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 177                                                  |

| 11  | <ul><li>11.1</li><li>11.2</li><li>11.3</li></ul> | SIMT architecture  11.1.1 Management of multiple branches: mask stack  11.1.2 Dynamic Warp Formation  11.1.3 Thread frontier  Towards NIMT architecture  11.2.1 Multiple Fetch units  11.2.2 Enforcing earliest possible reconvergence: min-PC scheduling policy  11.2.3 Simultaneous Branch Interweaving  11.2.4 Simultaneous Warp Interweaving  11.2.5 Hot and cold context tables: providing minPC list with easy access  Evaluation  Conclusion and perspectives | 181<br>183<br>184<br>185<br>186<br>187<br>188<br>188 |

|     |                                                  | onclusion and perspectives                                                                                                                                                                                                                                                                                                                                                                                                                                           | 193                                                  |

|     |                                                  | clusion and future works                                                                                                                                                                                                                                                                                                                                                                                                                                             | 195                                                  |

|     | -                                                | pendix                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 197                                                  |

| 13  | Intro                                            | oduction to correctly rounded implementation                                                                                                                                                                                                                                                                                                                                                                                                                         | 199                                                  |

| 14  |                                                  | ful basic blocks for FPU design         Synthesis results          14.1.1 Integer adder          14.1.2 Leading zero counter          14.1.3 Logic shifter          14.1.4 Multiplier                                                                                                                                                                                                                                                                                | 201<br>202<br>203                                    |

| Contents                     | 9 |

|------------------------------|---|

|                              |   |

| 14.2 Analysis and conclusion |   |

# **List of Figures**

| 1.1  | and performance                                                                                    | 20  |

|------|----------------------------------------------------------------------------------------------------|-----|

| 1.2  | 1                                                                                                  |     |

| 1.3  |                                                                                                    |     |

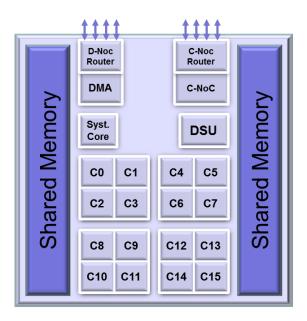

| 1.4  | MPPA's cluster architecture                                                                        | 26  |

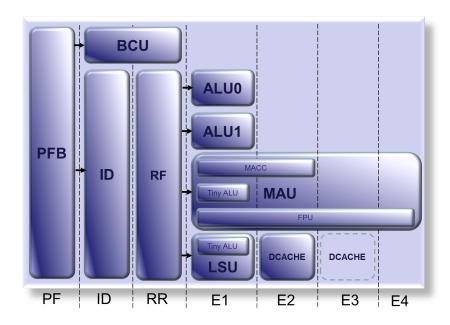

| 1.5  | Kalray's K1 core architecture                                                                      | 27  |

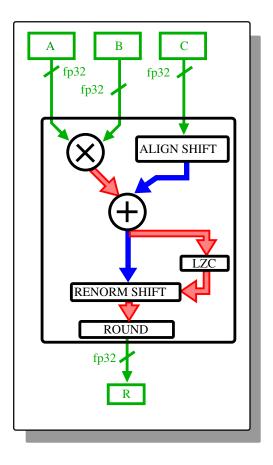

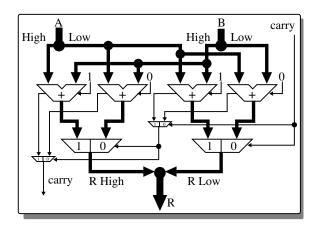

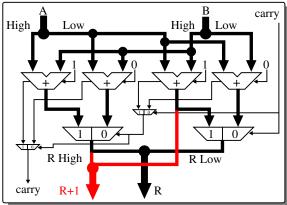

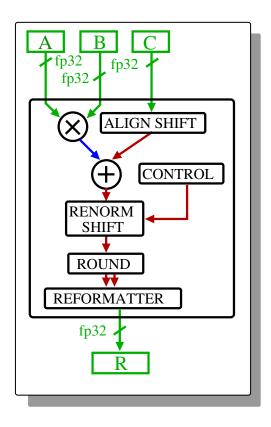

| 3.1  | FMA simplified micro-architecture. The internal critical path is indicated by boxed                |     |

|      | arrows                                                                                             | 39  |

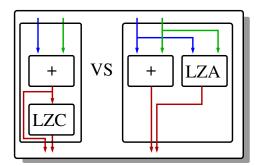

| 3.2  | Comparison leading zero count mechanisms on addition: LZC versus LZA                               | 40  |

| 3.3  | Last-level carry-select adder structure ( <i>Left</i> ). Compound adder structure ( <i>Right</i> ) | 43  |

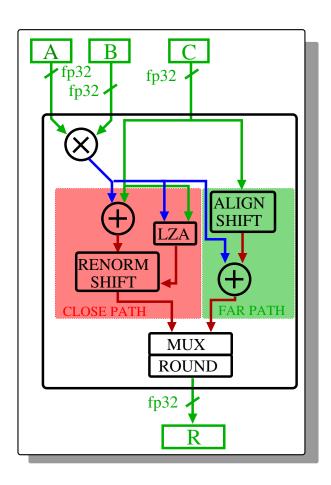

| 3.4  | FMA multi-path architecture                                                                        | 44  |

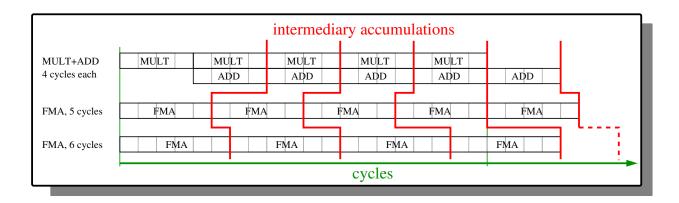

| 3.5  | Comparison of latencies: FMA versus paired FADD/FMUL                                               | 46  |

| 3.6  | IBM High and Low part FMA overview                                                                 | 47  |

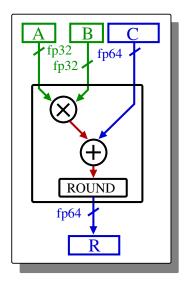

| 3.7  | Mixed precision FMA overview                                                                       | 50  |

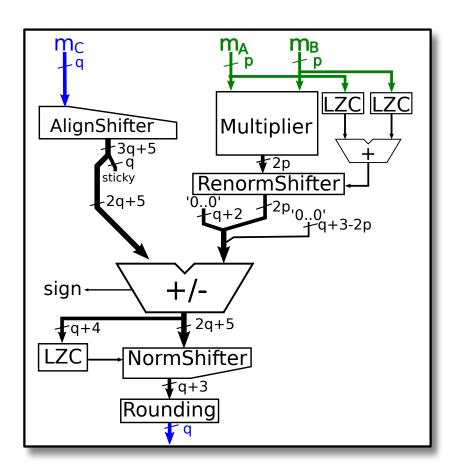

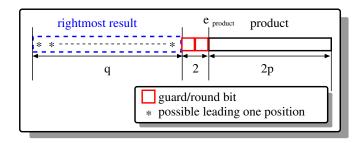

| 3.8  | MPFMA simplified architecture                                                                      | 51  |

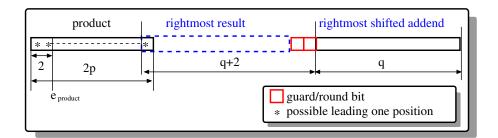

| 3.9  | MPFMA datapath layout, and possible leading digit positions, for product-anchored                  | 52  |

| 3 10 | cases, $e_{product} - e_{addend} > 2p-1$                                                           | 32  |

| 3.10 | cases, $e_{product} - e_{addend} < -2$                                                             | 52  |

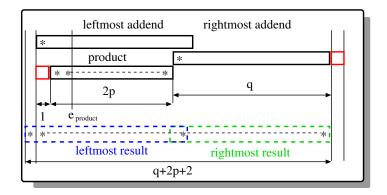

| 3 11 | MPFMA datapath layout, and leading digit possible positions, for cancellation cases,               | 02  |

| 0.11 | $-2 \le e_{product} - e_{addend} \le 2p-1 \dots \dots \dots \dots \dots \dots \dots \dots$         | 53  |

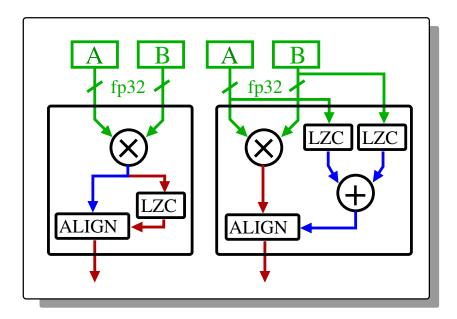

| 3.12 | Two solutions for product pre-normalization in the MPFMA                                           | 54  |

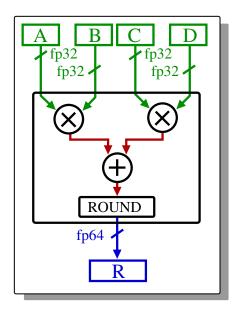

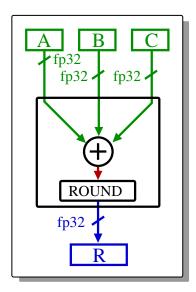

|      | 2D dot-product operation scheme                                                                    | 58  |

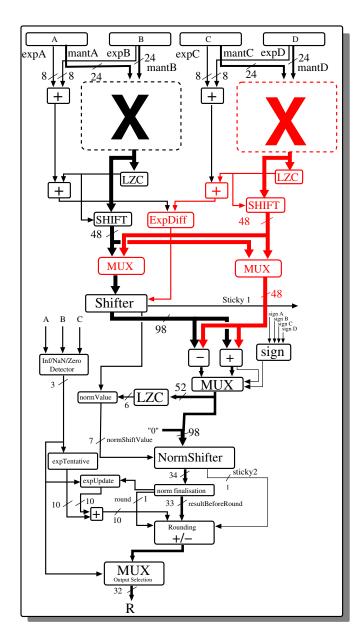

|      | 2D dot-product micro-architecture (main differences with FMA32 are highlighted                     |     |

|      | in red)                                                                                            | 59  |

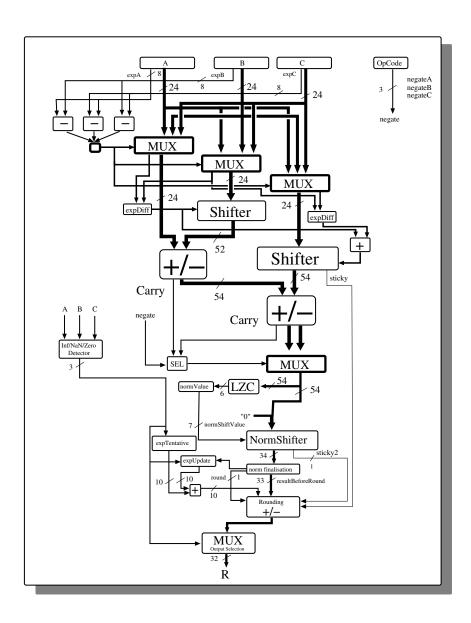

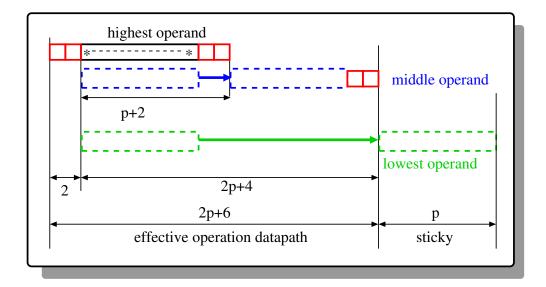

| 3.15 | Triple-operand addition operation scheme                                                           | 60  |

|      | Triple-operand micro-architecture                                                                  | 62  |

|      | Alignment scheme for triple-operand add                                                            | 63  |

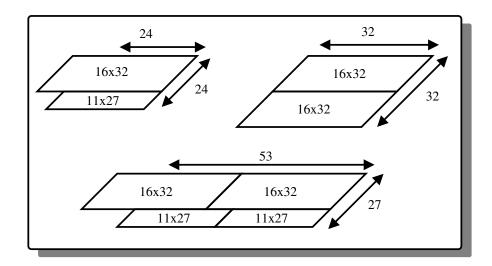

| 3.18 | Tiling of $16 \times 32$ and $11 \times 27$ multipliers used to implement K1 operations            | 68  |

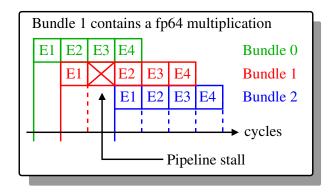

| 3.19 | Iterative binary64 multiplication effect on K1's pipeline                                          | 69  |

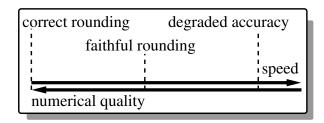

| 4.1  | Correlation between function implementation speed and numerical quality                            | 74  |

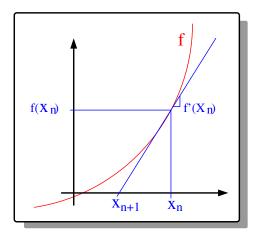

| 4.2  | Newton-Raphson method                                                                              | 77  |

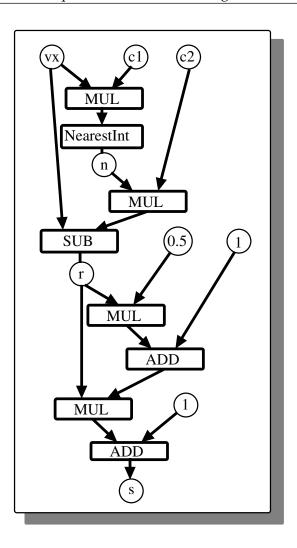

| 5.1  | Operation graph of MDL description reproduced in Listing 5.2                                       | 98  |

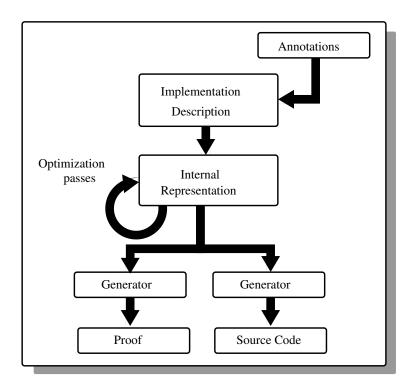

| 5.2  | Metalibm's process overview                                                                        |     |

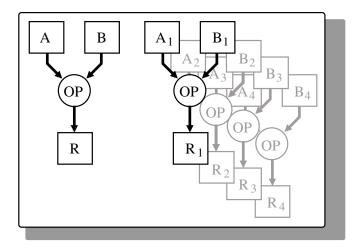

| 5.3  | Example of Super Word Level Parallelism extraction                                                 |     |

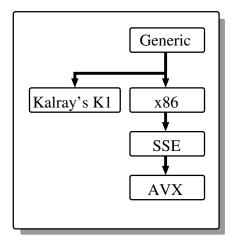

| 5.4  | Metalibm architecture-description hierarchy                                                        | 109 |

12 List of Figures

| 5.5   | Scalar operation scheme (left) comparison to vector operation scheme (right)                                                                                                       | 111 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

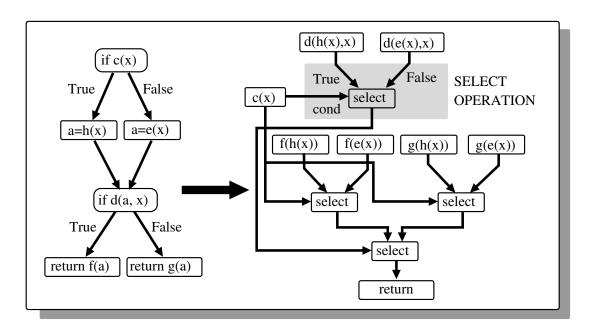

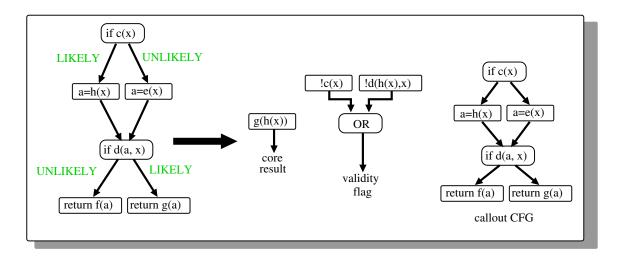

| 5.6   | Example of blending result reduction effect on an operation graph                                                                                                                  | 112 |

| 5.7   | Example of core, validity flag and callout extraction                                                                                                                              |     |

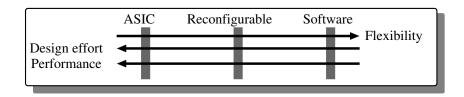

| 6.1   | ASIC, Reconfigurable and Software ordered according to flexibility, design effort                                                                                                  |     |

|       | and performance                                                                                                                                                                    | 121 |

| 6.2   | LUT and registered/direct output                                                                                                                                                   |     |

| 6.3   | General architecture of an FPGA matrix                                                                                                                                             |     |

| 6.4   | The DREAM architecture (figure extracted from [23])                                                                                                                                | 125 |

| 6.5   | Example of transport-triggered architecture                                                                                                                                        |     |

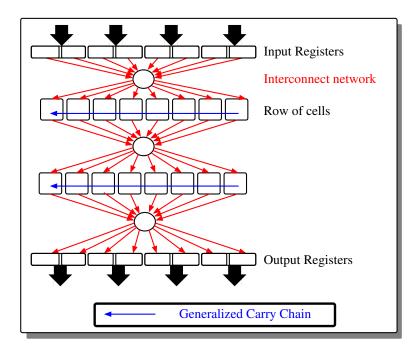

| 7.1   | Reconfigurable matrix overview                                                                                                                                                     | 130 |

| 7.1   |                                                                                                                                                                                    |     |

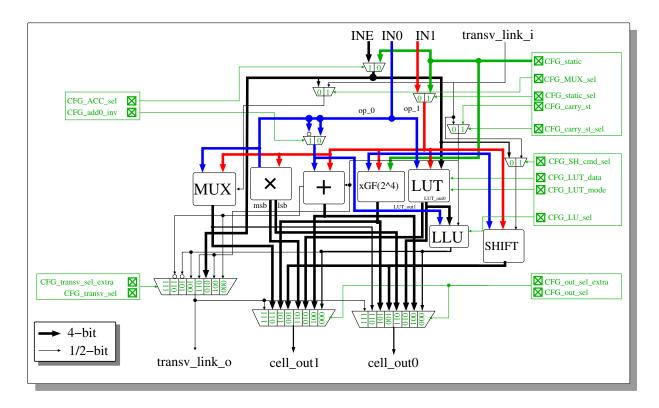

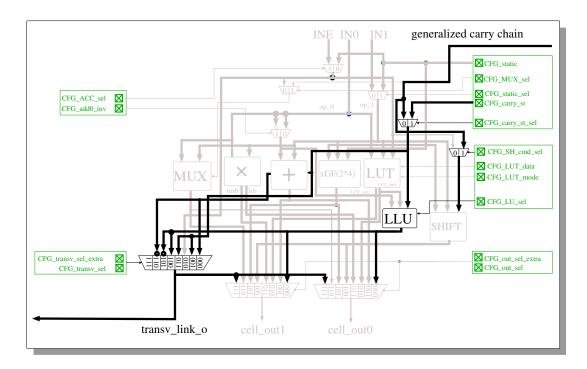

|       | Reconfigurable Logic Cell interfaces and micro-architecture                                                                                                                        |     |

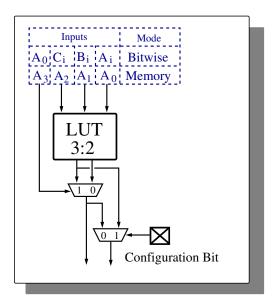

| 7.3   | The two operation modes of the <i>i</i> -th $8 \times 2$ LUTs of a RLC                                                                                                             |     |

| 7.4   | RLC generalized carry chain                                                                                                                                                        |     |

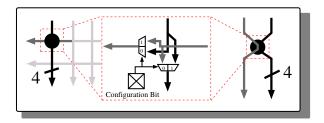

| 7.5   | Interconnect junction point                                                                                                                                                        |     |

| 7.6   | An example of crossbar-based interconnect architecture                                                                                                                             |     |

| 7.7   | Example of crossbar-based routing configuration                                                                                                                                    | 136 |

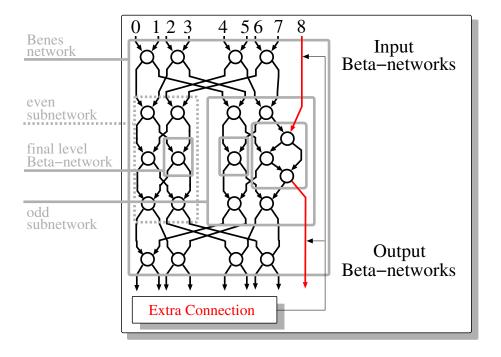

| 7.8   | Two types of half 16-input Benes networks: <b>butterfly</b> (left) and <b>unshuffle</b> (right)                                                                                    | 137 |

| 7.9   | Full butterfly-based 8-input Benes network                                                                                                                                         | 138 |

| 7.10  | Full shuffle-based 8-input Benes network                                                                                                                                           |     |

|       | Differences between runtime-static and runtime-dynamic rotation modes                                                                                                              |     |

|       | Example of configuration unfolding for rotation in shuffle-based Benes network                                                                                                     |     |

|       | Extension of shuffle-based Benes network for odd sizes                                                                                                                             |     |

| 0.1   |                                                                                                                                                                                    | 150 |

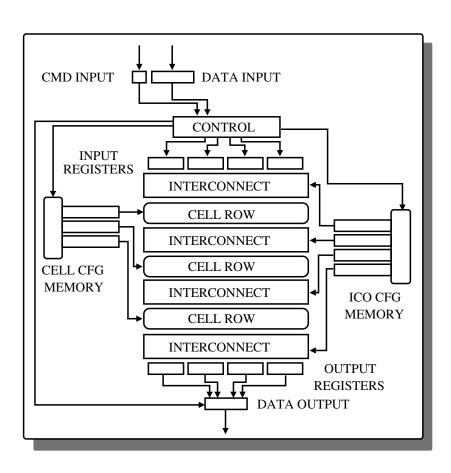

| 8.1   | Reconfigurable coprocessor architecture                                                                                                                                            |     |

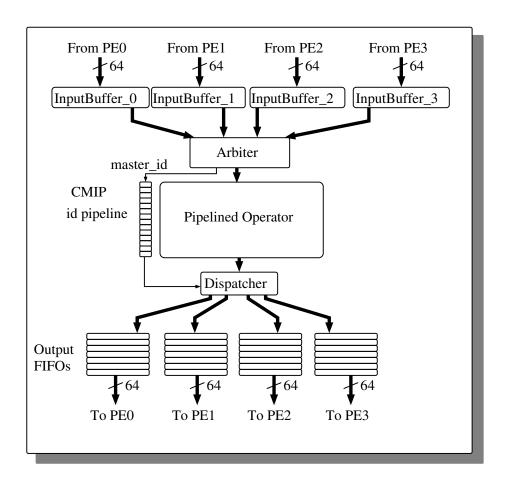

| 8.2   | Architecture for TTA operator virtual sharing                                                                                                                                      |     |

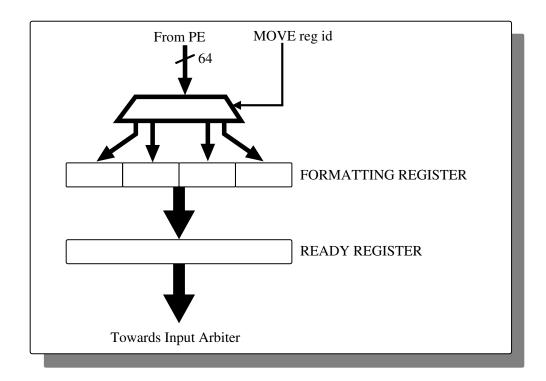

| 8.3   | Structure of an input register                                                                                                                                                     | 154 |

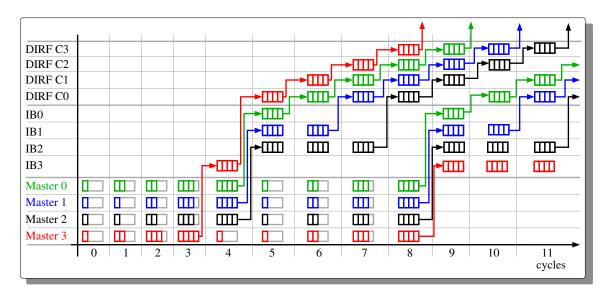

| 8.4   | Example of multiple masters accessing the coprocessor with input buffering and arbitration towards the DIRF (master <i>i</i> : formatting register of the <i>i</i> -th master, IB: |     |

|       | input buffer ready register, C i: DIRF i-th pipeline stage)                                                                                                                        | 155 |

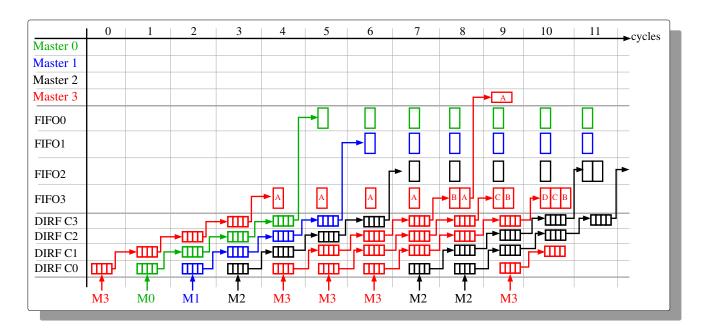

| 8.5   | Example of multiple masters accessing the coprocessor with output FIFO buffering                                                                                                   | 100 |

| 0.5   | and shared pipeline steps (M $i$ : data originating from Master $i$ )                                                                                                              | 156 |

|       |                                                                                                                                                                                    |     |

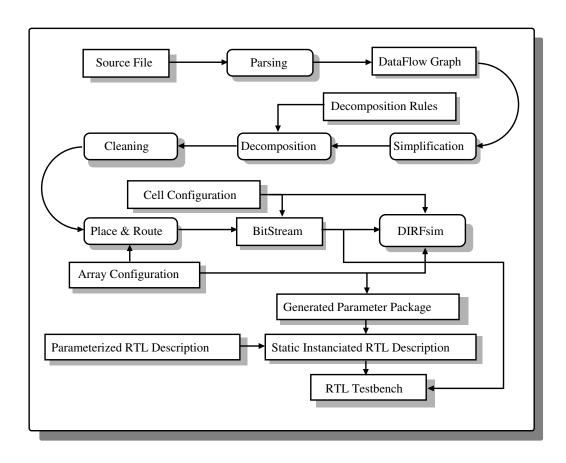

| 9.1   | Steps of the reconfigurable kernel toolchain                                                                                                                                       | 159 |

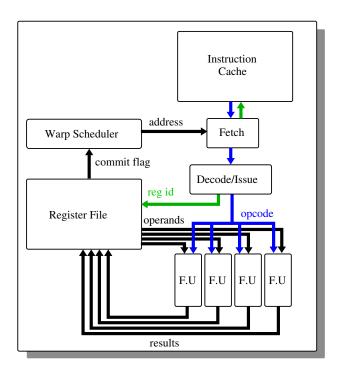

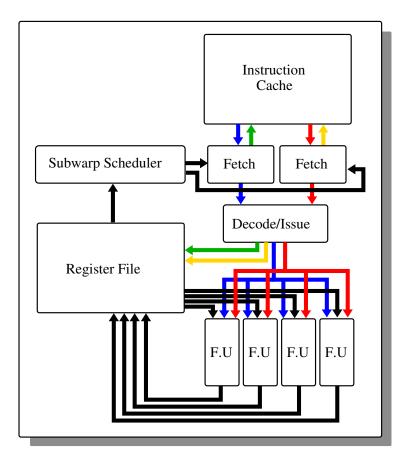

| 11.1  | Single-Instruction Multiple-Thread architecture                                                                                                                                    | 180 |

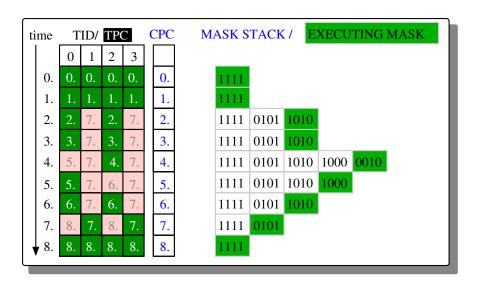

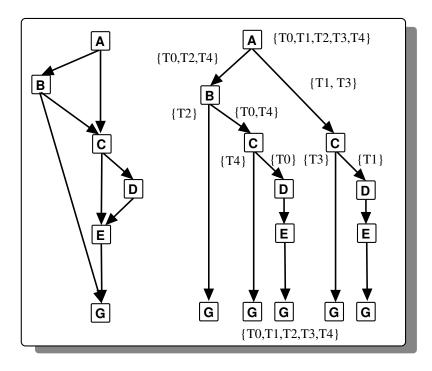

| 11.2  | Example program execution on SIMT architecture with mask-stack                                                                                                                     | 182 |

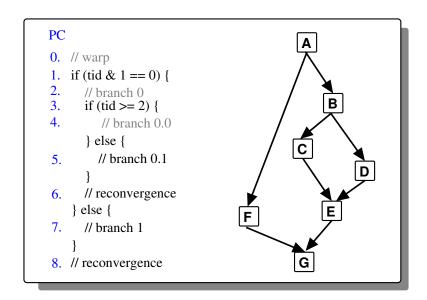

|       | Example of kernel program, tid is the thread identifier (unique for each thread in a                                                                                               |     |

|       | warp)                                                                                                                                                                              | 182 |

| 11 4  | Dynamic Warp Formation with thread migration                                                                                                                                       |     |

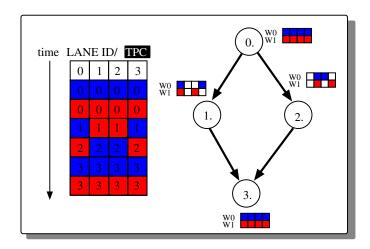

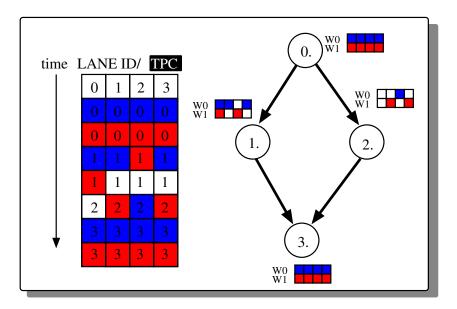

|       | Lane-aware Dynamic Warp Formation                                                                                                                                                  |     |

|       |                                                                                                                                                                                    |     |

| 11.0  | Example of thread frontier                                                                                                                                                         | 100 |

|       | N-Instruction Multiple-Thread architecture for N=2                                                                                                                                 |     |

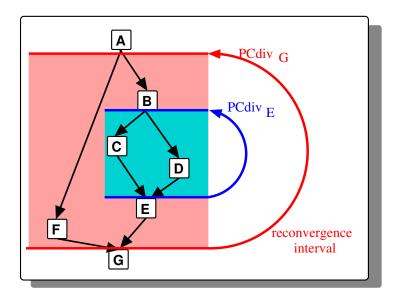

|       | Reconvergence instruction and min-PC policy for the example program                                                                                                                |     |

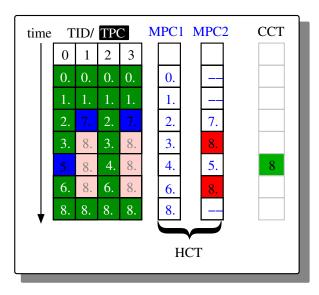

|       | Example program execution with SBI                                                                                                                                                 | 188 |

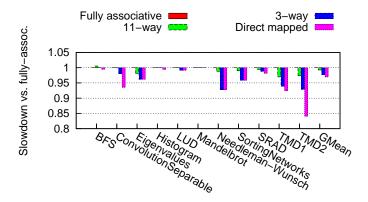

| 11.10 | OSlowdown of various set-associativity with respect to fully associative friendly warp                                                                                             |     |

|       | lookup tables                                                                                                                                                                      |     |

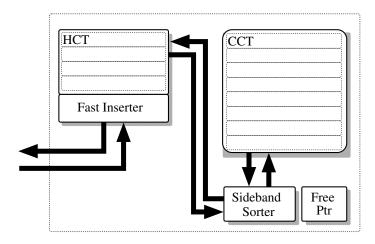

| 11.11 | 1Structure and relations of the context tables                                                                                                                                     | 189 |

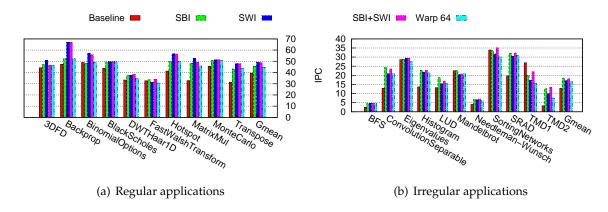

| 11.12 | 2Performance of SBI, SWI, and combination of SBI and SWI, with a thread-frontier                                                                                                   |     |

|       | based 64-wide warp implementation for reference                                                                                                                                    | 190 |

List of Figures 13

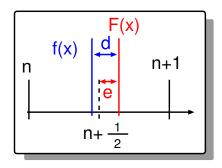

| 13.1 | Illustration of hard-to-round case condition              | 199 |

|------|-----------------------------------------------------------|-----|

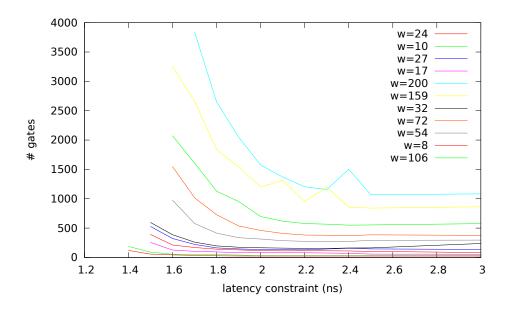

| 14.1 | Adder area with respect to latency and width              | 202 |

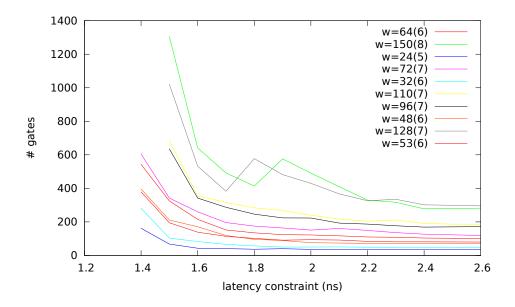

| 14.2 | Leading Zero Count area with respect to latency and width | 203 |

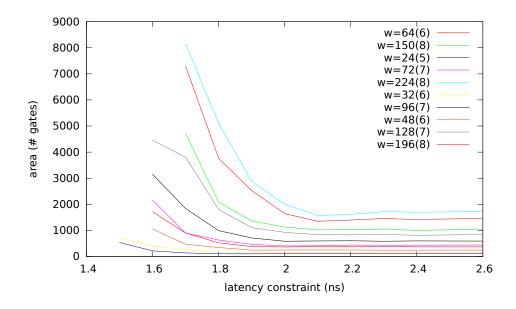

| 14.3 | Logic shift area with respect to latency and width        | 204 |

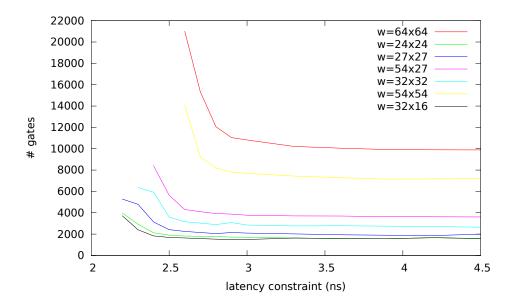

| 14.4 | Multiplier area with respect to latency and width         | 205 |

## **List of Tables**

| 2.1                               | IEEE floating-point format                                                                                                                                        | 31                               |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5   | ARM Cortex-A9: binary32 performance results                                                                                                                       | 37<br>38<br>55<br>55<br>57<br>58 |

| 3.7                               | Summary of K1 FPU performance                                                                                                                                     | 72                               |

| 4.1                               | Binary32 implementation of $\frac{1}{b}$ based on Newton-Raphson algorithm Binary32 implementation of $\frac{1}{\sqrt{a}}$ based on Newton-Raphson algorithm      | 78<br>79                         |

| 4.3<br>4.4                        | Code size for K1 binary32 approximation table and division function without table . Latencies for Newton-Raphson initial approximation loading from memory, in K1 | 80                               |

| 4.5<br>4.6                        | Synthesis result for hard-coded approximation tables and seed operators                                                                                           | 80<br>81<br>84                   |

| 4.7                               | Performance of several implementations of binary32 reciprocal, division and square root                                                                           | 85                               |

| <ul><li>4.8</li><li>4.9</li></ul> | •                                                                                                                                                                 | 90<br>90                         |

| 5.1<br>5.2                        | Accuracy requirement for correctly-rounded implementation                                                                                                         | l04                              |

| 5.2                               | Performance results of scalar function generated by our metalibm and compared to manual implementations                                                           | 116                              |

| J.J                               | several Intel's architectures                                                                                                                                     | 116                              |

| 7.1                               | Synthesis results for shuffle-based and butterfly-bases Benes networks, with and without dynamic rotation support                                                 | l <b>44</b>                      |

| 9.1                               | Synthesis result comparison various multiplication by constant algorithms implemented in RKC                                                                      | l65                              |

| 10.2                              | Comparison of interconnect efficiency on AES                                                                                                                      | 175                              |

16 List of Tables

| 11.1 | Area overhead SBI, SWI and SBI+SWI components | 191 |

|------|-----------------------------------------------|-----|

| 14.1 | Integer adder synthesis results               | 201 |

| 14.2 | Leading Zero Counter synthesis results        | 202 |

| 14.3 | Logic Shifter synthesis results               | 203 |

| 14.4 | Multiplier synthesis results                  | 204 |

# **List of Code Listings**

| 3.1  | binary64 accumulation of binary32 operand products                               |

|------|----------------------------------------------------------------------------------|

| 3.2  | Sum-of-product of binary32 operands in binary64 precision                        |

| 4.1  | K1's software implementation of binary32 reciprocal core based on Newton-Raphson |

|      | method                                                                           |

| 4.2  | Gappa proof for the error of our implementation of Newton-Raphson method for     |

|      | the binary32 reciprocal                                                          |

| 4.3  | PythonSollya script used to determine $p^*$ and $\epsilon_{approx}$              |

| 4.4  | Gappa script for the error evaluation of exponential argument reduction 88       |

| 5.1  | Some examples of PythonSollya calls into the Python interpreter                  |

| 5.2  | Example of function implementation using Metalibm's description language 97      |

| 5.3  | Generation of a bi-partite approximation to log(2) with PythonSollya, for use in |

|      | exponential argument reduction                                                   |

| 5.4  | Example of Table creation, initialization and use                                |

| 5.5  | Example of Gappa script generated by metalibm for the computation of the evalu-  |

|      | ation error of a polynomial in fixed-point                                       |

| 5.6  | Using backend pass to instantiated undetermined precision                        |

| 5.7  | Example of architecture description, deriving from <b>GenericProcessor</b>       |

| 9.1  | Example of array configuration file used for an AES kernel                       |

| 9.2  | Example of basic cell configuration file                                         |

| 9.3  | Example of VHDL-like source file for RKC                                         |

| 9.4  | Example of C-like source file for RKC                                            |

| 9.5  | Example of program containing a multiplication by a constant                     |

| 10.1 | SHA1 code kernel                                                                 |

# CHAPTER 1 Introduction

Embedded computing used to be the computing that does not show itself, hidden inside systems (appliances, automotive, aerospace) where computation was only one component among many others. The main asset of embedded architecture was to be easily forgotten while providing sufficient computation capabilities. They have extended far beyond this initial outlet and reached markets where they are much more visible, conquering a wider audience. For example, every handheld device (mobile phones, smartphones, MP3 players) relies on a embedded processor for its computation needs. A more accurate and up-to-date definition of embedded computing could be computing with constraints: low power, low cost, integrated into a more complex system and sometime invisible. This evolution is still on-going, but already embedded systems success goes far beyond the embedded market: embedded architectures are almost everywhere, from the nocontact radio-frequency tags to low-power servers and laptops. This success came along growing application requests: embedded architectures are expected to provide increasing computation capabilities. Arithmetic, the science of calculus, is at the center of this challenge. Efficient and versatile arithmetic support is both a reason of this success and a requirement for future designs.

#### 1.1 Embedded architectures

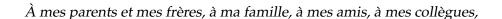

Embedded systems start with micro-controller: low power/ low capabilities processors embedded into systems where energy consumption is at least as important as peak performance. This market, very low power, represents the low left corner of the power / performance taxonomy presented in Figure 1.1. A good representative of that market is the TI MSP430, a very low power 16-bit micro-controller. It is very successful in application markets such as RFID tags and sensors which benefit from its capability to perform low intensity computations on very limited power resources. Such energy efficiency contributed to the development of more complex embedded systems such as handheld devices (eg: mobile phones, mp3 players, portable gaming consoles and more recently smartphones and tablets). Those products have known a large success in the general public and have become the main outlet for embedded processors. Those systems rely on stronger energy supplies but also require higher computation capabilities. They created a demand for more powerful embedded architectures. The middle and high-end embedded systems have evolved to supply this demand: they have become more capable and more versatile. Energy efficiency is still key, but peak performance comes close second. ARM architectures have conquered this market. Designed by Acorn (which became the fabless ARM Holdings), this RISC instruction-set architecture has known many extensions (VFP, Thumb, NEON, ...) since its initial design in 1985. It is implemented in low-power processors built by numerous partners (Apple,

Figure 1.1: Taxonomy of current architectures and markets according to power consumption and performance

Samsung, Qualcomm, Nvidia, ...) and is nowadays part of almost every smartphone and tablet. Other successful architectures include embedded versions of IBM's Power architecture such as Freescale PowerPC e6500 or custom VLIW architectures such as Texas Instrument TMS 320.

As low-power processors gained in performance, the other end of the computer market (desktop computers, data-centers and High Performance Computing servers [HPC] ), located on the top right-hand corner of Figure 1.1, moved towards lower power consumption. For long, these markets relied on very powerful systems, providing much more peak performance that any embedded architecture could provide. Recent examples of such systems include Intel's Pentium, Core and Xeon processors, IBM POWER, HP PA-Risc then Itanium, SPARC (Sun then Fujitsu). But those systems were not very power efficient: silicon area and power were used to reduce latency. Finally this market hit the power wall. Power concern became critical and high-end architecture started to evolve towards more energy efficiency. In the meantime, performance of embedded architectures kept increasing, without impacting their energy efficiency, making them already interesting for these markets. In the last years, architectures originating from embedded system designs have started to conquer the low-end part of the server/data-center and laptop markets. The new ARM-v8A 64-bit architecture is an example of embedded architecture evolution which interests the low-end server market. Embedded architecture are also considered serious candidates for the HPC challenge of the decade: exaflops capabilities under 20MW [141]. Nowadays, embedded systems are everywhere, from RFID tags to cars. Embedded architectures are spreading well passed their native market.

Because of this, embedded architectures have been expected to support a growing set of applications. This set, first limited to low-power computation-light tasks, has been extended to intensive tasks such as cryptography, digital signal processing, graphics processing, advanced operating systems. Many of those applications are computation intensive: they require a large number of operations per time unit (and per energy unit). The G(Fl)ops. $s^{-1}$ . $W^{-1}$  expected from an embedded architecture has been increasing continuously as the market requires more multitasking, smoother interfaces, nicer graphics and overall more capabilities inside a still limited power budget. Those operations are also very diverse. Cryptography algorithms, such as encryption/decryption or hashing, rely on intensive arithmetic (integer, finite fields, modulo arithmetic,

bit-wise logic). Digital Signal Processing (DSP) and graphic processing are intensive in fixed-point and floating-point computations (linear algebra, mathematical functions). To meet these application needs, embedded architectures have to provide efficient and versatile arithmetic. It is one of the keys to market success.

#### 1.2 Exploiting arithmetic parallelism

When the targeted applications hold enough parallelism there is a straightforward way to improve arithmetic efficiency: increase the number of arithmetic units per embedded chip. Adding more units is facilitated by exploiting Moore's law [109]: the number of transistor on a chip doubles approximately every two years. With each new generation of fabrication process it becomes clearer that this law is coming to an end, but it stayed unchallenged until now. What is certain is that the power dissipation is caped and leakage is increasing as transistors become smaller. In any case, newly available transistors can be used to implement more arithmetic units. We can distinguish three ways to do so: SIMD architectures, superscalar architectures and multicores. Both SIMD and superscalar architectures consist in increasing the number of units per computing core. Superscalar architecture adds more independent units to the core. Independents units are more flexible, they do not necessitate compiler support (eg: hardware-managed parallelism in superscalar out-of-order architectures). SIMD architectures add vector units to the core. These architectures trade some of the superscalar flexibility for better energy efficiency, since part of the control is shared across a vector.

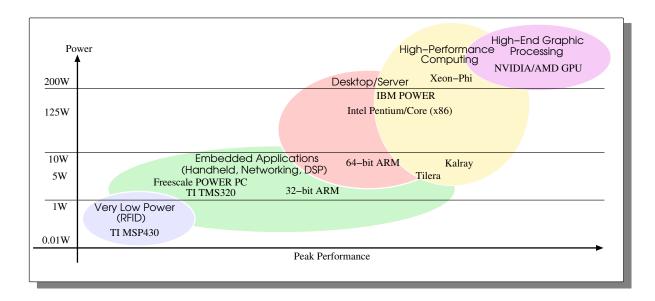

The third way is to increase the number of cores in a circuit, automatically increasing the number of arithmetic units. This trend was illustrated by the apparition of multi-core CPUs in general public products (eg: Intel's Pentium D, IBM's Power 4, AMD's Opteron). Those general purpose processors (GPP) are built with high-complexity cores: CISC architecture, overabundant instruction set, superscalar out-of-order, high frequency. As the power consumption is directly related to a core complexity and frequency, those multi-cores were never interesting for the embedded market. There, this multicore trend echoed slightly differently. To improve a system efficiency, increasing the number of cores while keeping them simple appears more efficient than using fewer, faster, and more complex cores. Following this idea, embedded systems were the first to welcome manycore processors. Manycore processors pack several tens of rather simple cores on a single silicon die. Some foresee that we should reach several thousands of independent core in a single die before the end of the decade. Current GPUs already reached that number with processing elements paired through the Single Instruction Multiple Threads architecture (eg: NVIDIA's Maxwell architecture). As illustrated by Figure 1.2, manycores represent a better balance between power efficiency, flexibility and peak performance than GPUs. They outperform single and multicore CPUs in both power efficiency and peak performance. This makes manycores more interesting to meet the versatility requirements of the embedded market.

Several manycore architectures have already been released. Tilera, a company founded in 2004, was among the first to offer a manycore: the TILE architecture. This architecture offered up to 64 cores embedded in a mesh network. Each core integrates two integer ALUs, a Load/Store unit, two levels of cache plus a router to access the network on chip (NoC) but no floating-point support. In 2009, the new Tile-GX architecture made up for this absence. Each TILE-Gx core integrates a 32/64-bit floating-point unit. The architecture has been implemented in several chip models, containing between 9 and 72 cores.

Adapteva, a small start-up founded in 2008, is also about to launch its Parallela board using its own Epipahny chip [5]: a scalable manycore implementing a RISC proprietary Instruction Set Architecture (ISA).

Small companies are not the only one to consider manycore architectures. Intel, better known

for its desktop/laptop and server processors (Pentium, Core, Xeon), also designed its own many-core: the Xeon-Phi coprocessor [74]. It implements Intel's Knight architecture (declined as Knight Landing, Knight Corner ...) with 61 improved x86 cores (modified version of the original Pentium core). Each of them contains a 512-bit wide vector unit able to process up to 16 binary32 operations in parallel. As a result, considering each vector lane as a processing element, the Xeon-Phi can also be seen as containing 976 processing elements (PEs). In June 2013, Intel took back the head of the Top 500 (500 more efficient supercomputers) with the Tianhe-2 supercomputer built around Ivy-Bridge processors and Xeon-Phi coprocessors. A new iteration of the product, called Knight Landing, was announced, also in June 2013, for a future release. It will use a 14nm process and will contain 72 cores derived from the Atom architecture.

Kalray, a French start-up, develops its own architecture: the Multi-Purpose Processor Array (MPPA) [40], a clustered manycore designed, among other markets, for embedded computing. Kalray's MPPA will be described in more details in Section 1.5. This thesis describes work which was made during and towards the development of MPPA's processing element: the K1 core.

SIMD, superscalar and manycore architectures can be mixed and matched to better suit silicon/power budget and application requirements. Intel's Xeon-Phi is a good example: a manycore with vector units in each core.

The other side of the arithmetic challenge is versatility. Managing versatility while providing efficiency can be difficult: different application domains often require distinct arithmetic supports.

Embedded systems often provide adaptable support: a core architecture can be augmented with instruction-set extensions to improve specific arithmetic support. For example, ARM extended its ISA with floating-point extensions: VFP and NEON. Those extensions provide floatingpoint capabilities (plus vector capabilities for NEON) to the ARM architecture. They are mandatory in the most recent architecture iteration (ARMv8-A) which illustrates the need for efficient floating-point support. ARM also introduced a cryptography ISA extension to better support AES and SHA algorithms. Texas Instrument offers floating-point oriented version of its TMS320: the C67x series. This architecture implements several floating-point units in each core and transforms the TMS320 from an integer DSP into a very capable floating-point DSP. Nowadays, embedded systems, especially the high-end, have to support simultaneously a very wide range of application domains with as many diverse arithmetic requirements. It is not a good fit for limited hardware customization, which is more suited when the set of application to support is limited. Indeed, supporting every complicated operation with a dedicated hardware unit is too costly both in area and development time. Other ways are used to provide a versatile support: for example highlytuned software libraries. Those libraries try to exploit to its maximum the available hardware and extend the architecture capabilities: providing mathematical functions, multi-precision arithmetic, cryptography. But software can only bring limited performance, it is always limited in some way by the underlying hardware. Reconfigurable circuits, such as field-programmable gate arrays (FPGAs), present a possible way to circumvent that difficulty and mix hardware efficiency and software flexibility. For now, they did not break through in the general market, but are already being successful in some niche markets.

Finding the most efficient balance between, hardware, software and reconfigurable computing remains a challenge.

#### 1.3 Versatility versus efficiency in arithmetic

The challenge we chose to address in this work is to provide very efficient arithmetic implementations, using hardware, software and reconfigurable circuit. Our goal is to allow embedded systems in general and the MPPA in particular to offer sufficient computing capabilities to address every single need they may encounter.

1.4 Outline of this thesis

Figure 1.2: Comparison of architectures according to their number of cores

In our context, efficient means: with the required level of performance (operations per second) using the smallest possible amount of resources. In an embedded system, the two most restricted resources are die size (silicon area) and power. However, other considerations have to be taken into account. The first one is time predictability: embedded systems often have to do real-time processing. This implies that operation processing time should be limited and statically determined to assert operational deadlines. We will study this aspect mostly in relation with floating-point computations. The IEEE standard (IEEE-754 rev 2008) that defines floating-point formats and computations introduces many complex cases to be managed. Managing those cases in an acceptable delay appears to be of the highest importance for the system to be certified for correct real-time processing.

This is linked to the second consideration: numerical predictability. Most often, understanding finely the accuracy requirements of an application can lead to more efficient implementations. This is nicely summed-up by the motto "computing just right", which we try to follow when developing floating-point software.

We tackle the challenge of efficient embedded arithmetic through the optic of the hardware/software co-design: determining which arithmetic elements require a hardware support and to which extent, and at the same time which part can be implemented in software with good enough performance.

#### 1.4 Outline of this thesis

The first part of this thesis studies the implementation of floating-point computing in embedded systems. For the most common floating-point operations, a full hardware implementation is often required. Basic floating-point operations are used so extensively in a wide range of applications that they justify the integration of a dedicated unit in an embedded system CPU (including the development cost). This constitutes the focus of the first chapter of this work: design and implementation of an efficient Floating-Point Unit (FPU) for embedded systems.

Less common floating-point operations cannot justify extensive hardware development in embedded systems. Thus we study the manual development of highly optimized software kernels to support two floating-point primitives: division and square root. We extend this development flow to an even less common primitive: floating-point exponential, chosen as an example of mathematical functions.

Such manual development appears too troublesome when considering the various flavours of the numerous mathematical functions which should be provided to fit various needs (architecture, latency, throughput, accuracy). To address this problem, we suggest a domain-specific framework for implementation automation and code generation of mathematical kernels. The project, called *Metalibm*, provides a specific generator for elementary functions, which processes a common implementation description and generates source code and proof code from an unified intermediate representation. Metalibm tries to use as efficiently as possible the generic floating-point operations provided by the FPU integrated into the processor. This project tries to address the two extra considerations listed previously: time and numerical predictability. On the one hand, we offer the generation of correctly rounded functions which represent the ultimate goal for floating-point predictability at a given precision. On the other hand, we also provide several parametric implementations to decrease the computation accuracy while staying in known bounds and thus we are able to save precious computation time.

The next part of this thesis starts from the following analysis: the hardware/software codesign, that proved successful for floating-point, can not be applied to every single operation that needs to be supported by embedded systems. Some operations (e.g. cryptography primitives) require a performance level close to what hardware can bring without being able to justify specific hardware, except for very dedicated systems. As software implementations lack efficiency, another solution must be studied. We suggest the design of a new reconfigurable fabric to be integrated as a CPU functional unit. The hardware reconfigurability brings close to hardware performance for operations only required intensively by a few applications. We focus our design on latency and area efficiency, studying original architectural possibilities. This project is supported by an architectural exploration framework that includes a parametric RTL description, a configurable compiler and the corresponding simulator.

Finally we extend our horizon and tackle a more architectural problem: improving the use of arithmetic processing elements in GPU-like Single Instruction Multiple Thread (SIMT) architecture. This part focuses on the following challenge: making sure that the system arithmetic resources are used as much as possible. This can prove especially complicated on a system managing hundred of threads at the same time. We suggest new mechanisms to improve GPU efficiency on heterogeneous and branching workloads.

Let us know present Kalray's MPPA architecture, which was used as integration target for most of our contributions.

#### 1.5 Kalray's MPPA

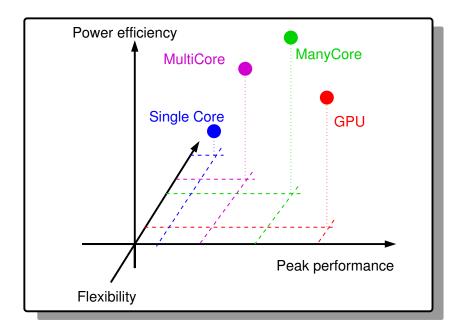

The Multi Purpose Processor Array (MPPA) is a manycore architecture developed by Kalray [2]. The first available product derived from this architecture is the MPPA-256. The MPPA-256 was commercially available by the end of this thesis. At the beginning of this work most of the architecture features were already fixed but no floating-point support was implemented. The floating-point stack (FPU and software primitives) developed during this thesis was integrated into the MPPA-256 and is currently used in production with the product. The reconfigurable fabric was also studied for possible integration in the MPPA architecture but was not selected.

Let us now describe the MPPA-256 architecture, illustrated by Figure 1.3. It contains 256 processing elements (K1 cores) which are organized in 16 clusters of 16 cores. The clusters are con-

1.5 Kalray's MPPA 25

Figure 1.3: MPPA architecture [82]

nected by a Network on Chip (NoC) which also connects them to I/O clusters. I/O clusters are in charge of interfacing the clusters with the exterior through high speed I/Os (Ethernet, PCI-Express, Interlaken) and running an operating system (Linux).

#### 1.5.1 Architecture of the MPPA cluster

The cluster architecture is illustrated by Figure 1.4. Each cluster contains 16 K1 cores plus an extra K1 core called the Resource Manager (RM) which is used to manage the control part of an application. Each cluster has several Mbytes of local shared memory, accessible by the 17 cores and by a Direct Memory Access (DMA) micro-core. The DMA manages accesses to the NoC from and to the cluster; it can also execute local memory moves.

#### 1.5.2 Architecture of the K1 core

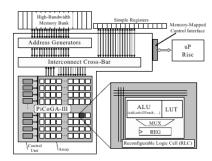

Each core has an instruction and a data cache to alleviate memory access latency. It implements a 5-issue VLIW architecture built around:

- a double arithmetic and logic unit (ALU), which manages up to two 32-bit ALU operations, or a single 64-bit ALU operation each cycle;

- a multiply-accumulate unit, which manages the integer MAC operation (which includes simpler multiplication) or a floating-point operation;

- a load-and-store unit, which manages exchanges with the memory system;

- a branch and control unit, which manages branches and control operations (modifying/accessing status registers ...).

Figure 1.4: MPPA's cluster architecture

Figure 1.5 illustrates the structure of a Kalray K1 core pipeline. PFB stands for prefetch buffer, it is the connection between the instruction cache and the core instruction pipeline. ID is the instruction decode stage. RR is the register read stage. The K1 instruction set architecture (ISA) has been designed for embedded systems efficiency. It contains 397 instructions including some advanced bitwise operations, fixed-point and floating-point arithmetic and extended integer arithmetic.

This architecture is predictable: under certain conditions timings of instruction execution and memory accesses are deterministic. This feature allows some strong real-time constraints to be enforced on the MPPA. It is provided by determinism enforced at every level of memory and operation hierarchy. Implication for the floating-point unit will be detailed on chapter 3.

This feature is also enforced by the fact that the K1 core executes in-order: the order of instructions in the program is not modified by the execution. Thus it is easy to pre-compute an execution latency, and an Instruction Set Simulator (ISS) can be used very accurately, as soon as the program does not make heavy use of the higher levels of the memory hierarchy whose timing behavior, while being easily bounded, remains difficult to predict accurately.

In order to save power, the MPPA-256 is built using a low-power standard library of cells. This implies that it runs at a low frequency (400 to 600 Mhz). This allows us to relax some synthesis constraints and to build a shorter floating-point pipeline than usual. In nominal conditions the whole chip consumes around 5W of power.

Nonetheless, it offers interesting peak performance: the 5-issue VLIW is able to deliver peak performance of around 2 Giga integer operations per second (Gops) at 400 Mhz. With the contributions of Chapter 3, it is also able to sustain 1.2 Giga floating-point operations per second (GFlops). However the K1 core is simple enough to make an interesting brick to build a manycore.

1.5 Kalray's MPPA 27

Figure 1.5: Kalray's K1 core architecture

# Part I Contributions to Floating-Point Arithmetic

#### Context and state of the art

#### 2.1 The IEEE-754 floating-point standard

Integer are not well-suited for computation with a wide dynamic range. Floating-point numbers were designed to improve computer accuracy in such calculus. A floating-point number f is defined with respect to a base b, and encoded using a mantissa m and an exponent e such as:  $f = m \times b^e$ . Zuse's Z3 computer was the first commercial system to provide, in 1942, floating-point capabilities [154]. It started a trend among manufacturers, and until the mid 1980s many companies integrated their own proprietary floating-point formats into their architectures. Those formats were generally not compatible between manufacturers and sometimes within the products of a same manufacturer (eg: IBM). Size, encoding and behaviour were machine-dependant which made the development of portable floating-point programs and architecture comparison very difficult. In 1985, under the impulse of Intel proposal, following the development of its i8087 numerical co-processor, a IEEE standard was accepted: [10]. It normalized the formats (e.g. single, double precision) and the behaviours (required operations, rounding modes). This standard was recently revised (2008, [73]) to take into account the latest evolutions (e.g. decimal floating-point [11], binary16 format, Fused Multiply and Add).

Let us now review three points of the standard which are relevant to this work: the binary floating-point formats and roundings and exceptions.

#### 2.1.1 Floating-point formats

Table 2.1 lists the most common formats defined by the IEEE standard. Each format is built on the same basis: a number is expressed as  $s.m \times 2^{e-p-bias}$  with s the sign, m the mantissa and e the exponent encoded in the bit string. p is the format precision (length of the mantissa) and bias is an exponent offset defined for each format.

| format          | bit width | mantissa size $(p-1)$ | exponent size | bias  | common name |

|-----------------|-----------|-----------------------|---------------|-------|-------------|

| binary16 (fp16) | 16        | 10                    | 5             | 15    | half float  |

| binary32 (fp32) | 32        | 23                    | 8             | 127   | float       |

| binary64 (fp64) | 64        | 52                    | 11            | 1023  | double      |

| binary80 (fp80) | 80        | 64                    | 15            | 16383 | extended    |

Table 2.1: IEEE floating-point format

Mantissas are encoded in sign-magnitude format. According to value of e, three cases are distinguished:

- *e* **is the max value**: the number is a specific value, non numerical value, among Not a Number (NaN) or signed infinities.

- *e* **non zero**: the number is said to be normal, mantissa leading bit is a one. The leading one is not encoded into the mantissa bitfield which saves 1 bit. It is called the **implicit one**.

- e is zero: the number is said to be subnormal or denormalized (deprecated name used in [10]). The leading bit is an implicit zero and the mantissa leading one can be located anywhere in the remaining p-1 bits of mantissa.

Because of the space occupied by sign and exponent fields, the encoded mantissa width is less than the word length: 23 vs 32 bits in binary32 and 52 vs 64 bits in binary64. We add the implicit bit to the encoded with, to get the format precision p: 24 for binary32 and 53 for binary64. Specific values (encoded by an exponent equals to the max value) are distinguished through mantissa values (0 for infinities, non-zero for NaN).

#### 2.1.2 Rounding modes and exception

For binary floating-point arithmetic, the IEEE standard [10] requires the exact implementation of several floating-point operations including addition/subtraction, multiplication, square root, division, conversion from and to integers. The 2008 revision [73] added the fused-multiply and add operation (FMA) to that list. Here, **exact** means that the operation result should, first, be computed as if in infinite precision and unbounded exponent range, and eventually rounded toward the output format according to the current rounding mode. In binary floating-point arithmetic, this rounding mode has to be chosen among the four modes defined by the standard:

- roundTiesToEven: the exact result is rounded to the nearest floating-point value, ties are rounded to the nearest floating-point number with an even mantissa.

- roundTowardPositive:: the result is rounded to the nearest greater or equal floating-point value.

- roundTowardNegative: the result is rounded to the nearest less or equal floating-point value.

- roundTowardZero: positive results are rounded as if rounding towards minus infinity was in place, negative results are rounded as if rounding towards plus infinity was in place.

To detect and manage specific computation events, the standard defines 5 exceptions:

- division by zero

- inexact result

- invalid operation

- underflow

- overflow

A precise definition for these exceptions can be found on section 7 of [73]. A compliant implementation of the standard, should have them raised by every operations when the conditions are met.

#### 2.2 Unit in the last place

The unit in the last place or **ulp** is an important concept used to measure floating-point errors. However this concept has many definitions that were summarized and studied in [114]. We are not going to go into details about the specificities of each ulp definition and for the simple examples illustrating this work the following [114]'s definition should suffice:

**Definition 2.2.1** If x is a real number that lies between two finite consecutive floating-point numbers a and b, without being equal to one of them, then ulp(x) = |b - a|, otherwise ulp(x) is the distance between the two finite floating-point numbers nearest x. Moreover, ulp(NaN) is NaN.

In a coarse approximation, for a floating-point number X, ulp(X) can be considered as the weight of the least significant bit of X's mantissa.

#### 2.3 State of the art of floating-point support in embedded processors

Floating-point constitutes the core of numerous embedded applications. It is key in digital signal processing, graphics processing. Thus many embedded architectures, especially if they target floating-point intensive applications, provide hardware support. Let us review in more details the floating-point support provided by some architectures representatives of the embedded taxonomy.

#### 2.3.1 ARM architecture

VFP ARM architecture offers a floating-point coprocessor extension since the ARMv5 architecture. This extension called Vector Floating Point (VFP) [12] provides support for single and double precision formats. It is implemented as a coprocessor and features a separate floating-point register file containing between 16 and 32 64-bit floating-point registers. Later versions were extended with support for a fused-multiply accumulate. The extension is compliant with IEEE 754 [73], and also provides a *Run-Fast* mode which degrades compliance and improves performance. Contrary to what its appellation could suggest, this extension does not provides SIMD acceleration, as vectors are executed sequentially. This feature (vector sequential execution) was removed in last version of VFP.

**NEON** To provide efficient SIMD acceleration, ARM introduced an other extension called NEON [1]. The NEON extension features a truly SIMD engine containing 128-bit vector registers. It provides both integer and floating-point vector instructions. Floating-point support is limited to single precision, compliant with IEEE 754[73], with up to 4 elements simultaneously processed by each instruction. NEON provides conversions and standard arithmetic (addition, subtraction, multiply and fused multiply-add).

ARM architecture can feature both VFP and NEON, for example the ARM cortex A8 implements a VFPv3 coprocessor and a NEON extension. It is one of the advantages of ARM architecture: it can be customized to adapt to application requirements. In the most recent architectures (e.g. ARMv8-A), both extensions are mandatory.

#### 2.3.2 ST231

The ST231 is an embedded processor from the ST200 family by ST Microelectronics. It is a digital signal processor targeting the embedded media processing market. It implements a Very Long

Instruction Word (VLIW) architecture able to execute two integer multiplies and two integer adds each cycle. It constitutes an interesting example of floating-point support because it does not integrate a hardware floating-point unit. Floating-point capabilities are provided by a highly optimized software library: FLIP [79]. FLIP is a state of the art software library implementing the basic floating-point operations in compliance with the IEEE standard [73]. A more detailed presentation of FLIP is given in Section 3.1, p. 37.

#### 2.3.3 IBM's Power architecture

The Power architecture was first introduced in 1990, in the RISC System/6000 computers. Initially designed for mainframe computers, it has since known several iterations and has been extended to the embedded market.

The Power ISA v2.06, last iteration of IBM's Power architecture, provides both 32-bit and 64-bit binary floating-point support, compliant with the IEEE 754 standard. This support includes most current operations (including Fused Multiply-Add) and exists in vector format with the Altivec ISA extension. Altivec extension works on 128-bit vector registers and supports up to 4 32-bit floating-point operations in parallel. It does not support 64-bit floating-point. IBM's Power is among the very few architectures which provide hardware support for decimal floating-point (32, 64 and 128-bit Decimal Floating-Point (DFP) numbers are supported). It provides common operations (conversions, comparisons) and four basic arithmetic primitives: addition, subtraction, multiplication and division. It does not provides a decimal Fused Multiply-Add. The DFP unit is not part of the embedded implementation of the Power architecture.

The Power architecture is implemented by several manufacturers beyond IBM. Among them we can cite Freescale, that produces the PowerPC e6500, an embedded processor which implements a Power architecture. A e6500 core contains five integer units, two load-store units and a 128-bit Altivec unit providing vectorized floating-point support for binary32 computation.

#### 2.3.4 Texas Instrument TMS320

In 1983, Texas Instruments introduced the first representative of the TMS320 family: the TMS32010. This DSP was rather successful in the embedded market and has since known several variations. It still appears, as a DSP coprocessor connected to ARM cores, in the OMAP System on Chip (SoC), processor from TI used in handheld devices. It implements a VLIW architecture. The floating-point unit is not part of the main ISA and appears as a hardware option. Some specialized DSP, for instance the TMS320C6731B of the C67x series, have been designed to provide a heavy 32-bit floating-point support. This version features four floating-point ALUs (addition) and two floating-point multiply units: it is able to compute up to two floating-point multiply-accumulate each cycle. It does not provides a Fused Multiply-and-Add and thus is not fully compliant with the revised standard [73].

# 2.3.5 Conclusion