## Addressing the Challenges of I/O Variability in Post-Petascale HPC Simulations

Matthieu Dorier

### ► To cite this version:

Matthieu Dorier. Addressing the Challenges of I/O Variability in Post-Petascale HPC Simulations. Distributed, Parallel, and Cluster Computing [cs.DC]. Ecole Normale Supérieure de Rennes, 2014. English. NNT: . tel-01099105

## HAL Id: tel-01099105 https://theses.hal.science/tel-01099105

Submitted on 31 Dec 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE / ENS RENNES**

sous le sceau de l'Université européenne de Bretagne pour obtenir le titre de DOCTEUR DE L'ÉCOLE NORMALE SUPÉRIEURE DE RENNES Mention : Informatique École doctorale MATISSE **Matthieu Dorier**

Préparée à l'unité mixte de recherche 6074 Institut de recherche en informatique et systèmes aléatoires

Addressing the Challenges of I/O Variability in Post-Petascale HPC Simulations

Thèse soutenue le 9 décembre 2014 devant le jury composé de :

**Jean Roman** / rapporteur Professeur, Institut Polytechnique de Bordeaux, France

Toni Cortes / rapporteur Associate Professor, Universitat Politècnica de Catalunya, Spain

Franck Cappello / examinateur Senior Computer Scientist, Argonne National Laboratory, IL, USA

**Jean-François Méhaut** / examinateur Professeur, Université de Grenoble 1, France

**Gabriel Antoniu** / directeur de thèse Directeur de recherche, Inria Rennes - Bretagne Atlantique, France

**Luc Bougé** / directeur de thèse Professeur, ENS Rennes, France

And word by word they handed down the light that shines today. Alan Parsons Project (Ammonia Avenue)

## Acknowledgements

I would like to start by thanking my reviewers: Toni Cortes and Jean Roman, as well as the other members of my jury: Jean-François Mehaut and Franck Cappello, for taking the time to evaluate my PhD thesis. I felt honored to see my work validated by such a committee.

This work was made possible thanks to the constant support and advice from my two PhD advisors: Gabriel Antoniu, who shared his energy and his connections with the top researchers in our field, and pushed me to publish in top conferences while providing me all the help necessary to reach these targets. I want to thank Luc Bougé as well. Before supervising this thesis, he welcomed me at ENS in 2008 as a bachelor student, hosted me for an internship in 2009 in the KerData team, and later relied on me as a teaching assistant.

I owe the work presented here to the great collaboration that is the JLPC/JLESC, and to its leaders Franck Cappello and Marc Snir. My internship under their joint supervision in 2010 decided of my future carrier. I can truly say that none of the contributions presented hereafter would have been possible without them getting me access to top supercomputers and introducing me to their professional network. I'm also very grateful to Rob Ross, with whom I worked on many occasions since 2012. He hosted me twice at ANL, where I found an excellent place to continue my work.

Many thanks go to all the other contributors: Leigh Orf for helping me understand a real climate code and getting me to evaluate Damaris on a top supercomputer (Kraken), Tom Peterka and Rob Sisneros for our collaboration around in situ visualization, Dries Kimpe for our work on CALCioM, Shadi Ibrahim and Orçun Yildiz for the most recent work on Omnisc'IO and the energy consumption in Damaris.

I would like to thank the present and former members of the KerData team (those I haven't mentioned already): Houssem, Radu, Viet-Trung, Alexandru, Tien Dat, Pierre, Lokman, Alvaro, Luis, Diana, Alexandra, and all the interns, engineers and visitors who made this team such a convivial and lively group.

I was very lucky to have the support and encouragements of my family all these years: my parents, my grand-parents, my uncle and my brothers. Most of them travelled across the country to attend my defense, this meant a lot to me.

A special thank to Aurore, for our musical breaks at INRIA in 2013.

Finally my thoughts go to all the friends I have made while working in this field, and that I'm always very happy to meet during conferences or internships: Amina, Ana, Tatiana, Leo, Thomas, Francieli, Laércio, Kassick.

I still feel like many other would deserve an acknowledgment, from those who helped me understand the code of some software, or solved technical problems, to the team assistants who helped with all the paperwork and the missions... to all these people, thank you for your support!

## Résumé en Français

**E** N 2008, la communauté du calcul hautes performances (HPC) atteignait le *Petascale* avec Roadrunner d'IBM, un supercalculateur de 122400 cœurs ayant une performance de 1.375 Petaflops  $(1.375 \times 10^{15} floating point operations per second)$ . La barre du million de cœurs a été atteinte en 2012 avec le supercalculateur Sequoia à LLNL et, en suivant la loi de Moore – laquelle indique que le nombre de transistors dans les systèmes de calculs de pointe double tous les 18 mois –, des supercalculateurs dits *Exascale* (atteignant  $10^{18}$  flops) sont attendus pour 2018. Une telle puissance de calcul est mise à profit dans de nombreux domaines de recherche tels que les sciences de la Terre, la biologie, le climat ou l'astrophysique, domaines dans lesquels les simulations à large échelle sont employées pour mieux comprendre les phénomènes physiques qui nous entourent. Ces simulations ont vocation de remplacer des expériences réelles qui peuvent être trop coûteuses, trop dangereuses ou simplement irréalisables, comme les études portant sur la jeunesse de l'univers. *"We have this problem in astrophysics that we can't go and do experiments in the lab to test our theories"*,<sup>1</sup> explique Mark Vogelsberger, du MIT, dans une interview pour The Guardian<sup>2</sup> au sujet des résultats d'une récente simulation de l'univers.

Les entreprises de production utilisent également les supercalculateurs pour diminuer leurs coûts de conception. Par exemple, l'utilisation de souffleries virtuelles (c'est-à-dire simulées par ordinateur) a permis à Boeing de réduire à 11 le nombre de prototypes d'ailes d'avions construits pour leur modèle 787 "Dreamliner" en 2005, en comparaison des 77 prototypes utilisés pour la conception du modèle 767 dans les années 80.<sup>3</sup> Les simulations hautes performances ont en effet l'avantage d'être plus rapides et moins chères que la conception et les tests de prototypes réels. De plus, ces simulations peuvent être reproduites et les modèles virtuels peuvent être évalués dans des conditions variées avec une très grande précision.

Mais comme Ken Batcher le dit, *"a supercomputer is a device for turning compute-bound problems into I/O-bound problems"*.<sup>4</sup> En effet, de plus grosses machines mènent à une production accrue de données. Ces données doivent être stockées et traitées efficacement en vue d'en tirer un résultat scientifique. L'approche traditionnelle de gestion de données consiste à sto-

<sup>&</sup>lt;sup>1</sup>Traduction : "En astrophysique, nous avons ce problème de ne pas pouvoir effectuer d'expériences en laboratoire pour tester nos théories."

<sup>&</sup>lt;sup>2</sup>www.theguardian.com/science/2014/may/07/universe-recreated-computer-simulation-model-big-bang

<sup>&</sup>lt;sup>3</sup>www.scientificamerican.com/article/big-computers-for-little/

<sup>&</sup>lt;sup>4</sup>Traduction : "un supercalculateur est un appareil transformant un problème limité par les performances de calculs en un problème limité par les performances des entrées/sorties".

cker les données produites par la simulation dans des fichiers pendant que celle-ci s'exécute, et à analyser ces fichiers plus tard, lorsque la simulation est terminée. On observe cependant un fossé de plus en plus profond entre les performances des systèmes de stockage et les performances des systèmes de calculs dans les supercalculateurs récents. Par exemple, alors que le supercalculateur Jaguar à ORNL (premier du Top 500 en novembre 2009 et Juin 2010) fournit un débit de 240 Go/s vers son système de stockage, pour une performance de pointe de 1,75 Petaflops, son successeur Titan (premier au Top 500 en novembre 2012) fournit un débit de stockage seulement six fois supérieur (1,4 To/s) pour une puissance de calculs dix fois supérieure (17,59 Petaflops). Ce fossé rend obsolètes les approches traditionnelles pour les entrées-sorties (E/S), qui prennent en effet une part grandissante du temps d'exécution des applications et sont sujettes à une *variabilité* croissante de leurs performances.

D'une part, il devient donc nécessaire d'optimiser la pile d'E/S à tous les niveaux, de la simulation jusqu'au système de fichiers, dans le but d'en améliorer les performances ainsi que la predictibilité de ces performances. Cela implique également d'améliorer la manière de gérer une concurrence croissante au niveau du système de fichiers, non seulement entre des centaines de milliers de processus constituant une seule application, mais également entre un nombre croissant d'applications qui s'exécutent sur la même machine et en partagent le système de stockage.

D'autre part, il devient inévitable de rapprocher les tâches d'analyse et de visualisation de la simulation elle-même afin d'éviter de stocker de larges quantités de données. Cette tendance soulève de nouveaux défis liés aux moyens dont disposent les simulations pour communiquer efficacement leurs données et partager ces dernières avec les outils d'analyse sans dégrader leurs performances.

Enfin, la consommation énergétique des futurs supercalculateurs est un problème de plus en plus important dans la communauté HPC. Alors que les machines actuelles consomment une puissance d'environs 10 MW, la Defense Advanced Research Projects Agency (DARPA) a imposé une limite de 20 MW pour les futures machines Exascale. Cela représente une multiplication par deux de la consommation d'énergie pour des plateformes qui devront être mille fois plus performantes en termes de calculs. Cette contrainte ne pourra être satisfaite seulement par des améliorations matérielles, mais nécessitera par la conception d'approches logicielles plus économes en énergie. Les mouvements et le stockage de grandes masses de données constituent notamment des tâches coûteuses en énergie et doivent être optimisées en conséquence.

#### Contributions

De nombreux problèmes de performance dans le contexte des simulations HPC proviennent en réalité d'un problème de *variabilité*. Des différences dans le temps de complétion des tâches d'E/S d'un processus à un autre au sein d'une application massivement parallèle forcent tous les processus à attendre le plus lent d'entre eux. Ces processus gâchent ainsi un temps précieux et de l'énergie. Dans les approches actuelles de gestion des données, cette variabilité a de multiples causes. Premièrement, dans la majorité des applications les tâches d'E/S sont exécutées de manière périodique par tous les processus en même temps, ce qui produit des pics d'activité au sein du système de fichiers. Ce comportement engendre des conflits d'utilisation des ressources et une variabilité des performances des E/S de chaque processus, produisant un impact négatif sur les performances générales de l'application. Deuxièmement, coupler les simulations avec des outils de visualisation et d'analyse accroît cette variabilité, notamment lorsque les tâches de visualisation sont exécutées de manière interactive. Enfin une troisième source de variabilité provient des accès concurrents au système de stockage par plusieurs applications indépendantes s'exécutant sur la même machine.

Dans cette thèse, nous nous proposons de relever les défis posés par la variabilité des performances des approches actuelles de gestion de données. Notre travail a été principalement conduit dans le contexte du JLPC (Joint Laboratory for Petascale Computing), un laboratoire commun à l'Inria, le National Center for Supercomputing Applications (NCSA) à l'Université d'Illinois à Urbana-Champaign (UIUC) et Argonne National Laboratory (ANL). Ce travail a mené à différents projets communs entre l'équipe KerData, ANL et UIUC : FACCTS (France and Chicago Collaborating in the Sciences), PUF (Partner University Fund), l'équipe associée Data@Exascale. Les contributions de cette thèse peuvent être résumées comme suit.

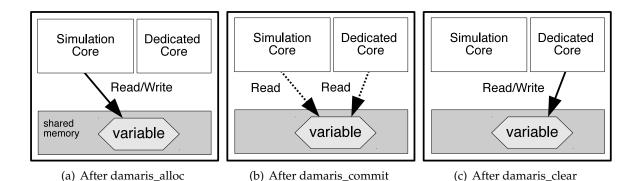

#### Utilisation de cœurs dédiés pour cacher la variabilité des E/S

Alors que le nombre de cœurs dans les nœuds multicœurs augmente, des conflits apparaissent lorsque plusieurs processus d'un même nœud tentent d'accéder à la même interface réseau. Ces conflits entraînent une variabilité substantielle des performances des E/S. On appellera *jitter* ce type de variabilité, qui trouve sa source dans les conflits d'accès au sein des processus d'une même application. Dans ce travail, nous proposons une nouvelle méthode de gestion des E/S, appelée Damaris, qui se sert de cœurs dédiés aux E/S sur chaque nœud multicœur, ainsi que de mémoire partagée. Damaris permet réaliser les tâches de traitement de données et d'E/S de manière asynchrone, et de cacher la variabilité de ces dernières en conséquence. Nous évaluons Damaris sur trois plateformes différentes, notamment le supercalculateur Kraken (11<sup>e</sup> du Top500 au moment des expériences) avec la simulation atmosphérique CM1. En permettant le recouvrement des E/S et des calculs, et en regroupant les données dans des fichiers plus volumineux tout en évitant les synchronisations entre cœurs, notre solution apporte un certain nombre d'avantages.

- 1. Elle permet de cacher complètement le jitter ainsi que tous les coûts liés aux E/S, rendant les performances de la simulation prévisibles ;

- 2. Elle multiplie le débit en écriture par un facteur allant jusqu'à 15 en comparaison des approches standard ;

- 3. Elle permet un passage à l'échelle de la simulation (testée jusqu'à 9000 cœurs) à l'inverse des approches standards qui ne passent pas à l'échelle ;

- 4. Elle permet d'atteindre un taux de compression des données de 600 % sans surcoût pour l'application, menant à une réduction majeure de l'espace de stockage nécessaire.

En plus d'initier le développement d'une implémentation de Damaris, ce travail a été récompensé du 2<sup>e</sup> prix à l'ACM Student Research Competition qui s'est tenue en marge de la conférence ICS '11. Ce travail a également mené à une publication à la conférence CLUS-TER '12.

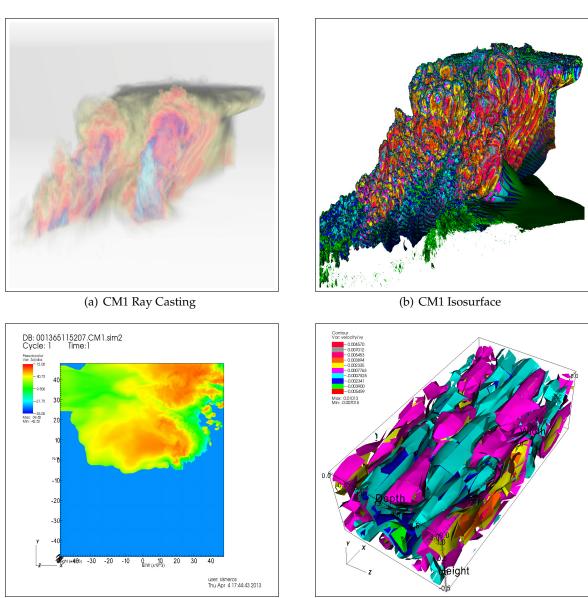

#### Extension de l'usage des cœurs dédiés à la visualisation in situ

Réduire la quantité de données stockées par les simulations va devenir d'une importance critique pour les prochaines générations de supercalculateurs. En conséquence, de nombreuses recherches tentent de promouvoir des approches dans lesquelles les tâches d'analyse et de visualisation sont exécutées in situ, c'est-à-dire à proximité de la simulation et en partageant les ressources de cette dernière. Ces approches possèdent l'avantage d'éviter de stocker de grandes quantités de données pour des post-traitements. Elles peuvent cependant avoir un impact important sur le temps d'exécution de la simulation si elles ne sont pas implémentées correctement. Notre travail se concentre précisément sur le cas d'une visualisation in situ où le code de visualisation est co-localisé avec le code de la simulation et s'exécute sur les mêmes ressources. Il est important pour une telle technique de visualisation in situ de nécessiter le moins de modifications possibles dans les codes existants, d'être adaptable et d'avoir un faible impact à la fois sur le temps d'exécution et sur l'utilisation des ressources. Nous accomplissons cela grâce à Damaris/Viz, une extension de Damaris fournissant un support pour la visualisation in situ. L'utilisation de Damaris comme passerelle vers des codes de visualisation existants permet

- 1. de réduire les modifications de code au maximum dans les simulations existantes,

- 2. de réunir les fonctionnalités de divers outils de visualisation pour offrir une interface unifiée de gestion de données,

- 3. d'utiliser efficacement des cœurs dédiés pour cacher l'impact de la visualisation in situ sur le temps d'exécution de la simulation, et

- 4. d'utiliser efficacement la mémoire au travers d'une couche de communication basée sur de la mémoire partagée.

Damaris/Viz est évalué sur Blue Waters et Grid'5000 pour visualiser les données produites par la simulation atmosphérique CM1 et la simulation de dynamique des fluides Nek5000. Ce travail a mené à une publication à la conférence LDAV '13.

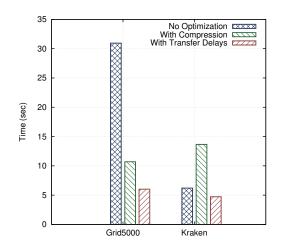

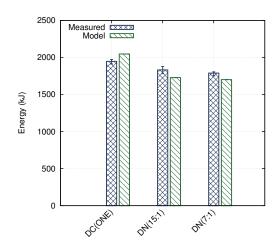

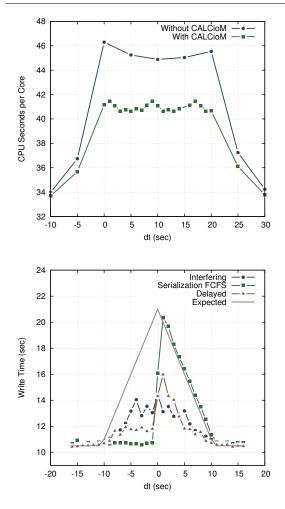

#### Analyse des compromis energie/performance dans diverses approches d'E/S

Un défi majeur pour les futures machines Exascale consiste à atteindre de hautes performances tout en maintenant une faible consommation d'énergie. Beaucoup de travaux récents, et en particulier la première contribution de cette thèse, ont exploré de nouvelles approches pour les E/S visant à réduire le goulot d'étranglement présent au niveau des E/S dans les applications large échelle (permettant ainsi d'améliorer leurs performances). Les travaux évaluant l'impact de ces approches sur la consommation d'énergie restent pourtant rares. Néanmoins, les approches qui permettent un recouvrement des E/S et des calculs ont un effet bénéfique en termes de variabilité des performance et *a fortiori* en termes de consommation d'énergie. Dans ce travail, nous avons complété notre implémentation de Damaris en lui donnant la possibilité d'utiliser des nœuds dédiés à la place de cœurs dédiés, ainsi que la possibilité d'exécuter les tâches de traitement des E/S en mode synchrone, c'est-à-dire sans ressources dédiées. Nous examinons ces différentes approches d'E/S à l'aide d'expériences avec la simulation CM1. Nos résultats, obtenus sur Grid'5000, montrent l'impact sur les performances et sur la consommation d'énergie de ces différentes approches. Ils mettent également en évidence les relations entre la consommation d'énergie et certains paramètres de l'application et du matériel. Nous proposons ensuite un modèle mathématique permettant d'estimer la consommation d'énergie d'une simulation en fonction de l'approche utilisée pour ses E/S. Ce travail a été en partie publié au workshop DIDC '14, tenu en marge de la conférence HPDC '14.

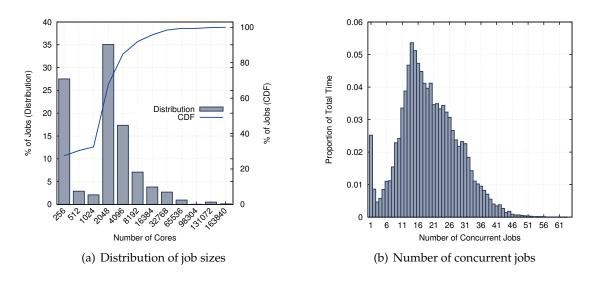

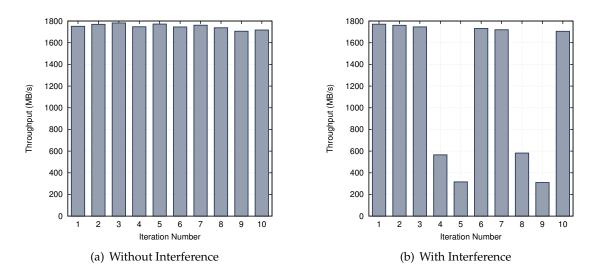

#### Atténuation des conflits d'E/S par coordination inter-application

De plus grosses machines étant inévitablement exploitées par un plus grand nombre d'applications de manière concurrente, les interférences produites par plusieurs applications accédant à un système de fichiers parallèle partagé deviennent un problème majeur. Les interférences perturbent souvent les optimisations des E/S utilisées par les applications individuellement, tels que les accès optimisés au préalable pour améliorer la localité des accès disques. Ceci a pour effet de dégrader les performances des E/S de ces applications, d'accroître leur temps d'exécution et la variabilité de ce temps d'exécution, réduisant d'autant plus l'efficacité globale de la machine. Pour résoudre ce problème, nous proposons CAL-CioM, une approche ayant pour but d'atténuer les interférences d'E/S au travers de la sélection dynamique d'une stratégie d'ordonnancement dépendant d'informations fournies par les applications elles-mêmes. CALCioM permet à plusieurs applications s'exécutant sur un supercalculateur de coordonner leurs stratégies d'E/S en vue d'éviter d'interférer les unes avec les autres. Dans ce travail, nous examinons quatre stratégies qui peuvent être implémentées par CALCioM : sérialiser, interrompre, interférer ou coordonner. Nos expériences sur le supercalculateur BG/P Surveyor d'Argonne ainsi que sur plusieurs sites de Grid'5000 montrent comment CALCioM peut être utilisé pour implémenter des stratégies d'ordonnancement entre des applications qui autrement interfèreraient, avec pour objectif l'optimisation de l'efficacité globale de la machine. Ce travail, partiellement effectué durant un stage de 3 mois à ANL, a mené à une publication à la conférence IPDPS '14.

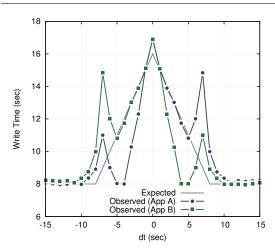

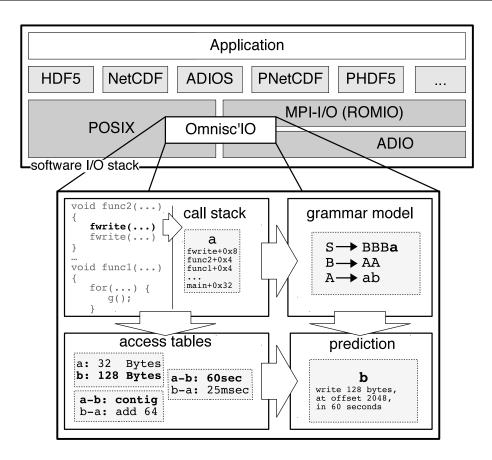

#### Prédiction des motifs spatiaux et temporels d'E/S des applications HPC

De nombreuses optimisations des E/S, tels que le préchargement, la mise en cache ou l'ordonnancement, ont été proposées pour améliorer les performances de la pile d'E/S. Afin d'optimiser ces techniques, modéliser et prédire les caractéristiques spatiales et temporelles des E/S des applications HPC alors qu'elles s'exécutent s'avèrent crucial. Dans cette direction, nous proposons Omnisc'IO, une approche ayant pour but de faire un pas en avant vers une gestion intelligente des E/S des applications HPC sur les futures plateformes. Omnisc'IO construit un modèle basé sur des grammaires formelles des E/S de n'importe quelle application HPC. Il utilise ensuite ce modèle pour prédire quand les futures opérations d'E/S vont se produire ainsi que la quantité et la localisation des données en jeu. Omnisc'IO est intégré de manière transparente dans les couches POSIX et MPI-I/O et ne nécessite aucune modification dans les sources des applications ou des bibliothèques d'E/S de haut niveau. Il ne nécessite pas d'information *a priori* sur les applications, et converge vers un modèle permettant des prédictions précises en seulement quelques itérations. L'implémentation d'Omnisc'IO est efficace à la fois en temps et en mémoire. Omnisc'IO a été évalué avec quatre applications HPC réelles – CM1, Nek5000, GTC, and LAMMPS – utilisant différentes bibliothèques d'E/S allant de POSIX à Parallel HDF5. Nos expériences montrent qu'Omnisc'IO peut atteindre une précision allant de 79.5 à 100% pour la prédiction des paramètres spatiaux des futurs accès, et une précision moyenne de la date de ces futurs accès allant de 0.2 secondes à moins d'une milliseconde. Ce travail a mené à une publication à la conférence SC '14 et a donné lieu au développement de la bibliothèque Omnisc'IO.

## **Publications**

#### **Conférences Internationales**

- Bogdan Nicolae, Diana Moise, Gabriel Antoniu, Luc Bougé, **Matthieu Dorier**. *BlobSeer* : *Bringing High Throughput under Heavy Concurrency to Hadoop Map/Reduce Applications*, Proceeding of the 2010 IEEE International Parallel & Distributed Processing Symposium (IPDPS '10), *Atlanta*, *septembre* 2010. CORE Rank A (taux d'acceptation de 24%).

- Matthieu Dorier, Gabriel Antoniu, Franck Cappello, Marc Snir, Leigh Orf. Damaris : How to Efficiently Leverage Multicore Parallelism to Achieve Scalable, Jitter-free I/O, Proceedings of the 2012 IEEE International Conference on Cluster Computing (CLUSTER '12), Pékin, septembre 2012. CORE Rank A (taux d'acceptation de 28%).

- Matthieu Dorier, Roberto Sisneros, Tom Peterka, Gabriel Antoniu, Dave Semeraro. *Damaris/Viz, a Nonintrusive, Adaptable and User-Friendly In Situ Visualization Framework,* Proceedings of the 2013 IEEE Symposium on Large Data Analysis and Visualization (LDAV '13), *Atlanta, octobre 2013.* (taux d'acceptation de 37%).

- Matthieu Dorier, Gabriel Antoniu, Rob Ross, Dries Kimpe, Shadi Ibrahim. *CALCioM* : *Mitigating I/O Interference in HPC Systems through Cross-Application Coordination*, Proceedings of the 2014 IEEE International Parallel & Distributed Processing Symposium (IPDPS '14), *Phoenix, mai* 2014. CORE Rank A (taux d'acceptation de 21%).

- Matthieu Dorier, Shadi Ibrahim, Gabriel Antoniu, Rob Ross. *Omnisc'IO : A Grammar-Based Approach to Spatial and Temporal I/O Patterns Prediction*, Proceedings of ACM/IEEE 2014 Supercomputing Conference (SC '14), La Nouvelle Orléans, novembre 2014. CORE Rank A (taux d'acceptation de 21%).

#### Workshops dans des Conférences Internationalles

Orçun Yildiz, Matthieu Dorier, Shadi Ibrahim, Gabriel Antoniu. A Performance and Energy Analysis of I/O Management Approaches for Exascale Systems, in Proceedings of the 2014 Data-Intensive Distributed Computing (DIDC '14) workshop, tenu conjointement avec le 23<sup>rd</sup> International ACM Symposium on High Performance Parallel and Distributed Computing (HPDC '14), Vancouver, juin 2014.

#### **Posters at International Conferences**

• Matthieu Dorier. Damaris - Using Dedicated I/O Cores for Scalable Post-petascale HPC Simulations, 2011 ACM/SIGARCH International Conference on Supercomputing (ICS '11), Tucson, avril 2011. 2<sup>eme</sup> prix de l'ACM Student Research Competition.

• Matthieu Dorier. Efficient I/O using Dedicated Cores in Large-Scale HPC Simulations, 2013 IEEE International Parallel & Distributed Processing Symposium (IPDPS '13) : PhD Forum, Boston, mai 2013.

### Logiciels

Damaris est un intergiciel pour les noeuds multicœurs, leur permettant de gérer efficacement les transfères de données pour le stockage ou la visualisation en dédiant un sous-ensemble des cœurs aux opérations d'entrées/sorties (E/S). Il permet des E/S asynchrones efficaces et cache tout surcoût lié aux opérations d'E/S, tels que la compression de données, le post-traitement ou la visualisation in situ (via son extension Damaris/Viz). Damaris a été évalué sur Blue Waters (Cray XE6, NCSA), Kraken (Cray XT5, NICS), Titan (Cray XK7, ORNL), Intrepid (IBM BlueGene/P, ANL), Grid'5000 (grille de calculs française), Blue Print (cluster Power5, NCSA), avec la simulation atmosphérique CM1 et la simulation de dynamique des fluides Nek5000. Damaris a été formellement validé pour une utilisation sur le supercalculateur Blue Waters an NCSA. A notre connaissance, il a été utilisé par plusieurs chercheurs du NCSA, de Central Michigan University et de l'Université Fédérale de de Rio Grande do Sul (UFRGS). Lien : http://damaris.gforge.inria.fr

**Taille and langage(s) :** 19500 lignes, C++, Fortran, XML **License :** LGPL

- Omnisc'IO est un intergiciel intégré dans les couches POSIX et MPI-I/O et permet de capturer les E/S des applications HPC de manière transparente, d'en produire un modèle et d'utiliser ce modèle pour prédire les futurs accès. Omnisc'IO est basé sur des grammaires formelles et utilise une version modifiée de l'algorithme Sequitur. Elle a été utilisé sur Grid'5000 avec la simulation atmosphérique CM1, la simulation de dynamique moléculaire LAMMPS, la simulation de fusion GTC et la simulation de dynamique des fluides Nek5000. Lien : http://omniscio.gforge.inria.fr Taille et langage(s) : 4400 lines, C++ License : LGPL

- Darshan-Ruby/Darshan-Web Darshan-Ruby est une bibliothèque Ruby permettant de lire les fichiers produits par Darhan (outil de trace d'E/S produit par Argonne National Lab), en utilisant un paradygme orienté objets. Darshan-Ruby a été développé dans le but de simplifier l'analyse du comportement d'E/S des applications à grande échelle. Il accède directement au contenu des fichiers Darshan sans nécessiter de conversion en format text. Darshan-Ruby est accessible comme Ruby Gem sur le dépot officiel rubygems.org. Darshan-Ruby a mené au développement du projet Darshan-Web, qui propose une plateforme web pour aider à l'analyse des traces d'E/S. Lien : http://darshan-ruby.gforge.inria.fr

Taille and langage(s) : 400 lines, C, Ruby License : LGPL

## Contents

| 1 | Intr | troduction 1 |                                                                      |    |  |

|---|------|--------------|----------------------------------------------------------------------|----|--|

|   | 1.1  |              | xt                                                                   | 1  |  |

|   | 1.2  |              | ibutions                                                             | 2  |  |

|   | 1.3  | Public       | cations                                                              | 5  |  |

|   | 1.4  | Softwa       | are                                                                  | 6  |  |

|   | 1.5  |              | nization of the Manuscript                                           | 7  |  |

| 2 | Bacl | cgroun       | d: I/O and Data Analysis in Supercomputers                           | 9  |  |

|   | 2.1  | The E        | ra of Supercomputing                                                 | 10 |  |

|   |      | 2.1.1        | Large-Scale Scientific Simulations                                   | 10 |  |

|   |      | 2.1.2        | Post-Petascale Supercomputers                                        | 10 |  |

|   | 2.2  |              | nd Storage in HPC Systems                                            | 11 |  |

|   |      | 2.2.1        | Parallel File Systems                                                | 11 |  |

|   |      | 2.2.2        | The MPI-I/O and POSIX Interfaces                                     | 12 |  |

|   |      | 2.2.3        | High-Level I/O Libraries                                             | 13 |  |

|   |      | 2.2.4        | Application-Level I/O Approaches                                     | 13 |  |

|   | 2.3  | Variał       | pility in Traditional I/O Approaches                                 | 14 |  |

|   |      | 2.3.1        | Causes and Effects of the I/O Variability                            | 15 |  |

|   |      | 2.3.2        | Approaches to Mitigate the I/O Variability                           | 16 |  |

|   |      | 2.3.3        | I/O Variability: Energy Concerns                                     | 17 |  |

|   |      | 2.3.4        | Variable I/O, Yet Predictable of I/O Patterns                        | 18 |  |

|   | 2.4  | Analy        | sis and Visualization: an Overlooked Process                         | 20 |  |

|   |      | 2.4.1        | Visualization Software and Techniques                                | 20 |  |

|   |      | 2.4.2        | Toward Simulation/Visualization Coupling                             | 21 |  |

|   |      | 2.4.3        | A Taxonomy of In Situ Visualization Methods                          | 21 |  |

|   |      | 2.4.4        | From Offline to In Situ Visualization: Another Source of Variability | 22 |  |

|   |      | 2.4.5        | Our Vision: Pushing (Harder) Toward In Situ Visualization            | 22 |  |

|   | 2.5  | Discus       | ssion: Addressing I/O Performance Variability                        | 23 |  |

| 3 | Dan  | naris: L     | everaging Dedicated Cores to Hide the I/O Variability                | 25 |  |

|   | 3.1  | Addre        | essing I/O Variability through Dedicated I/O Cores                   | 26 |  |

|   | 3.2  | The D        | Pamaris Approach                                                     | 27 |  |

|   |      | 3.2.1        | Design Principles                                                    | 27 |  |

|   |      | 3.2.2        | Architecture and Implementation                                      | 28 |  |

|   |      | 3.2.3 Client API                                            | 31       |

|---|------|-------------------------------------------------------------|----------|

|   |      | 3.2.4 Writing with Damaris                                  | 33       |

|   | 3.3  | 8                                                           | 33       |

|   |      |                                                             | 33       |

|   |      |                                                             | 34       |

|   |      | 0                                                           | 35       |

|   |      |                                                             | 41       |

|   | 3.4  |                                                             | 41       |

|   | 0.1  |                                                             | 41       |

|   |      |                                                             | 42       |

|   | 3.5  |                                                             | 12<br>43 |

|   | 0.0  |                                                             | 13<br>43 |

|   |      |                                                             | 13<br>44 |

|   |      |                                                             | 11<br>44 |

|   |      |                                                             | гт       |

| 4 | Exte | ending Damaris to Support In Situ Visualization             | 45       |

|   | 4.1  | <b>e 1</b>                                                  | 46       |

|   |      |                                                             | 46       |

|   |      |                                                             | 47       |

|   |      |                                                             | 49       |

|   |      | 0                                                           | 51       |

|   | 4.2  |                                                             | 52       |

|   | 1.2  |                                                             | 52       |

|   |      |                                                             | 55       |

|   | 4.3  |                                                             | 56       |

|   | 1.0  | 1                                                           | 56       |

|   |      | 1                                                           | 59       |

|   | 4.4  | 1                                                           | 62       |

|   | 1.1  |                                                             | 62       |

|   |      |                                                             | 63       |

|   | 4.5  |                                                             | 64       |

|   | 1.0  |                                                             | 64       |

|   |      |                                                             | 65       |

|   |      |                                                             | ,0       |

| 5 | Ene  | rgy and Performance Tradeoffs in Data Management Approaches | 67       |

|   | 5.1  |                                                             | 68       |

|   |      | 5.1.1 Three I/O Approaches                                  | 68       |

|   |      | 5.1.2 From Dedicated Cores to Dedicating Nodes              | 68       |

|   | 5.2  | Experimental Insight into the Energy/Performance Tradeoff   | 70       |

|   |      |                                                             | 70       |

|   |      |                                                             | 71       |

|   | 5.3  |                                                             | 76       |

|   |      |                                                             | 76       |

|   |      |                                                             | 77       |

|   |      | •                                                           | 79       |

|   | 5.4  | 1                                                           | 81       |

|   |      |                                                             | 81       |

|   |      | 0 0/ ····                                                   | _        |

|   |     | 5.4.2    | Saving Energy                                                      | 81  |

|---|-----|----------|--------------------------------------------------------------------|-----|

|   |     | 5.4.3    | Power Measurement Methods                                          | 83  |

|   | 5.5 | Concl    | usions                                                             | 83  |

| 6 |     |          | Mitigating I/O Interference through Cross-Application Coordination | 85  |

|   | 6.1 |          | nterference: an Increasingly Important Issue                       | 86  |

|   |     | 6.1.1    | Probability of Concurrent Accesses                                 | 86  |

|   |     | 6.1.2    | Studying I/O Interference: a Methodology                           | 88  |

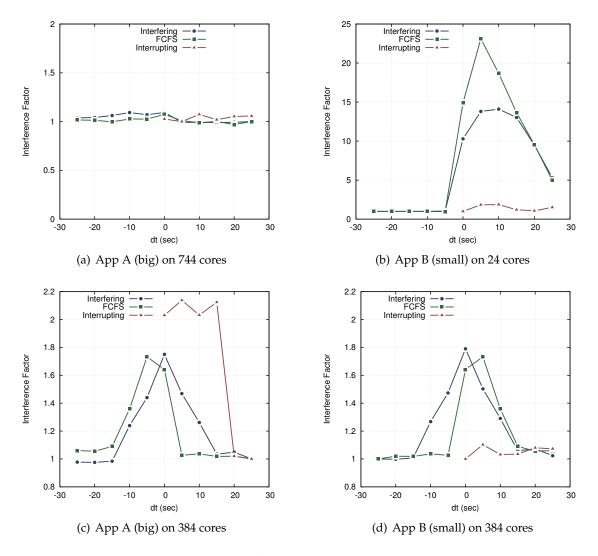

|   |     | 6.1.3    | Impact of Interference on I/O Optimizations                        | 89  |

|   |     | 6.1.4    | From Diversity to System-wide Inefficiency                         | 90  |

|   | 6.2 | 0        | ating Interference within the CALCioM Framework                    | 91  |

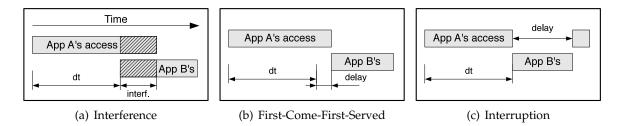

|   |     | 6.2.1    | Interference-avoiding Strategies                                   | 91  |

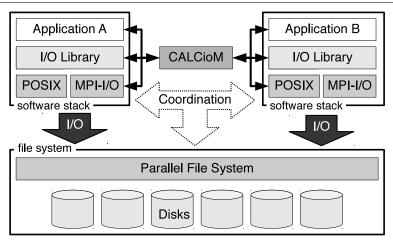

|   |     | 6.2.2    | CALCioM: Design Principles                                         | 93  |

|   |     | 6.2.3    | Architecture and API                                               | 93  |

|   | 6.3 | Exper    | imental Evaluation                                                 | 97  |

|   |     | 6.3.1    | Platforms and Methodology                                          | 97  |

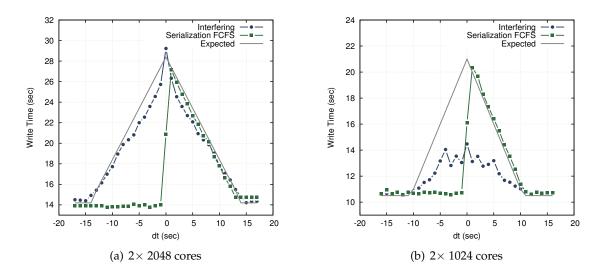

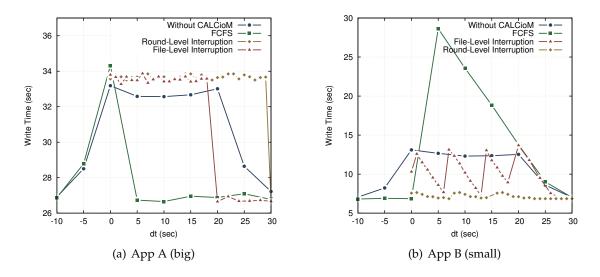

|   |     | 6.3.2    | Interfere or Serialize Accesses?                                   | 98  |

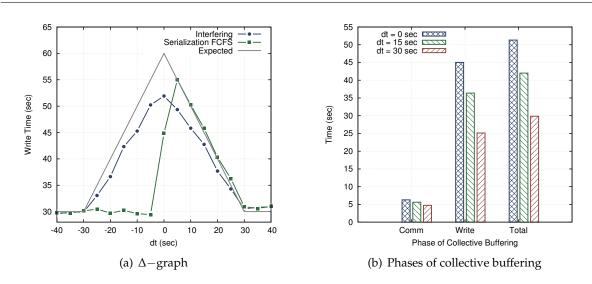

|   |     | 6.3.3    | A Third Option: Access Interruption                                | 102 |

|   |     | 6.3.4    | Dynamic Choice: Interfere, Serialize, or Interrupt?                | 102 |

|   | 6.4 | Discus   | ssion and Related Work                                             | 104 |

|   |     | 6.4.1    | Application-Side I/O Scheduling                                    | 105 |

|   |     | 6.4.2    | Server-Side I/O Scheduling                                         | 105 |

|   |     | 6.4.3    | Application-Aware I/O Scheduling                                   | 105 |

|   | 6.5 | Concl    | usion                                                              | 107 |

| 7 | Mo  | deling a | and Predicting I/O: the Omnisc'IO Approach                         | 109 |

|   | 7.1 | 0        | ations of Current Approaches to I/O Prediction                     | 110 |

|   | 7.2 |          | mnisc'IO Approach                                                  | 112 |

|   |     | 7.2.1    | Overview of Omnisc'IO                                              | 112 |

|   |     | 7.2.2    | Algorithmic and Technical Description                              | 113 |

|   | 7.3 | Exper    | imental Evaluation                                                 | 119 |

|   |     | 7.3.1    |                                                                    | 119 |

|   |     | 7.3.2    |                                                                    |     |

|   |     | 7.3.3    | Results Discussion                                                 | 120 |

|   |     | 7.3.4    | Limitations of Our Approach                                        | 131 |

|   | 7.4 |          | ssion and Related Work                                             | 131 |

|   |     | 7.4.1    | Grammar-based Modeling                                             | 131 |

|   |     | 7.4.2    | I/O Patterns Prediction                                            | 132 |

|   | 7.5 |          |                                                                    | 134 |

|   | 7.0 | 7.5.1    | Achievements of the Omnisc'IO Approach                             | 134 |

|   |     | 7.5.2    | Omnisc'IO as a Building Block for a Smart I/O Stack                | 134 |

| 8 | Con | clusior  | n and Perspectives                                                 | 135 |

| 5 | 8.1 |          | vements                                                            | 136 |

|   |     | 8.1.1    | Using Dedicated Cores for Data Services in Large Scale Simulations | 136 |

|   |     | 8.1.2    | Addressing Cross-Application I/O interference                      | 137 |

|   |     | 8.1.3    | Predicting Spatial and Temporal I/O Patterns                       | 137 |

|   |     | 0.1.0    |                                                                    | 107 |

| 8.2      | Prospects |                                            |     |

|----------|-----------|--------------------------------------------|-----|

|          | 8.2.1     | Prospects Related to the Damaris Approach  | 138 |

|          | 8.2.2     | Prospects Related to CALCioM and Omnisc'IO | 139 |

| Bibliogr | aphy      |                                            | 141 |

# **List of Figures**

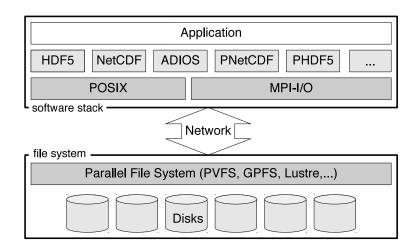

| 2.1  | The typical I/O Stack of HPC Simulations                               | 11 |

|------|------------------------------------------------------------------------|----|

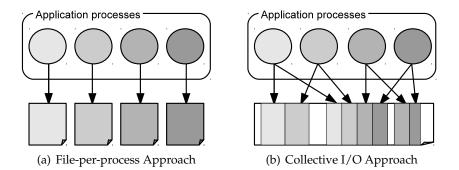

| 2.2  | Traditional approaches to I/O in HPC simulations                       | 14 |

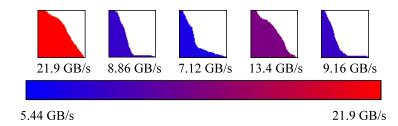

| 2.3  | Illustration of the I/O variability across processes and I/O phases    | 15 |

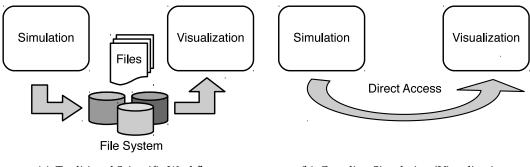

| 2.4  | Two approaches to retrieve insight from large-scale simulations        | 21 |

| 3.1  | Software architecture of the implementation of Damaris                 | 28 |

| 3.2  | Simulation of a supercell producing a long-track EF5 tornado           | 34 |

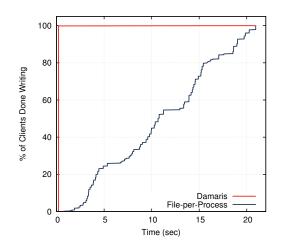

| 3.3  | Write time of CM1 on Kraken                                            | 36 |

| 3.4  | Write time of CM1 on BluePrint                                         | 36 |

| 3.5  | Cumulative distribution function of the write time of CM1 on Grid'5000 | 38 |

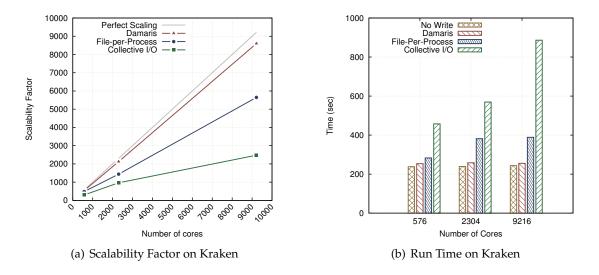

| 3.6  | Scalability and total run time of CM1 on Kraken                        | 39 |

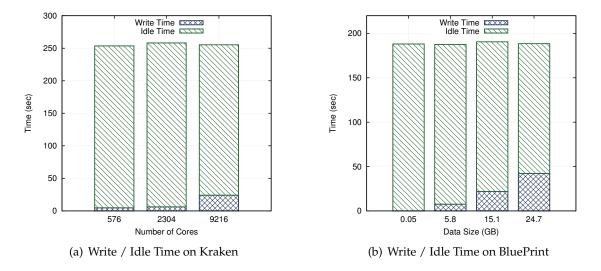

| 3.7  | Write and idle time of dedicated cores on Kraken and BluePrint         | 39 |

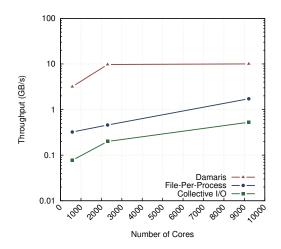

| 3.8  | Aggregate throughput of CM1 on Kraken                                  | 40 |

| 3.9  | Write time in Damaris using compression and transfer delays            | 42 |

| 4.1  | Semantics of Damaris' direct data access functions                     | 47 |

| 4.2  | Example of rectilinear grid                                            | 50 |

| 4.3  | Example of visualizations from the CM1 and Nek5000 simulations         | 57 |

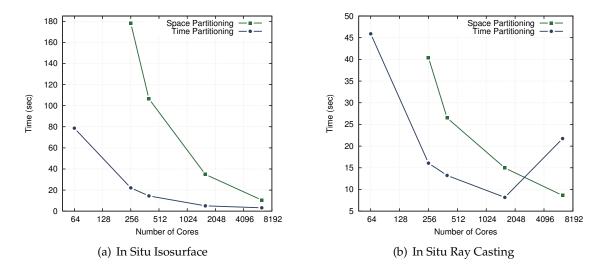

| 4.4  | Rendering time of in situ ray-casting and isosurfaces of CM1           | 58 |

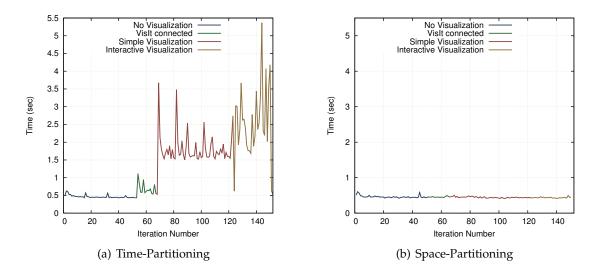

| 4.5  | Run-time variability in CM1 due to ISV                                 | 60 |

| 4.6  | Iteration time of Nek5000's MATiS configuration with and without ISV   | 61 |

| 5.1  | Three approaches to I/O for HPC applications                           | 68 |

| 5.2  | Data transfer protocols using dedicated cores and dedicated nodes      | 69 |

| 5.3  | Energy consumption and completion time of CM1 on Grid'5000 (Nancy)     | 72 |

| 5.4  | Energy consumption of CM1 on Nancy with different output frequencies   | 73 |

| 5.5  | Energy consumption and completion time of CM1 on Grid'5000 (Rennes)    | 74 |

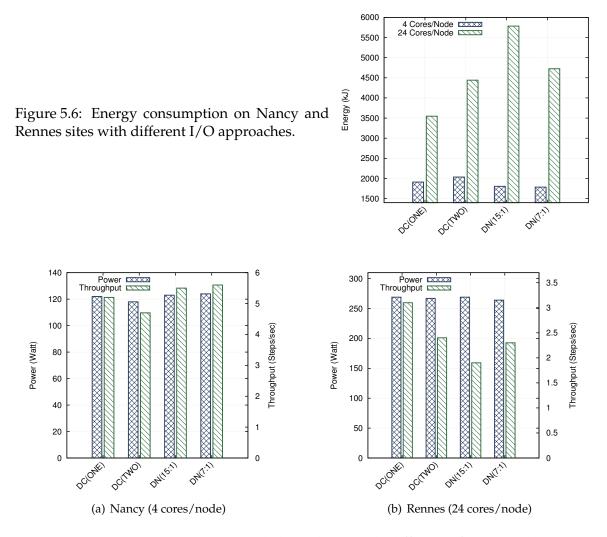

| 5.6  | Energy consumption of CM1 on Nancy and Rennes                          | 75 |

| 5.7  | Average power usage and throughput of CM1 on Nancy and Rennes          | 75 |

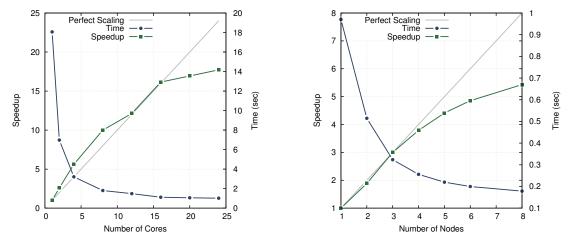

| 5.8  | Scalability of CM1 on Grid'5000 (Rennes)                               | 78 |

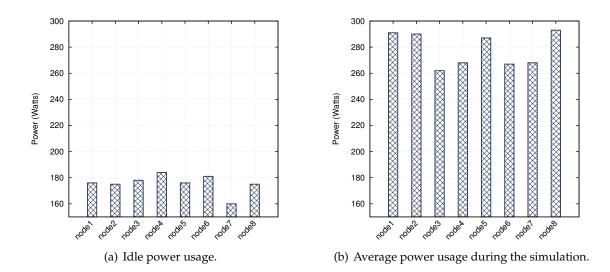

| 5.9  | Power usage of CM1 on Grid'5000 (Rennes)                               | 79 |

| 5.10 |                                                                        | 79 |

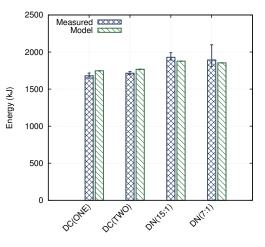

| 5.11 | Observed and estimated energy consumption of CM1 on Grid'5000 (Nancy). | 80 |

| 6.1  | Distribution of job sizes and concurrency on Intrepid                  | 87 |

|      |                                                                        |    |

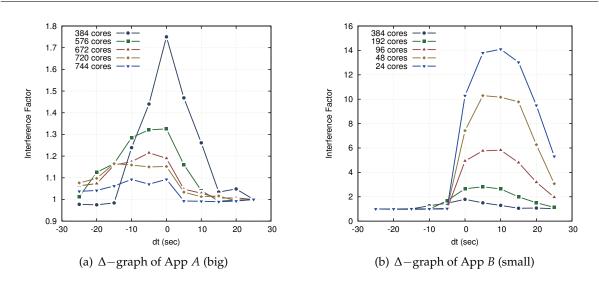

| 6.2  | Example of $\Delta$ -graph: interference between two applications on Grid'5000          | 88  |

|------|-----------------------------------------------------------------------------------------|-----|

| 6.3  | Impact of interference on caching, experiment with IOR on Grid'5000                     | 89  |

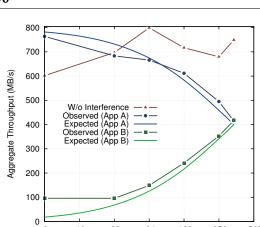

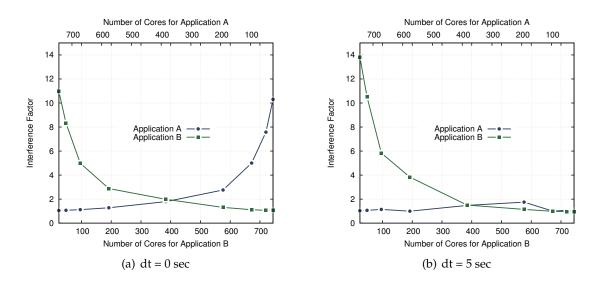

| 6.4  | Throughput of interfering applications of different sizes on Grid'5000                  | 90  |

| 6.5  | Interference between applications of different sizes on Grid'5000, with differ-         |     |

|      | ent starting delays between applications                                                | 91  |

| 6.6  | Three possible policies to deal with cross-application interference                     | 92  |

| 6.7  | Schema of the CALCioM approach                                                          | 94  |

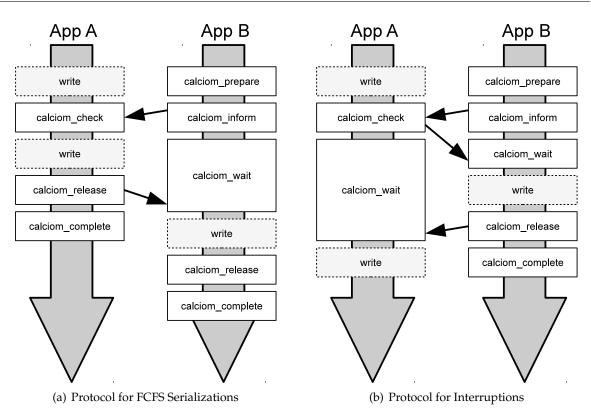

| 6.8  | CALCioM's protocols for serialization and interruptions                                 | 96  |

| 6.9  | $\Delta$ -graph of applications running on different numbers of cores (Grid'5000) .     | 98  |

| 6.10 | $\Delta$ -graph of interference between two applications of the same size (Surveyor)    | 99  |

| 6.11 | $\Delta$ -graph and proportion of communications vs. writes for applications inter-     |     |

|      | fering on a strided pattern (Surveyor)                                                  | 100 |

| 6.12 | $\Delta$ -graphs of applications with different sizes, using the three policies offered |     |

|      | by CALCioM (Grid'5000)                                                                  | 101 |

| 6.13 | $\Delta$ -graph of interference for applications with different write sizes (Surveyor)  | 103 |

| 6.14 | Synthesis on CALCioM's choices and their impact on computational efficiency             | 104 |

| 6.15 | $\Delta$ -graph of interference between two small applications (Surveyor) $\ldots$      | 104 |

| 7.1  | Overview of the Omnisc'IO approach                                                      | 112 |

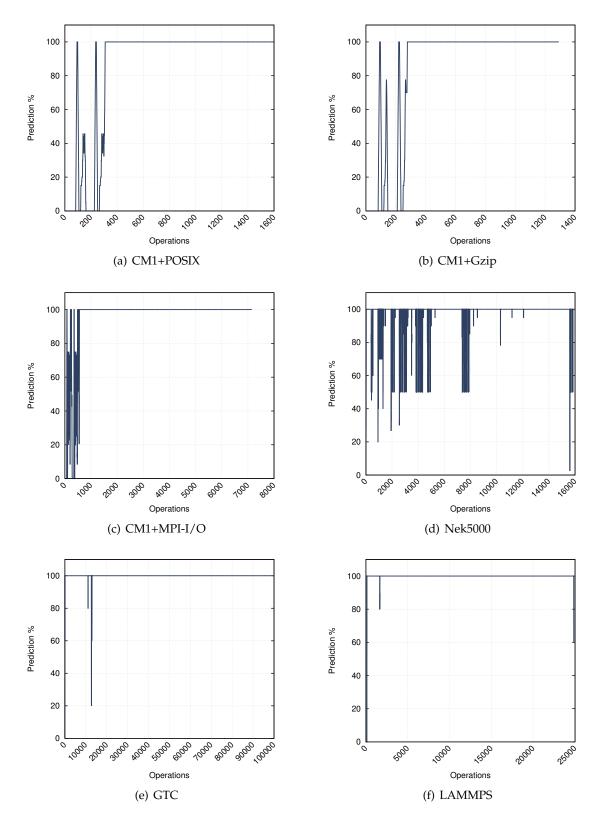

| 7.2  | Context prediction capability of Omnisc'IO                                              | 121 |

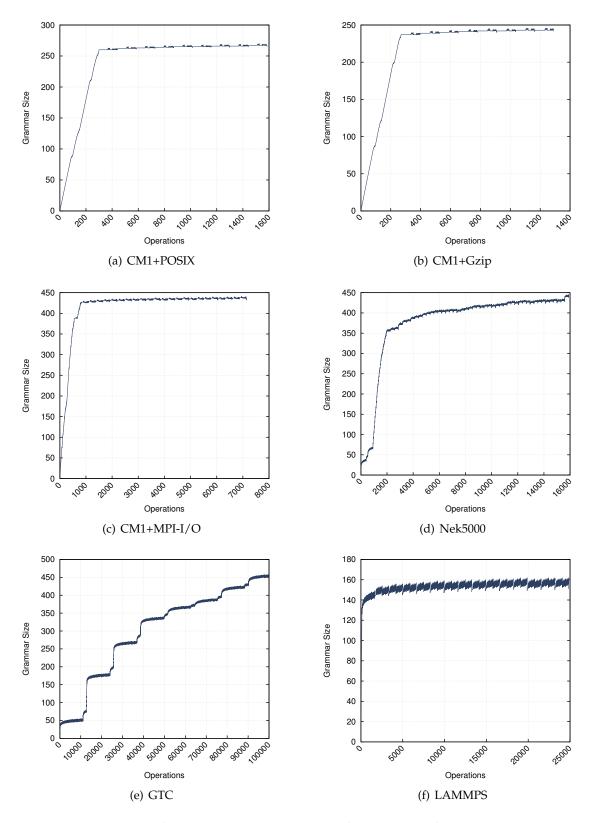

| 7.3  | Evolution of the size of Omnisc'IO's main grammar                                       | 124 |

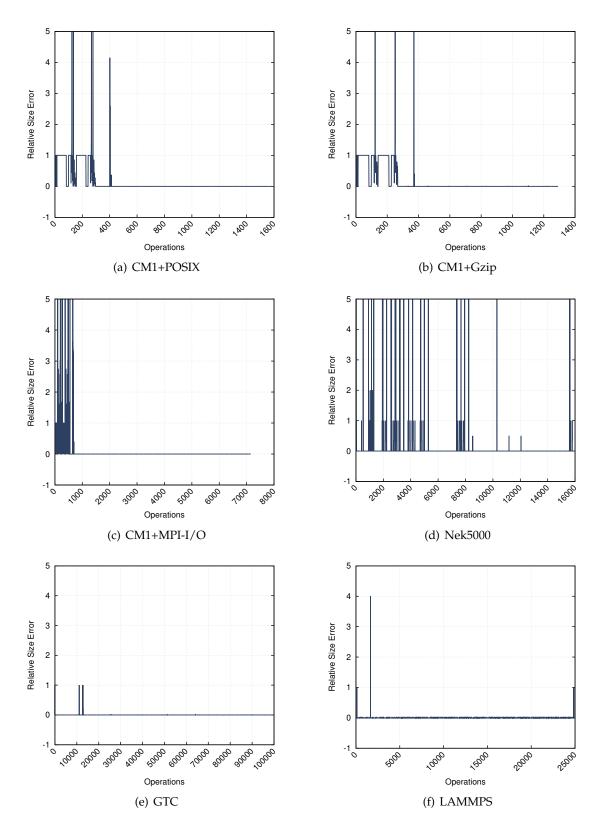

| 7.4  | Relative error in the prediction of access sizes                                        | 125 |

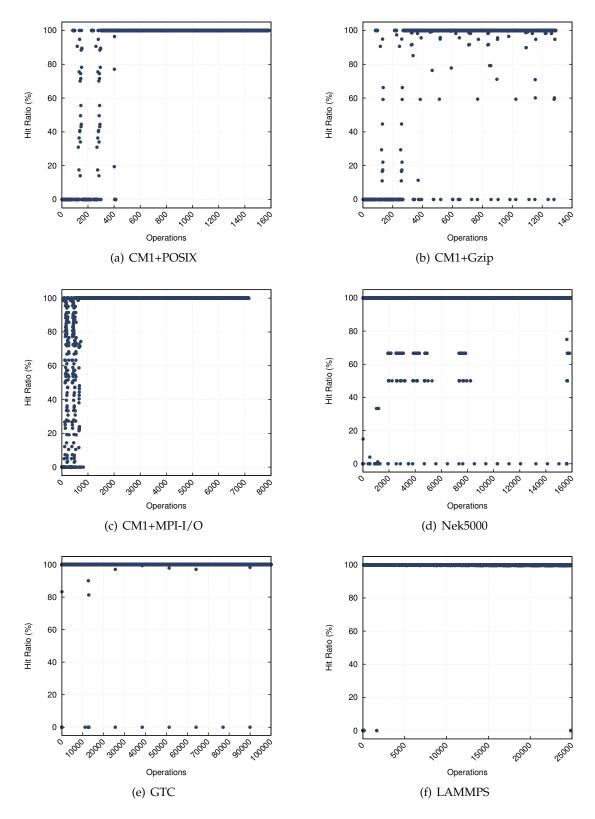

| 7.5  | Hit ratio using Omnisc'IO                                                               | 128 |

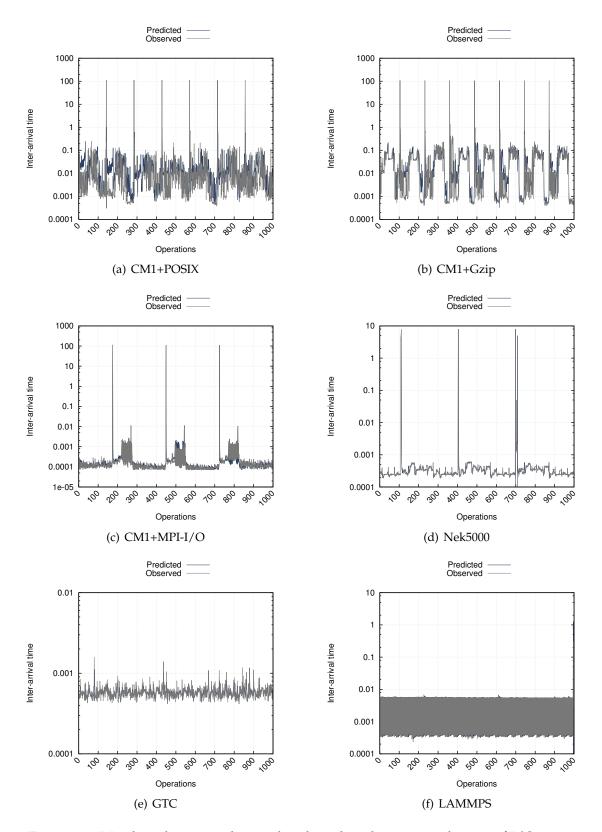

| 7.6  | Matching between observed and predicted interarrival time of I/O events                 | 129 |

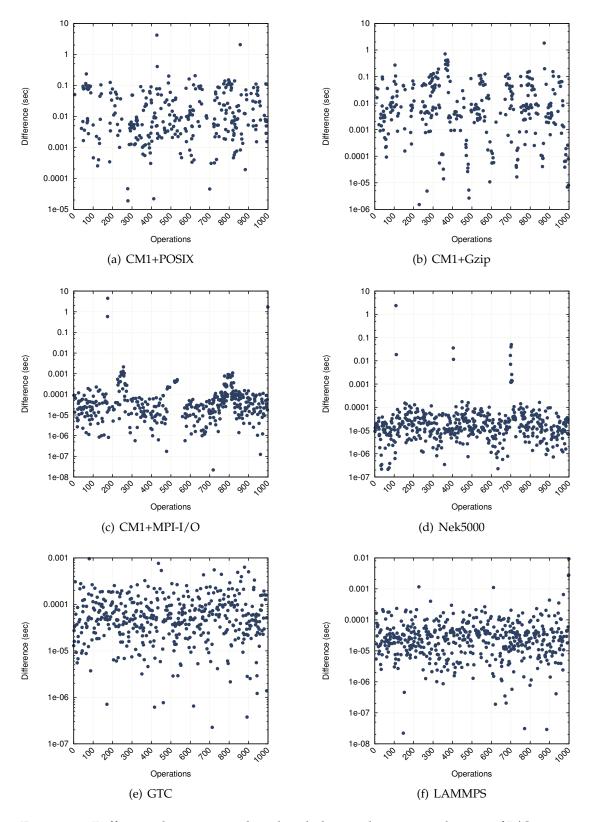

| 7.7  | Difference between predicted and observed interarrival times of I/O events .            | 130 |

# **List of Tables**

| Average aggregate throughput of CM1 on Grid'5000                                                                                 | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Amount of code modifications in example codes using VisIt and Damaris<br>Average iteration time of Nek5000's MATiS configuration | 54<br>62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Statistics on energy consumption of CM1 on Grid'5000 (Nancy) Accuracy of the energy model on Grid'5000 (Rennes and Nancy)        | 73<br>81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| List of approaches to I/O prediction in the literature                                                                           | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Examples of context-free grammars                                                                                                | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Predictors incrementation matching a given input                                                                                 | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Discovery of new predictors matching the last input                                                                              | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| List of applications used to evaluate Omnisc'IO and their I/O backends                                                           | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Proportion of correct offset predictions with Omnisc'IO                                                                          | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Average hit ratio achieved by Omnisc'IO                                                                                          | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Average time different between predicted and observed interarrival times                                                         | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Run-time overhead of Omnisc'IO                                                                                                   | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                  | Amount of code modifications in example codes using VisIt and DamarisAverage iteration time of Nek5000's MATiS configurationStatistics on energy consumption of CM1 on Grid'5000 (Nancy)Accuracy of the energy model on Grid'5000 (Rennes and Nancy)List of approaches to I/O prediction in the literatureExamples of context-free grammarsPredictors incrementation matching a given inputDiscovery of new predictors matching the last inputList of applications used to evaluate Omnisc'IO and their I/O backendsAverage hit ratio achieved by Omnisc'IOAverage time different between predicted and observed interarrival times |

# **List of Listings**

| 3.1 | Example of Fortran simulation using Damaris            | 32 |

|-----|--------------------------------------------------------|----|

| 3.2 | Configuration file associated with the Fortran example | 33 |

| 4.1 | Description of a mesh in the Damaris/Viz configuration | 51 |

| 4.2 | Allocation for data accessed by Damaris                | 52 |

| 4.3 | Example of Damaris' Python interface                   | 52 |

| 4.4 | In situ data access functions using VisIt              | 53 |

| 4.5 | In situ data access functions using ParaView           | 55 |

|     |                                                        |    |

# Chapter

## Introduction

#### Contents 1.1 1 1.2 2 1.3 5 1.4 6 Organization of the Manuscript 7 1.5

#### 1.1 Context

In 2008, the high-performance computing (HPC) community reached *Petascale* capabilities with IBM's Roadrunner, a 122,400 core supercomputer with a peak performance of 1.375 Petaflops  $(1.375 \times 10^{15} floating point operations per second)$  [130]. Million-core machines have become a reality in 2012 with LLNL's Sequoia supercomputer and, following Moore's law, which states that the number of transistors in cutting-edge computing systems doubles every 18 months, *Exascale* supercomputers (capable of  $10^{18}$  flops) are expected by 2018 [127]. Such an immense computational power is used in many research areas, including earth sciences, biology, climate, or cosmology, where large scale simulations are conducted to better understand the physical phenomena that surround us. These simulations aim to replace real experiments that are either too expensive, too dangerous or simply unfeasible, such as studies of the early universe: "We have this problem in astrophysics that we can't go and do experiments in the lab to test our theories" says Mark Vogelsberger, from MIT, in an interview for The Guardian [112] on the results of a recent simulation of the universe [40, 136].

The manufacturing sector also uses supercomputers to decrease design costs. For example, the use of virtual (i.e., numerically simulated) wind tunnels allowed Boeing to reduce

to 11 the number of wing prototypes effectively constructed for their 787 "Dreamliner" aircraft in 2005, in contrast with the 77 prototypes used in the design of the 767 model back in the 1980s [65]. High performance simulations have indeed the benefits of being faster and cheaper than designing actual prototypes. Besides, HPC simulations can be reproduced, and virtual models can be evaluated in various conditions with very high accuracy.

But as Ken Batcher stated, "a supercomputer is a device for turning compute-bound problems into I/O-bound problems". Indeed, larger machines lead to the production of larger amounts of data that have to be efficiently stored and processed in order to retrieve scientific insights. The traditional approach to data management consists of storing the output of the simulation in files during its run, move these files and analyze them later offline. Yet we observe an increasing gap between the performance of storage systems and the computation capabilities of recent supercomputers. For instance, while ORNL's Jaguar machine (ranked 1<sup>st</sup> in the Top 500 list of supercomputers [130] in November 2009 and June 2010) provided 240 GB/s of storage throughput for a peak performance of 1.75 Petaflops, its successor Titan (ranked 1<sup>st</sup> in November 2012) was subject to a tenfold improvement of performance (achieving 17.59 Petaflops) for only a sixfold increase of storage throughput (achieving 1.4 TB/s). This gap makes traditional approaches to I/O (input/output) unsustainable, as they take an increasingly larger portion of the application's run time and lead to a *variability* of this run time.

On one hand, it becomes necessary to optimize the I/O stack at every level, from the simulation down to the file system, in order to improve I/O performance together with the predictability of these performances. This also involves improving the way storage systems deal with a higher degree of concurrency, not only from the hundreds of thousands of processes that constitute a single application, but also from many applications concurrently running on the machine.

On the other hand, bringing data analysis and visualization tasks closer to the simulation will become inevitable to avoid storing massive amounts of data in the near future. This rises challenges in the way simulations can efficiently communicate and share data without impacting their performance.

Finally, the energy consumption of next-generation supercomputers is a rising concern in the HPC community. While current Petascale machines run at around 10 MW, the US's Defense Advanced Research Projects Agency (DARPA) has set a 20 MW power budget for Exascale machines [52]; a twofold increase of energy consumption for a thousandfold increase of computation performance. This target will be achieved not only through hardware improvements, but also with novel, energy-efficient software approaches. In particular, data movements and storage constitute some of the most energy-demanding tasks in high performance computing, and must now evolve with energy-efficiency in mind.

#### 1.2 Contributions

Many performance issues in the context of data management for HPC simulations boil down to a problem of *performance variability*. Differences in the time to complete an I/O task from a process to another in a massively parallel application lead to all processes waiting for the slowest one. These processes thus waste valuable computation time and energy. With today's approaches to data management, this variability has multiple causes. First, in most HPC applications I/O is concurrently performed by all processes, which leads to I/O bursts. This causes resource contention and substantial variability of the I/O performance of individual processes, which significantly impacts the overall application performance. Second, coupling simulations with visualization and analysis packages further increases this variability, especially when visualization tasks are performed interactively. A third source of variability comes from concurrent accesses to the storage system by many independent applications running on the same machine.

In this thesis, we aim to address the challenges posed by the increasing variability in the performance of current data management approaches. Our work was mainly carried out in the context of the JLPC (Joint Laboratory for Petascale Computing), a joint laboratory between Inria, the National Center for Supercomputing Applications (NCSA) at the University of Illinois at Urbana-Champaign (UIUC), and Argonne National Laboratory (ANL). It led to several projects between the KerData team, ANL and UIUC: FACCTS (France and Chicago Collaborating in the Sciences), PUF (Partner University Fund), and the Data@Exascale associated team. The main contributions of this Ph.D thesis can be summarized as follows.

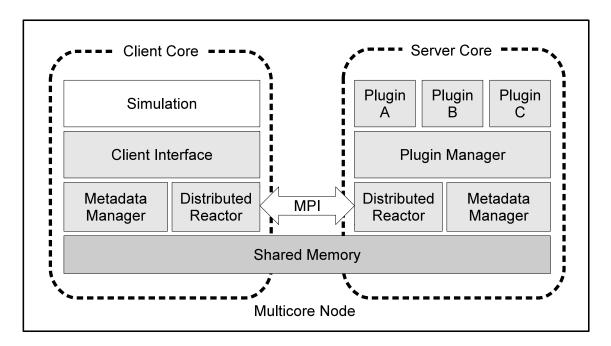

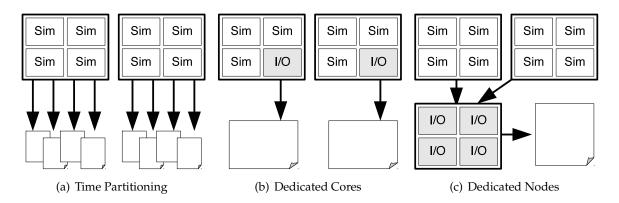

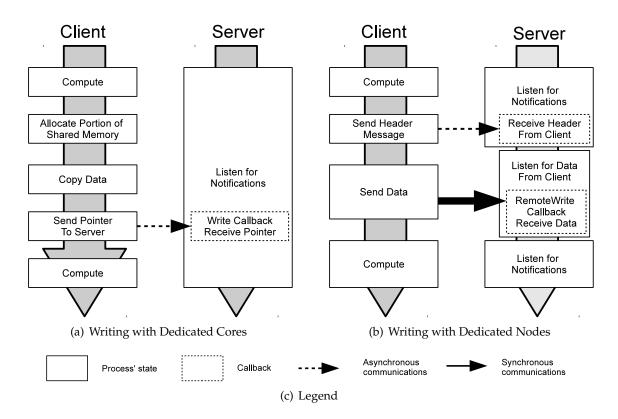

#### Using Dedicated Cores in Multicore Nodes to Hide the I/O Jitter

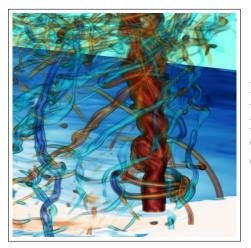

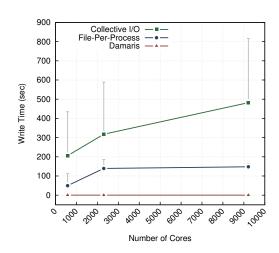

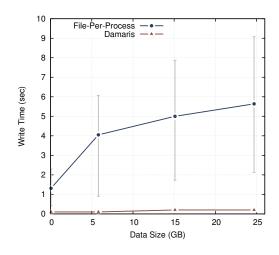

With an increasing use of massively multicore nodes, a first level of contention occurs when many processes in the same node try to concurrently access the same network interface. This causes substantial performance variability. We call I/O jitter this type of variability, originating from I/O contention within a single application. In this work, we propose a new approach to I/O, called Damaris, which leverages dedicated I/O cores on each multicore SMP (Symmetric multiprocessing) node, along with the use of shared memory, to efficiently perform asynchronous data processing and I/O in order to hide this jitter. We evaluate Damaris on three different platforms including the Kraken Cray XT5 supercomputer [63], with the CM1 atmospheric model [7]. By overlapping I/O with computation and by gathering data into large files while avoiding synchronization between cores, our solution brings several benefits: (1) it fully hides the jitter as well as all I/O-related costs, which makes the simulation's performance predictable; (2) it increases the sustained write throughput by a factor of 15 compared to standard approaches; (3) it allows almost perfect scalability of the simulation up to over 9,000 cores, as opposed to state-of-the-art approaches which fail to scale; (4) it enables a 600% compression ratio without any additional overhead, leading to a major reduction of storage requirements. In addition to initiating the development of an implementation of Damaris, this work was awarded the 2<sup>nd</sup> prize at the ACM Student Research Competition held in conjunction with the ICS '11 conference (see [23]). It also led to a publication at the CLUSTER '12 conference (see [24]).

#### Bringing In Situ Visualization Capabilities to Dedicated Cores

Reducing the amount of data stored by simulations will be of utmost importance for the next generation of large-scale computing. Accordingly, there is active research to shift analysis and visualization tasks to run in situ, that is, closer to the simulation by sharing its resources. This approach is beneficial as it can avoid the necessity to store large amounts of data for post-processing. However, it can lead to an important impact on the simulation's run time if not carefully implemented. This work focuses on the specific case of in

situ visualization where analysis codes are collocated with the simulation's code and run on the same resources. It is important for an in situ technique to require minimum modifications to existing codes, be adaptable, and have a low impact on both run times and resource usage. We accomplish this through the Damaris/Viz framework, which provides in situ visualization support to our implementation of the Damaris approach. The use of Damaris as a bridge to existing visualization packages allows us to (1) reduce code modification in existing simulations, (2) gather capabilities of several visualization tools to offer a unified data management interface, (3) use dedicated cores to hide the run-time impact of in situ visualization and (4) efficiently use memory through a shared-memory-based communication model. Experiments were conducted on Blue Waters and Grid'5000 [53] to visualize the CM1 atmospheric simulation and the Nek5000 CFD solver [98]. This work led to a publication at the LDAV '13 conference (see [26]).

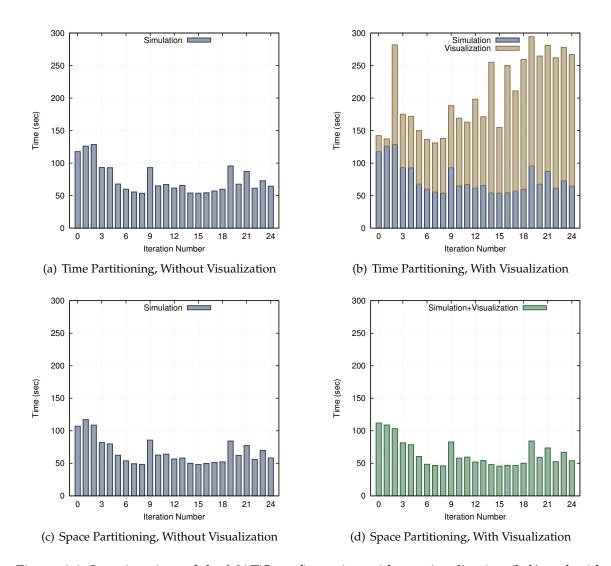

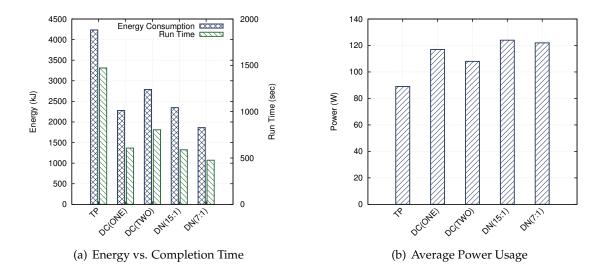

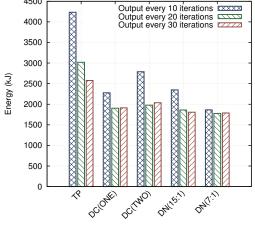

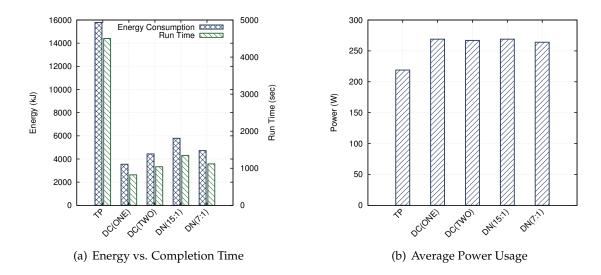

#### Analyzing the Energy vs. Performance Tradeoff in Diverse I/O Approaches

A major challenge of future Exascale machines consists of sustaining a high performance per watt ratio. Many recent works, including the first contribution of this Ph.D. thesis, have explored new approaches to I/O management aiming to reduce the I/O performance bottleneck exhibited by HPC applications (and hence to improve application performance). There is comparatively little work investigating the impact of I/O management approaches on energy consumption. In particular, approaches that attempt to overlap computation with I/O have a beneficial effect on performance variability and thus, on energy consumption. In this work, we completed our implementation of the Damaris I/O middleware with various approaches to data management, including the possibility to use dedicated nodes instead of dedicated cores, and the possibility to run I/O tasks synchronously, i.e., with no dedicated resources at all. We closely examine these radically different I/O schemes and perform extensive experiments with the CM1 atmospheric model. Our experimental results obtained on the Grid'5000 platform highlights the differences between these approaches and illustrates in which way various configurations of the application and of the system impact performance and energy consumption. We then propose and validate a mathematical model to estimate the energy consumption of a simulation under different I/O approaches. Part of this work was published at the DIDC '14 workshop, held in conjunction with the HPDC '14 conference (see [140]).

#### Mitigating I/O Contention through Cross-Application Coordination

As larger machines are used by an increasing number of applications in a concurrent manner, the interference produced by multiple applications accessing a shared parallel file system in contention becomes a major problem. Interference often breaks single-application I/O optimizations (such as access patterns preliminarily optimized to improve data locality on disks), dramatically degrading application I/O performance, increasing run time variability and, as a result, lowering machine-wide efficiency. We addressed this challenge by proposing CALCioM, a framework that aims to mitigate I/O interference through the dynamic selection of appropriate scheduling policies. CALCioM allows several applications running on a supercomputer to communicate and coordinate their I/O strategy in order to avoid interfering with one another. In this work, we examine four I/O strategies that can be accommodated in this framework: serializing, interrupting, interfering and coordinating. Experiments on Argonne's BG/P Surveyor machine and on several clusters of Grid'5000 show how CALCioM can be used to efficiently and transparently improve the scheduling strategy between two otherwise interfering applications, given specified metrics of machine wide efficiency. This work, partially carried out during a 3-month internship at ANL, led to a publication at the IPDPS '14 conference (see [27]).

#### Predicting the Spatial and Temporal I/O Patterns of HPC Applications

Many I/O optimizations including prefetching, caching, and scheduling, have been proposed to improve the performance of the I/O stack. In order to optimize these techniques, modeling and predicting spatial and temporal I/O patterns of HPC applications as they run have become crucial. In this direction we introduce Omnisc'IO, an original approach that aims to make a step forward toward an intelligent I/O management of HPC applications in next-generation post-Petascale supercomputers. It builds a grammar-based model of the I/O behavior of any HPC application and uses this model to predict when future I/O operations will occur, as well as where and how much data will be accessed. Omnisc'IO is transparently integrated into the POSIX and MPI-I/O stacks and does not require any modification to application sources or to high-level I/O libraries. It works without prior knowledge of the application, and converges to accurate predictions within a couple of iterations only. Its implementation is efficient both in computation time and in memory footprint. Omnisc'IO was evaluated with four real HPC applications – CM1, Nek5000, GTC [43], and LAMMPS [105] – using a variety of I/O backends ranging from simple POSIX to Parallel HDF5 on top of MPI-I/O. Our experiments show that Omnisc'IO achieves from 79.5% to 100% accuracy in spatial prediction and an average precision of temporal predictions ranging from 0.2 seconds to less than a millisecond. This work was published at the SC '14 conference and initiated the development of the Omnisc'IO software (see [28]).

#### **1.3** Publications

#### **International Conferences**

- Bogdan Nicolae, Diana Moise, Gabriel Antoniu, Luc Bougé, **Matthieu Dorier**. *BlobSeer: Bringing High Throughput under Heavy Concurrency to Hadoop Map/Reduce Applications,* in Proceeding of the 2010 IEEE International Parallel & Distributed Processing Symposium (IPDPS '10), *Atlanta, September* 2010. CORE Rank A (acceptance rate 24%).

- Matthieu Dorier, Gabriel Antoniu, Franck Cappello, Marc Snir, Leigh Orf. *Damaris: How to Efficiently Leverage Multicore Parallelism to Achieve Scalable, Jitter-free I/O,* in Proceedings of the 2012 IEEE International Conference on Cluster Computing (CLUSTER '12), *Beijing, September 2012.* CORE Rank A (acceptance rate 28%).

- Matthieu Dorier, Roberto Sisneros, Tom Peterka, Gabriel Antoniu, Dave Semeraro. Damaris/Viz, a Nonintrusive, Adaptable and User-Friendly In Situ Visualization Framework, in Proceedings of the 2013 IEEE Symposium on Large Data Analysis and Visualization (LDAV '13), Atlanta, October 2013. (acceptance rate 37%).

- Matthieu Dorier, Gabriel Antoniu, Rob Ross, Dries Kimpe, Shadi Ibrahim. CALCioM: Mitigating I/O Interference in HPC Systems through Cross-Application Coordination, in Proceedings of the 2014 IEEE International Parallel & Distributed Processing Symposium (IPDPS '14), Phoenix, May 2014. CORE Rank A (acceptance rate 21%).

- Matthieu Dorier, Shadi Ibrahim, Gabriel Antoniu, Rob Ross. *Omnisc'IO: A Grammar-Based Approach to Spatial and Temporal I/O Patterns Prediction,* in Proceedings of ACM/IEEE 2014 Supercomputing Conference (SC '14), *New Orleans, November 2014.* CORE Rank A (acceptance rate 21%).

#### Workshops at International Conferences

Orçun Yildiz, Matthieu Dorier, Shadi Ibrahim, Gabriel Antoniu. A Performance and Energy Analysis of I/O Management Approaches for Exascale Systems, in Proceedings of the 2014 Data-Intensive Distributed Computing (DIDC '14) workshop, held in conjunction with the 23<sup>rd</sup> International ACM Symposium on High Performance Parallel and Distributed Computing (HPDC '14), Vancouver, June 2014.

#### **Posters at International Conferences**

- Matthieu Dorier. Damaris Using Dedicated I/O Cores for Scalable Post-petascale HPC Simulations, 2011 ACM/SIGARCH International Conference on Supercomputing (ICS '11), Tucson, April 2011. 2<sup>nd</sup> prize at the ACM Student Research Competition.

- Matthieu Dorier. Efficient I/O using Dedicated Cores in Large-Scale HPC Simulations, 2013 IEEE International Parallel & Distributed Processing Symposium (IPDPS '13): PhD Forum, Boston, May 2013.

#### 1.4 Software

Damaris is a middleware for multicore SMP nodes allowing them to efficiently handle data transfers for storage and visualization by dedicating one or a few cores to the application I/O. It allows efficient asynchronous I/O, hiding all I/O related overheads such as data compression, post-processing and in situ visualization (through its Damaris/Viz extension). Damaris was evaluated on Blue Waters (Cray XE6, NCSA), Kraken (Cray XT5, NICS), Titan (Cray XK7, ORNL), Intrepid (IBM BlueGene/P, ANL), Grid'5000 (French grid testbed), Blue Print (Power5 cluster, NCSA), with the CM1 atmospheric simulation and the Nek5000 CFD simulation. Damaris is at the core of Chapters 3 to 5 of this thesis. Damaris was formally validated for use on NCSA's Blue Waters supercomputer. To our knowledge, it has been used successfully by several researchers from NCSA, Central Michigan University and the Federal University of Rio Grande do Sul (UFRGS).

Link: http://damaris.gforge.inria.fr

**Size and language(s):** 19500 lines, C++, Fortran, XML **License:** LGPL

- Omnisc'IO is a middleware integrated in the POSIX and MPI-I/O stacks to transparently observe, model and predict the I/O behavior of any HPC application. It is based on formal grammars and implements a modified version of the Sequitur algorithm. Omnisc'IO has been used on Grid'5000 with the CM1 atmospheric simulation, the LAMMPS molecular dynamics simulation, the GTC fusion simulation and the Nek5000 CFD simulation. Omnisc'IO is at the core of Chapter 7 of this thesis. Link: http://omniscio.gforge.inria.fr

Size and language(s): 4400 lines, C++

License: LGPL

- **Darshan-Ruby** is an object-oriented extension to simplify the analysis of ANL's Darshan [10] log files (a tool that traces the I/O of simulations running on supercomputers) using the Ruby language. It was developed to help us get a faster insight into the I/O behavior of large-scale applications. Darshan-Ruby efficiently accesses Darshan data without intermediate conversion into text format. It is available as a Ruby Gem package on the official rubygems.org repository and, as of September 2014, was downloaded 1600 times. Darshan-Ruby led to the Darshan-Web project, which proposes a web platform that analyzes traces and provides users with hints on how to improve the I/O performance of their applications.

Link: http://darshan-ruby.gforge.inria.fr Size and language(s): 400 lines, C, Ruby License: LGPL

#### **1.5** Organization of the Manuscript

The rest of this manuscript is organized in seven chapters.

The first chapter presents the context of our research. We introduce the applications and platforms, as well as the traditional approaches to data management in post-Petascale systems. We then dive into the challenges posed by these approaches in terms of I/O variability at large scale and highlight the opportunities that drove our contributions.

Chapters 3 to 5 focus on contributions related to the Damaris approach. Three major objectives are being tackled: (1) hiding the I/O costs and variability from HPC applications, (2) offering a non-impacting and adaptable way of conducting in situ analysis and visualization of large-scale simulations and (3) understanding the effect of I/O on energy consumption under different I/O approaches. Chapter 3 addresses the first objective. It presents the core of our Damaris approach and its results in addressing the challenge of hiding the I/O variability while improving I/O performance. Based on the observation that dedicated cores in Damaris remain idle an important fraction of the time, we added the support for in situ visualization. Our results on leveraging Damaris to provide in situ visualization capabilities to simulations are presented in Chapter 4. Finally, in order to compare different approaches in Damaris and conducted an extensive evaluation of the energy/performance tradeoff. This contribution is described in Chapter 5. While each chapter focuses on a particular challenge related to data management, the use of Damaris as a common framework for all three chapters allows us to zoom on particular implementation details relevant for each of them.