# Model-based Synthesis of Distributed Real-time Automotive Architectures

Ernest Wozniak Woźniak

### ▶ To cite this version:

Ernest Wozniak Woźniak. Model-based Synthesis of Distributed Real-time Automotive Architectures. Embedded Systems. Université Paris Sud - Paris XI, 2014. English. NNT: 2014PA112145. tel-01124003

## HAL Id: tel-01124003 https://theses.hal.science/tel-01124003

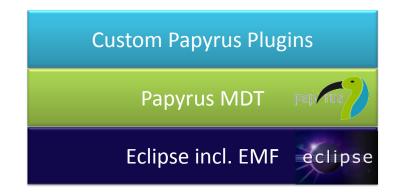

Submitted on 6 Mar 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Comprendre le monde, construire l'avenir®

# **UNIVERSITÉ PARIS-SUD**

## ÉCOLE DOCTORALE INFORMATIQUE PARIS-SUD Laboratoire de CEA Tech LIST

### **DISCIPLINE :** Informatique

## THÈSE DE DOCTORAT

soutenue le 07/07/2014

par

**Ernest Wozniak**

# Model-based Synthesis of Distributed Real-time

# Automotive Architectures

| Directeur de thèse:<br>Co-directeur de thèse | Dr. Sébasti<br>e: Dr. Chokri |                  | CEA Tech LIST<br>CEA Tech LIST                |

|----------------------------------------------|------------------------------|------------------|-----------------------------------------------|

| Composition du jury                          |                              |                  |                                               |

| Président du jury :                          | Burkhart Wolff               | Professeur (Univ | versité Paris-Sud, CNRS)                      |

| Rapporteur :                                 | Maryline Chetto              | Professeur (Univ | versité de Nantes, IRCCyN Research Institute) |

| Rapporteur :                                 | Martin Törngren              | Professeur (KTH  | Royal Institute of Technology)                |

| Examinateur :                                | Claire Pagetti               | Ingénieur-Cherc  | heur (ONERA)                                  |

| Examinateur :                                | Manfred Broy                 | Professeur (Tec  | hnische Universität München)                  |

Model-based Synthesis of Distributed Real-time Automotive Architectures

Copyright © 2014 by Ernest Wozniak

#### ACKNOWLEDGEMENTS

First I wish to thank my supervisor Dr. Sébastien Gérard. He guided me into the domain of modeling and provided almost unlimited resources and support for my research. It was a great pleasure for me to work with Sébastien Gérard. His professionalism, friendliness and openness to other people let me to simply enjoy my work under his supervision.

I am very grateful to my co-supervisor, Dr. Chokri Mraidha for his guidance throughout my entire PhD work from the very beginning where he helped me to arrange my arrival to the CEA Tech LIST institute till the very end where he dealt with all the necessary preparations to organize my defense. I am especially thankful for all his reviews done on my papers and thesis report as well as numerous discussions that influenced my research.

I would like to thank to Dr. Sara Tucci-Piergiovanni for all the discussions that we had. They were very motivating and had a great impact on the direction of my research. Her academic skills which I truly admire instilled in me a real scientific spirit.

I am deeply grateful to Prof. Haibo Zeng for hosting me as an exchange PhD student during my stay at the McGill University. Work with him was a lifetime experience and a great privilege which cemented and further expanded my knowledge.

I also had a great pleasure to work with Prof. Marco Di Natale whom I would like to thank for the numerous, fruitful, remote discussions and his commitment in a work on publications that I had a pleasure to publish with him.

I am grateful to my reviewers, i.e. Prof. Maryline Chetto and Prof. Martin Törngren for agreeing to evaluate my work and for their insightful comments. I am also very thankful to them for devoting their time to participate in my defense and be part of the committee. Similarly I would like to thank other committee members, i.e. Prof. Claire Pagetti, Prof. Burkhart Wolff and Prof. Manfred Broy. It was a privilege to have you in my jury.

I am thankful to all of my colleagues at the CEA Tech LIST for a fabulous working environment, discussions and their patience in understanding and helping to improve my French. I especially thank to Asma Mehiaoui, Ahmed Daghsen and Florian Noyrit for the joint work, conversations and sharing an office with me.

I am very grateful to my cousin Marcin Fedor who showed me numerous opportunities for professional development and inspired me to pursue the PhD work.

Last but not least I would like to thank my parents. They were always very supportive in this fabulous PhD journey. Dziękuję Wam drodzy rodzice za wsparcie!

#### PUBLICATIONS

- E. Wozniak, M. D. Natale, H. Zeng, C. Mraidha, S. T. Piergiovanni, and S. Gérard, "Assigning Time Budgets to Component Functions in the Design of Time-Critical Automotive Systems," *Automated Software Engineering (ASE), 2014 IEEE/ACM 29th International Conference, Västerås, Sweden, September 15-19, 2014*

- E. Wozniak, C. Mraidha, S. Tucci-Piergiovanni, S. Gerard, "An Optimization Approach for the Synthesis of AUTOSAR Architectures," in Proceedings of the 18th IEEE International Conference on Emerging Technologies and Factory Automation (ETFA), Cagliari, Italy, September 10-13, 2013.

- A. Mehiaoui, **E. Wozniak**, S. T. Piergiovanni, C. Mraidha, M. D. Natale, H. Zeng, J.-P. Babau, L. Lemarchand, and S. Gérard, "A two-step optimization technique for functions placement, partitioning, and priority assignment in distributed systems," in *LCTES*, 2013, Seattle, WA, USA, pp. 121–132.

- E. Wozniak, C. Mraidha, S. Tucci-Piergiovanni, S. Gerard "A Model-Based Approach for Real-Time Systems Architecture Exploration", *IST-115 Symposium on Architecture Definition & Evaluation (The NATO Science and Technology Organization), Toulouse, France 13 - 14 MAY 2013*

- E. Wozniak, S. Tucci-Piergiovanni, C. Mraidha, and S. Gerard, "An Integrated Approach for Modeling, Analysis and Optimization of Systems whose Design Follows the EASTADL2/ AUTOSAR Methodology," SAE International Journal of Passenger Cars - Electronic and Electrical Systems, May 2013 vol. 6 no. 1 276-286

- E. Wozniak, C. Mraidha, S. Gerard, "Guided Task Model Construction for Automotive Systems based on Time Budgets", *in Proceedings of the 17<sup>th</sup> IEEE International Conference on Emerging Technologies and Factory Automation (ETFA 2012), Cracow, Poland, 2012*

- S. Tucci-Piergiovanni, C. Mraidha, E. Wozniak, A. Lanusse, and S. Gerard "A UML Modelbased Approach for Replication Assessment of AUTOSAR Safety-critical Applications", *In Proceedings of the 2011 IEEE 10th International Conference on Trust, Security and Privacy in Computing and Communications (Changsha, China).*

- E. Wozniak, C. Mraidha, S. Gerard, F. Terrier, "Guidance Framework for the Generation of Implementation Models in the Automotive Domain", *in Proceedings of the 37<sup>th</sup> EUROMICRO Conference on Software Engineering and Advanced Applications (EUROMICRO-SEAA 2011) (Oulu, Finland).*

#### ABSTRACT

Model-based Synthesis of Distributed Real-time Automotive Architectures

by

#### Ernest Wozniak

Hardware/software based solutions play significant role in the automotive domain. They deliver functionality that normally wouldn't be accomplishable with pure mechanics or electronics. In fact it is common that the implementation of certain functions that was done in a mechanical manner, like hydraulic brakes, in nowadays cars is done through the software and hardware. This tendency lead to the substantial number of functions operating as a set of software components deployed into hardware entities, i.e. Electronic Control Units (ECU). As a consequence the capacity of the overall code is estimated as tens of gigabytes and the number of ECUs easily reaches 50 up to 80. Therefore the industrial state of the practice development approaches become inefficient.

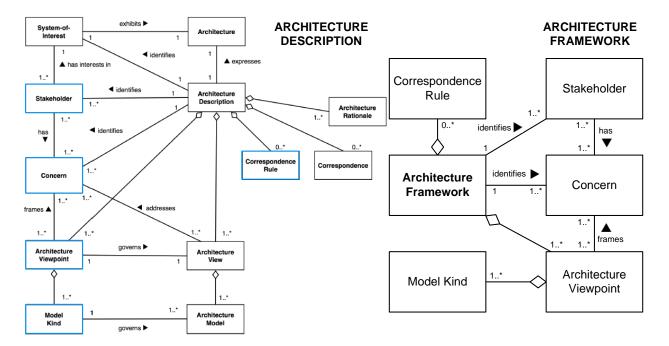

The objective of this thesis is to add to the current efforts trying to employ the Model Driven Engineering (MDE) in the context of the automotive SW/HW architectures design. Adoption of the MDE is a sound choice towards an efficient and cheaper development process. To comply with this tendency this work introduces a framework developed as an instance of an Architecture Framework and aligned to the principles of the MDE. It serves for the modeling, analysis and optimization of the automotive architectures. Within the context of this framework a set of particular contributions is presented.

First set of contributions relates to the guided strategies supporting the key engineering activities of the EAST-ADL2/AUTOSAR methodology. The main is the integration of the software architecture with the hardware platform. Although the amount of work on the synthesis is substantial, this thesis presents shortcomings that disable them to fully support the EAST-ADL2/AUTOSAR methodology. Firstly, this is

the omission of functional entities and secondly, incapability to handle situations in which execution times for them are missing. Presence of the functional entities is due to the introduction of the atomic functions and runnable entities correspondingly in the EAST-ADL2 and the AUTOSAR. The missing execution times, this is a very likely scenario to occur during the integration process as the synthesis is done on the abstract models without code implementation which is necessary to estimate them. The presence of the lasts is obligatory to enable qualitative synthesis. On the canvas of these shortcomings, a collection of new techniques to handle the synthesis step is presented. They account for the functional entities, are capable of dealing with missing execution times and optimize key parameters of the architectures, i.e. the end-to-end responses and the memory.

Second contribution concerns approaches for the UML based modeling. Comprehensible specification is the key factor for the effective maintenance of the system architecture throughout the development cycle. Surprisingly the usage of general purpose modeling languages such as the UML, SysML and MARTE although beneficial, haven't found its way yet to be fully exploited by the automotive OEMs (Original Equipment Manufacturer). This especially relates to the modeling of the analyzable input and the optimization concerns which would enable the analysis and optimization to be run directly on the model or generation of the input models for the other tools that serve for this purpose. Consequently this thesis presents models supporting these concerns, expressed with the OMG (Object Management Group) standards: UML, SysML and MARTE.

#### RESUME

Synthèse Basée sur les Modèles d'Architectures Automobiles Temps Réel Distribuées

#### 1. Contexte de la thèse

Les systèmes véhicules d'aujourd'hui sont caractérisés par une large gamme de solutions qui améliorent la performance, la sécurité et le confort de conduite. Des fonctionnalités telles que le système stationnement automatique vont au-delà des attentes des conducteurs ordinaires d'il y a seulement 10 ans. Les premiers prototypes des véhicules autonomes ont déjà été réalisés.

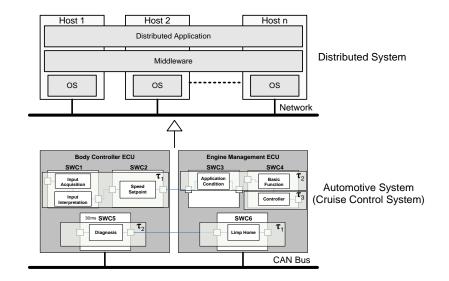

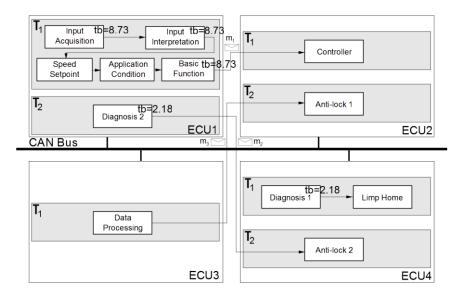

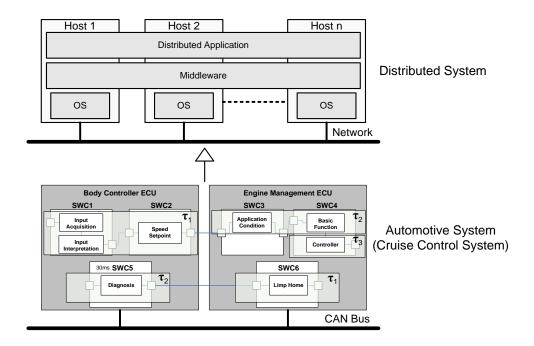

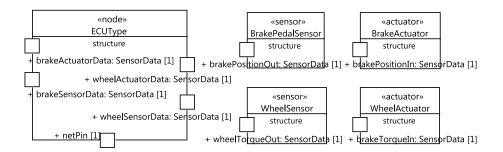

Les systèmes automobiles sont des systèmes distribués, embarqués et tems réel. Tout d'abord, les fonctionnalités logicielles des véhicules sont distribuées sur plusieurs composants matériels embarqués nommées unités de commande électronique (ang. ECU – Electronic Control Unit) ou sur des capteurs/actionneurs. La couche d'application qui s'étend sur des ECU différents est composée de composants logiciels qui peuvent être conçus et livrés par plusieurs fournisseurs. Le middleware est responsable de la communication entre les composants logiciels distribués. Chaque ECU exécute un système d'exploitation. Tout cela implique une nature distribuée des systèmes automobiles (voir la Figure 1). Deuxièmement leur fonctionnement est contraint par des contraintes de temps de différents types, par exemple des contraintes temporelles de bout-en-bout. Par exemple, l'ouverture de l'airbag en cas d'accident doit se produire dans les 20 ms. Cette dernière est une contrainte de temps réel, dont la violation non seulement affirme le comportement incorrect du système, mais plus important, peut mettre en danger la vie de personnes humaines.

Figure 1. Système Distribué et Système Distribué Automobile

Les architectures de systèmes automobiles (en raccourci architectures automobiles) sont des produits très complexes, de haute technologie. Différents facteurs contribuent à leur complexité:

- **Taille:** le nombre de fonctions contrôlées par le logiciel et le matériel est substantiel dans les véhicules d'aujourd'hui. En une trentaine d'années, la quantité de code est passée de 0 à près de 10 Go, ce qui représente des millions de lignes de code.

- Nature distribuée: les architectures automobiles d'aujourd'hui sont fortement distribuées, c.-à-d. les fonctions atomiques de la même fonctionnalités d'un véhicule sont distribuées sur plusieurs ECUs. Le même ECU peut accueillir des fonctions atomiques de différentes fonctionnalités du véhicule. Cela permet une meilleure optimisation de l'utilisation des ressources.

- Les contraintes temps réel: le fonctionnement correct d'un système de véhicule n'est pas seulement défini par l'absence d'erreurs fonctionnelles, mais aussi par strict respect des contraintes temps réel. Leur existence sert principalement dans les situations critiques pour la sécurité, comme le freinage ou pendant un accident lorsque les airbags doivent être activés immédiatement.

- Exigences de sécurité: l'aspect de la sécurité joue un rôle important car maintenant ce n'est pas seulement une préoccupation interne d'un OEM (ang.

Original Equipment Manufacturer) de fournir des véhicules fiables, mais aussi un sujet pour les réglementations gouvernementales.

- Exigences contradictoires: les différentes exigences comme les contraintes de temps, la réduction des ressources matérielles pour réduire les coûts, la sécurité, etc. sont dans de nombreux cas des exigences orthogonales. Cela signifie que la satisfaction d'une exigence peut conduire la dégradation des autres exigences.

- Sensible aux changements: de légers changements de conception ou certaines propriétés des éléments d'architecture peuvent conduire à une modification radicale des caractéristiques non-fonctionnelles d'architecture. Par exemple, l'augmentation d'un temps d'exécution d'une fonction atomique peut conduire à la violation de plusieurs contraintes de temps.

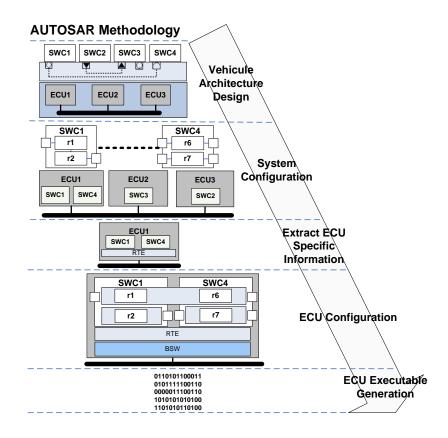

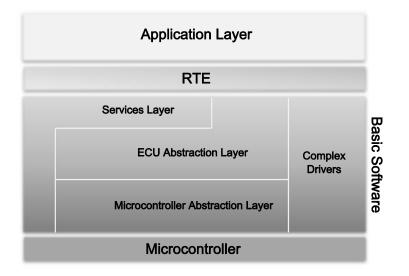

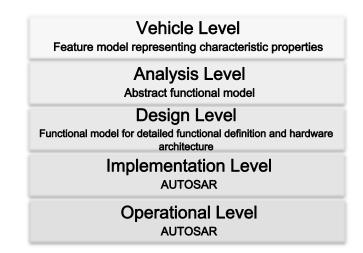

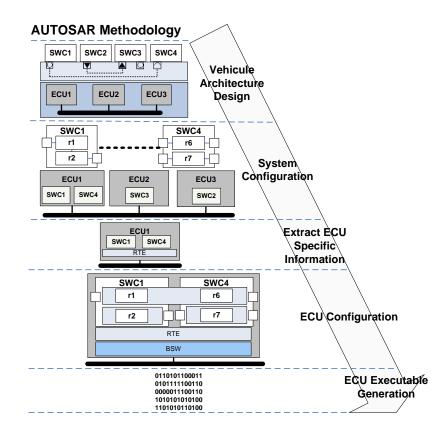

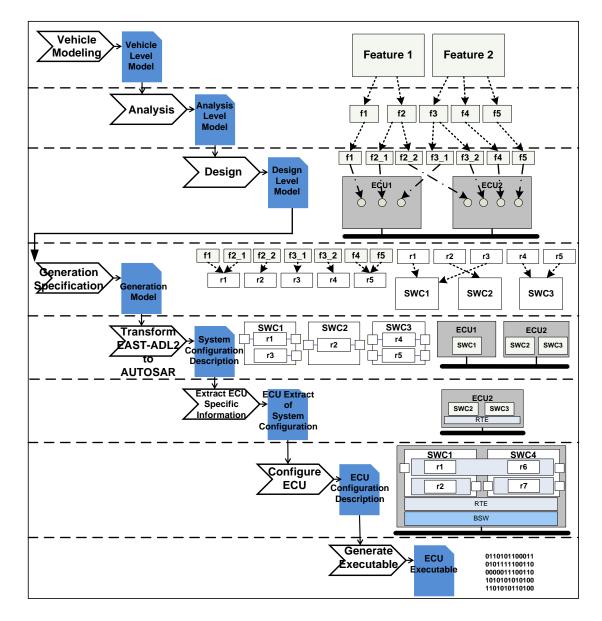

En raison de cette complexité qui a été et est encore en croissance exponentielle (prévue pour les 20 prochaines années), de nouvelles stratégies pour la conception des systèmes automobiles doivent être introduites. L'une d'entre elles est l'adoption de l'ingénierie dirigée par les modèles (IDM) pour le développement des systèmes automobiles. Le principe de l'approche IDM consiste à intégrer des modèles pour spécifier les exigences fonctionnelles et non fonctionnelles, et enfin, pour produire un code binaire qui respecte la spécification. Le potentiel de l'IDM a été identifié par les grands constructeurs automobiles et les fournisseurs qui ont initié un projet avec un objectif de fournir un standard commun fondé sur les principes de l'IDM. Ce projet appelé AUTOSAR (Automotive Open System Architecture) est actuellement le standard la plus influent en termes de modélisation des systèmes automobiles. La chaîne de développement de la méthodologie AUTOSAR (voir Figure 2) s'étend à partir de la représentation de composants logiciels d'application à l'infrastructure d'exécution, y compris la description de la plate-forme matérielle. Un inconvénient d'AUTOSAR est son manque de support pour la modélisation du niveau fonctionnel. Par conséquent, il y a un intérêt dans la combinaison de ce standard avec le langage de modélisation EAST-ADL2 qui prend en charge la spécification fonctionnelle.

Figure 2. AUTOSAR Méthodologie

EAST-ADL2 et AUTOSAR imposent des règles méthodologiques pour la construction de modèles. Leur avantage est qu'ils fournissent un cadre commun pour la conception de systèmes électroniques automobile. Toutefois, aucune de ces méthodologies ne définit comment effectuer certaines étapes de conception, par exemple, la façon de distribuer les composants logiciels sur les éléments matériels ou comment partitionner des entités fonctionnelles sur des tâches OS (ang. Operating System). À cet égard, ces deux standards comptent entièrement sur une expérience de concepteur, augmentant ainsi le potentiel nombre de défauts de conception. En conséquence, il est essentiel de procéder à une analyse comme, l'analyse temporelle ou l'analyse de sécurité pour assurer que les décisions prises par le concepteur n'a pas conduit à des architectures irréalisables. Nous pouvons aller encore plus loin et utiliser des techniques pour l'exploration de l'espace de conception (ang. DSE – Design Space Exploration). Leur emploi pourrait assurer la faisabilité, mais en plus permet d'optimiser les propriétés non-fonctionnelles clés.

#### 2. Énoncé du problème & motivation

Comme indiqué dans le paragraphe précédent, une vision claire et exhaustive d'une conception de système automobile, ainsi que son analyse / optimisation, sont les activités nécessaires pour rester compétitif sur le marché de l'automobile. Cela nécessite des langages de modélisation, de méthodes d'analyse et des techniques pour permettre le DSE. L'objectif général et initial de cette thèse est d'intégrer ces trois activités dans un cadre méthodologique, soutien de la conception des architectures automobiles et suivie par la méthodologie EAST-ADL2/AUTOSAR. Dans ce cadre, un ensemble de problèmes intéressants sont posés. La recherche de solutions appropriées est important pour rendre possible l'intégration de ces activités et la fourniture d'un flot continu guidé entre eux pour finalement produire un modèle d'implémentation optimisé d'un système automobile.

Disposer de différents types de modèles, c.-à-d. le modèle d'architecture, modèle d'analyse et modèle d'optimisation, est nécessaire pour effectuer une synthèse optimisée du logiciel avec le matériel. La phase principale de la synthèse est appelée déploiement. Selon AUTOSAR, le déploiement concerne 1) l'allocation des composants logiciels sur ECU 2) le partitionnement des entités du comportement du composant (appelées runnable entities) sur des OS tâches et enfin 3) l'ordonnancement des tâches OS. Un point crucial pour cette étape est sa validité en fonction de ses propriétés temporelles. Depuis le raffinement du système (dont le déploiement est une partie intégrante), la validité peut être assurée sous certaines hypothèses concernant des détails de niveau inférieur. Un exemple typique est l'hypothèse sur la connaissance des temps d'exécution pire cas (WCETs) des entités exécutables AUTOSAR. Il est évident que l'hypothèse de la connaissance précise des WCETs de runnables avant l'implémentation du code est la plupart du temps irréaliste. Dans de nombreux cas, certains runnables de systèmes précédents sont réutilisés. Le WCET de ces runnables est alors connu. Cependant, ce n'est pas le cas quand les nouveaux runnables implémentant de nouvelles fonctionnalités sont introduits. Cela représente un problème pour la synthèse de l'architecture et, en général, la fourniture d'un flot top-down. Ce qui est encore plus important est que le déploiement défini dans AUTOSAR n'est pas supporté de manière holistique par les techniques existantes. Bien que la quantité de travail qui existe semble être conséquente,

un fossé existe. Les techniques proposées soit représentent les tâches OS comme entités d'allocation ou résolvent le problème dans les étapes sans tenir compte d'un impact négatif qu'elle a sur les résultats finaux par rapport à l'approche holistique.

EAST-ADL2 et les spécifications AUTOSAR offrent un large éventail de concepts qui sont nécessaires pour définir l'architecture complète d'un système. Les efforts récents pour étendre ces standards ont fourni les capacités pour modéliser les informations nécessaires à l'analyse temporelle. Le travail adéquat n'a pas été fait jusqu'à présent pour gérer les optimisations. Bien que le domaine temps réel et des systèmes distribués est riche en techniques d'optimisation, il n'y a pas de concepts de modélisation qui permettraient de spécifier une entrée nécessaire pour cette activité tels que les objectifs d'optimisation (temps des réponses, la consommation de mémoire, etc.). En conséquence, la modélisation et l'analyse/l'optimisation ne sont pas bien intégrées. Cela a abouti à de nombreux outils décousus pour la modélisation ou l'analyse et/ou l'optimisation.

#### 3. Contributions

Afin de permettre de développement sans couture dans le cadre proposé, ce travail propose un ensemble de solutions aux problèmes mentionnés ci-dessus:

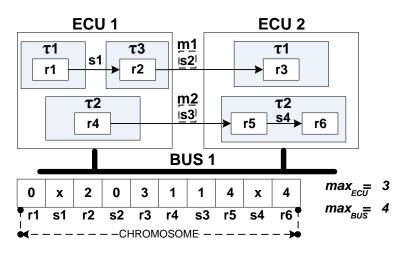

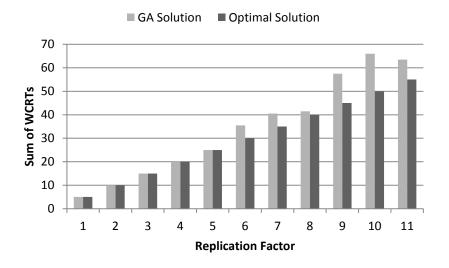

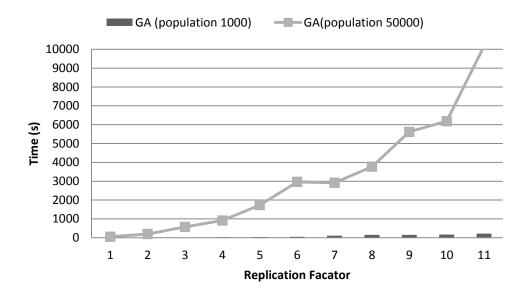

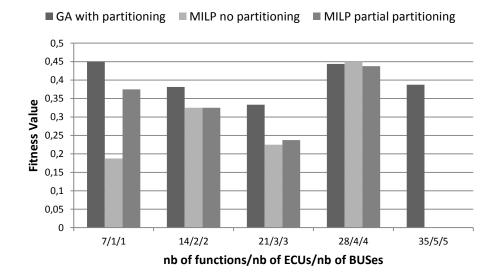

1) Concernant les techniques de DES les principales contributions portent sur la définition de nouvelles techniques pour optimiser le déploiement. Les techniques proposées sont conformes à la définition du déploiement comme inclus dans le standard AUTOSAR. C'est-à-dire, ils considèrent les runnable entities que les unités d'allocation. Par conséquent, l'étape de partitionnement qui n'est pas considérée par les approches existantes est supportée par la technique définie dans ce travail. Les techniques proposées sont basées sur des heuristiques, algorithmes évolutionnistes, diviser pour régner, amélioration itérative, c'est pourquoi ils sont capables de traiter de grandes architectures d'entrée. Cette caractéristique a été évaluée en effectuant plusieurs tests, atteignant 250 runnables. Un critère d'évaluation important a été la qualité des architectures déployées. Ceci a été réalisé en comparant les résultats à ceux obtenus avec les méthodes exactes ou des architectures pour lesquelles la configuration optimale de déploiement était connue a priori. Dans AUTOSAR, des modèles de comportement

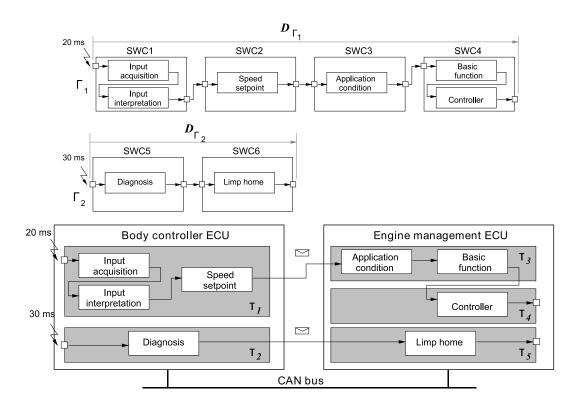

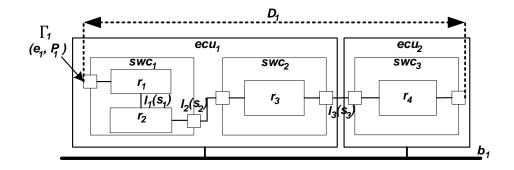

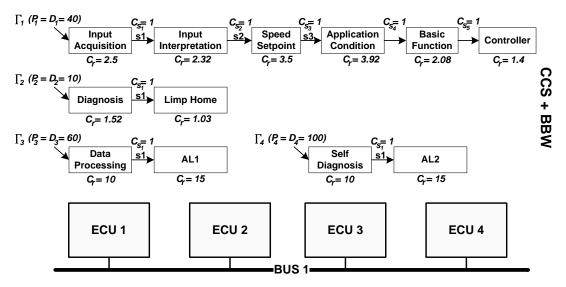

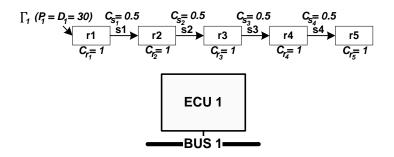

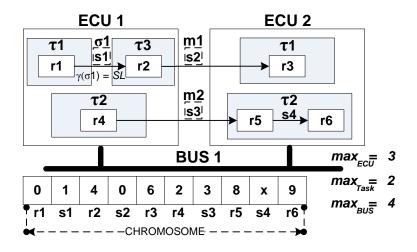

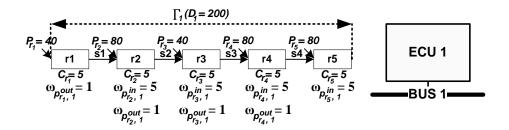

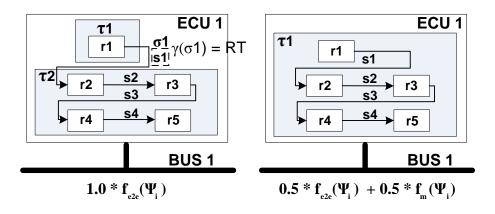

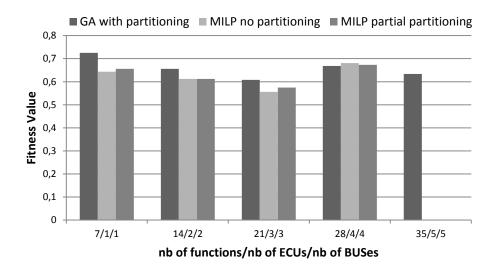

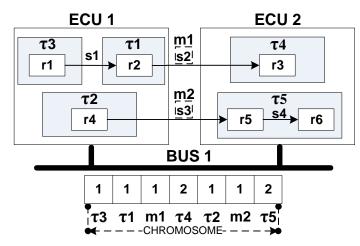

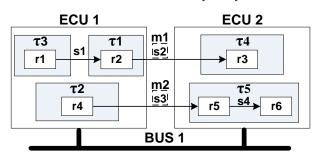

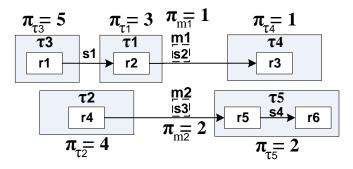

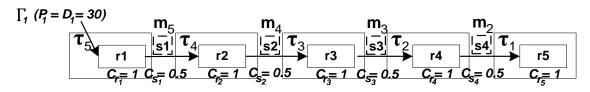

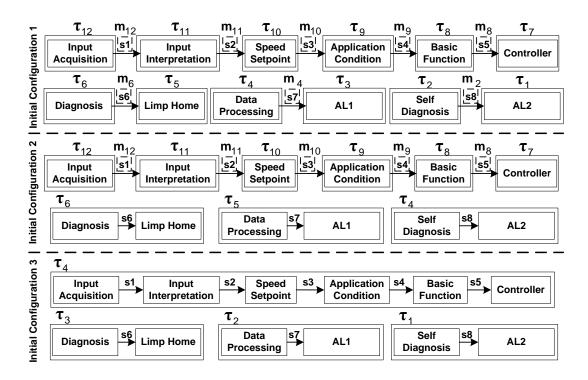

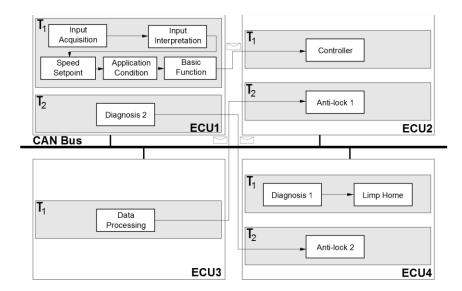

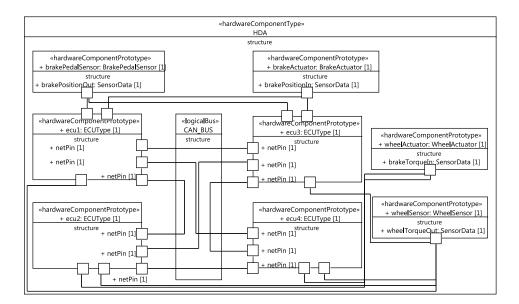

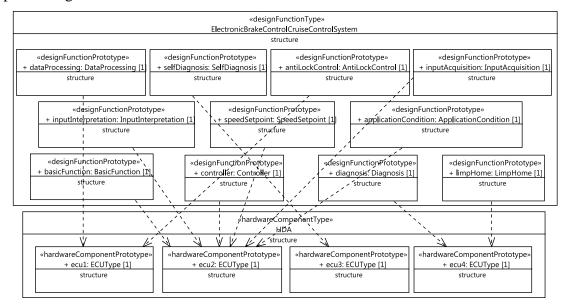

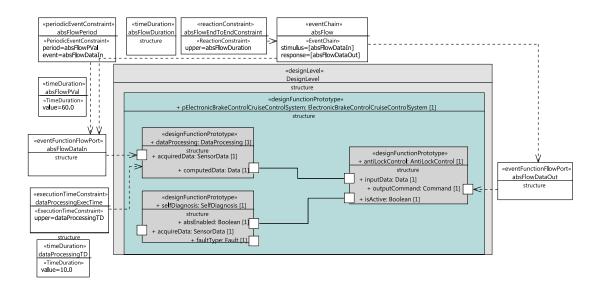

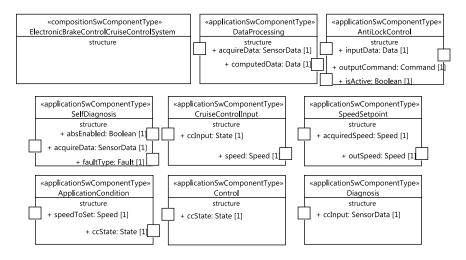

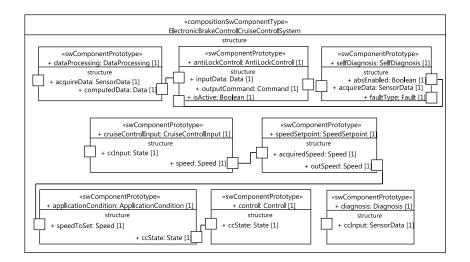

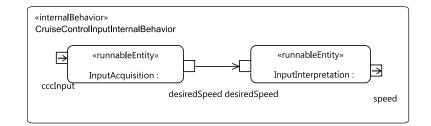

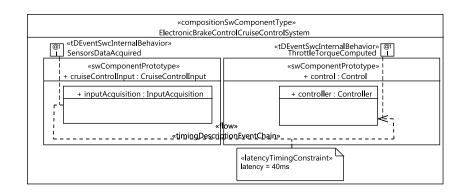

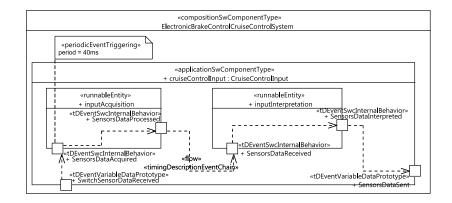

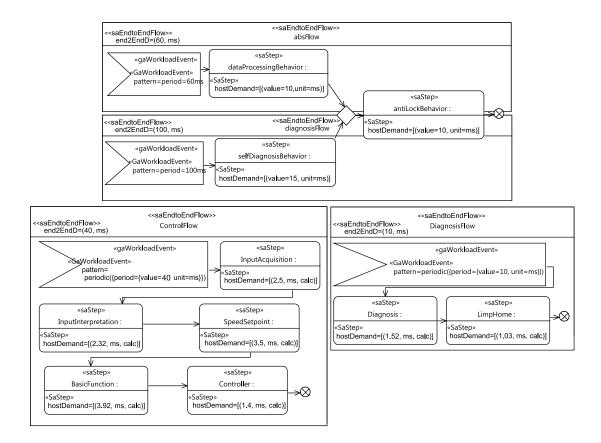

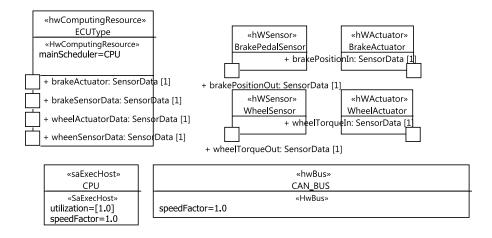

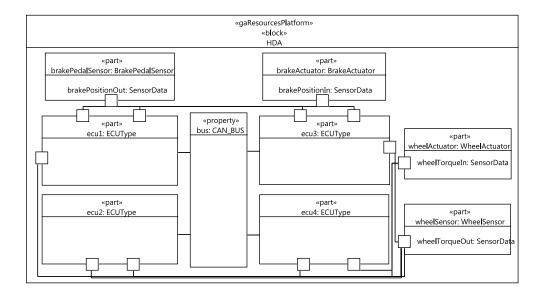

pourraient correspondre soit à une sémantique d'exécution data driven ou time driven. Cela nécessite de définir les différents types de stratégies d'optimisation. La différence se situe dans l'analyse d'ordonnançabilité. En outre, les métriques d'optimisation telles que les métriques temporelles, les métriques de mémoire sont affectées d'une manière différente par les choix particuliers d'un déploiement. Ce qui caractérise aussi les techniques proposées est la prise en compte de critères multiples (par exemple, les réponses de bout-en-bout, les propriétés temporelles, la consommation mémoire) qui définit une bonne configuration de déploiement de l'architecture d'entrée. La Figure 3 montre un exemple de l'architecture logicielle d'entrée (partie supérieure) et sa spécification de déploiement.

Figure 3. Exemple de l'architecture logicielle d'entrée (partie supérieure) et sa spécification de déploiement (partie basse)

2) Pour améliorer les résultats d'un déploiement, ce travail suggère un raffinement de la méthodologie EST-ADL2/AUTOSAR. Le but est de permettre de résoudre de manière holistique le problème de déploiement, ce qui n'est pas possible avec définition

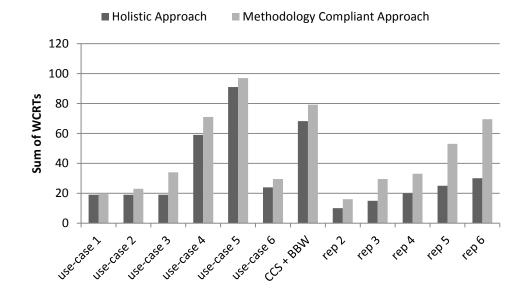

actuelle de cette méthodologie. Le changement concerne la répartition des responsabilités entre les deux niveaux, le niveau fonctionnel couvert par EST-ADL2 et le niveau implémentation couvert par AUTOSAR. L'activité *Design* qui se fait au niveau fonctionnel comprend l'étape d'allocation des fonctions atomiques aux ressources matérielles, c.-à-d. ECUs. Ceci détermine la répartition des runnable entities en raison de l'hypothèse dans laquelle les runnable entities sont transformés à partir des fonctions atomiques. C'est pourquoi le problème de déploiement ne peut pas être résolu d'une manière holistique au niveau AUTOSAR parce qu'une dimension du problème, c.-à-d. l'allocation est déjà fixée. Par conséquent, ce travail préconise le changement dans lequel l'allocation est reportée jusqu'au niveau d'implémentation. L'évaluation de ce changement montré une amélioration remarquable des caractéristiques de l'architecture.

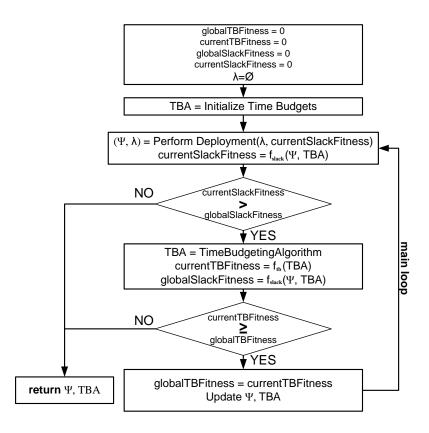

3) Pour effectuer un déploiement qui optimise les réponses de bout-en-bout, les temps d'exécution des runnable entities sont nécessaires. Comme cette information peutêtre manquante pour certains runnables, la définition d'une nouvelle stratégie pour la configuration de l'architecture est inévitable. Pour contourner le problème, certains travaux proposent d'ajouter à la méthodologie d'une activité appelée budgétisation de temps (ang. time budgeting). Au lieu d'estimer WCETs, l'intégrateur de système spécifie des budgets temporels (ang. time budgets), c'est à dire des contraintes à des temps de réponse pire cas - WCRTs (ang. Worst Case Execution Times). Les budgets temporels doivent être respectés par les fournisseurs livrant l'implémentation des composants. Le problème typique de cette approche est que le fournisseur livre l'implémentation d'un composant particulier, qui sera intégrée par l'intégrateur en tant que partie intégrante du système, dans une étape ultérieure. Entre temps, le fournisseur valide le composant en isolation, sans tenir compte d'éventuelles interférences avec d'autres composants. Il est alors incapable de calculer un temps de réponse pire cas (WCRT) correct. C'est-à-dire si le composant répond à la contrainte du budget temporel l'intégrateur du système doit prendre soin d'éviter toute interférence possible avec d'autres composants. Ce n'est pas seulement une tâche difficile, mais qui provoque généralement un surdimensionnement des ressources. Ce surdimensionnement des ressources peut représenter des coûts insoutenables pour une production en série. Une solution alternative est celle dans laquelle les budgets temporels représentent des contraintes de WCET de runnable entity

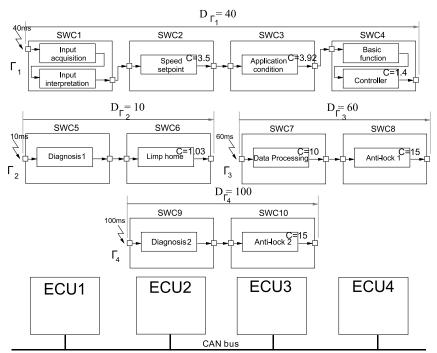

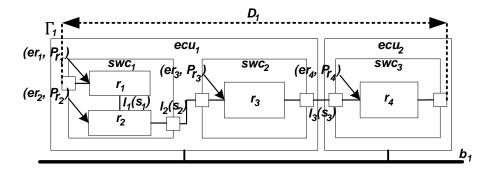

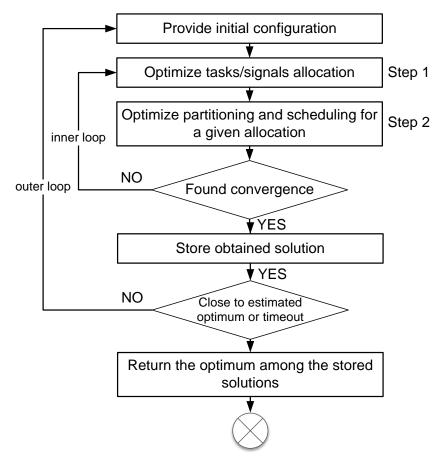

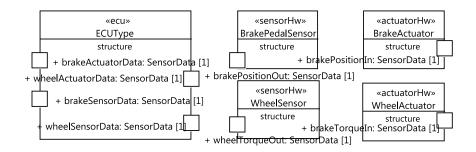

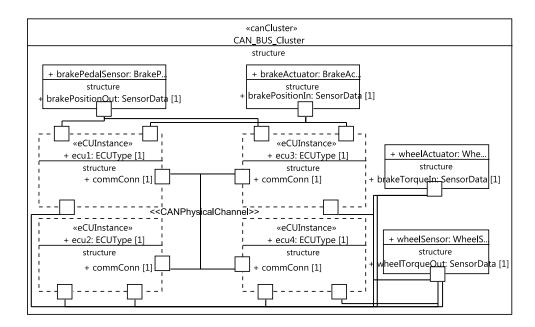

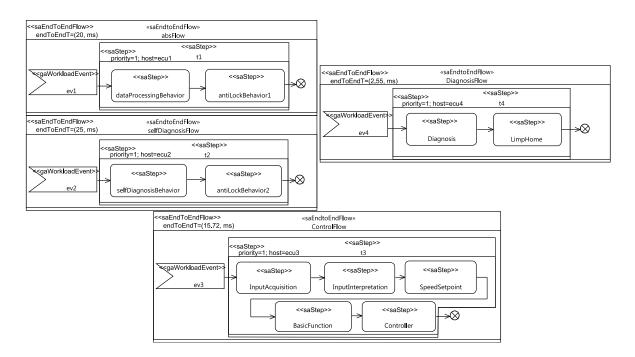

à la place de son WCRT. Ce travail propose une solution de budgétisation des WCETs. La plupart des travaux existants sur budget de WCRT ne pas bien adaptés à l'idée de « l'architecture intégré » proposée par AUTOSAR. Un autre avantage de la technique proposée dans ce travail par rapport aux approches existantes est l'hypothèse que le déploiement n'est pas connu à l'avance. En conséquence, un objectif de la technique proposée est de trouver conjointement le déploiement et l'affectation optimale des budgets temporels. La Figure 4 illustre une architecture logicielle d'entrée et une architecture matérielle pour lesquelles le déploiement ainsi que les budgets de temporels doit être spécifié. En fait, les budgets temporels doivent être définis pour ces runnable entities pour lesquels les informations sur le WCET n'est pas présent. La Figure 5 présente le résultat de la technique proposée, c.-à-d. l'architecture déployée ainsi que les budgets temporels.

Figure 4. L'architecture Logicielle et Matérielle avec certains Runnables qui manquent WCETs

Figure 5. Résultant Déploiement avec la Spécification des Budgets Temps

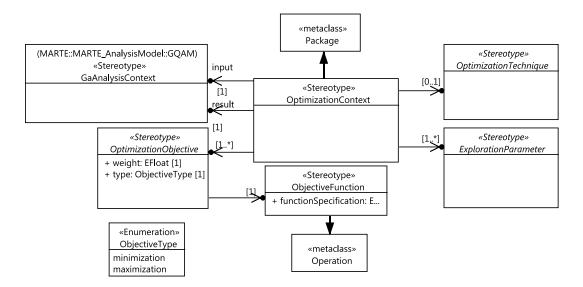

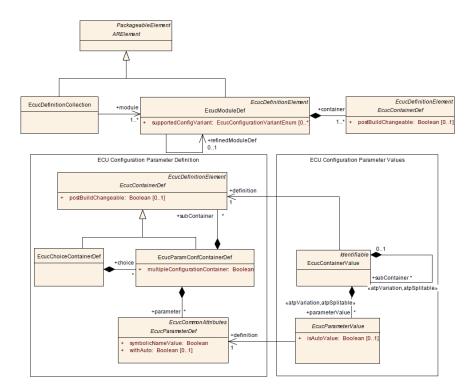

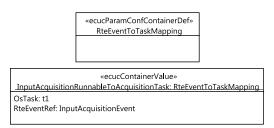

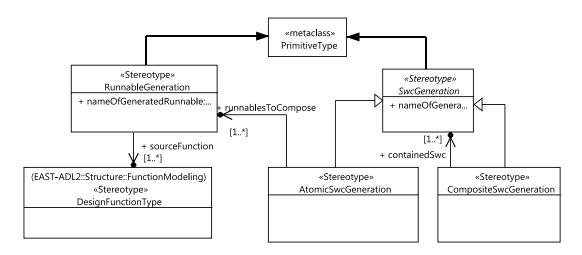

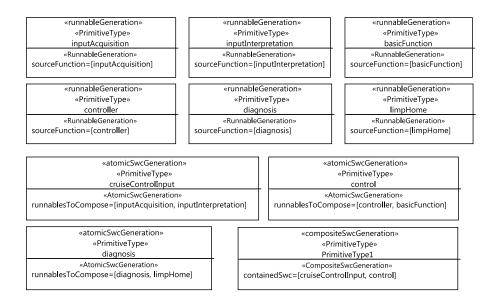

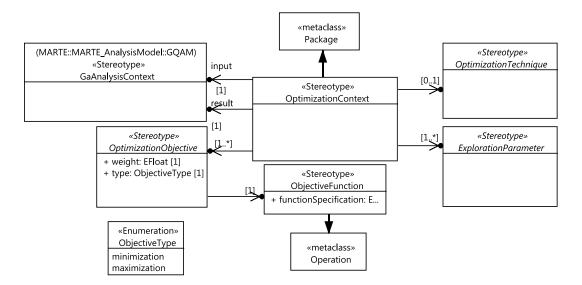

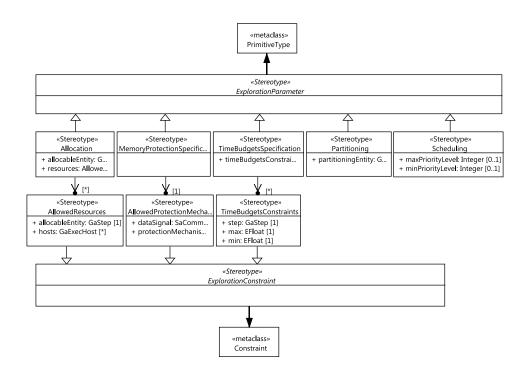

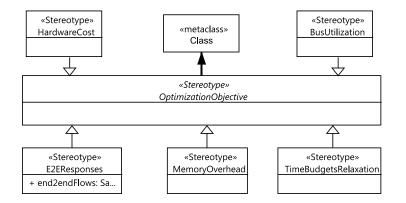

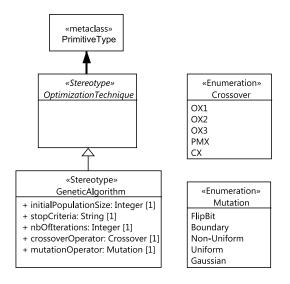

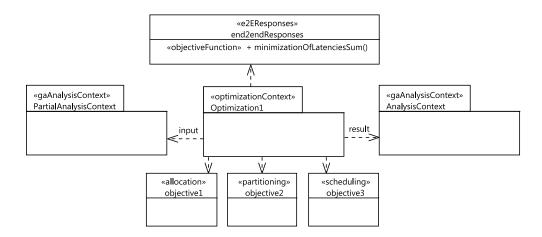

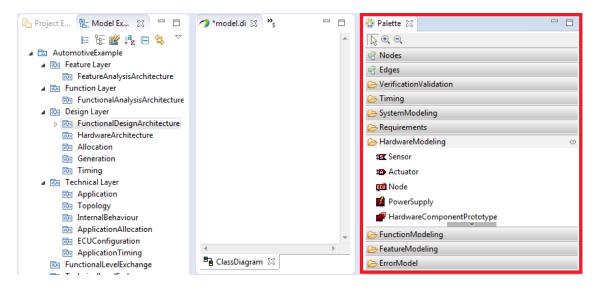

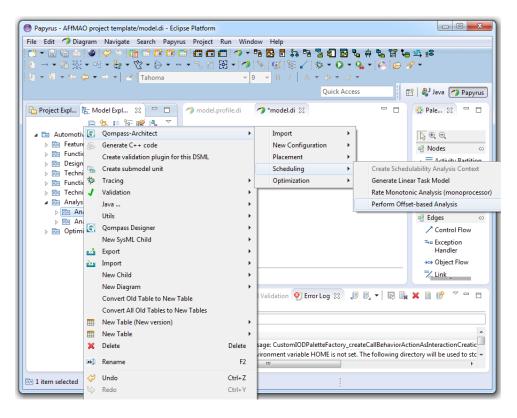

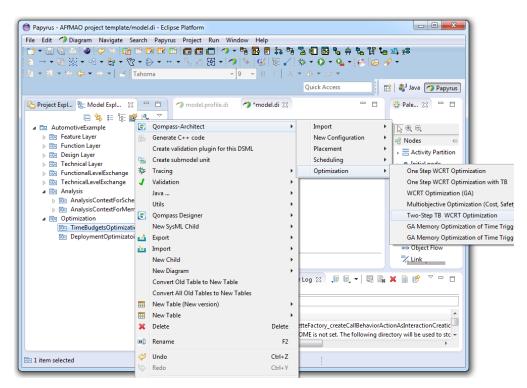

4) En ce qui concerne la modélisation de la première contribution, une spécification de concepts essentiels pour construire un modèle d'optimisation et pour exécuter des techniques DES telles que celles définies dans ce travail, servant pour le déploiement ou budgétisation de temps, a été réalisée. La Figure 6 représente une partie du profil UML définissant les principaux concepts permettant de construire un contexte d'optimisation. Au-dessus du modèle d'optimisation, des techniques d'optimisation peuvent être exécutés.

Figure 6. UML Profile pour le contexte d'optimisation

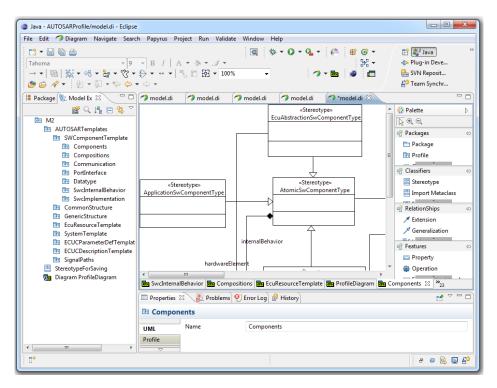

5) Les modèles d'optimisation ainsi que des modèles pour l'analyse et la spécification de l'architecture sont basés sur UML. L'utilisation de l'UML permet de faciliter l'intégration des différentes activités. Ceci est obtenu en majeure partie par l'ensemble des transformations qui automatisent des étapes importantes telles que la production du modèle AUTOSAR préliminaire à partir du modèle EAST-ADL2. En fait, la spécification d'architecture basée sur les concepts de EAST-ADL2 et AUTOSAR est réalisée dans ce travail par un mécanisme de profil UML. Le profil UML complet pour l'EST-ADL2 était disponible. Ce n'était pas le cas pour AUTOSAR et donc ce travail en définit un. Les modèles d'analyse sont établis avec SysML et MARTE pour lesquels les profils UML ont été définis et standardisés par l'OMG (Object Management Group). Les concepts pour l'optimisation ne peuvent pas être exprimés ni avec SysML, ni MARTE ainsi qu'EST-ADL2 et AUTOSAR. En conséquence, pour eux, un modèle de domaine est formalisé et son profil UML est défini comme susmentionné dans le cadre de la contribution 4.

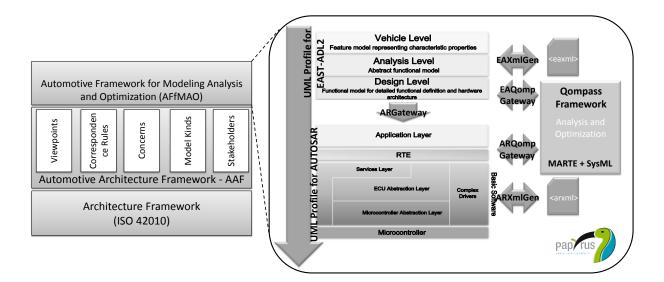

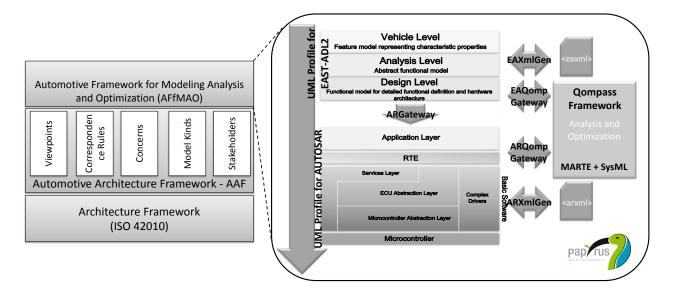

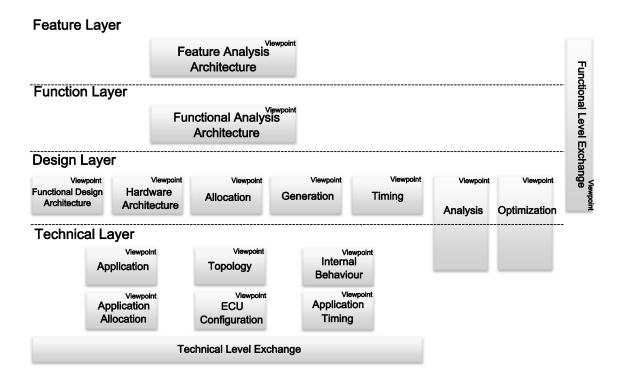

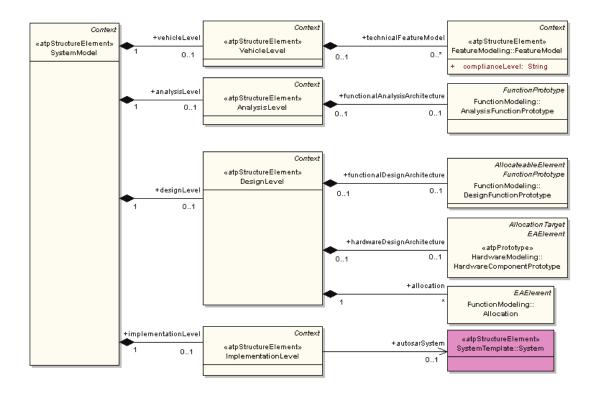

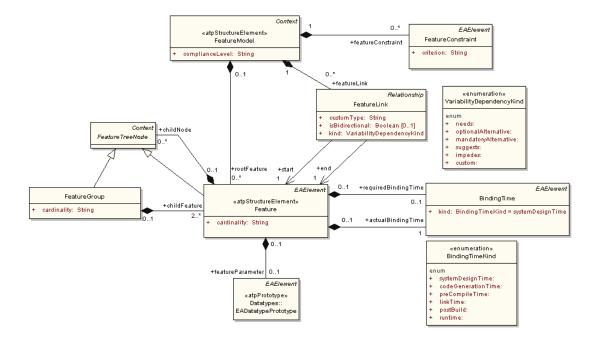

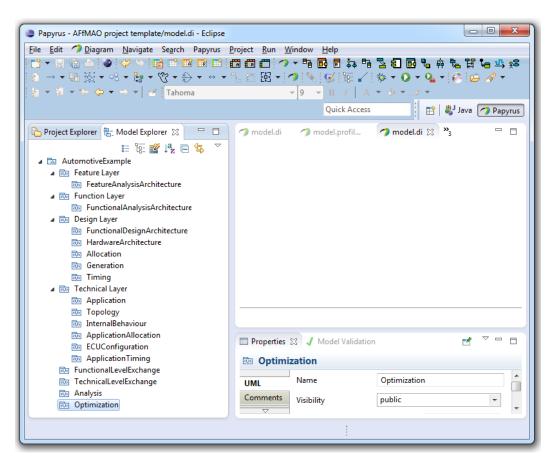

Tous ces modèles, modèles d'architecture, d'analyse et d'optimisation avec des algorithmes d'analyse et d'optimisation peuvent être exécutés et ont été intégrés dans un cadre et structurés le long de couches d'abstraction et de points de vue. Le cadre luimême (appelé AFfMAO – Architecture Framework for Modeling Analysis and Optimization) a été développé comme une instance d'un Cadre d'Architecture de l'Automobile (ang. Automotive Architecture Framework - AAF) définie dans ce travail. AAF a été construit en suivant les principes du Cadre Architectural (ang. Architecture Framework - AF) définie dans la norme ISO 42010. Cette relation est représentée sur la partie gauche de la Figure 7. En substance, le cadre d'architecture est un ensemble de conventions, principes et pratiques pour la description des architectures dans un domaine et/ou communauté des parties prenantes. Par conséquent la spécification de l'AAF a été faite en définissant des points de vue de l'architecture avec leurs préoccupations, sortes de modèles et de règles de correspondance. Le côté droit de la Figure 7 présente la perspective détaillée de AFfMAO. Les informations pertinentes à partir de cette figure concernent les choix des techniques de modélisation, un ensemble de transformations, des algorithmes d'analyse et d'optimisation et plate-forme utilisée pour réaliser l'AAF comme AFfMAO.

Figure 7. AFfMAO construit comme une instance de l'AAF

Les contributions de cette thèse apportent des solutions pour résoudre les problèmes cruciaux qui entravent la livraison d'un cadre pour une conception guidée des systèmes automobiles, alignés sur les principes de l'ingénierie dirigée par les modèles. Ils sont bénéfiques non seulement dans le contexte de ce cadre particulier, mais en général à ces constructeurs qui tentent de s'engager dans l'utilisation des standards EAST-ADL2 et AUTOSAR comme base de conception de leurs systèmes.

### TABLE OF CONTENTS

| 1. lı       | ntroduction                                                      | 30 |

|-------------|------------------------------------------------------------------|----|

| 1.1.        | Context                                                          | 30 |

| 1.2.        | Problem Statement & Motivation                                   | 33 |

| 1.3.        | Contribution outlines                                            | 35 |

| 1.4.        | Thesis Structure                                                 | 37 |

| 2. A        | utomotive Context                                                | 39 |

| 2.1.        | Automotive System                                                | 39 |

| 2.2.        | Model Driven Engineering                                         | 45 |

| 2.3.        | Architecture Framework                                           | 46 |

| 2.4.        | Automotive Standards                                             | 47 |

| 2.4         | .1. AUTOSAR                                                      | 47 |

| 2.4         | .2. EAST-ADL2                                                    | 49 |

| 2.5.        | Methodology of Design (EAST-ADL2/AUTOSAR Methodology)            | 50 |

| <i>3. C</i> | hallenges                                                        | 56 |

| 3.1.        | General Challenges                                               | 56 |

| 3.2.        | Configuration of Automotive Architectures                        | 58 |

| 3.3.        | Architecture Description Specification                           | 60 |

| 3.4.        | Conclusions                                                      | 61 |

| 4. A        | pproaches for the Computer-aided Configuration of the Automotive |    |

| Architectu  | 'es                                                              | 62 |

| 4.1.        | Formalism                                                        | 62 |

| 4.1         |                                                                  |    |

| 4.1         |                                                                  |    |

| 4.2.        | Schedulability Analysis                                          | 68 |

| 4.2        | 2.1.  | Schedulability Analysis for DD                        | 68  |

|------------|-------|-------------------------------------------------------|-----|

| 4.2        | 2.2.  | Schedulability Analysis for TD                        | 70  |

| 4.3.       | Re    | finement of the EAST-ADL2/AUTOSAR Methodology         | 72  |

| 4.4.       | De    | ployment                                              | 73  |

| 4.4        | 4.1.  | Formalization of Deployment                           | 73  |

| 4.4        | 4.2.  | Related Work                                          |     |

| 4.4        | 4.3.  | Technique for Optimized Deployment of DD              | 83  |

| 4.4        | 4.4.  | Evaluation & Conclusions                              | 88  |

| 4.4        | 4.5.  | Technique for Optimized Deployment of TD              | 95  |

| 4.4        | 4.6.  | Evaluation & Conclusions                              | 97  |

| 4.5.       | Tw    | o-Step Approach                                       | 104 |

| 4.5        | 5.1.  | GA Formulation for the Two-Step Approach              | 105 |

| 4.5        | 5.2.  | Establishment of the Global Order                     | 108 |

| 4.5        | 5.3.  | Evaluation & Conclusions                              | 110 |

| 4.6.       | Eva   | aluation of the new Methodology                       | 115 |

| 4.6        | 6.1.  | Allocation at the EAST-ADL2 Level                     | 116 |

| 4.6        | 6.2.  | Partitioning and Scheduling at the AUTOSAR level      | 117 |

| 4.0        | 6.3.  | Evaluation & Conclusions                              | 117 |

| 4.7.       | Tin   | ne Budgets Assignment                                 | 119 |

| 4.7        | 7.1.  | Formalism                                             | 120 |

| 4.7        | 7.2.  | Related Work                                          | 121 |

| 4.7        | 7.3.  | Method for Time Budgeting                             | 123 |

| 4.7        | 7.4.  | Evaluation & Conclusions                              | 131 |

| 4.8.       | Со    | nclusions                                             | 139 |

| 5. U       | JML   | based & Optimization-aware modeling of the Automotive |     |

| Architectu | res - |                                                       | 140 |

| 5.1.       | Re    | ated Work                                             | 141 |

| 5.3        | 1.1.  | Commercial Tooling                                    | 141 |

| 5.3        | 1.2.  | Academia Tooling                                      |     |

| 5.:        | 1.3.  | Automotive Architecture Framework                     | 143 |

| 5.2        | 1.4.  | Related Work Conclusions                              | 146 |

| 5.2.    | Aut  | tomotive Framework for Modeling Analysis and Optimization | 147 |

|---------|------|-----------------------------------------------------------|-----|

| 5.3.    | Vie  | wpoints                                                   | 149 |

| 5.3     | .1.  | Feature, Functional and Design Level Viewpoints           | 152 |

| 5.3     | .2.  | Technical Level Viewpoints                                | 160 |

| 5.3     | .3.  | Generation Viewpoint                                      | 169 |

| 5.3     | .4.  | Analysis Viewpoint                                        | 172 |

| 5.3     | .5.  | Optimization Viewpoint                                    | 177 |

| 5.4.    | Inte | eroperability Viewpoints                                  | 183 |

| 5.5.    | Cor  | rrespondence Rules                                        | 184 |

| 5.5     | .1.  | EAST-ADL2 and AUTOSAR                                     | 184 |

| 5.5     | .2.  | EAST-ADL2 and Analyzable Model                            | 185 |

| 5.5     | .3.  | AUTOSAR and Analyzable Model                              | 186 |

| 5.6.    | Cor  | nclusions                                                 | 187 |

| 5. C    | oncl | lusion                                                    | 188 |

| 6.1.    | Sur  | nmary                                                     | 188 |

| 6.2.    | Fut  | ure Work                                                  | 190 |

| Referer | nces |                                                           | 192 |

| \ppend  | dix  |                                                           | 201 |

| Α.      | Тос  | ol Prototype                                              | 201 |

| в.      | AA   | F Revisited                                               | 208 |

### LIST OF FIGURES

| Figure 1. Système Distribué et Système Distribué Automobile x                          |

|----------------------------------------------------------------------------------------|

| Figure 2. AUTOSAR Méthodologiexii                                                      |

| Figure 3. Exemple de l'architecture logicielle d'entrée (partie supérieure) et sa      |

| spécification de déploiement (partie basse)xv                                          |

| Figure 4. L'architecture Logicielle et Matérielle avec certains Runnables qui manquent |

| WCETsxvii                                                                              |

| Figure 5. Résultant Déploiement avec la Spécification des Budgets Tempsxviii           |

| Figure 6. UML Profile pour le contexte d'optimisationxix                               |

| Figure 7. AFfMAO construit comme une instance de l'AAF xx                              |

| Figure 1.1. Distributed System and Automotive Distributed System                       |

| Figure 2.1. Conceptual Model of Architecture Description and Architecture Framework.   |

|                                                                                        |

| Figure 2.2. AUTOSAR Architecture Layers Schema                                         |

| Figure 2.3. EAST-ADL2 Abstraction Layers                                               |

| Figure 2.4. AUTOSAR Methodology                                                        |

| Figure 2.5. EAST-ADL2/AUTOSAR Methodology                                              |

| Figure 4.1. Data Driven Activation Model                                               |

| Figure 4.2. Time Driven Activation Model                                               |

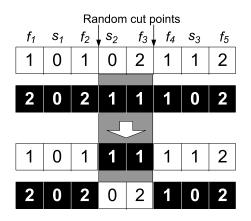

| Figure 4.3. Example of a Chromosome for a Specific Deployment Configuration 85         |

| Figure 4.4. OX3 Crossover Operator                                                     |

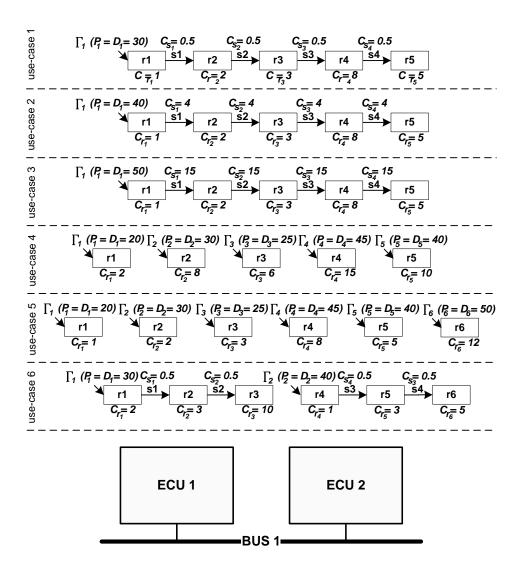

| Figure 4.5. Simple Use-Cases                                                           |

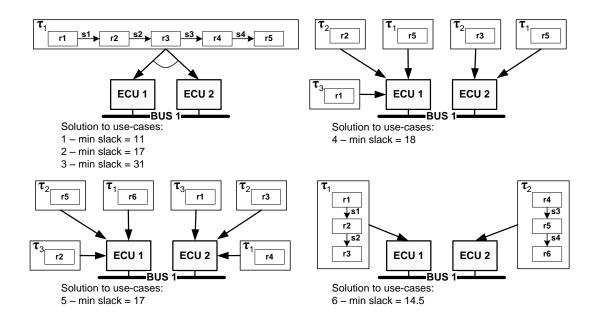

| Figure 4.6. Solutions for the Simple Use-Cases obtained with the Metric 4.1391         |

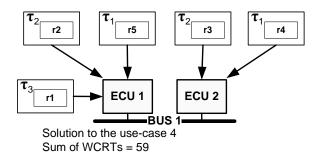

| Figure 4.7. Solution for the Simple Use-Case nr 4 obtained with the Metric 4.1291      |

| Figure 4.8. CCS + ABS System                                                           |

| Figure 4.9. Non-replicated Use-Case                                                    |

| Figure 4.10. Comparison of the Optimal Solution with the Solution obtained with the    |

| GA94                                                                                   |

| Figure 4.11. Runtimes for the GA with Different Initial Population                     |

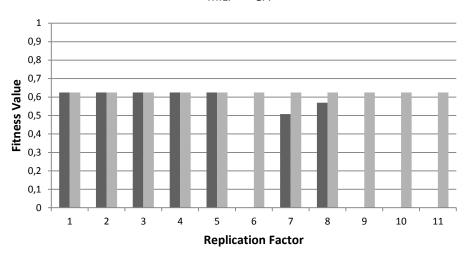

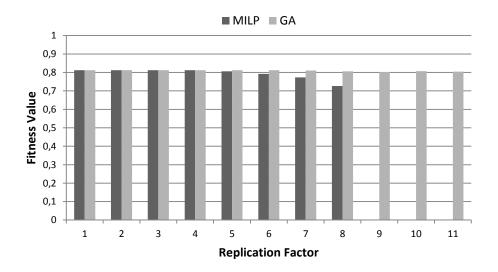

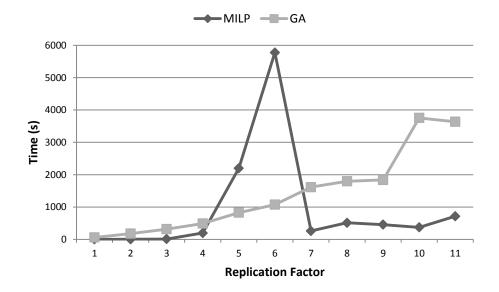

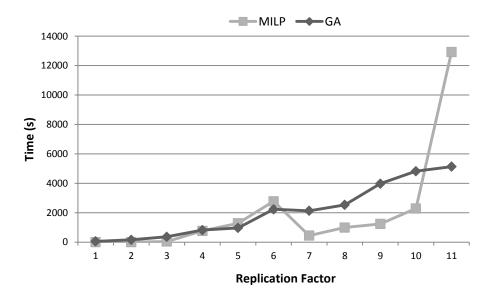

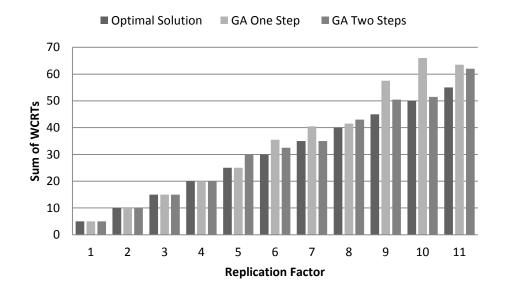

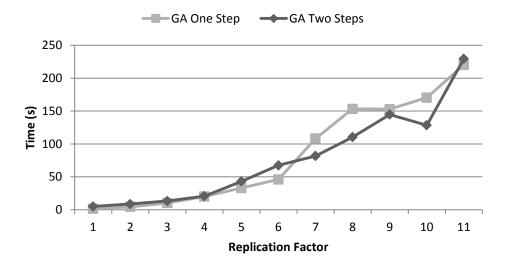

| Context of the TD.97Figure 4.13. Non-replicated Use-Case with TD Semantics99Figure 4.14. Optimal Configurations for Non-replicated Use-Case99Figure 4.15. Results for MILP and GA $(1.0 * fe2e(\Psi i))$ 100Figure 4.16. Results for MILP and GA $(0.5 * fe2e\Psi i + 0.5 * fm\Psi i)$ 100Figure 4.17. Runtime for MILP and GA $(1.0 * fe2e(\Psi i))$ 101Figure 4.18. Runtime for MILP and GA $(0.5 * fe2e\Psi i + 0.5 * fm\Psi i)$ 102Figure 4.19. Comparison using Fitness Function $(1.0 * fe2e(\Psi i))$ 103Figure 4.20. Comparison using Fitness Function $(0.5 * fe2e\Psi i + 0.5 * fm\Psi i)$ 103Figure 4.21. The Two-Steps Deployment Approach (TSDA)105Figure 4.22. Example of a Chromosome for a particular Allocation Configuration 106Figure 4.23. Example of the Input Configuration109Figure 4.24. Example of the Input Configuration109Figure 4.25. Global Order for the Example of the Figure 4.24109Figure 4.26. Initial Configuration for the Simple Use-Case111Figure 4.28. Runtimes of the OS-GA and the TSDA-GA113Figure 4.29. Initial Configurations for the ABS + CCS114Figure 4.30. Comparison between the results of the MCDT and the Holistic Approach118Figure 4.31. Iterative Improvement Loop for the Staged Approach129 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.14. Optimal Configurations for Non-replicated Use-Case99Figure 4.15. Results for MILP and GA ( $1.0 * fe2e(\Psi i)$ )100Figure 4.16. Results for MILP and GA ( $0.5 * fe2e\Psi i + 0.5 * fm\Psi i$ )100Figure 4.17. Runtime for MILP and GA ( $1.0 * fe2e(\Psi i)$ )101Figure 4.18. Runtime for MILP and GA ( $0.5 * fe2e\Psi i + 0.5 * fm\Psi i$ )102Figure 4.19. Comparison using Fitness Function ( $1.0 * fe2e(\Psi i)$ )103Figure 4.20. Comparison using Fitness Function ( $0.5 * fe2e\Psi i + 0.5 * fm\Psi i$ )103Figure 4.21. The Two-Steps Deployment Approach (TSDA)105Figure 4.22. Example of a Chromosome for a particular Allocation Configuration108Figure 4.23. Example of the Input Configuration109Figure 4.24. Example of the Input Configuration109Figure 4.25. Global Order for the Example of the Figure 4.24.109Figure 4.27. Comparison of the Two Steps Approach with the Holistic Approach and the<br>Optimal Solution112Figure 4.28. Runtimes of the OS-GA and the TSDA-GA113Figure 4.30. Comparison between the results of the MCDT and the Holistic Approach118                                                                                                                                                   |

| Figure 4.15. Results for MILP and GA $(1.0 * fe2e(\Psi i))$ 100Figure 4.16. Results for MILP and GA $(0.5 * fe2e\Psi i + 0.5 * fm\Psi i)$ 100Figure 4.17. Runtime for MILP and GA $(0.5 * fe2e\Psi i + 0.5 * fm\Psi i)$ 101Figure 4.18. Runtime for MILP and GA $(0.5 * fe2e\Psi i + 0.5 * fm\Psi i)$ 102Figure 4.19. Comparison using Fitness Function $(1.0 * fe2e(\Psi i))$ 103Figure 4.20. Comparison using Fitness Function $(0.5 * fe2e\Psi i + 0.5 * fm\Psi i)$ 103Figure 4.21. The Two-Steps Deployment Approach (TSDA)105Figure 4.22. Example of a Chromosome for a particular Allocation Configuration106Figure 4.23. Example of the Input Configuration108Figure 4.24. Example of the Input Configuration109Figure 4.25. Global Order for the Example of the Figure 4.24.109Figure 4.26. Initial Configuration for the Simple Use-Case111Figure 4.27. Comparison of the Two Steps Approach with the Holistic Approach and the Optimal Solution112Figure 4.28. Runtimes of the OS-GA and the TSDA-GA113Figure 4.30. Comparison between the results of the MCDT and the Holistic Approach118                                                                                                                                                 |

| Figure 4.16. Results for MILP and GA ( $0.5 * fe2e\Psi i + 0.5 * fm\Psi i$ )100Figure 4.17. Runtime for MILP and GA ( $1.0 * fe2e(\Psi i)$ )101Figure 4.18. Runtime for MILP and GA ( $0.5 * fe2e\Psi i + 0.5 * fm\Psi i$ )102Figure 4.19. Comparison using Fitness Function ( $1.0 * fe2e(\Psi i)$ )103Figure 4.20. Comparison using Fitness Function ( $0.5 * fe2e\Psi i + 0.5 * fm\Psi i$ )103Figure 4.21. The Two-Steps Deployment Approach (TSDA)105Figure 4.22. Example of a Chromosome for a particular Allocation Configuration106Figure 4.23. Example of the Input Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 4.17. Runtime for MILP and GA $(1.0 * fe2e(\Psi i))$ 101Figure 4.18. Runtime for MILP and GA $(0.5 * fe2e\Psi i + 0.5 * fm\Psi i)$ 102Figure 4.19. Comparison using Fitness Function $(1.0 * fe2e(\Psi i))$ 103Figure 4.20. Comparison using Fitness Function $(0.5 * fe2e\Psi i + 0.5 * fm\Psi i)$ 103Figure 4.21. The Two-Steps Deployment Approach (TSDA)105Figure 4.22. Example of a Chromosome for a particular Allocation Configuration 106108Figure 4.23. Example chromosome for the Partitioning and Scheduling Configuration108Figure 4.24. Example of the Input Configuration109Figure 4.25. Global Order for the Example of the Figure 4.24109Figure 4.26. Initial Configuration for the Simple Use-Case111Figure 4.27. Comparison of the Two Steps Approach with the Holistic Approach and the Optimal Solution112Figure 4.28. Runtimes of the OS-GA and the TSDA-GA113Figure 4.30. Comparison between the results of the MCDT and the Holistic Approach118                                                                                                                                                                                                                                                                        |

| Figure 4.18. Runtime for MILP and GA ( $0.5 * fe2e\Psi i + 0.5 * fm\Psi i$ )102Figure 4.19. Comparison using Fitness Function ( $1.0 * fe2e(\Psi i)$ )103Figure 4.20. Comparison using Fitness Function ( $0.5 * fe2e\Psi i + 0.5 * fm\Psi i$ )103Figure 4.21. The Two-Steps Deployment Approach (TSDA)105Figure 4.22. Example of a Chromosome for a particular Allocation Configuration 106108Figure 4.23. Example chromosome for the Partitioning and Scheduling Configuration108Figure 4.24. Example of the Input Configuration109Figure 4.25. Global Order for the Example of the Figure 4.24.109Figure 4.26. Initial Configuration for the Simple Use-Case111Figure 4.27. Comparison of the Two Steps Approach with the Holistic Approach and the Optimal Solution112Figure 4.28. Runtimes of the OS-GA and the TSDA-GA113Figure 4.30. Comparison between the results of the MCDT and the Holistic Approach118                                                                                                                                                                                                                                                                                                                                   |

| Figure 4.19. Comparison using Fitness Function $(1.0 * fe2e(\Psi i))$ 103Figure 4.20. Comparison using Fitness Function $(0.5 * fe2e\Psi i + 0.5 * fm\Psi i)$ . 103Figure 4.21. The Two-Steps Deployment Approach (TSDA)105Figure 4.22. Example of a Chromosome for a particular Allocation Configuration 106Figure 4.23. Example chromosome for the Partitioning and Scheduling Configuration108Figure 4.24. Example of the Input Configuration109Figure 4.25. Global Order for the Example of the Figure 4.24.109Figure 4.26. Initial Configuration for the Simple Use-Case111Figure 4.27. Comparison of the Two Steps Approach with the Holistic Approach and the<br>Optimal Solution112Figure 4.28. Runtimes of the OS-GA and the TSDA-GA113Figure 4.29. Initial Configurations for the ABS + CCS114Figure 4.30. Comparison between the results of the MCDT and the Holistic Approach118                                                                                                                                                                                                                                                                                                                                                          |

| Figure 4.20. Comparison using Fitness Function ( $0.5 * fe2e\Psi i + 0.5 * fm\Psi i$ ). 103Figure 4.21. The Two-Steps Deployment Approach (TSDA)105Figure 4.22. Example of a Chromosome for a particular Allocation Configuration 106Figure 4.23. Example chromosome for the Partitioning and Scheduling Configuration108Figure 4.24. Example of the Input Configuration109Figure 4.25. Global Order for the Example of the Figure 4.24.109Figure 4.26. Initial Configuration for the Simple Use-Case111Figure 4.27. Comparison of the Two Steps Approach with the Holistic Approach and the<br>Optimal Solution112Figure 4.28. Runtimes of the OS-GA and the TSDA-GA113Figure 4.30. Comparison between the results of the MCDT and the Holistic Approach118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 4.21. The Two-Steps Deployment Approach (TSDA)       105         Figure 4.22. Example of a Chromosome for a particular Allocation Configuration 106       108         Figure 4.23. Example chromosome for the Partitioning and Scheduling Configuration 108       108         Figure 4.24. Example of the Input Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 4.22. Example of a Chromosome for a particular Allocation Configuration 106         Figure 4.23. Example chromosome for the Partitioning and Scheduling Configuration 108         Figure 4.24. Example of the Input Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 4.23. Example chromosome for the Partitioning and Scheduling Configuration       108         Figure 4.24. Example of the Input Configuration       109         Figure 4.25. Global Order for the Example of the Figure 4.24.       109         Figure 4.26. Initial Configuration for the Simple Use-Case       111         Figure 4.27. Comparison of the Two Steps Approach with the Holistic Approach and the Optimal Solution       112         Figure 4.28. Runtimes of the OS-GA and the TSDA-GA       113         Figure 4.29. Initial Configurations for the ABS + CCS       114         Figure 4.30. Comparison between the results of the MCDT and the Holistic Approach       118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 108         Figure 4.24. Example of the Input Configuration       109         Figure 4.25. Global Order for the Example of the Figure 4.24       109         Figure 4.26. Initial Configuration for the Simple Use-Case       111         Figure 4.27. Comparison of the Two Steps Approach with the Holistic Approach and the Optimal Solution       112         Figure 4.28. Runtimes of the OS-GA and the TSDA-GA       113         Figure 4.29. Initial Configurations for the ABS + CCS       114         Figure 4.30. Comparison between the results of the MCDT and the Holistic Approach       118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 4.24. Example of the Input Configuration109Figure 4.25. Global Order for the Example of the Figure 4.24109Figure 4.26. Initial Configuration for the Simple Use-Case111Figure 4.27. Comparison of the Two Steps Approach with the Holistic Approach and the<br>Optimal Solution112Figure 4.28. Runtimes of the OS-GA and the TSDA-GA113Figure 4.29. Initial Configurations for the ABS + CCS114Figure 4.30. Comparison between the results of the MCDT and the Holistic Approach118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>Figure 4.25. Global Order for the Example of the Figure 4.24</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ul> <li>Figure 4.26. Initial Configuration for the Simple Use-Case</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>Figure 4.27. Comparison of the Two Steps Approach with the Holistic Approach and the Optimal Solution</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Optimal Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 4.28. Runtimes of the OS-GA and the TSDA-GA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 4.29. Initial Configurations for the ABS + CCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 4.30. Comparison between the results of the MCDT and the Holistic Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4.31. Iterative Improvement Loop for the Staged Approach 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4.32. Deployment Configuration for CCS and ABS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

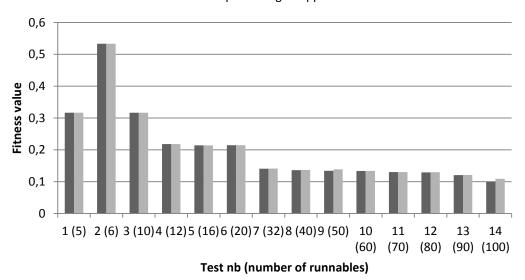

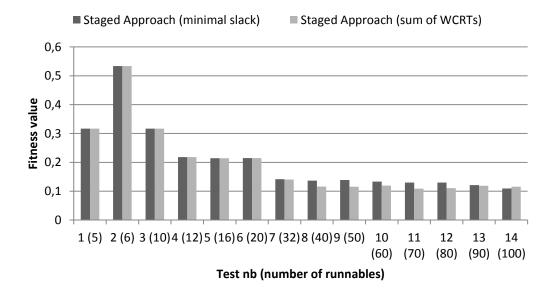

| Figure 4.33. Results for One-step and Staged Approach (GA Initial Population = 10000)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

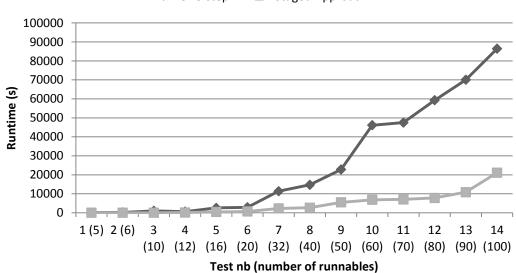

| Figure 4.34. Runtimes of One-step and Staged TTBA (GA initial population = 10000)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

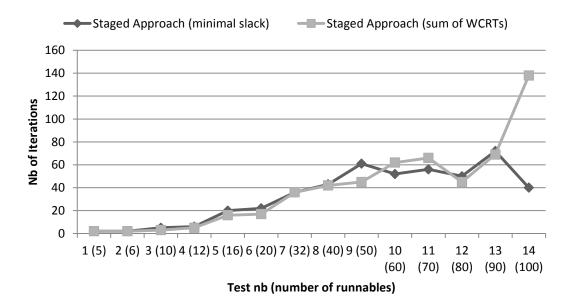

| Figure 4.36. Comparison of Number of Iterations of two different metrics for Staged    |

|----------------------------------------------------------------------------------------|

| TTBA                                                                                   |

| Figure 5.1. AFfMAO built as an instance of the AAF                                     |

| Figure 5.2. Layers and Viewpoints of the Automotive Architecture Framework 150         |

| Figure 5.3. Levels of the EAST-ADL2 Model                                              |

| Figure 5.4. Part of the EAST-ADL2 Metamodel for the FAA from [6] 153                   |

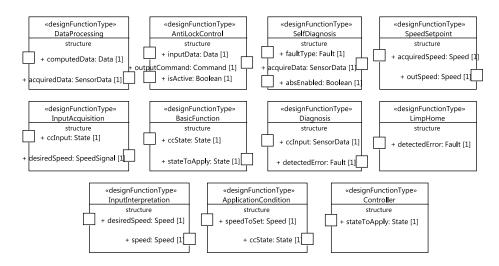

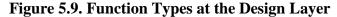

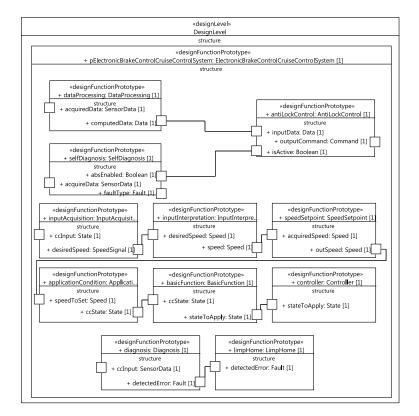

| Figure 5.5. Model of two Features                                                      |