# Binary Arithmetic for Finite-Word-Length Linear Controllers: MEMS Applications

Abdelkrim Kamel Oudjida

#### ▶ To cite this version:

Abdelkrim Kamel Oudjida. Binary Arithmetic for Finite-Word-Length Linear Controllers: MEMS Applications. Automatic Control Engineering. Université de Franche-Comté, 2014. English. NNT: 2014BESA2001. tel-01124332

# HAL Id: tel-01124332 https://theses.hal.science/tel-01124332v1

Submitted on 6 Mar 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# SPIM Thèse de Doctorat

FC UNIVERSITÉ DEFRANCHE-COMTÉ

# **Binary Arithmetic for Finite-Word-Length**

école doctorale sciences pour l'ingénieur et microtechniques

# Linear Controllers: MEMS Applications

ABDELKRIM KAMEL OUDJIDA

# Source of the sector of the se

école doctorale sciences pour l'ingénieur et microtechniques UNIVERSITÉ DE FRANCHE - COMTÉ

THÈSE présentée par

#### Abdelkrim Kamel OUDJIDA

pour obtenir le Grade de Docteur de L'Université de Franche-Compté

Spécialité: Automatique

### Binary Arithmetic for Finite-Word-Length Linear Controllers: MEMS Applications

Unité de Recherche: FEMTO-ST, UMR CNRS 6174

Soutenue le 20 Janvier 2014 devant le jury:

| Amara AMARA      | Président          | Professeur des Universités,<br>ISEP, Paris            |

|------------------|--------------------|-------------------------------------------------------|

| Adel BELOUCHRANI | Rapporteur         | Professeur, ENP, Alger                                |

| Chouki AKTOUF    | Rapporteur         | Maître de Conférences HDR,<br>INP de Grenoble         |

| Thibault HILAIRE | Examinateur        | Maître de Conférences,<br>Université Paris 6          |

| Brahim BOUZOUIA  | Examinateur        | Directeur de Recherche,<br>CDTA, Alger                |

| Nicolas CHAILLET | Directeur de Thèse | Professeur des Universités,<br>Université de Besançon |

# **Gödel's Incompleteness Theorems**

<u>Theorem</u> 1 – Blind spot: There is a sentence G such that if the formal system is consistent, G is not a theorem nor is it not a theorem.

<u>Theorem</u> 2 – Consistency: *No consistent theory, with a certain amount of arithmetic, can prove its own consistency.*

#### Acknowledgments

I wish to thank my supervisor, Prof. Nicolas Chaillet, for the support and trust he so generously provided me in the course of the accomplishment of my task. His continuous enthusiasm and encouragement constituted the driving force of this work.

I am deeply grateful to Dr. Brahim Bouzouia, Director of CDTA, for his help and support during all the period of the thesis.

I am so indebted to Prof. Noureddine Zerhouni, Mr. Karim Henda, and Prof. Yassine Haddab for their precious help. Without their effective contribution, this thesis would not have been concretized.

My special thanks go to my two colleagues, Mohamed Lamine Berrandjia and Ahmed Liacha, for their technical help in a warm and joyful atmosphere.

I am much thankful to my ex-student, Khaled Tahraoui, for having provided me with a tremendous number of papers that much contributed to enhance the quality of the work.

I would like to acknowledge Dr. Joël Agnus, research engineer within AS2M department of Femto-St institute, for his valuable advices.

Finally, I would like to thank my wife and sons for their great patience and support during my seemingly never-ending nights preparing the thesis.

#### Abstract

This thesis addresses the problem of optimal hardware-realization of finite-word-length (FWL) linear controllers dedicated to MEMS applications. The biggest challenge is to ensure satisfactory control performances with a minimal hardware. To come up, two distinct but complementary optimizations can be undertaken: in control theory and in binary arithmetic. Only the latter is involved in this work.

Because MEMS applications are targeted, the binary arithmetic must be fast enough to cope with the rapid dynamic of MEMS; power-efficient for an embedded control; highly scalable for an easy adjustment of the control performances; and easily predictable to provide a precise idea on the required logic resources before the implementation.

The exploration of a number of binary arithmetics showed that  $radix-2^{r}$  is the best candidate that fits the aforementioned requirements. It has been fully exploited to designing efficient multiplier cores, which are the real engine of the linear systems.

The radix-2<sup>*r*</sup> arithmetic was applied to the hardware integration of two FWL structures: a linear time variant PID controller and a linear time invariant LQG controller with a Kalman filter. Both controllers showed a clear superiority over their existing counterparts, or in comparison to their initial forms.

#### Glossary

- Abstraction Simplification of details, approximation of complex problems

- **ADC** Analog to Digital Converter

- AFM Atomic Force Microscopy

- ALU Arithmetic and Logic Unit

- **ASIC** Application Specific Integration Circuit

- Ath Adder Depth, the maximum number of serial adder-operations from input to output

- Avg Average number of additions

- BHM Bull Horrocks modified, an existing heuristic MCM algorithm

- BIGE Bounded Inverse Graph Enumeration, an optimal SCM algorithm

- BMA Booth Multiplication Algorithm, an existing algorithm for signed multiplication

- CAD Computer-aided design, tools for design automation

- **CDE** Common Digit Elimination

- **CLB** Configurable Logic Bloc

- CMOS Complementary Metal Oxide Semiconductor

- **COTS** Commercial Off-The-Shelf

- **CSD** Canonical Signed Digit, the SD form with no adjacent nonzero digits and the minimum number of nonzero digits

- CSE Common Subexpression Elimination, a framework for solving SCM and MCM

- DAC Digital to Analog Converter

- DAG Directed Acyclic Graphs, a framework for solving SCM and MCM

- DBNS Double Base Number System, an existing number representation system

- **DFS** Dynamic Frequency Scaling

- Digit Clashing The CSE problem of disappearing patterns due to colliding digits

- DMAC Double Multiply-And-Accumulate

- DSP Digital-Signal-Processor/Processing

- FF Flip-Flop

- FPGA Field Programmable Gate Array

- FPR Fixed-Point Representation

- FWL Finite Word Length

- H(k) Heuristic with k extra nonzero digits, an existing heuristic SCM algorithm

- H(k)+ODP The H(k) algorithm with ODPs, a proposed heuristic SCM algorithm

- Hcub Cumulative Benefit Heuristic, an existing MCM algorithm

- HDL Hardware Description Language

- Heuristic An effective but potentially suboptimal method for solving a problem

- HIS Host Side Interface

- HPM High Performance Multiplication, an existing adder reduction technique

- **IOB** Input Output Block

- Logic resources An abstraction of the amount of silicon required to implement a logic function

- LQG Linear Quadratic Gaussian

- LTI Linear Time Invariant

- LTV Linear Time Variant

- MAC Multiply-And-Accumulate

- MAG Minimized Adder Graph, an existing optimal SCM algorithm

- MBMA Modified Booth Multiplication Algorithm, , an existing algorithm for signed multiplication

- **MCM** Multiple Constant Multiplication, find a low-cost add-shift-subtract realization of multiplication by each of the given constants

- MEMS Micro-Electro-Mechanical Structure

- **MM** Matrix Multiplication

- MPC Model Predictive Control

- MPM Multi-Precision Multiplication

- MSD Minimal Signed Digit, any SD representation with the minimum number of nonzero digits

- **MV** Multiplication by a Variable

- NEMS Nano-Electro-Mechanical Structure

- NP-hard Non-deterministic Polynomial-time hard

- **ODMAC** Optimized Double Multiply-And-Accumulate

- **ODP** Overlapping Digit Pattern, a proposed technique for partially resolving the CSE digit clashing problem

- **OS** Operating System

- Pattern (CSE) A collection of signed digits that define how existing terms are added-operated together

- PC Personal Computer

- PID Proportional Integral Derivative, an existing control law

- PLD Programmable Logic Device

- PPG Partial Product Generator

- **RAG-***n n*-dimensional Reduced Adder Graph, an existing heuristic MCM algorithm **RMRMA** Recursive-Multibit-Recoding Multiplication Algorithm, a new algorithm

- RNS Residue Number System, an existing number representation system

- **RTL** Register Transfer Level

- RTOS Real Time Operating System

- SCM Single Constant Multiplication, same as MCM but for a single constant

- SD Signed Digit, a recoding used in the CSE framework

- **Search space** The set of all solutions that can be found by an algorithm, this is smaller than the solution space for heuristic algorithms

- SEM Scanning Electron Microscopy

- SiGe Silicon Germanium

- SM Sign and Magnitude

- SOC System On Chip

- Solution space The set of all feasible solutions

- SRAM Static Random Access Memory

- TC True and Complement

- TSMC Taiwan Semiconductor Manufacturing Company

- Upb Upper bound, maximum number of additions

- VHDL Very high speed integrated circuit Hardware Description Language

- VLIW Very Large Instruction Word

# Contents

| 1 | General Introduction                                                                                         | 1   |

|---|--------------------------------------------------------------------------------------------------------------|-----|

|   | 1.1 Motivation and Problem Statement                                                                         | 1   |

|   | 1.2 Objective of the Thesis                                                                                  | 1   |

|   | 1.3 Requirements and Specifications                                                                          | 2   |

|   | 1.4 Contribution of the Thesis                                                                               | 3   |

|   | 1.5 Organization of the Thesis                                                                               | 4   |

| 2 | Problem Background                                                                                           | 6   |

|   | 2.1 Application Context                                                                                      |     |

|   | 2.2 Micromanipulation as a MEMS application                                                                  | .8  |

|   | 2.3 Embedded Control-Electronics for MEMS                                                                    | 10  |

|   | 2.4 Review of the Basic Digital Solutions for Embedded Control                                               | .12 |

|   | 2.4.1 Commercial Off-The-Shelf (COTS) Electronics Components                                                 |     |

|   | 2.4.2 Digital Signal Processors (DSPs)                                                                       |     |

|   | 2.4.3 Field Programmable Gate Arrays (FPGA)                                                                  | -   |

|   | 2.4.4 Application Specific Integrated Circuits (ASIC)                                                        |     |

|   | 2.5 Overview of Finite-Word-Length (FWL) Controller Optimizations                                            |     |

|   | 2.5.1 Definition of the FWL Effect.                                                                          | -   |

|   | 2.5.2 Control-Theory Based Optimization.                                                                     |     |

|   | 2.5.3 Binary-Arithmetic Based Optimization                                                                   |     |

|   | 2.5.3.1 Multiplication by a Constant                                                                         |     |

|   | 2.5.3.2 Multiplication by a Variable         2.5.3.3 Multi-Precision Multiplication                          |     |

|   | 2.6 Conclusion                                                                                               |     |

| ~ |                                                                                                              |     |

| 3 | ,                                                                                                            |     |

|   | 3.1 Introduction to the Binary Arithmetic                                                                    |     |

|   | 3.2 Number Representation Formats.                                                                           |     |

|   | 3.2.1 Fixed-Point Format.                                                                                    |     |

|   | 3.2.1.1 Representation of Nonnegative Integers.                                                              |     |

|   | 3.2.1.2 Representation of Signed Integers         3.2.1.3 Fixed-Point Arithmetic of Two's Complement Numbers |     |

|   | 3.2.1.4 Multiplication.                                                                                      |     |

|   | 3.2.1.5 Addition.                                                                                            |     |

|   | 3.2.1.6 Overflow Detection                                                                                   |     |

|   | 3.2.2 Floating-Point Format.                                                                                 |     |

|   |                                                                                                              | 00  |

|   |     | 3.2.2.1 Dynamic Range                                    | 36  |

|---|-----|----------------------------------------------------------|-----|

|   |     | 3.2.2.2 Precision                                        | .36 |

|   | 3.3 | Number Representation Systems                            | 38  |

|   |     | 3.3.1 Canonical Signed Digit (CSD)                       | 39  |

|   |     | 3.3.2 Double Base Number System (DBNS)                   | 40  |

|   |     | 3.3.2.1 Basic ARDBNR reduction rules                     | 41  |

|   |     | 3.3.2.2 Advanced ARDBNR reduction rules                  | .41 |

|   |     | 3.3.2.3 Addition                                         | 42  |

|   |     | 3.3.2.4 Multiplication                                   | .43 |

|   |     | 3.3.3 Residue Number System (RNS)                        | 43  |

|   |     | 3.3.3.1 Addition and Multiplication                      | .44 |

|   |     | 3.3.3.2 Choosing the RNS Moduli                          | 45  |

|   |     | 3.3.4 Radix-2 <sup>r</sup> Number System                 | 46  |

|   |     | 3.3.4.1 Canonical Radix-2 <sup>r</sup> Representation    | 48  |

|   | 3.4 | Comparison of the Number Systems                         | .48 |

|   | 3.5 | Conclusion                                               | .49 |

| 4 | Mul | tiplication by a Constant                                | .51 |

|   | 4.1 | Optimizations of LTI Systems.                            | .51 |

|   |     | 4.1.1 Formulation of LTI Systems                         | 51  |

|   |     | 4.1.2 Single-Constant Multiplication (SCM)               | 52  |

|   |     | 4.1.3 Multiple-Constant Multiplication (MCM)             | 54  |

|   |     | 4.1.4 Subexpression Sharing between Output Variables     | 55  |

|   |     | 4.1.5 Matrix Decomposition                               | 55  |

|   | 4.2 | Formal Definition of the SCM Problem.                    | 56  |

|   | 4.3 | Existing SCM/MCM Algorithms                              | 57  |

|   |     | 4.3.1 Digit-Recoding Algorithms                          | 58  |

|   |     | 4.3.1.1 Avizienis's CSD Algorithm                        | 58  |

|   |     | 4.3.1.2 Dimitrov's DBNS Algorithm                        | .59 |

|   |     | 4.3.2 Common Subexpression Elimination (CSE)             | 62  |

|   |     | 4.3.2.1 Optimization Problems Due to the Initial SD Form | 62  |

|   |     | 4.3.2.2 CSE digit clashing problem                       | 63  |

|   |     | 4.3.2.3 Lefèvre's Common Subpattern (CSP) Algorithm.     | 63  |

|   |     | 4.3.3 Directed Acyclic Graphs (DAG) Algorithms.          | .64 |

|   |     | 4.3.3.1 Bernstein's Algorithm.                           | .64 |

|   |     | 4.3.3.2 Voronenko's Hcub Algorithm.                      | 65  |

|   |     | 4.3.4 Hybrid Algorithms(CSE & DAG)                       |     |

|   |     | 4.3.4.1 Thong's BIGE Algorithm                           | 68  |

|   | 4.4 | Metrics Definition for SCM/MCM Algorithms.               | 69  |

|   | 4.5 | Key Limitations of the Existing SCM/MCM Algorithms       | 71  |

|   |     | 4.5.1 Predictability.                                    | 71  |

|   |     | 4.5.2 Runtime and Memory Storage                         |     |

|   |     | 4.5.3 Overflow Risk.                                     | 72  |

|   |     | 4.5.4 Ease of Use                                        | .72 |

|   | 4.6 | New Recoding Algorithm (RADIX-2 <sup>r</sup> )                                       | 72  |

|---|-----|--------------------------------------------------------------------------------------|-----|

|   |     | 4.6.1 Maximum Number of Additions (Upb)                                              | 73  |

|   |     | 4.6.2 Average Number of Additions (Avg)                                              | 79  |

|   |     | 4.6.3 Length of the Critical-Path in Cascaded Adders (Ath)                           | 80  |

|   |     | 4.6.4 Overflow Safety                                                                | 81  |

|   | 4.7 | New Redundant Radix-2 <sup>r</sup> Recoding (R3) Algorithm                           | 82  |

|   | 4.8 | New MCM Algorithm (RADIX-2 <sup>r</sup> MCM)                                         | 88  |

|   | 4.9 | Conclusion                                                                           | 89  |

| 5 | Mul | Itiplication by a Variable                                                           | 93  |

|   |     | Optimizations of LTV Systems.                                                        |     |

|   |     | Formal Definition of the MV Problem                                                  |     |

|   |     | 5.2.1 New Radix-2 <sup>r</sup> Design concept                                        | 94  |

|   |     | 5.2.2 New MV Complexity                                                              | 95  |

|   | 5.3 | High-Radix Multiplication Algorithms                                                 | 96  |

|   |     | 5.3.1 Dimitrov's DBNS Algorithm                                                      | 96  |

|   |     | 5.3.2 Seidel's RNS Algorithm                                                         | 100 |

|   | 5.4 | New Radix-2 <sup>r</sup> Multiplication Algorithms                                   |     |

|   |     | 5.4.1 Two New High Radix (2 <sup>8</sup> and 2 <sup>16</sup> ) Illustrative Examples |     |

|   |     | 5.4.1.1 New Radix-2 <sup>8</sup> Recoding                                            |     |

|   |     | 5.4.1.2 New Radix-2 <sup>16</sup> Recoding                                           |     |

|   |     | 5.4.1.3 Analytical Characterization of Area and Speed.                               |     |

|   |     | 5.4.2 Preliminary Study to an Optimal Partitionning                                  |     |

|   |     | 5.4.3 The Optimal Space/Time Partitioning                                            |     |

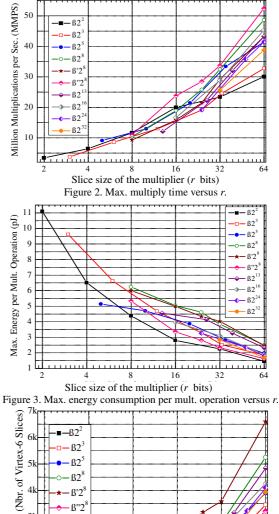

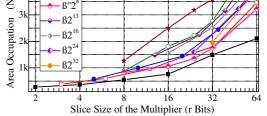

|   |     | 5.4.4 Discussion of the Implementation Results                                       |     |

|   |     | 5.4.4.1 Alea Occupation                                                              |     |

|   | 55  | New Radix-2 <sup><i>r</i></sup> Multip-recision Multiplication Algorithms.           |     |

|   | 5.5 | 5.5.1 New Radix-2 <sup><i>r</i></sup> Sign Extension Technique                       |     |

|   |     | 5.5.2 New Radix-2 <sup><i>r</i></sup> Multi-Precision Multiplication Techniques      |     |

|   | 56  | Conclusion                                                                           |     |

| ~ |     |                                                                                      |     |

| 6 |     | plications                                                                           |     |

|   | 6.1 | PID Controllers                                                                      |     |

|   |     | 6.1.1 The Two Mostly-Used Discrete Versions of PID.                                  |     |

|   |     | 6.1.2 BMA Based PID.         6.1.3 MBMA Based PID.                                   | -   |

|   |     | 6.1.4 RMRMA Based PID                                                                |     |

|   |     | 6.1.5 Discussion                                                                     |     |

|   |     | 6.1.6 Verification Method.                                                           |     |

|   |     | 6.1.7 The Finite-Word-Lenght (FWL) Effect                                            |     |

|   | 6.2 | LQG Controller with Kalman Filter                                                    | -   |

|   |     | 6.2.1 Dynamic Model of the FT-G100 Micro-Gripper                                     |     |

|   |     |                                                                                      |     |

| 6.2.2 Kalman Filtering                                              |

|---------------------------------------------------------------------|

| 6.2.3 Force Control of the FT-G100 Micro-Gripper                    |

| 6.2.4 Hardware integration of the LQG controller with Kalman Filter |

| 6.3 Conclusion                                                      |

| 7 General Conclusion154                                             |

| 7.1 Major Contributions                                             |

| 7.2 Current Limitations                                             |

| 7.3 Perspectives                                                    |

| Appendix A: Proofs of Theorems 4.3 and 4.4                          |

| Appendix B: A Series of New High-Radix Recodings                    |

| Appendix C: PID Equations 163                                       |

| Appendix D: LQG Controller with Kalman Filter166                    |

| Bibliography                                                        |

| Chapter 1                                                           |

| Chapter 2                                                           |

| Chapter 3                                                           |

| Chapter 4                                                           |

| Chapter 5                                                           |

| Chapter 6                                                           |

| Chapter 7                                                           |

# List of Figures

| 1.1        | ASIC solution for MEMS control providing 100% autonomy                                                                                                                     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1<br>2.2 | Microgripper with two degrees of freedom piezocantilevers                                                                                                                  |

| 2.3        | Some force spans characterizing the microworld                                                                                                                             |

| 2.4        | Amplitude of the forces in the microworld for a microsphere of radius <i>r</i>                                                                                             |

| 2.5        | Micromanipulation problem due to adhesion forces                                                                                                                           |

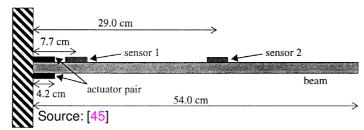

| 2.6        | Simple cantilever beam                                                                                                                                                     |

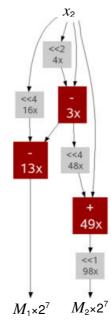

| 2.7        | Minimum number of additions of $M_1$ and $M_2$ using a separate optimization of $a_{12}$ and $a_{22}$ 20                                                                   |

| 2.8        | Minimum number of additions of $M_1$ and $M_2$ using a combined optimization of $a_{12}$ and $a_{22}$ 20                                                                   |

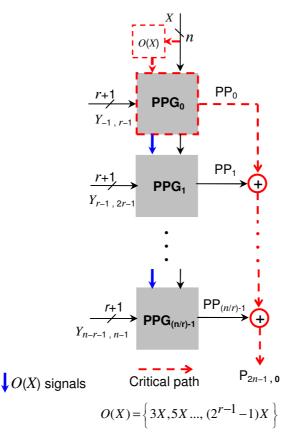

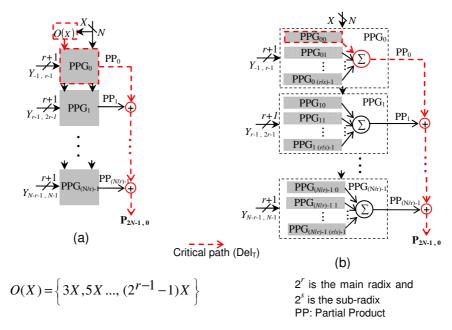

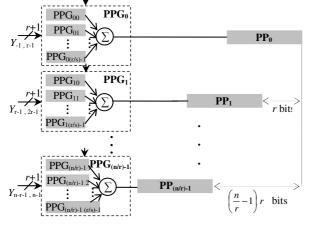

| 2.9        | Generalized $N \times N$ bit radix-2 <sup><i>r</i></sup> parallel multiplier                                                                                               |

| 2.10       | Illustration of an unsigned 8-bit multiplication, where a 4-bit multiplication, shown in white, is computed in parallel with a second 4-bit multiplication, shown in black |

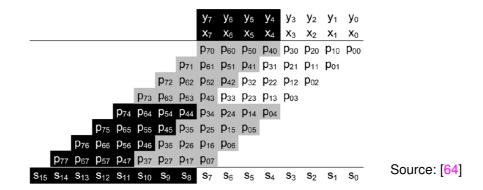

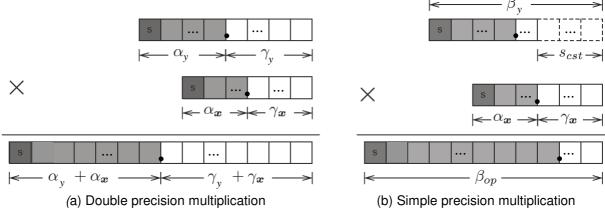

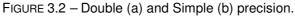

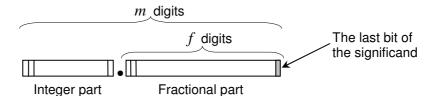

| 3.1        | Fixed-point representation of a signed real number in two's complement system                                                                                              |

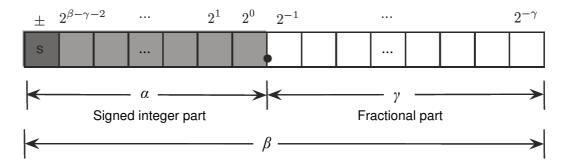

| 3.2        | Double (a) and Simple (b) precision                                                                                                                                        |

| 3.3        | Significand in radix- <i>r</i> fixed-point representation                                                                                                                  |

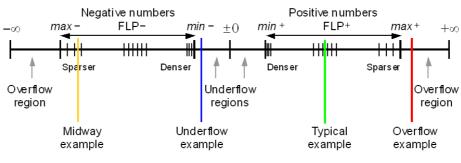

| 3.4        | Distribution of floating-point numbers within the dynamic range                                                                                                            |

| 3.5<br>3.6 | The ANSI/IEEE standard 754-1988 floating-point representation                                                                                                              |

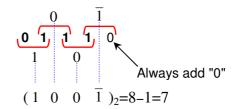

| 0.0        | integer "7"                                                                                                                                                                |

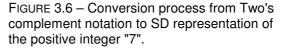

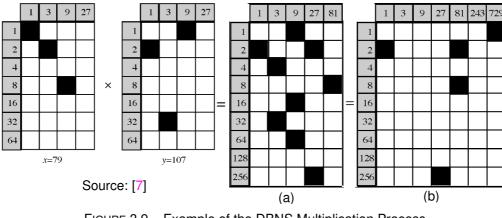

| 3.7        | Reduction of consecutive active cells lying in one column (a) and in one row (b)41                                                                                         |

| 3.8        | Example of the DBNS addition process                                                                                                                                       |

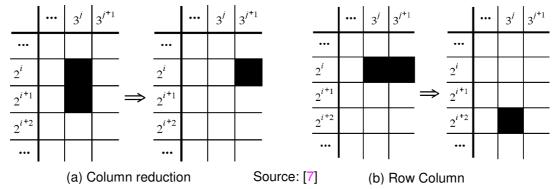

| 3.9        | Example of the DBNS Multiplication Process                                                                                                                                 |

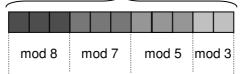

| 3.10       | Binary-coded number format for RNS(8   7   5   3)                                                                                                                          |

| 3.11       | Partitioning of $(10599)_{10}$ in radix-2 <sup>4</sup>                                                                                                                     |

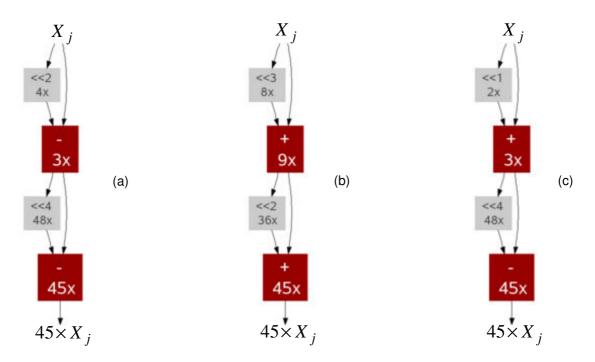

| 4.1        | The minimal number of addition for $45 \times X_j$                                                                                                                         |

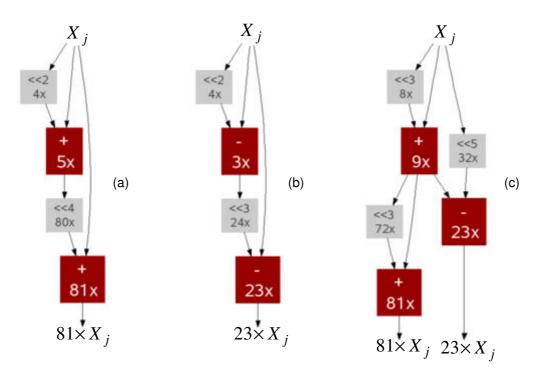

| 4.2        | Multiplication of the constants 81 and 23                                                                                                                                  |

| 4.3        | An example that shows the benefit obtained by considering common subexpressions that                                                                                       |

|            | span across multiple output variables                                                                                                                                      |

| 4.4        | Matrix decomposition                                                                                                                                                       |

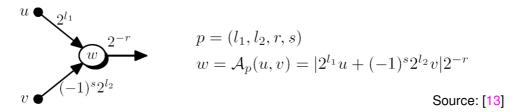

| 4.5        | A-operation: $u$ and $v$ are the input fundamentals and $w$ is the output fundamental                                                                                      |

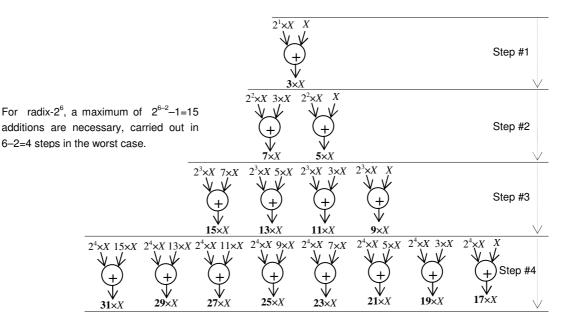

| 4.5        | Sequential order of computation of the entire set of partial-products needed by radix- $2^6$ 74                                                                            |

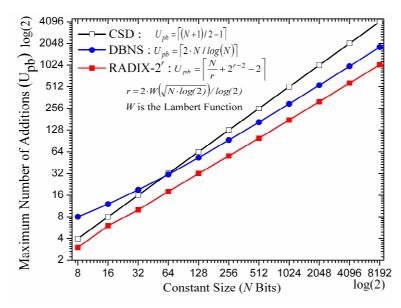

| 4.6        | Upb comparison for an <i>N</i> -bit constant                                                                                                                               |

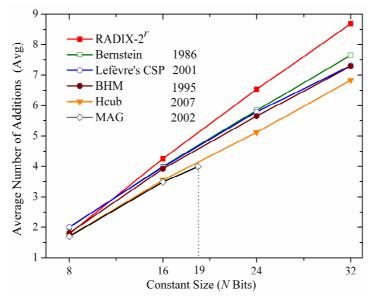

| 4.7        | Avg comparison for an N-bit constant    76                                                                                                                                 |

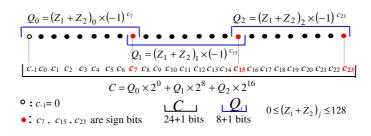

| 4.8        | Partitioning of a 24-bit $C$ constant using R3 algorithm                                                                                                                   |

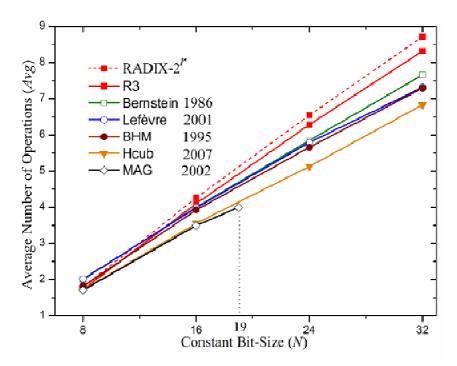

| 4.9        | Avg comparison for a <i>N</i> -bit constant                                                                                                                                |

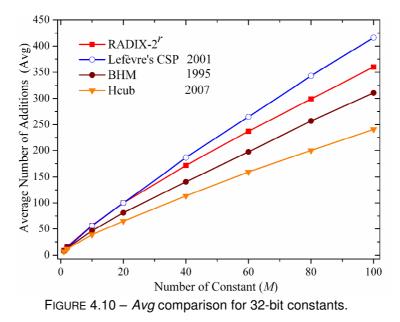

| 4.9        | Avg comparison for a 32-bit constant                                                                                                                                       |

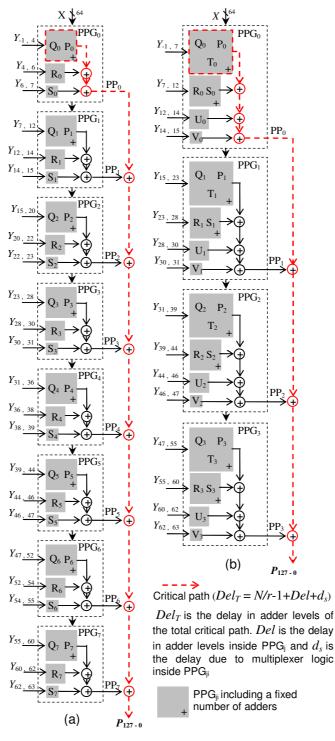

| 5.1        | Generalized $N \times N$ bit radix-2 <sup><math>r</math></sup> parallel multiplier                      | .95  |

|------------|---------------------------------------------------------------------------------------------------------|------|

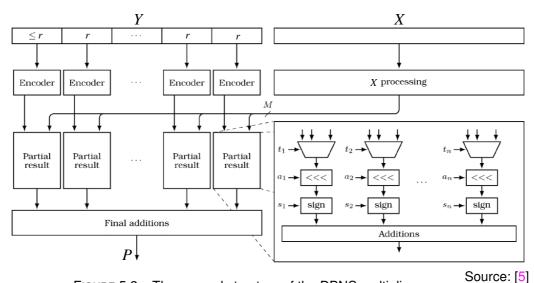

| 5.2        | The general structure of the DBNS multiplier                                                            | 97   |

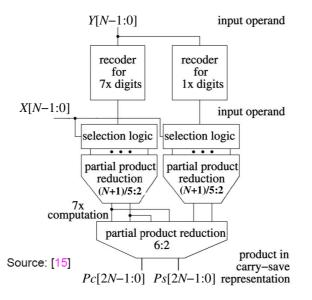

| 5.3        | Recoding (32,7) with postcomputation of 7×                                                              | 101  |

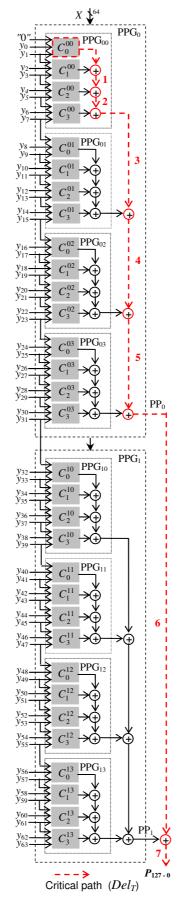

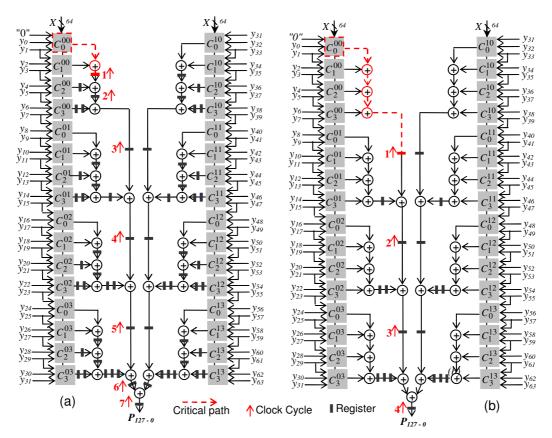

| 5.4        | Two's complement 64×64 bit multiplier                                                                   | 107  |

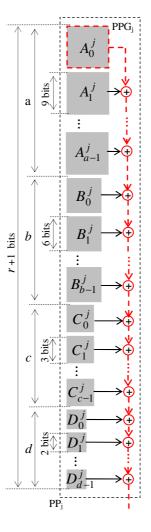

| 5.5        | Critical path ( $Del+d_i$ ) inside a generalized PPG <sub>j</sub>                                       | 111  |

| 5.6        | Optimal partitioning of a two's complement 64×64 bit radix-2 <sup>32</sup> parallel multiplier based on |      |

|            | Eq. 5.22 with ( <i>r</i> , <i>s</i> )=(32,8)                                                            | 116  |

| 5.7        | Space/Time partitioning of a two's complement 64×64 bit radix-2 <sup>32</sup> parallel multiplier based |      |

|            | on Eq. 5.22                                                                                             | 118  |

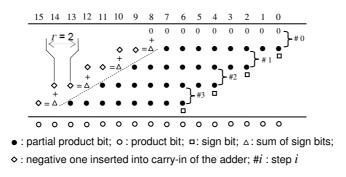

| 5.8        | Low-power sign-extension technique for the particular case $(N, r)=(8, 2)$                              | 119  |

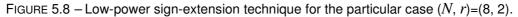

| 5.9        | Multiplication matrix of partial-products bits for 16-b multiplication with one level recursion         | 119  |

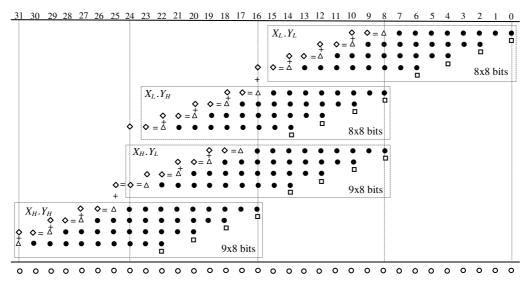

| 5.10       | Low-power multi-precision multiplier for the particular case $(N,r)=(16,2)$ with 8-bit sub-             |      |

|            | operand size                                                                                            | 120  |

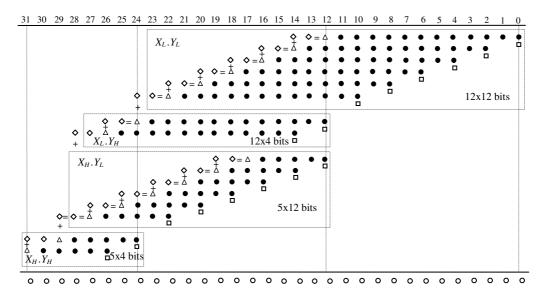

| 5.11       | Low-power multi-precision multiplier for the particular case $(N,r)=(16, 2)$ with 12 and 4 bit          |      |

|            | sub-operand sizes                                                                                       | 121  |

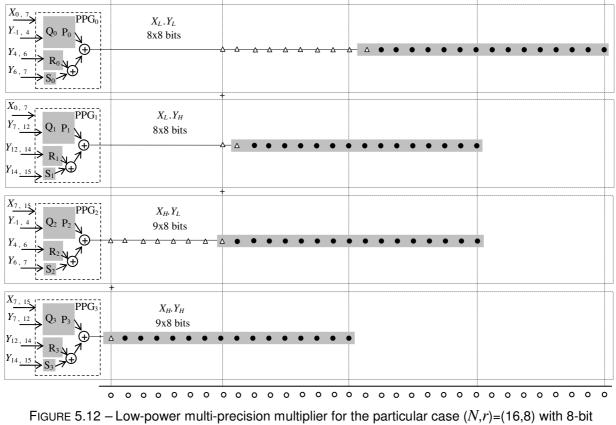

| 5.12       | Low-power multi-precision multiplier for the particular case $(N,r)=(16,8)$ with 8-bit sub-             |      |

|            | operand size                                                                                            | .121 |

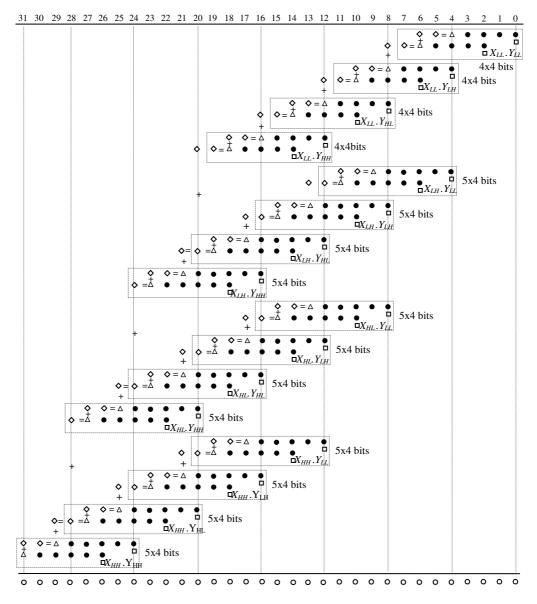

| 5.13       | Low-power multi-precision multiplier for the particular case $(N,r)=(16,2)$ with 4-bit sub-             |      |

|            | operand size                                                                                            | .123 |

|            |                                                                                                         |      |

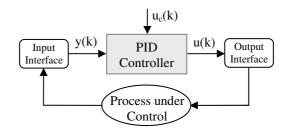

| 6.1        | Typical closed-loop control system using a PID                                                          |      |

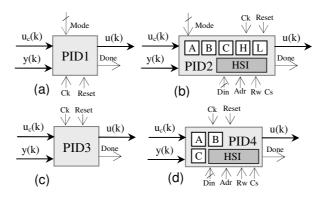

| 6.2        | Various PID IP-cores                                                                                    |      |

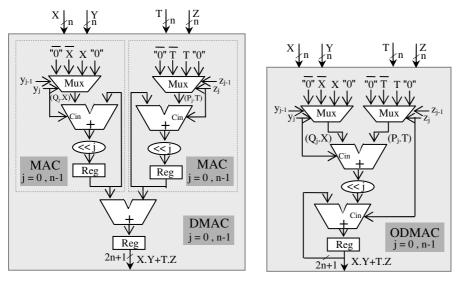

| 6.3        | Straightforward DMAC implementation                                                                     |      |

| 6.4        |                                                                                                         |      |

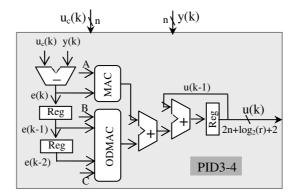

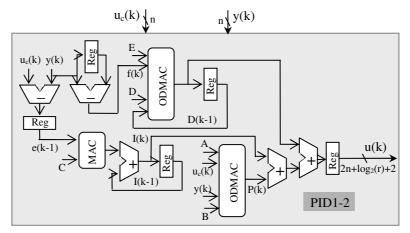

| 6.5<br>6.6 | Incremental PID architecture                                                                            |      |

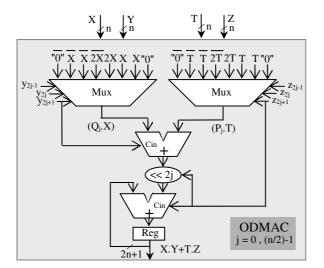

|            | Optimized DMAC architecture for $r=2$                                                                   |      |

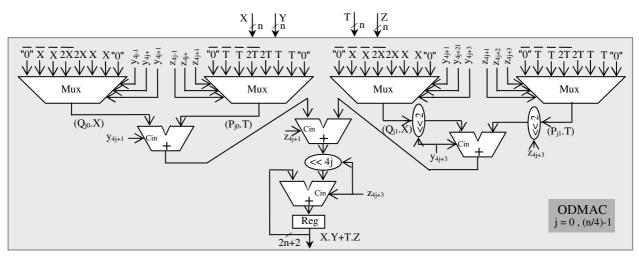

| 6.7        |                                                                                                         |      |

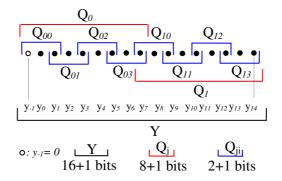

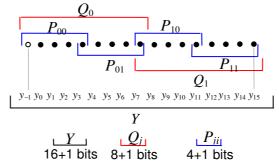

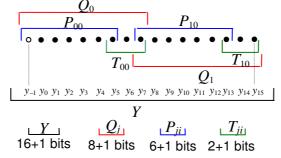

| 6.8        | Partitioning of a 16-bit $Y$ operand with $r=8$                                                         |      |

| 6.9        | Optimized DMAC architecture for <i>r</i> =4                                                             |      |

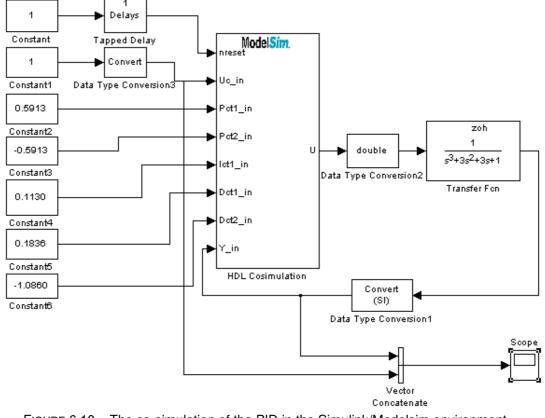

|            | The co-simulation of the PID in the Simulink/Modelsim environment                                       |      |

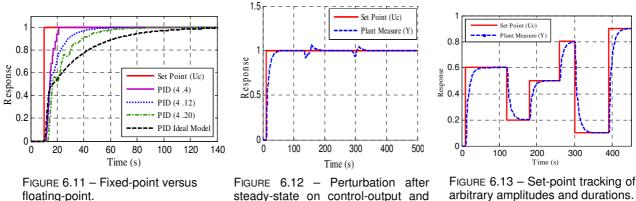

|            | Fixed-point versus floating-point.                                                                      |      |

|            | Perturbation after steady-state on control-output and on plant measure, successively                    |      |

|            | Set-point tracking of arbitrary amplitudes and durations                                                |      |

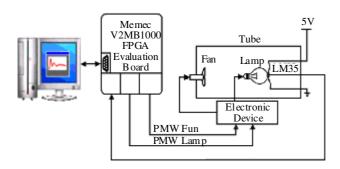

|            | Setup of temperature regulation.                                                                        |      |

|            | Effect of the setpoint fractional length on temperature regulation                                      |      |

|            | Structure of the FT-G100 microgripper (Femto Tools GmbH)                                                |      |

|            | System modelling.                                                                                       |      |

|            | Kalman recursive algorithm                                                                              |      |

|            | General scheme of the LQG controller with Kalman filter.                                                |      |

| 6.21       | Standard methodology for an optimized hardware integration of LTI systems: from Matlab                  |      |

|            | functional model to HDL synthesizable code                                                              | 146  |

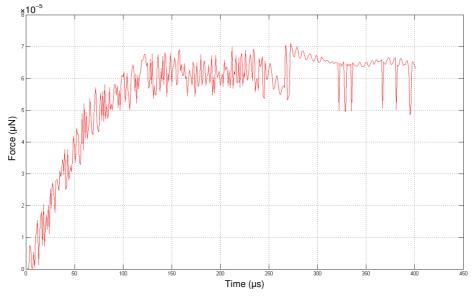

| 6.22       | The noisy and filtered force ( $F_c$ ) of the actuated arm                                              | 147  |

|            | The difference between the floating-point and the fixed-point filtered force $(F_c)$                    |      |

# List of Tables

| 2.1<br>2.2 | Main features of the basic digital solutions for embedded control       15         Main features of the most known SCM algorithms in the literature.       20 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1<br>3.2 | Representation of the integer "thirty" in different number systems.                                                                                           |

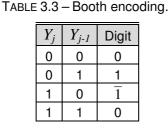

| 3.3        | Booth encoding                                                                                                                                                |

| 3.4        | Radix-2 <sup>4</sup> look-up table                                                                                                                            |

| 3.5<br>3.6 | Number of digits required by each number system for the integer value (10599) <sub>10</sub>                                                                   |

| 4.1        | A DBNS representation of $c = 10599$ obtained using two blocks of 7 bits each                                                                                 |

| 4.2        | Constant type and allowed operations                                                                                                                          |

| 4.3        | Upper-bound ( <i>Upb</i> ) and $r$ values for an $N$ -bit constant using RADIX-2 <sup><math>r</math></sup>                                                    |

| 4.4        | RADIX-2 <sup><i>r</i></sup> versus CSD: average number of additions ( <i>Avg</i> ) and upper-bound ( <i>Upb</i> )75                                           |

| 4.5        | RADIX-2 <sup><i>r</i></sup> versus DBNS: average number of additions ( <i>Avg</i> ) and upper-bound ( <i>Upb</i> )                                            |

| 4.6        | RADIX-2 <sup>r</sup> versus non-recoding algorithms: runtime complexity and number of additions of                                                            |

|            | some special cases                                                                                                                                            |

| 4.7        | RADIX-2 <sup>r</sup> versus CSD, Lefevre's CSP, and exhaustive search: smallest values up to a 32-bit                                                         |

|            | constant                                                                                                                                                      |

| 4.8        | RADIX-2 <sup><i>r</i></sup> versus CSD: <i>Avg</i> , <i>Ath</i> , and <i>Upb</i> for <i>N</i> -bit constant                                                   |

| 4.9        | Upper-bound and $r$ values for $N$ -bit constant using RADIX-2 <sup><math>r</math></sup>                                                                      |

| 4.10       | Odd and even $ Q_j $ digit recoding using R3 algorithm                                                                                                        |

| 4.11       | R3 versus radix-2 <sup>r</sup> : average number of additions ( <i>Avg</i> )                                                                                   |

| 4.12       | R3 versus RADIX-2 <sup><i>r</i></sup> : smallest values up to 32-bit constant                                                                                 |

| 4.13       | R3 and RADIX-2 <sup><i>r</i></sup> versus non-recoding algorithms: runtime complexity and number of additions of some special cases                           |

| 4.14       | RADIX-2 <sup><i>r</i></sup> MCM versus non-recoding MCM algorithms: runtime complexity for a number of                                                        |

|            | M constants with N-bit each                                                                                                                                   |

| 4.15       |                                                                                                                                                               |

| 5.1        | Dimitrov's high-radix DBNS algorithms                                                                                                                         |

| 5.2        | Main features of the multibit recoding multiplication algorithm                                                                                               |

| 5.3        | Main feature comparison                                                                                                                                       |

| 5.4  | Implementation results of a two's complement 64-bit parallel multiplier on Xilinx xc6vsx475t-<br>2ff1156 circuit                |

|------|---------------------------------------------------------------------------------------------------------------------------------|

| 5.5  | Delay and multiplexer complexity of basic radices: step #1                                                                      |

| 5.6  | Optimal PPG <sub><i>i</i></sub> solution $(a,b,c,d)$ leading to the optimal radix-2 <sup><i>r</i></sup> multiplier according to |

| 0.0  | composite metrics $A^{i}T^{j}$ : step #1                                                                                        |

| 5.7  | Delay and multiplexer complexity of the new basic radices: step #2113                                                           |

| 5.8  | Optimal PPG <sub>j</sub> solution $(a, b, c, d)$ leading to the optimal radix-2 <sup>r</sup> multiplier according to            |

|      | composite metrics $A^{i}T^{j}$ : step #2                                                                                        |

| 5.9  | Delay and multiplexer complexity of the new basic radices: step #3114                                                           |

| 5.10 | Optimal PPG <sub>j</sub> solution $(a, b, c, d)$ leading to the optimal radix-2 <sup>r</sup> multiplier according to            |

|      | composite metrics $A^{i}T^{j}$ : step #3                                                                                        |

| 5.11 | The optimal partitioning versus operand size $N$                                                                                |

| 6.1  | Coefficients of discrete recurrent equations                                                                                    |

| 6.2  | Booth algorithm                                                                                                                 |

| 6.3  | Implementation result comparison of MBA-based PID131                                                                            |

| 6.4  | Modified Booth algorithm                                                                                                        |

| 6.5  | Implementation result comparison of MBMA-based PID132                                                                           |

| 6.6  | Implementation result comparison of RMRMA-based PID135                                                                          |

| 6.7  | Maximum power-consumption and control-loop-cycle of PID1136                                                                     |

| 6.8  | Maximum power-consumption and control-loop-cycle of PID2136                                                                     |

| 6.9  | Maximum power-consumption and control-loop-cycle of PID2 mapped on Virtex6137                                                   |

# **Personal Publications**

#### **Publications in Indexed Journals**

- A.K. Oudjida, N. Chaillet, "Radix-2<sup>r</sup> Arithmetic for the Multiplication by a Constant," Accepted for publication on January 20th 2014. IEEE Trans. on Circuits and Systems II, Expess Brief.

- A.K. Oudjida, N. Chaillet, A. Liacha, M.L. Berrandjia, and M. Hamerlain, "Design of High-Speed and Low-Power Finite-Word-Length PID Controllers," Journal of Control Theory and Applications (JCTA), vol. 12, N° 1, pp.68-83, 2014, ISSN:1672-6340, SPRINGER, Germany.

- A.K. Oudjida, N. Chaillet, M.L. Berrandjia, and A. Liacha, "A New High Radix-2<sup>r</sup> (r ≥ 8) Multibit Recoding Algorithm for Large Operand Size (N ≥ 32) Multipliers,". Journal of Low Power Electronics (JOLPE), vol. 9, N° 1, pp. 50-62, April 2013, ISSN:1546-1998, American Scientific Publishers (ASP), USA.

- A.K. Oudjida, N. Chaillet, A. Liacha, and M.L. Berrandjia, "A New Recursive Multibit Recoding Algorithm for High-Speed and Low-Power Multiplier,". Journal of Low Power Electronics (JOLPE), vol. 8, N° 5, pp. 579-594, Dec.2012, ISSN:1546-1998, American Scientific Publishers (ASP), USA.

#### **Publications in International Conferences**

- A.K. Oudjida, M.L. Berrandjia, and N. Chaillet, "A New Low-Power Recoding Algorithm for Multiplierless Single/Multiple Constant Multiplication," Proceedings of the 12th edition of IEEE-FTFC Low-Voltage Low-Power Conference, ISBN:978-1-4673-6104-0/13, June 19-21 2013, Paris, France.

- A.K. Oudjida, N. Chaillet, A. Liacha, and M.L. Berrandjia "New High-Speed and Low-Power Radix-2<sup>r</sup> Multiplication Algorithms," Proceedings of the 11th edition of IEEE-FTFC Low-Voltage Low-Power Conference, ISBN:978-1-4673-0821-2/12, June 06-08 2012, Paris, France.

- A.K. Oudjida, N. Chaillet, A. Liacha, M. Hamerlain, and M.L. Berrandjia, "High-Speed and Low-Power PID Structures for Embedded Applications," Proceedings of the 21th Edition of the International Workshop on Power and Timing Modeling, Optimization and Simulation PATMOS, LNCS 6951, pp. 257-266, SPRINGER-VERLAG Editor, September 26-29 2011, Madrid, Spain.

# Chapter 1

# **General Introduction**

#### **Chapter 1**

#### **General Introduction**

This chapter defines the problematic issue treated in this thesis and indicates the objective to achieve. It sets the main requirements and specifications that fixe the research scope and limitation, and informs on the essential contribution of the thesis. It also gives an idea on the organization of this manuscript.

#### **1.1 Motivation and Problem Statement**

As a MEMS application, micromanipulation is a field which has the particularity of being very sensitive to noise. To reach the desired force/position accuracy in the gripping of micrometric objects, the development of advanced control methods is necessary. The latter often results in control laws, filters, and algorithms which are executed in real-time on platforms that are in total disproportion with the dimensions of the manipulator tool (micro-gripper) and the micro-objects manipulated. They are bulky and expensive, and have the huge drawback of preventing any embedded or mobile utilisation (*portability*). Therefore, the *hardware integration* of these control laws and all related problems is quite worthwhile, and constitutes a real challenge.

With a sound experience in micromanipulation, and being aware of the hardware integration as an ineluctable future step, the Automatic Control and Micro-Mechatronic Systems (AS2M) department of FEMTO-ST Institute, Besançon, initiated in 2010 a new research project called embedded electronics for MEMS. This project has been elaborated in conjunction with the Microelectronics and Nanotechnology Division (DMN) of CDTA, Algiers, joining their complementary skills together for the same objective. It is within the framework of this collaboration project CDTA/FEMTO-ST that the present thesis has evolved.

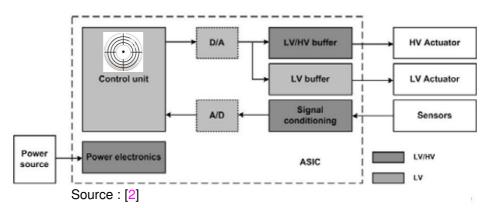

The most commonly used platform for micromanipulation setups is composed of a PC (with Matlab/Simulink or Labview software for instance) connected to a processor (dSPACE compatible for instance) for the real-time control, incorporating a sophisticated floating-point arithmetic unit with a high precision and large dynamic range. One intermediate step toward portability will be to *substitute* the calculation unit used for the real-time calculation by an FPGA board, wherein only the *control algorithm* is embedded [1]. The ideal solution would be to incorporate the whole electronics (control, power, signal conditioning, and conversion) into a low-power ASIC [2], directly connected to the microgripper (Fig. 1.1). Such a solution provides 100% autonomy, but its implementation requires varied and multidisciplinary skills.

#### 1.2 Objective of the Thesis

The replacement of the dSPACE unit by an FPGA control board will primarily arise the problem of stability. The latter is due to the inaccuracies of calculations caused by the use of an approximate representation of real numbers (Fixed-point) with a reduced precision and dynamic range. The fixed-point representation is dictated in this specific case by implementation considerations. Not only it is much easier to implement, but also leads to more computational speed and less power consumption and logic resources, in comparison to floating-point representation.

FIGURE 1.1 – ASIC solution for MEMS control providing 100% autonomy.

More precisely, the use of fixed-point instead of floating-point will exaggerate the quantification and rounding effects on the transfer function of the system (disturbance of the pole-zero position). This effect is assimilated to an additional source of noise (white noise) which is added to the already existing environmental noise. Consequently, the biggest challenge is to ensure satisfactory control performances with a minimum hardware (minimum word sizing of the controller structure). This problematic issue is well known under the name of optimal realizations of digital Finite-Word-Length (FWL) controllers. It involves optimizations in control theory and binary arithmetic.

The objective of the thesis is the development of a new binary arithmetic adapted to the FWL problem, enabling an easy generation of minimum word-size controller-structures with acceptable control performances.

#### **1.3 Requirements and Specifications**

The hardware integration of FWL controllers is a vast problematic issue. In order to define the research scope and limitation of the thesis, a number of requirements and specifications are established. They are summarized as follows:

- Only linear controllers are considered. This includes both the Linear Time-Invariant (LTI) and Time-Variant (LTV) controllers;

- Only binary arithmetic is used as a mean of optimization. Are not considered the optimization methods based on the utilization of sparse and insensitive matrices with minimization of transfer-function or pole-zero disturbance.

- A new fixed-point binary arithmetic is to be proposed. It must be:

- Fast to cope with the high dynamics of MEMS;

- Power efficient for an embedded control;

- Highly scalable for an easy adjustment of the control performances;

- Predictable to provide a more-or-less precise idea on the speed and logic resources before the implementation. This feature is very useful to the automatic synthesis of linear controllers.

- Use of the same word size and the same fixed-point position in the word for all the coefficients and variables involved. Are not addressed issues related to the order of sum-of-product operations, nor those pertaining to different rounding modes (truncation, to-the-nearest, etc.).

- To target a wide range of applications, the arithmetic optimization is undertaken at the algorithmic level, and not at the architectural level;

- Because only LTI and LTV controllers are concerned, the main arithmetic functions involved are:

- Single and Multiple Coefficient Multiplication (SCM and MCM);

- Variable operand multiplication;

- Multi-precision multiplication.

- As the optimization effort is deployed at algorithmic level, there is a need to explore a large number of alternative algorithms in order to select the best one. Therefore, reconfigurable circuits (FPGA) stand in this case as the most appropriate option of integration. FPGA allows a fast prototyping;

- Although FPGA serves for the validation of the developed algorithms, HDL code must be fully compliant to the standard IP design-reuse methodology. This means also that the HDL-RTL code will be 100% technology independent, offering the possibility to be mapped both on FPGA and ASIC using a digital standard-cell-library of a given technology foundry. This measure guarantees a systematic reuse of the same code for any future ASIC integration.

- Arithmetic optimization results are applied to PID and LQG controllers with Kalman's filter. These two linear controllers were used in a previous work [3] to control the FTG-100 microgripper (www.femtools.com) on a dSPACE platform.

#### 1.4 Contribution of the Thesis

We have investigated and compared four binary arithmetics: CSD, DBNS, RNS, and Radix-2<sup>*r*</sup>. In spite of a serious limitation of Radix-2<sup>*r*</sup> for high values of *r* due to the generation of an important number of odd-multiples  $\{1,3,5,\dots,2^{r-1}-1\}$ , it seems relatively the most liable arithmetic to fulfil the above-set requirements. We have circumvented the limitation of Radix-2<sup>*r*</sup> by a recursive construction of higher radices based on a combination of lower radices. This technique has enabled to develop:

- A new heuristic (RADIX-2<sup>r</sup>) for SCM. It has the major advantage of being 100% predictable in maximum number of additions (upper-bound), in average number of additions, and in number of cascaded adders (adder-depth) forming the critical path. Furthermore, its computational complexity is linearly proportional to the constant bit size (*N*), which means that it has no limitation with regard to *N*. Despite the big number of existing heuristics, none of them is predictable, not even partially. Besides, most of them exhibit a polynomial runtime complexity  $O(N^{\alpha})$  with  $\alpha \ge 3$ , and some of them show even an exponential  $O(2^N)$  complexity. Only CSD is linear and predictable. But the latter is largely superseded by RADIX-2<sup>r</sup> which requires 18% less additions for a 64-bit constant.

- A new fully predictable heuristic (RADIX-2<sup>*r*</sup>) for MCM with a computational complexity  $O(N \times M)$ , where *M* is the number of constants. Compared to the standard CSD for (N,M)=(64,10), a saving of 53% is obtained. The saving increases as the product  $N \times M$  increases.

- A series of new high-radix multiplication algorithms with variable operands. They have the merit of being fast, energy efficient, highly-scalable, and predictable. Contrary to existing Radix-2<sup>*r*</sup> algorithms where the highest value of *r* is limited to 16, the proposed algorithms have no limitation with regard to *r*. Theoretically, the higher the radix, the shorter the critical path (faster).

- A new mathematical formalism which enables to derive the optimal high-radix multiplication algorithm from a given combination of low-radix multiplication algorithms. The idea has been physically validated on FPGA.

- A series of new multi-precision multiplication algorithms, offering the possibility to run simultaneously several small-size multiplications on the same *N*×*N*-bit multiplication array. The proposed algorithms have the superiority over exiting ones to support a generic partitioning of the array. This results in a higher computational throughput with reduced power consumption.

- The currently best known analytically-proved bounds (Upper-bound, Adder-depth, Average) with the exact number of additions for SCM and MCM.

#### 1.5 Organization of the Thesis

Except the introduction and conclusion, the remainder of the manuscript is structured in five chapters.

Because of the intended applications, corresponding informations are given in chapter 2. We first start with micromanipulation as a MEMS application. We describe its specificities and requirements. This is followed by the state-of-the-art of embedded control-electronics for MEMS. We review the basic digital solutions and discuss the pros and cons of each option. At the end, we present an overview of the different optimization techniques applied to FWL controllers.

In chapter 3 we deal with the binary arithmetic. First, the mostly used number formats, fixed-point and floating-point, are introduced and compared to one another with regard to the precision and dynamic range. We then introduce the most commonly used number representation systems. We insist more particularly on the two arithmetic operations  $(+, \times)$  required by linear systems.

Chapter 4 is devoted to the operation of multiplication by a constant. A range of the most frequently cited algorithms are presented, followed by the introduction of a new heuristic called RADIX-2<sup>*r*</sup>. A detailed description of the latter is given, accompanied with a discussion on the experimental results.

The same is done in chapter 5 for the variable-operand multiplication. We first describe the most advanced high-radix multiplication algorithms, and then we introduce a series of new high-radix algorithms and show how to extract the optimal one. Next, we discuss the experimental results. The same presentation scheme is applied to multi-precision multiplication.

In chapter 6, we apply the results of research developed in the previous chapters on the PID and LQG controllers with Kalman's filter.

Finally, we provide some concluding remarks on the accomplished work. We comment its strengths and weaknesses, and propose a roadmap for the continuation of the project of embedded electronics for MEMS.

#### Bibliography

- [1] E. Manmasson et *al.*, "FPGA in Industrial Control Applications," IEEE Trans. on Industrial Informatics Journal, vol. 7, N° 2, pp. 224-243, May 2011.

- [2] R. Casanova et al, "Integration of the Control Electronics for a mm<sup>3</sup>-sized Autonomous Microrobot into a Single Chip," Proceedings of the IEEE International Conference on Robotics and Automation (ICRA'09), pp. 3007-3012, Kobe, Japan, May 12-17, 2009.

- [3] M. Boudaoud, "Commande en Effort d'une Micropince en Actionnement Electrostatique," Master Thesis, AS2M Department, FEMTO-ST, Besançon, July 2009.

Chapter 2

# **Problem Background**

#### **Chapter 2**

#### **Problem Background**

In this chapter, we first define the application context of the thesis and then give the state-of-the-art of each topic involved. We describe the main characteristics of the micromanipulation domain as a MEMS application, followed by a survey of hardware integration solutions adapted to the embedded control. We examine the solution space with regard to the MEMS requirements and select, wherever possible, the best option that leads to an optimized implementation of the controller. The selection is carried out depending on the control-bandwidth, the power consumption, and the precision of calculation.

#### 2.1 Application Context

MEMS (Micro-Electro-Mechanical Systems) technology dates back to the discovery of the piezoresistive effect in silicon and germanium at Bell Labs in early 1950s [1]. It combines lithographically formed mechanical-structures with electrical elements to create physical systems that operate on the scale of microns. A MEMS is defined as a system of micrometric dimension (less than 100  $\mu$ m) incorporating at least two of the following features: sensor, signal processing electronics, actuator, power or transmission. Over the last 60 years, an impressive variety of MEMS devices were developed, constantly pushing the boundaries of physics, mechanics, electronics, and control theory.

Microrobotics is one of the MEMS applications. It is the field of miniature robotics, in particular mobile robots with characteristic dimensions less than 1mm. Microrobots [2] and Micromanipulators [3] are two outstanding examples of MEMS devices, dedicated to work in the micro-world. At this scale, the systems should have accuracy and resolution that are better than one micron.

The AS2M department of FEMTO-ST is specialized in micromanipulation/microassembly applications. For their setups, researchers use bulky equipments (typically standard PC and additional electronic cards) to control the developed micromanipulators. This constraining environment makes any mobile utilisation difficult. One of the smallest components of the micromanipulator is the end-effector. In most cases, this is a micro-gripper. It becomes really interesting if the microgripper can be easily changed for the adaptation to a new task. Therefore, the solution is to integrate the control electronics within the MEMS part to obtain some sort of a "plug-and-play" micro-gripper. However, the implementation of this solution requires advanced skills in hardware integration. For such a purpose, a collaboration project between FEMTO-ST and CDTA has been established in 2010. It aims at exploring and proposing appropriate solutions for the hardware integration of the control part of the micro-gripper. The present thesis is a part of this collaboration project.

However, controlling structures at the scale of micron is not only challenging from the modeling and control-law point-of-view, but also *computationally* challenging [4], mainly for three reasons:

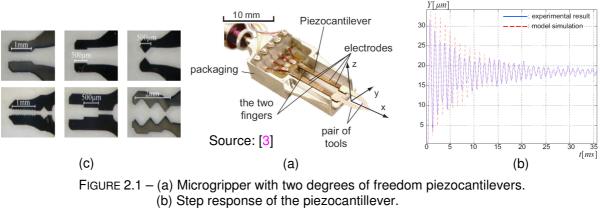

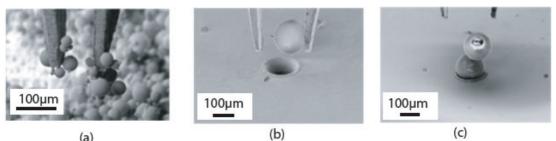

• These miniature devices are capable of extremely fast movements, requiring very high control bandwidth to ensure their stability. For instance, in [3] a micro-gripper with two degrees of freedom piezocantilevers is proposed (Fig. 2.1a). It is dedicated to applications where both

high performance and high dexterity are required. Such a micro-gripper presents a strong coupling between the two axes. In addition, it is very oscillating and strongly nonlinear (hysteresis and creep). All these problems are compensated using additional control/filtering techniques that require more computational time. Thus, the stability is guaranteed only if enough computational power is provided. To give an order of magnitude, the dynamic of the piezocantilever is typically controlled with a sampling time of <u>20µs</u> (Fig. 2.1b).

- With small physical sizes and high resolution come low tolerance to error, and therefore a need for a high computational control precision. For instance, in micromanipulation and microassembly, fixing a micro-lens at the tip of an optical fiber with 1µm of relative positioning error or 0.4µrad of orientation error, may cause a loss of 50% of the light flux [3].

- The reality is that most of the MEMS devices are embedded in autonomous equipments which are bound by power and size constraints. This dictates the use of power-efficient solutions in control and in the implementation of the controller as well. A typical example is the mm<sup>3</sup> robots [2], called I-SWARM. It is a real autonomous mobile micro-robot; powered by solar cells, equipped with a locomotion unit for moving, an infra-red unit for communication, and a contact tip for detecting near objects. The whole is managed by a *low-power* ASIC, which is in fact a real system-on-chip (SoC) solution.

(c) Terminal parts of the microgripper.

Consequently, in addition to an advanced modeling and control, *high-speed*, *low-power*, and *high precision of calculation* are mandatory for the MEMS control. In the case of an embedded control, which is the purpose of this thesis, the precision of calculation becomes even a more severe constraint, harder to satisfy without compromising speed and power. This is essentially due to the utilization of fixed-point numbers which are an *approximation* of real numbers. The fixed-point format is dictated in embedded applications for its high-speed and low-power features.

Obviously, this thesis does not have the pretention to address all issues related to embedded control for MEMS. Such a complex and substantial problem would require a series of complementary works. The objective is rather restricted only to the determination of a suitable binary arithmetic that conciliates into a good compromise speed, power, and precision, while preserving satisfactory control performances.

Because micromanipulation is the MEMS application domain to which the proposed arithmetic is applied, a brief summary of its characteristics is given hereafter for a better understanding of the real *control* challenges.

#### 2.2 Micromanipulation as a MEMS application

Micromanipluation addresses the problem of gripping, handling, moving, and placing objects of micrometric sizes. During the last decade, the need for micromanipulation systems (Fig. 2.1) with micro/nanometers accuracy and fast dynamics has been growing rapidly [5]. Such systems occur in applications including:

- Manipulation of biological elements in medicine and biotechnology (micro-organisms, cells, DNA, etc.).;

- Assembly of micromechanical rigid parts (micro sprocket wheels, optical micro lens, hybrid circuits, etc. );

- Micro/ Nano-sensors for environnemental monitoring;

- Metrology and nanometer resolution imaging (AFM and SEM);

- Study of micro-world phenomena, such as adhesion forces.

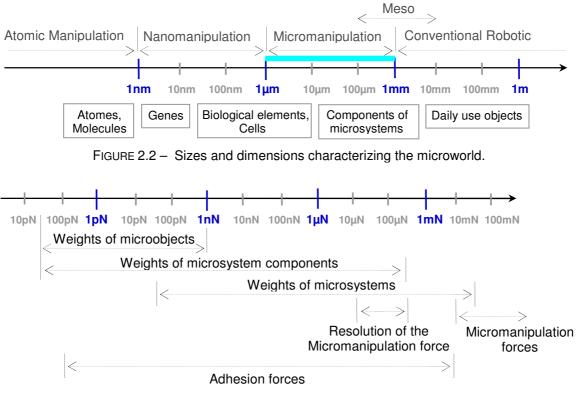

Before exposing the major problems pertaining to the microworld, it is useful to have a precise idea on the order of magnitude in size and weight of the physical entities manipulated (Fig. 2.2 and 2.3).

Force and position measurements are very important to perform micromanipulation and microassembly tasks. Small components are often fragile (e.g. biological cells) and may be damaged or destroyed if they are grasped without force *control*.

FIGURE 2.3 – Some force spans characterizing the microworld.

Working in the micro/nano-world involves displacements from nanometers to tens of microns [6]. Because of this precision requirement, environmental conditions could generate noise and disturbance that are in the same range as the desired displacements (very low signal/noise ratio). These environmental conditions include: thermal variation; vibration; air-flow; and humidity.

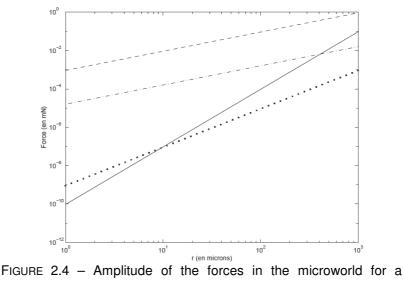

In fact the forces that come into play at the micro level are different from those at the macro level. This is due to what is commonly called the scale effect [7]. Indeed, when the size becomes small enough, the surface effects become dominant over the volume effects. Gravity, which is often relied on in control and assembly of macro systems, plays only a minimal role at the micro level. Instead, the dominant forces are (Fig. 2.4):

- Electrostatic forces (F<sub>elec</sub>) generated by tribo-electrification and charge transfer during the contact;

- Surface-tension forces (F<sub>tens</sub>) between the two contacting elements, related to the level of humidity;

- Van der Waal's forces (F<sub>Vdw</sub>, atomic forces).

There is also another kind of problems related to uncertainties. It is interesting to note that because of adhesion forces, that still remain difficult to control, the equations of the dynamics and kinematics of the micro-objects are subject to uncertainties, so that the movements are unpredictable. The uncertainties are also due to the limited performances of the sensors. To handle a micro-object, the required accuracy is the tenth of the size of the micro-object in the worst case, and the resolution is equal to 1/n times of the precision (n>1). At present, propose force and position sensors with such a performance and a suitable size remains a challenge [8]. Precise position sensors already exist, such as interferometers, but their size is not suitable (bulky).

Another problem of the scale-effect is the inability to directly use the human sight sense in the microworld. A microscope-camera system is often used to monitor micromanipulation tasks. Fully automated or remotely operated, these systems are equipped with a micromanipulation screen, enabling the human operator to intervene [9].

microsphere of radius  $r(F_g: - ; F_{tens}: - - ; F_{Vdw}: - - ; F_{elec}: ... ).$

The specific complexities of the microworld (adhesive forces) added to the lack of appropriate sensors is a real challenge that is far from being mastered [6]. The capture and release by a microgripper of "sticky" parts (Fig. 2.5) is a hard problematic issue [6][7][10][11][12].

Because of all these difficulties, the design of micromanipulation systems (Microgrippers) must offer the best performance in terms of accuracy and resolution. As to their use, it must reproduce as accurately as possible the user commands. In order to respond to this double requirement, there is an increasing resort to use:

- Smart materials such as piezoceramics [5][6][13], magnetostrictive, shape memory, electroactive polymer, are used to develop microactuators, microrobots, micromanipulators and Microsystems;

- Robust control techniques (both in theory and implementation) based on closed-loop feedback [14][15] combined with advanced filtering techniques [8].

FIGURE 2.5 – Micromanipulation problem due to adhesion forces. (a): Difficulty to grip microobjets; (b): Problems in placing a micro-object; (c): difficulty of positioning a micro-object due to adhesion forces created by surrounding micro-objects.

#### 2.3 Embedded Control-Electronics for MEMS

The literature on the control issue of MEMS/NEMS systems is so extensive, but all proposed solutions fall into two distinct categories:

- Analog controllers: that is, implementing the controller as an active analog feedback circuit. Used to be the primary method of implementing controllers before digital systems of sufficient performance became widely and cheaply available. This type of controllers presents numerous challenges since analog systems are more difficult to design (requiring careful control of all active components), implement (especially in modern low-cost processes optimized for digital systems), and maintain (there is not possibility of "patching" the system). Furthermore, the physical complexity of modern mechanical devices may require modal control that cannot be implemented by a single analog controller [4].

- Digital controllers: due to the above shortcomings of analog controllers and aided by the fulgurous progress in semiconductor technology (transistor size shrinking) [16], tightly integrated solutions that combine high-performance power of digital processing with accurate sensors are used (*closed-loop control*).

To provide stable and robust control, a digital control system must be able to measure the process variables and set actuator output command within a fixed period of time (loop-cycle time). However, recent experience of MEMS/NEMS developers [4] has shown that the *state-space representation* [17] [18] is being extensively applied across a wide variety of MEMS devices for two reasons:

- Its relative ease in determining stable control equations;

- It forms the basis for many more complex control techniques;

- Its recursive behaviour is suitable for a digital implementation.

Hereafter, are the discrete state-space equations for LTI and LTV, respectively:

Explicit discrete time-invariant

$$\begin{aligned} x(k+1) &= A \cdot x(k) + B \cdot u(k) \\ y(k) &= C \cdot x(k) + D \cdot u(k) \end{aligned}$$

(2.1)

Explicit discrete time-variant

$x(k+1) = A(k) \cdot x(k) + B(k) \cdot u(k)$  $y(k) = C(k) \cdot x(k) + D(k) \cdot u(k)$ (2.2)

where:

- $x(\cdot)$  is called the "state vector",  $x(t) \in \Re^n$ ;

- $y(\cdot)$  is called the "output vector",  $y(t) \in \Re^q$ ;

- $u(\cdot)$  is called the "input (or control) vector",  $u(t) \in \Re^p$ ;

- $A(\cdot)$  is the "state (or system) matrix",  $dim[A(\cdot)] = n \times n$ ;

- $B(\cdot)$  is the "input matrix",  $dim[B(\cdot)] = n \times p$ ;

- $C(\cdot)$  is the "output matrix",  $dim[C(\cdot)] = q \times n$ ;

- $D(\cdot)$  is the "feedthrough (or feedforward) matrix",  $dim[D(\cdot)] = q \times p$ .

A depth in-sight into state-space equations reveals that the computation pattern is mainly based upon:

- *Matrix Multiplications (MMs)*, which involve the use of the elementary but time-critical multiplyand-accumulate (*MAC*) operation [19][20] in the case of LTV systems, and SCM/MCM in the case of LTI systems;

- And a limited movement of data between temporary storage elements (load/store of data from/in memory and registers).

The computational overhead is maximal when digital controller is performing these operations, more especially when it is performing MMs. Hence the sampling-rate (*performance*) is limited by the rate at which the device performs these computations. However, the high potential of parallelism inherent in MM suggests that significant performance improvements can be achieved [21][22] by providing increased architectural parallelism.

The number of elementary scalar operations (MAC, SCM/MCM) involved depends on the *control complexity*, based on:

- The number of state variables that fixes the dimension of the matrices;

- The number of I/O required;

- And, the density of the matrices (the use of sparse and insensitive matrices wherever possible considerably reduces the computation complexity);

With time constants several orders of magnitude faster than their non-MEMS counterparts, many MEMS devices require *control-bandwidth* and accuracy exceeding the ability of conventional digital solutions [4]. On the other side, for autonomy purposes and size constraints [2], many MEMS devices dictate the use of *low-power* consumption solutions. There is a trade-off between performance and power consumption that is quite critical.

The important question that arises at this stage is: with a plethora of available solutions for digital embedded control [23][24][25][26][27][28], which one fits the best MEMS application requirements?

This question can be quickly answered for the most part by looking to the pros and cons of existing solutions with respect to the above-mentioned severe antagonistic constraints (high performance & low power consumption), but the ultimate solution must be tightly tailored to the application case according to the intended objectives.

#### 2.4 Review of the Basic Digital Solutions for Embedded Control

The current state-of-the-art [24][16] of embedded solutions offers mainly four possibilities based on the use of:

- Commercial Off-The-Shelf (COTS) electronics components. This includes general purpose microprocessors and microcontrollers;

- Digital-Signal-Processors (DSPs) such as the TMS320C55x [29] and TMS320C64x [30], which are respectively the lowest power and the highest performance DSP available [15];

- Field-Programmable-Gate-Array (FPGAs) such as Xilinx's [31] and Altera's [32] FPGAs;

- Application-Specific-Integrated-Circuits (ASICs) which are chips designed from scratch according to a given technology foundry (e.g. TSMC 90 nm).

Let us examine in detail the pros and cons of each solution, focusing more particularly on the MEMS control requirements.

#### 2.4.1 Commercial Off-The-Shelf (COTS) Electronics Components

The common measure of control system performance and robustness is *jitter*, which is a measure of the variation of the actual loop cycle-time from the desired loop cycle-time. However, the *nondeterminism* in the execution of microprocessors makes static timing boundaries difficult to determine and limits reliable bandwidth. This is mainly due to three reasons:

- In a general purpose microprocessor, the processor resources are held up while it is busy performing the MAC operations and the speed or the sampling rate is decided by the latency of these instructions;

- Additionally, priority interrupts and bus contention contribute to the nondeterminism encountered in typical microprocessors or microcontrollers [24][27].

- Worse enough, in general-purpose operating systems (OS) such as Windows (Ex: PC based control platform) where the microprocessor is programmed to handle multiple asynchronous tasks, the jitter becomes exaggeratedly unbounded (*random*) so closed-loop control system stability cannot be guaranteed [33]. Processor-based control systems with real-time operating systems (RTOS) are commonly able to guarantee control-loop jitter of less than 100 microseconds.

#### 2.4.2 Digital Signal Processors (DSPs)

DSP are mainly differentiated from general purpose microprocessors by additional parallelism [24][25]. For instance, the TMS320C64x is a VLIW architecture with eight execution units, including four multipliers and four ALUs [30]. Using its eight execution units, the processor can execute up to

eight 32-bit instructions in a single clock cycle (up to 1GHz), allowing it to achieve a high level of parallelism. The TMS320C64x is able to perform four 16-bit multiplications in parallel. All execution units in the TMS320C64x have a throughput of one cycle and latencies from one to several cycles depending on the instruction.

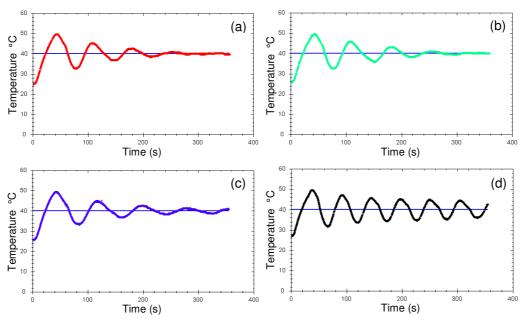

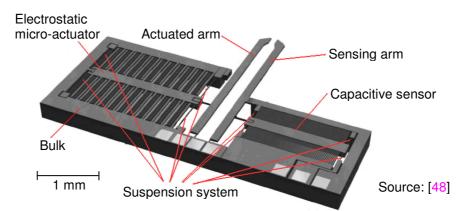

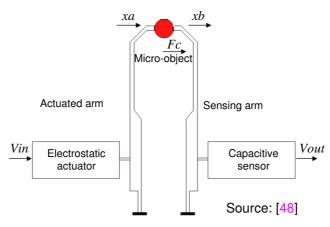

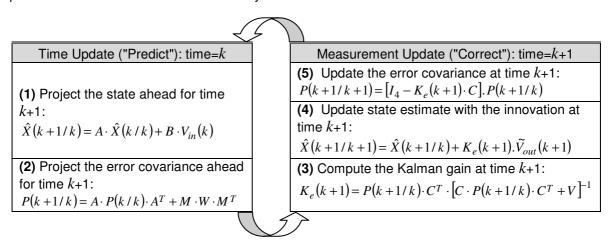

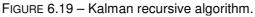

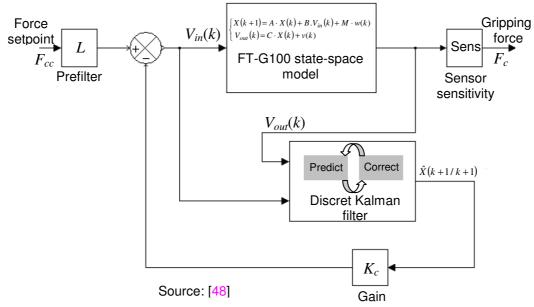

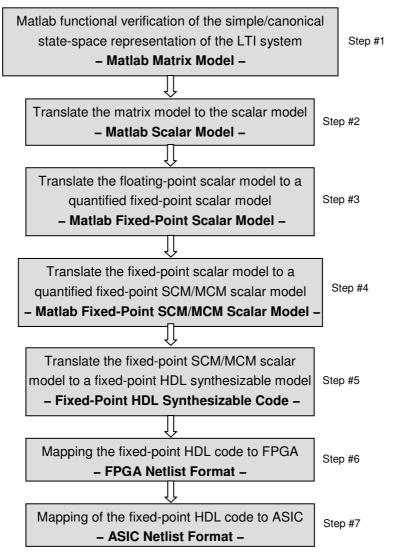

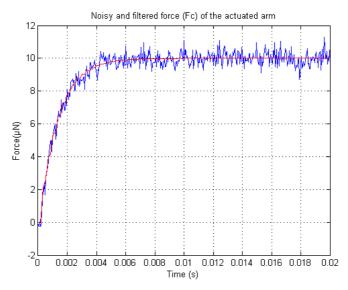

To date, for sound/image/video applications, conventional DSPs have provided more than adequate bandwidth, with consistent performance gains from feature scaling [16] and added architectural parallelism. However, for this new class of control applications (MEMS), the *latencies* that are inherent to many DSP architectures limit the achievable control bandwidth which refers to the throughput of the controller as each state-space time step is dependent on the last. The latency becomes then a critical aspect. Further, MEMS systems, by nature, are small in size and complexity, resulting in simple control computations that must be performed at very high rates [34]. For small control systems, the benefits of added parallelism in high performance DSPs fails to mitigate the complexity and performance overhead of the architecture. In other words, DSP architecture is oversized for MEMS applications.