# Development of a CMOS pixel sensor for embedded space dosimeter with low weight and minimal power dissipation

Yang Zhou

#### ▶ To cite this version:

Yang Zhou. Development of a CMOS pixel sensor for embedded space dosimeter with low weight and minimal power dissipation. Micro and nanotechnologies/Microelectronics. Universit\'e de Strasbourg, 2014. English. NNT: 2014STRAE021. tel-01126914

### HAL Id: tel-01126914 https://theses.hal.science/tel-01126914

Submitted on 6 Mar 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### UNIVERSITÉ DE STRASBOURG

# ÉCOLE DOCTORALE DE PHYSIQUE ET CHIMIE PHYSIQUE Institut Pluridisciplinaire Hubert Curien (IPHC)

## THÈSE présentée par:

Yang ZHOU

soutenue le : 23 Septembre 2014

pour obtenir le grade de : Docteur de l'Université de Strasbourg

Discipline: Électronique, Électrotechnique et Automatique

Spécialité: Instrumentation et Microélectronique

# Development of a CMOS pixel sensor for embedded space dosimeter with low weight and minimal power dissipation

#### Composition du jury:

Directeurs de thèse: M. Yann HU Professeur, Université de Strasbourg

M. Jérôme BAUDOT Professeur, Université de Strasbourg

Rapporteurs externes: M. Michel PAINDAVOINE Professeur, Université de Bourgogne

M. Martin POHL Professeur, Université de Genève

Examinateurs: M. Rémi BARBIER Maître de Conférences, Université de Lyon

M. Olivier DORVAUX Maître de Conférences, Université de Strasbourg

# Acknowledgements

I am very grateful to my supervisors Prof. Yann Hu and Prof. Jérôme BAUDOT for their support, guidance and encouragement, and for the opportunities provided to me. I would also like to thank China Scholarship Council (CSC) and Prof. Marc Winter, the leader of PICSEL group, for funding my 4 years study in France.

I sincerely appreciate Prof. Jérôme BAUDOT for his guidance and fruitful discussions in the physics part, offering the analysis of the prototype test results, and providing the corrections and suggestions for this manuscript. I would also like to thank Cyril Duverger, a master student in physics, for his contribution in the Monte-Carlo sensor response simulations of this work.

I would like to thank all the colleagues in microelectronics group: Christine Hu-Guo, Claude Colledani, Wojciech Dulinski, Xiaochao Fang, Andrei Dorokhov, Frédéric Morel, Maciej Kachel, Abdelkader Himmi, Yunan Fu, Ying Zhang, Wei Zhao, Tianyang Wang, Isabelle Valin, Hung Pham, Guy Doziere, Christian Illinger and Sylviane Molinet for their suggestions, helps and technical supports during the sensor design.

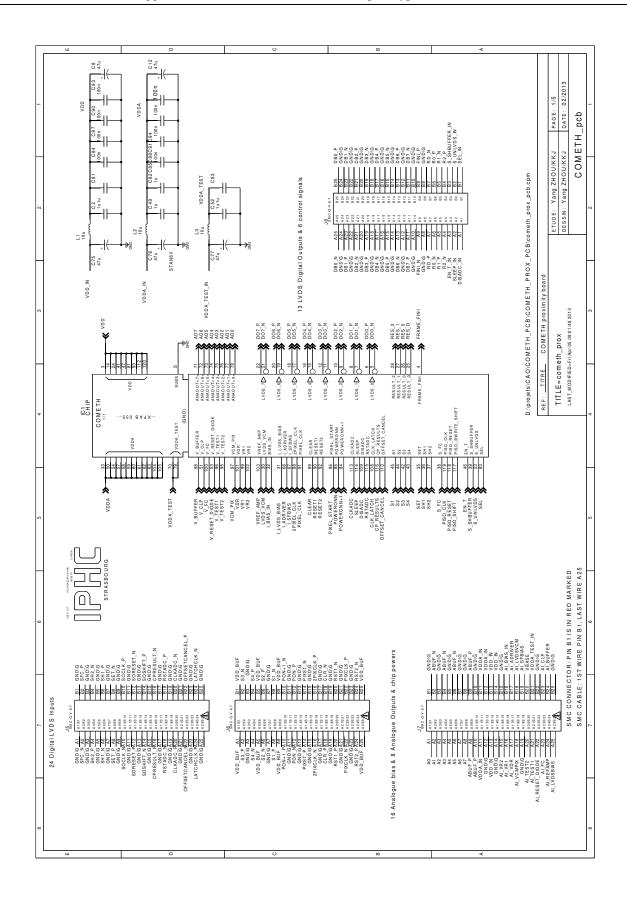

I owe my gratitude to Kimmo Jaaskelainen for his fully support during the test of the prototype, including the PCB design and test bench set up. I also appreciate Gilles Claus and Mathieu Goffe for their suggestions and helps during the prototype test.

Last but not least, I would like to thank my parents for their unconditional love, support and understanding.

Strasbourg, 09/10/2014

# Contents

| Table of Contents                                   | i  |

|-----------------------------------------------------|----|

| List of Figures                                     | V  |

| List of Tables                                      | ix |

| Résumé en Français                                  | 1  |

| Introduction                                        | 13 |

| 1 Ionization based particle detection               | 17 |

| 1.1 Interactions of particles with matter           |    |

| 1.1.1 Interaction of electrons                      |    |

| 1.1.2 Interaction of protons and ions               | 20 |

| 1.1.3 Interaction of photons                        | 22 |

| 1.2 Properties of Radiation Detector                | 23 |

| 1.3 Silicon detectors                               | 26 |

| 1.3.1 Silicon detector physics                      | 26 |

| 1.3.2 Radiation damages                             | 30 |

| 1.3.3 Single diode detectors                        | 33 |

| 1.3.4 Pixelated detectors                           | 33 |

| 1.4 Conclusion                                      | 38 |

| 2 MAPS for particle tracking detection              | 42 |

| 2.1 Specifications for particle tracking            | 42 |

| 2.1.1 Physics goals Driven Specifications           | 43 |

| 2.1.2 Environment Driven Specifications             | 43 |

| 2.2 MAPS technology                                 | 44 |

| 2.2.1 Global architecture and fast readout strategy | 45 |

| 2.2.2 Basic pixel architectures                     | 46 |

| 2.2.3 Sources of Noise in MAPS                      | 48 |

| 2.3 MIMOSA 26                                       | 51 |

| 2.3.1 Pixel                                         | 52 |

| 2.3.2 Analogue to Digital Conversion                | 53 |

| 2.3.3 Zero suppression                              | 54 |

| 2.3.4 Performances                                                                         | 54  |

|--------------------------------------------------------------------------------------------|-----|

| 2.4 Conclusions                                                                            | 55  |

| 3 Space radiation monitoring                                                               | 58  |

| 3.1 The energetic particle environment                                                     | 58  |

| 3.2 Space radiation monitors                                                               | 60  |

| 3.2.1 The Geiger-Mueller tube                                                              | 61  |

| 3.2.2 The Scintillating Fibre Detector (SFD)                                               | 61  |

| 3.2.3 RadFETs (MOS structures sensitive to ionizing radiation)                             | 62  |

| 3.2.4 The Standard Radiation Environment Monitor (SREM)                                    | 62  |

| 3.2.5 Pixel sensors                                                                        | 63  |

| 3.3 From measurement requirements to design specifications: simulation methods and results | 65  |

| 3.3.1 The choice of sensor sensitive area, pixel pitch size and readout speed              | 65  |

| 3.3.2 Simulation of pixel response                                                         | 67  |

| 3.3.3 Complementary Monte-Carlo simulation and estimated performances                      | 81  |

| 3.4 Conclusions                                                                            | 84  |

| 4 General COMETH architecture                                                              | 87  |

| 4.1 The analogue signal processing.                                                        | 87  |

| 4.2 Analogue to Digital conversion                                                         | 88  |

| 4.2.1 ADC definition                                                                       | 89  |

| 4.2.2 ADC Characterization                                                                 | 91  |

| 4.2.3 Specifications for the ADC used in COMETH                                            | 95  |

| 4.3 The embedded digital signal processing.                                                | 96  |

| 4.4 Global architecture of COMETH                                                          | 97  |

| 5 Analogue signal processing                                                               | 100 |

| 5.1 Pixel design                                                                           | 100 |

| 5.1.1 The CS pre-amplify stage                                                             | 103 |

| 5.1.2 The SF stage                                                                         | 106 |

| 5.1.3 The global pixel performance                                                         | 107 |

| 5.2 Test of the pixel matrix                                                               | 108 |

| 5.2.1 Experimental set-up                                                                  | 108 |

| 5.2.2 Noise performances                                                                   | 110 |

| 5.2.3 Test with the <sup>55</sup> Fe source                                                | 112 |

| 5.2.4 Test with a Beta minus source                              | 114 |

|------------------------------------------------------------------|-----|

| 5.2.5 Test with infrared laser illumination                      | 117 |

| 5.3 Conclusion and perspectives                                  | 118 |

| 6 From analogue to digital                                       | 121 |

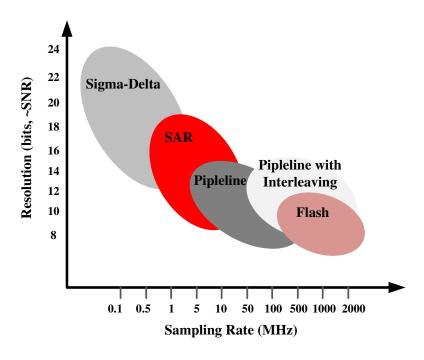

| 6.1 Standard ADC architectures                                   | 122 |

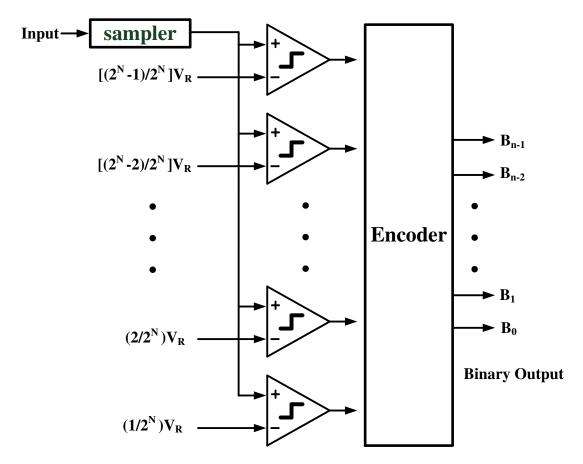

| 6.1.1 Flash ADC                                                  | 122 |

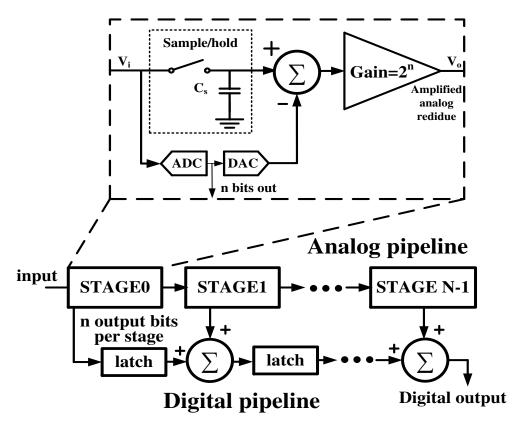

| 6.1.2 Pipelined ADC                                              | 123 |

| 6.1.3 Successive approximation ADC                               | 124 |

| 6.2 Design of the column ADC for COMETH                          | 125 |

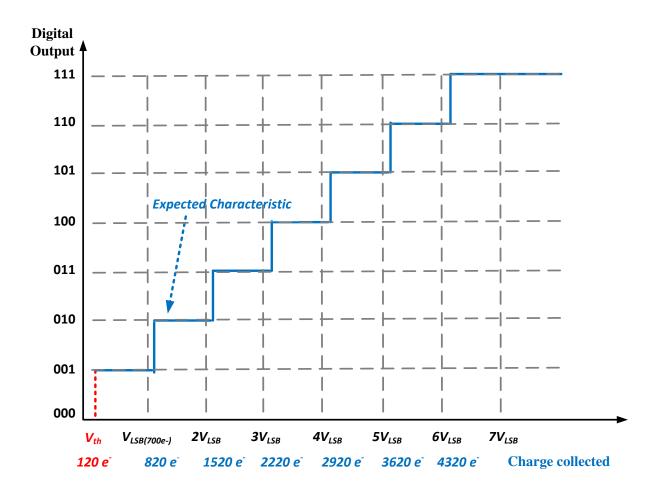

| 6.2.1 Global architecture and processing principle               | 126 |

| 6.2.2 Design of the S/H circuit                                  | 130 |

| 6.2.3 Design of the comparator                                   | 134 |

| 6.2.4 Layout and estimated power dissipation                     | 140 |

| 6.3 Test of the column level ADC                                 | 141 |

| 6.3.1 Characteristics of a single ADC                            | 141 |

| 6.3.2 Characteristics of the 32 columns                          | 142 |

| 6.4 Solutions for the ADC performance improvement                | 144 |

| 7 Embedded digital signal processing                             | 148 |

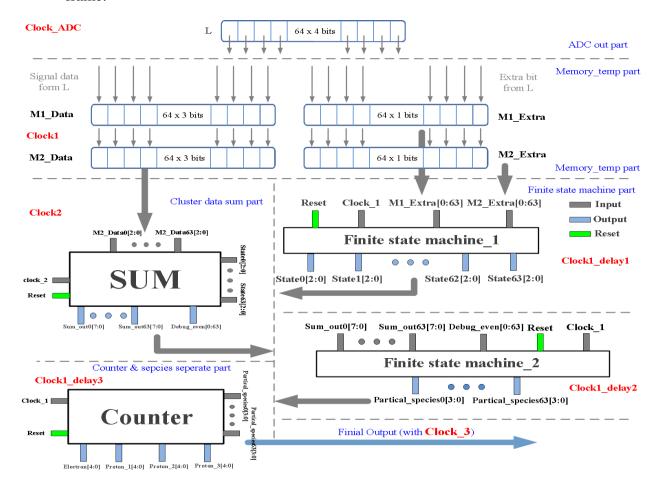

| 7.1 Operation principle                                          | 148 |

| 7.2 The hardware system                                          | 151 |

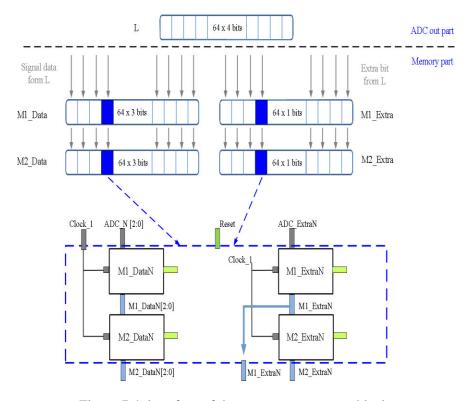

| 7.2.1 The temporary memory block                                 | 153 |

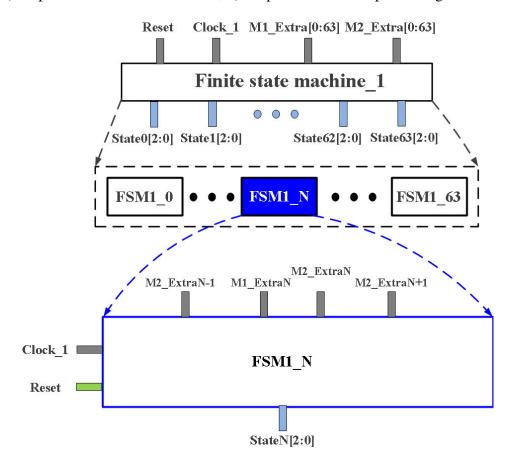

| 7.2.2 The finite state machine_1                                 | 154 |

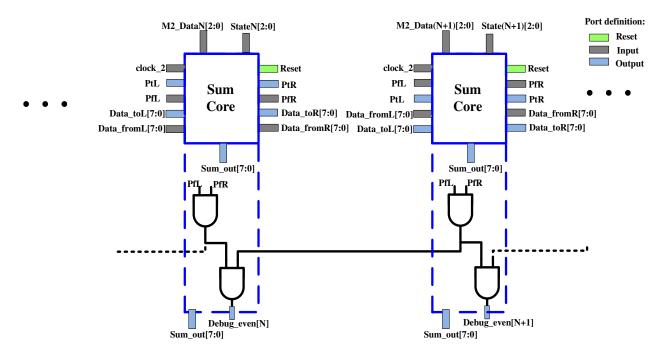

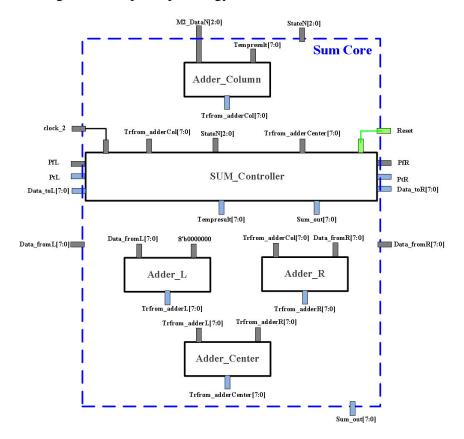

| 7.2.3 The cluster data sum block                                 | 154 |

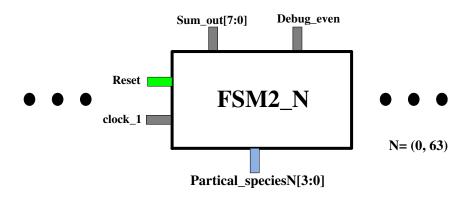

| 7.2.4 The finite state machine_2                                 | 155 |

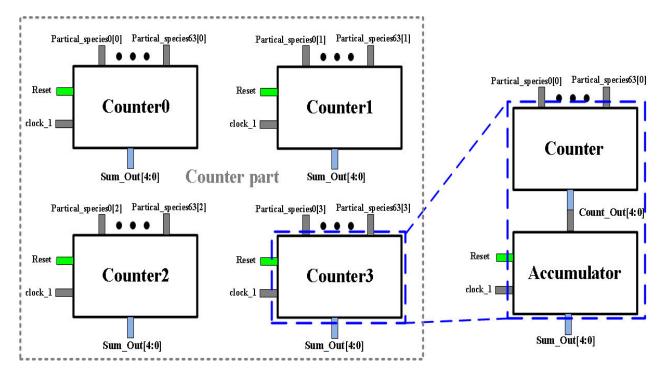

| 7.2.5 The Counter and final output                               | 156 |

| 7.2.6 Layout and estimated power dissipation                     | 157 |

| 7.3 Reconstruction performances                                  | 158 |

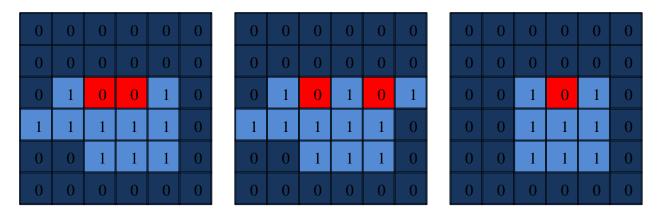

| 7.3.1 Tricky cluster cases could be reconstructed correctly      | 159 |

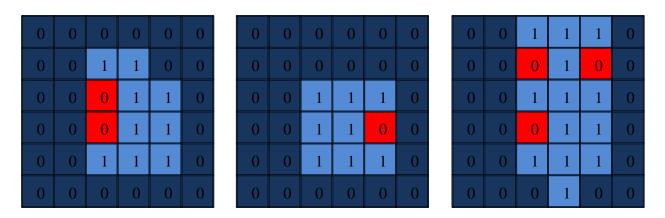

| 7.3.2 Tricky cluster cases which lead to reconstruction failures | 161 |

| 7.3.3 Performances for clusters merging                          | 162 |

| 7.4 Conclusions                                                  | 162 |

| Ceneral conclusions                                              | 164 |

#### Table of contents

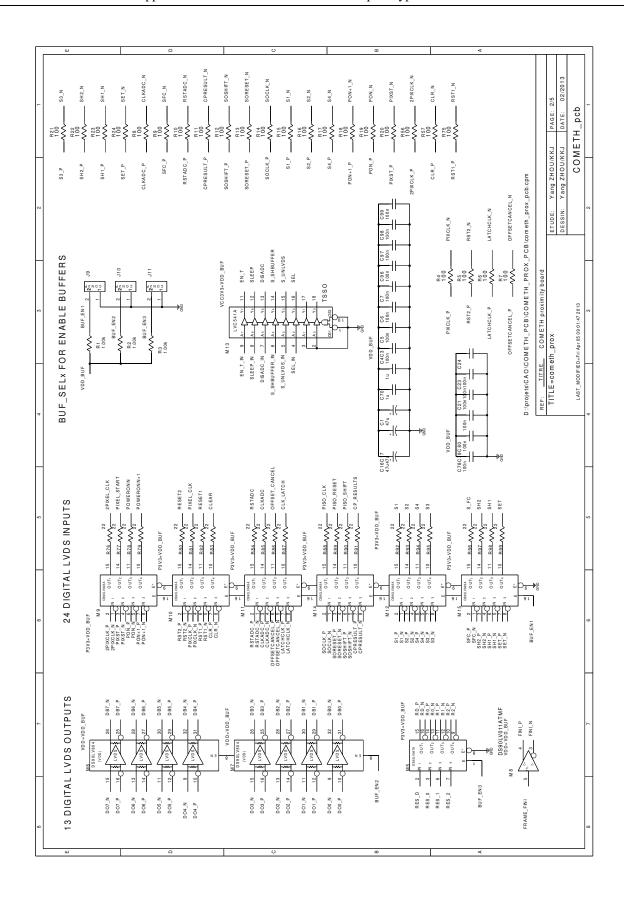

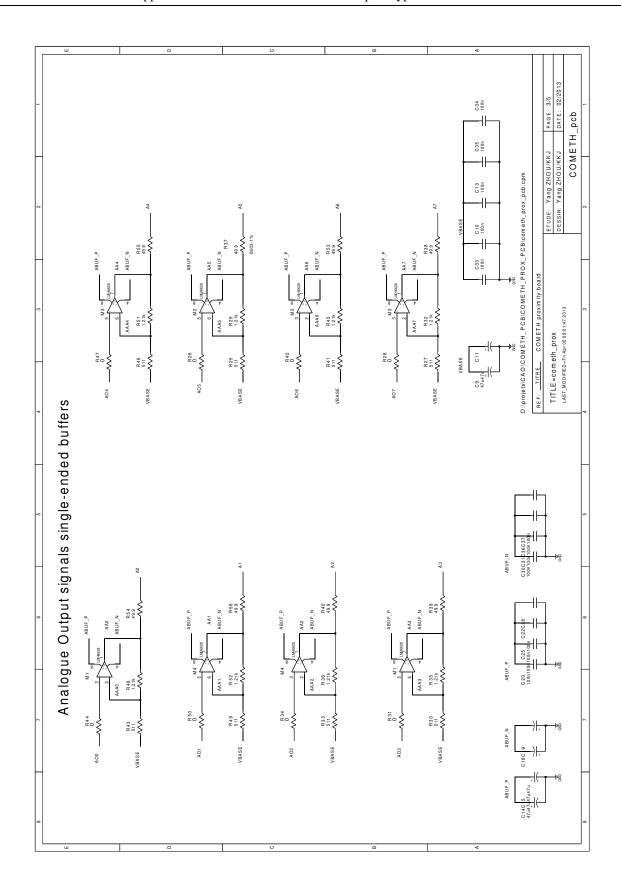

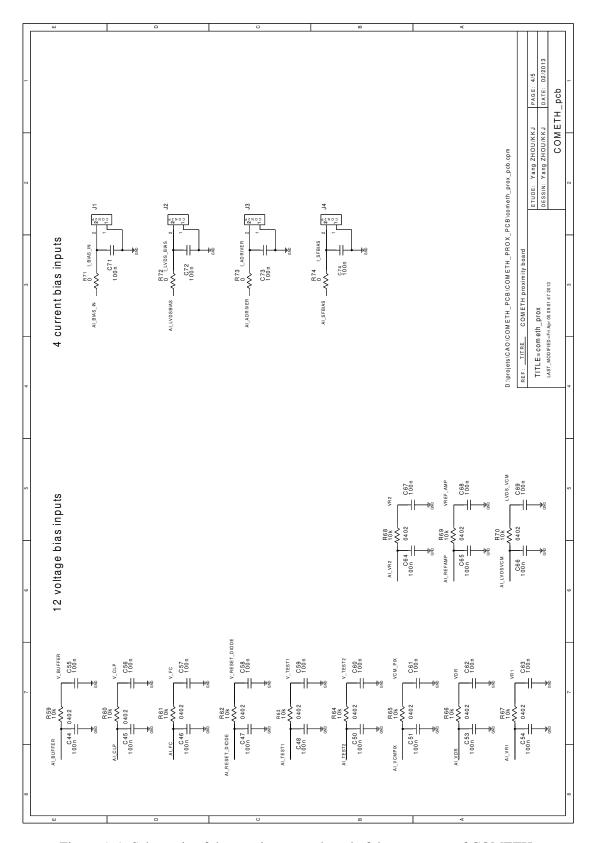

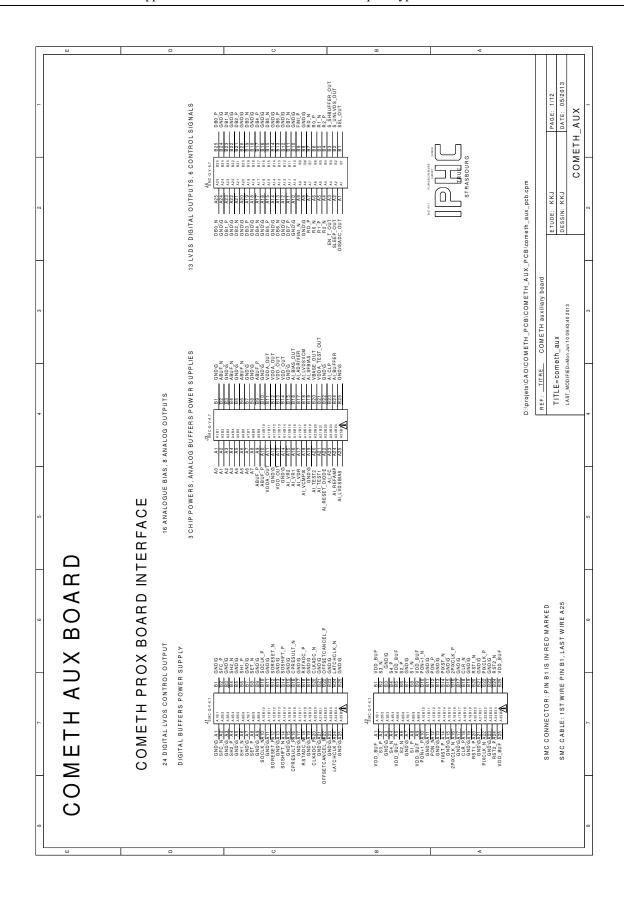

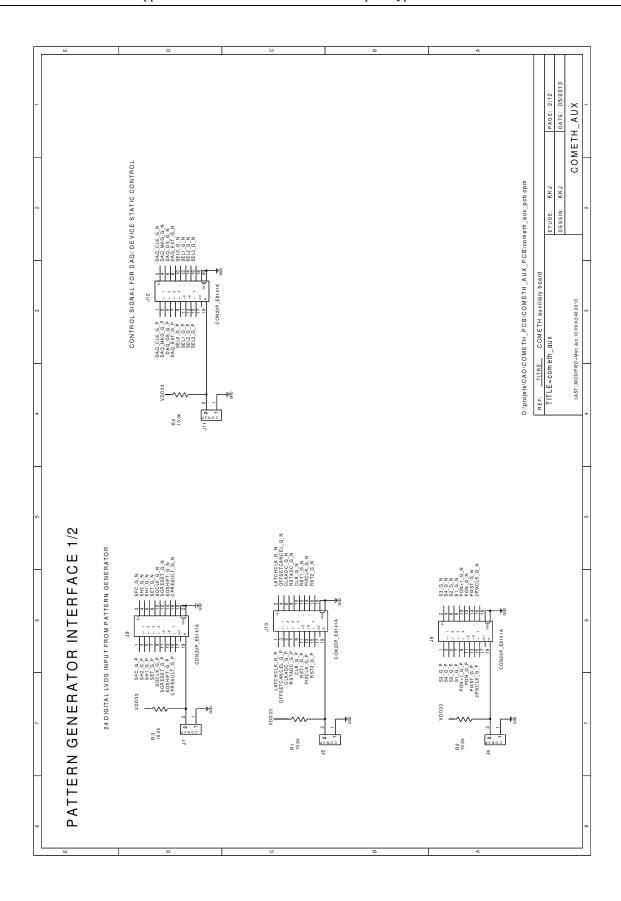

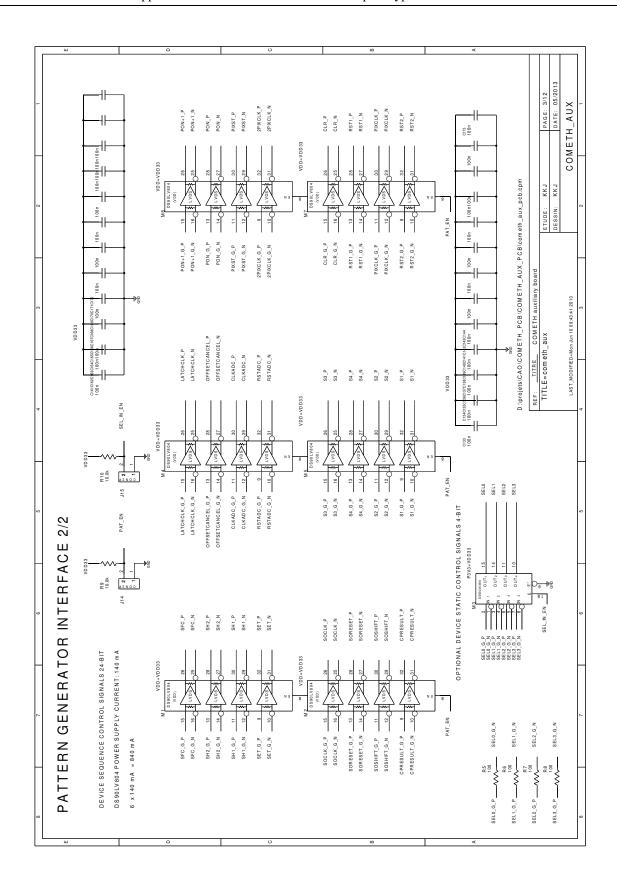

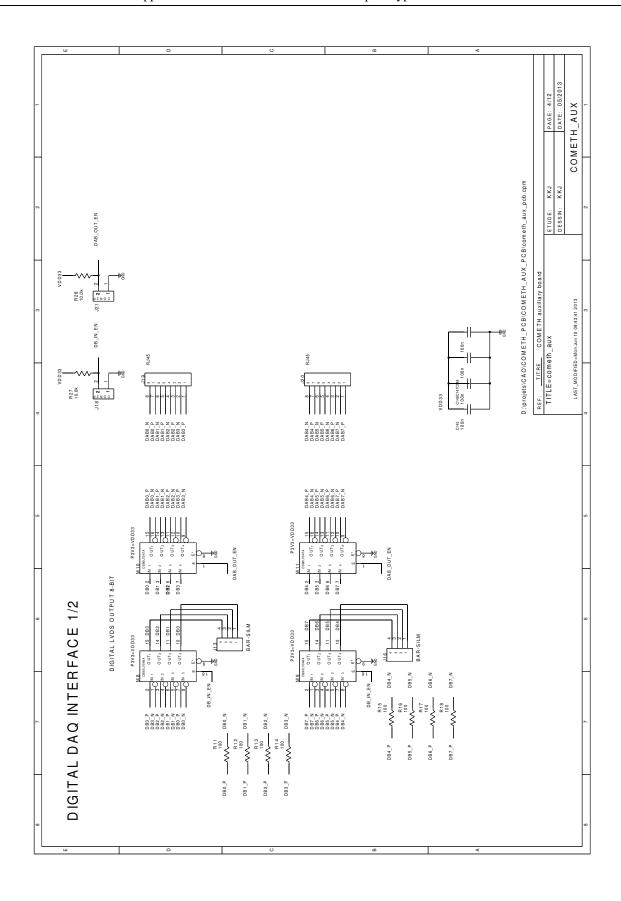

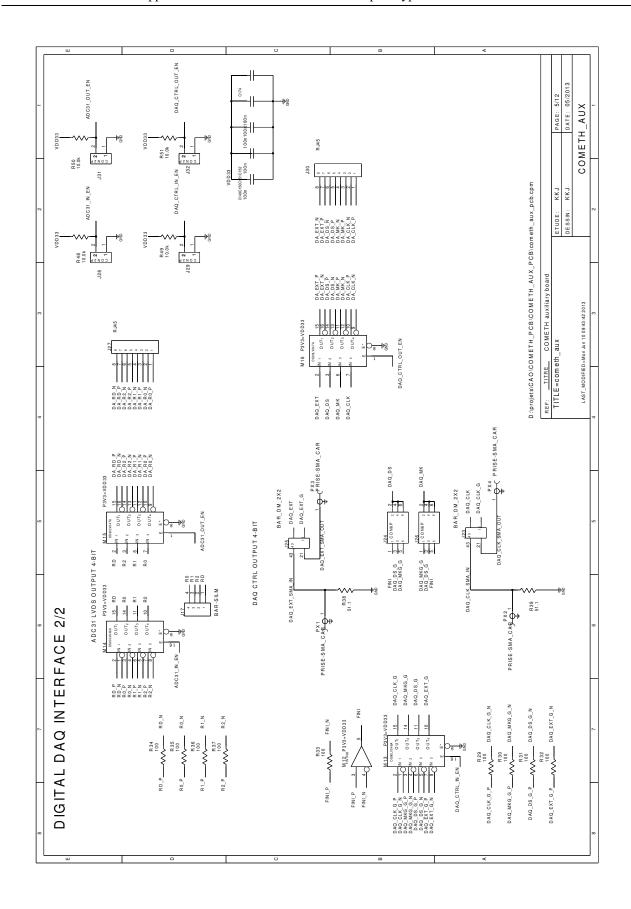

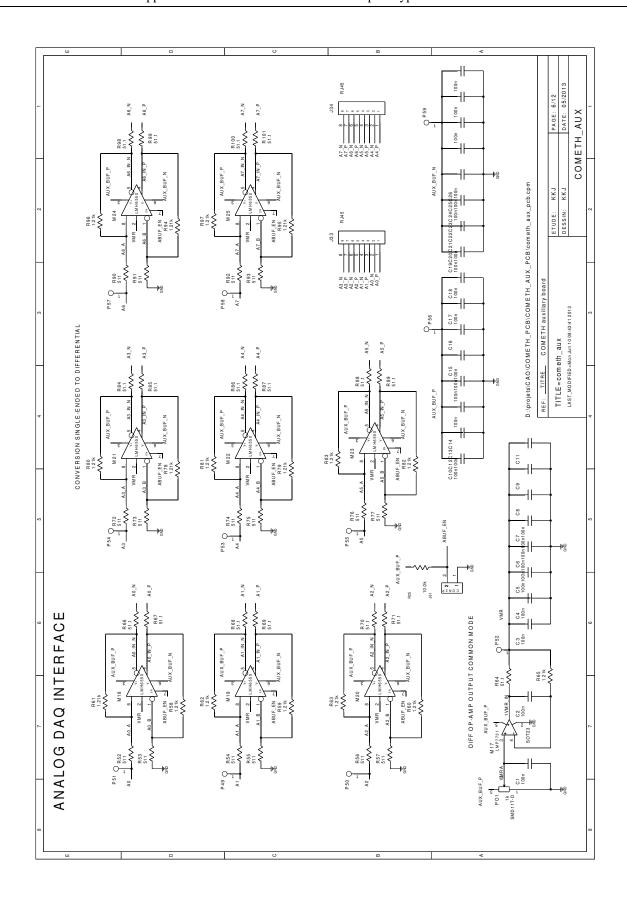

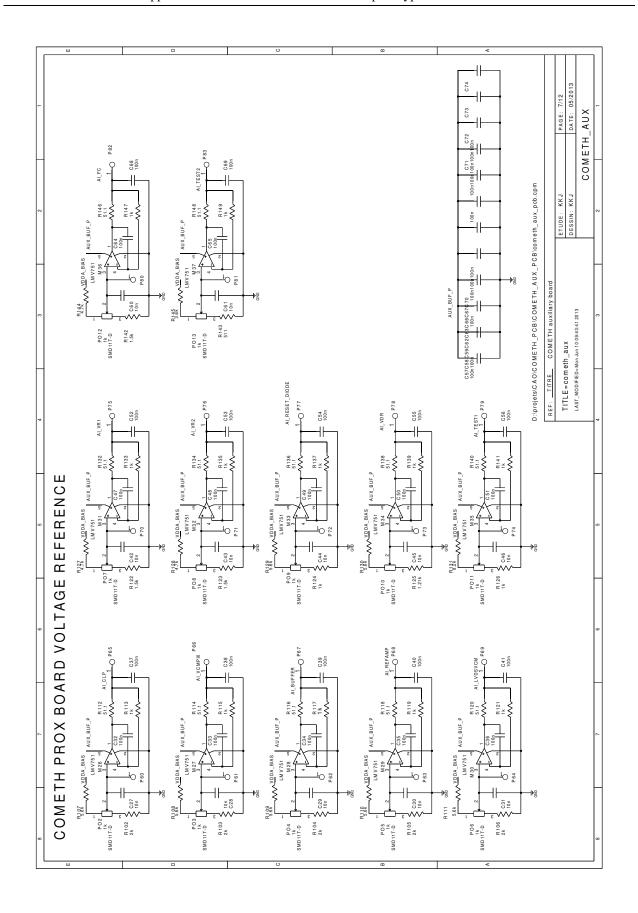

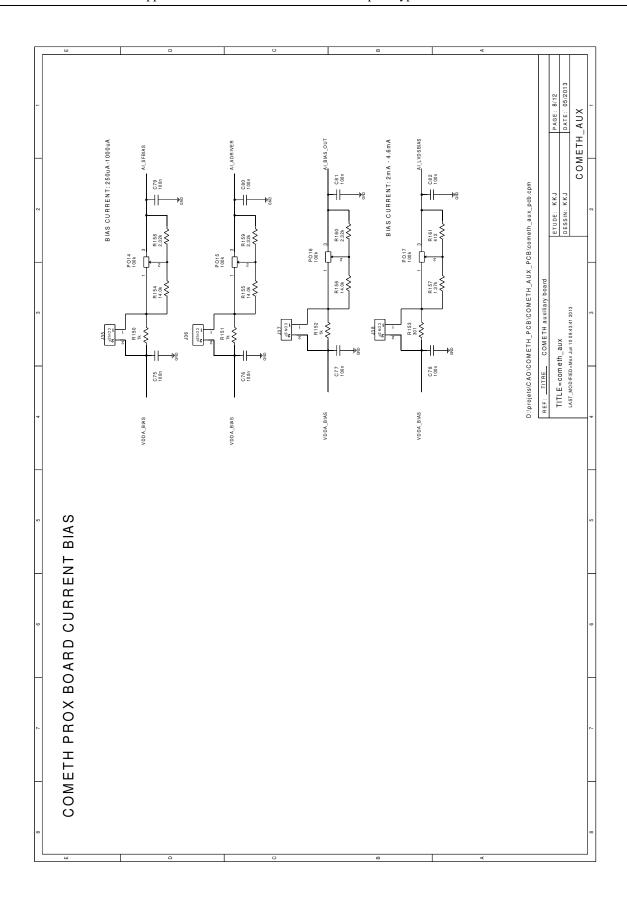

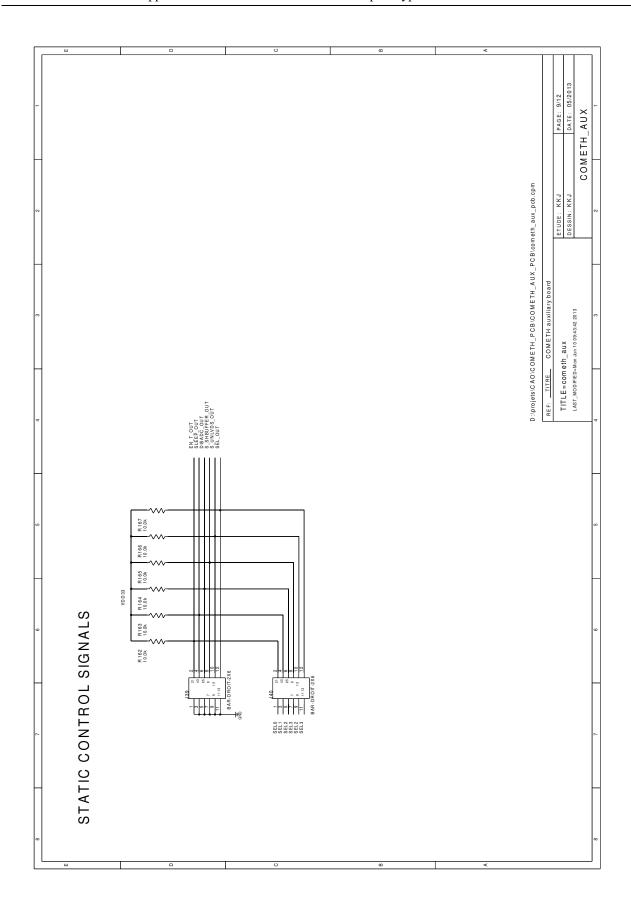

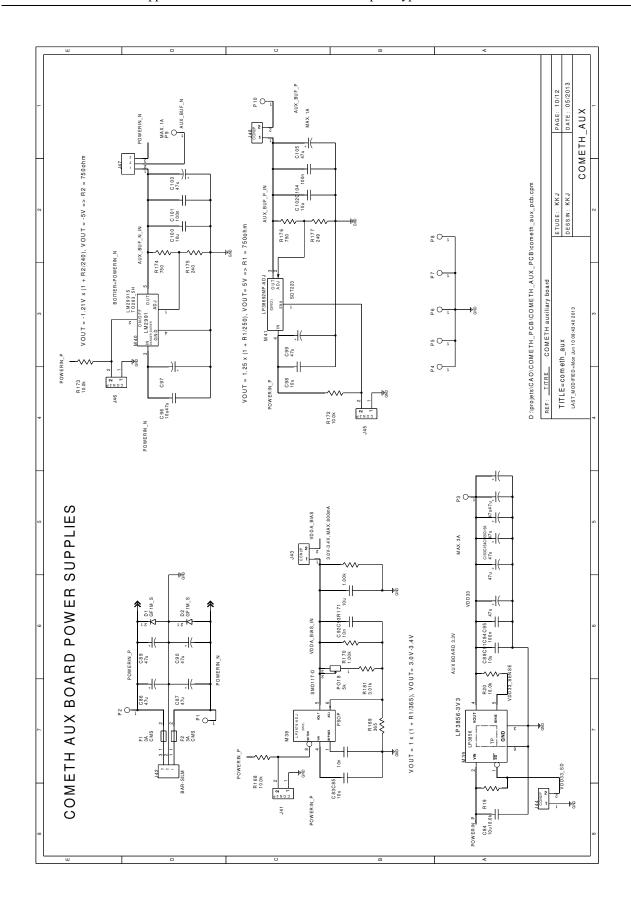

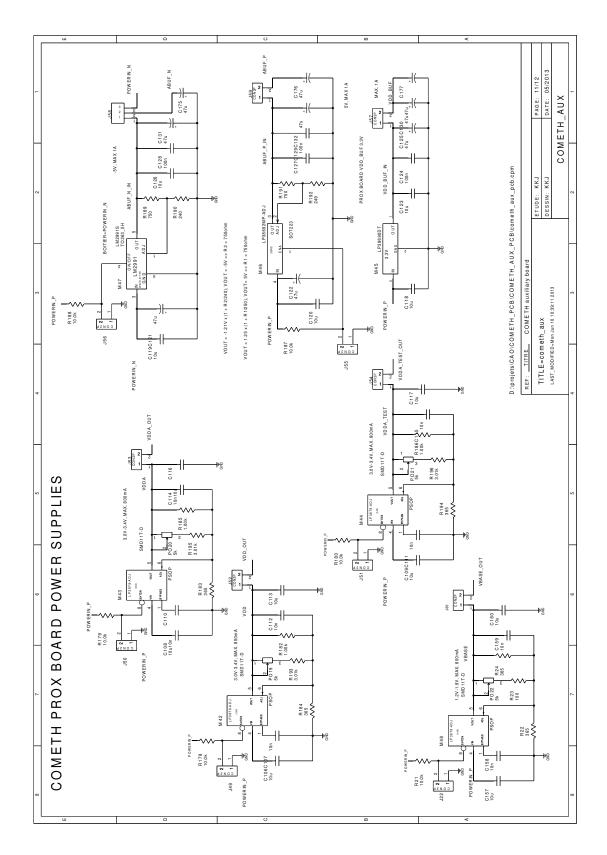

| Test board schematic for the prototype of COMETH | 166 |

|--------------------------------------------------|-----|

| Publications and communications                  | 182 |

| Abstract                                         | 183 |

# List of Figures

| Figure 1.1: Sketch of electron tracks might appear in material.                                                              | . 19       |

|------------------------------------------------------------------------------------------------------------------------------|------------|

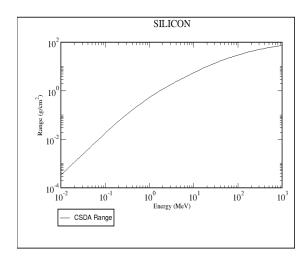

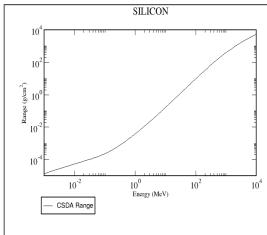

| Figure 1.2: Mean CSDA range in silicon for electrons (left) and proton (right)                                               | . 20       |

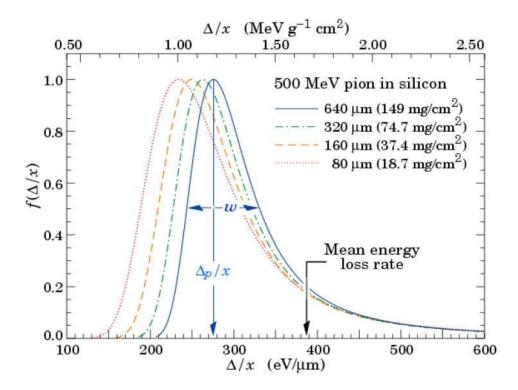

| Figure 1.3: Straggling functions in silicon for 500 MeV pions, normalized to unity at the most probable                      | ;          |

| value $\delta x$ . The width $\omega$ is the full width at half maximum.                                                     | . 21       |

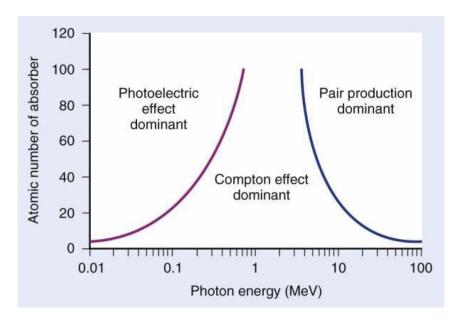

| Figure 1.4: Regions where the photoelectric effect, Compton effect and pair production dominate as a                         |            |

| function of the photon energy and the atomic number of the absorber.                                                         | . 22       |

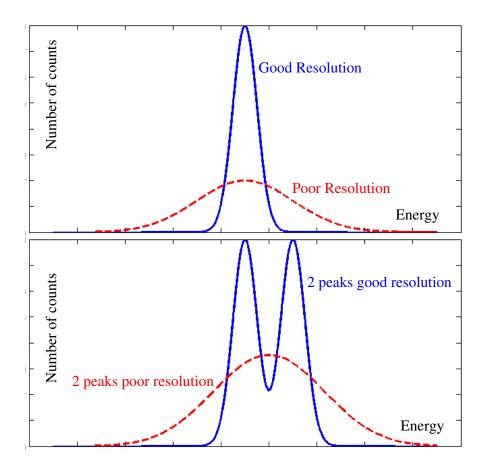

| Figure 1.5: Examples of good and poor energy resolutions                                                                     | . 24       |

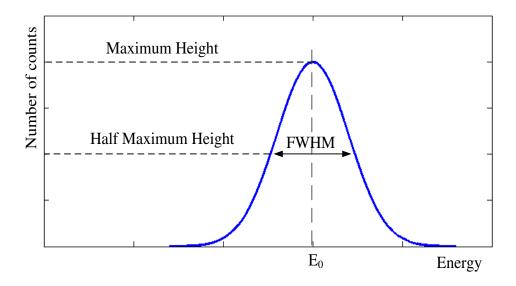

| Figure 1.6: Definition of detector resolution.                                                                               | . 24       |

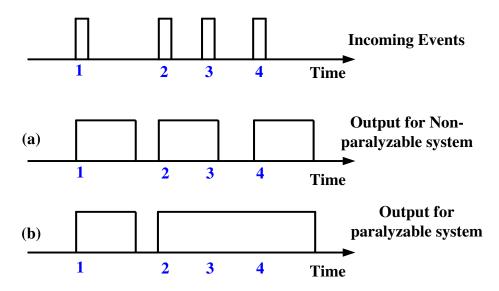

| Figure 1.7: Incoming events recorded with non-paralyzeble (a) and paralyzable (b) devices                                    | . 25       |

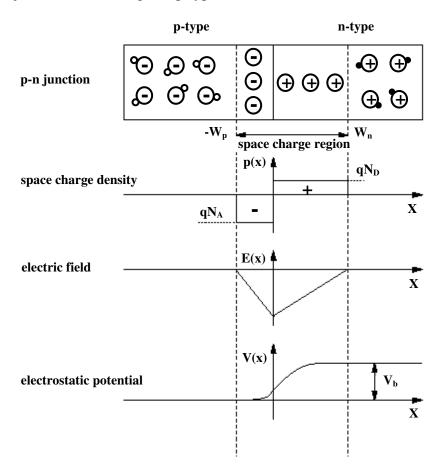

| Figure 1.8: Approximation of an abrupt p-n junction: space charge density, electric field distribution, an                   | nd         |

| electrostatic potential distribution.                                                                                        | . 27       |

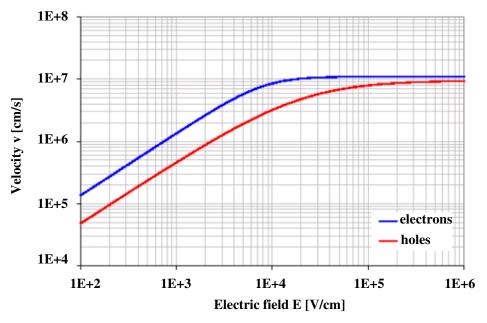

| Figure 1.9: Electron and hole velocities vs. the electric field strength in silicon.                                         | . 29       |

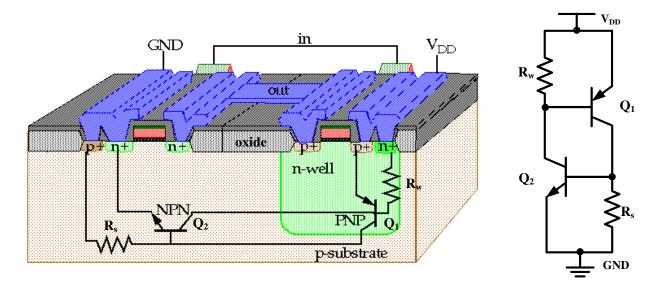

| Figure 1.10: A typical CMOS device with elements of a parasitic thyristor                                                    | . 32       |

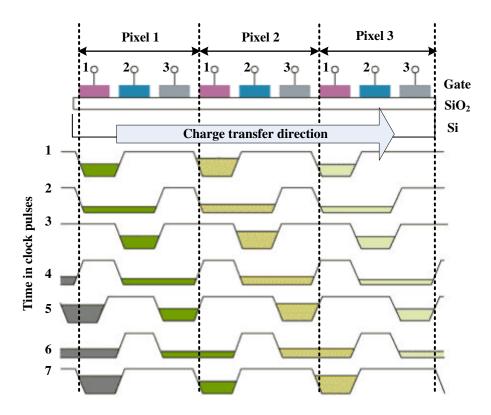

| Figure 1.11: Typical CCD detectors with three gates for each pixel.                                                          | . 34       |

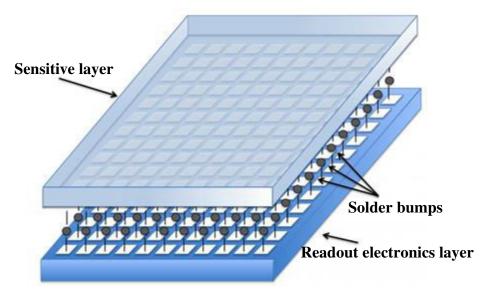

| Figure 1.12: Illustration of a hybrid pixel detector.                                                                        | . 35       |

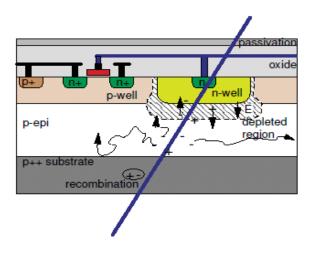

| Figure 1.13: Cross section view of a CPS pixel.                                                                              |            |

|                                                                                                                              |            |

| Figure 2.1: Column parallel readout principle.                                                                               | . 45       |

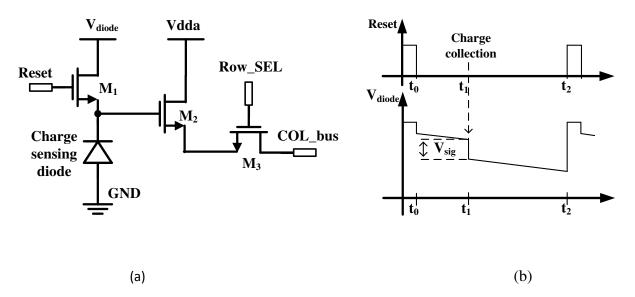

| Figure 2.2: The classical single pixel cell: (a) schematic, (b) timing diagram showing the operation and                     | the        |

| signal shape.                                                                                                                | . 46       |

| Figure 2.3: Self-biased pixel cell: (a) schematic, (b) timing diagram showing the operation and the signal                   | al         |

| shape                                                                                                                        | . 47       |

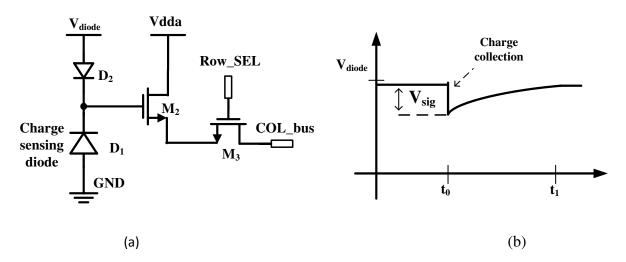

| Figure 2.4: Pixel topology with in pixel amplification and CDS.                                                              | . 50       |

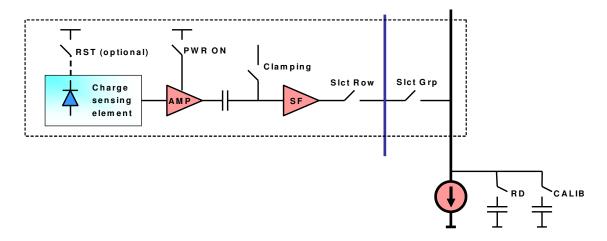

| Figure 2.5: Illustration of Random Telegraph Signal (RTS).                                                                   | . 50       |

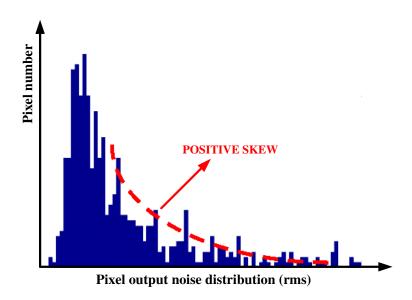

| Figure 2.6: Pixel output noise distribution at the sensor output                                                             | . 51       |

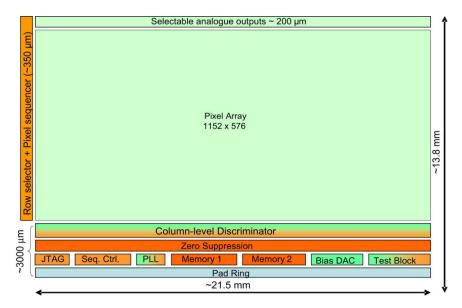

| Figure 2.7: MIMOSA 26 block diagram.                                                                                         | . 52       |

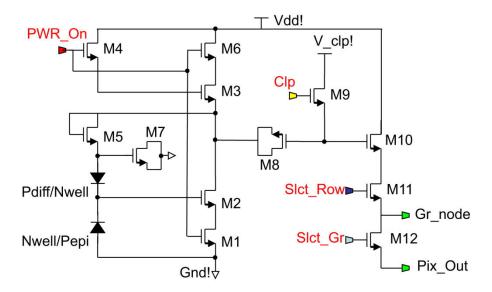

| Figure 2.8: Pixel schematic of MIMOSA 26                                                                                     | . 53       |

| Figure 2.9: Architecture of the column-level discriminator.                                                                  | . 53       |

|                                                                                                                              |            |

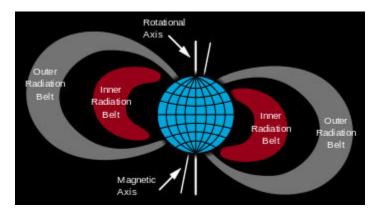

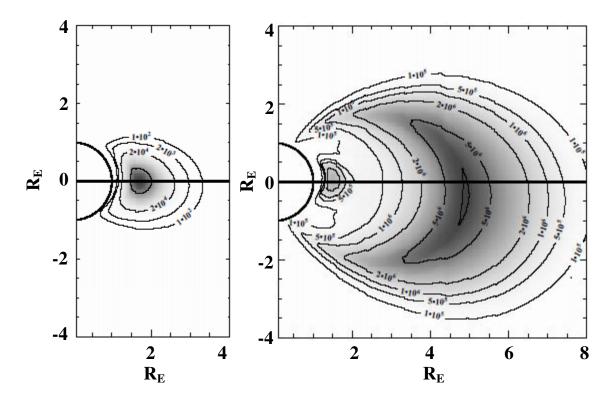

| Figure 3.1: cross section of radiation belts.                                                                                | . 59       |

| Figure 3.2: Earth's radiation belts as represented by the standard AP8 and AE8 models. The two panels                        |            |

| show contour plots of integral proton flux $> 10 \text{ MeV}$ (left) and integral electron flux $> 0.6 \text{ MeV}$ (right). |            |

| Whereas electrons populate the inner and outer zone, protons are only trapped in the inner zone                              | . 60       |

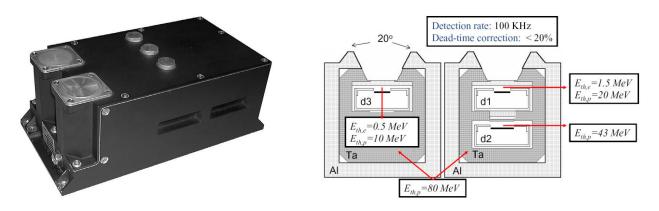

| Figure 3.3: Picture of SREM flight model and the schema of its two detector head.                                            | . 63       |

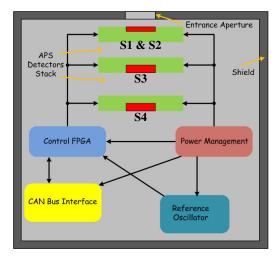

| Figure 3.4: Block diagram (left) and photo (right) of HMRM structure. It features a stack of four CPS (S                     | <b>S</b> 1 |

| to S4), where S1 and S2 in close proximity.                                                                                  | . 64       |

#### Table of figures

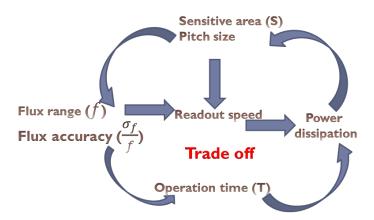

| Figure 3.5: relations between speed, accuracy, power, sensitive area and pitch size                                                                                                                                                                                                                                                                                                                                               | 65           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

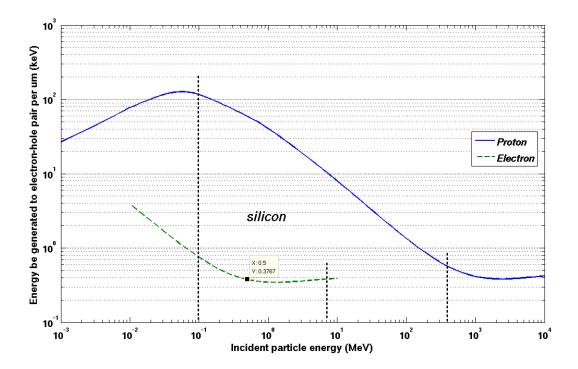

| Figure 3.6: Incident proton and electron energy versus their energy loss used to generate e-/h pairs p                                                                                                                                                                                                                                                                                                                            | er µm        |

| in silicon, the vertical dashed lines indicate energy intervals concerned.                                                                                                                                                                                                                                                                                                                                                        | 68           |

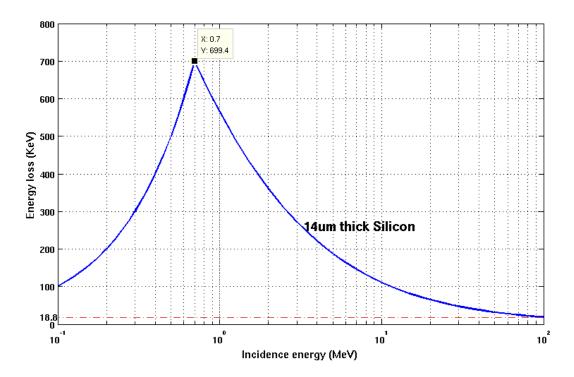

| Figure 3.7: total energy loss of proton in 14 µm thick silicon with respect to its kinetic energy                                                                                                                                                                                                                                                                                                                                 | 69           |

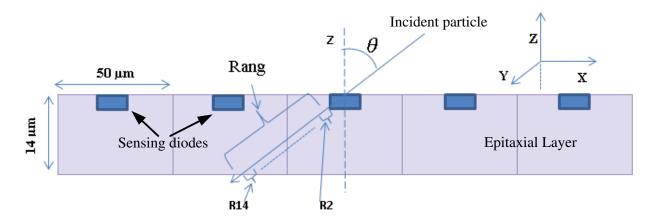

| Figure 3.8: Schematic diagram of particle range in the cross section of epitaxial layer                                                                                                                                                                                                                                                                                                                                           | 70           |

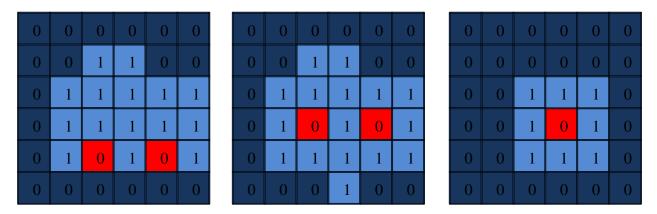

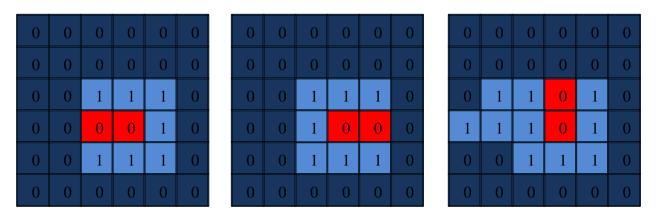

| Figure 3.9: Simulation result of signal over pixels for a typical situation: particles hit in junction regifuur adjacent pixels at normal incidence.                                                                                                                                                                                                                                                                              | 71           |

| Figure 3.10: Simulation result of signal over pixels for a typical situation: particles hit in the center of pixel at normal incidence.                                                                                                                                                                                                                                                                                           |              |

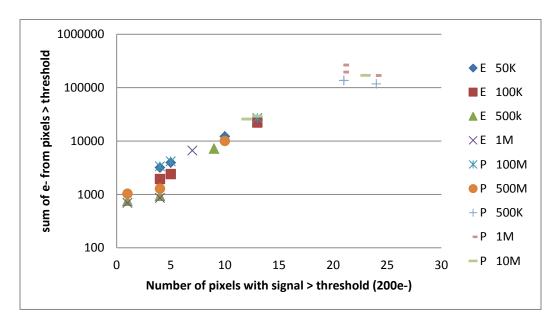

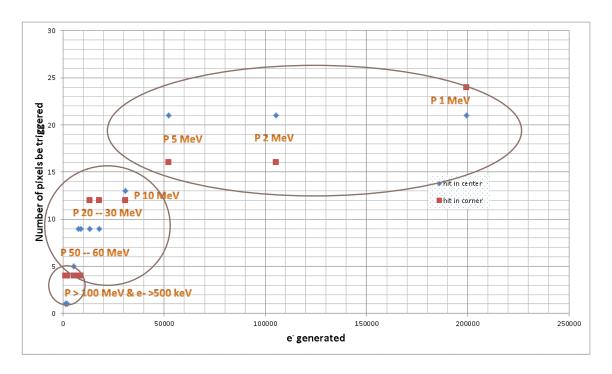

| Figure 3.11: sensor responses for various particles with respect to number of pixels fired (threshold 2) and totally number of e- collected from fired pixels. For each kind of particle, there are 3 points rep 3 incident situations on behalf of hit position or angular effects. Two of them are normal incident with different position relative to the sensing diode, another is $\theta$ =80° as illustrated in figure 3.8 | resent<br>th |

| Figure 3.12: Total e- generated by various particles with respect to the number of pixels with collecte charges higher than 200 e-                                                                                                                                                                                                                                                                                                | ed           |

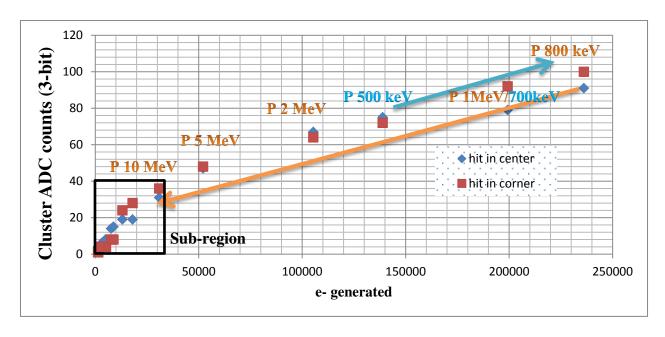

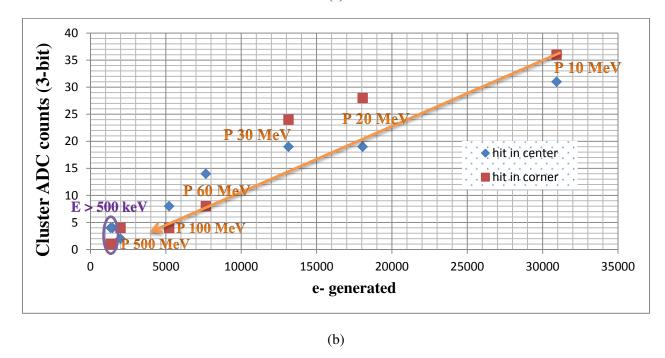

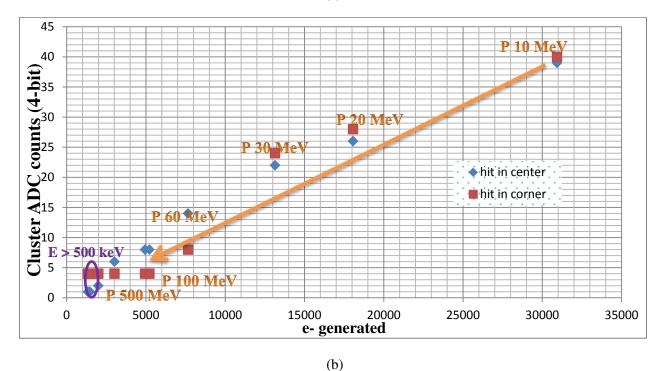

| Figure 3.13: Total e- generated by various particles with respect to sum of 3-bit ADC counts for all t pixels in a cluster (a) and its sub-region (b).                                                                                                                                                                                                                                                                            | he           |

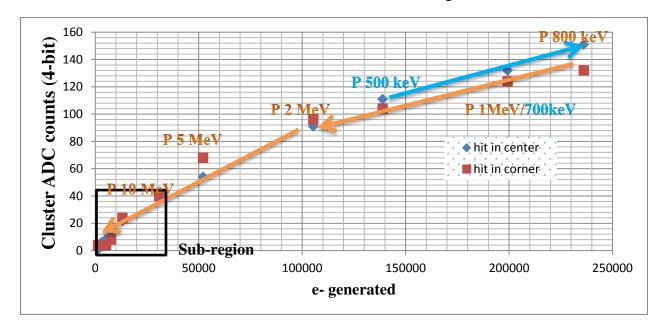

| Figure 3.14: Total e- generated by various particles with respect to sum of 4-bit ADC counts for all t pixels in a cluster (a) and its sub-region (b).                                                                                                                                                                                                                                                                            |              |

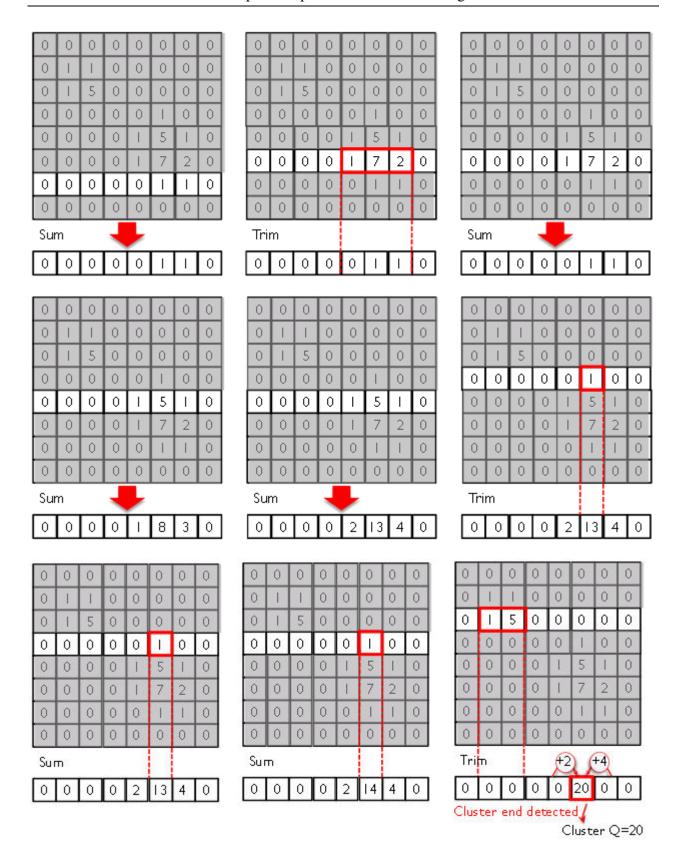

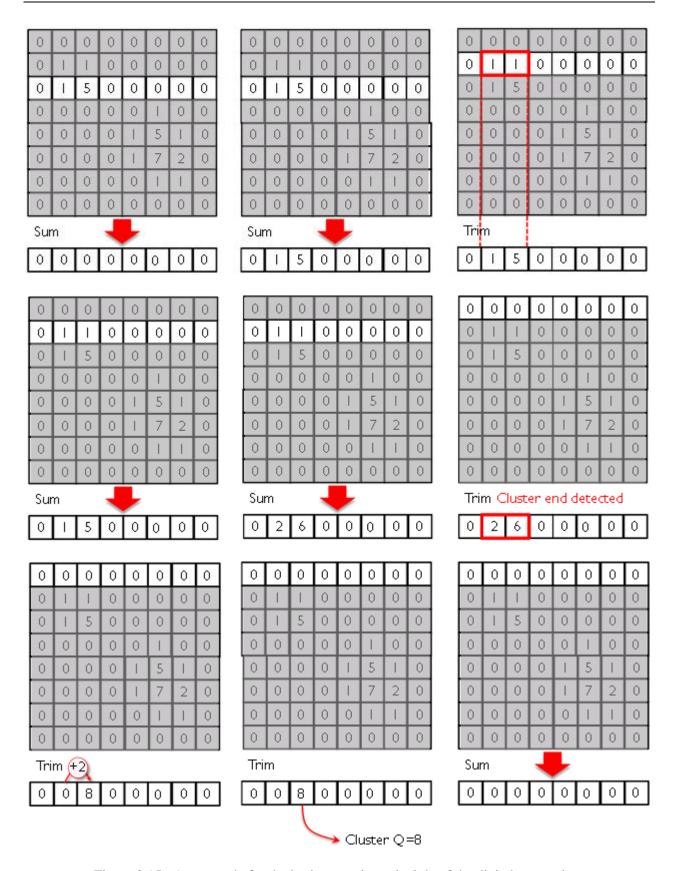

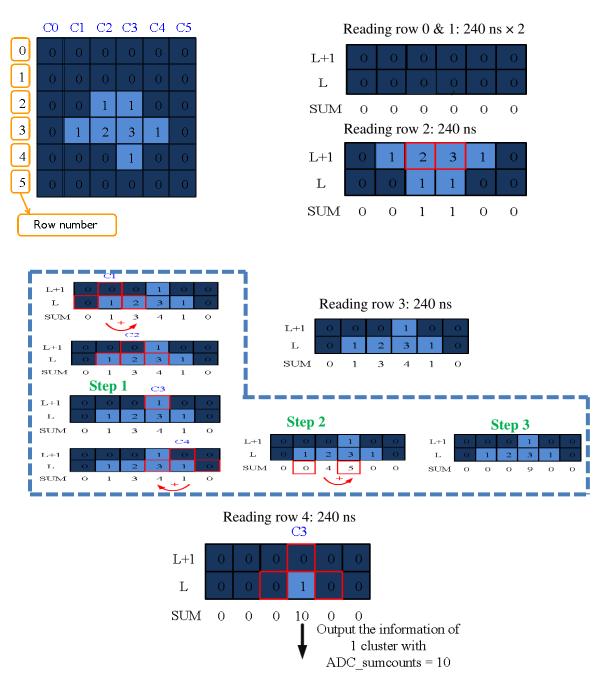

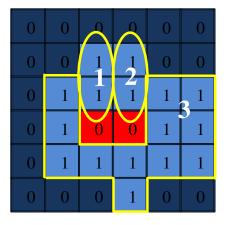

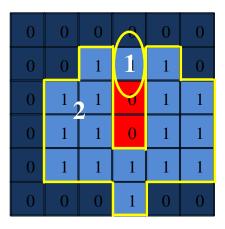

| Figure 3.15 : An example for the basic operation principle of the digital processing                                                                                                                                                                                                                                                                                                                                              | 80           |

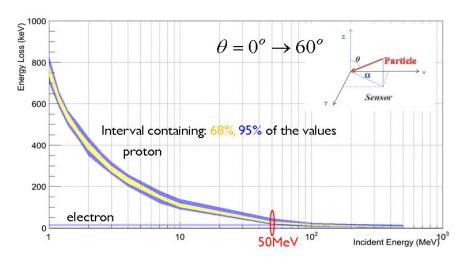

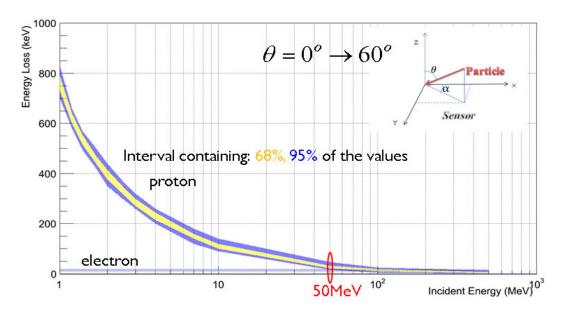

| Figure 3.16: Monte-Carlo simulation results of energy loss in the sensor's sensitive area versus partic                                                                                                                                                                                                                                                                                                                           |              |

| incident energy.                                                                                                                                                                                                                                                                                                                                                                                                                  | 81           |

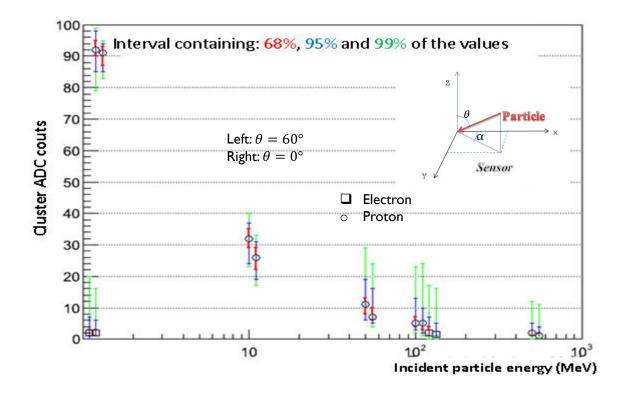

| Figure 3.17: Monte-Carlo simulation results of incident particle energy versus triggered cluster ADC                                                                                                                                                                                                                                                                                                                              | •            |

| counts.                                                                                                                                                                                                                                                                                                                                                                                                                           | 82           |

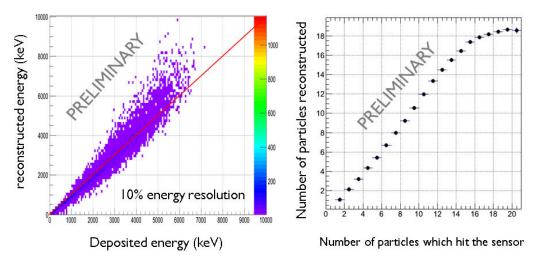

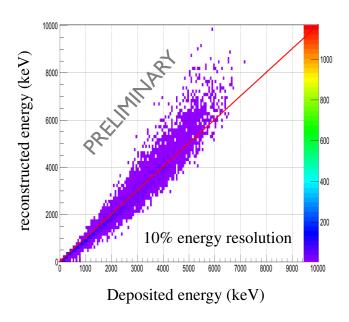

| Figure 3.18: Reconstructed energy versus deposited energy.                                                                                                                                                                                                                                                                                                                                                                        | 83           |

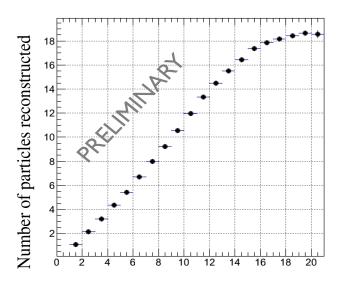

| Figure 3.19: Number of clusters reconstructed per frame versus number of particles effectively impiritue sensor.                                                                                                                                                                                                                                                                                                                  | -            |

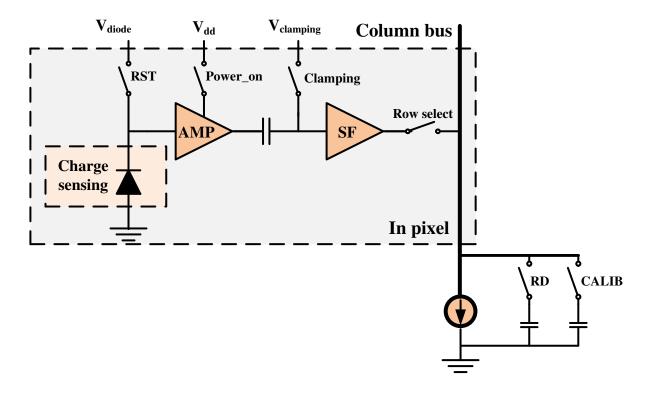

| Figure 4.1: Analogue signal processing architecture of COMETH.                                                                                                                                                                                                                                                                                                                                                                    |              |

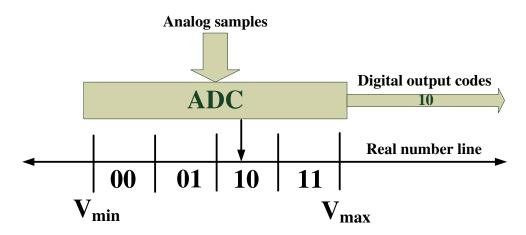

| Figure 4.2: ADC description.                                                                                                                                                                                                                                                                                                                                                                                                      |              |

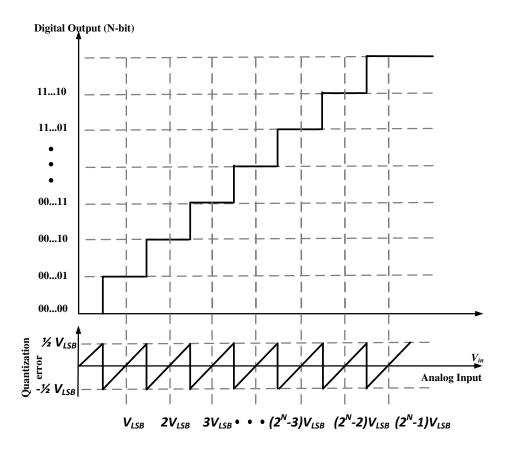

| Figure 4.3: Typical transfer curve of an N-bit ADC.                                                                                                                                                                                                                                                                                                                                                                               |              |

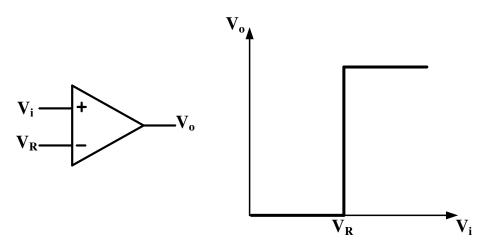

| Figure 4.4: Comparator Circuit and Transfer Function.                                                                                                                                                                                                                                                                                                                                                                             |              |

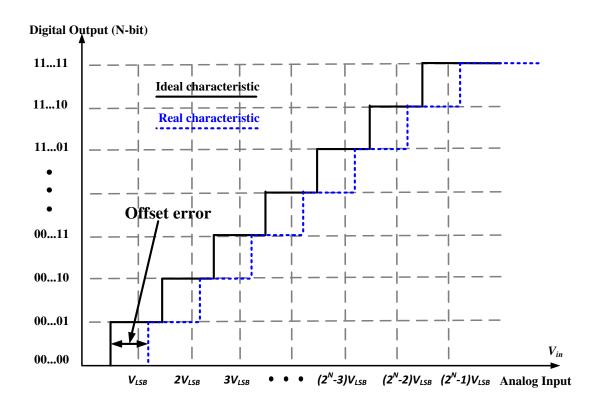

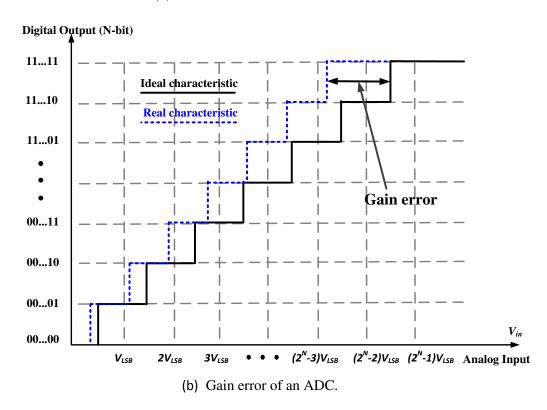

| Figure 4.5: Offset and gain error of an N-bit ADC. It is assumed that all other errors are not presente                                                                                                                                                                                                                                                                                                                           |              |

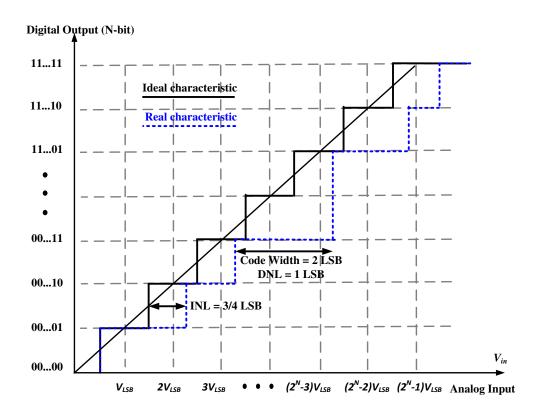

| Figure 4.6: Example Transfer Characteristic of an N-bit ADC Showing DNL and INL.                                                                                                                                                                                                                                                                                                                                                  |              |

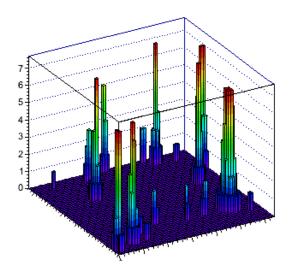

| Figure 4.7: Emulated COMETH 3-bit digitized response of one frame.                                                                                                                                                                                                                                                                                                                                                                |              |

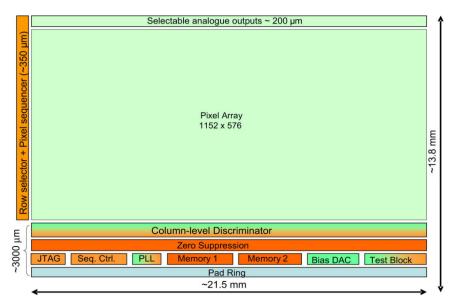

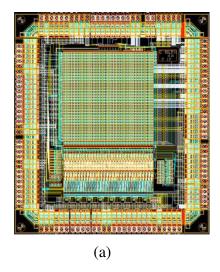

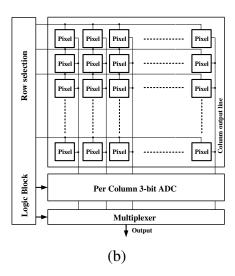

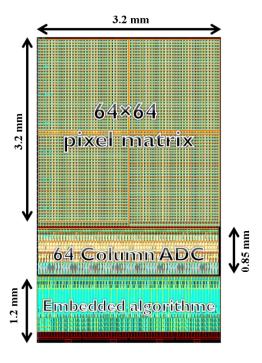

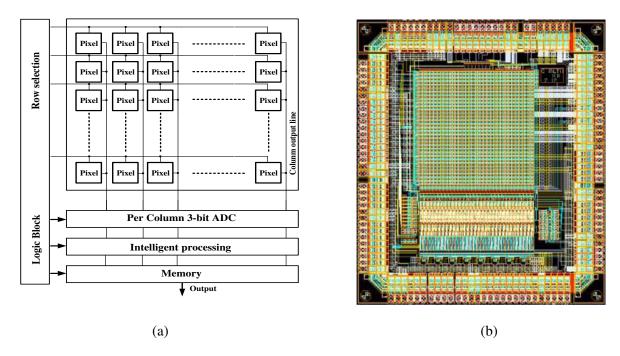

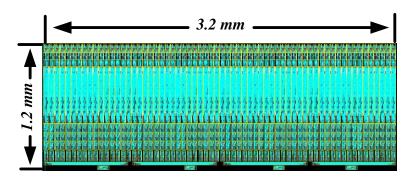

| Figure 4.8: Global architecture of COMETH (a) and the layout (3.5 mm × 4 mm) of the first reduced prototype (b)                                                                                                                                                                                                                                                                                                                   |              |

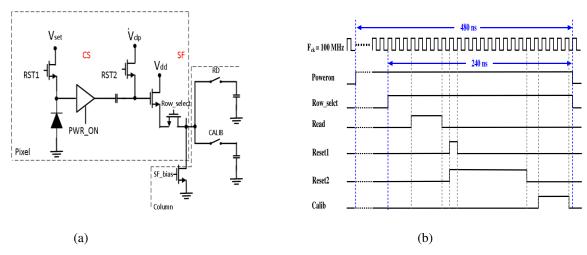

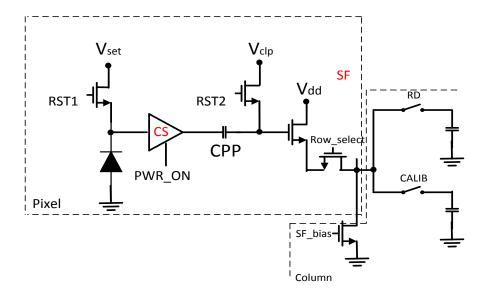

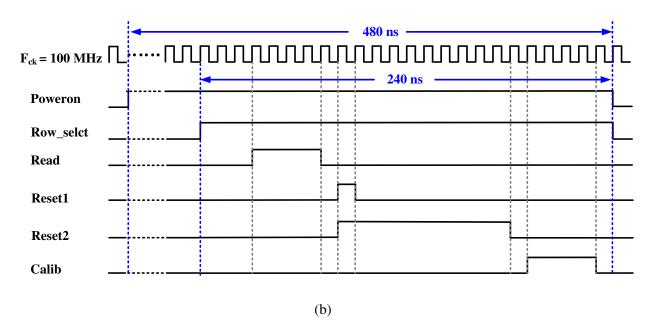

| Figure 5.1 : (a) Schematic of the pixel and, (b) related timing                                                                                                                                                                                                                                                                                                                                                                   |              |

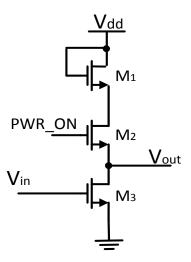

| Figure 5.2: Common source amplifier stage used inside the pixel                                                                                                                                                                                                                                                                                                                                                                   |              |

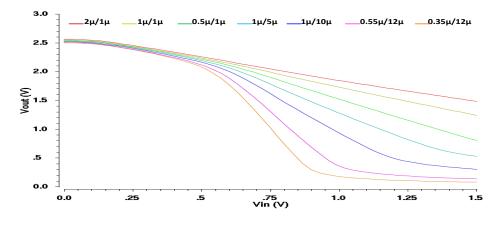

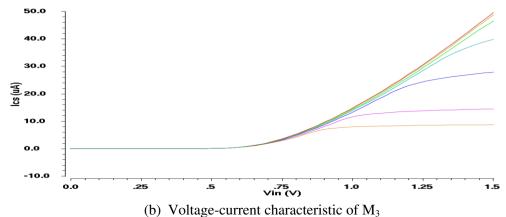

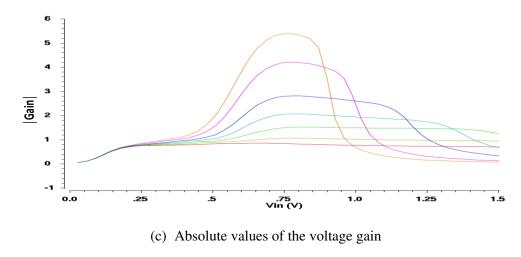

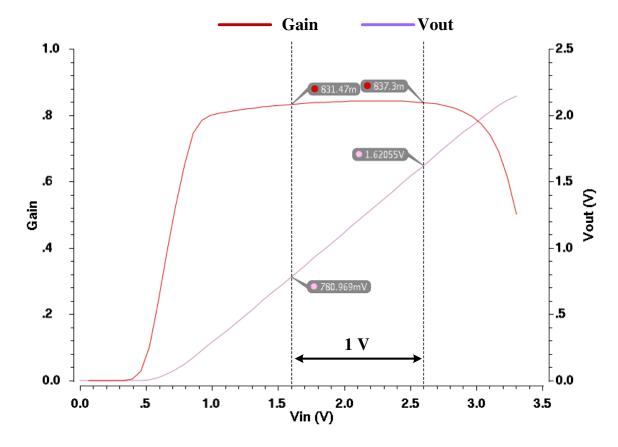

| Figure 5.3: Static characteristics of the CS stage under different W/L values of M1                                                                                                                                                                                                                                                                                                                                               | 105          |

#### Table of figures

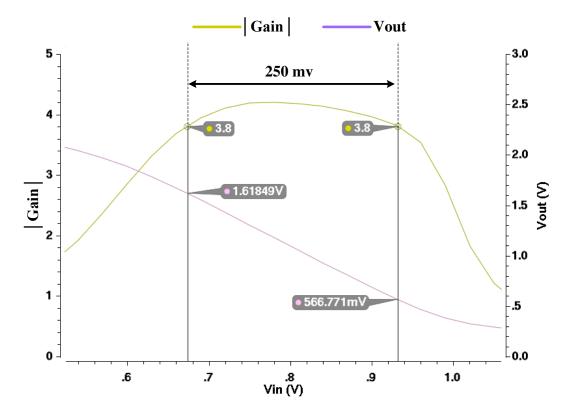

| Figure 5.4: Static characteristics of the CS stage with W/L ratio of M1 equals to $0.55\mu m/12\mu m$                       | . 105 |

|-----------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 5.5: Gain and input-output voltage characteristic of the SF stage.                                                   | . 106 |

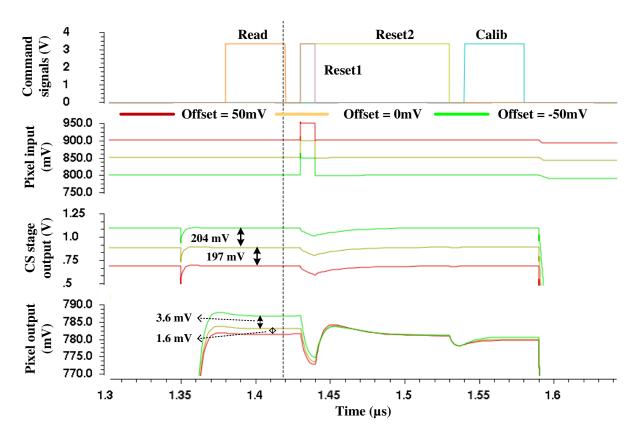

| Figure 5.6: Simulation of the in-pixel offset cancellation operation.                                                       | . 107 |

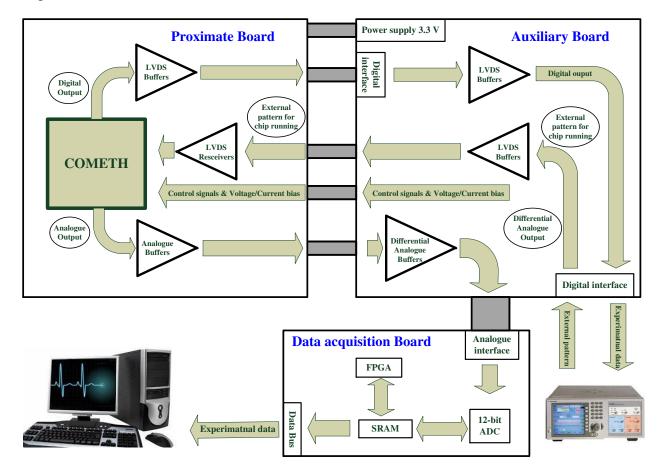

| Figure 5.7: Set-up for laboratory test.                                                                                     | . 109 |

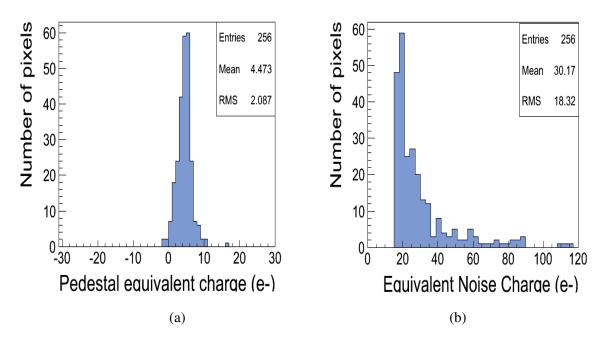

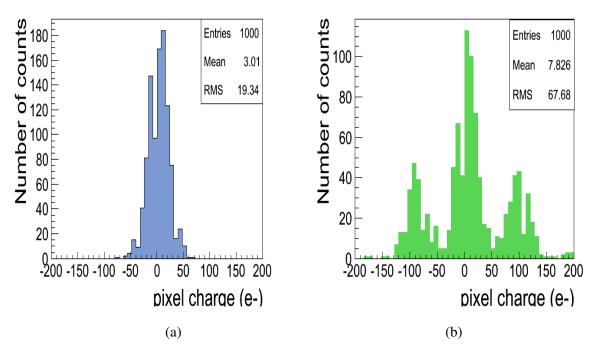

| Figure 5.8: Distribution of pedestal values (a) and temper noise (b) for the sub-array with 8×32 pixels.                    | . 112 |

| Figure 5.9: Noise of a normal pixel (a), and a noisy pixel with RTS noise (b)                                               | . 112 |

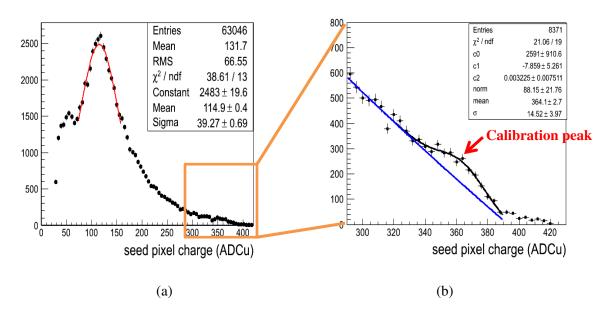

| Figure 5.10: Collected charge distribution observed with a <sup>55</sup> Fe source. Fig. (a) shows the entire               |       |

| distribution while Fig. (b) displays a zoom on the calibration peak                                                         |       |

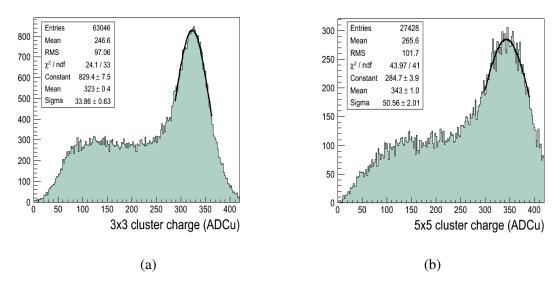

| Figure 5.11: Cluster collected charge with the <sup>55</sup> Fe source: 3×3 pixels (a) and 5×5 pixels (b). The lines        | ;     |

| represent gaussian fits to estimate the MPV of the distribution.                                                            | . 114 |

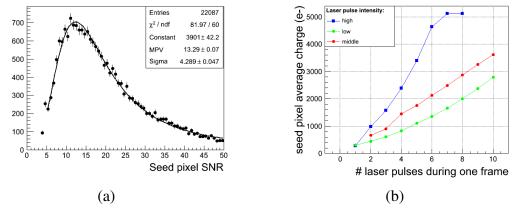

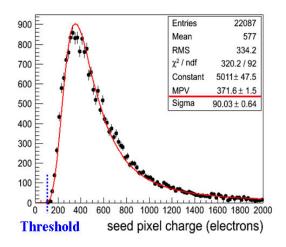

| Figure 5.12: Seed pixel collected charge with a $^{90}$ Sr β- source.                                                       | . 114 |

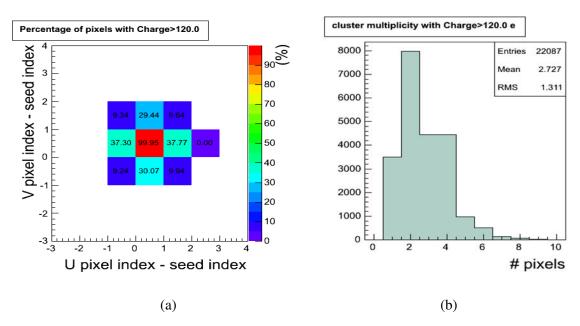

| Figure 5.13: Percentage of pixels with charge $> 120 e^{-}$ with a $^{90}$ Sr $\beta$ - source (a) and cluster multiplicity | 7     |

| with charge > 120 e- (b).                                                                                                   | . 115 |

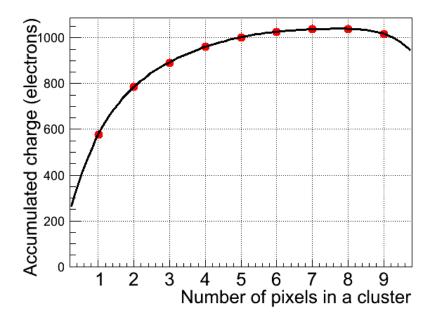

| Figure 5.14: Accumulated charge with different number of pixels in a cluster.                                               | . 116 |

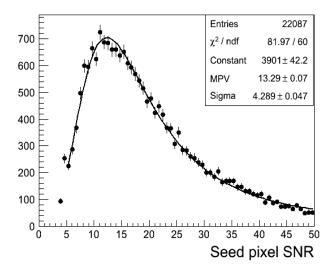

| Figure 5.15: SNR of the seed pixel to electrons.                                                                            | . 117 |

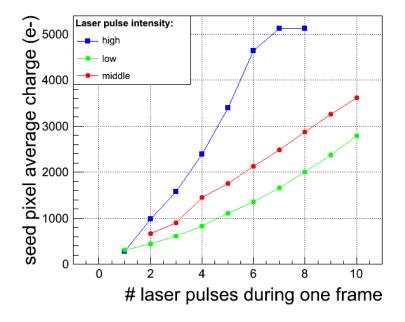

| Figure 5.16: Evolution of the pixel response to a linear increase of the laser illumination, for three                      |       |

| different laser currents. The laser illumination amplitude depends linearly on the number of laser pluses                   | es    |

| shot during one sensor frame                                                                                                | . 118 |

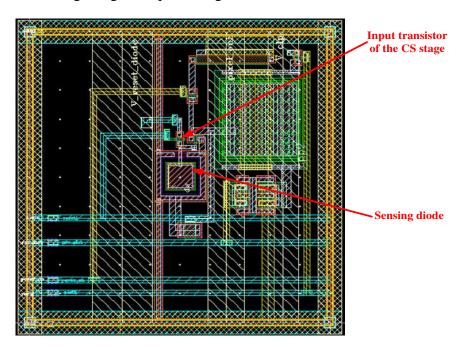

| Figure 5.17: layout of a single pixel.                                                                                      | . 119 |

|                                                                                                                             |       |

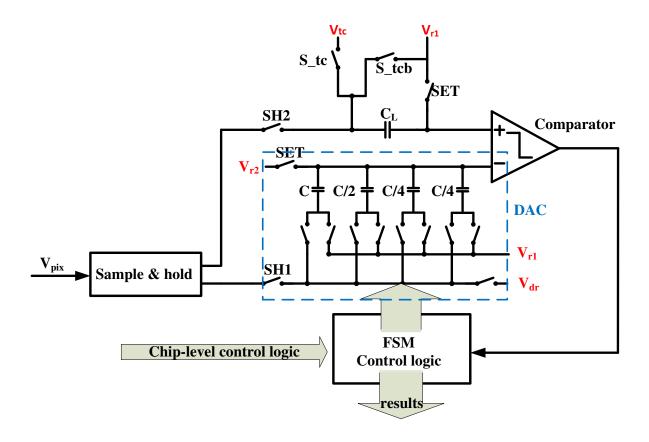

| Figure 6.1: ADC architecture vs Resolution and sampling rate.                                                               | . 121 |

| Figure 6.2: Architecture of an N-bit flash ADC.                                                                             |       |

| Figure 6.3: Block Diagram of a Typical Pipelined ADC.                                                                       |       |

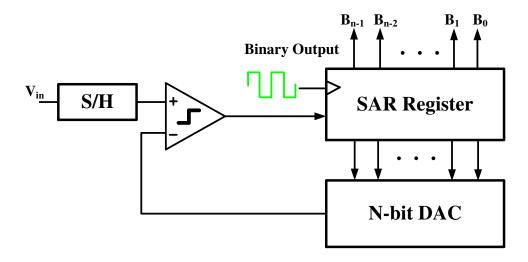

| Figure 6.4: Basic architecture of an N-bit successive approximation ADC                                                     |       |

| Figure 6.5: Example of the searching process of a 4-bit SAR conversion. The digital output is 0101                          |       |

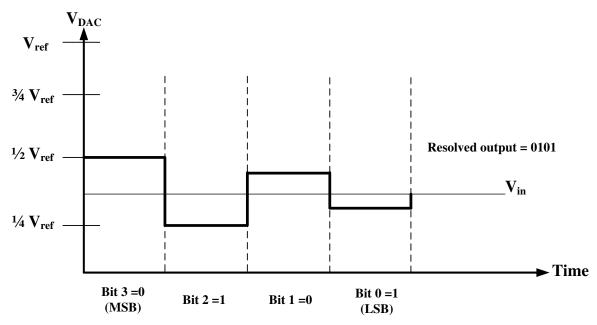

| Figure 6.6: Expected transfer function of the 3-bit ADC in COMETH.                                                          |       |

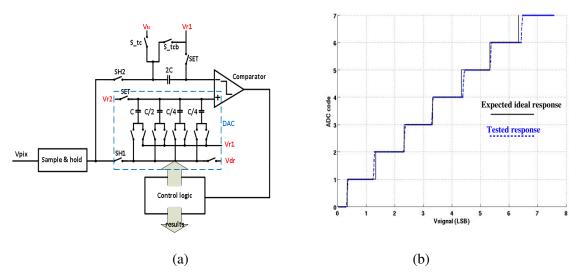

| Figure 6.7: Global architecture of the column 3-bit SAR ADC for COMETH.                                                     |       |

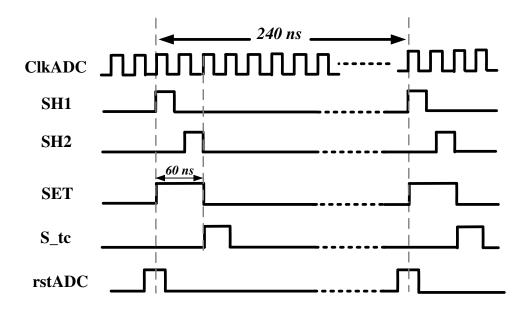

| Figure 6.8: Timing diagram for the column 3-bit SAR ADC.                                                                    |       |

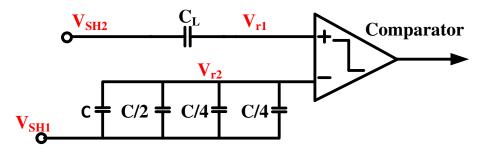

| Figure 6.9: Equivalent ADC circuit during the SET phase.                                                                    |       |

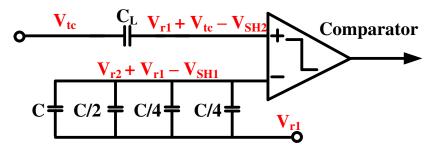

| Figure 6.10: Equivalent ADC circuit for the threshold comparison                                                            |       |

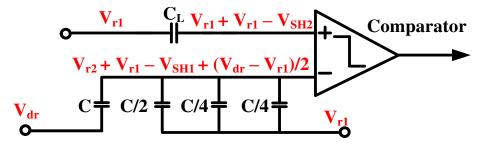

| Figure 6.11: Equivalent ADC circuit for the conversion of the MSB.                                                          |       |

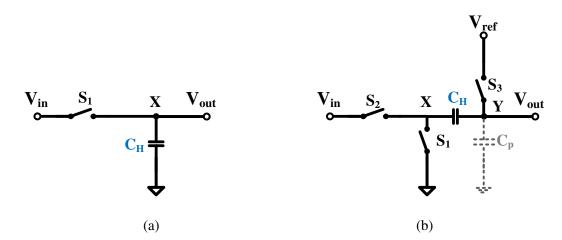

| Figure 6.12: Sampling structure: (a) parallel sampling, (b) series sampling                                                 |       |

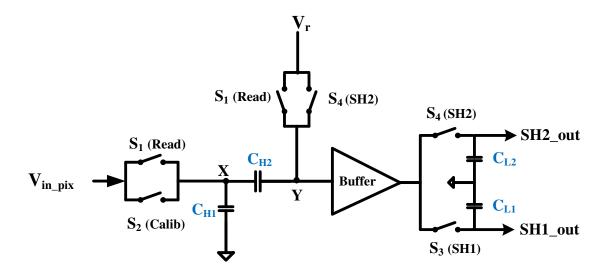

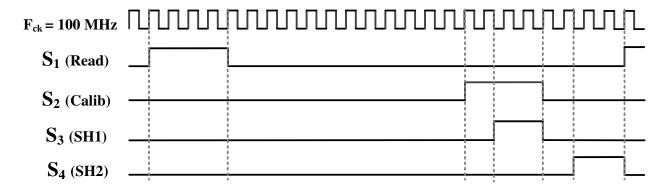

| Figure 6.13: Schematic of the S/H circuit.                                                                                  |       |

| Figure 6.14: Timing diagram of the S/H circuit.                                                                             | . 132 |

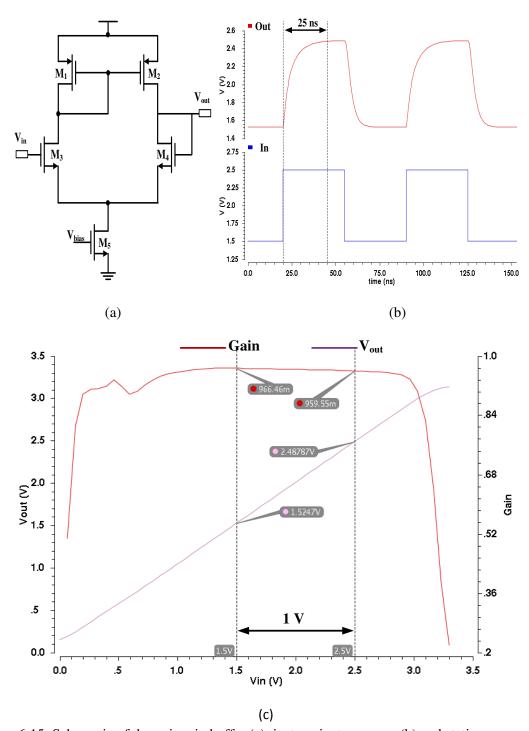

| Figure 6.15: Schematic of the unit gain buffer (a); its transient response (b) and static response (c)                      |       |

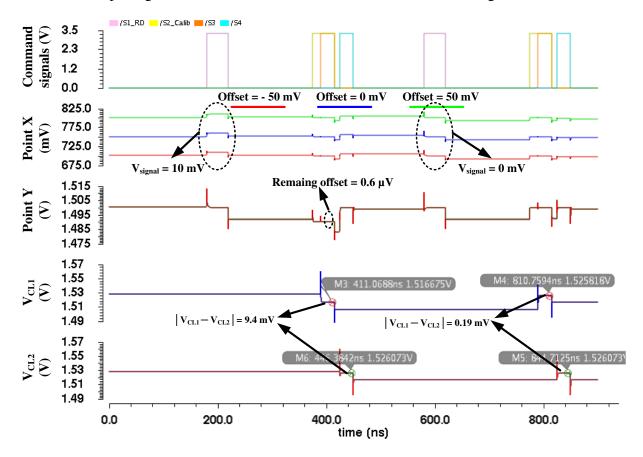

| Figure 6.16: Column level offset cancellation simulation results.                                                           |       |

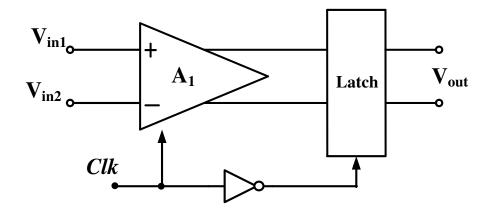

| Figure 6.17: Typical comparator architecture.                                                                               |       |

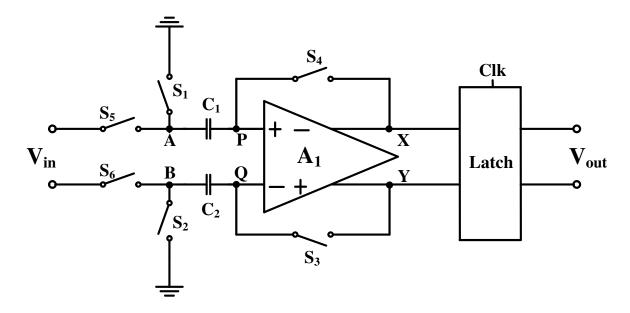

| Figure 6.18: Input offset storage architecture                                                                              |       |

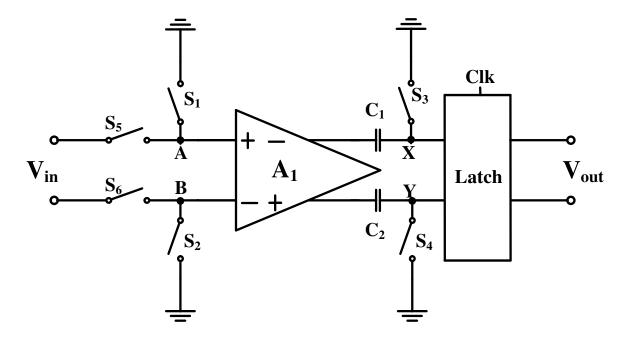

| Figure 6.19: Output offset storage architecture.                                                                            |       |

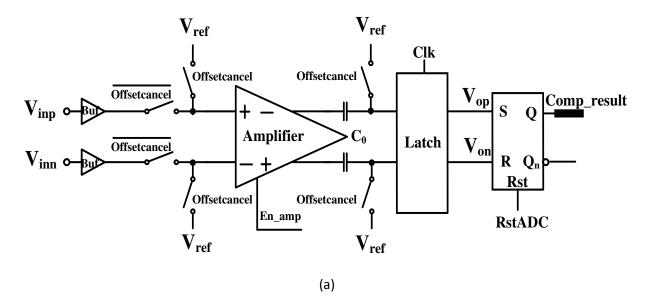

| Figure 6.20: The architecture (a) and its operation timing (b).                                                             |       |

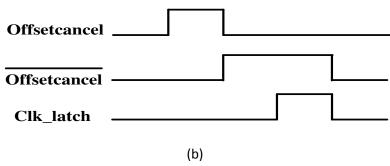

| Figure 6.21: schematic of the preamplifier used in the comparator                                                           | 138   |

#### Table of figures

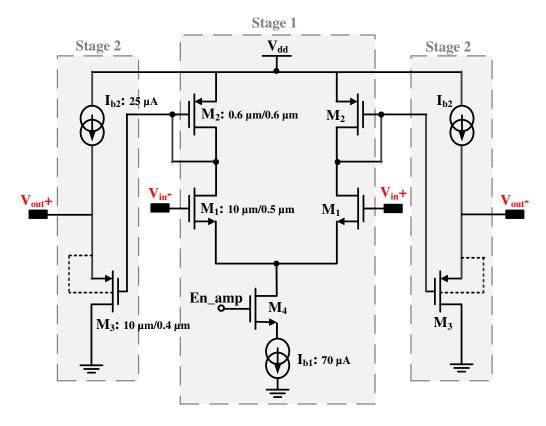

| Figure 6.22: Schematic of the dynamic latch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 120      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

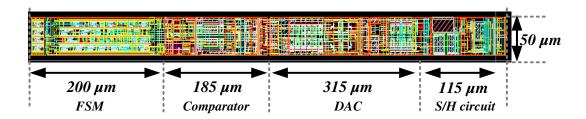

| Figure 6.23: layout of the column-level ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

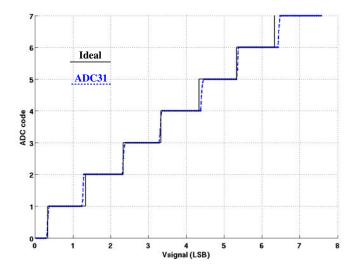

| Figure 6.24: Transfer functions of ADC31 and the expected ideal one.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

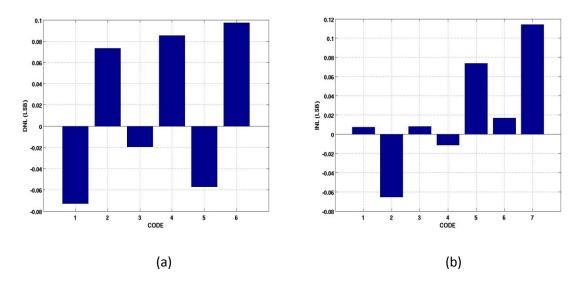

| Figure 6.25: DNL (a) and INL (b) characteristics of ADC31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

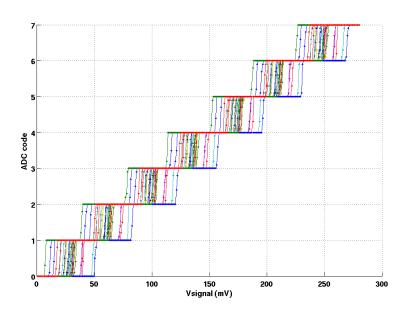

| Figure 6.26: Transfer functions of the 32 column ADCs (enlarged LSB value)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

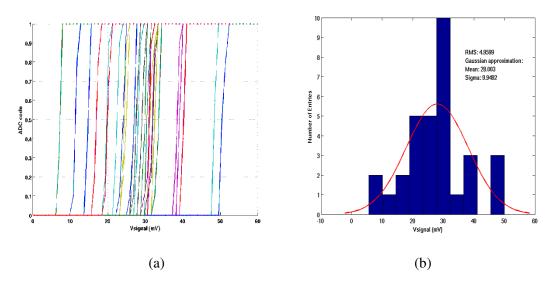

| Figure 6.27: Column dispersion of the first bit: (a) zoom of the 1 <sup>st</sup> bit; (b) fixed pattern noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

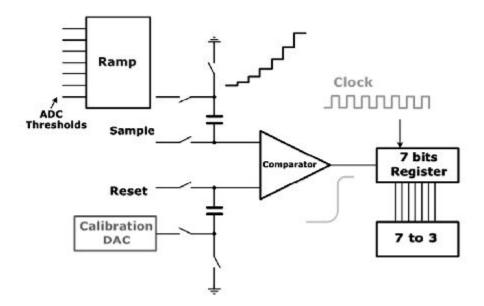

| Figure 6.28: Overview of the ADC designed for the HMRM ASIC. An 8-bit trimming DAC compe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| the comparator offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

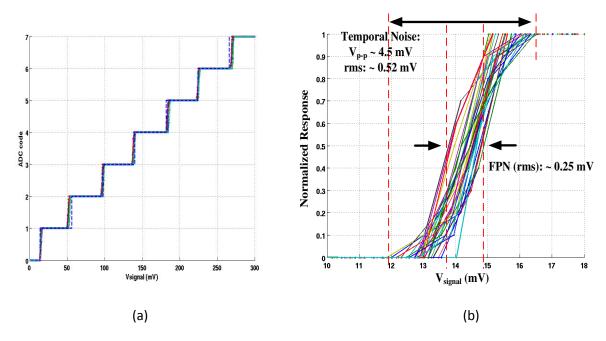

| Figure 6.29: Results with compensation: (a) transfer functions of 32 columns; (b) noise of the first because the first b | oit. 145 |

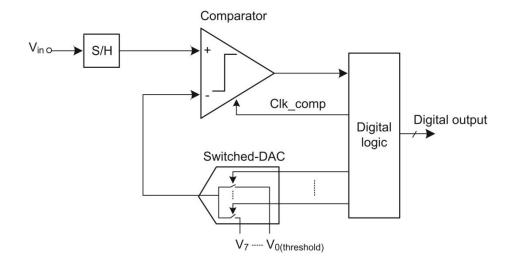

| Figure 6.30: The column ADC architecture with Switched-DAC for comparator references                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 145      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

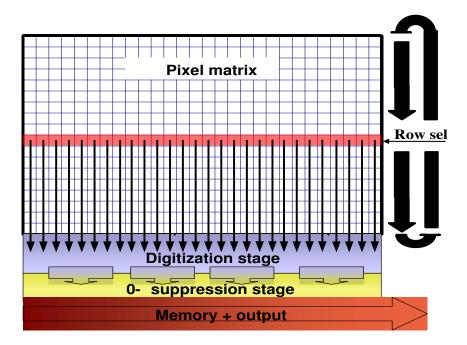

| Figure 7.1: Principle of the clusterization and summation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 149      |

| Figure 7.2: the digital processing hardware system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

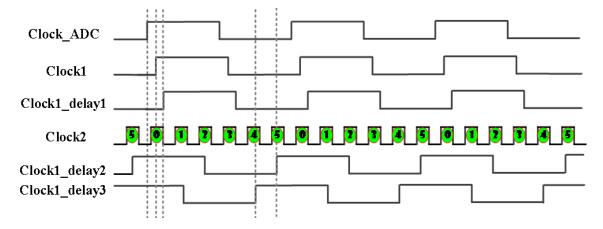

| Figure 7.3: Timing for the digital processing system (not scaled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| Figure 7.4: interface of the temporary memory block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| Figure 7.5: interface of the Finite state machine_1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| Figure 7.6: column cell interfaces of the cluster data sum block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

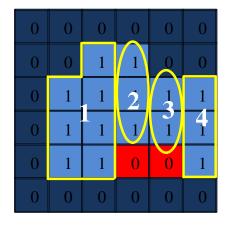

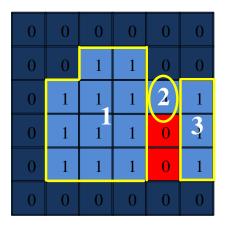

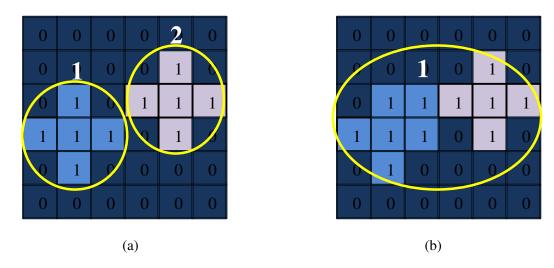

| Figure 7.7: Architecture of the "Sum Core"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |