### Specification Platform for Library IP Development Jung Kyu Chae

### ▶ To cite this version:

Jung Kyu Chae. Specification Platform for Library IP Development. Other [cs.OH]. Université Pierre et Marie Curie - Paris VI, 2014. English. NNT: 2014PA066140 . tel-01126920

### HAL Id: tel-01126920 https://theses.hal.science/tel-01126920

Submitted on 6 Mar 2015  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Université Pierre et Marie Curie

Ecole doctorale informatique, télécommunications et électronique Laboratoire d'informatique de Paris 6 / Equipe Circuits Intégrés Numériques et Analogiques

## Plateforme de spécification pour le développement de bibliothèques de cellules et d'IPs

Par Jung Kyu CHAE

Thèse de doctorat d'informatique

### Dirigée par Habib MEHREZ et Roselyne CHOTIN-AVOT

Présentée et soutenue publiquement le 9 Juillet 2014

Le jury est composé de :

| M. Philippe COUSSY        | Maître de conférence      | Rapporteur             |

|---------------------------|---------------------------|------------------------|

| M. Naohiko SHIMIZU        | Professeur                | Rapporteur             |

| Mme. Emmanuelle ENCRENAZ  | Maître de conférence      | Examinateur            |

| M. Habib MEHREZ           | Professeur                | Directeur de thèse     |

| Mme. Roselyne CHOTIN-AVOT | Maître de conférence      | Co-directrice de thèse |

| M. Jean-Arnaud FRANCOIS   | Manager de l'équipe HW/SW | Co-directeur de thèse  |

CC () S (=) Except where otherwise noted, this work is licensed under http://creativecommons.org/licenses/by-nc-nd/3.0/

## Acknowledgements

I would like to express my gratitude, appreciation and sincere thanks to my supervisors Prof. Habib MEHREZ and Assoc. Prof. Roselyne CHOTIN-AVOT for their excellent guidance, helpful and useful discussions, and continuous encouragement.

I would like to express my thanks to my ST supervisor Dr. Jean-Arnaud François for giving me the opportunity to carry out my thesis within Central CAD & Design Solutions Department at STMicroelectronics. Moreover, I also sincerely thank him for his support, guidance, encouragement and advice.

I am really grateful to Paul MOUGEAT, who provided valuable expertise, insightful comments and constructive critiques. His cool personality and sense of humor always inspired me. I have learnt a lot from him.

I wish to express my deepest gratitude to Dr. Marc QUAST for the helpful and valuable discussions, constructive remarks and encouragement which helped me carry out the PhD thesis work in an efficient manner.

I am especially grateful to my colleagues Severine BERTRAND, Sylvain LANDELLE, Pierre-Francois OLLAGNONG, Syed Shahkar KAKAKHAIL, Brice SERVAIS, Frederic ESTEBAN, Lahcen HAMOUCHE, Sophie RABADAN, Lionel MAIAUX, Pierre MONNOT, Aymen ALBOUCHI, Christophe BOURELY, Sami ABBADI, Mohamed Karim KSONTINI and Arnaud MAGRY for their support both in terms of resources and encouragement.

My special thanks go to my family members who have been extremely understanding and supportive of my studies. This thesis is dedicated to my parents.

### Abstract

A design platform (DP) is a total solution to build a System-On-Chip (SOC). DP consists of a set of libraries/IPs, CAD tools and design kits in conformity with the supported design flows and methodologies. The DP specifications provide a wide range of information from technology parameters like Process-Voltage-Temperature (PVT) corners to CAD tools' information for library/IP development. However, the library/IP developers have difficulties in obtaining the desired data from the existing specifications due to their informality and complexity.

In this thesis, we propose methodologies, flows and tools to formalize the DP specifications for their unification and to deal with it. The proposed description is targeting to be used as a reference to generate and validate libraries (standard cells, I/O, memory) as well as complex IPs (PLL, Serdes, etc.).

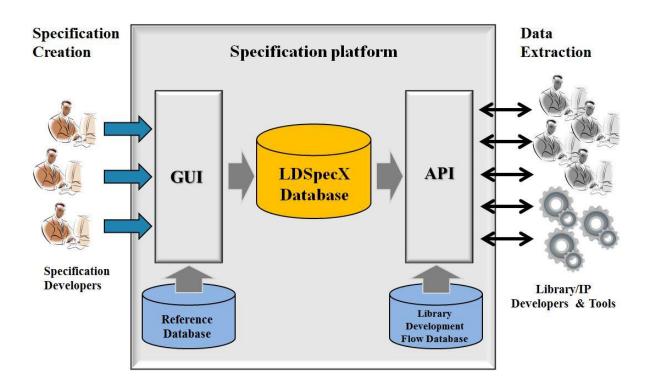

First, we build a data model to represent all required information for library/IP development and then propose a specification language named Library Development Specification based on XML (LDSpecX). Furthermore, we introduce a reference-based method to create a reliable specification in LDSpecX and task-based keywords to efficiently extract data from it. On the basis of the proposed solutions, we develop a specification platform. This platform allows not only creating a complete and consistent specification with a huge amount of data but also rapidly and precisely extracting data depending on the task.

We develop a standard cell library from the specification creation to library validation by using the specification platform. We show that our approach enables to create a complete and consistent specification with a considerable reduction in time. It also bridges the gap between the specification and current automatic system for rapid library/IP development.

**Keywords**: Design Platform, Design Methodology, Unified specification, Library/IP development, Specification creation, Data extraction

## Résumé

Une plateforme de conception est une solution totale qui permet à une équipe de conception de développer un système sur puce. Une telle plateforme se compose d'un ensemble de bibliothèques et de circuits réutilisables (IPs), d'outils de CAO et de kits de conception en conformité avec les flots de conception et les méthodologies supportés. Les spécifications de ce type de plateforme offrent un large éventail d'informations, depuis des paramètres de technologie, jusqu'aux informations sur les outils de CAO pour le développement des bibliothèques/IPs. En outre, les développeurs de bibliothèque/IP ont des difficultés à obtenir les données nécessaires à partir des spécifications existantes en raison du fait qu'elles ne soient pas formellement spécifiées et de leur complexité.

Dans cette thèse, nous proposons des méthodologies, des flots et des outils pour formaliser les spécifications d'une plateforme de conception pour leurs unification et les traiter. Cette description proposée vise à être utilisée comme une référence pour générer et valider les bibliothèques (cellules standard, entrée/sortie et mémoire) ainsi que les IPs complexes (PLL, Serdes, etc.).

Premièrement, nous construisons un modèle de données pour représenter toutes les informations nécessaires pour le développement de bibliothèques et proposons un langage de spécification pour le développement de bibliothèques basé sur XML (LDSpecX). De plus, nous présentons une méthode basée sur des références pour créer une spécification fiable en LDSpecX et des mots-clés basés sur des tâches pour en extraire les données. A l'aide des solutions proposées, nous développons une plateforme de spécification qui fournit une interface utilisateur graphique (GUI) et une interface de programmation (API). Cette plateforme permet non seulement la création de la spécification, mais aussi l'extraction rapide des données en fonction de la tâche.

Nous développons une bibliothèque de cellules standard depuis la création de la spécification jusqu'à la validation de la bibliothèque en utilisant cette plateforme de spécification. Nous montrons ainsi que notre approche permet de créer une spécification complète et cohérente avec une réduction considérable du temps. Cette proposition comble également l'écart entre les spécifications et le système automatique existant pour le développement rapide de bibliothèques/IPs.

V

**Mots-clés** : Plateforme de conception, Méthodologie de conception, Spécification unifiée, Développement des bibliothèques/IPs, Création de la spécification, Extraction des données

## **Table of Contents**

| 1  | . Int      | roduction                                                          | . 1 |

|----|------------|--------------------------------------------------------------------|-----|

|    | 1.1        | Motivation                                                         |     |

|    | 1.2        | Thesis Objectives                                                  |     |

|    | 1.3        | Structure of this Manuscript                                       |     |

| 2. | . Lik      | orary Development from the Design Platform Specifications          | .7  |

|    | 2.1        | Introduction                                                       |     |

|    | 2.2        | System-on-Chip Design Flow                                         | . 8 |

|    | 2.3        | Design Platform                                                    |     |

|    | 2.4        | Library Development Flow                                           |     |

|    | 2.4.       | 1                                                                  |     |

|    | 2.4.       | - 0                                                                |     |

|    | 2.4.       |                                                                    |     |

|    | 2.4.       |                                                                    |     |

|    |            | Existing Automatic System for Library Development                  |     |

|    | 2.5.       | 1                                                                  |     |

|    | 2.5.       | $\mathcal{O}$                                                      |     |

|    | 2.5.       |                                                                    |     |

|    | 2.5.       |                                                                    |     |

|    | 2.6        | Example of the Development of a Standard-cell Library              |     |

|    | 2.7        | Problems                                                           |     |

| 2  | 2.8        | Conclusion                                                         |     |

| 3. |            | ite-of-the-art                                                     |     |

|    | 3.1<br>3.2 | Introduction                                                       |     |

|    |            |                                                                    |     |

|    | 3.3.       | Table-based Specification1System Requirements Specification in SCR |     |

|    | 3.3.       |                                                                    |     |

|    |            | UML-based Specification                                            |     |

|    | 3.5        | XML-based Specification                                            |     |

|    | 3.5.       | 1                                                                  |     |

|    | 3.5.       | -                                                                  |     |

|    | 3.6        | STMicroelectronics' Design Platform Specifications                 |     |

|    | 3.7        | Discussion                                                         |     |

|    | 3.8        | Conclusion                                                         |     |

| 4. |            | ethodology for Library Development Specifications                  |     |

| -  | 4.1        | Introduction                                                       |     |

|    |            | Formalism of the Specification.                                    |     |

|    | 4.2.       | •                                                                  |     |

|    | 4.2.       |                                                                    |     |

|    | 4.2.       | 1 5                                                                |     |

|    | 4.2.       | -                                                                  |     |

|    | 4.3        | Reliable Specification Creation Method.                            |     |

|    | 4.3.       |                                                                    |     |

|    | 4.3.       |                                                                    |     |

|    | 4.4        | Efficient Method for Data Extraction from the Specification        |     |

| 4.4              | 4.1 Keyword for Precise Data Identification                                  |    |

|------------------|------------------------------------------------------------------------------|----|

| 4.4              | 1.2 Task-based Keywords for Efficient Data Extraction                        |    |

| 4.5              | Validation of the Specification                                              |    |

| 4.6              | Validation of the Library against the Specification                          |    |

| 4.7              | Conclusion                                                                   |    |

| 5. Sp            | ecification Platform                                                         | 71 |

| 5.1              | Introduction                                                                 | 71 |

| 5.2              | LDSpecX: Library Development Specification based on XML                      | 72 |

| 5.3              | Specification Creation Tool                                                  |    |

| 5.3              | 3.1 XML-based Reference Database                                             | 74 |

| 5.3              | 3.2 User-friendly GUI for Specification Creation                             | 76 |

| 5.4              | API for Specification Data Extraction                                        |    |

| 5.4              | Library Development Task Definition                                          |    |

|                  | I.2 Specification Data API                                                   |    |

| 5.4              | Library Verification Tool using the API                                      |    |

| 5.5              |                                                                              |    |

| 6. Ex            | xperiments                                                                   |    |

| 6.1              | Introduction                                                                 |    |

| 6.2              |                                                                              |    |

| 6.2              | 2.1 Specification Creation                                                   |    |

|                  | 2.2 Library Development from the Specification                               |    |

|                  | Evaluation                                                                   |    |

| 6.3              | 3.1 Specification Evaluation against Five Requirements                       |    |

| 6.3              | 3.2 Specification Data Processing                                            |    |

| 6.4              | Conclusion                                                                   |    |

|                  | onclusion and Perspectives                                                   |    |

| 7.1              | Conclusion                                                                   |    |

| 7.2              | Perspectives                                                                 |    |

| Biblio           | graphy                                                                       |    |

|                  | s                                                                            |    |

|                  | né                                                                           |    |

|                  | Introduction                                                                 |    |

| 2.               | Développement d'une bibliothèque de cellules et d'IPs à partir de la spécifi |    |

|                  | teforme de conception                                                        |    |

| 3.               | Etat de l'art                                                                |    |

| 4.               | Méthodologies pour la spécification du développement de bibliothèques        |    |

| ч.<br>5.         | Implémentation : Plateforme de spécification                                 |    |

| <i>5</i> .<br>6. | Expérimentation                                                              |    |

| 0.<br>7.         | Conclusion et perspectives                                                   |    |

| <i>'</i> •       |                                                                              |    |

## **List of Figures**

| Figure 1.1 Product Technology Trends: MPU Product Functions/Chip and Industry Average        |    |

|----------------------------------------------------------------------------------------------|----|

| "Moore's Law" and Chip Size Trends (source: ITRS)                                            | 1  |

| Figure 1.2 'Moore's law' and 'More than Moore' trends in the semi-conductor industry         | _  |

| (source: ITRS)                                                                               |    |

| Figure 2.1 Example of a SoC (source: ST)                                                     |    |

| Figure 2.2 Cell-based design flow                                                            |    |

| Figure 2.3 Design platform                                                                   |    |

| Figure 2.4 Foundry's library development flow (source: ST)                                   |    |

| Figure 2.5 PVT corners for standard cell library (source: ST)                                |    |

| Figure 2.6 Design platform specifications vs. library development specification (source: ST) |    |

| Figure 2.7 Environmental considerations for library development [41]                         | 14 |

| Figure 2.8 Layout development flow with manual layout [42]                                   | 15 |

| Figure 2.9 Overview of P2Lib [70]                                                            | 18 |

| Figure 2.10 Overview of an automatic library development system (source: ST)                 | 18 |

| Figure 2.11 Maximum capacitance (source: ST)                                                 |    |

| Figure 2.12 Cell characterization                                                            | 20 |

| Figure 2.13 LEF generation methods (source: ST)                                              |    |

| Figure 2.14 Methodology of the transformation between Cadence OA and Synopsys MW             |    |

| databases [59]                                                                               | 22 |

| Figure 2.15 Schematic of a 4-bit Flip-Flop Bank                                              | 23 |

| Figure 3.1 The cruise control system in SCR [88]                                             |    |

| Figure 3.2 Mode transition table defining the mode class mcCruise [88]                       |    |

| Figure 3.3 Variable dictionary table for the CCS [88]                                        |    |

| Figure 3.4 SpecEdit GUI [89]                                                                 |    |

| Figure 3.5 Example of MTT [89]                                                               |    |

| Figure 3.6 Example of DTT [89]                                                               |    |

| Figure 3.7 Dependency graph tool for the CCS [88]                                            |    |

| Figure 3.8 Taxonomy of structure and behavior diagrams [112]                                 |    |

| Figure 3.9 Specification based verification process [93]                                     |    |

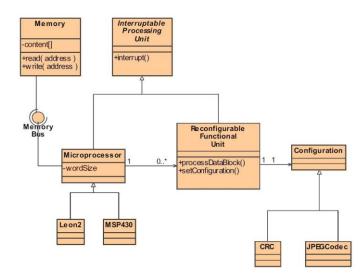

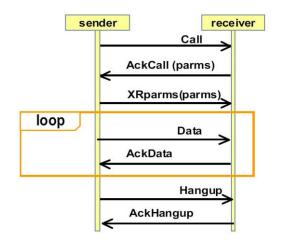

| Figure 3.10 UML class diagram [94]                                                           |    |

| Figure 3.11 UML sequence diagram [94]                                                        |    |

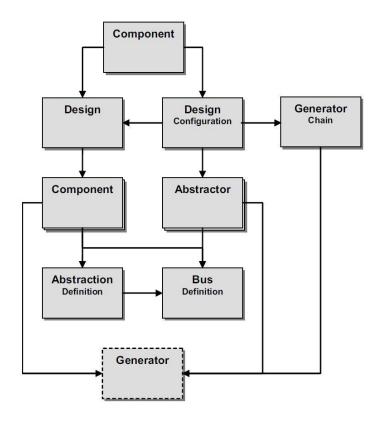

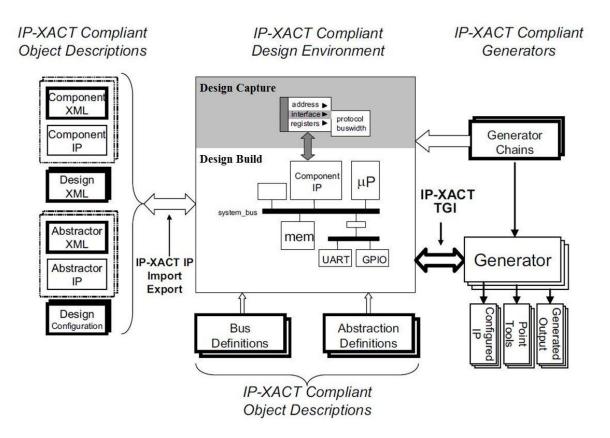

| Figure 3.12 IP-XACT data object interactions [98]                                            | 37 |

| Figure 3.13 IP-XACT design environment [98]                                                  |    |

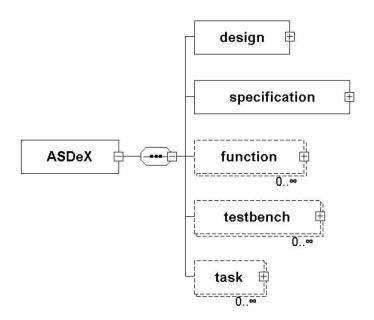

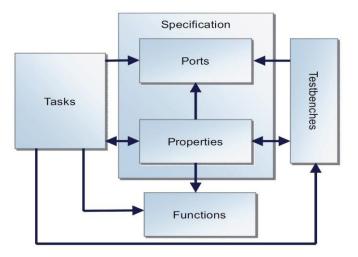

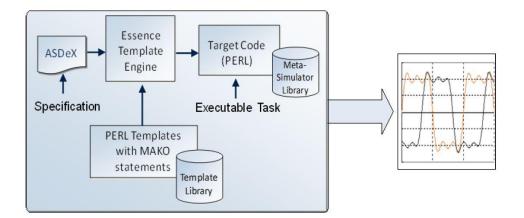

| Figure 3.14 Schema of ASDeX [104]                                                            |    |

| Figure 3.15 ASDeX data object interactions [104]                                             |    |

| Figure 3.16 Validation work flow based on ASDeX [104]                                        |    |

| Figure 3.17 STMicroelectroincs' design platform specifications (source : ST)                 | 41 |

| Figure 4.1 Automatic library development system (source: ST)                                 |    |

| Figure 4.2 A task for library development (source: ST)                                       |    |

| Figure 4.3 Timing characterization of a non-scan D flip-flop (source: ST)                    |    |

| Figure 4.4 Tool input data analysis results (source: ST)                                     |    |

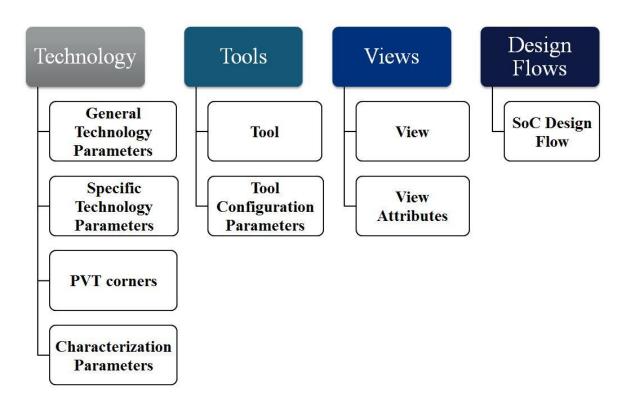

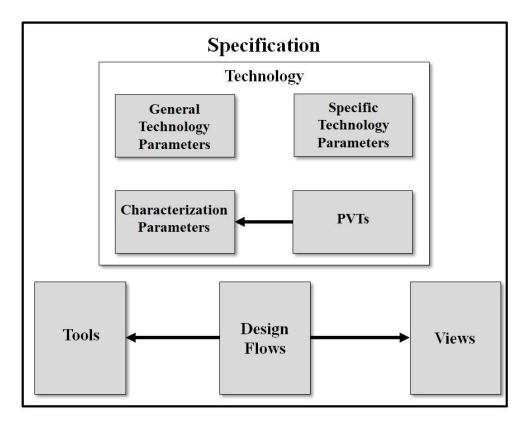

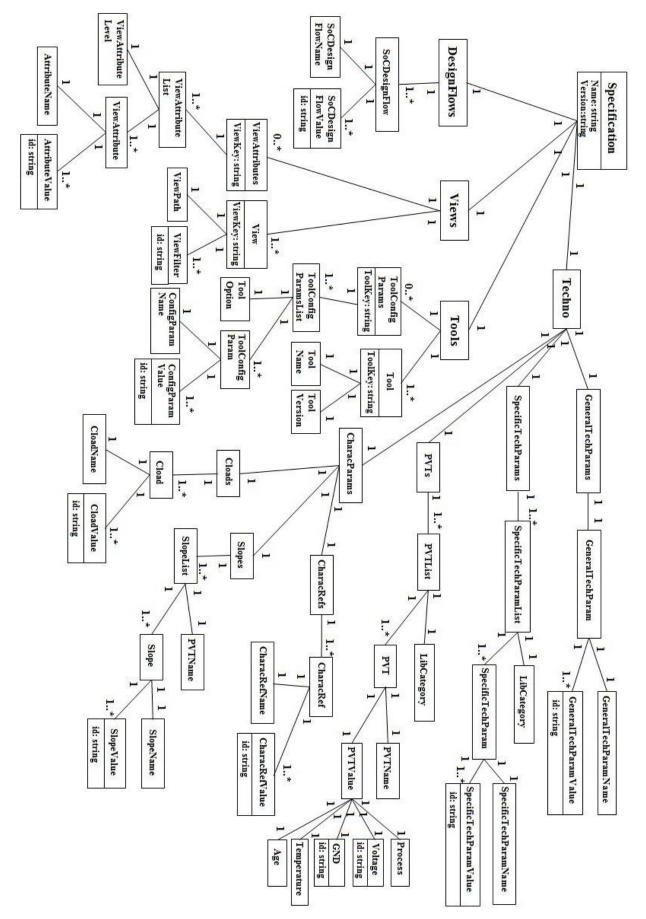

| Figure 4.5 Specification data taxonomy                                                       |    |

| Figure 4.6 Specification data objects and their reference relationship                       |    |

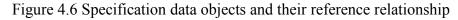

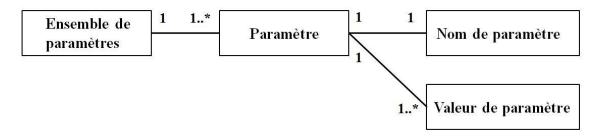

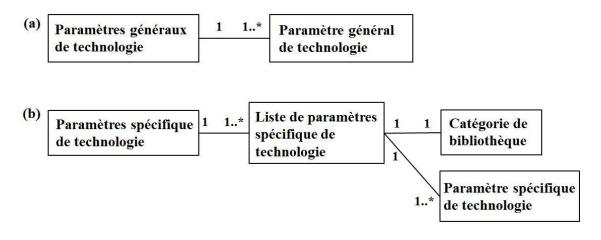

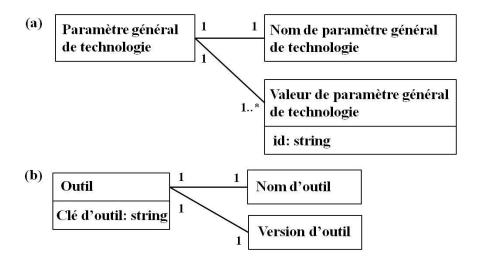

| Figure 4.7 Basic data model of the data object                                               |    |

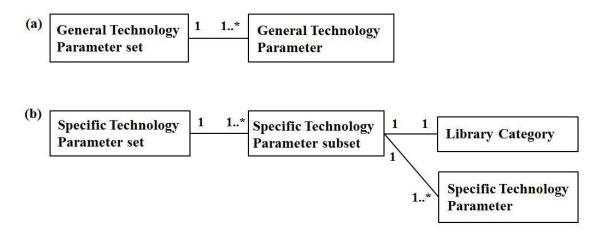

| Figure 4.8 Examples of (a) non-subcategorized parameter set (b) sub-categorized parameter   | •  |

|---------------------------------------------------------------------------------------------|----|

| set                                                                                         | 55 |

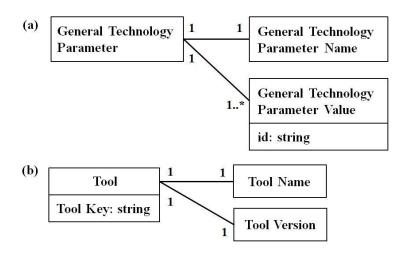

| Figure 4.9 Examples of (a) parameter without key attribute (b) parameter with key attribute | 56 |

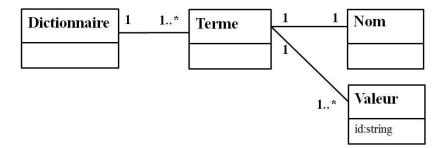

| Figure 4.10 Data model of the specification                                                 |    |

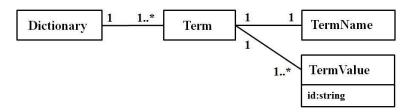

| Figure 4.11 Dictionary                                                                      |    |

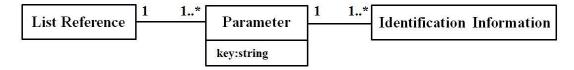

| Figure 4.12 List reference                                                                  | 61 |

| Figure 4.13 Tool list reference                                                             | 62 |

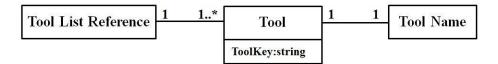

| Figure 4.14 Specification creation using a reference database                               | 63 |

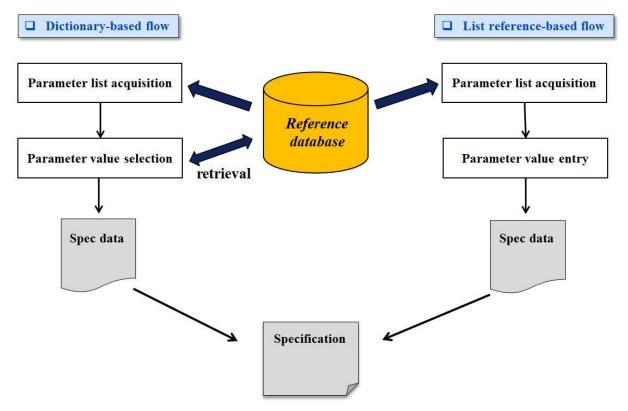

| Figure 4.15 Data extraction with keyword                                                    | 65 |

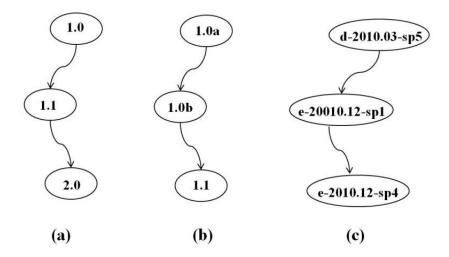

| Figure 4.16 (a) simple tool versioning with numerical increment (b) simple tool versioning  |    |

| with numerical and alphabetical increments (c) complex tool versioning                      | 68 |

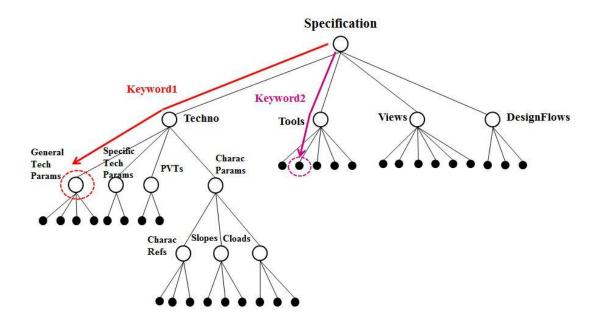

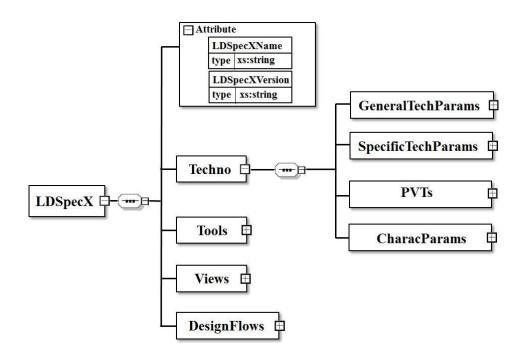

| Figure 5.1 Schema of LDSpecX                                                                | 72 |

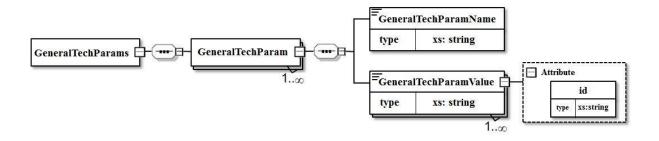

| Figure 5.2 Schema of GeneralTechParams element                                              | 73 |

| Figure 5.3 Example of GeneralTechParams element                                             | 73 |

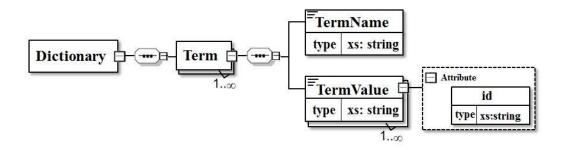

| Figure 5.4 Schema of dictionary                                                             | 74 |

| Figure 5.5 Example of a dictionary                                                          | 75 |

| Figure 5.6 Schema of tool list reference                                                    | 75 |

| Figure 5.7 Example of a tool list reference                                                 | 75 |

| Figure 5.8 Reference-based specification creation flow                                      | 76 |

| Figure 5.9 (a) Specification information entry window (b) Fragment selection window         | 78 |

| Figure 5.10 Data entry page of GeneralTechParams fragment                                   | 79 |

| Figure 5.11 Data entry page of Tool List fragment                                           | 80 |

| Figure 5.12 Specification creation page                                                     | 81 |

| Figure 5.13 Dictionary edit page                                                            | 82 |

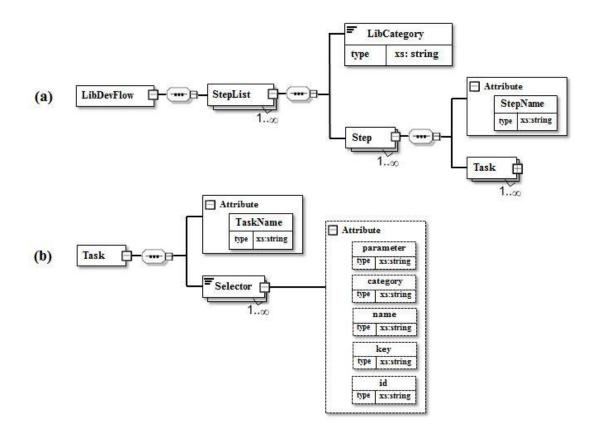

| Figure 5.14 (a) Library development flow (b) Task                                           |    |

| Figure 5.15 Example of a library development flow for standard cell library                 | 84 |

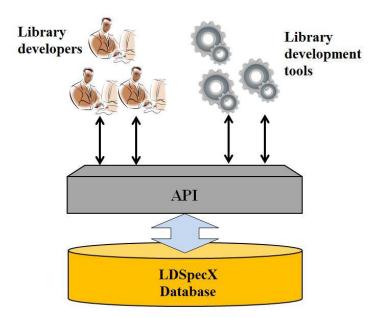

| Figure 5.16 Overview of the API                                                             | 84 |

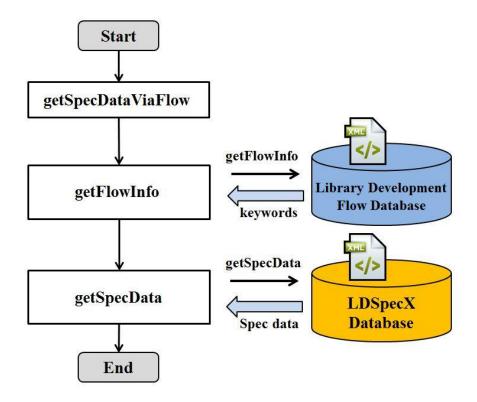

| Figure 5.17 Data extraction flow by using task-based keywords                               | 85 |

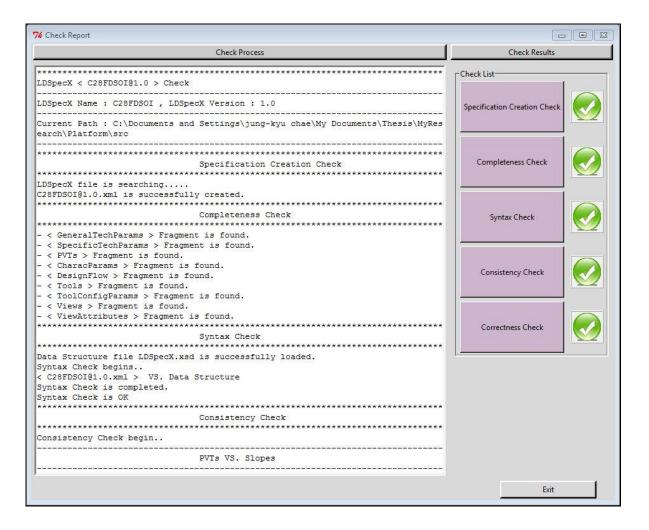

| Figure 6.1 Screenshot of specification check report                                         | 89 |

| Figure 7.1 Overview of the specification platform 1                                         | 00 |

## **List of Tables**

| Table 3.1: Summary of the specifications                                            | 42 |

|-------------------------------------------------------------------------------------|----|

| Table 4.1: Specification data                                                       |    |

| Table 4.2: Library checklist                                                        |    |

| Table 6.1: Comparison of LDSpecX-based specification and traditional specifications |    |

| Table 6.2: Summary of input and output for library development tasks                |    |

|                                                                                     |    |

# 1. Introduction

### Contents

| 1.1 | Motivation                   | 3 |

|-----|------------------------------|---|

| 1.2 | Thesis Objectives            | 4 |

|     | Structure of this Manuscript |   |

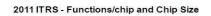

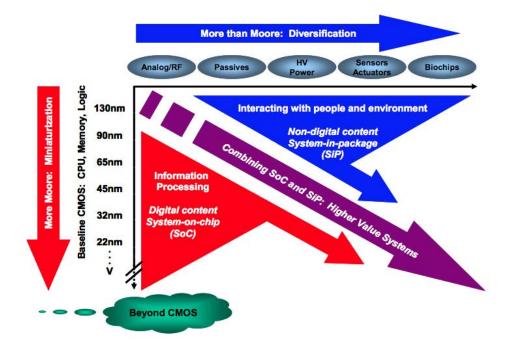

Gordon E. Moore presented the well-known Moore's law in an article published in 1965 [1]. This law describes a trend that the number of transistors on a chip doubles every 24 months. Until now, the development of new process technologies enables to follow Moore's law as shown in Figure 1.1 [2]. In addition to the increasing number of transistors on a chip, the performance of System-on-Chip (SoC) (speed, functionality, etc.) considerably increases but the cost decreases by 30% per year [3].

Figure 1.1 Product Technology Trends: MPU Product Functions/Chip and Industry Average "Moore's Law" and Chip Size Trends (source: ITRS)

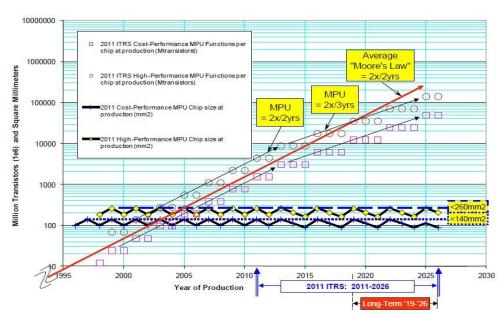

Recently, a new trend called "More than Moore" for the functional diversification of semiconductor-based devices is also remarked. This "More than Moore" trend gives more possibilities to diversify the applications of SoC by interacting with the outside world through an appropriate transduction such as RF communication, passive component, sensor and actuators [4]. The International Technology Roadmap for Semiconductors (ITRS) represents the overview of these two trends toward the miniaturization and diversification as described in Figure 1.2. These trends allow various applications of SoC such as automotive, set-top box and telecommunication so that the market is growing rapidly [3].

Figure 1.2 'Moore's law' and 'More than Moore' trends in the semi-conductor industry (source: ITRS)

However, there are more and more challenges with the new advanced technologies in the manufacturing process, circuit design, system design, and CAD technology [5]. In the manufacturing process, to achieve the downscaling of the devices, both front- and back-end processing must overcome major technological challenges: lithography, device isolation, gate stack, shallow junctions, device engineering, high- and low-k dielectrics, and interconnect schemes [6], [7], [8]. For circuit design, technology scaling brings some advantages such as high speed and density of integration. Nevertheless, circuit designers have to face significant issues such as increased leakage, variability, reducing power supply voltage, signal integrity problems, etc. Some of these issues were never encountered before. In addition, new types of devices and new materials may increase the complexity of the circuit design [9], [10], [11],

[12]. To illustrate an example, for sub-20nm IC technologies, Ultra-Thin Body Silicon on Insulator (UTB-SOI) and FinFET were proposed in order to address the problems derived from the short-channel effects of Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) like decreased sub-threshold voltage  $(V_t)$  and increased device variations by eliminating the leakage paths far from the gate [13], [14]. Hence, more efforts are needed for circuit design with such new types of devices. Likewise, system designers must deal with the issues and challenges for system design in nanometer-scale technologies (inferior to 100nm). Chang [15] remarked three challenges in system design: escalating cost, design complexity and time to market. For example, one of the key challenges is to reduce the power dissipated by the clock tree up to 40% of the total power consumption because of the increased number of flip-flops in the system [16]. For that purpose, the clock gating method [17], [18] and flipflop banking method [19] were proposed to save power consumption of the clock tree. On the other hand, the challenges for CAD technology are strictly related to the aforementioned manufacturing and design challenges. Thus, CAD vendors endeavor to provide users with an efficient tool to assist them in order to overcome their challenges as well as to improve the productivity [20], [21], [22].

Foundries and Integrated Device Manufacturer (IDM) like STMicroelectronics fabricate chips for their customers. They must therefore provide customers with a design platform containing all necessary components such as libraries and Intellectual Property (IP) for chip design. However, the aforementioned issues complicate the development of components. In this thesis, such issues are considered from the perspective of the library development.

### **1.1 Motivation**

In order to rapidly and efficiently bridge increasing design productivity gap with advanced technology, a new paradigm is highly required for system designers as well as library providers.

In the system design, the top-down approach is recently more significant than the bottom-up to efficiently improve the productivity. Thus, many recent researches focused on this approach, for example, a new level of abstraction so-called Electronic System Level (ESL) above the familiar Register-Transfer Level (RTL) and design verification based on the formal specifications [23].

From this aspect, we intend to improve the library development in a top-down approach from the specification because it is the most important starting point for library development. On the other hand, the specifications for library development consist of a celldependent part and a cell-independent one. The former represents functional and structural descriptions of the cell, whereas the latter represents all other information such as process parameters. Especially, the design platform specifications, which we need to deal with, cover only the cell-independent information such as Process-Voltage-Temperature (PVT) corners, CAD tool information, etc. Since such information has an impact on the cell design, we need to discuss it in order to efficiently provide this information for cell design.

However, the design platform specifications are usually written in natural language or tabular form. Thus, they represent a collection of heterogeneous elements. Despite their excessive complexity, library developers must extract the desired data from them either manually or through their own scripts. On top of that, since the current specifications may lack a part of the required information for library development, they should also complete missing information. The lack of information for library development in the current specifications can be caused by two reasons. The first reason is the difference of the view points of the system designers and library developers. For example, the references for the cell characterization such as time threshold and unit information are not defined in these specifications because such information is required for library development but not for SoC design. The second one is the current specification creation method. The specification creation is a manual work. For this reason, it often results in missing information. For example, the specification developer may omit to mention the version of CAD tools. Such missing information leads to increase library development time because we must get it in order to accomplish the library development. Thus, dealing with the specifications depends highly on the expertise of the library developer and manual interventions. It becomes a significant bottleneck in library/IP development.

### **1.2 Thesis Objectives**

The main goal of this thesis is to precisely and rapidly provide library developers with all required information for library development from the specification in order to improve the productivity and quality of the library. Firstly, we propose a unified specification for library development. Secondly, this thesis describes how to efficiently cope with it by developing new methods and tools which provide library developers with a powerful way to smoothly accomplish their tasks for library development.

### **1.3 Structure of this Manuscript**

**Chapter 2** introduces the system design flow as well as its corresponding design platform. Since this design flow is based on predefined libraries/IPs, we explain how to develop them. Then, an example of library development is described. With the help of these observations and experiments, we present crucial issues related to the specification itself and its current processing methods.

**Chapter 3** reviews the state of the art with two traditional specifications in natural language and tabular form. In addition, Unified Modeling Language (UML) and eXtensible Markup Language (XML)-based specifications are presented as emerging ones in SoC design. STMicroelectronics' design platform specifications are also described. Finally, we evaluate them with respect to their advantages and disadvantages.

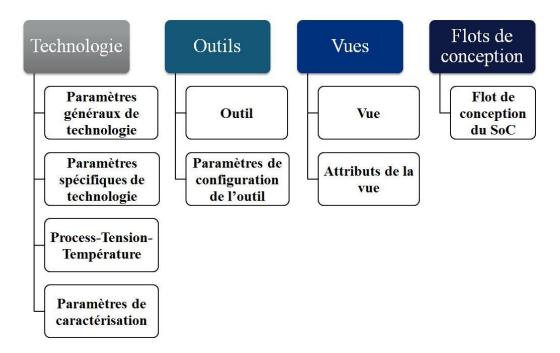

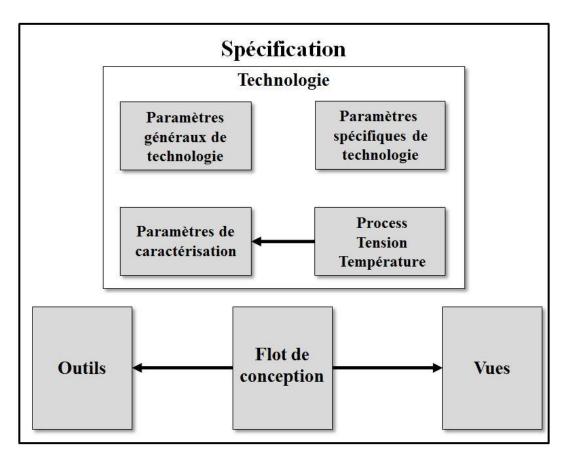

**Chapter 4** proposes the identification of all required data for library development and their classification. This survey helps to propose a suitable data model to represent our specification. To deal with it in an efficient way, we propose some methods to create a reliable specification and to efficiently extract data from it. Furthermore, how to verify both the specification and library is also explained at the end of this chapter.

**Chapter 5** describes a specification language in XML named LDSpecX (Library Development Specification based on XML) based on the data model proposed in the previous chapter. Then, we present a specification platform that consists of two parts. The first one is a user-friendly GUI to create a complete and consistent specification in LDSpecX. The second one is an API to precisely and rapidly extract desired data from the LDSpecX-based specification database.

**Chapter 6** presents the evaluation of our solutions. We show the creation of specification in LDSpecX and the development of a standard cell library from it on the proposed platform.

**Chapter 7** gives the conclusion and proposes relevant directions for future work based on the researches presented in this thesis.

## 2. Library Development from the Design Platform Specifications

### Contents

| 2.1 | Introduction                                          | 7  |

|-----|-------------------------------------------------------|----|

| 2.2 | System-on-Chip Design Flow                            |    |

| 2.3 | Design Platform                                       |    |

| 2.4 | Library Development Flow                              |    |

| 2.4 | 4.1 Specification Phase                               |    |

| 2.4 | 1.2 Design Phase                                      |    |

| 2.4 | 1.3 Derivation Phase                                  |    |

| 2.4 | 1.4 Validation Phase                                  |    |

| 2.5 | Existing Automatic System for Library Development     |    |

| 2.5 | 5.1 Specification Creation Tools                      | 19 |

| 2.5 | 5.2 Circuit Design Tools                              | 19 |

| 2.5 | 5.3 View Derivation Tool                              |    |

| 2.5 | 5.4 Library Verification Tool                         |    |

| 2.6 | Example of the Development of a Standard-cell Library |    |

| 2.7 | Problems                                              |    |

| 2.8 | Conclusion                                            |    |

### **2.1 Introduction**

The system design requires more and more predefined libraries/IPs due to the increasing complexity of the system. Thus, foundries provide system designers with a design platform containing all necessary libraries/IPs in order to support their system design.

The library includes a collection of cells. Its main goal is to offer a wide range of information about the cells to system designer for integrating them into his system. For example, STMicroelectronics's standard cell library for CMOS 28nm FD-SOI technology contains several hundreds of basic cells like combinational and sequential cells. This library package provides various library views to transmit the required cell information to all CAD tools for system design. This library package is produced according to the given library development flow with the help of an automatic system. This system permits to automatically execute more and more tasks instead of the manual work in order to improve the productivity.

Consequently, to achieve the objectives of this thesis, a good understanding of such library development flow and automatic system is indispensable. Additionally, the analysis of the extremely complex relationship between the library development environment and the specification is also required because it may give a key idea to address the issues that arise in library development at the specification level.

In the following section, we present the design flow and design platform for SoC design. Then, we introduce how to develop libraries from the design platform specifications. In addition, an example of the development of a standard cell library is described. From these observations, we discuss the issues related to the specification.

### 2.2 System-on-Chip Design Flow

As mentioned in the previous chapter, technology scaling brings not only attractive advantages but also significant issues and challenges. Thus, many attempts were made to address them from different angles. For system designers, the most crucial challenge is how to rapidly and reliably design the complex system which meets the system requirements. For this purpose, there are several major approaches: custom design, Field Programmable Gate Array (FPGA), standard-cell based design and platform/structured design [24]. Among them, the cell-based design technique is widely adopted to reduce the design cycle as well as to guarantee the functionality and performance of the complex system although the full custom design usually provides a high-performance system than the cell-based design [24], [25], [26], [27], [28], [29], [116], [117]. The richness or optimization of cells in the library may have a great influence on the improvement of the performance of system, for example, in terms of area, delay, and power [60], [61]. Hence, it helps to reduce the performance gap. For instance,

Hashimoto *et al.* [30] demonstrated that a rich library including various driving strength cells improved circuit performance close to transistor-level optimized circuits.

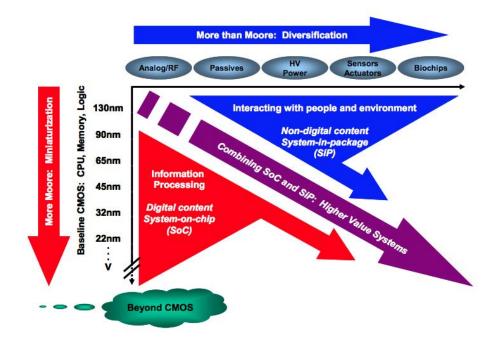

The cell library now plays a central role in SoC design. Various library categories are required, for example, standard-cell library and macro cells such as I/Os and memories. Like these cell libraries, the macro-cell devoted to a specific function, also known as IP has recently become very important. In other words, the library offers a set of cells of the same category, whereas IP deals with only one block such as Pulse-Locked Loop (PLL). They have the same goal: to provide pre-designed cells for system design. As shown in Figure 2.1, the library cells and IPs account for a large part of the recent SoC up to almost 75% [82].

Figure 2.1 Example of a SoC (source: ST)

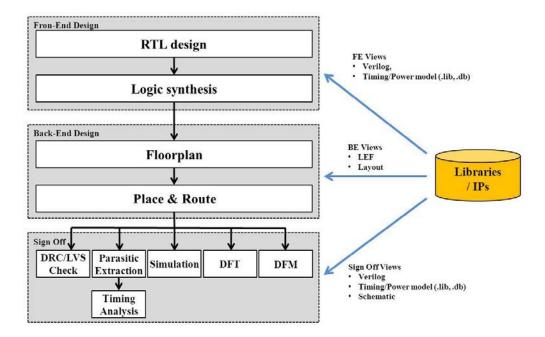

Figure 2.2 represents the cell-based design flow. This design flow splits into three principal steps: Front-End (FE) design, Back-End (BE) design and Sign-Off phases [24], [31]. For the integration of cells, the given library and IP packages provide the required views by CAD tools at all design steps to build a complete SoC.

Figure 2.2 Cell-based design flow

Firstly, the FE design for logical creation can begin with RTL design. This step describes the functionality of the system in Hardware Description Language (HDL) according to its specification. After the RTL design, the logical synthesis must be executed for translating an abstract form of desired circuit behavior (RTL model) into a design implementation in terms of logic gates by using logical views provided by the library/IP package.

After FE design, the Back-End (BE) design for physical creation must be performed to create a physical view of the system so that the floor-planning and place-and-route activities should be accomplished using physical views of the library/IP package. The floor planning activity is the first step in physical design. The process of floor-planning allows analyzing the die size, selecting the packaging, placing I/Os, placing the macro cells, planning the distribution of power and clocks, and partitioning the hierarchy. Then, the placement process determines where each individual cell is physically located on the chip and the routing process permits to create the physical wire connections for the signal and power nets.

Finally, the Sign-Off phase should be carried out to check the final physical layout by several criteria such as design rules and timing constraints. For this purpose, library views such as Verilog view and timing/power models are needed. This phase is absolutely critical to catch any remaining error before tape-out. The created and validated layout of a system can be delivered to fab for manufacturing.

### 2.3 Design Platform

Figure 2.3 Design platform

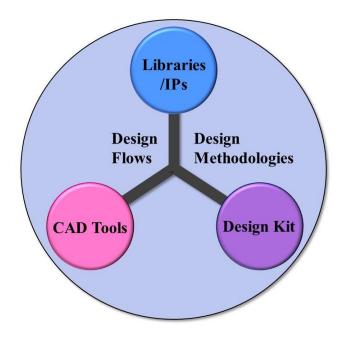

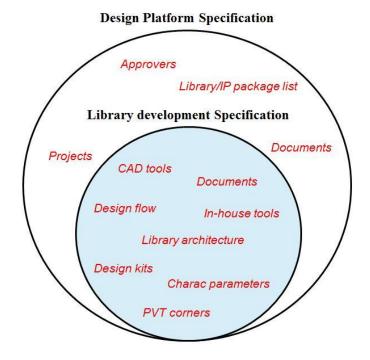

The design platform is a total solution to achieve the SoC design [32], [33], [34]. Since the system designer needs a complete set of libraries and IPs, CAD tools and design kits in conformity with his design flows and methodologies, the design platform consists of all such elements as described in Figure 2.3.

In order to develop a design platform, its specification must first be defined. This specification contains all information related to the target design platform. For each manufacturing technology, a suitable design platform should be developed according to its given specification. Except for commercial CAD tools, which are selected but not developed by definition, all the other components have to be created: libraries, IPs, and design kits including a collection of target manufacturing technology data files such as SPICE models, tech files, and DRC/LVS rule files [35].

In this thesis, we concentrate on the library development from the design platform specifications but this study can also cover IP development because both can be developed by the same activities even if the used methods and tools are slightly different.

### 2.4 Library Development Flow

Figure 2.4 Foundry's library development flow (source: ST)

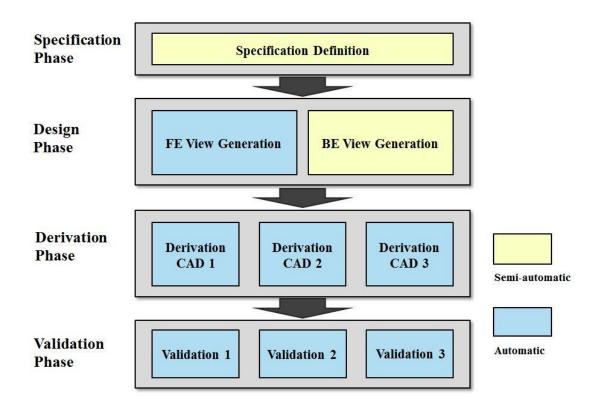

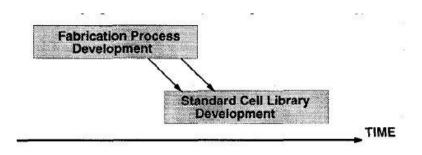

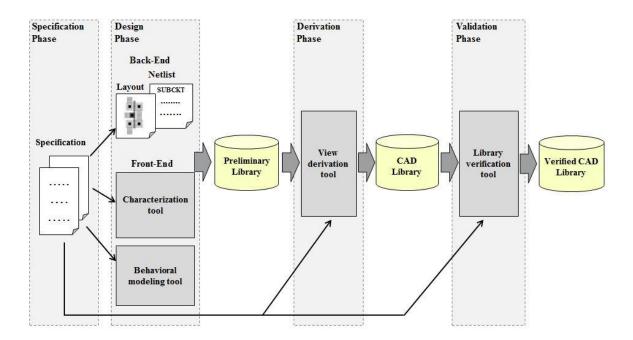

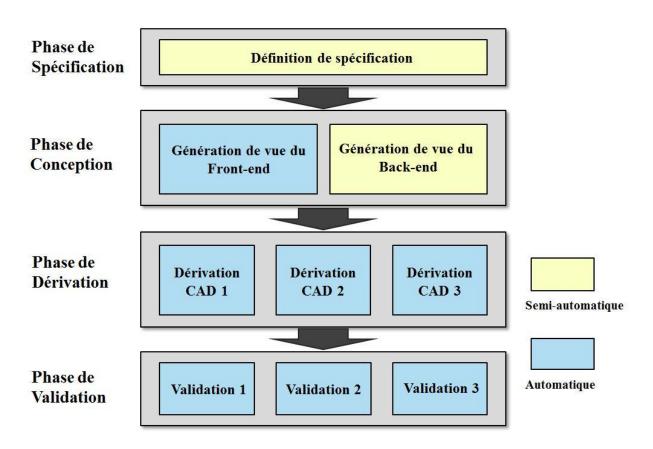

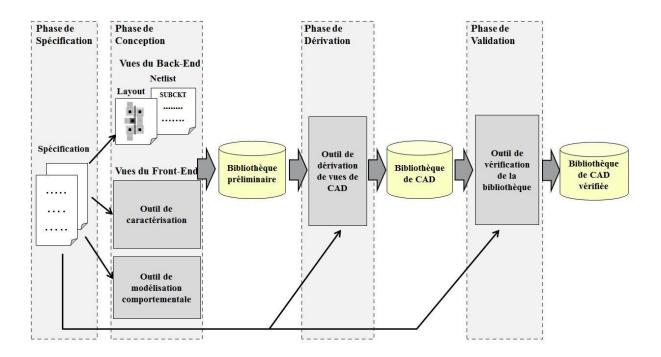

The traditional library development flow presented in the literature focus only on the design phase including FE and BE designs [36], [37], [38], [39], [40]. However, as shown in Figure 2.4, the library development flow in industry is more complex than that. In general, it is composed of four major phases. The first phase is to define a specification for the target technology. The second phase is to design all library cells. The third phase is to derive from the fundamental library views (e.g. layout and schematic) developed during the design phase to various CAD views for supporting various CAD flows. The last phase is to validate the library package by several criteria before their delivery to customers.

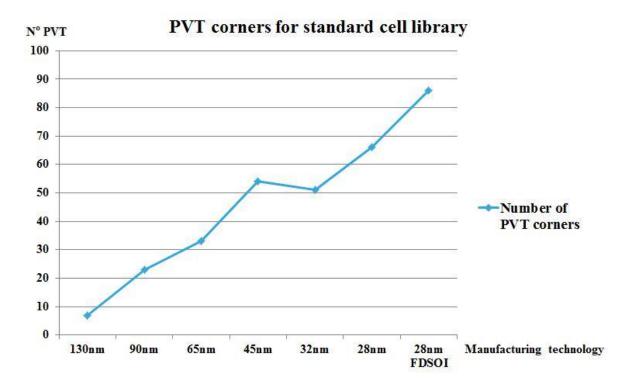

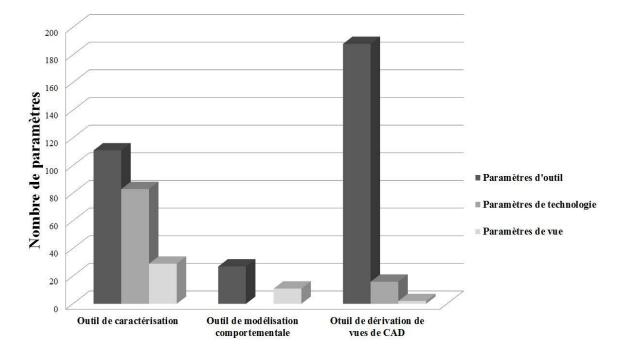

The library development requires the specification which can be divided into the celldependent part and cell-independent one. The cell-dependent part states the structural and functional description of the cell such as its pin name and logical functionality. On the contrary, the cell-independent part specifies all other information that are required for cell design but independent of cell such as process parameters and CAD tools' information. This specification data become increasingly complex. To give an example, each library category needs a set of PVT corners for its cell design. The number of required PVT corners increases with the evolution of manufacturing technology. Figure 2.5 shows the increasing number of PVT corners for standard cell library according to the manufacturing technology. In addition, the required PVT corners may be multiplied by the necessary library categories.

Figure 2.5 PVT corners for standard cell library (source: ST)

Where can the library developers obtain such cell-independent information?

Usually, they can get this information from the design platform specification because it covers most of the cell-independent information. As depicted in Figure 2.6, its scope is larger than that of the library development specification. In other words, some information of the design platform specifications is not necessary to develop libraries. For example, a list of approvers about the information may be required for specification definition but not for library development. On the contrary, the complete list of library/IP packages can be given after finishing their development. Therefore, in this thesis, we limited the scope of the specification to cover only the required information for library development because there are difficulties to deal with the entire design platform specifications under limited conditions. Taking account of it, the following subsections present each phase of the library development flow.

Figure 2.6 Design platform specifications vs. library development specification (source: ST)

### 2.4.1 Specification Phase

The specification phase is significantly important for library development because it aims at collecting all required information. Yuan [41] highlighted the interaction with various functional groups such as process engineering, reliability engineering, CAD tool developers, and the marketing group for gathering the environmental considerations for library development as summarized in Figure 2.7.

|    | Considerations                                                                                                                                | Related Functional Group                        |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 1. | Customer requirement and competitive analysis                                                                                                 | Marketing/Design<br>Engineering                 |

| 2. | Process limitations and reliability<br>considerations - latchup, metal migration,<br>ESD, hot electrons, and associated layout<br>constraints | Process, Reliability,<br>and Design Engineering |

| 3. | Performance limitations based on above                                                                                                        | Design Engineering                              |

| 4. | Place and Route tool capabilities                                                                                                             | CAD/Design Engineering                          |

| 5. | Chip statistics of interconnect capacitance,<br>routability, process variation, voltage<br>and temperature sensitivity                        | CAD, Process, and<br>Design Engineering         |

| 6. | Packaging limitations and modeling                                                                                                            | Packaging and Design Engineering                |

| 7. | Modeling restrictions and workarounds                                                                                                         | CAD/Design Engineering                          |

| 8. | Tool development for the library                                                                                                              | CAD/Design Engineering                          |

Figure 2.7 Environmental considerations for library development [41]

Baltus [42] remarked the essential relationship between the process parameters obtained from the fabrication process development and the cell layout generation in library development as shown in Figure 2.8

Figure 2.8 Layout development flow with manual layout [42]

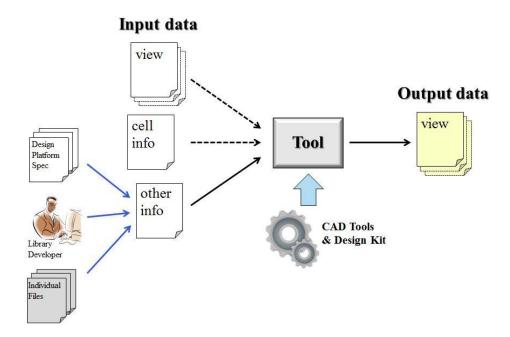

As stated in these studies, the specification for library development must cover a wide range of information. Moreover, the information must be collected from several information owners. Thus, the specification phase is a collaborative work. It consists of collecting the information and creating a specification with the collected information. For example, we need a list of library views and CAD tools' information for library development. The library architect defines the contents of the library package for each library category. The design kit developer determines necessary CAD tools in order to develop a design kit for supporting them. Thus, the information relevant to library views and CAD tools can be obtained from them respectively. Then, the gathered information is defined in the specification.

#### 2.4.2 Design Phase

The design phase is to design all library cells. This phase permits to generate all fundamental views for FE and BE designs of the system. Specifically, in accordance with the cell specification, the cell is designed and then its physical view is created by using a layout editor. However, much effort and time should be devoted to layout design because it determines the performance of the cells. For example, Bittlestone [43] stated that cell height must be considered for layout of standard cells because increasing track height allows reducing total resistance and improving performance. Additionally, power rail also influences the performance of the standard cells. Thus, layout design has to be done by taking into consideration the physical architecture.

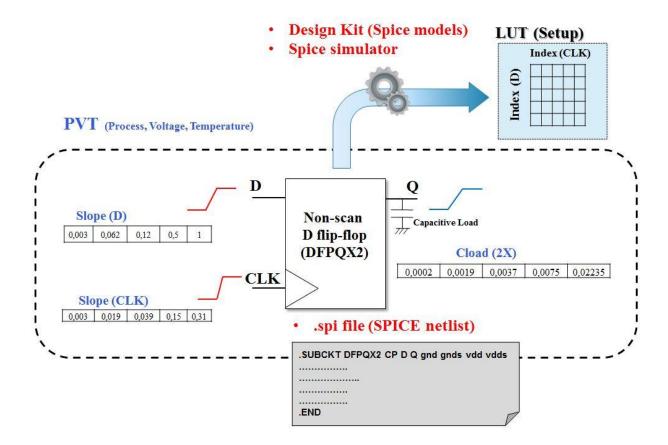

After finishing physical design, library views such as behavioral model for FE design must be produced. This design step involves generating behavioral model and timing model. Behavioral model represents the structural description and the functionality of the cell in Hardware Description Language (HDL) such as Verilog. On the contrary, the timing model containing the timing characteristics of the cell can be generated by two steps. The first step is to characterize the cell in order to extract its timing information such as delay and constraints. The second step is to create a timing model by encapsulating the obtained timing information in Liberty format which is an open source industry standard for library modeling [44]. Since it is very important to provide an accurate timing model for verifying the functionality of the system, various characterization and timing modeling methods were proposed in order to create a more accurate timing model [45], [46], [47], [48], [49], [50]. Traditionally, the timing characterization of the standard cells is based on SPICE simulations to obtain the most accurate timing information by using manufacturer-provided SPICE models although the simulations requires a lot of time. Furthermore, for timing model, Non-Linear Delay Model (NLDM) based on Look Up Table (LUT) is widely used in industry. LUT aims at providing corresponding timing information according to input slope and output load because the timing characteristics rely on them. Thus, various input slope and output load values should be applied to the simulation in order to create a LUT. Recently, for 90nm designs and below, Synopsys's Composite Current Source (CCS) timing model based on the current instead of the voltage threshold for NLDM was proposed because it takes into account some physical effects such as Miller effects, high interconnect impedance, and noise propagation. However, it has several major inconveniences, high runtime being one of them [51], [52]. In addition, power and noise models may also be provided for analyzing the system in terms of power and noise [53], [54], [55], [56], [57]. Moreover, such characteristic models must be made for each PVT corner. It means that they will be multiplied by the number of PVT corners.

### 2.4.3 Derivation Phase

The derivation phase allows generating various CAD views from the fundamental views in order to completely support customers' CAD flows because some of them require their own semantics due to the lack of standardization efforts [58]. For instance, Cadence and Synopsys tools are based on different database platform OpenAccess and MilkyWay respectively [59]. For this reason, we must create these two physical databases for supporting

both CAD implementation flows. Consequently, all required CAD views should be created by the derivation phase to satisfy all customers' design flows.

### 2.4.4 Validation Phase

The quality of the libraries and IPs is directly related to not only their reuse and integration but also the design efficiency of SoC [62]. So they must be verified before their delivery to customers. For that purpose, Lin [63] first discussed the requirements of the high-quality cell library such as the correct functionality of the cell, its accurate timing performance and its layout having no design rule violation. Then, he classified possible errors into five types: incompleteness, inconsistency, functional errors, design rule violation and inaccuracy. As he remarked, errors are easily made during library development process. Therefore, this phase is greatly needed for generating high quality library.

### **2.5 Existing Automatic System for Library Development**

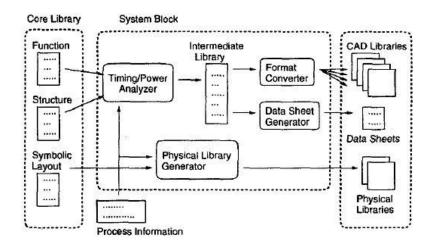

The design automation is an inevitable trend in the SoC design due to the increased complexity of systems [64], [65], [66]. Likewise, it is also indispensable for library development [67] because it is almost impossible to manually perform all related activities. Therefore, an automatic system is needed to facilitate the library development execution as well as to reduce its development time. Indeed, many efforts were made to develop this kind of system in industry but only some of them were presented in literature [68], [69] because all know-how relevant to the library development is related to the competitiveness of the company. In addition, several academic researches were introduced in literature [70], [71], [72], [73] even if there were some limitations to entirely deal with the issues concerning library development due to the restricted accessibility of information. For instance, Onodera [70] developed an automatic generation system of process-portable library named P2Lib which represents the fundamental process as shown in Figure 2.9. This system allows library designers to generate process-portable libraries from a core library containing processindependent information like functional and structural information and process-dependent information. Specifically, the timing/power analyzer generates timing and power information of each cell from process-independent and process-dependent information and then produces an intermediate library containing them. From the intermediate library, the format converter produces tool-specific library views. In addition, two other tools create data sheets and physical library views. Finally, the proposed automatic system produces a complete set of libraries.

Figure 2.9 Overview of P2Lib [70]

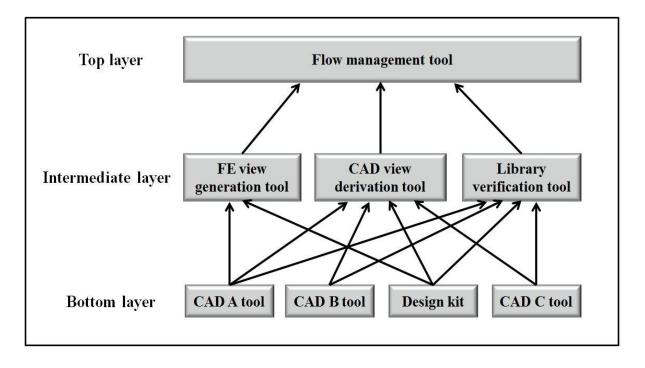

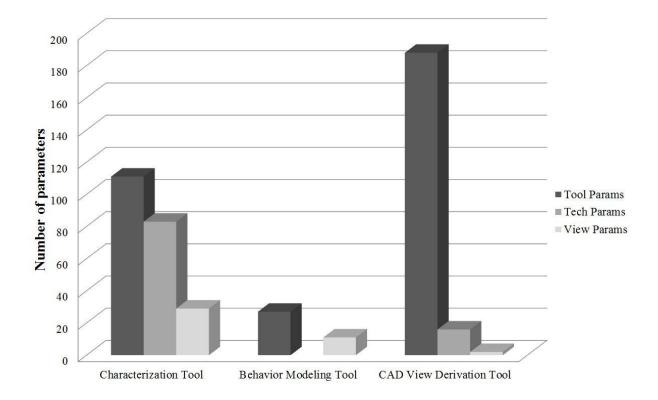

The automatic library development system often consists of several in-house tools developed in programming languages like TCL, Scheme and Perl. Figure 2.10 describes the overview of STMicroelectronics' automatic library development system with only principal in-house tools. These tools which enable to perform the activities for generating library views or verifying them cover most of the phases in Figure 2.4 except semi-automatic steps. In the following sections, we introduce how to accomplish each phase by using these specific in-house tools.

Figure 2.10 Overview of an automatic library development system (source: ST)

### 2.5.1 Specification Creation Tools

Traditionally, the specifications for library development are based on natural language and tables. Thus, according to the characteristics of the information, the specification developer defines data in natural language or tabular form so that he can store them in a file by using office tools like Word and Excel. To illustrate an example, the person in charge of the information relevant to the cell characterization has to enter manually all process parameters such as capacitive loads in the tables. Figure 2.11 shows an example of the definition of maximum capacitance in table form by using Excel. In this manner, other process parameters for cell characterization can also be defined. However, each group of process parameters must be given in different tables or different spreadsheets.

| 1  | A             | В               |

|----|---------------|-----------------|

| 1  | DRIVE STRENTH | MAX CAPACITANCE |

| 2  | X2LOAD        | 0,02235         |

| 3  | X3LOAD        | 0,03278         |

| 4  | X4LOAD        | 0,0447          |

| 5  | X5LOAD        | 0,05513         |

| 6  | X6LOAD        | 0,06705         |

| 7  | X7LOAD        | 0,07748         |

| 8  | X8LOAD        | 0,0894          |

| 9  | X9LOAD        | 0,10132         |

| 10 | X10LOAD       | 0,11175         |

| 11 | X11LOAD       | 0,12218         |

| 12 | X12LOAD       | 0,1341          |

| 13 | X13LOAD       | 0,14602         |

| 14 | X14LOAD       | 0,149           |

| 15 | X15LOAD       | 0,1639          |

| 16 | X16LOAD       | 0,1788          |

| 17 | X17LOAD       | 0,1937          |

| 18 | X18LOAD       | 0,2086          |

| 19 | X19LOAD       | 0,2086          |

| 20 | X20LOAD       | 0,2235          |

Figure 2.11 Maximum capacitance (source: ST)

### 2.5.2 Circuit Design Tools

The library designer must design all involved cells in the library according to their functional and structural description. For circuit design, he also needs the correct information about CAD tools, design kit, and various technology-dependent parameters. All such information should be obtained from the given design platform specifications. If all fundamental information is prepared, the circuit design can be performed by using CAD tools. Firstly, in order to create BE views such as schematic, symbol, and layout, a CAD tool suite for physical creation is required. The cell design is often carried out manually with expertise in designing the high performance cell in terms of area and delay. On the contrary, FE view

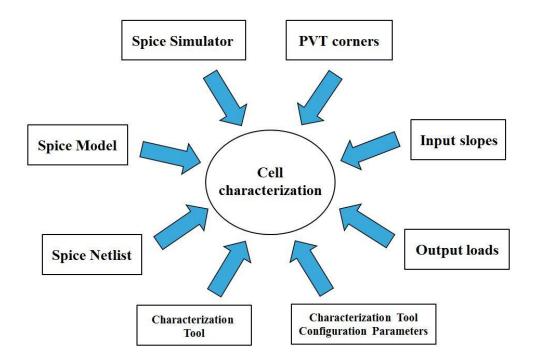

generation can be accomplished automatically by using in-house tools such as characterization and behavioral modeling tools depicted in Figure 2.10. As a result, logical models in HDL and timing/power models can be produced for logical synthesis and timing analysis [74], [75], [76], [77], [78], [79], [80]. The logical model can be derived from only functional and structural information by using a behavioral modeling tool because it is independent of technology. On the contrary, the timing/power modeling is highly dependent of technology so that its generation requires lots of information related to the target technology for cell characterization as shown in Figure 2.12. To make accurate timing/power models, we must extract the timing/power data from the simulations under various conditions which is made of PVT corners, input slopes and output loads. The characterization tool first create SPICE input file (.cir) including a SPICE netlist, stimuli and statements for the data extraction with the given characterization conditions. Then, the obtained characteristics of the cells can usually be encapsulated in Liberty library file (.lib).

Figure 2.12 Cell characterization

### 2.5.3 View Derivation Tool

The library package must contain the appropriate CAD views for customers' CAD tools supported by the design platform. The required CAD view can be created by transforming a reference view into a desired CAD view by using the view derivation tool. For

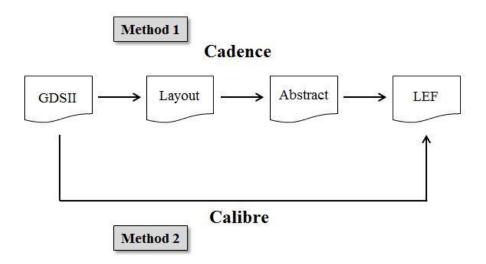

example, Library Exchange Format (LEF) containing physical layout information of the cells is required for place-and-route step in system design. This physical abstract view can be derived from GDSII view depending on the type of library cells. There are two possible methods to generate this view from GDSII view as described in Figure 2.13. The first method is to use Cadence tool through several steps from GDSII view to LEF view. The second method is to directly produce LEF view from GDSII view by using the design rule of Mentor Calibre [118].

Figure 2.13 LEF generation methods (source: ST)

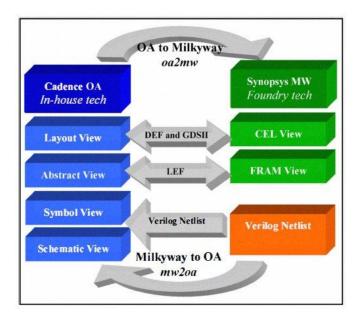

[59] presents two principal programs named **oa2mw** and **mw2oa** to translate between Cadence OpenAccess (OA) [119] and Synopsys Milkyway (MW) [120] databases. Figure 2.14 briefly describes the proposed method and tool for view transformation. The **oa2mw** program permits to transform Cadence OpenAccess database into Synopsys Milkyway database via the following files: Design Exchange Format (DEF), GDSII, LEF and Verilog netlist. To give an example of generating a place and route abstract (FRAM) view (Synopsys MW) from an abstract view (Cadence OA), an in-house tool first generates an abstract view. By using **oa2mw** program, the abstract view is translated into LEF view and then, LEF view can be translated into FRAM view.

As shown previously, the view derivation tool permits to generate the desired CAD views from the reference views by applying appropriate methods for each CAD view.

Figure 2.14 Methodology of the transformation between Cadence OA and Synopsys MW databases [59]

#### 2.5.4 Library Verification Tool

The current library verification tool provides several categories of check: library view list, syntax, consistency, modelization, etc. It helps to verify the completeness and correctness of the library for its high quality. For instance, the library should be verified in accordance with a list of library views to make sure if the library contains all necessary views. For that, the library verification tool reads a specification file containing this list, and then compares the generated library views with the given list of library views. In addition, the correctness of library view is also verified. For instance, an attempt to read Verilog model by synthesis tool allows checking its correctness in terms of syntax. Consequently, if the library verification tool provides more checks, the quality of the library would be more guaranteed.

#### 2.6 Example of the Development of a Standard-cell Library

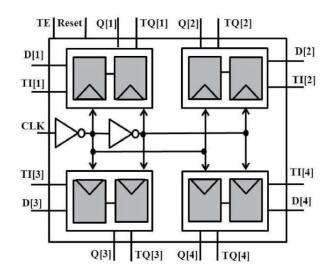

In this section, we describe how to develop this standard-cell library through the library development process by using in-house tools because developing a library can be very beneficial to effectively understand the library development process with its automatic system. A standard-cell library including sequential circuits named 'multi-bit flip-flop bank' has been developed from BE views with the specification for 90nm CMOS technology. This

library contains 2-, 4- and 8- bit flip-flop banks. The schematic of a 4-bit flip-flop bank is given in Figure 2.15.

Figure 2.15 Schematic of a 4-bit Flip-Flop Bank

#### • Specification Data Preparation

As mentioned above, the library development requires a large number of data that must first be gathered from the specifications. Firstly, we need a list of library views to produce a complete library package. Secondly, a list of PVT corners and a set of process parameters must be obtained from the characterization specification. Thirdly, the correct design kit and tools' information like tool version are needed to execute tasks for library view generation and validation. Finally, for in-house tool use, the configuration of tool should be correctly fitted by defining the specific tool configuration parameters. A large part of these parameters can be obtained from the current specifications by human inspection or scripts of the library developer. The extracted specification data have been stored in several machinereadable files for in-house tools.

In this observation, we needed to accomplish the FE and CAD view generation and to perform library validation. For these steps, all necessary data have been manually collected from several scattered files containing specification data in natural language or tabular form.

#### • Front-End View Generation

FE view generation is divided into two major tasks: timing/power models and behavioral model generations. For creating timing/power models, all library cells were

#### CHAE Jung Kyu – Doctoral thesis - 2014

characterized under three PVT corners (for best, typical and worst process corners) with various process parameters such as input slope by using SPICE simulations. The corresponding timing and power characteristics could be obtained from the simulation results for each PVT corner. As multi-bit flip-flop bank is a sequential circuit, delay, setup, hold and min pulse width must be extracted as timing information of the cell. In addition, the worst value is used to make a timing model. In contrast, leakage power and internal energy must be extracted to provide power information of the cell [107]. The obtained timing and power information was built in LUT form according to the corresponding input slope and output load values and then these characteristic information and the structural and functional description of the cell were written in Liberty library format (.lib) [44]. Furthermore, 90nm and below, CCS timing model is required so CCS timing models were also produced. Unlike timing/power model, which aims at providing the characteristics of the cells, the behavioral model gives the description of the circuit and its function. Such information could be extracted from the cell specification and then written in Verilog by using behavioral modeling tool.

#### • CAD View Generation from the Fundamental Views

After generating fundamental views, supplementary CAD views must be produced for the supported CAD flows. By using the view derivation tool, Liberty library files (.lib) were first compiled by Library Compiler and then, LEF file was generated from GDSII by Method 2 presented in Figure 2.13. Additionally, OpenAccess and Milkyway databases were also generated from the fundamental physical view for supporting Cadence and Synopsys CAD flows respectively.

#### • Library View Validation

By using the library verification tool, the multi-bit flip-flop bank library obtained from the previous phases has been verified according to the checklist below:

- ✓ Completeness check (library view list)

- ✓ Syntax check (Verilog, Liberty library)

- ✓ Consistency check of library views

Finally, multi-bit flip-flop bank library package was obtained through the aforementioned library development process.

#### 2.7 Problems

In the context of this thesis, we focused on the cell-independent specification for library development. Thanks to the aforementioned observations and experiments, we remarked several crucial issues related to the specification from various view-points. These issues can be divided into two parts depending on whether they relate to the specification contents or specification processing. Many individuals like design platform developers, library architects and library developers deal with our target specifications. They can be regrouped into two groups according to their role: specification developer and specification user. The specification developer is the person who participates in creating the specifications. On the contrary, the specification user is the person who uses data obtained from the specifications. According to these two roles, the specification processing can be divided into two activities: specification and data extraction from the specification. Thus, the issues regarding the specification processing are also classified by these activities.

All remarked issues are summarized as follows:

#### \* Specification:

- *Informality*: No unified formalism is currently available to define a wide range of information in the specification. As a consequence, information is often written in different ways like natural language or table form and stored in different files according to the characteristics of information and author's ability.

- *Inconsistency*: The current specifications are created by several individuals and stored in scattered files having duplicate data so that the specification may often have consistency problems like mismatching CAD tool version and naming convention.

- *Missing information*: The specification developer defines a specification from the different point of view with the library developer. Thus, it is difficult to know precisely which information is required to develop libraries. In other words, there is always a gap between the information provided by specification developers and the required information for specification users which results in missing information.

- *Increasing specification data volume*: Technology scaling leads to continuously increase the process variation which considerable influences the functionality of

the system. For instance, PVT variability causes fluctuation in timing and power for SoC designs, hence more and more PVT corners are required as shown in Figure 2.5 [43], [81], [82], [83]. In addition to technology scaling, supported library categories and new design flows also may increase the volume of specification data like the number of the necessary library views.

• *Ambiguity*: The specification information is interpreted by specification developers and specification users. In order to define obvious information in the specification, the interaction between them is significantly important. However, it is not sufficiently done and thus, some information may provoke ambiguity problems.

#### **\*** Specification creation:

- Lack of a unique reference database: To define a specification requires a set of golden references such as library naming convention, tool list and library structure. However, there is no unique repository containing all references. In addition, since the existing references represent the documents in natural language and tabular form, it is difficult to centralize them. For these reasons, their accessibility can be low. It results in increasing specification creation time.

- *Absence of a specification assistant tool*: The specification developer enters all specification data manually with the help of office tools. Furthermore, they prefer to copy the old specification rather than refer to the references in order to create a new specification. As a result, such tedious way may cause specification errors.

- *Absence of specification checks*: The verification of specification relies on the specification developers so that the specification errors can be detected by human inspection. It is not sufficient to ensure the high quality of the specification as well as cover increasing specification data volume.

#### **\*** Specification data extraction:

• *Need for efficient methods and tools for the specification data extraction*: One of the important issues in library development is to extract necessary data from the specification by human inspections and individual scripts. Thus, current specification data extraction method can significantly degrade library development time. The average time consumption for the data extraction from the current specifications is obtained from library developers. It is about 4 hours because most of data should be extracted manually. For example, the cell characterization requires a lot of process parameters but their extraction is now carried out manually.

#### **2.8** Conclusion

In this chapter, we have introduced the cell-based design flow and design platform for supporting this design flow. In order to produce a design platform, all of the required libraries/IPs must be developed. Firstly, the library development flow has been presented phase by phase. Then, we explained how to perform each phase in the existing automatic system. Additionally, we also developed a standard cell library containing several multi-bit flip-flop banks throughout the development flow with the help of the existing automatic system.

In summary, the library developers need to get an amount of required data from the specification for successfully accomplishing the library development. It enables to build a complete design platform. Furthermore, efficiently dealing with the specification data is one of the most important challenges in library development. Thus, all crucial issues relevant to the specification have been remarked in the previous section. By addressing these issues, we may considerably improve the productivity of the library by quickly and precisely providing all required data to the automatic library development system. For this purpose, the following chapter first reviews various kinds of the specifications presented in the literature as well as the current specifications employed by STMicroelectronics.

CHAE Jung Kyu – Doctoral thesis - 2014

# 3. State-of-the-art

#### Contents

| 3.1 | Introduction                                       | . 28 |

|-----|----------------------------------------------------|------|

| 3.2 | Natural Language-based Specification               | . 29 |

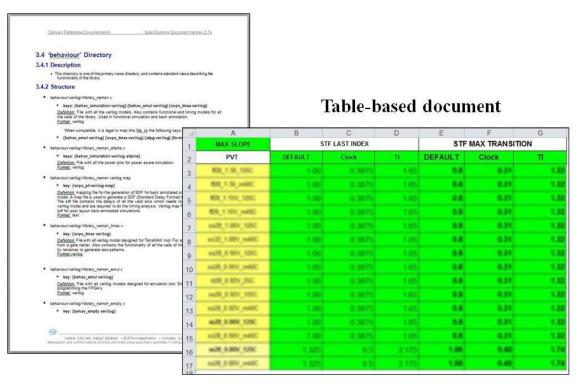

| 3.3 | Table-based Specification                          | . 29 |

| 3.3 | .1 System Requirements Specification in SCR        | . 30 |

| 3.3 | .2 ADeVA                                           | . 32 |

| 3.4 | UML-based Specification                            | . 34 |

| 3.5 | XML-based Specification                            | . 36 |

| 3.5 | .1 IP-XACT for Digital IPs                         | . 37 |

| 3.5 | .2 ASDeX for Analog IPs                            | . 39 |

| 3.6 | STMicroelectronics' Design Platform Specifications | . 41 |

| 3.7 | Discussion                                         | . 42 |

| 3.8 | Conclusion                                         | . 43 |

#### **3.1 Introduction**

The specification represents a collection of information to carry out an activity and is considered as its starting point. For instance, the component specification provides all the information relevant to cells such as their functionality and structural description for cell design. Likewise, the specification is required for library development as described in the previous chapter. However, it is highly important to determine which information must be defined in the specification and how to deal with it. We need a unified specification instead of current ones because it may facilitate to deal with its information.

There are various kinds of specifications from the natural language-based specification to the specification based on XML in order to represent the information. In this chapter, we first discuss the traditional specifications in natural language and tabular form, and the emerging specifications based on UML and XML. Furthermore, the current specifications employed at STMicroelectronics are also introduced.

#### 3.2 Natural Language-based Specification

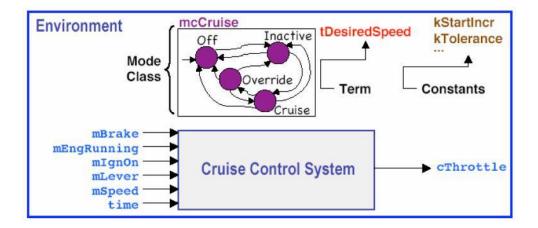

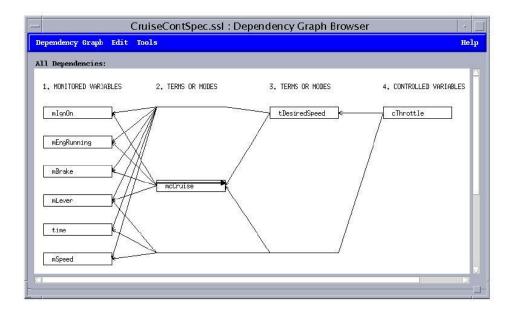

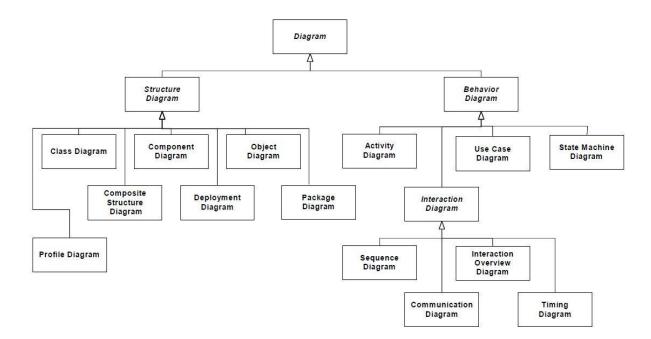

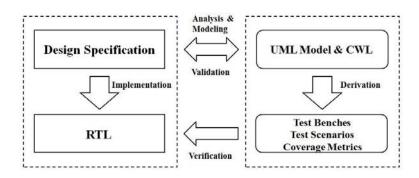

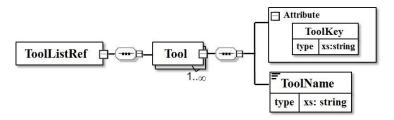

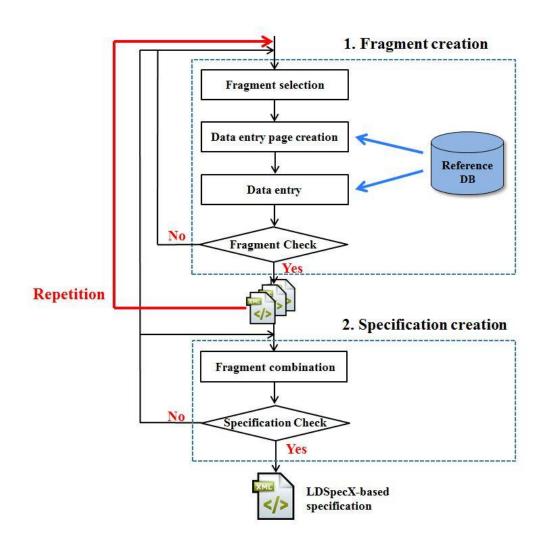

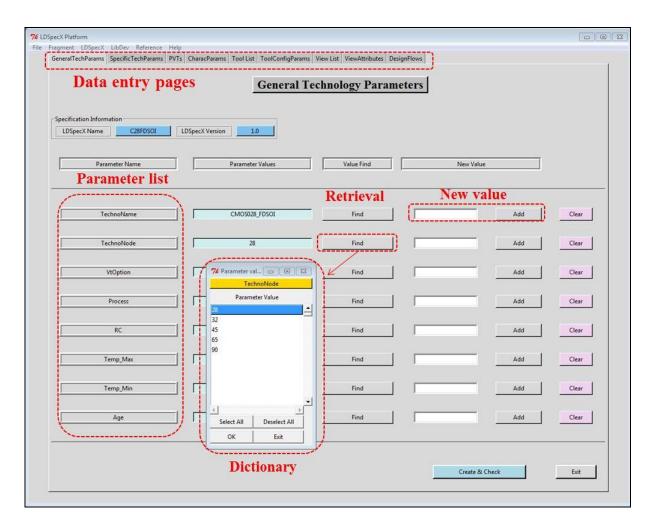

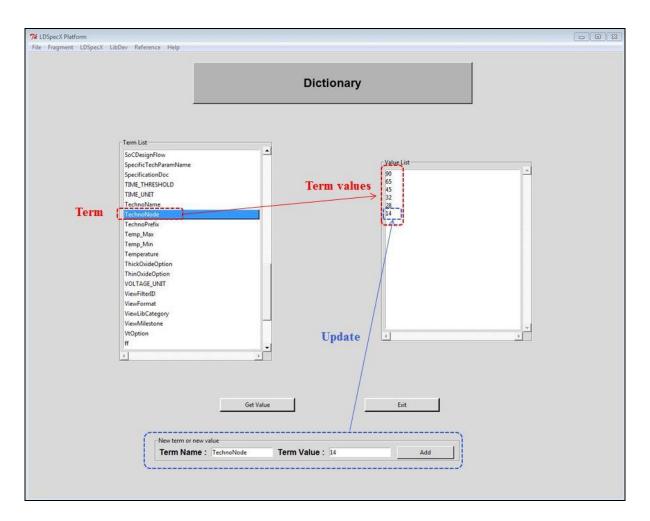

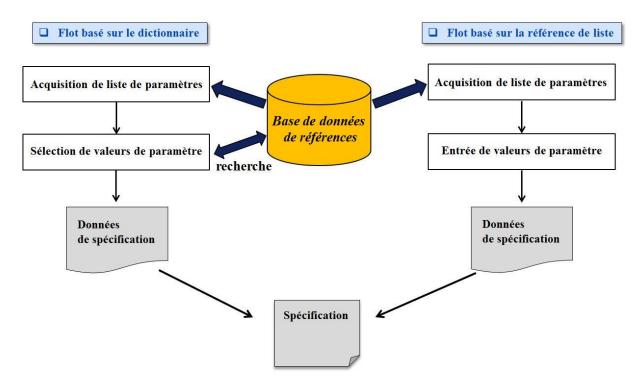

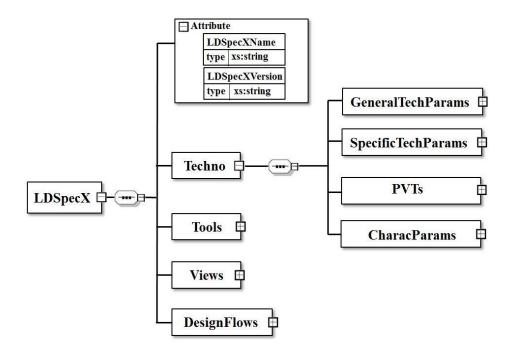

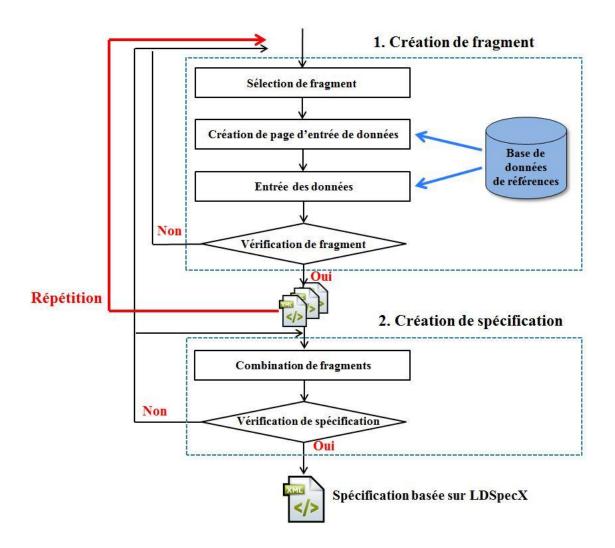

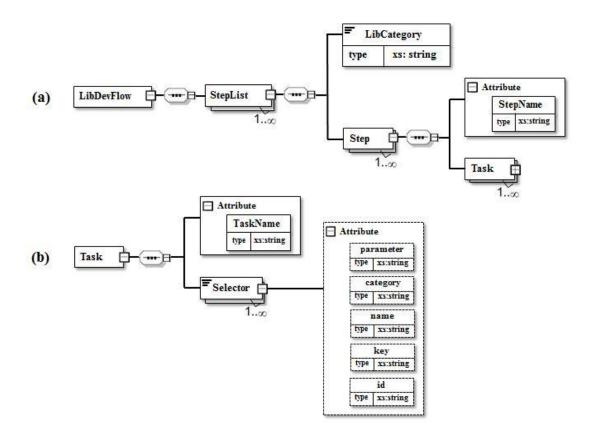

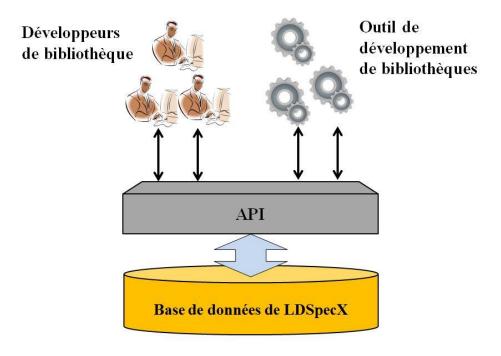

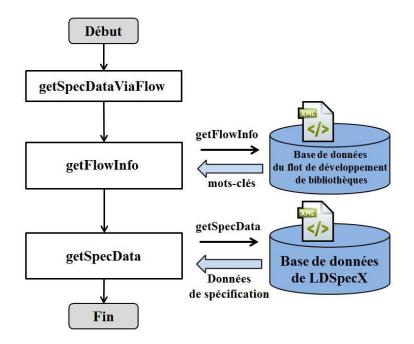

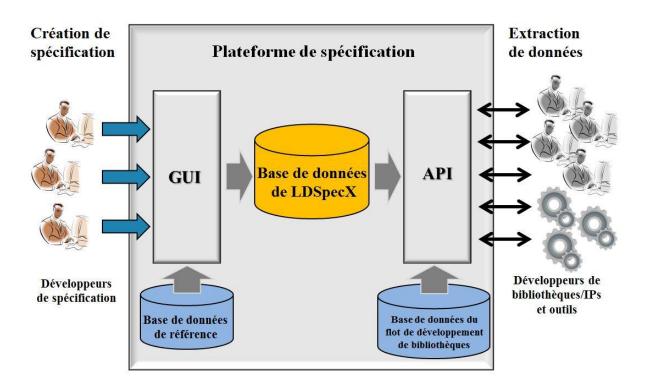

The specification has often been written in natural language until now although the development of computer engineering enables to efficiently manage information. It is so because the natural language is preferred as the initial and simple way to describe the desired information. Furthermore, the component specification and system specification are also defined by designers with the same method. Thus, in system design, some previous works focused on translating the natural language-based specification into a formal description, e.g. HDL or ESL by using a semantic analysis that allows extracting the information from the given textual specifications. For example, [84] presents a translator named Semantic Parser, which is based on a syntactic parser, the Natural Language ToolKit and a semantic grammar. This parser enables to translate the natural language description of a component into a simulatable Verilog model by extracting the key information from the given sentences and rewriting it in Verilog. Similarly, [85] introduces the translation of informal textbook specifications into a formal ESL implementation such as SystemC. For this purpose, Formal Specification Level (FSL) has been proposed to bridge them. Specifically, this intermediate level allows decomposing the sentences in terms of noun, verb, and adjective by syntactic and grammatical analysis and then extracting the structure behavior and properties of the system from the decomposed sentences. Finally, the obtained information is used to create a SystemC model.