### Reconciling performance and predictability on a noc-based mpsoc using off-line scheduling techniques

Manel Djemal Fakhfakh

#### ▶ To cite this version:

Manel Djemal Fakhfakh. Reconciling performance and predictability on a noc-based mpsoc using off-line scheduling techniques. Other [cs.OH]. Université Pierre et Marie Curie - Paris VI, 2014. English. NNT: 2014PA066145. tel-01126944

#### HAL Id: tel-01126944 https://theses.hal.science/tel-01126944

Submitted on 6 Mar 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

#### Spécialité Informatique

(École Doctorale Informatique, Télécommunication et Électronique)

## Présentée par MANEL DJEMAL

Pour obtenir le grade de DOCTEUR DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

## RÉCONCILIER PERFORMANCE ET PRÉDICTIBILITÉ SUR UN MANY-COEUR EN UTILISANT DES TECHNIQUES D'ORDONNANCEMENT HORS-LIGNE

#### Soutenue le 27 juin 2014, devant le jury composé de

| Mme. | FLORENCE MARANINCHI    | Verimag, Grenoble        | Rapporteur         |

|------|------------------------|--------------------------|--------------------|

| M.   | RENAUD SIRDEY          | CEA, Saclay              | Rapporteur         |

| M.   | BERTRAND GRANADO       | UPMC, LIP6, Paris        | Examinateur        |

| M.   | François Irigoin       | CRI - MINES ParisTech    | Examinateur        |

| M.   | LOUIS MANDEL           | Collège de France, Paris | Examinateur        |

| M.   | François Pêcheux       | UPMC, LIP6, Paris        | Examinateur        |

| Mme. | ALIX MUNIER-KORDON     | UPMC, LIP6, Paris        | Directeur de thèse |

| M.   | DUMITRU POTOP-BUTUCARU | INRIA, Rocquencourt      | Encadrant de thèse |

## PH.D. THESIS OF THE UNIVERSITY PIERRE AND MARIE CURIE

Department : COMPUTER SCIENCE AND MICRO-ELECTRONICS

Presented by: MANEL DJEMAL

Thesis submitted to obtain the degree of DOCTOR OF THE UNIVERSITY PIERRE AND MARIE CURIE

# RECONCILING PERFORMANCE AND PREDICTABILITY ON A NOC-BASED MPSOC USING OFF-LINE SCHEDULING TECHNIQUES

#### Defence on 27 June 2014, Committee:

| Mme. | FLORENCE MARANINCHI    | Verimag, Grenoble        | Reviewer   |

|------|------------------------|--------------------------|------------|

| M.   | RENAUD SIRDEY          | CEA, Saclay              | Reviewer   |

| M.   | BERTRAND GRANADO       | UPMC, LIP6, Paris        | Examiner   |

| M.   | François Irigoin       | CRI - MINES ParisTech    | Examiner   |

| M.   | LOUIS MANDEL           | Collège de France, Paris | Examiner   |

| M.   | François Pêcheux       | UPMC, LIP6, Paris        | Examiner   |

| Mme. | ALIX MUNIER-KORDON     | UPMC, LIP6, Paris        | Advisor    |

| M.   | DUMITRU POTOP-BUTUCARU | INRIA, Rocquencourt      | Co-Advisor |

#### Remerciements

Je tiens à remercier en premier lieu Alix Munier, ma directrice de thèse, qui a toujours été à mon écoute et a veillé sur le bon déroulement de ma thèse.

Je remercie également Dumitru Potop-Butucaru, mon encadrant de thèse, pour m'avoir proposé un sujet passionnant, pour avoir eu la patience de m'encadrer pendant tout ce temps et pour les discussions fructueuses et les conseils avisés qil a su me prodiguer durant tout ce travail.

Ensuite, toutes mes remerciments à Florence Maraninchi et Renaud Sirdey d'avoir accepté la lourde tâche d'être rapporteurs de cette thèse, leurs commentaires ont augmenté mon recul par rapport aux domaines traités. Je remercie de même Bertrand Granado, François Irigoin, Louis Mandel et François Pêcheux de m'avoir fait l'honneur de faire partie de mon jury.

Mes remerciments s'adressent plus particulièrement à François Pêcheux, Frank Wajsburt et Zhen Zhang avec qui j'ai eu le plaisir de travailler sur certains aspects de ma thèse. Le temps n'aurait pas passé si vite s'il n'y avait pas eu Meriem Zidouni, Thomas Carle, Cécile Stentzel sans oublier leur soutien pendant la rédaction du manuscrit.

Je voudrais remercier aussi ma famille et mes amis qui m'ont soutenu, pour tout ce que je leur ai fait subir pendant tout ce temps, chacun à sa façon m'a aidé à traverser ces trois ans de ma vie.

Enfin, je remercie mon mari qui m'a soutenu, encouragé et supporté. Sans lui, cette thèse n'aurait été qu'une thèse et certainement la vie n'aurait pas été si belle. Sans oublier biensur mon ange Nour.

#### Résumé

Les réseaux-sur-puces (NoCs) utilisés dans les architectures multiprocesseurs-sur-puces posent des défis importants aux approches d'ordonnancement temps réel en ligne (dynamique) et hors-ligne (statique). Un NoC contient un grand nombre de points de contention potentiels, a une capacité de bufferisation limitée et le contrôle réseau fonctionne à l'échelle de petits paquets de données. Par conséquent, l'allocation efficace de ressources nécessite l'utilisation des algorithmes da faible complexité sur des modèles de matériel avec un niveau de détail sans précédent dans l'ordonnancement temps réel. Nous considérons dans cette thèse une approche d'ordonnancement statique sur des architectures massivement parallèles (Massively parallel processor arrays ou MPPAs) caractérisées par un grand nombre (quelques centaines) de coeurs de calculs. Nous identifions les mécanismes materiels facilitant l'analyse temporelle et l'allocation efficace de ressources dans les MPPAs existants. Nous déterminons que le NoC devrait permettre l'ordonnancement hors-ligne de communications, d'une manière synchronisée avec l'ordonnancement de calculs sur les processeurs. Au niveau logiciel, nous proposons une nouvelle méthode d'allocation et d'ordonnancement capable de synthétiser des ordonnancements globaux de calculs et de communications couvrants toutes les ressources d'exécution, de communication et de la mémoire d'un MPPA. Afin de permettre une utilisation efficace de ressources du matériel, notre méthode prend en compte les spécificités architecturales d'un MPPA et implémente des techniques d'ordonnancement avancées comme la préemption pré-calculée de transmissions de données. Nous avons évalué notre technique de mapping par l'implantation de deux applications de traitement du signal. Nous obtenons dans les deux cas de bonnes performances du point de vue de la latence, du débit et de l'utilisation des ressources.

**Mots clés:** Multiprocesseurs-sur-puce (many-coeur), réseau-sur-puce (NoC), ordonnancement hors-ligne, ordonnancement temps réel

**Titre en anglais:** Reconciling performance and predictability on a NoC-based MPSoC using off-line scheduling technique.

#### **Abstract**

On-chip networks (NoCs) used in multiprocessor systems-on-chips (MPSoCs) pose significant challenges to both on-line (dynamic) and off-line (static) real-time scheduling approaches. They have large numbers of potential contention points, have limited internal buffering capabilities, and network control operates at the scale of small data packets. Therefore, efficient resource allocation requires scalable algorithms working on hardware models with a level of detail that is unprecedented in real-time scheduling. We consider in this thesis a static scheduling approach, and we target massively parallel processor arrays (MPPAs), which are MPSoCs with large numbers (hundreds) of processing cores. We first identify and compare the hardware mechanisms supporting precise timing analysis and efficient resource allocation in existing MPPA platforms. We determine that the NoC should ideally provide the means of enforcing a global communications schedule that is computed off-line (before execution) and which is synchronized with the scheduling of computations on processors. On the software side, we propose a novel allocation and scheduling method capable of synthesizing such global computation and communication schedules covering all the execution, communication, and memory resources in an MPPA. To allow an efficient use of the hardware resources, our method takes into account the specificities of MPPA hardware and implements advanced scheduling techniques such as pre-computed preemption of data transmissions. We evaluate our technique by mapping two signal processing applications, for which we obtain good latency, throughput, and resource use figures.

**Keywords:** Chip-multiprocessor (Many-core), On-chip network (NoC), Off-line scheduling, Real-time scheduling

**English Title:** Reconciling performance and predictability on a NoC-based MPSoC using off-line scheduling technique.

## **Table of Contents**

| Re | emerc  | iements  |                                                             | 2  |

|----|--------|----------|-------------------------------------------------------------|----|

| Ré | ésumé  |          |                                                             | 3  |

| Ał | ostrac | t        |                                                             | 4  |

| 1  | Intr   | oduction | n                                                           | 8  |

|    | 1.1    | Thesis   | motivation                                                  | 8  |

|    |        | 1.1.1    | The advent of many-cores                                    | 8  |

|    |        | 1.1.2    | The advent of Networks-on-Chips                             | 12 |

|    |        | 1.1.3    | Many-cores for hard real-time applications                  | 13 |

|    |        | 1.1.4    | Mapping applications onto NoC-based many-cores              | 15 |

|    | 1.2    | Thesis   | contributions                                               | 16 |

|    |        | 1.2.1    | The DSPINpro programmable Network-on-Chip                   | 17 |

|    |        | 1.2.2    | The Automatic real-time mapping and code generation         | 17 |

|    |        | 1.2.3    | An environment for virtual prototyping of MPPA applications | 19 |

|    | 1.3    | Outline  | e                                                           | 21 |

| 2  | Stat   | e of the | art                                                         | 22 |

|    | 2.1    |          | rk-on-Chip design                                           | 23 |

|    |        | 2.1.1    | NoC building blocks                                         | 23 |

|    |        | 2.1.2    | NoC topology                                                | 24 |

|    |        | 2.1.3    | NoC switching                                               | 24 |

|    |        |          | 2.1.3.1 Routing                                             | 25 |

|    |        |          | 2.1.3.2 Switching method and buffering policy               | 26 |

|    |        |          | 2.1.3.3 Arbitration/Scheduling                              | 29 |

|    |        | 2.1.4    | Existing Network-on-Chip architectures                      | 33 |

|    |        |          | 2.1.4.1 DSPIN                                               | 33 |

|    |        |          | 2.1.4.2 Æthereal                                            | 33 |

|    |        |          | 2.1.4.3 Nostrum                                             | 35 |

|    |        |          | 2.1.4.4 Kalray MPPA NoC                                     | 36 |

|    |        |          | 2.1.4.5 The scalar interconnect of MIT RAW                  | 38 |

|    |        |          | 2.1.4.6 Other NoC architectures                             | 39 |

|    |        |          | 2.1.4.7 Comparison with our work                            | 40 |

|    | 2.2    | Massiv   | ely parallel processor arrays                               | 40 |

|    |        | 2.2.1    | Tilera TILE <i>Pro</i> 64                                   | 40 |

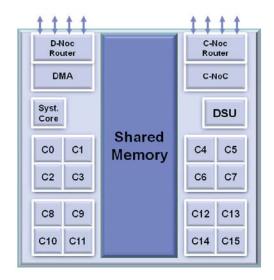

|    |        | 2.2.2    | Kalray MPPA-256                                             | 42 |

|   |      | 2.2.3   | Adapteva Epiphany                                                   | 43       |

|---|------|---------|---------------------------------------------------------------------|----------|

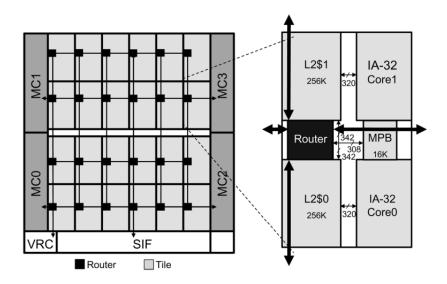

|   |      | 2.2.4   | Intel SCC                                                           | 45       |

|   |      | 2.2.5   | ST Microelectronics STHORM                                          | 46       |

|   |      | 2.2.6   | TSAR                                                                | 46       |

|   |      | 2.2.7   | Academic MPSoC architectures with TDM-based NoC arbitration         | 47       |

|   | 2.3  | Static  | application mapping                                                 | 47       |

|   |      | 2.3.1   | Off-line real-time multi-processor scheduling                       | 49       |

|   |      |         | 2.3.1.1 The AAA/SynDEx methodology                                  | 49       |

|   |      | 2.3.2   | The StreamIt compiler for the MIT RAW architecture                  | 52       |

|   |      | 2.3.3   | Compilation of the $\Sigma C$ language for the Kalray MPPA256 plat- |          |

|   |      |         | form                                                                | 54       |

|   |      | 2.3.4   | Other mapping approaches                                            | 55       |

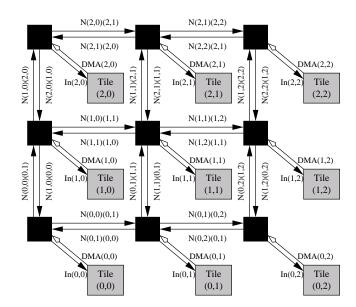

| 3 | Tile | d MPPA  | A architectures in SoCLib                                           | 57       |

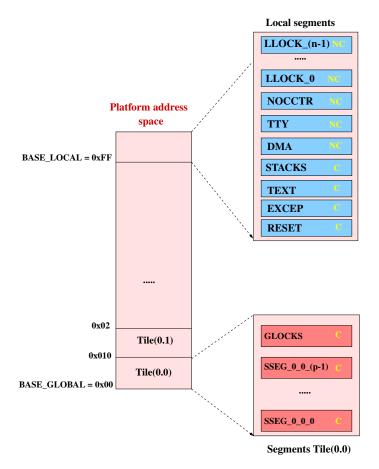

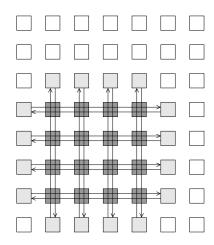

|   | 3.1  | MPPA    | structure                                                           | 57       |

|   | 3.2  | Memo    | ory organization                                                    | 59       |

|   |      | 3.2.1   |                                                                     | 59       |

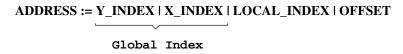

|   |      | 3.2.2   | Address structure                                                   | 60       |

|   |      | 3.2.3   | Global memory organization                                          | 61       |

|   |      | 3.2.4   |                                                                     | 62       |

|   |      | 3.2.5   | Hardware/software interface                                         | 63       |

|   | 3.3  | Improv  |                                                                     | 64       |

|   | 3.4  | Systen  | mC simulation and compilation support                               | 68       |

| 4 | Prog | gramma  | able NoC arbitration                                                | 70       |

|   | 4.1  | The ca  | ase for programmed arbitration                                      | 71       |

|   |      | 4.1.1   | The principle                                                       | 71       |

|   |      | 4.1.2   |                                                                     | 72       |

|   |      | 4.1.3   | The cost of programmability                                         | 73       |

|   | 4.2  | Progra  | mmable DSPIN                                                        | 74       |

|   |      | 4.2.1   | NoC router extensions                                               | 74       |

|   |      | 4.2.2   | Area overhead                                                       | 77       |

|   | 4.3  |         |                                                                     | 78       |

|   | 4.4  | Case s  | tudy: the FFT                                                       | 84       |

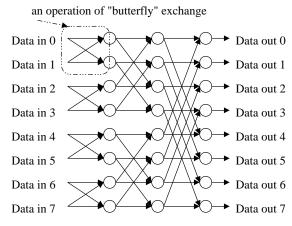

|   |      | 4.4.1   | FFT algorithm description                                           | 85       |

|   |      |         | 4.4.1.1 Mapping onto the MPPA architecture                          | 86       |

|   |      |         | 4.4.1.2 Traffic injection configuration                             | 87       |

|   |      | 4.4.2   | 3                                                                   | 88       |

|   |      | 4.4.3   | Removing the slow-down through NoC programming                      | 89       |

| 5 | Off  | line ma | pping of real-time applications using LoPhT                         | 94       |

|   | OII- |         |                                                                     |          |

|   | 5.1  |         |                                                                     | 95       |

|   |      |         | round: AAA using the Clocked Graphs formalism                       | 95<br>95 |

|   |      | Backg   | round: AAA using the Clocked Graphs formalism                       |          |

|   |      | Backg   | round: AAA using the Clocked Graphs formalism                       | 95       |

|   |      | Backg   | round: AAA using the Clocked Graphs formalism                       | 95<br>95 |

|           |          | S            | Support of a clock                           |

|-----------|----------|--------------|----------------------------------------------|

|           |          | V            | Vell-formed properties                       |

|           |          | 5.1.1.2      | Non-functional specification                 |

|           |          | P            | Platform model                               |

|           |          |              | Non-functional properties                    |

|           | 5.1.2    |              | scheduling of CG specifications              |

|           |          | 5.1.2.1      | Scheduled clocked graphs                     |

|           |          | 5.1.2.2      | Real-time scheduling problem                 |

|           |          | 5.1.2.3      | Consistency of a scheduled clocked graph 103 |

|           |          | N            | Notations                                    |

|           |          | C            | Consistency properties                       |

|           |          | 5.1.2.4      | Makespan-optimizing scheduling algorithm 106 |

| 5.2       | Static   | (off-line) r | mapping onto MPPA architectures 109          |

|           | 5.2.1    |              | NoC-based MPPA: The problem                  |

|           |          | L            | imitations                                   |

|           | 5.2.2    | Extensio     | n of the CG format                           |

|           |          | 5.2.2.1      | Modeling of MPPA resources                   |

|           |          | N            | NoC ressources:                              |

|           |          | T            | ile ressources:                              |

|           |          | 5.2.2.2      | Memory footprint specification               |

|           |          | 5.2.2.3      | Non-functional properties                    |

|           |          | V            | Vorst-case computation durations             |

|           |          | V            | Vorst-case communication durations           |

|           | 5.2.3    | Makespa      | un-optimizing scheduling                     |

|           |          | 5.2.3.1      | Mapping NoC communications                   |

|           |          | 5.2.3.2      | Multiple reservations                        |

| 5.3       | Autom    |              | generation                                   |

|           | 5.3.1    | Tile code    | e generation                                 |

| 5.4       | Experi   | mental res   | sults                                        |

| Conclus   | sion     |              | 127                                          |

| List of l | Publicat | tions        | 129                                          |

| Bibliog   | raphy    |              | 130                                          |

## Chapter 1

## Introduction

#### **Contents**

| 1.1 | Thesis | motivation                                                       |

|-----|--------|------------------------------------------------------------------|

|     | 1.1.1  | The advent of many-cores                                         |

|     | 1.1.2  | The advent of Networks-on-Chips                                  |

|     | 1.1.3  | Many-cores for hard real-time applications                       |

|     | 1.1.4  | Mapping applications onto NoC-based many-cores 15                |

| 1.2 | Thesis | contributions                                                    |

|     | 1.2.1  | The DSPINpro programmable Network-on-Chip 17                     |

|     | 1.2.2  | The Automatic real-time mapping and code generation 17           |

|     | 1.2.3  | An environment for virtual prototyping of MPPA applications . 19 |

| 1.3 | Outlin | ne                                                               |

#### 1.1 Thesis motivation

#### 1.1.1 The advent of many-cores

Due to advances in circuit technology and performance limitation in wide-issue, superspeculative processors, Chip-Multiprocessor (CMP) or multi-core technology has become the mainstream in CPU designs. [Peng et al., 2007]

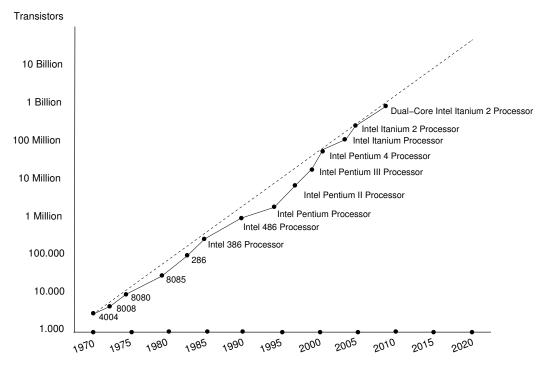

The number of transistors in micro-processor chips upholds today its historic trend of exponential growth, known as Moore's law, which is expected to continue until at least 2020 [Gordon E. Moore, 1965, Gordon E. Moore, 2005], as pictured in Fig. 1.1.

Until the years 2000, this growth mostly translated into micro-architecture gains aimed at improving mono-processor performance. Combined with a steady increase in operating frequencies, this allowed the continued use of a von Neumann computing paradigm [John von Neumann, 1945] where a sequential processor offers the performance needed by most general-purpose applications.

Figure 1.1: Moore's law (cf. [Held et al., 2006])

However, this is no longer possible. First of all, the last decade brought the end of the fast operating frequency increases which were the dominant cause of processor performance gains [J.Flynn, 2004]. Second, performance increase by micro-architectural advances alone follows the (empirical) Pollack's rule [Pollack, 1999] which states that the performance increase is roughly proportional to the square root of the increase in complexity (complexity in this context means processor logic, *i.e.* transistor count). In other words, doubling the logic in a processor core delivers only 40% more performance, while doubling the number of processors can almost double the speed for many applications.

The end of fast performance scaling for sequential processors led to an industry-wide shift towards parallel computing. While parallel architectures already existed, mainly in the high-performance and embedded computing fields, parallelism now entered the mainstream of general-purpose computing under the form of multi-core, and then many-core architectures. This trend started in 2001, when the first general-purpose processor that featured multiple processing cores on the same die was released by IBM: the POWER4 processor [IBM, 2001]. Since then, all major hardware vendors started shipping multi-core processors. Today, most personal computers, workstations and servers are based on multi-core chips.

Multi-core processors have clear benefits, such as scalable performance, improved reliability, or an easier energy and thermal management. But these benefits come at the price of as many challenges (we only list here a few):

• Scalable performance: Our computing environments offer more and more potential for parallelism, coming from either the nature of the applications (e.g. video

streaming) or the fact that multiple applications are run in parallel. But exploiting this parallelism requires significant changes in the way systems are built, in both software and hardware.

In software, the main difficulty is that of producing correct and efficient parallel programs. These programs must expose parallelism at the good level, and also provide guarantees of correctness in the presence of concurrency. To facilitate multicore programming, a variety of languages and formalisms have been proposed in the past years, and significant effort has been invested in the software engineering of such applications [OpenMP, 2008, Khronos, 2011] and in the automatic parallelization of previously-existing sequential code [Beletska et al., 2011, Cetus, 2004, Irigoin et al., 2012].

In hardware, as the computing cores are counted in dozens and hundreds, the classical shared-bus communication approaches no longer scale. This leads to major bottlenecks in the memory hierarchy, in the inter-core communication network, and in the access to external data sources. Solving these issues requires a significant improvement of the on-chip and the off-chip interconnects.

But the most challenging issues are the complex design decisions concerning both hardware and software. Indeed, designing a complex hardware/software system consists in solving a multi-criteria optimization problem having as parameters efficiency, facility of programming, predictability, hardware complexity, price, etc. Solving such an optimization problem involves complex trade-offs. For instance, choosing a multi-core architecture with support for cache coherency facilitates shared memory programming, but leads to a poor temporal predictability and an increased hardware complexity. On the contrary, having no hardware support for cache coherency improves predictability but requires software control of memory consistency. Clearly, these architectural choices have a profond influence on both the specification and mapping of parallel applications onto multi-core platforms.

- Energy efficiency and thermal management: As the number of transistors and the computation power increase, power and temperature management becomes more and more critical and difficult, and needs to be addressed in either hardware or a combination of both hardware and software [Hanumaiah and Vrudhula, 2012].

- Multi-core architectures usually provide at least one of two classical hardware mechanisms that facilitate power and temperature management: The possibility of turning off unused processor cores and the possibility of running cores at optimized supply voltages and frequencies. Furthermore, load balancing among the processor cores can be used to distribute thermal dissipation across the die.

- Fault-tolerance and reliability: The evolution of silicon technologies results in a steady increase of transistor densities. At the same time, the increase in transistor counts means that chip sizes do not decrease. The combination of the two results in a significant increase of the probability of hardware defects per chip [Furber, 2006].

Coupled with the need for reasonable yields, the increase in transistor count will bring an end to current design practices where only chips that are 100% functional are accepted. However, tolerating defects in chips requires support in both hardware and software, through redundancy and support for failure isolation and (re-)configuration [Zhang, 2011].

Intense research and industrial developments have resulted in the definition of several classes of multi-core processors corresponding to different contexts of use and programming styles. Among them:

- General-purpose multi-cores, such as AMD Phenom or Intel Core.

- Application-specific System-on-Chip (SoC) platforms, such as TI OMAP or Qual-comm SnapDragon [Texas Instruments, 2009, Qualcomm, 2011], which have emerged from the embedded computing community.

- Graphics Processing Units (GPUs) [Nvidia, 1999], which have emerged from the image processing and high-performance computing community, and which are optimized for Single Instruction Multiple Data (SIMD) execution.

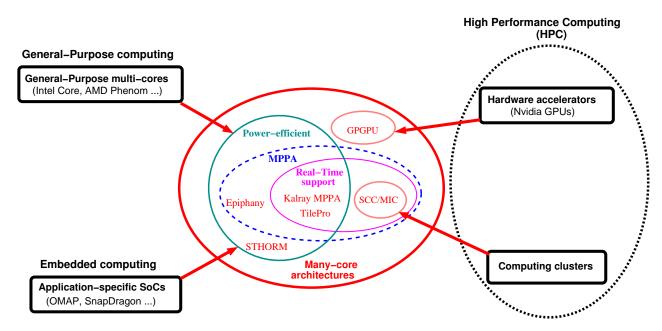

But in the past few years, a clear and consistent convergence can be seen between the historically isolated communities of general-purpose, embedded, and high-performance computing. All three communities have moved towards so-called *many-core* platforms characterized by:

- Large numbers of simpler cores. The number of cores ranges here from a few tens to a few hundreds in production architectures, and to thousands of cores in research platforms.

- *Novel memory architectures* that can deliver higher bandwidth access through the use of multiple memory banks localized near the processors. Data localization often requires that the memory hierarchy is exposed, at least in part, to the programmer.

- *New interconnect types*, like the Network-on-Chips (NoCs), that provide higher performance and/or scalability than classical interconnects such as buses and crossbars.

As graphically illustrated in Fig. 1.2, this hardware-level convergence between the general-purpose, embedded, and high-performance computing communities has several causes:

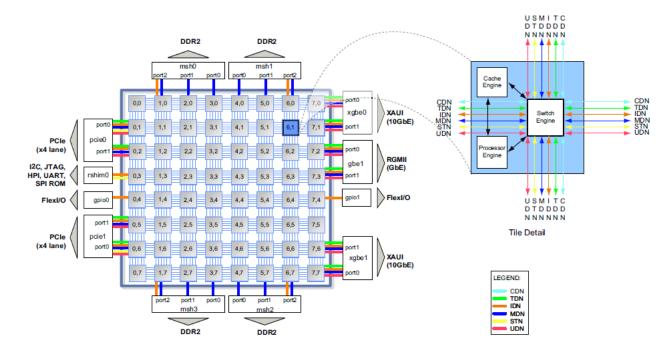

• In the general-purpose computing community, the use of the *massively parallel* processor array (MPPA) chips <sup>1</sup> such as Kalray MPPA [MPPA, 2012], Adapteva Epiphany [Adapteva, 2012], Tilera TilePro [Tilera, 2008], or Intel SCC and MIC [Howard and al., 2011, MIC, 2010] improves scalability and/or energy efficiency.

<sup>&</sup>lt;sup>1</sup>We will come back with an in-depth description of MPPA architectures in the following chapters.

Figure 1.2: The many-core convergence

- Embedded applications also benefit from improved scalability and energy efficiency, like in the ST STHORM [Benini, 2010] platform. In addition, they often require some support for real-time implementation, such as mechanisms for resource reservation or spatial and temporal separation, as offered by the Kalray MPPA and Tilera TilePro chips.

- In the high-performance computing community, hardware accelerators like the GPUs evolved towards General-Purpose GPUs (GPGPUs) architectures whose more expressive instruction sets provide more flexibility to the programmer. Energy-efficient architectures such as Adapteva Epiphany also position themselves as accelerator chips. Finally, many-core chips, such as Intel SCC and MIC [Howard and al., 2011, MIC, 2010], are the result of yet anothor tradition. Here energy efficiency is not an objective *per se*, but appears as a by-product of the need to parallelize high-performance applications through methods previously used on computing clusters.

#### 1.1.2 The advent of Networks-on-Chips

The first multi-core architectures used bus-based interconnects such as ARM's AMBA [ARM, 1999] and IBM's CoreConnect [PLB, 2001]. However, an on-chip bus can only perform one communication at a time. As the number of cores increased, the buses became major contention points and performance bottlenecks, and new interconnect paradigms were investigated.

From a computation speed point of view, the ideal choice is that of crossbar interconnects where every two components are directly linked. A crossbar introduces no contention point in addition to the ones associated with the resources connected to it (RAM banks and other peripherals). But the hardware cost of a crossbar increases quadratically with the number of resources connected to it. Thus, crossbars can only be used in systems or sub-systems with a small number of components.

Finding a trade-off between performance (*e.g.* speed), scalability, and system cost led to the development of the Network-on-Chip (NoC) paradigm, which takes inspiration from classical computer networks [Benini and De Micheli, 2002, Sgroi et al., 2001]. Like a classical computer network, a NoC is formed of standardized point-to-point links and NoC routers that can be composed following simple rules to form complex interconnect graphs (regular or not). The use of multiple links avoids the creation of global bottlenecks. At the same time, the number of links is kept at a reasonable level (usually linear in the number of computation and storage components) guaranteeing scalability in large designs.

#### 1.1.3 Many-cores for hard real-time applications

The objective of this thesis is to investigate the use of many-core architectures using a NoC interconnect in the implementation of complex real-time applications. We are targeting two types of applications:

- Hard real-time applications, like those used in embedded control systems in the

avionics and automotive industries. In such applications, the non-respect of deadlines may lead to catastrophic results like the loss of life or serious damage to the

environment.

- Highly regular signal/image processing applications. In such applications, a tight control of timing, like the one we propose, helps in improving computation speed.

In such applications, timing guarantees should be obtained before execution, ideally by static analysis methods (as opposed to measurement-based ones). Furthermore, the timing guarantees should be *precise* in order to avoid the waste of computing resources. But determining precise timing guarantees is inherently difficult on many-core platforms due to the large number of potential contention points. It is imperative to identify (and then eliminate or control) the sources of timing impredictability at all levels of the many-core architecture<sup>2</sup> and the application software.

From existing work on WCET analysis for classical single-core and multi-core architectures, we know that certain microarchitectural features make timing analysis more difficult [Wilhelm and Reineke, 2012, Hardy and Puaut, 2008]. Such features are the shared caches and the cache/memory coherency mechanisms. We shall assume that neither of them is used in the many-core platforms considered in this thesis. One particular consequence of this assumption is that *all* communications and synchronizations between different processor cores are performed through one or more NoCs.<sup>3</sup>

<sup>&</sup>lt;sup>2</sup>Comprising the processor cores, the memory sub-system, the communication network, and the I/O devices.

<sup>&</sup>lt;sup>3</sup>As opposed to using dedicated communication devices such as the complex memory hierarchies of TSAR [TSAR, 2008].

But eliminating microarchitectural sources of impredictability is not enough, as the NoCs themselves raise serious problems when the objective is to ensure efficiency and predictibility. Indeed, a NoC has large numbers of potential contention points: Whenever a NoC router is connected to at least 3 links, contentions are possible when data arriving on 2 links must be sent onto the third. In common NoC architectures, this is the case of all routers, and arbitration is needed to control the access to every NoC link.

Furthermore, one communication often traverses several NoC routers, and can be subject to contentions at the level of each one. This is why the use of fair arbitration policies at the level of NoC routers is not good when the objective is to provide tight timing guarantees for NoC communications. Previous work on NoC-based architectures for the real-time subject have explored the use of arbitration policies similar to those used for ensuring Quality-of-Service (QoS) in computer networks. Several approaches have been proposed: circuit switching, bandwidth reservation, priority-based scheduling, and programmed arbitration.

In NoCs based on *circuit switching* [Hilton and Nelson, 2006], communications are performed along a set of *circuits*. Each circuit is a sequence of point-to-point NoC links. The fundamental constraint is that two circuits cannot share a link. The absence of resource sharing lowers utilization of NoC resources and increases costs. However, once a connection has been established, it can use the full bandwidth of all its links and real-time guarantees are easily computed.

Virtual circuit switching is an evolution of circuit switching which allows resource sharing between circuits. Resource sharing requires the use of arbitration, and several types of arbitration techniques have been proposed: TDM-based, bandwidth management-based, and priority-based.

Most interesting from the point of view of timing predictability are NoCs where arbitration is based on *time division multiplexing (TDM)*. TDM-based NoCs [Goossens et al., 2005, Millberg et al., 2004b] allow the computation of precise latency and throughput guarantees. The same type of latency and throughput guarantees (albeit less precise) can be obtained in NoCs relying on bandwidth management mechanisms, such as Kalray MPPA [Harrand and Durand, 2011].

But NoCs using TDM arbitration or bandwidth management have certain limitations. The most important is that they largely ignore the fact that the needs of an application may change during execution, depending on the *state* of the application. One way of taking into account the application state is by using NoCs with support for *priority-based arbitration*. But priority-based arbitration requires the use of costly virtual channel mechanisms [Howard and al., 2011, Miro Panades et al., 2006], which limits applicability to systems supporting only a few priority levels. The alternative to priority-based approaches is to use a NoC allowing *programmed NoC arbitration*, such as MIT RAW [Waingold et al., 1997] or the architecture proposed in this thesis. Programmed arbitration allows the enforcement of static arbitration and routing patterns of data transmissions, as demanded by the application.

#### 1.1.4 Mapping applications onto NoC-based many-cores

The introduction of NoC-based architectures was accompanied by the definition of novel mapping techniques targeting NoC-based MPSoCs. Indeed, if paralelism is recognized as the only way of providing scalable performance, this scalability comes at the price of increased complexity of both the software and the software mapping (allocation and scheduling) process.

Part of this complexity can be attributed to the steady increase in the *quantity* of software that is run by a single system. But there are also significant *qualitative* changes concerning both the software and the hardware. In software, more and more applications include *parallel* versions of classical signal or image processing algorithms [Aubry et al., 2013, Gerdes et al., 2012, Villalpando et al., 2010], involving potentially complex synchronizations between the sequential programs executed on the various cores. Such applications are best modeled using data-flow models (as opposed to so-called *independent tasks* that are common in classical real-time).

Designing parallel software is difficult in itself, relying on notoriously hard disciplines such as parallel programming [Kwok and Ahmad, 1999] and multi-processor scheduling [Ramamritham et al., 1993]. The picture is further complicated when considering real-time aspects. Providing functional and real-time correctness guarantees requires an accurate control of the functional and temporal interferences due to concurrent use of shared resources. Depending on the hardware and software architecture, this can be very difficult [Wilhelm and Reineke, 2012]. In our case, there are two main reasons to this: The first one concerns the NoCs: as the tasks are more tightly coupled and the number of resources in the system increases, the on-chip networks become critical resources, which need to be explicitly considered and managed during real-time scheduling. Recent work [Shi and Burns, 2010, Kashif et al., 2013, Nikolic et al., 2013] has determined that NoCs have distinctive traits requiring significant changes to classical multi-processor scheduling theory [Goossens et al., 2003]. The second reason concerns automation: the complexity of many-cores and of the (parallel) applications mapped on them is such that the *allocation and scheduling must be largely automated*.

Efficient and real-time implementation of applications onto NoC-based systems remains largely an open problem, with the issue of best mapping of computation parts (threads, tasks,...) onto processing resources amply recognized, while the issue of best use of the interconnect NoC to route and transfer data still less commonly tackled.

In the most general case, dynamic allocation of applications and channel virtualization can be guided by user-provided information under various forms as in OpenMP for Open Multi-Processing [OpenMP, 2008], CUDA for Compute Unified Device Architecture [Nvidia CUDA, 2006], and OpenCL for Open Computing Language [Khronos, 2011]. But there is no clear guarantee of optimality. Conversely there are consistent efforts, in the domains of embedded and HPC computing, aiming at automatic parallelization, compiletime mapping and scheduling optimization. They rely on the fact that applications are often known in advance, and deployed without disturbance from foreign applications, and

without uncontrolled dynamic creation of tasks.

The results of this thesis fit in this "static application mapping" case. We focus on mapping techniques where *all* allocation and scheduling decisions are taken off-line. In theory, off-line algorithms allow the computation of *scheduling tables* specifying an *optimal* allocation and real-time scheduling of the various computations and communications onto the resources of the MPPA. In practice, this ability is severely limited by 3 factors:

- 1. The **application** may exhibit a high degree of dynamicity due to either environment constraints or to execution time variability resulting from data-dependent conditional control.<sup>4</sup>

- 2. The **hardware** may not allow the implementation of optimal scheduling tables. For instance, most MPPA architectures provide only limited control over the scheduling of communications inside the NoC.

- 3. The **mapping** problems we consider here are NP-hard. In practice, this means that optimality cannot be attained, and that efficient heuristics are needed.

#### 1.2 Thesis contributions

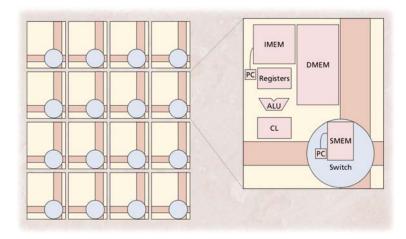

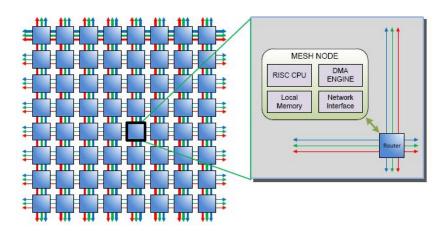

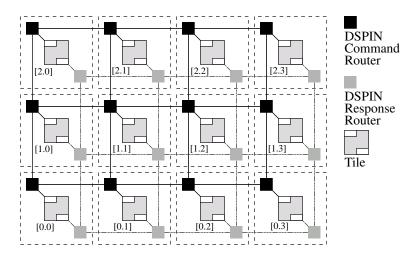

In our work, we are interested in a specific sub-class of many-core architectures: the *massively parallel processor arrays (MPPAs)* characterized by:

- A large number of processing cores, ranging in current silicon implementations from a few tens to a few hundreds. The cores are typically chosen for their area and energy efficiency, instead of raw computing power.

- A regular internal structure where processor cores and internal storage (RAM banks) are divided among a set of identical *tiles*, which are connected through one or more NoCs with regular structure (*e.g.* mesh or torus topologies). In this thesis, we are focusing on 2D-Mesh micro topologies.

- The capability of executing in parallel a different task on each core. Known as *task* parallelism or multiple-instruction, multiple-data (MIMD), this parallel computing paradigm is also that of classical distributed computing and multi-processor real-time scheduling.

My contributions in this thesis concern the **hardware** and the **mapping** technique. On the hardware design side, I extend an existing state-of-the-art NoC architecture to allow programmed arbitration and thus provide the best support for off-line scheduling. On the mapping side, I explain how low-level details of NoC-based MPPA architectures can be taken into account in a scalable way to allow the synthesis of schedules with

<sup>&</sup>lt;sup>4</sup>Implementing an optimal control scheme for such an application may require more resources than the application itself, which is why on-line scheduling techniques are often preferred.

unprecedented timing precision. To evaluate our novel NoC architecture and mapping technique we build a cycle-accurate model of a NoC-based MPPA and a new tool for the automatic real-time mapping and code generation, called LoPhT.

#### 1.2.1 The DSPINpro programmable Network-on-Chip

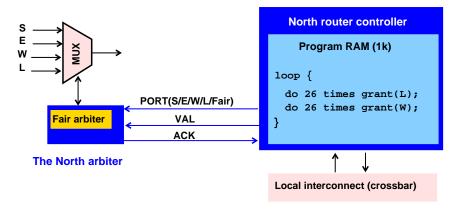

Our purpose is to investigate how the underlying architecture should offer the proper infrastructures to implement optimal computation <u>and</u> communication mappings and schedules. We concretely support our proposed approach by extending the DSPIN 2D mesh network-on-chip (NoC) [Panades, 2008] developed at UPMC-LIP6. In the DSPIN NoC, we replace the fair arbitration modules of the NoC routers with static, micro-programmable arbiters that can enforce a given packet routing sequence, as specified by small programs. We advocate the desired level of expressiveness/complexity for such simple configuration programs. The result is named Programmable DSPIN, or *DSPINpro*.

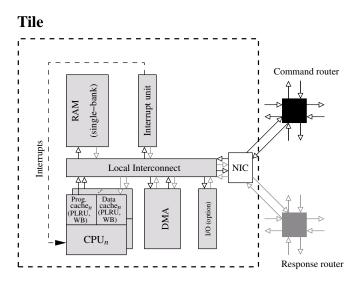

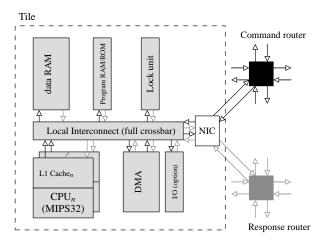

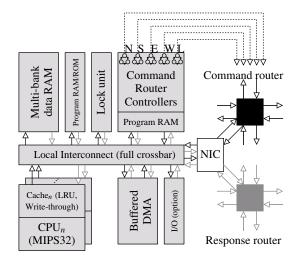

To improve the efficiency and predictability of our MPPA architecture, and thus facilitate real-time mapping, we also constrained and standardized the structure of the computing tiles connected to the *DSPINpro* NoC, as well as the software architecture of our implementations. On the hardware side, we constrain the type and number of tile components (CPUs, RAM banks, DMA units ...).<sup>5</sup> On the software architecture side, we constrain the memory organization, we impose that all computations are performed on local tile data, with specific "send" operations being in charge of all inter-tile data transfers (along with a software lock mecanism), and we require the explicit placement of input and output data of the tile on memory banks.

#### 1.2.2 The Automatic real-time mapping and code generation

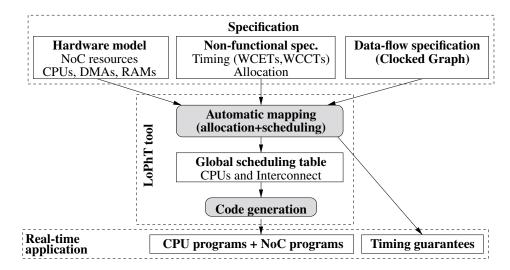

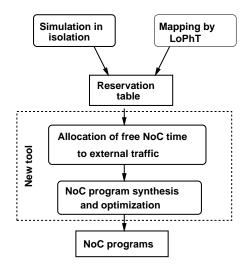

We propose a technique and tool for the automated mapping of real-time applications onto MPPA architectures based on 2D mesh NoCs. Our tool is named LoPhT, for **Lo**gical to **Physical Time** Compiler.

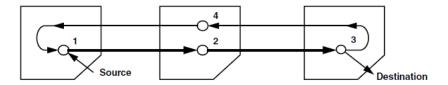

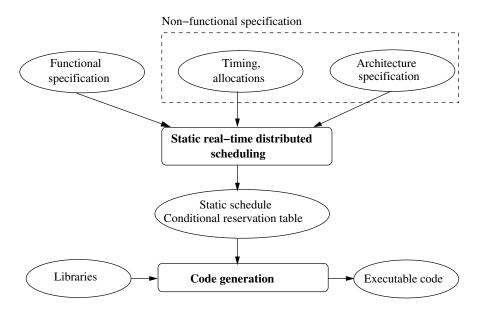

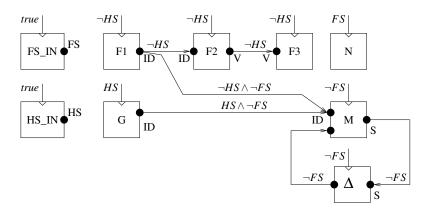

The global flow of our mapping technique, pictured in Fig. 1.3, is similar to that of the AAA methodology and the SynDEx tool [Grandpierre and Sorel, 2003]. It takes as input functional specifications provided under the form of data-flow synchronous specifications à la Scade/Lustre [Caspi et al., 2003]. Our input formalism allows the specification of conditional execution and execution modes, which are common features in complex embedded control specifications.

To map such specifications onto MPPA architectures and provide hard real-time guarantees, we rely on *off-line* allocation and scheduling algorithms. These algorithms also take as input a description of the MPPA platform, and non-functional constraints including allocation constraints and conservative upper estimates for the:

<sup>&</sup>lt;sup>5</sup>We have also developed a tool allowing the automatic synthesis of the corresponding SystemC models and memory maps from simple architecture specifications defining the NoC size and the type and number of tile components.

Figure 1.3: Global flow of the proposed mapping technique

- Worst-case execution times (WCETs) of the data-flow blocks (seen as atomic computations).

- The worst-case size of data transmitted through the data-flow arcs, needed to determine the worst-case communication time (WCCT) of basic communication/synchronization operations.

Starting from these inputs, our algorithms build *reservation tables* (also called *scheduling tables* or simply *time tables*) specifying for each resource of the platform its use by various computations or communications. Reservation tables are then converted into sequential code ensuring the correct ordering of operations on each resource and the respect of the real-time guarantees.

Our main contribution was to provide new mapping algorithms that explicitly take into account MPPA-specific features. The first problem here is that NoCs are very different from the communication buses used in classical real-time scheduling work. NoCs are composed of *multiple communication resources* that must be considered separately during mapping. However, reservation of a communication path along the NoC requires the *synchronized reservation* of resources along the path, due to the limited amount of buffer memory inside the NoC. The second problem is that the large number of computation and communication resources requires the use of scalable, yet precise mapping algorithms.

To provide tight real-time guarantees, our mapping heuristics seek to achieve a good parallelization of the application while *ensuring that concurrent computations and communications do not interfere* (functionally or temporally) with each other outside of functionally-needed synchronization points. The absence of interferences reduces the pessimism of the worst-case timing analysis, and limits resource over-allocation. Achieving such functional and temporal isolation can be done with low overhead in MPPA architectures that provide the programmer with good control over the memory hierarchy and the interconnect.

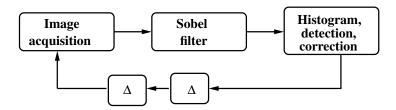

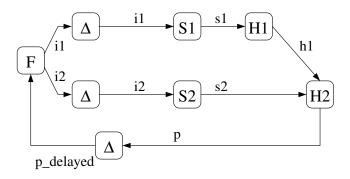

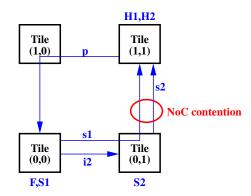

We evaluated our hardware extensions and mapping technique by automatically implementing two signal processing applications: A model of an automotive embedded control application and an implementation of the Fast Fourier Transform (FFT). These two examples provide a good illustration of how abstract data-flow communications between compute operations have to be organized according to crossroad traffics at routers, once computations have been mapped to processing elements. For both applications, NoC arbitration programming reduces contentions, communication time, and therefore global execution time. We obtain in both cases good latency, throughput, and resource use figures.

#### 1.2.3 An environment for virtual prototyping of MPPA applications

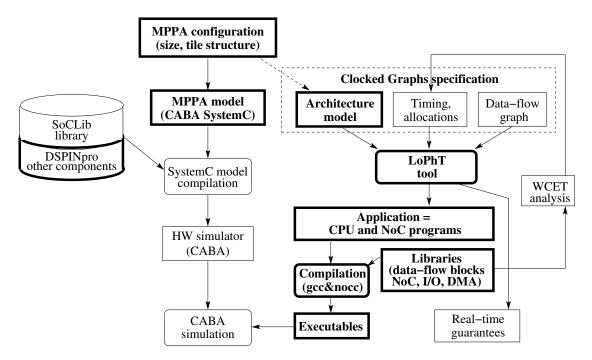

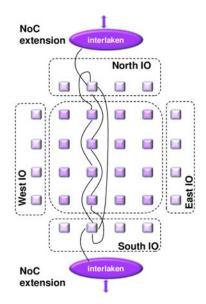

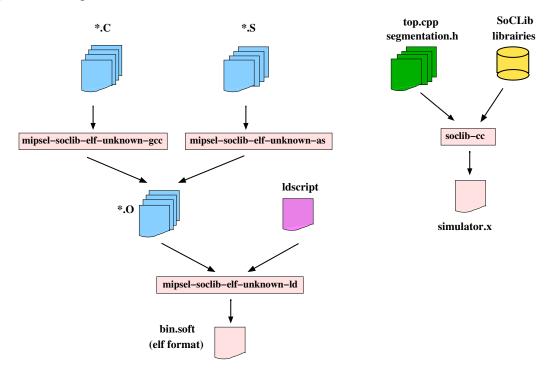

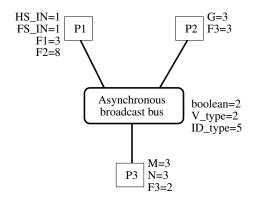

Together, our extension of the DSPIN NoC and the development of a novel mapping technique and tool define a new environment for the virtual prototyping of real-time MPPA applications. The expression "virtual prototyping" is used here to mark the fact that hardware execution is simulated in software, as opposed to "emulated" on an FPGA target after full hardware synthesis. The SoCLib library [LIP6, 2011] allows both. We preferred the simulation-based approach because it facilitated both hardware design and the precise timing measures needed to evaluate our real-time mapping technique on the resulting platform. Note that no difference exists between simulation and emulation from the point of view of software or the real-time properties, given that simulation is of *cycle-accurate*, *bit-accurate* (*CABA*) type.

Figure 1.4: An environment for virtual prototyping of MPPA applications

In our environment, described in Fig. 1.4, objects with thick borders are artefacts or

transformations that were created or significantly modified as part of this thesis. In our environment, we start by choosing the high-level configuration parameters of the MPPA platform, which include the size (number of tiles) of the MPPA, the structure of the standard tile, and the positioning of I/O devices. Once configuration is fixed, we can instantiate the MPPA SystemC model. This model uses standard components from the SoCLib library, but also the DSPINpro network-on-chip and other hardware components developed on top of SoCLib as part of our effort to build an MPPA platform reconciling timing predictability and efficiency. The model is then compiled to obtain the hardware simulator.

The configuration parameters are also used to build the architecture model taken as input by our mapping tool LoPhT. LoPhT also takes as input a functional specification provided under the form of a data-flow synchronous specification and a non-functional specification defining the worst-case durations of all data-flow blocks and communications, and possible allocation constraints. Worst-case durations are obtained through WCET analysis of the C code associated with the data-flow blocks and other library functions (but this aspect will not be covered in this thesis, the interested reader is invited to read [Puaut and Potop-Butucaru, 2013]). The LoPhT tool takes this input specification and transforms it into statically scheduled code for the CPU cores and the NoC routers. This code is compiled, separately for each sequential resources, using either gcc (the C code of the CPUs) or with nocc (designed and implemented by us) for the NoC programs. Resulting code is executed on the hardware simulator, which allows us to verify that the real-time guarantees computed by LoPhT are respected.

Of course, this environment is the result of highly collaborative work started between my team (INRIA AOSTE) and the SoC team of the UPMC/Lip6 laboratory (led at the time by A.Munier). From the SoC team, the main participants were François Pêcheux, Franck Wajsburt and Zhen Zhang, which have carried out most of the hardware design. From the AOSTE team, in addition to myself, Thomas Carle helped in the implementation of the scheduler, and Robert de Simone provided major insights on the high-level architectural modeling. My personal contributions are the following:

- I participated in the definition of the DSPINpro NoC and the MPPA platform by specifying what services the hardware should provide in order to allow efficient and predictable real-time implementation. Actual definition of the hardware was carried out by the Lip6 team and D. Potop.

- I defined the architecture model taken as input by LoPhT.

- Starting from off-line mapping algorithms originally defined by T. Carle and D. Potop, I have extended them to cover the NoC-specific and MPPA-specific aspects, such as the synchronized reservation of NoC resources.

- I have defined the code generation scheme which ensures that the real-time guarantees computed by LoPhT are respected in the running implementations. This

1.3. OUTLINE 21

scheme takes into account the low-level detail of the MPPA platform to allow for low-overhead synchronization and for high precision in resource allocation.

#### 1.3 Outline

My thesis is organized as follows:

Chapter 2 summarizes the state of the art in NoC design and in the mapping and scheduling for multi-core and many-core platforms.

Chapter 3 presents the detail of the DSPIN NoC and the SoCLib-based MPPA architecture on which our work is based. It also presents the changes brought to the tiles of the SoCLib-based MPPA to allow predictable and efficient implementation.

Chapter 4 presents the concept of programmed arbitration and its implementation in the DSPINpro NoC. It also presents an evaluation of the gains obtained through semiautomatic mapping of two applications onto the new platform.

Chapter 5 presents the LoPhT tool for automatic real-time mapping of embedded control specifications onto MPPAs.

## Chapter 2

## State of the art

2.3.4

| <b>Contents</b> |        |                                                                     |           |

|-----------------|--------|---------------------------------------------------------------------|-----------|

| 2.1             | Netwo  | ork-on-Chip design                                                  | 23        |

|                 | 2.1.1  | NoC building blocks                                                 | 23        |

|                 | 2.1.2  | NoC topology                                                        | 24        |

|                 | 2.1.3  | NoC switching                                                       | 24        |

|                 | 2.1.4  | Existing Network-on-Chip architectures                              | 33        |

| 2.2             | Massi  | vely parallel processor arrays                                      | 40        |

|                 | 2.2.1  | Tilera TILE <i>Pro</i> 64                                           | 40        |

|                 | 2.2.2  | Kalray MPPA-256                                                     | 42        |

|                 | 2.2.3  | Adapteva Epiphany                                                   | 43        |

|                 | 2.2.4  | Intel SCC                                                           | 45        |

|                 | 2.2.5  | ST Microelectronics STHORM                                          | 46        |

|                 | 2.2.6  | TSAR                                                                | 46        |

|                 | 2.2.7  | Academic MPSoC architectures with TDM-based NoC arbitra-            |           |

|                 |        | tion                                                                | 47        |

| 2.3             | Static | application mapping                                                 | <b>47</b> |

|                 | 2.3.1  | Off-line real-time multi-processor scheduling                       | 49        |

|                 | 2.3.2  | The StreamIt compiler for the MIT RAW architecture                  | 52        |

|                 | 2.3.3  | Compilation of the $\Sigma C$ language for the Kalray MPPA256 plat- |           |

|                 |        | form                                                                | 54        |

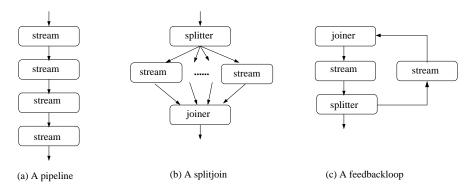

Our work extends the state of the art in three fields: Network-on-Chip (NoC) design, Massively Parallel Processor Array (MPPA) design, and mapping techniques for multi/many-cores. We start this section with a general introduction of NoC-related concepts, and then we identify and compare the hardware mechanisms supporting precise timing analysis and efficient resource allocation in existing NoC architectures. Most important, Section 2.1.3 reviews existing NoC switching paradigms and their support for

real-time application mapping. Section 2.2 presents some examples of existing industrial and academic MPPA platforms. Finally, we review related work on application mapping for multi-core, distributed, and many-core architectures.

#### 2.1 Network-on-Chip design

The Network-on-Chip (NoC) paradigm has been defined by its authors as a "layered-stack" approach to the design of on-chip interconnect [Sgroi et al., 2001], inspired by the classical layered models for computer networks [Zimmermann, 1988]. In this paradigm, the communication functions of the NoC are organized in a set of logical layers, each layer using the services of the lower layers in order to provide higher-level services.

At the highest abstraction level, a NoC can be viewed as a classical telecommunication network offering lossless communication services with some QoS properties between a set of computation and storage elements (CPU cores, RAM banks, I/O devices, etc). These services rely on lower-level routing and switching algorithms controlling the behavior of the NoC building blocks: links, routers, and interfaces. We briefly describe these elements here. Our description insists on the traffic management mechanisms supporting real-time implementation.

#### 2.1.1 NoC building blocks

A Network-on-Chip (NoC) is formed of components of three types: links, routers, and Network Interface Controllers (NICs).

- Links: The communication links are the central data transmission media. They interconnect all the routers and the NICs. Links are unidirectional, point-to-point media. Bidirectional point-to-point communication lines can be obtained by pairing two links, one for each communication direction. One fundamental characteristic of links is their buffering capability, which will be discussed later.

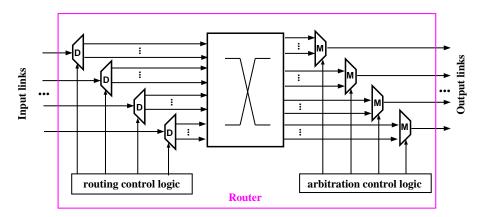

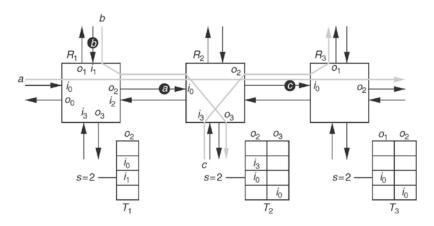

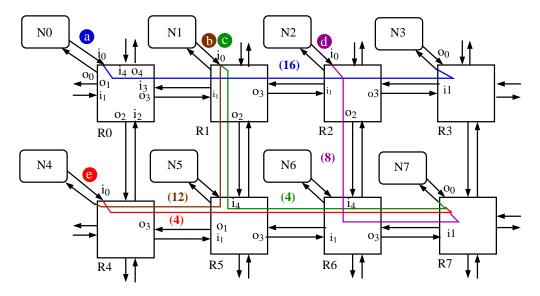

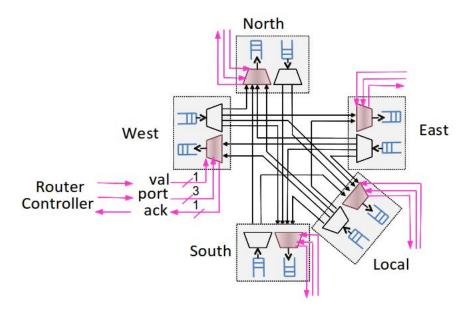

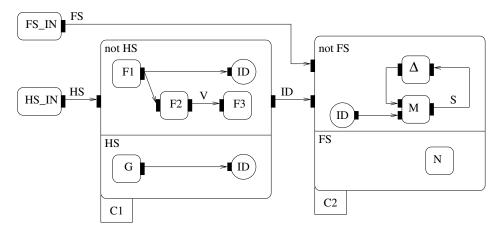

- Routers: They implement the flow control policies (routing, arbitration) and define the overall strategy for moving data through the NoC. As shown in Fig. 2.1, each NoC router is composed of *buffers*, which provide temporary storage for incoming and outgoing data, *routing components*, which are essentially *demultiplexers* (labeled **D**) with some control logic, and *scheduling/arbitration components*, which are essentially multiplexers (labeled **M**) with some control logic.

- Network Interface Controllers (NICs): Like in a classical computer network, storage and computing components of a many-core are often grouped in a number of sub-systems, called Processing Elements (PEs). The NICs provide the logic

Figure 2.1: Generic router model

connection between the PEs and the NoC. Its main task is protocol conversion between the one used locally within the PE and the one of the NoC. In particular, NICs are responsible for building the data packets transferred through the NoC.

#### 2.1.2 NoC topology

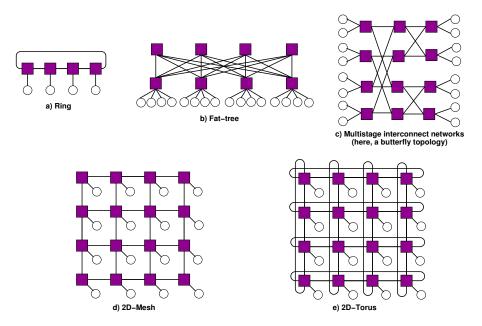

The topology of a NoC is usually modeled by an adjacency graph describing how the routers, NICs, and PEs are interconnected using NoC links. NoC topologies can be either regular or irregular. The most common regular topologies are presented in Fig. 2.2. In this figure, the routers are represented with squares and the PEs with circles. Each PE contains exactly one NIC. The arcs represent either unidirectional links, or bidirectional pairs of links.

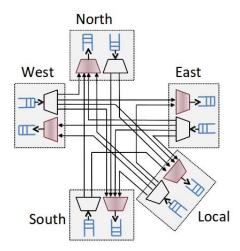

Various comparisons between various regular topologies (in terms of latency, throughput, and energy dissipation) can be found in [Pande et al., 2005]. In this thesis we focus on 2D-Mesh NoCs like the ones used in the Adapteva Epiphany [Adapteva, 2012], Tilera Tilepro [Tilera, 2008], or DSPIN [Panades, 2008]. The structure of a router in a 2D mesh NoC (which is a specialization of the general router structure of Fig. 2.1) is presented in Fig. 2.3. It has five bidirectional connections (labeled North, South, East, West, and Local) to the bidirectional links leading to the four routers next to it and the local PEs. Note that mesh and torus NoCs are often used in so-called *tiled many-core* architectures, where most PEs have a standard form (approximated with a rectangle) resulting in a regular, tiled organization of the many-core chip. This is why in tiled many-cores the PEs are usually called *computing tiles* or simply *tiles*.

#### 2.1.3 NoC switching

The allocation of NoC resources to the various data transmissions is governed by a set of design choices and algorithms commonly known as the *switching policy* of the NoC. This

Figure 2.2: Some regular NoC topologies

very general notion covers all aspects of NoC data transmission: the organization of data into transmission units, routing, buffering, and arbitration/scheduling. We briefly discuss these aspects.

#### **2.1.3.1** Routing

The routing algorithm, implemented by the NoC router demultiplexers, defines how data is routed from its source towards its destination. It must decide at each intermediate router which output link(s) are to be selected for each incoming data packet. Routing algorithms can be classified according to various criteria. According to the number of destinations of individual data transmission operations, routing algorithms can be *unicast*, when each data transmission operation has a single destination, *multicast*, when a transmission can have several destinations, or *broadcast*, when each data is transmitted to all PEs. In this thesis, we use unicast routing. In unicast routing each data message arriving at a router through an incoming link must be forwarded through only one of the output links.

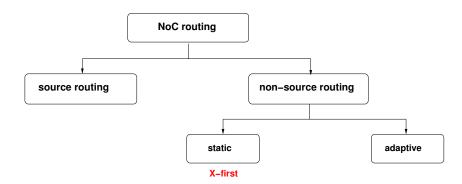

Depending on *where* routing decisions are taken, routing algorithms can be divided into *source* routing and *non-source* routing algorithms. In source routing, the whole path is fixed by the sender of the data and explicitly encoded in the headers of the data packets. The path information is read and used at each router traversed by the packet. In non-source routing, each router makes its own decisions locally, depending on parameters such as the final destination of the packet.

Non-source routing algorithms are either *static* (sometimes called deterministic) or *adaptive*. When static routing is used, all traffic between given source and destination fol-

Figure 2.3: Generic router for a 2D mesh NoC with X-first routing policy

Figure 2.4: Classification of NoC routing algorithms

lows the same route (path). Adaptive algorithms can dynamically modify the routing path depending on network conditions such as the presence of faulty or congested channels. In an adaptive NoC, data packets sent from a given source towards a given destination can follow different paths and arrive in an order different from the sending order. Adaptive routing can reduce congestion situations but the dynamic nature of adaptive routing means that it makes timing analysis more difficult, and thus complicates implementation when hard real-time guarantees are needed. Existing NoC architectures with support for real-time scheduling do not employ adaptive routing, and we make the same choice. In this thesis, we will use the classical X-first policy.

#### 2.1.3.2 Switching method and buffering policy

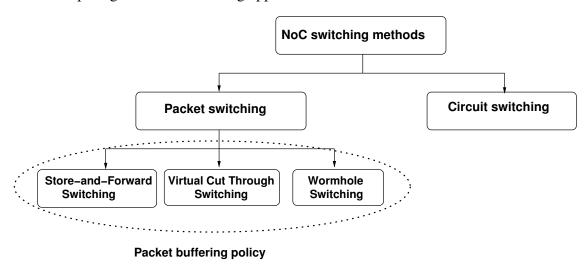

All NoC switching methods belong to one of two basic switching paradigms: circuit switching or packet switching. In *circuit switching* [Hilton and Nelson, 2006], communications are performed through dedicated communication channels (called circuits) that connect the source and destination PEs. A circuit consists in a sequence of point-to-point

physical links going all the way from the source PE to the destination PE. Two channels cannot share a physical link. This is achieved by statically fixing the output direction of each demultiplexer and the data source of each multiplexer along the channel path. Timing interferences between circuits are imposible. Thus, throughput is guaranteed and latency is predictible, but NoC use is usually low.

In *packet switching*, data is divided into small *packets* that are transmitted independently. Each packet is formed of a sequence of *flits*, where a flit is the amount of data that a link can transmit at the same time (in one clock cycle, for a synchronous NoC). Each packet must contain, in its *header flits* all the information needed to perform its communication, such as destination, priority, *etc*. The packetization of data allows a link to be used by multiple data transitions at the same time, by interleaving the transmission of the packets coming from different sources. This is why NoC use figures are usually improved when comparing to circuit switching approaches.

Figure 2.5: Classification of NoC switching techniques (part 1)

NoCs are complex communication networks where each data transmission traverses at least 2 routers. Achieving a good transmission throughput over such a network requires the use of some buffering in its routers and links. As pictured in Fig. 2.5, commonly-used buffering policies are *store-and-forward*, *virtual cut-through* and *wormhole*.

**Store-and-forward** This is the simplest buffering policy, used in most telecommunication networks. It requires that a router receives and stores a full data packet before forwarding it to the next router or NIC. To allow the storage of full packets, this method requires a large amount of buffering space in each router. This is why it is seldom used in NoCs [Kumar et al., 2002].

**Wormhole** In this buffering policy, a router makes its routing and arbitration decisions as soon as the header flits of a packet arrive. These flits are needed because they

may contain information such as the packet destination, or its priority, which are required by the routing and arbitration algorithms. Once the decisions are made, transmission can start as soon as the needed outgoing link allows transmission. This policy reduces communication latency and only requires a small buffering capacity. This is why it is the most common buffering policy in NoCs, used in all architectures described in the remainder of this thesis.

Virtual cut-through This approach is intermediate between the store-and-forward and wormhole buffering policies. Like in wormhole switching, forwarding can start as soon as one flit has been received. But forwarding can only start when signalling ensures that the next router on the path can receive the full packet [Sadawarte et al., 2011]. Thus, if a packet is blocked waiting for a link to be freed, it will be stored entirely on one router without blocking others. By comparison, in wormhole routing a blocked packet can stretch over several routers, blocking resources in all of them. Virtual cut-through is used in the NoC of the Intel SCC many-core chip [Howard and al., 2011].

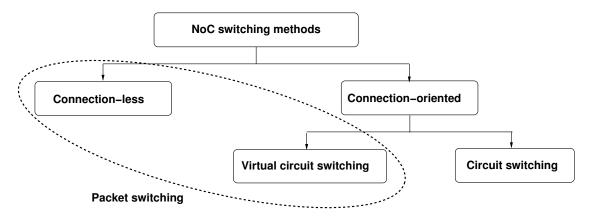

A second classification criterion divides NoC switching techniques into *connection-oriented* and *connection-less* ones (*cf.* Fig. 2.6): Connection-oriented techniques rely on dedicated (logical) connection paths established prior to the actual transmission of data. Connections can be created and destroyed using specific operations that typicaly carry a large timing penalty, but once a connection is established, communication along it is facilitated. In connectionless switching techniques, the communication occurs in a dynamic manner with no prior connection-oriented resource allocation. By definition, circuit switched communication is connection-oriented, wheras packet switched communication can be either connection-oriented (based on virtual circuit approaches detailed below), or connection-less.

Figure 2.6: Classification of NoC switching techniques (part 2)

#### 2.1.3.3 Arbitration/Scheduling

In packet switching NoCs a link can be shared by several data transmissions, and arbitration is needed to determine how packets belonging to multiple data transmissions are interleaved. Arbitration is realized at the level of NoC multiplexers.<sup>1</sup> As pictured in Fig. 2.7, several arbitration mechanisms are used in practice, each offering different levels of support for real-time implementation.

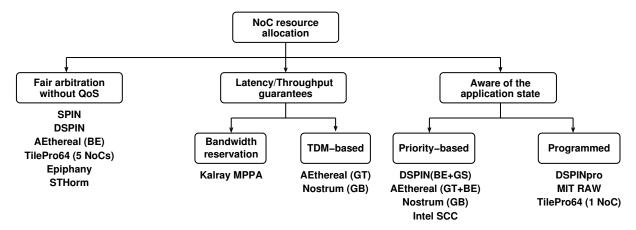

The simplest and most common arbitration technique is fair arbitration. In this approach, if two or more packets arriving from different sources request at the same time to pass through a NoC multiplexer, a fair arbitration policy such as Round Robin is used to decide which one passes first. The process is repeated whenever such a contention occurs. Along with a limitation on NoC packet sizes, the use of fair arbitration ensures that the NoC resources are evenly distributed among the data transmissions using them, with good NoC utilization factors and guaranteed (albeit possibly low) transmission throughputs for each transmission. Fair arbitration is used in the industrial NoC-based platforms Adapteva Epiphany [Adapteva, 2012], Kalray MPPA256 [MPPA, 2012], and ST STHorm [Benini, 2010]. In the Tilera TilePro64 [Tilera, 2008] chip, fair arbitration is used in 5 out of the 6 NoCs. In research prototypes, fair arbitration can be found from the early NoC architectures, such as SPIN [Guerrier and Greiner, 2000], to the more recent designs, where it is used in conjunction with other types of arbitration, such as priority-based, time division multiplexing-based, or programmed arbitration, as described below.

When designing real-time systems, the objective is to respect the real-time requirements. Achieving this goal on resource-constrained architectures usually amounts to achieving the best possible *predictable efficiency*. Given the large number of potential NoC contention points (router multiplexers), and the synchronizations induced by data transmissions, providing *tight* static timing guarantees is only possible if some form of system-level flow control mechanism is used. The tightest timing control is provided by circuit switching approaches. As explained earlier in this section, in circuit switching NoCs all communications are performed through dedicated communication channels formed of point-to-point physical links. Channels are set up so that they share no NoC resource, which makes timing interferences impossible. Once a channel is set up, communication latency and throughput are the best possible and timing analysis is easy. But the absence of resource sharing is also the main drawback of circuit switching, resulting in low utilization of the NoC resources. Even more important, the number of channels that can be established is limited by the number of NoC links, which severely limits application mapping choices.

This is why most NoCs use a packet switching approach. In this case, four types of

<sup>&</sup>lt;sup>1</sup>Arbitration mechanisms will be presented in greater detail in Chapter 4

NoC control mechanisms have been proposed to improve the real-time properties: Time Divison Multiplexing (TDM), bandwidth reservation, priority-based arbitration, and programmed arbitration. As shown in Fig. 2.7, more than one arbitration scheme can be supported in a NoC architecture, like in Æthereal (TDM-based, fair, and priority-based) or DSPIN (fair and priority-based).

Figure 2.7: Classification of NoC resource allocation policies in packet-switched NoCs

TDM-based and bandwidth reservation resource allocation techniques are often used in the context of *virtual circuit switching* communication protocols. Virtual circuit switching is an evolution of circuit switching which allows NoC link sharing between circuits, but ensures that each circuit has configurable and guaranteed latency and throughput.

The most popular way of providing these guarantees is by relying on *time division multiplexing (TDM)* arbitration in the NoC routers. Such NoCs relying on TDM arbitration are Æthereal [Goossens et al., 2005], Nostrum [Millberg et al., 2004b], and others [Sorensen et al., 2012]. In a TDM NoC, all routers share a common time base (the hardware clock). The point-to-point links are reserved for the use of the virtual circuits following a fixed cyclic schedule (a scheduling table). The reservations made on the various links ensure that communications can follow their path without waiting. TDM-based NoCs allow the computation of *precise latency and throughput guarantees*. They also ensure a strong *temporal isolation* between virtual circuits, so that changes to a virtual circuit do not modify the real-time characteristics of the other.

When no global time base exists, the same type of latency and throughput guarantees can be obtained in NoCs relying on *bandwidth management* mechanisms such as Kalray MPPA [MPPA, 2012, Harrand and Durand, 2011]. The idea here is to ensure that the throughput of each virtual circuit is limited to a fraction of the transmission capacity of a physical point-to-point link, by either the emitting tile<sup>2</sup> or by the NoC routers. Two or

<sup>&</sup>lt;sup>2</sup>In which case the actual NoC arbiters can be simple fair arbiters.

more virtual circuits can share a point-to-point link if the sum of their transmission needs is less than what the physical link provides.

But TDM and bandwidth management NoCs have certain limitations: One of them is that latency and throughput are correlated [Shi and Burns, 2010], which may result in a waste of resources. But the latency-throughput correlation is just one consequence of a more profound limitation: TDM and bandwith management NoCs largely ignore the fact that the needs of an application may change during execution, depending on its state. For instance, when scheduling a dependent task system with the objective of reducing task graph makespan, it is often useful to allow some communications to use 100% of the physical link, so that they complete faster, before allowing all other communications to be performed. One way of taking into account the application state is by using NoCs with support for priority-based scheduling [Shi and Burns, 2010, Panades, 2008, Howard and al., 2011]. In these NoCs, each data packet is assigned a priority level (a small integer), and NoC routers allow higher-priority packets to pass before lower-priority packets. To avoid *priority inversion* phenomenons, higher-priority packets have the right to preempt the transmission of lower-priority ones. In turn, this requires the use of one separate buffer for each priority level in each router multiplexer, a mechanism known as virtual channels in the NoC community[Panades, 2008].

The need for virtual channels is the main limiting factor of priority-based arbitration in NoCs. Indeed, adding a virtual channel (VC) is as complex as adding a whole new NoC[Yoon et al., 2010, Carara et al., 2007], and NoC resources (especially buffers) are expensive in both power consumption and area [Moscibroda and Mutlu, 2009]. To our best knowledge, among existing silicon implementations only the Intel SCC chip offers a relatively large numbers of VCs (eight) [Howard and al., 2011], and it is targeted at high-performance computing applications. Industrial MPPA chips targeting an embedded market usually feature multiple, specialized NoCs [Tilera, 2008, Adapteva, 2012, Harrand and Durand, 2011] without virtual channels. Other academic NoC architectures feature low numbers of VCs. Two VCs is a popular choice, in which case the channels are often labeled "guaranteed service", for the high-priority one, and "best effort", for the low-priority one [Goossens et al., 2005, Panades, 2008]. Current research on priority-based communication scheduling has already integrated this limitation, by investigating the sharing of priority levels [Shi and Burns, 2010].

The second limiting factor related to priority-based NoCs is that the associated scheduling theory mainly focuses on independent task systems. However, we have already explained that the large number of computing cores in an many-core architecture means that applications are likely to include parallelized code which is best modeled by large sets of relatively small *dependent tasks* with predictable functional and temporal behavior [Villalpando et al., 2010, Aubry et al., 2013, Gerdes et al., 2012]. Such timing-

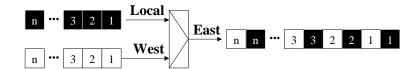

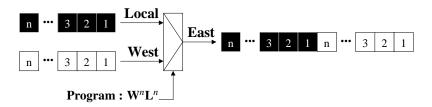

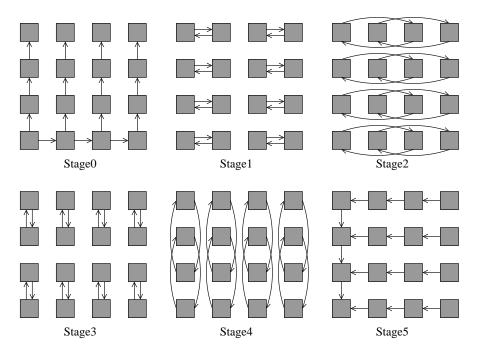

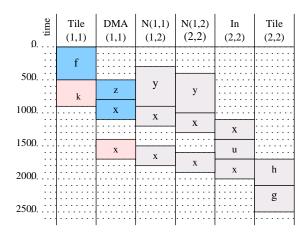

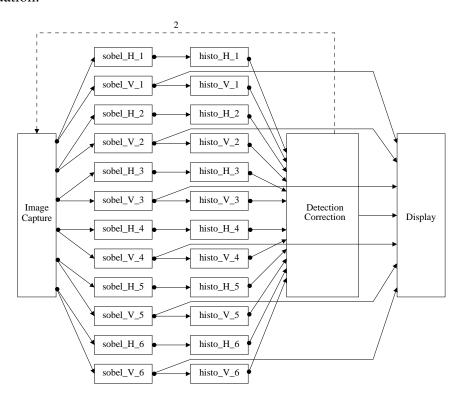

predictable dependent task systems are those that can *a priori* take advantage of an off-line scheduling approach, as opposed to on-line priority-based scheduling. But *efficient* off-line mapping requires NoCs with support for *static communication scheduling* [Tilera, 2008, Djemal et al., 2012, Waingold et al., 1997]. The idea here is to determine an efficient (possibly optimal) global computation and communication schedule, represented with a scheduling table, and then enforce it through synchronized *sequential computation and communication programs*. Computation programs run on processor cores to sequence task executions and the initiation of communications. Communication programs run on specially-designed micro-controllers that control each NoC multiplexer to fix the order in which individual data packets are transmitted. Synchronization between the programs is ensured by the data packet communications themselves.