# Memory Study and Dataflow Representations for Rapid Prototyping of Signal Processing Applications on MPSoCs

Karol Desnos

# ► To cite this version:

Karol Desnos. Memory Study and Dataflow Representations for Rapid Prototyping of Signal Processing Applications on MPSoCs. Signal and Image processing. INSA de Rennes, 2014. English. NNT: 2014ISAR0004 . tel-01127297

# HAL Id: tel-01127297 https://theses.hal.science/tel-01127297

Submitted on 7 Mar 2015  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Thèse

THESE INSA Rennes sous le sceau de l'Université européenne de Bretagne pour obtenir le titre de DOCTEUR DE L'INSA DE RENNES Spécialité : Traitement du Signal et des Images présentée par Karol Desnos ECOLE DOCTORALE : MATISSE LABORATOIRE : IETR

*u*e **b**

Memory Study and Dataflow Representations for Rapid Prototyping of Signal Processing Applications on MPSoCs Thèse soutenue le 26.09.2014 devant le jury composé de :

Jarmo TAKALA Professeur à l'Université Technologique de Tampere (Finlande) / Président Alix MUNIER-KORDON Professeur des Universités à l'Université Paris 6 / Rapporteur Renaud SIRDEY HDR, Commissariat à l'Energie Atomique de Saclay / Rapporteur Shuvra S. BHATTACHARYYA Professeur à l'Université du Maryland (USA) / Examinateur Slaheddine ARIDHI Docteur, Texas Instruments France / Encadrant Maxime PELCAT Maitre de Conférence à l'INSA de Rennes / Encadrant Jean-François NEZAN Professeur des Universités à l'INSA de Rennes / Directeur de thèse

Memory Study and Dataflow Representations for Rapid Prototyping of Signal Processing Applications on MPSoCs

Karol Desnos

Document protégé par les droits d'auteur

# Contents

| Acknowledgements 1 |                                  |         |                                                                |                         |

|--------------------|----------------------------------|---------|----------------------------------------------------------------|-------------------------|

| 1                  | <b>Intr</b><br>1.1<br>1.2<br>1.3 | Scope   | ion<br>al Context                                              | <b>3</b><br>3<br>6<br>7 |

| Ι                  | Ba                               | ckgrou  | ınd                                                            | 9                       |

| 2                  | Dat                              | aflow   | Models of Computation                                          | 11                      |

|                    | 2.1                              | Introd  | luction                                                        | 11                      |

|                    | 2.2                              | What    | is a Dataflow Model of Computation?                            | 12                      |

|                    |                                  | 2.2.1   | Models of Computation                                          | 12                      |

|                    |                                  | 2.2.2   | Dataflow Process Network                                       | 13                      |

|                    |                                  | 2.2.3   | Expression of Parallelisms                                     | 14                      |

|                    |                                  | 2.2.4   | Dataflow Models Properties                                     | 16                      |

|                    | 2.3                              | Static  | Dataflow Models of Computation                                 | 18                      |

|                    |                                  | 2.3.1   | Synchronous Dataflow (SDF)                                     | 18                      |

|                    |                                  | 2.3.2   | Single-Rate SDF, Homogeneous SDF, and Directed Acyclic Graph . | 21                      |

|                    |                                  | 2.3.3   | Cyclo-Static Dataflow (CSDF) and Affine Dataflow (ADF)         | 23                      |

|                    | 2.4                              | Hierar  | chical SDF Modeling                                            | 24                      |

|                    |                                  | 2.4.1   | Naive Hierarchy Mechanism for SDF                              | 24                      |

|                    |                                  | 2.4.2   | Interface-Based SDF (IBSDF): a Compositional Dataflow MoC      | 25                      |

|                    |                                  | 2.4.3   | Deterministic SDF with Shared FIFOs                            | 27                      |

|                    | 2.5                              | Dynar   | mic Dataflow Models of Computation                             | 28                      |

|                    |                                  | 2.5.1   | Parameterized SDF (PSDF)                                       | 28                      |

|                    |                                  | 2.5.2   | Schedulable Parametric Dataflow (SPDF)                         | 31                      |

|                    |                                  | 2.5.3   | Scenario Aware Dataflow (SADF)                                 | 32                      |

|                    | 2.6                              | Summ    | nary of Presented Dataflow MoCs                                | 33                      |

| 3                  | Rap                              | oid Pro | ototyping Context                                              | <b>35</b>               |

|                    |                                  |         | luction                                                        | 35                      |

|                    | 3.2                              | What    | is Rapid Prototyping?                                          | 35                      |

$\mathbf{53}$

|     | 3.2.1 | Heterogeneous Architecture Modeling                   | 37 |

|-----|-------|-------------------------------------------------------|----|

|     | 3.2.2 | Parallel Application Modeling                         | 38 |

|     | 3.2.3 | Application Deployment Constraints                    | 39 |

|     | 3.2.4 | Mapping and Scheduling                                | 40 |

|     | 3.2.5 | Simulation                                            | 41 |

| 3.3 | PREES | SM Rapid Prototyping Framework                        | 42 |

|     | 3.3.1 | Related Work on Dataflow Programming                  | 42 |

|     | 3.3.2 | PREESM Typical Rapid Prototyping Workflow             | 43 |

|     | 3.3.3 | PREESM Additional Features                            | 45 |

| 3.4 | Memo  | ory Optimization for MPSoCs                           | 47 |

|     | 3.4.1 | Modern Memory Architectures                           | 47 |

|     | 3.4.2 | Memory Management for Multicore Architectures         | 48 |

|     | 3.4.3 | Usual Memory Allocation Techniques                    | 48 |

|     | 3.4.4 | Literature on Memory Optimization and Dataflow Graphs | 50 |

| 3.5 | Concl | usion of the Background Part                          | 51 |

# **II** Contributions

| 4 | Dat                                                              | aflow  | Memory Optimization: From Theoretical Bounds to Buffer                                                                                                       |    |  |  |  |  |

|---|------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|   | Allocation 55                                                    |        |                                                                                                                                                              |    |  |  |  |  |

|   | 4.1                                                              | Introd | uction                                                                                                                                                       | 55 |  |  |  |  |

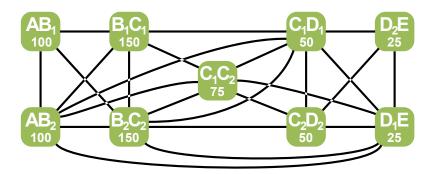

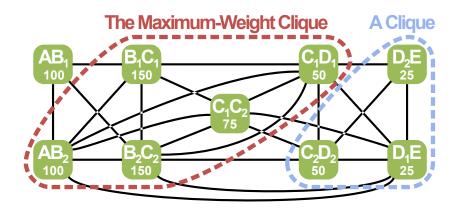

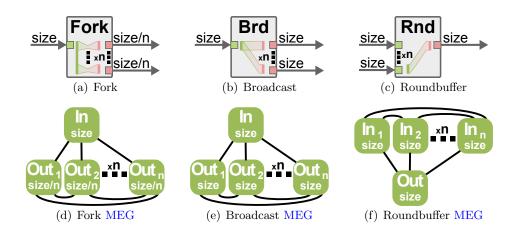

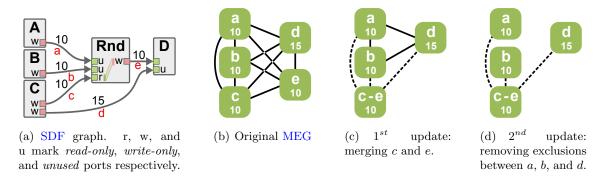

|   | 4.2                                                              | Memo   | ry Exclusion Graph (MEG)                                                                                                                                     | 55 |  |  |  |  |

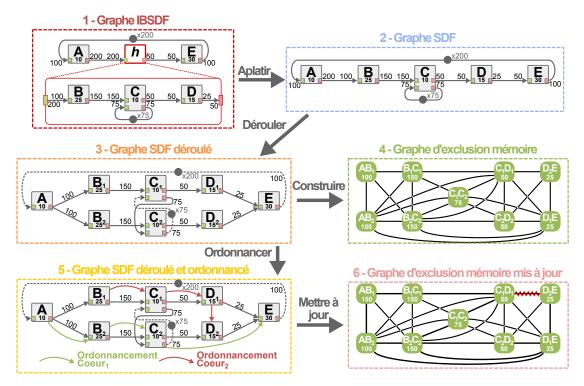

|   |                                                                  | 4.2.1  | IBSDF Pre-Processing for Memory Analysis                                                                                                                     | 55 |  |  |  |  |

|   |                                                                  | 4.2.2  | MEG Definition                                                                                                                                               | 57 |  |  |  |  |

|   |                                                                  | 4.2.3  | MEG Construction                                                                                                                                             | 61 |  |  |  |  |

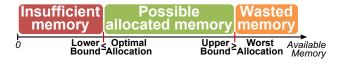

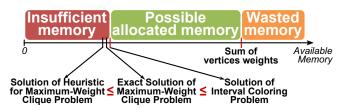

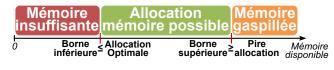

|   | 4.3                                                              | Bound  | ls for the Memory Allocation of IBSDF Graphs                                                                                                                 | 61 |  |  |  |  |

|   |                                                                  | 4.3.1  | Least Upper Bound                                                                                                                                            | 63 |  |  |  |  |

|   |                                                                  | 4.3.2  | Lower Bounds                                                                                                                                                 | 63 |  |  |  |  |

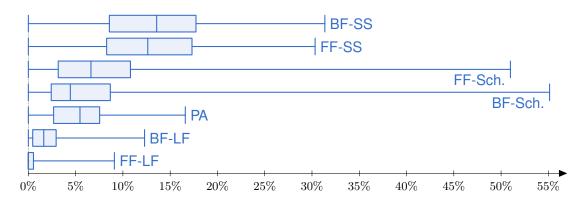

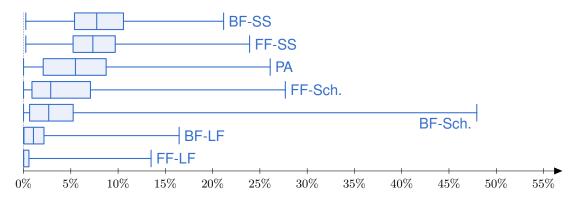

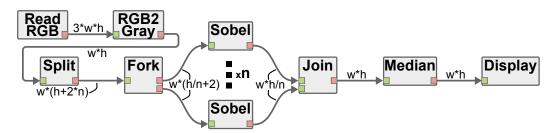

|   |                                                                  | 4.3.3  | Experiments                                                                                                                                                  | 67 |  |  |  |  |

|   | 4.4                                                              | Memo   | ry Allocation of a MEG                                                                                                                                       | 70 |  |  |  |  |

|   |                                                                  | 4.4.1  | MEG Updates with Scheduling and Time Information                                                                                                             | 71 |  |  |  |  |

|   |                                                                  | 4.4.2  | Memory Allocation Strategies                                                                                                                                 | 72 |  |  |  |  |

|   |                                                                  | 4.4.3  | Experiments                                                                                                                                                  | 74 |  |  |  |  |

|   | 4.5                                                              | Discus | sion                                                                                                                                                         | 79 |  |  |  |  |

|   |                                                                  | 4.5.1  | Approach Limitations                                                                                                                                         | 79 |  |  |  |  |

|   |                                                                  | 4.5.2  | Comparison with a FIFO dimensioning technique $\ldots \ldots \ldots \ldots$                                                                                  | 79 |  |  |  |  |

| 5 | Actor Memory Optimization: Studying Data Access to Minimize Mem- |        |                                                                                                                                                              |    |  |  |  |  |

| Č |                                                                  | Footp  |                                                                                                                                                              | 83 |  |  |  |  |

|   | 5.1                                                              | -      | $\operatorname{uction} \ldots \ldots$ | 83 |  |  |  |  |

|   | 5.2                                                              |        | ation: Memory Reuse Opportunities Offered by Actor Internal Behavior                                                                                         |    |  |  |  |  |

|   | 0                                                                | 5.2.1  | Actors Inserted During Graph Transformations                                                                                                                 | 84 |  |  |  |  |

|   |                                                                  | 5.2.2  | Actors with User-Defined Behavior                                                                                                                            | 86 |  |  |  |  |

|   | 5.3                                                              | -      | d Work                                                                                                                                                       | 88 |  |  |  |  |

|   | 0.0                                                              | 5.3.1  | Compiler optimization                                                                                                                                        | 88 |  |  |  |  |

|   |                                                                  | 5.3.2  | Dataflow Optimization                                                                                                                                        | 89 |  |  |  |  |

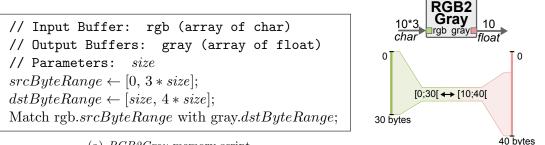

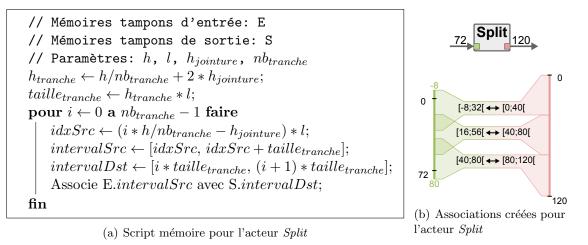

|   | 5.4                                                              |        | act Description of Actor Internal Behavior                                                                                                                   | 90 |  |  |  |  |

|   | 0.1                                                              | 5.4.1  | Matching Input and Output Buffers with Memory Scripts                                                                                                        | 90 |  |  |  |  |

|   |                                                                  | 5.4.2  | Port Annotations                                                                                                                                             | 94 |  |  |  |  |

|   |                                                                  | J. 1.4 |                                                                                                                                                              | 01 |  |  |  |  |

|          | 5.5                                              | Match          | Tree Memory Minimization                                                                                                  | . 96          |  |  |  |  |

|----------|--------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|--|

|          |                                                  | 5.5.1          | Applicability of Buffer Matches                                                                                           |               |  |  |  |  |

|          |                                                  | 5.5.2          | Match Trees Optimization Process                                                                                          | . 101         |  |  |  |  |

|          |                                                  | 5.5.3          | MEG Update                                                                                                                |               |  |  |  |  |

| 6        | Memory Study of a Stereo Matching Application 10 |                |                                                                                                                           |               |  |  |  |  |

| Ŭ        | 6.1                                              | -              |                                                                                                                           |               |  |  |  |  |

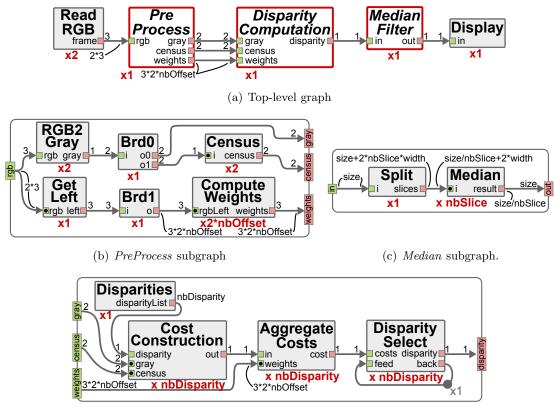

|          | 6.2                                              |                | n Presentation                                                                                                            |               |  |  |  |  |

|          |                                                  | 6.2.1          | Stereo Matching Application                                                                                               |               |  |  |  |  |

|          |                                                  | 6.2.2          | Target Multicore Shared Memory Architectures                                                                              |               |  |  |  |  |

|          | 6.3                                              | Practie        | cal Issues                                                                                                                |               |  |  |  |  |

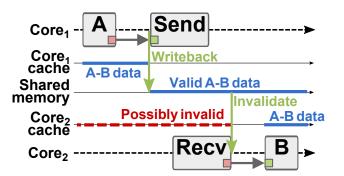

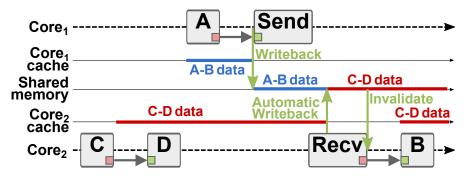

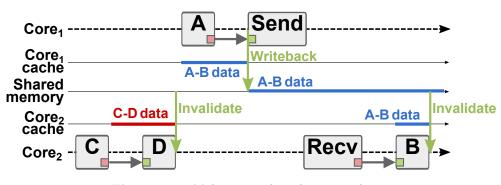

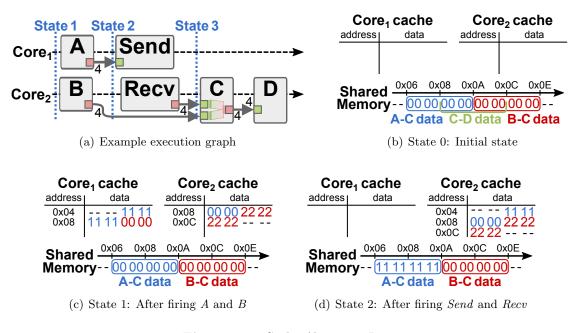

|          |                                                  | 6.3.1          | Multicore Cache Coherence                                                                                                 |               |  |  |  |  |

|          |                                                  | 6.3.2          | Data Alignment                                                                                                            |               |  |  |  |  |

|          | 6.4                                              |                | imental Results                                                                                                           |               |  |  |  |  |

|          |                                                  | 6.4.1          | Static Memory Optimization                                                                                                |               |  |  |  |  |

|          |                                                  | 6.4.2          | Comparison with Dynamic Memory Allocation                                                                                 |               |  |  |  |  |

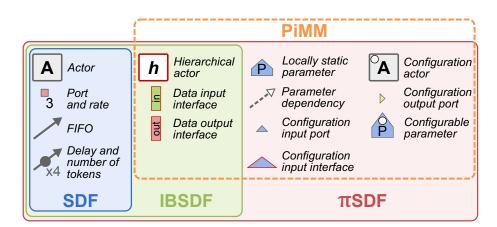

| 7        | Точ                                              | vards F        | Parameterized Results: The PiSDF Model                                                                                    | 123           |  |  |  |  |

|          | 7.1                                              | Introd         | uction                                                                                                                    | . 123         |  |  |  |  |

|          |                                                  | 7.1.1          | Motivation: Need for Reconfigurable Models of Computation                                                                 | . 123         |  |  |  |  |

|          | 7.2                                              | Found          | ation Dataflow Models of Computation                                                                                      | . 124         |  |  |  |  |

|          |                                                  | 7.2.1          | Synchronous Dataflow                                                                                                      | . 124         |  |  |  |  |

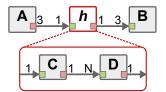

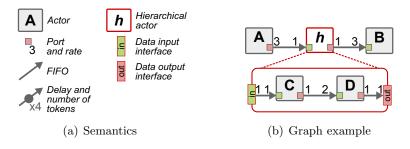

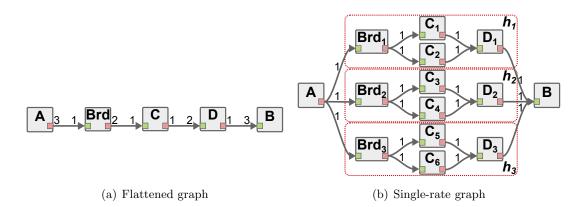

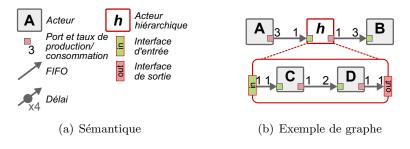

|          |                                                  | 7.2.2          | Interface-Based Synchronous Dataflow                                                                                      |               |  |  |  |  |

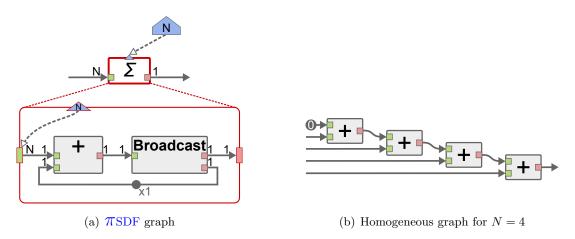

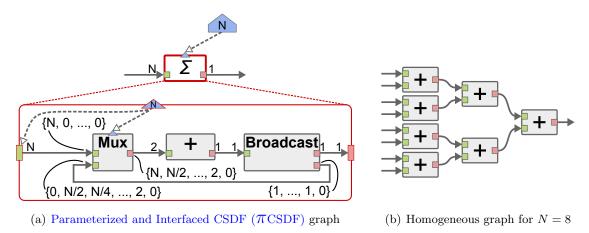

|          |                                                  | 7.2.3          | Parameterized Dataflow                                                                                                    | . 125         |  |  |  |  |

|          | 7.3                                              | Param          | eterized and Interfaced Dataflow Meta-Modeling                                                                            | . 127         |  |  |  |  |

|          |                                                  | 7.3.1          | $\pi$ SDF Semantics                                                                                                       | . 127         |  |  |  |  |

|          |                                                  | 7.3.2          | $\pi$ SDF Reconfiguration                                                                                                 | . 129         |  |  |  |  |

|          | 7.4                                              | Model          | Analysis and Behavior                                                                                                     | . 131         |  |  |  |  |

|          |                                                  | 7.4.1          | Compile Time Schedulability Analysis                                                                                      | . 132         |  |  |  |  |

|          |                                                  | 7.4.2          | Runtime Operational Semantics                                                                                             | . 132         |  |  |  |  |

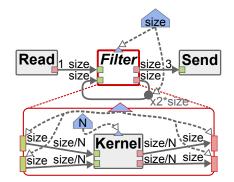

|          | 7.5                                              | PiMM           | Application Examples                                                                                                      | . 133         |  |  |  |  |

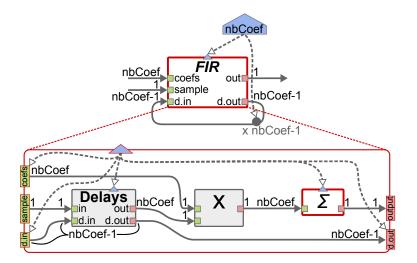

|          |                                                  | 7.5.1          | FIR Filter                                                                                                                | . 134         |  |  |  |  |

|          |                                                  | 7.5.2          | LTE PUSCH                                                                                                                 |               |  |  |  |  |

|          | 7.6                                              | Compa          | arison with Existing MoCs                                                                                                 | . 138         |  |  |  |  |

|          |                                                  | 7.6.1          | PiMM versus Parameterized Dataflow                                                                                        | . 140         |  |  |  |  |

|          |                                                  | 7.6.2          | PiMM versus SADF                                                                                                          | . 141         |  |  |  |  |

| 0        | C                                                | -1             |                                                                                                                           | 1 4 9         |  |  |  |  |

| 8        | <b>Con</b><br>8.1                                | clusion        | n<br>ary                                                                                                                  | 143           |  |  |  |  |

|          | 8.1<br>8.2                                       |                | e Work                                                                                                                    |               |  |  |  |  |

|          | 0.2                                              | 8.2.1          | Support for Complex Memory Architectures                                                                                  |               |  |  |  |  |

|          |                                                  | 8.2.1<br>8.2.2 |                                                                                                                           |               |  |  |  |  |

|          |                                                  | 8.2.2<br>8.2.3 | Memory-Aware Scheduling Techniques $\dots$ Rapid Prototyping for $\pi$ SDF graphs $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ |               |  |  |  |  |

| Δ        | French Summary 14                                |                |                                                                                                                           |               |  |  |  |  |

| <b>1</b> |                                                  |                | $\operatorname{uction}$                                                                                                   |               |  |  |  |  |

|          | A.1<br>A.2                                       |                | es de calcul de type flux de données                                                                                      |               |  |  |  |  |

|          | A.2<br>A.3                                       |                | ypage rapide avec PREESM                                                                                                  |               |  |  |  |  |

|          | -                                                |                | isation mémoire des diagrammes de flux de données                                                                         |               |  |  |  |  |

|          |                                                  | ~ Pum          | and an another and an and and                              | . <u>-</u> 01 |  |  |  |  |

| A.5 Optimisation mémoire des acteurs                                                                               |     |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| A.6Etude de cas : application d'appariement stéréoscopiqueA.7Vers plus de dynamisme : le modèle PiSDFA.8Conclusion | 158 |  |  |  |

| List of Figures                                                                                                    |     |  |  |  |

| List of Tables                                                                                                     |     |  |  |  |

| Acronyms                                                                                                           |     |  |  |  |

| Personal Publications                                                                                              |     |  |  |  |

| Bibliography                                                                                                       |     |  |  |  |

# Acknowledgements

First, I would like to thank my advisors Dr. Maxime Pelcat and Dr. Slaheddine Aridhi, and my thesis director Pr. Jean-François Nezan for their guidance, their support, and their trust for the last three years. Thank you for giving me the opportunity to pursue a PhD on such an interesting topic and in such a motivating and friendly working environment. Maxime, thank you for your organizational and technical insights and thank you for your open-mindedness on research directions followed during this PhD. Slah, thank you for your warm welcome at Texas Instruments and for giving an industrial perspective to this PhD. Jeff, thank you for all your advice during these three years, and thank you for giving me the opportunity to work with international scientists of world renown.

I want to express my gratitude to Pr. Alix Munier-Kordon and Dr. Renaud Sirdey for being part of the PhD committee and for taking the time to review this thesis during their summer vacation. I also want to thank Pr. Jarmo Takala for presiding the PhD committee and Pr. Shuvra S. Bhattacharyya for being a member of the PhD committee. Shuvra, thanks also for welcoming me to the University of Maryland, for sharing your expertise on dataflow models, and for making this visit such an inspiring and fruitful collaboration.

I also would like to thank all members of the image group of the IETR for making me feel part of the team since the beginning. Special thanks to all my officemates during these three years: Jérome Gorin, Julien Heulot, Khaled Jerbi, Antoine Lorence, Erwan Nogues, and Fabien Racapé. Thanks also to Aurore Arlicot, Safwan El Assad, Clément Guy, Judicaël Menant, Yaset Oliva, Romina Racca and former members of the team Jonathan Piat and Matthieu Wipliez for their help and collaboration during this PhD. Also, thanks to Frédéric Garesché for his IT support and many thanks to Corinne Calo, Aurore Gouin and Jocelyne Trémier for their administrative support.

It has been a pleasure working with the High Performance Embedded Processing team from Texas Instruments France. Special thanks to Eric Biscondi, Raphael Defosseux, Renaud Keller, Lidwine Martinot, Filip Moerman, Alexandre Romana, Olivier Paviot, and Sébastien Tomas for helping me with the subtlety of multicore DSP programming.

Many thanks to all members of the DSPCAD group from the University of Maryland. Special thanks to Zheng "Joe" Zhou, it was a real pleasure to carpool and have these very interesting conversations with you everyday during my stay in Maryland. Thanks also to George Zaki for his helpful advice before and during my visit.

Thanks to Karina Aridhi for reading and correcting this documents and previous publications. Thanks to the French taxpayers for, mostly reluctantly, funding the last 23 years of my education, including this PhD. Thanks also to all coffee producers around the world for making this work possible.

I am deeply grateful to my family and friends for their support and for helping me keep my sanity during these last three years. In particular, I would like to express my infinite gratitude to my parents, my sister, and my brother for their unconditional support and their love. I also want to thank the Martials for their encouragements and for making me feel part of the family. Thanks also to Nymeria and Burrito for their fluffiness.

Finally, and most importantly, I want to thank my dear love, Pauline, for sharing my life during the last 7 years. Pauline, thank you for your continuous support and for your indulgence to my crappy mood during the redaction of this document.

# chapter 1

# Introduction

# **1.1 General Context**

Over the last decade, **embedded systems** have been one of the most remarkable technological advances, driving the development of many industries, and entering the daily life of most human beings. An embedded system is an integrated electronic and computer system designed to serve a dedicated purpose. Car Anti-lock Braking Systems (ABS), Global Positioning Systems (GPS), e-readers, pacemakers, digital cameras, and autonomous vacuum cleaners are examples of modern appliances containing one or more embedded systems.

# **Embedded Systems Development Constraints**

The development of an embedded system requires consideration of many constraints. These constraints can be classified in three categories, *application constraints*, *cost constraints* and *external constraints*.

- Application constraints refer to the requirements that an embedded system must satisfy to serve its intended purpose. For example, many embedded systems have performance requirements and must react to external events within a limited amount of time, or must produce results at a fixed rate. Another example of an application constraint is the reliability of an embedded system that restricts the probability of a system failure, primarily for safety reasons. Size limitation and power consumption are also major requirements for handheld or autonomous embedded systems.

- **Cost constraints** refer to all factors influencing the total cost of an embedded system. These factors cover the engineering development cost, the production cost, the maintenance cost, and also include the recycling cost of an embedded system.

- External constraints refer to the requirements that an embedded system must satisfy but that are nonessential to its purpose. Regulations and standards are examples of external constraints that dictate certain characteristics of an embedded system, but non-compliance would not prevent an embedded system from serving its purpose. The environment in which an embedded system is used can also have an impact on its design. Extreme temperatures, high humidity, rapidly changing pressure are examples of external constraints.

All these constraints are often contradictory, even within a single category. For example, reducing the power consumption of an embedded system can be achieved by lowering its clock frequency, which in turn will decrease the performance of this system. Hence, the development of an embedded system often consists of satisfying the most important constraints, and finding an acceptable trade-off between remaining ones.

#### Hardware and Software of Embedded Systems

Embedded systems, like most computer systems, are composed of two complementary parts: the *Hardware* and the *Software* part.

• Hardware refers to all the physical components that are assembled in order to create an embedded system. These components include processing elements, clock generators, sensors, actuators, analog-to-digital converters, memories, external communication interfaces, user interfaces, internal means of communication, and power management units among other elements. The set of hardware components contained in an embedded system and the connections between these components is defined as the **architecture** of this system. The most important hardware components are the processing elements that are responsible both for controlling the embedded system, and for performing its computation. Depending on the purpose of an embedded system, different kind of processing elements can be used. For example, simple low-power microcontrollers are often used in control systems that require little or no computation. For computation intensive systems, like audio and video Digital Signal Processing (DSP) systems, specialized processors providing a high computational power for a limited cost are used.

In the early 1960s, following the creation of the first integrated circuit by Jack Kilby [Kil64], the first embedded systems were expensive, were composed of discrete hardware components, and were used only for military and space exploration projects. Progressively, the miniaturization of integrated circuits led to the integration of more and more hardware components within a single chip called a System-on-Chip (SoC). Nowadays, embedded systems are often based on complex integrated circuits called heterogeneous Multiprocessor Systems-on-Chips (MPSoCs). An heterogeneous MPSoC integrates all the elements of an embedded system, including different processing elements, on a single chip.

• Software refers to the computer programs executed by the processing elements of an embedded system. A program is a sequence of instructions stored as binary words in memory components of an embedded system. Processing elements of an embedded system iteratively read and execute the primitive operations encoded by the successive instructions of a program. Primitive operations include arithmetic and logic operations, jumps in the program sequence, configuration and control of other components of the embedded system, communication and synchronization with other processing elements, and read and write operations to the system memories.

Programming an embedded system consists of writing a sequence of instructions that specify the behavior of its processing elements. In early embedded systems, program binary words were written directly by system developers. Progressively, this technique was replaced with higher-level programming methods that allow the specification of a program behavior with languages easier to understand for developers. Programs written in these high-level languages are then automatically translated into equivalent binary instructions by a computer program called a compiler. In an effort to reduce development time of embedded systems, hardware and software parts are generally developed jointly as part of a hardware/software co-design process.

#### Embedded System Software Productivity Gap

In 1965, Moore predicted that the number of transistors in an integrated circuit would double every two years [Moo65]. Since then, this prediction has revealed itself to be true, driving an ever-increasing complexity of hardware components. In the meantime, the introduction of new programming languages with higher levels of abstraction has considerably improved the software productivity of developers. The software productivity measures the complexity of a program written by a developer within a given amount of time. As presented by Ecker et al. in [EMD09], the software productivity of developers is doubled every five years, or 2.5 times slower than hardware complexity. Hence, it is becoming more and more difficult for software developers to fully exploit the capabilities of hardware systems. This problem is often referred as the **software productivity gap**.

In recent years, the computational power of hardware was increased primarily by multiplying the number of processing elements running concurrently in MPSoCs. To fully exploit the computational power offered by these new architectures, programming languages must allow developers to specify applications where computations can be executed in parallel. A reason for the software productivity gap is that, as presented in [Bar09], the most popular language for programming embedded systems, namely the C language, is an imperative language whose basic syntax has a limited ability to express parallelism. This issue highlights the pressing need for new software programming techniques, such as dataflow programming, to bridge the software productivity gap.

#### **Dataflow Programming**

Dataflow Models of Computation (MoCs) have emerged as efficient programming paradigms to capture the parallelism of software. Applications modeled with dataflow MoCs consist of a directed graph where each vertex represents an independent computational module, and each edge represents an explicit communication channel between two vertices. The popularity of dataflow models and languages in the research, academic, and industrial communities is due to their natural expressivity of parallelism, their modularity, and their compatibility with legacy code. Indeed, dataflow graphs are used to specify networks of computational modules, but the specification of the internal behavior of these modules can be written in any programming language, including C code. The compatibility with legacy code has a positive impact on developers' productivity, since development time can be reduced by reusing previously developed and optimized programs.

Since the introduction of the first dataflow MoC by Kahn in [Kah74], many dataflow models have been proposed in the literature, each promoting a custom set of properties for application descriptions. For example, some dataflow models define construction rules for dataflow graphs that guarantee certain application properties at compile time, such as the performance or the reliability of applications. Such dataflow models are often used to capture the *application constraints* of embedded systems.

### **Rapid Prototyping Context**

Rapid prototyping techniques and tools are developed as part of an effort to accelerate and ease the development of embedded systems. The classic embedded system design flow is a relatively straightforward process whose ultimate goal is to produce an embedded system satisfying all design constraints. By contrast, the purpose of rapid prototyping techniques is to create an inexpensive prototype as early as possible in the development process. Generating new prototypes and analyzing their characteristics allow developers to identify critical issues of the prototype, and then to iteratively improve and refine the developed embedded system.

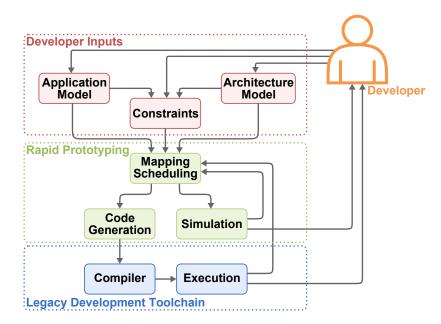

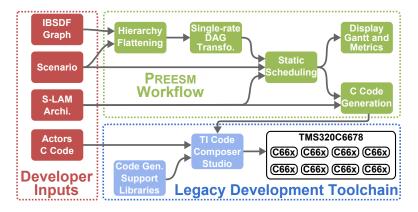

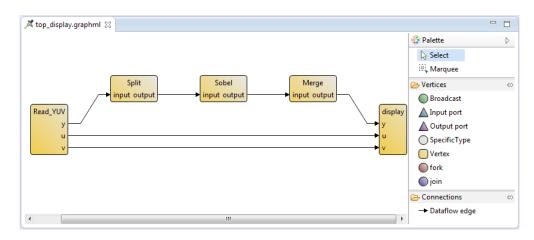

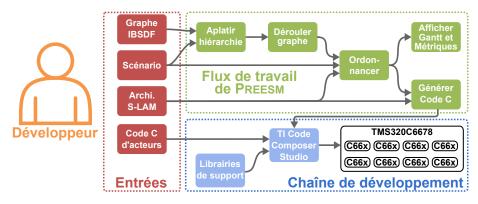

The work presented in this thesis is developed as part of a rapid prototyping framework called the Parallel and Real-time Embedded Executives Scheduling Method (PREESM). PREESM is a software rapid prototyping framework being developed at the Institute of Electronics and Telecommunications of Rennes (IETR) since 2007. The main objective of PREESM is to automate the deployment of applications modeled with dataflow graphs on heterogeneous MPSoCs. In addition to dataflow specification of the application, PREESM inputs include a System-Level Architecture Model (S-LAM) for specifying the targeted hardware components, and a *scenario* specifying design constraints of the embedded system. Using these inputs, PREESM can generate simulations of the embedded system behavior and can generate compilable code for the targeted MPSoC. PREESM has been successfully used for the rapid prototyping of real-time constrained Digital Signal Processing applications, computer vision, telecommunication, and multimedia applications on several heterogeneous MPSoCs [PAPN12, HDN<sup>+</sup>12, Zha13].

# 1.2 Scope of Thesis

After the processing elements, memories are the next most important components of an architecture. Indeed, from the hardware perspective, memory banks can cover up to 80% of the silicon area of an integrated circuit [DGCDM97]. Despite this large area overhead, and the associated power consumption, memory is still a scarce resource from the software perspective. For example, in the MPPA256 many-core chip from Kalray, each memory bank of 2 MBytes is shared between 16 processing elements, for a total of 32 MBytes of on-chip memory [Kal14]. Another example is the TMS320C6678 from Texas Instrument where 8.5 MBytes of memory are embedded on a chip with 8 DSP cores [Tex13]. These memory capacities remain relatively low compared to software requirements. For example, in a video decoding application, more than 3 MBytes are needed to store a single Full HD frame of  $1920 \times 1080$  pixels. Although external memories can still be used as a complement to the memory embedded in MPSoCs, access to these external memory banks is much slower, and has a negative impact on the performance of an embedded system. Hence, the study and optimization of memory issues is a critical part in the development of an embedded system, as it can strongly impact the system performance and cost.

In this thesis, new techniques are introduced to study the memory issues encountered during the deployment of applications modeled with dataflow graphs onto heterogeneous multiprocessors architectures. The main contributions of this thesis are:

- 1. A method to derive the memory bound requirements of an embedded system in the early stages of its development, when there is a complete abstraction of the system architecture [DPNA12]. This method is based on an analysis of the system application, and allows the developer of a multi-core shared-memory system to adequately size the chip memory.

- 2. A flexible method to **minimize the amount of memory allocated** for applications implemented on a shared-memory MPSoC [DPNA13]. In this method, memory allocation can be performed at three distinct stages of the rapid prototyping process,

each offering a distinct trade-off between memory footprint and flexibility of the application execution.

- 3. A set of **annotations for dataflow graphs** that allows software developers to specify internal data dependencies of the computational modules. An optimization technique is also presented to automatically **exploit the memory reuse opportunities** offered by these new annotations and reduce the amount of memory allocated by the rapid prototyping process.

- 4. A case study of the deployment of a state-of-the-art computer-vision application on a physical MPSoC. In addition to showing the efficiency of the new memory optimization technique, this case study also presents technical solutions to support the execution of a dataflow graph on a cache-incoherent MPSoC [DPNA14].

- 5. A new reconfigurable dataflow meta-model that overcomes the limitations of the dataflow model currently used in PREESM while preserving its most advantageous characteristics [DPN<sup>+</sup>13].

All these contributions have been developed as part of a scientific collaboration between the IETR, Texas Instrument France (contributions 1 to 5), and the DSPCAD group from the University of Maryland (contribution 5).

# 1.3 Outline

This thesis is organized in two parts: Part I introduces the concepts and research issues studied in this thesis, and Part II presents and evaluates the contributions of this thesis.

In Part I, Chapter 2 formally defines the concept of dataflow Model of Computation (MoC) and presents the specific characteristics of all dataflow MoCs studied in this thesis. Then, Chapter 3 details the design challenges addressed in rapid prototyping frameworks and emphasizes the importance of memory-related issues.

In Part II, the memory bounding technique and the memory allocation techniques based on dataflow descriptions of applications are presented and evaluated in Chapter 4. Then, Chapter 5 presents the memory minimization technique based on a new set of annotations for the computational modules of a dataflow graph. In Chapter 6, the memory analysis and optimization techniques are evaluated for the rapid prototyping of a computer vision application on a real MPSoC. Chapter 7 defines the semantics of the new dataflow meta-model and compares its characteristics with existing MoCs. Finally, Chapter 8 concludes this work and proposes potential research directions for future research.

# Part I Background

# CHAPTER 2

# Dataflow Models of Computation

# 2.1 Introduction

Sketches are commonly used by engineers, scholars, and researchers as a way to conceptualize and illustrate systems and ideas in early stages of development. These informal graphical representations are used in many engineering domains to specify the purpose of the components of a system and the relations between these components.

Block diagrams are among the most popular informal models for the high-level specification of electronic and computer systems. A block diagram is a drawing composed of a set of boxes, usually representing the components of the system, and a set of lines and arrows representing the relations between components. In 1921, Gilbreth et al. [GG21] proposed a first formalization of block diagrams called "process chart" for the specification of production processes.

In the computer science domain, Kelly et al. [KLV61] introduced the BLOck DIagram compiler (BLODI) in 1961. BLODI is the first compiler for programs described with a formalized block diagram language. At the time of punched cards, the main objective of the BLODI language was to make computer programming accessible to persons with no knowledge in programming languages. The BLODI language was composed of a set of 30 primitive blocks, like adders, filters, and quantizers, that could be used to compose Digital Signal Processing (DSP) applications.

Nowadays, graphical languages are still popular for the specification and the development of software and hardware systems. For example, the MCSE (methodology for the design of electronic systems) [Cal93], is a hardware/software co-design methodology that is partly based on a formal block diagram description of the specified system. In computer science, the UML (Unified Modeling Language) [RJB04] is a collection of diagrams used for the high-level specification of software solutions. Following the BLODI language, several diagram-based alternatives to classical text-based programming languages have been proposed for different purposes. Labview<sup>®</sup> [Joh97] and Matlab Simulink<sup>®</sup> [Mat96] are among the most popular diagram-based programming languages used in commercial development environments.

This thesis focuses on the study of applications described with diagram-based Models of Computation (MoCs) called dataflow MoCs. Dataflow MoCs can be used to specify a wide

range of Digital Signal Processing (DSP) applications such as video decoding [TGB+06], telecommunication [PAPN12], and computer vision [NSD05] applications.

Dataflow MoCs and their properties are formally defined in Section 2.2. Sections 2.3, 2.4, and 2.5, respectively, present state-of-the-art static, hierarchical, and dynamic dataflow models proposed in the literature. Finally, Section 2.6 summarizes the properties of all dataflow MoCs presented in this chapter.

# 2.2 What is a Dataflow Model of Computation?

### 2.2.1 Models of Computation

A Model of Computation (MoC) is a set of operational elements that can be composed to describe the behavior of an application. The set of operational elements of a MoC and the set of relations that can be used to link these elements are called the semantics of a MoC.

As presented in [Sav98], MoCs can be seen as an interface between the computer science and the mathematical domain. A MoC specifies a set of rules that control how systems described with the MoC are executed. Each element of the semantics of a MoC can be associated to a set of properties such as timing properties or resource requirements. These rules and properties provide the theoretical framework that can be used to formally analyze the characteristics of applications described with a MoC. For example, using a mathematical analysis, it may be possible to prove that an application described with a MoC will never get stuck in an unwanted state or that it will always run in a bounded execution time.

There exists a wide variety of MoCs that each have their own specificities and objectives. The following MoCs are examples of popular MoCs among programmers and system designers.

- Finite-State Machine (FSM): The FSM MoC semantics consists of 2 elements: states and transitions between states. Each transition of the model is associated with a condition that guards the traversal of this transition. In an FSM, a unique state is active at any given time. A transition from a state to another can be traversed only when the associated condition is valid. FSMs are commonly used for the description of sequential control systems. For example, FSMs are used in VHDL to capture the control part of a hardware system [Gol94].

- Lambda calculus: The lambda calculus MoC semantics consists of a single element called lambda term [Chu32]. A lambda term is either a variable, a function with a unique lambda term argument, or the application of a function to a lambda term. Any lambda calculus is obtained by composing lambda terms. Lambda calculus was originally developed by mathematicians as a way to study and characterize functions [Ros84]. Today, MoCs derived from the lambda calculus MoC are the foundation of functional programming languages such as Haskell, Lisp, Scheme, and OCaml.

- **Process network:** The process network MoC semantics consists of 2 elements: processes and unbounded First-In First-Out queues (FIFOs). The processes of a process network are independent tasks that perform computation concurrently. Processes communicate with each other by sending quanta of data, called data tokens, through the FIFOs of the process network. The process network MoC was originally developed by Kahn as a semantics for parallel programming languages [Kah74]. The dataflow MoCs studied in this thesis are derivatives of the process network MoC.

• Logic circuit: The logic circuit MoC semantics consists of 2 elements: logic gates and boolean signals. In the logic circuit MoC, systems have no state and the boolean value (*true* or *false*) of an output signal of a logic gate only depends on the current values of the input signals of this logic gate [Sav98]. The logic circuit MoC is commonly used in VHDL to describe the basic blocks composing a hardware system.

Most programming languages implement the semantics of several MoCs. For example, the VHDL language supports many MoCs including *logic circuits*, *finite state machines*, and *process networks* [Ash90]. Composing several MoCs into a single programming language allows the developer of a system to choose the best suited MoC for the description of each part of the system.

#### 2.2.2 Dataflow Process Network

In [LP95], Lee and Parks formalize the semantics of the Dataflow Process Network (DPN) MoC as a subset of the process network MoC. Although the Dataflow Process Network (DPN) MoC is not the first dataflow MoC published in the literature [Kah74, Den74], it constitutes a first attempt to provide a formal semantics for dataflow MoCs. In this thesis, a DPN is formally defined as follows:

**Definition 2.2.1.** A Dataflow Process Network (DPN) is a directed graph denoted by  $\mathbf{G} = \langle \mathbf{A}, \mathbf{F} \rangle$  where:

- **A** is the set of vertices of *G*. Each vertex  $a \in A$  is a computational entity named an actor of the DPN. Each actor  $a \in A$  is defined as a tuple  $\mathbf{a} = \langle \mathbf{P}_{data}^{in}, \mathbf{P}_{data}^{out}, \mathbf{R}, \mathbf{rate} \rangle$  where:

- $\mathbf{P}_{data}^{in}$  and  $\mathbf{P}_{data}^{out}$  respectively refer to the set of data input and output ports of the actor.

- $\mathbf{R} = \{R_1, R_2, ..., R_n\}$  is the set of firing rules of the actor. A firing rule  $R_i \in R$  is a condition that, when satisfied, can start an execution, called firing, of the associated actor.

- rate :  $(R, P_{data}^{in} \cup P_{data}^{out}) \rightarrow \mathbb{N}$  associates a firing rule to the number of atomic data objects, called data tokens, consumed or produced on a given data port, for a firing of the actor resulting from the validation of this firing rule.

- $\mathbf{F} \subseteq A \times A$  is the set of edges of G. Each edge  $f \in F$  is an unbounded First-In First-Out queue (FIFO) that transmits data tokens between actors. Each FIFO  $f \in F$  is defined as a tuple  $\mathbf{f} = \langle \mathbf{prod}, \mathbf{cons}, \mathbf{src}, \mathbf{snk}, \mathbf{delay} \rangle$  where:

- **prod** :  $F \to A$  and **cons** :  $F \to A$  associate producer and consumer actors to a FIFO.

- src :  $F \rightarrow P_{data}^{out}$  and snk :  $F \rightarrow P_{data}^{in}$  associate source and sink ports to a FIFO.

- delay :  $F \to \mathbb{N}$  corresponds to a number of data tokens present in the FIFO when the described application is initialized.

The semantics of the DPN MoC only specifies the *external* behavior of the actors: the firing rules specify when an actor should be executed and the port rates specify how many tokens are exchanged by an actor for each firing. The description of the *internal* behavior of an actor is not part of the DPN MoC. In order to specify the actual computation performed by the actor at each firing, a *host language* must be used. In most

dataflow programming frameworks, imperative languages, like C or Java, or hardware description languages, like VHDL, are used as *host languages* to describe the internal behavior of actors [GLS99]. Alternatively, dedicated languages, like the CAL Actor Language (CAL) [EJ03] or  $\Sigma C$  [Bod13, GSLD11, ABB<sup>+</sup>13], have been proposed to describe both the *external* and *internal* behaviors of actors.

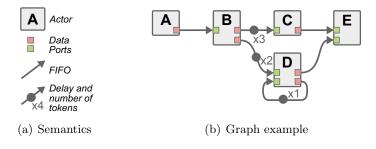

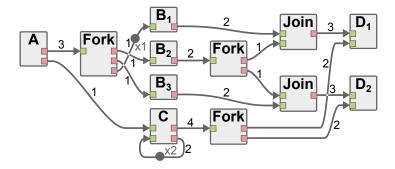

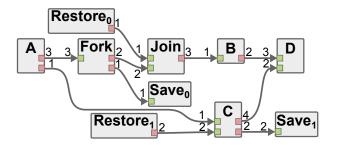

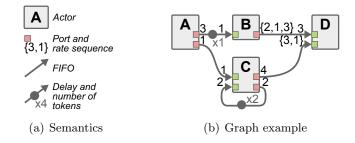

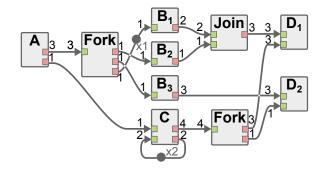

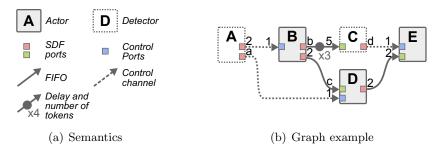

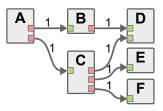

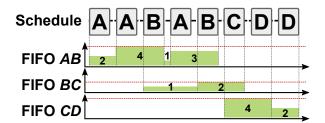

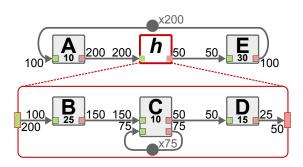

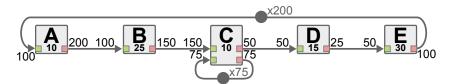

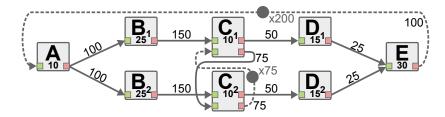

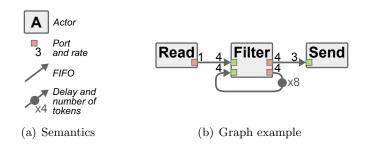

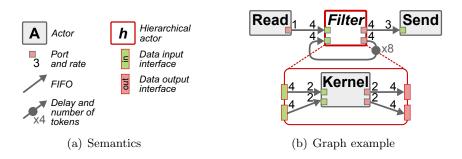

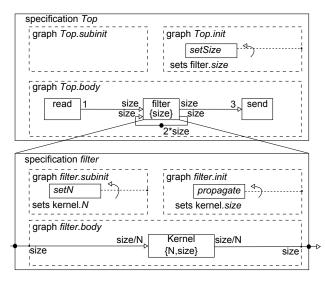

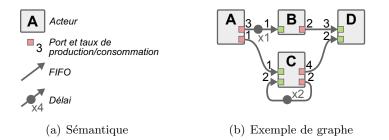

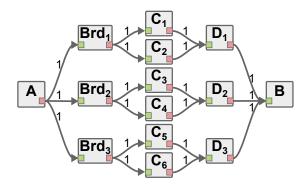

Figure 2.1 illustrates the graphical elements associated to the semantics of the DPN MoC and gives an example of a DPN graph. The example graph presented in Figure 2.1(b) contains 5 actors interconnected by a network of 6 FIFOs. The FIFOs linking actors B to C, actors B to D, and actor D to itself contain 3, 2, and 1 initial tokens respectively.

Figure 2.1: Dataflow Process Network (DPN) MoC

#### **Dataflow MoCs**

The semantics presented in Definition 2.2.1 serves as a basis for the semantics of many dataflow MoCs. Indeed, most dataflow MoCs are the result of a specialization or a generalization of the DPN semantics. Specializing the DPN semantics consists of adding new restrictions to the MoC. For example, the Synchronous Dataflow (SDF) MoC [LM87b] restricts the rates of data ports to a single scalar value [LM87b]. The DPN MoC itself is a specialization of the Kahn Process Network (KPN) MoC [Kah74]. Generalizing the DPN semantics consists of adding new elements to its semantics. For example, the Scenario-Aware Dataflow (SADF) MoC [TGB+06] introduces, among other new elements, a stochastic model of the execution time of actors. Specialization and generalization of the DPN semantics are often used jointly to derive new dataflow MoCs.

DPN and its derivatives (Sections 2.3 to 2.5) are popular MoCs for the description of Digital Signal Processing (DSP) applications and systems. Indeed, as shown in [LP95], data tokens provide an intuitive representation of the samples of a discrete signal, and networks of actors naturally capture the successive transformations applied to a digital signal. Finally, DPNs are often used to model repetitive DSP applications whose purpose is to process a continuous stream of data tokens.

## 2.2.3 Expression of Parallelisms

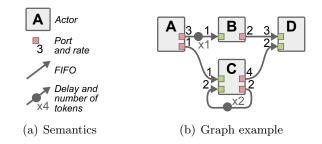

One of the major objectives of dataflow graphs is to ease the description of parallelism. In  $[ZDP^+13]$ , Zhou et al. identify 4 different sources of parallelism in a dataflow graph: task parallelism, data parallelism, pipeline parallelism, and parallel actor parallelism.

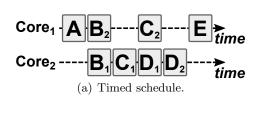

Figure 2.2 presents 4 Gantt diagrams that illustrate the different sources of parallelism. Each Gantt diagram represents a sequence of actor firings, called schedule, corresponding to an execution of the DPN presented in Figure 2.1(b) on two processing elements. In these schedules, it is assumed that the DPN is a repetitive process whose schedule can be repeated indefinitely. Each schedule contains a complete repetition, called **iteration**, of

the periodic schedule. Actors with a dotted border belong to prior or next iterations of the schedule, as indicated by the +1, -1, and +2 notations on these actors.

Figure 2.2: Illustration of the 4 sources of parallelism in dataflow MoCs

- Task parallelism: A FIFO of a dataflow graph induces a dependency constraint between its source and sink actors. A chain of actors linked by dependency constraints is called a **data-path**. Two actors belong to parallel data-paths if there exists no data-path between these actors. In such a case, there is no dependency constraint between these actors and their firings can be processed in parallel. For example, in Figure 2.1(b), actors C and D belong to parallel data-paths and can be executed concurrently, as can be seen in Figure 2.2(a).

- Data parallelism: In dataflow graphs, the computation of an actor only depends on the data tokens consumed during a firing. Hence, each firing of a single actor is independent from its other firings, and no state or context needs to be restored before firing an actor [LP95]. Since successive firings of an actor are independent, if enough data tokens are present in the input FIFOs, then several firings can be executed concurrently. For example, in Figure 2.2(b), it is assumed that actors Cand D produce enough data tokens for actor E to be executed twice in parallel. If the behavior of an actor requires the definition of a state, this state must be explicitly specified in the dataflow graph with a self-loop FIFO conveying state data-tokens from a firing to the next, as illustrated by actor D in Figure 2.1(b).

- **Pipeline parallelism:** Pipelining an application consists of starting a new iteration of a dataflow graph before the end of the previous iteration. Pipelining is possible if there is no data dependency between successive iterations of a dataflow graph. In order to pipeline a dataflow graph, the sequence of actor firings is divided into subsequences, called stages, that can be executed concurrently. Initial data tokens, also called delays, can be used to separate two pipeline stages explicitly in the application graph. For example, in Figure 2.2(c), FIFOS *BC* and *BD* contain initial data tokens that can be used to fire actors *C* and *D* without waiting for the first data tokens produced by actor *B*. Hence, actors *A* and *B* and actors *C*, *D*, and *E* respectively compose the two pipeline stages that can be repeatedly executed in parallel.

- **Parallel actor parallelism:** A parallel actor is an actor that embeds inner (intrafiring) parallelism, and whose execution may be accelerated by the use of multiple processing elements [ZDP<sup>+</sup>13]. The inner parallelism of a parallel actor can have different sources:

- The host language describing the internal behavior of actors allows parallel computation. For example, thread-based programming languages can be used to describe parallel computations. The advantage of running several threads in parallel instead of firing several actors concurrently is that multiple threads may access shared variables whereas several actors can not.

- The parallel actor is a hierarchical actor whose internal behavior is itself described with a dataflow graph. To this purpose, several hierarchical dataflow MoCs have been proposed in the literature [PBR09, BB01, NL04].

In Figure 2.2(d), it is assumed that actor A is a parallel actor whose firings require the concurrent use of 2 processing elements of the architecture.

In Figure 2.2, each subfigure illustrates a single source of parallelism. In real schedules, these 4 sources of parallelism are combined in order to fully exploit the parallelism offered by dataflow graphs.

### 2.2.4 Dataflow Models Properties

Research on dataflow modeling leads to the continuing introduction of new dataflow models [JHM04]. New dataflow MoCs are often introduced to fulfill objectives that preexisting models failed to achieve. For example, some dataflow models are introduced with a mathematical formalism that enforces the analyzability of the model [SGTB11]. Other models simply extend the semantics of existing models in order to improve their expressivity and enable the description of a broader range of applications [BB01].

To help the developer of an application select the dataflow MoC that best suits his needs, a set of application and model properties can be used to compare the capabilities of existing dataflow MoCs.

#### **Application properties**

To fully understand the model properties used for comparing dataflow MoCs, some properties of applications when described with dataflow graphs must be in introduced first.

- Schedulability: A dataflow graph is *schedulable* if it is possible to find at least one sequence of actor firings, called a schedule, that satisfies all the firing rules defined in the graph. Depending on the dataflow MoC used to model an application, the schedulability of this application can be checked at compile time or during the execution of the system. A possible cause of non-schedulability for a dataflow graph is the possibility to reach a *deadlock* state where no FIFO contains enough data tokens to initiate a firing of an actor. The non-schedulability of an application can also be caused by external factors such as the lack of sufficient hardware resource to schedule a dataflow graph under a time constraint.

- **Consistency:** A dataflow graph is *consistent* if its execution does not cause an indefinite accumulation of data tokens in one or several FIFOs of the graph. Although in Definition 2.2.1, the FIFOs of a DPN are supposed to be unbounded, in practice, the amount of memory used to execute a DPN is always limited. Hence, if a dataflow graph is *inconsistent*, its execution will eventually generate more data tokens than the available storage capacity.

#### **Dataflow MoCs properties**

The following properties can be used to compare several dataflow MoCs. The presented list of properties is not meant to be an exhaustive list of all the properties used for comparing dataflow MoCs. Indeed, many other terms are used in the literature to compare dataflow MoCs, often with an overlapping meaning with one or several of the properties defined in this list.

- **Decidability:** A dataflow MoC is *decidable* if the schedulability and the consistency of applications described with this model can be proved statically (i.e. at compile-time) [BL06]. Hence, using a decidable dataflow MoC makes it possible to guarantee at compile-time that a dataflow graph will never reach a deadlock state and that its execution will require a finite amount of memory. As presented in [BL06], decidable dataflow MoCs are not Turing complete and may be unable to describe certain applications.

- **Determinism:** A dataflow MoC is *deterministic* if the output of an algorithm only depends on its inputs, but not on external factors such as time or randomness [LP95]. If determinism is a desired feature for most control and DSP applications, non-determinism may also be needed to describe applications reacting to unpredictable inputs [LP95].

- Compositionality: A dataflow MoC is *compositional* if the properties of a dataflow graph described with this MoC are independent from the internal specification of the actors that compose it [Ost95, TBG<sup>+</sup>13]. Compositionality is a desirable feature especially for hierarchical dataflow MoCs where the internal behavior of actors may be specified with a dataflow graph (cf. Section 2.4.2). In hierarchical dataflow MoCs, compositionality guarantees that modifications made to the subgraph of an actor will have no impact on the consistency or the schedulability of graphs in upper levels of hierarchy [TBG<sup>+</sup>13, PBR09, NL04].

- **Reconfigurability:** A dataflow MoC is *reconfigurable* if the firing rules and rates associated to the data ports of its actors can be changed dynamically depending on the application inputs [NL04]. DPN is a reconfigurable MoC since each data port can be associated to a set of firing rules and token rates that are dynamically selected during the application execution, depending on the number and value of available data tokens.

These four properties are predicates that can be used to characterize a dataflow MoC objectively. Indeed, a dataflow MoC is either *deterministic* or *non-deterministic* but cannot be somewhere in between. In addition to these objective properties, several informal properties can be used to compare dataflow MoCs. Although these properties cannot be objectively measured, they are commonly used as arguments for the relative comparison of new dataflow MoCs with existing MoCs.

• **Predictability:** The *predictability* property is related to the *reconfigurability* property of a dataflow MoC. This property evaluates the amount of time between the reconfiguration of the firing rules of an actor and the actual firing of this actor. The *predictability* of a dataflow MoC is inversely proportional to how often the firing rule of an application graph can be reconfigured [NL04].

- **Conciseness:** The *conciseness* (or *succinctness* [SGTB11]) of a dataflow MoC evaluates the ability of a MoC to model an application with a small number of actors. When a graphical interface is used to edit dataflow graphs, conciseness is an important property to limit the size of edited graphs.

- Analyzability: The *analyzability* of a dataflow MoC evaluates the availability of analysis and synthesis algorithms that can be used to characterize application graphs. For example, analysis algorithms can be applied at compile-time to compute the worst-case latency or the maximum memory requirements of a dataflow graph [SGTB11].

- Expressivity: The expressivity, or expressive power of a dataflow MoC evaluates the complexity of application behaviors that can be described with this MoC. For example, the expressivity of the DPN MoC has been proven to be equivalent to a Turing machine [BL93], and can thus be used to describe any application. Specializations of the DPN MoCs often restrict the expressivity of the MoC in order to increase its analyzability and predictability. Expressivity is often mistaken for conciseness. For example, the CSDF MoC is often said to be more expressive than the SDF MoC, but meaning instead that it has a better conciseness (Section 2.3).

The following sections present the semantics and the properties of the dataflow MoCs that will be studied in this thesis. These dataflow MoCs are sorted into two categories depending on their reconfigurability. *Static* MoCs, which are non-reconfigurable MoCs, are presented in Sections 2.3 and 2.4, and *dynamic* MoCs, which are reconfigurable MoCs, are presented in Section 2.5.

# 2.3 Static Dataflow Models of Computation

Static dataflow MoCs are *non-reconfigurable* and *deterministic* MoCs where the sequence of firing rules executed by all actors of a graph is known at compile time [LM87b]. Since the sequence of firing rules of an actor is known *a priori*, the production and consumption rates of an actor never depend on the value of the data tokens processed by the actor. This condition restricts the *expressivity* of static dataflow MoCs. For example, conditional behaviors such as *if-then-else* statements have no equivalent in static dataflow MoCs.

As a counterpart for their restricted *expressivity*, static dataflow MoCs are *decidable* MoCs for which all application graphs can be scheduled at compile-time [LP95].

### 2.3.1 Synchronous Dataflow (SDF)

Synchronous Dataflow (SDF) [LM87b] is the most commonly used static specialization of the DPN MoC. Production and consumption token rates set by firing rules are fixed scalars in an SDF graph. Formally, the SDF MoC is defined as follows:

**Definition 2.3.1.** A Synchronous Dataflow (SDF) graph is a graph  $G = \langle A, F \rangle$  respecting the Dataflow Process Network (DPN) MoC with the following restrictions:

- Each actor  $a \in A$ , with  $a = \langle P_{data}^{in}, P_{data}^{out}, R, rate \rangle$ , is associated to a unique firing rule:  $R = \{R_1\}$

- For each data input port  $p \in P_{data}^{in}$  of an actor, the consumption rate associated to the unique firing rule  $R_1$  of the actor is a static scalar that also gives the number of data tokens that must be available in the FIFO to start the execution of the actor.

• For each data output port  $p \in P_{data}^{out}$  of an actor, the production rate associated to the unique firing rule  $R_1$  of the actor is a static scalar.

In addition to these restrictions, the following simplified notation is introduced.

• rate :  $A \times F \to \mathbb{N}$  is the production or consumption rate of actor  $a \in A$  on FIFO  $f \in F$ . If a is both producer and consumer of f, then rate(a, f) is the difference between the production and the consumption rates on f.

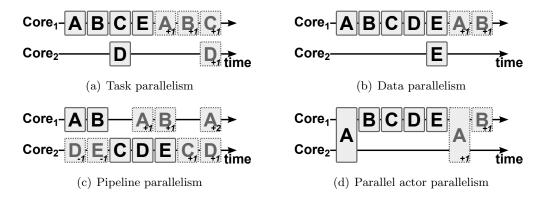

Figure 2.3 illustrates the graphical elements associated to the semantics of the SDF MoC and gives an example of SDF graph.

Figure 2.3: Synchronous Dataflow (SDF) MoC

The popularity of the SDF MoC comes from its great *analyzability*. Indeed, low complexity algorithms have been published to check the *consistency* and *schedulability* of SDF graphs [LM87b], to derive mono-core looped schedules of minimal length [BML96], but also to compute the maximum achievable throughput for the multicore execution of a graph [GGS<sup>+</sup>06].

#### **Consistency and Schedulability**

Checking the *schedulability* and the *consistency* of an SDF graph is a critical step in all dataflow programming frameworks, as it proves the absence of deadlock and the bounded memory requirements of an application.

The method introduced by Lee and Messerschmitt in [LM87b] to verify the *consistency* of an SDF graph is based on a **topology matrix** that characterizes the FIFOs and the *rates* of an SDF graph. The topology matrix is formally defined as follows:

**Definition 2.3.2.** Considering an SDF graph  $G = \langle A, F \rangle$ , the associated topology matrix  $\Gamma$  is a matrix of size  $|F| \times |A|$  such that:

- Each column  $\Gamma_j$  of the matrix is associated to an actor  $a_j \in A$  of G.

- Each row  $\Gamma_i$  of the matrix is associated to a FIFO  $f_i \in F$  of G.

• Matrix coefficient

$$\Gamma_{i,j} = \begin{cases} rate(a_j, f_i) & \text{if } a_j = prod(f_i) \\ -rate(a_j, f_i) & \text{if } a_j = cons(f_i) \\ 0 & \text{otherwise} \end{cases}$$

The topology matrix associated to the SDF graph of Figure 2.3(b) is presented hereafter. The columns and rows of the matrix are labeled with the corresponding actors and **FIFOs** respectively.

$$\Gamma = \begin{array}{ccc} A & B & C & D \\ AB & AC \\ AC \\ BD \\ CD \end{array} \begin{pmatrix} 3 & -1 & 0 & 0 \\ 1 & 0 & -1 & 0 \\ 0 & 0 & 0 & 0 \\ 0 & 2 & 0 & -3 \\ 0 & 0 & 4 & -2 \end{pmatrix}$$

An interesting coefficient in this matrix is the coefficient corresponding to tokens produced and consumed by actor C on FIFO CC. Because actor C produces and consumes the same number of token on this FIFO, the positive and negative rates cancel each other, and the coefficient is set to 0. When an actor possesses a self-loop FIFO, its production and consumption rates on this FIFO should always be equal. Otherwise, tokens will either accumulate indefinitely on this FIFO, or this FIFO will eventually cause a deadlock.

The state of an SDF graph is characterized by the number of data tokens stored in each FIFO, and can be represented by a vector of size |F|. For example, the initial state of the SDF graph of Figure 2.3(b) is:  $state(0) = \begin{pmatrix} 1 & 0 & 2 & 0 & 0 \end{pmatrix}^T$ . Given a state vector state(n), the state resulting from the firing of the  $j^{th}$  actor of the graph can be computed with the following equation:  $state(n+1) = state(n) + \Gamma \cdot e^j$  where  $e^j$  is the  $j^{th}$  canonical basis vector in Euclidean space (the vector with all coefficients equal to 0 but the  $j^{th}$  equal to 1). For example, the state resulting from firing of actor B of the example SDF graph is  $state(1) = state(0) + \Gamma \cdot e^1 = \begin{pmatrix} 0 & 0 & 2 & 2 & 0 \end{pmatrix}^T$ .

**Theorem 2.3.1.** A connected SDF graph  $G = \langle A, F \rangle$  with a topology matrix  $\Gamma$  is consistent if and only if rank $(\Gamma) = |A| - 1$

A non-connected SDF graph is a graph whose actors can be separated in two (or more) groups with no FIFO between actors belonging to different groups. Proving the consistency of a non-connected SDF graph consists of applying Theorem 2.3.1 separately to the connected SDF subgraphs formed by each group of actors.

A proof for Theorem 2.3.1 can be found in [LM87a]. Using Theorem 2.3.1, it is thus possible to prove that the repeated execution of an SDF graph will not result in an infinite accumulation of data tokens on a FIFO of this graph.

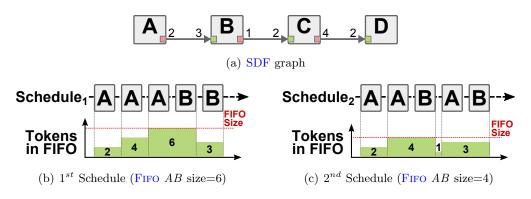

The consistency of an SDF graph implies the existence of a **Repetition Vector (RV)** of size |A|. The integer coefficients of the RV give the minimal number of firings of each actor to return the graph back to its original state. Executing an **iteration** of an SDF graph consists of firing each actor of this graph as many times as given by the RV.

Computing the RV q of a topology matrix  $\Gamma$  consists of finding a positive and integer vector that solves the following equation:  $\Gamma \cdot q = \begin{pmatrix} 0 & \cdots & 0 \end{pmatrix}^T$ . The RV for the SDF graph of Figure 2.3(b) is  $q = \begin{pmatrix} 1 & 3 & 1 & 2 \end{pmatrix}^T$ .

**Theorem 2.3.2.** An *SDF* graph  $G = \langle A, F \rangle$  is schedulable if and only if all following conditions are verified:

- G is consistent

- A sequence of actor firing can be constructed such that:

- each actor is fired as many times as required in the Repetition Vector (RV).

- the firing rule of each actor is respected: enough data tokens are available to start each firing of the sequence.

The existence of the RV (i.e. the consistency) is not a sufficient condition to guarantee the schedulability of an application. For example in Figure 2.3(b), if there were no initial data token in the self-loop FIFO of actor C, the graph would still be consistent, since the topology matrix does not depend on delays, but it would never be possible to fire actor C.

In [BELP96], Bilsen et al. propose an algorithm to build a sequence of actor firings that verifies the second condition of Theorem 2.3.2. If the algorithm fails, the SDF cannot be executed without reaching a deadlock. An example of valid sequence of actor firings for the SDF graph of Figure 2.3(b) is: B, A, B, D, C, B, D.

It is important to note that *consistency* and *schedulability* of an SDF graph can be checked without any information on the actual hardware architecture executing the application.

## 2.3.2 Single-Rate SDF, Homogeneous SDF, and Directed Acyclic Graph

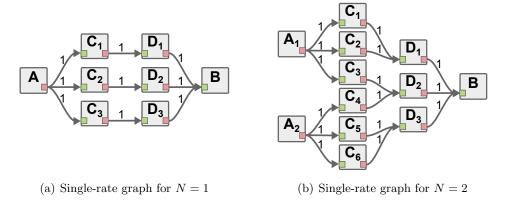

The single-rate SDF MoC is a specialization of the SDF MoC defined as follows:

**Definition 2.3.3.** A single-rate SDF graph is an SDF graph where the production and consumption values on each F IFO are equal. Formally:

$$\forall f \in F, rate(prod(f), f) = rate(cons(f), f)$$

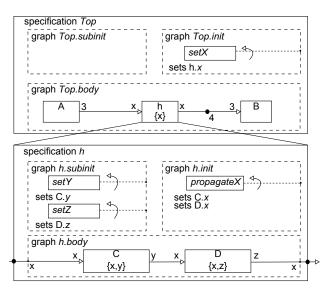

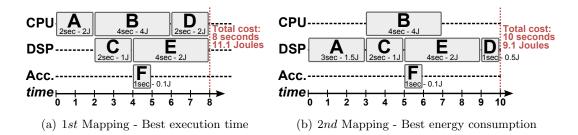

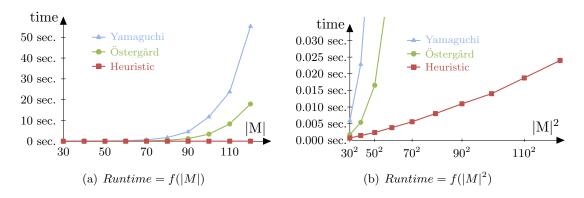

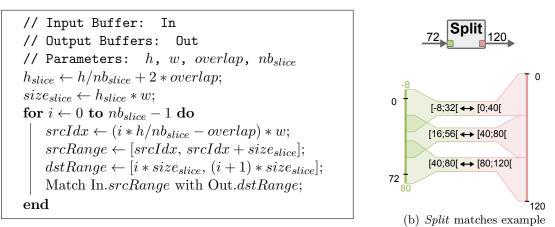

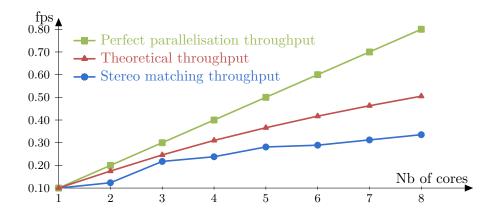

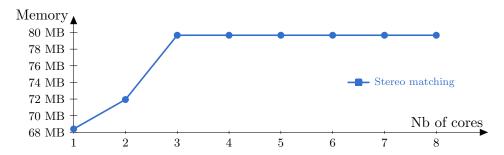

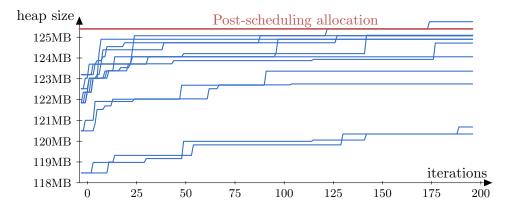

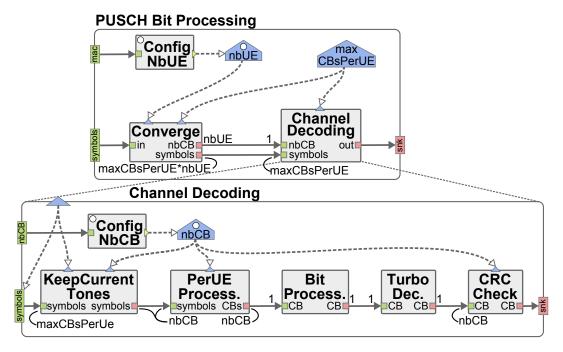

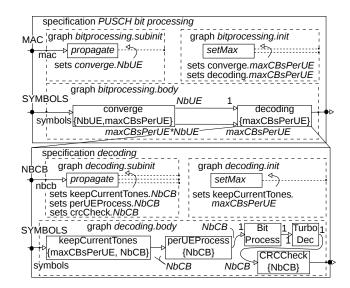

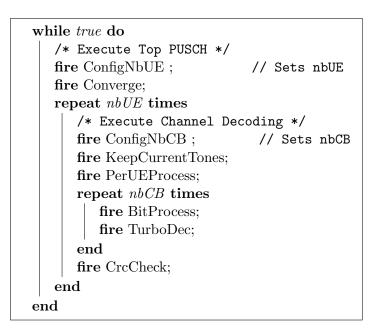

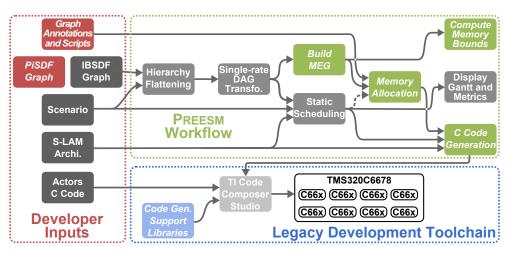

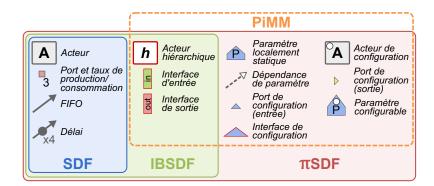

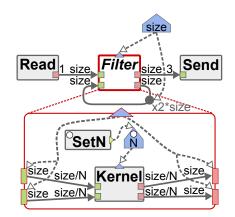

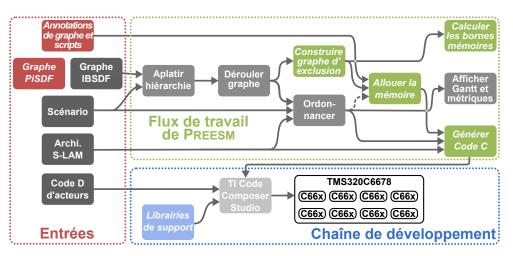

The single-rate SDF MoC has the same *expressivity* as the SDF MoC. Consequently, for all consistent SDF graphs, there exists an equivalent single-rate SDF graph.