## Conducted EMC modeling and EMI filter design integrated class-D amplifiers and power converters

Roberto Mrad

#### ▶ To cite this version:

Roberto Mrad. Conducted EMC modeling and EMI filter design integrated class-D amplifiers and power converters. Other. Ecole Centrale de Lyon, 2014. English. NNT: 2014ECDL0019. tel-01127319

## HAL Id: tel-01127319 https://theses.hal.science/tel-01127319

Submitted on 7 Mar 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Thèse de l'Université de Lyon

Délivrée par l'Ecole Centrale de Lyon

Spécialité : Energie et Systèmes

Soutenue publiquement le 30 Juin 2014

Par

#### Roberto Mrad

Préparée aux Laboratoires Ampère et INL Financée par la société ST Microelectronics

## Conducted EMC Modeling and EMI Filter Design for Integrated Class-D Amplifiers and Power Converters

#### **Ecole Doctorale**

Electronique, Electrotechnique, Automatique

#### Jury

Rapporteur Flavio Canavero Professeur (Politecnico di Torino) Rapporteur Jean-Luc Schannen Professeur (ENSE<sup>3</sup>, Grenoble) Examinateur **Etienne Sicard** Professeur (INSA, Toulouse) Directeur de thèse Christian Vollaire Professeur (Ecole Centrale de Lyon) Encadrant Florent Morel Maitre de conférences (Ecole Centrale de Lyon) Encadrant Gaël Pillonnet Chercheur (CEA, Grenoble) Invité Angelo Nagari Ingénieur (ST Microelectronics, Grenoble) Invité Bertrand Lacombe Ingénieur (SAFRAN Sagem, Massy)

## Abstract

Ecole Centrale de Lyon Doctor of Philosophy

## Conducted EMC Modeling and EMI Filter Design for Integrated Class-D Amplifiers and Power Converters

by Roberto MRAD

## English:

Switching power management circuits are widely used in battery powered embedded applications in order to increase their autonomy. In particular, for audio applications, Class-D amplifiers are a widespread industrial solution. These, have a similar architecture of a buck converter but having the audio signal as reference. The switching nature of these devices allows us to increase significantly the power efficiency compared to linear audio amplifiers without reducing the audio quality. However, because of the switching behavior, Class-D amplifiers have high levels of electromagnetic (EM) emissions which can disturb the surrounding electronics or might not comply with electromagnetic compatibility (EMC) standards. To overcome this problem much architecture appeared in the state of the art that reduces the emissions, however, this has never been enough to remove electromagnetic interference (EMI) filters. It is then useful to optimize these filters, thus, it has been set as the goal of this PhD thesis. The latter has been divided to four main axes which can be resumed by the following.

First, this work started by developing a frequency domain modeling method in order to simulate and predict the EMI of Class-D amplifiers in the final application. The method is based on system to block decomposition and impedance matrix modeling and manipulation. After providing all the theoretical background, the

method has been validated on integrated differential Class-D amplifier. The experimental measurements have permitted to validate the method only up to  $100\,MHz$ . However, this is sufficient to cover the conducted EMC frequency band.

Second, the EMI at the supply rails of Class-D amplifiers has been treated. As the battery is often the same power supply for all applications in an embedded system, an EMI filter or a decoupling capacitor is needed to prevent the noise coupling by common impedance. Designing this filter needs the knowledge of the battery impedance at the desired frequencies. Therefore the present work dealt also with measuring the high frequency impedance of a battery. Afterwards, an experimental validation has been carried on with a DC-DC converter and a Class-D amplifier.

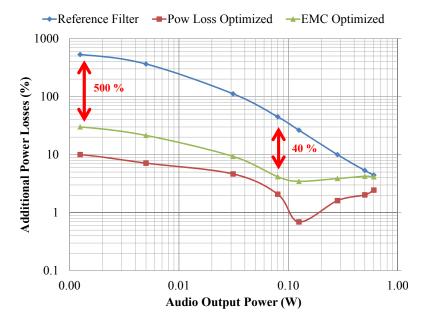

The developed model allows a virtual test of the switching device in the final application. However, it is more useful if the model is able to help the system integrator in designing filters. Thus, third, the model has been implemented in an optimization loop based on a genetic algorithm in order to optimize the filter response, and also, reduce the additional power losses introduced by an EMI filter. The optimization search space has been limited to the components available on the market and the optimization result is given as component references of the optimal filter referring to the optimal solution found. This procedure has been validated experimentally.

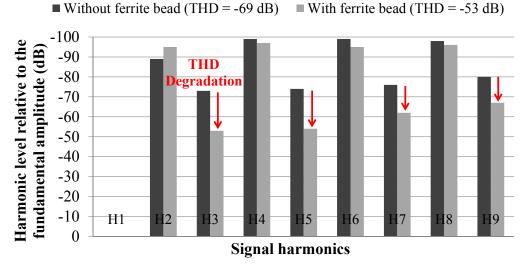

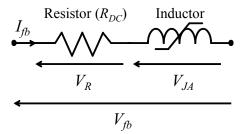

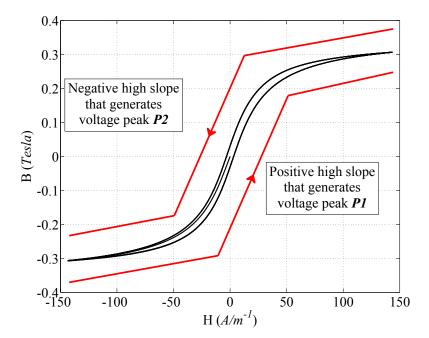

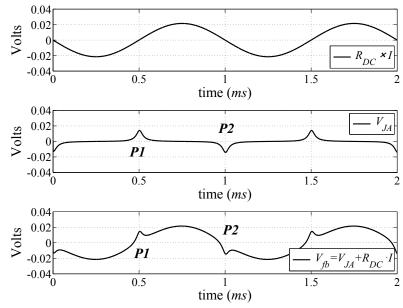

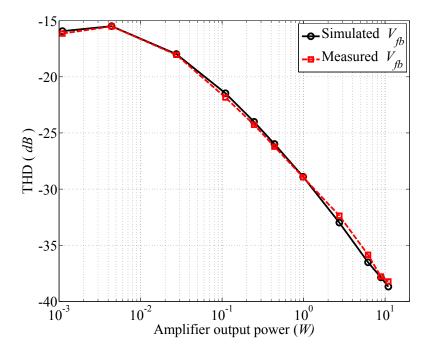

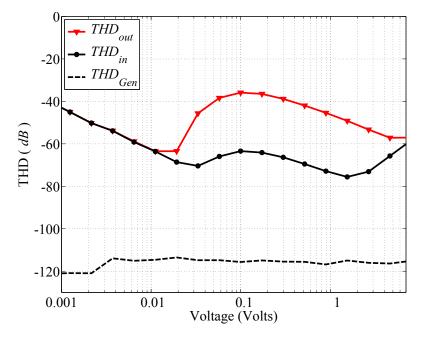

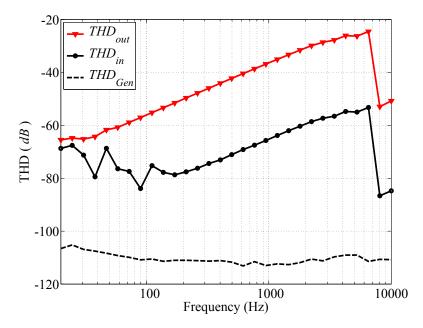

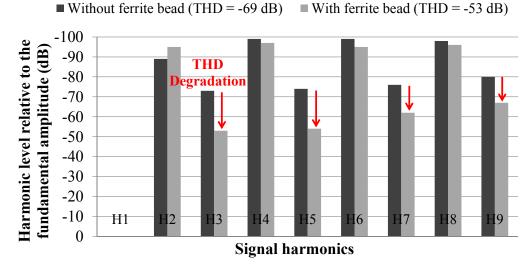

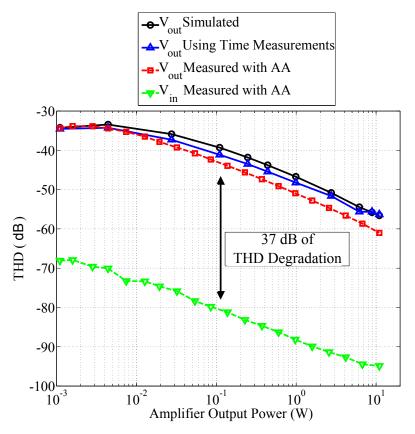

Finally, EMI filters often are constituted by magnetic components such as ferrite beads or inductors with magnetic cores. Thus, introducing the EMI filter in the audio path, adds a nonlinear behavior in the audio frequency band. Designing a high quality EMI filter require taking into account this phenomenon and studying its impact of the original amplifier audio performance. Therefore, the Jiles-Atherton model for magnetic materials has been used for ferrite bead modeling. Hereafter, the impact on the time and frequency domain signals has been simulated and compared to measurements. Finally, the total harmonic distortion (THD) has been computed for different signal amplitudes and compared to the THD measured using an audio analyzer. Accurate results have been obtained on a wide range of signal amplitudes.

As a conclusion, this work aimed to design optimal EMI filters for Class-D amplifiers. Thus, we dealt with improving their EMI response, reducing their additional power losses and evaluating their impact on the audio quality.

## Français:

Les convertisseurs de puissance sont largement utilisés de nos jours dans des applications qui demandent une grande autonomie énergétique, comme par exemple ceux qui sont alimentés par des batteries. En particulier, les amplificateurs de type Class-D sont fréquemment utilisés dans les applications audio. Ces amplificateurs commutés ont une architecture ressemblante à celle d'un convertisseur DC-DC, ce qui les permet d'avoir une efficacité énergétique élevée. Cependant, leur inconvénient majeur est la forte émission en perturbations électromagnétiques (EM). Cela peut causer des problèmes de conformité avec les normes de compatibilité électromagnétique (CEM), ou bien perturbé le bon fonctionnement des applications électroniques qui l'entour. Pour cela, ils existent de nombreuses études qui permettent de réduire les émissions d'un amplificateur de Class D. Cependant, cela n'est pas suffisant pour retirer le filtre de CEM. Il est donc nécessaire d'optimisé ces filtres et de faciliter leurs conceptions. Ceci est le but de la présente thèse et il est divisé en quatre grandes parties.

La première partie commence par développer une technique de modélisation dans le domaine fréquentiel. Cette technique qui est basée sur la détermination et la manipulation des matrices d'impédances a comme but de simuler et prédire les perturbations EM générés par un amplificateur de Class D. Tous les aspects théoriques de la méthode ont été développés. Ensuite, une application pratique sur un système de Class D dédié à la téléphonie mobile nous a permis de valider la méthode jusqu'à une fréquence de 100 MHz.

Un amplificateur de Class D est une source de perturbation aussi bien sur les rails d'alimentation que sur les rails de sortie. Pour cela, le filtre de CEM est nécessaire sur les rails de l'alimentation comme il y est en sortie. Néanmoins, un filtre correctement construit doit être conçu en prenant en compte l'impédance de la charge qui est la batterie dans ce cas. Pour cela, la deuxième partie a pour objectif la mesure de l'impédance de la batterie sur la gamme de fréquence considérée. Ainsi, une technique de mesure d'impédance de batterie en utilisant un impédance mètre est développée. Ensuite, une application expérimentale sur un convertisseur DC-DC et une batterie nous a permis de valider la procédure de mesure.

La troisième partie s'est focalisée sur l'optimisation du filtre de CEM. Le modèle fréquentiel développé dans la première partie est intégré dans une boucle d'optimisation

basée sur un algorithme génétique. L'optimisation inclus plusieurs critères dans sa fonction objective qui sont l'augmentation de la capacité du filtre à réduire les émissions EM, la diminution des pertes supplémentaire due à l'utilisation du filtre et finalement le gain du filtre dans la bande de fréquence du signal audio. Cette étude est poursuivie par une validation expérimentale.

La quatrième et la dernière partie étudie et quantifie les impacts du filtre de CEM sur la qualité audio de l'amplificateur. En effet, le filtre de CEM est l'un des chemins propagation du signal audio. Par suite, tout comportement non linéaire du filtre conduit à la distorsion du signal audio. Pour cela, cette partie est dédiée à la modélisation et la simulation des composants passifs contenant un matériau magnétique. En particulier, l'étude s'est focalisée sur la modélisation des perles de ferrite en utilisant le modèle de matériaux magnétiques Jiles-Aterthon. Les résultats de simulations sont comparés avec la mesure dans le domaine temporel et fréquentiel. En plus, le calcul du taux de distorsion harmonique nous a permis de valider le modèle sur une large plage d'amplitude.

## Contents

| A            | bstra      | act                                             |  |   | ii                     |

|--------------|------------|-------------------------------------------------|--|---|------------------------|

| $\mathbf{C}$ | ontei      | nts                                             |  |   | vi                     |

| Li           | ist of     | Figures                                         |  |   | xi                     |

| Li           | ist of     | Tables                                          |  |   | $\mathbf{x}\mathbf{v}$ |

| A            | bbre       | viations                                        |  | 3 | cvii                   |

| 1            | Inti       | $\operatorname{roduction}$                      |  |   | 1                      |

|              | 1.1        | EMC, definition and concern                     |  |   | 2                      |

|              | 1.2        | Problem background                              |  |   | 3                      |

|              | 1.3        | Objectives and scope of thesis                  |  |   | 5                      |

|              |            | 1.3.1 Scientific objectives                     |  |   | 5                      |

|              |            | 1.3.2 Company objectives                        |  |   | 6                      |

|              | 1.4        | Thesis structure                                |  |   | 6                      |

| 2            | Cla        | ss-D Amplifiers from the EMC Point of View      |  |   | 9                      |

|              | 2.1        | Class-D amplifier basics                        |  |   | 9                      |

|              |            | 2.1.1 Power stages                              |  |   | 10                     |

|              |            | The single ended power stage [21, 22]:          |  |   | 10                     |

|              |            | The differential power stage [16, 23]:          |  |   | 10                     |

|              |            | 2.1.2 Modulations                               |  |   | 12                     |

|              |            | 2.1.2.1 The Pulse Width Modulation (PWM)        |  |   | 12                     |

|              |            | 2.1.2.2 PWM for differential Class-D amplifiers |  |   | 14                     |

|              |            | Binary modulation:                              |  |   | 14                     |

|              |            | Ternary modulation:                             |  |   |                        |

|              | 0.0        | 2.1.2.3 Self oscillating modulation             |  |   |                        |

|              | 2.2        | EM emission of Class-D amplifiers               |  |   | 18                     |

|              |            | 2.2.1 EMI at the output rails                   |  |   | 18                     |

|              |            | 2.2.2 EMI at the supply rails                   |  |   | 20<br>22               |

|              | <b>9</b> 9 | 2.2.3 EMC solutions                             |  |   |                        |

|              | 2.3        | Onaracterizing a Class-D ambilher               |  |   | 24                     |

Contents viii

|   | 2.4                    | Summa    | ary                                                         | 24 |

|---|------------------------|----------|-------------------------------------------------------------|----|

| 3 | $\mathbf{E}\mathbf{M}$ | I Mode   | eling of Class-D Audio Amplifier                            | 27 |

|   | 3.1                    | Time d   | lomain simulations                                          | 27 |

|   | 3.2                    | Freque   | ncy domain modeling                                         | 28 |

|   | 3.3                    | Propos   | sed frequency domain modeling                               | 30 |

|   |                        | 3.3.1    | Active blocks model                                         | 31 |

|   |                        | 3.3.2    | Passive block types and models                              | 32 |

|   |                        | 3.3.3    | Impedance matrix determination                              | 33 |

|   |                        |          | 3.3.3.1 Impedance matrix determination by impedance an-     |    |

|   |                        |          | alyzer                                                      | 34 |

|   |                        |          | 3.3.3.2 Impedance matrix determination by VNA               | 35 |

|   |                        |          | 3.3.3.3 Impedance matrix determination by simulation        | 35 |

|   |                        | 3.3.4    | Impedance matrix association                                | 35 |

|   |                        |          | 3.3.4.1 Association of 2 Type A blocks                      | 36 |

|   |                        |          | 3.3.4.2 Type A and Type B blocks association                | 37 |

|   |                        | 3.3.5    | Currents and voltages computation                           | 37 |

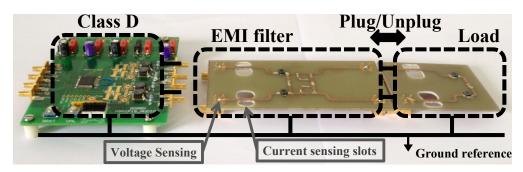

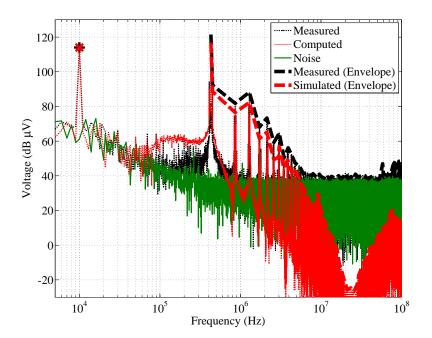

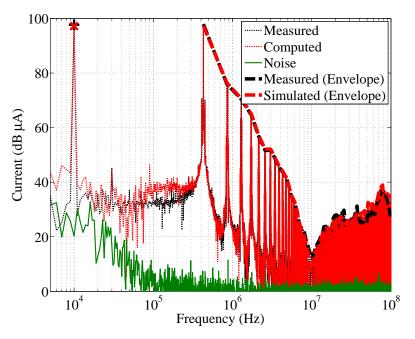

|   | 3.4                    | Experi   | mental application on a Class-D amplifier – Output side     | 39 |

|   |                        | 3.4.1    | Instrumentation used                                        | 40 |

|   |                        | 3.4.2    | Class-D amplifier modeling                                  | 42 |

|   |                        | 3.4.3    | Filter impedance matrix determination                       | 43 |

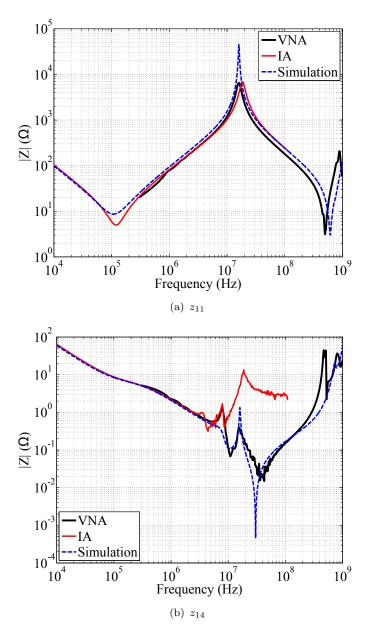

|   |                        |          | 3.4.3.1 Filter impedance matrix determination using an IA   | 43 |

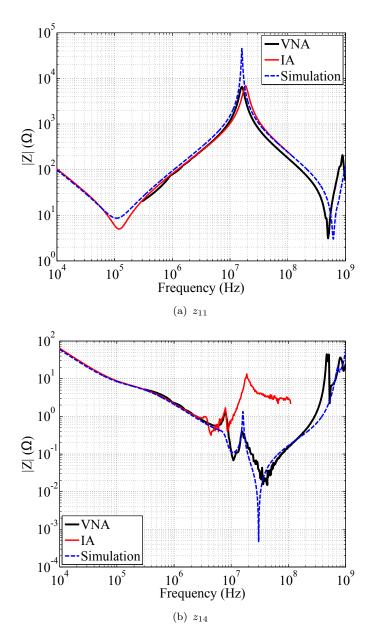

|   |                        |          | 3.4.3.2 Filter impedance matrix determination using a VNA   | 44 |

|   |                        |          | 3.4.3.3 Filter impedance matrix determination by simulation | 44 |

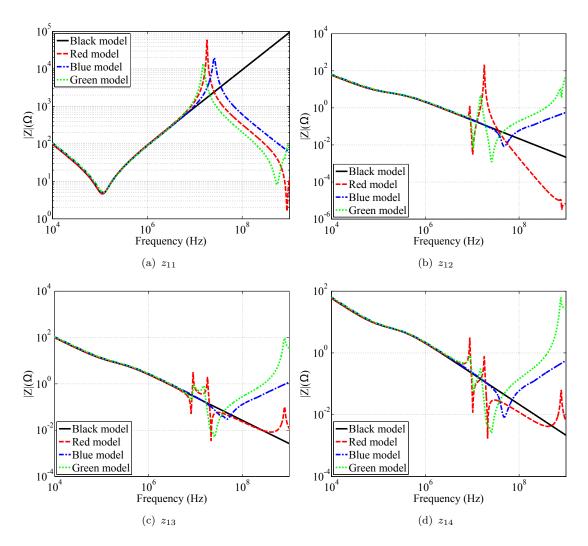

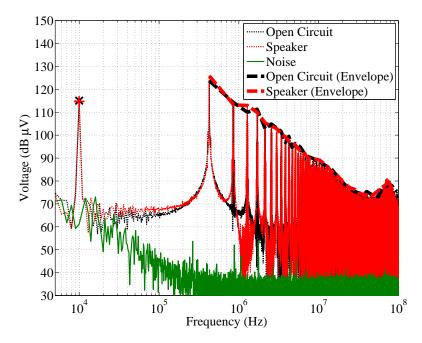

|   |                        |          | 3.4.3.4 Comparison between IA, VNA and ADS simulation       | 44 |

|   |                        | 3.4.4    | Load impedance matrix                                       | 46 |

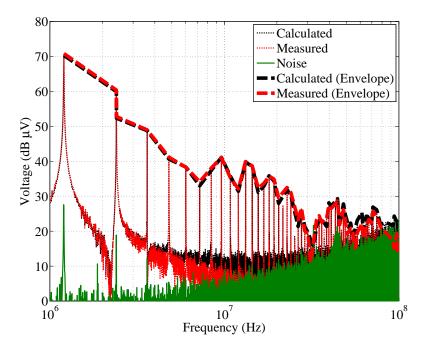

|   |                        | 3.4.5    | Currents and voltages computation                           | 47 |

|   | 3.5                    | Experi   | mental application on a Class-D amplifier – Supply side     | 50 |

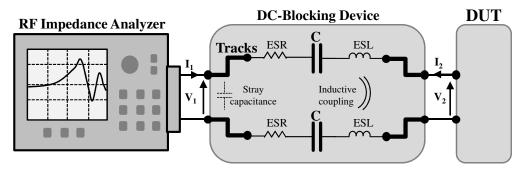

|   |                        | 3.5.1    | Measurement techniques for batteries                        | 51 |

|   |                        | 3.5.2    | Battery impedance measurement with an IA                    | 53 |

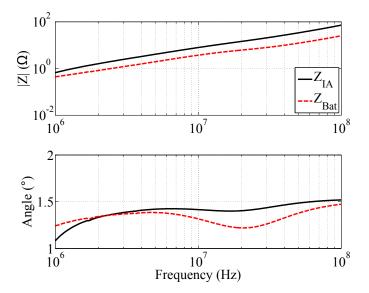

|   | 3.6                    | Validat  | tion example using a battery and a power converter          | 55 |

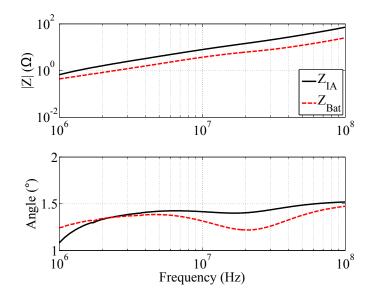

|   |                        | 3.6.1    | Battery impedance                                           | 55 |

|   |                        | 3.6.2    | Voltage computation and battery impedance verification      | 57 |

|   | 3.7                    | Chapte   | er conclusion                                               | 58 |

| 4 | $\mathbf{E}\mathbf{M}$ | I Filter | Design Using a Discrete Optimization Algorithm              | 61 |

|   | 4.1                    | State o  | of the art of EMI filter design                             | 62 |

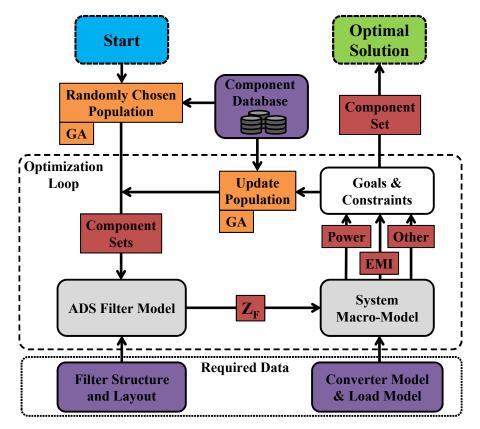

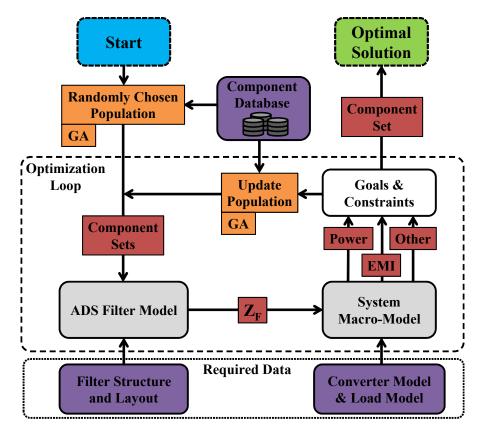

|   | 4.2                    | Propos   | sed filter design methodology                               | 63 |

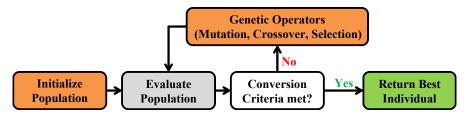

|   |                        | 4.2.1    | Optimization algorithm                                      | 63 |

|   |                        |          | 4.2.1.1 Choice of algorithm                                 | 63 |

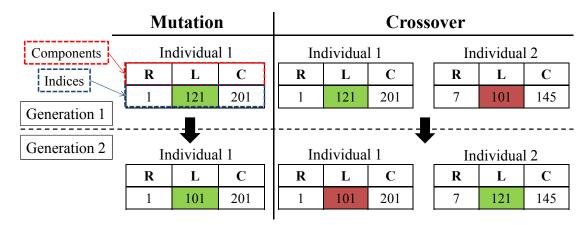

|   |                        |          | 4.2.1.2 Operators                                           | 64 |

|   |                        | 4.2.2    | Optimization process                                        | 65 |

|   | 4.3                    | Applica  | ation to Class-D amplifier                                  | 67 |

|   |                        |          | EMI filter and passive components                           | 67 |

Contents

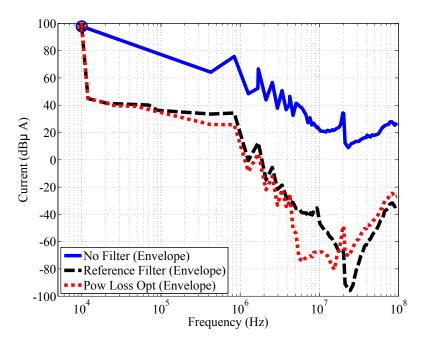

|              |     | 4.3.2 Power losses in Class-D amplifiers due to the EMI filter 68 |

|--------------|-----|-------------------------------------------------------------------|

|              |     | 4.3.3 Optimization formulation for Class-D amplifiers 70          |

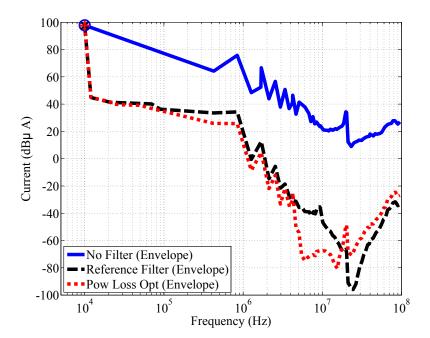

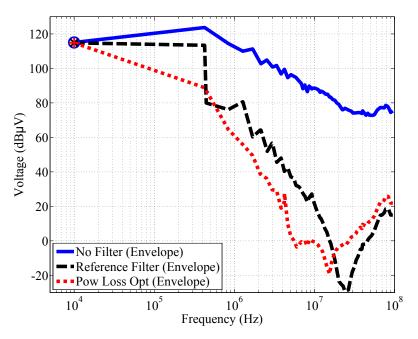

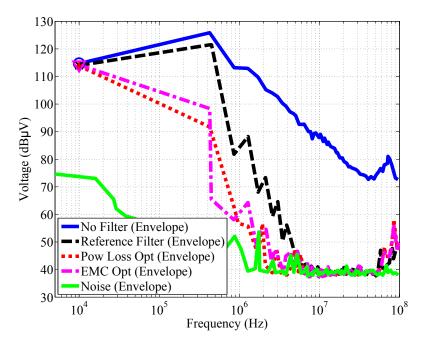

|              |     | 4.3.3.1 Formulation I: Power-loss optimization 70                 |

|              |     | 4.3.3.2 Formulation II: EMI optimization                          |

|              | 4.4 | Experimental Validation                                           |

|              | 4.5 | Chapter conclusion                                                |

| 5            | Imp | eact of the EMI Filter on the Amplifier Base-Band 85              |

|              | 5.1 | Ferrite beads and Class-D amplifiers                              |

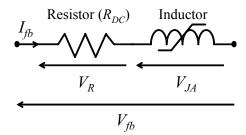

|              | 5.2 | Ferrite bead modeling                                             |

|              |     | 5.2.1 Jiles - Atherton model                                      |

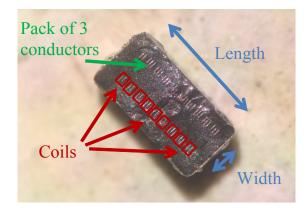

|              |     | 5.2.2 Physical architecture modeling 89                           |

|              | 5.3 | Measurements and validation                                       |

|              |     | 5.3.1 Measurements                                                |

|              |     | 5.3.2 Component parameter extraction                              |

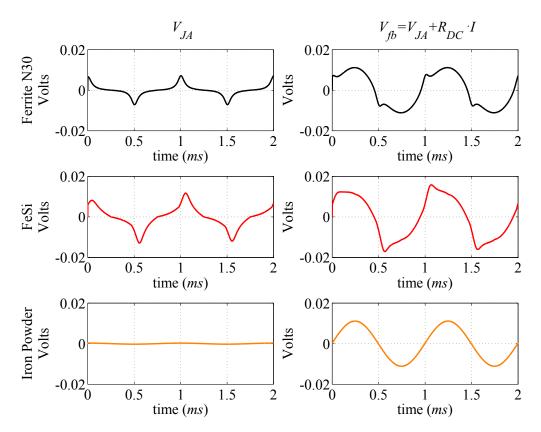

|              |     | 5.3.3 Time domain comparison                                      |

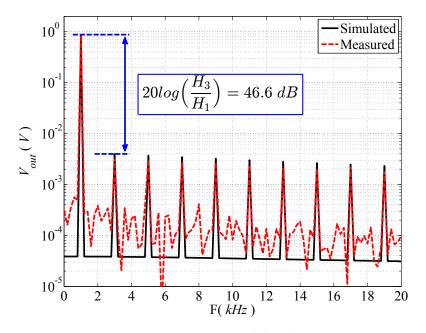

|              |     | 5.3.4 Frequency domain comparison                                 |

|              |     | 5.3.5 THD comparison                                              |

|              | 5.4 | Simulating different magnetic materials in ferrite beads          |

|              | 5.5 | Chapter conclusion                                                |

| 6            | Cor | aclusion & Perspectives 105                                       |

|              | 6.1 | General conclusion                                                |

|              | 6.2 | Perspectives                                                      |

|              |     | 6.2.1 Speed of edge and EMI filters                               |

|              |     | 6.2.2 Filter structure optimization and area on PCB reduction 108 |

|              |     | 6.2.3 On-chip coupling in differential Class-D amplifiers 108     |

|              |     | 6.2.4 Investigating the Schottky for free-wheeling diodes 111     |

|              | 6.3 | Evaluating ferrite beads with a switching amplifier               |

|              |     | 8                                                                 |

|              |     |                                                                   |

| A            | Def | initions 133                                                      |

|              |     | Total Harmonic Distortion:                                        |

|              |     | Signal to Noise Ratio:                                            |

|              |     | Power Supply Rejection Ratio:                                     |

|              |     | The audio gain                                                    |

| $\mathbf{B}$ | App | pendix of Chapter 3: Proofs 135                                   |

|              | B.1 | Proof of equation (3.5)                                           |

|              | B.2 | Proof of equation (3.8)                                           |

|              | B.3 | Proof of equation (3.9)                                           |

|              | B.4 | Proof of equation (3.11)                                          |

|              | B.5 | Proof of equation (3.13)                                          |

Contents

| $\mathbf{C}$ | App  | endix   | of Chapter 3: Additional Measurements and Simula            | <b>!</b> - |

|--------------|------|---------|-------------------------------------------------------------|------------|

|              | tion |         |                                                             | 141        |

|              | C.1  |         | O amplifier transient simulation                            |            |

|              | C.2  | EMI co  | omputation for a Class-D amplifier powered by a battery     | . 143      |

| D            | App  | endix   | of Chapter 3: Speaker Impedance                             | 147        |

|              | D.1  | Unders  | standing the speaker impedance matrix                       | . 147      |

|              | D.2  | Speake  | er impedance measurements under temperature variations      | . 149      |

| $\mathbf{E}$ |      | endix   | of Chapter 5: THD Measurements on a Linear Ampli            |            |

|              | fier |         |                                                             | 151        |

| $\mathbf{F}$ | Frer | nch Re  | port - Summarized Version                                   | 155        |

|              | F.1  | Introdu | $\operatorname{action}$                                     |            |

|              |      | F.1.1   | Objectifs de la thèse                                       |            |

|              |      |         | F.1.1.1 Objectifs scientifiques                             |            |

|              |      |         | F.1.1.2 Objectifs industriels                               |            |

|              |      | F.1.2   | Structure du rapport                                        |            |

|              | F.2  |         | ses et la CEM des amplificateurs de Classe D                |            |

|              |      | F.2.1   | Étage de puissance                                          |            |

|              |      | F.2.2   | Modulation                                                  |            |

|              |      | F.2.3   | MLI différentielle                                          |            |

|              |      | F.2.4   | Emission EM d'un amplificateur de Classe D                  |            |

|              | По   | F.2.5   | Caractérisation d'un amplificateur de Classe D              | . 164      |

|              | F.3  |         | sation des amplificateurs de Classe D du point de vue de la | 164        |

|              |      | F.3.1   | Identification des paramètres du modèle                     |            |

|              |      | F.3.2   | Association de matrices d'impédances                        |            |

|              |      | F.3.3   | Calcul des spectres de tensions et de courants              |            |

|              |      | F.3.4   | Validation expérimentale avec un amplificateur de Classe D  |            |

|              |      | F.3.5   | Détermination du modèle des différentes parties du système  |            |

|              |      | F.3.6   | Exemple de validation sur une batterie et un convertisseur  | 111        |

|              |      | 1 .0.0  | DC-DC                                                       | . 173      |

|              | F.4  | Optim   | isation discrète du filtre CEM                              |            |

|              |      | F.4.1   | Méthodologie de design du filtre                            |            |

|              |      | F.4.2   | Processus d'optimisation                                    |            |

|              |      | F.4.3   | Application à un amplificateur de Classe D                  |            |

|              |      | F.4.4   | Formulations pour le processus d'optimisation               |            |

|              |      | F.4.5   | Validation expérimentale                                    |            |

|              | F.5  |         | du filtre de CEM sur le signal audio de l'amplificateur     |            |

|              |      | F.5.1   | Modélisation d'une perle de ferrite                         |            |

|              |      | F.5.2   | Application expérimentale                                   |            |

|              | F.6  | Conclu  | sion                                                        |            |

| $\mathbf{G}$ | List | of Pul  | blications                                                  | 191        |

## List of Figures

| 1.1               | PCB of a modern smart-phone                                               |

|-------------------|---------------------------------------------------------------------------|

| 1.2               | Product development and noise reduction [5]                               |

| 1.3               | A Class-D amplifier and its dedicated EMI filter in the final appli-      |

|                   | cation.                                                                   |

| 2.1               | A block diagram of an open loop Class-D audio amplifier                   |

| $\frac{2.1}{2.2}$ |                                                                           |

|                   | Single ended power stage.                                                 |

| 2.3               | H-Bridge power stage.                                                     |

| 2.4               | PWM modulation.                                                           |

| 2.5               | Spectrum of a PWM signal.                                                 |

| 2.6               | Basic architecture of a Class-D amplifier [24]                            |

| 2.7               | H-Bridge binary modulation                                                |

| 2.8               | H-Bridge ternary modulation.                                              |

| 2.9               | Ternary modulation output spectrum                                        |

| 2.10              | Architecture of a differential Class-D amplifier                          |

|                   | Basic architecture of a self oscillating Class-D amplifier                |

| 2.12              | Self oscillating Class-D amplifier output spectrum                        |

| 2.13              | Frequency content of a Class-D amplifier                                  |

| 2.14              | EMI emissions at the supply level                                         |

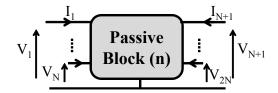

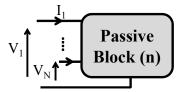

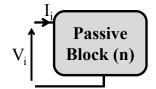

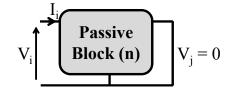

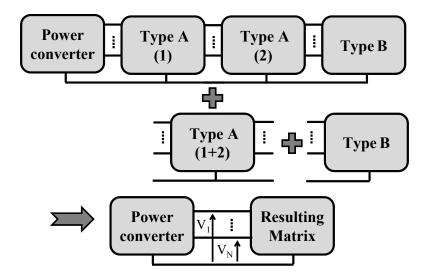

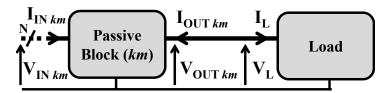

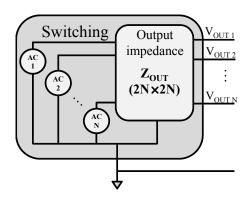

| 3.1               | System decomposition into blocks                                          |

| 3.2               | Active block model                                                        |

| 3.3               | Type $A: 2N+1$ ports                                                      |

| 3.4               | Type $B: N+1$ ports                                                       |

| 3.5               | $Z_{ii}$ measurements                                                     |

| 3.6               | $Z_{ij_{sc}}$ measurements                                                |

| 3.7               | Block association technique                                               |

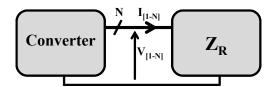

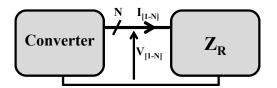

| 3.8               | Current computation at the converter output                               |

|                   |                                                                           |

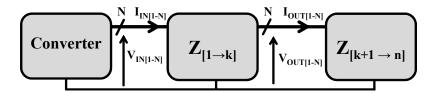

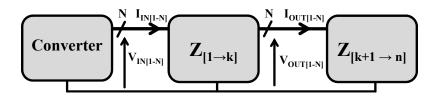

| 3.9               | Currents and voltages computation at a given node after the block named k |

| 9 10              |                                                                           |

| 3.10              |                                                                           |

| 3.11              | ·                                                                         |

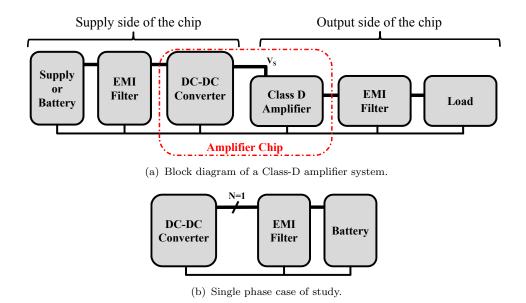

|                   | Class-D amplification system.                                             |

|                   | Current probe equivalent circuit.                                         |

|                   | Amplifier output voltage $V_{+}$ for two different load conditions        |

List of Figures xii

| 3.15 | Impedance matrix elements of the models in Table 3.3 using ADS     |

|------|--------------------------------------------------------------------|

|      | simulation                                                         |

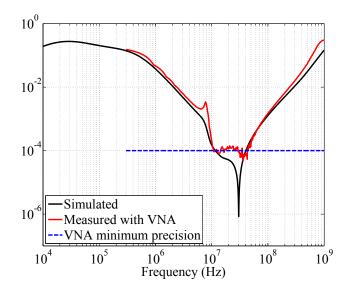

| 3.16 | Filter impedance results                                           |

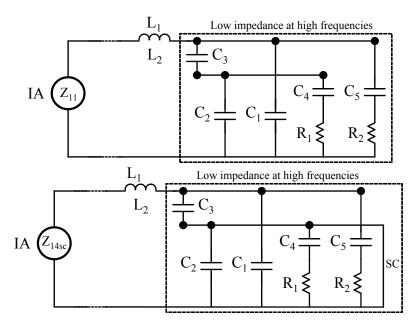

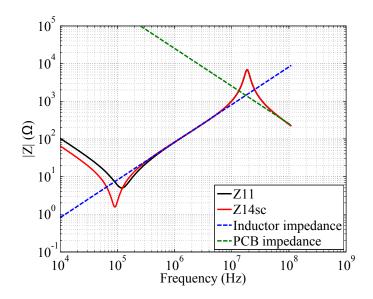

|      | $z_{11}$ and $z_{14_{sc}}$ impedances seen by the IA               |

|      | Filter: Measured $z_{11}$ and $z_{14_{sc}}$ with an IA             |

|      | Filter: VNA minimum precision seen in $s_{14}$                     |

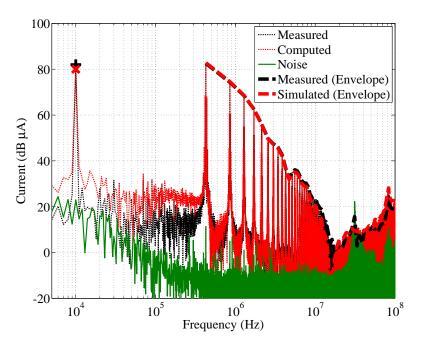

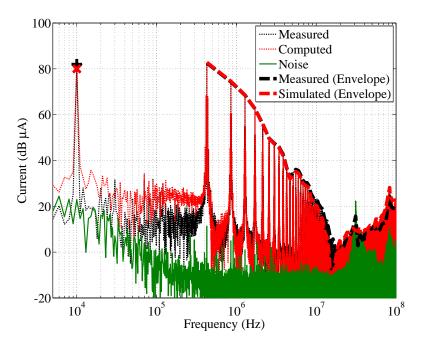

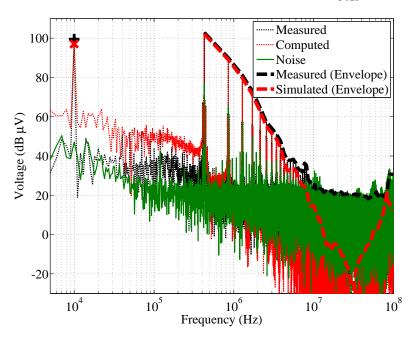

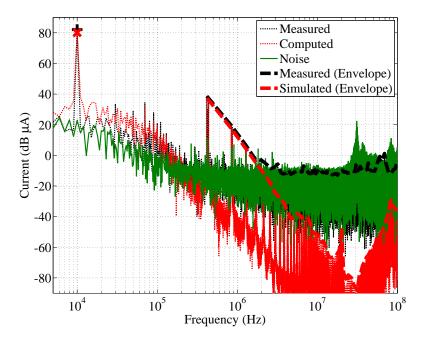

| 3.20 | Input current of the filter $I_{IN_{Plus}}$                        |

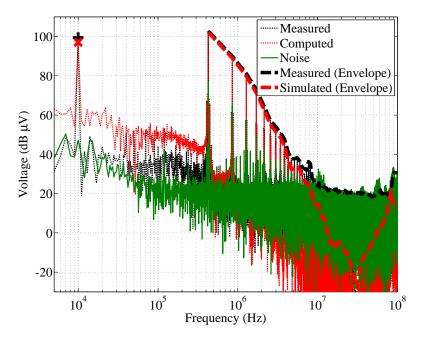

| 3.21 | Output voltage of the filter $V_{OUT_{Plus}}$                      |

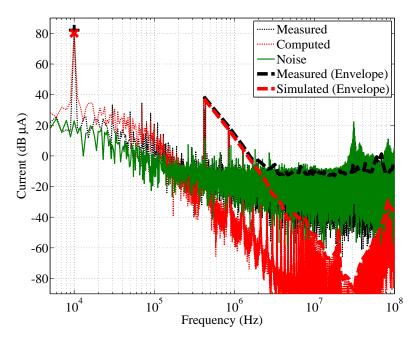

| 3.22 | Output current of the filter $I_{OUT_{Plus}}$                      |

| 3.23 | Class-D amplification system                                       |

| 3.24 | Measurement set-up principle                                       |

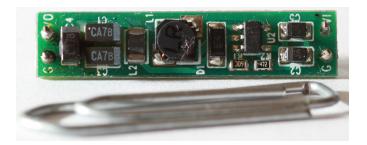

| 3.25 | DC-DC converter used for the experimental validation placed near   |

|      | to a paper clip                                                    |

| 3.26 | Battery impedance measurement                                      |

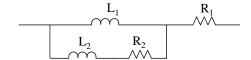

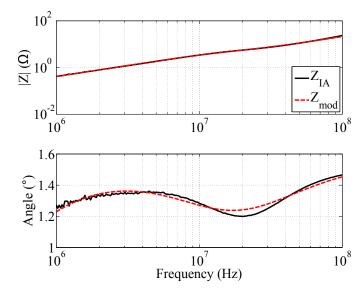

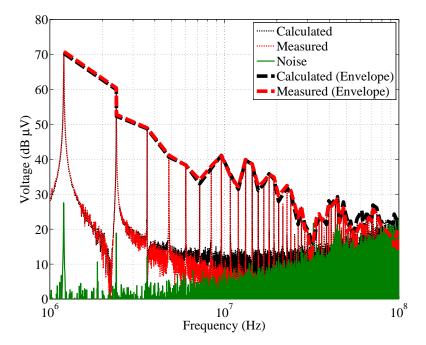

|      | Battery impedance model                                            |

| 3.28 | Battery model results                                              |

| 3.29 | Magnitude of the battery voltage FFT when feeding the SMPS         |

| 4.1  |                                                                    |

| 4.1  | General diagram of a GA                                            |

| 4.2  | Mutation and crossover examples                                    |

| 4.3  | Optimization application.                                          |

| 4.4  | Class-D amplifier losses due to the EMI filter                     |

| 4.5  | Output current in the power loss optimization case                 |

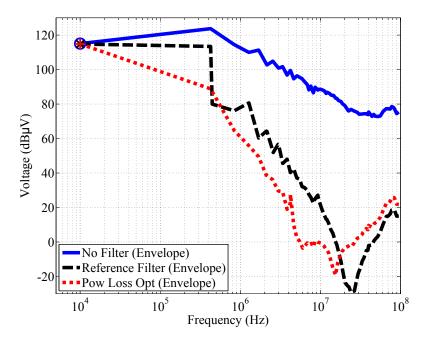

| 4.6  | Output voltage in the power loss optimization case                 |

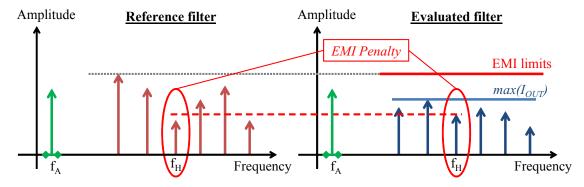

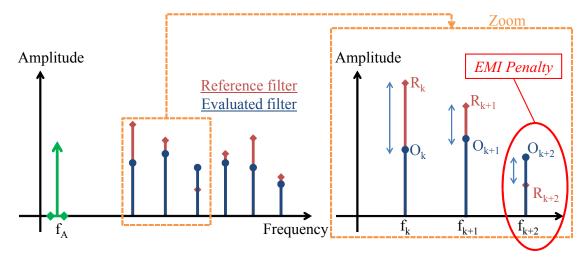

| 4.7  | Calculation of the EMI criterion.                                  |

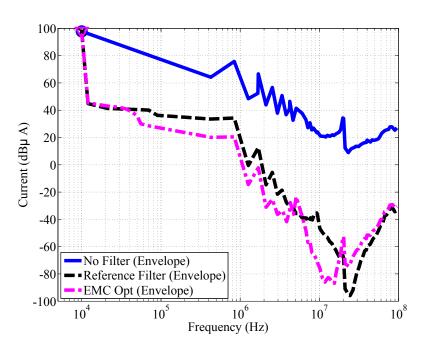

| 4.8  | Output current in the EMI optimization case                        |

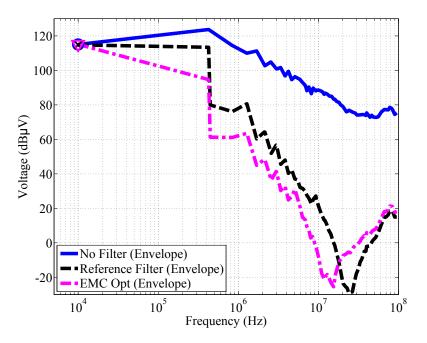

| 4.9  | Output voltage in the EMI optimization case                        |

| 4.10 | Another way for calculating the EMI criterion                      |

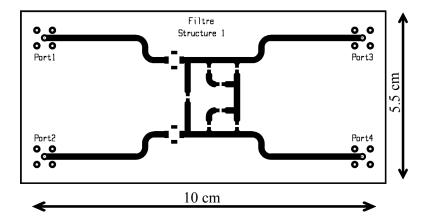

|      | Filter layout.                                                     |

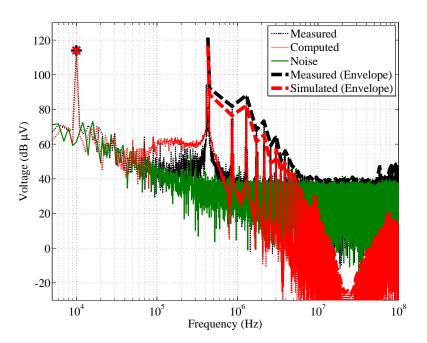

|      | Filter output voltage                                              |

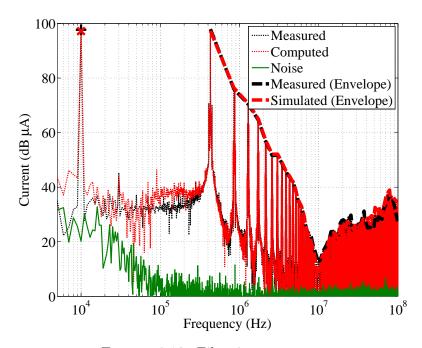

|      | Filter input current.                                              |

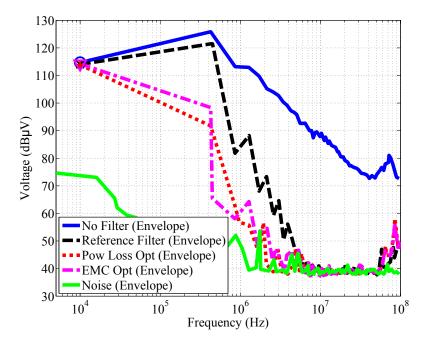

|      | Measurement comparison of filter's output voltage envelopes        |

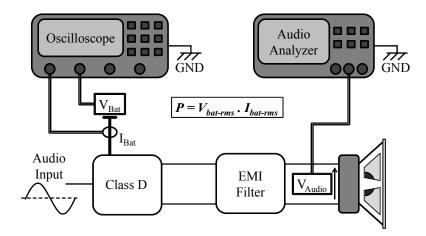

|      | Bench set-up for the power measurements                            |

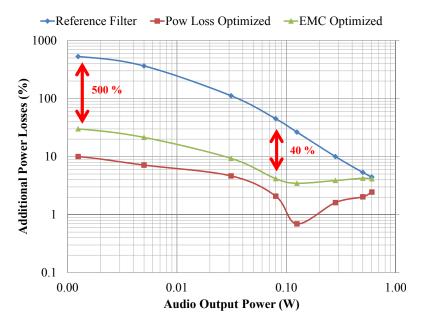

| 4.16 | Power losses introduced by the different EMI filters               |

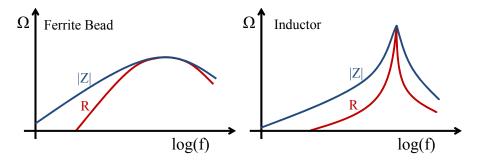

| 5.1  | Ferrite bead impedance (inspired from [125])                       |

| 5.2  | Example of Class-D THD and bargraph measurement. Note that,        |

| 0.4  | the more the bars are high the more the voltage is small since the |

|      | scale is an inverted $dB$ scale                                    |

| 5.3  | Ferrite bead model in the audio frequency band                     |

| 5.4  | Hysteresis loop obtained by the JA model and the parameters of     |

| 0.4  | the first column in Table 5.1                                      |

| 5.5  | A simulation example showing the occurring phenomenon              |

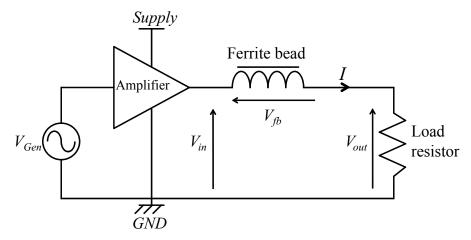

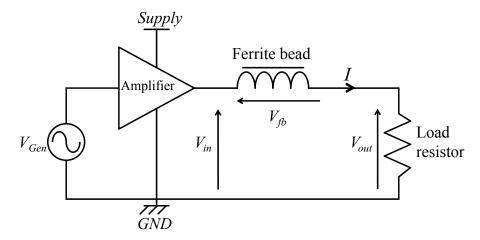

| 5.6  | Measurement schematic                                              |

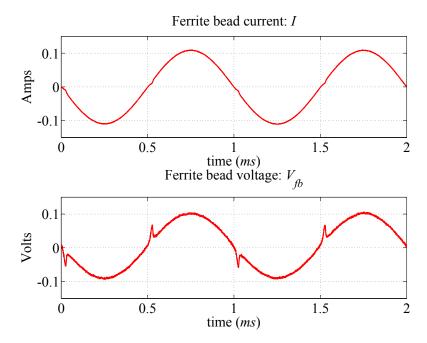

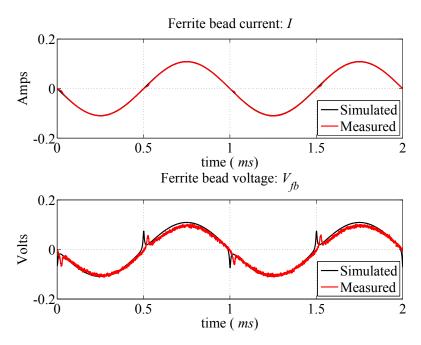

| 5.7  | Measurement results                                                |

| 0.1  | TYLOGOGITOTHOTH TOOUTUS                                            |

List of Figures xiii

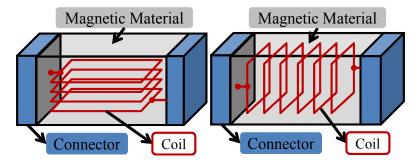

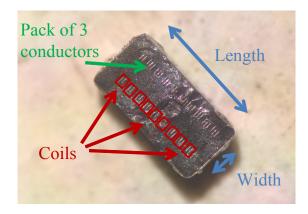

| 5.8        | Ferrite bead physical architectures                                        |

|------------|----------------------------------------------------------------------------|

| 5.9        | Ferrite bead broken in two part                                            |

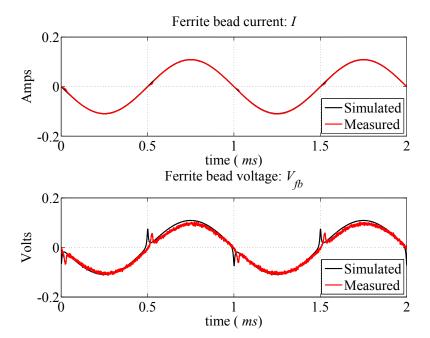

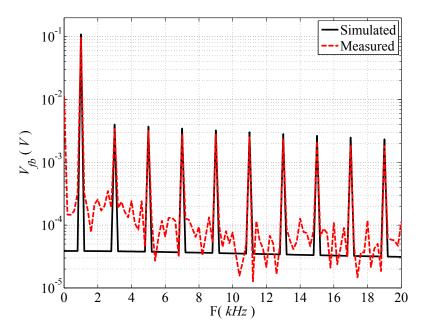

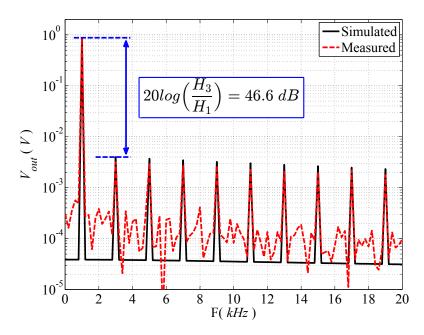

| 5.10       | Ferrite bead current and voltage                                           |

| 5.11       | Measured and simulated ferrite bead voltage                                |

| 5.12       | Measured and simulated output voltage                                      |

| 5.13       | $V_{fb}$ THD over the audio output power                                   |

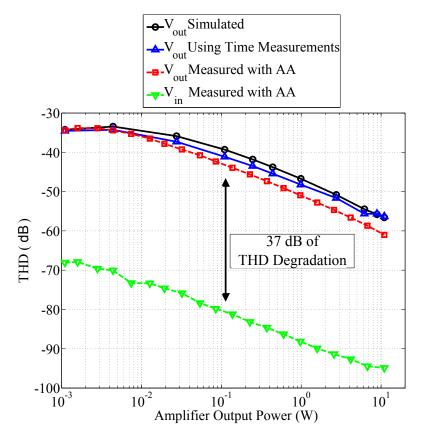

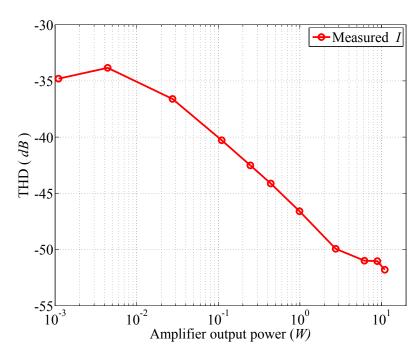

| 5.14       | $V_{in}$ and $V_{out}$ THD over the audio output power                     |

|            | The current $I$ THD over the audio output power                            |

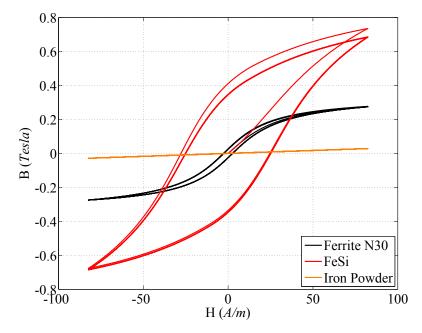

| 5.16       | Hysteresis loops obtained by the JA model and the parameters of Table 5.1  |

| 5.17       | Bead simulations with the three materials of Table 5.1 102                 |

| 5.18       | Frequency domain output voltages with the three materials of Table 5.1     |

| 6.1        | On ship coupling                                                           |

| 6.2        | On-chip coupling                                                           |

| 6.3        |                                                                            |

| 6.4        | Single switch in the frequency domain                                      |

| 6.5        |                                                                            |

| 6.6        | Coupling in case of a low to high transition                               |

| 0.0        | MOSFET body diode vs. Schottky diode                                       |

| B.1<br>B.2 | k and $m$ block association                                                |

|            |                                                                            |

| C.1        | Class-D amplifier transient model                                          |

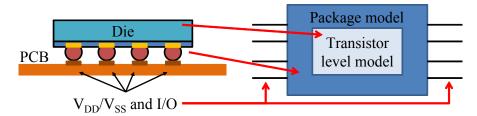

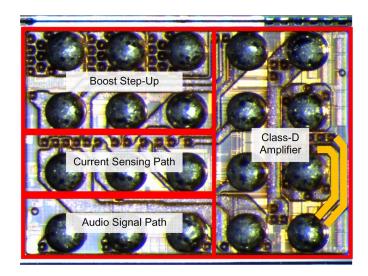

| C.2        | Chip photograph: 20 balls WL-CSP package [27]                              |

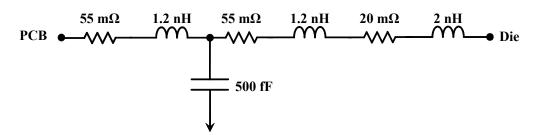

| C.3        | IC pin model according to the package                                      |

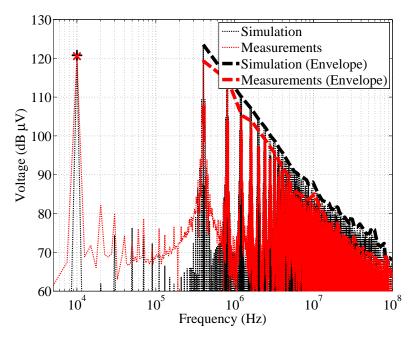

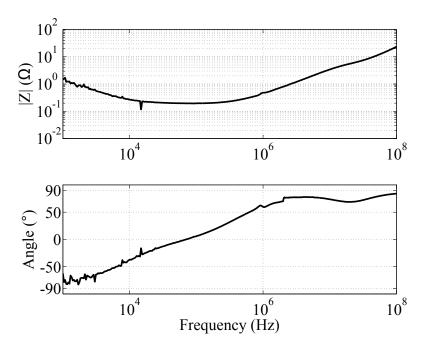

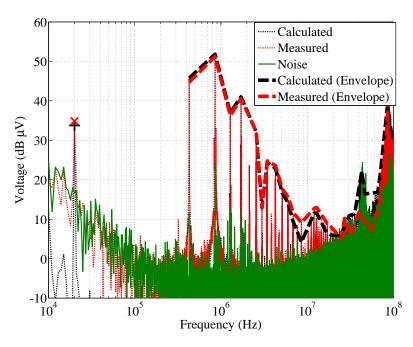

| C.4        | Comparison between the simulated and the measured output spectra. 143      |

| C.5        | Battery impedance                                                          |

| C.6        | Voltage of the battery when feeding a Class-D amplifier                    |

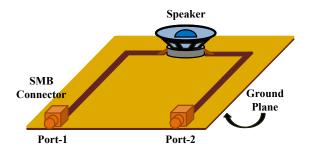

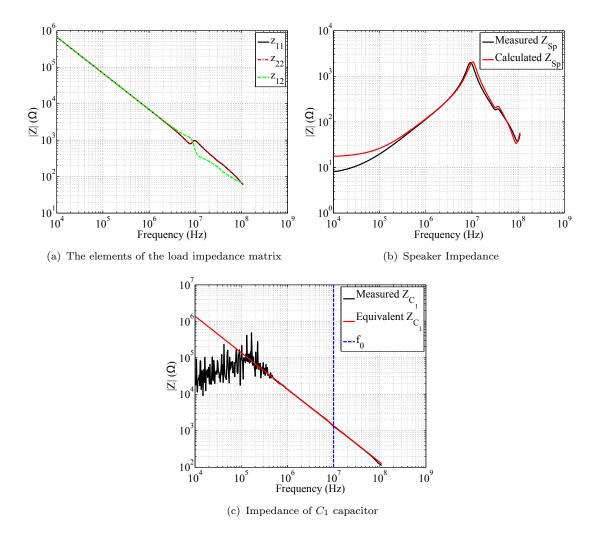

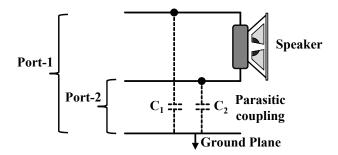

| D.1        | Board of the speaker load                                                  |

| D.2        | Impedances of the circuit in Fig. D.3                                      |

| D.3        | Speaker load equivalent circuit                                            |

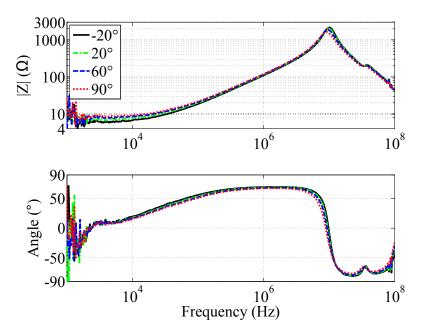

| D.4        | Speaker impedance measurements under temperature variations 150            |

|            |                                                                            |

| E.1        | THD measurements of a linear amplifier and a ferrite bead 152              |

| E.2        | THD measurements according to the signal amplitude at $1kHz$ 152           |

| E.3        | THD measurements according to signal frequency with $V_{in} = 200  mV.153$ |

| F.1        | Schéma de base d'un amplificateur de Classe D en boucle ouverte 159        |

| F.2        | Étage de puissance avec une cellule de commutation                         |

| F.3        | Étage de puissance avec deux cellules de commutations 160                  |

| F.4        | Exemple d'une modulation MLI                                               |

| F.5        | Spectre idéal d'une MLI                                                    |

| F.6        | Modulation binaire                                                         |

List of Figures xiv

| F.7  | Modulation ternaire                                                     | 3  |

|------|-------------------------------------------------------------------------|----|

| F.8  | Contenu fréquentiel d'un amplificateur de Classe D                      | 35 |

| F.9  | Émissions EM au niveau des rails de sorties                             | 36 |

| F.10 | Modèle proposé                                                          | 36 |

| F.11 | Modèle des blocs actifs                                                 | 37 |

| F.12 | Calcul du spectre du courant à la sortie du convertisseur               | 70 |

| F.13 | Calcul du spectre de tensions et de courants après un bloc nommé $k.17$ | 71 |

| F.14 | Filtre utilisé                                                          | 71 |

| F.15 | Charge utilisée pour les tests                                          | 72 |

| F.16 | Application de l'approche sur un amplificateur de Classe D 17           | 72 |

| F.17 | Tension de sortie de l'amplificateur avec deux charges différentes 17   | 73 |

| F.18 | Impédances du filtre                                                    | 74 |

| F.19 | Courant d'entrée du filtre $I_{IN_{Plus}}$                              | 75 |

| F.20 | Tension de sortie du filtre $V_{OUT_{Plus}}$                            | 75 |

| F.21 | Courant de sortie du filtre $I_{OUT_{Plus}}$                            | 76 |

| F.22 | Impédance de la batterie                                                | 76 |

| F.23 | Amplitude de la tension aux bornes de la batterie                       | 7  |

| F.24 | Circulation de courants dûs au filtre CEM                               | 78 |

| F.25 | Processus d'optimisation                                                | 79 |

| F.26 | Courants de sortie du filtre                                            | 31 |

| F.27 | Tensions de sortie du filtre                                            | 31 |

| F.28 | Tensions de sortie du filtre                                            | 33 |

| F.29 | Courant d'entrée du filtre                                              | 33 |

| F.30 | Enveloppes des spectres de sorties des différents filtres               | 34 |

| F.31 | Pertes introduites par différents filtres                               | 35 |

| F.32 | Exemple de mesure du bargraph et du taux de distorsion har-             |    |

|      | monique (THD) d'un amplificateur de Classe D avec et sans perles        |    |

|      | de ferrites                                                             |    |

|      | Modèle d'une ferrite dans la bande audio                                |    |

|      | Perle de ferrite casée en deux                                          |    |

|      | Circuit de validation                                                   |    |

| F.36 | Courant et tension de la ferrite                                        | 38 |

|      | Tension à la charge                                                     |    |

| F.38 | THD à la sortie de l'amplificateur et à la charge                       | 39 |

## List of Tables

| 2.1 | Order of magnitude for Class-D audio amplifiers [17, 47, 48]         | 24  |

|-----|----------------------------------------------------------------------|-----|

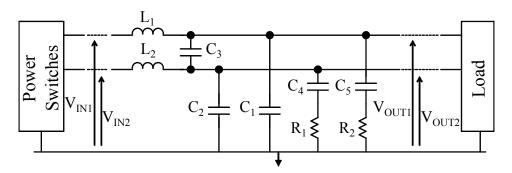

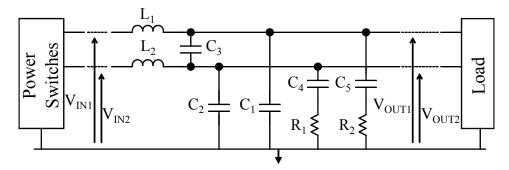

| 3.1 | Filter components values.                                            | 40  |

| 3.2 | Dummy load components values                                         | 40  |

| 3.3 | ADS filter models                                                    | 45  |

| 4.1 | Reference filter component values [84]                               | 68  |

| 4.2 | Power consumption obtained by simulation                             | 71  |

| 4.3 | Component values and references for the power loss optimized filter. | 71  |

| 4.4 | Component values and references for the EMI optimized filter         | 74  |

| 4.5 | Power consumption obtained by simulation                             | 74  |

| 5.1 | JA parameters for three different magnetic materials [144]           | 90  |

| 5.2 | Parameters for the ferrite bead under test                           | 95  |

| F.1 | Ordre de grandeur d'un amplificateur de Classe D. [17, 47, 48]       | 167 |

| F.2 | Valeurs nominales des composants du filtre                           | 172 |

| F.3 | Valeurs nominales des composants de la charge                        | 172 |

| F.4 | Référence des composants du filtre optimal.                          | 180 |

| F.5 | Comparaison des puissances et pertes pour différents filtres         | 182 |

## Abbreviations

AA Audio Analyzer

ADS Advanced Design System

CISPR International Special Committee on Radio Interference

CM Common Mode

DM Differential Mode

DUT Device Under Test

EM ElectroMagnetic

EMC ElectroMagnetic Compatibility

EMI ElectroMagnetic Interference

EIS Electrochemical Impedance Spectroscopy

FCC Federal Communications Commission

FFT Fast Fourier Transform

GA Genetic AlgorithmIA Impedance AnalyzerIC Integrated Circuit

ICEM Integrated Circuit Electromagnetic Model

JA Jiles-Atherton

LISN Line Impedance Stabilization Network

MCM Multi-Carrier Modulation

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PC Portable Computer

PCB Printed Circuit Board

PCM Pulse Code Modulation

PDM Pulse Density Modulation

PDN Power Distribution Network

PEEC Partial Element Equivalent Circuit

PWM Pulse Width Modulation

RLC Resistance, Inductance, Capacitance

Abbreviations xviii

rms root mean square

S Scattering parameters

SC Short Circuit

SMPS Switched Mode Power Supply

$\mathbf{SMT} \qquad \quad \mathbf{S} \text{urface } \mathbf{M} \text{ounted } \mathbf{T} \text{echnology}$

SNR Signal to Noise Ratio

SOC State Of Charge

THD Total Harmonic Distortion

VCCI Voluntary Control Council for Interference

VNA Vector Network Analyzer

WL-CSP Wafer-Level Chip Scale Package

$\Sigma\Delta$  Sigma Delta

Dedicated to those who believed in me... ... to my beloved family

## Chapter 1

## Introduction

Nowadays, embedded electronic systems became a necessity for every working environment and a companion in everyday life. Most of the time, many devices coexist on the same field or even many functionalities coexist in the same device. Hence, modern electronics offers complex devices that contain various kinds of applications, such as radio communication, navigation, audio, video, automation, control, etc. Therefore, analog and digital signals, high and low frequency signals, high and low power levels, etc., are taking place in the same package, or even more, on the same Printed Circuit Board (PCB). The decrease of the integration scale which is reported for semiconductor scaling by Gordon Moore's law [1], allows us to have more integrated scheme and more compact systems. The electronic applications are then closer and the PCBs are highly packed with electronic components. For instance, Fig. 1.1 shows the PCB of a modern smart-phone, where the electronic components are placed very close to each other. Therefore, due to the modern electronic requirements, Electromagnetic Compatibility (EMC) become a complex issue.

FIGURE 1.1: PCB of a modern smart-phone.

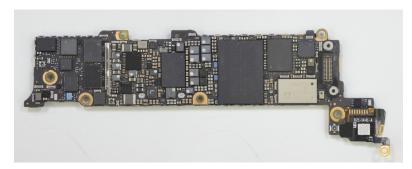

FIGURE 1.2: Product development and noise reduction [5].

## 1.1 EMC, definition and concern

The EMC of two electronic systems is the fact that the two of them are able to operate in the same ElectroMagnetic (EM) environment, without exchanging any undesirable interference of EM energy. This can be done whether by minimizing the level of unintentional EM emission, whether by maximizing the level of immunity against the unintentional EM emission, whether by limiting the coupling paths. In case of improper EMC, malfunctioning can occur which might lead to safety problems. The noise interference can for example disturb the police, fire and alarm communications, the radio and television broadcasting or even the air traffic control [2, 3]. Therefore, EMC standards were established in many countries such as European countries (CISPR: International Special Committee on Radio Interference), USA (FCC: Federal Communications Commission), Japan (VCCI: Voluntary Control Council for Interference), etc., in order to define the limits for EM emission and immunity. A number of EMC standards is listed in [4].

EMC is a major challenge for designers. The ElectroMagnetic Interference (EMI) can be the reason for a system failure or an important declination of the system performance. Such inconvenience drives the designers to use backup solutions, or to review their products from the early design stages. In both cases, additional time and cost are needed in the production chain. To avoid these functioning and extra cost problems, without forgetting the inconformity to standard risks, it is then necessary to include the EMC at the early stage of development. Knowing that, dealing with EMC in advance allows us a wider choice of available solutions with a lower cost (Fig. 1.2).

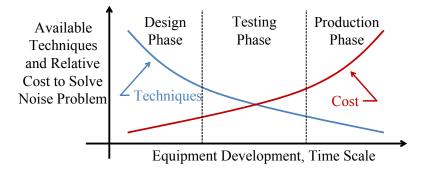

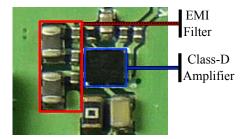

FIGURE 1.3: A Class-D amplifier and its dedicated EMI filter in the final application.

## 1.2 Problem background

Standalone and portable devices present an interesting solution for many applications and usually they are powered by batteries (or by energy harvesting). Due to the variety of applications in a device, many supply levels are needed. Hence, to fulfill the power requirements of complex devices and for a longer autonomy, power converters and power management circuits are widely used. These components have a high level of EM emissions as they deal with power switching. In general, such circuits are well-filtered to limit the noise leakage onto the supply lines.

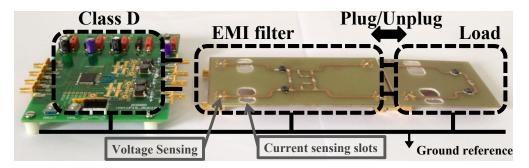

Currently the switching Class-D audio amplifier is extensively used in many types of applications, such as televisions, cars, portable computers (PCs), smart-phones, GPS, game pads and others. It is a relevant solution for audio applications because it allows us to increase significantly the power efficiency, comparing to the other amplifier classes [6, 7]. It has a similar architecture as a buck converter but having the audio signal as the reference voltage. However, as any switching circuit, Class-D amplifiers generate high level of EM emissions. A special care is needed to reduce its impact on the surrounding electronics. Many circuit solutions have been created to lower a Class-D EM emissions [8–11], nevertheless, in practical implementations the EMI filter is still mandatory. Fig. 1.3 shows an example of an integrated Class-D amplifier with the corresponding EMI filter. It can be seen that the filter occupy more than twice the area of the Class-D amplifier itself. For some applications, the filter can be even more expensive than the Class-D amplifier itself. EMI filters are bulky and add extra cost to the production. In addition, such filters are challenging to design because their behavior highly depends on parasitic components [12].

The present work is intended to study the EMC of integrated Class-D amplifiers (all the electronic units are integrated on the same silicon die). Generally, they are used in the systems where the primary function is display, audio, telecommunication, transmission, processing, etc., which generate unintentional EM emissions. Therefore, standards such as the EN55022 (Europe) [13] or the FCC-Part-15 Subpart-B (USA) [14] are often applied for these types of devices. According to these standards, the EMC study must be divided into conducted and radiated emissions. These norms define the conducted emission limits in the frequency band  $[150\,kHz,\,30\,MHz]$  and the radiated ones in the frequency band  $[30\,MHz,\,1\,GHz]$ . Dealing with both might need a long time period which exceed most probably the duration of a PhD thesis. Therefore, the present work focuses only on the conducted emissions generated by Class-D amplifiers.

As mentioned before, treating any EMC problem can be resumed to three different strategies: (i) reducing the emission of the aggressor, (ii) increasing the immunity or the victim or (iii) substituting the perturbation path. Knowing that a combination between strategies can be very efficient. This work focuses on one single strategy which is the coupling path. Usually, Class-D amplifier chips are built by semiconductor manufacturers, afterwards, each system integrator uses the same chip design into its own application. Thus, the amplifier chip is mounted on a different PCB and placed in a different environment for each different application. The coupling path is then dependent from the application itself. Therefore, the passive surrounding of the Class-D amplifier, in particularly the EMI filter, must be correctly designed for each different case. Often, due to the lack of tools, their design is based on experimental tests, which is a long process that lead to suboptimal solutions. In some cases, the previous design is also used for the newer version of the application which is not appropriate. Therefore, a method that predict the disturbances in the final application is then very interesting. Furthermore, an automated design of the EMI filter, using an accurate modeling method can lead to optimal filtering solutions.

EMI filters do not belong to the system main architecture. They are only added for EMC issues. However, as a part of the final application, they have an impact on the system performance. In the case of a Class-D amplifier, the EMI filter can create additional losses in the amplifier itself, thus, decrease the system power efficiency. Moreover, the EMI filter is on the audio path. When using nonlinear filtering

components such as magnetic components, the audio quality can be significantly reduced. Therefore, such phenomena must be carefully treated.

## 1.3 Objectives and scope of thesis

As a cooperation between four institutes, this PhD thesis have two different sides of objectives. On the first hand, the research laboratories AMPÈRE and INL focus on an innovative, rigorous and a scientific approach to reach the PhD goals. The AMPÈRE laboratory is specialized in the power electronics and in EMC. The INL laboratory is specialized in the analog design of integrated power circuits, in particularly Class-D amplifiers. On the second hand, both companies ST-Ericsson and ST-Microelectronics make sure that this Research and Development (R&D) work agree with the company perspectives. Both companies are worldwide leaders in semiconductor manufacturing, in particular integrated Class-D amplifiers. Therefore, the thesis objectives, which are described by the following, are dissociated as scientific objectives and company objectives.

## 1.3.1 Scientific objectives

According to the problem background which is presented in the precious section, the scientific objectives are set as follow:

- Develop a modeling approach for Class-D amplifiers which has a high accuracy in the conducted emission frequency band ( $[150\,kHz,\,30\,MHz]$ ). It must be a predictive method with a short simulation time to be used at the early design stage. The modeling approach should be easily applied on any Class-D application.

- Develop an automated EMI filter design that assist the system integrators while implementing Class-D amplifiers. The automated design must use the modeling approach developed in the previous point, in order to have an accurate filtering solutions. The latter must have realistic component values.

- Improving the EMI filter must not deteriorate any of the system performances. Thus, we must evaluate the impact of the EMI filter on the main function of a Class-D amplifier. In particular, it is required to model the

magnetic components used for EMI suppression and analyze the occurring phenomenon in the audio frequency band.

## 1.3.2 Company objectives

The above mentioned companies produce integrated Class-D amplifier chips. The analog designers tend to create amplifiers with the lowest possible of EM emissions. However, this is not enough if the amplifier is improperly implemented in the final applications. Therefore, the company objectives can be resumed as follow:

• Develop a tool or a method that helps the system integrators in implementing the Class-D amplifiers. The goal is to assist the company costumers while integrating these circuits in their final application. The method must be accurate and provide the user the best EMC results. The approach need to be predictive, accurate and user friendly. In addition, it is favorable that this method be able to generate filtering solutions dedicated to a given application, without degenerating any of the amplifier original performance provided by the manufacturer.

## 1.4 Thesis structure

The rest of this report is organized as follow:

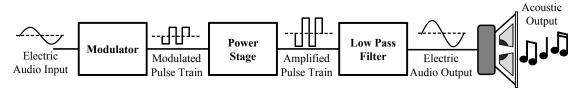

**Chapter 2** gives a short introduction to Class-D amplifiers. Therefore, it explains some of the functioning principles and reveals the main causes for Class-D amplifier EM emissions. Afterwards, this chapter provide a quick review on the state of the art for EMI reduction regarding Class-D amplifiers.

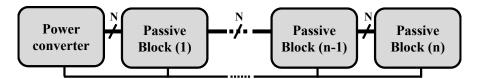

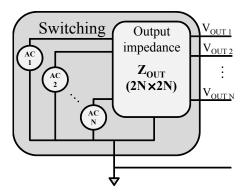

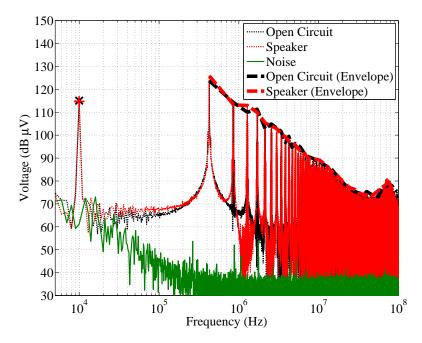

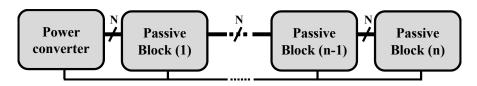

Chapter 3 develops a frequency domain modeling method in order to simulate and predict the EMI of Class-D amplifiers in the final application. The method which is dedicated for converters with N active conductors, is based on system to block decomposition and impedance matrix modeling and manipulation. After providing all the theoretical background, the method has been validated on two case of studies. The first case is an integrated differential Class-D amplifier followed by an EMI filter and a loudspeaker. The

second case is a DC-DC converter supplied by the battery. Here, the study has required to measure the high frequency impedance of the battery.

Chapter 4 focuses on the automation of the EMI filter design. Therefore, the model has been implemented in an optimization loop based on a genetic algorithm in order to optimize the filter response, and also, reduce the additional power losses introduced by an EMI filter. The optimization search space has been limited to the components available on the market and the optimization result is given as component references of the optimal filter referring to the optimal solution found. Afterwards, an experimental validation has been carried out.

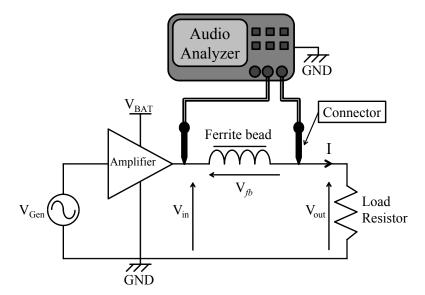

Chapter 5 is intended to study and evaluate the impact of EMI filters on the audio quality of Class-D amplifiers. Thus, it models the EMI suppression components and investigate their behavior in the audio frequency band. For this purpose, the Jiles-Atherton model for magnetic materials has been used for ferrite bead modeling. Hereafter, the impact on the time and frequency domain signals has been simulated and compared to measurements. Finally, the total harmonic distortion (THD) has been computed for different signal amplitudes and compared to the THD measured using an audio analyzer.

Chapter 6 concludes this report by summarizing the main ideas and results.

Afterwards, it proposes some of the possible perspectives for this work which are based on some early investigations.

## Chapter 2

# Class-D Amplifiers from the EMC Point of View

Class-D audio amplifier principles have been invented by Dr. A. H Reeves back in 1947 [15]. First practical designs appeared in the early 60's [15] and after that, Class-D amplifiers kept evolving until today. Nowadays, they are able to provide higher than 95 % of power efficiency [16, 17]. Classical audio amplifiers such as Class-A, Class-B or Class-AB offer the best audio quality [18, 19] comparing to the switching or the hybrid classes, but their power efficiency cannot exceed 78.5 % in theory [17, 20]. Indeed, the Class-D amplifier is mainly used in embedded systems due to its power efficiency, but also, in addition to its smaller chip size, for low power applications it doesn't need a heatsink to dissipate the heat due to the ohmic losses.

## 2.1 Class-D amplifier basics

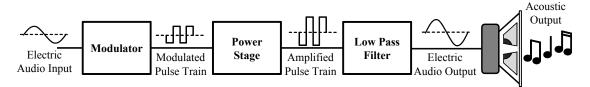

A Class-D amplifier can be divided into two major parts: the power stage and the modulator. The power stage is made by power switches (mostly Metal Oxide Semiconductor Field Effect Transistor or MOSFET) which are sized in a manner to handle all the power stress and also to obtain an optimal efficiency at the nominal output power. Its role is to provide the needed power to the loudspeaker. The modulator is an analog or digital design that generates a pulse train according to the audio signal. Its role is to control the power stage. A block diagram of an open loop Class-D audio amplifier is given in Fig. 2.1.

FIGURE 2.1: A block diagram of an open loop Class-D audio amplifier.

### 2.1.1 Power stages

Two different types of power stages can be distinguished:

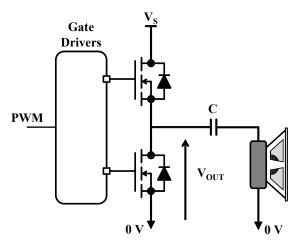

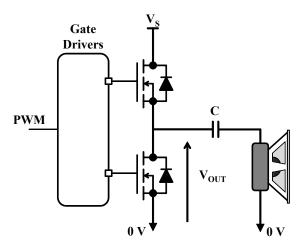

The single ended power stage [21, 22]: The single ended power stage is shown in Fig. 2.2 and contains one switching cell. This, contains two MOSFET power switches which can be a N-MOSFET or a P-MOSFET. The output voltage  $V_{OUT}$  which is the voltage across the load, can switch between the supply voltage  $V_S$  and the reference voltage 0V. Note that most of the single ended topologies enforce a DC current at the load which can be removed by placing a capacitor in series with the speaker.

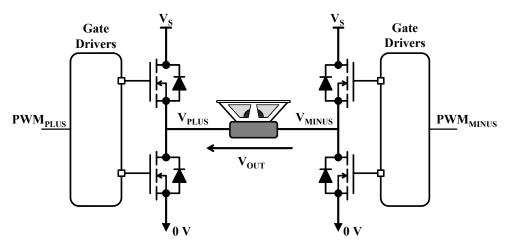

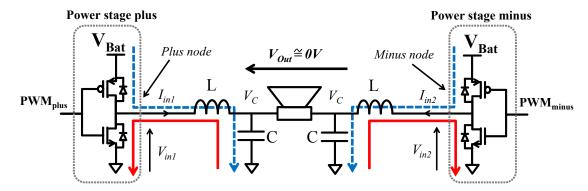

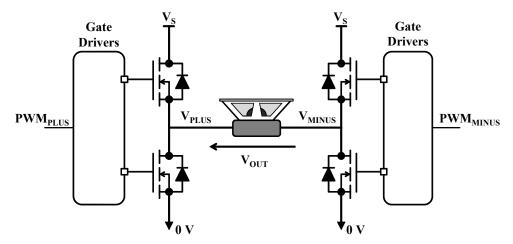

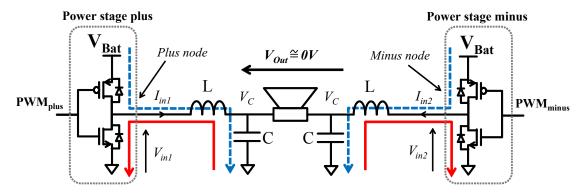

The differential power stage [16, 23]: Also called H-Bridge power stage, the differential power stage is shown in Fig. 2.3. It contains two switching cells which can switch between  $V_S$  and 0V. Thus, the voltage across the load  $V_{OUT}$  can switch between  $V_S$ , 0V and  $-V_S$ .

In both cases the gate drivers are used to ensure that for a single switching cell, the two power switches are never turned on at the same time [24], thus, prevent any short circuit between  $V_S$  and 0V which damaged the amplifier. This can be done by introducing a dead time between turning off one switch and turning on the other one. During the dead time the MOSFET body diode is used as a free-wheeling diode to assure the current flow of the inductor. Therefore, the shortest a dead time is, the better it is because the body diode has higher conduction losses due to it's narrower canal. Also, a longer dead time induce more audio distortion [24].

The switching nature of the power stage allows us to use the power transistors in a "digital mode". In other words, the transistors are used as fully on or fully off, thus, theoretically they behave as short circuits or open circuits, which lead

FIGURE 2.2: Single ended power stage.

FIGURE 2.3: H-Bridge power stage.

to a 100% of theoretical power efficiency. In the real world, the electrical units (transistors, diodes, inductors, capacitors, etc.) are not ideal, they have several imperfect properties such as the internal resistance, threshold voltage, leakage current, etc. that create power losses in the amplifier. Therefore, a typical power efficiency of a Class-D amplifier ranges between 80% and 97% [17].

Generally, in integrated solutions, the differential topology is used. It allows us to double the voltage across the load, thus, increase four times the amplifier output power for the same supply voltage and the same load impedance. In addition, the capacitor needed at the output of a single ended topology can be problematic in many embedded applications. As the audio frequency band starts from  $20\,Hz$ , few  $\mu F$  are needed [17] to stop the DC current without affecting the audio frequency band. Such capacitors are bulky which gives a considerable advantage to the

differential topology.

#### 2.1.2 Modulations

The signal at the output of a switching cell has the same shape as the modulated pulse stream, but with different voltage levels. The modulation type is then in direct relation with the structure of the amplifier output spectrum, which means a significant impact on the amplifier EMC, at frequencies related to the switching frequency. The most common modulation technique is the Pulse Width Modulation (PWM). However, other architectures and techniques also exist such as the Sigma Delta Modulation ( $\Sigma\Delta$ ) [25], Pulse Code Modulation (PCM) [26], Pulse Density Modulation (PDM) [6] etc. A quick review for the PWM is given by the following.

#### 2.1.2.1 The Pulse Width Modulation (PWM)

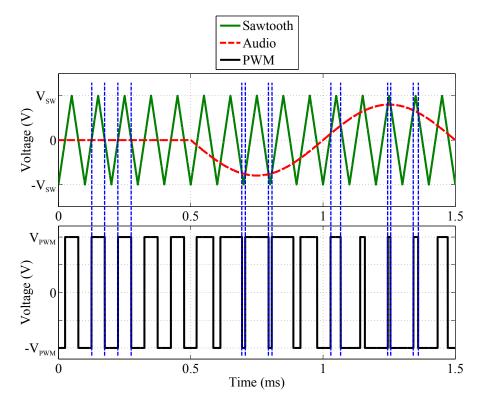

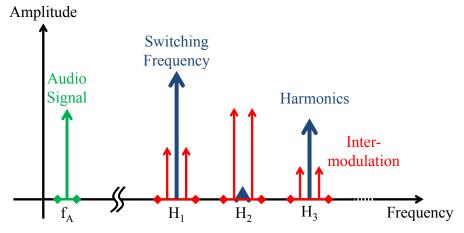

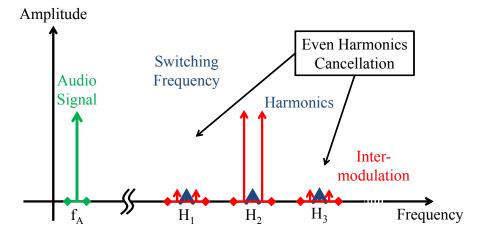

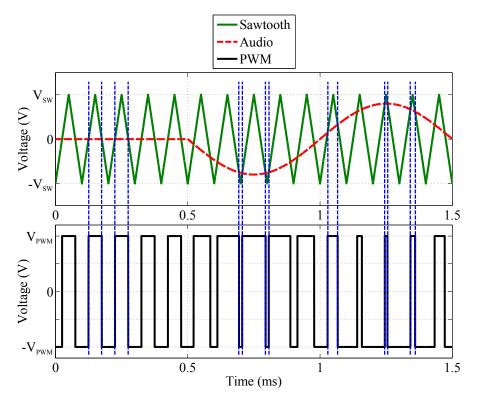

The PWM [27, 28] can be obtained by comparing the audio signal  $[20 \, Hz \, ; 20 \, kHz]$  to a ramp waveform with a higher frequency, as shown in the example of Fig. 2.4. Generally, the carrier which is a double-sided sawtooth has a frequency at least two times greater than the maximum frequency of the audio frequency band which is  $20 \, kHz$  [6, 16]. In practical implementations, the carrier frequency is chosen at least ten times greater than  $20 \, kHz$  for a better audio reconstitution [16]. The switching frequency is then the same as the ramp signal frequency and the pulse widths are modulated according to the audio signal. As a square signal, it has harmonics on the odd multiples of the switching frequency. Thus, the amplifier output spectrum can be described by Fig. 2.5. It contains the audio signal which is illustrated as sinusoidal signal in this figure, the switching frequency and its odd harmonics, in addition to the inter-modulation peaks located around each harmonic. The PWM spectrum components have been deeply studied in [29, 30]. Moreover, additional information concerning the carrier and it's influence on the spectral content of a PWM can be found in [6].

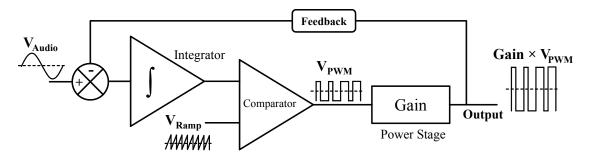

A basic amplifier architecture is shown in Fig. 2.6. The architecture is composed by a comparator that generates the PWM signal according to the ramp and the audio signals. The pulse train is then amplified by the power stage to drive the load. As a nonlinear device, the Class-D amplifier introduces a high amount of distortion

FIGURE 2.4: PWM modulation.

FIGURE 2.5: Spectrum of a PWM signal.

due to the modulation errors, the power switching and others. Moreover, gain variations can occur in case of unstable supply voltage (for example, a battery at different state of charge). Therefore, most of the time a feedback loop is introduced in order to reduce these errors and produce a better audio restitution.

FIGURE 2.6: Basic architecture of a Class-D amplifier [24].

#### 2.1.2.2 PWM for differential Class-D amplifiers

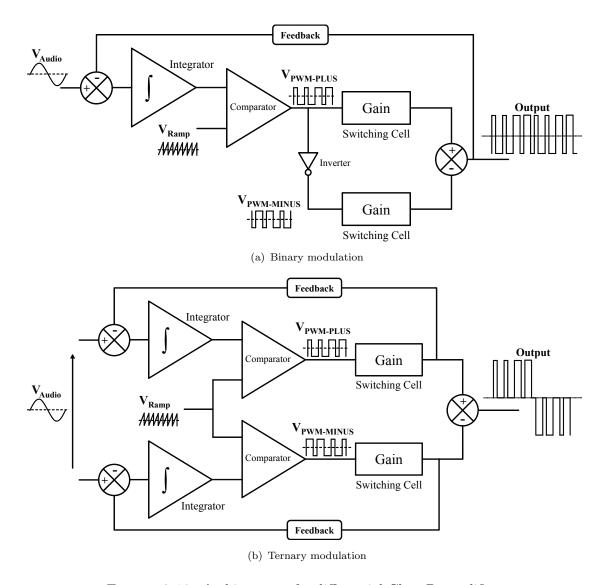

In the case of a differential power stage, an additional modulation feature can be included. The power stage can switch according to a binary or a ternary modulation. Considering an ideal power stage, a description is given by the following.

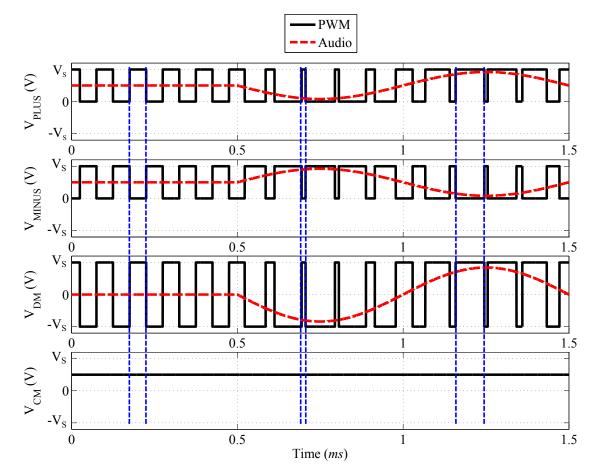

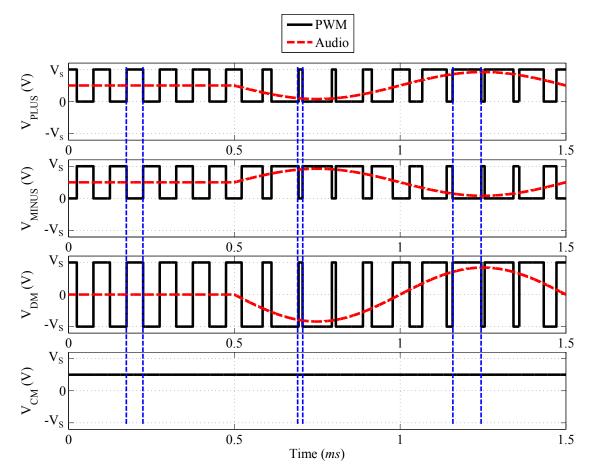

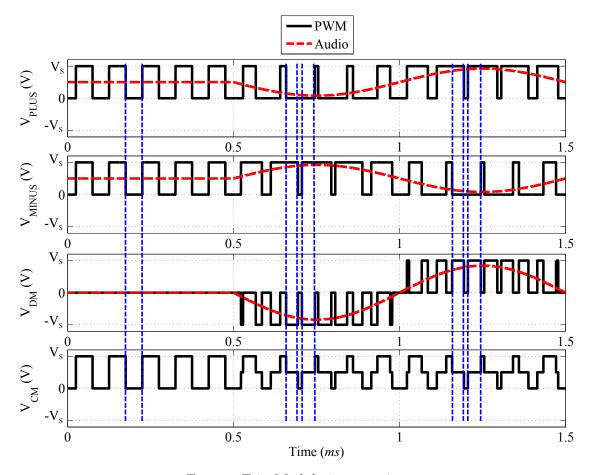

Binary modulation: The binary modulation [16, 31] is obtained when the two switching cells of an H-Bridge are switching with complementary values (0 V and  $V_S$ ). Thus, they switch at the same time as shown in Fig. 2.7. Two modes exist in the case of a differential topology, the first is the Common Mode (CM) which is given by equation (2.1). The second is the Differential Mode (DM) which is given by equation (2.2).

$$V_{CM} = \frac{V_{PLUS} + V_{MINUS}}{2} \tag{2.1}$$

$$V_{DM} = V_{PLUS} - V_{MINUS} (2.2)$$

The output signal which is the same as the DM voltage, keeps the same shape as the original single switch PWM, but it doubles the amplitude by switching between  $V_S$  and  $-V_S$ . The output spectrum is then the same as the one shown in Fig. 2.5, but with double the amplitudes. The CM which is the common voltage referring to the ground, is a DC voltage which is an advantage in term of EMC.

Note that, this architecture presents a major drawback and it is highlighted as follow. In the case of zero audio signal, as can be seen between  $0\,ms$  and  $0.5\,ms$  in Fig. 2.7, the differential voltage keep switching with  $50\,\%$  duty cycle corresponding to a  $0\,V$  mean value. Thus, the current in the load is not zero even if the audio

FIGURE 2.7: H-Bridge binary modulation.

signal is equal to zero. Note as well that, for this type of modulation the output voltage or  $V_{DM}$  switch with a step of  $2 \times V_S$ .

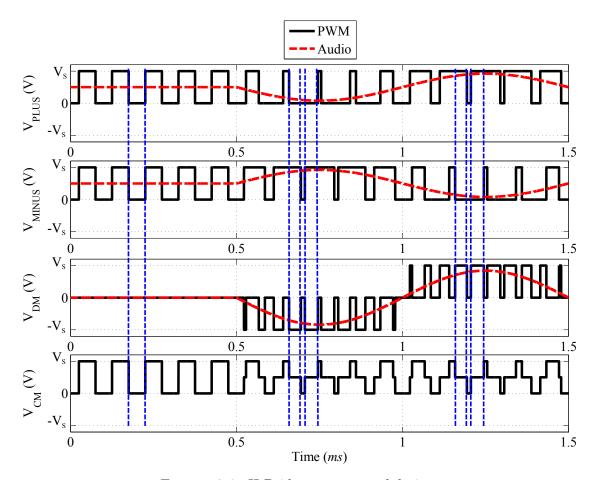

Ternary modulation: The ternary modulation [16, 31] is obtained when the two switching cells of an H-Bridge switch at different time as shown in Fig. 2.8. On the first hand, the differential output voltage or  $V_{DM}$ , switch between the three available levels:  $V_S$ , 0 V and  $-V_S$ . In this case, two pulses appear on each switching period of the original carrier, which doubles the switching frequency across the load. It implies in the frequency domain a cancellation of the odd harmonics, including their inter-modulations. The output voltage spectrum can be then expressed by Fig. 2.9. On the second hand, the common mode voltage or  $V_{CM}$  keeps switching with and without audio signal which is a negative point in term of EMC. However, this topology allows us to have a zero differential output signal in the case of a zero audio input signal. It is highlighted in Fig. 2.8 between

Figure 2.8: H-Bridge ternary modulation.

$0\,ms$  and  $0.5\,ms$ . In addition, the output voltage have a switching step equal to  $V_S$ .

As a conclusion, the ternary architecture presents many advantages comparing to the binary architecture. It allows us (i) to remove the odd harmonic in the output spectrum, (ii) to have a zero current in the load in case of a zero audio signal and (iii) to have a low switching step in the output voltage. Therefore, it can be more often found among commercial integrated Class-D amplifiers. Fig. 2.10 shows two architecture examples of a differential Class-D amplifier having a binary and a ternary modulation [27].

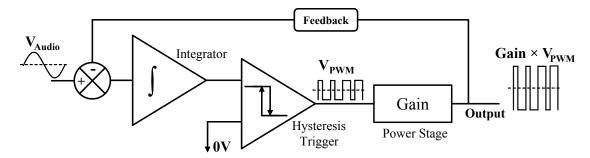

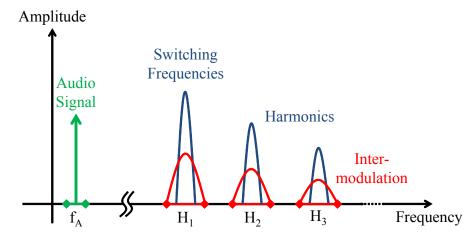

#### 2.1.2.3 Self oscillating modulation

The modulation techniques mentioned earlier are not the only existing techniques. By using a closed loop, it is also possible to generate a modulated pulse stream. These techniques can appear under several names such as the self oscillating,

Figure 2.9: Ternary modulation output spectrum.

the sliding mode or the bang-bang control. Some of the basics are given in the following:

The self oscillating modulation [7, 32, 33] can be obtained by creating an unstable feedback loop that force the system to oscillate. A basic architecture is given in Fig. 2.11. The error signal which is the difference between the input and the output signals is integrated and injected into an hysteresis trigger. By a comparison to 0V, the pulse train is obtained then amplified by the power stage to finally be fed to the speaker.

In such architecture, the switching frequency is dependent from the input signal level. Therefore, for an audio input, the switching frequency keep changing systematically [32] which creates a spread spectrum phenomenon. This allows us to reduce the harmonic power and spread it around the central switching frequency. This is the main advantage of such modulation which lead to some peak reduction, thus, to a certain amount of EMI reduction [34]. The output spectrum can be then described by Fig. 2.12.

Self oscillating techniques can also be used with differential power stages. Thus, generate a binary or a ternary modulation. However, this issue is not developed for conciseness.

FIGURE 2.10: Architecture of a differential Class-D amplifier.

## 2.2 EM emission of Class-D amplifiers

The switching nature of a Class-D amplifier provides an important advantage, which is the power efficiency. However, the switching behavior is also the source of EMI generated by such an amplifier.

## 2.2.1 EMI at the output rails

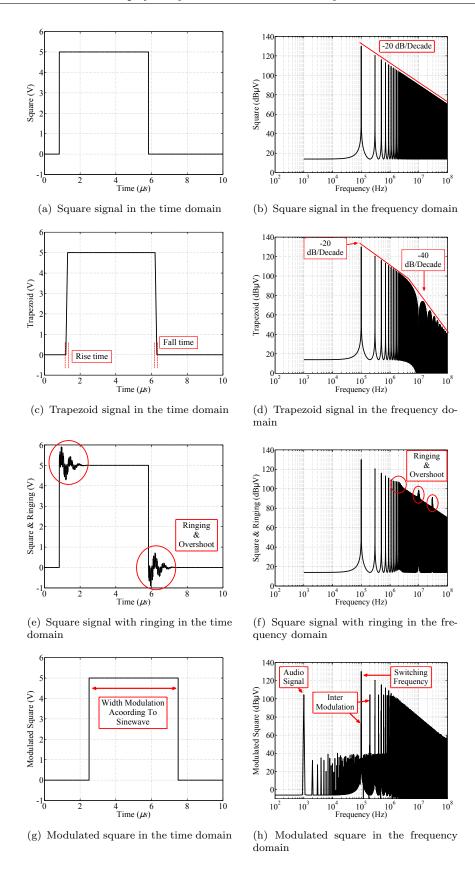

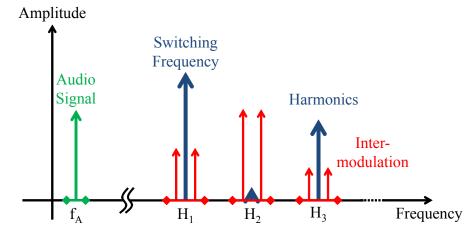

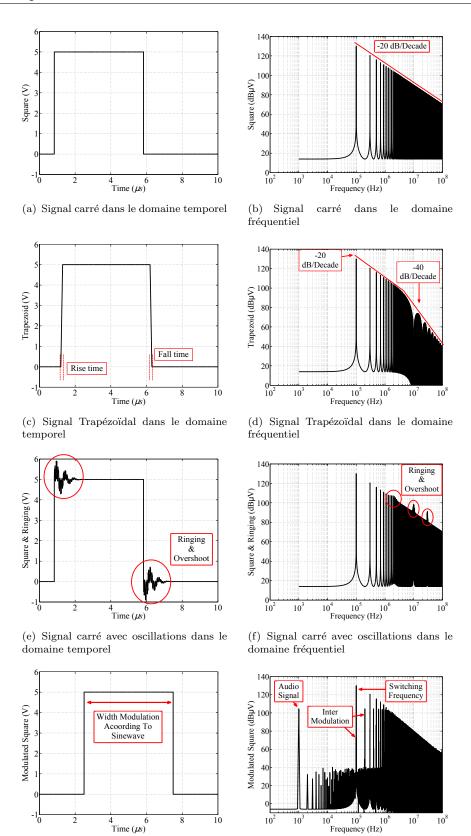

Fig. 2.13 shows the frequency content at the output of a Class-D amplifier. The frequency characteristics of a square signal (Fig. 2.13(a)) contains in the frequency domain (Fig. 2.13(b)) harmonics located on the odd multiples of the switching

FIGURE 2.11: Basic architecture of a self oscillating Class-D amplifier.

Figure 2.12: Self oscillating Class-D amplifier output spectrum.

frequency. These harmonics decrease by a negative slope equal to  $-20 \, dB/decade$ . A real voltage waveform has a certain non-zero rise and fall time [35]. It is then a better approximation to consider the pulse stream as a trapezoidal waveform (Fig. 2.13(c)). This latter presents as well odd harmonics over the frequency band (Fig. 2.13(d)), similar to the case of a square waveform. However, in the case of trapezoidal waveform, the harmonics decrease by a slope of  $-40 \, dB/decade$  after a corner frequency. If the rise and fall time are equal and called  $\tau_r$ , the corner frequency can be calculated by equation (2.3).

$$f_c = \frac{1}{\pi \tau_r} \tag{2.3}$$

A switching electronic system contains many parasitic components that can be modeled as inductors and capacitors. These are due to the chip bondings, to the connectors, and many others. Mixing these parasitic components with the high dv(t)/dt of the pulse switching, creates ringings and overshoots on each switching transition of the pulse stream (Fig. 2.13(e)). Indeed, it has an impact on the shape of the frequency spectrum as shown in Fig. 2.13(f).

Finally, in the case of a Class-D amplifier, the duty cycle of the square signal is modulated according to the audio signal (Fig. 2.13(g)). Thus, additional peaks appear in the frequency spectrum (Fig. 2.13(h)) which correspond to the intermodulation (also called side bands) between the carrier and the audio signal.

A Class-D amplifier generates a pulse stream that combines all the above features. In addition, many other features such as the MOSFET body diodes, switching dead time, disparity among component properties and component nonlinearities, etc., affect directly the output signal. Thus, a Class-D amplifier which mix the high power delivery with the complex output spectrum, appear to be a serious source of EM emissions.

Often, in electronic applications, the Class-D amplifier is placed distant from the speaker load. Thus, the long cables or PCB tracks used for connecting these two, are problematic in EMC. The conducted noise that propagates through long conductors and interfere with the surrounding electronics by inductive or capacitive coupling. Also, if the conductors are sufficiently long they behave as antennas. In this case, the EM emissions propagates in the atmosphere and provoke radiated emissions.

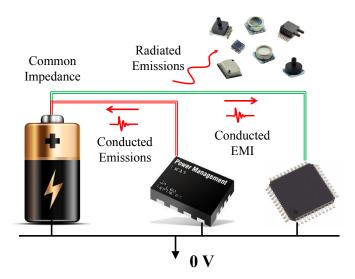

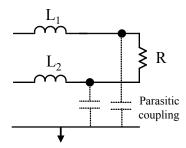

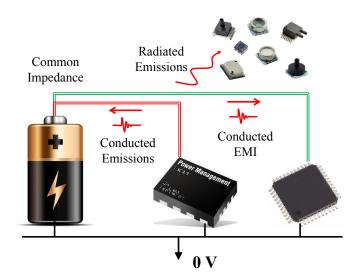

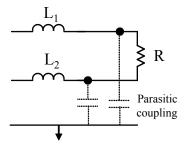

#### 2.2.2 EMI at the supply rails

In embedded and portable devices, batteries are the main power supply for the entire device, notably the Class-D amplifier. Because of the parasitic components combined with the power stage switching and other phenomena such as the bus pumping [24]; some of the perturbations leak to the supply bus. Hence, the voltage variations and the noise generated at the battery level, can disturb other circuits in the embedded system by common impedance coupling. Although, if the battery connections are long, the above stated couplings, crosstalk and radiations can occur. Thus, the Class-D amplifier is not a source of EMI only at the output side, but also at the supply side. This phenomenon exists as well in the case of power converters such as DC to DC converters and it is illustrated in Fig. 2.14.

Figure 2.13: Frequency content of a Class-D amplifier

FIGURE 2.14: EMI emissions at the supply level.

#### 2.2.3 EMC solutions

Class-D amplifiers are a serious source of EM emissions which is a crucial problem. Therefore, reducing their emissions has been one of the main interest of electronics designers for many years. For this purpose, numerous circuit design solutions have been created. A quick review is given by the following.

One of the most adopted techniques in power electronics is to control the switching transitions of the power stage [11, 36]. As can be seen from Fig. 2.13(c) and Fig. 2.13(d), the rise and the fall time of the trapezoidal waveform are in a direct relation with the frequency content of their spectrum. The more the rise/fall time is long (slow), the more the corner frequency is low and vise versa. Thus, for  $f > \frac{1}{\pi \tau_r}$ , a trapezoidal waveform with a long rise/fall time has a frequency spectral content which is lower than the one with a short rise/fall time [37]. This technique is cheep and simple to implement. However, a slow switching time increases the switching losses, thus, a trade-off must be made between the power efficiency and the EMI.

Spread spectrum or dithering, is another technique widely used in power electronics, in particular Class-D amplifiers [8, 38]. As described in section 2.1.2, by creating a random or a quasi-random switching frequency, the noise energy is spread around a central frequency, instead of being localized on a single one. This lead to a reduction of the peaks in the frequency spectra, thus, the reduction of

the EMI. The main drawback of this technique is the negative impact on the audio quality.

Recently, there has been a considerable interest in developing the active filtering technique [39–41]. The idea behind it is to sense the generated noise, then subtract it from the desired signal. This is an effective technique to reduce the EMI. However, it increases the complexity of the system control as well as the power losses of the converter.

The Multi-Carrier Modulation (MCM) [42, 43] is a technique where the audio signal is modulated twice, by two different carriers having two different frequencies. Two PWM signals are obtained, then combined by a logic circuit to deduce a single pulse stream. This latter has a frequency spectral content lower than the one of a single carrier, because the energy is split in two spectral components. This technique drawbacks are the reduced audio quality, the additional power losses and the additional inter-modulation peaks.

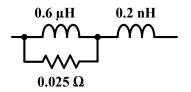

The most used EMI suppression method is the passive filtering [3, 12]. Even with the above presented techniques, most of the time, the passive filtering is unavoidable. Many different forms of passive filters exist such as the classical first, second or third order LC filters, the decoupling capacitors, the ferrite beads, the coupled inductors etc. Indeed, they have also a negative impact on the system performance like the audio quality degradation in case of nonlinear behavior [44], or the increase of power losses. However, it is still the most used technique to reduce the EMI.

Circuit design solutions are widely described in the literature as discussed earlier. Each different solution has been theoretically studied and practicably implemented several times. The advantages were highlighted and the disadvantages were discussed and some of them are improved. However, by the author best knowledge, apart [45] no studies in the literature are directly involved in improving the passive environment of a Class-D amplifier, in particular the EMI filters which are the most common EMI suppression methods. Accordingly, this will be the main focus of the present work.

## 2.3 Characterizing a Class-D amplifier

Eventually, apart the EMC and power efficiency, there exists many criteria in order to evaluate a Class-D amplifier. Some of them are used to evaluate the amplifier power characteristics, some others are used to evaluate the amplifier audio performance in the audio frequency band. Table 2.1 gives important orders of magnitude and few definitions are given in appendix A. Furthermore, more information about characterizing and evaluating a Class-D amplifier can be found in [46].

Magnitude [Unit]Minimum value Maximum value Output power W 0.5300 Power efficiency at full scale [%]80 97 V  $\overline{2.5}$ Supply voltage 100 Audio frequency Hz20 24000 Switching frequency 100 3000 |kHz|Switching Rise/Fall time 5  $^{\mathrm{ns}}$ 50  $[\Omega]$ 2 Load resistance 64 **Total Harmonic Distortion** dB50 90 Signal to Noise Ratio dB80 110 Power Supply Rejection Ratio dB60 110 Silicon area  $[\mathrm{mm}^2]$ 0.110 Chip price (PCB not included) [\$] 0.1 15EMI filter price \$ 0.5 10

Table 2.1: Order of magnitude for Class-D audio amplifiers [17, 47, 48]

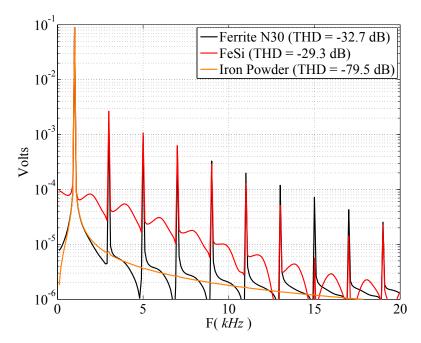

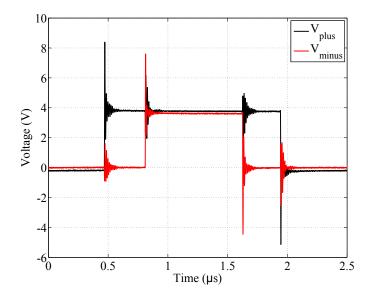

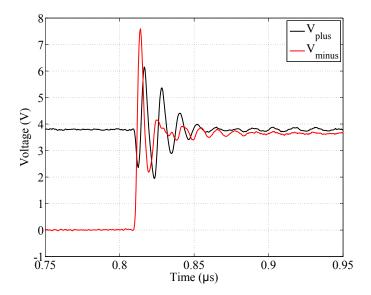

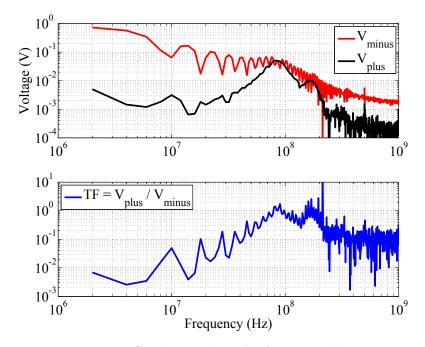

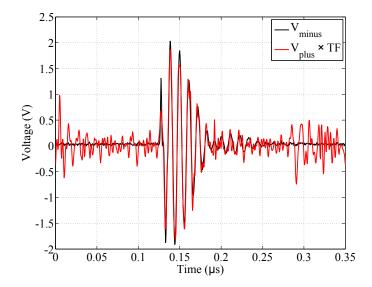

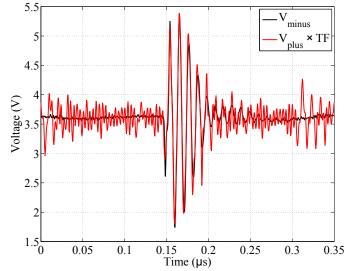

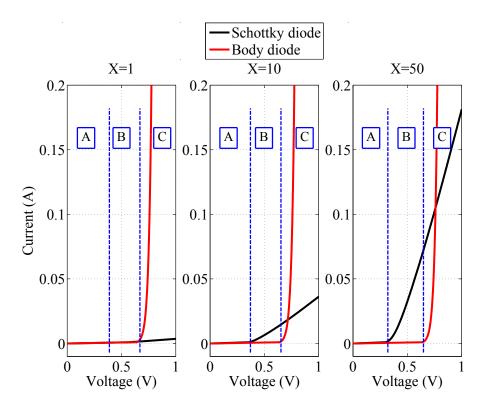

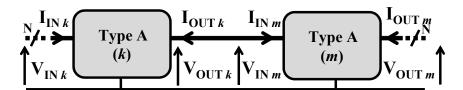

## 2.4 Summary