# A timed communication behaviour model for distributed systems

Yanwen Chen

### ► To cite this version:

Yanwen Chen. A timed communication behaviour model for distributed systems. Other [cs.OH]. Université Nice Sophia Antipolis; East China normal university (Shanghai), 2014. English. NNT: 2014NICE4090. tel-01127353

### HAL Id: tel-01127353 https://theses.hal.science/tel-01127353v1

Submitted on 7 Mar 2015  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. 2014 届研究生博士学位论文

学校代号: 10269 学号: 52101500002

華東師範大學

## 分布式系统的 时间化通信行为模型

| 院系:    | 软件学院                |

|--------|---------------------|

| 专业名称:  | 计算机应用技术             |

| 研究方向:  | 软件工程理论              |

| 博士研究生: | 陈艳文                 |

| 法国学校:  | 尼斯大学                |

| 项目:    | 中法联合培养, 973物联网专项    |

| 指导老师:  | 陈仪香, Eric Madelaine |

|        |                     |

二零一四年十月

## EAST CHINA NORMAL UNIVERSITY & UNIVERSITY DE NICE SOPHIA ANTIPOLIS

## A Timed Communication Behaviour Model for Distributed Systems

| Department: | Software Engineering Institute         |

|-------------|----------------------------------------|

| Major:      | Computer Application Technology        |

| Subject:    | Software Theories                      |

| Author:     | Yanwen Chen                            |

| Project:    | Joint Project, 973 CPS Project         |

| Tutor:      | Professor Yixiang Chen, Eric Madelaine |

2014. 10

### 华东师范大学学位论文原创性声明

郑重声明:本人呈交的学位论文《分布式系统的时间化通信行为模型》是在华东师范大学攻读硕士/博士(请勾选)学位期间,在导师的指导下进行的研究工作及取得的研究成果。除文中已经注明引用的内容外,本论文不包含其他个人已经发表或撰写过的研究成果。对本文的研究做出重要贡献的个人和集体,均已在文中做了明确说明并表示谢意。

作者签名:\_\_\_\_\_ 日期: 年 月 日

### 华东师范大学学位论文著作权使用声明

《分布式系统的时间化通信行为模型》系本人在华东师范大学攻读学 位期间在导师指导下完成的硕士/博士(请勾选)学位论文,本论文 的研 究成果归华东师范大学所有。本人同意华东师范大学根据相关规定保留和 使用此学位论文,并向主管部门 和相关机构如国家图书馆,中信所和"知 网"送交学位论文的印刷版和电子版;允许学位论文进入华东师范大学图书 馆及数据库被查阅,借阅;同意学校将学位论文加入全国博士,硕士学位 论文共建单位数据库进行检索,将学位论文的标题 和摘要汇编出版,采用 影印,缩印或者其他方式合理复制学位论文。

本学位论文属于 (请勾选)

( )1.经华东师范大学相关部门审查核定的"内部"或"保密"学位

论文<sup>1</sup>于 年 月 日解密,解密后适用上述授权。

( ) 2.不保密,适用上述授权。

导师签名:\_\_\_\_\_ 本人签名:\_\_\_\_\_ 年 月 日

<sup>1</sup>"保密"学位论文应是已经华东师范大学学位评定委员会办公室或保密委员会审定过的学位论文(需附获批的《华东师范大学研究生申请学位论文"保密"审批表》方为有效),未经上述部门审定的学位论文均为公开学位论文。此声明栏不填写的,默认为公开学位论文,均适用上述授权。

### 博士学位论文答辩委员会成员名单

| 姓名 | 职称 | 单位 | 备注 |

|----|----|----|----|

|    |    |    |    |

|    |    |    |    |

|    |    |    |    |

|    |    |    |    |

|    |    |    |    |

|    |    |    |    |

### 摘要

随着网络技术的不断发展,物联网/物理信息融合系统成为目前研究和 发展的热点。一个典型的例子是智能交通系统 (ITS)。 通信作为信息交 换的媒介,已成为物联网研究的核心问题之一。 在智能交通系统中,车辆 可以与服务中心沟通 (V2I),告知其他车辆他们的存在以便于车辆的安全 监控和安全驾驶;另外车辆和车辆之间也可以通信 (V2V),从而提高交通 的安全性,避免恶性交通事故的发生。

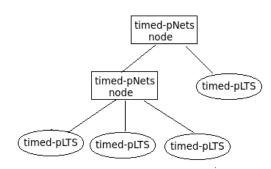

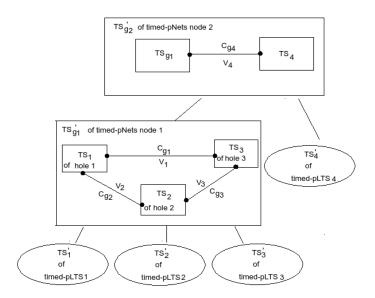

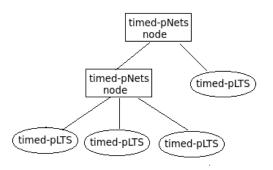

该系统通信的实时性研究是非常重要的。分布式的系统通信更强调逻辑时钟。为此本论文提出一种新型的适用于分布式系统通信的时间化网络通信模型(Timed-pNets)。该模型包括了刻画时间化动作(Time Action)的逻辑时钟(Logical Clock)、时间化规范(Timed Specification)、时间参数化标签迁移系统(timed Parameterized Label Transition System,timed-pLTS)等基本构件。Timed-pNets是树型分层结构模型,其叶子节点由Timed-pLTS表述,非叶子节点是子网的抽象,用于同步子网之间的通信。

本论文的主要贡献如下:

- 建立了一个分布式具有同步和异步通信的时间化模型Timed-pNets。 在引入时间化动作形成动作逻辑时钟基础上,建立时间化的pLTS系统(Timed-pLTS)。Timed-pLTS中的标签为逻辑时钟,用于触发系统从一个状态迁移到另一个状态。论文把信道设计为Timed-pLTS,具有信息接受和发送两个动作逻辑时钟,用来描述异步通信。基于Timed-pLTS,论文构造了Timed-pNets模型,它的同步向量用于描述不同节点之间的同步通信。研究Timed-pNets的相容性(Compatibility)和延迟性(Delay)。

- 提出了时间规范(Timed Specication)的概念。时间规范定义为一组 逻辑时钟和这些时钟上的关系,包括时钟优先关系和时钟同步关系。 提出了时钟划分和时钟合并的概念以简化时间规范,研究了时钟的 优先关系和同步关系作用在划分后时钟上的语义。

- 设计了一组算法用于把Timed-pLTS和Timed-pNets转化为时间规范,

并提出了一套利用时间规范来建立层次化模型的理论和方法。这样

人们可以灵活地设计通信系统:既可以先设计叶子节点,然后组合成Timed-pNets节点这种层层向上的方法构建系统,也可以先设计一个抽象的Timed-pNets系统,然后用具体的Timed-pLTS实例化该系统中每个抽象孔的由上至下方式构建系统。

以智能交通系统中车辆相互通信为例子,实现如何建立TimedpNets模型,以及检查通信的安全性和时间性质。使用TimeSquare工具完成这些性质的测试,结果表明论文建立的timed-pNets具有通用性和灵活性。

关键词: 分布式系统,物联网,逻辑时钟,时间规范,形式化方法,智能交通系统 (ITS),同步通信,异步通信

### Abstract

With the development of the Internet, CPSs (Cyber Physical Systems) become a hot topic. A typical example are ITSs (Intelligent Transportation Systems), where communication is a critical part. In this kind of systems, vehicles can communicate with the infrastructure (V2I) to inform their existence for safety checking; and vehicles can also communicate between each other to improve the efficiency of traffic and avoid accidents.

The real-time communication in the system is a critical aspect. This thesis presents a novel timed model called timed-pNets for modeling and verifying the timed communication behaviours for distributed systems. Since the nodes in distributed systems have no common physical clock, this brings the challenge of correctly specifying the system time constraints. TimedpNets build the time model on top of logical clocks such that the time of this model does not rely on a common physical clock.

The main contribution of the thesis are as follows:

- A formalism named Timed-pNets that is based on tree style hierarchical structures. The leaves of the structures are represented by timed Parametrized Label Transition Systems (timed-pLTSs). Non-leaf nodes (called timed-pNets nodes) are synchronisation devices that synchronize the behaviours of subnets (these subnets can be leaves or non-leaf nodes). Moreover, we discuss the compatibility and delay properties of the model.

- Timed specifications, which are at the core of this model and are designed to specify the system behaviours including synchronous and asynchronous communications. They consist of sets of logical clocks and some relations on these clocks. Moreover, we proposed the concept of clock partition and clock union to simplify the timed specifications, and investigate the clock relations on clock partitions.

- Algorithms design for the translation of timed-pLTS and timed-pNets

to timed specifications. Thanks to the timed specification, timed-pNets are able to model systems in a flexible way: from bottom to up, starting with detailed timed-pLTSs and assembling them in a compatible way; or from top to down, constructing timed specifications for abstract timed-pNets, using their holes timed specifications as hypotheses in an assume-guarantee style, and providing later some specific (compatible) implementations for these holes in various contexts.

• A discussion on time bound analysis, safety and latency properties based on the analysis of the relations conflicts between system logical clocks. We take a simple case of car insertion from the area of Intelligent Transportation Systems (ITS) as an example to demonstrate the use of the timed-pNets model. In the end, the TimeSquare tool is used to perform a logical simulation and check the validity of our model.

**Key words:** Distributed Systems, CPS (Cyber Physical Systems), Logical Clock, Timed Specification, Formal Methods, ITS, Synchronous Communication, Asynchronous Communication

### Résumé

Cette thèse présente un nouveau modèle temporisé appelé timed-pNets pour la modélisation et la vérification des comportements des systèmes distribués hétérogènes. Un défi essentiel de ces systèmes est de spécifier correctement les contraintes de temps du système, dans la mesure où les nœuds dans les systèmes distribués n'ont pas l'horloge physique commune. TimedpNets utilise un modèle de temps basé sur des horloges logiques, de manière à ce que les mesures de temps dans ce modèle ne reposent pas sur une horloge physique commune. Les timed-pNets ont une structure hiérarchique en arbre: les feuilles de cet arbre sont des Systèmes de Transition Étiquetés paramétrés temporisés (timed-LTSs), et les autres nœuds (appelés eux-aussi, par abus, Timed-pNets) sont des dispositifs de synchronisation qui permettent de composer les comportements de leurs sous-réseaux (eux-mêmes des timed-pNets). A chaque nœud d'un timed-pNet peut-être associée une Spécification temporisée, qui consiste en un ensemble d'horloges logiques et de relations sur ces horloges.

Les spécifications temporisées, en tant que le noyau de ce modèle, sont utilisées pour spécifier les comportements du système, y compris les communications synchrones et asynchrones. Grâce à la spécification temporisée, les timed-pNets peuvent modéliser des systèmes de manière flexible: soit de bas en haut, en commençant par des timed-pLTSs détaillés et en les composant de manière compatible; ou de haut en bas, construisant les spécifications temporisées pour des timed-pNets abstraits, en utilisant les spécifications temporisées de leurs arguments (trous) comme des hypothèses du style assumegarantee, et en fournissant plus tard des implémentations spécifiques (compatibles) pour ces trous dans divers contextes. Notre méthodologie permet un cycle de conception, qui part d'une spécification temporisée abstraite, et passe par des étapes de décisions d'architecture et de conception dépendant de l'infrastructure visée, correspondant à un raffinement des horloges logiques, contraint par des décisions d'ordonnance et de placements. La version finale (entièrement raffinée) sera soumise à des vérifications de propriétés et de contraintes temporelles. Les analyses des limites de temps (relatives aux différentes horloges ou à une horloge de référence), de la sûreté et de la latence sont discutées par l'étude des conflits de relations entre les horloges logiques du système. Nous utilisons un scénario d'insertion de voitures dans les systèmes de transport intelligents (ITS) comme un exemple pour illustrer l'utilisation de notre modèle timed-pNets. Finalement, l'outil TimeSquare est utilisé pour effectuer une simulation logique et vérifier la validité de notre modèle.

## Acknowledgement

The work described in this thesis was not and could not have been performed in isolation. It involved the help and support of many, to whom I am largely indebted. There are many people I would like to thank who directly or indirectly helped me achieve the milestone of completing this PhD thesis.

Foremost, I thank my PhD advisers Eric Madelaine and Yixiang Chen, for giving all possible support so that I make a successful research work. Thanks you for your encouragement and guidance throughout my research, for giving me opportunity to come to INRIA, Sophia Antipolis and to perform this work together with an enthusiastic team of researchers. Thanks Eric, for all useful discussions and wonderful words of wisdom. He has taught me most of what I know about formal method and supported me during a long period of research. It has been a wonderful time working with you and I couldn't have asked for more from you as my PhD adviser. This thesis would not be possible without you two!

I would like to thank all teachers, researchers, professors in SCALE team, INRIA and Fost team, ECNU for valuable discussions during round table, EPW and also many other occasions. Interacting with you all has always been a great learning experience. Special thanks to Ludovic HENRIO, Fabrice Huet for valuable suggestions. I also would like extend special thanks to Françoise BAUDE for her kindly support during my difficult period. Many thanks to Robert de Simone, Frédéric MALLET and Julien Deantoni for you suggestions on logical time, CCSL and TimeSquare. And thanks all professors and colleges of FOST team in ECNU, especially thanks to Min ZHANG, Tianmin BU, Jie ZHOU, Yanfang MA, etc. for all your supports. I thank all members of administrative staff and research coordinators for helping in many practical things. Special thanks to Christel KOZINSKI, Changbo WANG, Linjuan YE, Linying WU, etc.for their kindly help. I would like to thank all former and present members of my research group SCALE for inspiring research discussions and presentations. Thanks Sophie Song, for always giving an extra effort in making sure I continue my work without losing focus and passion during critical moments. I also would like to give my thanks to my office mate Alexandra Bardiau, even though you went to another world, your kindness will be always in my heart.

Finally, I would like to thank my family for always being there as an anchor of support and strength through all the trials and tribulations. I would like to thank my parents for all of the support, love, and encouragement they have given me. Their direction and advice has been invaluable, and without them, I could not have achieved nearly so much. I also thank my parents-in-law and sister-in-law for all the support they gave me.

Finally, I would like to thank my husband, Quirino Zagarese, for everything he has given to me. There is no other person I am indebted to on so many levels. Academically, his excellence has profoundly influenced me. I have learned uncountable lessons from his rigorous and careful pursuit of "the truth". He has been my sounding board, my expert reader, and my example to follow. For all of these, I thank him. Personally, his love and support has kept me alive and happy for the past three years. I am very lucky to have found such a wonderful person.

My deepest love to you all!

## **Table of Contents**

| A        | ckno           | wledgement                                        | vii |  |  |

|----------|----------------|---------------------------------------------------|-----|--|--|

| 1        | Introduction   |                                                   |     |  |  |

|          | 1.1            | Motivation and Challenges                         | 6   |  |  |

|          | 1.2            | Research Approach                                 | 10  |  |  |

|          | 1.3            | Research Contributions                            | 11  |  |  |

|          | 1.4            | Technical Background                              | 14  |  |  |

|          |                | 1.4.1 Logical Clocks                              | 14  |  |  |

|          |                | 1.4.2 CCSL                                        | 15  |  |  |

|          |                | 1.4.3 TimeSquare Tool                             | 17  |  |  |

|          |                | 1.4.4 pNets Model                                 | 18  |  |  |

|          | 1.5            | Use Case                                          | 22  |  |  |

|          |                | 1.5.1 Vehicle-to-Infrustructure Communications    | 22  |  |  |

|          |                | 1.5.2 Vehicle-to-Vehicle Communications           | 23  |  |  |

|          | 1.6            | The Outline of The Thesis                         |     |  |  |

| <b>2</b> | $\mathbf{Rel}$ | ated Work                                         | 27  |  |  |

|          | 2.1            | Discrete-event Models                             | 28  |  |  |

|          | 2.2            | Synchronous and Asynchronous Communication Models | 30  |  |  |

|          | 2.3            | BIP Framework                                     |     |  |  |

|          | 2.4            | Timed-automata                                    | 34  |  |  |

|          | 2.5            | Timed Petri Nets                                  | 36  |  |  |

|          | 2.6            | AADL                                              | 39  |  |  |

|          | 2.7            | MARTE                                             | 41  |  |  |

|   | 2.8                  | STeC                                                                                                                                               |                                                                                                     | 44 |  |  |

|---|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----|--|--|

|   | 2.9                  | Concl                                                                                                                                              | usion                                                                                               | 45 |  |  |

| 3 | pNe                  | ets Wi                                                                                                                                             | th Timed-Actions and Logical Constraints                                                            | 47 |  |  |

|   | 3.1                  | Model                                                                                                                                              | l Building                                                                                          | 48 |  |  |

|   |                      | 3.1.1                                                                                                                                              | Timed Actions                                                                                       | 48 |  |  |

|   |                      | 3.1.2                                                                                                                                              | Logical Constraints                                                                                 | 48 |  |  |

|   |                      | 3.1.3                                                                                                                                              | Introduce Logical Clocks into pNets Model                                                           | 49 |  |  |

|   | 3.2                  | Simula                                                                                                                                             | ation                                                                                               | 51 |  |  |

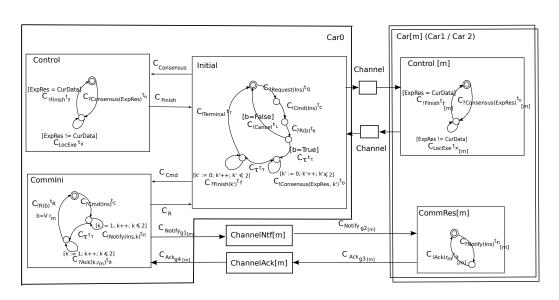

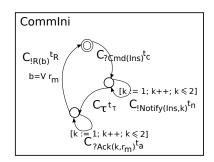

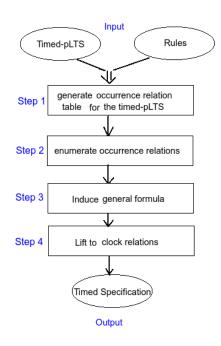

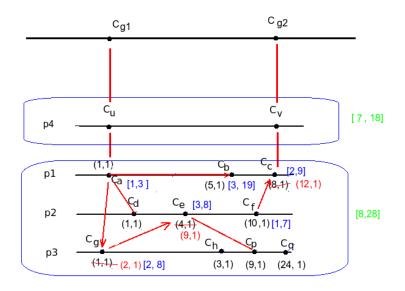

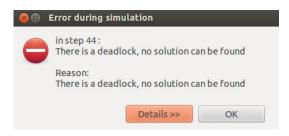

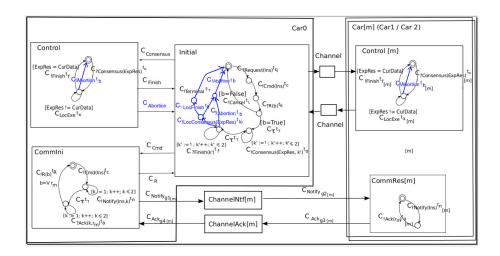

|   |                      | 3.2.1                                                                                                                                              | Formalisation of the Architecture                                                                   | 52 |  |  |

|   |                      | 3.2.2                                                                                                                                              | Result                                                                                              | 54 |  |  |

|   | 3.3                  | Concl                                                                                                                                              | usion $\ldots$     | 55 |  |  |

| 4 | $\operatorname{Tin}$ | ned-pN                                                                                                                                             | Nets Model                                                                                          | 57 |  |  |

|   | 4.1                  | Conte                                                                                                                                              | xt and problematic $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 58 |  |  |

|   | 4.2                  | Timed                                                                                                                                              | l Specification                                                                                     | 59 |  |  |

|   |                      | 4.2.1                                                                                                                                              | Syntax and Semantic of Clock Relations                                                              | 62 |  |  |

|   |                      | 4.2.2                                                                                                                                              | Properties of the logical clock relations                                                           | 63 |  |  |

|   | 4.3                  | Timed                                                                                                                                              | l-pLTS                                                                                              | 66 |  |  |

|   | 4.4                  | Timed-pNets $\ldots \ldots \ldots$ |                                                                                                     |    |  |  |

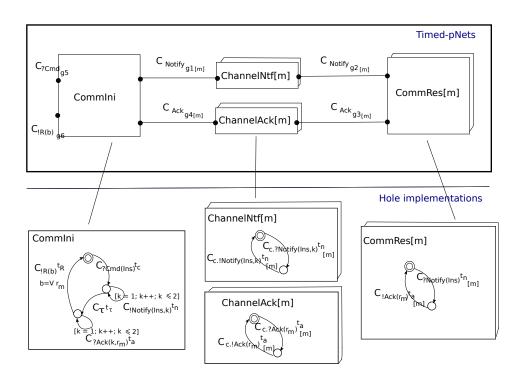

|   | 4.5                  | Generating Timed Specification                                                                                                                     |                                                                                                     | 75 |  |  |

|   |                      | 4.5.1                                                                                                                                              | Generating TS of timed-pLTS                                                                         | 75 |  |  |

|   |                      | 4.5.2                                                                                                                                              | Auxiliary functions: Pre/Post sets                                                                  | 75 |  |  |

|   |                      | 4.5.3                                                                                                                                              | Relations and assignment rules                                                                      | 77 |  |  |

|   |                      | 4.5.4                                                                                                                                              | The Method for Generating Timed Specification                                                       | 79 |  |  |

|   |                      | 4.5.5                                                                                                                                              | Generating TS of timed-pNets                                                                        | 85 |  |  |

|   | 4.6                  | Comp                                                                                                                                               | atibility                                                                                           | 91 |  |  |

|   | 4.7                  | Assem                                                                                                                                              | bling multi-layer timed-pNets system                                                                | 93 |  |  |

|   | 4.8                  | Simula                                                                                                                                             | ation                                                                                               | 95 |  |  |

|   |                      | 4.8.1                                                                                                                                              | Simulation 1:                                                                                       | 95 |  |  |

|   |                      | 4.8.2                                                                                                                                              | Simulation 2:                                                                                       | 96 |  |  |

|   | 4.9                  | Concl                                                                                                                                              | usion                                                                                               | 98 |  |  |

| <b>5</b> | Del            | ay in 7                                                 | Fimed-pNets101                                                                                                                     |  |

|----------|----------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

|          | 5.1            | 1 Context and problematic                               |                                                                                                                                    |  |

|          | 5.2            | Virtual TimeStamps                                      |                                                                                                                                    |  |

|          | 5.3            | Time Constraint Conflicts                               |                                                                                                                                    |  |

|          | 5.4            | Calculate Delays and Delay Bounds                       |                                                                                                                                    |  |

|          |                | 5.4.1                                                   | Causal Clocks and Causality Paths                                                                                                  |  |

|          |                | 5.4.2                                                   | Computing Delays of clocks                                                                                                         |  |

|          |                | 5.4.3                                                   | Computing Delay Bounds of Clocks                                                                                                   |  |

|          | 5.5            | Simulation                                              |                                                                                                                                    |  |

|          |                | 5.5.1                                                   | Encode Properties into TimeSquare                                                                                                  |  |

|          |                | 5.5.2                                                   | Property Checking                                                                                                                  |  |

|          |                | 5.5.3                                                   | Discussion                                                                                                                         |  |

|          | 5.6            | Concl                                                   | usion $\ldots \ldots 120$ |  |

| 6        | $\mathbf{Ext}$ | ension                                                  | of Timed-pNets 121                                                                                                                 |  |

|          | 6.1            | Conte                                                   | $\mathbf{x}$ t and problematic                                                                                                     |  |

|          | 6.2            | Clock                                                   | Partition                                                                                                                          |  |

|          |                | 6.2.1                                                   | Semantics of Precedence Relations on Partition Clocks 125                                                                          |  |

|          |                | 6.2.2                                                   | Semantics of Coincidence Relations on Partition Clocks 127                                                                         |  |

|          |                | 6.2.3                                                   | Partition Clock Property                                                                                                           |  |

|          | 6.3            | Clock Union                                             |                                                                                                                                    |  |

|          | 6.4            | Exam                                                    | ples and Simulations                                                                                                               |  |

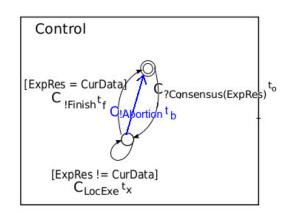

|          |                | 6.4.1 The Timed Specification of "Control" Component 13 |                                                                                                                                    |  |

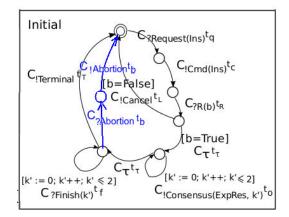

|          |                | 6.4.2                                                   | Timed Specification of "Initial" Component 138                                                                                     |  |

|          |                | 6.4.3                                                   | Simulate the "Control" component                                                                                                   |  |

|          |                | 6.4.4                                                   | Simulate the "Initial" component                                                                                                   |  |

|          | 6.5            | Concl                                                   | usion                                                                                                                              |  |

| 7        | Full           | Use (                                                   | Case 143                                                                                                                           |  |

|          | 7.1            | Use C                                                   | ase                                                                                                                                |  |

|          |                | 7.1.1                                                   | Background of ITS                                                                                                                  |  |

|          |                | 7.1.2                                                   | Car Inserting Use Case Scenario                                                                                                    |  |

|                 |                | 7.1.3   | Properties                                                          |     |     | . 146 |

|-----------------|----------------|---------|---------------------------------------------------------------------|-----|-----|-------|

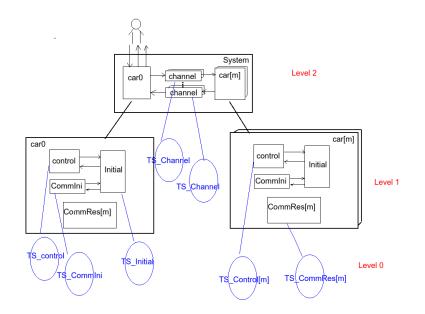

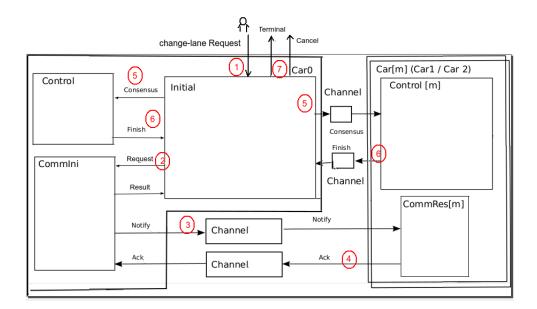

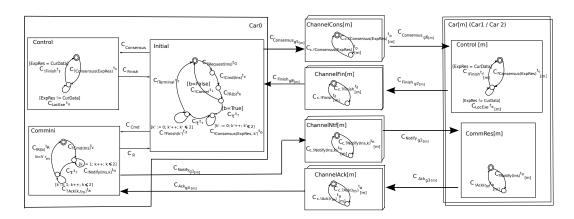

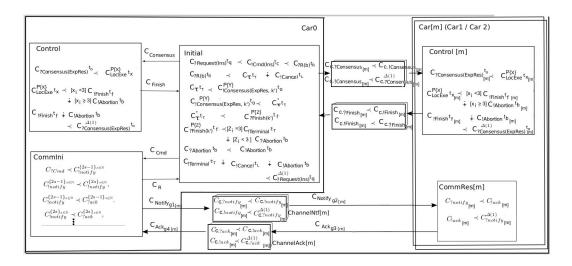

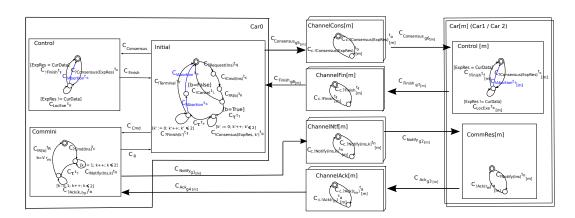

|                 | 7.2            | Build 7 | Timed-pNets Model                                                   |     |     | . 147 |

|                 |                | 7.2.1   | System Structure                                                    |     |     | . 147 |

|                 |                | 7.2.2   | Fill Holes                                                          |     |     | . 149 |

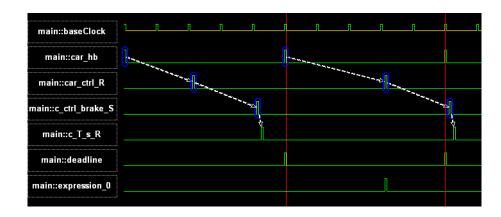

|                 | 7.3            | Simulat | tion                                                                |     |     | . 149 |

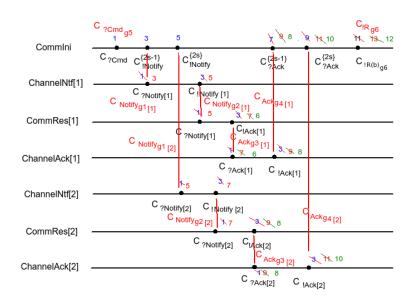

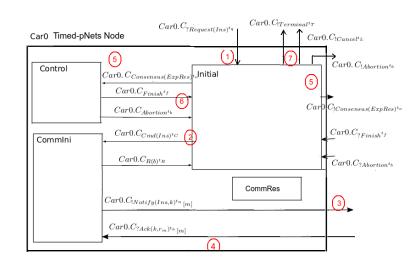

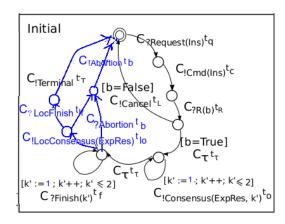

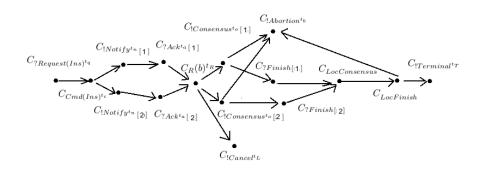

|                 |                | 7.3.1   | Simulate the leaf level                                             |     |     | . 152 |

|                 |                | 7.3.2   | Simulate the middle level                                           |     |     | . 153 |

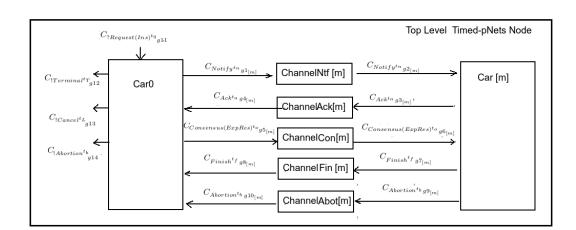

|                 |                | 7.3.3   | Simulate the top level $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |     |     | . 158 |

|                 | 7.4            | Other S | Simulations                                                         |     |     | . 161 |

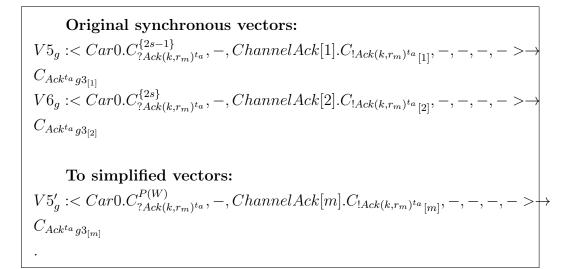

|                 |                | 7.4.1   | Car0 communicates with $m$ cars $(m > 2)$                           |     |     | . 161 |

|                 | 7.5            | Conclus | sion                                                                |     |     | . 163 |

| 8               | Con            | clusion |                                                                     |     |     | 165   |

|                 | 8.1            |         | ry and Conclusions                                                  |     |     |       |

|                 | 8.2            |         | Work                                                                |     |     |       |

|                 |                |         |                                                                     |     |     |       |

| 9               | 附录             | :论文约    | <b>宗述(中文版)</b>                                                      |     |     | 171   |

| Re              | eferei         | ices    |                                                                     |     |     | 176   |

| $\mathbf{Li}$   | st of          | publica | ations                                                              |     |     | 189   |

| list of figures |                |         |                                                                     | 191 |     |       |

| lis             | list of tables |         |                                                                     |     | 193 |       |

## Chapter 1 Introduction

### **1.1** Motivation and Challenges

The world is moving rapidly towards ubiquitous connectivity of smart devices that are interconnected and collaborating, which provides people with a wide range of innovative applications and services. It will further change how and where people associate, gather and share information, and consume media, which may be unimaginable today. The new world creates an unprecedented opportunity to connect not just devices, but peoples, data and processes as well, making networked connections more relevant and valuable.

One typical example is next-generation intelligent transportation systems (ITSs), in which wireless communications are used to exchange information among smart vehicles. These vehicles can communicate with service centers, inform other vehicles of their existence, monitor safety and use the latest road and weather conditions. Communications are needed to support safe driving, curtail traffic congestion and decrease travel delays by improving the way of the overall transportation system and its infrastructure work. The future of automotive safety is not about more airbags or stronger steel. It is about building smarter automobile that can "talk" to each other, so a car knows that another car is about to run a red light and applies brakes to avoid a possible accident. The U.S. Department of Transportation and the National Highway Traffic Safety Administration [91] have approved vehicle-to-vehicle (V2V) communication systems that will pave the way for connected cars to increase safety and reduce accidents. V2V communications can provide the vehicle and driver with 360-degree situational awareness to address additional crash situations. This technology would improve safety by allowing vehicles to "talk" to each other and ultimately avoid many crashes altogether by exchanging basic safety data, such as speed and position, ten times per second. In addition to enhancing safety, these future applications and technologies could help drivers to save fuel and time. Besides, German automakers have launched a pilot program that combines V2V with vehicle-to-infrastructure technology, allowing cars to communicate with each other and with traffic lights.

Not only vehicles, every devices can also connect to each other and communicate to provide better services. These devices include everything from cell phones, coffee makers, washing machines, headphones, lamps, wearable devices and almost anything else you can think of. The connection and communication of these devices bring a huge potential value to our life. For example, when you are on your way to a meeting, your car could have access to your calendar and already know the best route to take. If the traffic is heavy your car might send a text to the other parties to notify them that you will be late. It is also possible that your alarm clock can wake up you at 6 am and then notify your coffee maker to start brewing coffee for you. Also it will happen that your office equipment knows when it is running low on supplies and automatically re-orders more. And the wearable device you used in the workplace could tell you when and where you were most active and productive and share that information with other devices that you used while working. All these applications can help us reduce waste and improve efficiency and energy use. They will help us understand and improve how we work and live.

To realize the systems we expect especially for the efficiency we mentioned, very often it is necessary to consider real-time aspects of communication behaviours: quantitative information about time elapsing has to be handled explicitly. This can be the case to describe a particular behaviour (for instance, a time-out) or to state a complex property (for example, "the alarm has to be activated within at most 10 time units after a problem has occurred").

The real-time aspects for centralized systems such as embedded systems have been discussed for more than a decade. Usually, the communications in centralized systems are simple (synchronized communications) and limited (fixed number of communications are generated in a closed embedded system). Even though some systems include complex communications (asynchronous communication), the response time of the communications can be

### Introduction

measured by a global physical clock. Comparing to the centralized systems, the decentralized system in the next generation world will generate large quantities of communications. These communications are created by millions of diverse devices periodically sending observations about certain monitored phenomena or reporting the occurrence of certain abnormal events of interest [88]. Furthermore, distributed smart devices in our future system may have their own clocks and the time measurements of the behaviour of each device are based on the physical clock of the device. The fact that no common physical global clock exists causes the most typical problems of the next generation heterogeneous distributed systems. The time measurement of communication behaviour and deadlock detection are much more difficult to solve in a distributed environment than in a classical centralized environment.

Besides, depending on communications between these distributed smart devices, the distributed systems can be classified as either synchronous or asynchronous. Synchronous communication is direct communication where time is synchronized. This means that all parties involved in the communication are present at the same time and ready to accept input signals. Asynchronous communication is the exchange of messages with a certain time lag between sending and responding. This means that the data in asynchronous communication can be transmitted intermittently. Future systems need the collaboration of synchronous and asynchronous communication. Furthermore, future distributed sensors, actuators, and smart devices with both deterministic and stochastic data traffic require a new paradigm for timed communication behaviour model that goes far beyond traditional methods. The interconnection topology of smart devices is dynamic and the system infrastructure can also be dynamically reconfigured in order to contain system disruptions or optimize system performance. There is a need of novel distributed communication models for dynamic topology control.

When talking about asynchronous communications models of distributed systems, most published research is based on the time-free model [13] [37],

[47]. In these models, the specifications describe what outputs and state transitions should occur in response to inputs, without placing any bounds on the time it takes for these outputs and state transitions to occur. This kind of free-time models are of importance in practice, such as consensus, election, or membership. However, investigating time properties (e.g. if system behaviours can be successfully executed before a certain deadline [78]) in distributed systems become important aspects. So we need a timed asynchronous distributed system model (or, for short, a timed model) where all the behaviours are timed: their specification prescribes not only the outputs and state transitions that should occur in response to inputs, but also the time intervals within which a client can expect these outputs and transitions to occur.

As we know, formal methods provide powerful techniques for specifying and verifying complex distributed systems. Most formal methods strive for simplicity, to allow for efficient analysis. A formal model can be very abstract, capturing precisely those aspects that are to be analysed, or can be very detailed, trying to capture as many of the design aspects as possible. Formalisms to construct mathematical models of systems include process algebra, labelled transitions systems, finite state automata, petri nets, and markov chains. All have their particular views on a system and focus on particular aspects. Design a formal model for the distributed systems and assess the correctness of the design of the system especially taking the time constraints into account is a difficult problem, because distributed systems have complex communication mechanisms and lack of a common physical clock. The mix of synchronous and asynchronous communications, as well as the possible time bound requirement in the distributed systems may lead to incorrect behaviours. This requires us to check the correctness of the formal models in terms of property requirements. If the required properties are satisfied, the result should have a meaningful interpretation for the verification of the actual design. Formal models for modeling time constrained systems include timed automata [4], timed petri net [94], AUTOSAR [55], STeC [39],

BIP [14], etc. Each of them has its own special advantages, but, as far as we know, all of them use physical global time variables for time constraints, which does not match our goal of avoiding using a global common time when building models.

### 1.2 Research Approach

Heterogeneous distributed systems, as targeted in this thesis, can be characterized by the fact that the processors are spatially separated and that a common time base does not exist. Distinct processors in such systems communicate with each other by exchanging messages with an unpredictable (but non-zero) transmission delay. Each action in those processors is either a local step of a process, a send action, or a receive action. Since the processors in the systems may neither have synchronized clocks nor common physical time base, the logical order of the actions may not agree with the clock times associated with them. For example, we expect a logical view of the system in which the send action for a given message happens before the receive action for that message. However, if the clocks at the sender and the receiver are sufficiently skewed, a clock-based trace of the events might report that the receive occurred before the send.

One solution of this problem is to run algorithms to keep clocks closely synchronized, within some tolerance. In the Internet world, this is typically done with the Network Time Protocol (NTP). NTP is one of the earliest Internet protocols used and is probably one of the most used protocols today. However, it is much complicated and may cause problems by drastically changing time [70].

A better and simpler approach is to maintain logical clocks at the processors. Time-constrained models for distributed systems should take advantage of the system logical nature. The fact that one action causally affects another makes it possible to determine the practical order among actions. We use the concept of logical time to capture the causal relations of actions, which do not rely on a real time/clock. By this way, we are able to assign time values to actions such that it is possible to infer potential causality between these actions or to exclude causal influence in the sense that a "later" action cannot affect an "earlier" action.

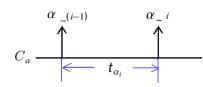

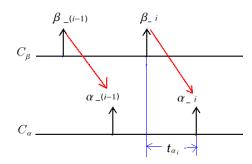

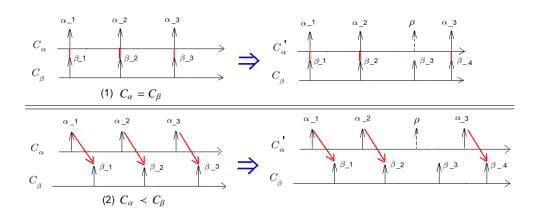

To reflect the fact that the actions in a processor can repetitively occur and their causality relations keep the same, we define a logical clock as a sequence of repetitive occurrences of an action. A logical clock does not "tick" like a real time clock that is equally spaced, but instead keeps track of the order of action occurrences. Furthermore, inspired by the CCSL model [7] (the detail technique background of CCSL is presented in section 1.4), we define clock relations to specify logical time constraints between clocks. In distributed systems, as communication between processors is either synchronous or asynchronous, we choose the basic CCSL clock relations like coincidence and precedence to specify synchronous and asynchronous communications. We propose a novel way of modeling distributed systems by building system logical clocks and clock relations (called timed specification). A timed specification is usually used to specify the behaviour of a processor. Since a clock relation of two clocks is applied on all corresponding action occurrences of them, we can ensure that these action occurrences are assigned consistent logical times according to the relations between clocks. Then we employ time specifications into pNets(parameterized networks of synchronized automata) [13] to build a hierarchical structure of timed specification framework. The timed specification in a higher level is an abstraction of it low level subsystems. In our design model, by analyzing the inherent conflicts that might exist in the timed specifications, we check the logical correctness of the systems.

### **1.3** Research Contributions

In this thesis, we attempt to build a formal timed model (called timedpNets) by introducing a set of logical clocks and clock relations into an

### Introduction

untimed model called pNets (parameterized networks of synchronized automata) [13]. In this novel model, timed specifications (a set of logical clocks and clock relations) are used to specify the system behaviours, and furthermore, be used to build a hierarchical structure by composing the timed specifications of subsystems. By taking advantage of the timed specifications, system time constraints and properties (e.g. safety, latency properties) can be specified and verified. The main contributions of the thesis are as follows.

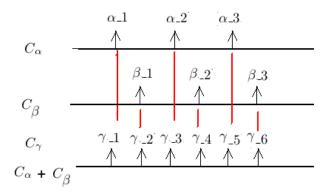

We design a novel model that is capable to specify logical time constraints in terms of system behaviours without relying on physical clocks (ref. chapter 3). In this new model, logical clock relations in bottom-level (synchronous) components are derived from the corresponding label transition systems ( called timed-pLTS). Usually logical clocks are a priori independent. They become dependent when the instants (or the timed-action occurrences) from different clocks are linked by relationships (e.g. coincidence or precedence). Instead of imposing local dependencies between the instants (or the timed-action occurrences), we impose dependencies directly between clocks. A clock relation specifies many (usually an infinity of) individual time instant relations. As a result of adding clock relations to multiple clocks, these clocks are no longer independent and the instants (or the timedaction occurrences) are partially ordered. This partial ordering of instants characterizes the time specifications (TSs) of an application.

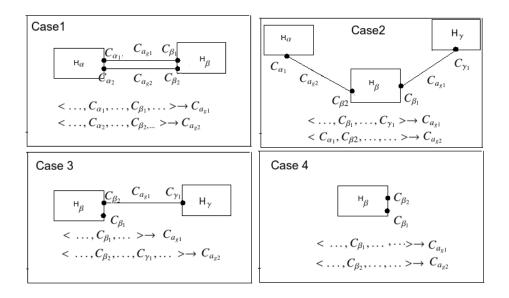

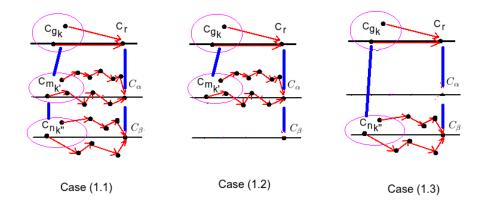

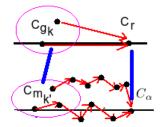

Timed specifications (TSs) are logical characterizations, that can be either provided by the application designer, or computed from the model. The consequence is that the two procedures above can be used arbitrarily in a bottom-up fashion, starting with detailed timed-pLTSs and assembling them in a compatible way; or in a top-down fashion, constructing TSs for abstract timed-pNets, using their holes TSs as hypotheses in an assume-guarantee style, and providing later some specific (compatible) implementations for these holes in various contexts. As our model has a hierarchical structure, the timed specification of an upper layer must be compatible with the timed specifications of its subnets (or subsystems). In order to be able to build a compatible model, we discuss the compatibility of refined implementations and abstract specifications. Moreover, we propose a theorem to generate a compatible structure of timed-pNets (ref. chapter 4).

Since the model does not rely on common physical clocks, the delays in the timed specifications that come from different subnets are uncomparable, which brings the difficulty of building a higher layer structure especially when the delays are taken into account. To solve the issue, we introduce the concept of reference clocks and virtual timestamps into our model so that the delays can be calculated in terms of a reference clock that a user choose (ref. chapter 5). The introducing of a reference clock also helps us to specify delay bounds and latency properties that are important aspects for a timed model. Therefore, this model has the capability of checking not only system's correctness and safety properties, but also the timed properties (e.g. deadline, latency properties).

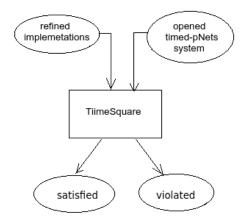

The fact of using timed specifications in the new model paves the way of utilizing the TimeSquare tool to check system time constraint conflicts. Thanks to the timed specifications, timed-pNets are able to represent the basic behaviours of heterogeneous distributed systems. However, when facing to complex behaviours (e.g. undetermined clock choices), the current timed specifications are not easy to specify them. To simplify the way of encoding the complex situations, we design the concept of clock partition and clock union (ref. chapter 6). The clock partition allows us to flexibly split the timed-action occurrences into groups so that the clock relations can be applied to the groups instead of to every single occurrence. We prove that the relations (precedence and coincidence relations) on partition clocks can be substituted by those relations on a set of filtered clocks, which illustrates the advantages of using partition clocks: simple and easy to understand. Another extension, clock union, provides us a way to compose logical clocks. Usually it is used to specify the branches of transition systems.

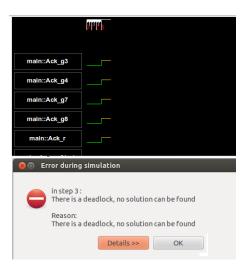

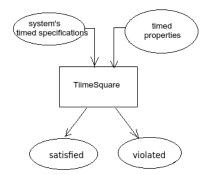

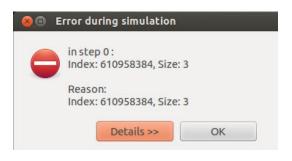

In the end, to gain insight into our model, we apply our model on the Intelligent Transportation Systems (ITSs). We choose the TimeSquare [41] tool to do simulation (ref. chapter 7). TimeSquare is a software environment for modelling and analyzing of timed systems. It displays possible time evolutions as waveforms generated in the standard VCD format (more information of TimeSquare are introduced in the next section). Errors can be reported if conflicts exist in timed specifications.

As a conclusion, we contribute to design a formal model that provides a simple and flexible way to model communication behaviours (synchronous and asynchronous) with time constraints without relying on physical clocks. This is the main difference with other current timed models. Moreover, our model is able to check the logical correctness and verify time properties of distributed systems.

### 1.4 Technical Background

In this section, we introduce the technique background of timed-pNets, including logical clocks, CCSL, TimeSquare and pNets.

### 1.4.1 Logical Clocks

The logical nature of time is of primary importance when designing or analyzing distributed systems. The concept of logical clocks was first introduced by Leslie Lamport in 1978 to represent the execution of distributed systems [58]. It has then been extended and used in distributed systems to check the communication and causality path correctness [45]. The logical clock timestamps each event with an integer value such that the resulting order of events is consistent with a happened-before relation. Logical time has also been intensively used in synchronous languages [23] [20] for its multiform nature. The multiform nature of logical time consists in the ability to use any repetitive event as a reference for the other ones. It is then possible to express temporal properties between various references. In the synchronous domain it has proved to be adaptable to any level of description, from very flexible causal time descriptions to very precise scheduling descriptions [30].

Based on Lamport's logical clock, two more advanced logical clock (vector clock and matrix clock) have been proposed to capture causality between events of a distributed computation. Vector clock is proposed in order to retain the complete partial order information in a logical clock system. It is represented by an n-dimensional vector. Such clocks have been introduced and used by several authors. Parker et al. used in 1983 a very rudimentary vector clocks system to detect inconsistencies of duplicated data due to partitioning [72]. Liskov and Ladin proposed a vector clock system to define highly available distributed services [63]. The theory associated to these vector clocks has been developed in 1988 independently by Fidge [46] [45], Mattern [67] and Schmuck [76]. Similar clocks systems have also been proposed and used by Strom and Yemini [81] to implement an optimistic recovery mechanism, and by Raynal to prevent drift between logical clocks [73]. Another advanced logical clock called matrix clock is represented by an  $n \times n$ matrix. Such a clock system has been proposed in 1984 by Wuu and Bernstein [90] to discard obsolete information of a log system. A similar mechanism has also been used by Lynch and Satin in 1987 for a similar purpose [75].

The aim of the logical time is to be able to timestamp consistently events in order to ensure some properties such as liveness, consistency, fairness, etc. In order to coordinate distributed processes, Jefferson proposed virtual time (or logical time, model time) [54] in 1985 for the causally connected distributed time. The virtual time is implemented with an optimistic time warp mechanism that is able to process messages quickly with independent of the future messages. The aim of using such virtual time is to ensure that the simulation program has the liveness property. The logical time is nothing else than the logical counterpart of the physical time offered by the environment and used in real-time applications [22].

### 1.4.2 CCSL

Logical time has been proved very useful to model heterogeneous and concurrent systems at various abstraction levels. The Clock Constraint Spec-

### Introduction

ification Language (CCSL) [7] uses logical clocks as first-class citizens and supports a set of (logical) time patterns to specify the time behaviours of systems. It is initially specified in an annex of MARTE [92], providing an expressive set of constructs to specify causality (both synchronous and asynchronous) as well as chronological and timing properties of the system models.

CCSL is a declarative language that specifies constraints imposed on the logical clocks of a model. A CCSL clock is defined as a sequence of clock instants (event occurrences). If c is a CCSL clock, for any  $k \in \mathbb{N}$ , c[k] denotes its  $k^{th}$  instant. Below, we describe only the constraints used in this thesis. A comprehensive description of CCSL constructs can be found in [7].

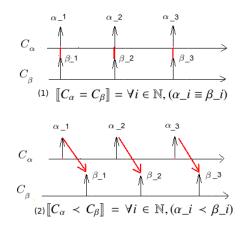

The basic clock relations can be classified in three main categories: 1) coincidence-based constraints, 2) precedence-based constraints, and 3) mixed constraints.

Synchronous constraints rely on the notion of coincidence of clock instants. For example, the clock constraint  $c_1$  isSubclockOf  $c_2$ , denoted by  $c_1 \subset c_2$ , specifies that each instant of  $c_1$  must coincide with an instant of  $c_2$ . In logical words this says that  $c_1$  ticks only if  $c_2$  ticks. Another example is coincidence constraint ( $c_1$  coincides  $c_2$ ), denoted by  $c_1 \equiv c_2$ . It is a special case of subclocking, when there is a bijection between the sets of instants of the two clocks. It states that  $c_1$  ticks if and only if  $c_2$  ticks. Other examples of synchronous constraints are excludes (denoted  $\ddagger$ ) or discretizedBy. The former prevents two clocks from ticking simultaneously. The latter discretizes a dense clock to derive discrete chronometric clocks, mostly from IdealClk, a perfect dense chronometric clock, predefined in MARTE Time Library [8], and assumed to follow "physical time" faithfully (without jitter).

Asynchronous constraints are based on instant precedence, which may appear in a strict  $(\checkmark)$  or a non-strict  $(\checkmark)$  form. The clock constraint  $c_1 isFasterThan c_2$  (denoted  $c_1 \leq c_2$ ) specifies that clock  $c_1$  is (non-strictly) faster than clock  $c_2$ , that is for all natural number k, the  $k^{th}$  instant of  $c_1$  precedes or coincides the  $k^{th}$  instant of  $c_2$  ( $\forall k \in \mathbb{N}, a[k] \leq b[k]$ ). The constraint  $c_1 \prec c_2$  specifies that clock  $c_1$  is strictly faster than clock  $c_2$ , that is for all natural number k, the  $k^{th}$  instant of  $c_1$  precedes the  $k^{th}$  instant of  $c_2$  ( $\forall k \in \mathbb{N}, a[k] \prec b[k]$ ).

Mixed constraints combine coincidence and precedence. For example, The constraint  $c_3 = c_1 \ delayedFor \ n \ on \ c_2$  enforces a delayed coincidence, i.e., imposes  $c_3$  to tick synchronously with the  $n^{th}$  tick of  $c_2$  following a tick of  $c_1$ . It is considered as a mixed constraint since  $c_1$  and  $c_2$  are not assumed to be synchronous.

Moreover, CCSL includes clock expressions that define a set of new clocks from existing ones. A CCSL specification consists of clock declarations and conjunctions of clock relations between clock expressions. All these clock relations and clock expressions constitute the kernel of CCSL.

### 1.4.3 TimeSquare Tool

TimeSquare [41] is a software environment dedicated to analyze timed systems specified with clock constraints using the CCSL language [7]. It is composed of a set of Eclipse plugins and has been integrated into the Open-EmbeDD platform. It developed with Ganymede Eclipse Modeling Tools: ANTLR for constraint parsing, and JavaBDD for the solver.

TimeSquare has four main functionalities: 1) interactive clock-related specifications, 2) clock constraint checking, 3) generation of a consistent temporal structure, using a Boolean solver, 4) displaying and exploring wave-forms, written in the IEEE standard VCD format.

TimeSquare has been designed to be used with the UML tools applying the MARTE profile. In this profile, clocks and clock constraints are associated with various model elements. A wizard is included in TimeSquare. It facilitates clock definitions, clock constraint specifications, model element browsing, and parameter setting. The second functionality checks constraint sanity. The third functionality relies on a constraint solver that yields a satisfying execution trace or issues an error message in case of inconsistency. The traces are given as waveforms written in VCD format. VCD (Value

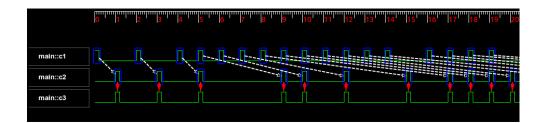

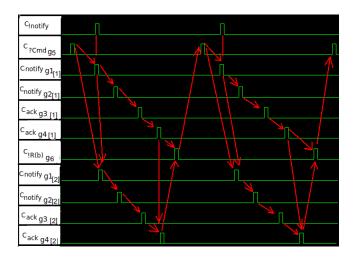

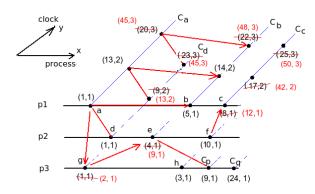

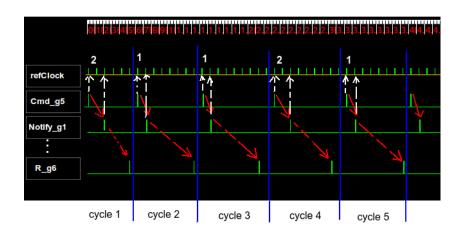

Fig. 1.1: VCD view of an example

Change Dump) is an IEEE standard textual format for dump files used by EDA (Electronic Design Automation) logic simulation tools. The solver intensively uses Binary Decision Diagrams (BDD). Waveforms can be displayed with any VCD viewer. TimeSquare has its own viewer enriched with interactive constraint highlighting and access facilities. For instance, the screen copy in Figure 1.1 shows precedence relations (white oblique dashed arrows) and coincidence relations (red vertical solid lines).

### 1.4.4 pNets Model

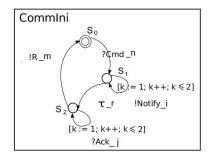

We build our behavioral semantic model by introducing logical clocks into pNets (parameterized networks of synchronized automata) [13]. pNets is an expressive and flexible semantic model for the modeling and verification of (untimed) distributed systems. pNets are networks of processes: they provide a hierarchical structure to organize processes. At the leaves of the structure, they have pLTS (parameterised labelled transition systems) describe in the definition II. Definition II describes the hierarchical composition. pNets are d To encode both families of processes and data value passing communications, parameters are used in pNets as communication arguments. The parameters is a set P of variables. The P is supposed to be defined globally, but it can also be defined locally in each pNet. The usage of parameters enables compact and generic description of parameterized and dynamic topologies. In the following part we recall definitions of pLTS and pNets. We start by giving the notion of parameterized actions that are basic elements for pLTSs. Parameterized Actions have a rich structure, because they take care of value passing in the communication actions, assignment of state variables and process parameters.

**Definition I** [Parameterized Actions] Let P be a set of parameter names,  $\mathcal{L}_{\mathcal{A},\mathcal{P}}$  a term algebra built over P, including at least a distinguished sort A for actions, and a constant action  $\tau$ . We call  $v \in P$  a parameter, and  $a \in \mathcal{L}_{\mathcal{A},\mathcal{P}}$  a parameterized action,  $\mathcal{B}_{\mathcal{A},\mathcal{P}}$  is the set of boolean expressions (guards) over  $\mathcal{L}_{\mathcal{A},\mathcal{P}}$ .

The behaviour of a process is modelled as a parameterized labelled transition system (pLTS), in which the variables can be written and read by the actions performed in the transitions. A pLTS can have guards and assignment of variables on transitions. Variables can be manipulated, defined, or accessed inside states, actions, guards, and assignments. Parameters are used both for encoding data in value passing messages and for manipulating indexed families of processes.

**Definition II** [pLTS] A parameterized LTS is a tuple  $\langle P, S, s_0, L, \rightarrow \rangle$ where:

- P is a finite set of parameters, from which we construct the term algebra *L*<sub>A,P</sub>,

- S is a set of states; each state  $s \in S$  is associated to a finite indexed set of free variables  $fv(s) = \tilde{x}_{J_s} \subseteq P$ ,

- $s_0 \in S$  is the initial state,

- L is the set of labels,  $\rightarrow$  the transition relation  $\rightarrow \subset S \times L \times S$ ,

- Labels have the form  $l=<\alpha, e_b, \widetilde{x}_{J_{s'}}:=\widetilde{e}_{J_{s'}}>$  such that if  $s\to s'$  , then:

- $-\alpha$  is a parameterized action, expressing a combination of inputs  $iv(\alpha) \subseteq P$  (defining new variables) and outputs  $oe(\alpha)$  (using action expressions),

- $-e_b \in \mathcal{B}_{\mathcal{A},\mathcal{P}}$  is the optional guard,

- the variables  $\widetilde{x}_{J_{s'}}$  are assigned during the transition by the optional expressions  $\widetilde{e}_{J_{s'}}$  with the constraints:  $fv(oe(\alpha)) \subset iv(\alpha) \cup \widetilde{x}_{J_s}$  and  $fv(e_b) \cup fv(\widetilde{e}_{J_{s'}}) \subseteq iv(\alpha) \cup \widetilde{x}_{J_s} \cup \widetilde{x}_{J_{s'}}$ .

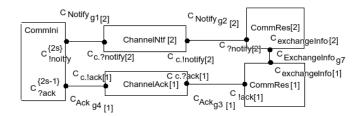

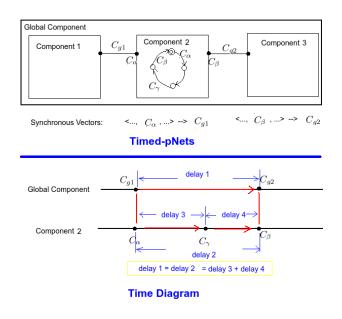

pNets are constructors for hierarchical behavioural structures: a pNet is formed of other pNets, or pLTSs at the bottom of the hierarchy tree. A composite pNet consists of a set of subnets, each exposing a set of actions. The synchronisation between a global action of the pNet and the actions of the subnets is given by synchronisation vectors [10] with the form  $\langle \alpha_i, \ldots, \alpha_j \rangle \rightarrow \alpha_g$ : a synchronisation vector synchronises one or several actions of subnets, and exposes a single resulting global action  $(\alpha_g)$ . The synchronous vectors are used to synchronise a (potentially infinite) number of processes. A pNet can either compose sub-pNets given explicitly, or be used as an operator accepting other pNets as parameters. Placeholders for the pNets that will be provided later are called holes. Actions synchronised in synchronisation vectors can involve both some sub-pNets that are given in the definition and some other that will be provided later. The holes in pNets can be indexed by a parameter, to represent (potentially unbounded) families of similar arguments. We represent the definition of pNets taken from [13] as follows:

**Definition III** [pNets] A pNet is a tuple  $\langle P, pA_G, J, \tilde{p}_J, \tilde{O}_J, \vec{V} \rangle$ where: P is a set of parameters,  $pA_G \subset \mathcal{L}_{\mathcal{A},\mathcal{P}}$  is its set of (parameterized) external actions, J is a finite set of holes, each hole j being associated with (at most) a parameter  $p_j \in P$  and with a sort  $O_j \subset \mathcal{L}_{\mathcal{A},\mathcal{P}}$ .  $\vec{V} = \{\vec{v}\}$  is a set of synchronisation vectors of the form:  $\vec{v} = \langle \alpha_g, \{\alpha_t\}_{i \in I, t \in B_i} \rangle$  such that:  $I \subseteq J \land B_i \subseteq Dom(p_i) \land \alpha_i \in O_i \land fv(\alpha_i) \subset P.$

Each hole in the pNet has a parameter  $p_j$ , expressing that this "parameterized hole" corresponds to as many actual processes as necessary in a given instantiation of its parameter. In other words, the parameterized holes express parameterized topologies of processes synchronised by a given Net. Each parameterized synchronisation vector in the pNet expresses a synchronisation between some instances ( $\{t\}_{t\in B_i}$ ) of some of the pNet holes ( $I \subseteq J$ ).

The hole parameters being part of the variables of the action algebras can be used in communications and synchronisations between the processes.

The pNets allow to model a large variety of synchronisation mechanisms and have been traditionally used for systems of either synchronously or asynchronously communicating objects, and of distributed components [13]. The flexibility of the synchronisation vectors mechanism naturally provides descriptions of heterogeneous systems, from point-to-point or multipoint synchronisations, to sophisticated asynchronous queuing policies. It is a lowlevel semantic model, supporting a large variety of parallel operators and communication mechanisms that are flexible enough to address a large set of distributed programming concepts. pNets can be used typically as the target of behaviour semantics for same high level language. For example, [13] gives the semantics of the component based framework in terms of pNets. Parametrization and hierarchy also makes pNet models compact, and close to the program structure, and as a consequence easy to generate in a compositional way [6]. Its parameterized and hierarchical features can build a tree like structure in which each node is pNets and leaves are pLTSs. Each pNets node, which can also be presented as a pLTS, is an upper layer abstract node composed by its subsystems in terms of the communication behaviours among them. The parameterized models have successfully been used for modelling ProActive [35] that is a pure Java implementation of distributed active objects with asynchronous remote method calls and replies. It has been proven that the pNets are suitable as a specification language for the distributed systems, and for the models resulting from static analysis of source code. Moreover, the model enables us to have a finite representation of infinite systems. It naturally encodes the semantics of languages for distributed applications.

All these incomparable advantages attracted us to choose it for modelling distributed systems. However, pNets have no mechanism to describe system time constraints.

## 1.5 Use Case

In this section, we represent two use cases taken from ITS. One is vehicleto-infrastructure communication application which intends to avoid vehicles accidents and to increase environmental benefits by wireless exchange of critical data between vehicles and highway infrastructures. Another is a vehicle-to-vehicle communication application that offers the opportunity for significant safety improvements by dynamic wireless exchange of data between nearby vehicles. The two cases will be used from the chapter 3 to the chapter 7 to explain our approach of building semantic behaviour models.

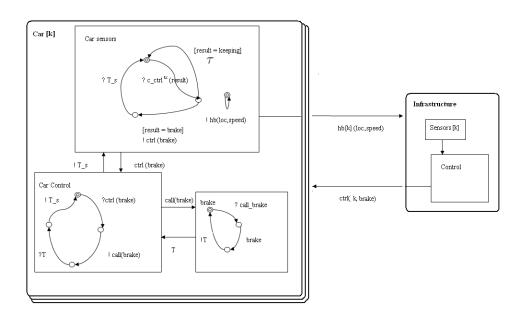

#### **1.5.1** Vehicle-to-Infrustructure Communications

We present a use case called speed controlling system taken from [91]. The speeds of cars are monitored by an infrastructure that collects information from cars and sends brake signals back to cars if they exceed the speed limit. To realize it, the cars in a highway keep on sending signal "I'm here" with their location and speed data. The infrastructure along the highway collects the heartbeat signals and checks the speeds of those cars. If the speed of a car exceeds the speed limit of the highway, the infrastructure will send a "brake" signal to let the car to reduce its speed. The communication protocol is described as follows:

- Cars send heartbeat signals "I'm here" with parameters "(location, speed)";

- A infrastructure collects heartbeat signals from cars;

- The infrastructure sends "brake" signal to the cars that exceed the speed limit;

- The cars reduce their speed when they get the "brake" signals.

We require that the cars can receive brake signals and response to the infrastructure before sending the next heartbeat signal. This use case will

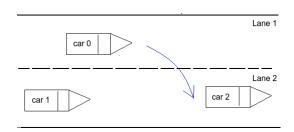

Fig. 1.2: Car Insertion

be simulated in chapter 3.

#### **1.5.2** Vehicle-to-Vehicle Communications

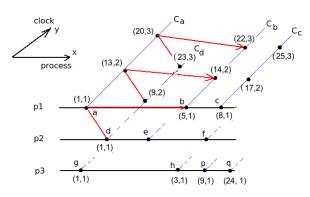

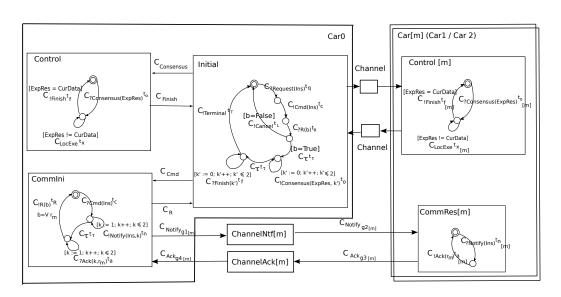

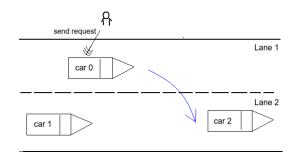

We choose another small scenario on vehicle-to-vehicle communications. It is about an autonomous lane change involving 3 smart cars. These cars are equipped with sensors to detect the physical environments and parameters (e.g. such as the speeds and distances of the cars). And they communicate among each other to coordinate their movements and avoid collisions. Assume three vehicles (car0, car1 and car2) are running on a road as Fig. 7.1.

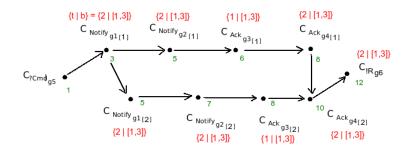

The scenario of inserting car0 between car1 and car2 may follow the following steps: 0) car0 gets a change-lane request (e.g. from a human user); 1) car0 sends "notify" requests to car1 and car2 to get an agreement; 2) car1 (resp. car2) acknowledges car0 "yes" or "no"; 3) car0 collects results from car1 and car2; 4) If both car1 and car2 answer "yes", car0 signals the consensus to car1 and car2 and then go to step 5, otherwise car0 aborts the procedure; 5) car1 slows down and/or car2 speeds up to leave more space between them for car0; 6) car0 changes its direction and moves to lane2; 7) car0 notifies the end of the procedure with a "finish" signal.

We require that the system has no deadlock or clock relation conflicts. Furthermore, assuming that the network communication delay is less than 10 time units, we require that the latency from sending notifications to finishing collecting all acknowledgements is no more than 30 time units. And the latency of whole procedure from car0 getting change-lane requests to sending "finish" signals is no more than 55 time units.

This use case will be used to explain the timed-pNets model in the chapters 4, 5 and 6. Moreover, the full simulation is represented in chapter 7.

## 1.6 The Outline of The Thesis

The rest of the thesis has been organized as follows.

- chapter 2 discusses related works and carefully investigates some time models like timed-automata, timed petri Nets, MARTE and AADL that are famous on modelling real-time systems.

- chapter 3 generalizes a novel semantic model by introducing logical clocks and clock relations into pNet so that it has the capability of modeling time constrained distributed systems.

- chapter 4 describes a communication behavioural semantic model called timed-pNets. It is an extension of chapter 3. Timed-pNets build a hierarchical structure of timed specifications by which the system timed constraints can be specified in a more compatible and easier way. Moreover we discuss the compatibility and refinement of timed specifications, as well as the property checking. We demonstrate that timed-pNets are able to model the timed constrained communication behavior for heterogeneous distributed systems that include synchronous and asynchronous communications.

- chapter 5 discusses how to compute the delays and delay bounds in timed-pNets. Moreover, we define the concept of time conflicts and propose a way to detect them.

- chapter 6 discusses advanced extensions of timed-pNets, including clock partition and clock union for simplify the timed specifications.

- chapter 7 represents the full details of car insertion use case to demonstrate how we build and refine a timed-pNets model and check its safety and timed properties.

- chapter 8 concludes our work and represents future works.

# Chapter 2 Related Work

If you want to understand today, you have to search yesterday.

Pearl Buck, American female writer

Our idea of avoiding using any common physical clock when modelling distributed systems leads us to investigate logical time and some existing time models. This chapter starts from introducing discrete-event model to understand how system behaviours are specified by taking advantage of events. Then we investigate globally asynchronous locally synchronous (GALS) model including HipHop to understand how synchronous and asynchronous communications are handled. BIP, as a framework for the incremental composition of heterogeneous components, is also investigated. Moreover, we carefully investigate some time models like timed-automata, timed petri net, MARTE and AADL that are famous on modelling real-time systems. Other time related systems like STeC are introduced to see how they specify time and location constraints for actions.

#### Related Work

Model-integrated development [53] [56] commonly uses actor-oriented software component models [60] [61]. In such models, software components (called actors) execute concurrently and communicate by sending messages via interconnected ports [71] [29]. Examples that support such designs include Simulink, LabVIEW, SystemC, SysML, UML and pNets.

A well-defined actor-oriented model of computations (MoCs) should always has well-defined semantics. One of the key challenges is to integrate actor-oriented models with practical and realistic notions of time. For example, when modeling distributed behaviours, it is essential to provide multiform models of time. The frameworks that include a semantic notion of time, such as Simulink, assume that time is homogeneous in the sense that it advances uniformly across the entire system. In practical distributed systems, even those as small as systems-on-chip, however, no such homogeneous notion of time is measurable or observable. In a distributed system, even though it uses network time synchronization protocols (such as IEEE 1588 [62]), local notions of time will differ. So when introducing time into the pNets model, we should carefully handle the notions of time. Failing to model such differences of time could cause errors in the design.

Based on the idea of logical time, the related models such as discreteevent models, asynchronous language models and so on have been proposed. Besides, some formal models or frameworks with time constraints have also been proposed to describe timed systems. Here we list and describe these previous works that relate to our work.

## 2.1 Discrete-event Models

Discrete-event (DE) [36] [59] [93] models are formal system specifications that have analyzable deterministic behaviours. DE models are concurrent compositions of components that interact via events. An event is a timestamped value, where time is "logical time" or "modeling time" [58]. Correct execution of such models requires respecting the order of time stamps. Using a global, consistent notion of time, DE components communicate via time-stamped events. DE models have primarily been used in performance modeling and simulation, where time stamps are a modeling property bearing no relationship to real time during execution of the model.