# Evaluation of a multiple criticality real-time virtual machine system and configuration of an RTOS's resources allocation techniques

Mohamed El Mehdi Aichouch

## ▶ To cite this version:

Mohamed El Mehdi Aichouch. Evaluation of a multiple criticality real-time virtual machine system and configuration of an RTOS's resources allocation techniques. Electronics. INSA de Rennes, 2014. English. NNT: 2014ISAR0014. tel-01127450

# HAL Id: tel-01127450 https://theses.hal.science/tel-01127450

Submitted on 7 Mar 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Evaluation of a Multiple Criticality Rea-Time Virtual Machine System and Configuration of an RTOS's Resources Allocation Techniques

Thèse soutenue le 28.05.2014 devant le jury composé de :

#### Isabelle Puaut

Professeur à l'université de Rennes 1 / Président

#### **Laurent Pautet**

Professeur à Télécom Paris-Tech / rapporteur

### François Verdier

Professeur à l'université de Nice-Sophia Antipolis / rapporteur

#### Jean-Luc Béchennec

Chargé de recherche à l'IRRCyN CNRS UMR 6597 à Nantes / examinateur

#### Jean-Christophe Prévotet

Maître de conférence à l'INSA de Rennes / Co-encadrant de thèse

#### **Fabienne Nouvel**

Maître de conférence à l'INSA de Rennes / Directeur de thèse

# Evaluation of a Multiple-Criticality Real-Time Virtual Machine System and Configuration of an RTOS's Resources Allocation Techniques.

Mohamed El Mehdi Aichouch

A dissertation submitted to the faculty of the INSA de Rennes in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electronic and Telecommunication.

INSA de Rennes 2014

Approved by:

Isabelle Puaut

Jean-Luc Béchennec

Laurent Pautet

François Verdier

Jean-Christophe Prévotet

Fabienne Nouvel

# ©2014 Mohamed El Mehdi Aichouch ALL RIGHTS RESERVED

## **ABSTRACT**

Mohamed El Mehdi Aichouch Evaluation of a Multiple-Criticality Real-Time Virtual Machine System and Configuration of an RTOS's Resources Allocation Techniques.

In the domain of server and mainframe systems, virtualizing a computing system's physical resources to achieve improved sharing and utilization has been well established for decades. Full virtualization of all system resources, including processor, memory and I/O devices makes it possible to run multiple operating systems on a single physical platform. Recently, the availability of full virtualization on physical platforms that target embedded systems creates new uses cases in the domain of real-time embedded systems. In a non virtualized system, a single OS controls all hardware platform resources. A virtualized system includes a new layer of software, the virtual machine monitor (VMM). The VMM's principal role is to arbitrate accesses to the underlying physical host platform's resources so that multiple operating systems can share them. The VMM presents to each OS a set of virtual platform interfaces that constitute a virtual machine.

Given the existence of a multitude of VMMs that have been proved efficient in the domain of server and mainframe systems, there is a trend to reuse the existing work. However, there is a difference in the performance metric required by these two domains.

In this dissertation we use an existing VMM to evaluate the performance of a real-time operating system. We observed that the virtual machine monitor affects the internal overheads and latencies of the guest operating system. This observation led us to conduct further investigation in order to answer the following question: what are the hardware mechanisms and software implementations that could prevent the system from meeting its deadlines and guaranteeing its real-time constraints?

Our analysis revealed that hardware mechanisms that allow a VMM to provide an efficient way to virtualize the memory management unit, and the device interrupts, are necessary to limit the overhead of the virtualization on real-time systems. More importantly, the scheduling of virtual

machines by the VMM is essential to guarantee the temporal constraints of the system and have to be configured carefully.

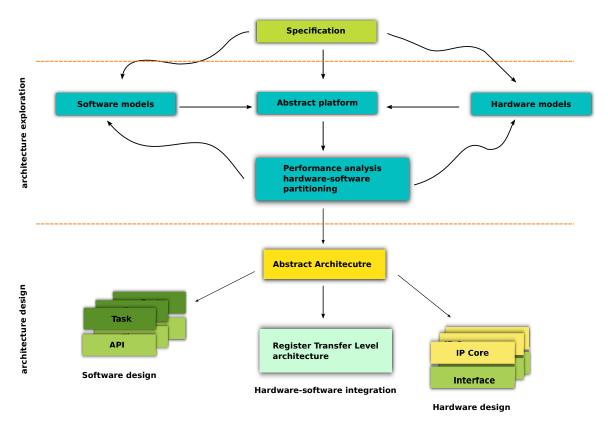

In a second work, and starting from a previous project aiming at helping a system designer to explore a software-hardware co-design of a solution using high-level simulation models, we proposed a methodology that allow the transformation of a simulation model into an executable program on a real hardware. The idea is to provide the system designer with the necessary tools to rapidly explore the design space and validate it, and then to generate a configuration that could be used directly on top of a real hardware.

We used a model-driven engineering approach to perform a model-to-model transformation to convert the simulation model into an executable model. And we used a middleware able to support a variety of resources allocation techniques in order to implement the configuration previously selected by the system designer during the simulation phase. We proposed a prototype that implements our methodology and validate our concepts. The results of the experiments confirmed the viability of the approach.

To my parents, Abdelhamid and Kalthoum.

## **ACKNOWLEDGEMENTS**

I would like to thank my advisors, Fabienne Nouvel and Jean-Christophe Prévotet for their unwavering support, for their help, and their precious advices.

I would like to express my thanks and appreciation to all the members of my committe, Professor Isabelle Puaut, Professor François Verdier, Professor Laurent Pautet, and Doctor Jean-Luc Béchennec for their guidance and advice. Your acceptance to be present in my committe is great honor for me.

I would also like to express my thanks and appreciation to all my colleagues. Very special thanks to Yaset Oliva, Yvan Kokar, Thierry Dubois, Tony Makdissy, Nicolas Cornillet, Jordan Lorandel, Philippe Tanguy, Simon Mener, Vincent Callec, Abdallah Hamini, Ahmed Jaban, Saber Dakhli, Imen Ben Trad, Rida El Chall, Hiba Bawab, Hua Fu, Jean-Christophe Sibel, Ming Liu, Hui Ji, Linning Peng, Tian Xia, Ali Cheaito, Mohamed Maaz, Roua Youssef, Hussein Kudoh, Hanna Farhat, Bachir Habib, Georges Da Silva, Sofiane Chaabane, Morad Larbi, and Abdul Fall. — thank y'all for your kindness and the great moment we shared in our beautiful work place.

I am deeply thankful to my colleague and friend Yaset Oliva for reviewing my research papers and giving me many precious adivces. Thank you very much for the interesting discussions, and for your help when I came to Rennes.

I would like also to thank all the professors, research scientists, and technical staff at the Institut d'Électronique et de Télécommunication de Rennes. I would like also to thank all the SRC department staff at the INSA de Rennes.

I am deeply thankful to my professor Benoît Miramond, thank you for inviting me to join your research team and for your encouragement that motivated me to continue in this scientific research field.

I am deeply thankful to my friend Mac Mollisson, from the real-time system group at the University of North Carolina at Chappel Hill, thank you very much for your support regarding the library, and thanks a lot for the great discussions and feedback regarding my research work.

Foremost, I am greatly indebted to my parents Abdelhamid and Kalthoum for their unwavering support, understanding, and encouragement, both during my research study and before.

I am also greatly indebted to my sister Nesrine and my brother-in-law Aimed, for their love and continuous support, for their help, and the wonderful times we spent together. I am also grateful to all my family members and friends. Thank you very much for your generosity and friendship. I could not finished this without you — thank y'all for your trust that this was indeed the right way.

# TABLE OF CONTENTS

| LI | ST OI | F TABL  | ES xi                                     | 11  |

|----|-------|---------|-------------------------------------------|-----|

| LI | ST OI | F FIGUI | RES x                                     | iv  |

| LI | ST OI | F ABBR  | REVIATIONSxv                              | 'ii |

| 1  | Intro | duction |                                           | 1   |

| 2  | Rela  | ted Wor | k                                         | 3   |

|    | 2.1   | Real-T  | Time OS alongside General-Purpose OS      | 4   |

|    |       | 2.1.1   | Dual-Kernel Design                        | 5   |

|    |       | 2.1.2   | Native Real-Time Linux                    | 6   |

|    | 2.2   | Virtual | Machine Systems                           | 7   |

|    | 2.3   | Real-T  | Time Virtual Machine Systems              | 9   |

|    |       | 2.3.1   | Linux Kernel-based Virtual Machine        | 9   |

|    |       | 2.3.2   | Microkernel Support for Virtualization    | .3  |

|    |       |         | 2.3.2.1 OKL <sup>4</sup> microvisor       | .4  |

|    |       |         | 2.3.2.2 Nova microhypervisor              | .5  |

|    |       |         | 2.3.2.3 L <sup>4</sup> Fiasco microkernel | 6   |

|    |       | 2.3.3   | Xen                                       | 9   |

|    |       | 2.3.4   | RT-Xen                                    | 23  |

|    |       | 2.3.5   | Real-Time Xen-ARM                         | 30  |

|    |       | 2.3.6   | Virtualization for safety-critical system | 32  |

|    | 2.4   | RTOS    | Configuration                             | 10  |

|    |       | 241     | Composite                                 | ın  |

|   |       | 2.4.2     | ExSched                                          | 42         |

|---|-------|-----------|--------------------------------------------------|------------|

|   |       | 2.4.3     | LITMUS <sup>RT</sup>                             | <b>4</b> 4 |

|   |       | 2.4.4     | Microkernel                                      | 46         |

|   |       | 2.4.5     | OveRSoC RTOS Model                               | 47         |

| 3 | Virtu | ıalizatio | on and Real-Time Systems                         | 50         |

|   | 3.1   | Hardw     | rare-Assisted Virtualization                     | 50         |

|   |       | 3.1.1     | Resource Virtualization - Processors             | 51         |

|   |       |           | 3.1.1.1 Conditions for ISA Virtualization        | 51         |

|   |       |           | 3.1.1.2 Intel Virtualization Extension           | 52         |

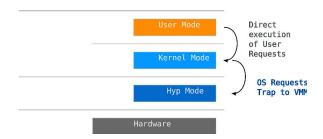

|   |       |           | 3.1.1.3 ARM Virtualization Extension             | 53         |

|   | 3.2   | Linux     | Kernel Virtual Machine                           | 54         |

|   |       | 3.2.1     | Qemu                                             | 55         |

|   |       | 3.2.2     | Virtual Machine Process                          | 55         |

|   | 3.3   | Schedu    | uling Latency Evaluation                         | 57         |

|   | 3.4   | Fine-C    | Grained Overheads and Latencies Evaluation       |            |

|   |       | 3.4.1     | Overheads and Latencies                          | 62         |

|   |       | 3.4.2     | Hardware platform                                | 63         |

|   |       | 3.4.3     | LITMUS <sup>RT</sup> and Feather Trace toolkit   | 64         |

|   |       | 3.4.4     | Synthetic Workloads                              | 66         |

|   | 3.5   | Result    | s                                                | 67         |

|   | 3.6   | Emula     | tion of the I/O interrupts                       | <b>7</b> 4 |

|   |       | 3.6.1     | Comparison with ARM I/O virtualization           | 75         |

|   |       | 3.6.2     | Comparison with Custom ARM Hardware Architecture | 77         |

|   | 3.7   | Summ      | ary                                              | 77         |

| 4 | Real  | -Time S   | cheduling of Virtual Machines                    | 79         |

|   | 4.1   | Real-T    | ime Task Model                                   | 79         |

|   |       | 4.1.1     | Temporal Correctness.                            | 80         |

|   |                          | 4.1.2  | Schedulability Test                               | 81  |

|---|--------------------------|--------|---------------------------------------------------|-----|

|   | 4.2 Real-Time Scheduling |        | ime Scheduling                                    | 81  |

|   |                          | 4.2.1  | Fixed-Priority Scheduling                         | 82  |

|   |                          | 4.2.2  | Dynamic-Priority Scheduling                       | 84  |

|   | 4.3                      | Algori | thmic Analysis                                    | 85  |

|   | 4.4                      | Comp   | uting of the Efficient Scheduling Parameters      | 87  |

|   |                          | 4.4.1  | Execution Length of a Virtual Machine             | 88  |

|   |                          | 4.4.2  | Schedulability Condition on a VM                  | 89  |

|   |                          | 4.4.3  | Computing of the Highest-Priority VM's Parameters | 92  |

|   | 4.5                      | Overho | ead-aware Schedulability Analysis                 | 96  |

|   | 4.6                      | Empiri | ical Evaluation                                   | 98  |

|   | 4.7                      | Summ   | ary                                               | 103 |

| 5 | RTO                      | S Mode | els Transformation and Configuration              | 105 |

|   | 5.1                      | Softwa | are/Hardware Co-design Process                    | 105 |

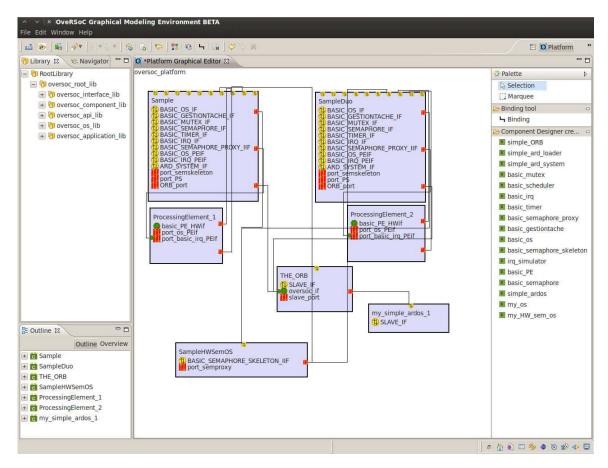

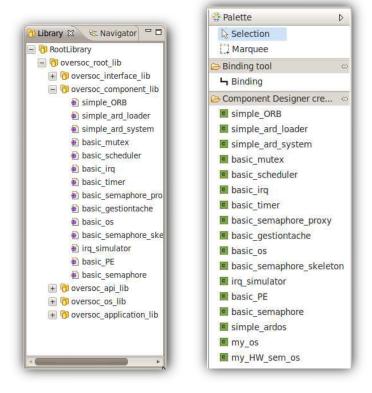

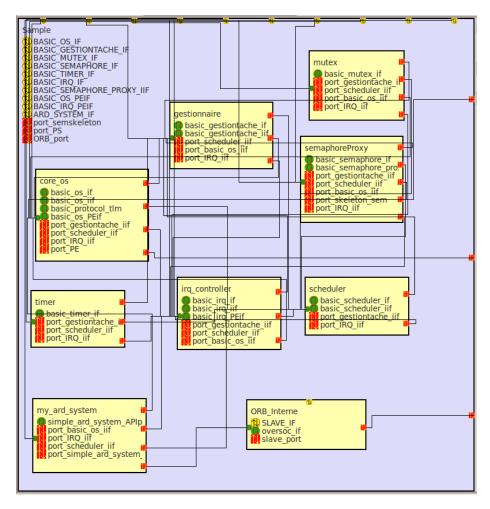

|   | 5.2                      | OveRS  | SoC Methodology                                   | 106 |

|   |                          | 5.2.1  | From Simulation Models to Executable Models       | 111 |

|   | 5.3                      | Model  | Driven Engineering                                | 112 |

|   |                          | 5.3.1  | Model Driven Architecture                         | 113 |

|   |                          | 5.3.2  | Domain Specific Language                          | 114 |

|   | 5.4                      | RTOS-  | -specific Modeling Language                       | 115 |

|   |                          | 5.4.1  | RTOS Meta-Model                                   | 115 |

|   |                          | 5.4.2  | Concrete Syntax                                   | 117 |

|   |                          | 5.4.3  | Model-to-Code Transformation                      | 118 |

|   |                          | 5.4.4  | Test of the Transformation                        | 120 |

|   |                          | 5.4.5  | Model-To-Model Transformation                     | 120 |

|   |                          | 5.4.6  | Limitation of the Approach                        | 121 |

|   | 5.5                      | Summ   | arv                                               | 122 |

| 6 | RTO  | S Configuration using User-Level Library |                                                          |     |  |  |

|---|------|------------------------------------------|----------------------------------------------------------|-----|--|--|

|   | 6.1  | User-L                                   | Level Scheduling on top of Microkernel                   | 125 |  |  |

|   | 6.2  | Tasks l                                  | Model and Thread Mechanisms                              | 126 |  |  |

|   |      | 6.2.1                                    | Sporadic Task Model                                      | 126 |  |  |

|   |      | 6.2.2                                    | Thread library                                           | 126 |  |  |

|   | 6.3  | Nova I                                   | Microkernel and Runtime Environment                      | 128 |  |  |

|   | 6.4  | Librar                                   | y Implementation                                         | 129 |  |  |

|   | 6.5  | Experi                                   | iments                                                   | 132 |  |  |

|   |      | 6.5.1                                    | Overheads and Latencies                                  | 132 |  |  |

|   |      | 6.5.2                                    | Experiment Setup                                         | 132 |  |  |

|   |      | 6.5.3                                    | Experimental Workloads and Execution Trace               | 132 |  |  |

|   |      | 6.5.4                                    | Measured Results                                         | 134 |  |  |

|   |      | 6.5.5                                    | Comparison with Similar Approaches                       | 136 |  |  |

|   | 6.6  | Summ                                     | ary                                                      | 138 |  |  |

| 7 | Cone | clusions                                 | S                                                        | 139 |  |  |

|   | 7.1  | Open (                                   | Question and Future Works                                | 141 |  |  |

| 8 | Résu | umé de la thèse                          |                                                          |     |  |  |

|   | 8.1  | Etat de                                  | e l'art sur la virtualisation                            | 143 |  |  |

|   |      | 8.1.1                                    | Linux Kernel Virtual Machine                             | 144 |  |  |

|   |      | 8.1.2                                    | Virtualisation basée sur le Micro-noyau                  | 145 |  |  |

|   |      | 8.1.3                                    | Xen                                                      | 146 |  |  |

|   |      | 8.1.4                                    | Virtualisation pour les systèmes critiques               | 149 |  |  |

|   | 8.2  | Etat de                                  | e l'art sur la configuration des systèmes d'exploitation | 150 |  |  |

|   | 8.3  | Impac                                    | t de la Virtualisation sur les Systèmes Temps-Réel       | 152 |  |  |

|   | 8.4  | Ordon                                    | nancement Temps-Réel des Machines Virtuelles             | 152 |  |  |

|   | 8.5  | Transf                                   | Formation d'un modèle d'OS Temps-Réel                    | 153 |  |  |

|   | 8.6  | Utilisa                                  | ation d'une Libraire pour la Configuration d'OS          | 153 |  |  |

| 8.7    | Conclusion et futurs travaux | 1 | 55 |

|--------|------------------------------|---|----|

| BIBLIO | OGRAPHY                      |   | 56 |

# LIST OF TABLES

| 4.1 | Example of real-time task set schedulable under RM scheduling | 82  |

|-----|---------------------------------------------------------------|-----|

| 4.2 | Task set of simple real-time automotive application           | 94  |

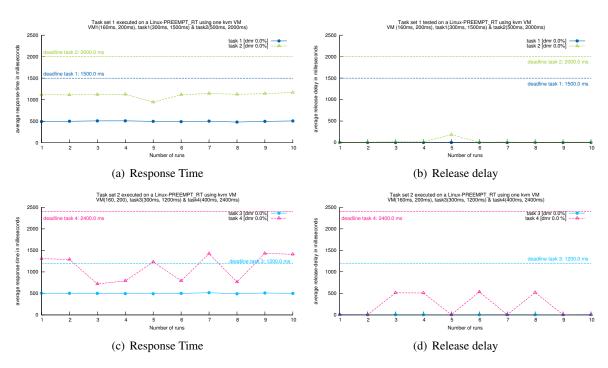

| 4.3 | Simplified real-time applications.                            | 99  |

| 4.4 | Real-Time Virtual Machine System configuration                | 99  |

| 6.1 | Example of real-time task set schedulable under RM scheduling | 133 |

| 6.2 | Overheads comparison.                                         | 137 |

# LIST OF FIGURES

| 2.1  | The native and the dual-kernel design of real-time Linux                                      | 4  |

|------|-----------------------------------------------------------------------------------------------|----|

| 2.2  | Native and Hosted VM Systems.                                                                 | 8  |

| 2.3  | kvm software architecture                                                                     | 10 |

| 2.4  | Comparison of the TCB of three different virtual machine systems                              | 15 |

| 2.5  | Nova software architecture.                                                                   | 16 |

| 2.6  | Hierarchical Scheduling Framework concept.                                                    | 17 |

| 2.7  | Xen software architecture.                                                                    | 20 |

| 2.8  | Request bound function.                                                                       | 27 |

| 2.9  | Schematic of the overall architecture of Hijack $^{ m COS}_{ m Linux}$ .                      | 41 |

| 2.10 | Schematic of the overall architecture of ExSched.                                             | 43 |

| 2.11 | Schematic of the overall architecture of LITMUS <sup>RT</sup>                                 | 45 |

| 3.1  | Virtual Machine System Concept.                                                               | 50 |

| 3.2  | Intel ISA's operation modes and privilege levels.                                             | 53 |

| 3.3  | ARM ISA's operation modes and privilege levels.                                               | 54 |

| 3.4  | Linux Kernel Virtual Machine and Qemu.                                                        | 55 |

| 3.5  | Scheduling of the kvm and Qemu threads                                                        | 56 |

| 3.6  | The relationship between the scheduling of the $kvm$ threads and the ksoftirq thread $\ldots$ | 56 |

| 3.7  | Scheduling latency of a real-time Linux running natively on an Intel hardware                 | 59 |

| 3.8  | Scheduling latency of a real-time Linux running on a virtual machine                          | 59 |

| 3.9  | Scheduling latency of a real-time Linux measured on a recent Intel core i7 hardware.          | 61 |

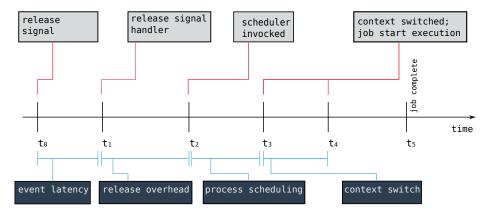

| 3.10 | Timeline illustrating release delay under fixed-priority scheduling                           | 63 |

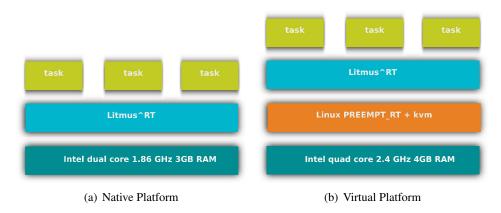

| 3.11 | Architecture of the native and the virtual platform used in the experiments                   | 64 |

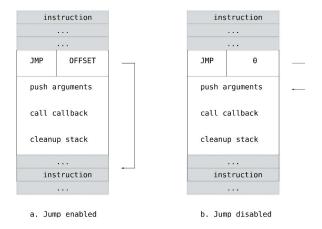

| 3.12 | Feather trace toolkit.                                                                        | 65 |

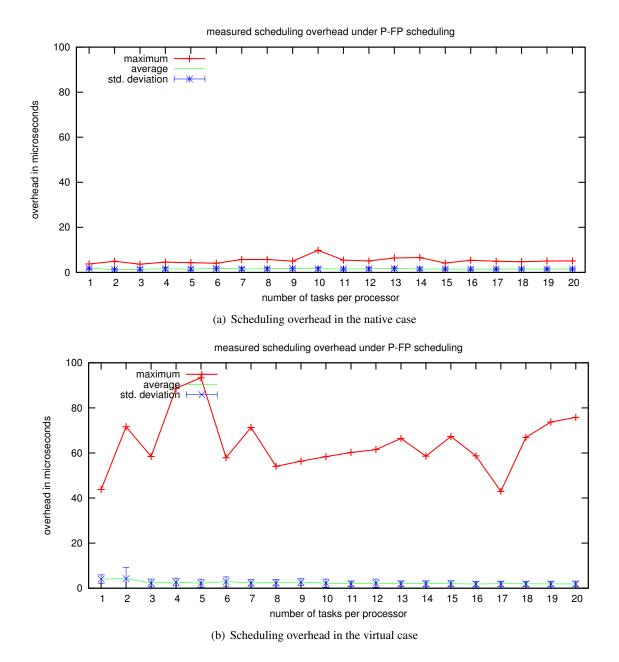

| 3.13 | Scheduling overhead                                                                           | 68 |

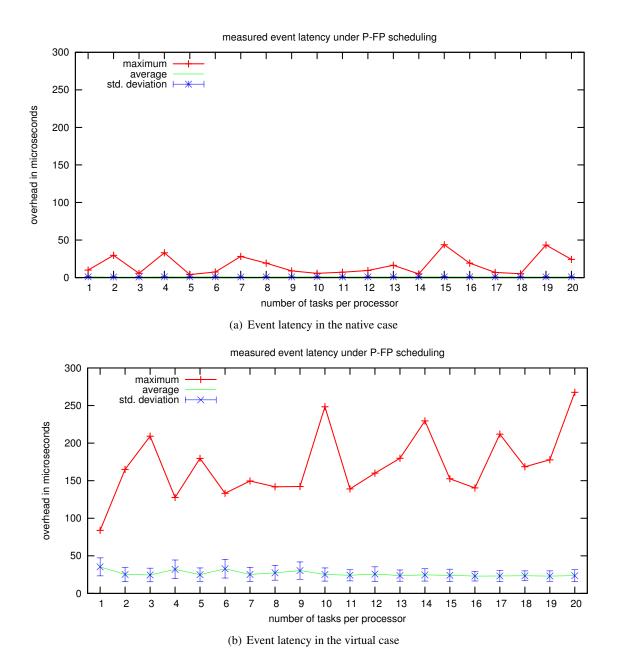

| 3.14 | Event latency                                                                                 | 69 |

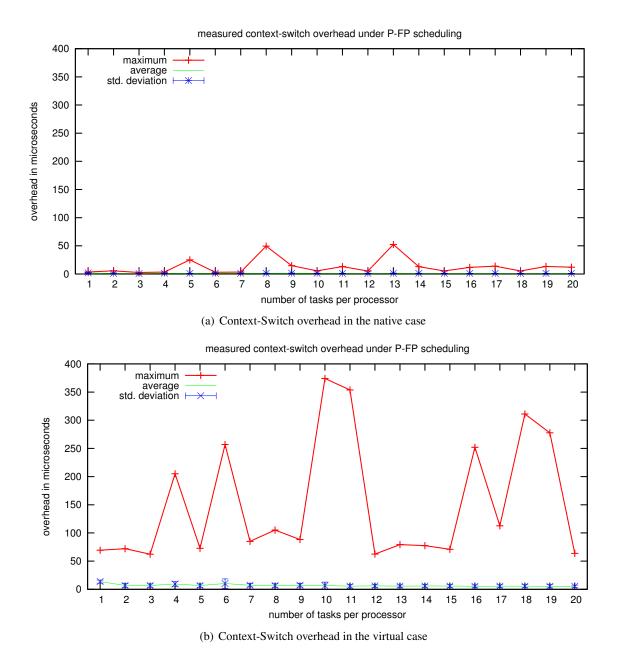

| 3.15 | Context-switch overhead                                                                    | 70  |

|------|--------------------------------------------------------------------------------------------|-----|

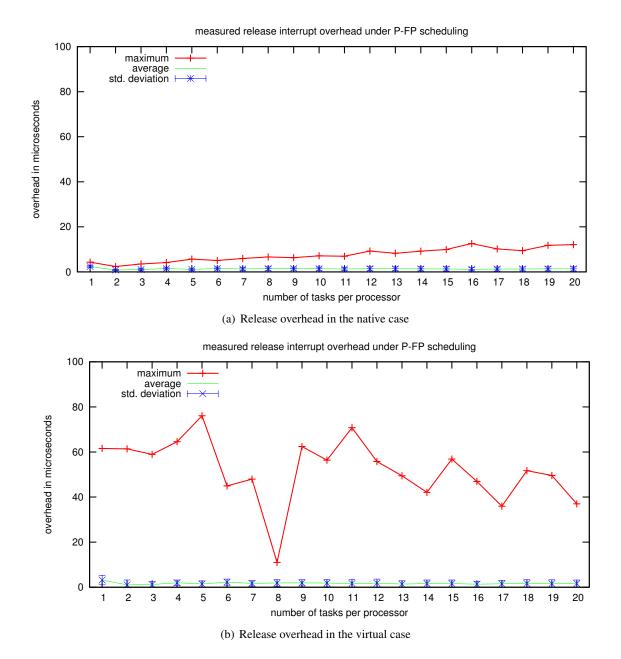

| 3.16 | Release overhead.                                                                          | 71  |

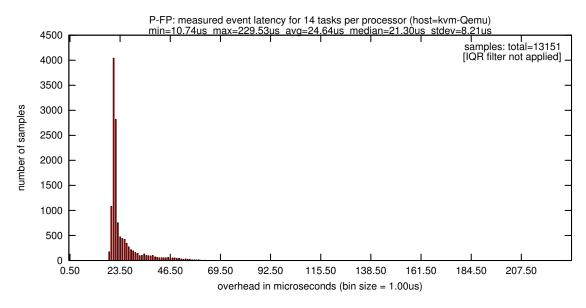

| 3.17 | Distribution of release latency at n equals 14 tasks per processor, in the virtual case    | 72  |

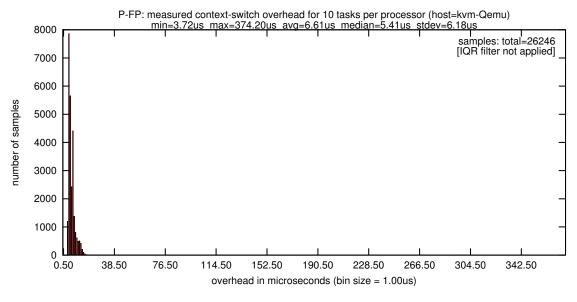

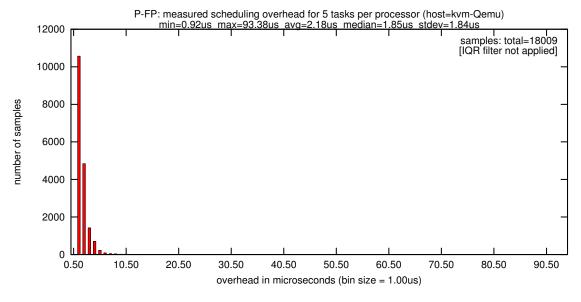

| 3.18 | Distribution of the context-switch overhead for n equals 10 tasks per processor            | 72  |

| 3.19 | Distribution of the context-switch overhead for n equals 20 tasks per processor            | 73  |

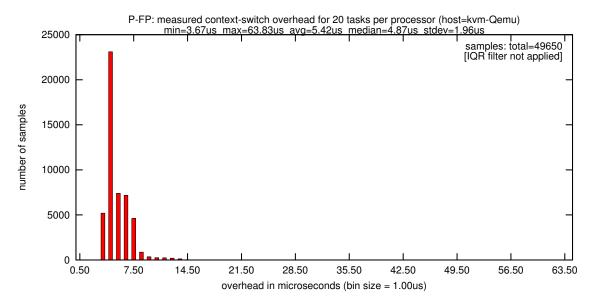

| 3.20 | Scheduling overhead at n equals 5 tasks per processor measured in the virtual case         | 73  |

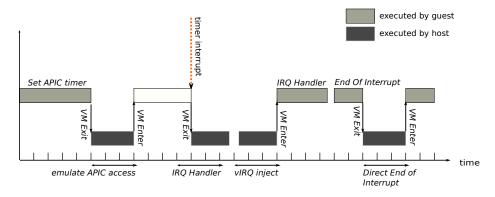

| 3.21 | Scheduling of virtual machines according to the fixed-priority algorithm                   | 75  |

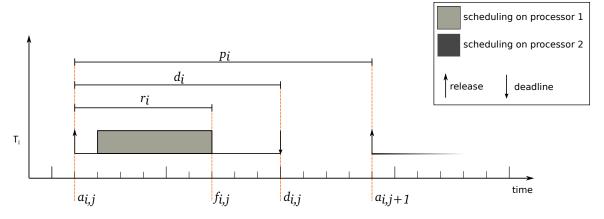

| 4.1  | Illustration of the temporal properties of a periodic task                                 | 80  |

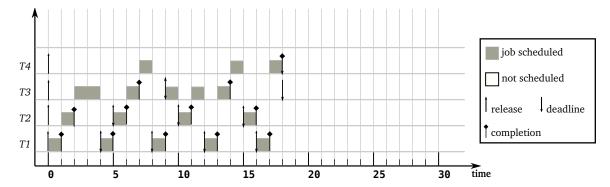

| 4.2  | Scheduling of the task set from Table 3.1 according to the RM algorithm                    | 83  |

| 4.3  | Scheduling of the task set from Table 3.1 according to the EDF policy                      | 85  |

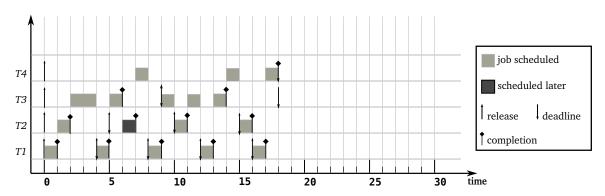

| 4.4  | Scheduling of virtual machines according to SCHED_FIFO scheduling algorithm                | 86  |

| 4.5  | Scheduling of virtual machines according to the RM algorithm                               | 87  |

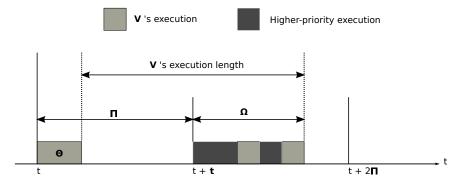

| 4.6  | $V_l$ execution length                                                                     | 88  |

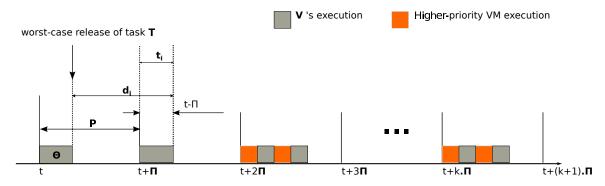

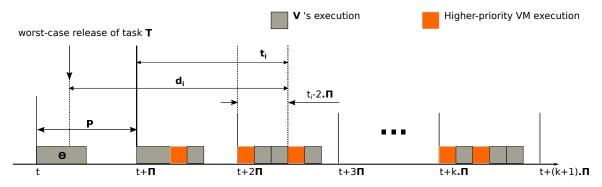

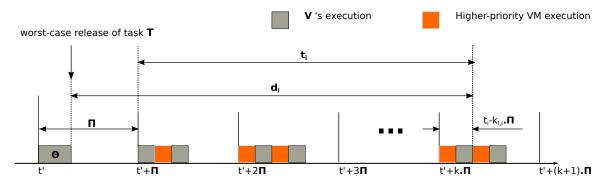

| 4.7  | Schedulability condition for a task $T_i$ at a time $t+\Pi_i$                              | 90  |

| 4.8  | Schedulability condition for a task $T_i$ at a time $t+2\cdot\Pi_i$                        | 91  |

| 4.9  | Schedulability condition of task $T_i$ executed on the virtual machine $V_l$               | 91  |

| 4.10 | Overhead related to release event                                                          | 96  |

| 4.11 | Scheduling of virtual machines using the periodic resource model                           | 99  |

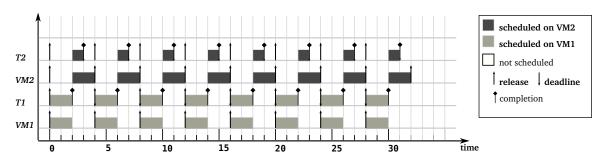

| 4.12 | Real-Time application executed on two VMs scheduled by SCHED_DEADLINE                      | 102 |

| 4.13 | Scheduling of virtual machines VM <sup>1</sup> and VM <sup>2</sup> using the same priority | 103 |

| 5.1  | System-level design flow for SoCs.                                                         | 106 |

| 5.2  | OveRSoC Development Tool.                                                                  | 108 |

| 5.3  | OveRSoC's Library and design Tool.                                                         | 109 |

| 5.4  | OveRSoC component designer.                                                                | 110 |

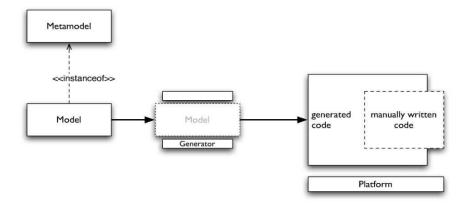

| 5.5  | Model-Driven software development process                                                  | 113 |

| 5.6  | Hierarchical Modeling Levels.                                                              | 114 |

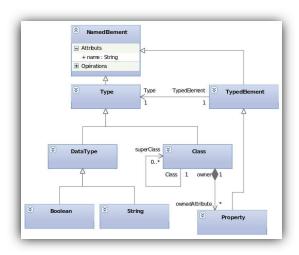

| 5.7  | Meta Object Facility language                                                              | 116 |

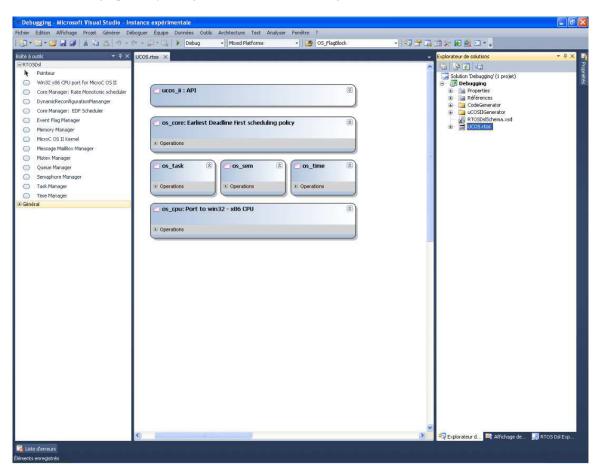

| 5.8  | RTOS structure meta-model.                                              | 116 |

|------|-------------------------------------------------------------------------|-----|

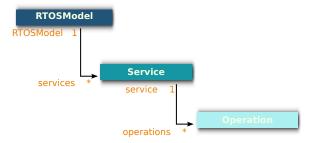

| 5.9  | RTOS-specific language tool.                                            | 117 |

| 5.10 | Extended RTOS meta-model.                                               | 119 |

| 5.11 | Model-to-Model transformation process                                   | 121 |

| 6.1  | Xilinx Zinq 7000.                                                       | 124 |

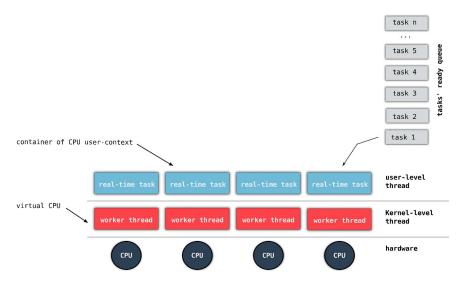

| 6.2  | Many-to-Many model.                                                     | 127 |

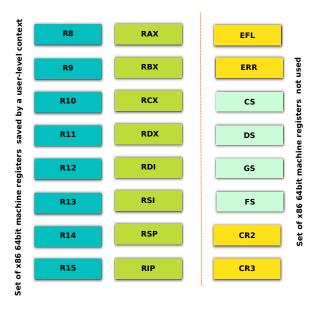

| 6.3  | Set of registers that constitute the CPU user-context                   | 128 |

| 6.4  | Schematic architecture of the user-level library                        | 130 |

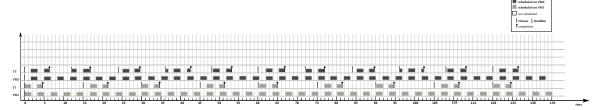

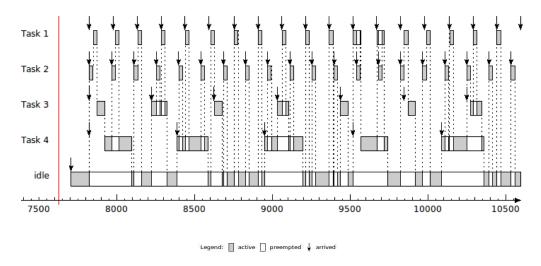

| 6.5  | Scheduling trace of a task set according to the RM algorithm.           | 133 |

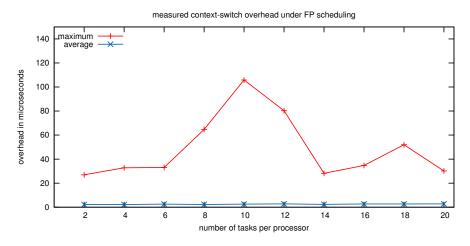

| 6.6  | Context-Switch overhead of the FP scheduler.                            | 134 |

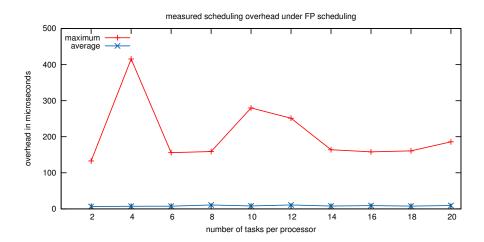

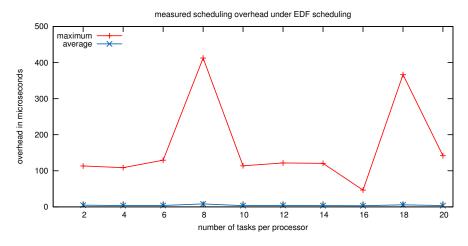

| 6.7  | Scheduling overhead of the FP scheduler                                 | 135 |

| 6.8  | Scheduling overhead of the EDF scheduler                                | 135 |

| 8.1  | Architecture logicielle des systèmes supportant des machines virtuelles | 143 |

## LIST OF ABBREVIATIONS

ABD All But Dissertation

BW Bandwidth

CBS Constant Bandwidth Server

DMR Deadline Miss Ratio

DS Deferable Server

EDF Earliest Deadline First

FP Fixed-Priority

G-EDF Global Earliest Deadline First

G-FP Global Fixed Priority

HRT Hard Real-Time

HSF Hierarchical Scheduling Framework

I/O Input/Output

IPC Inter-Process Communication

IPI Inter-Processor Interrupt

KVM Kernel Virtual Machine

LoC Lines of Code

PRM Periodic Resource Model

PS Periodic Server

RBF Request Bound Function

RM Rate-Monotonic

SBF Supply Bound Function

SEDF Simple Earliest Deadline First

SMI System Management Interrupts

SoC System-on-Chip

SRT Soft Real-Time

TLB Translation Lookaside Buffer

TSC Timestamp Counter

VM Virtual Machine

VMM Virtual Machine Monitor

WCET Worst-Case Execution Time

WSS Working Set Size

## **CHAPTER 1**

# Introduction

Multicore chips enabled with hardware-assisted virtualization mechanisms are commonly encountered in servers and personal computers. Such platforms offer a considerable processing capacity while reducing the space required to deploy the system. As a result, these platforms are also considered to be deployed in real-time embedded systems.

A key requirement when building safety-critical applications is isolation, *i.e.* the failure of one component should not crash the whole system. The easiest and historically most-commonly used way to ensure isolation is to employ a dedicated processor for each functionality. However, this approach has led to an increasingly unmanageable proliferation of such systems, to the effect that some modern cars may contain more than one hundred Electronic Control Unit. For example, the number of ECUs in the car has grown to the level where the complexity of the electrical and electronic system is difficult to manage. Every embedded system requires wiring and cooling, adds weight, requires space, drains power, and must be purchased, transported, tested, and documented, *etc.* Thus, instead of embedding one hundred networked, slow uniprocessors throughout a car, it would be desirable to use only ten (or fewer) shared, but ten-times as powerful, multicore processors that are highly utilized.

While in one case the migration of legacy applications from uniprocessors to multicore platforms requires the use of one operating system to manage all the applications, in other case, the use

of several operating systems is necessary. For example, in the automotive domain, one real-time operating system (RTOS) will be used for real-time tasks, and a general-purpose operating system will

be used to support in-vehicle infotainment applications. Each operating system will be executed in a

separate and secure *virtual machine*. A virtual machine (VM) is a hardware and software technique

that "gives the impression" to the operating system that it is running on the real hardware while in

reality it is not. Thus, multiple virtual machines could be deployed on a physical machine, and are controlled by a *Virtual Machine Monitor* (VMM).

In addition to dependability requirements, the correctness of real-time systems is dependent on the system's ability to meet application temporal constraints. Expressed in terms of tasks deadlines, applications' resources requirements define the service levels required from the system. To behave in a predictable manner and support the correctness of these applications, the system must contain resource management policies capable of dealing with specific applications temporal constraints.

The goal of this dissertation is, first, to determine how to securely deploy multiple operating systems on a same hardware platform while preserving the temporal correctness of the system. Second, how to easily configure the real-time operating systems in order to adapt it to the applications requirements.

This dissertation is organized as follows: in Chapter 2 we review the studies related to our work on the use of virtualization in real-time systems, and the configuration of the resources allocation techniques of an RTOS. In Chapter 3 we evaluate the overheads and latencies of an RTOS that is deployed on a virtual machine. Then, in Chapter 4 we analyze the role of scheduling in maintaining the performance of real-time virtual machine system. Next, in Chapter 5 we present a transformation of an RTOS simulation model into an executable programs on a real hardware, then we define in Chapter 6 a method to preserve its configurability feature. We conclude this dissertation in Chapter 7.

## **CHAPTER 2**

# **Related Work**

There are multiple applications of a software architecture able to co-locate a real-time operating system and a general-purpose operating system. For example, in the automotive domain, an AUTOSAR compliant RTOS and a Linux Genivi operating system that support in-vehicle infotainment application, could be co-located on the same electronic control unit (ECU) (Heiser, 2011).

Multicore chips enabled with instruction set architecture (ISA) that support virtualization offer an efficient solution to fulfill such a requirement. New processors extended with this virtualization feature allow to execute multiple virtual machines on the same real hardware. Thus, it is possible to execute multiple unmodified operating systems at the same speed rate as on the native hardware.

This dissertation addresses two fundamental questions to the design of a real-time virtual machine system: what is the order of magnitude of the overheads and latencies of an RTOS running in a Virtual Machine, and how these overheads and latencies impact the temporal characteristics of a real-time system.

The third question addressed in this thesis is: how to transform a component-based RTOS model from its simulation form into an executable program, while preserving the configurability property offered by its design? By configurability of the RTOS we mean changing for instance its internal resources allocation policy and adapting the operating system by selecting the appropriate services required by the application.

In this chapter, we first present some approaches that investigated the combination of an RTOS and general-purpose OS without using virtualization, then we review the research studies that investigated the use of virtualization in real-time systems. Second, we discuss different proposed solutions to enable the configuration of a real-time operating system.

# 2.1 Real-Time OS alongside General-Purpose OS

Running a real-time OS alongside a general-purpose OS could be achieved by "re-tailoring" an existing general-purpose OS to acquire the desired real-time features, for example, a real-time scheduler, temporal isolation, or low interrupt latency. One advantage of this approach is that it greatly reduces the development costs since basic OS functionality such as memory management, device drivers, and process abstraction, do not have to be re-implemented.

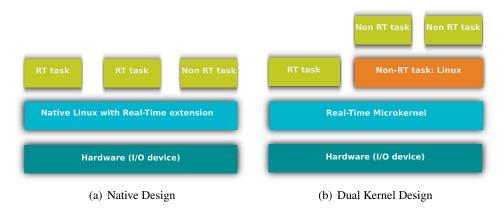

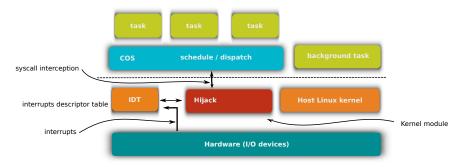

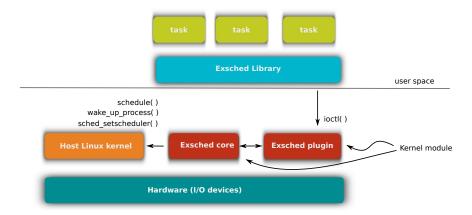

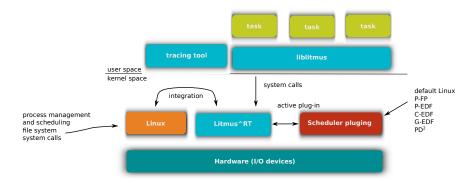

Due to its open source nature, Linux, is the most frequently chosen operating system when combining a general-purpose and a real-time operating system. There are two variants of solution based on Linux. In a *native design*, the Linux kernel is the only kernel responsible for meeting the real-time requirements. The real-time tasks are regular Linux processes as indicated in Figure 2.1(a). In contrast, in a *dual-kernel design*, a specialized hard real-time-capable kernel is inserted between the Linux and the hardware. Such an implementation follows the classical *microkernel* design in which Linux is an OS server and is scheduled as a background, non-real-time thread by the microkernel. Real-Time tasks are not Linux processes, they are specialized threads managed directly by the *small kernel* besides the Linux kernel as depicted in Figure 2.1(b). In the next two sections we first review the dual-kernel variant, then we discuss the native-kernel variant.

Figure 2.1: In a native real-time Linux, real-time tasks are processes of the Linux kernel. While in dual kernel design the real-time tasks are managed by a special real-time kernel isolated from Linux. Linux is executed as a non real-time task of that small kernel.

## 2.1.1 Dual-Kernel Design

In the early versions of Linux, all system calls and interrupts handling were executed as one non preemptive section. This greatly simplified synchronization requirements on a uniprocessor. However, it could lead to excessively long non preemptive section in the case of a real-time system. For example, when a high priority real-time job is released, the corresponding real-time process could be delayed if the kernel were executing on behalf of a lower-priority task. As a result, a non preemptive kernel with long code paths may cause real-time tasks to incur unacceptable delay in the worst case.

Consequently, real-time Linux variants, in particular those focused on hard real-time applications, chose to work around the Linux kernel and its internal limitations using a dual-kernel design approach. In this approach, Linux is executed as a real-time background task of a small real-time kernel. In this case, the Linux kernel is not in full control of the hardware, does not have the right to disable interrupts, and thus can be preempted at any time.

There are two key advantages to such dual-kernel design. First, low interrupt latencies can be guaranteed to real-time tasks regardless of any deficiencies in the Linux kernel. Second, only relatively small changes to the Linux kernel are required, which means that integrating improvements made in newer Linux versions is relatively easy.

A disadvantage of the dual-kernel design is that real-time tasks execute directly on top of the *small kernel* and cannot make use of the Linux services such as device drivers, POSIX IPC, synchronization primitives, file-systems, *etc*. This limitation is fundamental since a dual-kernel does not improve Linux's real-time capabilities, rather, it enables real-time tasks to safely co-exist with the Linux kernel.

There are two main classes of dual-kernel Linux. L<sup>4</sup>Linux (Lackorzynski, 2014) is an example of a dual-kernel system where both Linux and real-time tasks are executed in private address spaces and thus isolated from each other. Also several commercial RTOSs offer Linux dual-kernel support as well, among them Green Hills's INTEGRITY, Sysgo AG's PikeOS, and LynxWorks's Lynx OS. In contrast, real-time tasks execute in kernel mode in RT-Linux (Zijlstra, 2008) and are thus not isolated from the Linux kernel. Besides RT-Linux, two other well-known real-time Linux based on the dual-kernel design approach that omit isolation are the Real-Time Application Inter-

face (RTAI) (Cloutier et al., 2008), which targets industrial applications, and the *Xenomai* project, which targets similar use cases but also focuses on providing RTOS compatibility layers (so-called *skins*) to support legacy applications (Gerum, 2008).

### 2.1.2 Native Real-Time Linux

In a native design, one kernel is present and in full control of the hardware platform. Only the Linux kernel is modified in order to enhance its real-time capabilities. This design is preferred to the dual-kernel design in the vast majority of applications if timing constraints can be met, that is, if Linux's limitation such as high interrupt latencies can be addressed. In the case of applications with very stringent constraints (*e.g.* engine control software), a dual-kernel approach may be the only feasible design.

Multiple works attempted to integrate a real-time infrastructure to the Linux kernel. For example, the Kansas University Real-Time Linux (KURT Linux), developed by Srinivasan et al. (1998) provided the high-resolution (software) timers based on hardware timers operating in one-shot mode ("UTIME" patch). Later, this design was re-implemented in a POSIX-compliant way and merged into a standard Linux under the name *hrtimers* (Gleixner and Niehaus, 2006).

Linux versions higher than 3.0 are suited for use in real-time systems, and the current native real-time Linux design focus on scheduling and locking algorithmic changes. Linux 3.0 gained several improvements over the course of several versions that greatly improved its viability as an RTOS, namely high-resolution timers, priority inheritance, mostly preemptable kernel execution, much-shortened non-preemptive sections, and an improved lower-overhead fixed-priority scheduler. Main-line Linux is now almost POSIX-compliant and supports fixed-priority scheduling (SCHED\_FIFO and SCHED\_RR) with 100 distinct priorities, processor affinity masks, and the *priority inheritance protocol*.

However, the Linux kernel still contains some limitations in terms of non-preemptive code paths that are long in the context of real-time systems and architectural design choices that were made with throughput in mind. For example, interrupts are, by default, not serviced using split interrupt handling; rather, Interrupt Service Routines (ISRs) are typically executed immediately when an interrupt is raised and are not subject to scheduling. Executing ISRs right away benefits network and disk bandwidth, but can also delay real-time tasks. Thus, while API-compatible, current mainline

Linux is not yet comparable to purpose-built RTOSs such as VxWorks or QNX Neutrino in terms of predictability and interrupt latency.

Moving beyond this limitations is the goal of the PREEMPT\_RT patch, which is the *de facto* real-time standard variant of Linux. It changes the Linux core infrastructure significantly by reducing the number and the length of non-preemptive critical sections, converting most spin-locks in the kernel to semaphores, and further enables the *priority inheritance protocol* by default for all semaphores in the kernel. One important feature introduced by the patch is to force split interrupt handling for all ISRs except timers. The PREEMPT\_RT patch is under active development, and besides serving as a staging ground for real-time features that are intended to be incorporated into mainline Linux at a later point, it is also widely used in industrial projects.

**Summary.** While real-time Linux variants offer a good approach to co-locate a real-time OS and a general purpose OS, such a design could be problematic in the case where a legacy application has already been developed and certified on a existing RTOS. In this situation, adopting a design based on a real-time Linux variant would require the porting of the application using a new API, and going through a new certification process if the application is used in a safety-critical system. This extra work increases the development cost and the already tight time-to-market.

An alternative solution could be provided by the use of the virtual machine concept. By using a Virtual Machine System, it is possible to run the existing RTOS and the application in a virtual machine alongside a general-purpose operating system on the same hardware. We study this approach in the next section.

# 2.2 Virtual Machine Systems

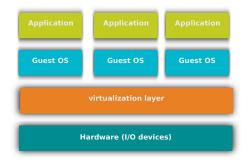

A Virtual Machine System is a concept intended to host multiple operating systems simultaneously on a single hardware platform. Each *guest* operating system is executed in a separate and secure Virtual Machine (VM). The virtual machine is the abstraction of the hardware resources provided to the guest operating systems, and managed by a low-complexity kernel referred to as a Virtual Machine Monitor (VMM).

The virtual machine monitor must ensure that a temporal or local fault in one virtual machine (e.g., an infinite loop, out-of-bounds array access, exhaustion of assigned resources) does not af-

fect the operation of other correct virtual machines. This requirement is referred to as *logical* and *temporal isolation* in the real-time community, and as *space* and *time partitioning* in the RTOS industry.

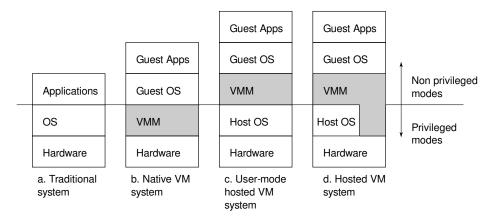

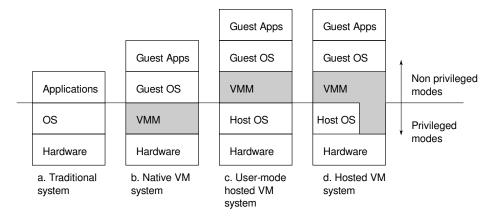

Virtualization can be implemented in different ways. The classic approach to design a virtual machine system is to place the VMM on bare hardware whereas the virtual machine fits on top. The VMM runs in the most highly *privileged level*<sup>1</sup>, while all guest operating systems run with lesser privileges, as shown in Figure 2.2. Then, in a completely transparent way, the VMM can intercept and implement all the guest OS's actions that interact with the hardware resources.

An alternative implementation builds the VMM on top of an existing host operating system, resulting in what is called a *hosted VM* as shown in Figure 2.2c and Figure 2.2d. In this configuration, the installation process is similar to installing a typical application program.

Figure 2.2: Native and Hosted VM Systems.

Executing multiple guest operating systems by a VMM is similar to the execution of multiple user processes by an operating system in a conventional time-sharing system. The VMM moves the entire guest registers' contents into the host's registers after saving the registers of the previous guest into memory. Then, the execution can proceed at the same speed rate as on a machine running the guest natively. Once the VMM gives the resources to a guest virtual machine, it is important that the VMM could get them back so they can be later assigned to a different VM. Again, this step

<sup>&</sup>lt;sup>1</sup>This level (reserved for the most privileged code, data, and stacks) is used for the segments containing the critical software, usually the kernel of an operating system. The other privilege levels are used for less critical software. For instance, the x86 Intel architecture has 4 privilege levels. Linux on the x86 architecture uses the highest privilege level, and the applications use the lowest one, the other intermediate levels are not used.

is similar to an operating system that regains control of all the hardware resources when it executes multiple user jobs concurrently on a machine.

Virtual Machine Systems have been widely deployed in the domain of enterprise server. Given this success, these systems are also increasingly deployed in the embedded real-time systems. A considerable research effort has been spent in adapting existing virtual machine systems used in the server domain to the real-time embedded system domain.

With regards to the questions of this thesis, we are interested in investigating the capability of the existing systems that were initially designed for the server domain to support the real-time embedded systems demands. While reviewing the existing work in this direction, our approach is to understand the limitation of the initial implementation targeting the server domain and how it was adapted to fulfil the requirements of the real-time systems.

# 2.3 Real-Time Virtual Machine Systems

In this section, we review how existing Virtual Machine Systems have been adapted to real-time systems. For each solution, we first describe its design and implementation, then we discuss its real-time performance.

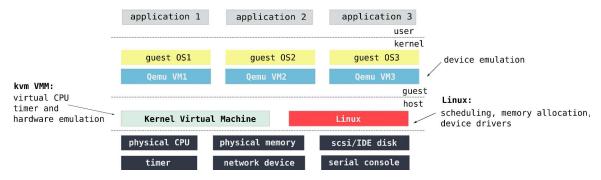

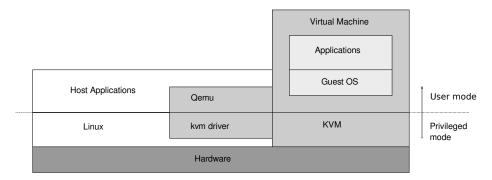

### 2.3.1 Linux Kernel-based Virtual Machine

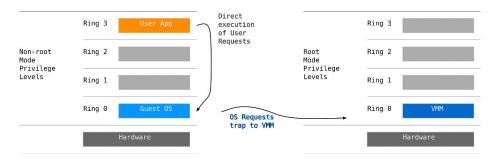

Linux Kernel Virtual Machine (shortened as kvm) is a *hosted VM* system (Kivity et al., 2007). Its main task is to manage unprivileged access to hardware features that can only be used directly by the privileged kernel. Its tremendous success is in large part due to its relative simplicity compared to other approaches. This simplicity is achieved by leveraging the functionality already provided by the Linux kernel, and relying on hardware-assisted virtualization, which allows it to be ported to wide range of architectures such as x86, PowerPC, ARM and IBM s390.

Under kvm, when a virtual machine is created, a data structure is instantiated to hold in memory the CPU registers used by the guest operating system, and acts as a **virtual CPU** (vCPU). A virtual CPU is associated to a regular Linux process and scheduled by the Linux kernel scheduler alongside the other processes. The spatial isolation between virtual machines relies on the Linux's virtual memory management, for each virtual machine a separate memory address space is created. Each

guest operating system has its own memory separated from the other guests. Figure 2.3 illustrates the integration of kvm into the Linux kernel.

Figure 2.3: kvm software architecture.

kvm is a hosted-VM system that requires two components: a VMM-native (VMM-n) and a VMM-user (VMM-u) components (see Figure 2.2d):

**VMM-n** (**native**). This component runs natively on the hardware and has characteristics similar to the VMM on a *native VM* system. It is the component that intercepts traps due to the privileged instructions executed by a guest operating system running in a virtual machine.

**VMM-u** (user). This component runs as a user-level process on the host operating system. It makes resource requests to the host OS, in particular, memory and I/O requests, on behalf of the native mode VMM using system library functions supplied by the host operating system.

An important task of kvm is to provide fast virtualization for frequently accessed guest devices. Specially, the interrupt and timer controllers are provided by the VMM-n component. The advantage is that no consultation of the VMM-u component is required if a guest accesses any of these devices, which reduces the virtualization overhead.

As mentioned earlier, kvm creates for each virtual machine a virtual CPU to hold the guest CPU state. When the guest operating system executes a *privileged instruction*<sup>2</sup>, the hardware virtualization mechanism triggers an "exit" from the virtual CPU execution context to the VMM. If the privileged instruction could not be handled by the VMM-n component, the exit event is propagated to the VMM-u component.

<sup>&</sup>lt;sup>2</sup>Some of the system instructions called "privileged instructions" are protected from use by application programs. They control system functions (such as the loading of system registers). They can be executed only at the most privileged level. If one of these instructions is executed at lower privilege level, a general-protection exception is generated. The x86 WRMSR instruction (write model specific registers) is an example.

The VMM-u component attach to the virtual CPU's execution context one of its threads. And when the Linux kernel schedules the thread, it results in running the guest code. Thus, any modification applied to the Linux scheduler influences also the scheduling of the virtual machines.

Consequently, a virtual machine process could also be preempted by the host interrupts and processes which represents a problem in the case where a real-time application is executed in the virtual machine. Because, if the thread associated to the virtual machine is preempted by another process or an interrupt running in the host, the response time of the currently running real-time task in the guest OS could be affected. A simple solution to this problem is to raise the priority of the virtual machine thread and to configure it as a real-time thread<sup>3</sup>.

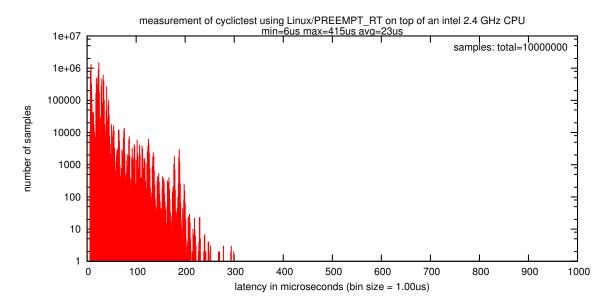

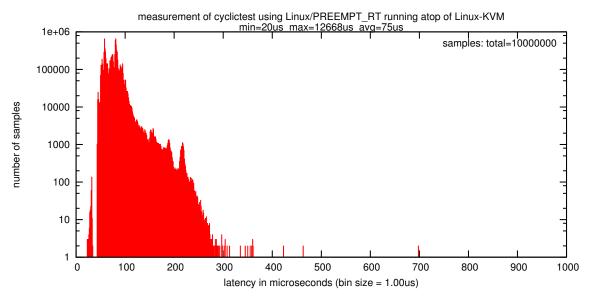

The evaluation of the real-time capability of kvm has been investigated from an implementation perspective. Multiple studies (Bing, 2010; Forsberg, 2011; Åsberg et al., 2011; Kiszka, 2010; Ramachandran, 2013; Zhang et al., 2010b,a; Zuo et al., 2010) measured the *scheduling latency* of the guest operating system. The measurement of this latency usually used the cyclictest benchmark from the rt-test project (Molnar, 2004). Concretely, it repeats the measurement of the sleep() system call latency during a specified duration, for example 15 minutes, or one hour. Then, the results of the minimum, the maximum and the average latency are reported at the end of the experiment.

Testing this benchmark on an operating system that is running on a real hardware and on a virtual machine allow to observe the effect of virtualization mechanism on the operating system performance, and whether the raise of the priority of the virtual machine's process results in an improved performance or not.

The comparison of the measurements of the latency from a native OS vs. an unprioritized guest OS, and vs. a prioritized guest OS, showed that the probability of the multiple milliseconds latency was much higher in the unprioritized guest than on the native OS. The maximum latency exceeded the 100ms (Zhang et al., 2010b). However, the prioritization of the guest OS, that is, configuring the virtual machine thread as a real-time thread and raising its priority, significantly decreased the average latency.

<sup>&</sup>lt;sup>3</sup>In Linux, the threads that are configured to be scheduled under the SCHED\_FIFO or SCHED\_RR scheduling classes are considered real-time as threads and treated prior to the regular non-real-time processes.

Being integrated to the Linux kernel, kvm benefits from the real-time properties of the Linux kernel. Any improvements to the real-time capability of Linux through scheduling algorithms, synchronization, preemption, low latency, or drivers will bring better performance to kvm.

One promising solution in this direction is the use of the PREEMPT\_RT real-time patch to configure the host Linux kernel. In this configuration, the host system is enabled with real-time capability which improves the response time of the virtual machine thread.

The repeating of the precedent experiment (the cyclictest benchmark) using the configured host OS (Linux configured with the real-time PREEMPT\_RT patch) revealed that the application of the PREEMPT\_RT patch reduced the average-case latency to less than 1ms, and removed the 100ms maximum latency observed in the non-prioritized guest OS.

Cucinotta et al. (2009a) evaluated the real-time capability of kvm from a theoretical perspective. The authors investigated the problem of guaranteeing temporal isolation among multiple VMs managed by Linux and kvm, and experimented two test cases. First, they executed two real-time tasks,  $T_1 = (30ms, 150ms)$  and  $T_2 = (50ms, 200ms)$ , on a real hardware. Second, they executed the same task set on a virtual machine using kvm. Then, they measured the response time of all the jobs of the two tasks. The observation of the results showed that when the task set is executed inside a virtual machine most of the deadlines were easily missed.

The authors attributed this result due to the general-purpose scheduling used to allocate the host CPU resources to the virtual machines. They stated that simple solution based on a proportional-fair share algorithm may fail to guarantee a sufficient degree of isolation, and do not generally provide enough control over the granularity of the CPU allocation to the various VMs. The authors also declared that using a *fixed-priority* algorithm would create a second problem because in the case where a higher priority VM consumes more CPU time than expected it could prevent a lower priority VM from running.

The alternative solution proposed by Cucinotta et al. (2009a) is to use the well established realtime scheduling techniques, in particular the *resource reservation* to schedule the virtual machines. Such a technique associates to each VM a reservation tuple  $(\Theta, \Pi)$ , where  $\Theta$  is the processor time reserved for a VM every  $\Pi$  time units.

The proposed approach suits the needs of concurrently running VMs, because it allows to control the amount of time required by each VM, and guarantees the respect of deadlines for the tasks

running inside the VM. This approach relies on the hard reservation variant<sup>4</sup> of the Constant Bandwidth Server (CBS) scheduling policy (Abeni and Buttazzo, 1998). It was implemented using kvm and the AQuoSA framework (Cucinotta et al., 2009b) for Linux kernel.

Given a task set  $\tau = \{T_1, ..., T_n\}$ , a virtual machine VM<sup>k</sup> that is allocated a resource reservation  $(\Theta, \Pi)$ , and using a CBS algorithm to schedule the virtual machine and fixed-priority algorithm to schedule the task set  $\tau$ , it is possible to guarantee the *schedulability* of the task set  $\tau$  if and only if:

$$\forall i \exists t \in P^k : e_i^k + \sum_{j < i} \left\lceil \frac{t}{T_j^k} \right\rceil \cdot e_j^k \le Z^k(t), \tag{2.1}$$

where  $e_i^k$  is the worst case execution time of a task  $\tau_i^k$  in a virtual machine  $VM^k$ .  $Z^k(t)$  is a characteristic function indicating the amount of time allocated to the  $VM^k$  by the root scheduler, and  $P^k$  is a set of appropriate scheduling points.

To evaluate this approach two experiments were conducted. In the first experiment two simple real-time task sets were used in order to easily understand the behavior of the system, and in the second experiment multiple web servers were executed in virtual machines to demonstrate the effectiveness of the approach in a real-world *service oriented architecture* scenario.

In the first test, two task set were used,  $\tau_a = \{T_1(30ms, 150ms), T_2(50ms, 200ms)\}$  was executed on the virtual machine VM<sup>a</sup>, and  $\tau_b = \{T_3(30ms, 120ms), T_4(40ms, 240ms)\}$  on VM<sup>b</sup>.

The results of the tests showed that when the two VMs were executed without CBS the deadlines were easily missed. However, by allocating a resource reservation (a=(28ms,50ms)) for VM<sup>a</sup> and (b=(52ms,120ms)) for VM<sup>b</sup>, all deadlines have been respected. However, the article does not demonstrate how the parameters  $(\Theta,\Pi)$  of each resource reservation were calculated.

### 2.3.2 Microkernel Support for Virtualization

Similar to monolithic operating system, microkernel-based operating systems were also extended to provide the virtual machine monitor functionality. OKL<sup>4</sup> microvisor from Open Kernel Labs, L<sup>4</sup>Fiasco and Nova microhypervisor from the Technische Universitaet Dresden are examples of

<sup>&</sup>lt;sup>4</sup>In the particular case of a hard reservation, the VM is not allowed to execute more than  $\Theta$  time units every  $\Pi$ .

microkernel-based operating systems that are derived from the L4 microkernel family (Liedtke, 1996).

## 2.3.2.1 OKL<sup>4</sup> microvisor

The OKL<sup>4</sup> microvisor is considered as the first commercial VMM deployed on a mobile phone (the Motorola QA4). A prototype based on OKL<sup>4</sup> (Varanasi and Heiser, 2011) was recently ported to the ARM Cortex A15, in order to benefit from the support of the new hardware instruction set that allows the execution of unmodified guest operating system binaries inside a virtual machine. The developed microkernel was evaluated on the ARM *Fast Models* simulator due to the unavailability of hardware implementation of the architecture that supports the virtualization extension.

The evaluation of the VMM implementation on the CPU simulator (not cycle-accurate) allowed to estimate its low-level performances. Using a number of micro-benchmarks the execution time measured in CPU cycles of the VMM routines were calculated based on the instructions count from collected traces, and the weighting of the instructions by their known latencies in cycles from the ARM Cortex A9 processor and an equivalent memory system.

For example, the IRQ (interrupt request) entry, which is the entry to the VMM IRQ routine upon the arrival of an interrupt, is estimated to 239 instructions, which is approximated to 700 cycles. As a comparison to x86 architecture, the same operation measured using the Nova microhypervisor, would costs 4,000 cycles. Switching between virtual machines contexts was done efficiently using the ARM's multi-register operations to save and restore state. Part of this state is kept in co-processor (MMU) and external core such as virtual interrupt and devices registers which are more expensive to access than internal registers. As a result, the overhead of switching between VMs was estimated to 2842 instructions which is equal to 7555 cycles.

The estimated performances of this VMM prototype, and its approximated 6,000 lines of code for its fully-functional version, allowed to take the decision of turning this prototype into a commercial product. However, due to the fact that this implementation is at prototype level, no real-time performance evaluation were conducted yet.

### 2.3.2.2 Nova microhypervisor

The Nova microhypervisor (Steinberg and Kauer, 2010) is the third generation of the L4 microkernel that supports virtualization since its design phase, and not as an extension of existing L4 microkernel versions such as L<sup>4</sup>Fiasco.

Like all the variants of L4 microkernel, Nova is designed based on the principle of small *trusted computing base* (TCB). These systems take an extreme approach to the principle of least privilege by using small kernel that implements only a minimal set of abstractions. Liedtke (1996) recommended three key abstractions that should be provided by a microkernel: address spaces, threads, and interprocess communication. The other functionality should be implemented at user-level.

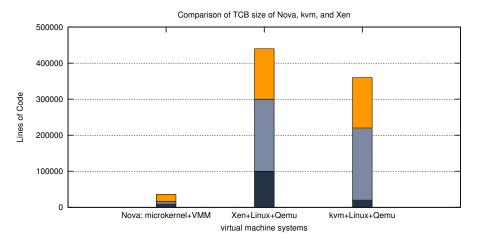

The main characteristic of Nova is its TCB size. The TCB is the part of the software that runs at the highest privilege level, and must be trusted. Comparing to Linux-kvm and Xen, the TCB of Nova is at least an order of magnitude smaller than these systems. Figure 2.4 summarizes the comparison of the total sizes of Nova, kvm and Xen.

Figure 2.4: Comparison of the TCB of three different virtual machine systems.

The size of the Nova's TCB is 9,000 lines of code (LoC), whereas the Xen's TCB is equal to 300,000 LoC, and the kvm is 220,000 LoC. This is because Xen VMM is about 100,000 LoC, and uses a privileged domain<sup>5</sup>, called *dom0*, which is a Linux kernel (200,000 LoC) and all its device drivers. In order to emulate devices, the Qemu hardware emulator is executed as a user application on top of Linux. kvm however is part of the Linux kernel, thus its TCB size is equal to the sum of

<sup>&</sup>lt;sup>5</sup>In the context of Xen, a domain is equivalent to a virtual machine.

Linux kernel source code plus the required file-system, plus device drivers, and the source code of kvm itself (20,000 LoC). In total it is estimated to be 220,000 LoC.

Small TCB is an important security requirement of safety-critical systems. The VMM is responsible for controlling the platform, and if an adversary manages to compromise it, subverting the security of all hosted operating systems would be easy. Reducing the TCB will reduce the attack surface significantly, and thereby improves the security of the system.

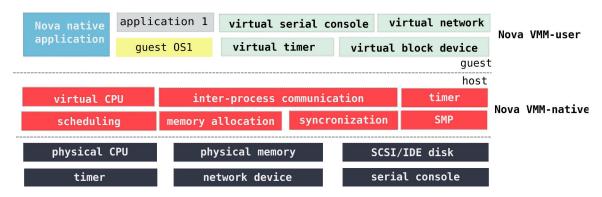

To achieve such a feature, the Nova VMM was designed as a decomposed virtualization architecture that minimizes the amount of code in the privileged VMM as illustrated in Figure 2.5. By implementing the part of the VMM that emulates the instructions at user-level, it was possible to trade improved security for a slight decrease in performance.

Figure 2.5: Nova software architecture.

Regarding the real-time characteristics, Nova implements a fair share scheduling using a preemptive priority-driven round-robin policy with one run-queue per CPU. When invoked, the scheduler selects the highest-priority thread from the run-queue and dispatches it. Once dispatched, the thread can run until its time quantum is depleted or until it is preempted by the release of a higherpriority scheduling context.

#### 2.3.2.3 L<sup>4</sup>Fiasco microkernel

The problem of using a microkernel in a real-time virtual machine system has been explored by Yang et al. (2011). The authors used the L<sup>4</sup>Fiasco microkernel as a VMM and the *paravirtualized*<sup>6</sup>

<sup>&</sup>lt;sup>6</sup>Paravirtualization is a technique for reducing the performance overhead of virtualization by making a guest operating system aware of the virtualization environment. It replaces *privileged instructions* in the guest OS with *hyper-calls* to the virtual machine monitor.

L<sup>4</sup>Linux, a modified version of Linux kernel, in which the HAL (hardware abstraction layer) in Linux have been replaced by a set of calls using the microkernel API (application programming interface). The L<sup>4</sup>Linux is considered by the microkernel as a user-level thread. The Linux kernel uses the set of *hyper-calls* provided by L<sup>4</sup>Fiasco to request the privileged operations that it is not able to perform due to its unprivileged status.

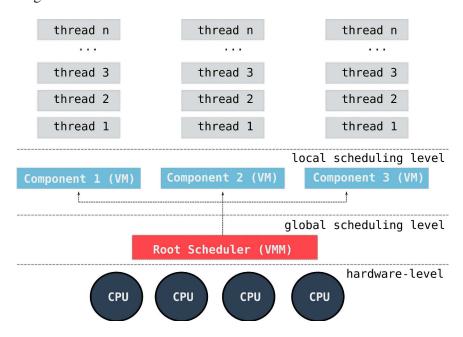

The authors argued that a two-level Hierarchical Scheduling Framework (HSF) is naturally suited to build a real-time virtual machine system. In such a design, the root scheduling level is the microkernel scheduler and the second level scheduler is located at the L<sup>4</sup>Linux scheduler as illustrated in Figure 2.6.

Figure 2.6: Hierarchical Scheduling Framework concept.

The root scheduler in the microkernel schedules the L<sup>4</sup>Linux server<sup>7</sup> using a *periodic resource* model (PRM), denoted by the tuple  $\Gamma = (\Theta, \Pi)$ . And the scheduler of L<sup>4</sup>Linux schedules the real-time tasks. Both scheduling levels employ the *fixed-priority rate-monotonic* policy.

The L<sup>4</sup>Linux server is composed by several L<sup>4</sup>Fiasco threads such as the Linux kernel thread, the timer interrupt thread, and an idle thread. For each real-time task created by L<sup>4</sup>Linux, an L<sup>4</sup>Fiasco *shadow* thread is created and attached to it. Releasing a real-time task in L<sup>4</sup>Linux releases a shadow thread in L<sup>4</sup>Fiasco that executes the user-code on behalf of the task.

<sup>&</sup>lt;sup>7</sup>In the context of hierarchical scheduling theory a server is synonym of component.

In the implementation, the Linux kernel thread and the L<sup>4</sup>Fiasco shadow threads are considered as one scheduling group, and scheduled together using the same execution budget from their associated PRM. However the corresponding interrupt timer thread is treated independently and given a higher priority to ensure that it is scheduled as soon as an interrupt is triggered.

To preserve the execution budget associated to each PRM, a *real-time timeout* has been created and set equal to  $\Theta$  to prevent that the current L<sup>4</sup>Linux kernel thread and subsequent shadow L<sup>4</sup>Fiasco threads from being disturbed by other VM's threads during this amount of time, except by other interrupt threads.

The PRM associated to each virtual machine is calculated dynamically by the L<sup>4</sup>Linux each time a new real-time task is created. The PRM is then given to the VMM which will take into account the new value at the next scheduling period. In the implementation the  $\Pi$  was fixed to 500ms.

To calculate the PRM, the authors fixed the period  $\Pi$  and used the *periodic capacity bound for* rate-monotonic scheduling as defined by Theorem 2.1 to determine  $\Theta$ .

**Theorem 2.1** (Shin and Lee (2003)). For a given workload W, a period  $\Pi$ , and under the fixed-priority rate-monotonic policy, the execution time  $\Theta$  is:

$$\Theta = \max_{\forall T_i \in W} \left( \frac{-(p_i - 2\Pi) + \sqrt{(p_i - 2\Pi) + 8\Pi \cdot I_i}}{4} \right), \tag{2.2}$$

where,

$$I_{i} = e_{i} + \sum_{\substack{T_{k} \in high-priority(W.T_{i})}} \left\lceil \frac{p_{i}}{p_{k}} \right\rceil \cdot e_{k}, \tag{2.3}$$

and  $p_i$ ,  $e_i$  are the period and the execution time of a task  $T_i$  respectively. The PRM is calculated at runtime by the L<sup>4</sup>Linux server and given to the L<sup>4</sup>Fiasco through the I4-rt-change-timeslice() hypercall.

The evaluation of the HSF implementation and its comparison with the round-robin scheduling policy and the RM scheduling policy already implemented in L<sup>4</sup>Fiasco using two virtual machine showed that the HSF was able to avoid any deadline miss of the real-time tasks running in the VMs. Two scenarios have been evaluated, first, the task sets  $\tau_a = \{T_1(1,0.2), T_2(1.2,0.2), T_3(1.5,0.2)\}$  and  $\tau_b = \{T_4(20,2), T_5(30,2)\}$  were executed in VM<sup>a</sup> and VM<sup>b</sup> respectively. Second, the task sets

$\tau_a = \{T_1(8, 1.5), T_2(10, 2)\}$  and  $\tau_b = \{T_3(2, 0.1), T_4(3, 0.1)\}$  were executed in VM<sup>a</sup> and VM<sup>b</sup> respectively.

In the first scenario, the tasks  $T_2$  and  $T_3$  miss some deadlines under the round-robin scheduling and this could be explained by the fact that if all tasks are released at the same time, and the CPU time is shared fairly among the two VMs, the execution of VM<sup>b</sup> delayed the execution of the tasks in VM<sup>a</sup>.

In the second scenario the task  $T_3$  and  $T_4$  incur some deadline miss under the RM scheduling. The reason for this is because VM<sup>a</sup> has given a higher priority than VM<sup>b</sup>, because VM<sup>a</sup>'s CPU utilization = 0.39 and VM<sup>b</sup>'s CPU utilization = 0.28, and VM<sup>a</sup> retains the CPU for 3.5 second which delays the execution of  $T_3$  and  $T_4$  jobs.

With regards to overheads, three operations have been measured, the *selecting of a next thread* in the ready queue, the *setting of the real-time timeout*, and the *calculation of the periodic resource* model interface on a dual-core Intel 2.0GHz machine. The setting of the timer is done every 500ms and is estimated to  $500\mu s$  when two VMs are running. Setting a real-time timeout prevent other VM's tasks from disturbing the execution of the current selected VM. The overhead of selecting the next ready task is less than  $25\mu s$  when two VMs are running. This overhead and the overhead of calculating the PRM depend linearly on the number of running VMs. The most expensive operation is the calculation of PRM due to IPC communication, however the authors argued that this is reasonable because it occurs only when a new task is spawned.

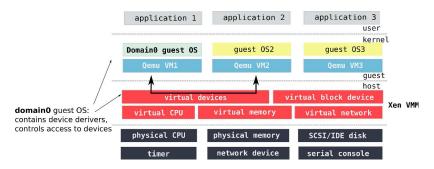

#### 2.3.3 Xen

Xen is a *native VM* system (Barham et al., 2003) that was initially designed to host multiple commodity operating system instances on a modern server. The Xen VMM is responsible for the CPU scheduling and the memory allocation. Xen uses a special guest operating system called *driver domain* containing the device drivers to provide access to the actual hardware I/O devices. Xen VMM grants the driver domain direct access to the devices and does not allow the other guest domains to access them directly. Therefore, all I/O requests must pass through the driver domain. Figure 2.7 illustrates the software architecture of Xen.

Figure 2.7: Xen software architecture.

The Xen VMM protects the guest domains from each other and shares I/O resources through the driver domain. This enables each guest operating system to behave as if it was running directly on the hardware without worrying about protection and fairness.

In the Xen terminology a virtual machine is also called a *domain*. The default scheduler in Xen is the *Credit* Scheduler. The domains in Xen are scheduled according to their state. Each domain could be in the UNDER state or in the OVER state. In the UNDER state, domains still have a remaining credits, and in the OVER state domains have gone over their credit allocation. Credits are periodically debited every 10ms. When a scheduler interrupt occurs the currently running domain is debited 100 credits. The domains' credits are replenished when the sum of the credits of all domains in the system goes negative. When making scheduling decisions, domains in the UNDER state are prioritized over the domains in the OVER state. If there is no domains in the UNDER state and the processors would be idle, the domains in the OVER state could be executed.

The Credit scheduler selects a domain to run depending on its state. It does not considers the absolute number of credits that remain for a domain. Rather, domains in the same state are selected according to the *first-in first-out* policy. Domains are always inserted at the end of the run queue after the domains in the same state. The scheduler selects the domain at the head of the run queue. A selected domains is allowed to run for 30ms as long as its credit allows.

Xen provides a real-time scheduler called the *simple earliest deadline first* (SEDF). It schedules domains according to two parameters: the *slice* and the *period*. Runnable domains are allowed to execute periodically for an amount of time units given by their slice. The SEDF scheduler maintains for each domains a *deadline*, the time at which the current domain's period ends, and the amount of

processing time the domain is due before the deadline passes. The domains are ordered in the run queue according to their deadlines.

According to the SEDF scheduler, a domain can only be activated once if it blocks during its period, independently of whether it has used its whole slice or not. This could represent a problem with regards to the *worst-case execution time*. For example, in the case of a driver domain that is reacting to multiple networking packets, if it finishes processing all pending packets and blocks itself for the remainder of its current period, then if packets arrive while driver domain is blocked, they will be delayed until the next activation of the driver domain by the Xen scheduler irrespective of whether the driver domain has used its complete slice in the current period or not.

Masrur et al. (2010) proposed an improvement of the SEDF by allowing the driver domain to utilize its complete slice within its period independently of its current state (waiting or blocked). Moreover, the critical domains are given higher fixed-priority than the other domains which improve their response time and avoid any deadline miss.

They experimented their implementation by running in each real time domain only one task because they used a standard operating system available for Xen which does not have real-time capabilities. Thus, by running one real-time task per domain, they can still guarantee correct timing behavior, because the real-time task will be scheduled whenever the corresponding domain is scheduled by Xen independently of the scheduler used by the OS in the domain. Using one task per domain allows for a higher CPU utilization, because it is possible to select the slice and the period of each VM to fit the specific requirements of the only task running on it.

In a second work (Masrur et al., 2011), the authors proposed a two-level hierarchical scheduling architecture in Xen. The domains were scheduled under the *rate-monotonic* policy (RM), and the tasks in each domain were scheduled under the *deadline-monotonic* policy (DM), resulting in a DM over RM hierarchical scheduling.

They proposed a method to calculate the optimal time-slice and period for each domain in order to provide a *schedulability condition* for a set of real-time tasks running in a set of domains to meet their deadlines. The period of a domain is specified by the minimum deadline that has to be scheduled on that domain. And the selection of an efficient time slice requires an iterative procedure. Using the minimum requirements for a VM and the schedulability condition of a task running on that VM, they compute the initial domain's time slice. Then, this value is improved towards the

optimum in a reduced number of subsequent steps. In their experimental setup they compared the case where one real-time task was executed per domain to the case where all application's tasks were executed in one domain. They observed that the average response time improves when only one task is executed in one domain.

By providing isolation and managing the access to the hardware resources, a virtual machine monitor allows multiple virtual machines to share the same physical machine safely and fairly. The scheduler within the VMM is responsible for maintaining the overall fairness and performance characteristics of the virtual machine system. Traditionally, maintaining the fair share of the processor resources among the domains was the main focus of the VMM scheduler, and the scheduling of I/O resources was left as a secondary concern. This could result in poor and unpredictable I/O performance, making the virtual machine system less desirable for application whose performance is critically dependent on I/O latency and bandwidth.

Ongaro et al. (2008) explored the relationship between domains scheduling in a VMM and I/O performance. To verify the correctness of their assumptions, the Xen scheduler was used. They examined a number of new and existing extensions to Xen's Credit scheduler targeted at improving the I/O performance.

They analyzed the impact of VMM scheduling on I/O performance using multiple guest domains concurrently running different types of applications. They concurrently tested processor-intensive, latency-intensive, and bandwidth-intensive applications to quantify the impacts of different scheduler configurations on processor and I/O performance. Their tests revealed several insights into the key problems in VMM scheduling.

For instance, they observed that both the Credit scheduler and the SEDF scheduler within Xen achieve a good performance of fairly sharing processor resources among compute-intensive domains. However, the schedulers do not achieve the same performance when bandwidth-intensive and latency-intensive domains are executed.

The Credit scheduler in Xen uses the credit/debit system to fairly share the processor resources. It is invoked whenever an I/O event is sent and boosts the priority of an idle domain receiving that I/O event. However, the domains are not sorted in a run queue according to their remaining credits. To improve the I/O performance, two key optimizations were proposed. First, avoid preempting the driver domain while it is de-multiplexing I/O packets. Second, sort the run queue using the

domains remaining credits. These optimizations come from the observation that the I/O-intensive domains will often consume less credits than the compute-intensive domains. In fact, I/O-intensive domains are not debited any credit if they happen to block before the occurring of the scheduler interrupt. When they become runnable later, their remaining credit do not influence their order in the run queue, it only determines their state (UNDER or OVER) as mentioned earlier. A domain is always enqueued after the last domain in the same state. In the case where there is multiple compute-intensive domains that are inserted in the run queue before the I/O-intensive domain, it will wait for all the preceding domains to finish before it can run, which could increase its response time. However, by sorting the run queue based on remaining credits allows infrequently running, but latency-sensitive domains to run sooner. These two optimizations have a positive effect on the I/O performance of the virtual machine system.

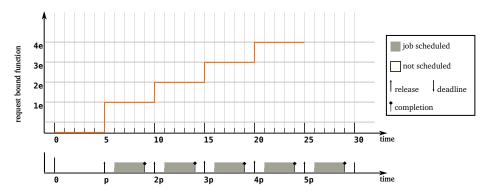

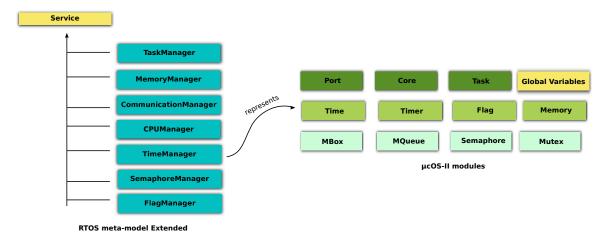

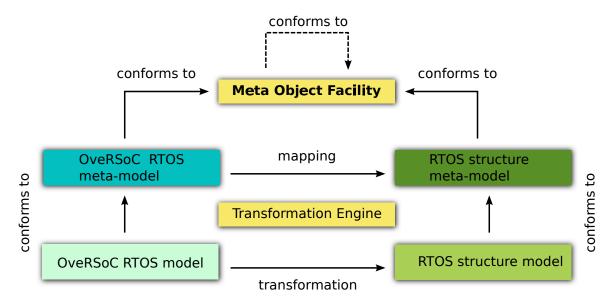

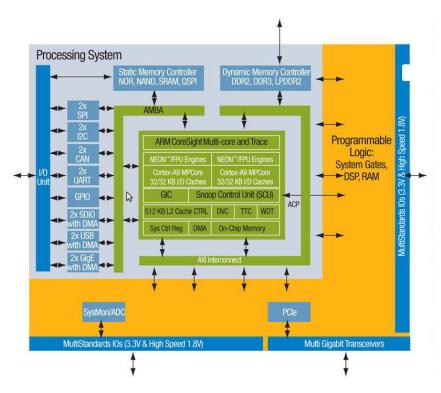

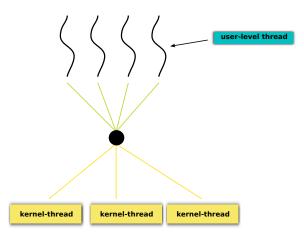

#### 2.3.4 RT-Xen