# Scheduling for new computing platforms with GPUs Florence Monna

# ▶ To cite this version:

Florence Monna. Scheduling for new computing platforms with GPUs. Data Structures and Algorithms [cs.DS]. Université Pierre et Marie Curie - Paris VI, 2014. English. NNT: 2014PA066390. tel-01127919

# HAL Id: tel-01127919 https://theses.hal.science/tel-01127919

Submitted on 9 Mar 2015  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE l'UNIVERSITÉ PIERRE ET MARIE CURIE

Spécialité

### Informatique

École doctorale Informatique, Télécommunications et Électronique (Paris)

Présentée par

# Florence MONNA

Pour obtenir le grade de

# DOCTEUR de l'UNIVERSITÉ PIERRE ET MARIE CURIE

Sujet de la thèse :

# Ordonnancement pour les nouvelles plateformes de calcul avec GPUs

devant le jury composé de :

| M. Jacek Blazewicz      | $\operatorname{Examinateur}$ | Université de Technologie de Poznan    |

|-------------------------|------------------------------|----------------------------------------|

| M. Christophe CÉRIN     | Rapporteur                   | LIPN, Université Paris XIII            |

| Mme Safia Kedad-Sidhoum | Directrice de thèse          | LIP6, Université Pierre et Marie Curie |

| M. Grégory Mounié       | $\operatorname{Examinateur}$ | LIG, Université de Grenoble            |

| Mme Alix MUNIER         | $\operatorname{Examinateur}$ | LIP6, Université Pierre et Marie Curie |

| M. Rizos . Sakellariou  | Rapporteur                   | Université de Manchester               |

| M. Samuel THIBAULT      | $\operatorname{Examinateur}$ | INRIA, Université de Bordeaux          |

| M. Denis Trystram       | Directeur de thèse           | ENSIMAG                                |

|                         |                              |                                        |

# Résumé

Depuis de nombreuses années, les problèmes d'ordonnancement ont traité des systèmes avec des processeurs en parallèle ou bien avec des processeurs dédiés. Avec le développement de nouvelles architectures de calcul, cette classification n'est plus si évidente. De plus en plus d'ordinateurs utilisent des architectures hybrides combinant des processeurs multi-coeurs (CPUs) et des accléérateurs matériels comme les GPUs (Graphics Processing Units). Ces plates-formes parallèles hybrides exigent de nouvelles stratégies d'ordonnancement adaptées. Cette thèse est consacrée à une caractérisation de ce nouveau type de problèmes d'ordonnancement. L'objectif le plus étudié dans ce travail est la minimisation du makespan, qui est un problème crucial pour atteindre le potentiel des nouvelles plates-formes en Calcul Haute Performance.

Après une introduction approfondie de ce nouveau type de systèmes de calcul, une extension de la notation classique des problèmes d'ordonnancement est proposée. Le problème central étudié dans ce travail est le problème d'ordonnancement efficace de ntâches séquentielles indépendantes sur une plateforme de m CPUs et k GPUs, où chaque tâche peut être exécutée soit sur un CPU ou sur un GPU, avec un makespan minimal. Après un aperçu des méthodes de résolution qui ont été utilisées dans ce travail pour s'attaquer à ce nouveau problème, et les problèmes classiques associés, nous présentons les méthodes que nous avons développées pour résoudre le problème d'ordonnancement en premier lieu sur un seul CPU et un GPU, puis ensuite sur m CPUs et k GPUs. Ces problèmes d'ordonnancement sont NP-difficiles, nous proposons donc des algorithmes d'approximation avec des garanties de performance allant de 2 à  $\frac{2q+1}{2q} + \frac{1}{2qk}$ , q > 0, et des complexités polynomiales correspondantes de  $\mathcal{O}(n \log n)$  à  $\mathcal{O}(n^2 k^{\overline{q+1}} m^q)$ , augmentant lorsque les ratios diminuent, en gardant à l'esprit qu'une véritable plate-forme de calcul a besoin d'efficacité autant que de précision dans l'ordonnancement de ses calculs. La méthode de résolution est basée sur un schéma d'approximation duale qui utilise la programmation dynamique de façon à répartir de manière équitable la charge entre les ressources hétérogènes. La méthode de résolution proposée dans ce travail est le premier algorithme générique pour la planification sur des machines hybrides avec une garantie de performance théorique qui peut être utilisé à des fins pratiques.

Des variates du problème d'ordonnancement avec m CPUs et k GPUs sont étudidees. Un cas particulier où toutes les tâches sont accléérées quand elles sont affectées à un GPU, avec un algorithme d'approximation rapide avec un ratio de  $\frac{3}{2}$  pour n'importe quel nombre de GPUs est analysé. Une attention est également accordé aux préemptions, qui peuvent être autorisées sur les CPUs, mais pas sur les GPUs en raison de leur architectures différentes. Nous considérons ensuite le problème de l'intégration du modèle de tâches malléables dans la problématique de l'ordonnancement sur plate-forme hétérogène, et proposons un algorithme avec un ratio d'approximation de  $\frac{3}{2}$ . Certains de ces algorithmes ont été implémentés. Des expériences basées sur des critères réalistes ont été réalisées. Ces algorithmes ont été intégré dans l'ordonnanceur du système d'exécution xKaapi pour les noyaux d'algèbre linéaire, et comparés au classique algorithme HEFT.

Enfin, nous étudions le problème de planification de tâches dépendantes sur des CPUs et GPUs. Nous proposons un algorithme d'approximation avec une garantie de performance de 6 pour ce problème. L'algorithme a une méthode de résolution en deux phases: une première phase basée sur l'arrondi d'une solution fournie par la résolution d'une formulation en programmation linéaire pour l'affectation des tâches aux ressources. Une deuxième phase utilise un algorithme classique de liste pour planifier les tâches en fonction de l'affectation déterminée dans la première phase. C'est le premier algorithme avec une garantie de performance pour la planification des tâches avec contraintes de précédence sur les plates-formes hybrides avec des ressources CPUs et GPUs.

4

# Abstract

For many years, scheduling problems have been concerned either with parallel processor systems or with dedicated processors. With the development of new computing architectures this partition is no longer so obvious. More and more computers use hybrid architectures combining multi-core processors (CPUs) and hardware accelerators like GPUs (Graphics Processing Units). These hybrid parallel platforms require new scheduling strategies. This work is devoted to a characterization of this new type of scheduling problems. The most studied objective in this work is the minimization of the makespan, which is a crucial problem for reaching the potential of new platforms in High Performance Computing.

After a thorough introduction of this new type of computing systems, an extension of the classical notation of scheduling problems is proposed. The core problem studied in this work is scheduling efficiently n independent sequential tasks with m CPUs and k GPUs, where each task of the application can be processed either on a CPU or on a GPU, with minimum makespan.

After an overview of the solving methods that were used in this work to tackle this new problem, and the classical problems associated with them, we present the methods we developed to solve the problem of scheduling on first only one CPU and one GPU, then m CPUs and k GPUs. These scheduling problems are NP-hard, therefore we propose approximation algorithms with performance ratios ranging from 2 to  $\frac{2q+1}{2q} + \frac{1}{2qk}$ , q > 0, and corresponding polynomial time complexities from  $\mathcal{O}(n \log n)$  to  $\mathcal{O}(n^2k^{q+1}m^q)$ , increasing when the ratios drop, keeping in mind that a real computing platform need efficiency as much as accuracy in the scheduling of its calculations. The solving method is based on a dual approximation scheme which uses dynamic programming to balance evenly the load between the heterogeneous resources. The proposed solving method is the first general purpose algorithm for scheduling on hybrid machines with a theoretical performance guarantee that can be used for practical purposes.

Some variants of the scheduling problem with m CPUs and k GPUs are studied. A special case where all the tasks are accelerated when assigned to a GPU, with a faster  $\frac{3}{2}$ -approximation algorithm for any number of GPUs is analyzed. An attention is also paid to preemptions, that can be allowed on CPUs but not on GPUs due to their different architectures. We also consider the problem of integrating the model of malleable tasks into the problem of scheduling on heterogeneous platform, and proposed an algorithm with a performance ratio of  $\frac{3}{2}$ .

Some of these algorithms were implemented. Experiments based on realistic benchmarks have been conducted. These algorithms have been integrated into the scheduler of the xKaapi runtime system for linear algebra kernels, and compared to the state-of-the-art algorithm HEFT.

Finally, we study the problem of scheduling dependent tasks on CPUs and GPUs. We provide an approximation algorithm with a performance guarantee of 6 to solve this problem. The algorithm is a two-phase solving method: a first phase based on rounding the solution provided by solving a linear programming formulation for the assignment of the tasks to the resources. A second phase uses a classical list algorithm to schedule the tasks according to the assignment determined in the first phase. This is the first algorithm with a performance guarantee for scheduling tasks with precedence constraints on hybrid platforms with CPUs and GPUs resources.

# Contents

| 1        | Intr | oducti | ion           |                                                       | 15        |

|----------|------|--------|---------------|-------------------------------------------------------|-----------|

|          | 1.1  | Conte  | xt            |                                                       | 15        |

|          | 1.2  | Objec  | tives and     | Contributions                                         | 17        |

|          | 1.3  | Outlin | ne            |                                                       | 18        |

| <b>2</b> | Intr | oducti | ion to H      | PC and GPUs                                           | 19        |

|          | 2.1  | High l | Performai     | nce Computing and Supercomputers                      | 19        |

|          | 2.2  | Graph  | ical Proc     | essing Units                                          | 21        |

|          |      | 2.2.1  | GPU A         | rchitecture                                           | 22        |

|          |      | 2.2.2  | GPU Pı        | ogramming                                             | 24        |

|          | 2.3  | Summ   | ary           |                                                       | 26        |

| 3        | Nev  | v Nota | ations an     | d Related Works on GPU Scheduling Algorithms          | <b>29</b> |

|          | 3.1  | Notat  | ions          |                                                       | 29        |

|          |      | 3.1.1  | Machine       | es $(\alpha)$                                         | 30        |

|          |      |        | 3.1.1.1       | Sets of Identical CPUs and Identical GPUs             | 30        |

|          |      |        | 3.1.1.2       | Sets of Uniform CPUs and Uniform GPUs                 | 31        |

|          |      |        | 3.1.1.3       | Unrelated CPUs and unrelated GPUs                     | 32        |

|          |      | 3.1.2  | Tasks ( $\mu$ | 3)                                                    | 32        |

|          |      |        | 3.1.2.1       | One type of tasks                                     | 32        |

|          |      |        | 3.1.2.2       | Partial Preemption                                    | 32        |

|          | 3.2  | Relate | ed Work o     | on Scheduling Independent Sequential Tasks            | 34        |

|          |      | 3.2.1  | Exact N       | fethods                                               | 34        |

|          |      |        | 3.2.1.1       | Linear Programming                                    | 34        |

|          |      |        | 3.2.1.2       | Transportation Networks and Network Flow Algorithms . | 36        |

|          |      |        | 3.2.1.3       | Dynamic programming                                   | 38        |

|          |      | 3.2.2  | Approxi       | mation Methods                                        | 39        |

|          |      |        | 3.2.2.1       | List Scheduling                                       | 39        |

|          |      |        | 3.2.2.2       | Dual Approximation Technique                          | 44        |

|          |      |        | 3.2.2.3       | Polynomial Time Approximation Scheme                  | 45        |

|          |      |        | 3.2.2.4       | Heuristics                                            | 46        |

| 4        | Min | imizing the Makespan with Independent Sequential Tasks                                                   | <b>49</b> |

|----------|-----|----------------------------------------------------------------------------------------------------------|-----------|

|          | 4.1 | Considering only one CPU and one GPU                                                                     | 49        |

|          |     | 4.1.1 An arbitrary list scheduling algorithm                                                             | 50        |

|          |     | 4.1.2 Minimizing the sum of the makespans                                                                | 51        |

|          |     | 4.1.3 A knapsack based approach                                                                          | 53        |

|          | 4.2 | Fast algorithms with $m$ CPUs, $k$ GPUs $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 58        |

|          |     | 4.2.1 HEFT algorithm                                                                                     | 58        |

|          |     | 4.2.2 Extending the Knapsack-based Approach                                                              | 59        |

|          |     | 4.2.3 Dual approximation Scheme for solving $(Pm, Pk) \parallel C_{max} \ldots \ldots$                   | 62        |

|          | 4.3 | Improving the Performance Ratio for $(Pm, P1) \parallel C_{max}$                                         | 65        |

|          |     | 4.3.1 Principle of the Scheduling Algorithm                                                              | 65        |

|          |     | 4.3.2 Structure of an Optimal Schedule                                                                   | 67        |

|          |     | 4.3.3 Partitioning the Tasks into Shelves                                                                | 68        |

|          | 4.4 | Extending the $\frac{4}{3}$ -appproximation Algorithm to the multi-GPUs case                             | 72        |

|          | 4.5 | Summary                                                                                                  | 74        |

| <b>5</b> | Two | o families of algorithms                                                                                 | 77        |

|          | 5.1 | Rationale of the Solving Method                                                                          | 77        |

|          | 5.2 | Theoretical Analysis                                                                                     | 80        |

|          |     | 5.2.1 Structure of an Optimal Schedule of Length at most $\lambda$                                       | 80        |

|          |     | 5.2.2 Building the Shelves                                                                               | 81        |

|          |     | 5.2.3 Assigning the Tasks to the Shelves                                                                 | 86        |

|          |     | 5.2.4 Dynamic Programming                                                                                | 87        |

|          | 5.3 | Solving the problem with $k \ge 2$                                                                       | 90        |

|          | 5.4 | Complementary Family of Approximation Algorithms                                                         | 92        |

|          | 5.5 | Summary                                                                                                  | 94        |

| 6        | Oth | er Instances with Independent tasks                                                                      | 97        |

|          | 6.1 | All the tasks are accelerated on GPU                                                                     | 97        |

|          | 6.2 | Partial Preemption                                                                                       | 99        |

|          |     | 6.2.1 Single GPU Case                                                                                    | 99        |

|          |     | 6.2.2 Multiple GPUs Case                                                                                 | 100       |

|          | 6.3 | Moldable Tasks                                                                                           | 101       |

|          |     | 6.3.1 Problem Definition                                                                                 | 102       |

|          |     | 6.3.2 Related Work                                                                                       | L03       |

|          |     | 6.3.3 Building a feasible Schedule                                                                       | 104       |

|          |     | 6.3.3.1 Structuring Tasks into Shelves                                                                   | 104       |

|          |     | 6.3.4 Analysis                                                                                           | 105       |

|          |     | 6.3.4.1 Structure of a Schedule                                                                          | 105       |

|          |     | 6.3.5 Formulation as a Linear Program                                                                    | 108       |

|          | 6.4 | Looking at uniform CPUs and uniform GPUs                                                                 | 12        |

## CONTENTS

| 7 | $\mathbf{Exp}$ | eriments                                                                 | 115 |

|---|----------------|--------------------------------------------------------------------------|-----|

|   | $7.1^{-}$      | $\frac{4}{3}$ -approximation Algorithm Experimental Analysis             | 115 |

|   |                | 7.1.1 First experiments based on random simulations                      |     |

|   |                | 7.1.2 A more realistic benchmark                                         |     |

|   | 7.2            | Experiments with the 2-approximation algorithm and the algorithm for the |     |

|   |                | case when all the tasks are accelerated                                  | 120 |

|   | 7.3            | Experiments on a real run-time                                           | 122 |

|   |                | 7.3.1 Implementation of the $\frac{4}{3}$ -approximation algorithm       | 122 |

|   |                | 7.3.2 Practical issues: 2-approximation algorithm versus HEFT            | 123 |

|   | 7.4            | An Application to Biological Sequence Comparison                         |     |

|   |                | 7.4.1 Motivation                                                         | 124 |

|   |                | 7.4.2 Biological Sequence Comparison and Smith-Waterman Algorithm .      | 125 |

|   |                | 7.4.3 SWDUAL implementation                                              | 127 |

|   |                | 7.4.4 Experimental Results                                               | 127 |

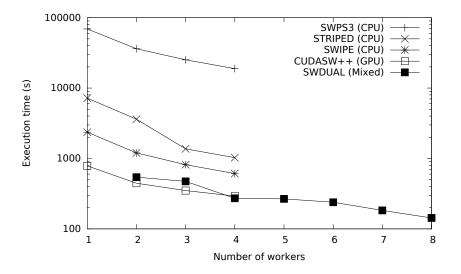

|   |                | 7.4.4.1 Comparison to other implementations                              | 128 |

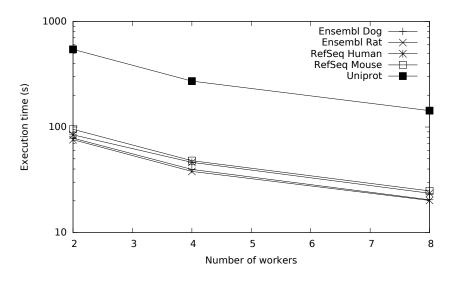

|   |                | 7.4.4.2 Comparison to 5 genomic databases                                | 130 |

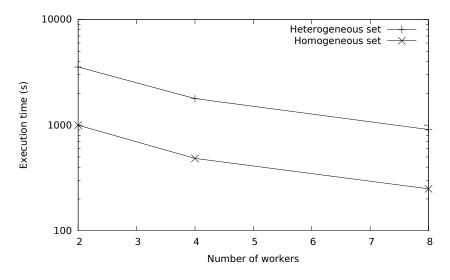

|   |                | 7.4.4.3 Comparison of homogeneous and heterogeneous sets                 | 131 |

|   | 7.5            | Summary                                                                  | 131 |

| 8 | Min            | imizing the Makespan with Dependent Sequential Tasks                     | 133 |

|   | 8.1            | Problem Definition                                                       | 133 |

|   | 8.2            | Related Work                                                             | 134 |

|   | 8.3            | Approximation Algorithm                                                  | 134 |

|   |                | 8.3.1 Preliminaries                                                      | 134 |

|   |                | 8.3.2 Principle of the algorithm                                         | 135 |

|   |                | 8.3.3 Linear Program                                                     |     |

|   |                | 8.3.4 Scheduling Algorithm                                               | 137 |

|   | 8.4            | Analysis of the Algorithm                                                |     |

|   |                | 8.4.1 Properties resulting from the rounding phase                       |     |

|   |                | 8.4.2 A closer look at the schedule                                      | 139 |

|   | 8.5            | A More Accurate Model for Communications                                 | 141 |

| _ | ~              |                                                                          |     |

#### 9 Conclusion

143

CONTENTS

10

# List of Figures

| $2.1 \\ 2.2$                             | An image of Titan, computing platform with GPUs                                                                                                                                                                               | $\begin{array}{c} 20\\ 22 \end{array}$  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

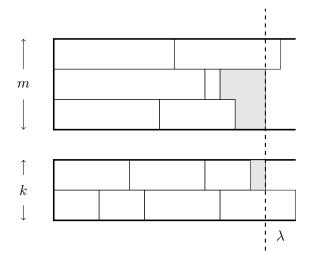

| $\begin{array}{c} 3.1\\ 3.2 \end{array}$ | An example with $m = 6$ CPUs and $k = 2$ GPUs                                                                                                                                                                                 | $\begin{array}{c} 31 \\ 40 \end{array}$ |

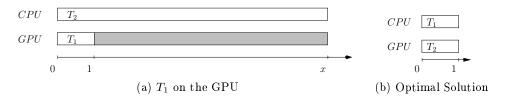

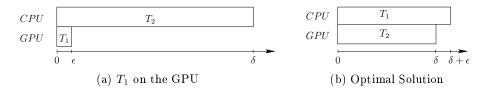

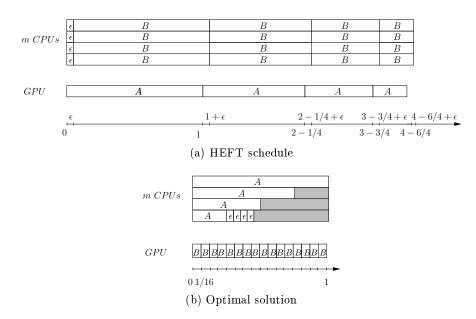

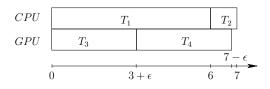

| $4.1 \\ 4.2 \\ 4.3$                      | List scheduling algorithm with two different list orders                                                                                                                                                                      | $50 \\ 52 \\ 59$                        |

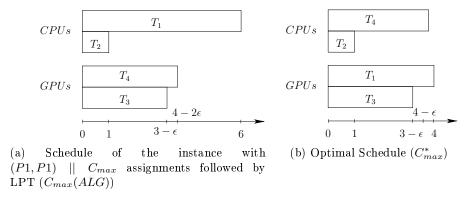

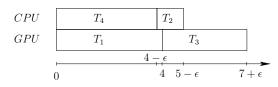

| 4.4                                      | Optimal Schedule of the instance when considered as $(P1, P1) \parallel C_{max}$ ,<br>with makespan $C_{max}(P1, P1)$                                                                                                         | 61                                      |

| 4.5<br>4.6                               | Schedule for the $(P2, P2)    C_{max}$ problem following the $(P1, P1)    C_{max}$<br>assignments, and the optimal solution                                                                                                   | 62                                      |

| 4.7                                      | $C_{max}$ problem                                                                                                                                                                                                             | 62                                      |

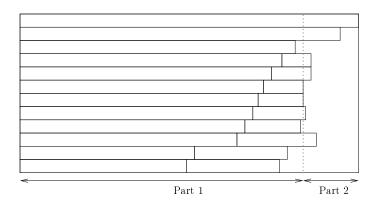

| 4.8                                      | area on the CPUs is lower than $m\lambda$ , otherwise $\lambda$ is lower than $C^*_{max}$<br>Partitioning the set of tasks on the CPUs into two sets of two shelves, the                                                      | 63<br>66                                |

| 4.9                                      | first one occupying $\mu$ CPUs, the second $m - \mu$ CPUs                                                                                                                                                                     | 66<br>70                                |

| 4.10                                     | All the shelves on CPUs and GPUs                                                                                                                                                                                              | 74                                      |

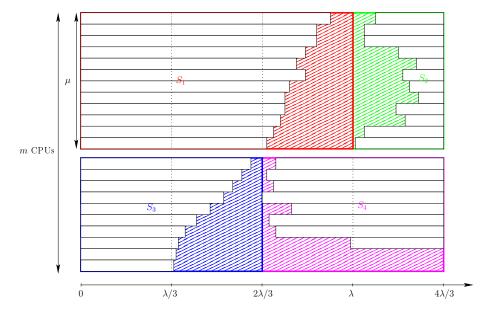

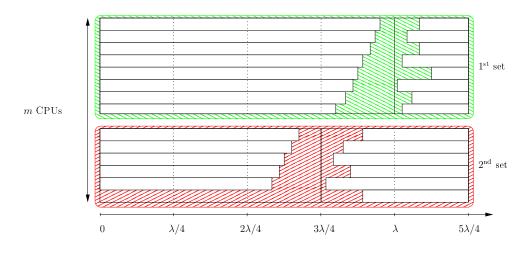

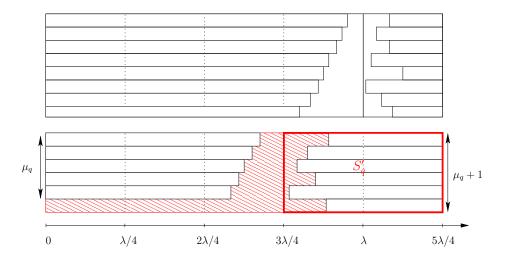

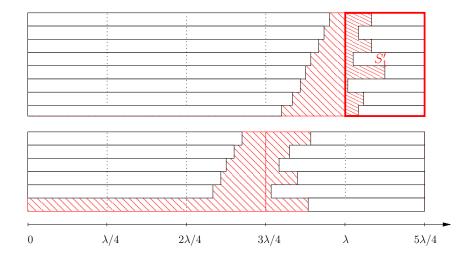

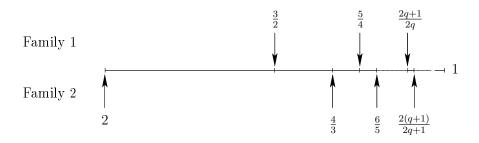

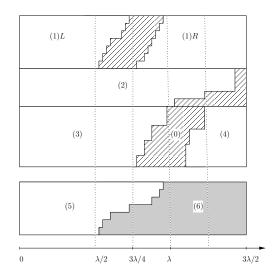

| 5.1                                      | Two sets of two shelves for $g = 5/4$ ( $q = 2$ ), with $m = 14$ CPUs: the first<br>set with two shelves of length $\lambda$ and $\lambda/4$ , and the second one with two<br>shelves of length $3\lambda/4$ and $2\lambda/4$ | 78                                      |

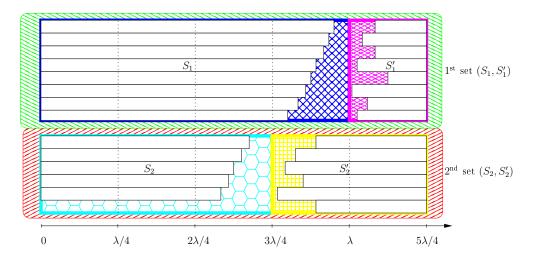

| 5.2                                      | Example for $g = 5/4$ with two sets of two shelves $(S_1, S'_1)$ and $(S_2, S'_2)$ .                                                                                                                                          | 81                                      |

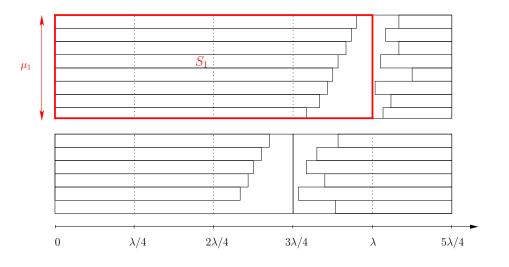

| 5.2                                      | Example for $g = 5/4$ with $m = 14$ , $\mu_1 = 8$ CPUs                                                                                                                                                                        | 82                                      |

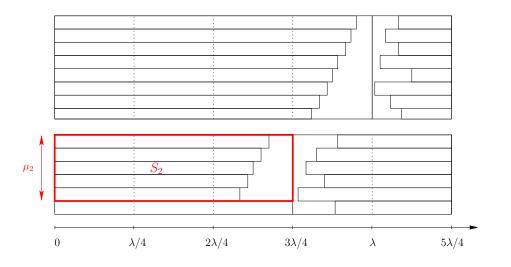

| 5.4                                      | Example for $g = 5/4$ with $m = 14$ , $\mu_1 = 8$ , $\mu_2 = 5$ CPUs                                                                                                                                                          | 83                                      |

| 5.5                                      | Example for $g = 5/4$ . The shelf $S'_q$ and where the tasks with processing                                                                                                                                                  |                                         |

|                                          | time lower than $\frac{\lambda}{2q}$ can be assigned to (for $q = 2$ )                                                                                                                                                        | 84                                      |

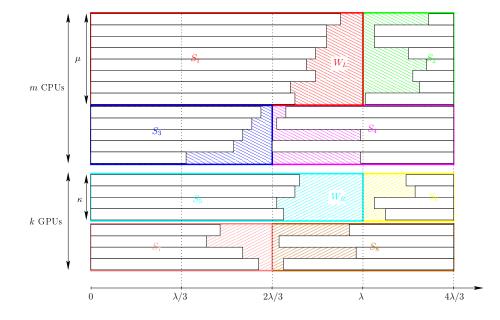

| 5.6                                      | Example for $g = 5/4$ . The free computational space $W_L$ is represented by                                                                                                                                                  | _                                       |

|                                          | the stripped area                                                                                                                                                                                                             | 85                                      |

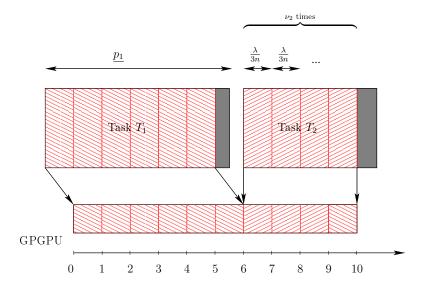

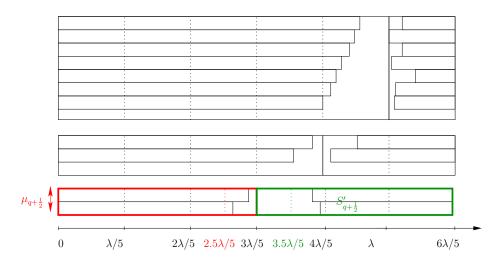

| $5.7 \\ 5.8$ | Example for $g = 6/5$ , where $\lambda$ is the guess                                  |

|--------------|---------------------------------------------------------------------------------------|

| 6.1          | Structure of the schedule. For a better understanding, the processors are overloaded. |

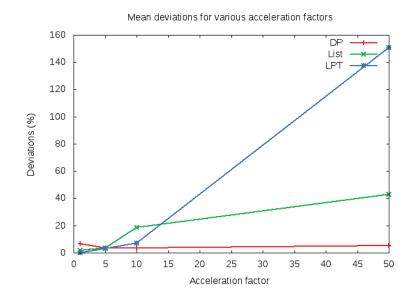

| 7.1          | Gaps for various acceleration factors, $n = 40$ , $m = 1$ and $k = 1$                 |

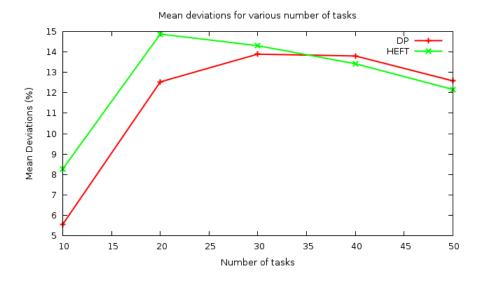

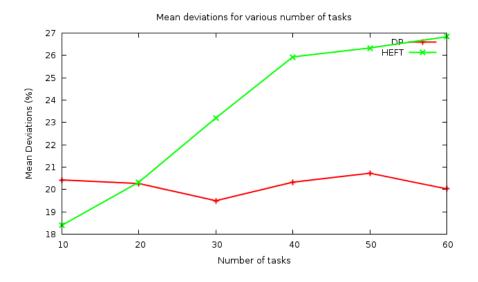

| 7.2          | Gaps for various numbers of tasks, $m = 16$ and $k = 4. \dots 118$                    |

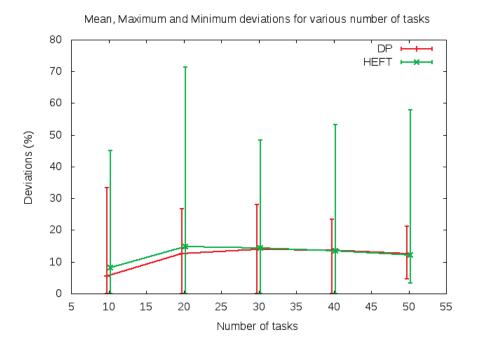

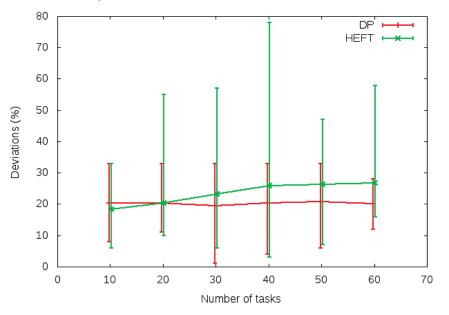

| 7.3          | Maximun, mean and minimum deviations for various numbers of tasks,                    |

|              | m = 16 and $k = 4$                                                                    |

| 7.4          | Gaps for various numbers of tasks, $m = 1$ and $k = 1$                                |

| 7.5          | Maximun, mean and minimum deviations for various numbers of tasks,                    |

|              | m = 1 and $k = 1$                                                                     |

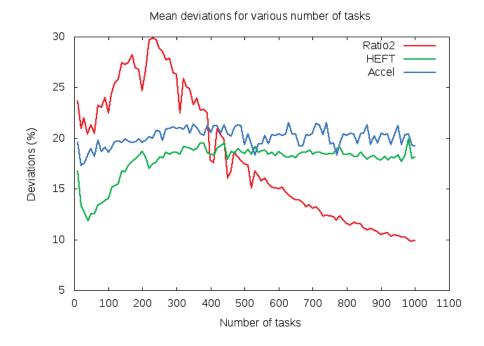

| 7.6          | Mean deviations of Ratio2, HEFT and Accel for various $n. \ldots 122$                 |

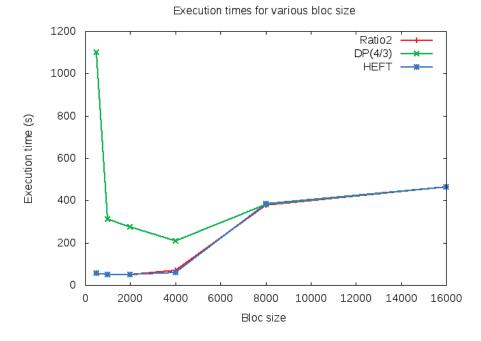

| 7.7          | Execution time of a Cholesky factorization scheduled by Ratio2, DP $(4/3)$            |

|              | and HEFT for various block sizes, on 3 hyper threaded CPUs and a single               |

|              | GPU                                                                                   |

| 7.8          | Example of an alignment and score                                                     |

| 7.9          | Execution times in seconds for the compared implementations                           |

| 7.10         | Execution times for the compared databases with SWDUAL                                |

| 7.11         | Execution times for the heterogeneous and homogeneous sets for SWDUAL.132             |

| 8.1          | An illustration of the different types of time intervals                              |

# List of Tables

| 3.1          | Problems with no equivalent counterpart in the literature studied in this work                                                                                                      |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2          | Problems related to classical scheduling problems                                                                                                                                   |

| 4.1          | Problems studied in this chapter and the algorithms developed for them. $~.~75$                                                                                                     |

| $5.1 \\ 5.2$ | Associated costs and ratios for different values of $k$                                                                                                                             |

| 7.1          | Mean deviation for $m = 16$ and $k = 1, 4$ with different values of $n \dots \dots 117$                                                                                             |

| 7.2          | Mean deviation for $m = 16$ and $k = 1, 4$ with different acceleration factors . 117                                                                                                |

| 7.3          | Maximal deviations (%) for Ratio2, HEFT and Accel                                                                                                                                   |

| 7.4          | Performance of the 2-approximation algorithm and HEFT for Cholesky                                                                                                                  |

|              | factorization with $m=4$ CPUs and $k=8$ GPUs $\ldots \ldots \ldots$ |

| 7.5          | Applications included in the comparison                                                                                                                                             |

| 7.6          | Execution times (s) for the compared implementations                                                                                                                                |

| 7.7          | Genomic Databases used on the tests                                                                                                                                                 |

| 7.8          | Results running on CPUs and GPUs                                                                                                                                                    |

| 7.9          | Results running the homogeneous and the heterogeneous sets for SWDUAL.132                                                                                                           |

| 9.1          | Problems related to the classical ones and the corresponding algorithm costs.143                                                                                                    |

| 9.2          | Problems with no equivalent counterpart in the literature studied in this                                                                                                           |

|              | work                                                                                                                                                                                |

# Chapter 1

# Introduction

## 1.1 Context

In several domains, complex and powerful computations are necessary. Their applications are very diverse, such as real-time finance, weather predictions, molecular modeling, and countless areas of physics.

This need for more computational resources and the considerable technological advances of these last few years have led to the construction of large-scale hierarchical computing platforms for High Performance Computing (HPC). These new platforms are constituted of parallel multi-core processors with a great number of computing units (again called processors), where these units can be heterogeneous: at the finest level, classical processors (CPUs) share a large memory with additional hardware accelerators like General Purpose Graphical Processing Units (GPGPUs, or, in short GPUs) [56]. Indeed, in some domains requiring HPC, the parallelism of processors of the same type is not the best solution. An example where different types of parallel processors are used is DNA assembling problem, where hundreds of millions of DNA chains have to be aligned and the resulting chromosome is to be constructed. In short, this approach requires at the first stage (alignment of DNA chains) a multi-GPU machine, while the second stage (construction of a corresponding DNA graph and finding the resulting path) should be done on a parallel CPU system [7,8,53], meaning several CPUs working in parallel to execute complex calculations.

There is an increasing complexity within the internal nodes of such hybrid parallel systems, mainly due to the heterogeneity of the computational resources. To take advantage of the benefits offered by these new features in terms of performance, there is an important need for an effective, automatic management of these hybrid resources at the finest level. Indeed, no just a computing platform does not execute one calculation at a time. There are only a few of these machines for a much greater number of customers with calculations to perform.

These new characteristics have given rise to new scheduling problems, consisting in allocating and sequencing the computations on the different resources such that a given

objective is optimized. The objective in High Performance Computing (HPC) is to execute as fast as possible all the tasks of an application. This means that the aim is to determine the ending time of the execution of the application defined by the largest completion time (makespan) of the tasks on CPUs and GPUs.

The existing scheduling algorithms and tools, abundantly studied and used on previous generation execution systems, are often not well-suited for these new platforms. Then the main challenge is to create adequate generic scheduling methods and software tools that fulfill the requirements for optimizing the performances.

In the field of parallel processing, a huge amount of work has been devoted to implementations of *ad hoc* algorithms using GPU or hybrid CPU-GPU architectures. They expand over several aspects of parallelism from operating system, runtime, application implementation or languages. However, only few of them focus on the intermediate problem of scheduling on hybrid platforms [71]. Most of the works in the literature consist in studying the gains and performances of parallel implementation of some specific numerical kernels [1,80], or specific applications like multiple alignments of biological sequences [13], or molecular dynamics [70]. The existing scheduling algorithms and tools are usually not well-suited for general purpose applications since the internal hardware organization of a GPU highly differs from a CPU and thus, the GPU should be considered as a new type of resources in order to determine efficient approaches. Scheduling is usually done on a case by case basis and often offers good performances, however, it lacks high-level mechanisms that provide transparent and efficient schedules for any application. Some actual runtime systems include the basic mechanisms for developing scheduling algorithms like OMPSS [16], StarPU [3] or XKaapi [34]. Several scheduling algorithms have been implemented on top of these systems and most scheduling policies are restricted to fast greedy algorithms or work stealing [10, 59]. An online algorithm with a performance guarantee [18] has recently been developed for CPU-GPU platforms, but, to the best of our knowledge, there is no performance guarantee for any offline problem on these systems.

This means that if a customer of a computing platform wishes his/her calculation done in a reasonable amount of time by the platform, considering other users' calculations, there is a chance that the platform scheduling algorithm will assign the calculation to a not-so-well suited processor that will upset the whole schedule of the platform and delay the obtaining of results for all the users of the computing platform.

Let us consider for example the case of one user: a nuclear physicist needs to calculate the independent trajectories of 10 billion neutrons, photons, electrons and positrons inside a nuclear reactor to determine the energy deposition that results from these particle movements inside the reactor [87]. In order to simulate these trajectories, he requests for 512 processors on the CEA computing platform Curie (see Chapter 2) for approximately 24 hours. The batch scheduler of Curie receives the request and assigns the 10 billion calculations a priority depending on the physicist computational quota on Curie. When there is no more calculations with a higher priority in the queue of Curie or if the occupation of 512 processors for 24 hours has not impact on the completion

#### 1.2. OBJECTIVES AND CONTRIBUTIONS

time of any task with a higher priority waiting to be scheduled, the physicist calculations are assigned to the first group of 512 processors that become free on the platform. The scheduler then considers those 512 processors occupied for the next 24 hours whereas the calculations could be finished earlier with a finer scheduling on these 512 processors. That is the problem we focused on during this PhD. We worked on providing scheduling algorithms for a given set of calculations on a given set of processors, composed on CPUs and GPUs, all gathered on a computing platforms.

#### **1.2** Objectives and Contributions

Since no generic method existed for scheduling calculations on a CPU-GPU platform prior to this work, our objective is to propose a characterization of this type of platform in the scheduling area as well as new scheduling algorithms for a general purpose execution on hybrid CPU-GPU architectures designed for HPC, algorithms that may remain suitable for the successive generations of the evolving computing platforms. The methods that we developed determine the assignment and schedule of the tasks of an application to the computing units, CPUs and GPUs. To the best of our knowledge, there was no automatic approach to solve this strategic problem prior to this work. Various sides were possible to address this problem. A first possibility was to adapt existing models such as unrelated processors or dedicated processors. Another way was to see this problem as the placement of malleable tasks with varying processing times. We could have also considered scheduling problems where it is assumed that the duration of tasks can be reduced with a compression  $\cos [76]$ . Approaches such as work stealing [10, 59] from GPU to CPU might also have been considered. The approach we followed was to first determine an appropriate model, capable of taking into account the new characteristics of these systems, and devise appropriate notations for the corresponding scheduling problems. We then developed several algorithms for the case with independent tasks, using several methods such as dynamic programming and the dual approximation technique [43]. Those algorithms are a major contribution to the field of heterogeneous scheduling, being the first in this field to have both practical efficiency and performance guarantee. From this basis we moved on to more specific or complex instances, such as the specific case where all the tasks to be scheduled are accelerated when assigned to a GPU, but not necessarily with the same acceleration factor for all the tasks, which is a case frequently encountered in practice, for instance in DNA sequence comparisons. Another case studied was the case where preemptions are allowed for the tasks assigned to the CPUs, but not for the tasks on the GPUs, since preemptions are possible on classical processors but not on GPUs. The case where the tasks are considered malleable when they are assigned to a CPU and sequential when assigned to a GPU was also considered, since the malleable task model is often used when communications occur within a platform. Finally, not every calculation is independent from the others on a computing platform, therefore the case where the tasks are linked by precedence relations. The last two problems mentioned

represent again a significant contribution to the heterogeneous scheduling field. We validated these algorithms conventionally in the combinatorial optimization community through complexity and approximation analysis, but also by real-sized tests on cards that were available, notably in Grenoble<sup>1</sup>, and applied them to DNA sequence comparisons on real genomic database.

### 1.3 Outline

The outline of the manuscript is as follows. We present in Chapter 2 an introduction to the multiprocessor architectures and the uses of GPUs. In Chapter 3 we introduce new notations for this type of scheduling problems, and present some related works in the field of scheduling and highlight the gaps that need filling in the area of CPU-GPU scheduling. We present in Chapter 4 a formal description of the problem of minimizing the makespan with independent tasks on m CPUs and k GPUs, which is followed by the detail of different approaches, and the corresponding experiments. In Chapter 5, we generalize the approach developed in the previous chapter into a whole family of approximation algorithms for the same scheduling problem. Chapter 6 deals with other scheduling problems with independent tasks we investigated, such as the special case where all the tasks are accelerated when assigned to a GPU, or the problem where the tasks are considered malleable, or when preemptions are allowed on the CPUs. Experiments realized for the problems studied in these chapters are presented in Chapter In Chapter 8, we present the problem of scheduling tasks linked by precedence constraints on CPUs and GPUs and the approximation algorithm we developed to solve this problem. Finally, the conclusion and perspectives of this work is presented in Chapter9.

<sup>&</sup>lt;sup>1</sup>the tests were performed by the MOAIS team from the LIG, notably Grégory Mounié, Raphaël Bleuse and Fernando Mendonca.

# Chapter 2

# An Introduction to High Performance Computing and GPUs

In Chapter 1, we have seen the need for large computing platforms with a great number of processors, an introduction to these platforms should be given more thoroughly, and the same should be done concerning the Graphical Processing Units (GPUs) that are the focus of this work. This chapter is more technical than the rest of the thesis, in order to highlight the major differences and therefore specificities of the heterogeneous platforms with GPUs that we dealt with in this work in terms of scheduling.

# 2.1 High Performance Computing and Supercomputers

The first large-scale computing platforms were designed in the 1960s by Seymour Cray [19] for the biggest company in the field of supercomputers until the 1970s, Control Data Corporation (CDC). Seymour Cray left CDC in the 1970s, and founded Cray Research, a company that surpassed CDC and its other opponents until 1990 [72]. During the 1980s, a lot of small companies went in the business of supercomputers, but most of them sank during the crash of this market in the middle of the 1990s. In the 21st century, large-scale computing platforms are mostly conceived as unique objects by traditional computer firms such as IBM, HP or Bull, whether they have a long lasting tradition in the domain (IBM) or that they bought in the 1990s some specialized companies to acquire their expertise.

The term computing platform varied with time, since the most powerful computers in the world at one moment in time tend to be equaled and then surpassed by ordinary desktop computers later on. The first supercomputers CDC were simple computers with a single processor (but having sometimes up to ten peripheral processors for the inputs and outputs) around ten times faster that their opponents [89]. During the 1970s, most supercomputers adopted vectorial processors, that decoded an instruction only once to apply it to a whole series of operations. It is only at the end of the 1980s that the technique of massively parallel systems was adopted, with the use in one computing platform of thousands of processors [27]. Nowadays, some computing parallel platforms use Reduced Instruction Set Computer (RISC) microprocessors designed for serial PCs, such as PowerPC (IBM) or PA-RISC (HP) processors [4]. Others use cheaper processors with a Complex Instruction Set Computer (CISC) [54] outer appearance that are microprogrammed in RISC in the chip (AMD, Intel), such as x86 processors: the performances are a little hindered, but the memory access, usually a key parameter, is far less solicited.

Computing platforms are used for all the tasks that need large computing power, such as weather predictions, climate studies, DNA sequencing, molecular modeling, physics simulations (aerodynamics, material resistance, nuclear explosions, nuclear fusion...), cryptography, finance and insurance simulations, etc... Research institutions, both civil and military, are some of the biggest users of computing platforms.

The scale and capabilities of these platforms have grown considerably since the first computing platforms were designed. The Top500 website [83] lists the 500 most powerful computing platforms in terms of the number of operations per second they can achieve. In the June 2014 list, the Chinese computing platform Tianhe-2 was ranked number one with a computing power of 33.86 PFlops ( $10^{15}$  FLoating point Operations Per Second). It is composed of 16,000 computer nodes, each comprising two Intel Ivy Bridge Xeon CPUs and three Xeon Phi accelerator chips, counting a total of 3,120,000 cores. The second place on the June 2014 list is occupied by a heterogeneous platform with GPUs: Titan, built by Cray Inc. for Oak Ridge national laboratory in Tennessee (see Figure 2.1). It uses a hybrid architecture composed of 18 688 CPUs, processors with 16 cores at 2.2 GHz, AMD Opteron 6274, and 18688 Nvidia GPU accelerators, Tesla K20X.

Figure 2.1: An image of Titan, computing platform with GPUs.

Titan's computing power reaches 17.59 PFlops, and could reach theoretically up to 27 PFlops at peak performance. It was also ranked 3rd on the Green500 list of November 2012, thanks to its hybrid architecture with GPUs: its performance per watt is about 2.1 GFlops/W.

In France, we find these machines in the computing centers of universities such as IDRIS, CINES, but also in the CEA and also in some large companies (Total, EDF or Meteo-France). One of these platforms is Curie, a computing platform for the CEA, designed by Bull, with a computing power of 2 PetaFlops (PFlops). It possesses three

20

#### 2.2. GRAPHICAL PROCESSING UNITS

computing architectures, the "fat" nodes, the "thin" nodes and the "hybrid" nodes, the last category being composed of heterogeneous processors with GPU accelerators: the "hybrid" nodes are composed of a combination of Intel Westmere CPUs and Nvidia M2090 T20A GPUs, for a total of 288 Intel and 288 Nvidia processors. In October 2012, Curie was the 9th most powerful computing platform in the world, and the most powerful computing platform in France until the Ada and Turing systems were installed at IDRIS in January 2013, and in march 2013, the computing platform Pangea, owned by Total, was launched, becoming the most powerful computing platform in France, with a computing power of 2.3 PFlops. Pangea and Curie were respectively ranked 16<sup>th</sup> and 26<sup>th</sup> on the June 2014 Top500 list.

We can see that computing platforms have reached high levels of computational power over the years and their overall complexity has grown with them. These platforms are able to process and transfer massive amounts of data in a very short amount of time. However, information cannot travel faster than the speed of light between two parts of a given platform. Therefore, when the size of a computing platform goes over several meters, the latency between some components can be counted in dozens of nanoseconds. The components of the platform have to be organized to limit the length of the cables linking the components, and the design of a computing platform must ensure that all data can be read, transferred and stored quickly, otherwise the computing power of the processors would be under-exploited. A possible solution to that problem is to use accelerating processors such as Intel Xeon Phi processors or GPUs, that are able to perform simple parallel computation at a very high speed, saving space and power. However, GPUs were not designed for such a general purpose use. Let us focus on the specificities of these processors.

## 2.2 Graphical Processing Units

Graphic calculations can be very costly, especially if the rendering must be of good quality. The first computers did not have graphical processors. Central processors (CPUs) did all the calculations necessary. In order to focus the CPUs resources on more demanding calculations, graphical processors were added to computers. A GPU (Graphical Processing Unit) was dedicated to the calculations regarding graphics. This specialization made it very fast, in opposition to the common CPU, with a more generic purpose and therefore slower. Over the years GPUs became more complex and versatile. At the end of the 90s, GPUs were capable of computing the calculations necessary for three dimensional graphics. During the 2000s, GPUs slowly became programmable for applications other than graphical imagery and video games. Two important companies design GPUs: NVIDIA and ATI. They increased over the years the raw computing power of their GPUs and at the same time rethought the processors' architecture to enable a more comfortable use. In 2007, NVIDIA released CUDA 1.0, a programming language only for its GPUs. ATI did not release its own software, but support a more generic language that works on the GPUs of both companies, OpenCL. From this point forward, the new generations of GPUs are called General Purpose Graphical Processing Units (GPGPU). This PhD thesis focuses on the newest generations of GPUs that are used in High Performance Computing, therefore the GPUs considered are all GPGPUs, but for simplicity, they will be called GPUs.

#### 2.2.1 GPU Architecture

Since it was originally designed to perform only graphical calculation, a GPU's architecture differs greatly from a CPU's architecture.

In Figure 2.2, different elements of GPUs and CPUs are represented. The size of the blocks in the figure is proportional to the real size of the components, considering the number of transistors in each component [29]. A CPU (resp. GPU) is composed of the upper block in the figure, the Dynamic Random Access Memory (DRAM) being physically separated from it.

Figure 2.2: Sketch of a CPU architecture (left), and a GPU architecture (right).

A CPU first has a cache, a memory space of a small size but extremely fast. It is used as a work memory for the CPU calculations. Half of the processor's transistors compose the cache. The Arithmetic Logic Unit (ALU, see Figure 2.2) are the calculation units. Their number varies from one architecture to the other. They represent one quarter of the CPU's transistors. Finally, the control structure (Control in Figure 2.2) occupies the last quarter of the CPU's transistors. It contains the connection prediction and has two functions. A CPU is able to perform a great number of operations, so using its different calculation units at the same time can be difficult. The operations are computed in a random order (when it is possible) to optimize the occupation of the ALUs of the CPU, and the control structure determines the order of these operations. The second function of this structure deals with memory latency [55]. When the process occupying the processor needs a variable stored in the memory to go on with the calculations, there are two possibilities: the variable is in the cache (fast access) and the calculation is not slowed, or the variable is in the central memory, with a slow access. The second case is called a "cache miss", and the time lost to retrieve the variable is a time lost for the

#### 2.2. GRAPHICAL PROCESSING UNITS

whole processor. In order to use this time better, the connection prediction makes an assumption on the value of the variable and goes on with the calculation. When the memory access is finished, the assumed value is compared to the real value: in some cases it is identical, and the processor has not lost any time. Otherwise the time is lost anyway. This method is particularly efficient on conditional loops such as:

The processor starts one of the two calculations and has (on average) a 50% chance to keep its calculations at the end of the memory access.

On a GPU, roughly 90% of the transistors are dedicated to the calculation units, giving it a raw calculation power extremely high. These calculation units are individually simpler (and thus less efficient) than the ones of a CPU, but their huge number greatly compensate this weakness. The GPU's calculation units are called Streaming Processor (SP), and are grouped at different scale. Eight Streaming Processor form a Streaming Multiprocessor (SM). Three Streaming Multiprocessor form a Thread Processing Cluster (TPC). All the SP of one Streaming Multiprocessor execute the same task called thread on different data. Each SM has a shared memory accessible by the eight SPs. Cumulated, the cache memory of the GPU is smaller than the cache memory of the CPU. This does not create too many problems, the cache requirements of a GPU being lower than the ones of a CPU. Finally there is one control structure per SM. These structures are very different from the ones observed on CPU because of specific constraints. There is no prediction mechanism on the GPU because there exists a more efficient solution. In the right configuration, the GPU has more threads to compute than it can run simultaneously. Therefore, when a thread being computed needs a value from the DRAM for a variable, it is put aside and a thread in a waiting queue gets access to the GPU and starts (or resumes) its calculation. This process exchange is called a content change. When the first thread receives the value for its variable in the GPU cache, it resumes its calculation. Context changes are extremely fast on GPU, and very slow on CPU, which explains why this solution is not used with CPUs. Therefore, it is essential to occupy the GPU with a great number of simultaneous tasks to allow it context changes as often as it needs.

Since a CPU sequentially processes complex tasks, it needs complex control structures with an important number of transistors. The cache must be large enough to ensure that the majority of the variables necessary for the calculations can be included in it. Since a GPU processes groups of simple identical tasks, its control structures have a small size and small caches are sufficient.

From a scheduling point of view, this indicates that the type of a task influences the values of its processing times on CPU and on GPU: if it requires a lot of data, its

processing time on GPU will not be much better than its processing time on CPU, since any computational time gained will be hindered by the time needed to fetch the data required for the computations, too big to fit on the small GPU cache. If the calculation time is much smaller than the time for data transfer, the full execution can actually take longer on GPU than on CPU. The calculations that are good candidates for an execution on GPU are complex calculations on a small data volume.

**Example 2.2.1.** Calculating the sum of two diagonal square matrix of size n. The time complexity of the calculation is in  $\mathcal{O}(n)$ , when the sizes of the entry data and exit data to copy vary in  $\mathcal{O}(n)$ .

**Example 2.2.2.** Inverting a square matrix of size n.

The size of the data to copy varies in  $\mathcal{O}(n^2)$ , and the time complexity of the calculations varies in  $\mathcal{O}(n^3)$ .

Example 2.2.2 seems to be a better candidate for GPU execution. Indeed, for a value of n large enough, the time of data transfer becomes negligible compared to the calculation time.

The different architectures of CPUs and GPUs leads to different memory management mechanisms that influence the processing times of a task on CPU and GPU, depending on the type of the task to compute.

### 2.2.2 GPU Programming

The different memory management mechanisms on CPU and GPU discussed in the previous section have an impact on the programming of GPUs. Indeed, the first phase of a calculation on a GPU must be the copy of the entry variables from the CPU memory to the GPU memory, and the last phase is always the copy of the exit variables from the GPU memory to the CPU memory. Let us take an example to visualize the different steps in a GPU calculation.

**Example 2.2.3.** Vector addition element by element Compute  $Y = \alpha + X$ , Y and X being two vectors of 1024 float.

The program allocate memory on the CPU (input, output) and on the GPU (input\_ gpu,output\_gpu)

```

input = OpenCL::VArray::new(FLOAT, 1024)

output = OpenCL::VArray::new(FLOAT, 1024)

input_gpu = create_buffer(1024*4)

output_gpu = create_buffer(1024*4)

```

The command to copy the input buffer from the CPU memory to the GPU memory is the following one in the programming language OpenCL

```

enqueue_write_buffer(1024*4, input, input_gpu)

```

#### 2.2. GRAPHICAL PROCESSING UNITS

and the following command is for copying the output buffer from the GPU memory to the CPU memory

enqueue\_read\_buffer(1024\*4, output\_gpu, output)

As we have seen in the previous section, these memory transfers have a non negligible impact on the total execution time on GPU and must be done carefully, in order to keep these transfer times minimal compared to the computation time of a task.

The other phase in a GPU calculation is the calculation itself. In order to get a good acceleration on the processing time of a task when compared to its CPU processing time, the calculations executed on GPUs must also be programmed with a lot of parallelization in their code, and therefore they have to be parallelizable. Matrix calculations are good candidates with respect to this criterion: there can be as many threads on the GPU as there are matrix coefficients. Each SP takes care of one coefficient of the calculation. It is up to the programmer to specify the number of threads he wants to execute, as well as their organization. On GPU, the parallel routines are called kernels: the threads of one kernel execute the same code on different data. The code for the calculation on the GPU corresponding to Example 2.2.3 is the following in OpenCL:

```

prog = create_program([<<EOF

__kernel void addition( float alpha,

__global const float *x,

__global float *y) {

size_t ig = get_global_id(0);

y[ig] = alpha + x[ig];

}

EOF

])

create_kernel("addition",prog)</pre>

```

In a kernel, threads are organized in blocks: a block can have one, two or three dimensions, depending on the programmer's choice and the material constraints. The blocks themselves are organized into a grid of blocks. Similarly, the grid can have one, two or three dimensions. Each thread has access to variables specifying its position in the grid and in the corresponding block. Therefore, a thread in a typical kernel working on matrix starts by using these variables to define a couple of indexes (i, j) that are specific to this thread. As a result, the thread works on index (i, j) of the matrix. This corresponds to the following command in OpenCL for Example 2.2.3, that computes the kernel with the arguments and vector of size  $1024 = 16 \times 64$  float split into a grid of 16 blocs, each block containing 64 threads:

Since threads share the same global memory, it is necessary to prevent different threads from writing in the same memory space at the same time. Loading threads regularly is also very important. GPU executes threads in groups (or *warps*), and the processing of one group is finished when all the threads of the group are finished. It is therefore essential to avoid conditional loops that disturb load balance.

These programming difficulties have to be considered by the programmer and are in no way handled by the scheduler of a computing platform, but it affects the processing times the tasks of the programmer will have on GPU, and therefore are another reason why the processing time of a task on GPU can be very variable and may not be determined with an acceleration rule corresponding to its type or its degree of parallelization. Depending of the skills of the programmer and the hardware specifications of the platform GPUs, this degree of parallelization may not be exploited to its full potential. However, it is commonly admitted that an accurate estimation of the processing times of tasks can be obtained at compile time for regular numerical applications in HPC. Therefore, from a scheduling point of view, this aspect only add to the arbitrariness of the ratio of the processing times of tasks on CPU and on GPU, with no impact on the knowledge of these processing times.

One last characteristic of the GPU to observe: the architecture of GPUs prevents them from preempting a task while it is executed on a GPU. A GPU computation is unstoppable, and has to run its course until the end of the execution. It cannot even be canceled during the processing. This means that the scheduling problems we study have no preemption of the tasks allowed on the GPUs, not even the cancellation of the tasks being allowed on GPU.

### 2.3 Summary

Computing platforms have reached high levels of computational power over the years, opening new fields of interest for High Performance Computing, ranging from economy with finance computations to scientific research with nuclear physics, fluids mechanics or DNA sequencing... The overall complexity has grown with their ability to process and transfer massive amounts of data in a very short amount of time, and new techniques and processors have been developed to create these new platforms, resulting in an often heterogeneous distribution of processors within these platforms.

One type of accelerating processors used on these platforms is the GPUs, that are able to perform simple parallel computation at a very high speed, since it is what they were designed to do in their primary use, graphical processing. However, this primary purpose of the GPUs means they have an architecture that greatly differs from a common CPU architecture, creating specific characteristics that alter the processing time of a task on a GPU. The two main differences are memory management, and the parallelization of the operations of a task.

Since these difference are based on to the GPU hardware and the user's programming, when given an arbitrary set of tasks to schedule, we have to assume that the processing

#### 2.3. SUMMARY

times of a task on CPU and GPU cannot be linked by any rule, and therefore have to be completely arbitrary in the generic case. If the tasks to be scheduled however share the same memory characteristics and have the same parallelization potential, we can assume that all the tasks will either be accelerated when assigned to a GPU, or slowed down. Another scheduling constraint to add to our model is that the tasks assigned to a GPU cannot be preempted or canceled.

With these scheduling parameters in mind, we can define the problems we studied during the course of this PhD thesis and present new notations for this new type of scheduling problems, as well as the methods from related scheduling problems that we used during this PhD thesis to tackle these problems.

# Chapter 3

# New Notations and Related Works on GPU Scheduling Algorithms

New computing platforms are composed of various processors, including standard processors, CPUs, but also accelerators like GPUs. Scheduling the calculations submitted by the platform users is a crucial problem in term of efficiency for a field where performance is key. These heterogeneous processors make the scheduling problem on these platforms at least atypical and very hard in terms of known problems, especially since there was no theoretical method prior to this work to deal with this particular scheduling problem. The closest problem in the classical literature would be the problem of scheduling tasks on unrelated processors, but it is far too generic for our problem, with only two types of unrelated processors.

The classical nomenclature for scheduling problems does not have a notation adapted to the problem of scheduling tasks on a heterogeneous platform composed of CPUs and GPUs. We extend here the traditional notation  $\alpha \mid \beta \mid \gamma$  introduced by Graham et al. [39] to fit our new scheduling problems, and then cover the related scheduling problems we have used during this work to establish and study a new adequate class of scheduling model.

### 3.1 Notations

In this work, only deterministic scheduling problems are considered, meaning that the number of tasks, the number of parallel processors, and all task characteristics (like processing times) of the problems are known in advance.

Each field of the classical *three field* notation  $\alpha \mid \beta \mid \gamma$  [39] represents a particular characteristic of a scheduling problem, where

•  $\alpha$  represents the resources of the problem, i.e. the available machines, or in our case, the number of CPUs available and the number of GPUs available. In the classical notation, when the machines are identical,  $\alpha = P$ , when the machines are

uniformly related i.e. when the machines have different speeds,  $\alpha = Q$ , and when the machines are unrelated,  $\alpha = R$ .

- $\beta$  represents the hypothesis on the tasks and the constraints imposed on the tasks. In our case, we assume that all processing times are positive integers.

- $\gamma$  represents the objective to minimize or maximize. In HPC, the favored objective is the minimization of the makespan,  $C_{max}$ , i.e. the maximum completion time over all tasks. Indeed, when dealing with parallel processors, the makespan becomes an objective of significant interest. In practice, one often has to deal with the problem of balancing the load on processors in parallel and by minimizing the makespan the scheduler ensures a good balance of the load.

Now we present the extensions we introduced in this notation in order to characterize our scheduling problem, starting with the  $\alpha$  field.

### 3.1.1 Machines $(\alpha)$

#### 3.1.1.1 Sets of Identical CPUs and Identical GPUs

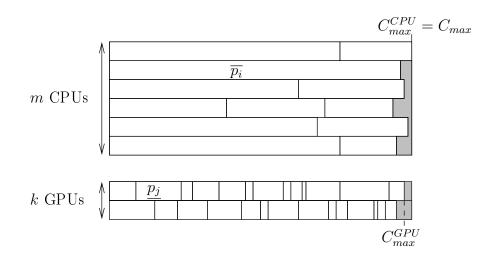

We denote by (Pm, Pk) the problem of scheduling a set  $\mathcal{T} = \{T_1, \ldots, T_n\}$  of n tasks on a heterogeneous computing platform constituted of m identical CPUs (Pm) and kidentical GPUs (Pk), where a task  $T_j$  has two distinct processing times,  $\overline{p_j}$  if it is executed on a CPU and  $p_j$  if it is processed on a GPU. The m CPUs are considered independent from the GPUs that are commanded by some extra driving CPUs, not mentioned here because they do not execute any task. Since the CPUs (resp. GPUs) are all identical, there is no need for a more complex notation involving the number of the CPU (resp. GPU) where one task is processed. The default hypothesis is that the acceleration factor  $\frac{\overline{p_j}}{p_j} = q_j$  of the different tasks is arbitrary. Tasks with a great degree of parallelism can have their processing times greatly reduced when assigned to a GPU, while some other tasks may have similar processing times on CPU and on GPU, or some might even be slowed down when assigned to a GPU. We assume that both processing times of a task are known in advance as it is commonly admitted. As we previously mentioned, an accurate estimation can be obtained at compile time for regular numerical applications in HPC.

For instance the problem  $(Pm, Pk) || C_{max}$  will denote the problem of scheduling n independent sequential tasks (i.e. they are only executed on one processor) on m CPUs and k GPUs where the objective is to minimize the makespan,

$C_{max} = \max\left(C_{max}^{CPU}, C_{max}^{GPU}\right)$  (see Figure 3.1). Other classical objectives found in the literature can also be integrated in this notation, as for example the sum of completion times,  $\sum C_i$ .

The notation (P, P) is used when the numbers of CPUs and GPUs are arbitrary, but all the CPUs are still considered identical as well as the GPUs.

Figure 3.1: An example with m = 6 CPUs and k = 2 GPUs.

#### 3.1.1.2 Sets of Uniform CPUs and Uniform GPUs

With the same reasoning as for identical processors, we denote by (Qm, Qk) the problem with n independent sequential tasks on a platform with m uniform CPUs (Qm) and k uniform GPUs (Qk). In this case, a task can have several distinct processing times. We denote by  $\overline{p_j}$  the processing time of task j on the slowest CPU, taken as the reference CPU. From there, the processing time of task j on CPU i is defined by  $\overline{p_{ij}} = \frac{\overline{p_j}}{\overline{s_i}}$ , where  $\overline{s_i}$  is the speedup factor of CPU i compared to the slowest CPU, whose speedup is 1, as described for classical scheduling problems with uniform machines. We introduce the same processing times for the GPUs, where  $\underline{p_j}$  denotes the processing time of a task j on the slowest GPU. The processing time of task j on GPU i is then defined by  $\underline{p_{ij}} = \frac{p_j}{\underline{s_i}}$ , where  $\underline{s_i}$  is the speedup factor of GPU i compared to the slowest the processing time of a task j on the slowest GPU. The processing time of task j on GPU i is then defined by  $\underline{p_{ij}} = \frac{p_j}{\underline{s_i}}$ , where  $\underline{s_i}$  is the speedup factor of GPU i compared to the slowest GPU, whose speedup is 1.

Using this notation, we define similarly the acceleration ratio of a task from its parallelization on a GPU with the processing times on the reference processors:  $q_j = \frac{\overline{p_j}}{\underline{p_j}}$ . Once again, the default hypothesis is that all the acceleration ratios of the different tasks can be arbitrary. The parallelization process allowing much greater acceleration that any increase in computing speed, it is assumed that even the largest speedup factor  $\overline{s_i}$  among the CPUs is lower than the smallest acceleration factor  $q_j$  for a task j on the reference GPU.

Again, the notation (Q, Q) is used when the numbers of CPUs and GPUs are arbitrary, as for instance in the problem of minimizing the makespan:  $(Q, Q) || C_{max}$ , but other objectives than the makespan could also be considered for this problem.

This new notation allows us to consider all the combinations for the sets of CPUs and GPUs: we could for instance study the problem (P2, Q2) corresponding to a simple laptop with 2 CPU cores and its built-in GPU on which another, different, GPU has

### 32 CHAPTER 3. NEW NOTATIONS AND RELATED WORKS ON GPU SCHEDULING ALGORITHMS

been plugged for graphical purposes.

### 3.1.1.3 Unrelated CPUs and unrelated GPUs

Extending the previous notation to unrelated sets of CPUs and GPUs would bring no additional material to the notation of  $\alpha = R$ , the processing times being completely arbitrary from one task and one machine to another.

## 3.1.2 Tasks $(\beta)$

In the generic case, the tasks can be independent or linked by some precedence constraints, they can be considered either sequential (i.e. they are only executed on only one processor), or malleable (they can be executed on several processors and their processing time depends on the number of processors they are assigned to).

### 3.1.2.1 One type of tasks

As mentioned in the previous section, the default hypothesis in the new notation is that the acceleration factors  $\frac{\overline{p_j}}{p_j} = q_j$  for the different tasks can be arbitrary. A restricted version of this hypothesis can be made in order to consider the problems dealing with the scheduling of only one type of tasks, i.e. all the considered tasks would have the same acceleration factor:  $\frac{\overline{p_j}}{p_j} = q$  for  $j = 1, \ldots, n$ .

For instance, the problem  $(Pm, Pk) || C_{max}$  with only one type of tasks will be denoted by  $(Pm, Pk) | q_j = q | C_{max}$  in the same way as equal processing times are denoted by  $p_j = p$  in the  $\beta$  field of the classical notation. All other entries from the  $\beta$  field in the classical notation can be integrated in order to refine the problem, with the exception of the preemption which is detailed in the following section.

### 3.1.2.2 Partial Preemption

Due to the different architectures of the GPUs as well as the different programming languages, it is difficult and costly to start a task on a CPU, interrupt it and pick it up where it was stopped on a GPU: complete preemption cannot be allowed between a CPU and a GPU. The GPU peculiar structure requires complex management of the preemption even between the GPUs themselves [6].

We introduce the notion of "partial preemption", denoted by *ppmtn*, where preemption is only allowed for tasks remaining on the CPUs. For the rest of the manuscript, we will suppose that preemption is not allowed between GPUs, or between a CPU and a GPU. The notion may evolve in the next few years with new accelerator architectures as the Intel MIC (Many Integrated Core) architecture of the Xeon Phi, which is roughly a "standard" 60 core disk-less system. Preemption inside a MIC should be much easier. Nevertheless, efficient task migration between the CPU and the MIC remains an open problem.

#### 3.1. NOTATIONS

With these notations, Table 3.1 summarizes the new scheduling problems we studied as well as the performance of the corresponding algorithms we developed during the course of this PhD, including several algorithms for the case with independent tasks, the specific case where all the tasks to be scheduled are accelerated when assigned to a GPU, but not necessarily with the same acceleration factor for all the tasks, the case where preemptions are allowed for the tasks assigned to the CPUs, but not for the tasks on the GPUs, the case where the tasks are considered malleable when they are assigned to a CPU and sequential when assigned to a GPU, and the case where the tasks are linked by precedence relations.

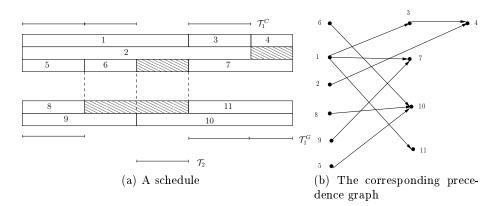

| Problem                                       | Approximation ratio achieved                                                      | Section  |

|-----------------------------------------------|-----------------------------------------------------------------------------------|----------|

| $(P1, P1) \parallel C_{max}$                  | $\frac{3}{2}$                                                                     | 4.1.3    |

|                                               | $1 + \epsilon$                                                                    |          |

|                                               | 2                                                                                 | 4.2.3    |

| $(Pm, Pk) \mid\mid C_{max}$                   | $\frac{4}{3} + \frac{1}{3k}$                                                      | 4.3, 4.4 |

|                                               | $\frac{2r+1}{2r} + \frac{1}{2rk}, r > 0$                                          | 5        |