# Rigorous Design Flow for Programming Manycore Platforms

Paraskevas Bourgos

# ► To cite this version:

Paraskevas Bourgos. Rigorous Design Flow for Programming Manycore Platforms. Other [cs.OH]. Université de Grenoble, 2013. English. NNT: 2013GRENM012. tel-01135186

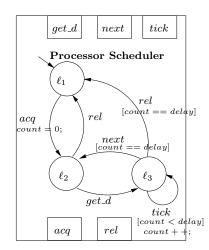

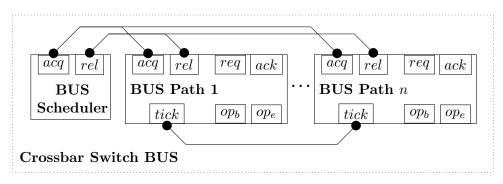

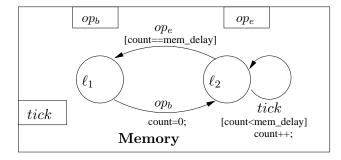

# HAL Id: tel-01135186 https://theses.hal.science/tel-01135186v1

Submitted on 24 Mar 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# THÈSE

Pour obtenir le grade de

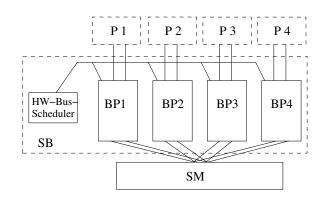

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique

Arrêté ministérial : 7 août 2006

Présentée par

# Paraskevas Bourgos

Thèse dirigée par Saddek Bensalem

préparée au sein du laboratoire VERIMAG et de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# **Rigorous Design Flow for Programming Manycore Platforms**

Thèse soutenue publiquement le **9 Avril 2013**, devant le jury composé de :

# M., Albert Cohen

Professeur, École Polytechnique, Rapporteur **M., Radu Grosu** Professeur, Vienna University of Technology (TUW), Rapporteur **M., Roberto Passerone** Professeur, University of Trento, Examinateur **M., Jean Claude Fernandez** Professeur, Université Joseph Fourier (UJF), Examinateur **M., Joseph Sifakis** Professeur, École Polytechnique Fédérale de Lausanne (EPFL), Examinateur **M., Saddek Bensalem** Professeur, Université Joseph Fourier (UJF), Directeur de thèse

...to my parents

# Abstract

The advent of many-core platforms is nowadays challenging our capabilities for efficient and predictable design. To meet this challenge, designers need methods and tools for guaranteeing essential properties and determining tradeoffs between performance and efficient resource management.

In the process of designing a mixed software/hardware system, functional constraints and also extra-functional specifications should be taken into account as an essential part for the design of embedded systems. The impact of design choices on the overall behavior of the system should also be analyzed. This implies a deep understanding of the interaction between application software and the underlying execution platform.

We present a rigorous model-based design flow for building parallel applications running on top of many-core platforms. The flow is based on the BIP - Behavior, Interaction, Priority - component framework and its associated toolbox. The method allows generation of a correct-by-construction mixed hardware/software system model for manycore platforms from an application software and a mapping. It is based on source-tosource correct-by-construction transformations of BIP models. It provides full support for modeling application software and validation of its functional correctness, modeling and performance analysis of system-level models, code generation and deployment on target many-core platforms.

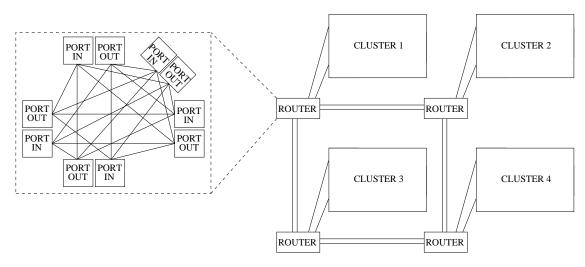

Our design flow is illustrated through the modeling and deployment of various software applications on two different hardware platforms; MPARM and platform P2012. MPARM is a virtual ARM-based multi-cluster manycore platform, configured by the number of clusters, the number of ARM cores per cluster, and their interconnections. On MPARM, the software applications considered are the Cholesky factorization, the MPEG-2 decoding, the MJPEG decoding, the Fast Fourier Transform and the Demosaicing algorithm. Platform 2012 (P2012) is a power efficient manycore computing fabric, which is highly modular and based on multiple clusters capable of aggressive fine-grained power management. As a case study on P2012, we used the HMAX algorithm.

Experimental results show the merits of the design flow, notably performance analysis as well as correct-by-construction system level modeling, code generation and efficient deployment.

# Résumé

L'objectif du travail présenté dans cette thèse est de répondre à un verrou fondamental, qui est "comment programmer d'une manière rigoureuse et efficace des applications embarquées sur des plateformes multi-coeurs?". Cette problématique pose plusieurs défis : 1) le développement dune approche rigoureuse basée sur les modèles pour pouvoir garantir la correction; 2) le "mariage "entre modèle physique et modèle de calcul, c'est-à-dire, l'intégration du fonctionnel et non-fonctionnel; 3) l'adaptabilité. Pour s'attaquer à ces défis, nous avons développé un flot de conception rigoureux autour du langage BIP. Ce flot de conception permet l'exploration de l'espace de conception, le traitement à diffèrent niveaux d'abstraction à la fois pour la plate-forme et l'application, la génération du code et le déploiement sur des plates-formes multi-cœurs. La méthode utilisée s'appuie sur des transformations source-vers-source des modèles BIP. Ces transformations sont correctespar-construction.

Nous illustrons ce flot de conception avec la modélisation et le déploiement de plusieurs applications sur deux plates-formes différentes. La première plate-forme considérée est MPARM, une plate-forme virtuelle, basée sur des processeurs ARM et structurée avec des clusters, o chacun contient plusieurs cœurs. Pour cette plate-forme, nous avons considérée les applications suivantes: la factorisation de Cholesky, le décodage MPEG-2, le décodage MJPEG, la Transformée de Fourier Rapide et un algorithme de demosaicing. La seconde plate-forme est P2012, une plate-forme multi-cœur, basée sur plusieurs clusters capable d'une gestion énergétique efficace. L'application considérée sur P2012 est l'algorithme HMAX.

Les résultats expérimentaux montrent l'intérêt de notre flot de conception, notamment l'analyse des performances ainsi que la modélisation au niveau du système, la génération de code et le déploiement.

# Contents

| Context                                  | 13                                                                                                             |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| .1    System Design Flow                 | <b>15</b><br>18<br>19<br>22                                                                                    |

| he BIP Framework                         | 23                                                                                                             |

| 2.1.1       Modeling Behavior            | $\begin{array}{c} 24\\ 24\\ 24\\ 24\\ 25\\ 25\\ 25\\ 25\\ 27\\ 28\\ 28\\ 30\\ 32\\ 34\\ 36\\ 37\\ \end{array}$ |

| System Designer                          | 39                                                                                                             |

| .1       Construction of Software Models | <b>41</b><br>43<br>43<br>44<br>45<br>46<br>46<br>49<br>52                                                      |

|                                          | 2       Related Work in System Design                                                                          |

| <b>4</b> | Mo             | deling of HW Platforms in BIP                                                   | 55  |

|----------|----------------|---------------------------------------------------------------------------------|-----|

|          | 4.1            | Abstract Model of Manycore Platforms                                            | 55  |

|          | 4.2            | Abstract Models of HW Platforms in BIP                                          | 56  |

|          |                | 4.2.1 Processor Abstract Model for Computation Constraints and Schedul-         |     |

|          |                | ing                                                                             | 57  |

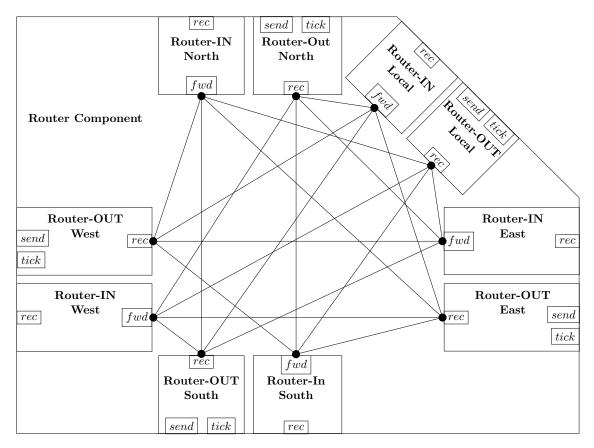

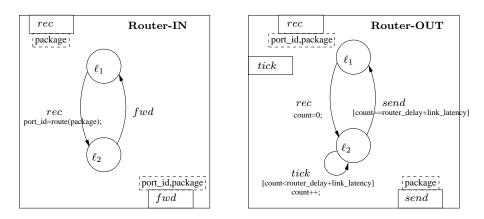

|          |                | 4.2.2 HW Components for Communication Constraints                               | 59  |

|          | 4.3            | Conclusion                                                                      | 73  |

| <b>5</b> | Bin            | ding BIP SW Model to HW Platforms                                               | 75  |

|          | 5.1            | Mapping Specification                                                           | 75  |

|          | 5.2            | Application-Software Model Refinement                                           | 76  |

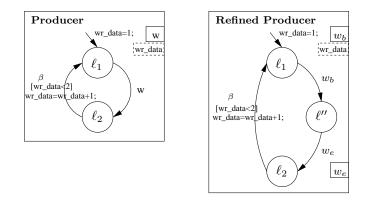

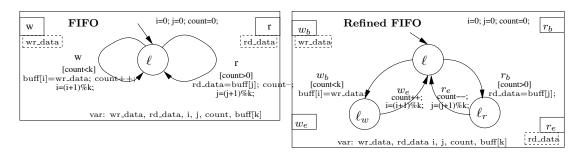

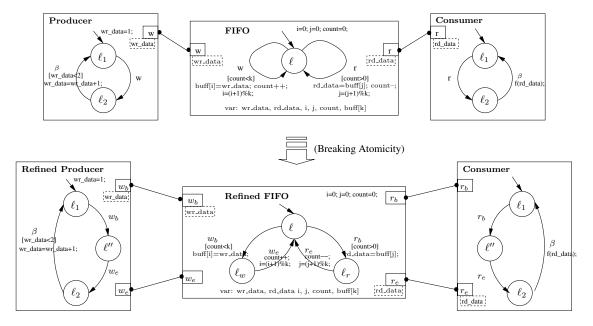

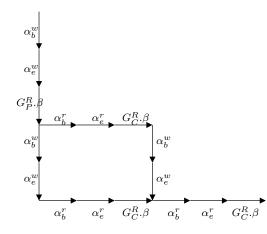

|          |                | 5.2.1 Breaking Atomicity - Refinement                                           | 76  |

|          |                | 5.2.2 FIFO Decomposition - Refinement                                           | 81  |

|          |                | 5.2.3 Mutual Exclusion and Computation Time Refinement                          | 87  |

|          | 5.3            | Conclusion                                                                      | 88  |

| 6        | Inte           | egration of HW Constraints                                                      | 91  |

|          | 6.1            | HW Constraints For Computation                                                  | 91  |

|          | 6.2            | HW Constraints For Communication                                                | 96  |

|          | 6.3            | Conclusion                                                                      | 101 |

|          |                |                                                                                 |     |

| 7        | Inte           |                                                                                 | 103 |

|          | 7.1            | System Model Calibration                                                        |     |

|          |                | 7.1.1 Instruction Weight Table                                                  |     |

|          |                | 7.1.2 Platform Dependent Code Generation                                        |     |

|          | 7.2            | Discussion                                                                      | 107 |

| 8        | $\mathbf{Per}$ | formance Analysis                                                               | 109 |

|          | 8.1            | Performance Model                                                               | 109 |

|          | 8.2            | Discussion                                                                      | 113 |

|          |                |                                                                                 |     |

| Π        | 1 1:           | mplementation and Experimentation                                               | 115 |

| 9        | Too            |                                                                                 | 117 |

|          | 9.1            | DOL2BIP Tool                                                                    |     |

|          | 9.2            | BIPWeaver                                                                       |     |

|          | 9.3            | Weight Table Profiler Tool                                                      |     |

|          | 9.4            | Code Generator Tool                                                             |     |

|          | 9.5            | Conclusion                                                                      | 124 |

| 10       | ) Cas          | e Study on MPARM Hardware Platform                                              | 125 |

|          | 10.1           | MPARM Hardware Platform                                                         | 125 |

|          |                | MPARM Hardware Template Model in BIP                                            |     |

|          | 10.3           | MPEG-2 Application on MPARM                                                     | 130 |

|          |                | MJPEG Application on MPARM                                                      |     |

|          | 10.5           | Fast Fourier Transform (FFT) Application on MPARM $\ldots \ldots \ldots \ldots$ | 134 |

|          | 10.6           | Demosaicing Algorithm Application on MPARM                                      | 137 |

|          | 10.7           | Cholesky Decomposition Application on MPARM                                     | 139 |

|          | 10.8           | Discussion                                                                      | 143 |

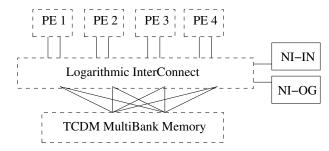

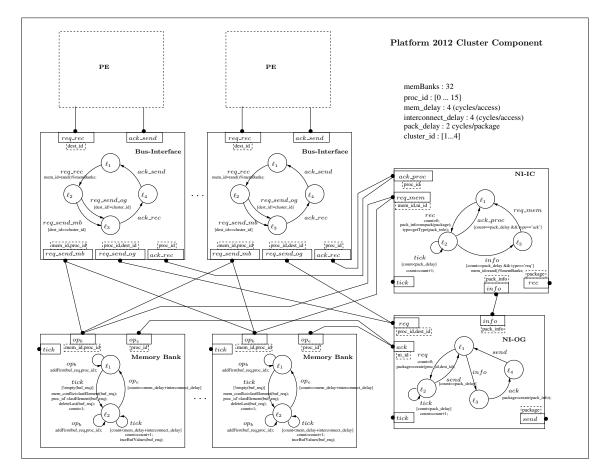

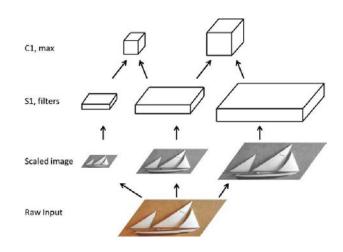

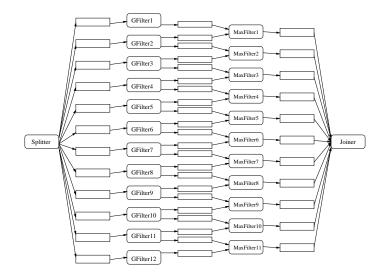

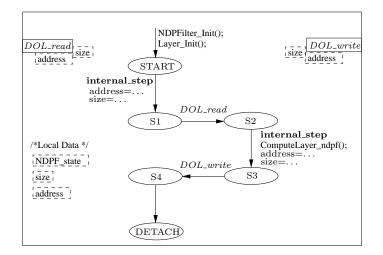

| 11 Case Study on P2012 Hardware Platform         11.1 P2012 Hardware Platform         11.2 Platform 2012 Hardware Template Model in BIP         11.3 HMAX application on P2012         11.4 Conclusion | $\ldots \ldots \ldots 148$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| IV Conclusion                                                                                                                                                                                          | 153                        |

| 12 Conclusion and Perspectives                                                                                                                                                                         | 155                        |

| List of figures                                                                                                                                                                                        | 159                        |

| List of tables                                                                                                                                                                                         | 163                        |

| Bibliography                                                                                                                                                                                           | 165                        |

# Part

Context

# - Chapter 1 -

# **Introduction - From Programs to Systems**

**General Context** Embedded systems have become essential part of our daily lives. In contrast to general purpose computer systems, embedded systems integrate software and hardware, and are specifically designed to perform particular predefined tasks, which are often critical. Usually, they are not standalone devices, but they constitute the computerized part of a larger device. Mainly, we divide embedded systems in two categories: the reactive systems that continuously interact with the environment and the transformational systems that compute a function and terminate. Embedded systems appeared in the market in the early 1960s and since then they have become ubiquitous. Applications can be found in a tremendous variety of domains covering medical equipment, telecommunications, military applications, household appliances and consumer electronics, wireless sensor networks, transportation and avionics. The complexity of embedded systems varies from single micro-controller chip to multiple units and networks incorporated inside a larger system.

Efficiency of embedded systems is of paramount importance. To construct efficient systems optimizations are eligible upon design for energy cost, code size, execution time, weight and dimension, performance and reliability for both the software and the hardware part.

Embedded systems require a synergistic function between software and hardware design and development. The software is specific and often executed in a repeated fashion. However, for reusability reasons software application are often platform independent and immaterial. Conceptually, it is developed based on a high-level model which is decomposed into multiple components for the sake of complexity. A component-based model is normally well structured and is ideally characterized by formal semantics.

A software application is designed to execute on a logical time rather than on a realtime axis. Specifically, abstractions are considered about the behavior such as concurrent execution, instantaneous computation and communication steps, atomicity of actions and zero delays. The above abstractions should consider the functional constraints imposed by the program specifications such as deadlocks, throughput and jitter. Along with the software design, the hardware design should also be considered as a part of an efficient embedded system design. Small homogeneous processing units connected by a Networkon-Chip tend to succeed the complex superscalar architectures nowadays. The number of cores to be integrated in a single chip is expected to rapidly increase in the coming years, moving from multicore to manycore architectures. This leads to investigate new approaches for embedded systems design. Many-core computing architectures require correct design and programming methodologies which exploit parallelism, thus increasing the performance, the scalability and the flexibility of the system. A correct design should also include successful resource allocation and run-time power management. It should also exploit the innovative capabilities of dynamic extension and reconfiguration, at run-time, of the architecture template depending on a possible variable workload and an interactive environment.

In the process of designing a mixed software/hardware system, functional constraints and also extra-functional specifications should also be taken into account as an essential part for the design of embedded systems. The extra-functional specifications concern the use of resources of the execution platform such as time, shared memory, semaphores, queues, energy, distribution and communication of tasks and scheduling policies. Interacting with the platform is real-time. Therefore, it becomes non-trivial the task of evaluating if a software/hardware system preserves the timing properties of its application software. It requires analysis of the impact of design choices on the overall behavior of the system. It also implies a deep understanding of the interaction between application software and the underlying execution platform. We currently lack approaches for modeling mixed hardware/software systems. There are no rigorous techniques for deriving global models of a given system from models of its application software and its execution platform.

**System Level Design** System design is the process leading to a mixed software/hardware system meeting given specifications. It involves the development of application software taking into account features of an execution platform. The latter is defined by its architecture involving a set of processors equipped with hardware-dependent software such as operating systems as well as primitives for coordination of the computation and interaction with the external environment. A simplified view of a system design is illustrated in Figure 1.1.

Figure 1.1: Simplified View of a System Design

Design approaches are developed based on the experience and expertise of the design teams. They tend to re-use, extend and improve existing solutions proven efficient and robust. This favors increased productivity since design methodologies are re-used. Reusability of components is an important issue. Systems are built by reusing and assembling components that are simpler sub-systems. This is the only way to master complexity and to ensure correctness of the overall design, while maintaining or increasing productivity. However, a design methodology may turn to be counter-productive and result to low adaptivity upon new system requirements. Better solutions may be a priori excluded because they do not fit the designers know-how. The main goal of a system design, albeit the heterogeneity of the assembling components and the difficulties upon integration of different technologies, is the efficient prediction of the behavior of a software application running on an execution platform.

A system design flow consists of steps starting from specifications and leading to an implementation on a given execution platform. It involves the use of methods and tools for progressively deriving the implementation by making adequate design choices.

We consider that a system design flow must meet the following essential requirements:

*Functionality and Performance.* The design flow must allow the satisfaction of both functional and extra-functional properties. This means that functional properties such as deadlock freedom, jitter, throughput and resources such as memory, time and energy are first class concepts encompassed by formal models. Moreover, it should be possible to analyze and evaluate efficiency in using resources, which conform with the functional requirements, as early as possible along the design flow. Lack of adequate semantic models does not allow consistency checking for timing requirements, or meaningful composition of features.

*Correctness.* This means that the designed system meets its specifications. Ensuring correctness requires that the design flow relies on models with well-defined semantics. Semantics should be defined at both the execution and the interaction level of the models. The models should consistently encompass system description at different levels of abstraction from application software to its implementation. Correctness can be achieved by application of verification techniques. It is desirable that if some specifications are met at some step of the design flow, they are preserved in all the subsequent steps. This can be achieved by transforming the application software model to include the important physical aspects of the target platform.

*Heterogeneity and Adaptivity.* Heterogeneity in systems design can be supported by developing high level domain-specific languages ease of expression. System model semantics should encompass heterogeneity in computation, interaction and abstraction level to facilitate modeling mixed hardware/software systems. This should be accompanied by reusability allowing the definition of libraries of components to be reused and the development of component-based solutions. The design flow should not enforce any particular programming or execution model. Specific programming models or implementation principles may a priori exclude efficient solutions and parallelism. For instance, programming multimedia applications in plain C may lead to designs obscuring the inherent functional parallelism and involving built-in scheduling mechanisms that are not optimal. It is essential that designers use adequate programming models. The above characteristics along with a tool integration for programming, validation and code generation perceive a productive design flow.

We call *rigorous* a design flow which allows guaranteeing essential properties of the specifications. Most of the rigorous design flows privilege a unique programming model together with an associated compilation chain adapted for a given execution model. For example, synchronous system design relies on synchronous programming models and usually targets hardware or sequential implementations on single processors [Hal93]. Alternatively, real-time programming based on scheduling theory for periodic tasks, targets dedicated real-time multitasking platforms [BW01].

A rigorous design flow should be characterized by the following:

• it is *model-based*, that is, both application software and mixed hardware/ software system descriptions are modeled by using a single, semantic framework. As stated

in [BBB<sup>+</sup>11], this allows maintaining the coherency along with the flow by proving various transformations used to move from one description to another while preserving essential properties. This means that the semantic model is expressive enough to directly encompass various types of component heterogeneity arising along the design flow [HS06].

- it should be *component-based*, that is, it should provide primitives for building composite components as the composition of simpler components. The use of components reduces development time by favoring component reuse and provides support for incremental analysis and design, as introduced in [BBNS08, BBNS09, BBL<sup>+</sup>10].

- it should be *correct-by-construction*, that is, all design flow steps concerning the synthesis of the final model should be proven to guarantee the preservation of all properties of the initial input model.

- it should be *tool-supported*, that is, all steps in the design flow should be realized automatically by tools ensuring significant productivity gains.

# **1.1** System Design Flow

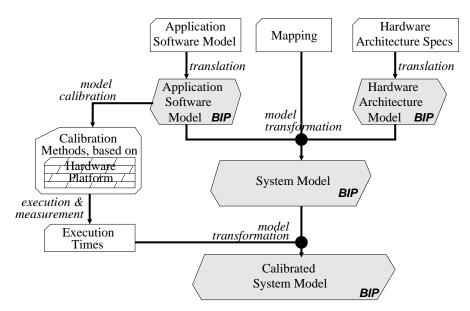

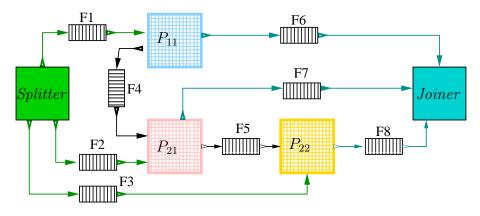

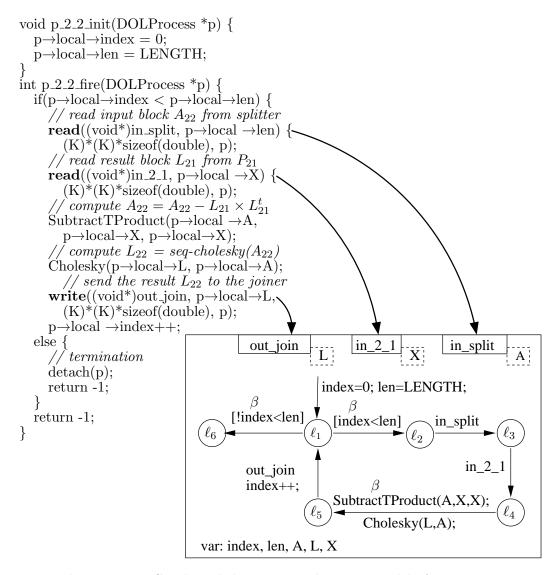

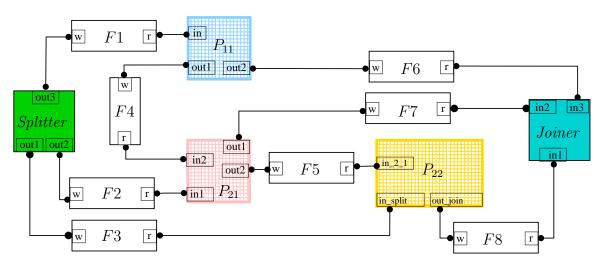

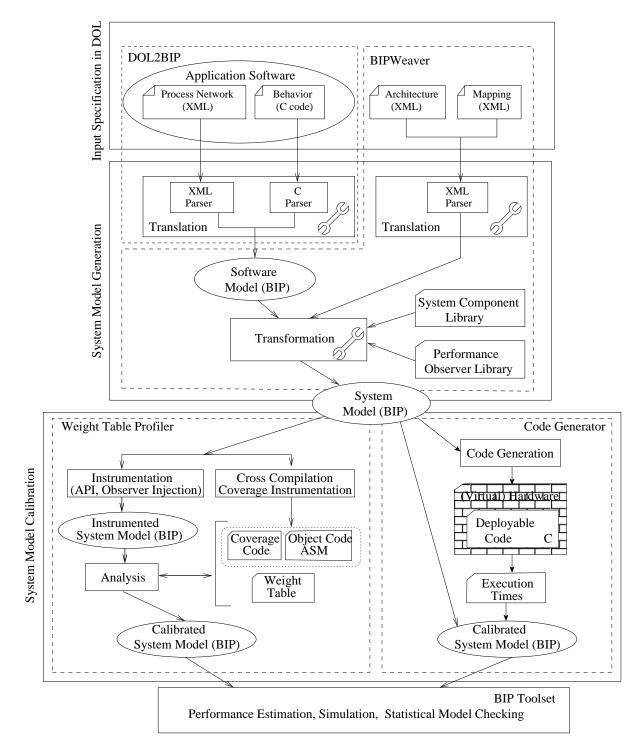

We propose a system construction method that is both rigorous and allows fine-grain analysis of system dynamics. It is rigorous because it is based on formal models described in BIP [BBS06], with precise semantics that can be analyzed by using formal techniques. A system model in BIP is derived by progressively integrating constraints induced on an application software by the underlying hardware architecture. In contrast to ad hoc modeling approaches, the system model is obtained, in a compositional and incremental manner, from BIP models of the application software and respectively, the hardware architecture, by application of source-to-source transformations that are proven correctby-construction. The system model describes the behavior of the mixed hardware/software system and can be simulated and formally verified using the BIP toolset [bip]. The method for the construction of mixed hardware/software system models is illustrated in Figure 1.2. It takes as inputs: (i) the application software model, the hardware architecture and (iii) the mapping between them. It proceeds in four main steps.

The first step is the generation of the *application software model in BIP*. This is achieved by an automatic translation of the input application software model which should be described in a process network with a well defined structure. The translation preserves intact the behavior and the characteristics of the initial application software.

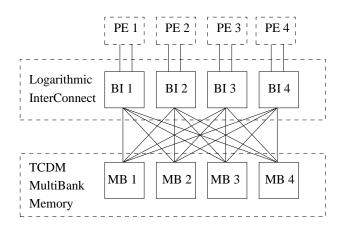

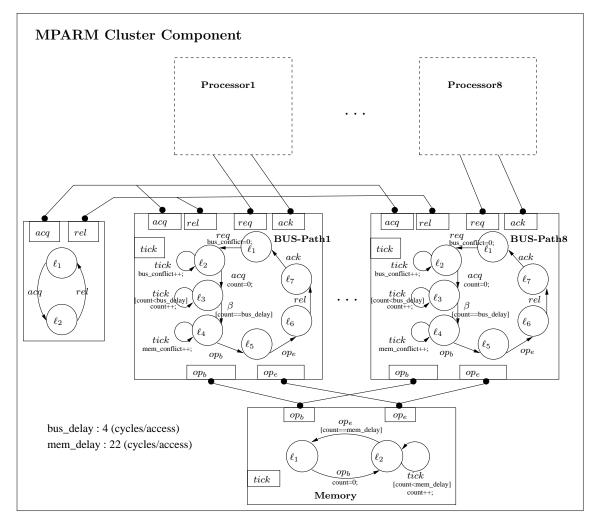

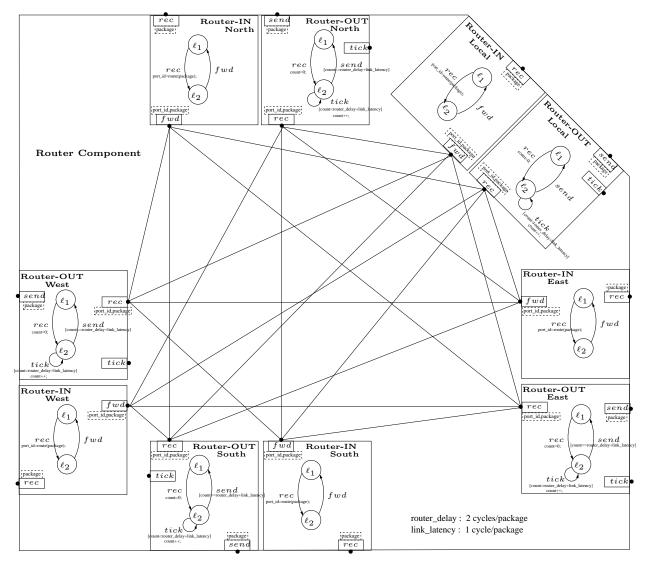

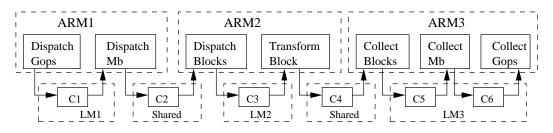

The second step is the synthesis of the *hardware architecture model in BIP*. A library of BIP atomic components that characterize manycore architectures is defined, including models for hardware components (e.g., processor, memory) and for hardware-dependent software components (e.g., FIFO channel read/write, bus controllers, schedulers). Combining the hardware architecture specifications and the suitable BIP library components, we synthesize the hardware architecture model in BIP. The model is parametrized and allows flexible integration of specific target architecture features, such as arbitration policy, latency for buses and memories, scheduling policy etc.

The third step is the construction of the mixed software/hardware system model. This model represents the behavior of the application software running on the hardware architecture according to the mapping, but without taking into account execution times for the software actions. This step consists in progressively enriching the application software model by doing: (1) Application of a sequence of source-to-source transformations to synthesize *hardware dependent software routines* implementing communication by using the hardware components. (2) Integration of hardware components used in the system model. The transformations are proved correct-by-construction, that is, they preserve functional properties of the application software.

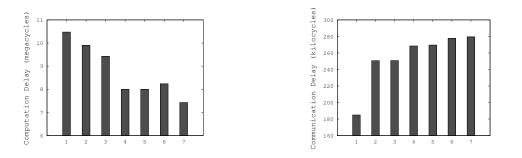

In the final step, the (bounds for) execution times are obtained by analysis or simulation of the run of every software process in isolation on the platform. These bounds are injected into the *system model* and lead to the *calibrated system model*. This final model allows accurate estimation through simulation of real-time characteristics (response times, delays, latencies, throughput, etc.) and indicators regarding resource usage (bus conflicts, memory conflicts, etc.).

The above design flow sticks to the general principles of *rigorous design* introduced in the previous section. Namely, it is *model-based*, *component-based*, *correct-by-construction* and *tool-supported*.

Figure 1.2: System Model Design Flow

# 1.2 Related Work in System Design

To the best of our knowledge, the BIP design flow is unique as it uses a single semantic framework to support application modeling, validation of functional correctness, performance analysis on system models and code generation for manycore platforms. Building faithful system models is mandatory for validation and performance analysis of concurrent software running on manycore platforms.

Synchronous languages [BB91] such as Esterel [BG92], Lustre [HCRP91] and Signal [BBGLG85] offer strong formal semantics that facilitate by construction verification and code generation, but they have remained limited to safety-critical domains such as aviation and automotive.

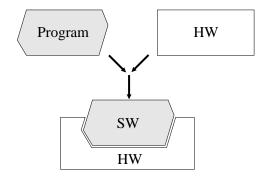

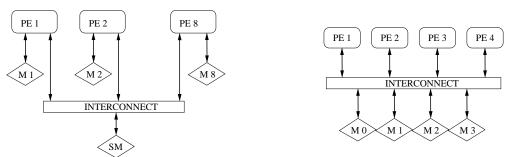

Simulink [Mat] and Stateflow [Sta] are synchronous formalisms that are mainly used to generate quickly an input for an FPGA prototype implementation through Verilog and VHDL. Many of the frameworks, which we present below, follow the Y-chart design principle [BCG<sup>+</sup>97, KDVvdW97] as we do in our design flow. Namely, these are DOL, SPADE, Sesame, Polis, Metropolis, Artemis, Octopus and CoFluent. This means that they decouple application from architecture by recognizing two distinct models for them. According to the Y-chart approach, an application model -derived from a target application domaindescribes the functional behavior of an application in an architecture-independent manner. The principle is illustrated in Figure 1.3.

Figure 1.3: Software Application - Hardware Platform mapping of a System Design

DOL [TBHH07] introduces a framework for specifying and mapping parallel applications onto heterogeneous multiprocessor platforms. It defines abstraction models for the application and architecture, as well as a format for the mapping specification. They integrate an analytic performance analysis strategy to replace modeling and analyzing a multiprocessor system using other methods. The system level performance analysis is based on formal analysis techniques using Real Time Calculus [TCN02].

Polis [BCG<sup>+</sup>97] is considered as a pioneer method for platform-dependent design as it set the separation of concern principle for architecture and function, communication, and computation. Polis supports one model of computation described in finite-state machines (FSM). It is focused on automotive application domain supporting architecture based on a single microprocessor and peripherals. The supported tools were simulation, architectural exploration with accurate and fast code execution time evaluation using automatically generated from the FSMs model. However, Polis is considered limited both the model of computation and in the target architecture.

Metropolis [BLP<sup>+</sup>02, BWH<sup>+</sup>03] is a framework which follows the mapping of function to architecture paradigm in the Y-chart organization. Architectures are represented as computation and communication services. The association of functionality to architectural services allow Metropolis to evaluate characteristics (such as latency, throughput, power, and energy) of an implementation of a particular functionality with a particular platform instance. Metropolis has back-end tool connection with a SystemC simulator and to verification of LTL and LOC constraints. MetroII [Aea07] is a framework extending Metropolis to import heterogeneous IPs, to facilitates performance analysis and design space exploration.

Artemis workbench [Pim08, PHL<sup>+</sup>01] begins with a Simulink representation of the functionality of the design that is converted in Kahn Process Networks (KPN). KPNs are also used to capture the architecture based on a set of virtual processors. Eventually, Artemis generates VHDL to obtain an FPGA implementation.

Ptolemy [EJL<sup>+</sup>03, Lee09] develops another approach analyzing the behavior of interfaces to find whether two models can be composed in a semantic framework that support this form of heterogeneity. In fact, interfaces are finite-state machines used for heterogeneous modeling. Ptolemy uses Java as an imperative language and is more embedded software oriented rather than dealing with hardware architectures.

CoFluent Studio [CoF] is developed for system architecting. It supports the MCSE methodology (Méthodologie de Conception des Systémes Electroniques). It follows the mapping of function to architecture in the Y-chart paradigm. The approach is dual: one for the software developer to satisfy the functional specifications and one for the architecture designer. Simulation and platform prototyping is supported.

Octopus [Tea10] is specifically designed to support Design-Space Exploration (DSE). It allows the independent specification of applications, platforms, and mappings, following the Y-chart approach, and aims to integrate existing formal analysis and simulation tools in the DSE process.

SystemCoDesigner [HSKM08] is tool for Design Space Exploration (DSE) and prototyping. SystemCoDesigner starts from a behavioral SystemC model and generates hardware accelerators and hardware/software solutions for DSE. It also provides the capability for prototyping on an FPGA basis constructing a link between Electronic System Level (ESL) and Register Transfer Level (RTL).

LusSy [MMMcMc] is a tool for the analysis of SystemC transactional models. Starting from the source code of a SystemC design, it uses GCCs C++ front-end and the SystemC library itself for parsing, then transform it into a set of automata, and finally dump it in the Lustre language. Thus, it provides a way to express safety properties directly in SystemC, by using identifying operational semantics for TLM models written in full SystemC. Although the method has a working connection to verification tools, the semantics remain abstract because Lustre is less expressive than a general-purpose language which deals with dynamic data structures.

VISTA [MGN03], based on SystemC [Gro02], provides a methodology and tool for modeling SoC virtual platform for SW development and system level performance analysis and exploration. The SoC provides a cycle-accurate functional model of the architecture using the basic SystemC Transaction Level Modeling (TLM) components provided by VISTA. It supports cross-compilation on the target processor and back annotation, therefore bypassing the use of an Instruction Set Simulator (ISS). However, it may hardly be used for other purposes than performance analysis due to the lack of a formal specification of the system.

A simulation based method is presented in [KDVvdW97]. The authors specify software applications as Kahn graphs and they textually instantiate different architectures from an architecture template. They obtain performance numbers by using a configurable simulator in C++ that has been constructed for the architecture template, using multi-threading and object oriented programming techniques. Even though the model is at a high level of abstraction, the simulator can efficiently execute different types of dataflow architectures at a level that is clock-cycle accurate.

The Sesame [EPTP07] modeling and simulation environment facilitates performance analysis of embedded media systems architectures according to the Y-chart design principle [BCG<sup>+</sup>97, KDVvdW97]. Sesame aims at early system evaluation and design space exploration using model calibration and trace-driven cosimulation.

Daedalus [NTS<sup>+</sup>08] offers a fully integrated tool-flow in which design space exploration (DSE), system-level synthesis, application mapping, and system prototyping of Multi-Processor System on Chips (MP-SoCs) are highly automated. It is based on Sesame framework [EPTP07] and automatically extends it to VHDL implementations of the MP-SoC platform architecture generated by the ESPAM tool [NSD08, NSD06]. The Daedalus high-level MP-SoC models aim at the accurate prediction of the overall system perfor-

mance.

SPADE [LSvdWD01] is a method and tool for architecture exploration of heterogeneous signal processing systems used to evaluate alternative multi-processor architectures. It follows the Y-chart paradigm for system level design, on which the application and architecture are modeled separately and mapped onto each other in an explicit design step. SPADE uses a trace-driven simulation technique and permits architectures to be modeled at an abstract level using a library of generic building blocks.

SymTA/S [Hea05] is a system-level performance analysis approach based on formal scheduling analysis techniques, event streams [RE02, RZJE02] and symbolic simulation. The tool supports heterogeneous architectures and determines system-level performance data such as end-to-end latencies, bus and processor utilization, and worst-case scheduling scenarios.

In [AAM06] the authors suggest a method of timed automata, for solving optimal scheduling problems. They demonstrate that the timed-automata-based methods can be used to synthesize scheduling strategies for applications with uncertain task durations. In [SBM09] the authors developed a methodology for automatic abstraction of systems modeled by timed automata allowing them to analyze timed automata of greater size and complexity. In [CMLS11], trade-offs between communication cost and computational workloads are modeled addressing the problem of mapping applications to processors in a multicore environment.

A hybrid approach for system level performance evaluation of embedded systems that combines formal analysis methods with a simulation framework in presented in [KPBT06]. However, the current approach is limited to small systems.

# 1.3 Organization of the Document

This document is composed of four parts, the first presenting the context of the work (Chapter 1 and Chapter 2), the second describing the system designer method which is the thesis contribution (Chapters 3, 4, 5, 6, 7 and 8), the third presenting the results of implementation and experimentation (Chapters 9, 10 and 11) describing the tool developed and applying the methodology presented in the contribution, and the last part (Chapter 12) drawing the conclusion and perspectives. The details of all Chapters are as follows. Chapter 2 describes the BIP component-based framework which is the foundation of this work. Chapter 3 presents the BIP Language Factory and the construction of software model in BIP using well structured models. The synthesis of HW Platforms in BIP and the library of HW components is provided in Chapter 4. In Chapter 5 we analyze the method and the necessary transformations used to efficiently map an application software model in BIP with the HW Platform model. Chapter 6 presents the mixed software/hardware system in BIP integrating all the HW platform constraints. Chapter 7 describes the two methods of integration the run-time HW/SW constraints which are the execution times of every software process in isolation. The method used for performance analysis and the comparison with related work is found in Chapter 8. Chapter 9 described the whole tool-flow developed to automatically generate an accurate system model in BIP. Chapter 10 and Chapter 11 present the two case studies considered in this work which respectively concern two different HW platforms. Chapter 12 draws the conclusion of this work and the futures perspectives.

# - Chapter 2 -

# The BIP Framework

The BIP –Behaviour/Interaction/Priority– framework [BBS06] is aiming at design and analysis of complex, heterogeneous embedded applications. BIP is a highly expressive, component-based framework with rigorous semantical basis. It allows the construction of complex, hierarchically structured models from atomic components characterized by their behavior and their interfaces. Such components are transition systems enriched with data. Transitions are used to move from a source to a destination location. Each time a transition is taken, component data (variables) may be assigned new values, computed by user-defined functions (in C/C++). Atomic components are composed by layered application of interactions and priorities. Interactions express synchronization constraints and define the transfer of data between the interacting components. Priorities are used to filter amongst possible interactions and to steer system evolution so as to meet performance requirements e.g., to express scheduling policies.

This chapter is structured as follows. The abstract model of BIP is described in Section 2.1 as an abstract formalization of the layers of *Behavior*, *Interactions* and *Priorities*. Section 2.2 describes the concrete model of BIP extended with data. We introduce the concepts of *Components* and *Connectors* to build system models and we define the operational semantics of all three layers (behavior, interaction, priorities). Section 2.3 describes the basic constructs of the BIP Language. Section 2.3 presents the BIP Tool-chain, the BIP execution engines and the Distributed Implementation. Conclusions are given in the last section.

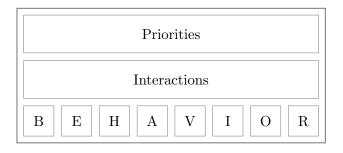

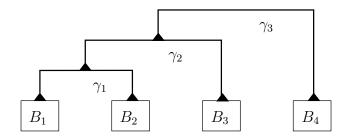

Figure 2.1: Structure of a BIP Model

# 2.1 Abstract Model of BIP

We provide a formalization of the BIP model focusing on the individual layers of behavior, interaction and priority glue (see Figure 2.1). In this section, we provide for each layer its abstract model.

# 2.1.1 Modeling Behavior

An atomic component is the most basic BIP component which represents behavior. A formal definition for the behavior of an atomic BIP component is given below:

#### 1 Definition (Behavior)

A behavior B is a labeled transition system represented by a triple  $(Q, P, \rightarrow)$ , where:

- Q is a finite set of control states,

- *P* is a set of communication ports,

- $\rightarrow \subseteq (Q \times P \times Q)$  is a set of transitions, each labeled by a port.

For a pair of states  $q, q' \in Q$  and a port  $p \in P$ , we write  $q \xrightarrow{p} q' \iff (q, p, q') \in \rightarrow$  and we say that p is enabled at q. If such q' does not exist, we say that p is disabled at q.

# 2.1.2 Modeling Interactions

We compose a set of n atomic components behaviors  $\{B_i = (Q_i, P_i, \rightarrow_i)\}_{i=1}^n$ , by using interactions. We assume that their respective sets of ports and sets of states are pairwise disjoint, i.e., for all  $i \neq j$ , we have  $P_i \cap P_j = \emptyset$  and  $Q_i \cap Q_j = \emptyset$ . We define the set  $P = \bigcup_{i=1}^n P_i$  of all ports in the system.

## 2 Definition (Interaction)

An interaction  $\alpha$  is a non-empty subset  $\alpha \subseteq P$  of ports. When we write  $\alpha = \{p_i\}_{i \in I'}$ ,  $I' \subseteq [1, n]$ . For each  $i \in I'$ ,  $p_i \in P_i$ .

The interaction model is specified by a set of interactions  $\gamma \subseteq 2^P$ . Interactions of  $\gamma$  can be enabled or disabled. An interaction  $\alpha$  is enabled *iff*, for all  $i \in [1, n]$ , the port  $\alpha \cap P_i$  is enabled in  $B_i$ . That is, an interaction is enabled if each port that is involved in this interaction is enabled. An interaction is disabled if there exists  $i \in [1, n]$ , for which the port  $\alpha \cap P_i$  is disabled in  $B_i$ . That is, an interaction is disabled if there exists at least a port involved in this interaction, that is disabled.

# 2.1.3 Modeling Priorities

In a behavior, more than one interaction can be enabled at the same time, introducing a degree of non-determinism. This can be restricted with priorities by filtering the possible interactions based on the current global state of the system.

We compose a set of n atomic components behaviors  $\{B_i = (Q_i, P_i, \rightarrow_i)\}_{i=1}^n$ .

# **3** Definition (Priority)

A priority is a partial order  $\prec \gamma \times \gamma$ , where:

•  $\gamma$  is the set of interactions,

For  $\alpha \in \gamma$  and  $\alpha' \in \gamma$ , the priority  $(\alpha, \alpha') \in \prec$  is denoted as  $\alpha \prec \alpha'$ . That is, interaction  $\alpha$  has less priority than  $\alpha'$ .

# 2.1.4 Composition of Abstract models

For a set of components  $\{B_i = (Q_i, P_i, \rightarrow_i)\}_{i=1}^n$ , an interaction model  $\gamma$  and a priority model  $\pi$ , the compound component is obtained by application of a glue GL.

The glue GL is composed of the two previous models  $\gamma$  and  $\pi$  and defined as  $GL = \pi \gamma$ , where the interaction model  $\gamma$  is a set of interactions and the priority model  $\pi$  is a set of priorities.

### 4 Definition (Composition for Interactions Model)

The composition of a set of atomic components  $\{B_i\}_{i=1}^n$ , parametrized by a set of interactions  $\gamma \subseteq 2^P$ , is a transition system  $B = (Q, \gamma, \rightarrow_{\gamma})$ , where:

- $Q = \bigotimes_{i=1}^{n} Q_i$ ,

- $\gamma$  is the set of interactions  $\gamma \subseteq 2^P$ , where  $P = \bigcup_{i=1}^n P_i$ ,

- For  $\alpha = \{p_i\}_{i \in I} \in \gamma$ , we have  $(q_1, \ldots, q_n) \xrightarrow{\alpha} \gamma(q'_1, \ldots, q'_n)$  in B if and only if,  $q_i \xrightarrow{p_i} q'_i$ in  $B_i$  for all  $i \in I$ , and  $q'_i = q_i$  for all  $i \notin I$ .

The obtained behavior B can execute a transition  $(\alpha = \{p_i\}_i \in I) \in \gamma$ , if and only if, for each  $i \in I$ , port  $p_i$  is enabled in  $B_i$ .

## 5 Definition (Composition restricted from the Priority Model)

Given a behavior  $B = (Q, \gamma, \rightarrow_{\gamma})$ , its restriction by the priority model  $\pi$  is the behavior  $B' = (Q, \gamma, \rightarrow_{\pi})$ , where for  $\alpha \in \gamma$ , we have  $q \xrightarrow{\alpha}_{\pi} q'$  in B' if and only if,  $q \xrightarrow{\alpha}_{\gamma} q'$  in B and for all  $\alpha' \in \gamma$  such that  $\alpha \prec \alpha', \alpha'$  is disabled.

The obtained behavior B' can execute a transition  $\alpha \in \gamma$  if and only if, each transition  $\alpha' \in \gamma$ , with higher priority than  $\alpha$  is disabled.

# 2.2 CONCRETE MODEL OF BIP

## 2.2.1 Atomic Components

In BIP, *atomic components* are automata equipped with a set of ports and a set of variables. Each transition is guarded by a predicate on the variables, triggers an update function, and is labelled by a port. Ports are used for communication among different components and are associated with variables of the component.

#### 6 Definition (Port)

Each port is a pair  $(p, X_p)$ , where p is the label and  $X_p$  is the set of variables associated with p. For the sake of simplicity we denote a port  $(p, X_p)$  by p. We refer to internal ports using the  $\beta$  character instead of p, which refers to communication ports.

#### 7 Definition (Atomic Component: Syntax)

An atomic component is a labelled transition system extended with data B = (L, X, P, T)where:

- $L = \{\ell_1, \ell_2, ..., \ell_k\}$  is a set of control locations,

- $X = \{x_1, x_2, ..., x_n\}$  is a set of variables,

- P is a set of communication ports. Each port is a pair  $(p, X_p)$ , where p is a label and  $X_p \subseteq X$  is the set of variables associated with p. For the sake of simplicity we denote a port  $(p, X_p)$  by p and we refer to port p that belongs to component B by B.p,

- $\mathcal{T}$  is a set of transitions of the form  $\tau = (\ell, p, g, f, \ell')$  or  $(\ell, \beta, g, f, \ell')$ , where  $\ell, \ell' \in L$  are control locations,  $p \in P$  is a communication port,  $\beta$  is an internal port, g is a guard, a predicate on X which can be true or false, and f(X, X') is an update relation, a predicate on X (current) and X' (next) state variables. We represent concretely update relations as sequential programs operating on data X. We use the term skip to denote f(X, X') as empty, where X = X'.

Let  $\mathcal{D}$  be a universal data domain. Given a set of variables X, we define valuations for X as functions  $v: X \to \mathcal{D}$ . The set of valuations is denoted as  $\mathcal{D}^X$ . Given two valuations  $u: X \to \mathcal{D}$  and  $v: Y \to \mathcal{D}$ , we define the substitution  $u \otimes v: X \cup Y \to \mathcal{D}$  as a valuation defined by:

$$(u \oslash v)(x) = \begin{cases} u(x) & : \text{if } x \in X \setminus Y \\ v(x) & : \text{if } x \in Y \end{cases}$$

## 8 Definition (Atomic Component: Semantics)

The semantics of  $B = (L, P, X, \mathcal{T})$  is a transition system  $(Q, \Sigma, \rightarrow_B)$  such that:

- $Q = L \times \mathcal{D}^X$ ,

- $\Sigma = \{p[v''] | p \in P, v'' \in \mathcal{D}^{X_p}\} \cup \{\beta\}$  is the set of labels. A label p[v''] marks instantaneous data change through the port p.

- $\rightarrow_B$  is the set including transitions

- $((\ell, v), p[v''], (\ell', v')) \text{ such that } g(v) \wedge f(v \otimes v'', v') \text{ for some } \tau = (\ell, p, g, f, \ell') \in \mathcal{T}.$ As usual, if  $((\ell, v), p[v''], (\ell', v')) \in \to_B$  we write  $(\ell, v) \xrightarrow{p[v'']}_B (\ell', v'),$  $- ((\ell, v), \beta, (\ell', v')) \text{ such that } g(v) \wedge f(v, v') \text{ for some } \tau = (\ell, \beta, g, f, \ell') \in \mathcal{T}.$  As

- usual, if  $((\ell, v), \beta, (\ell', v')) \in \to_B$  we write  $(\ell, v) \xrightarrow{\beta}_B (\ell', v')$ .

For a model built from a set of n atomic components  $\{B_i = (L_i, P_i, X_i, T_i)\}_{i=1}^n$ , we assume that their respective sets of ports and variables are pairwise disjoint, i.e. for any two  $i \neq j$  in  $\{1...n\}$ , we require that  $P_i \cap P_j = \emptyset$  and  $X_i \cap X_j = \emptyset$ . Thus, we define the set  $P = \bigcup_{i=1}^n P_i$  of all ports in the model as well as the set  $X = \bigcup_{i=1}^n X_i$  of all variables.

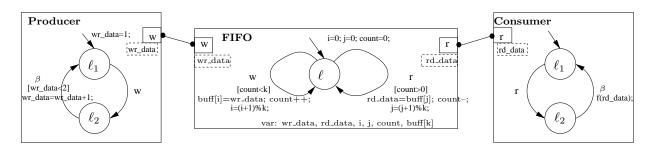

#### 1 Example

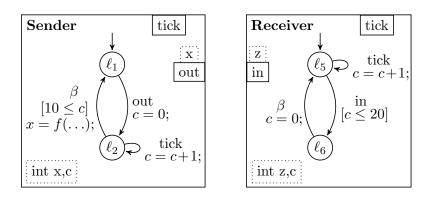

Figure 2.2 shows a graphical representation of two atomic components in BIP, the Sender and the Receiver. The behavior of Sender is described as a transition system with control locations  $\ell_1$  and  $\ell_2$ . It communicates through ports tick and out. Port out exports the variable x. Initially, the Sender communicates through port out exporting the variable x. Then, it ticks through the tick port at a maximum number of ten times. Finally, the guard  $[10 \leq c]$  enables the internal transition  $\beta$ . At the execution of the  $\beta$  transition the variable x is reevaluated depending on a user-defined function f(). Respectively, the behavior of Receiver has control locations  $\ell_5$  and  $\ell_6$  and communicates through port tick and port in, which exports the variable z. Initially, the Receiver ticks through the tick port at a maximum number of twenty times. Then, the guard  $[c \leq 20]$  enables the communication port in which exports the variable z. Finally, the internal transition  $\beta$  is enabled returning the component to the initial state. At the execution of the  $\beta$  transition the variable x is reevaluated depending on a user-defined function f().

Figure 2.2: Sender (left) and Receiver (right) BIP atomic components

# 2.2.2 Interactions

#### 9 Definition (Interaction)

An interaction  $\alpha$  is a triple  $(P_{\alpha}, g_{\alpha}, f_{\alpha})$ , where  $P_{\alpha} \subseteq P$  is a set of ports,  $g_{\alpha}$  is a guard, and  $f_{\alpha}$  is a data transfer function. We restrict  $P_{\alpha}$  so that it contains at most one port of each component, therefore we denote  $P_{\alpha} = \{p_i\}_{i \in I}$  with  $p_i \in P_i$  and  $I \subseteq \{1...n\}$ .  $g_{\alpha}$  and  $f_{\alpha}$  are defined on the variables available on the interacting ports  $\bigcup_{p \in \alpha} X_p$ .

Composition of components allows to build a system as a set of components that interact by respecting constraints of an interaction model. Connectors are used to specify possible interaction patterns between the ports of components.

### 10 Definition (Connector)

A connector  $\gamma$  defines sets of ports of atomic components  $B_i$  which can be involved in an interaction. It is formalized by  $\gamma = (P_{\gamma}, A_{\gamma}, p)$  where:

- $P_{\gamma}$  is the support set of  $\gamma$ , that is the set of ports that  $\gamma$  may synchronize.

- $A_{\gamma} \subseteq 2^{P_{\gamma}}$  is a set of interactions  $\alpha$  each labeled by the triple  $(P_a, G_a, F_a)$  where:

- $-P_a$  is the set of ports  $p_i, i \in I, I \subseteq [1, n]$  that takes part at interaction  $\alpha$ ,

- $G_a$  is the guard of  $\alpha$ , a predicate defined on variables  $\bigcup_{p_i \in \alpha} V_{p_i}$ ,

- $F_a$  is the data transfer function of  $\alpha$ , defined on variables  $\bigcup_{p_i \in \alpha} V_{p_i}$ .

- p is the exported port of the connector  $\gamma$ .

In BIP, we distinguish two models of synchronization on connectors:

- Strong synchronization or rendezvous, where the only feasible interaction of γ is the maximal one, i.e., it contains all the ports of γ. We note A<sub>γ</sub> = P<sub>γ</sub>.

- Weak synchronization or broadcast, where all feasible interactions are those containing a particular port  $p_{trig}$  which initiates the broadcast. We note  $A_{\gamma} = \{\alpha \in \gamma | \alpha \cap \{p_{trig}\} \neq \emptyset\}$  where  $p_{trig} \in P_{\gamma}$  is the port that initiates the broadcast.

There is a graphical notation for interactions. In a rendezvous interaction all ports (known as synchrons) are denoted by bullets. In a broadcast interaction, the port that initiates the interaction, also called trigger, is denoted by a triangle and all the rest with bullets.

**Hierarchical connectors** We have seen that a connector has an option to define a port and export it. This allows a connector to be used as a port in other connectors, and create structured connectors. The representation of structured connectors require connectors to be treated as expressions with typing and other operations on groups of connectors. This led to a formalization of the algebra of connectors defined in [BS08a, BS08b]. The Algebra of Connectors is a compact notation for algebraic representation and manipulation of connectors and formalizes the concept of connectors supported by the BIP component model.

## 2.2.3 Priorities

### 11 Definition (Priority)

A priority is a tuple  $(C, \prec)$  where C is a state predicate (boolean condition) characterizing the states where the priority applies and  $\prec$  gives the priority order on the set of interactions  $A_{\gamma}$ .

For  $\alpha_1 \in A_{\gamma}$  and  $\alpha_2 \in A_{\gamma}$ , a priority rule is textually expressed as  $C \to \alpha_1 \prec \alpha_2$ . When the state predicate C is true and both interactions  $\alpha_1$  and  $\alpha_2$  specified in the priority are enabled, the higher priority interaction, i.e.,  $\alpha_2$  is selected for execution.

# 2.2.4 Composition of Components

### 12 Definition (Composite Component: Syntax)

A composite component is defined by a set of atomic components, composed by a set of interactions  $\gamma$  and a priority  $\pi \subseteq \gamma \times \gamma$ . We denote by  $B \stackrel{def}{=} \pi \gamma(B_1, ..., B_n)$  the component obtained by composing components  $B_1, ..., B_n$  using the interactions  $\gamma$  and priority  $\pi$ . If  $\pi$  is the empty relation, then we may omit  $\pi$  and simply write  $\gamma(B_1, ..., B_n)$ .

A state of  $\pi\gamma(B_1, ..., B_n)$  is defined by a pair  $(\ell, v)$ , where  $\ell = (\ell_1, ..., \ell_n)$  is the control state of each component and  $v = (v_1, ..., v_n)$  is a valuation of component variables.

# 13 Definition (Composite Component: Semantics)

The behavior of a composite component  $\pi\gamma(B_1, ..., B_n)$  without priority, where  $B_i = (L_i, X_i, P_i, \mathcal{T}_i)$ , is a labeled transition system  $(Q, \gamma, \rightarrow_{\gamma})$ , where  $Q = \bigotimes_{i=1}^n L_i \times \bigotimes_{i=1}^n \mathcal{D}^{X_i}$ . We define  $\rightarrow_{\gamma}$  the least transition relation containing the interleaving of internal  $\beta$ -transitions from components  $B_i$  and moreover, satisfying the interaction rule:

$$\alpha = (\{p_i\}_{i \in I}, g_{\alpha}, f_{\alpha}) \in \gamma \qquad g_{\alpha}(\{v_i\}_{i \in I})$$

$$\frac{\{v_i''\}_{i \in I} = f_{\alpha}(\{v_i\}_{i \in I}) \qquad \forall i \in I(\ell_i, v_i) \qquad \frac{p_i[v_i'']}{B_i} \atop (\ell_i', v_i') \qquad \forall i \notin I. \ (\ell_i, v_i) = (\ell_i', v_i') }{((\ell_1, \dots, \ell_n), (v_1, \dots, v_n)) \xrightarrow{\alpha} \gamma ((\ell_1', \dots, \ell_n'), (v_1', \dots, v_n')) }$$

Intuitively, this inference rule specifies that a composite component  $B = \gamma(B_1, ..., B_n)$ can execute an interaction  $\alpha \in \gamma$ , iff(1) for each port  $p_i \in P_\alpha$ , the corresponding atomic component  $B_i$  allows a transition from the current state labelled by  $p_i$  (i.e. the corresponding guard  $g_i$  evaluates to true), and (2) the guard  $g_\alpha$  of the interaction evaluates to true. If these conditions hold for an interaction  $\alpha$  at state  $(\ell, v)$ ,  $\alpha$  is enabled at that state. Execution of  $\alpha$  modifies participating components' variables by first applying data transfer function  $f_\alpha$  on variables of all interacting components and then update functions inside each interacting component. The (local) states of components that do not participate in the interaction remain unchanged. In order to comply with the trace equivalence terminology we can simply refer to interactions as actions. We define the behavior of the composite component  $B = \pi \gamma(B_1, \ldots, B_n)$  with priority, as the labeled transition system  $(Q, \gamma, \rightarrow_{\pi\gamma})$  where  $\rightarrow_{\pi\gamma}$  is the least set of transitions satisfying the rule:

$$\frac{(\ell, v) \xrightarrow{\alpha}_{\gamma} (\ell', v') \qquad \forall \alpha' \in \gamma. \ \alpha \prec \alpha' \qquad (\ell, v) \xrightarrow{\alpha'}_{\gamma}}{(\ell, v) \xrightarrow{\alpha}_{\pi\gamma} (\ell', v')}$$

The inference rule filters out interactions which are not maximal with respect to the priority order. An interaction is executed only if no other one with higher priority is enabled.

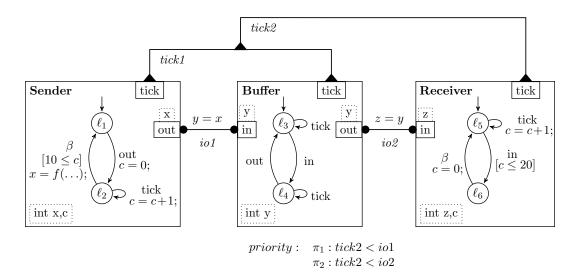

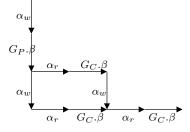

# 2 Example

Figure 2.3 shows a graphical representation of a composite component in BIP. It consists of three atomic components, the Sender, the Buffer and the Receiver. The behavior of Sender and Receiver is already introduced in Example 1. The behavior of Buffer has control locations  $\ell_3$  and  $\ell_4$ . It communicates through ports tick, in and out. Ports in, out export the variable y. The Buffer ticks through the tick port to synchronize with the Sender and the Receiver. It communicates through port in which modifies the variable y interacting with Sender via connector io1. Then, the Buffer forwards the same variable to Receiver through port and connector io2. The hierarchical connector tick2 which includes connector tick1, synchronizes all the available components. The tick2 connector has also the least priority among the connectors of the composite component.

Figure 2.3: Sender/Buffer/Receiver model as a composition of BIP atomic components

## 14 Definition (Transition Sequence)

We define:

• A run  $\theta$  is a finite sequence of transitions:

$$q_0 \xrightarrow{a_1}_{\gamma} q_1 \xrightarrow{a_2}_{\gamma} q_2 \xrightarrow{a_3}_{\gamma} \dots \xrightarrow{a_n}_{\gamma} q_n$$

, with  $a_i \in \gamma \cup \{\beta\}$

We say that for each **run**  $\theta$

• Runs(C) is the set of all runs observed on a composition model in BIP, such as  $C = \pi \gamma(B_1, \ldots, B_N).$

- $Runs(q_0)$  is the set of all runs started from  $q_0$ .

- A run is maximal if  $q_n$  has no successor.

- trace( $\theta$ ) is the sequence of labels  $a_1.a_2...a_n$  for a given run  $\theta$ .

- Traces(C) is the set of all traces which correspond to the set of Runs(C), for a given composition model in BIP, such as  $C = \pi \gamma(B_1, \ldots, B_N)$ .

# 2.3 THE BIP LANGUAGE

The BIP language represents components of the BIP framework [BBS06]. BIP language is a user-friendly textual language which provides syntactic constructs for describing systems. It leverages on C style variables and data type declarations, expressions and statements, and provides additional structural syntactic constructs for defining component behavior, specifying the coordination through connectors and describing the priorities. The basic constructs of the BIP language are the following:

- atomic: to specify behavior, with an interface consisting of ports. Behavior is described as a set of transitions.

- connector: to specify the coordination between the ports of components, and the associated guarded actions.

- priority: to restrict the possible interactions, based on conditions depending on the state of the integrated components.

- compound: to specify systems hierarchically, from other atoms or compounds, with connectors and priorities.

- model: to specify the entire system, encapsulating the definition of the components, and specify the top level instance of the system.

#### 3 Example

The BIP descriptions of the Sender atomic component of Figure 2.2(left) and Port types used are illustrated below:

model  $S_R_Buffer$

port type DataPort (int i)

port type EventPort

port type InternalPort

atomic type Sender

export port EventPort tick=tick export port DataPort out(x)=out port InternalPort  $\beta$

place  $\ell_1, \ell_2$ initial to  $\ell_1$  do {} on out from  $\ell_1$  to  $\ell_2$ do  $\{c = 0; \}$ on tick from  $\ell_2$  to  $\ell_2$ do  $\{c = c + 1; \}$ on  $\tau$  from  $\ell_2$  to  $\ell_1$  (provided  $10 \le c$ ) do  $\{x = f(); \}$

## end

Three types of ports are defined: DataPort, EventPort and InternalPort. A port type DataPort associates a port to an integer variable *i*. Variables associated to ports may be modified when executing the interaction in which the port participates. The port out is an instance of the type DataPort. A port type EventPort is an event port and it is not associated with any variable. The port tick is an instance of the type EventPort. All ports are exported at the interface of the component. Initially, the state of the component is at the place l1, the only place with token. The BIP code uses the constructs "on...from...to" to represent transitions from one place to the other. The construct "provided" is used when the execution of a transition is restricted by a guard. Moreover, if the transition is associated with a function, the C code inside the constructs "do {...}" is executed.

Components are composed by using connectors. A connector defines the set of possible interactions between ports of components and the corresponding data transfer between the variables associated with the ports. The BIP language allows the definition of connector types.

## 4 Example

Below is presented the syntax of two different types of connectors, RendezVous- Data and BroadcastEvents connector.

```

connector type RendezVousData(DataPort out, DataPort in)

define out in

on out in

up ;

down in.i=out.i;

end

connector type BroadcastEvents(EventPort e1, EventPort e2)

define e1' e2'

on e1

on e2

on e1 e2

export port EventPort e

end

```

The RendezVousData connector defines a strong synchronization between two ports of type DataPort, in and out. The value i is copied from the port in to the port out each time

the connector is executed. The BroadcastEvent connector defines a weak synchronization between the ports e1 and e2 of EventPort type. At least one of the ports is required to initiate the interaction. This interaction is exported to the environment through the EventPort e.

A compound component is a new component type defined from existing components by creating their instances, instantiating connectors between them and specifying the priorities. A compound offers the same interface as an atom, hence externally there is no difference between a compound and an atomic component.

#### 5 Example

The BIP description of the Send/Buffer/Receiver compound component of Figure 2.3 is given below.

compound type Compound\_S\_R\_Buffer

**component** Sender sender **component** Receiver receiver **component** Buffer buffer

**connector** RendezVousData io1 (sender.out, buffer.in) **connector** RendezVousData io2 (buffer.out, receiver.in)

connector BroadcastEvent tick1 (sender.tick, buffer.tick)

connector BroadcastEvent tick2 (tick1.e, receiver.tick)

priority  $\pi_1$  if(true) tick2<io1 priority  $\pi_2$  if(true) tick2<io2

### end

The three atomic components that constitute the Send/Buffer/Receiver model are instantiated. For example **component Sender sender**, creates an instance of **Sender** component named **sender**. Connectors are also instantiated, associating the ports of instantiated components through the interactions defined by the connector type. Finally, priorities are defined specifying an order between a pair of interactions.

# 2.4 THE BIP TOOL-CHAIN

This section presents the implementation of the BIP framework, formally described in the previous sections, in the form of a tool-chain called the BIP tool-chain. The BIP Tool-chain provides a complete implementation, with a rich set of tools for the modeling, the execution and the verification (both static and on-the-fly) of BIP models.

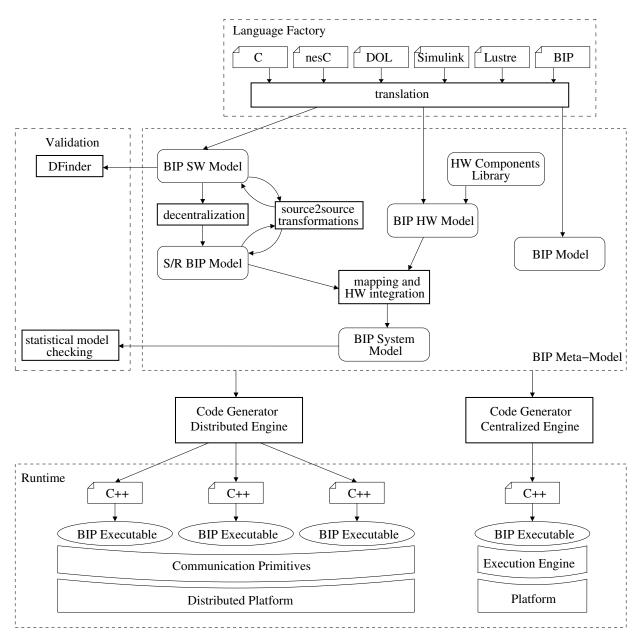

The overview of the BIP tool-chain is shown in Figure 2.4. It includes the following tools:

• *The BIP language.* It is used to build models using components, connectors and priorities and describes components architecture. It is used for the BIP description source.

Figure 2.4: The BIP Tool-Chain.

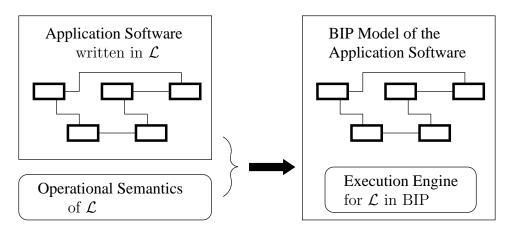

- Source-to-source transformation tools. They are used to transform various programming models, using different languages, into BIP models. The translation of a programming model into a BIP model allows its representation, in a rigorous semantic framework. There exist several translations, including LUSTRE, MAT-LAB/Simulink, AADL, GeNoM applications, NesC/TinyOS applications, C software and DOL systems.

- *The compiler.* It generates a BIP model from the BIP description source. It uses The BIP meta-model as the intermediate representation of BIP models and to implement model transformations. It includes :

- The BIP meta-model. It represents a template of the structure of the intermediate model to be generated from a BIP program, using EMF. All the modeling elements, presented in the BIP language, have a representation in the BIP model in the form of the data-structure. Class diagrams are used to define the relations between the different modeling elements, through inheritance and containment.

- The parser. It analyzes a BIP description source and generates an intermediate model conforming to the BIP meta-model. It performs syntactic analysis of the input program conforming to the BIP grammar and reports the programming errors.

- Model-to-model transformation tools. They are used in order to perform useful static transformations for systems optimizations including run-time. The transformations use a set of correct-by-construction models and preserve functional properties. Moreover, they can take into account extra functional constraints. There exist three types of transformations, architecture optimizations, such as flattening the hierarchy and transforming structured connectors to flat connectors [BJS09], distributed implementation [BBJ+10], such as the replacement of atomic multiparty interactions by protocols using asynchronous message passing (send/receive primitives) and memory management.

- The code generator. It generates C++ code from the model produced by the parser. The code generator has options for generating application code for the single-threaded BIP Engine, the multi-threaded BIP Engine and the distributed BIP implementation.

- *D-Finder*. It is a compositional verification tool for deadlock detection and generation of invariants [BBN<sup>+</sup>09, BGL<sup>+</sup>11]. Verification is applied only to high level models for checking safety properties such as invariants and deadlock-freedom.

- The BIP Execution engines. They are middleware responsible for the coordination of atomic components, that is, they apply the semantics of the interaction and priority layers of BIP. Execution engines are used for execution, simulation, run-time verifications, debug or state-space exploration (i.e. all traces) of BIP models. There are currently three engines available, the single-threaded engine, the multi-threaded engine and the engine supporting the distributed implementation of BIP.

# 2.4.1 The BIP Execution Engines

The BIP execution Engines and the distributed BIP implementations directly implement the BIP operational semantics. It plays the role of the coordinator in selecting and executing interactions between the components, taking into account the glue specified in the input component model. It monitors the state of the components and considering the interaction model, finds all the enabled interactions. It then applies the priority rules to eliminate the interactions with low priority, and selects one amongst the maximal enabled, for execution.

Here is the presentation of the current Engines.

#### The Single-Threaded BIP Engine

From a BIP model, a compiler is used to generate C++ code for atomic components and glue. The code is orchestrated by a sequential engine that interprets the BIP operational semantic rules.

The Engine computes from the set of ports for each atomic components and defined by connectors, the set of enabled interactions. It chooses an interaction  $\alpha = \{\alpha_i | i \in I\} \in \gamma_s$  enabled at state s. The choice of  $\alpha$  depends on the considered scheduling policy. For instance, EDF (Earliest Deadline First) scheduling policy can be used. It executes  $\alpha$  that corresponds to the execution of all atomic components involved in the interaction  $\alpha_i, i \in I$ , followed by the execution of the data transfer function  $F_{\alpha}$  and the update of control locations.

Algorithm 1 gives an implementation of the Execution Engine for the composition of BIP models. It basically consists of an infinite loop that first computes enabled interactions at current state s of the composition. It stops if no interaction is possible from s (i.e. deadlock). Otherwise, it chooses an interaction  $\alpha$ , executes the data transfer function  $F_{\alpha}$  associated to it and executes  $\alpha$ . Finally, the state s is updated in order to take into account the execution of  $\alpha$ .

Algorithm 1 Single Threaded Execution Engine

```

Require: Model M^i = (Q_i, \rightarrow_i), 1 \leq i \leq n, initial control location (q_0^1, \ldots, q_0^n), set of

interactions \gamma

s = (q^1, \dots, q^n) \leftarrow (q_0^1, \dots, q_0^n)

loop

\gamma_s = EnabledInteractions(s)

if \exists \alpha \in \gamma_s then

\alpha = \{\alpha_i | i \in I\} \leftarrow EDFScheduler(\gamma_s)

Execute DataTransfer(F_{\alpha})

for all i \in I do

Execute(\alpha_i)

q_i \leftarrow q'_i

end for

else

exit(DEADLOCK)

end if

end loop

```

## The Multi-Threaded BIP Engine

The implementation of the multi-threaded implementation with centralized engine is based on the notion of partial state semantics where interactions are allowed to fire as soon as only the involved components are stable [BBB<sup>+</sup>08]. Each atomic component is assigned to a different thread (process), the engine being assigned to a thread as well. Each atomic component performs its computations locally and then, when it reaches a stable state, it notifies the engine about the ports on which it is willing to interact. It waits for the engine to select the port to be executed upon the chosen interaction.

The Engine is parametrized by an oracle. As depicted in Algorithm 2, the engine computes feasible interactions available on state components. Then, if such interactions exist and the oracle allows them, the engine selects one for execution and notifies the involved components.

Iteratively, the Engine receives the sets of ports and the local states of components ready to interact. Depending on this information, the engine computes the feasible interactions. It chooses a feasible interaction, which is allowed by the oracle O. If such an interaction exists, the engine executes it by notifying sequentially, in some arbitrary order, all the involved components. Otherwise, it is a deadlock.

Algorithm 2 Multi-Threaded Execution Engine

```

Require: Model M^i = (Q_i, \rightarrow_i), 1 \leq i \leq n, initial control location (q_0^1, \ldots, q_0^n), set of

interactions \gamma

s = (q^1, \dots, q^n) \leftarrow (q_0^1, \dots, q_0^n)

loop

wait(P_i)

\gamma_s = EnabledInteractions(P_i)

\gamma_o = restriction(\gamma_s, O)

if \exists \alpha \in \gamma_o then

\alpha = \{\alpha_i | i \in I\} \leftarrow EDFScheduler(\gamma_s)

ExecuteDataTransfer(F_{\alpha})

for all i \in I do

notify(M_i, \alpha_i)

q_i \leftarrow q'_i

end for

else

exit(DEADLOCK)

end if

end loop

```

## 2.4.2 The Distributed BIP Implementation

Currently, powerful hardware platforms are needed for executing applications on multicore or many-core platforms. The application code should be optimally distributed over the platform to take advantage of its computing power. Although distributed systems are widely used nowadays, their implementation is still time-consuming and an error-prone task. The distributed implementation in BIP provides a method for automatic generation of efficient and correct-by-construction distributed model from a given application software in BIP. Coordination in BIP is achieved through multi-party interactions (i.e., those across multiple components), and scheduling by using dynamic priorities. Transforming the semantics of BIP, which is based on a global state model, into a distributed implementation is clearly a non-trivial task.

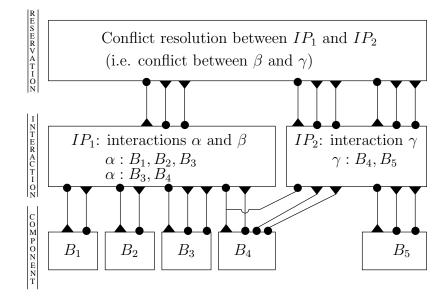

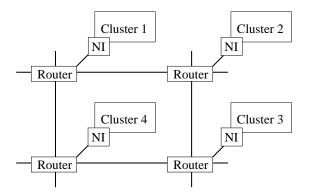

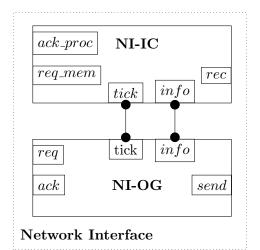

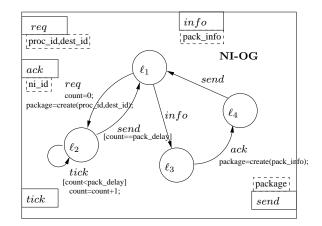

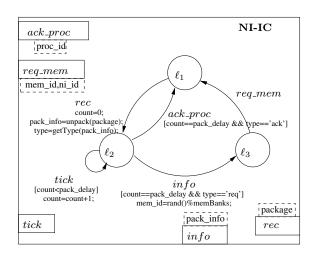

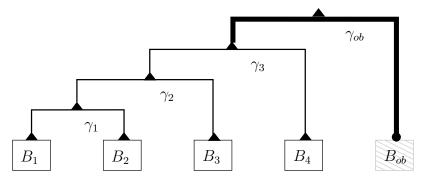

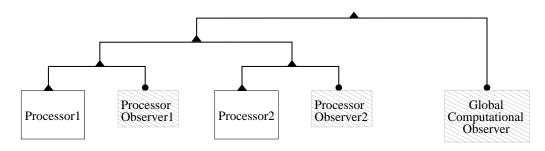

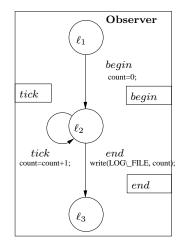

A generic framework allowing the transformation of high-level BIP models into distributed implementations has been recently developed [BBJ<sup>+</sup>10]. The method involves BIP to BIP transformations preserving observational equivalence. It transforms multiparty interactions into asynchronous message passing, that is, send/receive primitives. The target Send/Receive BIP model is structured in three layers (see Figure 2.5): (i) the component layer corresponds to a modified behavior of the components of the original model; (ii) the interaction protocol consists of a set of components such that each component detects enableness of a subset of interactions of the original model using partial-state knowledge, and executes them after resolving conflicts (e.g., regarding which interaction to execute when there is more than one involving the same port) either locally or by the help of the third layer; (iii) the reservation protocol resolves conflicts between components of the interaction protocol layer using committee coordination algorithms such as the token-ring distributed algorithm or the distributed dining philosophers algorithm. Notice that the obtained Send/Receive BIP model depends on a user-defined partition of the interactions of the original model, associating subsets of interactions to components of the interaction protocol layer.

Figure 2.5: Send/Receive BIP model obtained from BIP to BIP transformations.

A C++ code generator has been developed. Given a user-defined mapping of the components of a Send/Receive BIP model, it generates the distributed implementations using communication mechanisms offered by the platform. We have the following backends: Unix processes communicating through TCP sockets, MPI, and threads using semaphores and shared memory. Efficient monolithic code can be produced by merging components using another BIP to BIP transformation, according to the mapping of the components.

The method has been fully implemented in a toolset allowing the automatic generation of distributed implementations from BIP models. It is parametrized by the partitioning of interactions, a committee coordination algorithm, and the mapping of components.

# **2.5** CONCLUSION

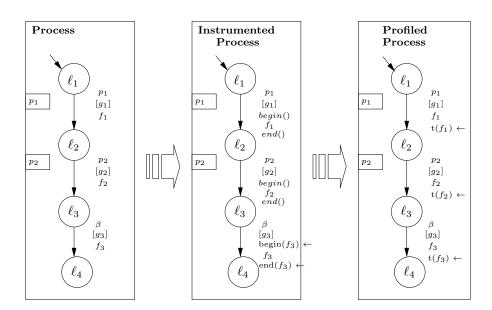

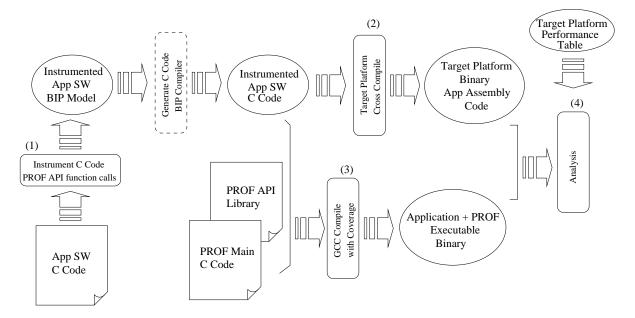

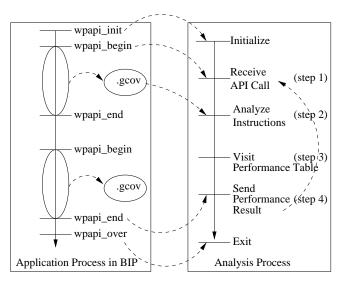

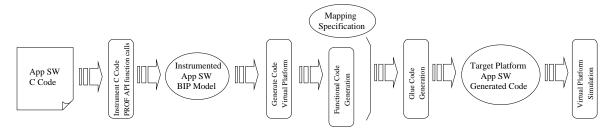

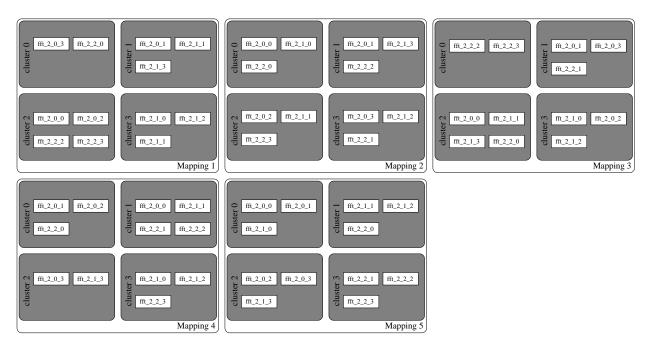

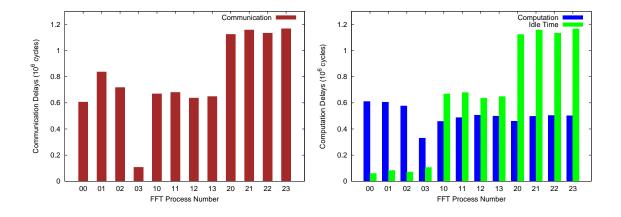

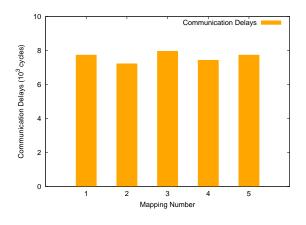

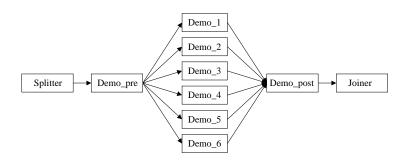

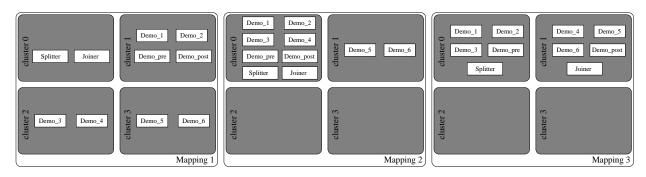

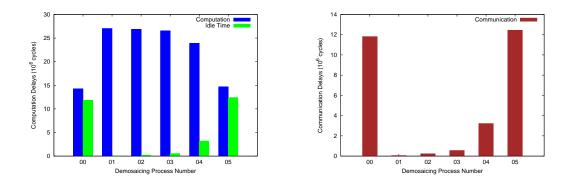

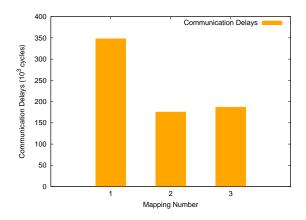

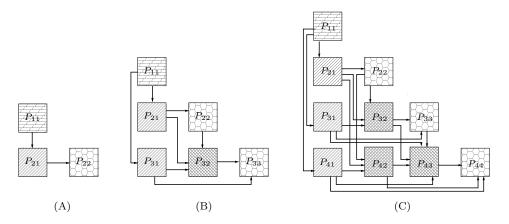

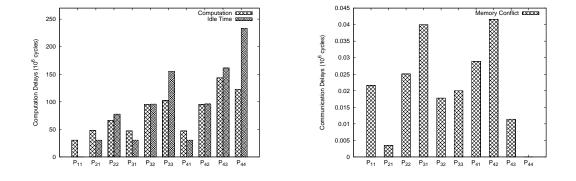

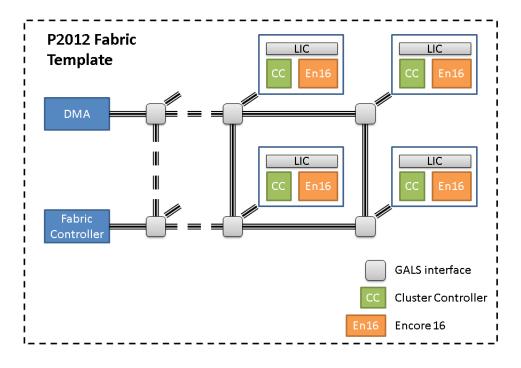

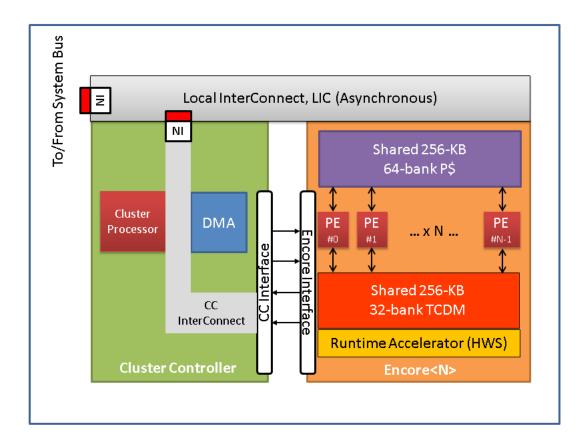

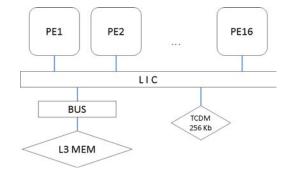

BIP [BBS06] (Behavior, Interaction, Priority) is a general framework encompassing rigorous design. It uses the BIP language and an associated toolset supporting the design flow. The BIP language is a notation which allows building complex systems by coordinating the behavior of a set of atomic components. Behavior is described as a finite-state automaton extended with data and functions described in C/C++. The transitions of the automata are labeled with guards (conditions on the state of a component and its environment) as well as functions that describe computations on local data. The description of coordination between components is layered. The first layer describes the interactions between components. The second layer describes dynamic priorities between the interactions and is used to express scheduling policies. The combination of interactions and priorities characterizes the overall architecture of a component. It confers BIP strong expressiveness that cannot be matched by other languages [BS08b]. BIP has clean operational semantics that describe the behavior of a composite component as the composition of the behaviors of its atomic components. This allows a direct relation between the underlying semantic model (transition systems) and its implementation.