## Design of a High Efficiency High Power Density DC/DC Converter for Low Voltage Power Supply in Electric and Hybrid Vehicles

Gang Yang

#### ► To cite this version:

Gang Yang. Design of a High Efficiency High Power Density DC/DC Converter for Low Voltage Power Supply in Electric and Hybrid Vehicles. Other. Supélec, 2014. English. NNT: 2014SUPL0011 . tel-01140766

## HAL Id: tel-01140766 https://theses.hal.science/tel-01140766

Submitted on 9 Apr 2015  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre : 2014-11-TH

## SUPELEC

**ECOLE DOCTORALE STITS** « Sciences et Technologies de l'Information des Télécommunications et des Systèmes »

# THÈSE DE DOCTORAT

DOMAINE : SPI Spécialité : Energie

Soutenue le 04/avril/2014

par :

## Gang YANG

Conception d'un Convertisseur à Haut Rendement et Très Forte Puissance Massique pour Alimentation du Réseau de Bord Basse Tension des Véhicules Electriques et Hybrides

| Directeur de thèse :                 | Daniel SADARNAC                                        | Professeur (SUPELEC)                                                                                                                                                      |

|--------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Composition du jury</u> :         |                                                        |                                                                                                                                                                           |

| Président du jury :<br>Rapporteurs : | Abdellatif MIRAOUI<br>Alain JAAFARI<br>Francois BERNOT | Professeur (Université de Technologie Belfort-Montbéliard)<br>Professeur (Université de Picardie Jules Verne Amiens)<br>Professeur (Université de Francois-Rabelais Tour) |

| Examinateurs :                       | Abdellatif MIRAOUI<br>Eric LABOURE<br>Zoubir KHATIR    | Professeur (Université de Technologie Belfort-Montbéliard)<br>Professeur (Université Paris-Sud LGEP)<br>Directeur de Recherche (IFSTTAR-LTN)                              |

| Membres invités :                    | Patrick DUBUS                                          | Ingénieur (VALEO)                                                                                                                                                         |

# Conception d'un Convertisseur à Haut Rendement et Très Forte Puissance Massique pour Alimentation du Réseau de Bord Basse Tension des Véhicules Electriques et Hybrides

## Résumé

Cette thèse traite de la conception d'un convertisseur DC / DC destiné aux véhicules électriques et hybrides (2,5 kW, 400V/14V, 250kHz). Dérivé de la topologie LLC à résonance, ce convertisseur bénéficie des nombreux avantages propres à cette structure particulière. C'est ainsi que le prototype réalisé présente un rendement très élevé, une densité de puissance très forte avec des perturbations EMI très réduites. La première partie de cette thèse est consacrée à l'analyse théorique du circuit LLC afin de dégager un modèle de conversion et une stratégie de contrôle adaptée à l'application visée. Afin de conserver un rendement important sur une large plage de charge, une structure basée sur la mise en parallèle de deux modules LLC est proposée. Une nouvelle stratégie de contrôle à deux boucles est également proposée pour équilibrer le courant entre les deux modules. La seconde partie de la thèse fait appel à la simulation et à l'expérimentation. Il s'agit de minimiser la masse et l'encombrement tout en maximisant le rendement. Un composant magnétique spécial est conçu puis dimensionné pour intégrer le transformateur et diverses inductances. Pour cela, les pertes dans le circuit magnétique et les enroulements sont quantifiées en fonction de divers modes de réalisation et diverses géométries. Ce convertisseur met également en œuvre un système de redressement synchrone robuste avec une compensation de phase, un module de puissance avec une résistance thermique très faible et un système de refroidissement efficace par air. Le rendement maximal mesuré est 95%. Le rendement demeure supérieur à 94% sur une plage de puissance s'étalant de 500 W à 2 kW. La densité de puissance est 1W/cm3. La CEM du convertisseur est développée dans cette thèse.

**Mots-clés**: convertisseur à résonance LLC, commutation douce, composant magnétique, augmentation du rendement, équilibrage de courant

# Design of a High Efficiency High Power Density DC/DC Converter for Low Voltage Power Supply in Electric and Hybrid Vehicles

### Abstracts

In this dissertation, a 2.5kW 400V/14V, 250kHz DC/DC converter prototype is developed targeted for electric vehicle/hybrid vehicle applications. Benefiting from numerous advantages brought by LLC resonant topology, this converter is able to perform high efficiency, high power density and low EMI. A first part of this dissertation is the theoretical analysis of LLC: topology analysis, electrical parameter calculation and control strategy. To arrange high output current, this thesis proposes parallel connected LLC structure with developed novel double loop control to realize an equal current distribution. The second part concerns on the system amelioration and efficiency improvement of developed LLC. A special transformer is dimensioned to integrate all magnetic components, and various types of power losses are quantified based on different realization modes and winding geometries to improve its efficiency. This converter also implements a robust synchronous rectification system with phase compensation, a power semiconductor module, and an air-cooling system. The power conversion performance of this prototype is presented and the developed prototype has a peak efficiency of 95% and efficiency is higher than 94% from 500W to 2kW, with a power density of 1W/cm<sup>3</sup>. The CEM analysis of this converter is also developed in this thesis.

Keywords: LLC resonant converter, soft switching, magnetic components, efficiency improvement, current sharing

## To my family:

My parents: Mr. Xiaoping YANG and Ms. Jie WANG

My fiancée: Miss. Qian WANG

To my tutors:

Prof. Daniel SADARNAC

Mr. Patrick DUBUS

And all the other comrades who contributed ...

# Table of contents

| Résumé .  |                                                                                                      | R.i         |

|-----------|------------------------------------------------------------------------------------------------------|-------------|

| Chapter 1 | . Introduction                                                                                       | 12          |

| 1.1       | Backgrounds and project introduction                                                                 | 12          |

| 1.2       | Discussions on existed soft-switching converter solutions                                            | 15          |

| 1.2.1     | H-bridge phase shift converter                                                                       | 15          |

| 1.2.2     | Series resonant converter                                                                            | 16          |

| 1.2.3     | Parallel resonant converter                                                                          | 19          |

| 1.2.4     | Series-parallel resonant converter                                                                   | 21          |

| 1.2.5     | LLC resonant converter                                                                               |             |

| 1.3       | Challenges of LLC resonant converters                                                                | 27          |

| 1.3.1     | High efficiency among large load range                                                               |             |

| 1.3.2     | High output current arrangement                                                                      |             |

| 1.3.3     | Large voltage variation capability at limited frequency range                                        |             |

| 1.3.4     | Transformer improvement and integration                                                              |             |

| 1.3.5     | Component and system for effective cooling                                                           |             |

| 1.3.6     | Robust synchronous rectification                                                                     |             |

| 1.4       | Dissertation outline                                                                                 |             |

| 1.5       | References                                                                                           |             |

| Chapter 2 | 2. Parallel-parallel double phase LLC: Topology and Dimensioning                                     |             |

| 2.1       | From single cell LLC to double cell LLC                                                              |             |

| 2.1.1     | Challenges of single phase LLC resonant converters for high current of                               | output 36   |

| 2.1.2     | <ul> <li>Proposition of double phase LLC resonant converter and its operation</li> <li>37</li> </ul> | al strategy |

| 2.2       | LLC optimal dimensioning                                                                             |             |

| 2.2.1     | Equivalent circuit and frequency domain analysis                                                     | 44          |

| 2.2.2     | Circuit design                                                                                       | 50          |

| 2.2.3     | Influence of secondary leakage inductance                                                            | 53          |

| 2.2.4     | Re-evaluation of Magnetizing Inductance vs. input voltage regulation 60                              | capability  |

| 2.2.5     | ZVS condition fulfilment                                                                             |             |

| 2.3       | References:                                                                                          | 67          |

| Chapter 3 | B. Parallel-parallel Double Phase LLC: Operation and Control                                         | 70          |

| 3.1       | Current Sharing in Double Phase LLC                                                                  | 70          |

| 2 1        | 1   | Current charing problems in phase shift perellel perellel LLC converter    | 70    |

|------------|-----|----------------------------------------------------------------------------|-------|

| 3.1        |     | Current sharing problems in phase-shift parallel-parallel LLC converter    |       |

| 3.1        |     | Current balancing among different power cells                              |       |

| 3.2        |     | ntrol and regulations                                                      |       |

| 3.2        |     | Current regulation control                                                 |       |

| 3.2        |     | Voltage regulation control                                                 |       |

| 3.3        |     | er Controls and Protections                                                |       |

| 3.4        |     | erences                                                                    |       |

| Chapter    |     | Efficiency Improvement and System Optimization of LLC Converter            |       |

| 4.1        |     | ver module development for LV MOSFETs integration                          |       |

| 4.2        | Tra | nsformer Design and Improvement                                            |       |

| 4.2        | .1  | Core Material Analysis and Selection                                       | . 102 |

| 4.2        | .2  | Transformer design and resonant inductance integration                     | . 106 |

| 4.2        | .3  | Eddy current loss study                                                    | . 116 |

| 4.3        | Imp | provement of synchronous rectification                                     | . 121 |

| 4.3        | .1  | Synchronous rectification and its imperfections in LLC resonant converters | . 121 |

| 4.3        |     | Proposed phase compensation scheme for synchronous rectification in LLC    | 127   |

| 4.3        |     |                                                                            |       |

|            |     | Snubber design for voltage spike elimination                               |       |

| 4.3        |     | Further discussion for practical applications                              |       |

| 4.4        |     | cooling system and prototype assembly                                      | . 133 |

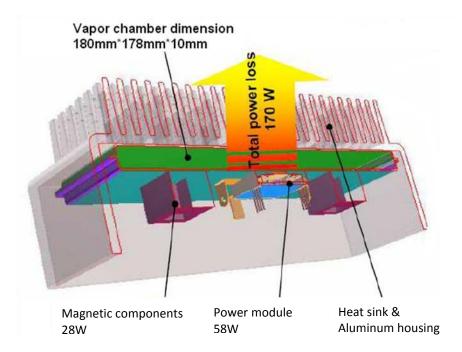

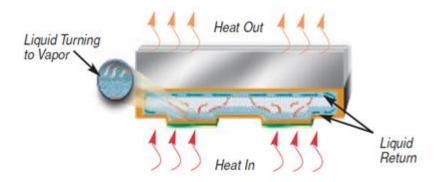

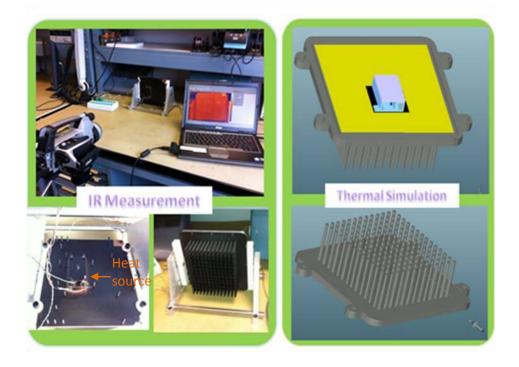

| 4.4<br>cor |     | Vapor chamber as a new solution for air cooling in automotive DCDC         | . 133 |

| 4.4        |     | Prototype assembly and cooling system performance                          |       |

| 4.5        |     | iciency and power loss analysis                                            |       |

| 4.6        |     | erences                                                                    |       |

| Chapter    |     | Electromagnetic Compatibility Analysis of Double Phase LLC                 |       |

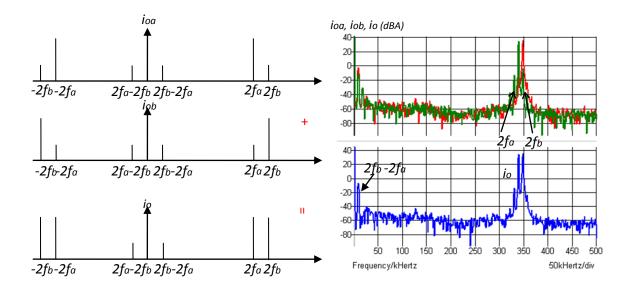

| 5.1        |     | provement of double phase LLC for conducted emission reduction             |       |

| 5.1        |     | LLC cell arrangement                                                       |       |

| 5.1        |     | EMC discussion of double phase LLC.                                        |       |

| 5.2        |     | er Design and Improvement                                                  |       |

| 5.2        |     | Input Filter Design and Dimensioning                                       |       |

| 5.2        |     | Output filter design and dimensioning                                      |       |

| 5.3        |     | asurement results on conducted EMC and Discussions                         |       |

| 5.4        |     | erences:                                                                   |       |

|            |     |                                                                            |       |

| Chapter    | υ.  | Conclusions                                                                | . 102 |

# List of Figures

| Figure 1-1: Typical electrical vehicles in mass production or demo (PHEV=plug-in hybrid electric vehicle, EREV= extended range electric vehicle)                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2: A typical mechanical traction and power conversion system in electric vehicles 13                                                                                     |

| Figure 1-3. The H-bridge phase shift PWM converter                                                                                                                                |

| Figure 1-4. Typical waveforms of H-bridge phase shift PWM converter                                                                                                               |

| Figure 1-5. VALEO's 2.5kW, 400/14V, 100kHz, full bridge phase shift DCDC converter with 0.61W/cm <sup>3</sup> power density                                                       |

| Figure 1-6. Half bridge series resonant converter with synchronous rectification                                                                                                  |

| Figure 1-7. Voltage conversion ratio characteristics of series resonant converter                                                                                                 |

| Figure 1-8. Half bridge parallel resonant converter with synchronous rectification                                                                                                |

| Figure 1-9. Equivalent ac resistors presented by different rectifier loads: (a) voltage source converter, (b) current source converter                                            |

| Figure 1-10. Voltage conversion ratio characteristics of parallel resonant converter                                                                                              |

| Figure 1-11. Half bridge series-parallel resonant converter with synchronous rectification 21                                                                                     |

| Figure 1-12. Gain characteristics of series-parallel resonant converter (Cr=Cp)                                                                                                   |

| Figure 1-13. Half bridge LLC converter with synchronous rectification                                                                                                             |

| Figure 1-14. Gain characteristics of LLC resonant converter (Lm=4Lr)                                                                                                              |

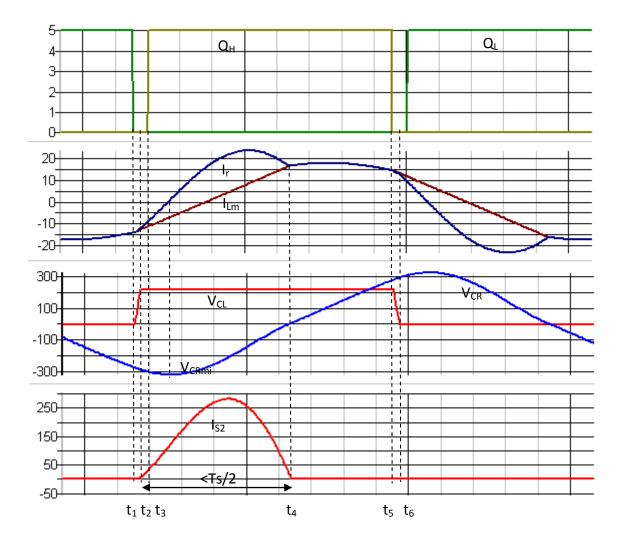

| Figure 1-15. Operating waveforms of LLC converter at ZVS-DCM                                                                                                                      |

| Figure 1-16. The operation of LLC resonant converter in ZVS-CCM                                                                                                                   |

| Figure 1-17. 1MHz 1kW, 400V/48V converter mock-up of Virginia Polytechnic University, peak efficiency up to 96%, with 8.9W/cm <sup>3</sup> power density (only main components)27 |

| Figure 1-18. Operating time distribution of the targeted 2.5kW converter                                                                                                          |

| Figure 1-19. Planar E cores and Standex center-tapped transformer with Planar ER cores 30                                                                                         |

| Figure 1-20. Three types of synchronous rectification circuit                                                                                                                     |

| Figure 2-1. The framework of proposed double phase LLC resonant converter                                                                                                         |

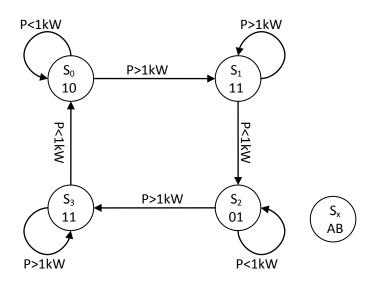

| Figure 2-2. State diagram of cell switching                                                                                                                                       |

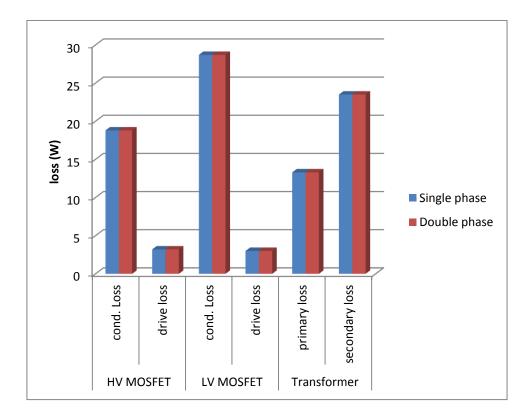

| Figure 2-3. Comparison of the calculated power loss between single phase LLC converter and double phase LLC at 2.5kW                                                              |

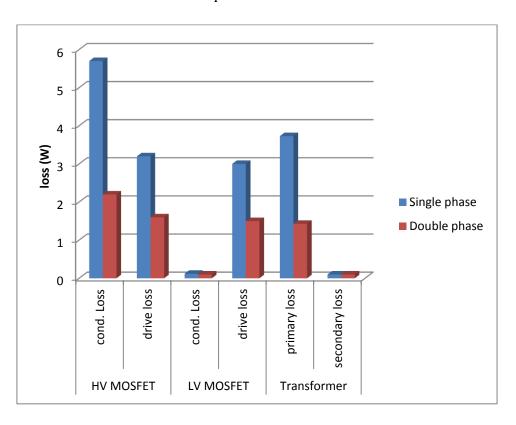

| Figure 2-4. Comparison of the calculated power loss between single phase LLC converter and double phase LLC at 100W                                                               |

| Figure 2-5. Comparison of the calculated power loss between single phase LLC converter and double phase LLC at 100W (considering only conduction losses & drive losses) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

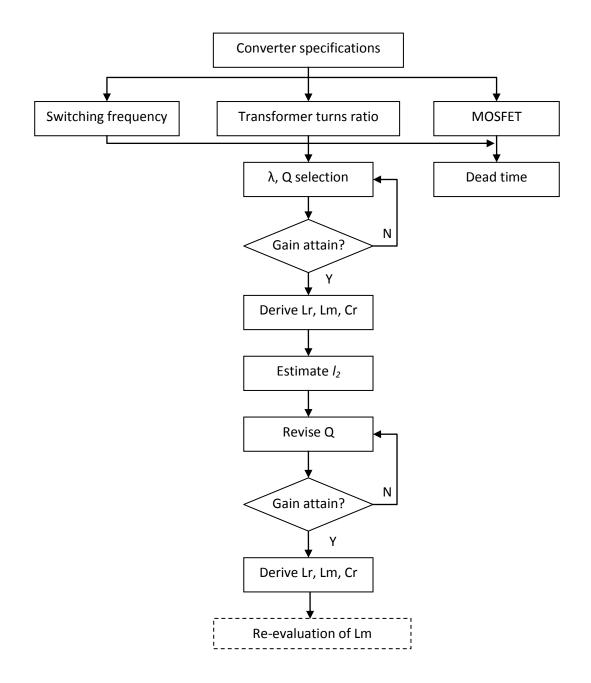

| Figure 2-6. Proposed design procedures                                                                                                                                  |

| Figure 2-7. The equivalent circuit of the single cell LLC resonant converter                                                                                            |

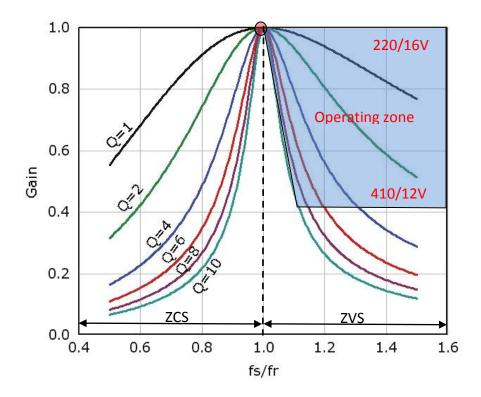

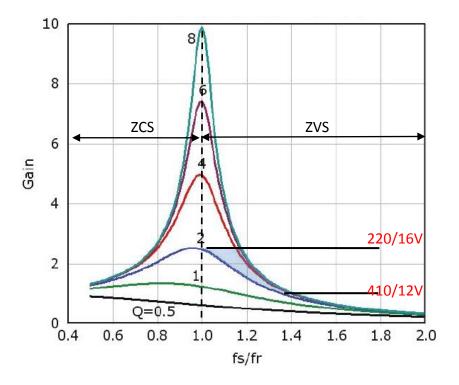

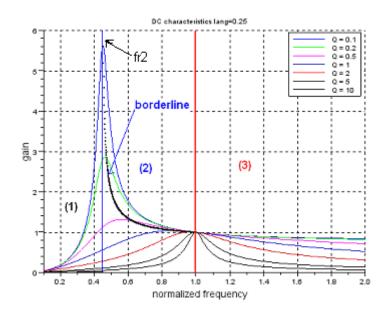

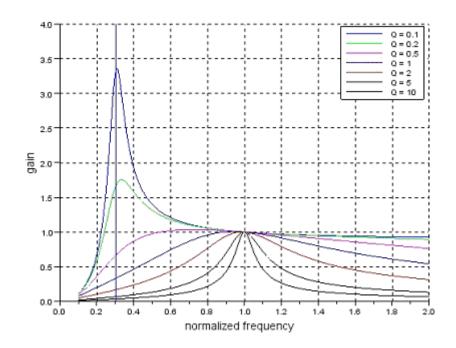

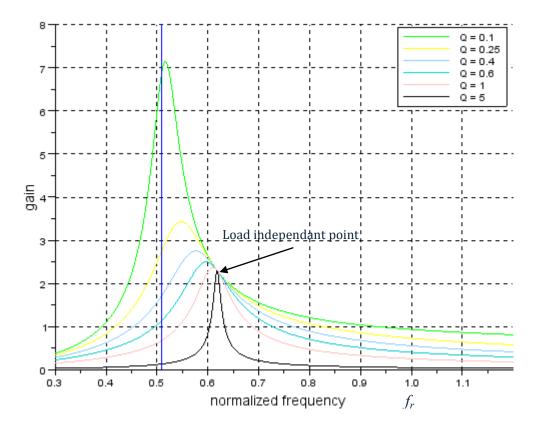

| Figure 2-8. The DC gain characteristics of LLC resonant converter at $\lambda$ =0.25                                                                                    |

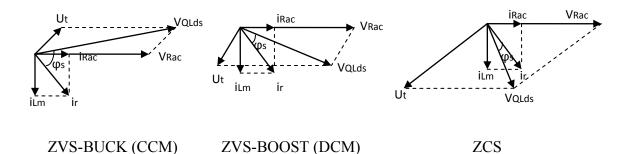

| Figure 2-9. The vector diagram of the LLC converter operating in different regions                                                                                      |

| Figure 2-10. The DC gain characteristics of LLC resonant converter at $\lambda$ =0.1                                                                                    |

| Figure 2-11. The DC gain characteristics of LLC resonant converter at $\lambda$ =0.5                                                                                    |

| Figure 2-12. The DC gain characteristics of LLC resonant converter at $\lambda$ =1                                                                                      |

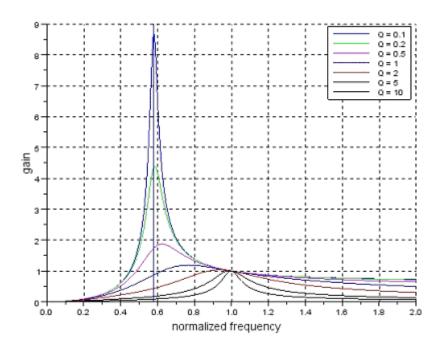

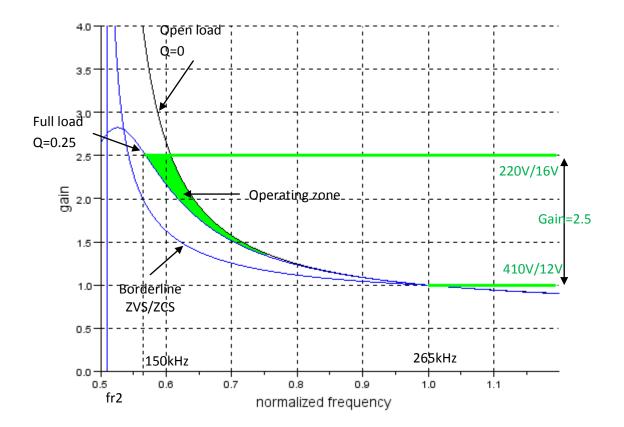

| Figure 2-13. The operating zone of the designed LLC resonant power cell                                                                                                 |

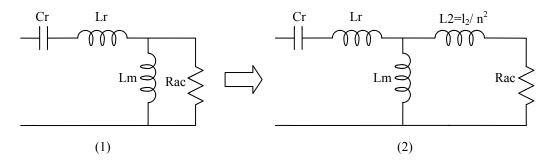

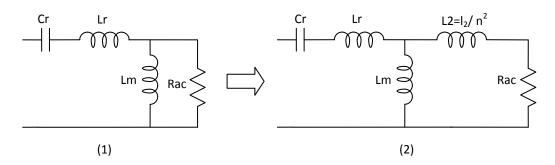

| Figure 2-14. Equivalent circuit of the LLC resonant converter cell (1) or with (2) secondary leakage inductance                                                         |

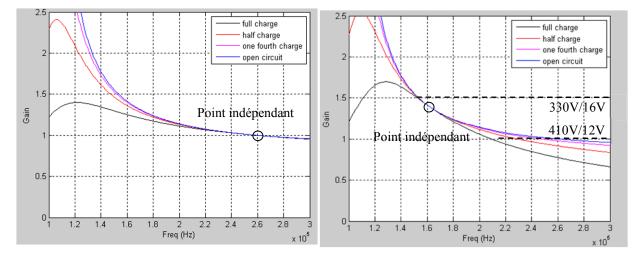

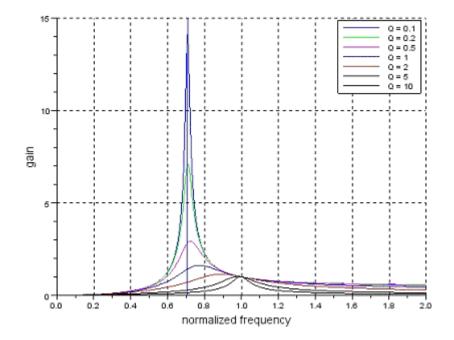

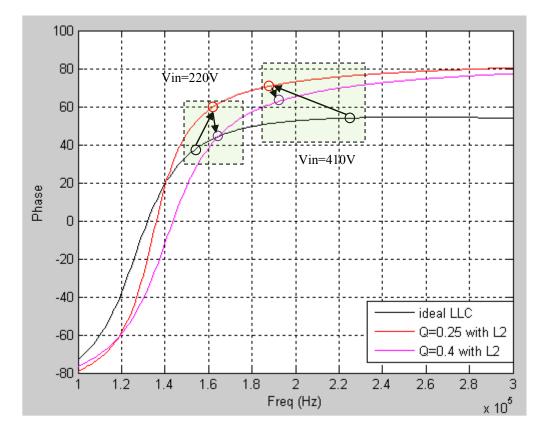

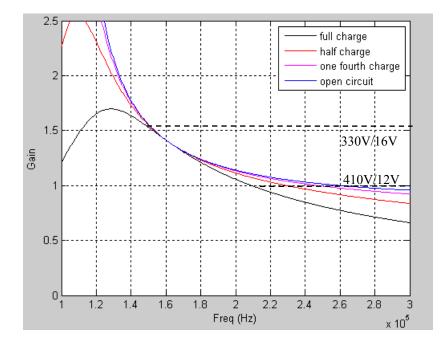

| Figure 2-15. DC gain characteristics of LLC resonant converter with $l_2$ =120nH                                                                                        |

| Figure 2-16. Operating points transition at nominal power under two different input voltages (Vin=220V, Vin=410V, separately)                                           |

| Figure 2-17. Theoretical and experimental voltage conversion ratio under different loading conditions, including transformer's secondary leakage inductance             |

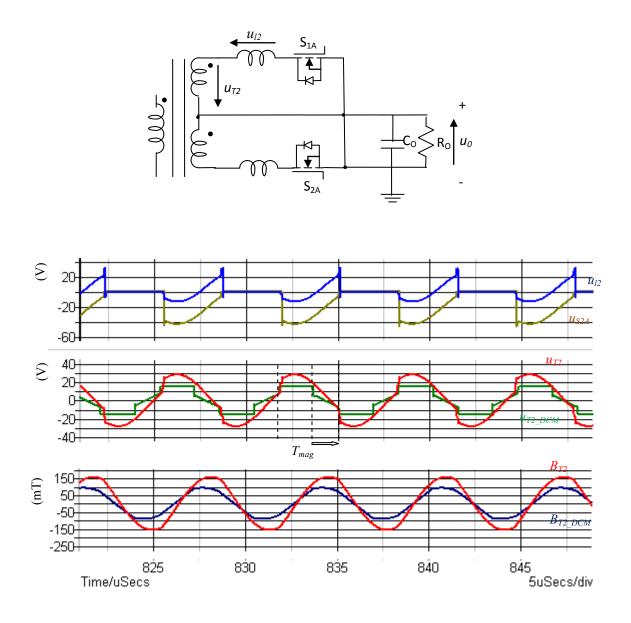

| Figure 2-18. Waveforms of circuit operation considering the secondary leakage inductance 59                                                                             |

| Figure 2-19. Proposal of BOOST+LLC to improve the power factor                                                                                                          |

| Figure 2-20. Typical state-of-charge (SOC) of a lithium ion battery in electric vehicles61                                                                              |

| Figure 2-21. Voltage conversion ratio of modified LLC resonant cell with Lm=42µH62                                                                                      |

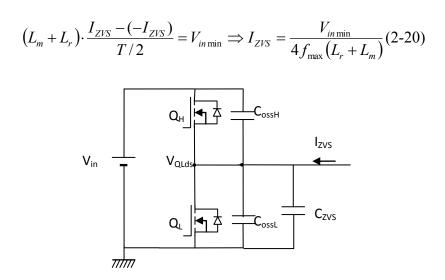

| Figure 2-22. ZVS operation at the half bridge middle point                                                                                                              |

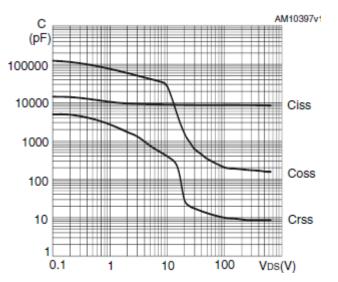

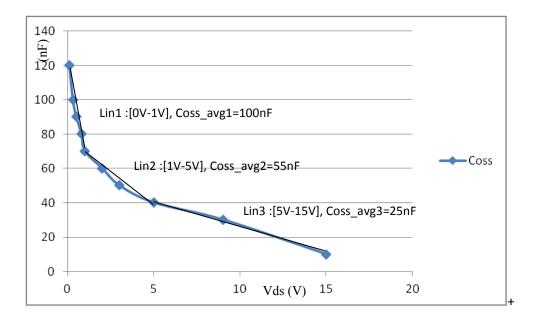

| Figure 2-23. Capacitance variations of MOSFET STW88N65M5 vs. Vds                                                                                                        |

| Figure 2-24. Capacitance variations of MOSFET STW88N65M5 vs. Vds                                                                                                        |

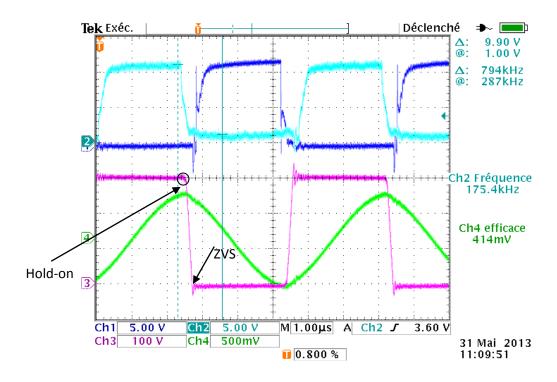

| Figure 2-25. Waveforms of ZVS switching with td=400ns at Vin=330V, P=300W66                                                                                             |

| Figure 2-26. Failure of a ZVS switching when td=200ns (tested at Vin=50V, no load)                                                                                      |

| Figure 3-1. Two-phase interleaving LLC resonant converter with 90° phase shift                                                                                          |

| Figure 3-2. Histogram plot of the current percentage shared by the power cell B in Monte-<br>Carlo analysis                                                             |

| Figure 3-3. Proposed double phase LLC resonant converter with primary current sensors 74                                                                                |

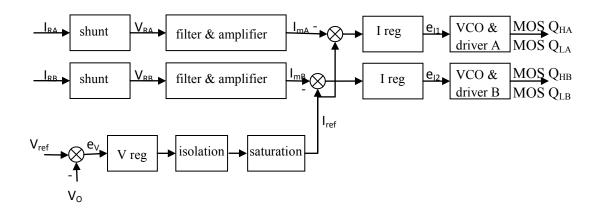

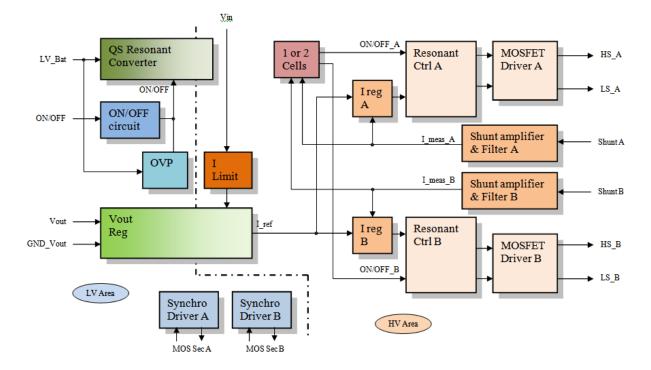

| Figure 3-4. Bloc schematic of the control circuit for input current balancing applied to double phase LLC converter                                                     |

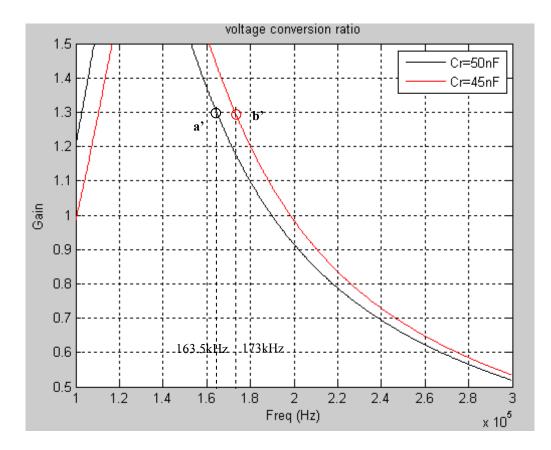

| Figure 3-5. Operational point movement with component mismatch at Vin=360V, Vo=14V, P=1250W under phase shift control                                                   |

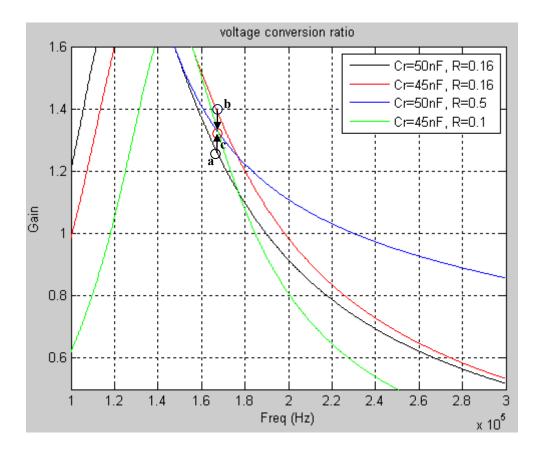

| Figure 3-6. Operational points determination for two phase parallel LLC with component mismatch at Vin=360V, Vo=14V, P=1250W under proposed double loop control77 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

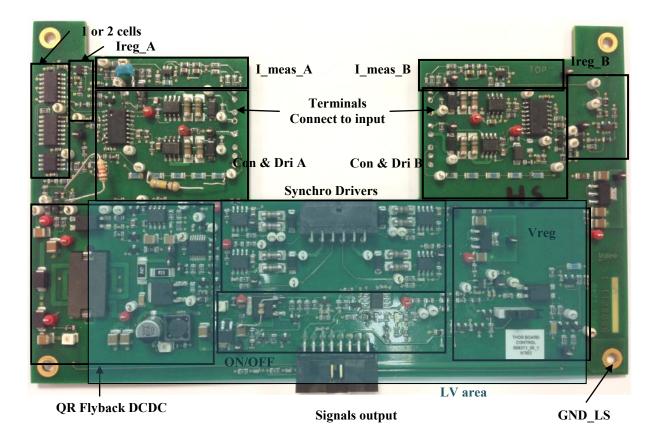

| Figure 3-7.Framework of the control board applying proposed control strategy                                                                                      |

| Figure 3-8. Components arrangement and design results of the control PCB card                                                                                     |

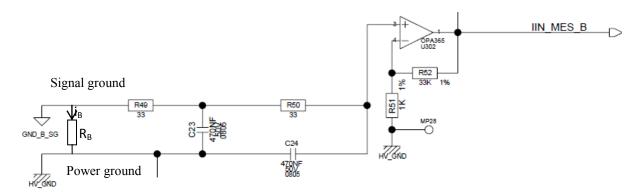

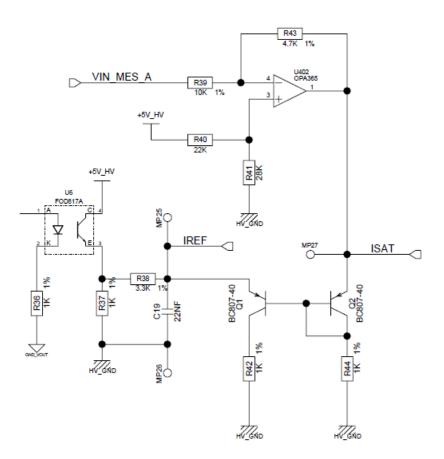

| Figure 3-9. Input current filtering and amplifier circuit at the cell B                                                                                           |

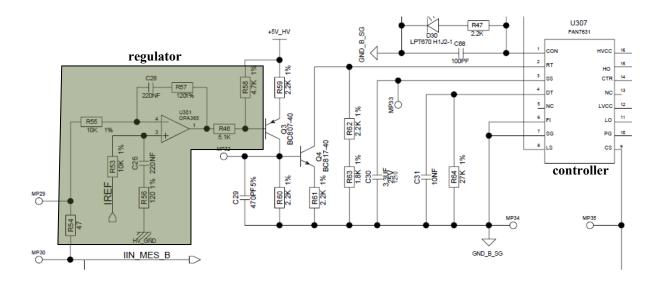

| Figure 3-10. Current regulation circuit applied for the power cell B                                                                                              |

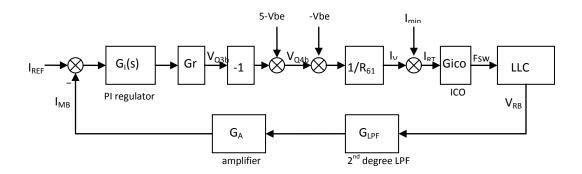

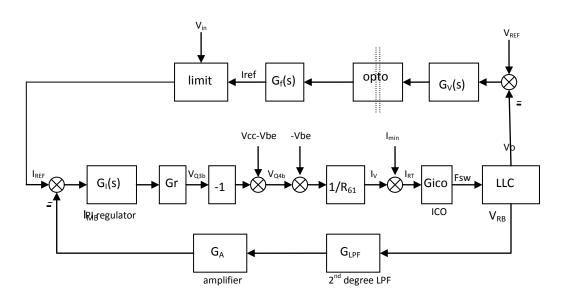

| Figure 3-11. Block diagram of current regulation in proposed LLC resonant converter                                                                               |

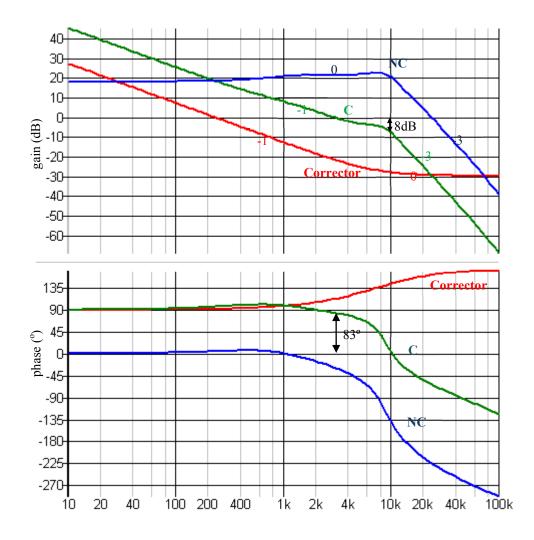

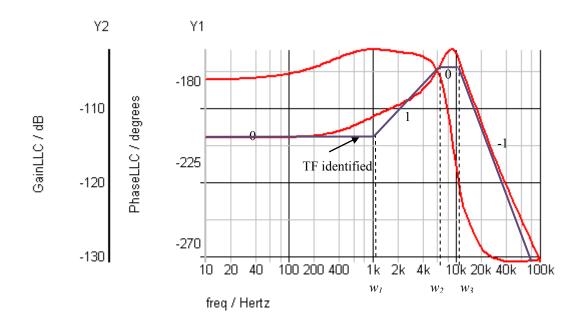

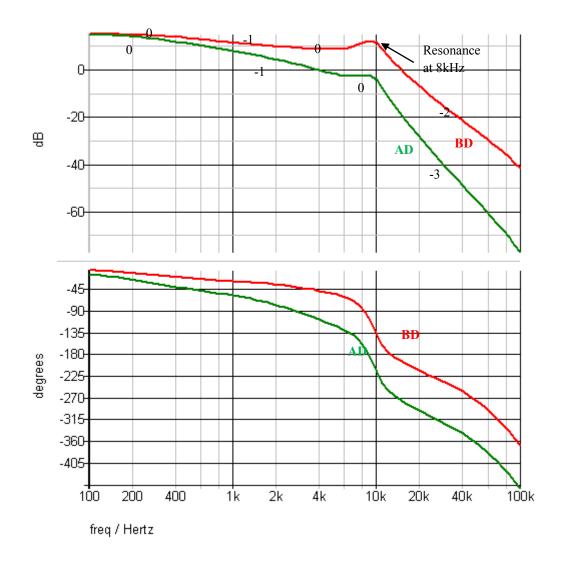

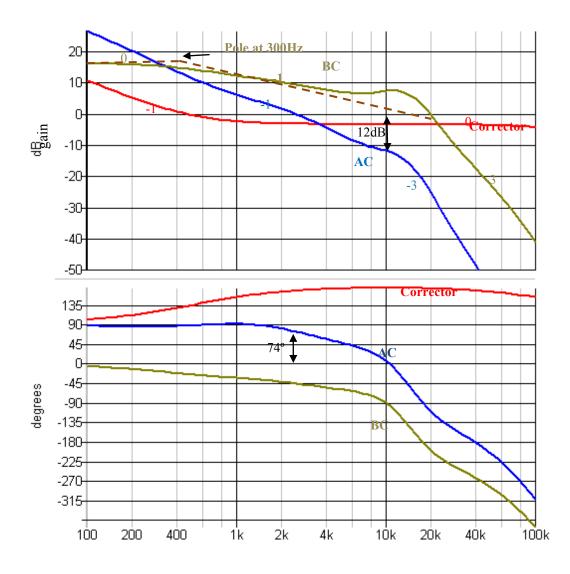

| Figure 3-12. Bode diagram of $G_{LLC}(s)$ , open loop transfer function before correction (BC) and after correction (AC) at nominal power 1250W, Vin=330V         |

| Figure 3-13. Bode diagram of open loop transfer function before correction (BC) and after correction (AC) at 100W, Vin=330V                                       |

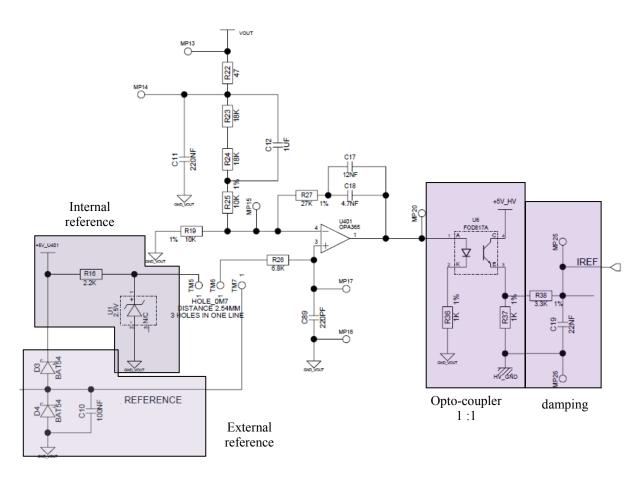

| Figure 3-14. Electric schema for voltage regulation                                                                                                               |

| Figure 3-15. Bode diagram of LLC's voltage open loop transfer function before RC damping (BD) and after RC damping (AD)                                           |

| Figure 3-16. Block diagram of voltage regulation in proposed LLC resonant converter 89                                                                            |

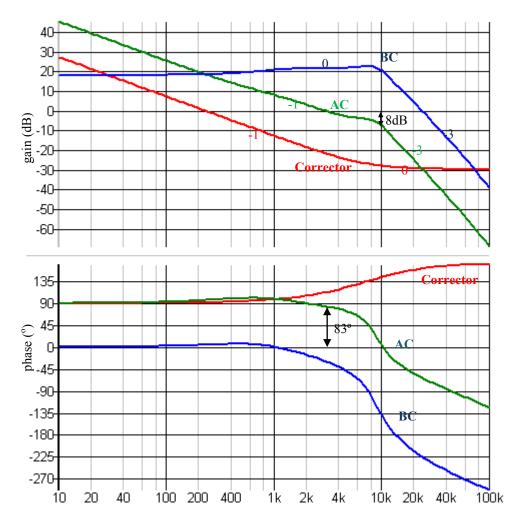

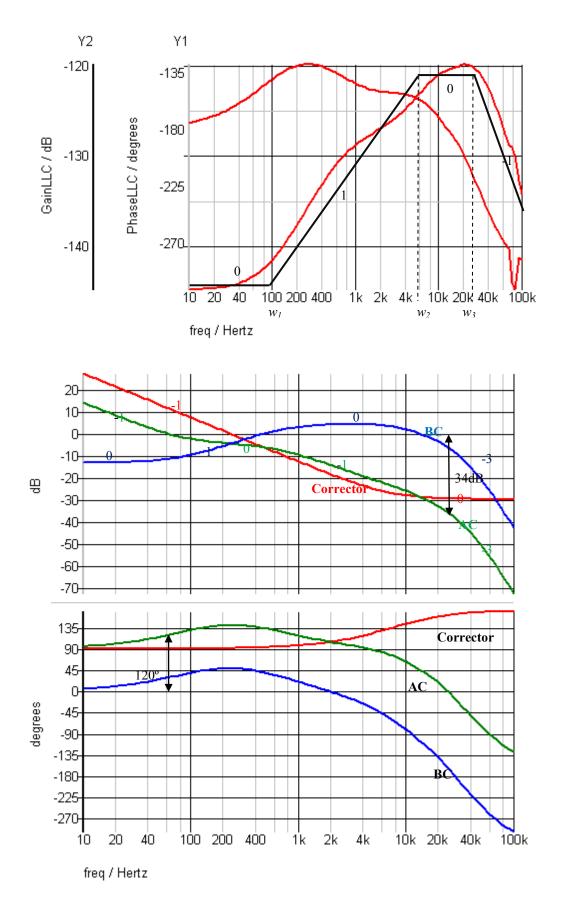

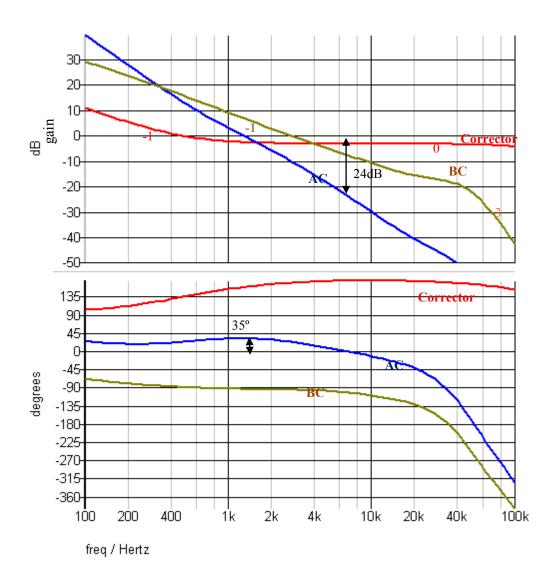

| Figure 3-17. Bode diagram of voltage open loop transfer function before correction (BC) and after correction (AC) at nominal power 1250W, Vin=330V                |

| Figure 3-18. Bode diagram of voltage open loop transfer function before correction (BC) and after correction (AC) at power 100W, Vin=330V                         |

| Figure 3-19. Iref saturation circuit design in voltage control loop                                                                                               |

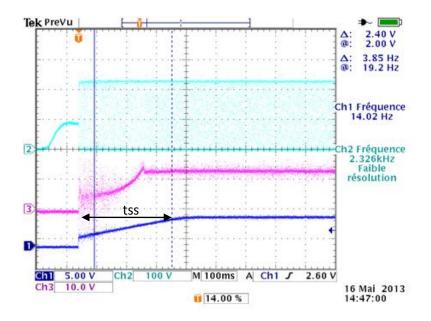

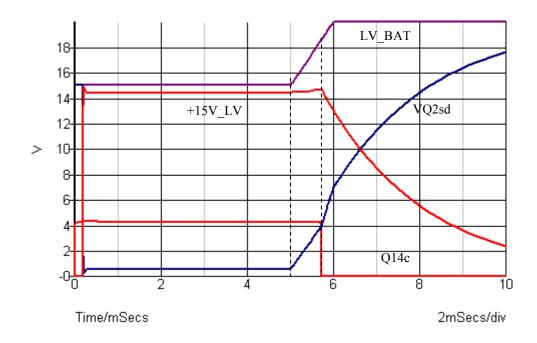

| Figure 3-20. Experimental results for converter's soft-start                                                                                                      |

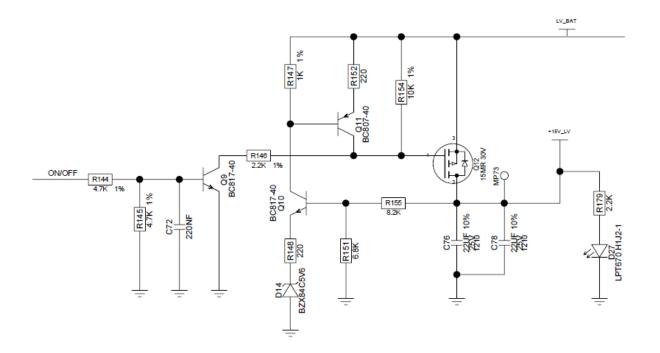

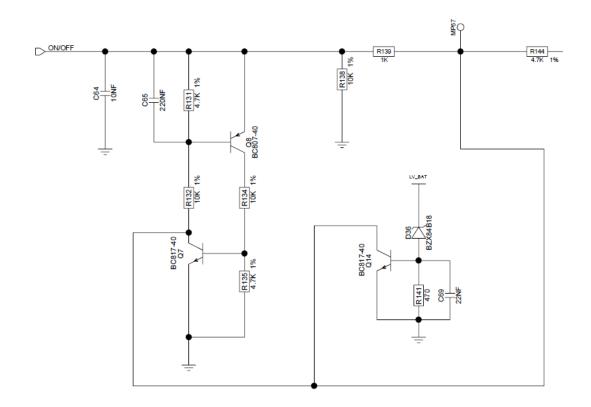

| Figure 3-21. Voltage limitation circuit limiting the LV supply voltage to 15V maximal95                                                                           |

| Figure 3-22. Over voltage protection circuit designed for the LLC converter                                                                                       |

| Figure 3-23. Simulation results for LV supply voltage limiting and over voltage protection . 97                                                                   |

| Figure 4-1. Integration of four LV MOSFETs dies in IML power module (3D model) 100                                                                                |

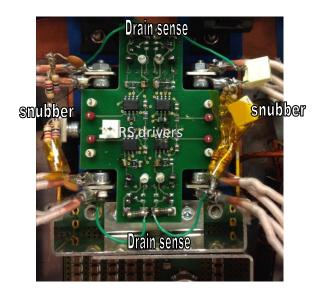

| Figure 4-2. Populated IML power module and its equivalent electrical circuits of the designed power module                                                        |

| Figure 4-3. Thermal resistances of IML power module                                                                                                               |

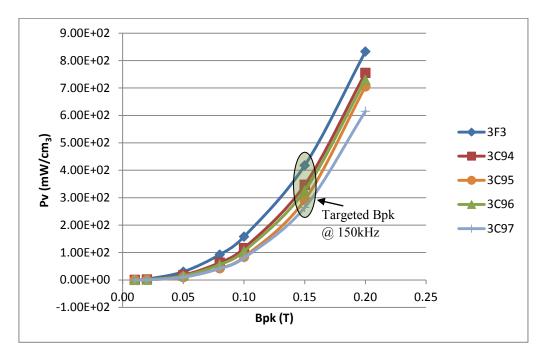

| Figure 4-4. Core loss of different magnetic materials at 100°C, 150 kHz with peak flux density as a parameter                                                     |

| Figure 4-5. Core loss of different magnetic materials at 100°C, 250kHz with peak flux density as a parameter                                                      |

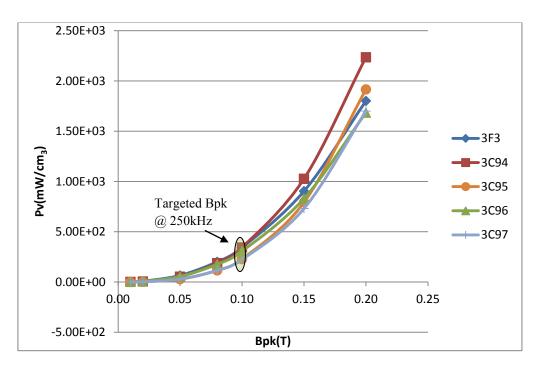

| Figure 4-6. Core loss of different magnetic materials at 150kHz, Bpk=160mT with temperature as a parameter                                                        |

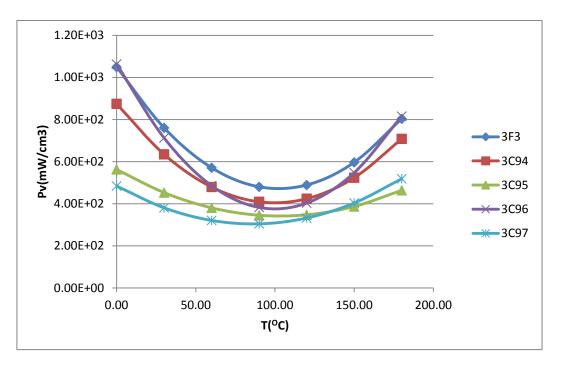

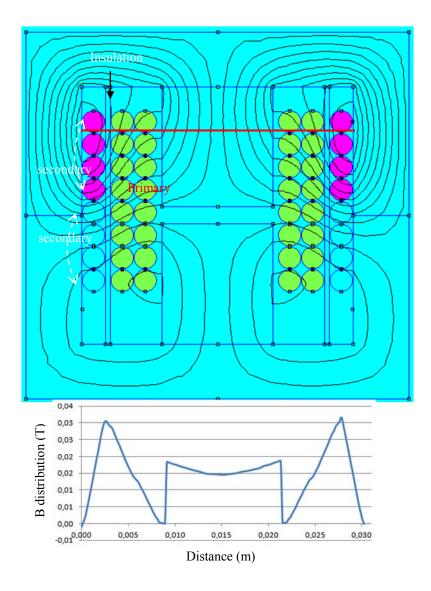

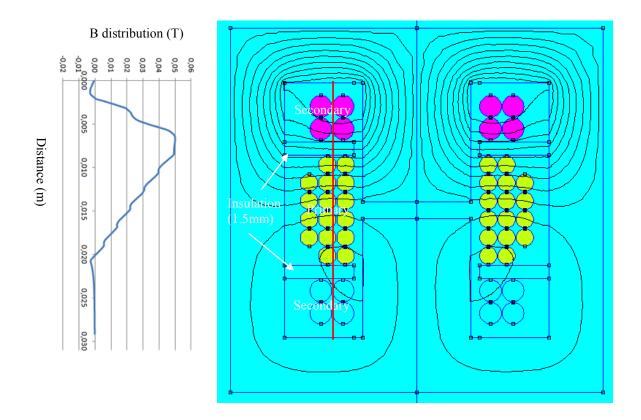

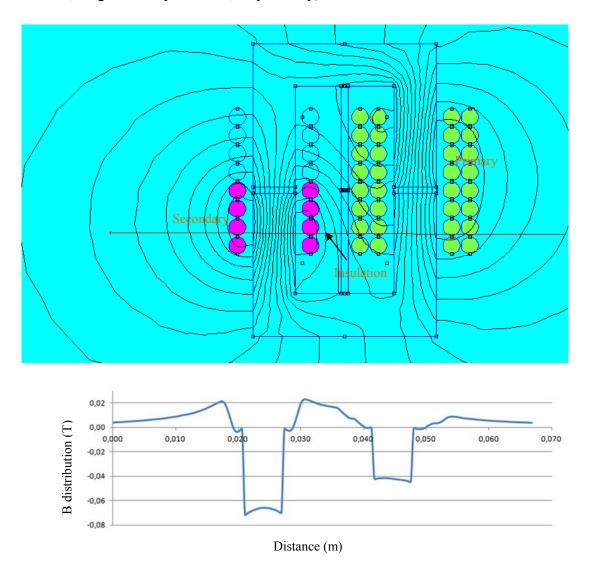

| Figure 4-7. Leakage induction distribution for transformer structure I, <i>lf</i> =320nH 108                                                                      |

| Figure 4-8. Leakage induction distribution for transformer structure II, $l_f=1.5 \mu$ H109                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

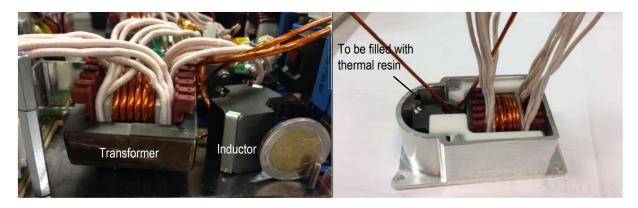

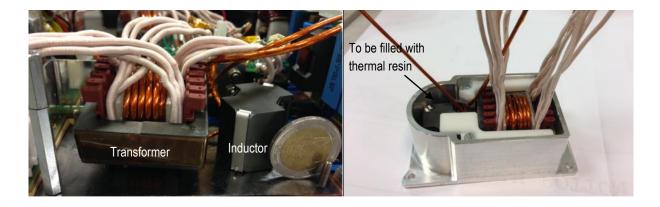

| Figure 4-9. Transformer structure II, with additional resonant inductor RM12 without cooling container (left) and in a cooling container (right) |

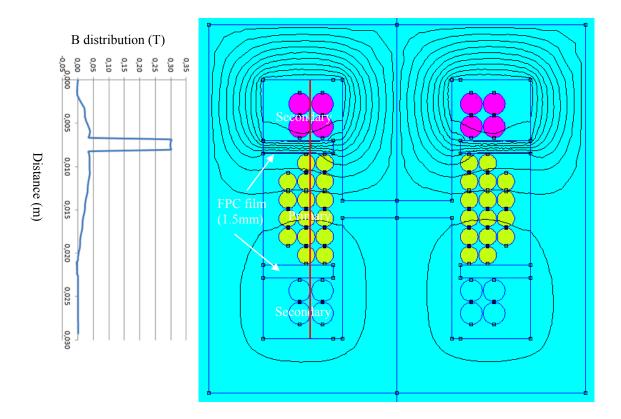

| Figure 4-10. Leakage induction distribution with FPC film insertion, structure III, <i>lf</i> =3.8uH                                             |

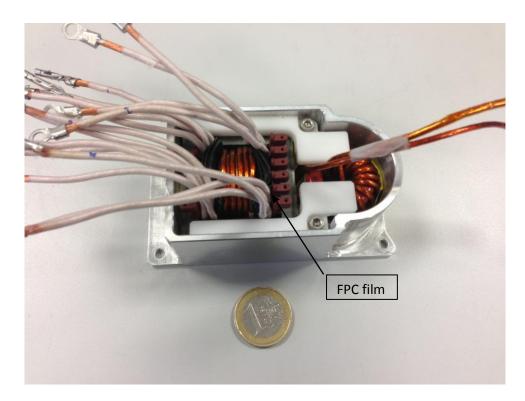

| Figure 4-11. Transformer structure III, with FPC material separating primary and secondary windings                                              |

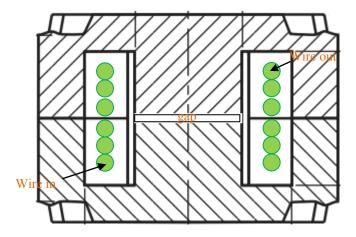

| Figure 4-12. Leakage induction distribution of transformer structure IV, <i>lf</i> =7.5uH112                                                     |

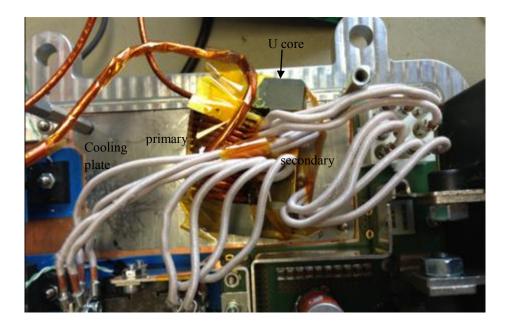

| Figure 4-13. Transformer structure IV mounted at the proto, with U cores integrating the resonant inductor                                       |

| Figure 4-14. Resonant inductor designed in RM12/I core                                                                                           |

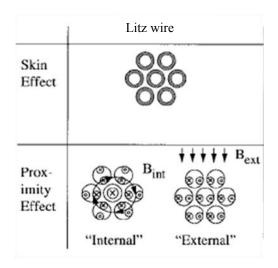

| Figure 4-15. Types of power loss in Litz wire and paralleled wires                                                                               |

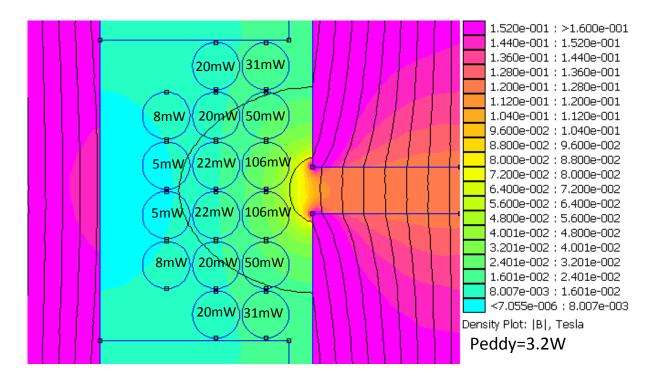

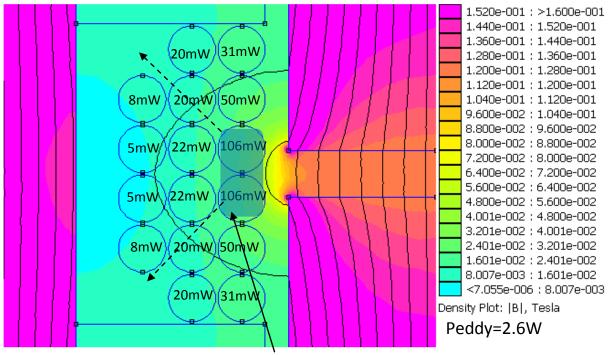

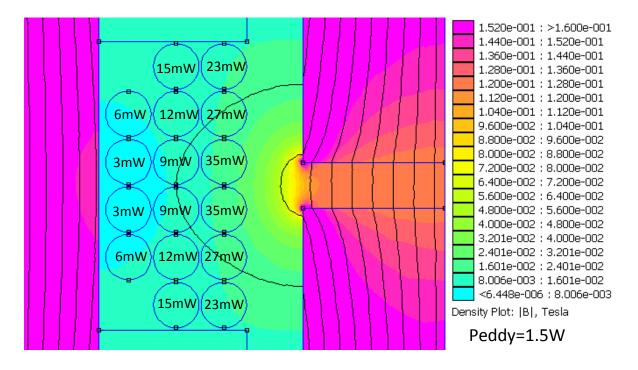

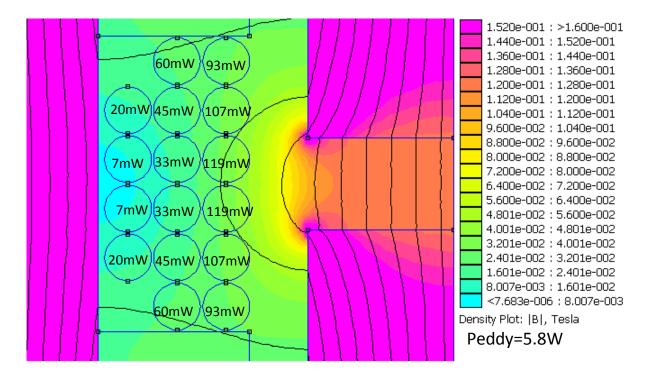

| Figure 4-16. The eddy current loss simulation results for primary windings                                                                       |

| Figure 4-17. Creating a forbidden zone to a get reduced proximity effect                                                                         |

| Figure 4-18. Proposal of shifting the primary winding to get a reduced proximity effect 120                                                      |

| Figure 4-19. Eddy current loss simulation under e=3.96mm for a reduced Lm=24uH 121                                                               |

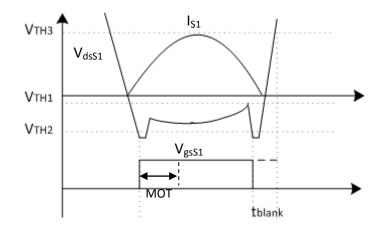

| Figure 4-20. Typical waveform of the LV synchronous rectification in a LLC converter by sensing the drain-source voltage of MOSFET               |

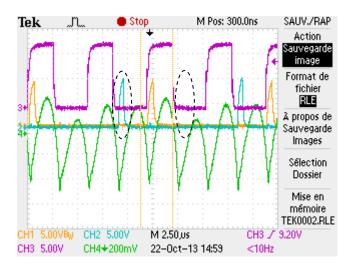

| Figure 4-21. Synchronous rectification error at the fault switching-off timing (CH1:VgsS1, CH2: VgsS2, CH3: Vgs_QL, CH4: Is2+Is1)                |

| Figure 4-22. Proposed drain-source measurement method to improve the SR robustness 124                                                           |

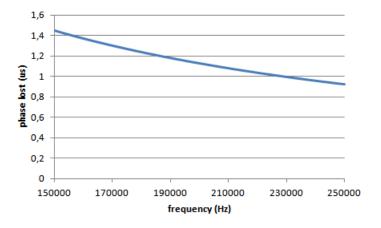

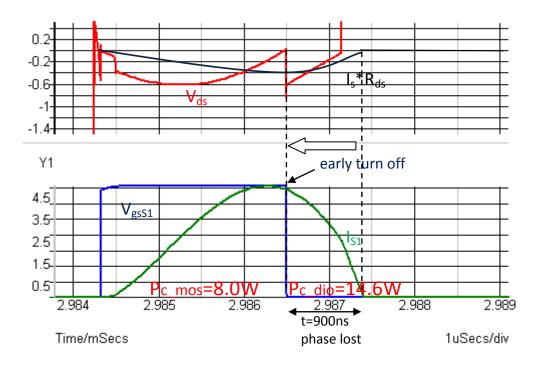

| Figure 4-23. Calculated phase lost for applied LV MOSFETs Vds voltage measurement 125                                                            |

| Figure 4-24. SR phase lost results of MOSFETs at nominal power, <i>f</i> =153kHz 126                                                             |

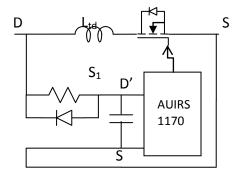

| Figure 4-25. Proposed phase compensation scheme                                                                                                  |

| Figure 4-26. Phase compensation results by using $R=150\Omega$ , $C=4.7nF$                                                                       |

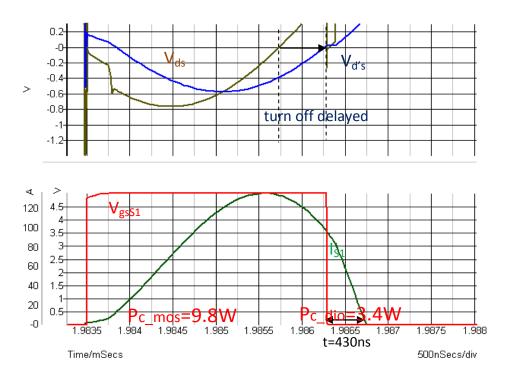

| Figure 4-27. Phase compensation results by using $R=220\Omega$ , $C=4.7nF$                                                                       |

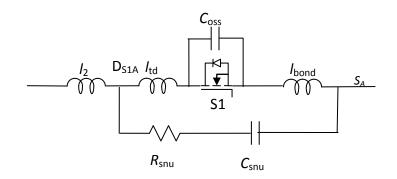

| Figure 4-28. Proposed Snubber circuit to reduce the voltage spike (for switch S1)                                                                |

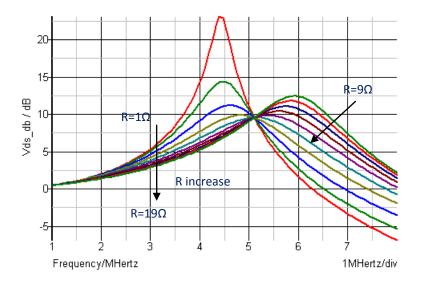

| Figure 4-29. Damping characteristics by trying different resistance values                                                                       |

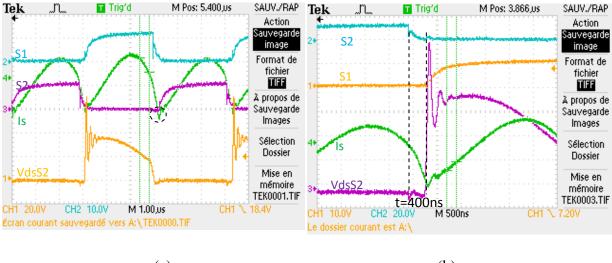

| Figure 4-30. Phase compensated secondary waveforms without (a) and with snubber (b) (Vin= 330V, Iout=80A)                                        |

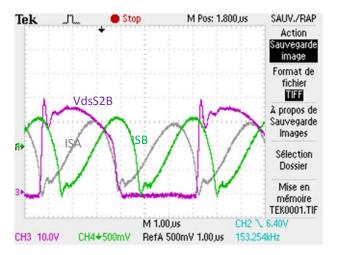

| Figure 4-31. Current sharing result at Iout=40A, IA=IB=20A, Vin=330V                                                                             |

| Figure 4-32. Practical ameliorations by a dedicated PCB board directly on the power module                                                       |

| Figure 4-33. Insertion of a vapor chamber into the base of the heat sink for cooling                                                             |

| Figure 4-34. Principles of vapor chambers for heat spreading                                                                 | 134       |

|------------------------------------------------------------------------------------------------------------------------------|-----------|

| Figure 4-35. Experiment and simulation set-up for vapor chamber study                                                        | 135       |

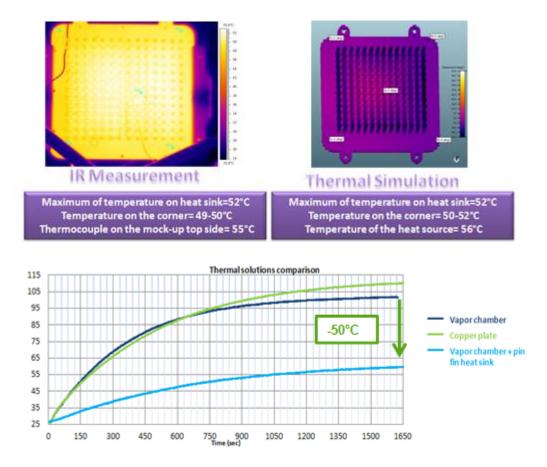

| Figure 4-36. Experimental and simulation results for vapor chamber study                                                     | 135       |

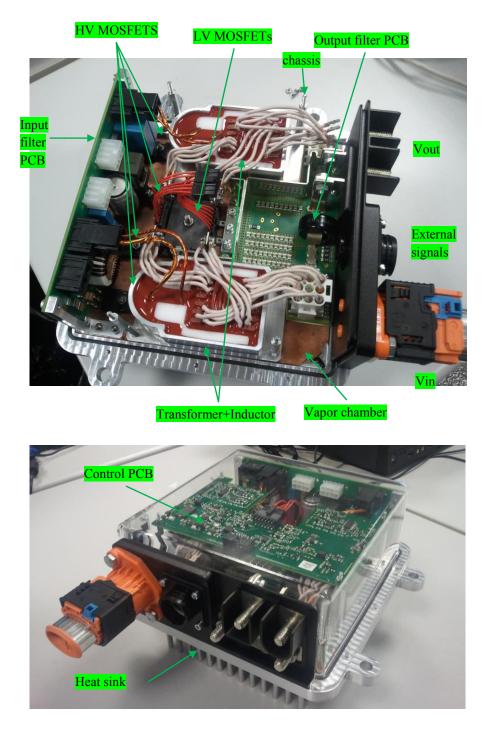

| Figure 4-37. Prototype assembly of LLC converter, power density 1W/cm3                                                       | 137       |

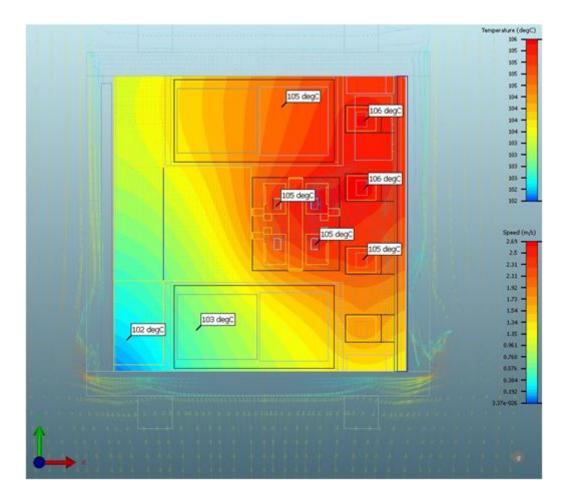

| Figure 4-38. Simulation results of temperature rise at nominal power with a forced air-<br>convection 1.5m/s at ambient 70°C | 139       |

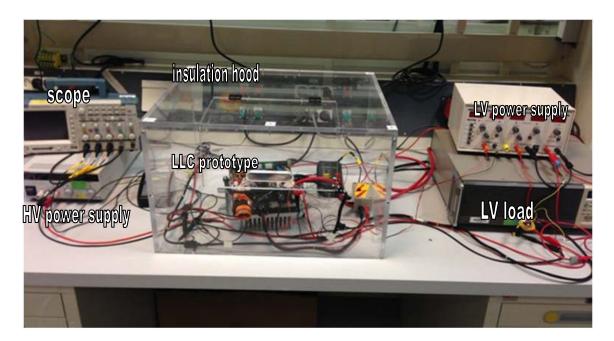

| Figure 4-39. Test bench of designed LLC converter prototype                                                                  | 140       |

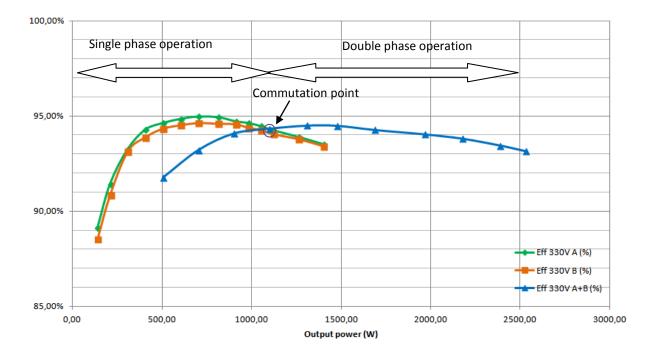

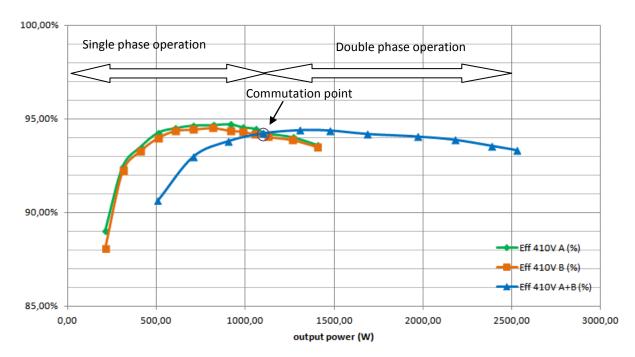

| Figure 4-40. Measured efficiency result for Vin=330V                                                                         | 141       |

| Figure 4-41. Measured efficiency result for Vin=410V                                                                         | 142       |

| Figure 4-42. An efficiency comparison of single stage LLC and double stage BOOST+LI                                          |           |

| Figure 5-1. Two different ways of arranging the LLC power cell                                                               | 148       |

| Figure 5-2. Circulating ac current from the phase (a) to phase (b) and a model for beat frequency analysis                   | 150       |

| Figure 5-3. Illustration of beat frequency at low frequency domain of double cell LLC                                        | 151       |

| Figure 5-4. Superposition of two output currents in frequency domain                                                         | 152       |

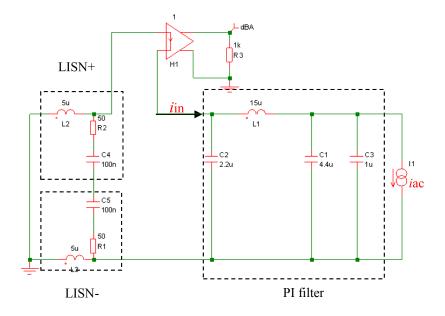

| Figure 5-5. Basic topology of PI filter as input filter for DM noise filtering                                               | 153       |

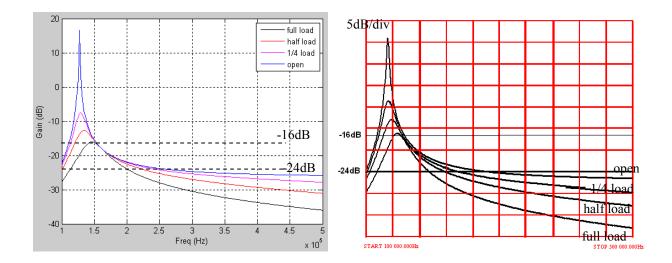

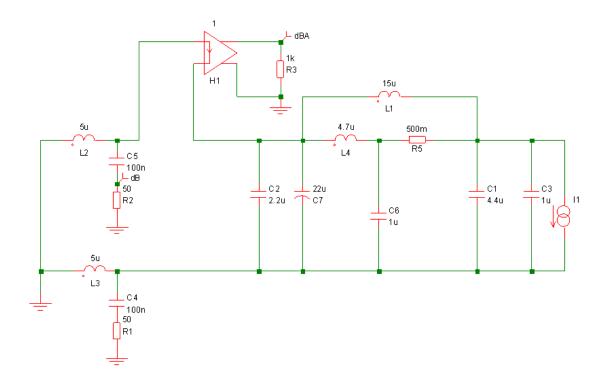

| Figure 5-6. Damped version of proposed PI filter                                                                             | 154       |

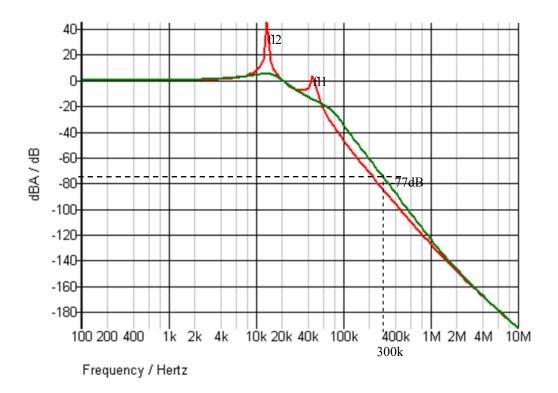

| Figure 5-7. Filter's gain before (red) and after (green) damping                                                             | 155       |

| Figure 5-8. PCB board design of input filter                                                                                 | 155       |

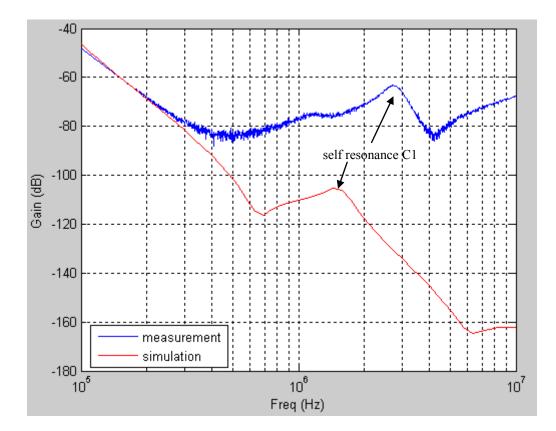

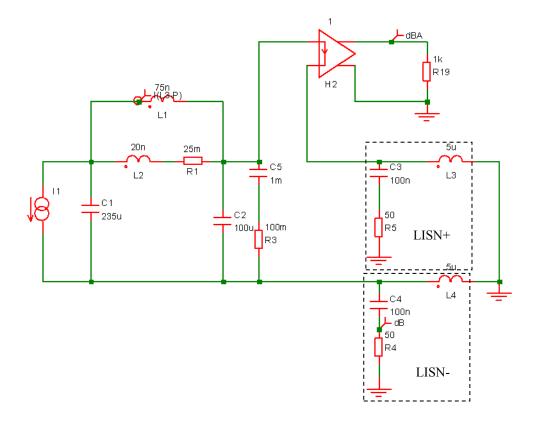

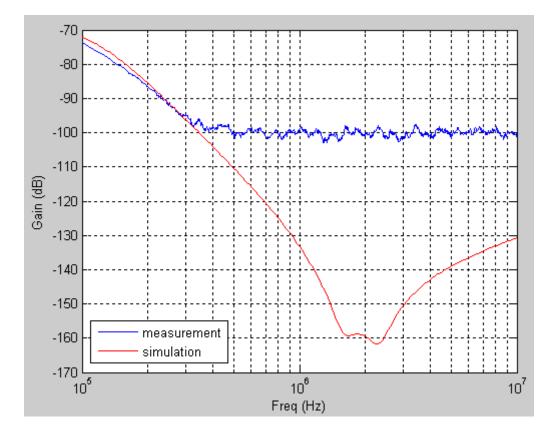

| Figure 5-9. Simulation results considering components parasite and experimental results input filter                         | of<br>156 |

| Figure 5-10. Proposed PI filter as output filter                                                                             | 157       |

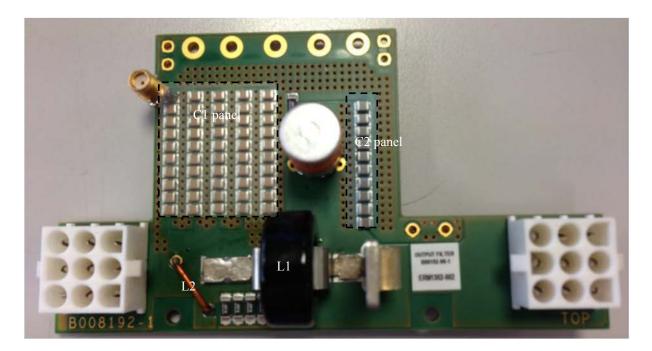

| Figure 5-11. PCB board design of the output filter                                                                           | 158       |

| Figure 5-12. Simulation results considering components parasite and experimental results output filter                       |           |

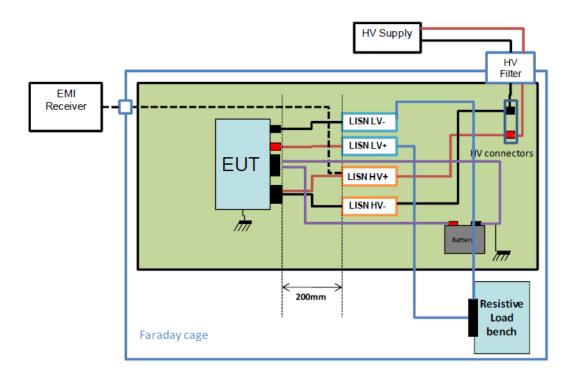

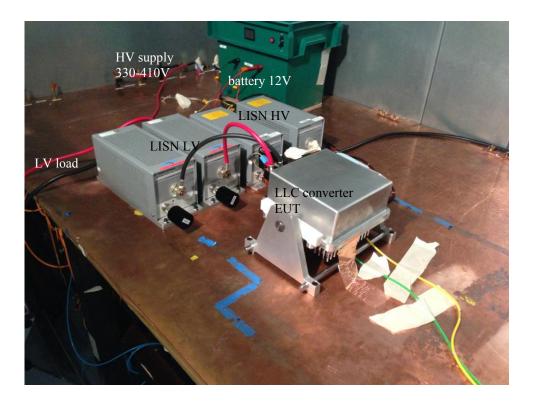

| Figure 5-13. EMC measurement set up and its pictures                                                                         | 159       |

| Figure 5-14. EMC conducted emission measurement at LISN LV (AVG detector, Vin=4)                                             |           |

| Figure 5-15. EMC measurement for low frequency at LISN LV+ (AVG detector, Vin=41                                             |           |

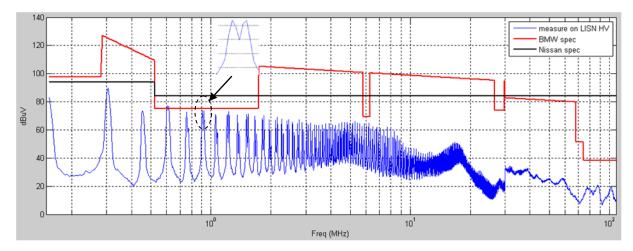

| Figure 5-16. EMC conducted emission measurement at LISN HV+ (AVG detector, Vin=330V)                                         |           |

# List of Tables

| Table 1-1: Objective specifications of the DCDC converter project                                                        |

|--------------------------------------------------------------------------------------------------------------------------|

| Table 2-1. Parameter dimensioning comparison results for 2.5kW and 1.25kW LLC resonantconverters, Vin=220-410V, Vout=14V |

| Table 2-2. Comparison of different selections of Lm with loss predicted for Vin=220V, one cell         61                |

| Table 3-1. Current dissymmetry simulation results between two different power cells                                      |

| Table 4-1. A comparison of available magnetic materials for core construction                                            |

| Table 4-2. Transformer design summary by structure II                                                                    |

| Table 4-3. Resonant Inductor design summary                                                                              |

| Table 4-4. Experimental results of the cooling system's thermal characteristics with the prototype                       |

| Table 4-5. Calculated loss breakdown of the designed LLC converter at 800W, Vin=330V (single cell operation)             |

| Table 4-6. Calculated loss breakdown of the designed LLC converter at 2.5kW, Vin=330V         (Double cell operation)    |

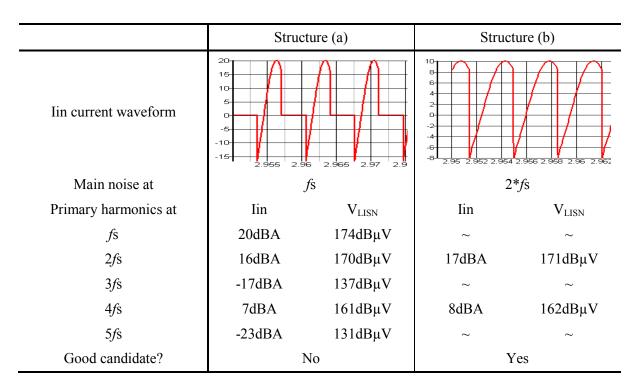

| Table 5-1. Comparison of conducted emissions for circuit structure (a) and (b)                                           |

| Table 5-2. Conducted emissions for at the secondary sides                                                                |

### RESUME

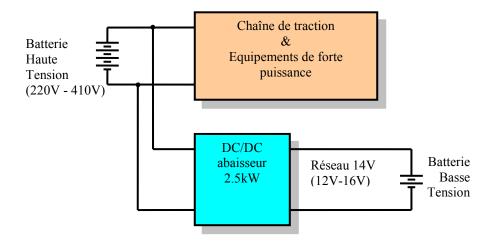

La principale source d'alimentation des futurs véhicules électriques sera généralement une batterie haute tension, de tension comprise entre 220V et 410V. Elle permettra essentiellement le pilotage de la chaîne de traction. Le choix d'une tension de batterie beaucoup plus élevée qu'actuellement s'explique par la puissance électrique à fournir (entre 15kW et 100kW selon le type de véhicule) et l'autonomie recherchée (variant de 100km à 400km selon les cahiers des charges). Pour des problèmes liés à la sécurité des personnes, ce réseau HT sera confiné dans une partie du véhicule et limité aux équipements de traction ou de forte puissance. En ce qui concerne les autres fonctions à assurer dans le véhicule, l'alimentation se fera via le réseau BT classique 14V (variant entre 12V et 16V).

Figure R-1. Chaine de traction électrique dans un véhicule électrique ou hybride

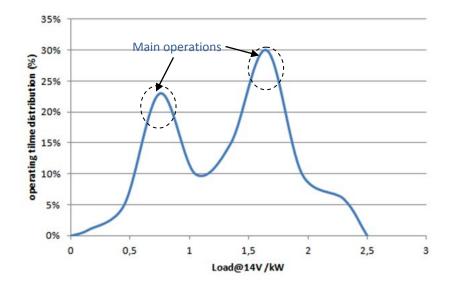

Tous les véhicules électriques (ou hybrides) seront équipés d'un convertisseur DC/DC abaisseur générant une tension 14V à partir de la batterie haute tension (figure R-1). Une seconde batterie 14V sera également connectée sur ce réseau pour les phases de démarrage, d'arrêt et de diagnostique (la batterie haute tension n'étant pas activée durant ces phases). Il est important d'innover pour la réalisation de cette fonction afin d'optimiser le rendement, le volume et les performances. Dans les véhicules électriques/hybrides, ce convertisseur DC/DC doit pouvoir fonctionner à n'importe quelle puissance, de 0 à 2.5kW. Cependant, il y a deux gammes de puissance particulièrement utilisées : 600-900W et 1,5k-1,8kW. Assurer un rendement de conversion plus élevé dans ces deux domaines de puissance est très important afin d'améliorer les performances globales du convertisseur.

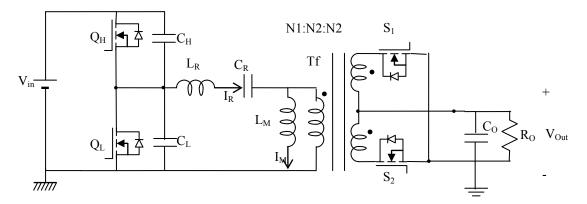

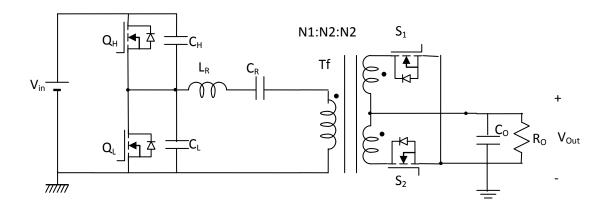

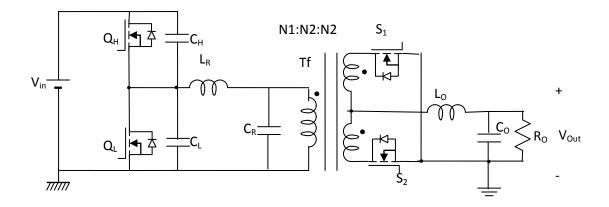

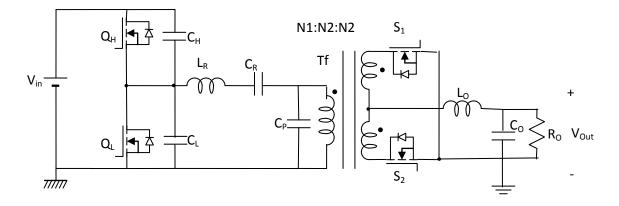

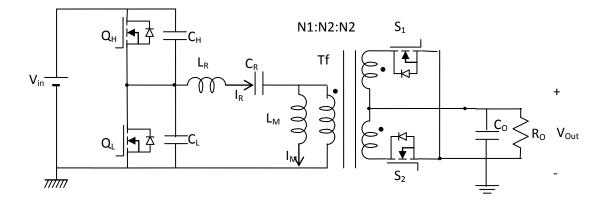

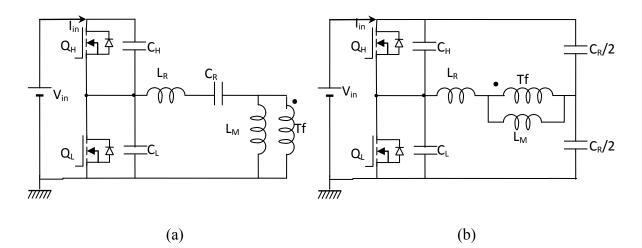

Le convertisseur LLC, dont la topologie est présentée à la figure R-2, se développe rapidement à l'heure actuelle dans les systèmes de conversion d'énergie de type 'front-end'. Le convertisseur LLC permet de réaliser des commutations à zéro de tension (ZVS) au niveau des interrupteurs primaires et des commutations à zéro de courant (ZCS) au niveau des interrupteurs secondaires. Cela permet d'augmenter beaucoup la fréquence de découpage par rapport à celle des convertisseurs MLI (PWM) traditionnels. Le circuit résonnant comprend deux inductances et un condensateur. L'inductance de magnétisation du transformateur peut être utilisée pour réaliser l'inductance Lm. De la même façon, l'inductance de fuite du transformateur est utilisable pour réaliser totalement ou partiellement l'inductance de résonance. Le volume global des composants magnétiques peut être donc réduit, ce qui présente un très grand avantage du convertisseur LLC par rapport à d'autres types de convertisseurs.

Figure R-2. Convertisseur LLC en forme de demi-pont avec redressement synchrone

#### **Etude théorique :**

Le choix d'un convertisseur à résonance LLC lors de la conception des alimentations DC/DC de puissance faible ou moyenne, dans les applications HT/BT, se traduit généralement par un très bon rendement. En général, les convertisseurs LLC mentionnés dans les publications sont de puissance inférieure à 1kW, souvent comprise entre 300W et 1kW. Une puissance supérieure mène à deux difficultés majeures :

Le premier problème réside dans la réalisation du transformateur. L'inductance magnétisante du transformateur nécessaire dans le circuit LLC est proportionnelle à la résistance de charge. Pour le convertisseur LLC de 2,5 kW, la charge équivalente est de  $80m\Omega$ . La valeur Lm requise est trop basse pour être réalisée en utilisant classiquement un noyau magnétique à entrefer. L'entrefer serait en effet beaucoup trop large, ce qui entrainerait notamment un flux

de fuite important vers les enroulements et donc des pertes supplémentaires par courants de Foucault. En comparaison pour un convertisseur LLC de puissance moitié, soit 1.25kW, l'inductance de magnétisation du transformateur requise est doublée et la largeur d'entrefer devient plus raisonnable.

La deuxième difficulté est l'augmentation très rapide des pertes par conduction dans les semiconducteurs et dans le transformateur en fonction de la puissance du convertisseur. Le courant efficace dans les MOSFETs primaires et secondaires d'un convertisseur LLC de 2,5 kW est deux fois plus élevé que dans un convertisseur LLC de 1.25kW. Afin de réduire les pertes globales par conduction, plusieurs transistors MOSFET doivent être connectés en parallèle. La section des enroulements du transformateur devant également être augmentée, il en résulte un volume supérieur de circuit magnétique, ce qui rend encore plus difficile d'obtenir une faible inductance magnétisante.

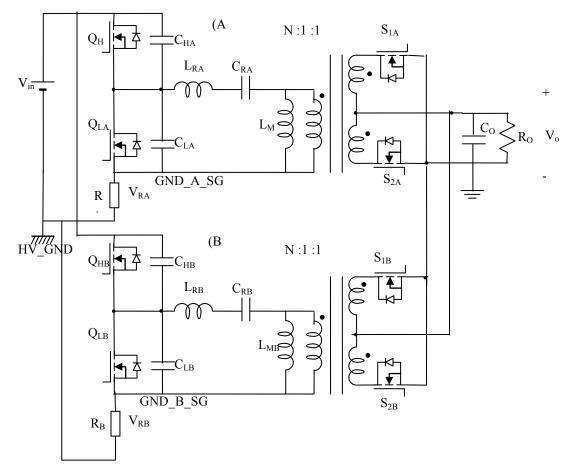

Nous avons retenu le convertisseur de type LLC compte tenu de ses caractéristiques intéressantes pour l'application visée. Cependant, pour pallier aux problèmes dus à l'augmentation de puissance, il est intéressant de réaliser le convertisseur sous la forme de plusieurs modules LLC fonctionnant en parallèle et se partageant le courant total. Nous avons opté pour l'utilisation de deux modules.

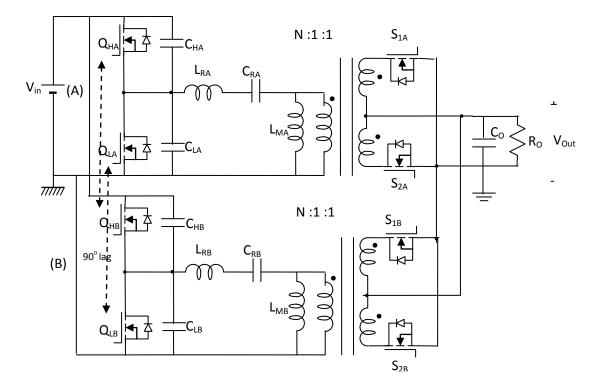

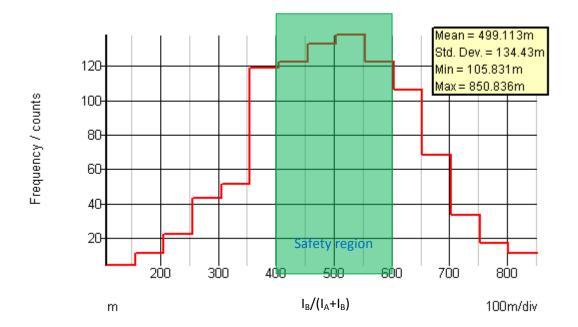

Le convertisseur LLC à deux cellules entrelacées, connectées en parallèle au primaire comme au secondaire est connu d'après la bibliographie comme un bon candidat pour gérer la forte puissance. Les principes décrits dans les publications font état de deux modules fonctionnant simultanément à une même fréquence. Les deux modules sont commandés par un même contrôleur imposant un déphasage de 90° entre eux de manière à minimiser le contenu harmonique des courants d'entrée et de sortie du convertisseur global. Cela fonctionne parfaitement si les deux circuits résonnants sont identiques. Cependant, la dispersion des valeurs de composants entraîne une répartition aléatoire de courant entre les deux cellules.

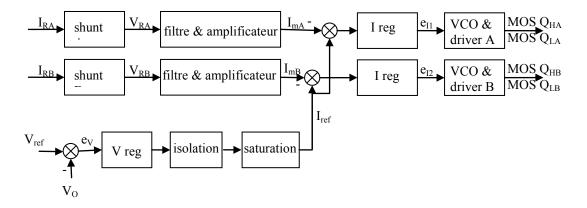

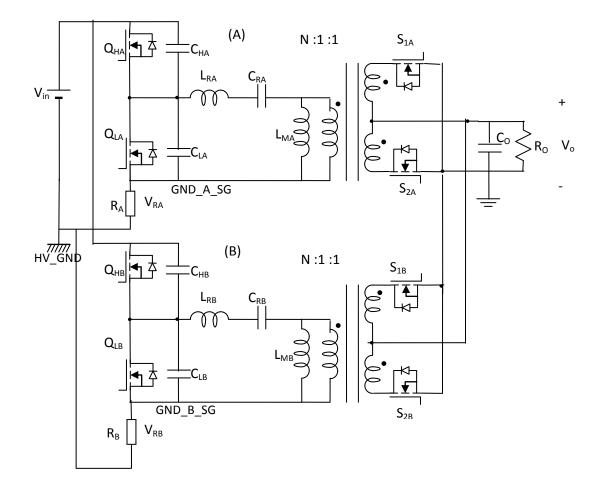

Afin d'équilibrer correctement les transferts d'énergie entre les deux modules et de leur faire partager équitablement les contraintes, notamment les pertes, nous proposons dans cette thèse une autre solution pour commander ce convertisseur LLC parallèle-parallèle. La nouvelle méthode de contrôle fait appel à deux boucles de régulation : une boucle externe pour la tension de sortie et une boucle interne pour le courant d'entrée. L'équilibrage de courant entre les deux modules en parallèle est assuré en contrôlant le courant d'entrée de chaque cellule. La mesure des courants d'entrée est assurée par un shunt résistif pour raison de simplicité. La

figure R-3 montre le convertisseur LLC proposé à double phase et avec les deux capteurs de courant RA et RB à l'entrée de chaque cellule. Le capteur de courant est placé entre la cellule de puissance et la masse primaire de manière à ce que la mesure de courant ne soit pas flottante.

Figure R-3. Convertisseur LLC à double phase proposé avec capteurs de courant

Figure R-4. Schéma-bloc du circuit de commande pour équilibrer les courants entre les deux modules LLC du convertisseur

Le schéma-bloc du circuit de commande proposé pour équilibrer les courants entre modules, adapté au convertisseur LLC à double phase, est présenté à la figure-R4. Le shunt RA de la cellule de puissance A et le shunt R<sub>B</sub> de la cellule de puissance B renvoient les signaux de courant d'entrée sous forme de tensions distinctes V<sub>RA</sub> et V<sub>RB</sub>. Après filtrage et amplification à un niveau approprié, ces signaux sont notés  $I_{mA}$  et  $I_{mB}$ . Ils reflètent les valeurs moyennes des courants en entrée de chaque cellule. Le filtre réalise une caractéristique de type passe-bas avec une forte atténuation dans la gamme de fréquence opérationnelle du convertisseur. En ce qui concerne la boucle externe de régulation de la tension de sortie, celle-ci est comparée à la tension de référence, puis l'erreur de comparaison  $e_V$  est soumise à un régulateur de tension du type PI. La régulation de tension fournit la référence de courant I<sub>ref</sub>, unique pour les deux cellules de puissance. Cette référence I<sub>ref</sub> doit être isolée de la partie BT et limitée à une certaine valeur pour éviter toute surintensité. Les images I<sub>mA</sub> et I<sub>mB</sub> des courants sont asservis à la référence I<sub>ref</sub> par le régulateur de courant respectif à chaque cellule. C'est ainsi que l'équilibrage des courants d'entrée entre les deux cellules de puissance peut être assuré. Les signaux e<sub>11</sub> et e<sub>12</sub> sont envoyés à deux oscillateurs (des oscillateurs contrôlés en tension de type VCO ou des oscillateurs contrôlés en courant de type ICO). Des drivers permettent de commander correctement les MOSFETs du demi-pont.

Il est important de remarquer que les deux convertisseurs fonctionnent ainsi à deux fréquences légèrement différentes afin de maintenir le même ratio de conversion de tension. La différence de fréquences provient de la dispersion des valeurs de composants dans les deux circuits résonnants. L'analyse des conséquences de cette double fréquence de découpage fait partie de cette thèse.

Le logiciel Simplis est utilisé pour étudier la fonction de transfert du convertisseur LLC et désigner les paramètres des régulations. La modèle dynamique du convertisseur à résonance en régime de faible amplitude est difficile à obtenir par la méthode de l'état moyenné. Le logiciel Simplis intègre une analyse périodique du point de fonctionnement (POP analysis) qui permet de déterminer la fonction de transfert du convertisseur LLC sans établir son modèle à faible signal. Grâce aux résultats obtenus par simulation, nous avons pu déterminer les paramètres de régulation pour obtenir un système rapide, stable et précis, comme l'atteste la figure R-5.

Figure R-5. Diagramme de Bode de la fonction de transfert en boucle ouverte non corrigée (NC) et corrigée (C) à P=1250W et Vin=330V pour la boucle interne de courant

Pour la boucle de courant, après correction, la bande passante obtenue est de 3kHz, avec une marge de phase de 83° et une marge de gain de 8dB. La même simulation est faite pour la boucle externe de tension, avec les résultats de la figure R-6.

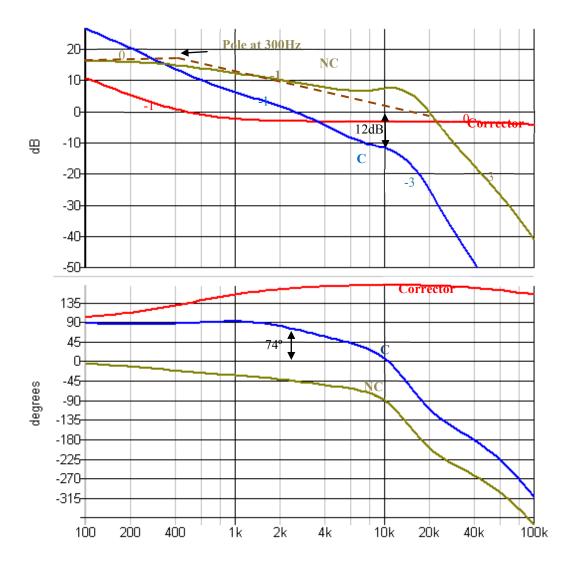

Figure R-6. Diagramme de bode de la fonction de transfert en boucle ouverte non corrigée (NC) et corrigée (C) à P=1250W et Vin=330V pour la boucle externe de tension

Pour le boucle de tension, après correction, la bande passante obtenue est de 2.5kHz, avec une marge de phase de 74° et une marge de gain de 12dB.

En outre, le convertisseur de LLC est capable de réaliser la fonction de démarrage progressif (soft-start), la protection en cas de surcharge ou de court-circuit, la protection en cas de surtension...

Concernant le dimensionnement du circuit LLC, afin d'obtenir une grande plage de variation de tension en entrée avec une plage de fréquence de fonctionnement limitée, une faible valeur est nécessaire pour l'inductance Lm. À cause de cette faible inductance, le courant de magnétisation est important en regard du courant de résonance, ce qui tend à dégrader le rendement global. Le moyen le plus efficace pour améliorer le facteur de puissance des bras

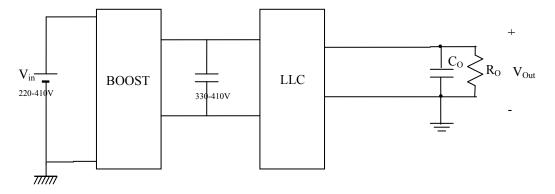

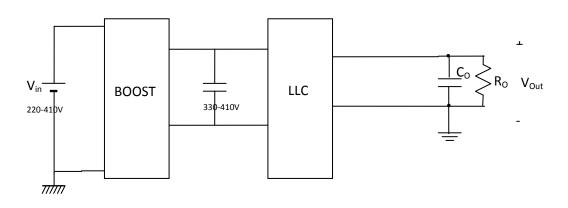

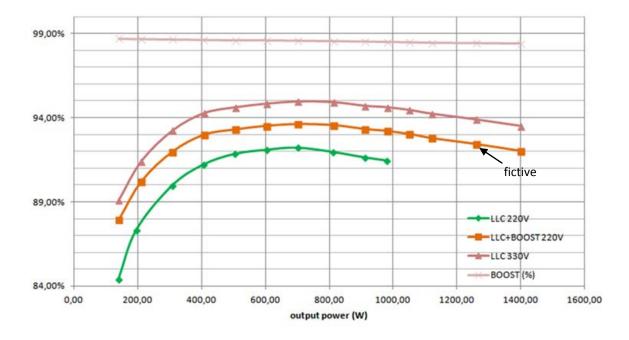

de pont est d'augmenter le plus possible l'inductance magnétisante Lm. Cependant, la plage de variation de tension en entrée doit alors être réduite. En particulier, une inductance Lm trop forte abaisse trop le gain statique du convertisseur et le rend inapte à fonctionner sous la tension minimale de 220 V en entrée. En conséquence, un convertisseur de type BOOST doit alors être placé en amont du convertisseur LLC, comme à la figure R-7.

Figure R-7. Double étage LLC+BOOST pour améliorer le rendement global

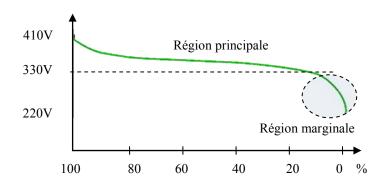

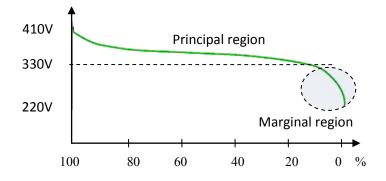

Comme indiqué sur la figure R-7, la plage de variation de la tension en entrée du convertisseur LLC est réduite à 330-410V. Pour une tension en entrée du système global Vin inférieure à 330 V, le convertisseur BOOST est activé pour augmenter la tension jusque vers 330V. Pour Vin supérieure à 330 V, le convertisseur BOOST est désactivé de manière à appliquer directement la tension d'entrée au convertisseur LLC (seule la diode du BOOST conduit alors). La limite de 330 V est choisie en fonction des caractéristiques de charge de la batterie dans les véhicules électriques (figure R-8).

Figure R-8. Etat de charge d'une batterie au lithium-ion dans les véhicules électriques

D'après la figure R-8, la plage de fonctionnement de [220V 330V] correspond en fait à un domaine de fonctionnement marginal du convertisseur. Ainsi, la plupart du temps, le

convertisseur BOOST n'est pas activé. La comparaison des performances, avec et sans BOOST, fait partie de cette thèse. C'est ainsi que le BOOST permet d'augmenter le rendement global d'au moins 2% dans la gamme de tension [330V 410V] et d'au moins 1% dans la gamme [220V 330V]. Durant la thèse, les travaux ont porté essentiellement sur la conception du convertisseur LLC, ce qui a permis de réaliser et d'optimiser un prototype toutefois sans BOOST.

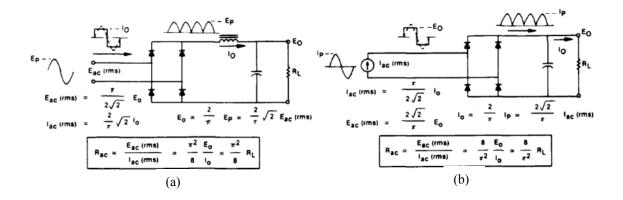

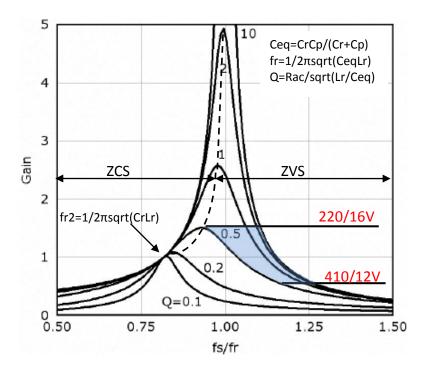

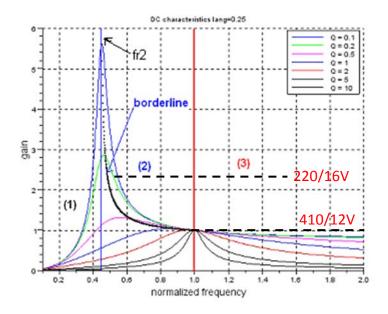

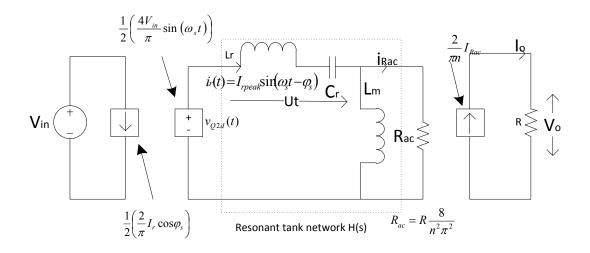

L'approximation dite « du premier harmonique » (FHA) est une méthode simplifiée permettant d'analyser beaucoup de convertisseurs à résonance. Elle permet en particulier d'établir le circuit électrique équivalent d'un convertisseur LLC en approchant les formes de courant et de tension par une forme sinusoïdale tout en négligeant les effets des autres harmoniques d'ordre plus élevé. Dans l'analyse traditionnelle du convertisseur LLC, l'effet de l'inductance de fuite partielle au secondaire du transformateur (et de l'inductance de câblage secondaire) est négligé. Toutefois, à fréquence suffisamment élevée et en cas de fort courant et faible tension en sortie, l'impédance de cette inductance parasite devient non négligeable devant la charge nominale :  $l_2=120$ nH, soit 116m $\Omega$  à 150kHz, comparable à la charge de 160m $\Omega$ . Son effet doit être donc pris en compte dans la conception et le dimensionnement du convertisseur. La figure R-9 représente les circuits équivalents d'une cellule de résonance LLC idéalisée et d'une cellule comprenant l'inductance parasite précédente.

Figure R-9. Les circuits équivalents d'une cellule de résonance LLC idéalisée et d'une cellule avec l'inductance parasite ramenée au primaire

L'étude analytique par la méthode du premier harmonique d'un convertisseur LLC doté d'une cellule de résonance idéale (figure R-9(1)) mène à un ratio de conversion normalisé donné par la relation R-1 :

$$G = \frac{1}{\left(1 + \lambda - \lambda \frac{1}{f_n^2}\right) + jQ\left(f_n - \frac{1}{f_n}\right)}$$

(R-1)

Dans cette expression :  $Q = \frac{\sqrt{L_r/C_r}}{R_{ac}}$  est le facteur de qualité ;  $f_n = \frac{f_s}{f_r}$  est la fréquence de

découpage normalisée;  $f_r = \frac{1}{2\pi\sqrt{L_r C_r}}$  est la fréquence de résonance principale;

$$f_{r2} = \frac{1}{2\pi\sqrt{(L_r + L_m)C_r}}$$

est la fréquence de résonance secondaire ;  $\lambda = \frac{L_r}{L_m}$  est le ratio entre

l'inductance de résonance et l'inductance magnétisante.

En considérant l'effet de l'inductance de fuite secondaire avec  $L_2 = \frac{l_2}{n^2}$ , le ratio de conversion normalisé du convertisseur LLC est donné par la relation R-2 :

$$G = \frac{1}{\left(1 + \lambda - \lambda \frac{1}{f_n^2}\right) + jQ\left(\left(\frac{L_2}{L_m}\left(1 + \frac{1}{\lambda}\right) + 1\right)f_n - \left(\frac{L_2}{L_m} + 1\right)\frac{1}{f_n}\right)}$$

(R-2)

La figure R-10 montre la différence entre les deux ratios.

Figure R-10. Caractéristiques des cellules LLC idéale (Lr=7.5uH, Cr=50nF, Lm=42 $\mu$ H) et non-idéale (avec  $l_2$ =120nH)

Plusieurs conclusions relatives à la présence de L<sub>2</sub> peuvent être tirées de ce qui précède :

(1) En l'absence de charge, Q = 0, le gain reste le même que dans le convertisseur LLC idéal. (2) La fréquence de résonance principale ne correspond plus à un gain indépendant de la charge. Le gain à la fréquence de résonnance est toujours inférieur ou égale à 1.

(3) Le point indépendant de la charge est déplacé vers une fréquence inférieure

$$f_{ind} = \frac{1}{2\pi\sqrt{C_r(L_r + L_m//L_2)}}, \text{ avec un gain supérieur à 1, } G_{f=find} = \frac{L_m + L_2}{L_m}$$

(4) Pour une même valeur de Q, le taux de conversion maximal est augmenté.

En conclusion, le dimensionnement des deux modules LLC doit prendre en compte toutes les inductances de fuite partielles du transformateur et les inductances de câblage. Comme indiqué sur la figure R-10, le convertisseur LLC est conçu pour fonctionner avec une tension d'entrée de 330-410V et une tension de sortie 12-16V. La fréquence de fonctionnement est alors comprise entre 150 kHz et 260kHz. Toutefois, afin de simplifier les tests du prototype, la tension de sortie a été régulée à une valeur constante de 14 V en présence d'une charge purement résistive, variable dans de grandes proportions (0 à 2.5 kW).

#### Réalisation pratique et expérimentation

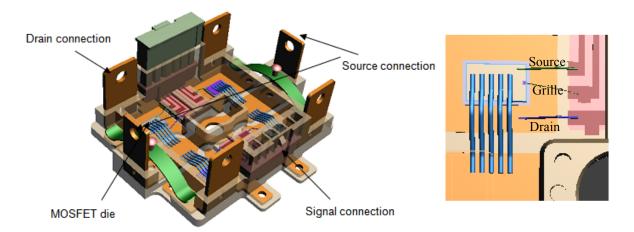

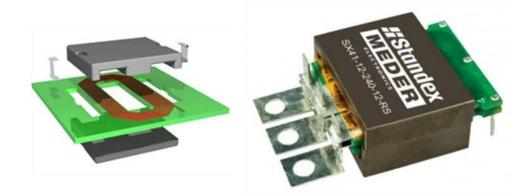

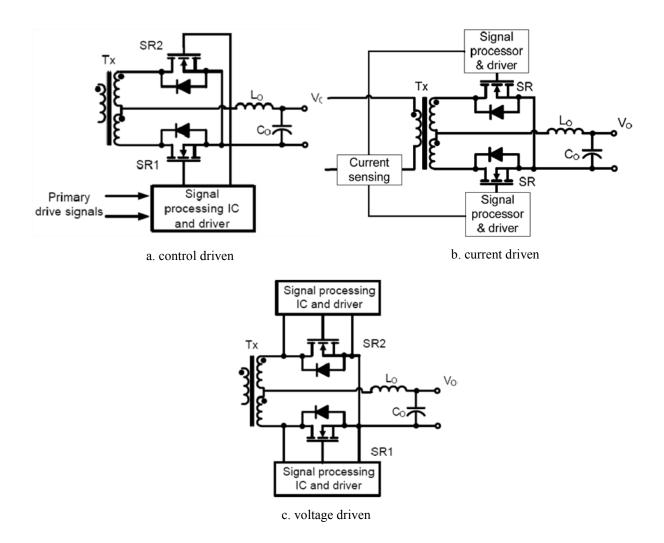

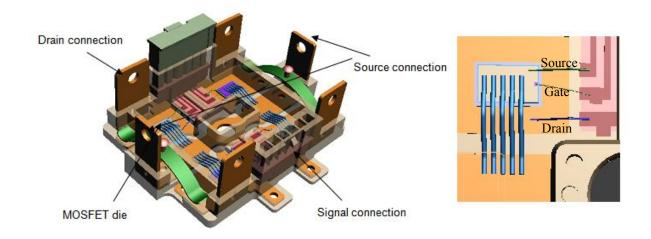

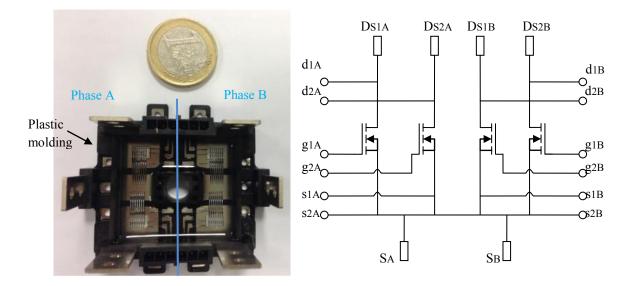

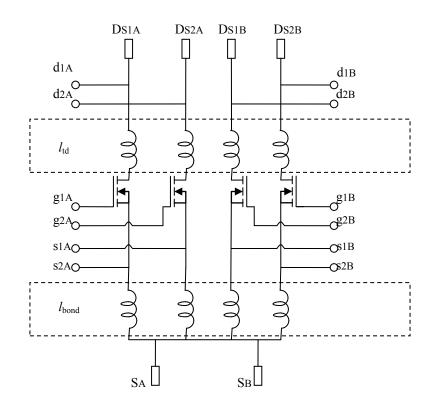

Un point critique concerne les pertes énergétiques dans la partie secondaire, notamment dans les MOSFETs des redresseurs synchrones, à cause du courant de sortie très intense sous basse tension. Les MOSFETs standards, sous forme d'éléments discrets, sont difficiles à utiliser ici en raison de leur conductivité thermique limitée et de leur résistance d'interconnexion. Plusieurs MOSFETs devraient être connectés en parallèle afin de résoudre ce problème, ce qui augmenterait le nombre global de semi-conducteurs et l'encombrement global. Nous avons plutôt opté pour un module de puissance dédié intégrant tous les MOSFETs BT.

Figure R-11. Intégration des 4 MOSFETs BT « nus » dans le module de puissance IML

Dans le cadre de notre projet, un module de puissance du type 'lead-frame inséré surmoulé (IML) a été conçu. Il est représenté à la figure R-11. Les lead-frames sont insérés dans une pièce moulée en matière plastique qui présente des zones ouvertes horizontales dans lesquelles les puces nues de MOSFETs sont brasées. Les lead-frames supportent donc les

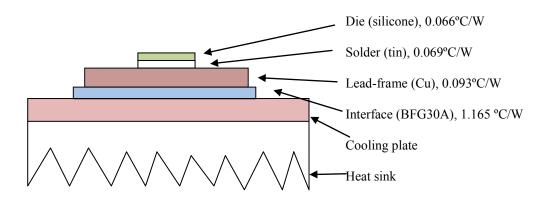

puces, et s'étendant aussi vers l'extérieur, ils forment également les bornes de connexion électrique. Le module de puissance conçu est composé de quatre puces nues formant une configuration à double phase. Les quatre sources des puces sont connectées ensemble (voir la figure R-3) et vers le lead-frame par des liaisons  $5x500\mu$ m. Afin d'effectuer la rectification synchrone, les connexions de signal sont réalisées par les liaisons  $125\mu$ m. Le module de puissance lui-même est fixé à la plaque de refroidissement par des vis. Le lead-frame est constitué de cuivre de 0,8 mm d'épaisseur permettant ainsi une bonne conductivité électrique et thermique. La puce nue choisie est fournie par Infineon : IIPC22S4N06. Elle présente une résistance interne Rdson =  $1.3m\Omega$ , une charge de grille Qg = 208nC et une tension VDSS = 60V. La résistance totale, y compris celle du lead-frame, est inférieure à  $2m\Omega$ . La résistance totale, y compris celle des interfaces thermiques, est Rth=1.393 °C/W.

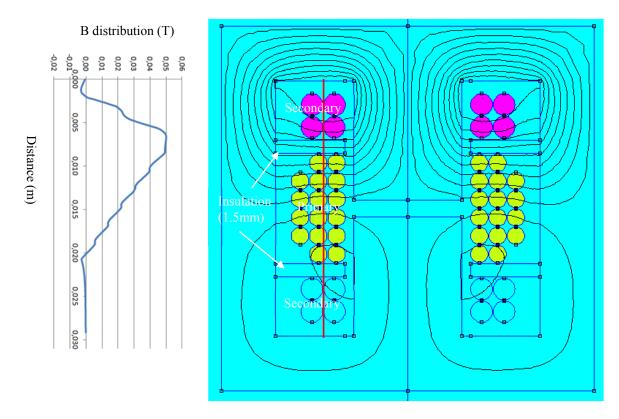

L'inductance magnétisante nécessaire est Lm = 42uH. La réalisation ne pose pas de problème : pour 16 tours du côté primaire du transformateur, un noyau magnétique possédant une faible inductance spécifique AL, de l'ordre de 165nH, doit être utilisé (ex : avec entrefer). Une inductance de fuite suffisante pour réaliser une inductance de résonance impose de séparer les enroulements secondaires du primaire. La solution retenue consiste à intercaler les 16 spires du primaire entre les enroulements secondaires, comme à la figure R-12.

Figure R-12. Réalisation du transformateur avec inductance de fuite lf=1.5 µH

Dans cette configuration, une plus forte densité de flux existe dans l'intervalle entre enroulements : Bpk $\approx$ 50mT. Avec un espace suffisant entre primaire et secondaires, ce transformateur peut ainsi réaliser une inductance de fuite  $l_f=1.5\mu$ H. L'inductance de résonance nécessaire étant plus élevée, il est nécessaire de rajouter un noyau RM12 à entrefer avec 6 tours. La photo d'un prototype de transformateur est donnée à la figure R-13.

Figure R-13. Transformateur et inductance additionnelle nus (à gauche) et dans un récipient (« sarcophage ») de refroidissement (à droite)

Du fil de Litz (800x0.05mm primaire, 1200x0.05mm secondaire) est utilisé pour éviter l'effet de peau et de réduire l'effet de proximité dans les enroulements du transformateur. Les pertes dans les fils de Litz doivent être finement analysées pour êtres estimées avec précision.

Pour le fil de Litz, le diamètre de chaque brin doit être inférieur à l'épaisseur de peau  $\sigma$ . Sous cette condition, la répartition de courant peut être considérée comme homogène dans la section de chaque brin. Cependant, des pertes importantes peuvent encore être dues à l'effet de proximité. Il est possible de distinguer l'effet de proximité interne et l'effet de proximité externe. L'effet de proximité interne fixe la distribution de courant dans un brin en fonction du courant dans tous les autres brins lorsqu'il n'y a pas de champ externe. L'effet de proximité externe est dû à un champ magnétique externe provenant par exemple, comme dans notre cas, de l'entrefer d'un transformateur. Les pertes dues à l'effet de proximité externe, les principales dans notre cas, peuvent être estimées par l'équation suivante :

$$P_{eddy} = \frac{4\omega^2 l B_{pk}^2 d^2 S}{128\rho}$$

$\rho$  est la résistivité du fil, *d* est le diamètre de chaque brin, *l* est la longueur du fil, Bpk est le pic du champ magnétique externe à une pulsation  $\omega$ . S est la section effective du fil de Litz,

avec  $S = N\pi d^2/4$ . Il semble évident que la diminution du diamètre des brins et l'augmentation de leur nombre pour conserver une même section effective permettent de réduire les pertes. Cependant, l'isolant nécessaire autour de chaque brin conserve une épaisseur équivalente. C'est ainsi qu'un plus grand nombre de brins plus fins pour une même section utile totale se traduit par une section totale supérieure, donc par un circuit magnétique plus volumineux. En outre, lorsque des brins plus fins sont nécessaires, le coût du fil de Litz augmente. Ainsi, le diamètre du brin doit être soigneusement sélectionné afin de réaliser le meilleur compromis entre rendement, encombrement et coût. Dans ce projet, nous avons choisi le fil de Litz de type 44AWG avec un diamètre de brin de 50 µm (soit environ 1/3 de l'épaisseur de peau).

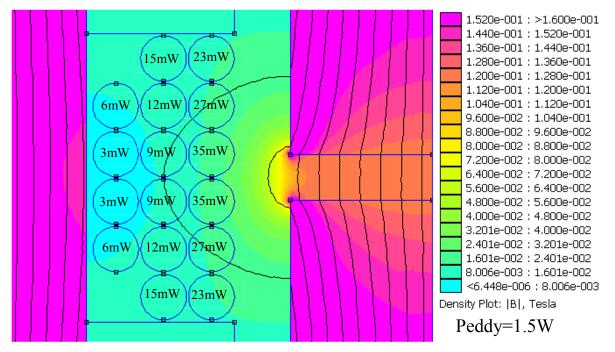

Certaines spires de l'enroulement primaire sont plus proches de l'entrefer et baignent dans un champ magnétique plus intense. Dans le but de réduire l'effet de proximité externe, il est intéressant d'éloigner les enroulements du noyau central. Afin d'estimer les pertes dans les enroulements du transformateur il est possible de recourir à la simulation numérique. La figure R-14 donne un exemple de calcul.

Figure R-14. Calcul des pertes dans chaque spire pour une géométrie donnée

La figure R-14 est relative à une distance de 2,5 mm entre enroulements et noyau central (épaisseur de la « carcasse »). Les pertes totales dans l'enroulement primaire, dues principalement à des courants induits (de Foucault), sont alors de 1.5W. Lorsque la distance diminue jusqu'à 1mm, ces pertes passent de 1.5W à 3.5W.

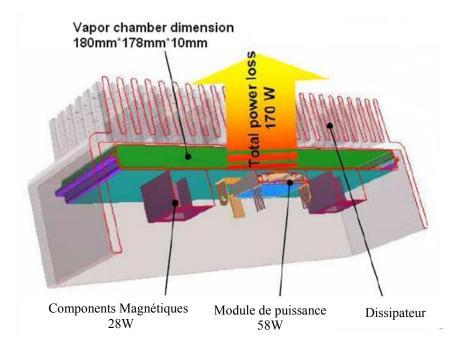

Dans le cadre de cette thèse, il nous a semblé intéressant de tester un mode de refroidissement innovant. Dans un système de refroidissement à air classique, le profilé d'aluminium n'a pas la capacité d'évacuer efficacement les calories générées par les composants de puissance car des points chauds existent. La solution de refroidissement adoptée ici passe par l'utilisation d'une chambre à vapeur à la base du dissipateur, comme indiqué à la figure R-15.

Figure R-15. Utilisation d'une chambre à vapeur à la base du dissipateur

Une chambre à vapeur est un caloduc plat qui utilise le principe de l'évaporation et de la condensation afin de répartir au mieux la chaleur sur le dissipateur, comme une plaque de conductivité thermique très élevée. La chaleur est évacuée par l'intermédiaire d'un fluide qui s'évapore puis se condense assurant ainsi une répartition uniforme de la température et une élimination des points chauds.

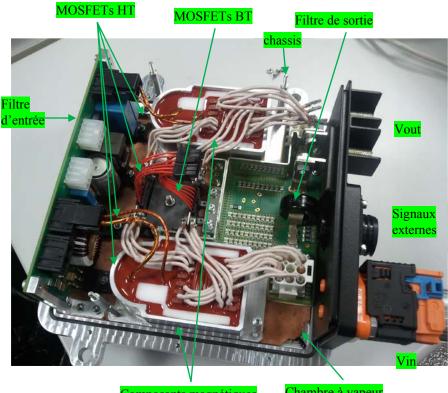

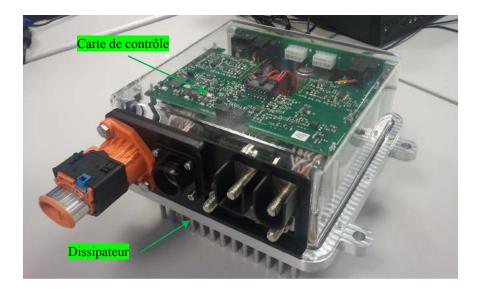

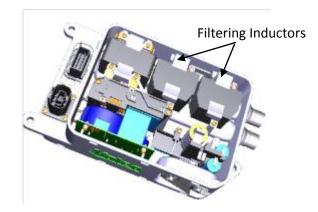

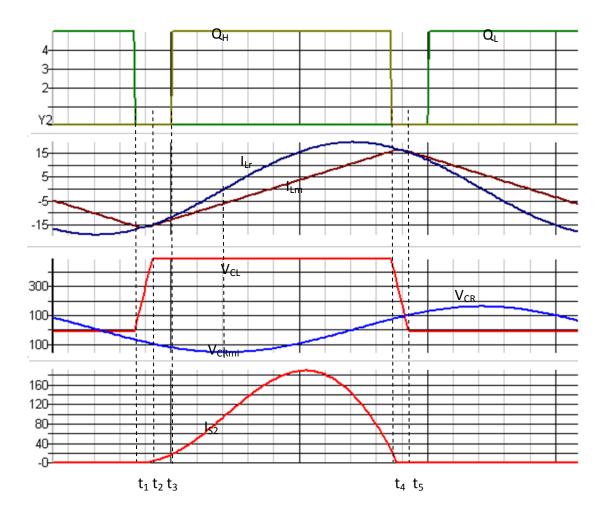

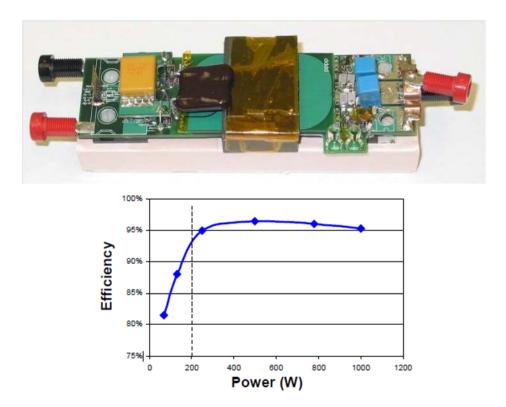

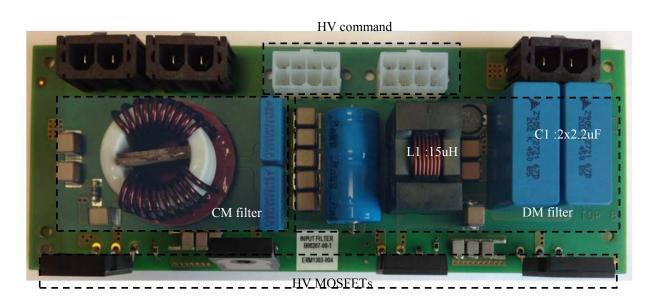

Les photos de la figure R-16 montrent l'implantation des composants dans le prototype. Comme les pertes dans le PCB du filtre d'entrée sont limitées, celui-ci est monté verticalement afin de réduire l'encombrement global. Les MOSFETs HT sont placés en dessous du filtre d'entrée et sont fixés directement à la chambre de vapeur par des vis afin de faciliter le refroidissement. Des interfaces thermiques sont toutefois nécessaires pour isoler les MOSFETs HT de la chambre de vapeur. Les composants magnétiques et les modules MOSFET BT sont également montés directement sur la chambre à vapeur. La carte de circuit imprimé de commande est montée sur quatre entretoises, au-dessus des composants de puissance. Un connecteur externe à 16 broches est utilisé pour échanger des signaux de commande et des signaux de mesure avec l'extérieur. Après assemblage, le prototype a un encombrement global de 2.51 et une masse de 3 kg. Pour une puissance nominale de 2,5kW (puissance crête de 3 kW), cela représente une densité volumique de 1W/cm<sup>3</sup> et une densité massique de 0.83W/kg, ce qui est très important pour ce type de convertisseur. A l'ambiant, seule la convection naturelle est suffisante. Quand la température ambiante s'élevée à 70°C, une convection forcé avec vitesse du vent 1.5m/s est nécessaire afin de garantir les composants de puissances sont bien au dessous de 105°C.

Composants magnétiques

Chambre à vapeur

Figure R-16. Prototype du convertisseur LLC réalisé avec une densité de 1W/cm3

#### Résultats

Les figures R-17 et R-18 montrent les résultats expérimentaux mesurés sur le prototype.

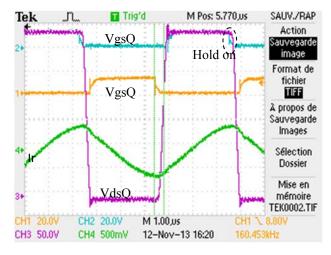

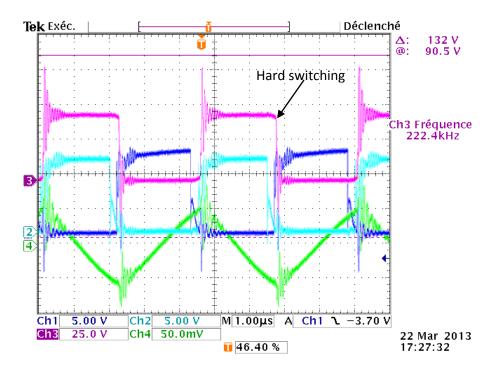

Figure R-17. Formes d'onde au primaire pour la phase B, avec Io = 150A, Vin=350V. (Ir:10A/div)

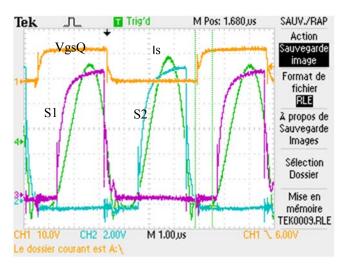

Figure R-18. Formes d'onde au secondaire pour la phase B, avec Io = 150A, Vin=350V. (Is:20A/div)

Les MOSFETs HT choisis (STW88N65M5) sont du type « super-jonction » avec une caractéristique très non-linéaire pour la capacité de sortie : Coss est très élevée à une tension Vds basse. La tension drain-source est maintenue constante au début du blocage ZVS, pendant environ 150 ns, puis la tension décroît linéairement jusqu'à zéro, avant la fin du temps mort. Les MOSFETs sont également mis en conduction en mode ZVS. Le temps mort finalement adopté est de 400ns. La partie secondaire du convertisseur fait appel au

redressement synchrone ce qui mène à des pertes par conduction extrêmement faibles. Comme le montre la figure R-18, le signal de redressement synchrone est pratiquement en phase avec le courant de sortie mais, durant un laps de temps très court, le redressement par transistor n'a pas lieu : le redressement synchrone se termine 300ns avant que le courant ne s'annule. Des pertes par conduction sont prévisibles dans la diode, mais ces pertes sont négligeables compte tenu de son temps de conduction. Le courant de recouvrement inverse ( $\sim 10A$ ) entraîne aussi des pertes de l'ordre de 1.5W par MOSFET. Le rendement a été mesuré pour chaque cellule A et B et pour les deux cellules de puissance fonctionnant ensemble en parallèle (figure R-19).

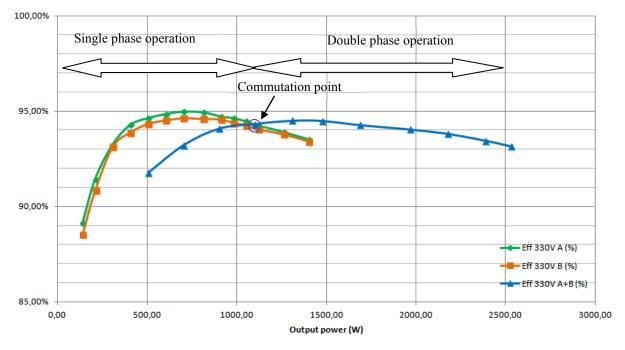

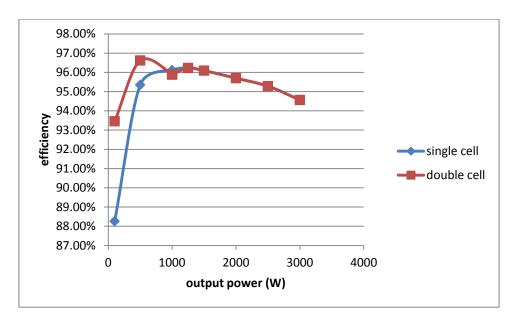

Figure R-19. Rendement mesuré pour Vin = 330V

Le rendement de conversion d'une seule cellule LLC est maximale lorsqu'elle délivre 700 W, avec un rendement maximal de 95% pour la phase A et 94,7 % pour la phase B. En raison des dispersions des composants, les performances de ces deux cellules de puissance sont légèrement différentes. Le rendement commence à diminuer lorsque la puissance de charge dépasse 700W. Il est intéressant de faire fonctionner une seule cellule tant que la puissance appelée par la charge ne dépasse pas 1,1 kW et de faire fonctionner les deux modules simultanément pour une puissance supérieure. C'est ainsi que le rendement de conversion global peut être maximisé. Le rendement continue d'augmenter entre 1,1 kW et 1,5 kW.

Le convertisseur LLC à deux phases permet donc d'obtenir un très bon rendement :  $\eta > 94 \%$  de 500W à 2kW ;  $\eta > 93 \%$  de 300W à 2,5 kW. Même à très faible charge (140W), le rendement de conversion est d'environ 89 %.

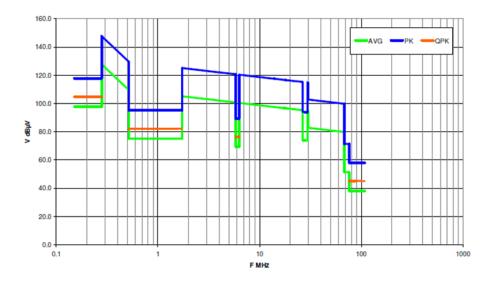

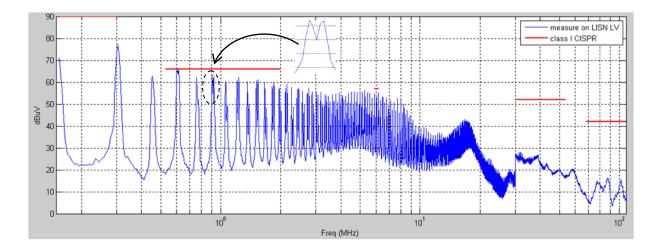

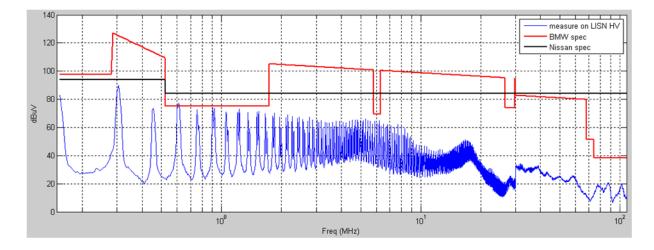

La figure R-20 présente les résultats de mesure CEM du côté haute tension.

Figure R-20. Mesure CEM de haute fréquence à LISN LV + (détecteur de AVG, Vin = 330V)

Comme le montre la figure R-20, tous les bruits sont maintenus en-dessous des limites spécifiées par des fabricants de véhicules. Le bruit principal est détecté aux fréquences 2kfs. L'asymétrie des secondaires de transformateurs (le courant n'est pas parfaitement distribué entre les deux enroulements secondaires du transformateur) provoque des bruits supplémentaires aux fréquences (2k-1)fs. En particulier pour fs, le niveau de bruit généré est inférieure à celui correspondant à 2fs; cependant, l'atténuation du filtre d'entrée pour fs est 15dB plus basse qu'à 2fs; ainsi le bruit mesuré à fs devient important devant celui à 2fs (72dBµV vs 78dBµV). La symétrie des enroulements secondaires du transformateur doit être précisément contrôlée pour éviter ce bruit.

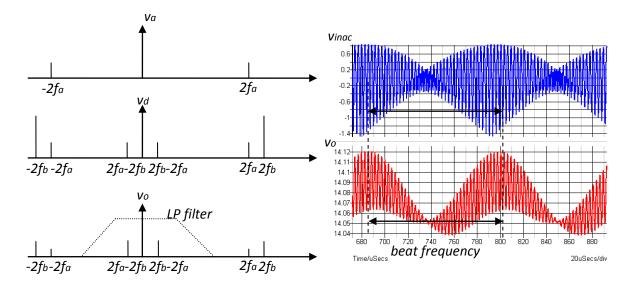

Pour la composante fondamentale et les premières composantes harmoniques, il n'est pas possible de distinguer une différence entre fa et fb à cause de la résolution de l'appareil de mesure. À partir de 5fs, les différences entre fréquences adjacentes deviennent apparentes. Les niveaux de bruits aux fréquences adjacentes sont égaux, ce qui vérifie que le bruit est superposé dans le domaine fréquentiel. En concevant des filtres d'entrée/sortie basés sur le niveau de bruit généré par une phase, l'autre phase bénéfice naturellement de la même atténuation à une fréquence adjacente.

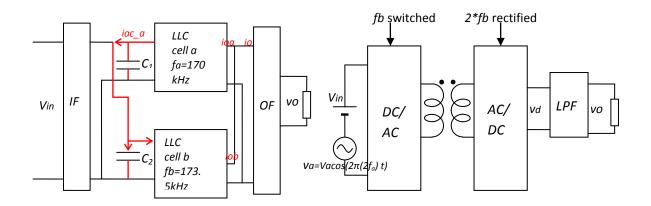

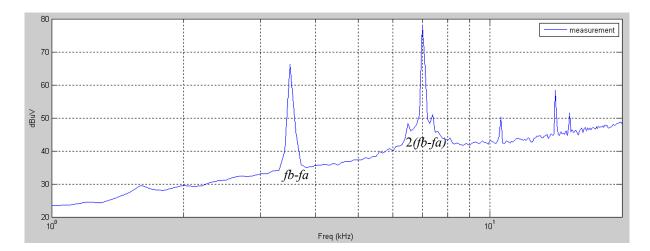

Dans le convertisseur, l'interaction entre les bruits de commutation de chaque cellule crée des fréquences de battement indésirables, à des fréquences multiples de la différence entre les

fréquences de fonctionnement : un battement à basse fréquence 2(fb-fa) apparaît en entrée et en sortie. Étant donné que les deux fréquences sont proches l'une de l'autre, ce battement ne peut pas être suffisamment atténué par le filtre passe bas d'entrée ou de sortie.

Pour atténuer ce battement, des condensateurs de découplage avec des capacités suffisantes sont nécessaires à l'entrée de chaque cellule de puissance. De plus, les filtres d'entrée et de sortie ne doivent pas faire apparaître de résonance à basse fréquence pour éviter d'amplifier ces battements. Ainsi, chaque filtre doit être précisément conçu et contrôlé. Les mesures à basse fréquences sont données à la figure R-21.

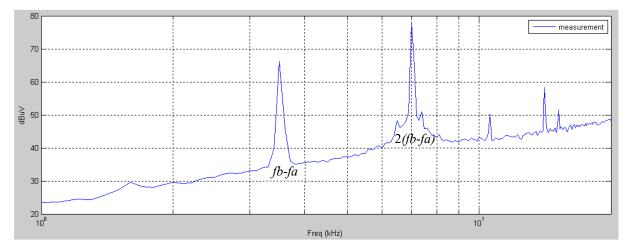

Figure R-21. Mesure CEM de basse fréquence à LISN LV + (détecteur de AVG, Vin = 410V)

Le principal battement à la fréquence 2(fb-fa) est mesuré à  $78dB\mu V$ ; un autre battement à la fréquence (fb-fa) à  $65dB\mu V$  est dû à l'asymétrie de transformateur. Comme le bruit de battement est inférieur au bruit de commutation principal, il n'a pas d'influence sur le bon fonctionnement du convertisseur LLC et sur ses performances.

#### Conclusion

La solution consistant à connecter en parallèle deux cellules de puissance LLC est intéressante dans les applications à fort courant, en particulier dans la notre (180A en sortie). Le rendement est ainsi optimisé. Il peut l'être davantage en faisant fonctionner une seule cellule à faible puissance et les deux simultanément à forte puissance. Afin d'équilibrer les courants entre les deux cellules, une stratégie de commande à double boucle est proposée. Elle repose sur des fréquences de fonctionnement indépendantes dans les deux cellules. Les deux fréquences sont légèrement différentes à cause de la dispersion des valeurs de composants dans chaque circuit résonnant.

Outre la conception de cette topologie, ce travail de thèse repose également sur de nombreux essais, à la fois par calcul, par simulation et expérimentalement, dans le but d'améliorer toujours davantage les performances du convertisseur LLC. En particulier, l'utilisation d'un noyau classique en E avec entrefer a été validée pour intégrer toutes les inductances de résonance nécessaires dans le transformateur sous les formes d'inductance de magnétisation et d'inductances de fuite. C'est ainsi que l'encombrement et la masse des composants magnétiques ont pu être minimisés. Le choix même du fil de Litz et celui de son emplacement dans la fenêtre du circuit magnétique ont été optimisés. Les MOSFET BT du secondaire ont été réalisés sous forme d'un seul module IML, ce qui a permis de réduire beaucoup les pertes par conduction ainsi que les résistances thermiques. L'emploi d'une chambre à vapeur a montré son efficacité dans ce type d'application. Le filtrage a lui aussi été optimisé compte tenu d'un petit défaut inhérent au principe retenu : deux fréquences de découpage doivent coexister. Moyennant quelques aménagements, les battements qui en découlent peuvent être rendus négligeables.

En conclusion, le convertisseur LLC à double phase proposé semble être une bonne solution pour construire des convertisseurs de quelques kilowatts à fort rendement et à forte puissance massique. Le prototype réalisé, presque directement industrialisable, convient en particulier pour les applications DC/DC de 2,5 kW HT / BT dans les futurs véhicules électriques et hybrides.

## **Chapter 1. Introduction**

### 1.1 Backgrounds and project introduction

Power electronics plays an important role in automotive and transport industrial applications, converting normally voltages from 200V to 3000V. Energy saving is now in strong demand to cope with growing demand for electrical applications and limited ecological resources, calling for rapid advancement in power semiconductor devices, conversion, and storage technologies. This puts a considerable pressure on all industries to innovate on levels of systems, device, technology and manufacturing [1-1]. (References are attached at the end of each chapter.)

In Automotive, the upcoming trend for electric vehicles calls for economical, efficient and low cost solutions, based on new packaging and innovative components. By a study combining from Strategy Analytics and IFX it is estimated that in 2015 roughly 6.2 million hybrid and electric vehicles will be produced per year. In total this indicates a market volume of roughly 1 Billion  $\in$  of automotive power electronics in 2015.

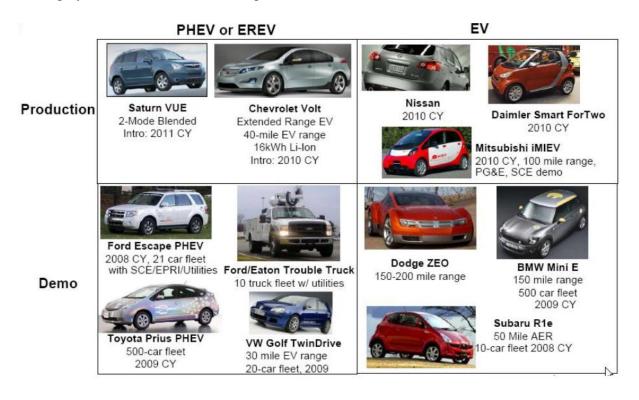

Figure 1-1: Typical electrical vehicles in mass production or demo (PHEV=plug-in hybrid electric vehicle, EREV= extended range electric vehicle, EV=electric vehicule)

Currently a variety of different electric vehicle concepts, battery systems, and individual technical solutions is pursued for concept cars and small fleets of electric vehicles in order to gather experience with this new kind of cars, shown as in Figure 1-1. Technologies are adapted from industry, but the power traction units are far from being optimized with respect to efficiency, volume, or mass production.

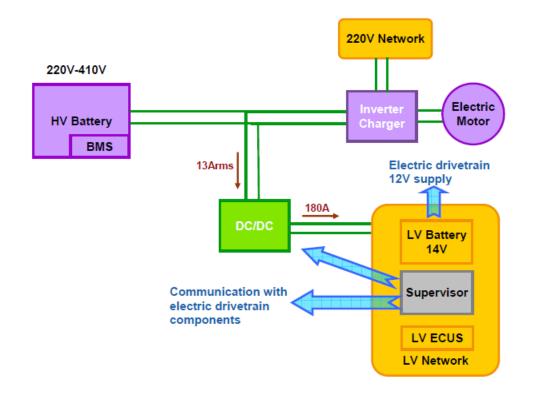

Figure 1-2: A typical mechanical traction and power conversion system in electric vehicles

The traction system in electric vehicles is shown as in the above Figure 1-2. The electric vehicles are principally powered by a high voltage battery permitting to drive the traction chains. The high voltage (HV) battery is constructed by connecting in series or parallel several battery cells, with the number of cells properly selected according to the required power (from 15kW to 100kW depending on the type of vehicle) and the targeted autonomic distance (variant from 100km to 400km depending on the specification). A DC/AC inverter converts the HV battery voltage to three phase AC voltage to drive the electric motors.

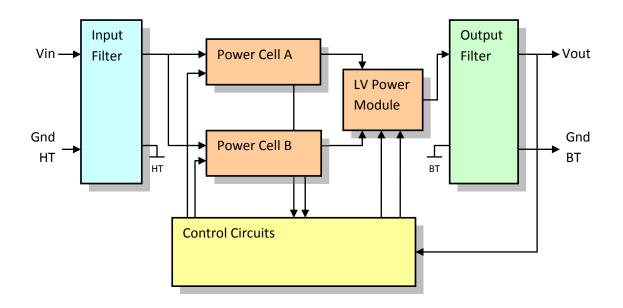

Considering the other functions, other equipments are all powered by a classical 14V low voltage (LV) network, as in Figure 1-2. In order to power the LV network, all the electric vehicles are equipped with a HV/LV DCDC converter generating an insulated 14V voltage based on the HV battery. A secondary 14V battery is connected at the LV network for the start, stop and diagnostic phases while the HV battery is not activated during these phases.

The aim of this dissertation is to develop a high efficient DCDC converter, with the following main requirements as electrical parameters:

| A                                  |                                           |  |

|------------------------------------|-------------------------------------------|--|

| Energy flow                        | From HV-DC to LV-DC unidirectional        |  |

| Efficiency                         | 93% peak, >92% from 1kW                   |  |

| Input voltage                      | 220-410V                                  |  |

| Output voltage                     | 12-16V                                    |  |

| Maxi output power                  | 2.5kW                                     |  |

| Mini output power                  | 0W                                        |  |

| Maxi continuous output current     | 180A                                      |  |

| Operating temperature              | -40°C to 70°C by using natural convection |  |

| Maximum volume (without heat sink) | 2.5L                                      |  |

| Mini power density                 | $1 \mathrm{W/cm}^3$                       |  |

| Voltage regulation accuracy        | ±1%                                       |  |

Table 1-1: Objective specifications of the DCDC converter project

Energy conversion efficiency and power density are the two top concerns for power electronics converters in electrical/hybrid car industries. In order to attain the objectives of conversion efficiency and volume, soft-switching techniques should be adopted to increase the switching frequency and minimize the size of magnetic components and passive filters. Synchronous rectification is mandatory to get high conversion efficiency rather than Schottky diodes. Besides, the converter should also be able to generate the low output voltage based on a large input voltage variation range. Therefore, this dissertation mainly focuses on the topology investigation and performance amelioration to comply with the specified objectives of HV/LV DCDC converters with wide input voltage range operation at a wide output power range.

The converter is designed to be capable of generating 12-16V output. But in order to simplify configuration, the converter demonstrator is regulated to 14V constant output and is connected to a pure resistive power load. This dissertation mainly draws its attention on power electronic issues in circuit operation and efficiency improvement.

# 1.2 Discussions on existed soft-switching converter solutions1.2.1 H-bridge phase shift converter

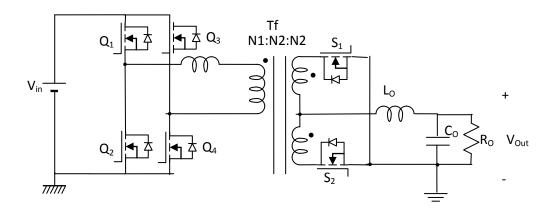

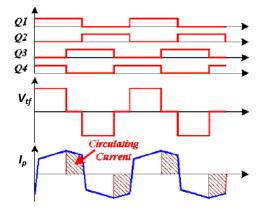

Soft-switching PWM converter, especially H-bridge (full bridge) phase shift PWM converter [1-2], is a widely used topology in HV/LV DCDC conversion, with its typical circuit schematic given at Figure 1-3. Primary side is in full bridge structure and secondary side is in a center-tapped structure.

Figure 1-3. The H-bridge phase shift PWM converter

Figure 1-4. Typical waveforms of H-bridge phase shift PWM converter