# A decoupled approach to high-level loop optimization: tile shapes, polyhedral building blocks and low-level compilers

Tobias Grosser

### ▶ To cite this version:

Tobias Grosser. A decoupled approach to high-level loop optimization: tile shapes, polyhedral building blocks and low-level compilers. Programming Languages [cs.PL]. Université Pierre et Marie Curie - Paris VI, 2014. English. NNT: 2014PA066270. tel-01144563

### HAL Id: tel-01144563 https://theses.hal.science/tel-01144563v1

Submitted on 22 Apr 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Université Pierre et Marie Curie

École Doctorale Informatique, Télécommunications et Électronique INRIA, École Normale Supérieure / Équipe PARKAS

### A DECOUPLED APPROACH TO HIGH-LEVEL LOOP OPTIMIZATION

- TILE SHAPES, POLYHEDRAL BUILDING BLOCKS AND LOW-LEVEL COMPILERS -

Par Tobias Christian Grosser

Thése de doctorat en informatique

Codirigée par Albert Cohen et Sven Verdoolaege

Présentée et soutenue publiquement le 21/10/2014 Devant le jury composé de:

**Rapporteurs:** Mary Hall University of Utah

Franz Franchetti Carnegie Mellon University

**Examinateurs:** Stef Graillat Université Pierre et Marie Curie

Jean-Luc Lamotte Université Pierre et Marie Curie Franz Franchetti Carnegie Mellon University

Ponnuswamy Sadayappan Ohio State University

Albert Cohen INRIA

Sven Verdoolaege École Normale Supérieure

Malgré des décennies de recherche sur l'optimisation de boucle aux haut niveau et leur intégration réussie dans les compilateurs C/C++ et FORTRAN, la plupart des systèmes de transformation de boucle ne traitent que partiellement les défis posé par la complexité croissante et la diversité du matériel d'aujourd'hui. L'exploitation de la connaissance dédiée a un domaine d'application pour obtenir le code optimal pour cibles complexes, tels que des accélérateurs ou des microprocessors multi-cœur, pose des problèmes pour les formalismes et outils d'optimisation de boucle existants. En conséquence, de nouveaux schémas d'optimisation qui exploitent la connaissance dédiée a un domaine sont développées indépendamment sans profiter de la technologie d'optimisation de boucle existante. Cela conduit à des possiblités d'optimisation raté et ainsi qu'à une faible portabilité de ces schémas d'optimisation entre des compilateurs différents. Un domaine pour lequel on voit la nécessité d'améliorer les optimisations est le calcul de pochoir itératifs, un probléme de calcul important qui est réguliérement optimisé par les compilateurs dédiées, mais pour lequel générer code efficace est difficile.

Dans ce travail, nous présentons des nouvelles stratégies pour l'optimisation dédiée qui permettent la génération de code GPU haute performance pour des calculs de pochoir. À la différence de la façon dont la plupart des compilateurs existants sont mis en œuvre, nous découplons la stratégie d'optimisation de haut niveau de l'optimisation de bas niveau et la spécialisation nécessaire pour obtenir la performance optimale. Comme schéma d'optimisation de haut niveau, nous présentons une nouvelle formulation de "split tiling", une technique qui permet la réutilisation de données dans la dimension du temps ainsi que le parallélisme équilibré à gros grain sans la nécessité de recourir à des calculs redondants. Avec le "split tiling", nous montrons comment intégrer une optimisation dédiée dans un traducteur générique source-à-source, C vers CUDA, une approche qui nous permet de réutiliser des optimisations existants non-dédiées. Nous présentons ensuite notre technique appelée "hybrid hexagonal / parallelogram tiling", un schéma qui nous permet de générer du code que cible directement les préoccupations spécifiques aux GPUs. Pour conclure notre travail sur le "loop tiling", nous étudions la rapport entre "diamond tiling" et "hexagonal tiling". À partir d'une analyse de "diamond tiling" détailée, qui comprend les exigences qu'elle pose sur la taille de tuile et les coefficients de front d'onde, nous fournissons une formulation unifiée de l'"hexagonal tiling" et du "diamond tiling" qui nous permet de réaliser un "hexagonal tiling" pour

des problèmes avec deux dimensions (un temps, un espace) dans le cadre d'un usage dans un optimiseur générique, comme "Pluto". Enfin, nous utilisons cette formulation pour évaluer l'"hexagonal tiling" et le "diamond tiling" en terme de rapport de calcul-à-communication et calcul-à-synchronisation.

Dans la deuxième partie de ce travail, nous discutons nos contributions aux composants de l'infrastructure les plus important, nos "building blocks", qui nous permettent de découpler notre optimisation de haut niveau tant des optimisations nécessaires dans la génération de code que de l'infrastructure de compilation générique. Nous commençons par présenter le nouveau "polyhedral extractor" (pet), qui obtient une représentation polyédrique d'un morceau de code C. pet utilise l'arithmétique de Presburger en sa généralité pour élargir le fragment de code C supporté et porter une attention particulière à la modélisation de la sémantique des langages même en présence de dépassement de capacité des entiers. Dans une prochaine étape, nous présentons une nouvelle approche polyédrique pour la génération de code, qui étend cell-ci au-delà de la génération de flot de contrôle classique en permettant la génération de expressions fournies par l'utilisateur. Avec un mécanisme d'option détaillé, nous donnons à l'utilisateur un contrôle précis sur les décisions de notre générateur du code et nous ajoutons un support pour la spécialisation extensive par exemple, avec une nouvelle forme de déroulage de boucle polyédrique. Pour faciliter la mise en œuvre de transformations polyédriques, nous présentons une nouvelle représentation, les "schedule trees", qui représentent explicitement la structure d'arbre inhérent aux ordonnancements polyédriques.

La dernière partie de cet ouvrage présente nos contributions aux compilateurs du bas niveau. L'objectif principal de cette partie est notre travail sur la délinéarisation optimiste, une approche pour dériver une vue de tableau multi-dimensionnel pour des formes accès en polynômiales multivariées qui résultent souvent de code qui travaille avec des tableaux multi-dimensionnels avec taille paramétrique.

Despite decades of research on high-level loop optimizations and their successful integration in production C/C++/FORTRAN compilers, most compiler internal loop transformation systems only partially address the challenges posed by the increased complexity and diversity of today's hardware. Especially when exploiting domain specific knowledge to obtain optimal code for complex targets such as accelerators or many-cores processors, many existing loop optimization frameworks have difficulties exploiting this hardware. As a result, new domain specific optimization schemes are developed independently without taking advantage of existing loop optimization technology. This results both in missed optimization opportunities as well as low portability of these optimization schemes to different compilers. One area where we see the need for better optimizations are iterative stencil computations, an important computational problem that is regularly optimized by specialized, domain specific compilers, but where generating efficient code is difficult.

In this work we present new domain specific optimization strategies that enable the generation of high-performance GPU code for stencil computations. Different to how most existing domain specific compilers are implemented, we decouple the high-level optimization strategy from the low-level optimization and specialization necessary to yield optimal performance. As high-level optimization scheme we present a new formulation of split tiling, a tiling technique that ensures reuse along the time dimension as well as balanced coarse grained parallelism without the need for redundant computations. Using split tiling we show how to integrate a domain specific optimization into a general purpose C-to-CUDA translator, an approach that allows us to reuse existing non-domain specific optimizations. We then evolve split tiling into a hybrid hexagonal/parallelogram tiling scheme that allows us to generate code that even better addresses GPU specific concerns. To conclude our work on tiling schemes we investigate the relation between diamond and hexagonal tiling. Starting with a detailed analysis of diamond tiling including the requirements it poses on tile sizes and wavefront coefficients, we provide a unified formulation of hexagonal and diamond tiling which enables us to perform hexagonal tiling for two dimensional problems (one time, one space) in the context of a general purpose optimizer such as Pluto. Finally, we use this formulation to evaluate hexagonal and diamond tiling in terms of compute-to-communication and compute-to-synchronization ratios.

In the second part of this work, we discuss our contributions to important infrastructure components, our building blocks, that en-

able us to decouple our high-level optimizations from both the necessary code generation optimizations as well as the compiler infrastructure we apply the optimization to. We start with presenting a new polyhedral extractor that obtains a polyhedral representation from a piece of C code, widening the supported C code to exploit the full generality of Presburger arithmetic and taking special care of modeling language semantics even in the presence of defined integer wrapping. As a next step, we present a new polyhedral AST generation approach, which extends AST generation beyond classical control flow generation by allowing the generation of user provided mappings. Providing a fine-grained option mechanism, we give the user fine grained control about AST generator decisions and add extensive support for specialization e.g., with a new generalized form of polyhedral unrolling. To facilitate the implementation of polyhedral transformations, we present a new schedule representation, schedule trees, which proposes to make the inherent tree structure of schedules explicit to simplify the work with complex polyhedral schedules.

The last part of this work takes a look at our contributions to low-level compilers. The main focus in this part is our work on optimistic delinearization, an approach to derive a multi-dimensional array view for multi-variate polynomial expressions which commonly result from code that models data as multi-dimensional arrays of parametric size.

The following is a list of publications I wrote or contributed to while working towards my doctoral degree. Ideas, figures, listings and text of some of these works have been incorporated in this thesis.

The work published in [8, 3] was mostly performed within the context of my diploma degree and is listed due to the relevance for parts of this work. [4] has been submitted for review, but has not yet been published. A new technical report which we cite in the AST generation chapter still needs to be published.

- [1] Tobias Grosser, Albert Cohen, Justin Holewinski, P. Sadayappan, and Sven Verdoolaege. Hybrid Hexagonal/Classical Tiling for GPUs. In *International Symposium on Code Generation and Optimization (CGO)*, Orlando, FL, United States, 2014.

- [2] Tobias Grosser, Albert Cohen, Paul HJ Kelly, J Ramanujam, P Sadayappan, and Sven Verdoolaege. Split tiling for GPUs: automatic parallelization using trapezoidal tiles. In 6th Workshop on General Purpose Processor Using Graphics Processing Units (GPGPU), pages 24–31. ACM, 2013.

- [3] Tobias Grosser, Armin Größlinger, and Christian Lengauer. Polly performing polyhedral optimizations on a low-level intermediate representation. *Parallel Processing Letters (PPL)*, 22(04), 2012.

- [4] Tobias Grosser, Sven Verdoolaege, and Albert Cohen. Polyhedral ast generation is more than scanning polyhedra. *ACM Transactions on Programming Languages and Systems (TOPLAS)*. (submitted for review).

- [5] Tobias Grosser, Sven Verdoolaege, Albert Cohen, and P. Sadayappan. The relation between diamond tiling and hexagonal tiling. In 1st International Workshop on High-Performance Stencil Computations (HiStencils).

- [6] Tobias Grosser, Sven Verdoolaege, Albert Cohen, and P. Sadayappan. The Promises of Hybrid Hexagonal/Classical Tiling for GPU. Rapport de recherche RR-8339, INRIA, July 2013.

- [7] Tobias Grosser, Sven Verdoolaege, and Sadayappan P. Cohen, Albert. The relation between diamond tiling and hexagonal tiling. *Parallel Processing Letters (PPL)*, 24(03), 2014.

- [8] Tobias Grosser, Hongbin Zheng, Ragesh Aloor, Andreas Simbürger, Armin Größlinger, and Louis-Noël Pouchet. Polly –

- polyhedral optimization in LLVM. In C. Alias and C. Bastoul, editors, 1st International Workshop on Polyhedral Compilation Techniques (IMPACT), Chamonix, France, 2011.

- [9] Kevin Stock, Martin Kong, Tobias Grosser, Louis-Noël Pouchet, Fabrice Rastello, J. Ramanujam, and P. Sadayappan. A framework for enhancing data reuse via associative reordering. In *Conference on Programming Language Design and Implementation* (*PLDI*), 2014.

- [10] Sven Verdoolaege and Tobias Grosser. Polyhedral extraction tool. In 2nd International Workshop on Polyhedral Compilation Techniques (IMPACT), Paris, France, January 2012.

- [11] Sven Verdoolaege, Serge Guelton, Tobias Grosser, and Albert Cohen. Schedule trees. In Sanjay Rajopadhye and Sven Verdoolaege, editors, 4th International Workshop on Polyhedral Compilation Techniques (IMPACT), Vienna, Austria, January 2014.

Many colleagues, friends and family members supported me during

Many colleagues, friends and family members supported me during the time of my doctoral studies, but also during the years leading towards them. Those influences have been important both in forming this work, but also in forming myself personally. I would like to express my deep gratefulness to all who have walked with me this path, the ones I will name personally, but especially the ones who I will inevitable forget to name.

First and foremost I would like to thank you, Albert, Sven and Saday, you who guided me through these three years of doctoral studies. Albert, I still remember the moment in a Canadian bar when you told me I should write you an email in case I would like to do my doctoral studies with you. From this moment, several years before I actually started, you have been immensely supportive, leaving me the freedom to choose the directions I want to follow, but still supporting me at any moment I was in need for guidance or help. Sven, working with you has been an experience. I must admit it was hard to read your first emails with your always very direct and open feedback, but I learned quickly how valuable your in-depth feedback is and now really enjoy working and discussing with you. Saday, thank you for your supervision and support both during my time in Ohio, but especially during the many phone calls and Paris visits throughout the last three years. You did not only help me to shape my research direction, but also gave helpful advices in so many other ways.

I would like to send a big thank you to Passau and the LooPo team, especially naming Martin Griebl, Christian Lengauer, Armin Größlinger and Andreas Simbürger as well as Dirk Beyer and Sven Apel. All of these supported me from the first years of my studies. Throughout my PhD I met and got to know many interesting researchers. I would like to especially thank Louis-Noël Pouchet, who I have been working with in Ohio, Uday Bondugula, who I visited in Bangalor and Ram (Ramanujam), who I also met very regularly at many different places. I would like to thank Aart Bik, Beate List and Stephen Hines for my great time at Google and their support in the context of my Google Doctoral Fellowship, Anton Lokmotov for the great time at ARM as well as Sebastian Pop, who I regularly interact with since my first internship at AMD. The Parkas team, including Mark, Francesco, Louis, Tim, Jean, Boubacar, Serge, Michael, Jun, Antoine, Feng, Guillaume, Riyadh, Adrien, Nhat, Robin, Cédric and Chandan for the many interesting discussions, the nice coffee breaks as well as joint travels excursions. Assia and Joelle as well as all the other administrative staff, who did a great job in supporting my travels and my conference organization. I would also like to thank you, Arnaud, Sylvestre and Duncan, for the great time when organizing the LLVM conference and our regular Paris social. As well as the LLVM and Polly open source community with many very nice people, starting to name them would inevitably make me forgot someone important. Finally, there are my thesis reviewers Mary Hall and Franz Franchetti as well as my thesis committee with Stef Graillat and Jean-Luc Lamotte who I would like to express my thankfulness for their efforts and comments.

I also had the support of many great friends, including Yulia who helped with my registration, Amalia who helped with my English and my roommates Mathieu, Gælle, Caro and Kristin, who supported my crazy working hours and always prepared great food for me.

I also would like to thank my parents and siblings, Rolf, Waltraud, Tanja and Michael, who I neglected way too many times as well as my you Kasia, the woman on my side, who I met right at the beginning of my studies and who had an infinite amount of patience supporting me while working on this thesis.

### CONTENTS

| Lis | t of I | Figures                                       |

|-----|--------|-----------------------------------------------|

| Lis | t of T | Tables                                        |

| Lis | t of I | Listings                                      |

|     |        | Acronyms xix                                  |

|     |        |                                               |

| i   | INTE   | RODUCTION                                     |

| 1   | INT    | RODUCTION                                     |

|     | 1.1    | Outline 6                                     |

| ii  | BAC    | KGROUND                                       |

| 2   | POL    | YHEDRAL COMPILATION                           |

|     | 2.1    | Mathematical Foundations                      |

|     |        | 2.1.1 Integer sets                            |

|     |        | 2.1.2 Integer maps                            |

|     |        | 2.1.3 Named unions sets/named union maps . 15 |

|     |        | 2.1.4 Libraries for integer sets / maps 15    |

|     | 2.2    | Model and Transform Imperative Programs 16    |

|     |        | 2.2.1 An illustrative example 16              |

|     |        | 2.2.2 What programs can be modeled? 19        |

|     |        | 2.2.3 The polyhedral representation 19        |

|     |        | 2.2.4 Transformations 20                      |

| iii | ттт    | INGS AND OPTIMIZATIONS FOR STENCILS 25        |

|     |        | · · · · · · · · · · · · · · · · · · ·         |

| 3   |        | ,                                             |

|     | 3.1    | What are Stencil Computations?                |

|     | 3.2    | Tiling of Stencil Computations                |

|     | 3.3    |                                               |

|     | 3.4    | 1                                             |

| 4   |        | TITILING                                      |

|     | 4.1    | Overview                                      |

|     | 4.2    | Preprocessing                                 |

|     | 4.3    | The Split Tiling Schedule                     |

|     |        | 4.3.1 Core algorithm 40                       |

|     |        | 4.3.2 Tile shape simplification               |

|     |        | 4.3.3 Multi-statement loop nests 42           |

|     | 4.4    | CUDA Code Generation                          |

|     |        | 4.4.1 Shared memory usage                     |

|     |        | 4.4.2 Instruction level parallelism           |

|     |        | 4.4.3 Full/partial tile separation 46         |

|     | 4.5    | Summary                                       |

| 5   | HYB    | RID HEXAGONAL/PARALLELOGRAM TILING 49         |

|     | - 1    | Organization                                  |

|    | 5.2 | The Hybrid Hexagonal/Parallelogram Schedule . 52       |

|----|-----|--------------------------------------------------------|

|    |     | 5.2.1 Hexagonal tiling 52                              |

|    |     | 5.2.2 The parallelogram tile schedule 57               |

|    |     | 5.2.3 Intra-tile schedules 57                          |

|    |     | 5.2.4 Hybrid tiling                                    |

|    |     | 5.2.5 Tile size selection 59                           |

|    | 5.3 | CUDA Code Generation                                   |

|    | 0 0 | 5.3.1 Generating CUDA code 59                          |

|    |     | 5.3.2 Shared memory                                    |

|    |     | 5.3.3 Interleaving computations and copy-out . 6:      |

|    |     | 5.3.4 Stencil specific code generation heuristics . 6: |

|    | 5.4 | Summary 69                                             |

| 6  |     | FICATION WITH DIAMOND TILING 6                         |

|    | 6.1 | Diamond Tiling 66                                      |

|    |     | 6.1.1 The pluto optimizer 66                           |

|    |     | 6.1.2 The diamond tiling extensions 68                 |

|    |     | 6.1.3 Relation between tile sizes and wavefronts 68    |

|    |     | 6.1.4 Optimal tiles with default wavefront 73          |

|    | 6.2 | Unified Diamond and Hexagonal Tiling                   |

|    | 6.3 | Tile Sizes that Maximize Compute/Communication 77      |

|    | 6.4 | Summary                                                |

| 7  | EXP | ERIMENTAL RESULTS                                      |

| •  | 7.1 | Split-tiling                                           |

|    | 7.2 | Hybrid-Hexagonal                                       |

|    | •   | 7.2.1 Comparison with state-of-the-art tools 8         |

|    |     | 7.2.2 Hybrid tiling and shared memory 89               |

|    | 7.3 | Summary                                                |

|    | , , | ,                                                      |

| iv | POI | LYHEDRAL BUILDING BLOCKS 92                            |

| 8  | THE | CONCEPT                                                |

| 9  | POL | YHEDRAL EXTRACTOR                                      |

|    | 9.1 | Overview                                               |

|    | 9.2 | Constructing a Polyhedral Representation 100           |

|    |     | 9.2.1 Access relations                                 |

|    |     | 9.2.2 Conditions                                       |

|    |     | 9.2.3 Loops                                            |

|    |     | 9.2.4 Schedule 103                                     |

|    | 9.3 | Additional Features 103                                |

|    |     | 9.3.1 CLooG specific features 102                      |

|    |     | 9.3.2 Support for unsigned integers 102                |

|    | 9.4 | Related Work                                           |

|    | 9.5 | Limitations and Future Work 100                        |

|    | 9.6 | Summary                                                |

| 10 | AST | GENERATION                                             |

|    |     | A new approach to AST generation 113                   |

|    |     | Input                                                  |

|            | 10.3 | Abstract Syntax Tree                                 | 118 |

|------------|------|------------------------------------------------------|-----|

|            | 10.4 | New AST Generation features                          | 118 |

|            |      | 10.4.1 Fine grained option mechanism                 | 119 |

|            |      | 10.4.2 Isolation                                     |     |

|            |      | 10.4.3 Polyhedral unrolling                          |     |

|            |      | 10.4.4 Partial Unrolling                             |     |

|            |      | 10.4.5 Generating AST Expressions                    | 127 |

|            | 10.5 | Experimental Results                                 | 128 |

|            |      | 10.5.1 Existentially quantified variables            | 128 |

|            |      | 10.5.2 Performance of AST generation strategies      | 132 |

|            |      | 10.5.3 Generation Time                               | 133 |

|            |      | Related Work                                         | 134 |

|            | 10.7 | Summary                                              | 135 |

| 11         | SCH  | EDULE TREES                                          | 137 |

|            | 11.1 | Schedule Uses                                        | 139 |

|            |      | 11.1.1 Original execution order                      | 139 |

|            |      | 11.1.2 Transformations                               | 140 |

|            |      | 11.1.3 AST generation                                | 141 |

|            | 11.2 | Schedule Representations                             | 141 |

|            |      | 11.2.1 Properties                                    | 142 |

|            |      | 11.2.2 Comparison                                    | 143 |

|            | 11.3 | Schedule Tree Representation                         |     |

|            | -    | 11.3.1 Nodes                                         | 147 |

|            |      | 11.3.2 Operations                                    |     |

|            | 11.4 | Hybrid hexagonal-parallelogram tiling                |     |

|            |      | Summary                                              | 153 |

| <b>X</b> 7 | LOW  | V-LEVEL COMPILERS                                    | 155 |

|            |      | TRIBUTIONS TO LLVM / POLLY                           |     |

| 12         |      |                                                      |     |

|            |      | Compute out                                          |     |

|            |      | AST Generation                                       |     |

|            |      | GPolly - Automatic GPU offloading                    |     |

|            | -    | Representing parallelism                             |     |

| 13         |      | IMISTIC DELINEARIZATION                              |     |

|            | -    | Motivating example                                   | _   |

|            | _    | Problem statement                                    |     |

|            | 13.3 | Array views with single-parameter sizes              |     |

|            |      | 13.3.1 Multiple array references                     |     |

|            |      | 13.3.2 Array sizes in subscript expressions          | -   |

|            |      | 13.3.3 Arrays of size $A[*][\beta_1P_1][\beta_2P_2]$ |     |

|            |      | Arrays of size "parameter + constant"                | -   |

|            |      | Implementation                                       |     |

|            |      | Experimental evaluation                              | 180 |

|            |      | Related work                                         | 181 |

|            | 13.8 | Summary                                              | 182 |

### xvi contents

| 37 |

|----|

|    |

| 37 |

| 88 |

|    |

| 1  |

| 3  |

|    |

### LIST OF FIGURES

| 1  | A two-dimensional integer set (dense) 12                          |    |

|----|-------------------------------------------------------------------|----|

| 2  | A two-dimensional integer set (sparse) 13                         |    |

| 3  | A two-dimensional integer map 14                                  |    |

| 4  | Iteration Space – Unmodified 17                                   |    |

| 5  | Iteration Space – Tiled 18                                        |    |

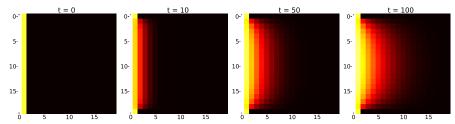

| 6  | Heat distribution after running the stencil in List-              |    |

|    | ing 1 28                                                          |    |

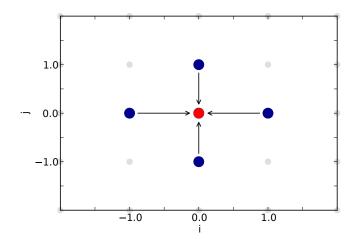

| 7  | Data-flow of the stencil in Listing 1 28                          |    |

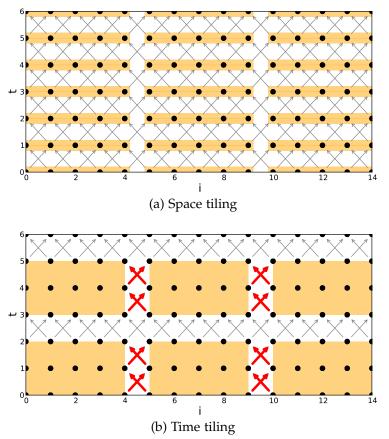

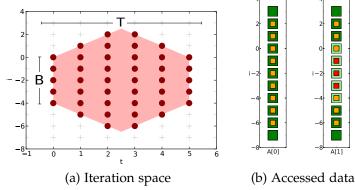

| 8  | Iteration space of 1D-space stencil 29                            |    |

| 9  | Rectangular tiling of 1D-space stencil 30                         |    |

| 10 | Iteration space of 1D-space stencil 31                            |    |

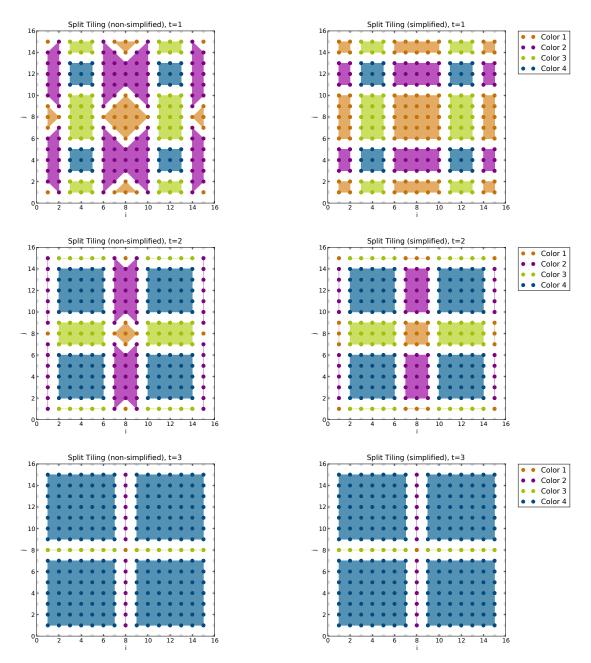

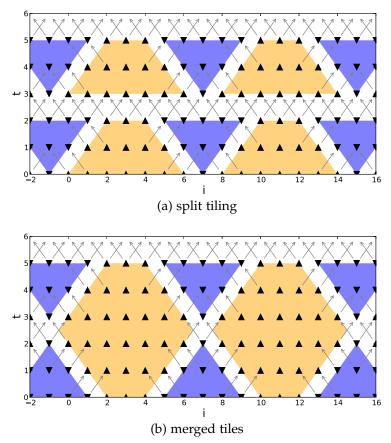

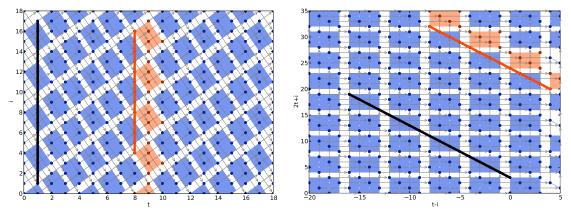

| 11 | Split tiling for the simple example (tile size $8 \times 3$ ). 38 |    |

| 12 | Split tiled jacobi-2d kernel 43                                   |    |

| 13 | Two statement kernel 44                                           |    |

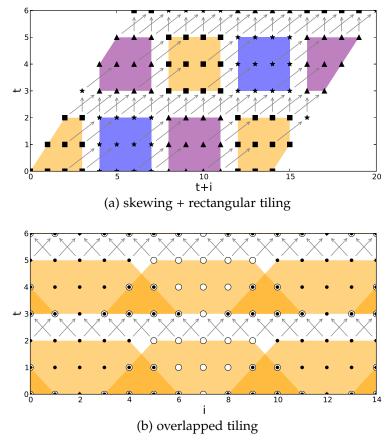

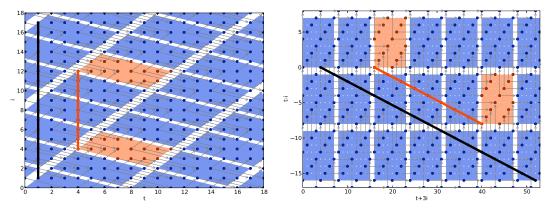

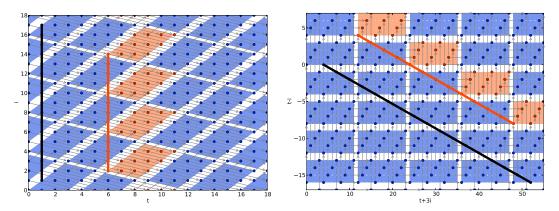

| 14 | 1D Hexagonal tiling - Created from 1D Split tiling 50             |    |

| 15 | Jacobi 2D stencil 51                                              |    |

| 16 | Generated PTX (CUDA bytecode) 51                                  |    |

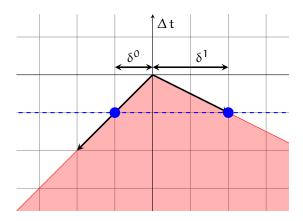

| 17 | Opposite dependence cone 53                                       |    |

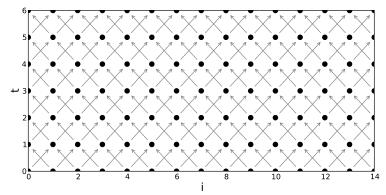

| 18 | A hexagonal tile 53                                               |    |

| 19 | Hexagonal tiling pattern 55                                       |    |

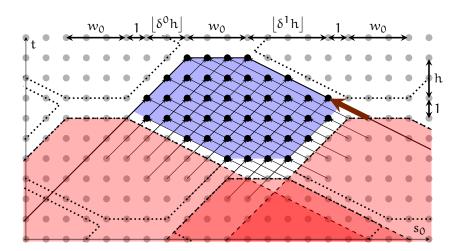

| 20 | n-dimensional tile schedule (±1 distances) 58                     |    |

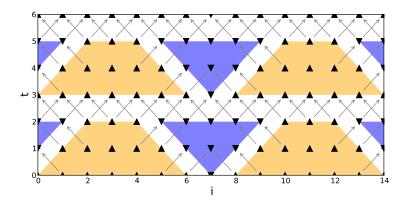

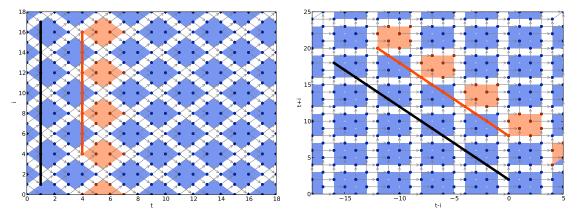

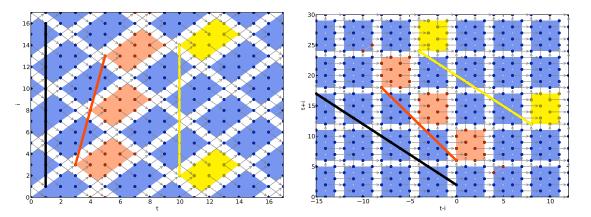

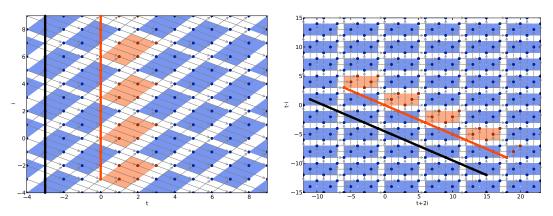

| 21 | Symmetric dependences & square tiling (original/transformed)      | 69 |

| 22 | Symmetric dependences & non-square tiling (origi-                 |    |

|    | nal/transformed) 69                                               |    |

| 23 | Asymmetric dependences & square tiling (original/transformed)     |    |

| 24 | Multiple time steps. Square tiles reduce parallelism.             |    |

|    | (original/transformed) 71                                         |    |

| 25 | Multiple time steps. Non-square tiles maximize par-               |    |

|    | allelism. (orig./trans.) 72                                       |    |

| 26 | Diamond tiling (original/transformed) 72                          |    |

| 27 | Hexagonal-tiling (original/transformed) 72                        |    |

| 28 | The stretching in the transformed space (unstretched/stretched)   | 7  |

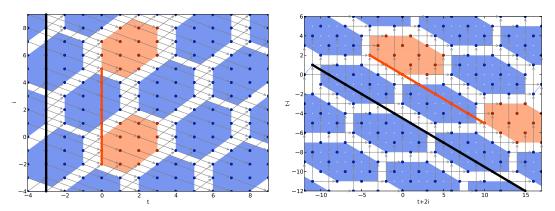

| 29 | 1D hexagonal tiling $(T = 6, B = 4)$ 78                           |    |

| 30 | The first two time steps of 1D hexagonal tiling (T =              |    |

|    | 6, B = 4) 79                                                      |    |

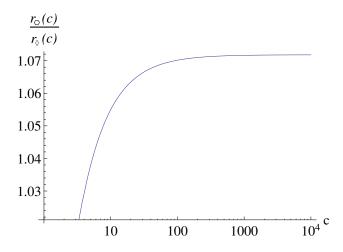

| 31 | Compute-to-read ratio - Hexagonal vs. diamond tiling 80           |    |

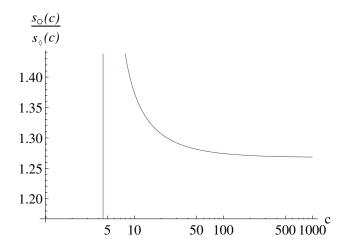

| 32 | Compute-to-sync ratio - Hexagonal vs. diamond tiling 81           |    |

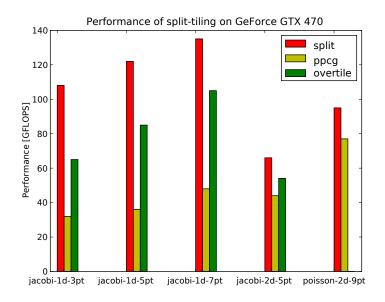

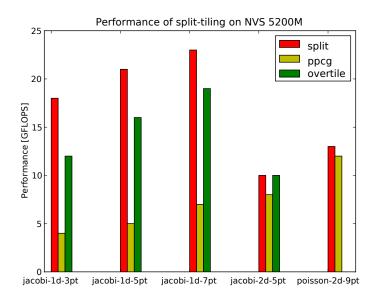

| 33 | Split-tiling performance (desktop GPU) 84                         |    |

| 34 | Split tiling performance (mobile GPU) 84                          |    |

| 35 | Copy code from hybrid hexagonal/parallelogram tiling              |    |

| -  | (a single loop) 114                                               |    |

xvii

| 36 | Copy code from hybrid hexagonal/parallelogram tiling        |

|----|-------------------------------------------------------------|

|    | (unrolled) 116                                              |

| 37 | Example Program 117                                         |

| 38 | Interleaved schedule without code generation options 119    |

| 39 | Interleaved schedule with code generation options 121       |

| 40 | Modulo conditions (examples not supported by CLooG) 129     |

| 41 | Existentially quantified variables (examples not sup-       |

|    | ported by CLooG/codegen+) 130                               |

| 42 | Example schedule tree representation 138                    |

| 43 | Band forest representation of the schedule in Figure 42 146 |

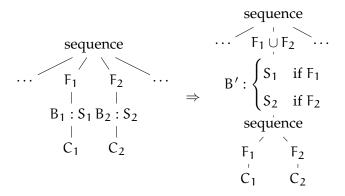

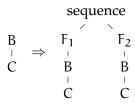

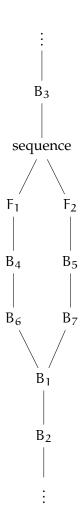

| 44 | Fuse bands B <sub>1</sub> and B <sub>2</sub> 150            |

| 45 | Order the active statement instances at B according         |

|    | to filters F <sub>1</sub> and F <sub>2</sub> 150            |

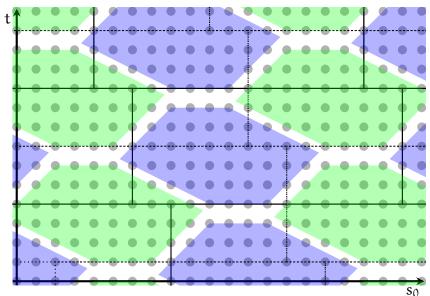

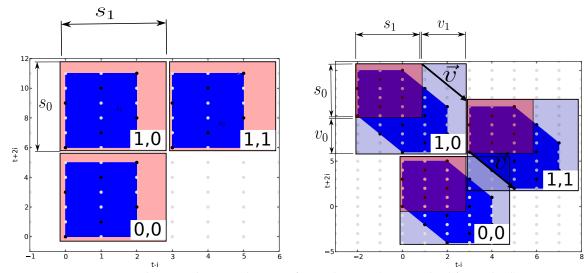

| 46 | Input pattern for hybrid tiling 151                         |

| 47 | Output pattern for hybrid tiling 152                        |

| 48 | Linearized expression for multi-dimensional array of        |

|    | constant size 161                                           |

| 49 | Linearized expression for multi-dimensional array of        |

|    | parametric size 162                                         |

| 50 | Subarrays accesses for different parameter values 168       |

|    |                                                             |

### LIST OF TABLES

| 1 | Performance on NVIDIA GTX 470: GStencils/second & Speedup 85 |     |

|---|--------------------------------------------------------------|-----|

| 2 | Performance on NVS 5200: GStencils/second & Speedup          | 85  |

| 3 | Characteristics of Stencils 86                               |     |

| 4 | Optimization steps: GFLOPS & Speedup 88                      |     |

| 5 | Performance counters (units of 10 <sup>9</sup> events) 89    |     |

| 6 | Features of different polyhedral extractors 108              |     |

| 7 | AST generation strategy based performance (GFLOPS)           | 132 |

| 8 | Comparison of some generic schedule representations          | 144 |

### LIST OF LISTINGS

| 1 | Implementatio | n of a | 5-point, | 2D-space, | jacobi-style |

|---|---------------|--------|----------|-----------|--------------|

|   | heat stencil  | 27     |          |           |              |

|   |               |        |          |           |              |

- 2 Split tiled code 39

- 3 A trivial program 100

| 4  | Part of CLoob output for thomasset test case 104      |

|----|-------------------------------------------------------|

| 5  | Unsigned operation in loop bound 105                  |

| 6  | Invalid fusion of program in Listing 5 105            |

| 7  | Loop with unsigned iterator 105                       |

| 8  | Trivial unrolling example 123                         |

| 9  | Unrolling in the presence of strides 123              |

| 10 | Unrolling in case of bound, non-constant number of    |

|    | iterations 124                                        |

| 11 | Unrolling with two lower bounds 125                   |

| 12 | Partial unrolling - original loop nest 125            |

| 13 | Partial unrolling - tiled 126                         |

| 14 | Partial unrolling - tiled + unrolled 126              |

| 15 | Partial unrolling - tiled + unrolled + isolated core  |

|    | computation 127                                       |

| 16 | A single loop marked parallel using LLVM metadata 159 |

| 17 | Nested loops marked parallel using LLVM metadata 159  |

| 18 | A gemm kernel written in C99 using variable length    |

|    | arrays 162                                            |

| 19 | A gemm kernel written using manually implemented      |

|    | multi-dimensional arrays. 164                         |

| 20 | Array dimensions used in subscripts 169               |

| 21 | A gemm kernel written in C++ using boost::ublas 180   |

| 22 | A gemm kernel written in Julia 180                    |

### LIST OF ACRONYMS

AST Abstract syntax tree

CLooG Chunky loop generator

clang The LLVM C/C++ compiler

CPU Central processing unit

CUDA NVIDIA's parallel computing platform

DSL Domain specific language

DRAM Dynamic random-access memory

FPGA Field Programmable Gate Array

gcc gnu compiler collection

GPU Graphics processing unit

GPGPU General-purpose computing on graphics processing units

#### XX ACRONYMS

ILP Integer linear programming

IP Intellectual property

IR Intermediate representation

isl Integer set library

LLVM LLVM compiler infrastructure

LLVM-IR LLVM intermediate representation

OpenCL Open compute language

OpenMP Open multi-processing

PPCG Polyhedral parallel code generator

PTX Parallel thread execution (NVIDIA IR)

SCC Strongly connected component

SCEV Scalar evolution

SCoP Static control part/program

SIMD Single instruction multiple data

SPU Stream processing unit

# Part I INTRODUCTION

INTRODUCTION

The steadily growing complexity of problems solved in scientific and high performance computing has caused a continuous hunger for compute power. The same growth can be seen with mobile devices, which have been turned into personal super computers driven by the increasing demands of gaming and image processing. Looking back twenty years, the most powerful supercomputer as published on the TOP500 supercomputer list [52] of July 1994 had a theoretical peak performance of 236 GFLOPS (double precision) with a power consumption of almost 500.000 Watts. Today, NVIDIA claims a peak performance of 365 GFLOPS (single precision) with 5 Watt power consumption for their recently announced mobile platform Tegra K1 [45]. Even though those numbers are not directly comparable, they show clearly that large compute capabilities have reached mobile. And, with 54,902 TFLOPS peak performance at the top of today's Top500 list [52], supercomputers did not stand still either.

A major factor for this enormous progress in compute power and energy efficiency is, besides others, the increasingly *specialized* and *heterogeneous* hardware. Both mobile devices and super computer nodes rely today on multi or many cores, short vector instructions, various levels of caches and often dedicated accelerators. For programs to benefit, they need to be optimized to effectively exploit the available hardware.

In the world of supercomputers it was common to optimize important programs manually. Today manual optimization is, even on supercomputers, increasingly complemented with automatic program generation and search space exploration. In the mobile market the sheer number of different hardware platforms makes manual optimization impractical. This becomes evident just by looking at the mobile GPU market alone, where there are over ten entirely different hardware designs a program needs to be tuned for. IP suppliers such as ARM, DMP, Imagination Technologies, or Vivante and vertically integrated suppliers such as AMD, Intel, Nvidia, and Qualcomm, all provide their own designs, in addition to which vendors such as Samsung and Broadcom use their own internal designs [111]. On Android, the most widely used mobile platform, direct accelerator access is not even possible. Instead the RenderScript compute interface was designed with automatic performance optimization as a design goal.

"While testing and tuning a variety of devices is never bad, no amount of work allows them to tune for unreleased hardware they don't yet have. A more portable solution places the tuning burden on the runtime, providing greater average performance at the cost of peak performance." [Jason Sams, RenderScript Tech Lead, 112]

We can conclude that advances in automatic optimization of compute programs are important.

Automatic compiler optimizations have a long history [14]. In the context of this work, the optimization of loop programs is of particular interest. Loop optimizations had already been investigated in the context of FORTRAN compilers over thirty years ago. Together with early work on data dependence analysis [22], as well as the introduction of the data dependence graph [85], loop transformations such as fusion and fission have been introduced to improve program performance e.g., by enabling better use of vector hardware. For the very same reason automatic loop interchange has been discussed [15] and, to reduce expensive memory movements, loop blocking [12, 139] was introduced. Even though the precision of data dependence computation has increased throughout the years and loop transformations have evolved notably, the basic concept of taking a loop nest and optimizing it step-by-step by applying a set of individual loop transformations remains important today, with many production C/C++/FORTRAN compilers relying on the use of these "classical loop optimizations". Important work on classical non-trivial loop transformations has been performed in several commercial compilers such as the KAP compiler or icc, but also in research compilers such as Parafrase [98], Polaris [34], PIPS [74], SUIF [136] or Cetus [50].

Even though classical loop transformations are well understood, finding and reasoning about the right sequence to apply them in is hard. To address this problem researchers have investigated the possibility of computing an entirely new loop structure [58, 57] directly from a set of data dependences without ever applying any loop transformations, or of deriving combinations of classical loop transformations using a single unifying loop transformation theory [137, 138]. As a result of this research the polyhedral model (Chapter 2) evolved, a generic and compiler independent way to reason about complex loop nests and their transformation. Within the last two decades this model has been heavily investigated and regularly serves as an instrument to address challenging optimization problems. In fact, it often enables transformations difficult or even impossible to describe with classical loop transformations. One such use case are recent C to GPU code translators [24, 135] which have shown that polyhedral techniques can even be used for complex program transformations such as the generation of code to exploit software managed caches. Another interesting use case is a recent paper discussing the combination of SIMD code generation and polyhedral loop optimization techniques [83], a nice example of how to parameterise target independent loop transformations to obtain competitive platform specific code.

Even though polyhedral loop transformation frameworks have many benefits, at the moment they are, with the exception of IBM XL [36], mainly employed by research focused compilers [87, 35, 135, 40, 136]. Existing C/C++ open source compilers such as gcc or LLVM currently do not take advantage of polyhedral loop transformations in their default optimization sequence, despite the existence of loop transformation frameworks such as gcc/graphite [122] and LLVM/Polly [3]. As both compilers also do not incorporate an extensive set of classical loop transformations, programs [65] are required to incorporate program specific transformations in their source code which reduces performance portability and increases code bloat.

Domain or problem specific solutions are also hindered by the lack of generic loop transformation systems. Julia [31], a just-in-time compiled language specialized on scientific computing, does for example not leverage any loop optimization opportunities, even though their scientific compute kernels would strongly benefit. "Automatic" GPU code generation still requires explicit user annotated kernel code as proposed for example by openacc [64]. Anything more complicated is left to DSL compilers which hardcode specific transformations [70, 68]. Even though DSL compilers commonly obtain great performance, the ad hoc implementation of the required loop transformation causes redundant work and, most importantly, the benefits a generic and formal transformation framework would bring are missed. Overall, there is a strong need for making generic loop transformations more accessible.

Motivated by the missing reuse of loop optimization and the growing, but still lacking, adoption of polyhedral loop optimization techniques that could facilitate such reuse, we aim in this work to widen the scope in which polyhedral loop optimizations can be used effectively. As a driving force we develop a set of advanced domain specific loop optimizations that enable the efficient execution of stencil computations on GPUs. Stencil computations (Chapter 3) as discussed in this work are computations that iteratively recompute the elements of a (multi-)dimensional data space, just from the neighborhood of each individual element. Optimizing their execution is difficult and often requires sophisticated optimization strategies. However, in contrast to many existing works, we specifically avoid the implementation of a specialized optimizer. Instead, we aim for a solution that clearly separates domain and target specific optimizations from non-problem specific code generation strategies and techniques necessary to obtain peak performance. We do this by developing new problem specific tiling schemes, which are translated to highly performant code by a general purpose infrastructure that has only been parameterized to ensure the generation of optimal code. As a result we hope to show that polyhedral loop optimization techniques can be successfully used even in highly performance critical codes without the need to implement specialized code generation strategies.

Following the concept of reusability, we aim to make loop transformations less compiler dependent to facilitate the transfer of optimizations between different generic and domain specific compilers. To reach this goal we do not only take special care throughout this work to highlight and address corner cases that may inhibit the use of our work in production, but we specifically present a set of polyhedral building blocks. Such building blocks do not only enable our new stencil optimizations, but they are designed for reusability in the context of different domain specific and general purpose compilers. Going one step further, we present new work in the context of the LLVM compiler infrastructure that prepares the path for later integration of our optimizations in a low-level static compiler.

#### 1.1 OUTLINE

After some background information on integer sets and polyhedral compilation given in Chapter 2, the following topics will be discussed in this thesis.

### Tilings and Optimizations for Stencils

Our work on developing new tiling schemes that allow the efficient execution of iterative stencil computations and similar compute patterns on GPUs.

- In Chapter 4 we discuss the implementation of a split tiling scheme that enables the time tiled execution of stencil computations on GPUs ensuring balanced coarse-grained parallelism without the need for redundant computations. We discuss the implementation of this tiling scheme in a general purpose polyhedral optimizer, including a set of optimizations that enable the use of software managed shared caches on GPUs.

- In Chapter 5 we discuss an extension and specialization of our previous work on split tiling. The result is a new tiling scheme combining hexagonal tiling on one dimension with parallelogram tiling on the remaining dimensions. This new tiling scheme allows us to better address important GPU specific concerns now being able to ensure the absence of thread divergence and the use of coalesced and aligned loads. As a result, we obtain a tiling scheme that can, even for 3D test cases, profitably use software managed shared caches on GPUs.

• In Chapter 6 we present a detailed theoretical analysis of diamond tiling, a tiling scheme closely related to our hexagonal tiling work. In the context of this analysis we present new insights on constraints that diamond tiling poses on tile-sizes and on wavefront coefficients. We complement these results with a set of conditions that ensure that the integer points contained in different tiles are placed at identical offsets. We then unify the two tiling schemes by providing a formulation of hexagonal tiling for 2 dimensional problems (1 time dimension, 1 space dimension) in the framework of diamond tiling. We complete this chapter with an analysis of tile sizes that yield optimal compute-to-communication and compute-to-synchronization ratios.

### **Polyhedral Building Blocks**

A set of polyhedral building blocks that have been developed to facilitate and generalize the use of polyhedral schedule and data layout transformations and their use in imperative programs.

- In Chapter 9 we present a polyhedral extraction tool that, by combining a real C compiler with an advanced integer set library, pushes the limits of the amount of statically analyzable code that can be translated to a polyhedral representation. By presenting how to model integer wrapping with modulo constraints, we ensure correctness even in difficult areas of the C standard.

- In Chapter 10 we present a new AST generator with complete support for Presburger relations including support for piecewise schedules and their use to express index set splitting as a schedule-only transformation. Going beyond the generation of control flow, we support the generation of AST expressions from arbitrary user provided piecewise quasi affine expressions. New simplification methods for AST expressions allow the exploitation of local context information to generate fast modulo and division operations. With fine grained options we give the user precise control over AST generator decisions. Finally, we provide support for heavy specialization through polyhedral unrolling and user directed versioning.

- In Chapter 11 we provide a detailed analysis of existing approaches to describe polyhedral schedules as well as their uses within the polyhedral tool chain. We then derive a new approach to describe polyhedral schedules which makes the inherent tree structure of polyhedral schedules explicit and which we use to provide a more intuitive formulation of the schedule generated by hybrid-hexagonal tiling.

### **Low-level Compilers**

- We will briefly discuss various projects that have taken place in the context of Polly, our high-level loop optimizer for LLVM. This includes the need for compute outs to bound compile time, GPolly a project to bring automatic GPU code generation to a low-level compiler, our experience with using the isl AST generator in Polly as well as work on how to annotate parallelism on LLVM-IR.

- In Chapter 13 we discuss a new approach to delinearize a multivariate polynomial expression to an access to an array shape of parametric size. In our work we show how optimistic delinearizations enables us to delinearize expressions where the delinearization can not be proven statically. We evaluate our work on code written with Julia, boost::ublas and C99 variable length arrays.

# Part II BACKGROUND

Polyhedral compilation uses a compact mathematical representation to precisely model the individual elements of a compute program. The use of a solid mathematical model enables detailed static analysis and exact transformations. Dynamic extensions [30] are available for programs that lack static information. The following chapter gives an introduction to the mathematical concepts and explains how they are used to model, analyze and transform compute programs.

#### 2.1 MATHEMATICAL FOUNDATIONS

(Integer) polyhedra [89] or Presburger relations [106, 105] are the mathematical foundations of polyhedral compilation. In this section we give an introduction to the most important concepts. The notations [131, 130] presented are the ones proposed by isl [128], the integer set library we use for our work. isl itself is built around Presburger relations and uses many ideas originally introduced in the Omega project [81]. Another important concept used at the core of isl is parametric integer programming [55].

### 2.1.1 *Integer sets*

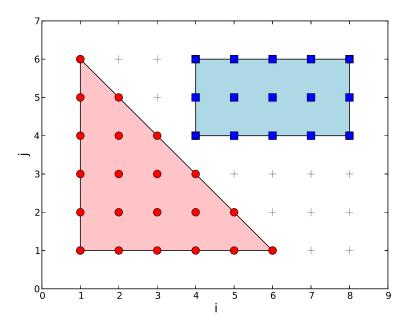

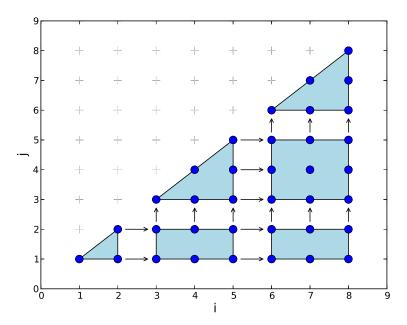

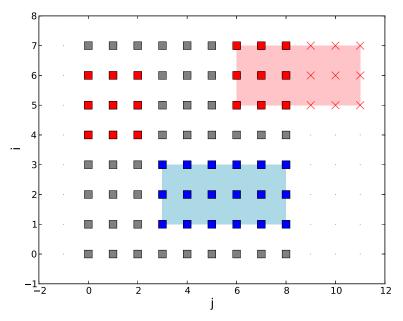

Integer sets as defined by isl are sets of integer tuples from  $\mathbb{Z}^d$  described by Presburger formulas.  $S = \{(i,j) \mid (\alpha \leqslant i,j \land i+j < b) \lor (4 \leqslant i,j \land i \leqslant b \land j \leqslant 6)\}$  is an example of a two-dimensional integer set described in terms of two parameters  $\alpha$  and  $\beta$ . Figure 1 illustrates  $\beta$  for  $\alpha = 1$  and  $\beta = 8$ . It shows a triangular red shape containing red points and a rectangular blue shape containing blue squares. Only the red points/blue squares located at the integer coordinates within the colored shapes are the actual elements of  $\beta$ . The colored shapes have been derived from the description of the integer set. They form a set of convex shapes that enclose the elements of  $\beta$  and help to visualize  $\beta$ . As there are generally different ways to represent an integer set, such visualizations are not unique.

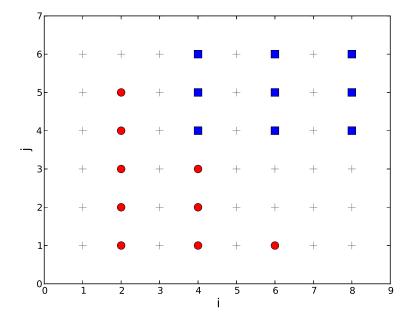

Figure 2 illustrates a second set  $S' = \{(i,j) \mid (\alpha \leq i,j \wedge i + j < b \wedge (i) \mod 2 = 0) \vee (4 \leq i,j \wedge i \leq b \wedge j \leq 6 \wedge i \mod 2 = 0)\}$ . It is similar to S with the only difference being that additional modulo constraints have been added that permit only even values on the idimension. Visualizing S' with a set of convex shapes that enclose its elements is hindered by the modulo constraints. Therefore, we

Figure 1: A two-dimensional integer set (dense)

illustrate S' by directly highlighting the points and squares that are part of the integer set.

In general, an integer set has the form

$$S = \{\vec{s} \in \mathcal{Z}^d \mid f(\vec{s}, \vec{p})\} \tag{1}$$

with  $\vec{s}$  representing the integer tuples contained in the integer set, d the dimensionality of the set,  $\vec{p} \in \mathcal{Z}^e$  a vector of e parameters and  $f(\vec{s}, \vec{p})$  a Presburger formula that evaluates to true,  $iff(\vec{s}, \vec{p})$  is element of  $\vec{s}$  for given parameters  $\vec{p}$ .

A Presburger formula p is defined recursively as either a boolean constant  $(\top, \bot)$ , the result of a boolean operation such as negation, conjunction, disjunction or implication  $(\neg p, p_1 \land p_2, p_1 \lor p_2, p_1 \Rightarrow p_2)$ , a quantified expression  $(\forall x: p, \exists x: p)$  or a comparison between different quasi-affine expressions  $(e_1 \oplus e_2, \oplus \in \{<, \le, >, >\})$ . A quasi-affine expression¹ e is defined as a plain integer constant (e.g., 10), a parameter, a set dimension or a previously introduced quantified variable. It can also be constructed recursively as the result of a unary negation of a quasi-affine expression (-e), a multiplication of an integer constant with a quasi-affine expression (e.g., 10e), an addition/subtraction of two quasi-affine expressions  $(e_1 \oplus e_2, \oplus \in \{+, -\})$ , an integer division of a quasi-affine expression by a constant (e.g., |e/10|) or the result of computing a quasi-affine expression modulo

<sup>1</sup> We use the term quasi-affine [54, 55] to describe the potential use of existentially quantified variables which are, besides set and parameter dimensions, needed to internally model constructs such as integer divisions, the modulo operations or quantified expressions as affine inequalities.

Figure 2: A two-dimensional integer set (sparse)

a constant (e.g.,  $e \mod 10$ ). The set  $\{\vec{s} \mid \top\}$  is called the universal set or the universe and is commonly abbreviated as  $\{\vec{s}\}\$ .

There are also various properties and operations that can be computed on integer sets. We present the most important ones. Given a single set we can check if the set is empty, if it is the universal set or if a certain dimension always has a fixed value. We can also ask for a sample value contained in the set, for the minimal/maximal value of a certain dimension or the lexicographically smallest/largest element of a set. Two sets can be checked for equality, disjointness or the existence of a subset relation. It is also possible to derive new sets by computing the complement of a set, by projecting out dimensions from a set or by adding new dimensions to a set. A set can be approximated by computing various hulls (convex, affine, simple, polyhedral). Two sets can be combined by intersecting them, computing their union or the difference between them. The properties and operations presented generally follow known mathematical semantics and notations. In case uncommon notations are used they will be explained at the point of usage.

### 2.1.2 Integer maps

Integer maps are binary relations between integer sets. The first set in the relation is called the *domain* or the input set, the second set is the *range* or the output set. Integer maps are modeled as pairs of integer tuples from  $\mathbb{Z}^{d_1} \times \mathbb{Z}^{d_2}$ .

Figure 3: A two-dimensional integer map

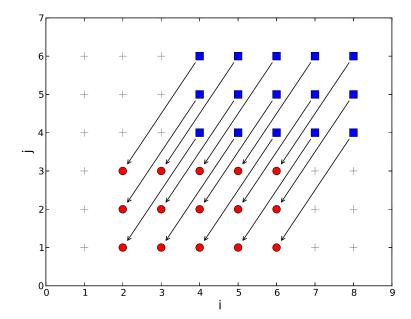

Figure 3 illustrates the integer map  $M = \{(i,j) \to (i-2,j-3)\}$  with the input values restricted to the elements contained in the blue rectangular of Figure 1. Each black arrow represents a relation between one input tuple and one output tuple. The input values (blue squares) shown are the very same values as illustrated in Figure 1. The output values (red circles) are the same values, but translated according to M.

The general form of an integer map is

$$M = \{\vec{i} \to \vec{o} \in \mathcal{Z}^{d_1} \times \mathcal{Z}^{d_2} \mid f(\vec{i}, \vec{o}, \vec{p})\}$$

(2)

where  $\vec{i}$  describes the  $d_1$ -dimensional input tuples,  $\vec{o}$  the  $d_2$ -dimensional output tuples,  $\vec{p} \in \mathcal{Z}^e$  a vector of e parameters and  $f(\vec{i}, \vec{o}, \vec{p})$  a Presburger formula that evaluates to true,  $iff \ \vec{i}$  and  $\vec{o}$  are related in M for given parameters  $\vec{p}$ . Integer maps can represent arbitrary relations and can, contrary to what the use of the " $\rightarrow$ " notation suggests, relate multiple output values to a single input value. The Presburger formulas that describe integer maps follow the rules presented for integer sets with the only difference, that they now reference  $\vec{i}$  and  $\vec{o}$  instead of  $\vec{s}$ . The description of an integer map  $\{\vec{i} \rightarrow (o_1, \ldots, o_{d_2}) \mid o_1 = f_1(\vec{i}, \vec{p}), \ldots, o_{d_2} = f_{d_2}(\vec{i}, \vec{p})\}$  is often syntactically shortened to  $\{\vec{i} \rightarrow (f_1(\vec{i}, \vec{p}), \ldots, f_{d_2}(\vec{i}, \vec{p}))\}$ , as shown in our example.

Various properties and operations are defined on integer maps. Most of them are similar to the ones on integer sets, but can often be applied to either the entire map or just its range or domain. One interesting operation is the "application" of a map to a set. In the previous example, we can *apply* M to the blue squares and the result

will be the set of red circles. Similarly, it is possible to apply maps to the ranges or domains of other maps. The result of this "chaining" of maps is a map that performs the combined mapping of the input maps. It is also possible to reverse maps to change the meaning of input and output dimensions, as well as to obtain the input set (domain) or the output set (range) of a map.

### 2.1.3 Named unions sets/named union maps

It is possible to name integer sets and maps according to where they are used or what they represent. Named integer sets are integer sets which contain named tuples. An example is the set  $\{S(i,j)\}$  which is an integer set that lives in a two-dimensional space with the name "S". We define named integer maps as integer maps between two named spaces. The map  $\{S(i,j) \rightarrow A(i)\}$  is an example of a named integer map. It is also possible to define integer sets that contain tuples from different spaces, e.g.  $\{S1(i,j);S2(i)\}$ . Such sets are called (named) union sets. Named union maps are defined accordingly. Operations that can be performed on sets and maps can often be performed on union sets and maps. In case we use such operations with non-obvious semantics, the actual semantics will be explained at the point of use. We may omit the prefix 'named' or 'union' in cases where it is either obvious or not relevant for the discussion.

### 2.1.4 Libraries for integer sets / maps

There exist several libraries that can express and modify integer sets or related data structures. isl [128], as discussed earlier, is the integer library we use for our work. It directly supports the operations and notations given above. Aside from isl, there is the Omega library [81] which, having served as a source of inspiration for isl, supports similar notations and operations. However, omega does not support the concepts of named sets (maps) or union sets (maps). isl and omega differ in the algorithms and internal data structures used. While isl relies on integer division in its internal representation, omega uses intersections of polyhedra and lattices to represent integer sets and maps.

In certain (common) situations it is also possible to approximate integer sets by a set of rational polytopes that enclose the points in the integer set. PolyLib [88] and PPL [20] are libraries which have been originally developed to perform computations on such rational polytopes. In case computations can be performed on rational polytopes, their use may reduce the theoretical (and practical) computational complexity at the cost of a reduced precision. PolyLib later gained support for computations on so called  $\mathfrak{Z}$ -polyhedra, polyhedra that model only the integer points they contain. PPL also supports inte-

ger lattices and allows the creation of objects that have the properties of both lattices and polyhedra, a feature that can possibly be used to model integer sets. While representing integer sets with the above libraries is possible, our experience has shown that doing so can be inconvenient. First, there is a certain risk for the library user to accidentally use rational computations for operations where integer computations are needed. This may result in incorrect results being obtained. Second, to model certain integer sets correctly additional helper dimensions (existentially quantified dimensions) need to be introduced, which the user of these classical libraries needs to keep track of manually. In contrast, native integer set libraries keep track of such dimensions automatically. As we make heavy use in our work of features that require existentially quantified dimensions (modulo constraints and integer divisions), we choose to use an integer library that supports them natively.

#### 2.2 MODEL AND TRANSFORM IMPERATIVE PROGRAMS

Polyhedra or, in our case, integer sets and maps can be used to model "sufficiently regular" compute programs with the goal to reason about and precisely control higher-level properties without distraction from imperative or lower-level constructs. To do so the individual statement instances in a program (i.e., each dynamic execution of a statement inside a loop nest), their execution order as well as the individual array elements accessed are modeled, analyzed and transformed, whereas control flow constructs, loop induction variables, loop bounds or array subscripts are hidden and only regenerated when converting a transformed loop nest back to imperative constructs.

## 2.2.1 *An illustrative example*

We start with a simple piece of code that consists of a single compute statement S, which is surrounded by two loops, the i-loop and the j-loop. Data is loaded and stored to a two-dimensional array A.

```

for (i = 1; i <= n; i+=1)

for (j = 1; j <= i; j+=1)

S: A[i][j] = A[i-1][j] + A[i][j-1];</pre>

```

To model this computation we construct four data structures. An *iteration space* I, a *schedule* S as well as a relation of *read-accesses*  $A_{read}$  and a relation of *must-write-accesses*  $A_{write}$ . I is an integer set that describes the set of statement instances that is executed. It gives no information about the execution order of these statement instances. S is an integer map that assigns to each statement instance a possibly multi-dimensional time. It allows us to define an execution order

Figure 4: Iteration Space - Unmodified

by sorting the statement instances according to the lexicographic order of their time stamps.  $A_{read}$  and  $A_{write}$  are integer maps which define for each statement instance the memory locations that are accessed.

For our example, we get the following model:

$$\begin{split} I &= \{S(i,jj) \mid 1 \leqslant j \leqslant i \leqslant n\} \\ S &= \{S(i,j) \rightarrow (i,j)\} \\ A_{read} &= \{S(i,j) \rightarrow A(i-1,j); S(i,j) \rightarrow A(i,j-1)\} \\ A_{write} &= \{S(i,j) \rightarrow A(i,j)\} \end{split}$$

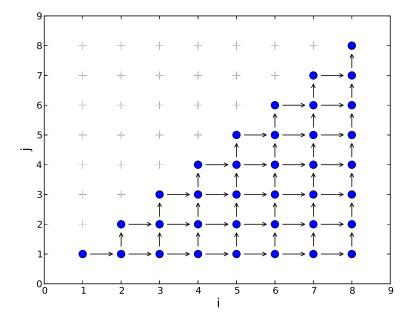

The illustration of I in Figure 4 represents each statement instance with a single dot. The arrows between such statement instances illustrate data flow dependences modeled by an integer map  $D = \{S(i,j) \rightarrow S(i,j+1); S(i,j) \rightarrow S(i+1,j)\}$ . Those dependences relate statement instances with the statement instances they depend on. Computing precise data-flow dependences [54, 104, 92] is one analysis that is significantly facilitated by the use of an integer set based representation.

We now try to improve data-locality by ensuring that statement instances that operate on the same data elements are executed in close time proximity. The data dependences force us to ensure that each statement instance is always mapped to a point in time that is later than the execution time of all statement instances it depends on. However, within these constraints we are free to modify the schedule. A common transformation to increase data locality is loop tiling. Loop

Figure 5: Iteration Space - Tiled

tiling is in this case both legal and effective. To implement loop tiling we define a new schedule

$$S' = \{S(i)(j) \to (|i/3|)(|j/3|)(i)(j)\}$$

which defines an execution order where the statement instances are always executed in blocks of size  $3 \times 3$ . The new execution order is illustrated in Figure 5 and is shown in two levels. At the higher level, the blue blocks are executed in lexicographic order. At the lower level, within the individual blue blocks, the statement instances are again executed in lexicographic order. As statement instances that are close by are placed in the same block, they are also executed close by in time.

Up to this point, the transformation has only be applied at the level of our abstract model. To materialize it, it is necessary to generate imperative code according to it. For this we use a polyhedral AST generator (discussed in Chapter 10) which translates our abstract schedules back into a set of imperative loops and conditions. For the example above the following AST could be generated.

```

for (i = 1; i <= n/3; i+=1)

for (j = 1; j <= n/3; j+=1)

for (ii = max(1,3 * i); ii <= min(n, 3*i+2); ii+=1)

for (jj = max(ii, 3 * j); ii <= min(n, 3*j+2); jj+=1)

S: A[ii][jj] = A[ii-1][jj-1];</pre>

```

# 2.2.2 What programs can be modeled?

A program that is "sufficiently regular" to be modeled, analyzed and transformed using integer sets and maps is traditionally called Static control part/program (SCoP) [56, 25]. What is considered a SCoP depends on what can be translated to an integer set based description and may look very different in the context of source-level C/C++ code [28][10], Graphical Dataflow Languages [33] or compiler IRs [122][3]. Ongoing research continuously widens the set of programs that can be modeled both by using approximation, but also by extending the underlying model [127, 30] and the generality of tools that extract this model. To give the reader an idea of how a SCoP may be defined, we present a set of common imperative constructs that can be translated into a polyhedral representation. For a precise and complete description of what state-of-the-art C/C++ code extractor can translate we refer to Chapter 9.

A SCoP is a program (region) that consists of a set of *statements* possibly enclosed by (not necessarily perfectly) *nested loops* and *conditional branches*. Within this region read-only scalar values are called *parameters*. The statements in the SCoP are side effect free, besides explicit *reads* and *writes* to multi-dimensional arrays or scalar values. Loops are regular loop bounds with a single lower and a single upper bound and increments by fixed, positive integers (i+=10). Both loop bounds and array accesses are (piecewise-quasi) affine expressions in terms of parameters and induction variables of outer loops.

# 2.2.3 The polyhedral representation

The representation we use to model SCoPs consists of the following components:

- ITERATION SPACE/DOMAIN The set of statements instances that are part of a SCoP. It is modeled as a named union set, where each named component of the union set describes a statement, with individual instances of a statement being described by the elements contained in the corresponding named set.

- ACCESS RELATIONS A set of read, write and may-write access relations relate statement instances to the data-locations they access. These access relations are modeled as named union maps.

- DEPENDENCES A relation between statement instances that defines restrictions on the execution order, due to producer-consumer relationships or the shared usage of certain data locations. Data dependences are modeled as named union maps.

- SCHEDULE An execution order which assigns each statement instance a multi-dimensional execution time. One statement instance is

executed before another statement instance, if its execution time is lexicographically smaller.

It is important to note that there is a strong separation between the statement instances themselves and the order in which they are executed. Program optimizations that do not change the set of statements that are executed, but only change the order they are executed in, consequently only affect the schedule.

We also want to note that there is a relation between the dependences and the schedule. A schedule is only valid if it is of a form such that all data-dependences go forward in time. This means, if we take the data dependences and apply the schedule to the related statement instances to translate them to the scheduling time they are executed at, the time at the source of the dependence must be lexicographically strictly smaller than the time at the target. Also, we know that given a set of dependences, we can compute a schedule and, vice versa, given an iteration space, access relations and a schedule the corresponding data dependences can be computed.

In contrast to many previous works we distinguish between (must) write and may write accesses. This distinction is important to understand if a certain write always overwrites a specific data-location and consequently makes previously written data inaccessible or if previously written data may possibly remain intact and accessible for later reads. This difference is important as in the former case data-dependences only need to be computed from the last write to subsequent reads whereas in the latter case data-dependences to all previous may writes up to the next must write access need to be computed. There is no need to track may read accesses separately.

## 2.2.4 Transformations

The use of integer sets or polyhedra to perform loop optimizations has a long tradition, both in the history of automatic parallelization, but also in the optimization of sequential code. Compared to classical loop transformations the use of integer sets as a mathematical model has several advantages. Besides the ability to use mathematical tools to reason about the possible transformations, they simplify the composition of transformations and they allow us to express transformations that are otherwise difficult or even impossible to express.

We can group loop transformations according to what program properties are modified:

- The order in which computations are performed

- The loop structure, but not the order of computation

- The data layout and the data locations accessed

- The computation (algorithmic changes)

The first three kinds of transformations are regularly modeled with integer sets, whereas modeling algorithmic changes is more difficult, but possible in some cases [140]. Integer sets are also used for accelerator programming and vectorization, but such transformations are mostly a combination of execution reordering and data layout transformations supplemented with the generation of specialized target instructions or library calls. We will use such GPU code generation techniques in Part iii. In this section we focus on basic computation reordering transformations, which will be used and extended later in this work.

Classical transformations that reorder computations are fusion, fission, reversal, interchange, strip-mining, and skewing. They all change the order statements instances are executed in and can consequently be modeled by schedule transformations. The same holds for combinations of such elementary transformations that yield tiling or unroll-and-jam. The subsequent examples illustrate these transformations as well as the corresponding iteration spaces  $\mathfrak I$ , the original schedule  $\mathfrak S_\mathsf T$ .

```

// Original loops

for (i=1; i<n; i+=1)

S1(i);

Fusion

\mathfrak{I} = \{ \mathsf{S1}(\mathfrak{i}) : \mathsf{1} \leqslant \mathfrak{i} < \mathsf{n} ;

for (i=1; i<m; i+=1)

S2(i): 1 \leqslant i < m

S2(i);

S = \{S1(i) \rightarrow (0, i);

// Fused loops

S2(i) \rightarrow (1,i)

for (i=1; i < min(n,m); i+=1) {</pre>

\mathfrak{T} = \{(0,i) \to (i,0);

S1(i);

(1,i) \rightarrow (i,1)

S2(i);

S_T = \{S1(i) \rightarrow (i,0);

}

S2(i) \rightarrow (i,1)

for (i=max(1,m); i<n; i+=1)</pre>

S1(i);

for (i=max(1,n); i<m; i+=1)</pre>

S2(i);

// Original loop

Fission

for (i=1; i<n; i+=1)</pre>

\mathfrak{I} = \{ \mathsf{S1}(\mathsf{i}) : \mathsf{1} \leqslant \mathsf{i} < \mathsf{n};

S1(i);

S2(i): 1 \leqslant i < n\}

S2(i);

S = \{S1(i) \rightarrow (i, 0);

S2(i) \rightarrow (i,1)

// Separated loops

\mathfrak{T} = \{(i,0) \to (0,i);

for (i=1; i<n; i+=1)</pre>

S1(i);

(i,1) \rightarrow (1,i)

S_T = \{S1(i) \rightarrow (0,i);

for (i=1; i<n; i+=1)</pre>

S2(i) \rightarrow (1,i)

S2(i);

```

```

// Original loop

Reversal

for (i=1; i<n; i+=1)</pre>

\mathfrak{I} = \{ \mathsf{S1}(\mathfrak{i}) : \mathsf{1} \leqslant \mathfrak{i} < \mathsf{n} \}

S1(i);

S = \{S1(i) \rightarrow (i)\}

\mathfrak{T} = \{(i) \to (-i)\}

// Reversed loop

for (i=1-n; i<0; i+=1)</pre>

S_T = \{S1(i) \to (-i)\}

S1(-i);

// Original loops

for (i=1; i<n; i+=1)</pre>

Interchange

\mathfrak{I} = \{ \mathsf{S1}(\mathsf{i},\mathsf{j}) : \mathsf{1} \leqslant \mathsf{i} < \mathsf{n} ;

for (j=1; j<m; j+=1)</pre>

S1(i,j);

\land 1 \leqslant j < \mathfrak{m}

S = \{S1(i,j) \rightarrow (i,j)\}\

// Interchanged loops

\mathfrak{T} = \{(i,j) \to (j,i)\}

for (i=1; i<m; i+=1)</pre>

S_T = \{S1(i,j) \rightarrow (i,j)\}

for (j=1; j<n; j+=1)

S1(j,i);

// Original loop

for (i=1; i<n; i+=1)</pre>

S1(i);

Strip-Mining

\mathfrak{I} = \{S1(\mathfrak{i}) : 1 \leqslant \mathfrak{i} < \mathfrak{n}\}

// Strip mined loop

S = \{S1(i) \rightarrow (i)\}

for (ti=0; ti<n; ti+=4)

\mathfrak{T} = \{(i) \to (4 * |i/4|, i)\}

for (i = max(1,ti);

S_{T} = \{S1(i) \rightarrow (4 * |i/4|, i)\}

i \leq min(n-1,ti+3);

i += 1

S1(i);

// Original loops

Skewing

for (i=1; i<n; i+=1)</pre>

\mathfrak{I} = \{ \mathsf{S1}(\mathsf{i},\mathsf{j}) : \mathsf{1} \leqslant \mathsf{i} < \mathsf{n} \}

for (j=1; j<n; j+=1)

S1(i,j);

\land 1 \leqslant i < m

S = \{S1(i,j) \rightarrow (i,j)\}

// Skewed loops

\mathfrak{I} = \{(i,j) \to (i,i+j)\}

for (i=1; i<n; i+=1)</pre>

S_T = \{S1(i) \rightarrow (i, i+j)\}

for (j=i+1; j<m+i; j+=1)</pre>

```

S1(i, j-i);

```

Tiling

\land 0 \le i < 1024

for (j=0; j<1024; j+=1)

S = \{S1(i,j) \rightarrow (i,j)\}

S1(i,j);

\mathfrak{T} = \{(\mathfrak{i}, \mathfrak{j}) \rightarrow

// Tiled loops

(4 * |i/4|,

for (ti=0; ti<1024; ti+=4)</pre>

4 * |j/4|, i, j)

for (tj=0; tj<1024; tj+=4)</pre>

S_T = \{S1(i) \rightarrow

for (i=tj; i<ti+4; i+=1)</pre>

(4 * |i/4|,

for (j=tj; j<tj+4; j+=1)

S1(i, j-i);

4 * |j/4|, i, j)

// Original loops

Unroll and Jam

\label{eq:continuous} \mathfrak{I} = \{S1(\mathfrak{i},\mathfrak{j}): 1\leqslant \mathfrak{i} < 1024 \text{ for (i=0; i<1024; i+=1)}

for (j=0; j<1024; j+=1)

\land 1 \le i < 1024

S1(i,j);

S = \{S1(i,j) \rightarrow (i,j)\}\

\mathfrak{T} = \{(\mathfrak{i}, \mathfrak{j}) \to (4 * |\mathfrak{i}/4|,

// Unroll and jammed loops

for (ti=0; ti<1024; ti+=4)</pre>

j, i)}

for (j=0; j<1024; j+=1)

S_T = \{S1(i) \rightarrow (4 * | i/4 |,

for (i=tj; i<ti+4; i+=1)

j,i)

S1(i, j-i);

```