#### A Runtime System for Data-Flow Task Programming on Multicore Architectures with Accelerators

Joao Vicente Ferreira Lima

#### ▶ To cite this version:

Joao Vicente Ferreira Lima. A Runtime System for Data-Flow Task Programming on Multicore Architectures with Accelerators. Other [cs.OH]. Université de Grenoble; Universidade Federal do Rio Grande do Sul (Porto Alegre, Brésil), 2014. English. NNT: 2014GRENM092. tel-01151787v2

#### HAL Id: tel-01151787 https://theses.hal.science/tel-01151787v2

Submitted on 16 Sep 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

prépareé dans le cadre d'une cotutelle entre l'*Université de Grenoble* et l'*Universidade Federal do Rio Grande do Sul*

Spécialité : Informatique

Arrêté ministérial : 6 janvier 2005 - 7 août 2006

Présentée par

#### João Vicente FERREIRA LIMA

Thèse dirigée par Bruno RAFFIN et Nicolas MAILLARD et codirigée par Vincent DANJEAN

préparée au Laboratoire d'Informatique de Grenoble dans le cadre de l'Ecole Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique et au Laboratoire de Parallelisme et Distribution dans le cadre du Programme de Doctorat en Informatique

## A Runtime System for Data-Flow Task Programming on Multicore Architectures with Accelerators

Thèse soutenue publiquement le **5 mai 2014**, devant le jury composé de :

#### M. Philippe O. A. NAVAUX

Professeur, Universidade Federal do Rio Grande do Sul, Président

#### M. Jairo PANETTA

Professeur, CPTEC/INPE, Rapporteur

#### M. Pierre MANNEBACK

Professeur, Université de Mons, Rapporteur

#### **Mme Andrea CHARÃO**

Maître de Conférences, Universidade Federal de Santa Maria, Examinatrice

#### M. Bruno RAFFIN

Chargé de Recherche, Université de Grenoble, Directeur de thèse

#### M. Nicolas MAILLARD

Maître de Conférences, Universidade Federal do Rio Grande do Sul, Directeur de thèse

#### Abstract

In this thesis, we propose to study the issues of task parallelism with data dependencies on multicore architectures with accelerators. We target those architectures with the XKaapi runtime system developed by the MOAIS team (INRIA Rhône-Alpes).

We first studied the issues on multi-GPU architectures for asynchronous execution and scheduling. Work stealing with heuristics showed significant performance results, but did not consider the computing power of different resources. Next, we designed a scheduling framework and a performance model to support scheduling strategies over XKaapi runtime. Finally, we performed experimental evaluations over the Intel Xeon Phi coprocessor in native execution.

Our conclusion is twofold. First we concluded that data-flow task programming can be efficient on accelerators, which may be GPUs or Intel Xeon Phi coprocessors. Second, the runtime support of different scheduling strategies is essential. Cost models provide significant performance results over very regular computations, while work stealing can react to imbalances at runtime.

**Keywords:** parallel programming, accelerators, task parallelism, data flow dependencies, work stealing.

#### Resumo

## Uma Ferramenta para Programação com Dependência de Dados em Arquiteturas Multicore com Aceleradores

Esta tese investiga os desafios no uso de paralelismo de tarefas com dependências de dados em arquiteturas multi-CPU com aceleradores. Para tanto, o XKaapi, desenvolvido no grupo de pesquisa MOAIS (INRIA Rhône-Alpes), é a ferramenta de programação base deste trabalho.

Em um primeiro momento, este trabalho propôs extensões ao XKaapi a fim de sobrepor transferência de dados com execução através de operações concorrentes em GPU, em

conjunto com escalonamento por roubo de tarefas em multi-GPU. Os resultados experimentais sugerem que o suporte a asincronismo é importante à escalabilidade e desempenho em

multi-GPU. Apesar da localidade de dados, o roubo de tarefas não pondera a capacidade

de processamento das unidades de processamento disponíveis. Nós estudamos estratégias

de escalonamento com predição de desempenho em tempo de execução através de modelos

de custo de execução. Desenvolveu-se um framework sobre o XKaapi de escalonamento

que proporciona a implementação de diferentes algoritmos de escalonamento. Esta tese

também avaliou o XKaapi em coprocessodores Intel Xeon Phi para execução nativa.

A conclusão desta tese é dupla. Primeiramente, nós concluímos que um modelo de programação com dependências de dados pode ser eficiente em aceleradores, tais como GPUs e coprocessadores Intel Xeon Phi. Não obstante, uma ferramenta de programação com suporte a diferentes estratégias de escalonamento é essencial. Modelos de custo podem ser usados no contexto de algoritmos paralelos regulares, enquanto que o roubo de tarefas poder reagir a desbalanceamentos em tempo de execução.

Palavras-chave: Programação paralela, aceleradores, paralelismo de tarefas, dependência de dados, roubo de tarefas.

#### Résumé

#### Vers un Support Exécutif avec Dépendance de Données pour les Architectures Multicœur avec des Accélérateurs

Dans cette thèse , nous proposons d'étudier des questions sur le parallélism de tâche avec dépendance de données dans le cadre de machines multicœur avec des accélérateurs. La solution proposée a été développée en utilisant l'interface de programmation haute niveau XKaapi du projet MOAIS de l'INRIA Rhône-Alpes.

D'abord nous avons étudié des questions liés à une approche d'exécution totalement asyncrone et l'ordonnancement par vol de travail sur des architectures multi-GPU. Le vol de travail avec localité de données a montré des résultats significatifs, mais il ne prend pas en compte des différents ressources de calcul. Ensuite nous avons conçu une interface et une modèle de coût qui permettent d'écrire des politiques d'ordonnancement sur XKaapi. Finalement on a évalué XKaapi sur un coprocesseur Intel Xeon Phi en mode natif.

Notre conclusion est double. D'abord nous avons montré que le modèle de programmation data-flow peut être efficace sur des accélérateurs tels que des GPUs ou des coprocesseurs Intel Xeon Phi. Ensuite, le support à des différents politiques d'ordonnancement est indispensable. Les modèles de coût permettent d'obtenir de performance significatifs sur des calculs très réguliers, tandis que le vol de travail permet de redistribuer la charge en cours d'exécution.

Mots-clés : Programmation parallèle, accélérateur, parallélisme de tâche, dépendance de données, vol de travail.

## Contents

| Li       | st of | Figur    | res                                      | XV  |

|----------|-------|----------|------------------------------------------|-----|

| Li       | st of | Table    | es ·                                     | xvi |

| Li       | st of | Algor    | rithms                                   | xix |

| 1        | Intr  | oducti   | ion                                      | 1   |

|          | 1.1   | Motiv    | $\operatorname{ration}$                  | 1   |

|          | 1.2   | Hypot    | thesis                                   | 2   |

|          | 1.3   | Objec    | tives                                    | 2   |

|          | 1.4   | Contri   | ibutions                                 | 3   |

|          | 1.5   | Conte    | $\exp - x t$                             | 4   |

|          | 1.6   | Thesis   | s Outline                                | 4   |

| Ι        | Pai   | rallel 1 | Programming                              | 7   |

| <b>2</b> | Bac   | kgroui   | nd                                       | g   |

|          | 2.1   | _        | lel Architectures                        | ç   |

|          |       | 2.1.1    | Architecture Models                      | 10  |

|          |       | 2.1.2    | Memory Systems                           | 10  |

|          |       | 2.1.3    | General Purpose Processors               | 11  |

|          |       | 2.1.4    | Manycore and Heterogeneous Architectures | 11  |

|          |       | 2.1.5    | A Heterogeneous Machine: Idgraf          | 16  |

|          |       | 2.1.6    | Discussion                               | 17  |

|          | 2.2   | Progra   | amming Models                            | 18  |

|          |       | 2.2.1    | Message Passing                          | 20  |

|          |       | 2.2.2    | Shared Memory                            | 20  |

|          |       | 2.2.3    | Distributed Shared Memory                | 21  |

|          |       | 2.2.4    | Data and Task Parallelism                | 21  |

|          |       | 2.2.5    | Discussion                               | 22  |

|          | 2.3   | Sched    | uling Algorithms                         | 22  |

|          |       | 2.3.1    | Work Stealing                            | 23  |

|          |       | 2.3.2    | Heterogeneous Earliest-Finish-Time       | 25  |

|          |       | 2.3.3    | Algorithms for Heterogeneous Systems     | 26  |

|          |       | 2.3.4    | Discussion                               | 28  |

|          | 2.4   | Summ     | nary                                     | 28  |

| 3        |       | _        | ning Environments                        | 31  |

|          | 3.1   |          | d Memory Programming                     |     |

|          |       | 3.1.1    | OpenMP                                   |     |

|          |       | 3.1.2    | Cilk and Cilk++                          | 32  |

Contents

|         |                         | 3.1.3 Threading Building Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|---------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         |                         | 3.1.4 Athapascan/KAAPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|         | 3.2                     | Heterogeneous Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|         |                         | 3.2.1 CUDA, OpenCL, and OpenACC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|         |                         | 3.2.2 Charm++                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|         |                         | 3.2.3 StarPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|         |                         | 3.2.4 StarSs and OmpSs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|         |                         | 3.2.5 KAAPI Extensions for Iterative Computations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|         |                         | 3.2.6 Intel Xeon Phi Coprocessor Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|         |                         | 3.2.7 Other High Level Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|         | 3.3                     | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|         |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 4       |                         | api Runtime System 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|         | 4.1                     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|         | 4.2                     | Kaapi++ Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|         | 4.3                     | Scheduling by Work Stealing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|         |                         | 4.3.1 Runtime Data Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|         |                         | 4.3.2 Concurrent Steal Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|         |                         | 4.3.3 Reduction of Steal Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|         | 4.4                     | Data Flow Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|         |                         | 4.4.1 DFG Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|         | 4.5                     | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|         |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|         |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| II      | Co                      | ntribution 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| II<br>5 |                         | ntribution 57 time Support for Multi-GPU Architectures 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|         |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|         | Rur                     | time Support for Multi-GPU Architectures 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|         | <b>Ru</b> r 5.1         | time Support for Multi-GPU Architectures 59 Kaapi++ User Annotations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|         | Rur 5.1 5.2             | time Support for Multi-GPU Architectures 59 Kaapi++ User Annotations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|         | Rur 5.1 5.2             | time Support for Multi-GPU Architectures 59 Kaapi++ User Annotations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|         | Rur 5.1 5.2             | time Support for Multi-GPU Architectures 59 Kaapi++ User Annotations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

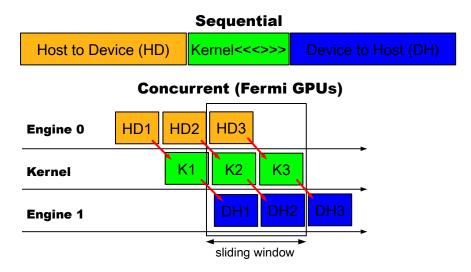

|         | Rur 5.1 5.2 5.3         | time Support for Multi-GPU Architectures  Kaapi++ User Annotations 60 GPU workers and Task Execution 61 Concurrent Operations between CPU and GPU 62 5.3.1 Kstream Structure 62 5.3.2 Sliding Window 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|         | Rur 5.1 5.2 5.3         | time Support for Multi-GPU Architectures  Kaapi++ User Annotations 60 GPU workers and Task Execution 61 Concurrent Operations between CPU and GPU 62 5.3.1 Kstream Structure 62 5.3.2 Sliding Window 62 Memory Management 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|         | Rur 5.1 5.2 5.3         | time Support for Multi-GPU Architectures       59         Kaapi++ User Annotations       60         GPU workers and Task Execution       61         Concurrent Operations between CPU and GPU       62         5.3.1 Kstream Structure       62         5.3.2 Sliding Window       62         Memory Management       63         5.4.1 Software Cache       64                                                                                                                                                                                                                                                                                                                                          |  |

|         | Rur 5.1 5.2 5.3 5.4     | time Support for Multi-GPU Architectures       59         Kaapi++ User Annotations       60         GPU workers and Task Execution       61         Concurrent Operations between CPU and GPU       62         5.3.1 Kstream Structure       62         5.3.2 Sliding Window       62         Memory Management       63         5.4.1 Software Cache       64         5.4.2 Consistency       65                                                                                                                                                                                                                                                                                                       |  |

|         | Rur 5.1 5.2 5.3 5.4     | time Support for Multi-GPU Architectures       59         Kaapi++ User Annotations       60         GPU workers and Task Execution       61         Concurrent Operations between CPU and GPU       62         5.3.1 Kstream Structure       62         5.3.2 Sliding Window       62         Memory Management       63         5.4.1 Software Cache       64         5.4.2 Consistency       65         Runtime Scheduling       65                                                                                                                                                                                                                                                                   |  |

|         | Rur 5.1 5.2 5.3 5.4     | time Support for Multi-GPU Architectures       59         Kaapi++ User Annotations       60         GPU workers and Task Execution       61         Concurrent Operations between CPU and GPU       62         5.3.1 Kstream Structure       62         5.3.2 Sliding Window       62         Memory Management       63         5.4.1 Software Cache       64         5.4.2 Consistency       65         Runtime Scheduling       65         5.5.1 Work Stealing       65                                                                                                                                                                                                                              |  |

|         | Rur 5.1 5.2 5.3 5.4     | time Support for Multi-GPU Architectures       59         Kaapi++ User Annotations       60         GPU workers and Task Execution       61         Concurrent Operations between CPU and GPU       62         5.3.1 Kstream Structure       62         5.3.2 Sliding Window       62         Memory Management       63         5.4.1 Software Cache       64         5.4.2 Consistency       65         Runtime Scheduling       65         5.5.1 Work Stealing       65         5.5.2 Data-Aware Work Stealing (H1)       66                                                                                                                                                                         |  |

|         | Rur 5.1 5.2 5.3 5.4 5.5 | time Support for Multi-GPU Architectures       59         Kaapi++ User Annotations       60         GPU workers and Task Execution       61         Concurrent Operations between CPU and GPU       62         5.3.1 Kstream Structure       62         5.3.2 Sliding Window       62         Memory Management       63         5.4.1 Software Cache       64         5.4.2 Consistency       65         Runtime Scheduling       65         5.5.1 Work Stealing       65         5.5.2 Data-Aware Work Stealing (H1)       66         5.5.3 Locality-Aware Work Stealing (H2)       66                                                                                                                |  |

|         | Rur 5.1 5.2 5.3 5.4 5.5 | time Support for Multi-GPU Architectures       59         Kaapi++ User Annotations       60         GPU workers and Task Execution       61         Concurrent Operations between CPU and GPU       62         5.3.1 Kstream Structure       62         5.3.2 Sliding Window       62         Memory Management       63         5.4.1 Software Cache       64         5.4.2 Consistency       65         Runtime Scheduling       65         5.5.1 Work Stealing       65         5.5.2 Data-Aware Work Stealing (H1)       66         5.5.3 Locality-Aware Work Stealing (H2)       66         Experiments       67                                                                                   |  |

|         | Rur 5.1 5.2 5.3 5.4 5.5 | time Support for Multi-GPU Architectures       59         Kaapi++ User Annotations       60         GPU workers and Task Execution       61         Concurrent Operations between CPU and GPU       62         5.3.1 Kstream Structure       62         5.3.2 Sliding Window       62         Memory Management       63         5.4.1 Software Cache       64         5.4.2 Consistency       65         Runtime Scheduling       65         5.5.1 Work Stealing       65         5.5.2 Data-Aware Work Stealing (H1)       66         5.5.3 Locality-Aware Work Stealing (H2)       66         Experiments       67         5.6.1 Platform and Environment       68                                   |  |

|         | Rur 5.1 5.2 5.3 5.4 5.5 | time Support for Multi-GPU Architectures       59         Kaapi++ User Annotations       60         GPU workers and Task Execution       61         Concurrent Operations between CPU and GPU       62         5.3.1 Kstream Structure       62         5.3.2 Sliding Window       62         Memory Management       63         5.4.1 Software Cache       64         5.4.2 Consistency       65         Runtime Scheduling       65         5.5.1 Work Stealing       65         5.5.2 Data-Aware Work Stealing (H1)       66         5.5.3 Locality-Aware Work Stealing (H2)       66         Experiments       67         5.6.1 Platform and Environment       68         5.6.2 Benchmarks       68 |  |

Contents

|    |        | 5.6.6 Multi-CPU Performance Impact                         | 76               |

|----|--------|------------------------------------------------------------|------------------|

|    | 5.7    | Summary                                                    | 77               |

| 6  | Sch    | duling Strategies over Multi-CPU and Multi-GPU Systems     | <b>7</b> 9       |

|    | 6.1    |                                                            | 80               |

|    |        | 6.1.1 Overview of Task List and Task Descriptor            | 80               |

|    |        |                                                            | 81               |

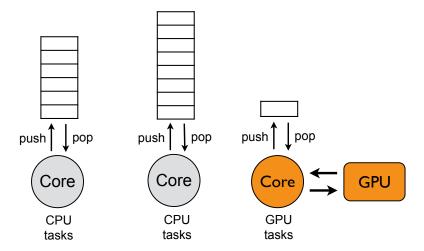

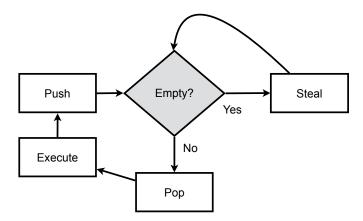

|    |        | 6.1.3 Scheduling by Pop, Push, and Steal                   | 82               |

|    |        |                                                            | 83               |

|    | 6.2    |                                                            | 84               |

|    |        |                                                            | 84               |

|    |        | e e e e e e e e e e e e e e e e e e e                      | 85               |

|    | 6.3    |                                                            | 85               |

|    |        |                                                            | 86               |

|    |        |                                                            | 86               |

|    |        | e e e e e e e e e e e e e e e e e e e                      | 87               |

|    | 6.4    |                                                            | 87               |

|    |        | -                                                          | 88               |

|    |        |                                                            | 88               |

|    |        | 30                                                         | 89               |

|    |        |                                                            | 90               |

|    |        |                                                            | 93               |

|    | 6.5    |                                                            | 95               |

| 7  | Rur    | time Support for Native Mode on Intel Xeon Phi Coprocessor | 99               |

| •  | 7.1    | Thread Placement                                           |                  |

|    | 7.2    | Work Stealing Scheduler                                    |                  |

|    | 7.3    | Experiments                                                |                  |

|    | 1.0    | 7.3.1 Platform and Environment                             |                  |

|    |        | 7.3.2 Comparison Xeon vs Xeon Phi                          |                  |

|    |        | 7.3.3 PLASMA: Cholesky, LU, and QR                         |                  |

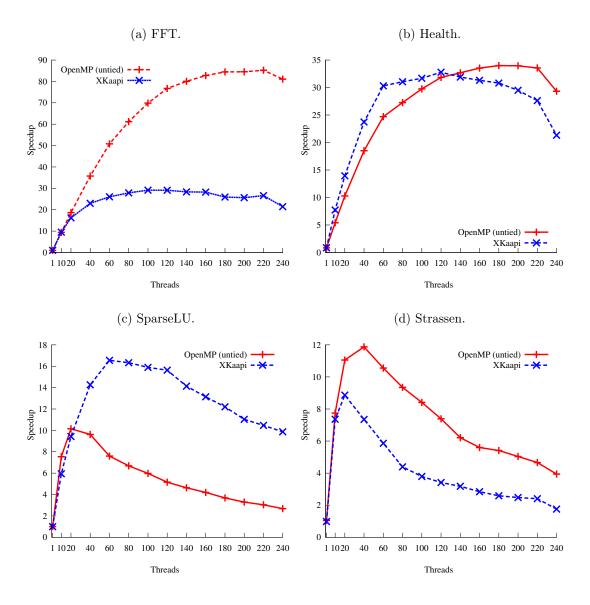

|    |        | 7.3.4 BOTS: FFT, Health, SparseLU, and Strassen            |                  |

|    | 7.4    | Discussion                                                 |                  |

|    | 7.5    | Summary                                                    |                  |

| 8  | Com    | clusion 1                                                  | 17               |

| 0  | 8.1    |                                                            | 1 <i>1</i><br>18 |

|    | 8.2    | Perspectives                                               |                  |

|    | 0.2    | 8.2.1 Compiler Directives                                  |                  |

|    |        | 1                                                          |                  |

|    |        | 8.2.2 XKaapi Benchmarks                                    |                  |

|    |        | 8.2.3 Intel Xeon Phi Extensions                            |                  |

|    |        | 8.2.4 Parallel Adaptive Algorithms                         |                  |

|    |        | 8.2.5 Exascale Systems                                     | 21               |

| Bi | ibliog | raphy 12                                                   | 23               |

<u>xii</u> Contents

| II           | [ <b>A</b> | appendixes                               | 137 |

|--------------|------------|------------------------------------------|-----|

| $\mathbf{A}$ | Cho        | olesky over XKaapi                       | 139 |

|              | A.1        | Tiled Cholesky Algorithm                 | 139 |

|              | A.2        | XKaapi Data-Flow Version                 | 140 |

|              | A.3        | Parallel Diagonal Decomposition          | 141 |

|              | A.4        | Version with Compiler Annotations        | 143 |

| В            | XK         | aapi Performance Model Results           | 149 |

|              | B.1        | History-based Model Results              | 149 |

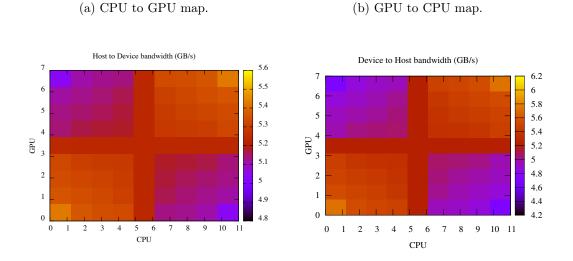

|              | B.2        | Communication Bandwidth Results          | 149 |

| $\mathbf{C}$ | Exp        | periments with XKaapi, OmpSs, and StarPU | 151 |

|              | C.1        | Cholesky                                 | 152 |

|              | C.2        | Blocked Matrix Multiplication            | 152 |

|              | C.3        | Summary                                  | 152 |

| D            | Pub        | olications                               | 155 |

## List of Figures

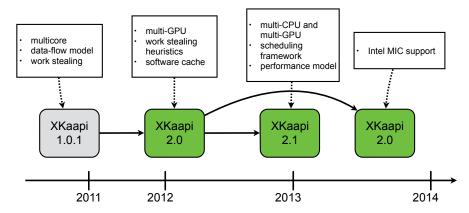

| 1.1        | Timeline of the contributions of this thesis (green boxes)                                                                                                                                                                  | 4        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

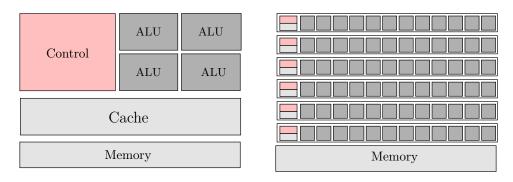

| 2.1        | Design differences between a multicore (left) and a manycore (right) microprocessor. This multicore layout is based on a basic model from recent microprocessors, and the manycore layout is similar to a GPU architecture  |          |

|            | representation                                                                                                                                                                                                              | 12       |

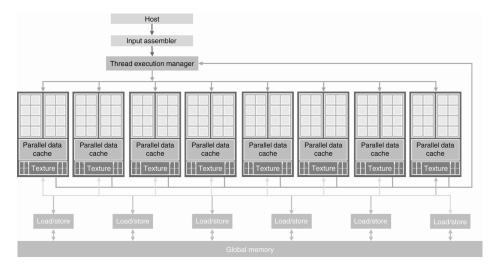

| 2.2        | Overview of a CUDA-capable GPU architecture                                                                                                                                                                                 | 14       |

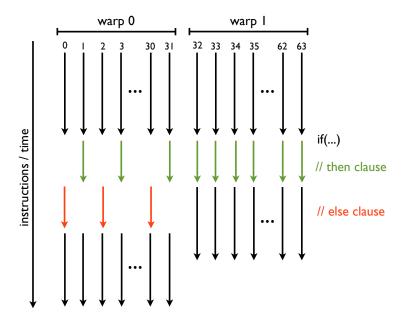

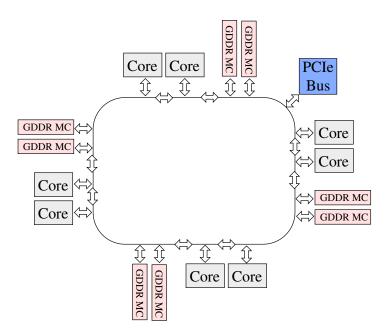

| 2.3<br>2.4 | GPU branch divergence example on the first warp                                                                                                                                                                             | 15       |

|            | the cores interconnected by a bidirectional ring                                                                                                                                                                            | 16       |

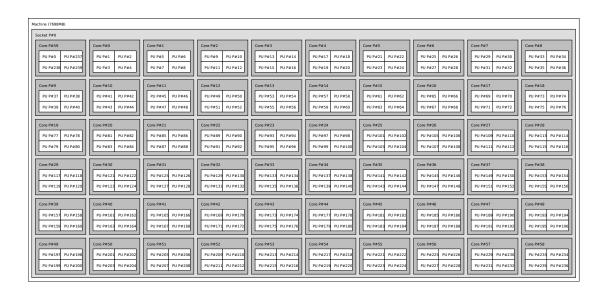

| 2.5        | Topology of an Intel Xeon Phi 5110P coprocessor using hwloc                                                                                                                                                                 | 17       |

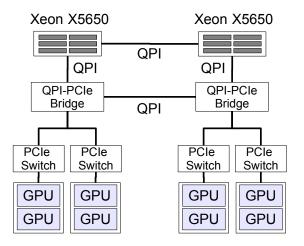

| 2.6        | Idgraf hardware topology with two hexa-core CPUs and eight Tesla C2050                                                                                                                                                      | 1.5      |

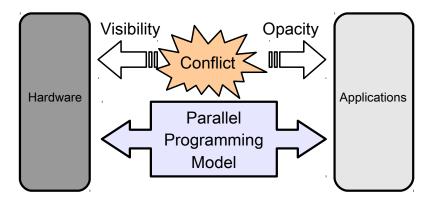

| 2.7        | GPUs                                                                                                                                                                                                                        | 17       |

|            | sents the parallel programming models                                                                                                                                                                                       | 19       |

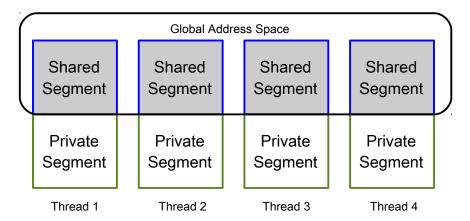

| 2.8        | Memory view of PGAS programming model with shared segments composing the global space, and private segments per thread                                                                                                      | 21       |

| 3.1        | Example of the Fibonacci computation with OpenMP tasks                                                                                                                                                                      | 32       |

| 3.2        | Recursive implementation of the Fibonacci number computation (left) compared to its Cilk version (right). Each recursive call with spawn creates a new task asynchronously. The sync keyword is used to wait the previously |          |

|            | created tasks and sums their result                                                                                                                                                                                         | 33       |

| 3.3        | Example of an Intel TBB task of the Fibonacci sequence                                                                                                                                                                      | 34       |

| 3.4        | Recursive version of the Fibonacci sequence with Athapascan interface                                                                                                                                                       | 36       |

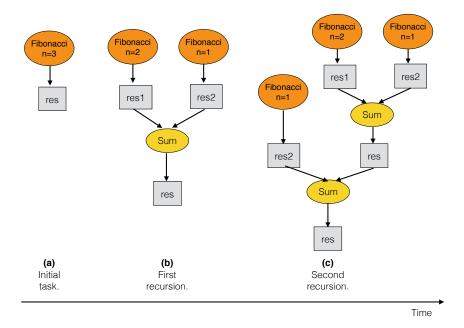

| 3.5        | Fibonacci dependency graph on Athapascan model                                                                                                                                                                              | 37       |

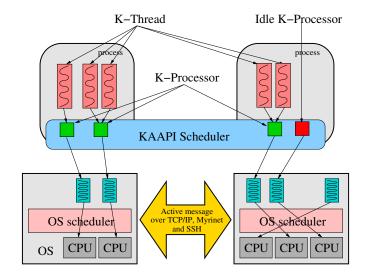

| 3.6        | KAAPI runtime structure                                                                                                                                                                                                     | 37       |

| 3.7        | A code example of the Charm++ GPU Manager with a task submission to a GPU                                                                                                                                                   | 39       |

| 3.8        | StarPU program example for vector scaling                                                                                                                                                                                   | 41       |

| 3.9        | Example of matrix multiplication using multi-versioning with OmpSs anno-                                                                                                                                                    |          |

| 0.10       | tations.                                                                                                                                                                                                                    | 42       |

| 3.10       | C++ example of KAAPI multi-implementation task definition. In left is the                                                                                                                                                   | 40       |

| 3.11       | CPU implementation, and in right the GPU implementation                                                                                                                                                                     | 43<br>44 |

| 0.11       | Example of a seasing vector program using the most emount complete.                                                                                                                                                         |          |

| 4.1        | Comparison between KAAPI and XKaapi runtime                                                                                                                                                                                 | 48       |

| 4.2        | Example of a Kaapi++ task signature from a C++ function                                                                                                                                                                     | 49       |

| 4.3        | Mapping of a C++ function to a Kaapi++ task                                                                                                                                                                                 | 49       |

| 4.4        | Kaapi++ Conversion rules between task's signature and task body arguments.                                                                                                                                                  | 50       |

| 4.5        | Example of Kaapi++ task creation                                                                                                                                                                                            | 50       |

xiv List of Figures

| 4.6   | Example of Kaapi++ multi-versioning with CPU and GPU implementations.                                 | 51  |

|-------|-------------------------------------------------------------------------------------------------------|-----|

| 4.7   | Simplified example of a Kaapi++ blocked matrix product                                                | 55  |

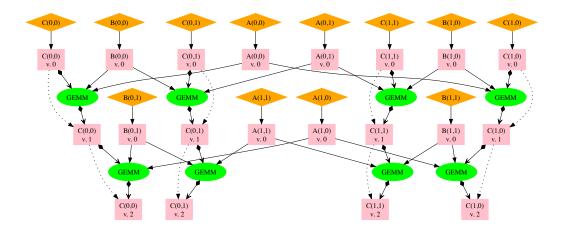

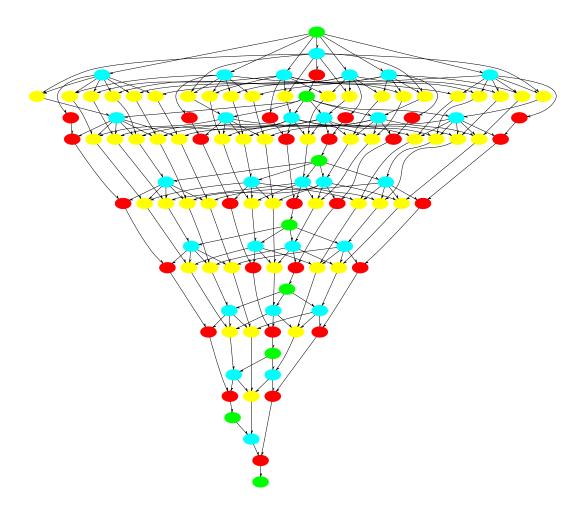

| 4.8   | A XKaapi DFG of the blocked matrix product                                                            | 56  |

| 5.1   | Example of scheduling hints in the Kaapi++ API                                                        | 60  |

| 5.2   | Runtime structure of XKaapi with multi-GPU. A core is dedicated to control                            |     |

|       | a target GPU                                                                                          | 61  |

| 5.3   | Sequential and concurrent operations in a recent GPU card                                             | 63  |

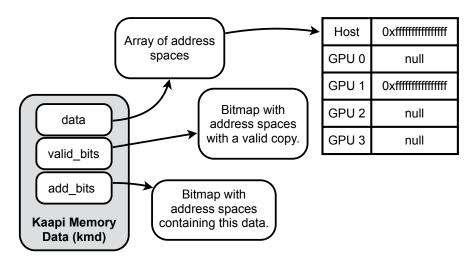

| 5.4   | XKaapi kmd structure to track valid replicas of a shared data                                         | 64  |

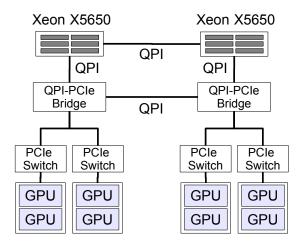

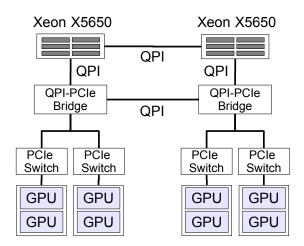

| 5.5   | Idgraf hardware topology for multi-GPU experiments                                                    | 68  |

| 5.6   | Performance results from DGEMM on Idgraf for a single CPU and a single GPU, and different block sizes | 69  |

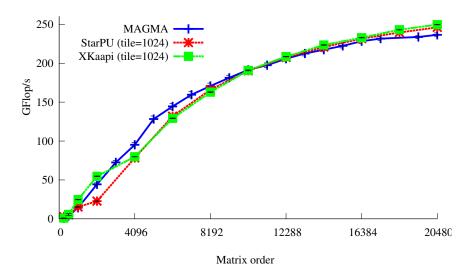

| 5.7   | Cholesky performance results on Idgraf for single-CPU and single-GPU with                             |     |

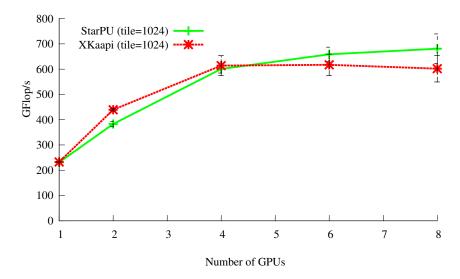

|       | block size $1024 \times 1024$                                                                         | 71  |

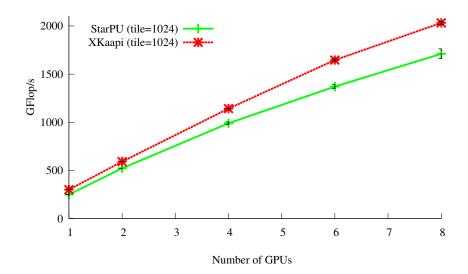

| 5.8   | DGEMM performance up to 8 GPUs. The matrix size was $16384 \times 16384$ with                         |     |

|       | block size $1024 \times 1024$                                                                         | 71  |

| 5.9   | Multi-GPU Cholesky factorization with $16384 \times 16384$ matrices and block                         |     |

|       | size $1024 \times 1024$                                                                               | 72  |

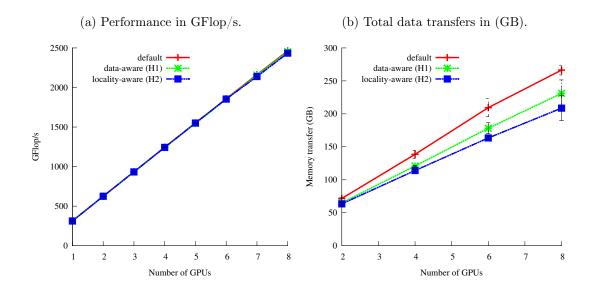

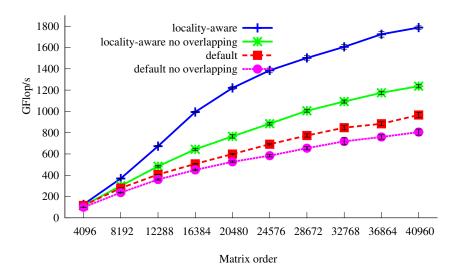

| 5.10  | Comparison of our three work stealing heuristics for DGEMM on 8 GPUs for                              |     |

|       | a matrix size of $40960 \times 40960$                                                                 | 74  |

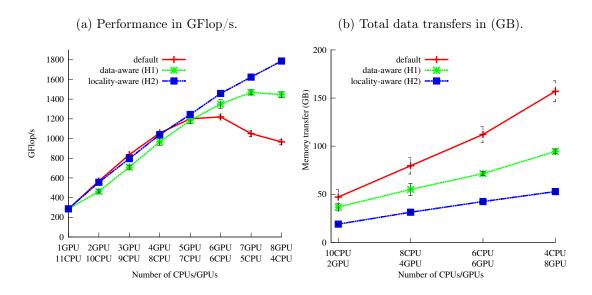

| 5.11  | Performance results of DPOTRF on eight GPUs and four CPUs for a matrix                                |     |

|       | size of 40960 × 40960                                                                                 | 75  |

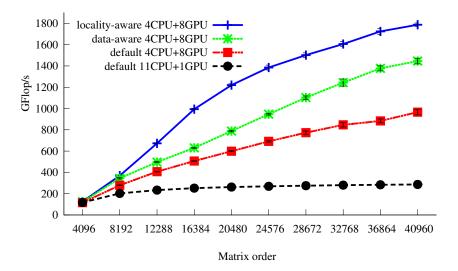

| 5.12  | Scalability of the work stealing heuristics for Cholesky on 8 GPUs and 4                              |     |

| F 10  | CPUs compared to one GPU and one CPU execution                                                        | 75  |

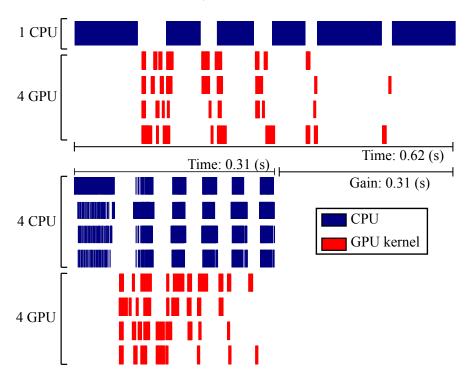

| 5.13  | Impact of overlapping in XKaapi default and locality-aware work stealing                              | 70  |

| 5 1 1 | algorithm for Cholesky on 4 CPUs and 8 GPUs                                                           | 76  |

| 5.14  | on 4 GPUs (red) and up to 4 CPUs (blue)                                                               | 77  |

|       | on 4 or os (red) and up to 4 or os (blue).                                                            | ' ' |

| 6.1   | General scheduling loop of the XKaapi scheduling framework                                            | 81  |

| 6.2   | Data structure in C of a scheduling strategy on XKaapi                                                | 83  |

| 6.3   | ${\bf Idgraf\ hardware\ topology\ for\ experimental\ results\ on\ scheduling\ strategies.\ .}$        | 89  |

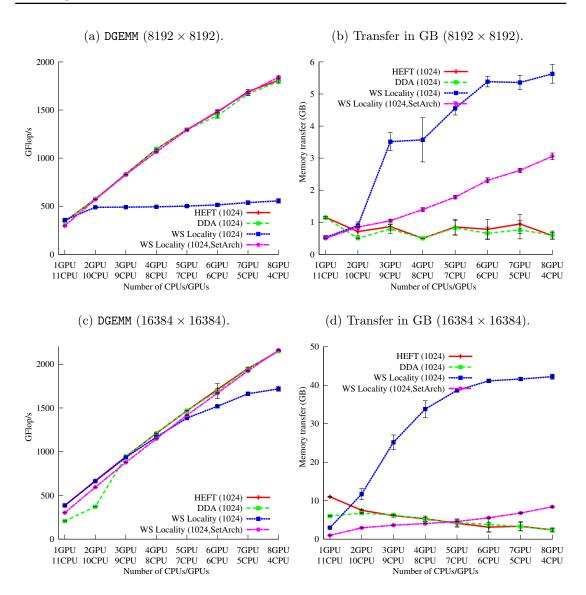

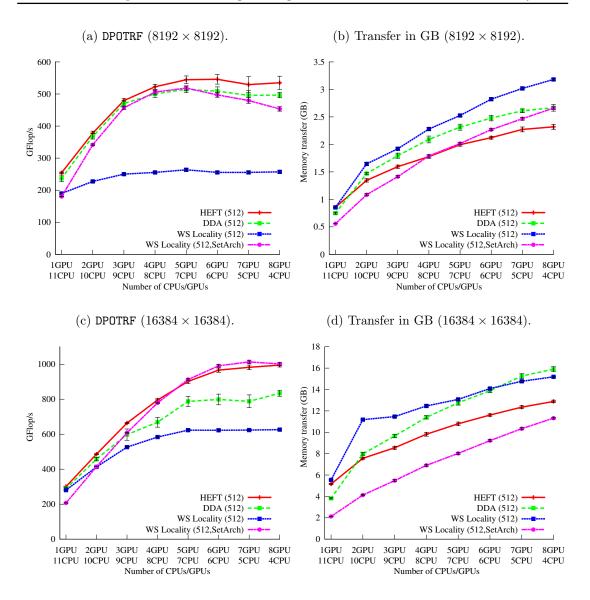

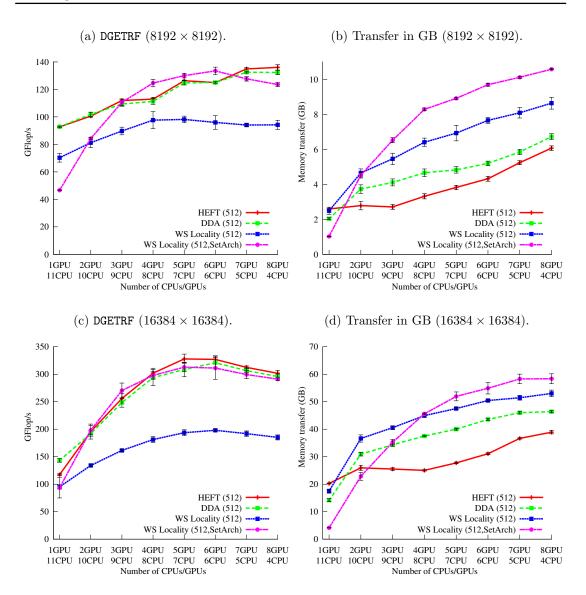

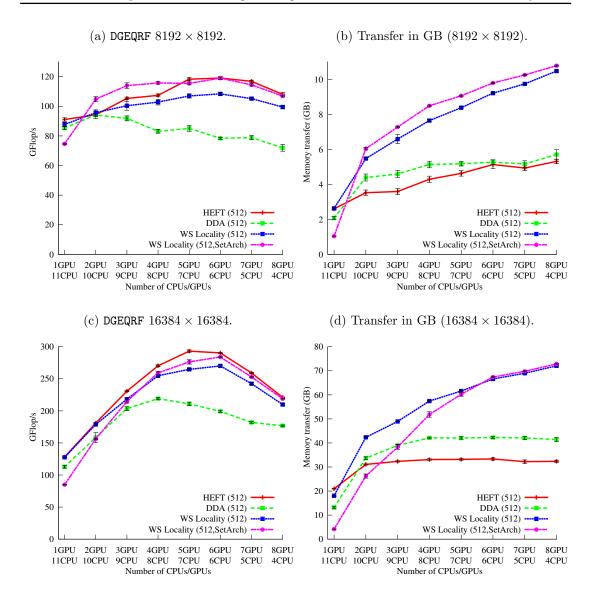

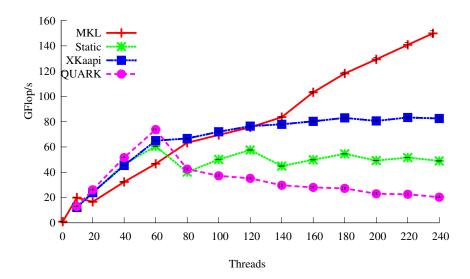

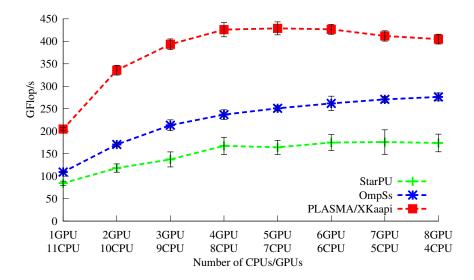

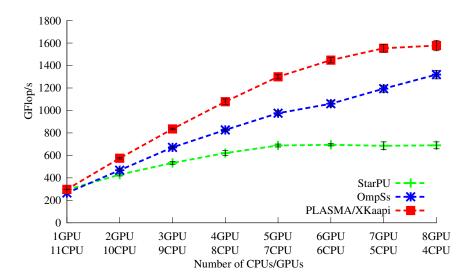

| 6.4   | Performance results of matrix product (DGEMM)                                                         | 91  |

| 6.5   | Performance results of Cholesky (DPOTRF)                                                              | 92  |

| 6.6   | Performance results of LU (DGETRF)                                                                    | 93  |

| 6.7   | Performance results of QR (DGEQRF)                                                                    | 94  |

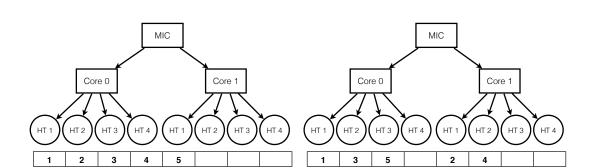

| 7.1   | XKaapi thread placement of five threads on the Intel Xeon Phi                                         | 101 |

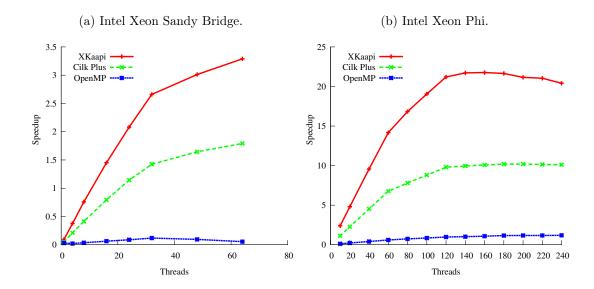

| 7.2   | Fibonacci speedup over sequential execution for XKaapi, OpenMP, and Intel                             | 101 |

|       | Cilk Plus (input of $N = 38$ )                                                                        | 104 |

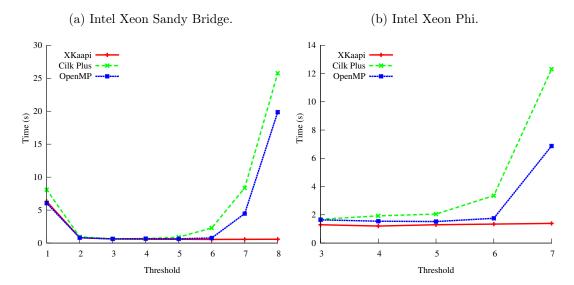

| 7.3   | Time versus threshold for NQueens benchmark (N=17) for XKaapi, Intel                                  |     |

| . •   | Cilk Plus and OpenMP                                                                                  | 105 |

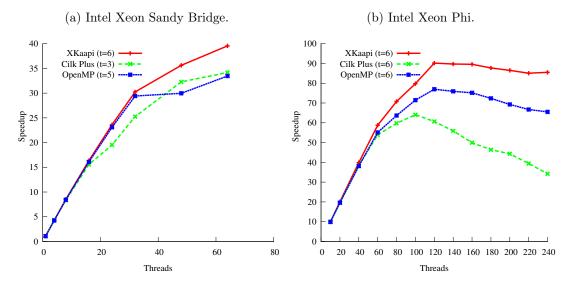

| 7.4   | Scalability of the NQueens benchmark (N=17) for XKaapi, Intel Cilk Plus                               |     |

|       | and OpenMP.                                                                                           | 106 |

| 7.5   | Example of a left-looking Cholesky factorization with XKaapi and Intel Cilk                           |     |

|       | Plus                                                                                                  | 107 |

List of Figures xv

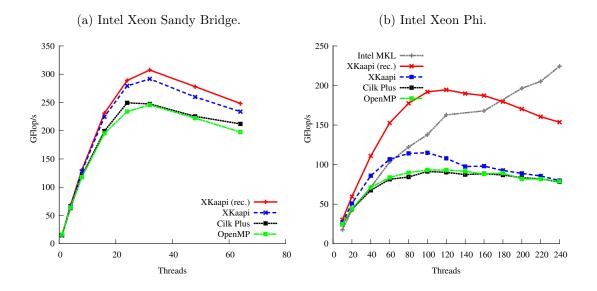

| 7.6      | Results of Cholesky benchmarks for XKaapi, OpenMP, and Intel Cilk Plus for matrix size $8192 \times 8192$ and tile size $256 \times 256$ . MKL was only measured       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.7      | on the Intel Xeon Phi and omitted on the Intel Xeon Sandy Bridge 108 Results of Cholesky benchmarks for XKaapi, OpenMP, and Intel Cilk Plus                            |

|          | for a matrix of size $16384 \times 16384$ and tile size $512 \times 512$ . MKL was only measured on the Intel Xeon Phi and omitted on the Intel Xeon Sandy Bridge. 108 |

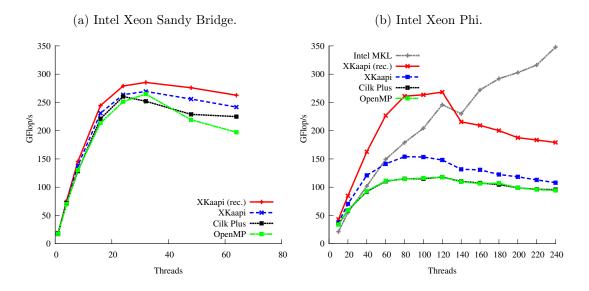

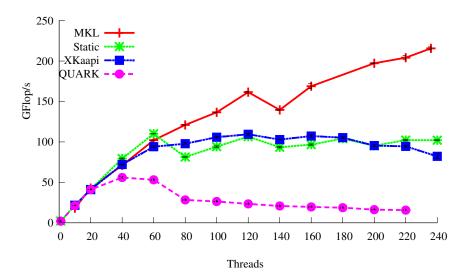

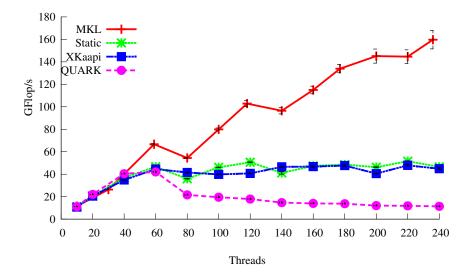

| 7.8      | Cholesky factorization results from PLASMA with matrix size $8192\times8192$ on Intel Xeon Phi                                                                         |

| 7.9      | LU factorization results from PLASMA with matrix size $8192 \times 8192$ on Intel Xeon Phi                                                                             |

| 7.10     | QR factorization results from PLASMA with matrix size $8192 \times 8192$ on Intel Xeon Phi                                                                             |

| 7.11     | $Preliminary\ results\ of\ BOTS\ benchmarks\ FFT,\ Health,\ SparseLU,\ and\ Strassen$                                                                                  |

|          | on the Intel Xeon Phi                                                                                                                                                  |

| 8.1      | Example of matrix multiplication on OpenMP 4.0 standard                                                                                                                |

| A.1      | Initialization and data handling for the Cholesky program. Data is registered before execution and unregistered at the end                                             |

| A.2      | Left-looking Cholesky implementation with XKaapi C++ API (kaapi++). It shows the task <i>Signature</i> with its parameters and access modes, as well                   |

| A.3      | as the parallel CPU version                                                                                                                                            |

| A.3      | multi-versioning with task signature and CPU and GPU versions 144                                                                                                      |

| A.4      | The resulting data-flow graph (DFG) of a Cholesky factorization 145                                                                                                    |

| A.5      | Two-level Cholesky version with XKaapi                                                                                                                                 |

| A.6      | A Cholesky version with XKaapi compiler                                                                                                                                |

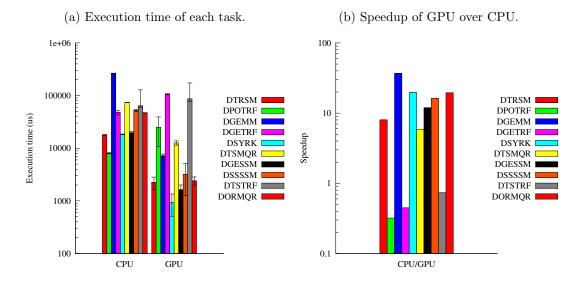

| B.1      | Performance model results in time (left) and speedup (right) for tasks with                                                                                            |

| B.2      | CPU and GPU versions. Logarithm scale was used for $y$ axis                                                                                                            |

| C.1      | Performance results of Cholesky factorization for a matrix size of 10240 $\times$                                                                                      |

| $\alpha$ | 10240 and block size $1024 \times 1024$                                                                                                                                |

| C.2      | Performance results of matrix multiplication for a matrix size of $10240 \times 10240$ and block size $1024 \times 1024$                                               |

|          | 10210 WIR DIOOR DIEO 1021 // 1021                                                                                                                                      |

## List of Tables

| 2.1 | Idgraf peak performance as well as estimated DGEMM performance for all processing units in the system. | 18  |

|-----|--------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Memory transfers of DGEMM in GB with matrix order $16384 \times 16384$ and                             |     |

|     | block size $1024 \times 1024$ . The sum of input and output data transfers is 8 GB.                    | 72  |

| 5.2 | Memory transfers of Cholesky in GB with matrix size $16384 \times 16384$ and                           |     |

|     | block size $1024 \times 1024$ . The sum of input and output data transfers is 4 GB.                    | 73  |

| 5.3 | Performance results (in GFlop/s) using 4 GPUs and variable number of                                   |     |

|     | CPUs                                                                                                   | 76  |

| 7.1 | Runtime overhead for Fibonacci and NQueens on Intel Xeon Sandy Bridge                                  |     |

|     | and Intel Xeon Phi                                                                                     | 109 |

| 7.2 | PLASMA method and parameters for experiments on the Intel Xeon Phi.                                    |     |

|     | The parameters of PLASMA are matrix size, block size (NB), and internal                                |     |

|     | block size (IB)                                                                                        | 110 |

| 7.3 | Input parameters and runtime overhead of BOTS on the Intel Xeon Phi 1                                  | 112 |

## List of Algorithms

| 1 | Heterogeneous Earliest-Finish-Time                         | 26  |

|---|------------------------------------------------------------|-----|

| 2 | Data-flow computation in XKaapi                            | 54  |

| 3 | Data-aware work stealing to reduce data transfers          | 66  |

| 4 | Locality-aware work stealing to reduce cache invalidations | 67  |

| 5 | General scheduling loop of a worker $w_i$                  | 81  |

| 6 | Heterogeneous Earliest-Finish-Time (push_activated)        | 86  |

| 7 | Distributed Dual Approximation (push_activated)            | 88  |

| 8 | XKaapi algorithm to steal tasks on the Intel Xeon Phi      | 102 |

| 9 | The tiled algorithm for Cholesky factorization             | 139 |

#### Introduction

Parallelism can be see as an ubiquitous aspect in life. Although our speech is sequential, music has a lot of concurrent elements at same time presented by each instrument. Yet, those instruments play a stream of sound that may not sense anything pleasant if taken isolated. In parallel computing, there are many research areas ranging from architectures to high-level paradigms that can not be taken separately. For instance, parallel programming models abstract underlying architecture details; but it also may be depend on hardware tendencies.

Most programmers may prefer sequential processors as observed in the years predominated by technology advances such as deep pipeline, out-of-order, speculative processors. These architectures maintained the existing sequential programming model and the increasing performance at affordable price for technology at that time. However, this demand for more performance led to inefficient chips in terms of transistor and power (Asanovic et al., 2009).

In the last few years the industry decided to replace the power-inefficient processor with efficient processors on the same chip, providing more and more on-die cores each year. Current microprocessors are homogeneous multicore chips containing from two to sixteen cores, with even higher core counts in the near future. An architectural trend is the emergence of manycore accelerators with many tightly coupled processing units (PU) such as graphics cards (GPU) or Intel Xeon Phi coprocessors for high performance computing (HPC). Although multicore chips seeks to maintain the execution speed of sequential programs while moving into multiple cores, accelerators favor the execution throughput (Kirk and Hwu, 2012). Therefore, such architectures have heterogeneous PUs in terms of computing power and programming model.

Hence, in many cases, familiar and widely used algorithms need to be rethought and rewritten to take advantage of modern multicore and manycore architectures. Parallel algorithms with fine granularity and asynchronicity are essential in order to exploit parallelism and to improve scalability (Buttari et al., 2009).

#### 1.1 Motivation

A challenge in heterogeneous systems is delegate work efficiently to take advantage of all available parallelism since the workload can be affected by the differences in the processing power of each PU. Besides, there are more issues to be considered as dependencies between tasks of different PUs and overhead costs. These costs come from decisions of where actually execute a task, loading its execution code at runtime, costs of library calls from

different PU softwares, and memory transfers required since the PUs do not share the same memory address space.

A well-known load balancing strategy is work stealing. It is a decentralized scheduling algorithm that whenever a processor runs out of work, it steals work from a randomly chosen processor. This strategy achieves provably good performance results for shared-memory systems, but it is not actually applied to heterogeneous systems because of its cache-unfriendly limitations (Acar et al., 2000) and co-processor nature of PU units.

Little research has been done on comparing scheduling strategies on heterogeneous architectures. Augonnet et al. (2009b) compare three strategies in one experiment, which may be insufficient to assert the strengths and weaknesses of each strategy. Most common strategies rely on cost models such as HEFT (Augonnet et al., 2010a) or centralized scheduling (Ayguadé et al., 2009a; Bueno et al., 2011, 2012). We note that both approaches have drawbacks. A cost model scheduling depends on regular computations and does not adapt to load variation at runtime. Besides, a centralized scheduling does not scale as the number of workers increase, and is not suitable for fine-grained computations.

#### 1.2 Hypothesis

In order to deal with the issues on heterogeneous systems, we must consider some hypothesis about runtime systems for accelerators:

- A data-flow task programming model should allow to loose synchronization and exploit parallelism on accelerators;

- A runtime system should improve performance on accelerators by fully asynchronous operations;

- Work stealing scheduler with data locality heuristics should overcome its cacheunfriendly problem;

- Dynamic scheduling strategies should react to unbalances compared to cost models at runtime.

#### 1.3 Objectives

The main objective of this work is to study the issues of task parallelism with data dependencies on multi-CPU architectures with accelerators. We target those architectures with the XKaapi runtime developed by the french team MOAIS (INRIA Rhône-Alpes).

We first propose the use of data-flow task programming model as a solution to program heterogeneous architectures. Task parallelism seems to be a well-suited programming model since parallelism is explicit and processor oblivious, *i.e.*, applications can unfold more parallelism than resources available. In addition, data-flow dependencies provide an explicit memory view and abstract data transfers.

Concerning the work distribution at runtime, we then study the work stealing scheduler for multi-GPU architectures. We overcome the cache-unfriendly problem of work stealing by locality heuristics that, consequently, reduce data transfers substantially.

1.4. Contributions 3

In order to evaluate our work stealing strategies, we study strategies that predict execution cost at runtime by cost models. They may avoid erroneous decisions since work stealing does not consider the processing power of the available resources. We propose a broader approach in which a scheduling framework is designed to support different scheduling algorithms over multi-CPU and multi-GPU architectures.

In addition, one of our objectives is to evaluate the XKaapi runtime on the Intel Xeon Phi coprocessor. The coprocessor has support for x86 instructions and can run CPU programs entirely inside the accelerator. Our hypothesis is that our runtime may scale in a manycore architecture because of its overhead cost and scheduling by work stealing.

#### 1.4 Contributions

The first contribution of this thesis concerns the proposal of XKaapi extensions in order to support multi-GPU systems. This contribution was published in two papers. The first was published in *IEEE 24th International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD'12)* (Lima et al., 2012). In this paper we described our concurrent GPU operations to overlap data transfer and execution, along with work stealing scheduler of XKaapi.

The second paper was published in *IEEE 27th International Symposium on Parallel & Distributed Processing (IPDPS'13)* (Gautier et al., 2013b). In this paper we described our proposed scheduling heuristics to overcome the cache-unfriendly problem of work stealing.

The second contribution of this thesis concerns a study of scheduling strategies that include dynamic scheduling and cost model with performance prediction. Part of this contribution was submitted to *Parallel Computing* journal. In this paper we evaluated different scheduling strategies over XKaapi scheduling framework on multi-CPU and multi-GPU architectures.

Finally, the third contribution of this thesis concerns the evaluation of a data-flow task programming model over the Intel Xeon Phi coprocessor. The preliminary results of our third contribution were presented in *IEEE 25th International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD'13)* (Lima et al., 2013). In this paper, we described preliminary results of data-flow programming and work stealing scheduler of XKaapi on the Intel Xeon Phi coprocessor in native mode.

We give an overview of our contributions in Figure 1.1 on the following page that are highlighted in green. XKaapi version 1.0.1 provided support for the basic building blocks of our contributions: data-flow programming model, multicore support, and work stealing scheduler. Since this version we extended the runtime at our first contribution with multi-GPU support and work stealing heuristics (Chapter 5). Furthermore, our first work originated our two other contributions: version 2.1 with multi-CPU and multi-GPU support and scheduling framework (Chapter 6) and version 2.0 for Intel MIC architecture (Chapter 7).

Figure 1.1 – Timeline of the contributions of this thesis (green boxes).

#### 1.5 Context

In my master thesis at UFRGS, advised by Nicolas Maillard, I studied dynamic process creation in MPI in conjunction with system threads. After the master defense, I went to Grenoble for two months in order to establish a collaboration in the context of parallel programming with XKaapi. The initial PhD subject was defined after a number of meetings with Everton Hermann (early PhD student) and Bruno Raffin.

This work has been developed in the brazilian research group GPPD¹ (UFRGS) and the french research team MOAIS² (LIG). Besides, it has been involved in the context of the internacional associated lab LICIA³ composed of research groups from UFRGS and LIG. This work is also part of the efforts for efficient execution of fine-grained algorithms on multicore architectures with the XKaapi environment developed by the MOAIS team. It also continues the work of Everton Hermann's thesis (Hermann, 2010), co-supervised MOAIS/EVASION, that studied the parallelization of SOFA with KAAPI for multi-GPU architectures using work stealing. In addition to my advisors Nicolas Maillard (advisor at UFRGS), Bruno Raffin (directeur de thése at LIG), and Vincent Danjean (encadrant at LIG), I worked in collaboration with:

- Claudio Schepke about parallel applications, mostly climatological models such as OLAM (Schepke et al., 2013);

- Stéfano D. K. Mór about scheduling algorithms and theoretical aspects;

- Thierry Gautier in XKaapi development and most of experiments;

- Grégory Mounié and Denis Trystram about scheduling algorithms for GPUs.

#### 1.6 Thesis Outline

The text of this thesis is composed of three parts and eight chapters, as follows:

<sup>1</sup>http://ppgc.inf.ufrgs.br

<sup>&</sup>lt;sup>2</sup>http://moais.imag.fr

<sup>3</sup>licia-lab.org

1.6. Thesis Outline 5

#### Part I – Parallel Programming

This Part, composed of three chapters, gives an overview on parallel architectures and programming, along with related works in runtime systems.

#### Chapter 2 - Background

In this Chapter we provide background for parallel architectures and programming models, as well as scheduling algorithms for multicore and manycore architectures.

#### Chapter 3 – Programming Environments

This Chapter presents related works on parallel programming environments. It starts with programming tools for multicore and SMP architectures. The Chapter ends with runtime systems that target multi-CPU architectures with accelerators.

#### Chapter 4 – XKaapi Runtime System

In this Chapter we detail the XKaapi runtime that is the basis of this work. We first describe its goal and programming interface. We then detail its work stealing scheduler from previous works. The Chapter ends with a description of XKaapi data-flow computation.

#### Part II – Contribution