# Ordonnancement d'applications à flux de données pour les MPSoC embarqués hybrides comprenant des unités de calcul programmables et des accélérateurs matériels

Paul-Antoine Arras

## ▶ To cite this version:

Paul-Antoine Arras. Ordonnancement d'applications à flux de données pour les MPSoC embarqués hybrides comprenant des unités de calcul programmables et des accélérateurs matériels. Architectures Matérielles [cs.AR]. Université de Bordeaux, 2015. Français. NNT: 2015BORD0031. tel-01159519

# HAL Id: tel-01159519 https://theses.hal.science/tel-01159519v1

Submitted on 3 Jun 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Thèse présentée pour obtenir le grade de

# Docteur de l'Université de Bordeaux

École doctorale de mathématiques et d'informatique Spécialité informatique

## Par Paul-Antoine Arras

# Ordonnancement d'applications dynamiques à flux de données pour les MPSoC embarqués hybrides comprenant des unités de calcul programmables et des accélérateurs matériels

Sous la direction de : Emmanuel JEANNOT (co-directeur : Samuel Thibault)

Soutenue le mardi 3 février 2015

#### Membres du jury :

| M. Pierre Boulet    | Professeur, Université Lille 1                | Rapporteur            |

|---------------------|-----------------------------------------------|-----------------------|

| M. Daniel Éтіемвье  | Professeur, Université Paris Sud              | Rapporteur            |

| M. Didier Fuin      | STMicroelectronics Grenoble                   | Encadrant             |

| M. Alain GIRAULT    | Directeur de recherche, Inria                 | Examinateur           |

| M. Pascal Guitton   | Professeur, Université de Bordeaux            | Président             |

| M. Emmanuel Jeannot | Directeur de recherche, Inria                 | Directeur de thèse    |

| M. Samuel Тніваціт  | Maître de conférences, Université de Bordeaux | Co-directeur de thèse |

**Titre :** Ordonnancement d'applications dynamiques à flux de données pour les MPSoC embarqués hybrides comprenant des unités de calcul programmables et des accélérateurs matériels.

**Résumé**: Bien que de nombreux appareils numériques soient aujourd'hui capables de lire des contenus vidéo en temps réel et d'offrir une restitution de grande qualité, le décodage vidéo dans les systèmes embarqués n'en est pas pour autant devenu une opération anodine. En effet, les codecs récents tels que H.264 et HEVC sont d'une complexité telle que le recours à des architectures mixtes logiciel/matériel est presque incontournable. Or les plateformes de ce type sont notoirement difficiles à programmer efficacement.

Cette thèse relève le défi du développement d'applications à flux de données pour les cibles embarquées hybrides et de leur exécution efficace, et propose plusieurs contributions. La première est une extension des heuristiques d'ordonnancement de liste pour tenir compte des contraintes mémorielles. La seconde est un modèle d'exécution à flot de données compatible avec la plupart des modèles existants et avec une large classe de plateformes matérielles, ainsi qu'un ordonnanceur dynamique. Enfin, de nombreux développements ont été menés sur une architecture réelle de STMicroelectronics pour démontrer la faisabilité de l'approche.

**Mots-clés :** ordonnancement ; flot de données ; flux de données ; modèle d'exécution ; architectures hétérogènes ; architectures hybrides ; systèmes embarqués.

**Title:** Scheduling of dynamic streaming applications on hybrid embedded MPSoCs comprising programmable computing units and hardware accelerators.

**Abstract**: Although numerous electronic devices are nowadays able to play video contents in real time and offer high-quality reproduction, video decoding in embedded systems has not become a trivial process yet. As a matter of fact, recent codecs such as H.264 and HEVC exhibit such a complexity that resorting to mixed software-hardware architecture is almost unavoidable. However, programming efficiently this kind of platforms is well-known to be tricky.

This thesis addresses the issue of developing streaming applications for hybrid embedded targets and executing them efficiently, and proposes several contributions. The first one is an extension of the classical list-scheduling heuristics to take memory constraints into account. The second one is a dataflow execution model compatible with most existing models and with a large set of hardware platforms, as well as a dynamic scheduler. Lastly, numerous developments have been carried out on a real-world architecture from STMicroelectronics so as to demonstrate the feasibility of the approach.

**Keywords:** scheduling; dataflow; streaming; execution model; heterogeneous architectures; hybrid architectures; embedded systems.

**Unité de recherche :** Équipe-projet Inria Runtime, Centre de recherche Inria Bordeaux Sud-Ouest, 200 avenue de la Vieille Tour, 33 405 Talence Cedex.

« Chaque chose devrait être aussi simple que possible, mais pas davantage. »

Albert Einstein, cité par Shapiro [79].

# Remerciements

Mes remerciements vont en premier lieu à mes directeurs de thèse, Emmanuel Jeannot et Samuel Thibault côté Inria, et à mes encadrants, Didier Fuin et Arthur Stoutchinin côté STMicroelectronics, d'abord pour avoir accepté de me prendre en thèse, puis pour m'avoir toujours soutenu et écouté pendant toute la durée de celle-ci, surtout dans les moments difficiles – et il y en a eu! Je leur dois également des remerciements pour m'avoir laissé une grande liberté dans mon travail de recherche, tout en ayant su me guider chaque fois que le besoin s'en faisait sentir – équilibre difficile à trouver, s'il en est! Je remercie ensuite les membres de mon jury: Pierre Boulet et Daniel Étiemble, qui ont en outre accepté de rapporter cette thèse; Alain Girault qui, bien que n'étant pas rapporteur, a fourni de nombreux commentaires fort constructifs; et enfin Pascal Guitton qui a bien voulu en assumer la présidence.

J'aimerais ensuite remercier toutes les personnes qui m'ont permis d'effectuer mon travail dans de bonnes conditions - entendre par là, non pas qui m'ont permis d'être plus productif, mais qui m'ont permis de me sentir mieux dans ce que je faisais. Je commencerai par les plus proches physiquement, c'est-à-dire la fine équipe de l'open-space Runtime, et en particulier du carré VIP. Parmi eux, les anciens: Sylvain, sa vision fonctionnelle et son militantisme contagieux; Bertrand, ses blagues corses ou basques (selon les circonstances) et l'approche pyramidale du sport; Cyril B., fervent défenseur de Xchat et LibreOffice; Cyril R. pour les discussions interminables sur le travail libre. Les occupants du carré VIP au moment de mon départ: François, notre libriste national, avec qui j'ai partagé ce parcours du combattant qu'est la thèse – et bien d'autres choses...; Marc, qui a toujours su se montrer à la hauteur de mes attentes - voire au-delà; Chris, et ses calembours qui cartonnent; Nicolas et sa vision pessimiste mais néanmoins fort constructive; Théo, avec son arme de punition massive contre les blagues indigentes. De l'autre côté de l'open-space, j'aimerais remercier: Terry, qui a ouvert mon oreille à de nouveaux horizons musicaux; Samuel, fin connaisseur de La Grange et jamais le dernier pour les soirées arrosées; Thomas, pour ses conseils avisés en vue de la soutenance; James et Adèle, moins exubérants que le reste de la clique, mais tout aussi jovials.

Toujours par ordre de proximité, viennent ensuite les autres membres de Runtime. J'aimerais d'abord remercier: Emmanuel, Denis et Guillaume pour les soirées jeux mémorables; Brice qui, bien que n'étant pas, la plupart du temps, physiquement dans l'*open-space*, en porte l'esprit trolleur jusque dans son bureau. Je remercie aussi Andra, Nathalie, Pierre-André, Marie-Christine, Alexandre, Olivier et, bien sûr, Raymond, le charismatique chef d'équipe, pour m'avoir accueilli chaleureusement au labo.

Avant de quitter le cadre professionnel, je voudrais remercier l'AGOS pour avoir fourni et entretenu avec le plus grand soin notre principal outil de travail: le baby-foot. À cet égard, je me dois de 10 Remerciements

remercier l'ensemble de l'équipe Hiepacs pour leur contribution soutenue, et plus particulièrement: Emmanuel, pour les commentaires taquins – vexants, diront les mauvaises langues – pendant les matchs; Julien, pour les gamelles imaginaires; Damien et Aurel, pour les scènes de ménage derrière les cannes; François, pour les coups de hachoir; Elmer, pour sa mauvaise foi et son arrogance merveilleuses. Je remercie du fond du cœur mes infortunés partenaires, qui ont accepté de jouer avec moi malgré mon incompétence flagrante. Pour ce qui est d'Hiepacs, je remercie également Abdou et Mathieu pour les discussions informelles autour d'un verre ou d'un bon repas. À ce propos, je remercie également toute l'équipe du RU du Haut-Carré pour leur bonne humeur quotidienne et pour le solide soutien apporté à nos estomacs insatiables le midi; de même pour la cafétéria Inria et les petits-déjeuners.

Hors Inria, je souhaite remercier les nombreux colocataires avec qui j'ai eu la chance de partager des moments de vie, par ordre chronologique: Nicolas, qui m'a apporté un soutien fort appréciable à mon arrivée à Grenoble, ce pour quoi je lui suis profondément reconnaissant; Christine; Fred; JB, à qui, il me semble, je dois le qualificatif de « nazi de la télé »; Gaylord, qui m'a vendu du rêve avec ses potes vendéens; Juliette; Pierre; Plou; PM; Céline; Yuran et son adorable boule de poils; Sophie et son abominable rongeur aux oreilles tombantes; Théo, la personne la plus joviale que j'ai rencontrée à Bordeaux, avec qui j'ai pu avoir des échanges très positifs sur les difficultés de mener une thèse en entreprise; Coline, toujours très sport; Aurélie, gentiment délurée, qui a rythmé nos vendredis soirs à la bière et favorisé les échanges inter-colocs; Benoît; Lucie; et nos voisins de maisonnée: Benoît, Pierre, Clémence, Vincent, Maëva, Alexy et Marie. En outre, je remercie tous ceux avec qui j'ai passé de bons moments à Grenoble: Jun-Young, pour les nombreuses sorties ski démentielles; Betül; Yeter, l'organisatrice en chef de soirées; Lionel; Jérôme et ses lettres d'excuse « canoniques »; Maud; Jander; Ronan, à qui je dois mon unique expérience de ski nocturne; Victor; Ozan; Molka; ainsi que tous ceux, trop nombreux pour être cités, que j'ai eu le plaisir de côtoyer lors de soirées ou sorties.

Pour conclure, je remercie toute ma famille pour leur soutien permanent pendant ces trois ans, et en particulier mes parents et ma sœur qui sont venus de loin pour ma soutenance.

# **Avant-propos**

L'électronique embarquée imprègne nos vies. C'est un fait. Il n'y a qu'à observer l'essor des téléphones portables, aussi bien d'un point de vue commercial qu'au regard de l'usage qui en est fait, pour s'en convaincre. Et pourtant, la plupart des gens soit n'ont aucune idée de ce que le terme « électronique embarquée » recouvre, soit en ont une réductrice. Quand on entend « électronique embarquée », on pense bien souvent robotique, aérospatiale, aviation, automobile,... mais certainement pas téléphonie mobile, et encore moins décodage vidéo. « On » c'était moi jusqu'à il y a un peu moins de cinq ans, en 2010. À l'époque, j'étais plutôt intéressé par l'électronique de puissance (hacheurs, redresseurs, harmoniques, etc.). Mais ça, c'était avant que le responsable de la filière Électronique et systèmes embarqués (ESE) de l'École nationale supérieure de l'électronique et de ses applications (ENSEA) ne me détrompe. Les quelques minutes qu'a durées sa présentation ont suffi à me convaincre de choisir ESE plutôt que la filière consacrée à la puissance. Depuis, je n'ai pas regretté ce choix une seule seconde. En revanche, ma perception des différentes réalités que recouvre la conception de systèmes embarqués a sensiblement évolué au fil du temps. Au cours de ma dernière année à l'ENSEA, mon intérêt se portait essentiellement sur les aspects logiciels de bas niveau.

J'ai alors fait mon stage de fin d'études au Commissariat à l'énergie atomique et aux énergies alternatives (CEA) de Saclay (91), au sein du Laboratoire de calcul embarqué, où j'ai travaillé sur le portage du logiciel système développé sur place pour une architecture multicœur (P2012) conçue en partenariat avec STMicroelectronics. Mon passage au CEA, premier contact avec le monde de la recherche, m'a ouvert les yeux sur les défis intellectuels immenses à relever et les libertés bien plus grandes offertes aux chercheurs par rapport aux ingénieurs. De plus, mon travail sur P2012 a été très enrichissant et, à l'issue de mon stage, j'étais convaincu de son potentiel, aussi bien d'un point de vue industriel qu'académique. L'idée de poursuivre en thèse est néanmoins venue tardivement en regard du calendrier institutionnel: mon stage ayant commencé en avril et les dossiers de thèse au CEA devant être déposés en mai, il était trop tard pour postuler. Vu mon intérêt pour P2012, j'ai donc cherché à intégrer STMicroelectronics, d'abord comme ingénieur, puis j'ai très vite découvert les offres de thèses CIFRE, en particulier celle qui a abouti à la rédaction du présent document. J'ai donc postulé via l'immonde interface web de ST1... et n'ai jamais obtenu de réponse par ce biais. En parallèle, j'ai cherché l'annonce correspondante via les canaux académiques (forum ASR, etc.) et ai contacté le laboratoire d'accueil. C'est par ce dernier biais que j'ai obtenu le premier entretien d'une longue série. Après un aller-retour à Bordeaux et un à Grenoble, un entretien scientifique, deux tests de personnalités, un entretien avec un cabinet de recrutement, un autre avec les RH de ST et enfin un dernier avec mon futur encadrant, le dossier

<sup>1</sup> En plus d'être esthétiquement ignoble et anti-ergonomique, le site de recrutement ne fonctionne qu'avec Internet Explorer...

est envoyé à l'Agence nationale de la recherche technologique – chargée de valider les demandes de thèses CIFRE en vue de leur financement –, puis accepté deux mois plus tard. Je me dois, à ce titre, de rendre grâce à mes encadrants et à l'administration pour leur efficacité – en particulier celle de ST qui, par la suite, ne m'a pas vraiment habitué à de telles prouesses...

Voilà pour les prémisses. Il me semblait important de souligner les conditions qui m'ont accompagné jusqu'à cette thèse. Pour ce qui est du déroulement des trois années qui ont suivi, je n'énoncerai que quelques remarques à même d'éclairer la lecture du reste du document. Avant toute autre chose, il convient d'insister sur les difficultés inhérentes au travail de recherche en entreprise en général, et dans le cadre d'une thèse en particulier. D'autant plus quand les moyens mis à disposition dans ce sens sont réduits à leur plus simple expression:

- pas d'accès aux ressources documentaires<sup>2</sup>: Scopus, WoS, ACM, Springer, Elsevier, etc.;

- pas de formations adaptées<sup>3</sup>: méthodes de recherche et outils bibliographiques, rédaction, publication, etc.;

- pas de façon simple de contacter les autres doctorants;

- restrictions inacceptables dans l'utilisation des moyens informatiques:

- toutes les connexions vers l'extérieur sont bloquées par défaut, en particulier: accès web uniquement via proxy authentifié et man-in-the-middle en SSL, SSH interdit sauf dérogation longue et difficile à obtenir puis après authentification durant une courte fenêtre temporelle, etc.;

- pas de PC de bureau sous Linux, sauf dérogation motivée et très difficile à obtenir, puis, le cas échéant, pas de wifi, pas de VPN, image installée inadaptée au matériel, pas d'accès *root*, etc.

- sous Windows, interdiction de gérer ses courriels avec autre chose que M\$ Outlook.

Par ailleurs, l'environnement de travail est celui d'un ingénieur, pas celui d'un chercheur. Les discussions sont donc plus centrées sur la satisfaction du client que sur les défis scientifiques et technologiques à relever. En revanche, les ressources propres d'une grande entreprise, bien supérieures à celles d'un laboratoire de recherche académique, lui permettent de mettre en œuvre des moyens sans commune mesure, notamment pour ce qui est de l'informatique:

- ressources de calcul parfaitement dimensionnées, aussi bien en nombre qu'en puissance: il n'y a jamais d'attente pour le lancement d'une simulation;

- taux de plantage et de panne très faibles;

- stockage de toutes les données sur disques redondés avec accès extrêmement rapide;

- serveurs de travail à très haute capacité mémorielle, y compris pour les applications graphiques.

<sup>2</sup> Sauf IEEEXplore, à condition de passer par un portail fort peu pratique...

Pour être tout à fait exact, en tout et pour tout, en trois ans, une seule formation à destination des doctorants a été proposée par ST, sur le thème de la propriété intellectuelle et des brevets, vantant les mérites de ces derniers. Sujet primordial pour mener à bien un travail de recherche...

Un autre avantage supposé du travail en entreprise est l'existence de débouchés sur le marché qui sont censés garantir – ou, pour le moins, favoriser – la réutilisation des produits de la recherche en dehors du cercle académique. Dans mon cas, cet espoir de voir les fruits de son travail largement diffusés, même sous forme commerciale, n'a été qu'un mirage. En effet, le projet P2012 (devenu entre-temps STHORM) a été abandonné par ST en plein milieu de ma thèse. Les autres personnes travaillant dessus ont été transférées dans diverses équipes ou ont quitté l'entreprise. En conséquence, le modèle de programmation servant de base à mes travaux (PEDF) n'a dès lors plus été maintenu et le support est devenu pour ainsi dire inexistant, rendant d'autant plus difficiles les développements afférents.

Outre les difficultés liées au travail en entreprise, un autre inconvénient – certes moindre – a marqué le déroulement de cette thèse, côté Inria cette fois-ci: j'étais la seule personne du laboratoire dont le domaine de recherche était l'électronique embarquée, tous les autres travaillant sur le parallélisme et le calcul intensif. Côtoyer des chercheurs en informatique a néanmoins eu l'avantage de me faire prendre conscience des différences nombreuses et fondamentales entre ces deux domaines que je croyais initialement bien plus proches; j'y consacre d'ailleurs une part substantielle du premier chapitre. Cela dit, on aurait tort de sous-estimer l'impact négatif du déracinement, qu'il soit de l'ordre du domaine – faire de l'électronique dans un laboratoire d'informatique – ou de l'activité – être chercheur au milieu d'ingénieurs. En effet, le travailleur déraciné souffre d'un certain sentiment d'exclusion résultant de son incapacité à prendre pleinement part à la vie professionnelle du milieu dans lequel il baigne sans s'y fondre. Par ailleurs, le fait qu'il ne parle pas le même langage et ne raisonne pas de la même manière que ses collègues gêne la communication.

Enfin, d'un point de vue pratique – et contrairement à ce que l'on pourrait imaginer au premier abord –, partager son temps entre deux lieux de travail à 600 km l'un de l'autre ne relève pas forcément du défi logistique. Dans mon cas, le laboratoire remboursant le logement à Bordeaux, je pouvais garder deux domiciles pendant une partie de l'année, ce qui facilitait les échanges. En fin de compte, le surcoût financier a pour moi été quasi nul étant donné la prise en charge des déplacements et déménagements sous forme de missions, bien que le paiement en fût différé.

Pour conclure, malgré les nombreuses difficultés rencontrées, cette thèse a été pour moi une expérience globalement fort positive à la fois aux points de vue professionnel et personnel. Mon envie de faire de la recherche est venue tardivement mais se trouve maintenant bien ancrée et adossée à celle d'enseigner<sup>4</sup>. C'est pourquoi, après un post-doc au CEA sur la gestion d'architectures hétérogènes embarquées, je me destine aux fonctions d'enseignant-chercheur.

<sup>4</sup> Bien que n'étant pas doctorant contractuel, j'ai eu la chance de pouvoir m'initier à la pédagogie en suivant des formations et en encadrant des TD et TP de réseaux à l'Université de Bordeaux.

# Table des matières

| Remerciements                                                                                                                             | 9  |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| Avant-propos                                                                                                                              | 11 |

| Introduction                                                                                                                              | 17 |

| Chapitre 1. Contexte et environnement                                                                                                     | 21 |

| 1.1. Applications: traitement d'images et décodage vidéo                                                                                  | 21 |

| 1.1.1. Généralités sur le codage vidéo                                                                                                    |    |

| 1.1.2. Questions d'implémentation                                                                                                         | 24 |

| 1.2. Spécificités de l'embarqué                                                                                                           | 24 |

| 1.2.1. Différences entre électronique et informatique                                                                                     |    |

| 1.2.2. Matériel                                                                                                                           | 26 |

| 1.2.3. Logiciel                                                                                                                           | 26 |

| 1.2.3.1. Inadéquation des techniques de développement généralistes                                                                        |    |

| 1.2.3.2. Simulation et débogage                                                                                                           |    |

| 1.3. Plateforme cible                                                                                                                     |    |

| 1.3.1. Description du modèle d'architecture                                                                                               |    |

| 1.3.2. Présentation de STHORM                                                                                                             |    |

| 1.3.2.1. Accélérateurs matériels et flux de données                                                                                       |    |

| 1.3.3. Autres architectures similaires                                                                                                    |    |

| 1.3.3.1. Mega-Leon                                                                                                                        |    |

| 1.3.3.2. FISC                                                                                                                             |    |

| 1.3.3.4. DySER                                                                                                                            |    |

| 1.4. Problème abordé                                                                                                                      |    |

|                                                                                                                                           |    |

| Chapitre 2. Modèles à flot de données                                                                                                     |    |

| 2.1. État de l'art.                                                                                                                       |    |

| 2.1.1. Paramètres et reconfigurations                                                                                                     |    |

| 2.1.2. Réseaux de processus                                                                                                               |    |

| 2.1.3. Modèles statiques.                                                                                                                 |    |

| 2.1.4. Synthèse et comparaison des modèles existants                                                                                      |    |

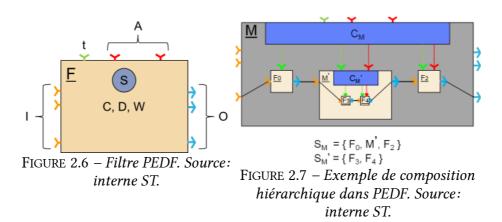

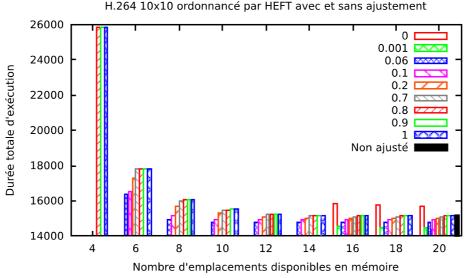

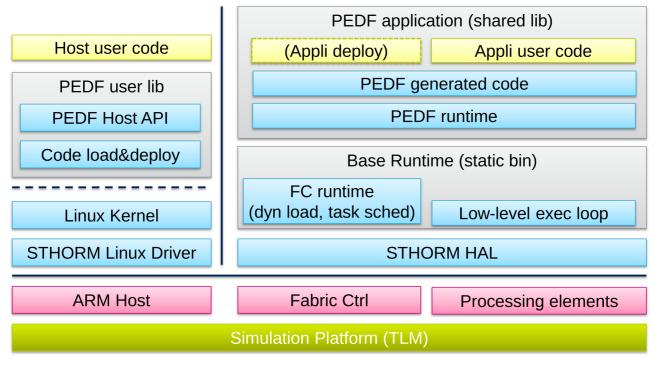

| 2.1.5. Modèles de programmation et outils de synthèse d'applications à flux de données 2.1.5.1. PEDF: modèle de programmation pour STHORM |    |

| 2.2. Modèle d'exécution proposé                                                                                                           |    |

| 2.2.1. Description du modèle inspiré de l'existant                                                                                        |    |

| 2.2.2. Contributions                                                                                                                      |    |

| 2.2.2.1. Sémantique de composition                                                                                                        |    |

| 2.2.2.2. Classification des paramètres                                                                                                    |    |

| 2.2.2.3. Paramètres indicatifs                                 | 48 |

|----------------------------------------------------------------|----|

| 2.2.3. Exemple d'application                                   | 48 |

| 2.3. Réflexion sur la gestion du risque d'interblocage         | 50 |

| 2.4. Conclusion                                                | 51 |

| Chapitre 3. Ordonnancement de liste sous contrainte de mémoire | 53 |

| 3.1. État de l'art                                             | 53 |

| 3.1.1. Heuristiques existantes                                 | 55 |

| 3.2. Définitions et modèles                                    | 56 |

| 3.2.1. Environnement de calcul                                 | 56 |

| 3.2.2. Modèle d'exécution                                      | 57 |

| 3.2.3. Modèle de mémoire                                       | 57 |

| 3.3. Définition du problème                                    | 59 |

| 3.3.1. Entrées                                                 |    |

| 3.3.2. Métriques                                               |    |

| 3.3.3. Discussion                                              |    |

| 3.3.4. Exemple motivant                                        |    |

| 3.3.5. NP-difficulté                                           |    |

| 3.3.5.1. Le problème Pebble(K)                                 |    |

| 3.4. Description de la solution proposée                       |    |

| 3.4.1. Ajustement des priorités                                |    |

| 3.4.2. Forçage des priorités                                   |    |

| 3.4.3. Gestion de l'insertion                                  |    |

| 3.4.4. Ordonnancement auto-séquencé                            |    |

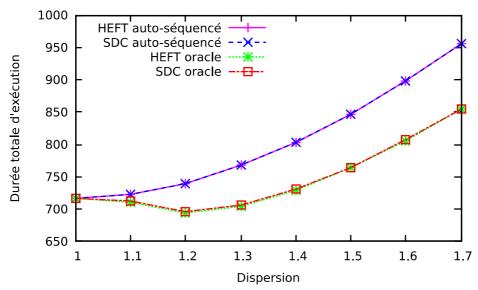

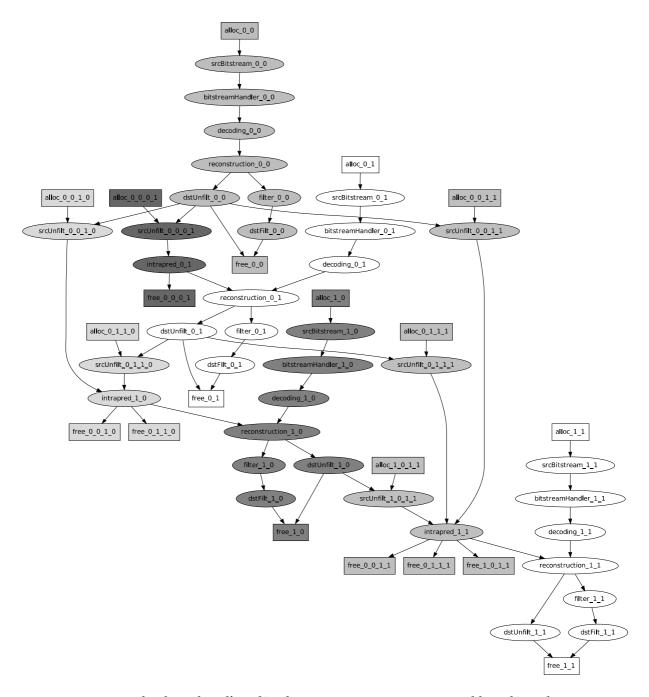

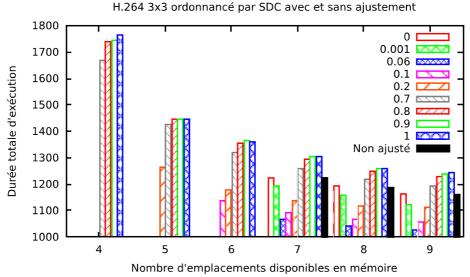

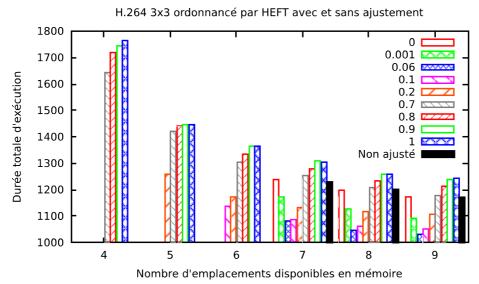

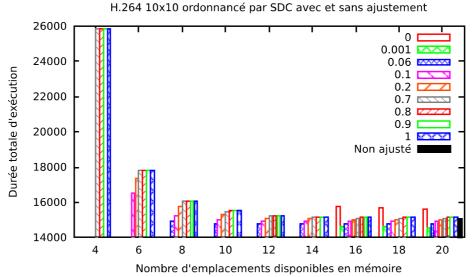

| 3.5. Expérimentations                                          |    |

| 3.5.1. TNR                                                     |    |

| 3.5.2. H.264                                                   |    |

| 3.6. Conclusion                                                | 78 |

| Chapitre 4. Implémentation et aspects expérimentaux            | 79 |

| 4.1. Co-conception matériel-logiciel                           |    |

| 4.1.1. Outils                                                  |    |

| 4.1.1.1 PEDF                                                   |    |

| 4.1.1.2. Orcc                                                  |    |

| 4.1.1.3. MAPS                                                  |    |

| 4.1.1.4. Discussion                                            |    |

| 4.2. Simulation                                                |    |

| 4.2.1. STHORN                                                  |    |

|                                                                |    |

| 4.3. Applications                                              |    |

| 4.3.2. H.264                                                   |    |

| 4.4. Conclusion                                                |    |

|                                                                |    |

| Chapitre 5. Contributions sur le logiciel système              |    |

| 5.1. Ordonnancement et gestion dynamique                       |    |

|                                                                | 91 |

| 5.1.2. Politiques d'ordonnancement                        | 97  |

|-----------------------------------------------------------|-----|

| 5.2. Filtres logiciels                                    | 98  |

| 5.3. Communication matériel-logiciel                      | 100 |

| 5.4. Assignation des acteurs aux ressources matérielles   | 101 |

| 5.5. Intégration dans PEDF et adaptation des applications | 102 |

| 5.6. Conclusion                                           | 104 |

| Chapitre 6. Expérimentations                              | 105 |

| 6.1. Protocole expérimental                               | 105 |

| 6.1.1. Paramètres indicatifs                              |     |

| 6.1.2. Flot moyen                                         | 105 |

| 6.1.3. Stratégies d'ordonnancement                        | 107 |

| 6.1.4. Applications                                       | 107 |

| 6.1.5. Simulation et mesures                              | 108 |

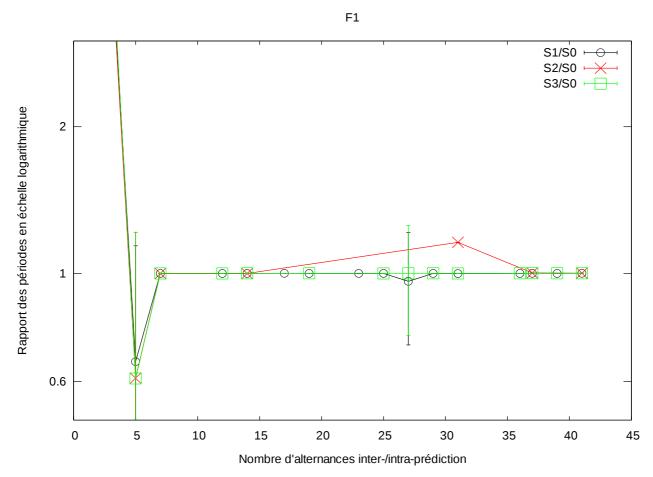

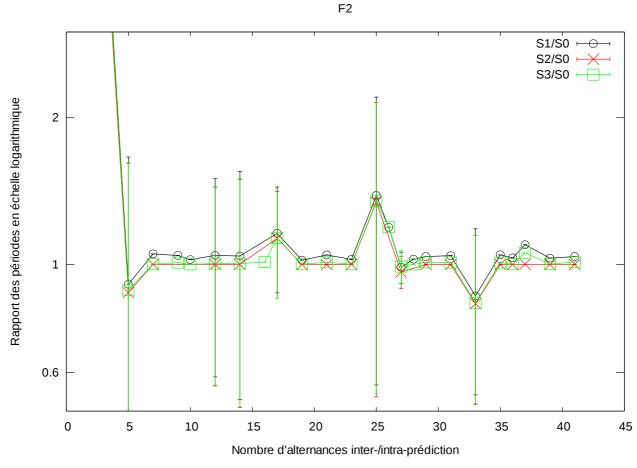

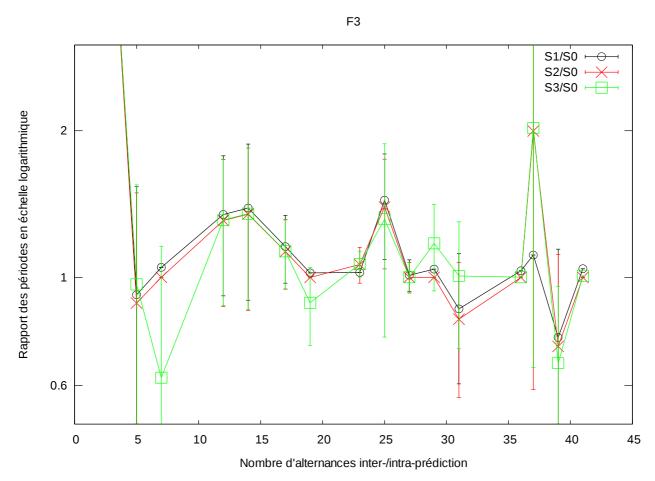

| 6.2. Résultats                                            | 108 |

| 6.2.1. TNR                                                | 108 |

| 6.2.2. H.264                                              | 110 |

| 6.3. Conclusion                                           | 115 |

| Conclusion                                                | 117 |

| Bibliographie                                             | 121 |

# Introduction

Plus que jamais, l'électronique multimédia imprègne nos vies. Et cette tendance ne semble pas près de se démentir. Après que les supports analogiques tels que les cassettes eurent laissé la place au numérique avec les CD, ces derniers furent à leur tour supplantés par le MP3. À chaque nouveau format son lecteur portable: en trente ans, l'évolution des baladeurs a été fulgurante [1]. Alors que les premiers Walkman de Sony étaient lourds, volumineux et énergivores, l'iPod d'Apple<sup>5</sup> est fin, léger et capable de distiller des heures de musique sans être rechargé. Mais cette évolution ne s'arrête pas à la musique: à partir de 2005, la lecture de vidéos fait immersion dans un monde où l'audio régnait jusqu'alors en maitre. Le marketing remplissant son office, ce qui passait quelque temps auparavant pour une idée farfelue devient rapidement un passe-temps indispensable. Ainsi l'expansion des appareils capables de lire des vidéos ne connaît-elle pas de limites. Les fabricants de téléphones mobiles ne tardent pas à surfer eux aussi sur la vague multimédia, complétant la panoplie des usages n'étant pas directement liés à la téléphonie. En fin de compte, l'essor de terminaux embarqués de plus en plus diversifiés disposant de fonctionnalités liées au son et à l'image équivalentes voire supérieures à celles des appareils dédiés a profondément modifié les pratiques des utilisateurs, au point de poser des problèmes sanitaires [2].

Ces mutations peuvent s'expliquer par les avancées technologiques réalisées dans différents domaines: les télécommunications avec les réseaux sans fil à haut débit, l'électronique embarquée avec une nouvelle génération d'architectures spécialisées, et la compression vidéo. Leur convergence se traduit, par exemple, par la possibilité d'assister en direct depuis son téléphone portable à des retransmissions filmées d'évènements sportifs ou culturels. Si cet état de fait peut laisser penser que l'opération consistant à décoder un flux d'images serait devenue une tâche anodine à la portée de n'importe quel système embarqué, il n'en est rien. En réalité, la complexité des applications précède bien souvent celle du matériel; de ce fait, il revient aux concepteurs de ce dernier de suivre le rythme des innovations. Or, la conception des systèmes embarqués est un processus long et qui n'admet pas les imperfections tolérées dans le développement des logiciels informatiques. Des solutions doivent donc être proposées en amont, avec la caractéristique de pouvoir s'adapter rapidement aux nouvelles exigences. Il s'agit généralement d'un assortiment d'unités de calcul programmables et d'accélérateurs matériels regroupés dans un même système sur puce multiprocesseur (multiprocessor system on chip, MPSoC). Le très populaire Raspberry Pi<sup>6</sup>, bien que s'adressant à un public averti, est représentatif de cette tendance: il comprend un cœur ARM destiné à exécuter du code logiciel généraliste, et un processeur graphique Broadcom permettant de décoder des vidéos de qualité équivalente au format Blu-ray. De tels systèmes sont qualifiés

<sup>5</sup> Pour ne citer que les deux plus grands succès commerciaux.

<sup>6 &</sup>lt;a href="http://www.raspberrypi.org/">http://www.raspberrypi.org/</a>

20 Introduction

d'hétérogènes au sens où ils comprennent plusieurs types de processeurs – deux dans le cas du Raspberry Pi.

Du point de vue des applications, la complexité se traduit par une implantation difficile sur le matériel existant. C'est le cas, en particulier, des applications à flux de données (*streaming*) dont les algorithmes de décodage vidéo utilisés pour le visionnage sur les terminaux des utilisateurs sont de bons représentants. Pour cette classe d'applications, l'implantation peut être facilitée par le recours à des modèles à flot de données (*dataflow*). Côté matériel, il est également possible de favoriser l'exécution en adaptant la plateforme à ce modèle, de sorte qu'il puisse cohabiter avec le paradigme Von Neumann classique: on parle alors d'architecture hybride, ce qui constitue un cas particulier d'hétérogénéité. À cela s'ajoute le caractère dynamique et imprévisible de ces applications, dû à la complexité des algorithmes récents, qui pèse sur l'efficacité de l'exécution et soulève d'importantes questions d'ordonnancement auxquelles s'attache à répondre cette thèse.

## Cadre de la thèse et contributions

STMicroelectronics a commencé à travailler en 2009 sur un projet de plateforme multicœur hybride embarquée répondant à ces critères. L'absence d'outils existants satisfaisants pour le placement efficace du code applicatif sur une telle architecture a conduit l'entreprise à faire appel au savoir-faire de l'équipe Runtime d'Inria dans ce domaine. Cette thèse CIFRE s'inscrit dans ce contexte.

En vue de réduire le fossé entre les applications et l'architecture, il est nécessaire de recourir à des modèles de calcul, de programmation et d'exécution adaptés. Le dynamisme et la complexité d'une part, l'hybridité d'autre part, rendent ce besoin encore plus criant. C'est pourquoi le premier objectif de la thèse est de tenter de combler ce fossé en proposant un modèle d'exécution à flot de données adapté à ces caractéristiques particulières. Cette solution se différencie de l'existant par le support d'un nouveau type de paramètres à même de capturer les facteurs de variabilité de l'application.

L'exécution efficace des applications étant étroitement liée à l'ordonnancement, cet aspect est également abordé. La question cruciale du choix entre approche statique et dynamique est soule-vée. Il semblerait que la seconde soit plus adaptée pour les applications à forte variabilité: cette conjecture est discutée et des outils d'évaluation sont présentés. Par ailleurs, le problème fondamental des contraintes mémorielles dans les systèmes embarqués est également traité, et une solution concrète fondée sur des techniques existantes et éprouvées est apportée. Enfin, le modèle d'exécution proposé est lui aussi adossé à un ordonnanceur spécifique dont la stratégie peut être définie par l'utilisateur pour plus de flexibilité.

# Organisation du document

La présente thèse s'articule autour de six chapitres. Le premier expose le contexte et les hypothèses de travail, et formule la problématique. Le second décrit le modèle d'exécution à flot de données proposé, en quoi il se distingue de l'existant et les réponses qu'il apporte aux problèmes soulevés. Le troisième aborde la question de l'ordonnancement sous contrainte de mémoire et propose un ajustement d'une classe répandue d'heuristiques en vue d'y introduire des garanties fortes. Le quatrième revient brièvement sur des considérations relatives à l'implémentation et au

Introduction 21

protocole expérimental adoptés pour le modèle présenté au chapitre 2. Le cinquième relate les contributions apportées au logiciel système en vue de supporter le modèle défini précédemment. Enfin, le dernier chapitre conclut l'exposé en présentant les résultats expérimentaux liés à l'évaluation des travaux présentés dans les chapitres 2 et 5, à savoir le modèle d'exécution adossé au support logiciel.

# **CHAPITRE 1. Contexte et environnement**

Ce chapitre a pour objet de décrire le contexte scientifique et technique de cette thèse. La première section évoque les applications visées en insistant sur leurs particularités et les défis qu'elles soulèvent. La deuxième section explicite les spécificités de l'électronique embarquée et notamment en quoi celles-ci doivent impérativement être prises en compte tout au long du processus de développement. La troisième section est consacrée au modèle d'architecture ciblé ainsi qu'à la plateforme réelle sur laquelle ont eu lieu les expérimentations de la thèse. Enfin, la dernière section expose formellement le problème abordé.

# 1.1 Applications: traitement d'images et décodage vidéo

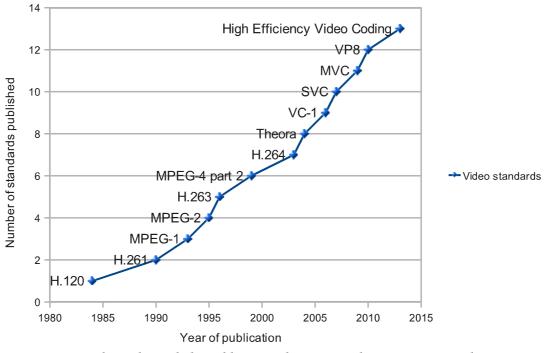

FIGURE 1.1 – Chronologie de la publication des normes de compression vidéo. Source: Wipliez [80].

À l'heure où la convergence des terminaux numériques repousse les limites de l'intégration de fonctionnalités multimédias autrefois dévolues à des appareils *ad hoc*, il n'est pas rare de rencontrer des téléphones mobiles capables de reproduire des contenus vidéo en diffusion continue émanant d'un réseau sans fil. De fait, l'électronique grand public du divertissement – baladeurs, tablettes, décodeurs télévisuels, etc. – a connu une croissance exponentielle durant la dernière décennie, et qui, selon toute vraisemblance, ne devrait pas se démentir au cours des prochaines années, en particulier dans le domaine du décodage vidéo. En effet, les normes de compression

audiovisuelle ont connu dans la même période une évolution effrénée (voir figure 1.1) qui a permis d'atteindre une qualité de restitution sans précédent. Néanmoins, cette amélioration ne va pas sans un accroissement de la complexité [3] des algorithmes employés, qui rend l'implémentation d'autant plus ardue (cf. section 1.1.2), posant de nombreux défis.

Pour cette raison, cette thèse s'intéresse prioritairement au décodage vidéo, mais également à toute une classe d'applications dites « à flux de données » – c'est-à-dire dont la structure et le fonctionnement sont tels que, d'un point de vue haut niveau, les données « s'écoulent » entre unités fonctionnelles en cascade – dont la plupart des algorithmes dédiés au traitement du signal sont des exemples éloquents. Les travaux présentés dans les prochains chapitres sont donc applicables à l'ensemble de cette classe, et en particulier à un sous-ensemble rendu difficile à appréhender du fait d'un fort dynamisme caractérisé par une imprédictibilité et une variabilité nécessitant des reconfigurations à l'exécution.

## 1.1.1 Généralités sur le codage vidéo

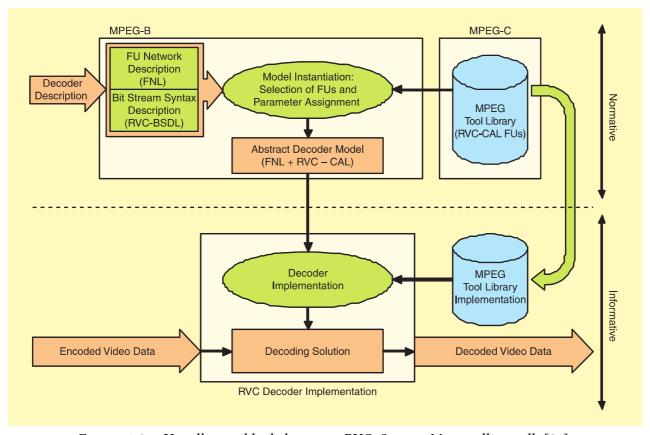

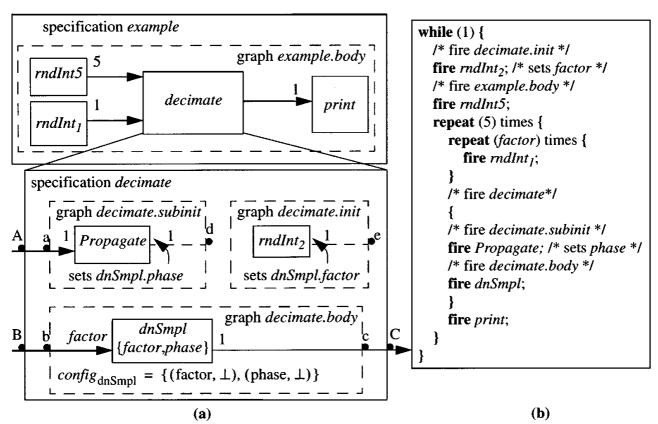

FIGURE 1.2 – Vue d'ensemble de la norme RVC. Source: Mattavelli et coll. [81].

Les évolutions récentes des algorithmes d'encodage et décodage (codecs) vidéo visant à améliorer l'expérience des utilisateurs – image ultra haute définition (UHD, 4K voire 8K), 3D, etc. – ainsi que l'efficacité accrue de la compression justifient un besoin croissant en puissance de calcul. Parmi les codecs modernes les plus répandus, on peut citer, par ordre chronologique [4]:

- MPEG-2: DVD, SVCD, télévision numérique terrestre (TNT) simple définition;

- H.264 (ou MPEG-4 partie 10/AVC): HD-DVD, Blu-ray, TNT haute définition;

- HEVC (ou H.265): télévision UHD (4K, 8K).

Devant la complexité croissante des codecs et l'apparition de plus en plus fréquente de nouveaux venus, une nouvelle norme de codage vidéo reconfigurable (RVC) [5] a été introduite pour adapter leur description de façon à faciliter leur implémentation sur des cibles diverses, aussi bien matérielles que logicielles. Comme le montre la figure 1.2, cette norme comprend une restriction du langage CAL [6] (RVC-CAL) permettant de décrire l'algorithme sous forme d'un modèle de décodeur abstrait (abstract decoder model) qui remplace les implémentations de référence en C; elle fournit également une bibliothèque standard (MPEG Tool Library) comprenant des briques de base (functional units, FUs) pour construire de tels décodeurs, mais laisse la porte ouverte à des implémentations propriétaires. Le chapitre 4 présente Orcc, une chaine d'outils dédiée à RVC.

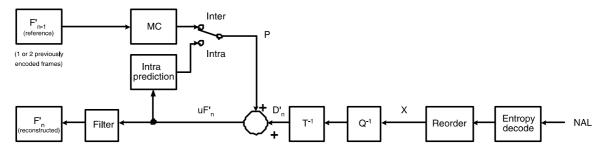

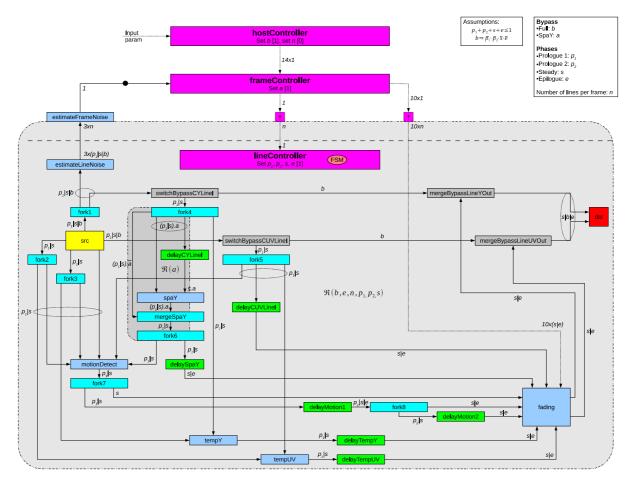

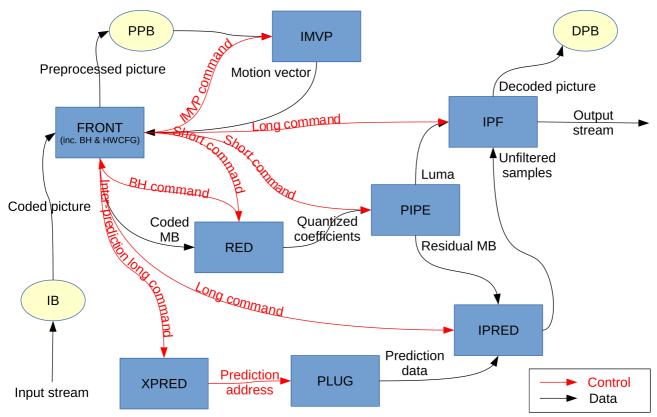

FIGURE 1.3 – Décodeur H.264. Source: Richardson [8].

Cette approche est d'autant plus valorisable que tous les codecs sont fondés sur les mêmes bases et partagent une structure commune. Une séquence vidéo est composée d'images ou *trames*, divisées en groupes de pixels – typiquement de forme carrée et de taille 16 ×16 [7] –, appelés *macroblocs*, regroupés en séquences contigües dans l'ordre de balayage<sup>7</sup>, appelées *tranches*. La figure 1.3 représente le schéma d'un décodeur H.264, mais le principe reste le même pour les autres codecs. La première partie (à droite sur la figure) consiste à décoder les échantillons, appelés résidus, à les réordonner, et à leur appliquer une quantification et une transformée en cosinus discrète inverse (IDCT). La deuxième (à gauche sur la figure) comprend la prédiction intra- ou inter-images, ainsi que le filtrage<sup>8</sup>.

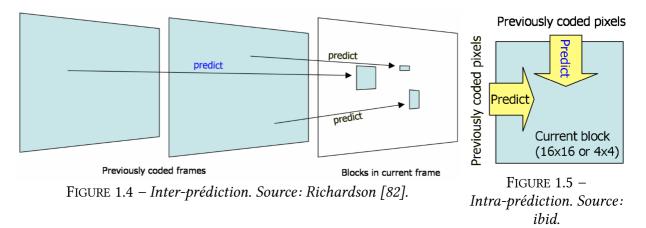

L'intra-prédiction [9] (fig. 1.4) est une méthode de codage qui réduit les redondances spatiales en utilisant les pixels limitrophes déjà codés (à gauche et au-dessus) au sein d'une même image pour

<sup>7</sup> Historiquement, les écrans analogiques affichaient les images par projection d'un faisceau qui balayait la surface horizontalement de gauche à droite, ligne par ligne de haut en bas. Les codecs numériques ont conservé cet ordre pour le traitement des macroblocs.

<sup>8</sup> Se reporter à Richardson [8] pour les détails de chaque étape.

reconstruire un macrobloc. L'inter-prédiction [10] (fig. 1.5) opère quant à elle dans le domaine temporel, en s'appuyant sur des échantillons provenant d'images déjà décodées, par le biais d'un mécanisme appelé compensation de mouvement et connu pour être le principal goulet d'étranglement dans le décodage vidéo en temps réel [11]. L'alternance entre macroblocs intra- et inter-codés au sein d'une même trame est un bon exemple de variabilité induisant un fort dynamisme chez tous les codecs vidéo récents.

# 1.1.2 Questions d'implémentation

Le processus de décodage vidéo est d'autant plus délicat qu'il doit le plus souvent être effectué en temps réel: le flux brut est traité au fur et à mesure qu'il est lu, et si une trame n'a pu être correctement reconstruite au terme du temps imparti, l'expérience de l'utilisateur risque d'être dégradée par un affichage saccadé, des artéfacts dans l'image, etc. À titre d'exemple, un décodeur H.264 certifié 1080p<sup>9</sup> doit être en mesure de décoder jusqu'à 589824 macroblocs par seconde, ce qui, avec un seul processeur cadencé à 600 MHz, correspond à un budget de 1017 cycles par macrobloc. Dans ces conditions, il est clair qu'un traitement séquentiel par un processeur embarqué généraliste n'est pas envisageable.

Pourtant, jusqu'à il y a peu, les pratiques courantes pour l'implémentation de décodeurs vidéo étaient essentiellement centrées sur des solutions logicielles avec peu – voire pas – de parallé-lisme. En effet, la conception matérielle est longue et coûteuse, ce qui est incompatible avec les impératifs de réduction des temps de mise sur le marché dus à la concurrence industrielle féroce. En revanche, le développement logiciel est un processus beaucoup plus rapide, itératif et flexible, qui permet notamment la correction de défauts de conception à posteriori. De plus, les implémentations de référence des décodeurs étant, jusqu'à l'avènement récent de RVC, purement séquentielles, la parallélisation était une tâche fastidieuse. Mais aujourd'hui, la complexité des derniers codecs est telle que la seule solution viable consiste à avoir recours à un parallélisme fonctionnel, d'une part, et à des accélérateurs matériels dont chacun est spécialisé dans l'exécution d'une tâche bien déterminée, d'autre part.

Cette solution hybride, alliant la flexibilité du logiciel et l'efficacité – à la fois en termes de rapidité d'exécution, de surface de silicium et de consommation énergétique – du matériel, peut prendre la forme d'une plateforme hétérogène modulable extensible telle que celle décrite à la section 1.3.2. La mise en œuvre d'une telle solution implique en outre de disposer d'une description de l'application à haut niveau d'abstraction permettant de cibler à la fois le matériel et le logiciel: les modèles à flot de données présentés au chapitre 2 répondent à cette nécessité.

# 1.2 Spécificités de l'embarqué

Cette section tente d'abord de circonscrire ce que l'on entend usuellement par le terme « embarqué », employé dans des contextes très divers, avant de définir aussi précisément que possible l'acception retenue dans le cadre de cette thèse. Ses spécificités seront ensuite étudiées, à la fois sur les plans matériel et logiciel.

<sup>9</sup> La notation 1080p signifie 1080 lignes de pixels par image et balayage progressif. Les chiffres fournis ici correspondent à un décodeur de niveau 5.

# 1.2.1 Différences entre électronique et informatique

Samek [12] définit un système embarqué comme « ayant un ordinateur enfoui en son sein mais n'étant pas perçu comme tel par l'utilisateur », ce qui n'est pas dénué de subjectivité. Une autre définition parfois adoptée par les enseignants en guise d'introduction est qu'il s'agit d'un système informatique qui n'est pas un ordinateur. Ces deux définitions soulignent, à juste titre, l'aspect informatique, mais omettent - peut-être volontairement - le non moins important aspect électronique. Celle donnée par Wikipédia comble ce manque: « Un système embarqué (ou système enfoui) est défini comme un système électronique et informatique autonome, souvent temps réel, spécialisé dans une tâche bien précise. » Est-ce à dire que les deux composantes coexistent toujours à parts égales dans de tels systèmes? L'observation de l'extrême hétérogénéité qui caractérise la vaste classe de l'embarqué permet d'y répondre: la dimension informatique est par exemple bien plus prépondérante dans un téléphone dit « intelligent » que dans un commutateur de réseau. Il apparaît donc nécessaire d'opérer une distinction entre électronique embarquée et informatique embarquée. Hennesy & Patterson [13] choisissent comme critère le support de logiciels tiers, ce qui implique la présence d'un système d'exploitation. Au contraire, en électronique embarquée, seul un logiciel système est nécessaire pour gérer un ensemble prédéfini d'applications. Le tableau 1 résume les caractéristiques des différentes classes de systèmes.

|                          | Perçu par l'utilisateur comme<br>un ordinateur | Système d'exploitation | Exemple      |

|--------------------------|------------------------------------------------|------------------------|--------------|

| Électronique embarquée   | Non                                            | Non                    | Décodeur TV  |

| Informatique embarquée   | Pas forcément                                  | Oui                    | Raspberry Pi |

| Informatique généraliste | Oui                                            | Oui                    | PC de bureau |

TABLEAU 1 – Caractéristiques des différentes classes de systèmes.

De manière générale, l'objectif principal de conception en électronique embarquée est de minimiser les coûts de production (surface de silicium) tout en garantissant le niveau de performance requis (prédictibilité), et non d'atteindre la performance maximale. De ce fait, les métriques utilisées sont la densité de performance (en millions d'instructions par seconde par millimètre carré [MIPS/mm²]) et la densité de puissance (en watts par millimètre carré [W/mm²]), plutôt que la puissance brute en MIPS ou en nombre d'opérations flottantes par seconde (FLOPS). Enfin, comme le soulignent Sheng et coll. [14], le modèle commercial est également différent: le haut niveau de désagrégation de l'industrie électronique, où les fabricants sont souvent spécialisés dans des domaines précis, favorise une approche horizontale – plusieurs processeurs de différents fabricants dans un même système – plutôt que verticale – chaque fournisseur contrôle l'ensemble de la chaine du matériel au logiciel. S'ajoute à cela un cycle de vie raccourci pour l'embarqué: la pression visant à la réduction du temps de mise sur le marché impose de fréquentes évolutions sur les plateformes produites, avec pour conséquence la nécessaire adaptabilité de la pile logicielle associée.

<sup>10</sup> http://fr.wikipedia.org/wiki/Syst%C3%A8me\_embarqu%C3%A9

#### 1.2.2 Matériel

Les systèmes embarqués étant définis comme « spécialisés dans une tâche bien précise<sup>11</sup> », il est clair que les architectures et micro-architectures généralistes que l'on trouve dans les ordinateurs sont hautement inadaptées à ce dessein. Au contraire, la spécialisation de l'architecture est un facteur décisif qui permet d'atteindre le niveau de performance souhaité sans gaspillage de ressources. Des exemples de telles architectures sont données à la section 1.3.3.

Parmi les spécificités du matériel embarqué, on peut citer la très haute intégration des systèmes sur puces (systems on chips, SoC) pour notamment satisfaire aux contraintes d'espace et de mobilité, mais aussi le calcul sur composants discrets de toutes sortes: processeurs généralistes ou spécialisés (par exemple dans le traitement du signal), circuits logiques programmables (p. ex. FPGA ou CPLD), accélérateurs matériels, etc. Les contraintes d'espace et de mobilité imposent également des limites sur la quantité et la nature de la mémoire: les disques durs, lourds et volumineux, sont délaissés au profit de mémoire de type Flash pour le stockage de masse, et la mémoire volatile statique est largement utilisée, pas uniquement pour les caches (voir l'exemple de STHORM à la section 1.3.2). Les processeurs sont aussi plus simples: le Sandy Bridge d'Intel dispose de dix-sept étages de pipeline, tandis qu'un STxP70 de STMicroelectronics n'en a que cinq. D'autre part, l'adressage est direct afin d'éviter le surcoût lié à la mémoire virtuelle: pas de matériel dédié à sa gestion – mais éventuellement une unité de protection visant à prévenir les accès illicites – ni de couche logicielle supplémentaire dans le noyau; en pratique, le chargement de l'application s'en trouve simplifié, l'imprédictibilité réduite et les performances améliorées.

Bien souvent, la spécialisation de la micro-architecture va de pair avec un jeu d'instructions réduit et simplifié, permettant une taille de code diminuée et un décodage plus aisé. Une fonctionnalité particulièrement intéressante, et qui fait pourtant défaut à la plupart des architectures généralistes, est le support des évènements: ils permettent à plusieurs processeurs de communiquer de façon moins intrusive et beaucoup plus efficace que par le biais d'interruptions. Enfin, tous les systèmes embarqués sont conçus avec le souci de minimiser la consommation énergétique, à plus forte raison pour les appareils mobiles dont l'autonomie doit être préservée, ainsi que la dissipation thermique.

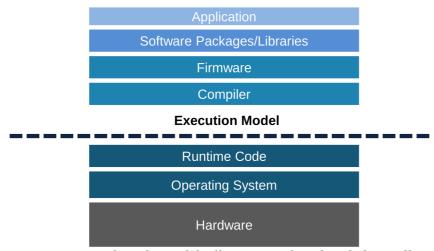

## 1.2.3 Logiciel

Outre les différences matérielles, les systèmes embarqués se distinguent également par leur programmation qui, selon Samek [12], nécessite une approche fondamentalement différente. En effet, le développement pour les cibles embarquées offre à la fois des facilités – par exemple des hypothèses fortes sur l'environnement logiciel et matériel – et des difficultés – comme la gestion manuelle de la mémoire – totalement étrangères à l'informatique générique. Le développeur embarqué dispose d'un contrôle accru – accès direct aux périphériques via des registres mappés en mémoire – qui peut être vu comme un avantage ou un inconvénient: les garde-fous mis en place par le système d'exploitation sont autant d'entraves, tandis que les primitives de haut niveau exposées ajoutent de nombreux niveaux d'indirection pouvant être jugés inutiles voire néfastes. Au contraire du développement informatique conventionnel où le recours à de larges bibliothèques tierces est la norme, l'embarqué adopte une approche minimaliste privilégiant la simplici-

<sup>11</sup> Le niveau de précision de la tâche en question peut ou non impliquer la Turing-complétude, selon les cas.

té au détriment de la réutilisabilité; à plus forte raison pour des systèmes critiques, un développeur ne prendra pas le risque d'introduire du code qu'il ne maîtrise pas parfaitement. Il est également des compromis jugés inhabituels: les contraintes de mémoire sont parfois telles qu'elles conduisent à préférer réduire l'empreinte du code quitte à perdre en performance.

## 1.2.3.1 Inadéquation des techniques de développement généralistes

Cette sous-section énumère un certain nombre de techniques largement répandues en informatique, à tel point qu'il ne viendrait à l'esprit d'aucun développeur conventionnel de les remettre en cause; et pourtant, ce qui suit expose les raisons pour lesquelles elles doivent, autant que faire se peut, être évitées dans un contexte embarqué.

#### 2.3.1.1 Allocation de mémoire dynamique

Comme le souligne Samek [12], allouer de la mémoire dynamiquement fait appel à une structure de donnée de type tas qui, à elle seule, concentre un grand nombre de problème. En premier lieu, le tas gaspille une quantité de mémoire certes négligeable dans un environnement de type PC mais rédhibitoire dans le cas d'un système embarqué: cela est dû pour partie au stockage des méta-données, mais surtout à la fragmentation qui se forme au fur et à mesure que des segments de tailles diverses sont alloués puis libérés, à tel point qu'il est possible que la mémoire restante soit suffisante pour une allocation mais que celle-ci ne puisse pas avoir lieu par défaut de contigüité. De plus, il est extrêmement difficile de prédire la taille adéquate du tas, ce qui amène généralement à le surdimensionner grossièrement. Par ailleurs, les primitives d'allocation et de libération sont coûteuses, non déterministes – ce qui est inacceptable pour un grand nombre d'applications subissant des contraintes d'exécution en temps réel dur – et non réentrantes.

En outre, les dangers de l'allocation dynamique bien connus de tous les développeurs, sont encore plus prégnants en électronique embarquée: une seule fuite, même de taille réduite, peut suffire à saturer la mémoire; la technique consistant à sécuriser un pointeur en le mettant à zéro ne fonctionne pas si l'adresse nulle existe – c'est le cas de STHORM; le débogage est difficile car l'on ne sait pas à l'avance où seront stockées les données et, en l'absence de mémoire virtuelle, les erreurs de segmentation n'existent pas.

# 2.3.1.2 Édition des liens et chargement dynamiques

L'éditeur de liens est un programme qui modifie le code objet d'une application en remplaçant les références sous forme de symboles par leurs adresses relatives, tandis que le chargeur copie l'application de la mémoire de stockage vers la mémoire exécutable [15]. Les deux étapes les plus longues et complexes [16] sont la résolution des symboles et la relocalisation, qui sont, pour cette raison, généralement effectuées juste après la compilation: on parle alors d'édition des liens statique; dans le cas dynamique, au contraire, ces deux étapes ont lieu à l'exécution. Autant, sur un PC, cette dernière méthode peut être quasi transparente, autant, en électronique embarquée, son coût est la plupart du temps rédhibitoire.

De manière générale, les inconvénients de l'édition des liens – et, dans une moindre mesure, du chargement – dynamique sont nombreux. On peut en citer quelques-uns:

- ce qui pourrait être fait une seule fois à la compilation est répété inutilement à chaque exécution pour produire toujours le même résultat, et, la plupart du temps, de manière bien moins efficace, ralentissant d'autant le chargement de l'application;

- les erreurs liées à des références non résolues ou des symboles introuvables sont détectées et signalées tardivement;

- le surcoût est proportionnel au nombre de relocalisations et de symboles à chercher [16], ainsi qu'à la taille du programme, ce qui incite le développeur à réduire le nombre de références externes, quitte à dégrader la qualité du code;

- au cours de l'exécution, chaque accès à un membre (objet ou fonction) d'une bibliothèque dynamique ajoute au moins un niveau d'indirection et consomme inutilement des cycles de processeur.

## 1.2.3.2 Simulation et débogage

Contrairement au monde de l'informatique où la plupart des expérimentations ont lieu sur du matériel réel, en électronique embarquée les prototypes sont souvent indisponibles voire inexistants. En effet, le temps et le coût de leur fabrication sont élevés et ne peuvent être assumés qu'à un stade avancé du cycle de développement. Le recours à des plateformes de simulation s'impose donc (cf. chapitre 4), ce qui conduit à des différences d'approche substantielles. Au chapitre des avantages, on peut noter la possibilité d'instrumenter le simulateur de façon à mener des mesures non intrusives, les facilités d'introspection permises par les modèles de plus haut niveau, ainsi que la parallélisation des expériences. En revanche, les inconvénients sont nombreux et prennent parfois le pas sur les bénéfices:

- temps de simulation d'autant plus longs que la modélisation est fine (jusqu'à un million de fois plus lent que le matériel), une conséquence non négligeable étant la nécessité de compiler le logiciel à un niveau d'optimisation élevé qui rend le débogage en assembleur obligatoire et laborieux;

- source de bogues supplémentaire quand le code n'est pas le même que celui de référence (utilisé pour la synthèse);

- mesures dépendantes de la précision du modèle retenu (cf. chapitre 4), donc parfois très approximatives voire impossibles.

En outre, le recours massif aux sorties formatées est à éviter – car très coûteux en temps et en mémoire, intrusif et nécessitant des recompilations fréquentes, elles-mêmes très longues du fait de la spécificité des générateurs de code et de la complexité des optimisations – quand il n'est pas tout simplement impossible. En effet, pour ce faire, une interface de sortie universelle est nécessaire, et bon nombre de systèmes embarqués n'en disposent pas.

#### 1.3 Plateforme cible

Cette section décrit de façon générale le type d'architecture visé, puis expose plus en détails les spécificités de la plateforme STHORM, cible des travaux de cette thèse, et enfin conclut en présentant des architectures similaires.

# 1.3.1 Description du modèle d'architecture

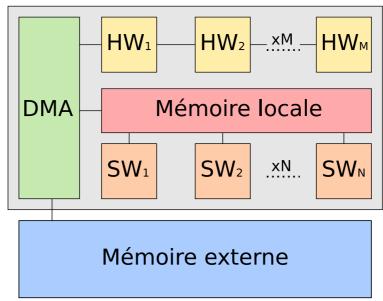

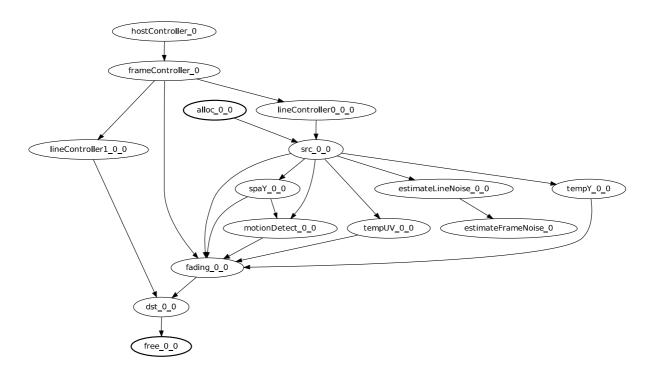

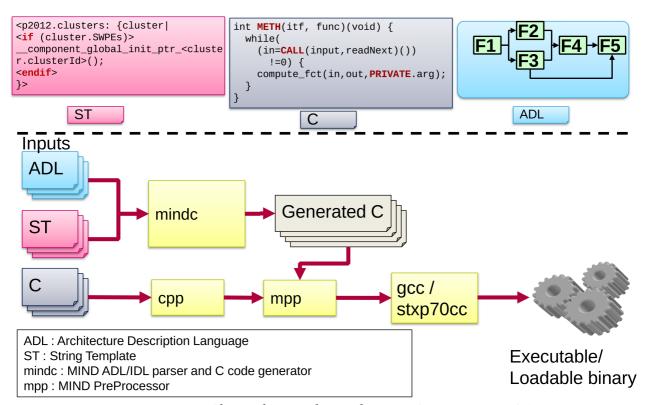

FIGURE 1.6 – Modèle de plateforme.

Le modèle d'architecture représenté par la figure 1.6 est une plateforme hétérogène comprenant à la fois des processeurs généralistes programmables (software processing elements, SWPE), peu performants mais offrant l'avantage de la flexibilité, et des accélérateurs spécialisés câblés (hardware processing elements, HWPE), très efficaces mais conçus pour une tâche unique. Les unités de calcul, quel que soit leur type, sont totalement interconnectées via un réseau sur puce. Elle dispose d'une mémoire hiérarchique à deux niveaux: une mémoire locale partagée en quantité limitée mais à accès rapide et une mémoire externe globale à capacité élevée mais forte latence. L'implémentation de la première se fait typiquement avec de la mémoire statique, offrant des performances similaires à celles d'un cache, et ayant de surcroît l'avantage d'une plus faible consommation énergétique que la mémoire dynamique généralement utilisée pour la seconde. Un contrôleur d'accès direct à la mémoire (DMA) est présent et permet de soulager les processeurs des tâches de communication entre les différents niveaux de la hiérarchie.

#### 1.3.2 Présentation de STHORM

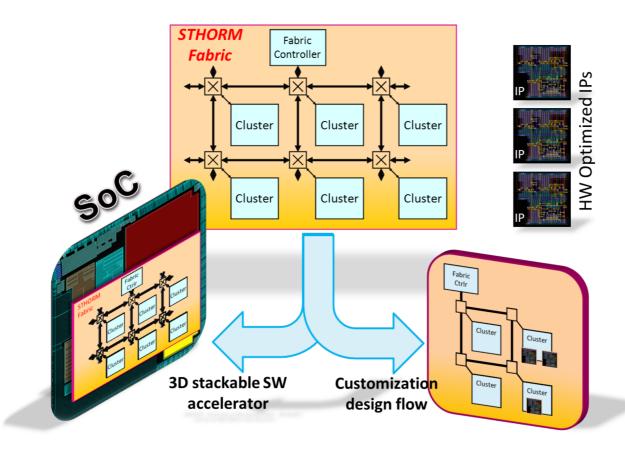

La plateforme multicœur hybride à basse consommation de STMicroelectronics (*ST Hybrid lOw poweR Manycore*, STHORM) a pour but d'accélérer des applications nécessitant un nombre d'opérations par seconde allant de quelques centaines de millions à plusieurs centaines de milliards, typiquement dans les domaines du traitement d'images, du décodage vidéo, de la réalité augmentée et de la compréhension de l'environnement.

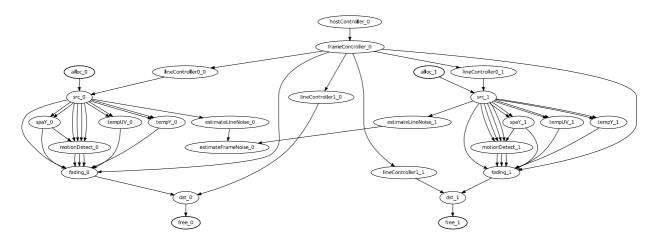

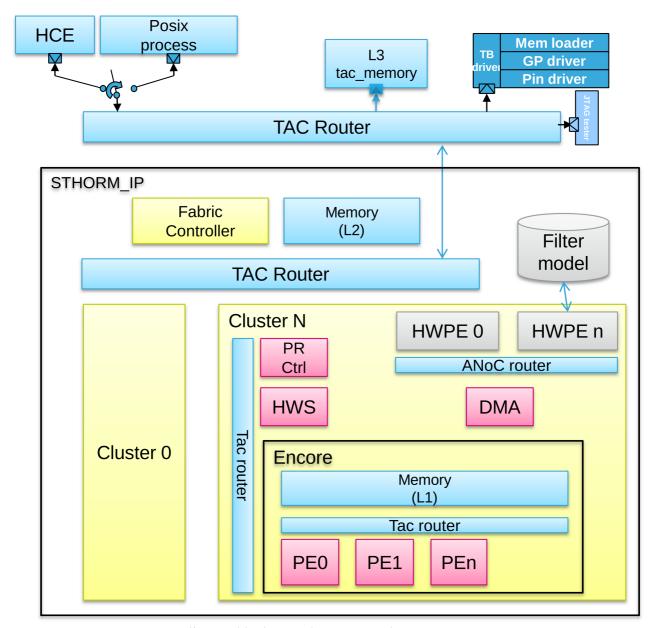

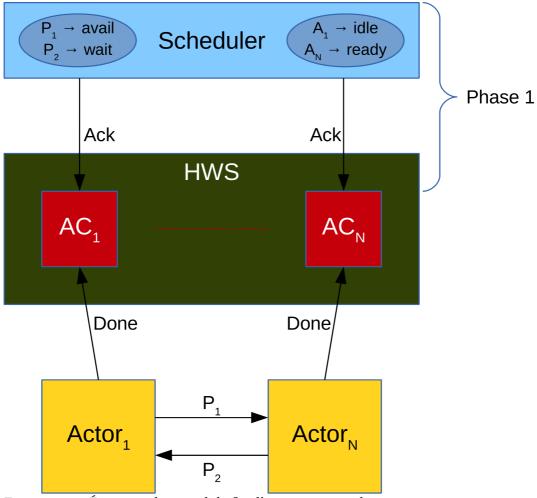

Comme l'illustre la figure 1.7, STHORM est constitué d'une fabrique divisée en groupes de calcul (clusters), d'un contrôleur (fabric controller) et d'un réseau sur puce asynchrone assurant l'interconnexion de l'ensemble. Les groupes de calcul comprennent jusqu'à dix-sept processeurs chacun – avec des flux d'instructions indépendants, et partageant une mémoire de premier niveau accessible en un cycle –, jusqu'à deux contrôleurs DMA et un support matériel pour la synchronisation et l'accélération des tâches d'ordonnancement. La plateforme supporte jusqu'à trente-deux groupes de calcul, mais, dans le cadre de cette thèse, seule une configuration mono-groupe a été envisagée.

FIGURE 1.7 – La fabrique de STHORM. Source: interne ST.

La fabrique dispose de sa propre mémoire de deuxième niveau, ainsi que d'une mémoire externe qu'elle partage avec les autres modules du SoC. Le plan mémoriel est plat, ce qui signifie que l'ensemble des adresses, y compris celles des registres de périphériques, sont accessibles par tous les processeurs. Cependant, dans cette architecture mémorielle non uniforme, l'accès aux niveaux éloignés de la hiérarchie sont plus coûteux. Pour cette raison, les DMA sont là pour accélérer les transferts au sein de la fabrique et avec le reste du SoC.

Le contrôleur de la fabrique assure l'interface entre celle-ci et le SoC en communiquant avec son processeur hôte. Son rôle est de contrôler la procédure d'amorçage, ainsi que le placement et le chargement des applications.

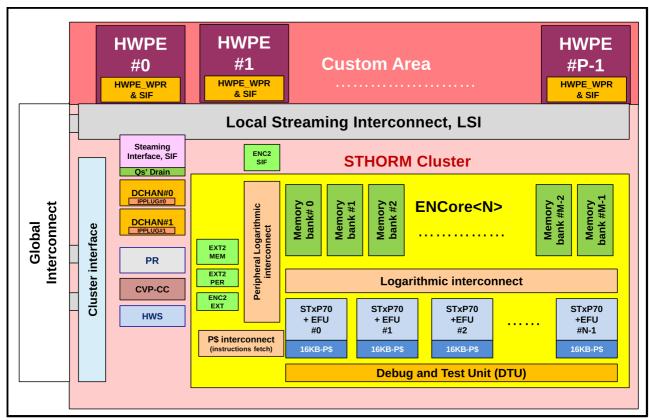

La figure 1.8 illustre plus en détails la composition d'un groupe de calcul. Le sous-ensemble appelé ENCore<N> (où N est le nombre de SWPE) comprend des cœurs STxP70 en guise de processeurs programmables couplés à des mémoires caches d'instructions – mais pas de données – et des extensions pour les divisions et les évènements. Le reste englobe les HWPE et leur bus dédié, ainsi qu'un certain nombre de périphériques dont deux canaux DMA (*DMA channels*, DCHAN) et un module de synchronisation matérielle (*hardware synchronizer*, HWS).

FIGURE 1.8 – Un groupe de calcul de STHORM. Source: interne ST.

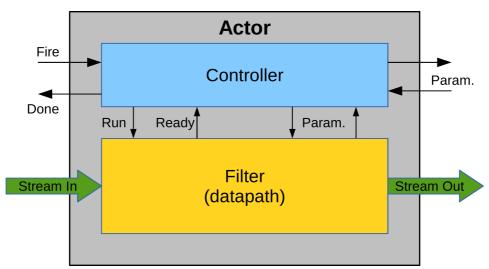

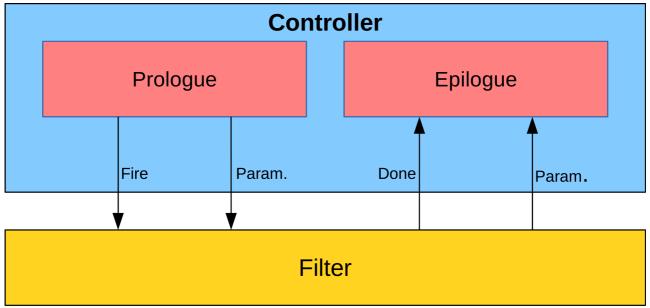

## 1.3.2.1 Accélérateurs matériels et flux de données

STHORM a été conçu dans l'idée de pouvoir exécuter efficacement des applications à flux de données, c'est pourquoi les HWPE évoluent dans un espace distinct des SWPE où ce ne sont pas les instructions qui s'écoulent – comme dans le modèle de Von Neumann – mais les données. Pour cette raison, les HWPE disposent de leur propre bus d'interconnexion pour transporter les données sous forme de flux.

Dans le détail, un HWPE est constitué d'une enveloppe dont la structure est commune à toutes les instances, et d'une partie conçue par l'utilisateur qui dépend de la fonction à réaliser et contient les filtres à proprement parler. L'enveloppe comprend essentiellement les interfaces avec le bus, ainsi qu'un contrôleur. Ce dernier orchestre l'exécution des filtres *via* une machine à états et reçoit sa configuration de la part du logiciel par le truchement de registres mappés en mémoire. Celle-ci se fait en deux étapes:

- 1. sélection d'un jeu de filtres à exécuter;

- 2. lancement simultané de tous les filtres sélectionnés.

Quand ceux-ci ont terminé leur exécution, le contrôleur écrit une valeur prédéfinie à une adresse mentionnée dans les registres *ad hoc*. Il est par exemple possible, par ce biais, de signaler au logiciel la fin d'exécution en demandant au synchroniseur matériel d'envoyer un évènement au SWPE initiateur.

#### 1.3.3 Autres architectures similaires

Cette sous-section présente une sélection de quatre architectures présentant des caractéristiques comparables à STHORM. Pour une liste plus complète d'architectures hybrides de ce type, se reporter aux travaux de Yazdanpanah et coll. [17].

### 1.3.3.1 Mega-Leon

L'université de Bologne, qui a pris part à la conception de STHORM, a également développé pour ses propres recherches un groupe de calcul multicœur avec mémoire partagée et accélérateurs matériels étroitement couplés [18] très similaire. L'hétérogénéité repose ici sur l'association de processeurs généralistes SPARC-V8 – au lieu des STxP70 – et d'unités de calcul spécialisées directement connectées à la mémoire partagée. Le choix a ainsi été fait de privilégier un accès facilité à la mémoire de manière à pouvoir échanger efficacement entre SWPE et HWPE, au détriment d'une transmission optimisée entre accélérateurs. Pour assister la conception des unités de calcul matérielles, les auteurs proposent une méthode basée sur la synthèse de haut niveau.

#### 1.3.3.2 FISC

Chen et coll. [19] proposent d'introduire dans le jeu d'instructions de processeurs généralistes des macro-opérations qui remplaceraient des fonctions par des appels à des accélérateurs (ensembles reconfigurables de modules câblés). La reconfiguration puis l'appel des HWPE ont lieu dans un étage dédié du pipeline des SWPE, après le décodage. Les HWPE sont étroitement couplés aux SWPE au sens où ils ont accès à la fois à la mémoire et aux registres. En matière de programmabilité, le matériel sous-jacent est caché au développeur par l'introduction d'une phase de compilation supplémentaire. On notera l'absence de support pour les flux de données.

#### 1.3.3.3 Tartan

Mishra et coll. [20] présentent une architecture hybride qui comprend un SWPE et une fabrique hiérarchique reconfigurable sans horloge autorisant une exécution asynchrone dirigée par les données. L'application de l'utilisateur est scindée en deux parties: l'une s'exécutant sur le SWPE, l'autre sur la fabrique. L'espace mémoriel est partagé entre les deux unités de calcul. Le jeu d'instructions du SWPE doit être étendu avec des instructions de contrôle spécifiques. Le partitionnement de l'application, la génération du code pour le SWPE et la fabrique, ainsi que la synthèse de cette dernière sont effectués par le compilateur, de manière transparente pour l'utilisateur.

#### 1.3.3.4 DySER

Cette dernière architecture [21] est constituée d'un tableau hétérogène de HWPE connectés par un réseau de commutateurs qui s'intègre dans le pipeline d'un SWPE. Comme STHORM, les communications se font par flux de données avec un protocole de transport à base de crédits. Ici encore, une extension du jeu d'instructions du SWPE est nécessaire pour contrôler et reconfigurer DySER. De même, le partitionnement de l'application et l'insertion des instructions spéciales sont faits par le compilateur.

#### 1.4 Problème abordé

Suite aux observations formulées dans les sections précédentes concernant les caractéristiques des applications visées ainsi que celles des architectures ciblées, la problématique soulevée par cette

thèse peut s'exprimer de la manière suivante: comment exécuter efficacement une application à flux de données très dynamique sur une plateforme embarquée hybride ?

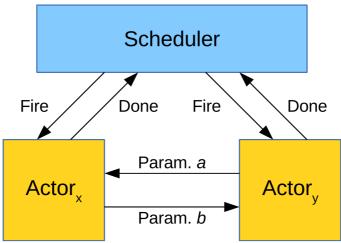

Cette question s'articule principalement autour de deux axes: le modèle d'exécution et l'ordonnancement. Dans le premier, il s'agit de faire correspondre un modèle adapté à une description à haut niveau d'abstraction des applications visées, à un modèle de programmation de bas niveau. Les modèles existants sont soit de haut niveau, ne prenant pas en compte les spécificités des architectures modernes - en particulier l'hybridité -, soit de bas niveau, ciblant une classe restreinte d'architectures voire une plateforme unique. Le modèle d'exécution présenté au chapitre 2 propose une solution intermédiaire située à mi-chemin entre ces deux pôles. Dans le second axe, au problème classique d'assignation et d'ordre en vue de minimiser la durée totale d'exécution, s'ajoute la contrainte liée à la capacité limitée de la mémoire. De plus, une grande part des applications pour l'embarqué étant caractérisées par une régularité permettant un ordonnancement statique peu coûteux, les solutions utilisées usuellement se prêtent moins à l'exécution efficace de programmes très dynamiques. Le chapitre 3 propose une solution fondée sur les heuristiques d'ordonnancement de liste et évalue les bénéfices potentiels d'un dynamisme accru; le chapitre 5 propose une structure d'ordonnanceur compatible avec le modèle d'exécution du chapitre 2 et capable de supporter les formes les plus avancées de variabilité et d'imprédictibilité. En outre, deux contraintes supplémentaires doivent être introduites: la nécessité pour le logiciel système de rester aussi léger que possible, à la fois en matière de temps et d'espace, et la prise en compte de l'exécution en temps réel.

D'après ce qui précède, le problème abordé peut alors se formuler comme suit:

Étant donné: une application à flux de données très dynamique décrite dans un modèle à haut niveau d'abstraction, une plateforme hybride embarquée et un ensemble de contraintes de temps; trouver une exécution garantissant la sémantique de l'application, limitant l'empreinte mémorielle et respectant les contraintes temporelles.

## CHAPITRE 2. Modèles à flot de données

Il a été mentionné au chapitre 1 qu'un modèle de haut niveau était nécessaire pour décrire les applications à flux de données afin d'être en mesure de cibler des unités de calcul aussi bien matérielles que logiciels de façon efficace. Dans cette optique, le présent chapitre décrit les modèles de type flot de données (*dataflow*) et montre qu'ils représentent de bons candidats à cet égard. La première section expose les fondements théoriques puis énumère les solutions précédemment proposées, en particulier celle utilisée dans le cadre de STHORM; la seconde présente la contribution de ce chapitre: un modèle d'exécution répondant à la problématique de la thèse; enfin, la dernière conclut sur une réflexion concernant le risque d'interblocage.

### 2.1 État de l'art

Historiquement, toutes les recherches sur les modèles à flot de données font suite aux travaux fondateurs de Dennis [22] qui remontent à 1974. De nombreuses variantes – appelées modèles de calcul – ont depuis été proposées (voir les sous-sections suivantes pour un tour d'horizon de celles-ci) mais elles partagent toutes les mêmes principes de base suivants.

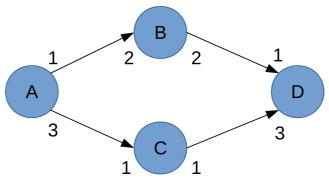

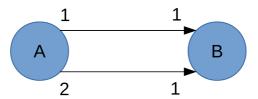

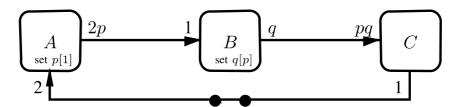

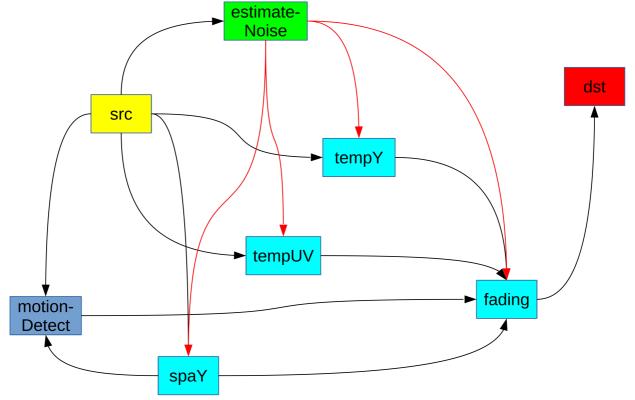

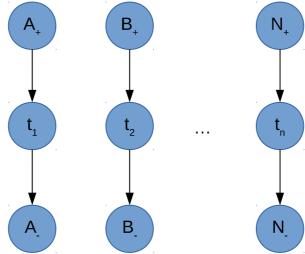

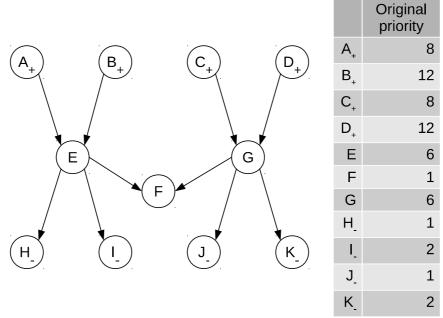

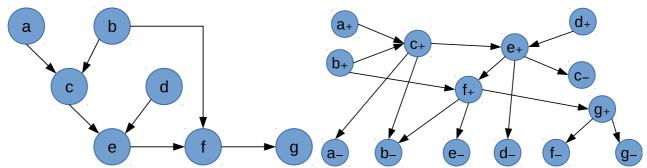

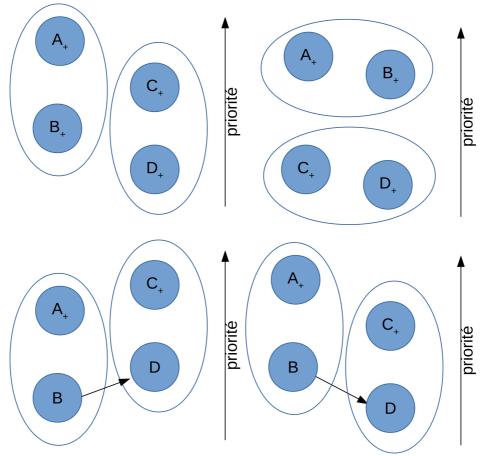

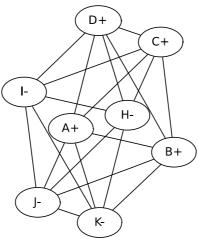

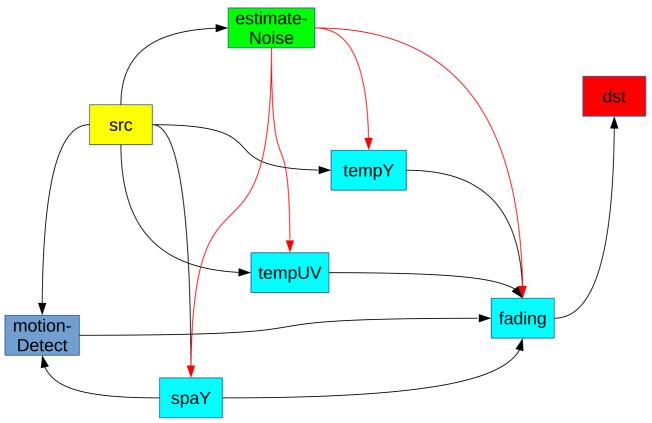

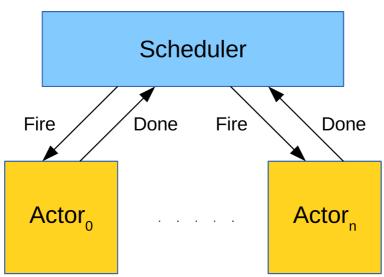

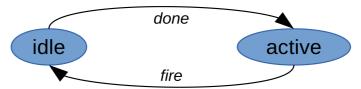

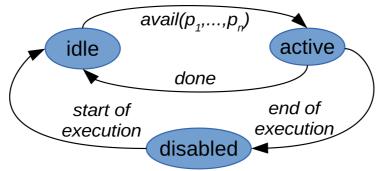

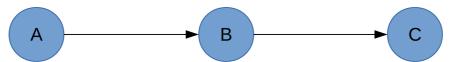

Les modèles à flot de données proposent de décrire chaque programme sous forme d'un graphe orienté dont les nœuds sont des entités de calcul fonctionnelles appelées *acteurs*, et les arcs sont des canaux de communication de taille conceptuellement infinie constituant la seule source de dépendance entre acteurs. Les données transitent d'un acteur à l'autre exclusivement par le biais des arcs, sous forme d'unités atomiques appelées *jetons* (*tokens*). La figure 2.1 donne un exemple simple d'un tel graphe où A, B, C et D sont quatre acteurs qui échangent des jetons de A vers D par l'intermédiaire de B et C.

FIGURE 2.1 – Exemple de graphe à flot de données comprenant quatre acteurs. Les chiffres aux extrémités des flèches indiquent les débits des ports.

L'exécution d'un acteur, appelée *invocation* (*firing*), correspond à une séquence ordonnée et indivisible de trois étapes:

- 1. consommation d'un certain nombre de jetons sur les arcs entrants;

- 2. application de la fonction de calcul sur les jetons consommés;

- 3. production d'un certain nombre de jetons sur les arcs sortants correspondant aux résultats de la fonction de calcul.

Pour chaque acteur, un ensemble de règles d'activation (*firing rules*) définies par l'application déterminent sous quelles conditions celui-ci peut être invoqué: il s'agit, dans le cas général, du nombre et de la nature des jetons devant être présents sur les arcs d'entrée. Les interfaces des acteurs connectées à des arcs, et permettant donc le transfert de jetons, sont appelées *ports*. Le *débit (rate)* d'un port correspond au nombre de jetons transférés lors d'une invocation. Sur la figure 2.1, l'acteur A dispose de deux ports de sortie produisant respectivement 1 et 3 jetons, B dispose d'un port d'entrée et d'un port de sortie consommant tous deux 2 jetons, etc. Dans le cadre de cet exemple, si l'on suppose que les règles d'activation correspondent uniquement aux jetons consommés au niveau des ports d'entrée, alors l'acteur A est toujours activé, B nécessite 2 jetons, C en requiert 1, et D respectivement 1 et 3 sur chacun de ses ports.

Dans les modèles à flot de données, les lectures – c'est-à-dire l'opération consistant à tenter de consommer des jetons sur un arc donné – ne bloquent jamais grâce à l'existence des règles d'activation qui garantissent qu'une lecture n'aura lieu qu'à la condition que les jetons nécessaires soient présents (la section 2.1.2 présente un modèle analogue où les lectures sont bloquantes). De même, les canaux de communication étant supposés infinis, donc capables de stocker une quantité illimitée de jetons, les écritures ne peuvent pas non plus bloquer. On notera néanmoins que, en raison des contraintes d'implémentation, les écritures sont bloquantes en pratique: les canaux de communication doivent nécessairement avoir une capacité limitée dans un environnement où la mémoire est finie.

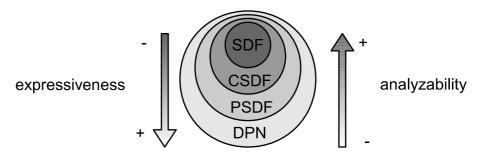

En outre, les nombreuses variantes des modèles à flot de données présentées dans les sous-sections suivantes disposent de certaines propriétés théoriques apportant des garanties spécifiques, parmi lesquelles:

- vivacité: absence d'interblocage intrinsèque au graphe (par opposition aux impasses artificielles introduites par le modèle d'exécution ou l'ordonnanceur);

- bornitude: possibilité pour un graphe donné d'être exécuté en mémoire finie;

- cohérence: le nombre de jetons produits sur chaque arc tend vers le nombre de jetons consommés [23]

- terminaison: une exécution complète comprend un nombre fini d'opérations [24].

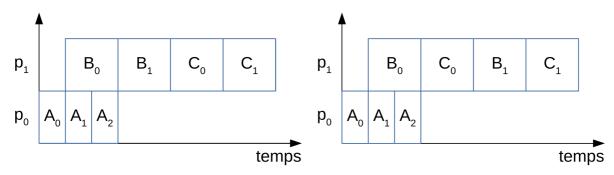

Les modèles de calcul dont les propriétés précédentes sont décidables sont généralement ordonnançables de manière *statique*, c'est-à-dire qu'il est possible de générer un ordonnancement correct à la compilation. Les modèles disposant d'une plus grande expressivité sont quant à eux ordonnançables de façon *quasi-statique* – c'est-à-dire qu'un ordonnancement peut être pré-calculé

2.1 État de l'art

à la compilation mais doit être ajusté à l'exécution – voire dynamique – tout le travail de l'ordonnanceur doit être mené à l'exécution. Dans l'exemple de la figure 2.1, il est possible de construire l'ordonnancement statique suivant: 2A 1B 6C 2D. Cette séquence peut être répétée indéfiniment avec une capacité de 2 jetons pour les files du haut et 6 jetons pour les files du bas, ce qui démontre à la fois la vivacité, la cohérence et la bornitude. La figure 2.2, en revanche, présente un exemple de graphe résultant nécessairement en une accumulation illimitée de jetons dans la file du bas: il n'est donc ni cohérent ni borné.

FIGURE 2.2 – Exemple de graphe non borné.

Les avantages de cette classe de modèles sont nombreux. Du point de vue de la description de l'application, la représentation graphique lui confère un aspect visuel intuitif. Le haut niveau d'abstraction rend la modélisation suffisamment générique pour pouvoir s'adapter à des cibles variées – il est par exemple possible de générer à partir d'un même graphe à flot de données du code dans différents langages aussi bien logiciels (p. ex. C ou Java) que matériels (p. ex. VHDL ou Verilog) ; à cela s'ajoute l'expression naturelle de la concurrence et l'exposition du parallélisme potentiel. Le découpage en acteurs facilite le partitionnement; de plus, il permet une programmation modulaire et incite à la réutilisabilité des composants, critère de choix pour les décodeurs vidéo (cf. chapitre 1). Du point de vue de l'implémentation, l'intérêt de décomposer le calcul en quantums indivisibles réside dans l'opportunité de s'affranchir de coûteux changements de contexte. Et le placement des acteurs sur des architectures parallèles telles que celles visées par cette thèse s'en trouve facilité.