# Modelling and characterization of physically unclonable functions

Zouha Cherif

#### ▶ To cite this version:

Zouha Cherif. Modelling and characterization of physically unclonable functions. Micro and nanotechnologies/Microelectronics. Université Jean Monnet - Saint-Etienne, 2014. English. NNT: 2014STET4005. tel-01162286

### HAL Id: tel-01162286 https://theses.hal.science/tel-01162286

Submitted on 10 Jun 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE

#### pour obtenir le grade de docteur délivré par :

Présentée et soutenue publiquement par

#### **Zouha CHERIF**

le 08 avril 2014

# Modélisation et Caractérisation des Fonctions non Clonables Physiquement

Discipline: Microélectronique

Équipes : Systèmes Embarqués Sécurisés - Laboratoire Hubert Curien

Systèmes Électronique Numériques - TELECOM ParisTech

Directeurs de thèse : Lilian Bossuet, Maître de Conférences HDR, Université Jean Monnet

Jean-Luc Danger, Directeur d'études, TELECOM ParisTech

#### Jury

| M. lan O'CONNOR, Professeur, École Centrale Lyon, FRANCE                    | Président   |

|-----------------------------------------------------------------------------|-------------|

| Mme.Ingrid VERBAUWHEDE, Professeur, K. U. Leuven, BELGIQUE                  | Rapporteur  |

| M. Bruno ROUZEYRE, Professeur, Université Montpellier 2, FRANCE             | Rapporteur  |

| M. Viktor FISCHER, Professeur, Université Jean Monnet saint Etienne, FRANCE | Examinateur |

| M. Gilles MACARIO-RAT, Docteur, Ingénieur de recherche, Orange Labs, FRANCE | Examinateur |

## Doctor of Philosophy in Microelectronics

at the

# **Modelling and Characterization of Physically Unclonable Functions**

#### **Zouha Cherif**

April 8, 2014

Research Groups: Secure Embedded Systems - Hubert Curien Laboratory

Digital Electronic systems - TELECOM ParisTech

PhD Supervisors: Lilian Bossuet, Associated Professor, University of Lyon, Saint-Etienne

Jean-Luc Danger, Professor, TELECOM ParisTech

A la mémoire de mon père,

A ma mère, mes frères et ma sœur,

A mon mari et mon fils, \*\*\*

$A\ toute\ ma\ famille...$

### Résumé

Les fonctions non clonables physiquement, appelées PUF (Physically Unclonable Functions), représentent une technologie innovante qui permet de résoudre certains problèmes de sécurité et d'identification. Comme pour les empreintes humaines, les PUF permettent de différencier des circuits électroniques car chaque exemplaire produit une signature unique. Ces fonctions peuvent être utilisées pour des applications telles que l'authentification et la génération de clés cryptographiques. La propriété principale que l'on cherche à obtenir avec les PUF est la génération d'une réponse unique qui varie de façon aléatoire d'un circuit à un autre, sans la possibilité de la prédire. Une autre propriété de ces PUF est de toujours reproduire, quelque soit la variation de l'environnement de test, la même réponse à un même défi d'entrée. En plus, une fonction PUF doit être sécurisée contre les attaques qui permettraient de révéler sa réponse. Dans cette thèse, nous nous intéressons aux PUF en silicium profitant des variations inhérentes aux technologies de fabrication des circuits intégrés CMOS. Nous présentons les principales architectures de PUF, leurs propriétés, et les techniques mises en œuvre pour les utiliser dans des applications de sécurité.

Nous présentons d'abord deux nouvelles structures de PUF. La première structure appelée "Loop PUF" est basée sur des chaînes d'éléments à retard contrôlés. Elle consiste à comparer les délais de chaînes à retard identiques qui sont mises en série. Les points forts de cette structure sont la facilité de sa mise en œuvre sur les deux plates-formes ASIC et FPGA, la grande flexibilité pour l'authentification des circuits intégrés ainsi que la génération de clés de chiffrement. La deuxième structure proposée "TERO PUF" est basée sur le principe de cellules temporairement oscillantes. Elle exploite la métastabilité oscillatoire d'éléments couplés en croix, et peut aussi être utilisée pour un générateur vrai d'aléas (TRNG). Plus précisément, la réponse du PUF profite de la métastabilité oscillatoire introduite par une bascule SR lorsque les deux entrées S et R sont connectées au même signal d'entrée. Les résultats expérimentaux montrent le niveau de performances élevé des deux structures de PUF proposées.

Ensuite, afin de comparer équitablement la qualité des différentes PUF à retard, nous proposons une méthode de caractérisation spécifique. Elle est basée sur des mesures statistiques des éléments à retard. Le principal avantage de cette méthode vient de sa capacité à permettre au concepteur d'être sûr que la fonction

PUF aura les performances attendues avant sa mise en œuvre et sa fabrication.

Enfin, en se basant sur les propriétés de non clonabilité et de l'imprévisibilité des PUF, nous présentons de nouvelles techniques d'authentification et de génération de clés de chiffrement en utilisant la "loop PUF" proposée. Les résultats théoriques et expérimentaux montrent l'efficacité des techniques introduites en termes de complexité et de fiabilité.

### Abstract

Physically Unclonable Functions, or PUFs, are innovative technologies devoted to solve some security and identification issues. Similarly to a human fingerprint, PUFs allows to identify uniquely electronic devices as they produce an instance-specific signature. Applications as authentication or key generation can take advantage of this embedded function. The main property that we try to obtain from a PUF is the generation of a unique response that varies randomly from one physical device to another without allowing its prediction. Another important property of these PUF is to always reproduce the same response for the same input challenge even in a changing environment. Moreover, the PUF system should be secure against attacks that could reveal its response. In this thesis, we are interested in silicon PUF which take advantage of inherent process variations during the manufacturing of CMOS integrated circuits. We present several PUF constructions, discuss their properties and the implementation techniques to use them in security applications.

We first present two novel PUF structures. The first one, called "Loop PUF" is a delay based PUF which relies on the comparison of delay measurements of identical serial delay chains. The major contribution brought by the use of this structure is its implementation simplicity on both ASIC and FPGA platforms, and its flexibility as it can be used for reliable authentication or key generation. The second proposed structure is a ring-oscillator based PUF cells "TERO PUF". It exploits the oscillatory metastability of cross-coupled elements, and can also be used as True Random Number Generator (TRNG). More precisely, the PUF response takes advantage from the introduced oscillatory metastability of an SR flip-flop when the S and R inputs are connected to the same input signal. Experimental results show the high performance of these two proposed PUF structures.

Second, in order to fairly compare the quality of different delay based PUFs, we propose a specific characterization method. It is based on statistical measurements on basic delay elements. The main benefit of this method is that it allows the designer to be sure that the PUF will meet the expected performances before its implementation and fabrication.

Finally, Based on the unclonability and unpredictability properties of the PUFs, we present new techniques to perform "loop PUF" authentication and

cryptographic key generation. Theoretical and experimental results show the efficiency of the introduced techniques in terms of complexity and reliability.

### Remerciement

Ce travail est le fruit de nombreuses rencontres des personnes que je souhaite remercier ici pour toute l'aide, le soutien, les conseils qu'elles m'ont apportés ou tout simplement pour leur bonne humeur et leur joie de vivre qui ont fait de ces trois années de thèse, une aventure exceptionnelle.

J'adresse tout d'abord mes vifs remerciements à Lilian Bossuet et Jean-Luc Danger mes directeurs de thèse. Merci à Lilian, sa disponibilité, ses qualités humaines et sa bonté resteront pour moi un exemple à suivre. Que ce travail soit le témoignage de mon respect. Merci Jean-Luc de m'avoir accueilli dans son groupe de recherche. Je le remercie d'avoir dirigé cette thèse et de m'avoir soutenu durant ces trois années. Je le remercie enfin autant pour ses qualités pédagogiques et son implication dans ce travail que pour ses qualités humaines, qui ont rendu chaque moment que j'ai passé au laboratoire plus sympathique.

J'espère sincèrement que la collaboration que nous avons eue tous les trois se poursuivra dans le futur.

Je suis reconnaissante à **M. Ian O'connor** pour l'honneur qu'il m'a fait de présider le jury de ce travail.

J'ai eu la joie et la fierté de bénéficier de la participation de **Mme Ingrid Verbauwhede**. Cela a été un grand honneur qu'elle ait accepté de juger mon travail, j'ai admiré sa gentillesse et sa chaleur. Que cette réalisation soit le témoin de ma profonde reconnaissance.

La présence de M. Bruno Rouzeyre m'a été précieuse, il m'a impressionné par la précision de ses remarques et de son accueil chaleureux. Je lui exprime mes remerciements les plus sincères en témoignage de ma considération.

Mes remerciements vont aussi à M. Gilles Macariot-rat et M. Viktor Fisher, de m'avoir honorée d'assister à ma soutenance de thèse et de juger mon travail.

Au cours de toutes ces années j'ai partagé des moments agréables avec des amis exceptionnels: Shivam Bhasin, Houssem Maghrebi, Florent Lozac'h, Youssef Souissi, Molka Ben Romdhane, Tarik Graba, Annelie Husser, Mariem Slimani, Emna Amouri, Nicolas Debande, Jeremie Brunel, Arwa Ben Dhia, Asma Mejri, Salma Belhaj, Laurent Sauvage, Thuy Ngo, Tania, Zakaria Najm, Nidhal Selmane, Pablo, Lubos, Patrick Haddad, Nathalie Bochard, Sebastien Thomas, Taufik Chouta, Olivier Meynard, Aziz Elaabid, Amel Grira,...

Cela était une chance d'avoir une telle bonne compagnie. Ils ont toujours été présents pour partager ensemble le meilleur et le pire.

Ces remerciements ne seraient complets sans mentionner les personnes que j'aime le plus au monde, mon père Mohamed ali, que son Âme repose en paix, tu resteras à jamais gravé dans mon cœur; ma maman chérie Fethia, je t'admire pour ton soutien continu et ton courage; mon adorable fils Aziz et mon mari Oualid, je vous adore; ma bien aimable petite sœur Safa, mes deux frères Wassim et Ahmed et mes adorables neveux Youssef et Brahim, je vous aime; sans oublier, Mima, Fafa, Mo, Dorra, tata Afifa, am Nourdine, Sabrine, Olfa...

## Table des matières

| $\mathbf{R}$ | ésum   | ıé                     |                                                                                                                                    | iii                    |

|--------------|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| A            | bstra  | $\operatorname{ct}$    |                                                                                                                                    | $\mathbf{v}$           |

| R            | emer   | cieme                  | nt                                                                                                                                 | vii                    |

| Li           | ist of | Figur                  | es                                                                                                                                 | xi                     |

| Li           | ist of | Table                  | $\mathbf{s}$                                                                                                                       | $\mathbf{x}\mathbf{v}$ |

| G            | lossa  | $\mathbf{r}\mathbf{y}$ |                                                                                                                                    | xix                    |

| G            | enera  | al Intr                | oduction                                                                                                                           | 1                      |

| 1            | Phy    | sically                | Unclonable Functions : Basics                                                                                                      | 5                      |

|              | 1.1    | PUFs                   | : Concept, Properties and Applications $\ \ldots \ \ldots \ \ldots$                                                                | 6                      |

|              |        | 1.1.1                  | Concept of PUFs                                                                                                                    | 6                      |

|              |        | 1.1.2                  | Properties and Parameters of PUFs                                                                                                  | 6                      |

|              |        | 1.1.3                  | PUF Applications                                                                                                                   | 8                      |

|              | 1.2    | PUFs                   | $Classification \dots \dots$ | 11                     |

|              |        | 1.2.1                  | Non-electronic and Electronic PUFs                                                                                                 | 12                     |

|              |        | 1.2.2                  | Non-intrinsic and Intrinsic PUFs                                                                                                   | 13                     |

|              |        | 1.2.3                  | Strong and Weak PUFs                                                                                                               | 14                     |

|              | 1.3    | Attac                  | ks on Silicon PUFs                                                                                                                 | 15                     |

|              |        | 1.3.1                  | Modeling Attack                                                                                                                    | 15                     |

|              |        | 1.3.2                  | Side-Channel Analysis                                                                                                              | 15                     |

|              | 1.4    | Silicon                | n PUF Structures                                                                                                                   | 16                     |

|              |        | 1.4.1                  | Delay based PUFs                                                                                                                   | 16                     |

|              |        | 1.4.2                  | Memory based PUFs                                                                                                                  | 25                     |

|              |        | 1.4.3                  | Discussions                                                                                                                        | 29                     |

|              | 1.5    | PUFs                   | Evaluation Methods                                                                                                                 | 32                     |

|              |        | 1.5.1                  | Hamming Computation Based Metrics (Maiti et al. [MCMS]                                                                             | 10]) 33                |

|              |        | 1.5.2                  | Statistical Based Metrics (Hori et al. [HYKS10])                                                                                   | 34                     |

|              | 1.6    | Concl                  | usion                                                                                                                              | 35                     |

| 2 | Loo | pp PUF                                                  | 37         |

|---|-----|---------------------------------------------------------|------------|

|   | 2.1 | Loop PUF                                                | 38         |

|   |     | 2.1.1 Data path part                                    | 38         |

|   |     | 2.1.2 Control part                                      | 39         |

|   | 2.2 | Delay PUFs on CMOS 65nm technology : ASIC and FPGA      | 44         |

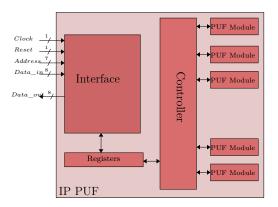

|   |     | 2.2.1 PUF IP Specification                              | 44         |

|   |     | 2.2.2 Design Under Tests : The PUF Module               | 46         |

|   |     | 2.2.3 Platforms Under Tests                             | 48         |

|   |     | 2.2.4 Experimental Results                              | 52         |

|   | 2.3 | Conclusions                                             | 57         |

| 3 | TE  | RO PUF                                                  | <b>5</b> 9 |

|   | 3.1 | TERO PUF                                                | 60         |

|   |     | 3.1.1 TERO loop Architecture and Behavior               | 60         |

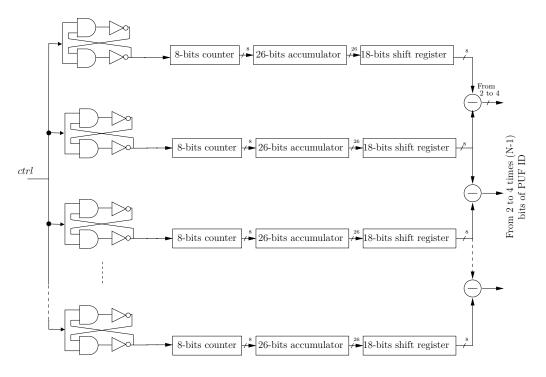

|   |     | 3.1.2 Extraction of the Process Variation Entropy       | 61         |

|   |     | 3.1.3 TERO PUF structure                                | 62         |

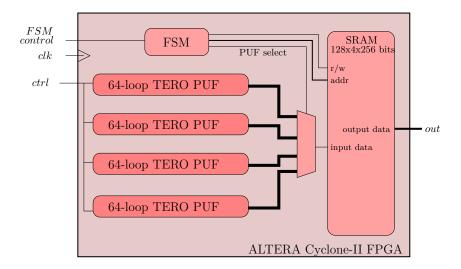

|   | 3.2 | TERO PUF on ALTERA FPGAs : Implementation and Evalua-   | -          |

|   |     | tion Results                                            | 63         |

|   |     | 3.2.1 TERO PUF IP : Design Requirements                 | 64         |

|   |     | 3.2.2 FPGA Implementation Details                       | 65         |

|   |     | 3.2.3 Metrics Definition and Experimental results       | 68         |

|   | 3.3 | Conclusion                                              | 74         |

| 4 | Del | ay PUF Performance Evaluation Method                    | 77         |

| - | 4.1 | Motivation                                              | 78         |

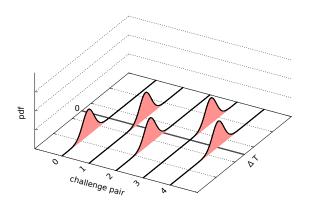

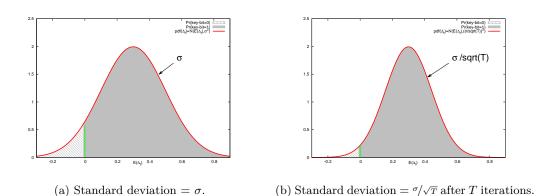

|   | 4.2 | Background on Gaussian Probability Density Function     | 78         |

|   | 4.3 | Proposed Metrics for Delay Based PUFs                   | 79         |

|   |     | 4.3.1 Notations                                         | 80         |

|   |     | 4.3.2 Metrics Computation                               | 80         |

|   | 4.4 | Experiments and Results                                 | 86         |

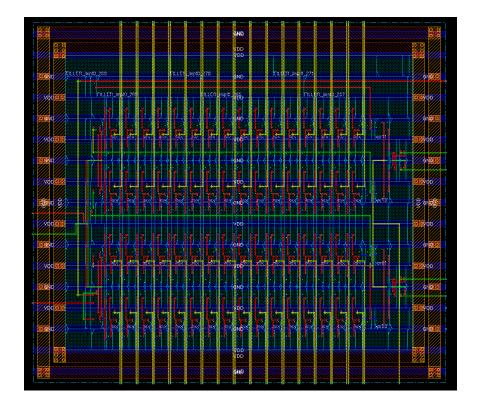

|   |     | 4.4.1 Arbiter PUF Design on ALTERA FPGAs                | 87         |

|   |     | 4.4.2 Loop PUF Design on ALTERA FPGAs                   | 89         |

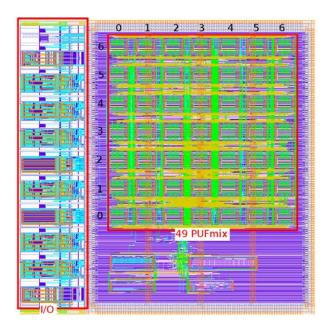

|   |     | 4.4.3 $PUF_{mix}$ Design on ASIC                        | 91         |

|   | 4.5 | Conclusion                                              | 92         |

| 5 | Loo | op PUF: Device Authentication and Cryptographic Key Ge- |            |

| 0 |     | ation                                                   | 95         |

|   | 5.1 | Motivation                                              | 96         |

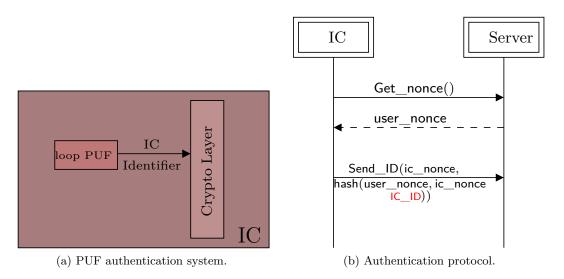

|   | 5.2 | Loop PUF for Authentication                             | 97         |

|   | J.∠ | 5.2.1 PUF-based IC Analysis                             | 97         |

|   |     | 5.2.1 FOr-based IC Analysis                             | 97         |

|   |     | 5.2.2 The Authentication Procedure                      | 98         |

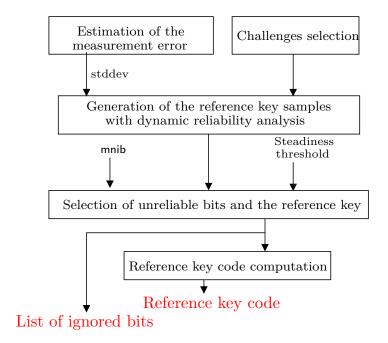

|   | 5.3 | _                                                       | 90<br>102  |

|              |       | 5.3.1 Principles                                                | 102         |

|--------------|-------|-----------------------------------------------------------------|-------------|

|              |       | 5.3.2 Reliability Improvement Techniques                        | 103         |

|              |       | 5.3.3 Profiling                                                 | 105         |

|              |       | 5.3.4 User Key Generation                                       | 112         |

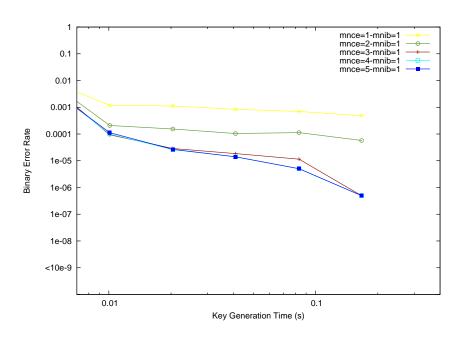

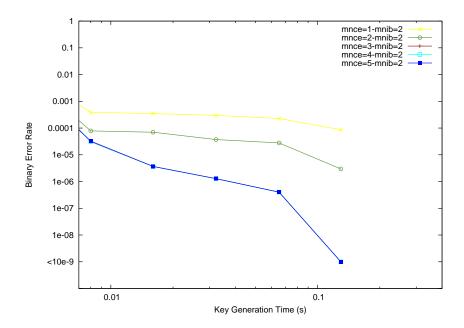

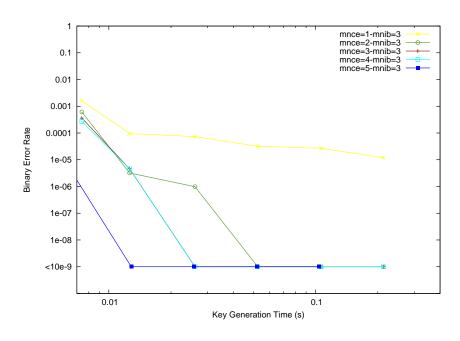

|              |       | 5.3.5 Experimental Results and Discussions                      | 116         |

|              | 5.4   | Conclusion                                                      | 122         |

| 6            | Con   | nclusion and Perspectives                                       | 127         |

|              | 6.1   | Conclusions                                                     | 128         |

|              | 6.2   | Future Research                                                 | 129         |

| Li           | st of | Publications                                                    | <b>13</b> 0 |

| Bi           | bliog | graphy                                                          | 133         |

| $\mathbf{A}$ | Intr  | roduction                                                       | 139         |

|              | A.1   | Contexte et Motivations                                         | 140         |

|              | A.2   | Plan de la Thèse et Contributions                               | 141         |

| В            | Ré    | sumé des Chapitres de la Thèse                                  | 143         |

|              | B.1   | Les Fonctions Non Clonables Physiquement : Concept de Base .    | 144         |

|              | B.2   | Loop PUF                                                        | 144         |

|              | B.3   | TERO PUF                                                        | 145         |

|              | B.4   | Méthode d'Évaluation des Performances des PUF à Délais          | 146         |

|              | B.5   | Loop PUF : Authentification des Circuits Intégrés et Génération |             |

|              |       | de Clés Cryptographiques                                        | 147         |

| $\mathbf{C}$ | Con   | nclusions et Perspectives                                       | 149         |

|              | C.1   | Conclusions                                                     | 150         |

|              | C.2   | Recherches Futures                                              | 151         |

# Table des figures

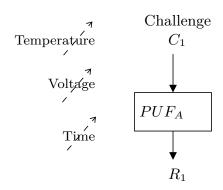

| 1.1  | Steadiness evaluation process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8               |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

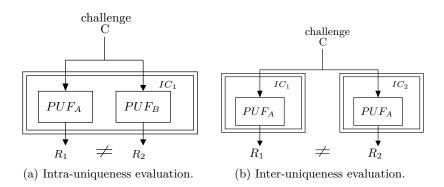

| 1.2  | Uniqueness evaluation process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8               |

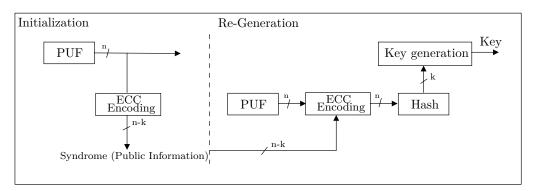

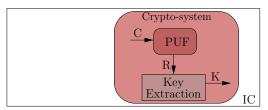

| 1.3  | Cryptographic key generation using PUFs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10              |

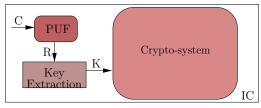

| 1.4  | Classical cryptographic key generation vs. hardware entangled cryp-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

|      | tography using PUFs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11              |

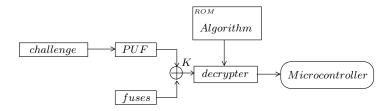

| 1.5  | IP protection using PUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11              |

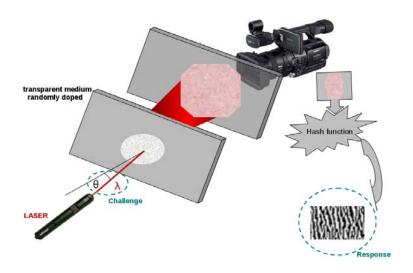

| 1.6  | Optical PUF principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12              |

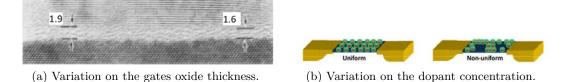

| 1.7  | Examples of process variation [Sap11]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14              |

| 1.8  | Die-to-die vs. within die variations [Sap11]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14              |

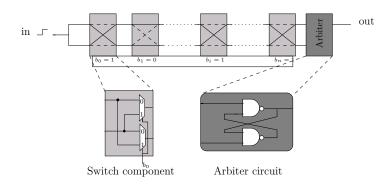

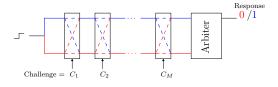

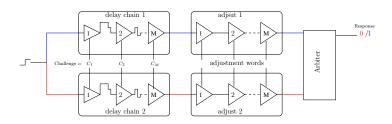

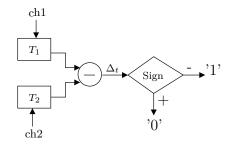

| 1.9  | Basic arbiter PUF structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17              |

| 1.10 | Tristate PUF structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17              |

| 1.11 | Arbiter PUF based on DPLs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18              |

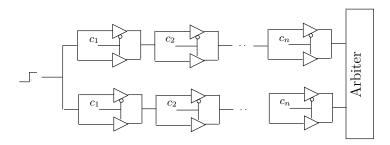

|      | FF-arbiter PUF structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19              |

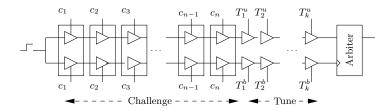

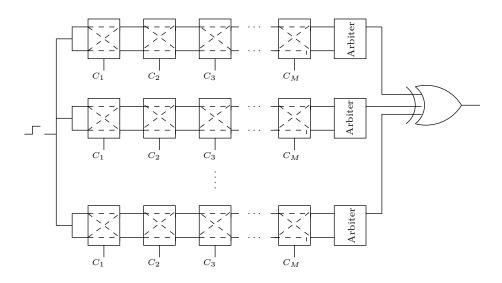

|      | Xor-arbiter PUF structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19              |

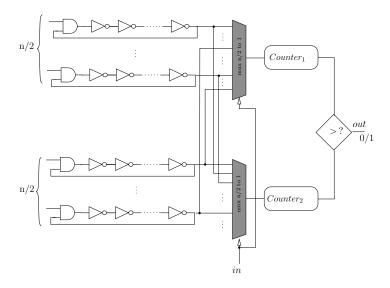

|      | Basic RO-PUF structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20              |

|      | An improvement of the RO-PUF structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22              |

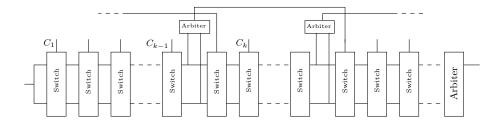

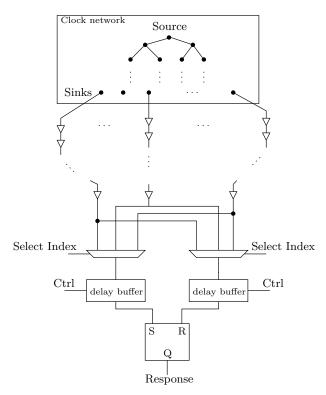

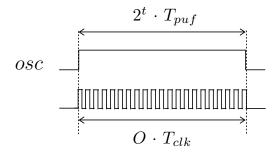

|      | Clock PUF structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24              |

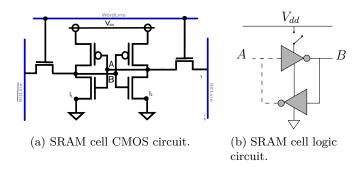

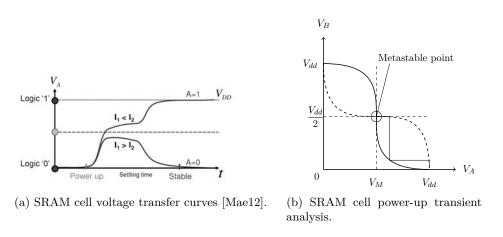

|      | Six transistors SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25              |

|      | SRAM cell voltage transfer curves and power-up transient analysis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\frac{-5}{25}$ |

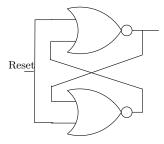

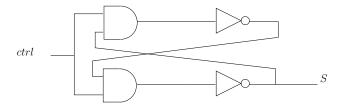

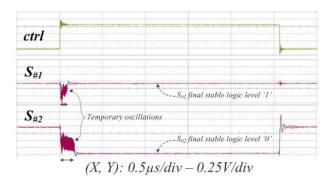

|      | Logical circuit of a latch PUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28              |

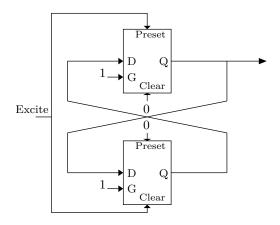

|      | Schematical circuit of a butterfly PUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29              |

|      | , and the state of |                 |

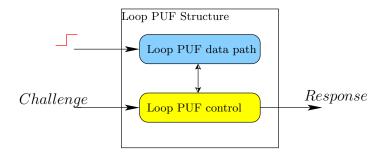

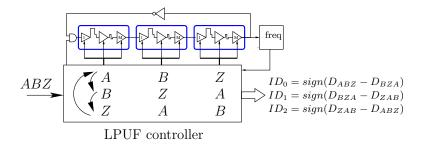

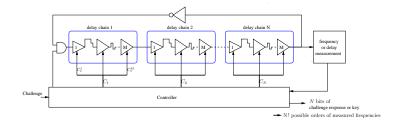

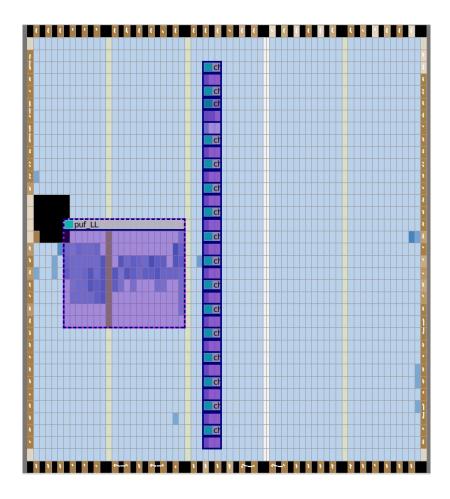

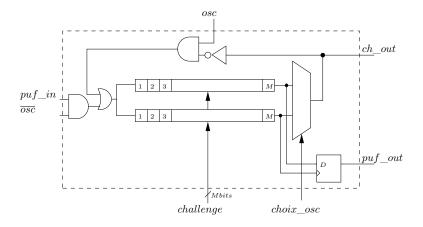

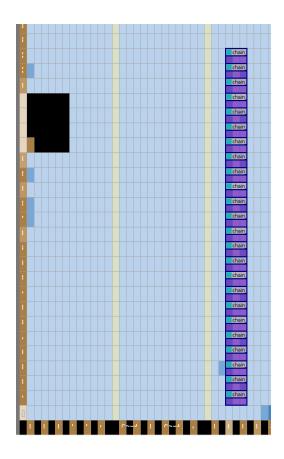

| 2.1  | The Loop PUF structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38              |

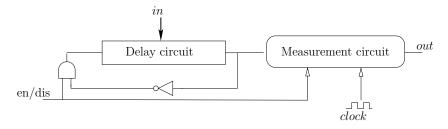

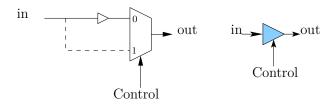

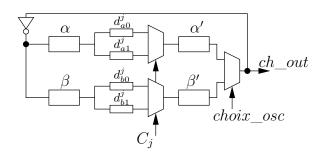

| 2.2  | Structure of a basic delay element                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39              |

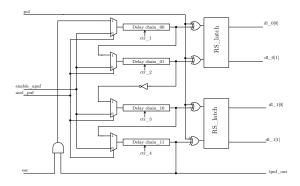

| 2.3  | Loop PUF datapath                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40              |

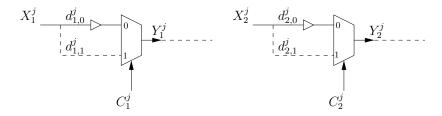

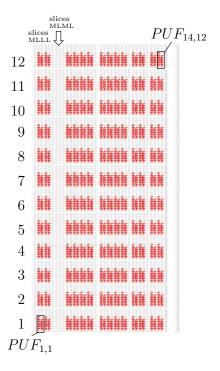

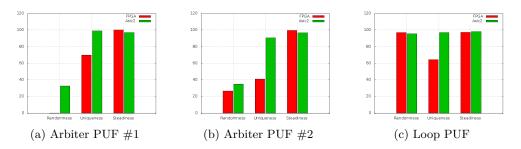

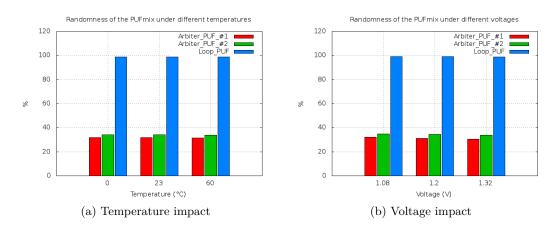

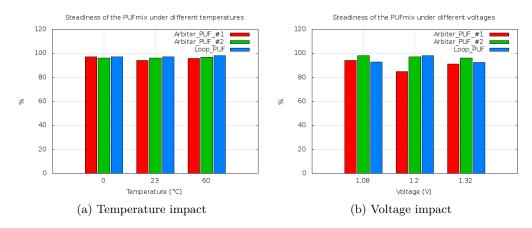

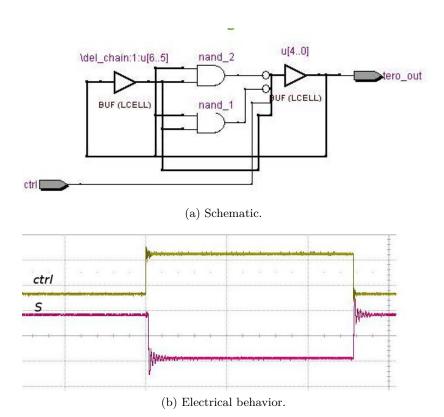

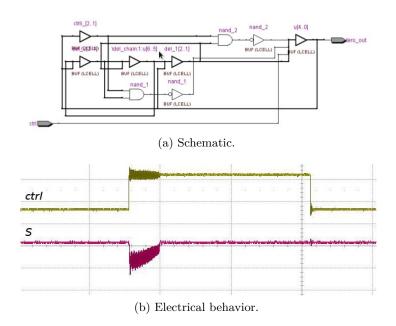

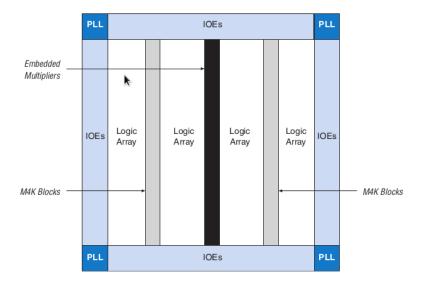

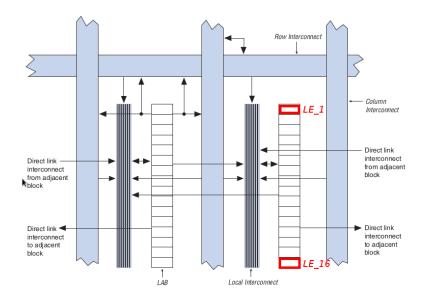

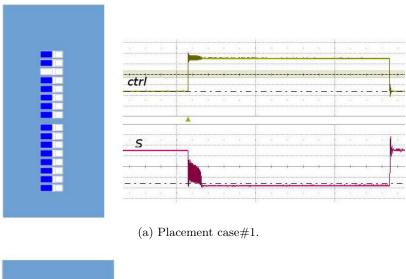

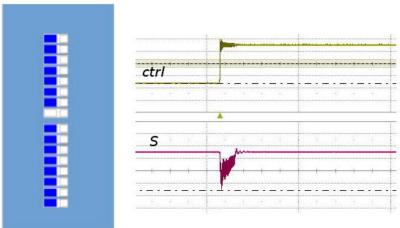

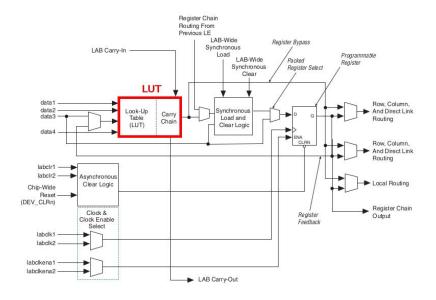

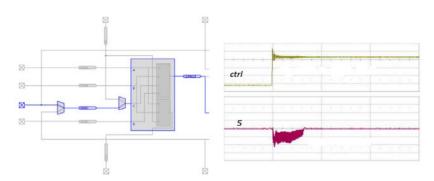

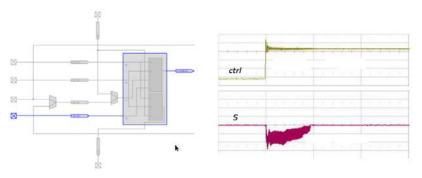

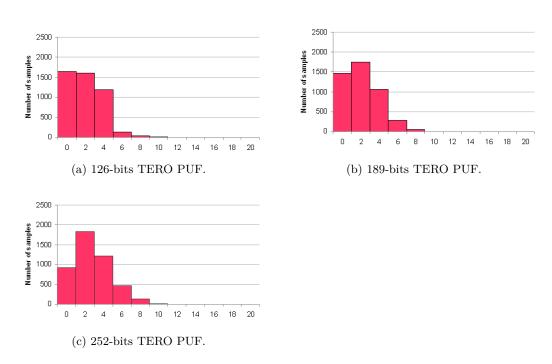

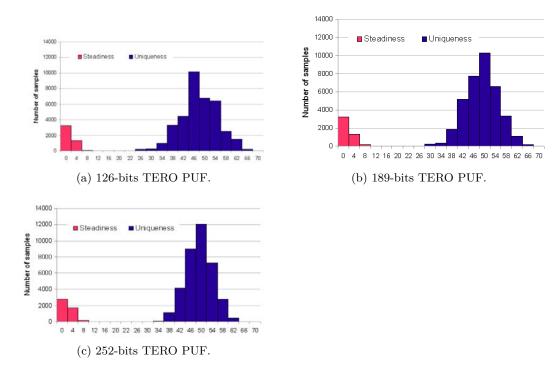

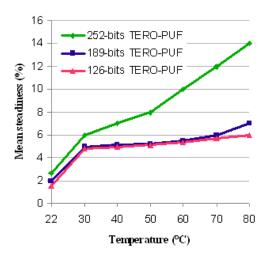

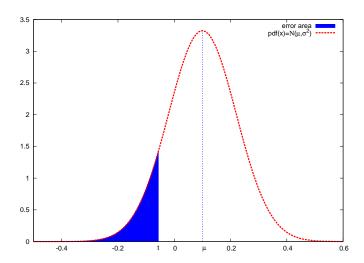

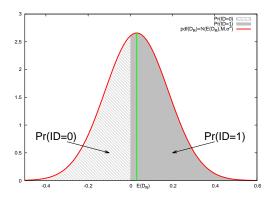

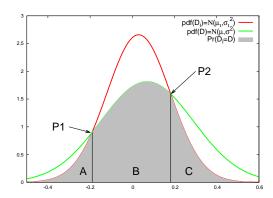

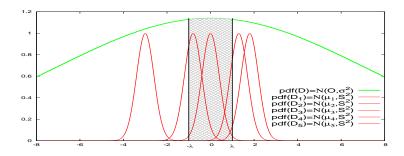

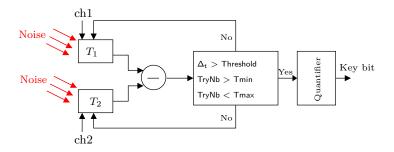

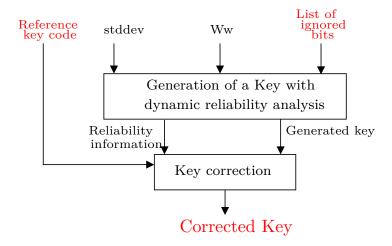

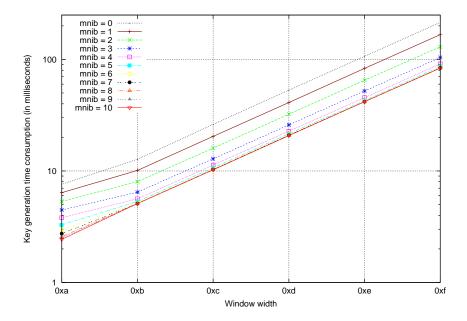

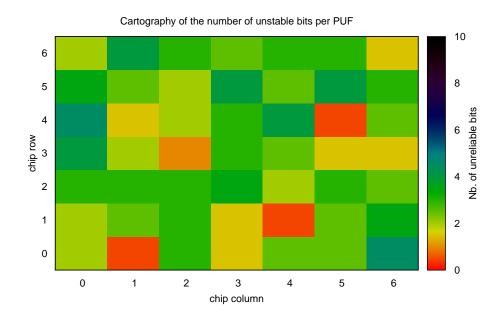

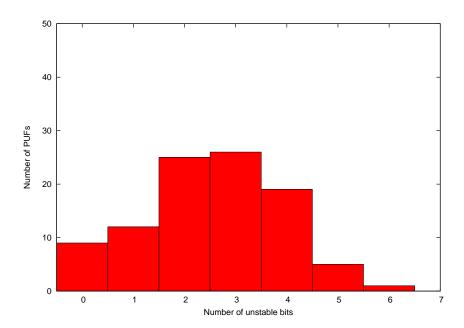

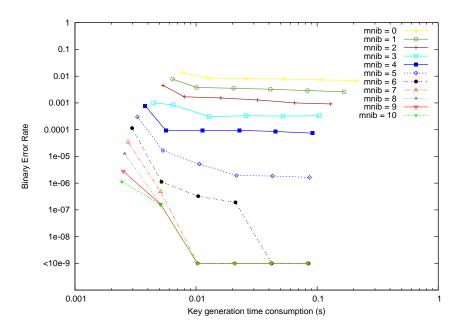

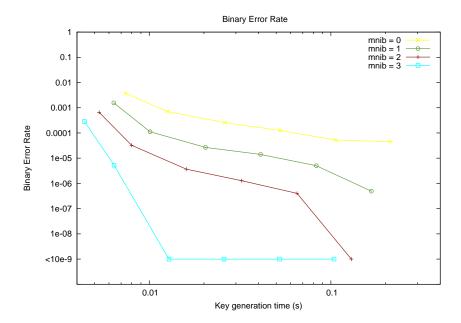

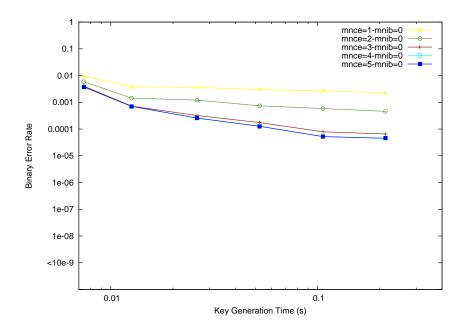

| 2.4  | Delay element $j$ for two delay chains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40              |