# Composability of parallel codes on heterogeneous architectures

Andra-Ecaterina Hugo

#### ▶ To cite this version:

Andra-Ecaterina Hugo. Composability of parallel codes on heterogeneous architectures. Computer science. Université de Bordeaux, 2014. English. NNT: 2014BORD0373. tel-01162975

# HAL Id: tel-01162975 https://theses.hal.science/tel-01162975

Submitted on 11 Jun 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE PRÉSENTÉE POUR OBTENIR LE GRADE DE

#### **DOCTEUR DE**

# L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DE MATHEMATIQUES ET INFORMATIQUE

SPÉCIALITÉ : INFORMATIQUE

#### Par Andra Hugo

## Composability of parallel codes on heterogeneous architectures

Sous la direction de : Raymond Namyst (co-directeurs : Pierre-Andre Wacrenier et Abdou Guermouche)

Soutenue le 12 décembre 2014

#### Membres du jury :

M. Frederic Desprez Directeur de Recherche INRIA Rapporteur M. Pierre Manneback Professeur des Universités Rapporteur M. Patrick Amestov Professeur des Universités Examinateur M. Thomas Herault Research Scientist Examinateur Mme. Isabelle Terrasse Professeur des Universités Examinateur M. Raymond Namyst Professeur des Universités Directeur de Thèse M. Pierre-Andre Wacrenier Maître de conférence Directeur de Thèse M. Abdou Guermouche Maître de conférence Directeur de Thèse

#### Remerciements

Je tiens tout d'abord à remercier mes directeurs de thèse, Raymond Namyst, Pierre-André Wacrenier et Abdou Guermouche de m'avoir guidée tout au long de ces trois années de thèse et également pendant les stages que j'ai effectués dans l'équipe Runtime et les cours que j'ai suivis à l'Université de Bordeaux. Au delà de la connaissance théorique, je voudrais les remercier de m'avoir appris à mieux structurer et présenter mes idées, à être plus rigoureuse dans mon travail scientifique et à mieux argumenter les solutions envisagées pour résoudre les problèmes que j'ai pu rencontrer tout au long de ces trois années de thèse.

J'adresse aussi mes remerciements aux membres de mon jury, Frédéric Desprez, Pierre Manneback, Patrick Amestoy, Thomas Herault et Isabelle Terrasse, pour avoir accepté et pris le temps de relire mon manuscrit et pour les questions pertinentes soulevées lors de la soutenance.

Un très grand merci à Marie-Christine pour ses conseils et sa patience lors des réunions assez bruyantes dans le bureau. Je souhaite ensuite remercier toute l'équipe Runtime de m'avoir accompagnée et soutenue au cours de cette thèse. Je pense particulièrement à Samuel et Nathalie qui ont répondu à pleins de questions sur StarPU et qui m'ont aidée lors des merges des branches de branches ..., de StarPU. Merci également à ma deuxième équipe Hiepacs qui m'a montrée le coté obscur de l'algèbre linéaire.

J'adresse de remerciements également à l'équipe pédagogique de l'IUT Bordeaux qui m'a accueillie pour que j'effectue mes heures d'enseignement. Je pense particulièrement à Pierre Ramet, Olivier Gauwin, Isabelle Dutour, Christine Uny, Michel Billaud. Un très grand merci à Jean-Michel Lépin pour ses conseils et son aide. Un deuxième merci à Pierre-André, Abdou et Samuel pour leur aide pendant mes six mois d'ATER à l'Université de Bordeaux.

Je pense également à Mehdi, Mathieu et Stole qui ont rendu cette période plus joyeuse. Merci pour les soirées films, pizza, bière ou même boite de nuit. Un grand merci à Julien pour m'avoir soutenue et supportée pendant le supplice de la rédaction.

Et enfin, les dernières mais non les moindres remerciements je les adresse à mes parents pour m'avoir guidée et soutenue à vouloir toujours apprendre des nouvelles choses et à essayer de devenir meilleure.

#### Titre: La composition des codes parallèles sur plate-formes hétérogènes

#### Résumé

Pour répondre aux besoins de précision et d'efficacité des simulations scientifiques, la communauté du Calcul Haute Performance augmente progressivement les demandes en terme de parallélisme, rajoutant ainsi un besoin croissant de réutiliser les bibliothèques parallèles optimisées pour les architectures complexes.

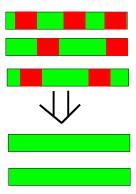

L'utilisation simultanée de plusieurs bibliothèques de calcul parallèle au sein d'une application soulève bien souvent des problèmes d'efficacité. En compétition pour l'obtention des ressources, les routines parallèles, pourtant optimisées, se gênent et l'on voit alors apparaître des phénomènes de surcharge, de contention ou de défaut de cache.

Dans cette thèse, nous présentons une technique de cloisonnement de flux de calculs qui permet de limiter les effets de telles interférences. Le cloisonnement est réalisé à l'aide de contextes d'exécution qui partitionnement les unités de calculs voire en partagent certaines. La répartition des ressources entre les contextes peut être modifiée dynamiquement afin d'optimiser le rendement de la machine. À cette fin, nous proposons l'utilisation de certaines métriques par un superviseur pour redistribuer automatiquement les ressources aux contextes. Nous décrivons l'intégration des contextes d'ordonnancement au support d'exécution pour machines hétérogènes StarPU et présentons des résultats d'expériences démontrant la pertinence de notre approche. Dans ce but, nous avons implémenté une extension du solveur direct creux qr\_mumps dans la quelle nous avons fait appel à ces mécanismes d'allocation de ressources. A travers les contextes d'ordonnancement nous décrivons une nouvelle méthode de décomposition du problème basée sur un algorithme de "proportional mapping". Le superviseur permet de réadapter dynamiquement et automatiquement l'allocation des ressources au parallélisme irrégulier de l'application. L'utilisation des contextes d'ordonnancement et du superviseur a amélioré la localité et la performance globale du solveur.

Mots-clés: Composition, Hypervisor, Support d'exécution

#### Title: Composability of parallel codes on heterogeneous architectures

#### Abstract

To face the ever demanding requirements in term of accuracy and speed of scientific simulations, the High Performance community is constantly increasing the demands in term of parallelism, adding thus tremendous value to parallel libraries strongly optimized for highly complex architectures.

Enabling HPC applications to perform efficiently when invoking multiple parallel libraries simultaneously is a great challenge. Even if a uniform runtime system is used underneath, scheduling tasks or threads coming from different libraries over the same set of hardware resources introduces many issues, such as resource oversubscription, undesirable cache flushes or memory bus contention.

In this thesis, we present an extension of StarPU, a runtime system specifically designed for heterogeneous architectures, that allows multiple parallel codes to run concurrently with minimal interference. Such parallel codes run within scheduling contexts that provide confined execution environments which can be used to partition computing resources. Scheduling contexts can be dynamically resized to optimize the allocation of computing resources among concurrently running libraries. We introduced a hypervisor that automatically expands or shrinks contexts using feedback from the runtime system (e.g. resource utilization). We demonstrated the relevance of this approach by extending an existing generic sparse direct solver (qr\_mumps) to use these mechanisms and introduced a new decomposition method based on proportional mapping that is used to build the scheduling contexts. In order to cope with the very irregular behavior of the application, the hypervisor manages dynamically the allocation of resources. By means of the scheduling contexts and the hypervisor we improved the locality and thus the overall performance of the solver.

Keywords: Composability, Hypervisor, Runtime

#### Résumé

L'introduction des processeurs multicœurs et des accélérateurs au sein des plates-formes de calcul haute performance a suscité de nombreux travaux de recherche autour de la portabilité des performances. Ces travaux se sont focalisés autour de supports d'exécution capables de fournir aux programmeurs des techniques et des outils permettant d'exploiter des architectures matérielles toujours plus complexes. Désormais les programmeurs disposent de supports d'exécution suffisamment matures pour exploiter de telles architectures (tels Cilk [29], OpenMP ou Intel TBB [49] pour les multicoeurs, Anthill [55], DAGuE [19], Charm++ [38], Harmony [26], KAAPI [34], StarPU [14] ou StarSs [17] pour les configurations hétérogènes) et peuvent maintenant construire des bibliothèques de calcul performantes. Ainsi la bibliothèque d'algèbre linéaire MAGMA [59], reposant sur des algorithmes particulièrement optimisés, s'appuie sur le support d'exécution StarPU pour exploiter de façon efficace et portable des architectures complexes.

L'émergence de telles bibliothèques facilite la tâche du programmeur qui a tout intérêt à recycler celles-ci pour construire son application. Cependant on observe que ces bibliothèques se comportent mal, au sens des performances, lorsqu'elles sont utilisées simultanément. En fait leur utilisation en série fournit souvent de meilleures performances. Cette dégradation des performances a été identifiée et est appelée problème de la composition parallèle [46, 42]. C'est un problème important puisqu'il représente un frein aux respects des principes de bases de la programmation (modularité, réutilisation).

Ce problème de composition survient lorsque plusieurs supports d'exécution entrent en compétition pour l'obtention des ressources et même parfois plus simplement lorsqu'on fait des appels simultanés à des routines parallèles d'une même bibliothèque. Les routines parallèles, pourtant optimisées, se gênent et l'on voit alors apparaître des phénomènes de surcharge (l'application utilise plus de threads qu'il n'y a de cœurs à sa disposition), de contention sur les bus ou défaut de cache. En effet, à des fins d'optimisation, les programmeurs de bibliothèques de calcul parallèle ont pris l'habitude d'avoir la maîtrise du nombre et du placement des threads, de l'ordonnancement des tâches de calcul et de l'utilisation des caches. Cependant ces optimisations locales peuvent s'avérer contre-productives dans un cadre plus général notamment en présence de plusieurs flux de calcul parallèles. Ce type de problème a amené la communauté à promouvoir des supports d'exécution capable d'exécuter de nombreux flots de calcul sans pour autant surcharger de threads la machine [29, 49].

À l'image des machines virtuelles, il existe aussi des supports d'exécution, tel Lithe [46], qui permettent d'attribuer dynamiquement des ressources matérielles à des flux de calcul : en cloisonnant ces flux on espère ainsi limiter leurs interférences. MPC [23] propose une solution MPI + OpenMP qui permet d'isoler les sections parallèles. Pour éviter de payer le coût de la consommation mémoire d'une telle approche, MPC se base sur une gestion TLS (Thread Local Storage) qui privatise les variables globales de chaque tâches MPI en fournissant des copies. Intel TBB [49] propose une manipulation de haute niveau qui isole les codes dans des structures appelées arènes, qui permettent un équilibrage de charge à travers la migration de threads mais qui sont limitées en terme de parallélisme. ForestGOMP [20] est un support d'exécution qui suit le parallélisme hiérarchique de l'application et qui propose un ordonnancement basé sur la topologie des machines. Il reste cependant un problème majeur : celui de l'attribution (automatique) des ressources à chaque partition.

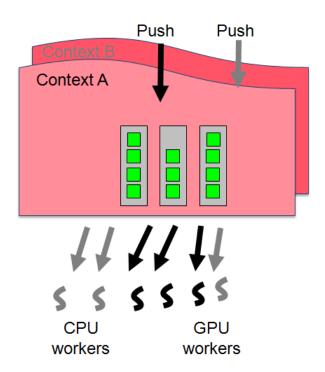

Dans cet thèse, nous présentons un support d'exécution où les différents flux de calcul parallèles s'exécutent dans des contextes d'ordonnancement séparés. Un contexte d'ordonnancement encap-

sule une instance d'un support d'exécution qui s'exécute sur un ensemble d'unités de calcul. La répartition des ressources entre les contextes peut être modifiée à la demande afin d'optimiser le rendement de la machine. À cette fin, nous proposons l'utilisation de certaines métriques (utilisation des ressources, progression du calcul) par un superviseur pour redistribuer automatiquement les ressources aux contextes. Nous avons implémenté cette approche en étendant le support d'exécution StarPU [14]. Les codes et bibliothèques de calcul développées au-dessus de StarPU peuvent ainsi tirer parti de cette fonctionnalité sans modification de code. Ceci nous permet de montrer expérimentalement l'intérêt de notre approche en l'appliquant à des exemples concrets.

#### Des contextes d'ordonnancement au sein de StarPU

S'attaquer au problème de la composition au niveau du support d'exécution est une approche qui assure la portabilité et la réutilisation de la solution. Ainsi, on fournit un outil qui a un accès direct à l'information de bas niveau sur l'architecture de la machine et qui permet au programmeur de contrôler l'allocation des ressources. Cependant, les supports d'exécution qui reposent sur une paradigme à base de tâches sont de plus en plus utilisés. Ils permettent au programmeur de fournir beaucoup d'informations (la charge de travaille, le parallélisme des noyaux) ainsi que de contrôler le flux d'exécution. Par conséquent on a choisi d'étudier le problème de la composition au sein du support exécutif StarPU. StarPU [14] est une bibliothèque qui propose aux programmeurs une interface portable pour ordonnancer des graphes de tâches dynamiques sur un ensemble hétérogène d'unités de calcul (CPUs et GPUs). Toute tâche est associée à une voire plusieurs implémentations afin de pouvoir être indifféremment exécutée sur un CPU ou un GPU, par exemple. De plus, StarPU utilise une mémoire virtuellement partagée automatisant la disponibilité et la cohérence des données.

Nous introduisons la notion de contexte d'ordonnancement au niveau de StarPU, afin de fournir au programmeur un outil capable de gérer l'allocation des ressources hétérogènes à plusieurs codes parallèles. Il s'agit de cloisonner les contextes en faisant en sorte que chaque contexte détienne (ou partage) des unités de calcul. Ainsi tout thread de l'application peut s'inscrire à un contexte pour soumettre ses tâches qui seront alors prises en charge par un ordonnanceur associé au contexte. Au niveau technique, l'intégration des contextes au sein de StarPU a été mise en œuvre à l'aide d'un dispositif permettant d'ajouter ou de supprimer dynamiquement une file d'ordonnancement à une instance d'ordonnanceur et ce de façon asynchrone. Ainsi alertés, les ordonnanceurs réagissent à toute nouvelle distribution des ressources permettant ainsi le redimensionnement dynamique des contextes. Cette capacité est importante puisque les besoins des différents flux de calcul évoluent au cours du déroulement de l'application.

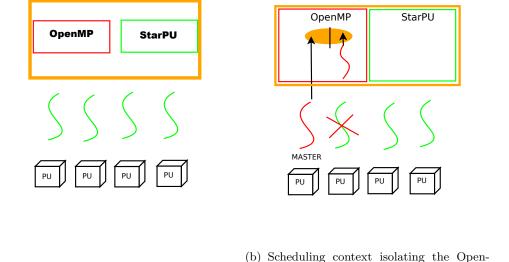

Nous avons proposé deux scénarios pour évaluer les contextes d'ordonnancement: composer plusieurs noyaux parallèles appartenant à la librairie d'algébre linéaire dense MKL sur une plate-forme homogènes (40 CPUs) et composer plusieurs noyaux parallèles appartenant à la librairie d'algébre linéaire dense MAGMA-MORSE sur une plate-forme hétérogènes (12 CPUs et 3 GPUs). Dans les deux cas nous avons montré qu'à travers les contextes d'ordonnancement on arrive à isoler les noyaux parallèles et ainsi améliorer leur localité et leur scalabilité. Le programmeur a donc le contrôle sur l'allocation des ressources. Néanmoins, décider combien de CPUs et de GPUs allouer à un certain code parallèle à et quand devient une tâche compliquée même pour un niveau d'expertise élevé.

#### Superviser pour redistribuer

Afin d'automatiser la répartition des ressources nous avons mis au point un système de supervision de l'activité des unités de calcul et de progression des contextes. Ce dispositif est mis en œuvre par un hyperviseur exécuté de façon distribuée par les CPUs. Le rôle de l'hyperviseur est de redimensionner les contextes d'ordonnancement lorsque des dégradations de performance sont observées. L'hyperviseur peut être invoqué depuis l'application (directement ou indirectement lors de création / destruction / modification de contexte) ou peut être déclenché automatiquement.

Lors de l'exécution, la progression du déroulement de l'application est évaluée au travers d'indications fournies soit directement par l'application, soit par les compteurs de performance ou encore par la routine d'estimation de la date de terminaison. Au besoin, une redistribution des ressources est appliquée. De plus cette redistribution peut être contrainte par le programmeur, les contraintes étant explicitées sous forme d'intervalle d'unités de calcul à respecter.

Dans ce cadre, nous avons étudié deux métriques pour piloter le redimensionnement des contextes. La première est basée sur un compteur bas-niveau mesurant l'inactivité des ressources et la seconde est basée sur la vitesse instantanée d'un contexte et sur le nombre d'opérations qu'il reste à exécuter. Le choix entre les deux est déterminé par les informations fournies par le programmeur.

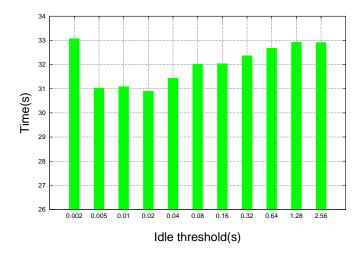

Dans la stratégie *Idleness-base resizing*, les contextes sont redimensionnés lorsqu'une des ressources est inactive pendant une période plus longue que celle spécifiée par le programmeur. Expérimentalement on s'est aperçu que ce seuil peut être dépendent du parallélisme de l'application.

Dans la stratégie *Speed-based resizing* l'application procure une estimation de la quantité totale de travail (le nombre de flops) correspondante à chaque noyau parallèle et à chaque tâche. Avec ces indications, l'hyperviseur calcule la vitesse instantanée de chaque noyau parallèle ce qui permet d'estimer la date de terminaison de chaque noyau. Lorsque la différence de vitesse entre les contextes est suffisamment grande, l'hyperviseur redimensionne les contextes.

L'hyperviseur utilise plusieurs stratégies afin d'optimiser l'exécution de l'application. Ainsi, celles-ci sont basées sur diffèrents crières: minimiser le temps de terminaison des flux en cours ou maximiser leurs vitesse instantanée. Pour ce faire on utilise des programmes linéaires qui formalisent ces problèmes à travers des systèmes d'équations. Ils prennent en entrée des informations comme la quantité de travail (le nombre d'opérations flottantes ou le nombre de tâches de chaque type) que doit réaliser chaque contexte. Ils fournissent le nombre de CPUs et GPUs nécessaire à chaque contexte de façon à minimiser la date de terminaison globale ou maximiser la vitesse de chaque contexte.

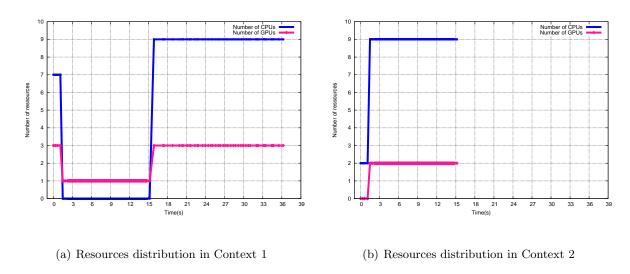

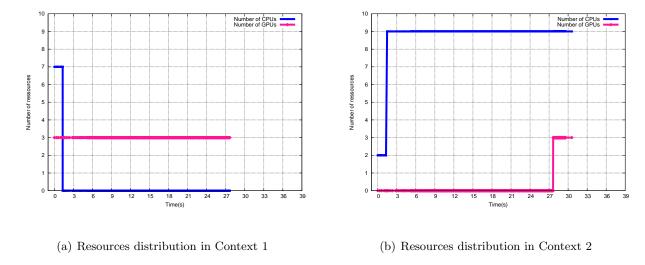

Dans un premier temps nous avons évalué le comportement de l'hyperviseur dans le cadre d'un scénario simple: nous avons composé deux noyaux parallèles appartenant à la librairie d'algèbre linéaire dense MAGMA-MORSE sur une architecture hétérogènes et nous avons fourni une allocation statique inefficace. Dans ce contexte nous avons analysé la réactivité et l'efficacité de l'hyperviseur à remettre en cause l'allocation initiale et à la régler en fonction des besoins de l'application. Nous avons comparer différentes stratégies de redimentionnement en terme de précision et surcoût.

#### Allocation dynamique des ressources pour un solveur des systèmes linéaires creux

Afin de valider notre approche on s'est attaqué à une application compliquée, plus concrètement à qr\_mumps, un solveur de systèmes linéaires creux. L'objectif principal a été d'évaluer une façon différente de gérer l'allocation des ressources et l'affinité mémoire au sein des applications HPC à

travers des mécanismes placés au niveau du support d'exécution.

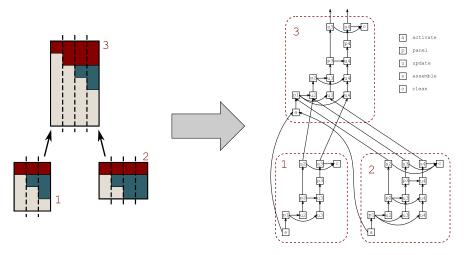

Le solveur qr\_mumps fourni une méthode de factorisation QR creuse basée sur une approche multifrontale. L'algorithme multifrontal considère un arbre d'élimination [51], qui représente la réduction transitive du graphe de la matrice remplie et qui décrit les dépendances entre les opérations d'élimination. Le graphe de tâches est donc construit pendant la phase d'analyse quand les algorithmes de pré-traitement sont appliqués. L'algorithme continue avec la factorisation numérique puis par les pas de résolution du système.

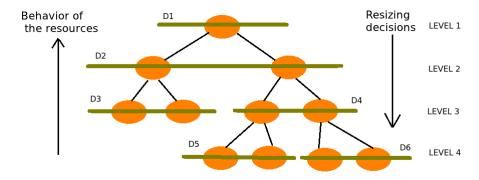

L'approche a été de capturer la structure parallèle de l'application de façon hiérarchique et de la projeter sur un arbre abstrait. Cette arbre est ensuite décrit à travers une hiérarchie de contextes d'ordonnancement qui va permettre une gestion dynamique de l'allocation de ressources.

L'hyperviseur intervient pour collecter des informations venant de l'application ainsi que des statistiques matérielles capturées au niveau du support d'exécution. Les stratégies de dimmentionement prennent en compte ces valeurs affin de régler le nombre d'unités de calcule assigné à chaque tâche parallèle.

On évalue l'efficacité de cette approche à travers une collection des problèmes différents venant de l'Université de Florida. On effectue des expériences sur des architectures multicœurs modernes avec des accès mémoire non uniformes. On observe a travers l'utilisation des contextes un meilleur moyen de respecter la localité des données entre les tâches. De plus la hiérarchie de contextes favorise le chemin critique. La mise en œuvre de cette solution permet d'obtenir des gains en terme de temps d'exécution atteignant 35%.

#### Conclusions

Dans cette thèse nous avons étudié le problème de la composition parallèle à l'aide de StarPU. Nous avons introduit la notion de contexte d'ordonnancement pour donner au programmeur la maîtrise des ressources attribuées à différents flux de calcul: les contextes peuvent être redimensionnés à volonté et les unités de calcul peuvent être partagées ou non. Nous proposons l'utilisation de métriques par un hyperviseur pour redistribuer automatiquement les ressources aux contextes. De plus, afin d'assurer la portabilité des performances, nous proposons d'utiliser des programmes linéaires dont la solution nous permet d'obtenir une bonne distribution correspondante aux indications de charge transmisses par l'application. Enfin, nous avons montré expérimentalement l'intérêt de cette approche à travers qr\_mumps, un solveur des systèmes linéaires creux. Nous avons ègalement montré l'apport d'un système de supervision pour redistribuer automatiquement les ressources aux contextes.

Ces travaux ouvrent de nombreuses perspectives de recherche. En terme d'amélioration, nous envisageons d'augmenter la précision et la réactivité de la détection de sous-utilisation des ressources à travers des conteurs matérielles. Cette approche peut également contribuer à une deuxième perspective, qui est d'améliorer la négociation des ressources parmi des codes qui ne reposent pas sur StarPU. Néanmoins, nos idées se dirigent vers des nouveaux stratégies de redimensionnement qui suivent des algorithmes d'ordonnancement de la littérature ou qui prennent en compte des nouveaux métriques comme la consommation d'énergie.

Les perspectives de plus long-termes se place au niveau de la valorisation de ces travaux dans le cadre des applications complexes de couplage de codes. Toutefois, les techniques présentées doivent suivre les évolutions des machines parallèles. Par conséquent, nous envisageons d'intégrer au niveau de l'Hyperviseur des nouveaux algorithmes pour mieux partitionner les architectures many-core et ainsi mieux passer à l'échelle.

# Contents

| In | Introduction |                                                                             |    |

|----|--------------|-----------------------------------------------------------------------------|----|

| 1  | Kee          | ping up with the evolution of computer architectures                        | 17 |

|    | 1.1          | From multi-cores to many-cores                                              | 17 |

|    | 1.2          | Programming environments in HPC                                             | 18 |

|    |              | 1.2.1 Implicit representations systems                                      | 19 |

|    |              | 1.2.2 Explicit representation systems                                       | 20 |

|    | 1.3          | Dealing with the composability of parallel libraries                        | 22 |

|    |              | 1.3.1 Oversubscription/undersubscription problem                            | 23 |

|    |              | 1.3.2 Parallel environments handling the oversubscription/undersubscription | 24 |

|    | 1.4          | Discussion                                                                  | 27 |

| 2  | Sche         | eduling Contexts: a solution to compose parallel codes                      | 29 |

|    | 2.1          | Composability-related issues on top of task-based runtimes                  | 29 |

|    | 2.2          | Proposed solution: scheduling contexts to isolate parallel codes            | 30 |

|    | 2.3          | Scheduling contexts on top of StarPU                                        | 31 |

|    | 2.4          | Allocate resources to scheduling contexts                                   | 31 |

|    |              | 2.4.1 Lightweight virtual machines                                          | 32 |

|    |              | 2.4.2 Information provided by the application                               | 33 |

|    | 2.5          | Scheduling policy inside the context                                        | 34 |

|    | 2.6          | Share computing resources                                                   | 34 |

|    | 2.7          | Implementation                                                              | 35 |

|    | 2.8          | Execution model                                                             | 35 |

|    |              | 2.8.1 Scheduling contexts using StarPU scheduling strategies                | 36 |

|    |              | 2.8.2 Scheduling contexts using Non-StarPU scheduling strategies            | 36 |

|    | 2.9          | Evaluation                                                                  | 36 |

|    |              | 2.9.1 Experimental scenarios                                                | 37 |

|    |              | 2.9.2 Experimental architectures                                            | 38 |

|    |              | 2.9.3 Homogeneous architecture                                              | 38 |

|    |              | 2.9.4 Heterogeneous architecture                                            | 39 |

|    | 2.10         | Discussion                                                                  | 42 |

| 3  | The          | Hypervisor                                                                  | 43 |

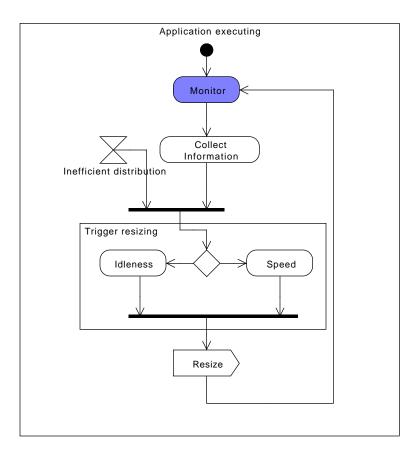

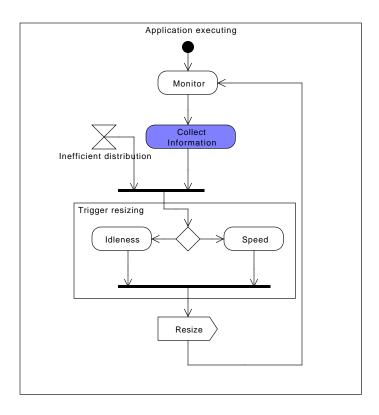

|    | 3.1          | Monitoring scheduling contexts' activity                                    | 43 |

|    | 3.2          | Collecting information                                                      | 44 |

|              | 3.3  | Triggering the resizing process                                          | 45       |

|--------------|------|--------------------------------------------------------------------------|----------|

|              |      | 3.3.1 When to trigger the resizing?                                      | 46       |

|              |      | 3.3.2 How to trigger the resizing?                                       | 46       |

|              | 3.4  | Resizing the scheduling contexts                                         | 46       |

|              |      | 3.4.1 (Re)allocate resource to scheduling contexts                       | 46       |

|              |      | 3.4.2 Adapt to resource reallocation constraints                         | 47       |

|              |      | 3.4.3 Strategies to resize scheduling contexts                           | 48       |

|              | 3.5  | Implementation                                                           | 52       |

|              |      | 3.5.1 Collaborating with the application                                 | 52       |

|              |      | 3.5.2 Collaborating with the runtime                                     | 53       |

|              |      | 3.5.3 Resizing policy platform                                           | 54       |

|              | 3.6  | Execution model                                                          | 55       |

|              | 3.7  | Evaluation                                                               | 56       |

|              |      | 3.7.1 Experimental architectures                                         | 56       |

|              |      | 3.7.2 Experimental scenarios                                             | 56       |

|              |      | 3.7.3 On-demand resizing                                                 | 57       |

|              |      | 3.7.4 Automatic resource distribution                                    | 57       |

|              | 3.8  | Discussion                                                               | 63       |

|              | _    |                                                                          |          |

| 4            |      | namic resource allocation for a sparse direct solver                     | 65       |

|              | 4.1  | qr_mumps                                                                 | 66       |

|              | 4.2  | qr_mumps on top of StarPU                                                | 66       |

|              | 4.3  | A partial task graph mapping strategy                                    | 67       |

|              | 4.4  | Build a hierarchy of scheduling contexts                                 | 69       |

|              | 4.5  | Hierarchical resizing of the Scheduling Contexts                         | 70       |

|              | 4.6  | Upper bounds to the allocation of resources                              | 71       |

|              | 4.7  | Triggering the reallocation of resources                                 | 72<br>74 |

|              | 4.8  | Evaluation                                                               | 74       |

|              |      | 4.8.1 Experimental environment                                           | 74       |

|              | 4.0  | 4.8.2 Experimental evaluation                                            | 75       |

|              | 4.9  | Discussion                                                               | 81       |

| 5            | Con  | nclusion                                                                 | 83       |

| <b>A</b>     | D    | oning out of libraries                                                   | 87       |

| A            | Ехр  | perimental libraries                                                     | 01       |

| В            | Exp  | perimental machines                                                      | 89       |

| $\mathbf{C}$ | Usi  | ng the Scheduling Contexts to compose a CFD and a Cholesky Factorization |          |

|              | kerr | nel                                                                      | 91       |

| ъ            |      |                                                                          |          |

| D            | Bib  | liography                                                                | 93       |

# List of Figures

| 1.1  | The architecture of the StarPU runtime system                                           |

|------|-----------------------------------------------------------------------------------------|

| 1.2  | HPC application calling 2 BLAS procedures simultaneously                                |

| 2.1  | Scheduling contexts                                                                     |

| 2.2  | Resource allocation for non-StarPU parallel kernels                                     |

| 2.3  | Scheduling Contexts in StarPU                                                           |

| 2.4  | Programming with Scheduling Contexts                                                    |

| 2.5  | Executing Intel MKL parallel codes within Scheduling Contexts                           |

| 2.6  | Using MCT to schedule two flows of tasks                                                |

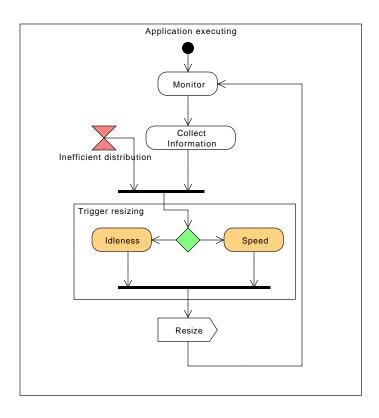

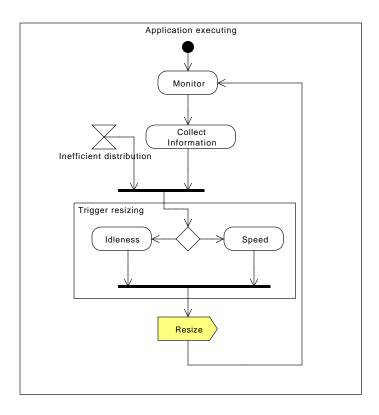

| 3.1  | A tool to monitor                                                                       |

| 3.2  | A tool to collect information                                                           |

| 3.3  | A tool to trigger                                                                       |

| 3.4  | A tool to resize                                                                        |

| 3.5  | On-demand strategy in StarPU                                                            |

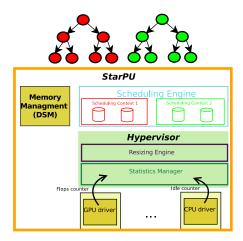

| 3.6  | Placing the Hypervisor in StarPU                                                        |

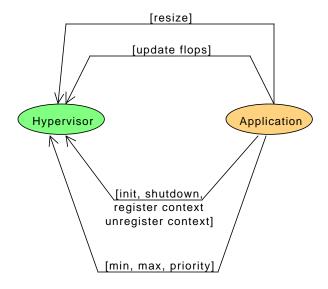

| 3.7  | Collaborating with the application                                                      |

| 3.8  | Collaborating with the runtime                                                          |

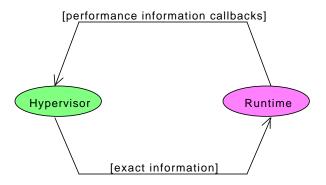

| 3.9  | The hypervisor updates performance information throughout runtime callbacks $\dots$ 5-  |

| 3.10 | Structure of a new resizing policy                                                      |

| 3.11 | 0 71                                                                                    |

| 3.12 | Reallocate resources to [Small_Cholesky2] and [Large_Cholesky2] streams using           |

|      | the On-demand strategy                                                                  |

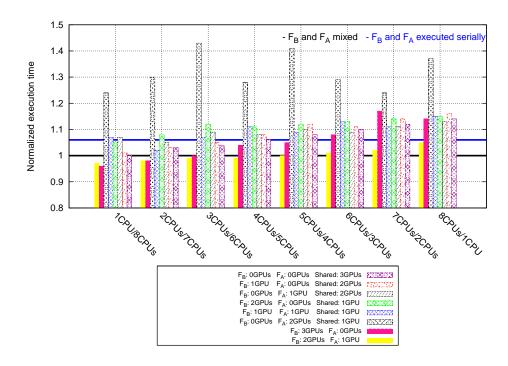

|      | Composing [Large_Cholesky] $(F_B)$ and [Small_Cholesky] $(F_A)$                         |

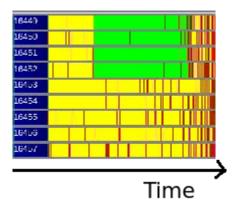

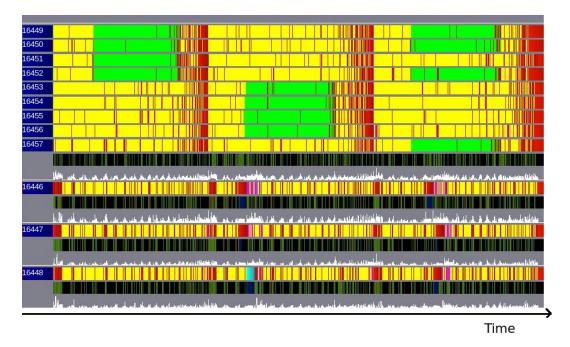

|      | Resource distribution over the contexts when using the instant speed based policy 60    |

|      | Choosing the idle threshold to trigger resizing                                         |

| 3.16 | Resource distribution over the contexts when using the completion time based policy. 63 |

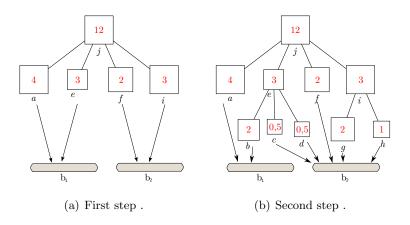

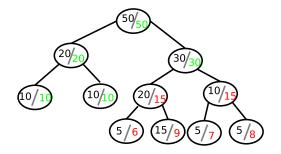

| 4.1  | An example of how a simple elimination tree with three nodes is transformed into        |

|      | a DAG in the qr_mumps code. Vertical, dashed lines show the partitioning of fronts      |

|      | into block-columns. Dashed-boxes group together all the tasks related to a front $6$    |

| 4.2  | Mapping algorithm                                                                       |

| 4.3  | Resizing hierarchical contexts by having local deadlines                                |

| 4.4  | Use idle time to compute $max$                                                          |

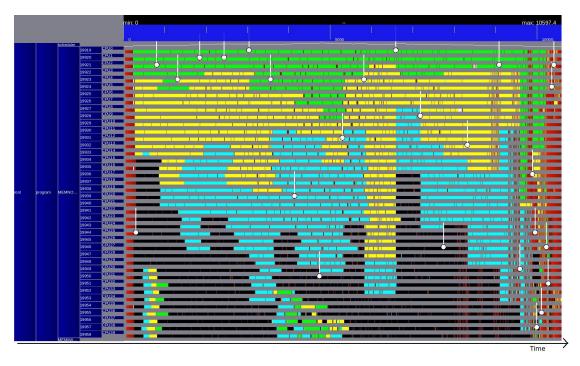

| 4.5  | Example of qr_mumps solving a simple problem using 4 scheduling contexts over 40        |

|      | CPUs 73                                                                                 |

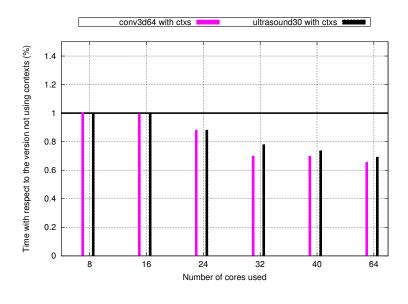

| 4.6      | Hierarchically trigger resizing of scheduling contexts                             | 74 |

|----------|------------------------------------------------------------------------------------|----|

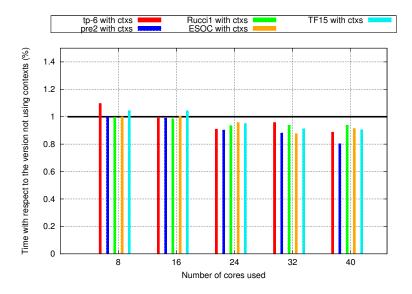

| 4.7      | Execution time of the hierarchical version of qr_mumps with respect to the non     |    |

|          | contexts StarPU version on the riri platform                                       | 77 |

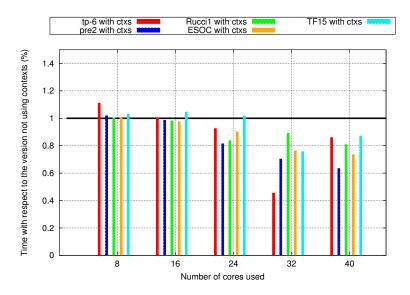

| 4.8      | Execution time of the hierarchical version version of qr_mumps with respect to the |    |

|          | non contexts StarPU version on the ares platform                                   | 78 |

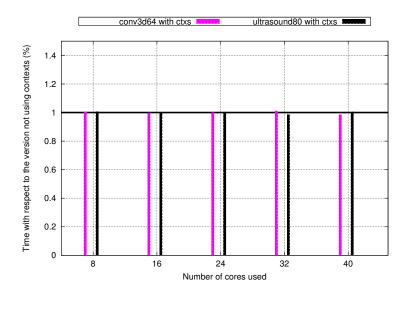

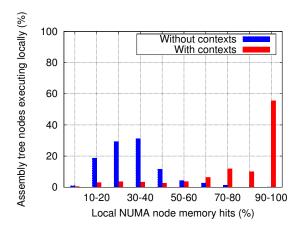

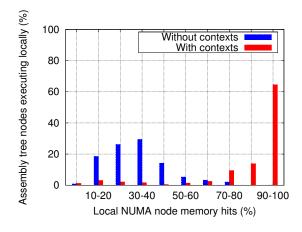

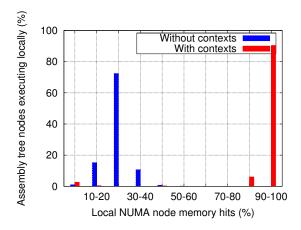

| 4.9      | Locality of data references for the Rucci1 problem                                 | 80 |

| 4.10     | Locality of data references for the conv3d64 problem                               | 80 |

| <u> </u> |                                                                                    |    |

| C.1      | Composing [Small_Cholesky_960] and [CFD] normalize with respect to the             | 92 |

# List of Tables

| 1.1 | Categorization of parallel libraries                                                    | 19 |

|-----|-----------------------------------------------------------------------------------------|----|

| 2.1 | Composing mkl kernels (Time in s)                                                       | 38 |

| 2.2 | Composing MAGMA kernels (Time in s)                                                     | 39 |

| 2.3 | Data transfer statistics of concurrent execution of three factorizations on mirage      |    |

|     | platform                                                                                | 40 |

| 2.4 | Data transfer statistics of concurrent execution of 9 factorizations on mirage platform | 41 |

| 3.1 | Application driven resizing policies                                                    | 57 |

| 3.2 | Cost of a redistribution of resources (ms)                                              | 61 |

| 4.1 | Matrices test set. The operation count is related to the matrix factorization with      |    |

|     | METIS column permutation                                                                | 75 |

| 4.2 | Cost of the resizing process with respect to the total execution time $(\%)$            | 76 |

| 4.3 | Execution time in seconds of different test problems of the regular qr_mumps imple-     |    |

|     | mentation on top of StarPU                                                              | 79 |

# Introduction

High Performance Computing community is nowadays investing considerable effort in continuously exploiting the parallelism of their applications. Fluid-structure interaction, magneto-hydro dynamics, thermal coupling, define only a subset of recent multi-physics code coupling simulations that require extreme-scale computing in order to accelerate their execution. In order to satisfy their demands hardware manufacturers keep on designing even more complex computer architectures. Yet, very few people have the expertize to program such architectures efficiently, adding thus a tremendous value to parallel libraries strongly optimized to use such architectures. Indeed, there is a common feeling in the community that reusing existing parallel libraries is indispensable.

Consequently, building high performance computing applications on top of parallel libraries is now commonplace. However, even if a natural approach would be to rely on as many external parallel libraries as needed and allow their concurrent execution, most applications invoke only one parallel library at a time. The reason lies in current implementations of parallel libraries not being ready to run simultaneously over the same hardware resources. Usually each one of them is making the assumption that their procedures have exclusive access to the computing resources. As a consequence, in order to fully tap into the potential of many-core architectures, parallel libraries typically invoke different optimizations in order to bypass the underlying operating system and better use the underlying resources. For instance, parallel libraries typically fix one thread per core in order to have a better utilization of the cache memory. However, when co-executing several parallel procedures, each one has its own set of threads and this optimization does not longer apply. As a result, applications resulting from the composition of parallel libraries usually exhibit poor performance.

The only safe solution is then to serially or sequentially use external parallel libraries. However, this situation is alarming because important software development concepts like modular and abstract structured programming are no longer used in HPC. Thus, parallel libraries do not attain their initial purpose: hide the complexity of designing an efficient and reusable collection of parallel algorithms.

Systematically used from the earliest days of programming in sequential applications, *software* reuse should also be possible in HPC. We think one of the main challenges for upcoming years is to make this possible by arbitrating the use of the computing resources between the co-existent parallel libraries. This can only be achieved by the negotiation of resources. A first step is to explore each party's requirements and workload. Then the goal is to seek "win-win" or mutually beneficial resource distributions.

#### Goals and Contribution of this thesis

The batch-job schedulers of cluster computing platforms have already dealt with the problem of nodes allocation for simultaneously executing applications. However, this issue is hardly addressed when executing parallel codes within the same application on the same machine. Every day more heterogeneous, with more cores and accelerators, these machines are hardly used at their full capacity. Code-coupling application would surely benefit of efficiently executing tightly coupled parts of their computation at the intra-node level as well. However, inside the node the negotiation of resources cannot only consider the load of the parallel codes but also their affinity towards the different types of computing resource. Indeed, programmers cannot deal with this problem alone. They need a low level tool that can provide an abstraction of the heterogeneous architecture of the machine and at the same time high level mechanisms to integrate user level information. Runtime systems represent thus the most appropriate level of the software stack for implementing such a tool as it can allow a strong interaction with both the hardware and the application. The contributions of this thesis cover the different aspects of the composability problem managed at the runtime level. More particularly, we identify the following main topics:

- Isolation of parallel libraries. We propose using the notion of *Scheduling Contexts* in order to restrict the execution of the parallel libraries on a section of the machine.

- Supervision of the execution of the application. We propose a tool called the *Hypervisor* that monitors the execution of the parallel kernels and collects both low-level (for instance the efficient execution of the computing resources) and high-level information (application hints).

- Dynamic allocation of computing resources. The hypervisor integrates different algorithms based on linear systems that provide solutions to dynamically reallocate computing resources between the parallel libraries.

- Validation of the approach. We validate our approach on simple case scenarios as well as on complex High Performance libraries like qr\_mumps sparse direct solver.

All the contributions described in this thesis have been implemented and experimented in the StarPU runtime system. Although the concept remains independent of the StarPU implementation and can easily be adapted to other runtime systems. Most of the contributions have been the subject of several refereed publications which are listed at the end of this document.

## Organization of this document

Chapter 1 presents a short overview of the High Performance Computing evolution both in term of hardware and programming environments leading thus to the need to reuse and compose parallel codes. Chapter 2 introduces the notion of Scheduling Contexts as a solution to the isolation of parallel libraries. Chapter 3 describes the Hypervisor as a StarPU plugin able to provide the necessary tools to dynamically redistribute computing resources to parallel libraries. Chapter 4 shows that the concept of dynamic co-existence of parallel codes allows improving the performance of qr\_mumps, a sparse direct solver. We finally conclude and describe our perspectives in Chapter 5.

# Chapter 1

# Keeping up with the evolution of computer architectures

Computer architectures are constantly evolving in order to satisfy the every day more demanding large scale applications. Both industrial and research areas require a tremendous amount of computing power, memory and storage. Therefore, the computer manufacturers constantly try to add more computation resources, more memory, providing every day more challenges to the programmers using them.

#### 1.1 From multi-cores to many-cores

The first attempts to introduce parallelism inside an application have been made at the instruction level of the processing unit, where the computer architects increased the clock frequencies by allowing the simultaneous execution of multiple instructions (Instruction Level Parallelism - ILP). When these techniques have reached the limits of power consumption and heat dissipation the manufacturers started focusing on adding more processing units (Thread Level Parallelism - TLP) to the computation platform.

With platforms having several processing units connected between them, applications started relying on an important increase in parallelism. However, the symmetric access to a common memory (Symmetric multiprocesseurs - SMP) generated an important contention on the bus memory. Cache hierarchies provided a good solution to limit the bus access but despite this, computing platform with several dozens of processing units could not scale on such an architecture.

NUMA (Non Uniform Memory Access) architectures became then more popular as they allow having different memory banks distributed all over the machine. Processing units grouped around a memory bank forming a NUMA node have a fast access to their data, however accessing a distant NUMA memory nodes is more costly. Thus, despite all the effort, the contention on the bus memory is still a problem unless the application has a solution for the locality management.

Therefore, the evolution of computers is now driven by a run towards higher and higher numbers of cores per chip. This trend was largely anticipated by Graphical Processing Units (GPUs). Originally designed for processing images, GPUs are now highly specialized computing devices meant to handle a particular class of applications with well defined characteristics: large computational requirements and substantial, fine-grained parallelism. Application Programming Interfaces (API) for GPUs such as CUDA or OpenCL have been rapidly evolving in the last few years: GPU pro-

grams can now be written in familiar programming languages (such as C or Fortran) according to a Single Program Multiple Data (SPMD) parallel programming model which opened the way for the collective effort that is commonly known under the name of *General Purpose GPU* (GPGPU) computing [45]. However, applications programmers find it difficult to achieve considerable performance when using it. Not only the programming paradigm is different compared to the CPUs one but also the memory coherence management becomes less straightforward when using it together with other types of processing units. Despite this, hybrid computing becomes a solid trend as there is an increasing need to exploit any computing power.

#### 1.2 Programming environments in HPC

Complex applications running on such platforms require important programming efforts in order to efficiently make profit of the heterogeneity of the processors, the frequency of their execution, the hierarchical memory access and the memory capacity.

Most of the times we can consider parallel applications as graphs with nodes representing the operations to be performed and edges representing ordering constraints imposed by dependencies. Programming these applications on large parallel platform consists in mapping the graphs on the machine. This task becomes less straightforward for a high connectivity of the graph and for a highly non uniform architecture. Runtime systems are considered to be a solution that simplifies the interaction of the application with the hardware. By using a runtime system, programmers target obtaining for their applications what we call *performance portability*, that is finding a trade-off between performance improvement and compatibility with different architectures.

Runtime systems represent a user level software that complements the basic, general purpose functions provided by the operating system calls. Applications delegate them all the parallelism management (e.g. scheduling, task dependencies, etc.) and the runtime systems optimize the use of the underlying hardware resources. For instance, the hybrid use of general purpose cores together with specialized accelerating ones (e.g. GPU) requires solving a difficult mapping problem, in order to decide which computation could efficiently execute on which type of core. Moreover, as GPUs have their own local memory, performing operations on such resources requires transferring data from main memory to the GPU's memory, potentially overlapping communication with computation and obviously considering the transfer time when mapping an operation on the GPU. The runtime systems usually take in charge all this and make this operations as transparent as possible for the application.

According to [61] the runtime systems can be split in several approaches to building and accessing these graphs. We show thus in Table 1.1 a set of runtime systems grouped according to this criteria (inspired by the table presented in [61]).

In implicit graph representations systems, runtime systems do not have access to the graph of operations of the application and therefore they rely on the programmer to indicate the order of the operations, to launch parallel work and manage the synchronizations. For instance MPI and X10 are systems in which the programmer manages when, how and in which order the operations of the application should execute. On the other hand, in the explicit graph representations systems, runtime systems have direct access to the graph and thus manage the synchronizations and scheduling.

Some explicit systems are static, that is the graph of operations is built at compile time. Some others are dynamic, that is they discover and manage the graph at runtime as it is generated on-line

```

Implicit Graph Representation Systems

MPI [52] OpenMP [13] TBB [49] X10 [54] Charm++ [38] UPC [22] CUDA [1] OpenCL [53] MPC [23] ForestGOMP [20]

Explicit Graph Representation Systems

Sequoia [27] PaRSEC [19] StarPU [14] XKaapi [31] Legion [18]/Realm [61] OmpSs [17]

```

Table 1.1: Categorization of parallel libraries

by the application. Static systems have the advantage of not inducing any runtime overhead to the scheduling of the graph. However dynamic runtime systems provide a better flexibility to adapt to more complex architectures as well as to applications based on irregular parallelism.

Therefore, on a general basis, implicit graph representation systems are based on a control flow approach, while the explicit graph representation systems are based on a data flow approach. However, even if there are significant differences between the two approaches, some applications may require using both of them.

#### 1.2.1 Implicit representations systems

Further on we discuss about a few of the runtime systems in table 1.1 mentioned in the implicit representation systems category. We choose one of each of the main data communication paradigms: shared memory, message passing, partition global address space (PGAS).

**OpenMP** [13] standard relies on a *shared memory paradigm* and it was first defined in 1997 by a consortium formed of universities, hardware and software vendors. It provides a set of annotations used to parallelize sequential programs written in C/C++ or Fortran. Thus, programmers can automatically generate the creation of threads, their synchronization as well as their termination. Generally used for loops, OpenMP automatically creates the number of threads equal to the number of CPUs and assigns an equivalent number of indexes of the loop to each thread. GOMP or Intel OpenMP are some of the most common implementations of the standard.

MPI [52] standard relies on a message passing paradigm and it was first proposed in 1993 by a consortium formed of universities, hardware and software vendors. It provides an interface that allows portable network communication. The vendors provide the network adapted implementation such that the applications are not aware of the underlying hardware. Some of the most used high Performance implementations are OpenMPI [30] and MPICH [33].

MPI is based on the idea of having a sender and a receiver that constantly change of roles between them. It relies on a SPMD programming model (Single Program Multiple Data), having thus a single program executed by several processes that exchange messages during the execution

whenever synchronizations or distant data is necessary. This feature revealed to be useful for intranode parallelism too, as it induces a good isolation of the programs without the synchronization issues of shared memory systems. Despite this, one important disadvantage leaded to having the programmers think of different solutions for intra-node implementations. Each process has its own virtual address space, requiring multi-processes systems to allocate the necessary memory for each process, and having potentially several copies of the same data whenever several processes required it. As the number of cores increased the memory consumption became a serious problem and programmers had to start using a different paradigm inside a node.

**X10** [54] is a parallel programming language relying on a *PGAS* (Partition Global Address Space) paradigm. Implemented by IBM and released for the first time in 2004, X10 is a language focusing on concurrency and distribution, while making profit of an object oriented programming tradition.

X10 uses the notion of Place to encapsulate binding of activities and globally addressable data. The management of synchronizations is done by means of a system of hierarchies between the activities. Nevertheless, the programmer is fully in charge with calling functions for asynchronous execution or synchronization. By means of atomic sections, X10 enforces mutual exclusion of shared data.

#### 1.2.2 Explicit representation systems

Static or dynamic, explicit representation systems rely on what we call task-based paradigm. Increasingly adopted recently, it provides an easy way to express concurrency and dependencies. Thus, a task represents a piece of computation that executes a certain kernel on a predefined set of data. Usually organized into a DAG (Direct Acyclic Graph) the tasks are used by the applications to describe the operations to be executed. We say applications use a data flow approach because the dependencies between different pieces of computation dictate the synchronization and the order of their execution. This is a portable approach that responds to the requirements of hybrid architectures because, provided an adapted implementation of the kernel, the task may execute on a CPU or on an accelerator. An efficient execution of such a DAG corresponds to finding a suitable mapping of the tasks on different processing units [15].

**PaRSEC** [19] previously called DAGuE, is a runtime system implemented at ICL (Innovative Computing Laboratory) at the University of Tennessee and it was first released in 2010. It is a distributed DAG scheduling engine, where tasks are sequential computations and edges are communications. Each process has its own instance of the scheduler, and all the communications are implicitly made by the runtime. Therefore, a PaRSEC user has to provide the DAG of tasks together with the data distribution.

PaRSEC uses a static description of the graph, by expressing all the task dependencies before starting the execution. This insures a limited overhead of the scheduling. However, the graph can be queried dynamically in a distributed fashion. PaRSEC provides a dynamic and fully distributed scheduler based on cache awareness, data locality and task priority.

**StarPU** [14] is a C library developed in the Runtime team at Inria Bordeaux and it was first released in 2009. It provides programmers with a portable interface for scheduling dynamic graphs of tasks onto a heterogeneous set of processing units (*i.e.* CPUs and GPUs). The two basic principles of StarPU are firstly that tasks can have several implementations, for some or each of the

various heterogeneous processing units available in the machine, and secondly that necessary data transfers to these processing units are handled transparently by the runtime system. StarPU tasks are defined as multi-version kernels, gathering the different implementations available for CPUs and GPUs, associated to a set of input/output data. To avoid unnecessary data transfers, StarPU allows multiple copies of the same registered data to reside at the same time on several processing units as long as it is not modified. Asynchronous data prefetching is also used to hide memory latencies.

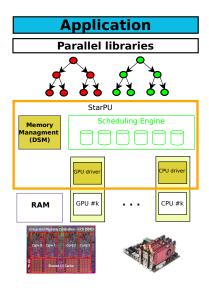

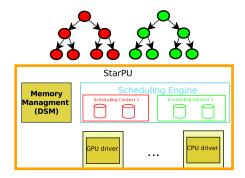

Figure 1.1: The architecture of the StarPU runtime system.

StarPU is a platform for developing, tuning and experimenting with various task scheduling policies in a portable way (see Figure 1.2). Implementing a scheduler consists in creating a set of queues, associating them with the different processing units, and defining the code that will be triggered each time a new task gets ready to be executed, or each time a processing unit is about to go idle. Various designs can be used to implement queues (e.g. FIFOs or stacks), and they can be organized according to different topologies. Several built-in schedulers are available, ranging from greedy and work-stealing based policies to more elaborate schedulers implementing variants of the Minimum Completion Time (MCT) policy [60]. This latter family of schedulers builds on auto-tuned history-based performance models that provide estimations of the expected durations of tasks and data transfers.

These models are actually performance history tables dynamically built during the application run. By observing the execution of the tasks, the runtime is able to capture the speedup and the affinities between the tasks and processors. Therefore, without the programmer's involvement, the runtime can provide a relatively accurate performance estimation of the expected requirements of the tasks allowing the scheduler to take appropriate decisions when assigning the tasks to a computing resource.

Similarly to other dynamic explicit graph representation systems, StarPU discovers the task

dependencies dynamically showing thus more flexibility but more overhead of the scheduling too. It provides a natural way to estimate the workload of an application, by keeping a history-based reference of the execution time of the tasks, the memory bandwidth, the data transfer costs, etc.

#### 1.3 Dealing with the composability of parallel libraries

Many years of research conducted to important breakthroughs for many parallel libraries (linear algebra, physics, etc.). By relying on available mature implementations of runtime systems (e.g. Cilk [2], OpenMP or Intel TBB [49] for multicore machines, Parsec [19], Charm++ [38], KAAPI [34], StarPU [14] or OmpSs [17] for heterogeneous configurations) programmers are able to rely on thread/task facilities to develop efficient implementations of parallel libraries, like for example: Intel MKL [25], FFTW [28], FMM [11], etc. They are now able to provide parallel procedures optimized to execute extremely efficiently by considering memory and scalability bottlenecks of the parallelism.

With both hardware and software users continually striving to reach performance, application programmers cannot afford spending any more effort in reimplementing already optimized procedures. By relying on existing parallel libraries, they not only factorize code and reuse existing implementations but they also delegate performance portability concerns. The widely used BLAS (Basic Linear Algebra Subroutines) procedures are one example of basic computations, that high-level programmers usually do not consider reimplementing.

Building high performance computing applications on top of specific parallel libraries is now commonplace [32]. However, even if a natural approach would be to rely on as many external parallel libraries as needed and allow their concurrent execution, most applications invoke only one parallel library at a time. The reason lies in current implementations of parallel libraries not being ready to run simultaneously over the same hardware resources. This problem, referred to as the parallel *composability* problem [46, 42] has already been raised by the programmers of different applications.

Intel MKL for instance is known to be one of the libraries that promotes calling the parallel kernels sequentially instead of simultaneously. Despite this they propose a solution for experienced low level programmers, they advise making profit of the fact that the parallel library is well integrated with the Intel OpenMP runtime system, and reuse thus its abstract view of the machine [3].

This situation is actually alarming, because it reveals that well-known programming principles such as code *composability* and code *reusability* are currently not applicable to High Performance Computing.

There is a wide panel of applications that face this problem, ranging from code-coupling applications (e.g. molecular dynamics coupled with finite elements methods), where opportunities for executing concurrent parallel kernels are still under-exploited, to linear algebra libraries, and more precisely sparse linear algebra methods and fast multipole methods. Typically, numerical factorizations of sparse matrices involve the execution of various dense linear algebra kernels. Some of these kernels operate on small and medium blocks, and thus exhibit poor scalability on high numbers of cores. In such situations, running several kernels concurrently to preserve good scalability of each instance may greatly help to improve overall performance.

#### 1.3.1 Oversubscription/undersubscription problem

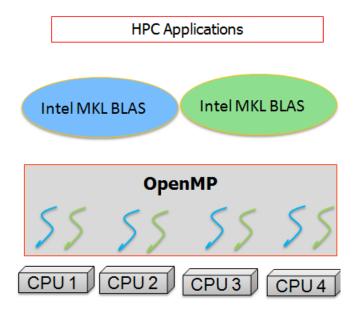

Calling simultaneously several parallel procedures is a difficult matter because usually parallel libraries make the assumption that each procedure has exclusive access to the architecture of the machine. The main reason is that in the past years, computer architectures were not large enough (in term of processing units or memory) to host several parallel codes. Therefore, in order to fully tap into the potential of many-core architectures, parallel libraries typically allocate and bind one thread per core to bypass the underlying operating system's scheduler. Specialized parallel libraries, such as BLAS for instance, strictly follow such a rigid approach, to better control cache utilization. As a result, applications resulting from the composition of parallel libraries usually exhibit poor performance, because each library is unaware of other libraries' resource utilization and they run into the oversubscription problem. Indeed, even composing parallel codes belonging

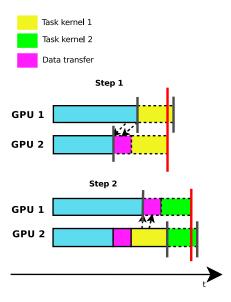

Figure 1.2: HPC application calling 2 BLAS procedures simultaneously

to the same library or relying on the same runtime exhibit severe performance issues when trying to simultaneously run independent parallel blocks within the same application. Determining the side-by-side or the nested parallelism and impose a certain allocation of resources is not an easy matter. Intel MKL, for instance, allows the application to specify the resources to allocate to each parallel code by using the OpenMP runtime to control them. However, the specificity of each parallel code (in terms of parallelism, granularity or memory access) requires additional knowledge in order to allocate the good number of processing units at the right moment of the execution.

However, for certain systems the oversubscription is necessary in order to perform well. The authors of [36] evaluate the task oversubscription on the performance of MPI, OpenMP and UPC and show that it can improve the execution time of certain applications running in competitive environments. Indeed, applications with less memory access and implicitly less synchronization requirements are less vulnerable in systems competing for resources. On the other side, systems

with significant parallelism and data dependencies are likely to benefit from the oversubscription to improve the load balancing and CPU utilization.

Nevertheless, oversubscription has been historically used to cover the latency, and complex parallel machines disposing of a hierarchical memory level structure could use it to overcome the cost of distant memory access. Despite this, we have to bear in mind that such a solution on many-cores machine is hardly scalable. Assigning tasks to each processing unit of the many-core architectures is a difficult matter. Applications partitioning the workload at a fine-grained level increase the parallelism by generating an important number of operations, but also impose an overhead on the execution time of the application due to the management of all these operations. Instead, the coarse-grained partitioning of the workload represents a burden to the parallelism but avoids the overhead. However, finding the best trade-off between fine and coarse grained partitioning seems to vary with the type of parallel code and the type of architecture.

This issue has led a few runtime system designers to provide implementations able to avoid *resource oversubscription* when multiple libraries simultaneously request the scheduling of tasks/threads. Static isolation of parallel codes may however lead to the undersubscription problem, where some libraries may have more resources assigned than they can use.

#### 1.3.2 Parallel environments handling the oversubscription/undersubscription

In the following section we analyze different environments that provide a solution to the oversubscription and sometimes to the undersubscription problem, we then discuss their benefits and their limitations.

#### 1.3.2.1 Intel TBB and Cilk

Intel TBB [49] is a runtime system that throughout the notion of arena allows for a pool of workers to execute different work stealing algorithms. However, when executing simultaneously different parallel codes in complex applications, the work stealing algorithms are not efficient any more. Low workload parallel codes expected to finish executing right away are burdened by high workload parallel codes. For this reason in the 3.0 version, Intel TBB allowed having several arenas used to isolate parallel codes and workers to migrate between arenas in order to respect the load balancing.

However, the degree of parallelism of *arenas* is limited, because the programmer has to indicate the maximum number of threads that can join the arena, therefore even if thread migration is allowed, no more than a certain number of threads can do this. This finally interferes with the distribution of resources since it can allow certain kernels to progress faster than others. Moreover, NUMA aspects of fair location are hardly respected as threads can migrate from one NUMA node to another.

Well integrated with the TBB runtime, Cilk [2] also tackled this problem by providing several parallel patterns (map, reduce, fork-join, etc.) that can be composed in an application. The solution for the composability of these codes was based on the philosophy of separating the notion of mandatory parallelism (tell the system what must run in parallel) and optional parallelism (tell the system what can run in parallel). Thus, the programmer decides on the type of parallelism, and the runtime takes advantage of this flexibility to balance the load across threads. However, Intel OpenMP was not integrated with TBB and Cilk, providing no tool to manage the oversubscription problem.

#### 1.3.2.2 ForestGOMP

ForestGOMP [20] is an OpenMP runtime compatible, offering a structured way to efficiently execute OpenMP applications on top of hierarchical architectures. Developed in the Runtime Team at Inria Bordeaux and first released in 2007, ForestGOMP proposes a topology aware OpenMP thread scheduling. It uses BubbleSched in order to automatically generate bubbles out of OpenMP parallel regions.

BubbleSched [56] provides a solution to detect the hierarchical structure of the application and map it on the hierarchical architecture of the targeted machine. By relying on the notion of "bubble", the runtime isolates groups of threads that present a certain affinity (for instance data sharing, collective operations). User-level threads belonging to the MARCEL library [44], can then be scheduled on the machine by using different strategies.

#### 1.3.2.3 PaRSEC

Driven by the need to enforce locality and to better scale on large NUMA machines, PaRSEC adopted a solution tackling the composability problem. By statically isolating certain parts of the graphs of tasks the programmers expected to better match the architecture. However, in order to enforce this structure of the application, branches are separated to be executed by what they call VPs (Virtual Processes) allowing an inner parallelism completely local. However, outer communication is made through shared memory in order to diminish the memory allocations.

#### 1.3.2.4 MPC

Mixing MPI and OpenMP is a good solution to benefit from both shared memory and message passing. Thus, isolating OpenMP parallel code inside an MPI process provides a solution to the oversubscription problem. However, it usually leads to the undersubscription problem as this approach is purely static and does not allow any load balancing. Moreover, mixing the inner and outer synchronizations usually forces one thread to manage MPI communications only, thus interfering with the performance of the inner threaded execution.

MPC [23] is a runtime system that also focuses on mixing OpenMP and MPI multi-threaded programming models, and harness the benefits of the two paradigms. Developed by the CEA (The French Alternative Energies and Atomic Energy Commission) and first released in 2008, MPC is a hybrid parallelism framework exposing a thread based MPI runtime (each MPI rank is a thread) and an OpenMP compatible runtime. Focused to diminish memory allocations, all threads (MPI ranks) share the same address space. It targets thus optimizing both network communication and shared memory one, by providing a dynamic workload balancing.

In order to avoid shared memory synchronization issues as well as locality constraints, the MPC runtime propose a TLS (Thread Local Storage) management that privatizes every global variable to obtain thus one copy per MPI task. Therefore, it is a solution to flexibly deal with hybrid MPI and OpenMP programming, as well as a good way to stack multiple parallel programming runtime systems.

However, mixing two different implementations of runtime systems leads to a certain overhead, as the interaction between the two interferes with the resource utilization, leading sometimes to an undersubscription situation. Therefore, MPC proposes using the oversubscription in order to create more parallelism and thus manage the load balancing between the MPI tasks.

In order to limit the consequent overhead on the scheduler, MPC proposes using the notion of micro VP(micro Virtual Processors) in order to create an abstraction of the MPI tasks, and then distribute the micro threads to each micro VP such that the latter schedules them locally.

This represents a good solution to the composability problem by finding an equilibrium between the undersubscription and the oversubscription situation. Using light implementations for the micro-threads and then isolating them in micro-VPs enforce computations to execute locally with a limited overhead of the context switch. However, it does not represent a solution to the undersubscription problem as it does not provide a dynamic load balancing system.

#### 1.3.2.5 Invasive Computing

Martin Schreiber in his dissertation [50] defended on January 2014 at the University from Munich (Germany), proposes an algorithm to deal with the oversubscription implemented on top of the X10 language. Initially designed for cluster based parallelizations, he describes a dynamic resource management for multi-processes applications. His algorithm relies on three notions: *invade*: requiring new computing resources, *infect*: replicating the program (no actual copy on shared memory systems) onto the successfully invaded resources and starting the program and *retreat*: freeing the previously invaded computing resources.

He proposes a Resource Manager that communicates with the applications through message passaging by using a client-server paradigm. The Client applications, parallelized with TBB or OpenMP, send messages with one of the three constraints (min/max number of resources, application's scalability or application's workload) to the Resource Manager(the server). The latter replies, at the end of a time step, in order to provide information with different scheduling decisions.

Dealing with distributed systems as well as shared memory system definitely requires having a uniform algorithm to manage both level of heterogeneity. Therefore, invasive computing seems to be a good solution to manage oversubscription at the cluster level and at the machine level as well.

#### 1.3.2.6 OpenCL

OpenCL [53] standard offers a common API for programs that execute across heterogeneous architectures. It was released for the first time in 2008 by the Khronos Compute Working Group, a consortium formed with representatives from CPU, GPU, embedded processors and software companies. OpenCL defines core functionalities that all devices support, insuring thus portability and correctness of the code. However, performance results vary according to the specificity of each hardware architecture as well as to the corresponding implementation.

OpenCL is a tool that allows the programmer to manage the devices, the memory allocations, the data transfers, including launching the kernels on the target devices. Meanwhile, OpenCL provides a more high-level feature that is called *device contexts*. Before doing any of the previous tasks, the programmer has to create a context associated with one or more devices. Further on the memory allocation is associated to a context, instead of a device as other paradigms require. This feature creates a constraint to have devices with similar requirements grouped together, as memory is limited to the least-capable one. One drawback is that they also have to belong to the same vendor.

Nevertheless, OpenCL provides a good feature to deal with the composability on a heterogeneous platform. Directly connected to the memory allocation it favors the memory consumption and the locality.

#### 1.3.2.7 Lithe

Lithe [46] is a framework developed as part of the DEGAS project, with the joint effort between UC Berkeley, LBNL, UT Austin, and Rice University. First released in 2009, Lithe provides an environment where threads no longer represent the virtual abstractions of the CPUs, and where each processing resource is represented by a hart (hardware thread). A parallel library can schedule an arbitrary number of tasks, which are very similar to lightweight threads, on top of a fixed set of harts managed by Lithe. Thus, instead of having the false illusion of unlimited processing resources, we have a fixed number of harts, cooperatively exchanged between libraries.

Lithe is based on a hierarchical system where schedulers are always attached to their parent scheduler upon creation. Therefore, children register themselves to their parents, and the parents provide harts to their children. A child may dynamically request additional harts. If accepted by its parent, it will receive the control of the harts through a transition context. Similarly, a parent receives the control of the harts back when one of its children finishes their computations.

By isolating the parallel sections, Lithe provides a solution to the interference generated by the simultaneous co-existence of these codes. However, problems like how and when a parent library should yield harts to a child library are still open to discussions.

#### 1.4 Discussion

Many years of research and development made us having today complex architectures targeting petaflop performance. Nevertheless, if we want to harness their full computing potential one may find them difficult to program. Therefore, specialized parallel libraries usually leave this tasks on behalf of runtimes, delegating the low level optimizations and the portability requirements.

Modularity and reusability concepts imply that applications should rely on these libraries for executing specialized basic operations. However, composing different parallel libraries in HPC applications is not a straightforward task. Parallel libraries are not aware of one another and the application may run into the oversubscription problem. Static solutions fixing the number of threads at compile time not only require significant code modifications but also sometimes lead to undersubscription problems.

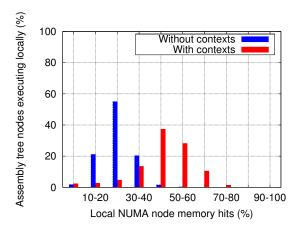

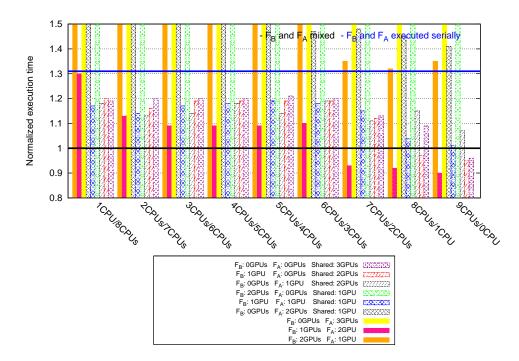

Several state of art solutions try to deal with this problem in different ways. A generic solution for shared memory systems is *Lithe*. It proposes removing the false illusion of unlimited resources and allows exchanging them between the parallel codes. Thus, Lithe eliminates the interference generated by the oversubscription and is able to allow different parallel libraries to co-execute on the same machine. MPC, on the other hand, advocates light well controlled oversubscription. It relies on the hybrid MPI and OpenMP approach in order to isolate parallel sections, but without the burden on the memory consumption that such a method implies. Intel TBB provides a much higher level programing environment where parallel codes are isolated into arenas. At the opposite side ForestGOMP focuses on the hierarchical parallelism of the applications in order to separate parallel sections and provides a topology aware OpenMP thread scheduling. All in all, these solutions provide different ways to deal with the composability problem, but they do not have quality information coming from the application in order to tell how many resources each kernel should use and at what point a resource should be reallocated.