# Integrated circuit immunity modelling beyond 1 GHz Sjoerd Op 'T Land

## ▶ To cite this version:

Sjoerd Op 'T Land. Integrated circuit immunity modelling beyond 1 GHz. Electromagnetism. INSA de Rennes, 2014. English. NNT: 2014ISAR0029 . tel-01165061

## HAL Id: tel-01165061 https://theses.hal.science/tel-01165061

Submitted on 18 Jun 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

La modélisation de l'immunité des circuits intégrés au-delà de 1 GHz

#### Thèse soutenue le 20.06.2014

devant le jury composé de :

### Frank Leferink

Professeur Université de Twente, Pays-Bas / président

## **Etienne Sicard**

Professeur – INSA de Toulouse / rapporteur

#### Geneviève Duchamp

Professeure – Université de Bordeaux 1 / rapporteur

#### Jean-Luc Levant

Expert CEM - Atmel Nantes / examinateur

#### Richard Perdriau

Enseignant Chercheur HDR - ESEO Angers / Co-encadrant de thèse

#### **Mohamed Ramdani**

Enseignant Chercheur HDR - ESEO Angers / Co-directeur de thèse

#### M'hamed Drissi

Professeur – IETR INSA de Rennes / Directeur de thèse

# La modélisation de l'immunité des circuits intégrés au-delà de 1 GHz

# Integrated Circuit Immunity Modelling Beyond 1 GHz

## En partenariat avec

[sumus] quasi nanos, gigantium humeris insidentes, ut possimus plura eis et remotiora videre, non utique proprii visus acumine, aut eminentia corporis, sed quia in altum subvenimur et extollimur magnitudine gigantea

[we are] like dwarfs on the shoulders of giants, so that we can see more than they, and things at a greater distance, not by virtue of any sharpness of sight on our part, or any physical distinction, but because we are carried high and raised up by their giant size

[nous sommes] des nains assis sur des épaules de géants, nous voyons plus de choses et plus lointaines qu'eux, ce n'est pas à cause de la perspicacité de notre vue, ni de notre grandeur, c'est parce que nous sommes élevés par eux.

als dwergen [zijn wij], gezeten op de schouders van reuzen, opdat we méér zien dan zij, en verder, niet door onze eigen scherpe blik of uitmuntend lichaam, maar omdat we, hoog opgetild, boven hen uit torenen

*Bernard of Chartres* (12<sup>th</sup> century)

## Résumé

La compatibilité électromagnétique (CEM) est l'aptitude des produits électroniques à coexister au niveau électromagnétique. Dans la pratique, c'est une tâche très complexe que de concevoir des produits compatibles. L'arme permettant de concevoir des produits bon-du-premier-coup est la modélisation. Cette thèse étudie l'utilité et la faisabilité de la modélisation de l'immunité des circuits intégrés (CI) au-delà de 1 GHz.

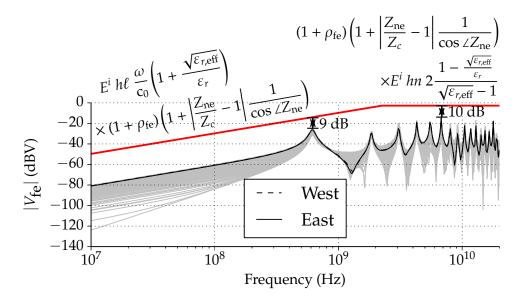

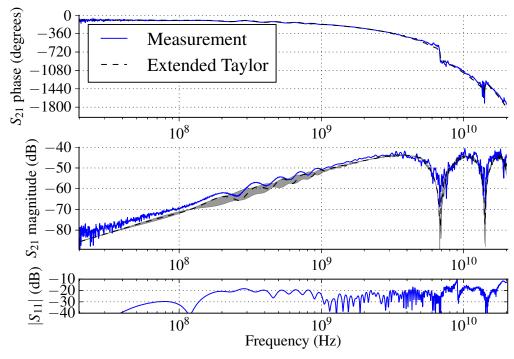

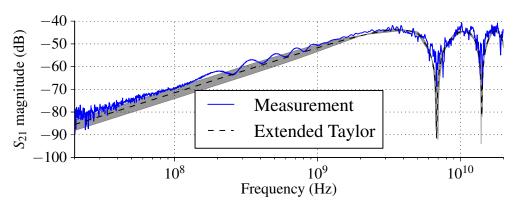

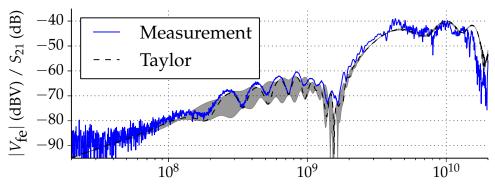

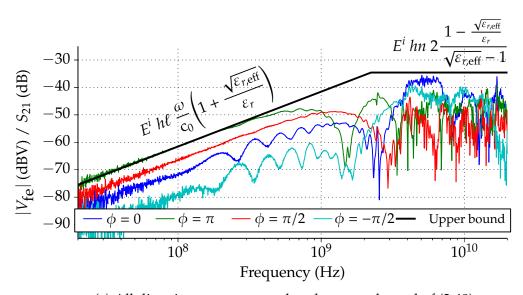

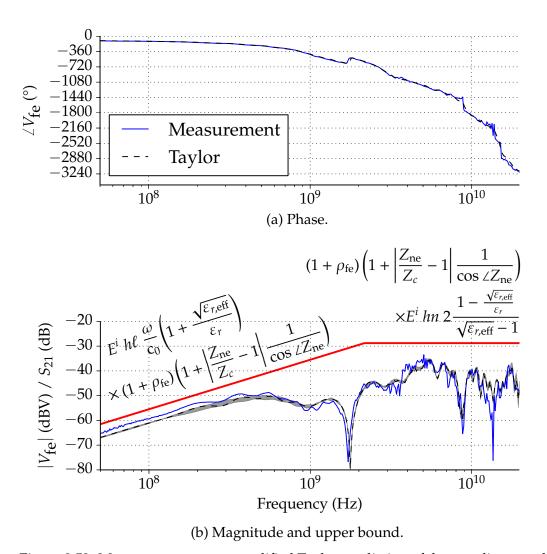

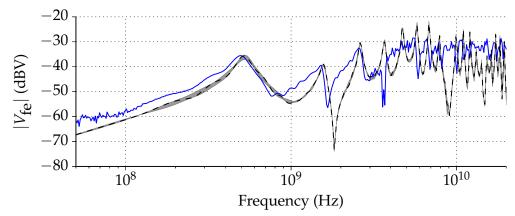

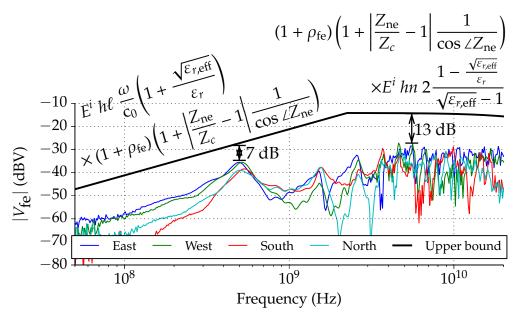

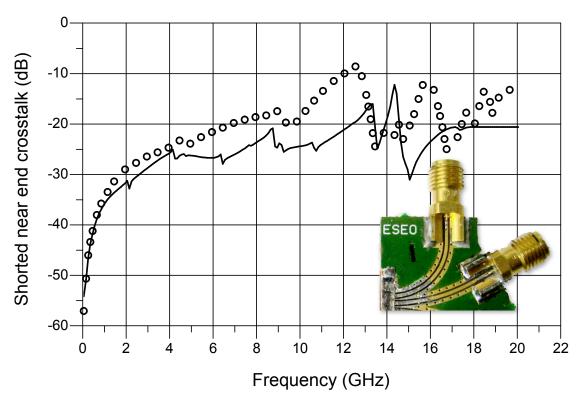

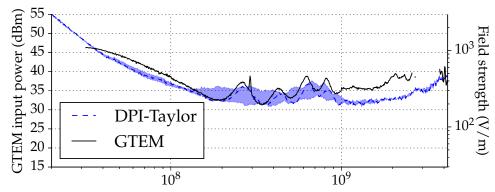

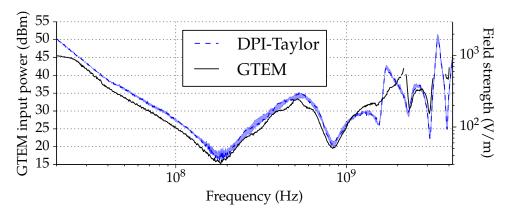

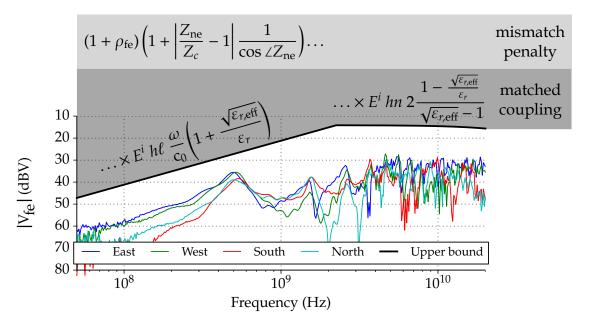

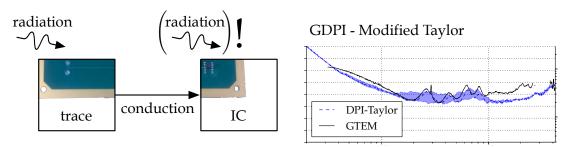

Si les pistes des circuits imprimés déterminent l'immunité rayonnée de ces circuits, il serait pertinent de pouvoir prévoir l'efficacité de couplage et de comprendre comment elle découle du routage des pistes. Les solveurs *full-wave* sont lents et ne contribuent pas à la compréhension. En conséquence, un modèle existant (la cellule de Taylor) est modifié de manière à ce que son temps de calcul soit divisé par 100. De plus, ce modèle modifié est capable de fournir une explication de la limite supérieure pour le couplage d'une onde plane, rasante et polarisée verticalement vers une piste de plusieurs segments, électriquement longue et avec des terminaisons arbitraires. Les résultats jusqu'à 20 GHz corrèlent avec des simulations full-wave à une erreur absolue moyenne de 2,6 dB près et avec des mesures en cellule GTEM (Gigahertz Transversale Electromagnétique) à une erreur absolue moyenne de 4,0 dB près.

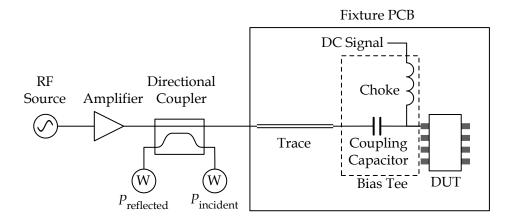

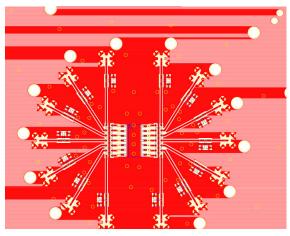

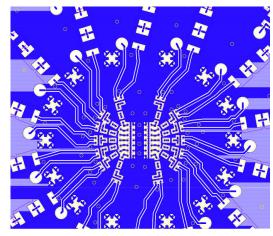

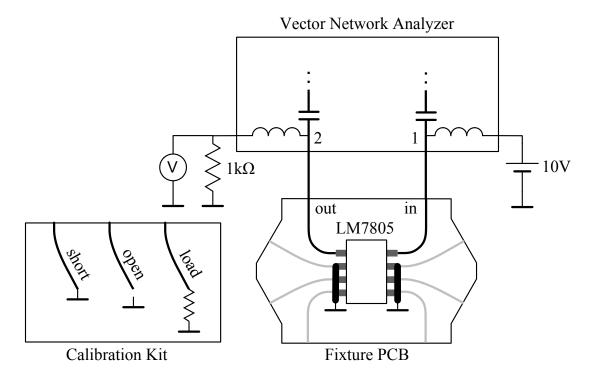

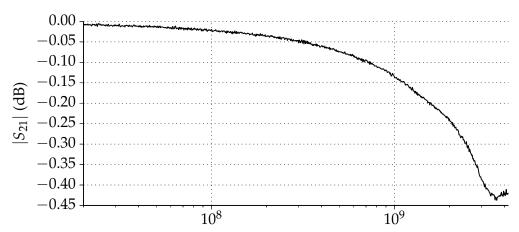

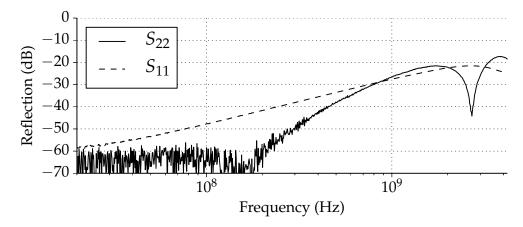

Si l'immunité conduite des CI est intéressante au-delà de 1 GHz, il faut une méthode de mesure, valable au-delà de 1 GHz. Actuellement, il n'y a pas de méthode normalisée, car la fréquence élevée fausse les observations faites avec la manipulation normalisée. Il est difficile de modéliser et de compenser le comportement de la manipulation normalisée. Par conséquent, une manipulation simplifiée et sa méthode d'extraction correspondante sont proposées, ainsi qu'une démonstration du principe de génération automatique de la carte d'essai utilisée dans la manipulation simplifiée. Pour illustrer la méthode simplifiée, l'immunité conduite d'un régulateur de tension LM7805 est mesurée jusqu'à 4,2 GHz.

A part la tendance générale des fréquences qui montent, il y a peu de preuve concrète qui étaye la pertinence de la modélisation de l'immunité conduite des CI audelà de 1 GHz. Une simulation *full-wave* suggère que jusqu'à 10 GHz, la plus grande partie de l'énergie rentre dans la puce à travers la piste. Par concaténation des modèles développés ci-dessus, l'immunité rayonnée d'une piste micro-ruban et d'un régulateur de tension LM7805 est prédite. Bien que ce modèle néglige l'immunité rayonnée du CI

lui-même, la prédiction corrèle avec des mesures en cellule GTEM à une erreur absolue de 2,1 dB en moyenne.

Ces expériences suggèrent que la plus grande partie du rayonnement entre dans un circuit imprimé à travers ses pistes, bien au-delà de 1 GHz. Dans ce cas, la modélisation de l'immunité conduite au-delà de 1 GHz serait utile. Par conséquent, l'extension jusqu'à 10 GHz de la méthode de mesure CEI 62132-4 devrait être considérée. De plus, la vitesse et la transparence du modèle de Taylor modifié pour le couplage champ-à-ligne permettent des innovations dans la conception assistée par l'ordinateur. La génération semi-automatique des cartes d'essais dites maigres pourrait faciliter l'extraction des modèles. Certaines questions critiques et importantes demeurent ouvertes.

Mots clefs : EMC, IC, immunité, couplage champ-à-piste, cellule de Taylor, DPI, ICIM-CI, mesure, modélisation, simulation, GHz

# Summary

ElectroMagnetic Compatibility (EMC) is the faculty of working devices to co-exist electromagnetically. In practice, it turns out to be very complex to create electromagnetically compatible devices. The weapon to succeed the complex challenge of creating First-Time-Right (FTR) compatible devices is modelling. This thesis investigates whether it makes sense to model the conducted immunity of Integrated Circuits (ICs) beyond 1 GHz and how to do that.

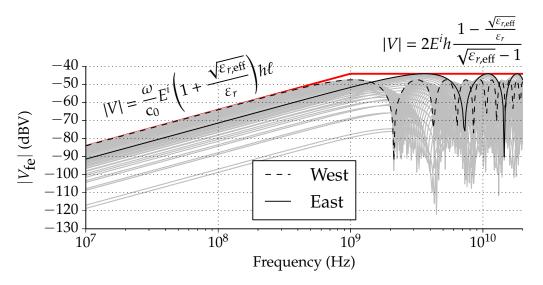

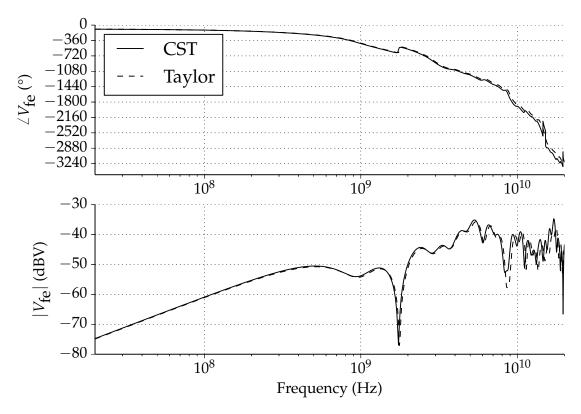

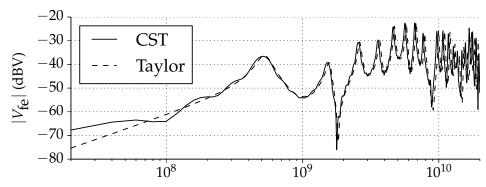

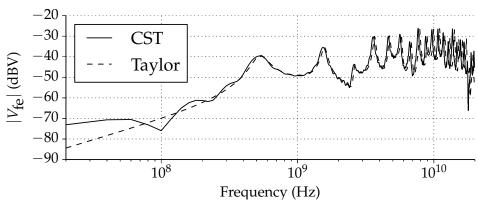

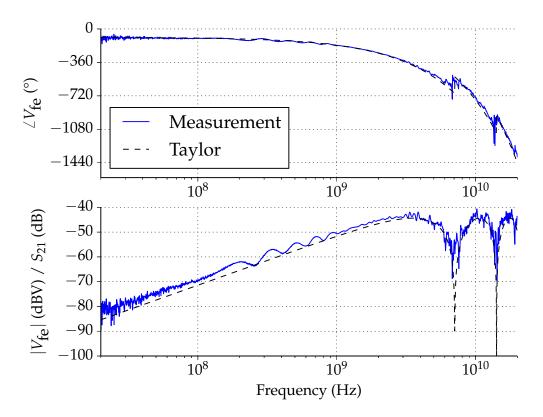

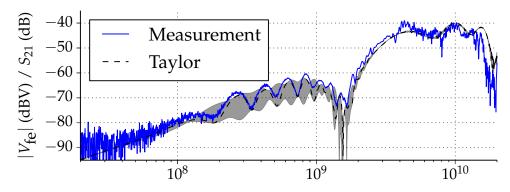

If the Printed Circuit Board (PCB) traces determine a PCB's radiated immunity, it is interesting to predict their coupling efficiency and to understand how that depends on the trace routing. Because full-wave solvers are slow and do not yield understanding, the existing Taylor cell model is modified to yield another 100× speedup and an insightful upper bound, for vertically polarised, grazing-incident plane wave illumination of electrically long, multi-segment traces with arbitrary terminal loads. The results up to 20 GHz match with full-wave simulations to within 2.6 dB average absolute error and with Gigahertz Transverse Electromagnetic-cell (GTEM-cell) measurements to within 4.0 dB average absolute error.

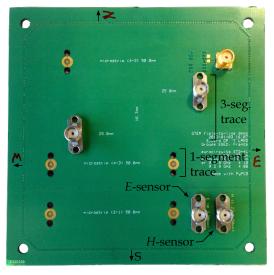

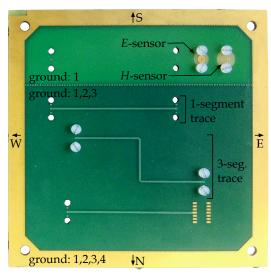

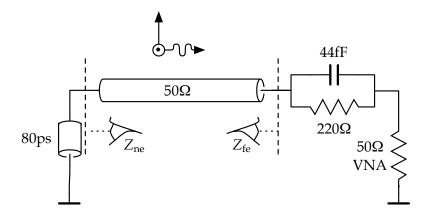

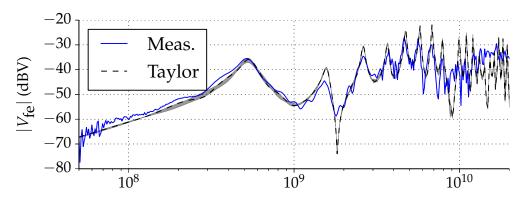

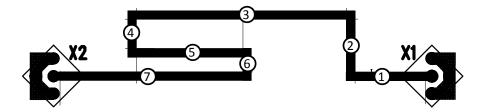

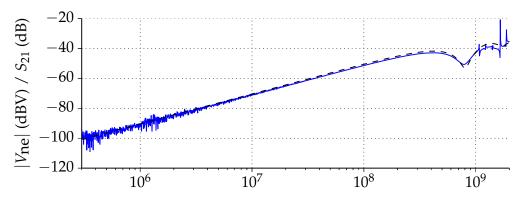

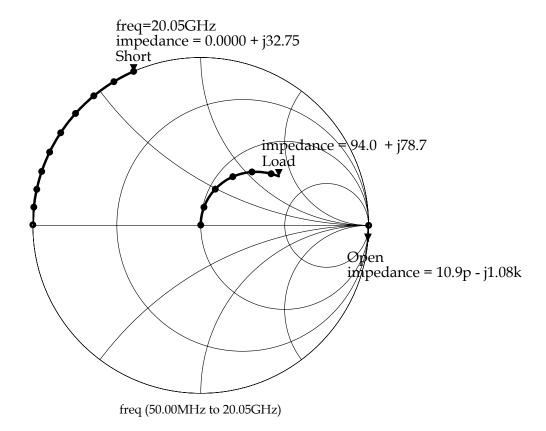

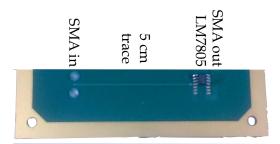

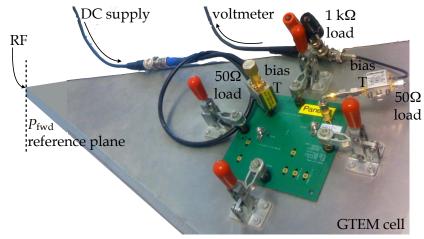

If the conducted immunity of ICs is interesting above 1 GHz, a measurement method is needed that is valid beyond 1 GHz. There is no standardised method yet, because with rising frequency, the common measurement set-up increasingly obscures the IC's immunity. An attempt to model and remove the set-up's impact on the measurement result proved difficult. Therefore, a simplified set-up and extraction method is proposed and a proof-of-concept of the automatic generation of the set-up's PCB is given. The conducted immunity of an LM7805 voltage regulator is measured up to 4.2 GHz to demonstrate the method.

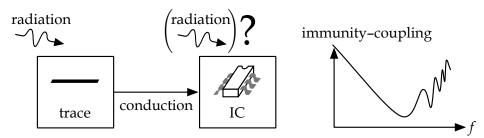

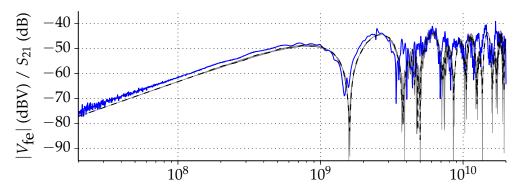

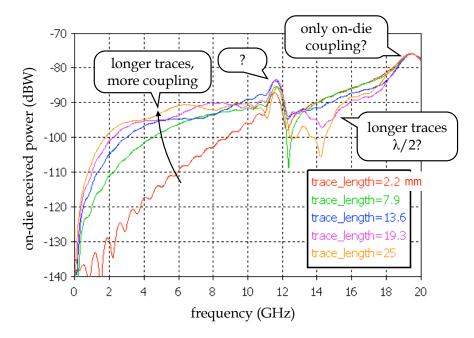

Except for a general trend of rising frequencies, there is only little concrete proof for the relevance of IC immunity modelling beyond 1 GHz. A full-wave simulation suggests that up to 10 GHz, most energy enters the die via the trace. Similarly, the radiated immunity of a microstrip trace and an LM7805 voltage regulator is predicted by concatenating the models developed above. Although this model neglects the radiated immunity of the IC itself, the prediction corresponds with GTEM-cell measurement to within 2.1 dB average absolute error.

These experiments suggest the most radiation enters a PCB via its traces, well beyond 1 GHz, hence it is useful to model the conducted immunity of ICs beyond 1 GHz. There-

iv Summary

fore, the extension of IEC 62132-4 to 10 GHz should be seriously considered. Moreover, the speed and transparency of the modified Taylor model for field-to-trace coupling open up new possibilities for computer-aided design. The semi-automatic generation of lean extraction PCB could facilitate model extraction. There are also critical remaining questions, remaining to be answered.

Keywords: EMC, IC, immunity, field-to-trace coupling, Taylor cell, DPI, ICIM-CI, measurement, modelling, simulation, GHz

# **Contents**

| Re | ésum  | é                                    | i   |

|----|-------|--------------------------------------|-----|

| Sı | ımma  | ary                                  | iii |

| C  | onten | ts                                   | v   |

| Co | onver | ntions                               | vii |

| 1  | Intr  | oduction                             | 1   |

|    | 1.1   | EMC                                  | 1   |

|    | 1.2   | Complexity                           | 2   |

|    | 1.3   | Industrial need                      | 7   |

|    | 1.4   | Research context                     | 9   |

|    | 1.5   | This thesis                          | 9   |

| 2  | Fiel  | d-to-trace Coupling                  | 13  |

|    | 2.1   | Introduction                         | 13  |

|    | 2.2   | State of the Art                     | 14  |

|    | 2.3   | Meshed Taylor Model                  | 18  |

|    | 2.4   | Modified Taylor Model                | 33  |

|    | 2.5   | Full-wave simulation                 | 54  |

|    | 2.6   | Measurement                          | 60  |

|    | 2.7   | Conclusions                          | 85  |

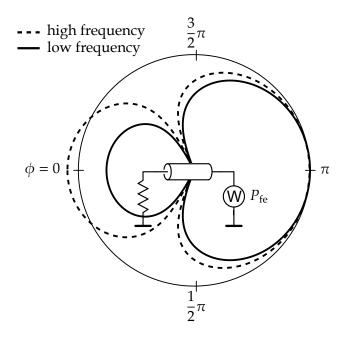

| 3  | IC (  | Conducted Immunity                   | 89  |

|    | 3.1   | Introduction                         | 89  |

|    | 3.2   | State of the Art                     | 90  |

|    | 3.3   | Modelling passive components         | 96  |

|    | 3.4   | Lean Method                          | 109 |

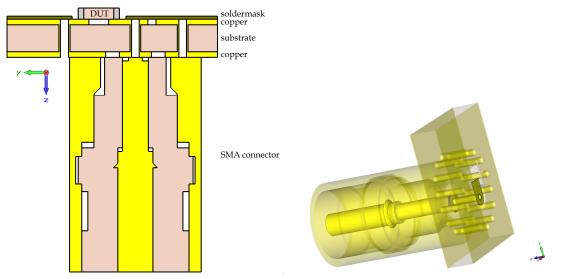

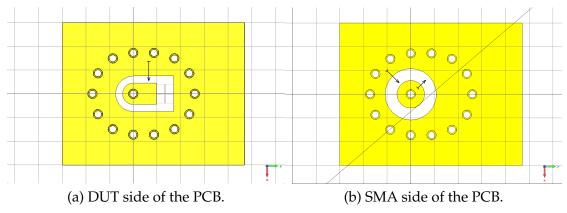

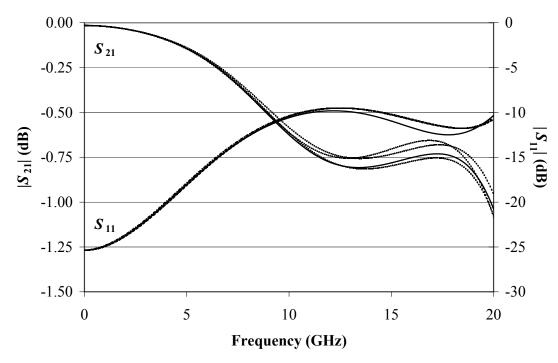

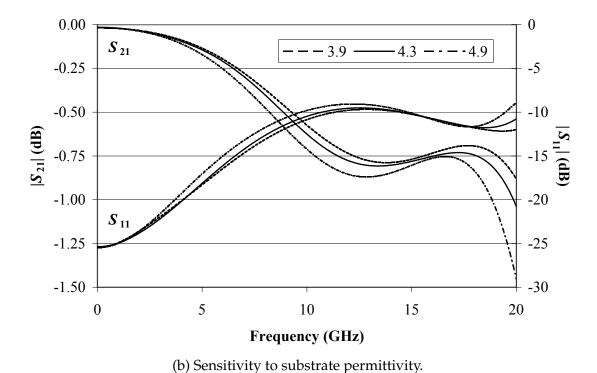

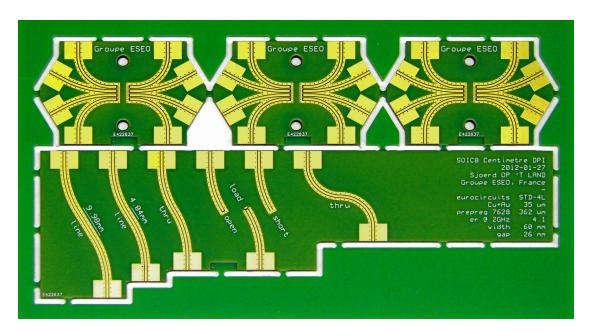

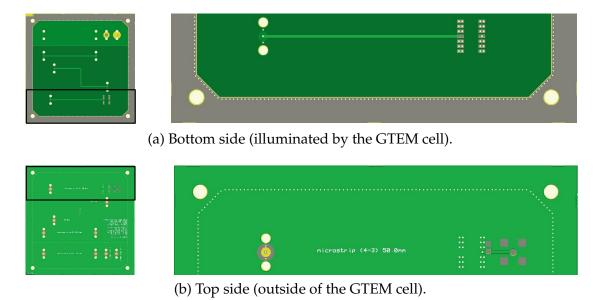

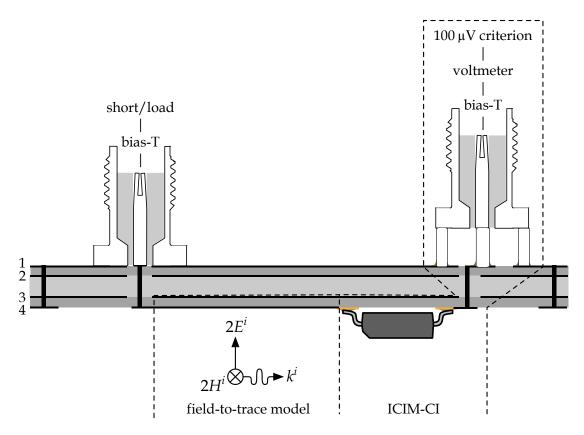

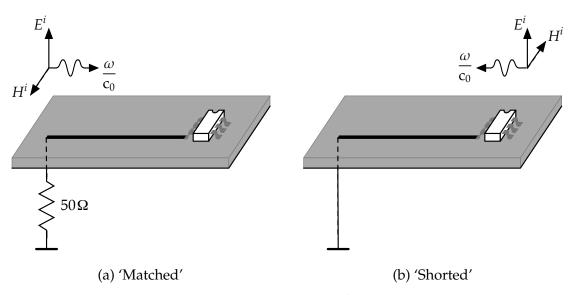

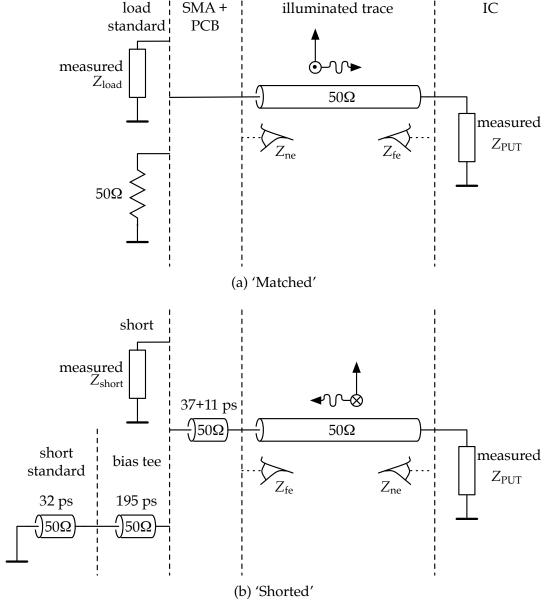

|    | 3.5   | Specialisation: SOIC8 Extraction PCB | 120 |

|    | 3.6   | Case study: LM7805                   | 131 |

|    | 3.7   | Conclusions                          | 140 |

vi *CONTENTS*

| 4  | PCB                   | Radiated Immunity                                   | 143 |  |  |

|----|-----------------------|-----------------------------------------------------|-----|--|--|

|    | 4.1                   | Introduction                                        | 143 |  |  |

|    | 4.2                   | State of the Art                                    | 144 |  |  |

|    | 4.3                   | Explorative Simulation                              | 145 |  |  |

|    | 4.4                   | Cascading Trace and IC Models                       | 148 |  |  |

|    | 4.5                   | Conclusions                                         | 161 |  |  |

| 5  | Con                   | clusion and Perspectives                            | 163 |  |  |

|    | 5.1                   | Introduction                                        | 163 |  |  |

|    | 5.2                   | Modified Taylor Model for Field-to-trace Coupling   | 163 |  |  |

|    | 5.3                   | Lean GDPI Method                                    | 167 |  |  |

|    | 5.4                   | ICIM-CI Beyond 1 GHz Considered Possible and Useful | 169 |  |  |

| Bi | bliog                 | raphy                                               | 173 |  |  |

| A  | Scientific Production |                                                     |     |  |  |

| A  | knov                  | vledgments                                          | 185 |  |  |

| Al | Abbreviations         |                                                     |     |  |  |

| D  | efiniti               | ions                                                | 195 |  |  |

# **Conventions**

**Units.** *Système Internationale* (SI) units, as opposed to Gaussian and imperial units, are employed, unless otherwise noted.

All decibel values, dimensional or dimensionless, are prefixed with their sign, so all excess pluses or minuses are operators [1].

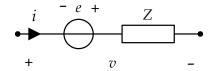

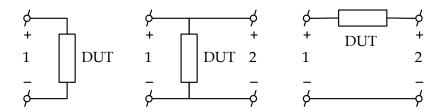

**Passivity.** The passive sign convention is used as shown in Figure 1.

**Responsibility.** When reading about the responsibility of anything but a person, this should of course be understood as a metaphor; it facilitates the explanation of cause and effect. In the end, only something with freedom of choice can be accountable. If anyone, these are human beings [2, p. 165ff.].

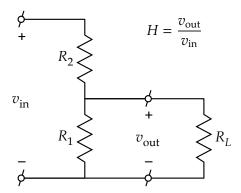

Figure 1: Passive sign convention for voltage and current: a positive product vi means that net power p is dissipated in the element.

viii Conventions

## Symbols.

B magnetic field in T

H magnetic field in Am<sup>-1</sup>

E electric field in Vm<sup>-1</sup>

ε The permittivity ε relates the displacement of charges D in a linear and homogeneous material with the electric field E as follows:

$$De^{j\omega t} \equiv \varepsilon_0 \varepsilon_r E e^{j\omega t}, \tag{1}$$

where the relative permittivity  $\varepsilon_r$  is a second rank tensor in general, which reduces to a scalar for isotropic materials. Conventionally, the real and imaginary parts are denoted as follows:

$$\varepsilon_r = \varepsilon_r' - j\varepsilon_r''. \tag{2}$$

Under above sign conventions,  $\varepsilon'_r$  quantifies the energy storage in the material and  $\varepsilon''_r$  quantifies the loss.

**=** minus for the near end and plus for the far end

c per unit length (pul) capacitance in Fm<sup>-1</sup>

*l* pul inductance in Hm<sup>-1</sup>

g pul conductanse in Sm<sup>-1</sup>

r pul resistance in  $\Omega$ m<sup>-1</sup>

$\ell$  total trace length in m

$\ell_u$  length of uth trace segment in m

$c_0$  the speed of light in m/s, supposedly a constant

p position parallel to the (first) trace segment in m

t position transversal to the (first) trace segment in m

*n* position normal to the (first) trace segment in m

$\phi$  azimuth

$\theta$  elevation

$Z_c$  characteristic impedance

CHAPTER 1

# Introduction

**Abstract.** ElectroMagnetic Compatibility (EMC) is the faculty of working devices to co-exist electromagnetically. In practice, it turns out to be very complex to create electromagnetically compatible devices. The weapon to succeed the complex challenge of creating First-Time-Right (FTR) compatible devices is modelling. In the context of worldwide Gigahertz Direct Power Injection (GDPI) research and the French SEISME project, this thesis investigates whether it makes sense to model the conducted immunity of ICs beyond 1 GHz and how to do that.

## 1.1 EMC

Problems due to electromagnetic interaction between devices range from funny to lethal. For example, a rusty microwave oven could trigger Mazda, Mitsubishi and Toyoto car alarms. For another example, a New Jersey TV transmitter set off baby monitors at nearby intensive care. Annoyed by the many false alarms, the nurses started to ignore the alarms, killing an estimated 6 babies [3].

For public health and safety, governments require devices to be compliant with EMC standards. For example, the Federal Communications Commission (FCC) essentially requires that 'no harmful interference is caused and that interference must be accepted (...)' by devices on the US market [4]. In Europe, manufacturers are trusted to distinguish and perform relevant EMC testing before labeling their products with a CE-marking.

Manufacturers may also be intrinsically motivated to deliver compatible products. Negatively, the fear for reputation damage pushes internal standards. Positively, manufacturers that strive for excellence will also take EMC into account.

Very often, EMC problems can be understood in terms of this directed graph of electromagnetic energy propagation:

$$aggressor \longrightarrow coupling path \longrightarrow victim. \tag{1.1}$$

For example, the New Jersey TV transmitter could be considered the aggressor, the baby monitor cabling the coupling path and the nurse's control panel the victim.

In this view, the problem could for example be solved by (1) reducing the TV transmitter power, by (2) shielding the cable, by (3) applying an input filter at the control panel or a combination of solutions.

The graph can be simplified by merging the coupling path into the victim:

$$aggressor \longrightarrow victim, \tag{1.2}$$

and we can say "the aggressor's *emissions* and the victim's *susceptibility* cause a problem".

In this view, proposed solution (1) is called a reduction of emissions, whereas solu-

In this view, proposed solution (1) is called a reduction of emissions, whereas solution (2) and (3) is called a reduction of susceptibility (or an increase of *immunity*). Notice that there are also cases where the system boundaries are less obvious.

Sometimes the electromagnetic energy is completely guided along the coupling path, for example from an IC power supply pin, along a PCB trace to an analog input pin of another IC. This problem is entirely *conducted*: the conducted emission of the first IC and the conducted susceptibility of the second IC cause a problem.

In all other cases, the coupling path contains free space propagation, for example in the mentioned New Jersey case. The unshielded cable acts as an antenna and converts *radiated* electromagnetic waves to conducted voltage/current waves. This way, the radiated emission of the TV transmitter and the conducted immunity of the control panel cause a problem.

In this paradigm, the EMC of any device can be quantified by its radiated emission and immunity. Devices that have interfaces along which guided electromagnetic energy can leave and enter, also have conducted emission and immunity. The EMC of ICs, for instance, can be quantified on all four aspects, as they have metallic pins.

Notice that the boundary between guided and free space energy is not always clear. For example, the Bulk Current Injection (BCI) method induces (guided) currents by a magnetic field (in free space). Therefore, it has been considered both a conducted and a radiated test method.

## 1.2 Complexity

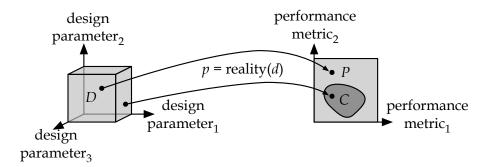

Designing a device that is electromagnetically compatible or modifying a device to become so is engineering. That is, solving a problem, given a number of degrees of freedom: the *design parameters* (e.g. resistor value, trace length or circuit topology). These design parameters span the design space *D*, which contains every possible design. The

1.2. COMPLEXITY 3

Figure 1.1: Reality maps design space into performance space. One successful design and one unsuccessful design are shown.

problem is solved when the performance of the design complies with the requirements, expressed in terms of performance metrics (e.g. immunity, speed, bandwidth, cost or development time). These performance metrics span the performance space P, of which compliance C is a subspace (e.g. immunity meets or exceeds DO-160F and development time is shorter than one month). Reality determines the performance of each design candidate, reality :  $D \rightarrow P$ . To successfully design is to find a design d, of which the performance p is compliant with the requirements: any  $d \in D$ , such that reality  $(d) \in C$ , as shown in Figure 1.1.

We believe the relevant reality to depend on a small number of deterministic physical laws: those of Newton<sup>1</sup>, Maxwell<sup>2</sup> and that of thermodynamics, for example. They can be summed up like so

$$U = (F - ma)^{2} + (\nabla \cdot D - \rho)^{2} + \dots + (TdS - PdV - dE)^{2}$$

(1.3)

and the behaviour of all matter can be described by this universal equation<sup>3</sup>

$$U = 0. (1.4)$$

The next step is to apply the universal equation to the design parameters and to solve for the performance metrics in order to obtain the reality function. Finally, the reality function needs to be inverted to find a compliant design d from a performance  $p \in C$ .

Except for the proverbial 'spherical cow in vacuum' [5], this is unfortunately never possible. The dimension of design space is generally high and reality is too hard to understand, let alone analytically invertible.

One practical alternative is physical simulation. For a given design d, a (multi-) physics simulator can calculate the performance p. Using trial-and-error, the design

<sup>&</sup>lt;sup>1</sup>Sir Isaac Newton (1643-1727)

<sup>&</sup>lt;sup>2</sup>James Clerc Maxwell (1831-1879)

<sup>&</sup>lt;sup>3</sup>I stole this idea of a useless universal equation from an author that I forgot.

parameters d can be tuned to make the design compliant. The advantage of physical simulation is that it is relatively easy to set-up. The downside is that it is generally time-consuming and it yields little insight. Moreover, the physical simulation of industrial products is often impossible, because the exact constitution of components is secret. Even if these details were available, simulation time would explode: a car of  $10^0$  m consisting of ICs with  $10^{-7}$  m details would require a hexahedral mesh in the order of  $10^{7\times7\times7}$  cells. Even when applying multi-scale meshing techniques to reduce the number of mesh cells, the simulation will remain time-consuming.

Another practical alternative is experimentation. The advantage with respect to simulation is that results may be obtained rather quickly, once the set-up is made. However, creating prototypes, setting up measurements and using rare instruments, like an anechoic chamber, is not free. Similarly to simulation, no fundamental insight is obtained by experimenting with complex systems.

It can be concluded that analysis and simulation of the physical laws, as well as experimentation on complex systems do not yield fundamental insight in the relation between design parameters and performance.

Therefore, simplified views on reality are always applied: *models*. Modeling is designoriented *approximation*: reality is approximated to become easily invertible. For example, the resistive voltage divider of Figure 1.2 is required to have a voltage transfer H = 1/3, when loaded by an unknown load  $R_L > 10 \,\mathrm{k}\Omega$ . The real relation between design parameters ( $R_1$  and  $R_2$ ) and the performance metric (H) is given by

$$H = \frac{R_1 /\!/ R_L}{R_1 /\!/ R_L + R_2} = \frac{R_1 R_L}{R_1 R_2 + R_1 R_L + R_2 R_L}.$$

(1.5)

Suppose that  $R_L$  and  $R_1$  ( $R_2$ ) would be given, it is not obvious to find  $R_2$  ( $R_1$ ). The equation is true, but one cannot 'see through' it, the relation is *opaque*.<sup>4</sup>

Conversely, when  $R_1$  is chosen much smaller than  $R_L$ , the transfer becomes approximately:

$$H \approx \frac{R_1}{R_1 + R_2} \to \frac{R_2}{R_1} \approx \frac{1}{H} - 1,$$

(1.6)

and  $R_2$  follows naturally. Moreover, one sees directly that only the ratio between  $R_1$  and  $R_2$  is fixed by H. Hence, the relation is considered *transparent*.

To summarize, the relation between design parameters and performance metrics can become more transparent by approximation. The price paid is reduction in accuracy and in validity domain (above approximation only holds for  $R_1 \ll R_L$ ).

Note that transparency is subjective: experienced engineers will also see through (1.5). However, even these subjects will consider (1.6) more transparent than (1.5). Therefore, relative transparency is objective.

<sup>&</sup>lt;sup>4</sup>Dr. Middlebrook calls this an *high-entropy* equation, useless in Design-Oriented Analysis (D-OA).

1.2. COMPLEXITY 5

Figure 1.2: Resistive voltage divider with resistive load.

There are general modeling techniques, that are not specific to EMC (although EMC examples will be given).

One modeling technique is *hierarchical segmentation*: a system topology is chosen, for which the system performance is known as function of the performances of its constituants (e.g. a cascade of blocks has a gain that amounts to the product of the gains of the blocks). Next, a successful set of sub-system performances is chosen (e.g. a link budget is distributed). Now, for each sub-system, the requirements are known, and the engineer can try to design them one by one, and simplify again if necessary.

A related technique is the *weak coupling* assumption. That is, although all interactions are really bilateral, only a one-way interaction is taken into account. In the New Jersey example cited on page 1, a TV transmitter induces a cable current, which in turn will reradiate and be received by the TV transmitter, which will slightly modify its operating point, which will in turn..., and so forth. Fortunately, the cable's re-radiation received by the TV transmitter is so weak, that it can be neglected. Only the action of the TV transmitter on the cable needs to be considered to explain the harmful interference. Indeed, when speaking about emission and immunity, weak coupling is implicitly assumed.

Another simplification is to only look at the *worst case*. For example, if decreasing the distance between aggressor and victim makes everything worse, it suffices to prove that there is no harmful interference at the smallest required distance. Instead of having to prove EMC for all distances, we only need to prove it for one particular distance (the worst case). A variant is to consider the *typical case* and base conclusions on a statistic or probabilistic mean.

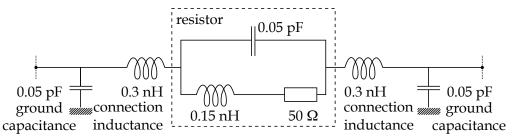

Intelligent use of phenomenological, descriptive or *black-box models* enables the construction of transparent models. For example, to design a circuit, it might suffice to know the constant ratio between the voltage across the terminals of a resistor and current through it (its resistance). That way, the resistor's material and dimensions do not clutter the circuit model. However, with rising frequency, a parallel capacitance depending on the pad distance becomes necessary to sufficiently model the resistor's

behaviour. Notice that this pad-distance-dependent resistor model is grey-box: it offers one more level of explanation, and then resorts to description again. Models with more than one level of explanation are called *white-box model*. Intelligence is needed to discern whether or not the validity domain of the black-box model matches its application.

There are also modelling techniques specific to electromagnetics or to EMC.

If structures are small with respect to the wavelength of propagating waves, electromagnetic waves can be supposed to propagate infinitely fast. That is, although the field is changing with time (not temporally uniform), fields (hence, voltages and currents) can be considered spatially uniform. Electro- and magnetostatic analysis may be applied to obtain lumped-element capacitances and inductances. This is called the *quasi-static approximation*.

If guided waves need to be considered, and the waveguide is homogeneous, uniform and has an infinitely small cross-section with respect to the wavelength, only the fundamental Transversal ElectroMagnetic (TEM) mode needs to be considered. As few real waveguides are homogeneous, no real waveguide is uniform (that would require infinite length) and all real waveguides have finite cross-section, a Quasi-TEM (QTEM) wave is said to propagate on them.

Finally, emission and susceptibility are often characterised in terms of the *far field magnitude*. In general, an aggressor can generate any spatiotemporal field that satisfies the Maxwell equations. Hence, it needs to be described as  $\vec{E}(\vec{r},t)$  or  $\vec{H}(\vec{r},t)$ . At some distance from the aggressor, however, the field tends to a plane wave with the wave impedance of the vacuum. Assuming susceptibility to be independent of the relative phase of the field's spectral components, it can be described with the magnitude vector of its Fourier transform:  $|\vec{E}(\vec{r},\omega)|$ . Assuming a linearly polarised wave, the field only decays with the distance  $\vec{r}$ . Now, the vector  $|\vec{E}(\omega)|$  at a rough distance suffices to describe the emissivity of a system. Reciprocally, the susceptibility of a system can be described in terms of a maximum allowed electric field magnitude vector.

Using these and other modelling techniques, the reality function can become invertible: the engineer then knows what knob (design parameter) to turn in which direction to improve performance.

Modelling is an art: if a model is too complicated, it does not yield the wanted insight or it is too expensive to use (tools, training, measurement and simulation time). If a model is too simple, it does not sufficiently describe the reality, so it does not yield the needed insight either. Breedveld calls a model that strikes the right balance for a given problem a competent model. Another way to put it: the Return On Modelling Effort (ROME) should be maximum.

7

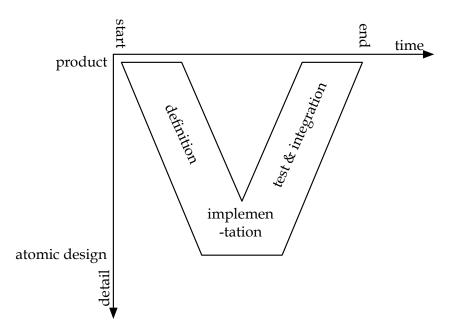

Figure 1.3: V-model for systems engineering.

#### 1.3 Industrial need

For an industrial product, EMC is only one of the performance metrics. Moreover, the total engineering task is distributed over multiple persons. One way of distributing the task is by the hierarchical segmentation mentioned on page 5. A classical way to map this method on time is by means of the V-model sketched in Figure 1.3 [6]. In this paradigm, EMC needs to be taken into account in each phase: definition, implementation and test.

In the definition phase, the product requirements are propagated down the product hierarchy. For example, law may require an electric car to meet the CISPR 12 limits on radiated emissions. Knowing that these emissions will mainly emanate from the electric motor and from the back-to-front cable, requirements can then be imposed on the motor and on the cabling. That way, the cabling designers and motor designers can both be given requirements, with confidence that the combination cable-motor will perform sufficiently when integrated. Generally, more understanding is needed on how subsystem EMC performance 'adds up' to system EMC performance.

In the implementation phase, the subsystem requirements should lead to produceable subsystems. There, the influence of detailed design decisions on subsystem performance is needed. For example, is this filter capacitor needed to pass the BCI test, imposed as subsystem requirement? Or: this IC seems to perform better in DPI, but it is  $\leqslant 0.02$  more expensive than another. Does the former IC cost outweigh the risk of not passing the BCI test? Generally and again, more understanding is needed as

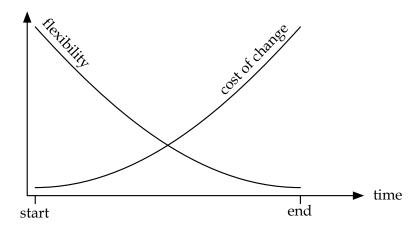

Figure 1.4: Flexibility and consequent cost of change along product design time.

to how component EMC performance 'adds up' to subsystem (PCB, assembly) EMC performance.

In the test and integration phase, the subsystems are assembled, performing the predefined tests at each hierarchical level. For example, after checking that the cable and the motor each do not radiate more than required, the combination battery-cable-motor is tested. If the latter test passes, too, the combination is mounted in an empty chassis to verify that the vehicle does not radiate more than required because of the cable and motor. Finally, the complete car prototype's radiated emissions are measured to make sure that the car is road legal. Standardised tests exist at all detail levels, but the main challenge remains to understand why a test failed in order to remove the root cause.

While the complete, feasible product crystallises along all these phases, there is less and less flexibility in the design. Consequently, the cost of a hypothetical change is high, as illustrated in Figure 1.4. For example, the car radio and Global Positioning System (GPS) receiver are discovered to interfere in a very late integration test. It would have been easy to place them apart early on, but now that the injection molds are already made, the only solution is to shield the GPS receiver stage. Therefore, although few details are available in the early design, the earlier tools can orient the design, the better.

The masterpiece of EMC engineering is to produce a product prototype that is First-Time-Right (FTR). This is currently only a dream, because commonly, multiple product prototypes are needed before reaching compliance.

9

## 1.4 Research context

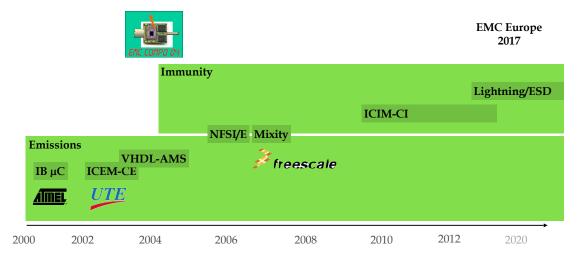

Around the world, thousands of people are trying to advance EMC in various ways: on different hierarchical levels (from vehicle to transistor), with different beneficiaries (from a company to the general public) and with different modelling techniques (as outlined before). The topic, beneficiaries and methodology of this thesis are partly determined by the context in which it was prepared: on the crossroads of the French project SEISME and the worldwide GDPI research, in the ESEO-EMC laboratory.

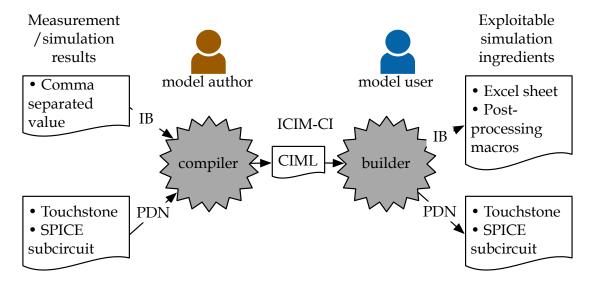

Simulation de l'Emission et de l'Immunité des Systèmes et des Modules Electroniques (SEISME) or Simulation of Emission and Immunity of Electronic Systems and Modules is a project labeled by Aerospace Valley, performed from 2010 to 2014 for the French Ministry of Defence. It financially federates research to lower the cost of EMC, by enabling virtual prototyping of new and modified electronic systems [7]. Indeed, the modification of systems is a recurring problem in aerospace industry, because of the obsolescence of components occurring before that of long-lived airplanes. For example, replacing just one IC by its successor in an airplane necessitates another qualification of the entire airplane. Instead, it would be a great cost saving to be able to reliably simulate the effect of replacing the IC on the EMC performance of the airplane. To that end, the SEISME project comprises work at all hierarchical levels (IC, PCB, rack and vehicle). This thesis is co-financed by the fifth SEISME work package: 'Modelling Methodology Development for EMC'. As a result, the beneficiary of this thesis is the general public.

Simultaneously, worldwide research on the EMC of ICs is going on. In 2009, Ramdani et al. predicted that measurement methods for conducted immunity of ICs in the 3 – 10 GHz range would be in industrial use around 2010, and modelling techniques around 2015 [8]. An informal collaboration on the measurement method was led by Etienne Sicard, with participants in France (ESEO, INSA Toulouse), in Spain (*Universitat Polytècnica de Catalunya* (UPC)) and in Taiwan (Bureau of Standards, Metrology & Inspection (BSMI)). Formerly called eXtended DPI (X-DPI), it was later given a more ontological name: Gigahertz Direct Power Injection (GDPI).

The author performed the research in the ESEO-EMC laboratory (formerly GRACE), part of *Institut d'Électronique et de Télécommunications de Rennes* (IETR), Mixed Research Unit (UMR) National Centre for Scientific Research (CNRS) 6164. Since 2000, Ecole Superieure d'Electronique de l'Ouest (ESEO) performs research on EMC in collaboration with industrial partners, as outlined in Figure 1.5. ESEO-EMC has experience in black-, gray- and white-box IC modelling for EMC, but is only autonomous in black-box modelling. For gray- and white-box modelling, close collaboration with semiconductor foundries is needed. This context favoured black-box modelling.

## 1.5 This thesis

Formulated as falsifiable main hypothesis, this thesis states that

Figure 1.5: Research topics, partnerships and events of ESEO-EMC.

it is useful and possible to model the conducted immunity of ICs beyond 1 GHz.

In Popper's<sup>5</sup> tradition of falsification and the more recent Test Driven Development (TDD), the goal of this thesis is to render the main hypothesis falsifiable by making our underpinning repeatable for anyone with an electronic or microwave background.

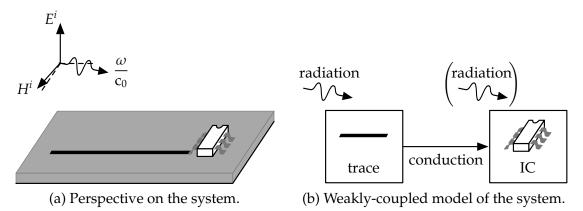

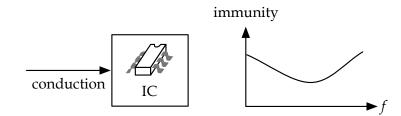

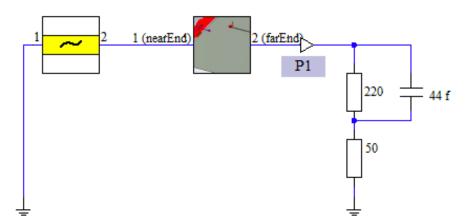

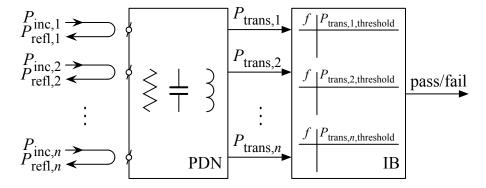

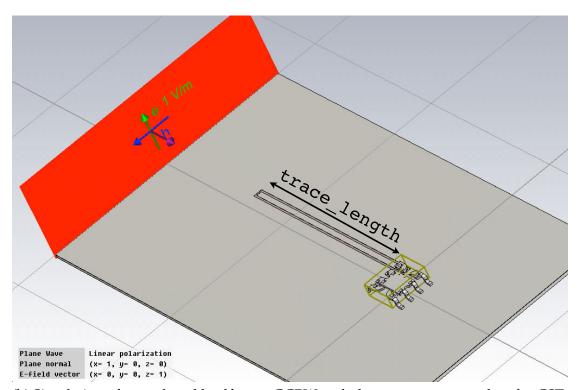

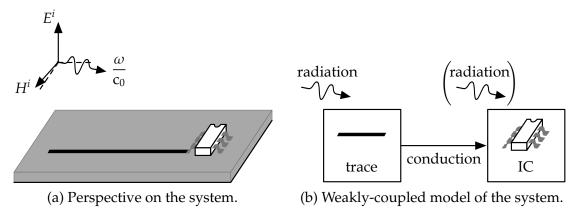

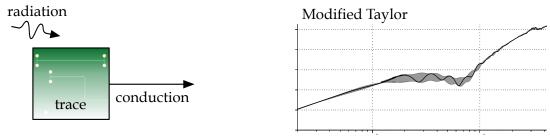

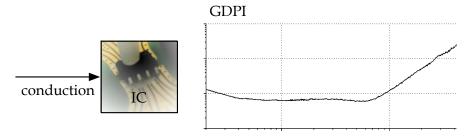

Modeling the IC's conducted immunity is *useful* if it is necessary for a competent model of the system's radiated immunity. This thesis will consider the common system of a microstrip PCB trace leading to an IC, as shown in Figure 1.6a. A weakly-coupled model of the system's immunity is given in Figure 1.6b: the incoming radiation illuminates both trace and IC, and electromagnetic energy is also conducted from the trace to the IC. If the IC suffers much more from the radiation picked up by the trace, than from the radiation picked up by the IC itself, the radiated immunity of the IC can be neglected. This is the *dominant-conduction* hypothesis:

in a typical trace-IC system, the IC is predominantly disturbed by the radiation gathered by the trace and conducted into the IC until above 1 GHz.

If the dominant-conduction hypothesis is true, modeling the conducted immunity of ICs beyond 1 GHz is useful.

Modeling the IC's conducted immunity beyond 1 GHz can be proved *possible* by doing it once.

This thesis is structured as shown in Figure 1.7. In Chapter 2, a model for field-to-trace coupling will be developed that remains transparent for high frequencies. In Chapter 3, a method for black-box-modeling of the conducted immunity of an IC beyond 1 GHz

<sup>&</sup>lt;sup>5</sup>Sir Karl Raimund Popper (1902–1996)

1.5. THIS THESIS

Figure 1.6: Illumination of the system: a trace connected to an IC.

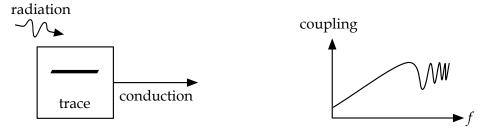

will be developed, which proves that it is *possible*. These two models will then be cascaded and compared to measurement in Chapter 4. If the latter cascade (which neglects the IC's radiated immunity) correlates well with measurement, this underpins the dominant-conduction hypothesis, i.e. that the exercise is *useful*. Overall conclusions and perspectives on future research will be given in Chapter 5. In each chapter, previous work on that topic will be reviewed.

(a) Chapter 2 models and measures field-to-trace coupling.

(b) Chapter 3 models IC conducted immunity from measurement.

(c) Chapter 4 models and measures PCB radiated immunity by concatenating Chapter 2 and 3.

Figure 1.7: Structure of this thesis.

CHAPTER 2

# Field-to-trace Coupling

**Abstract.** If the PCB traces determine a PCB's radiated immunity, it is interesting to predict their coupling efficiency and to understand how that depends on the trace routing. Because full-wave solvers are slow and do not yield understanding, a faster, existing circuit model is employed. This model is modified to yield another 100× speedup and an insightful upper bound, for vertically polarised, grazing-incident plane wave illumination of electrically long, multi-segment traces with arbitrary terminal loads. The results up to 20 GHz match with full-wave simulations to within 2.6 dB average absolute error and with GTEM-cell measurements to within 4.0 dB average absolute error.

## 2.1 Introduction

How much radiated electromagnetic energy is captured by typical PCB traces? What trace illumination induces the worst case? What are the design parameters that have significant effect on the worst-case coupling?

In practice, radiated electromagnetic energy can arrive in all sort of forms on a PCB trace. It can come from nearby aggressors, like neighbouring traces (*crosstalk*) or cabling. In that case, the full structure of the electric or magnetic field needs to be taken into account. Moreover, as the aggressor is close, the weak-coupling assumption might not hold. On the other hand, the disturbing energy can come from far-away aggressors, like a TV transmitter or Intentional ElectroMagnetic Interference (IEMI). In that case, the far-field and weak-coupling assumptions may be applied, as explained in section 1.2. In the sequel, a far-field, weakly coupled and linearly polarised source will be assumed.

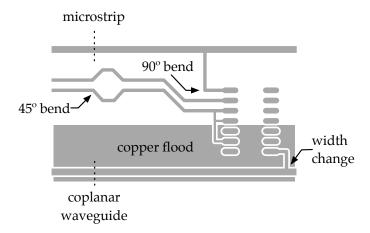

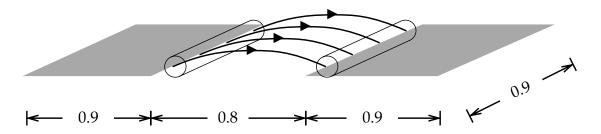

As illustrated in Figure 2.1, typical PCB traces meander with 90° and 45° bends. Width changes and none-chamfered bends occur, introducing impedance discontinuities. On typical 2-layer PCBs, traces can be considered as MicroStrip (MS) lines above

Figure 2.1: Example copper artwork of a typical PCB. Geometrical features that might need modelling are indicated.

a ground plane. On multi-layer PCBs, copper floods to the left and right of a trace make for a CoPlanar Waveguide (CPW) or Grounded CoPlanar Wave-guide (GCPW) if a ground plane is present. In the sequel, meandered MS traces of constant characteristic impedance will be considered, unless mentioned otherwise.

As most circuits are designed to function with node voltages and mesh currents (as opposed to travelling waves), we are interested in trace terminal voltages or currents. Knowing the terminal impedances, the terminal voltage can be converted into the terminal current and vice versa. Because of the author's taste for node analysis, the terminal voltages will be sought, but this really is an arbitrary choice. To simplify, only the case of a trace with exactly two terminals will be considered, unless stated otherwise.

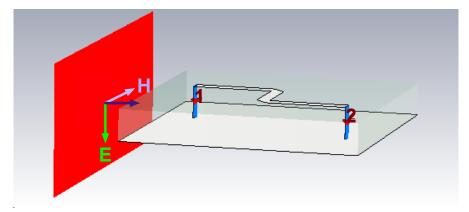

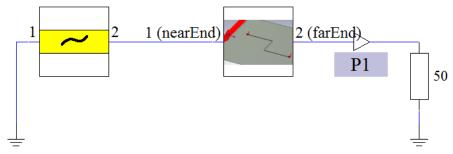

The state of the art will be reviewed in section 2.2. One existing model (Taylor's) will be applied with novel meshing in section 2.3. Although fast, this model is opaque, and therefore, a transparent model will be developed in section 2.4. To challenge both models, full-wave simulations will be performed in section 2.5 and measurements in section 2.6. A concluding overview of the developed models will be given in section 2.7.

#### 2.2 State of the Art

The quest for field-induced voltages at the terminals of general lines is not new. The published models until 2014 will be reviewed, going from physical but opaque to transparent but simplistic.

A versatile solution is to enter the entire aggressor and victim into a full-wave multiphysics solver with circuit co-simulation (e.g. CST Design Studio or COMSOL Multiphysics), thus including both geometry and electronics. The advantage is that quite many physical effects can be taken into account. Take for example a PCB that heats up, expands, thereby creating a resonating slit in its shielding enclosure, of which the emissions are captured by another PCB's trace and finally rectified to an interfering frequency by an ESD protection network. When all of the geometry and the circuit is precisely entered into the simulation, it is possible to predict this kind of phenomena.

However, it takes a lot of time to precisely enter the geometry and circuit into a simulation. Competent models of electronics are not free, if they are available at all. On top of that, very detailed multi-domain simulations necessitate significant calculation time. In the above example, the simulation must run for a sufficient time to reveal the thermally induced deformation with electromagnetic and then electronic consequences.

Moreover, this method yields little insight. For example, in practice, the aggressor PCB is not always installed in the same position in its enclosure. Does this matter? Did our simulation give the worst case result? Is it worth the extra cost to improve the mechanical fixation of the aggressor in its enclosure? Does it help to reduce the victim trace length? These kind of questions can only be answered by time-consuming parameter sweeps. Even then, sweeping the entire design space is impossible, so *cocktail-effects* (results of a particular mix of causes) might never be detected.

Over and above that, this approach yields very specific results. For example, the EMC of the victim PCB can be demonstrated for one specific aggressor, but in practice there is an infinity of potential aggressors. What can be generally concluded about the victim's immunity? Therefore, the first step towards genericity is splitting aggressor and victim, which requires the weak coupling assumption to hold.

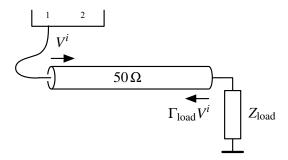

Under the weak coupling assumption, immutable electromagnetic energy impinges on PCB traces and causes induced terminal voltages – and the analysis stops there. A common means to understand the behaviour of PCB traces is transmission line theory: the supposition that there be only a differential transverse electromagnetic mode (TEM).

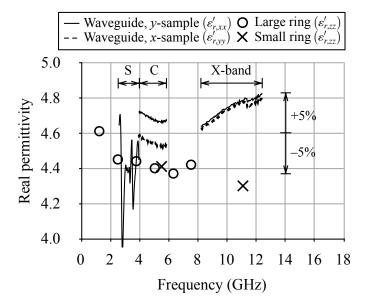

The common mode is negligible, because the ground planes of modern PCBs suppress it and because the common mode response across the terminals is generally small [9, 10]. A typical microstrip line gradually becomes multimodal above this cut-off frequency [11]:

$$f_{\text{MS,TEM}} = \frac{21.3 \times 10^6}{(w+2t)\sqrt{\varepsilon_r + 1}} = \frac{21.3 \times 10^6}{(1.0 \times 10^{-3} + 2 \cdot 1.6 \times 10^{-3})\sqrt{4.6 + 1}} = 2.3 \,\text{GHz}, \quad (2.1)$$

where trace width w and substrate thickness t represent a relatively large trace on a two-layer FR4 substrate (permittivity  $\varepsilon_r = 4.6$ ), employing *Système Internationale* (SI) units. With PCBs that have an increasing number of layers (decreasing t) and an increasing trace density (decreasing w), this cut-off frequency is only increasing (a 50  $\Omega$  microstrip on a four-layer substrate becomes multimodal from about 8.7 GHz upwards). It can be concluded that, while checking these validity limitations, PCB traces can be considered as transmission lines up to several GHz.

For example, using coupled transmission lines, Mandić predicted the coupling between a Transversal ElectroMagnetic (TEM) cell septum and PCB traces [12] with the Method of Lines (MoL) and a circuit simulator. His model is not transparent, because it uses a circuit simulator. Neither is it intrinsically generic, because the TEM cell geometry is entered in detail, whereas it is supposed to represent a general aggressor. Finally, Mandić' model is not weakly coupled, because it also predicts the effect of the trace on the TEM cell.

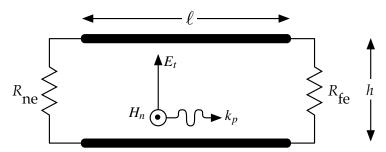

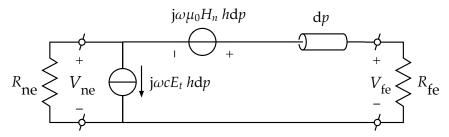

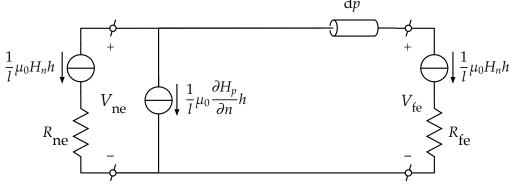

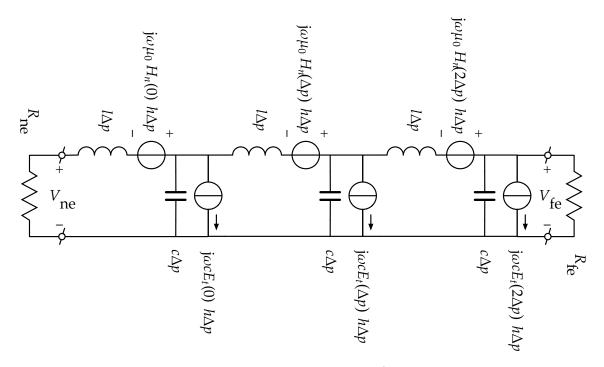

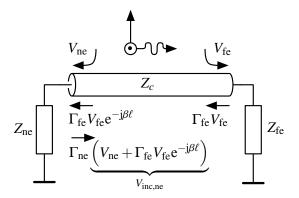

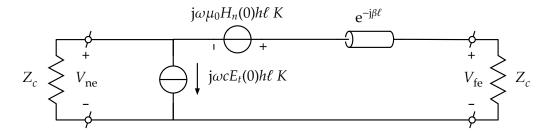

There are three weakly coupled transmission line based models [9, 13]: that of Taylor et al. [14], Agrawal et al. [15] and that of Rachidi [16]. They all model a transmission line as a cascade of *cells*. Each cell models a line slice that experiences a uniform field along its length dp. A bifilar (two-wire) transmission line and its one-cell models are depicted in Figure 2.2 for the case of uniform field between both wires (along t). As can be seen, the passive slice of transmission line dp is enriched with one or two distributed sources representing the field induction. In the case of Agrawal's and Rachidi's model, additional sources are needed at both terminals. As the wavelength along the line decreases, the line needs to be considered as a cascade of short enough cells, such that the field is uniform enough along each cell. From two cells upward, the terminal voltage expressions are no longer transparent.

Paul extended Agrawal's model to multi-conductor transmission lines [17, §12.2]. He showed that the coupling distributed on the line can be lumped into a voltage and a current source at only one terminal by means of convolution. Moreover, he elaborated the case of a lossless multi-conductor transmission line in a homogeneous medium, illuminated by a plane wave.

However, in the case of a PCB trace, the medium is non-homogeneous. Bernardi and Cichetti studied the case of arbitrary incident plane wave illumination of a microstrip with arbitrary loads [18]. Unfortunately, their result is opaque and only allows for numerical simulation.<sup>1</sup>

Leone, on the contrary, found transparent expressions for the same case, using Agrawal's model, the Baum-Liu-Tesche (BLT) equation [20] and Snell's law of refraction [19]. He then simplifies by assuming that both loads be matched, which he showed to be a reasonable approximation for moderately mismatched loads. Secondly, the transient excitation should be essentially low-frequency, which is reasonable for Nuclear ElectroMagnetic Pulse (NEMP) testing. From his model, he concludes that end-fire (parallel with the line), vertically-polarised illumination induced the worst case voltage at the near-end terminal.

Indeed, a simple expression for the worst case incidence and trace are useful for testing and design, respectively. Lagos built a numerical algorithm around Leone's model to find the worst case incidence with known load impedances [21]. Although this algorithm could serve to falsify analytical models, it does not prove anything general, nor is it transparent. Magdowski derived analytical expressions from Agrawal's formulation

<sup>&</sup>lt;sup>1</sup>Or, as Leone puts it, "general, but very lengthy equations" [19].

(a) Bifilar line geometry. p, n and t denote the Cartesian coordinates parallel, normal and transversal to the line. The 'ne' and 'fe' indices denote near-end and far-end, respectively.

(b) One-cell electrical model of Taylor et al.

(c) One-cell electrical model of Agrawal et al.

(d) One-cell electrical model of Rachidi.

Figure 2.2: Three equivalent weakly coupled field-to-line coupling models.

for the typical case, that is: for random incidence [22]. However, as it was derived using computer algebra tools, it does not necessarily contribute to the understanding of the coupling mechanism, nor does it simply reveal what trace geometry constitutes the worst case.

A last, extreme simplification is the quasi-static approximation. It lets waves propagate infinitely fast:  $c_0 \to \infty$ , which is representative for structures that are sufficiently small with respect to the wavelength. With susceptibility tests up to 18 GHz, free-space wavelength descends to 1.7 cm, while PCB traces may be tens of centimetres in length. Therefore, this approximation is too simplistic for high-frequency predictions. However, it may be useful to obtain a low-frequency limit.

To summarise, physical simulation is too costly and yields little insight on field-to-trace coupling. The transmission line approximation seems reasonable and yields insight on field-to-trace coupling (notably through the work of Leone), although not for high frequencies and/or extremely mismatched loads. The quasi-static approximation is too simplistic for practical traces, but yields insight and provides a low-frequency limit.

## 2.3 Meshed Taylor Model

The most obvious application of Taylor's model for a non-uniform incident field, is to mesh (slice) the line in short enough *cells*, in order for the field to become approximately uniform to each cell.

To demonstrate the Taylor model, a simple microstrip case study will first be drawn up. Then, it will be translated to a bifilar equivalent to match with the Taylor cell of Figure 2.2b. That way, it will be possible to mesh it manually under ADS, which will turn out to be time-consuming and error-prone. Therefore, it will be meshed using Kron's formalism, first on paper and then automatically. Finally, frequency-adaptive meshing will be tried out, which is novel for 1D circuit simulation.

## Case study

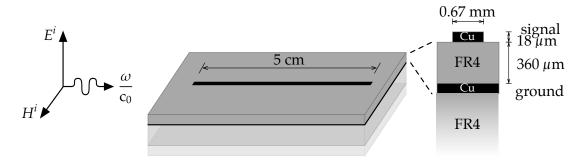

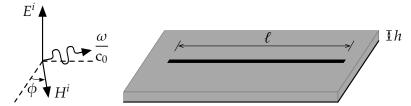

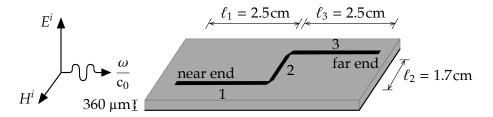

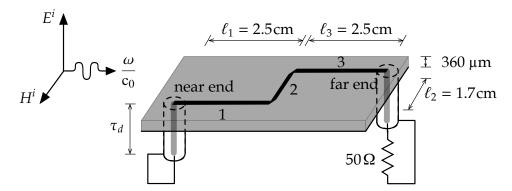

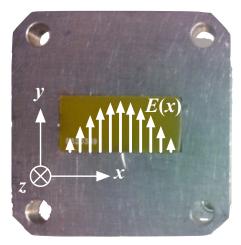

A rather simple case study will now be defined to evaluate the various models by simulation and measurement. However, more realistic PCB traces should be kept in mind when concluding on their performance.

Microstrips, i.e. traces above a ground plane are widely used. Moreover, with respect to CPWs and striplines, they are good antennas and therefore prone to create immunity problems. Hence, a microstrip will be taken as case study.

Operational and harmonic frequencies of electronics keep rising, so the wavelengths keep falling. For example, the Wireless Home Digital Interface (WHDI) uses a 5 GHz

Figure 2.3: Microstrip of 5 cm length, illuminated by a grazing-incident, vertically polarised, end-fire excitation.

carrier, or a 3 cm wavelength in typical substrate. Back-up radars may use ultra-wideband signals up to 24 GHz, or down to 1.25 cm. PCBs still have sizes in that order of magnitude, so long-line effects can be expected. Therefore, a 5 cm trace, illuminated with a frequency up to 20 GHz is chosen.

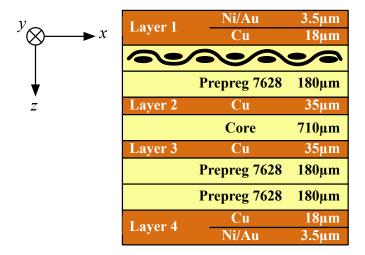

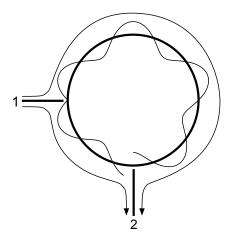

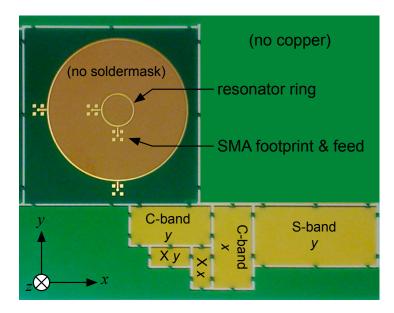

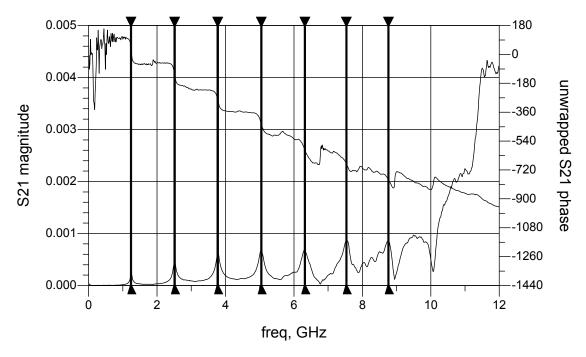

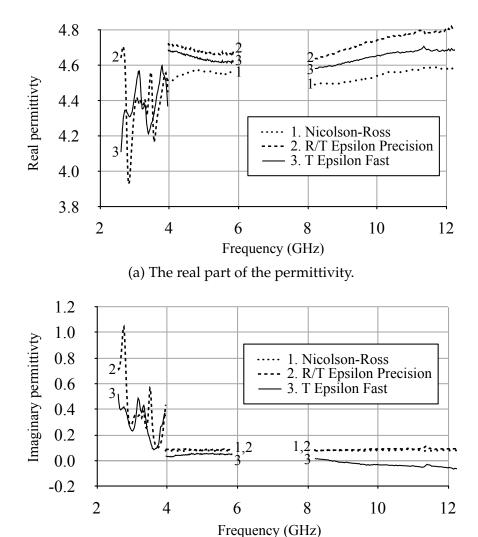

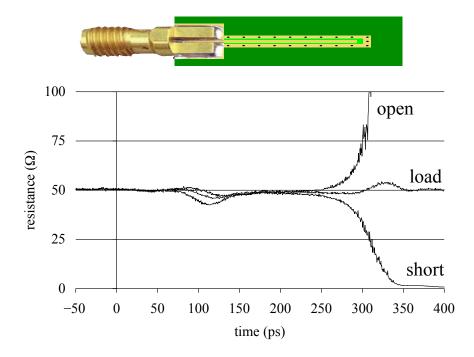

In practice, traces are never characteristically terminated, because the terminating ICs and passives have frequency dependent impedances. Neither are real-world traces uniform, because of width changes and unmitered (unchamfered) bends. Existing microwave theory could be employed to incorporate these non-idealities in simulation, whereas we would like to focus on modelling of field-to-trace coupling. Therefore, a uniform trace that is characteristically terminated will be studied. To facilitate measurement, the characteristic impedance is chosen to be  $50\,\Omega$ . A common substrate is chosen: FR4, which has a relative permittivity  $\varepsilon_r$  of about 4.6 . For an outer layer microstrip on a typical four-layer stack-up, the substrate is 360  $\mu$ m thick [23]. Typical traces are mostly covered by solder mask, hence only consist of unplated 18  $\mu$ m copper [23].

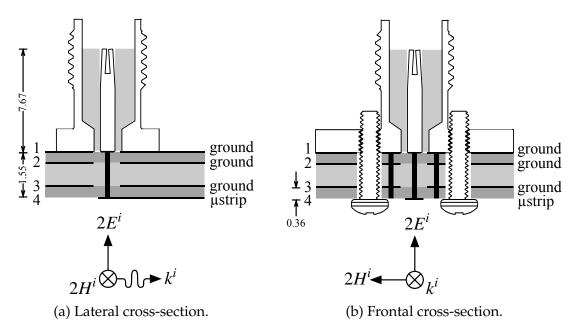

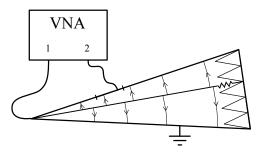

Finally, an illumination must be chosen. For low frequencies, the worst case (end-fire excitation) is grazing-incident [19]. Moreover, Gigahertz Transverse ElectroMagnetic (GTEM) cell measurements emulate a grazing-incident plane wave, by integrating a PCB in the waveguide wall. Finally, grazing-incident illumination will turn out to be easy to analyse. Therefore, a grazing incident, vertically polarised plane wave illumination is chosen. This case study is summarised in Figure 2.3. The remainder of this thesis will be restricted to grazing incidence, which is a considerable limitation.

The field strength  $E^i$  will be chosen to be representative of that generated by a standard GTEM cell, in order to allow for comparison with measurement. Because of linearity, this choice induces no loss of generality.

## Bifilar Microstrip Equivalent

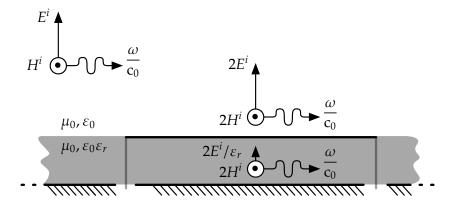

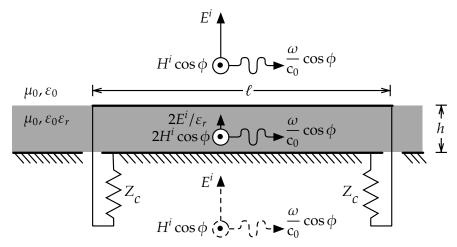

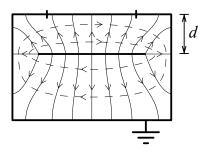

The essential difference between a bifilar line and a microstrip is the presence of a ground plane and a substrate.

The ground plane doubles the field strength  $E^i$ . This can be understood from the case of a Hertzian dipole, placed just above the np-plane, infinitely far from the origin, in an otherwise empty universe, such that the field  $E_t$  is 1 V/m at the origin. If a ground plane is now placed at the np-plane, there will be no field anymore under the np-plane and the field above it will have doubled. In the special case of a GTEM-cell, this free space field  $2E^i$  equals 23.7 V/m for 1 V at the GTEM input. That way, the induced voltages can be numerically interpreted as voltage transfers. More details about the GTEM-cell's electromagnetic field and the measurement set-up will be given in section 2.6.

As for the dielectric substrate, the plane wave just above it is imposed. Since the field in the substrate must follow with a constant phase lag, the wavenumber k in the dielectric is equal to that in free space. Moreover, the material is not magnetic, hence the magnetic field H in the substrate is  $2H^i$ . Considering the substrate as part of an infinitely broad parallel-plate voltage divider, the electric field E in the substrate turns out to be  $2E^i/\varepsilon_r$ .

In summary, the bifilar-equivalent grazing-incident illumination of a microstrip causes the following plane wave in the substrate:

$$H = 2H^i (2.2)$$

$$E = 2E^i/\varepsilon_r \tag{2.3}$$

$$k = \frac{\omega}{\mathsf{c}_0} \,, \tag{2.4}$$

as illustrated in Figure 2.4.

## Manual meshing

Now that the bifilar equivalent of the illuminated microstrip is known, the field-induced terminal voltages can be predicted using discrete Taylor's cell and a circuit simulator. Recall that a discrete Taylor's cell consists of a slice of passive transmission line  $\Delta p$ , enriched with sources representing the effect of an incident electromagnetic field (cf. Figure 2.2b).

The slice of passive transmission line  $\Delta p$  can be modeled with a telegrapher's cell, which lumps the distributed or per unit length (pul) resistance, conductance, inductance and capacitance into discrete elements  $r\Delta p$ ,  $g\Delta p$ ,  $l\Delta p$  and  $c\Delta p$ , respectively. The copper and dielectric losses are represented by the dissipative elements  $r\Delta p$  and  $g\Delta p$ , respectively. A line can be modeled as lossless or lossy by omitting or including these dissipative elements. For example, a lossless model of a line of length  $\ell$  meshed in three cells is depicted in Figure 2.5.

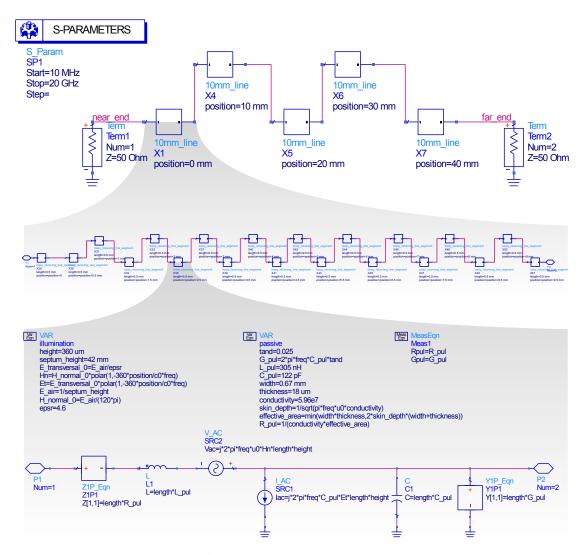

Practically, the 50-mm case study was entered in Agilent's Advanced Design System (ADS). To that end, a mesh size should be decided upon. As the case study goes up to 20 GHz, the free-space wavelength descends to 15 mm. Supposing a velocity factor of 2/3, the wavelength in substrate thus descends to 10 mm. Without further

Figure 2.4: The far-away plane wave source (top left) is reflected by the microstrip's ground plane (image source at the bottom left). This results in the fields shown at the right.

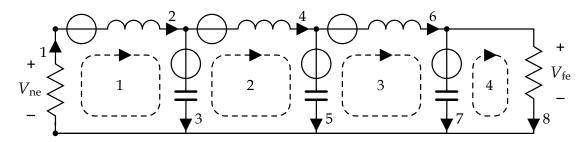

understanding of a problem, the line should be meshed to a small fraction of the wavelength. To be safe,  $\lambda/20$  was chosen, or 0.5 mm. To avoid placing 100 ADS cells, a 10mm\_line cell is defined, that contains 20 0.5-mm Taylor cells. The 50-mm line is then modeled by placing 5 10mm\_line cells, as shown in Figure 2.6.

In order to simulate the passive, 50-mm microstrip, values need to be entered for c, l, g and r. To that end, ADS LineCalc was used, which is based on the models of Hammerstad and Jensen [24], Wheeler [25] and Kirschning and Jansen [26]. From the case study definition, the length  $\ell=50\,\mathrm{mm}$ , the characteristic impedance  $Z_c=50\,\Omega$ , the substrate height  $h=360\,\mu\mathrm{m}$ , the copper thickness  $t=18\,\mu\mathrm{m}$ , copper conductivity  $\sigma=5.96\times10^{-7}\,\mathrm{S/m}$  and the relative permittivity  $\varepsilon_r=4.6$  were entered. A typical loss tangent of  $\tan\delta=0.025$  at 1 GHz [27, Table 3.3] and a typical copper roughness for outer layer copper of  $1.6\,\mu\mathrm{m_{rms}}$  [28] were supposed. LineCalc calculated the width w of this line to be  $0.67\,\mathrm{mm}$  and the effective permittivity  $\varepsilon_{r,\mathrm{eff}}=3.34$  and produced an MSUB two-port, allowing to simulate the microstrip behaviour.

From LineCalc's effective permittivity, the pul capacitance *c* was calculated:

$$Z_c = \frac{1}{cv} = \frac{\sqrt{\varepsilon_{r,\text{eff}}}}{cc_0} \Longrightarrow c = \frac{\sqrt{\varepsilon_{r,\text{eff}}}}{Z_c c_0} = \frac{\sqrt{3.34}}{50 \cdot 3 \times 10^8} \approx 122 \,\text{pF/m},$$

(2.5)

where v is the phase speed in substrate. From this result the pul inductance l was

Figure 2.5: Transmission line meshed in three cells ( $\Delta p = \frac{1}{3}\ell$ ). The passive transmission line is modeled as lossless, with l and c being the per-unit-length inductance and capacitance, respectively.

calculated:

$$Z_c = \sqrt{\frac{l}{c}} \Longrightarrow l = Z_c^2 \cdot c = 50^2 \cdot 122 \times 10^{-12} \approx 305 \,\text{nH/m}.$$

(2.6)

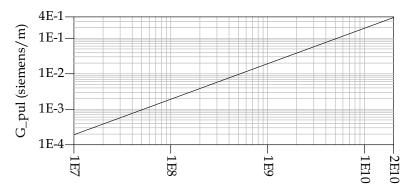

According to the simplest model, the pul conductance g is linearly dependent on frequency, supposing a frequency-independent loss tangent tan  $\delta$  [27]:

$$g = \omega c \tan \delta,$$

(2.7)

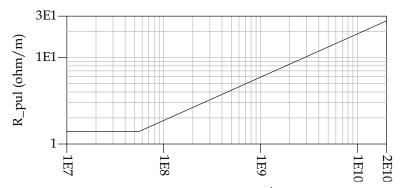

which is plotted in Figure 2.7a. Finally, the pul resistivity r is simply the resistance of the effective cross-section  $A_{\text{eff}}$ :

$$r = \frac{1}{\sigma A_{\text{eff}}},\tag{2.8}$$

where the effective cross-section is the apparent trace cross-section for low frequencies, but limited by the skin depth  $\delta_s$  for increasing frequency [10]:

$$A_{\text{eff}} = \min\left(wt, 2\delta_s\left(w + t\right)\right) \tag{2.9}$$

$$\delta_s = \frac{1}{\sqrt{\pi f \mu_0 \sigma}}. (2.10)$$

23

Figure 2.6: Implementation of the meshed transmission line under ADS as a chain of parametrised cells. The 50-mm line is meshed into 100 cells of 0.5 mm.

The resulting r is plotted in Figure 2.7b. Notice how these c, l, g and r pul parameters are implemented in the passive VAR block in the ADS cell at the bottom of Figure 2.6.

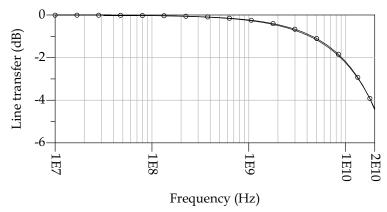

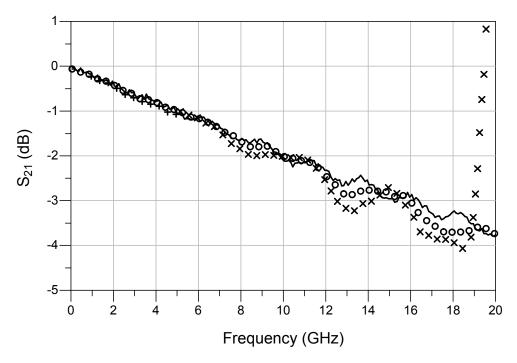

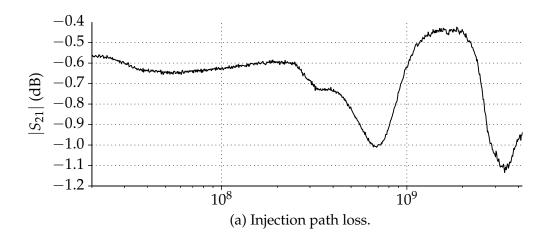

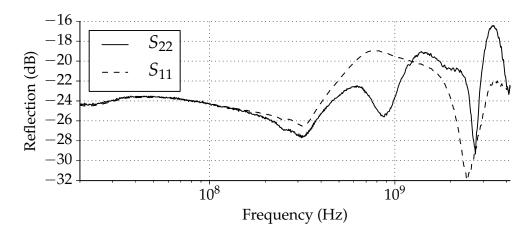

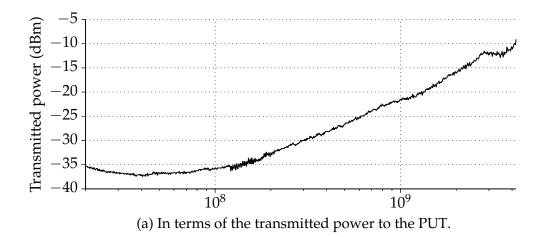

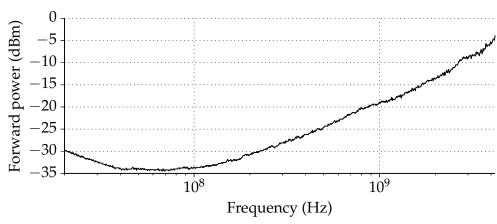

In order to gauge the accuracy of this simple clgr model, the S-parameter simulation of Figure 2.6 was run and compared to the S-parameters of ADS behavioural MSUB model. The either-end return loss  $-S_{11}$  and  $-S_{22}$  of the clgr model (not plotted) was very high for low frequencies and never descended under 20 dB up to 20 GHz, which indicates good matching. The transfer phase  $\angle S_{21}$  of the clgr and the MSUB model correspond to within 2° (not plotted). The line's transfer magnitude  $|S_{21}|$  according to the clgr and the MSUB correspond very well, as can be seen in Figure 2.7c.

Now that the passive *clgr* elements are checked to constitute a competent model of a passive transmission line, the active elements representing the field-to-trace coupling can be added: voltage and current sources representing magnetic and electric induction, respectively.

Contrary to the *clgr* elements, their values depend on the relative position to the plane wave origin. To that end, each cell takes a position parameter and calculates the local field accordingly. This is done in the ADS cell at the bottom of Figure 2.6, in the VAR illumination block of equations.

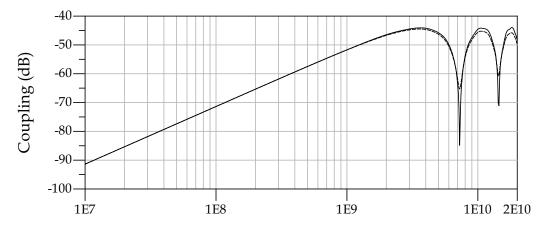

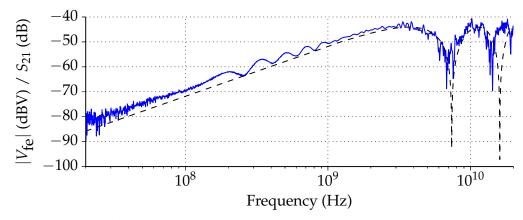

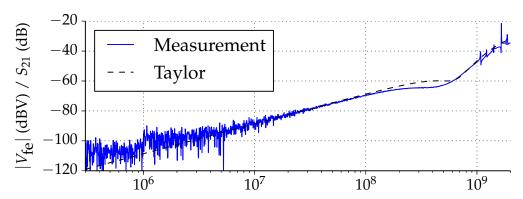

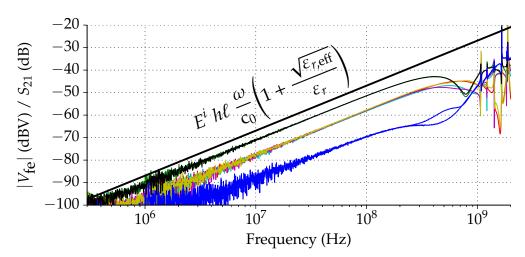

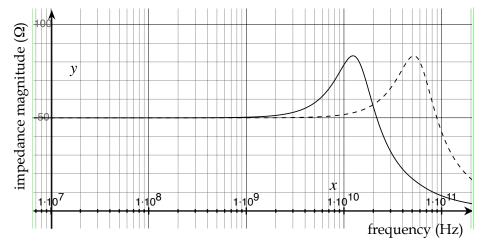

Now, an AC simulation can be run. In contrast to the *S*-parameter simulation, the distributed sources will be activated and thus simulate the effect of the illumination defined in the case study. The simulation was run for the far end, with and without the *rg* elements modeling the line's losses. The results are presented in Figure 2.8.

The *plateau* and null frequencies look like resonances, but this transmission line is not in resonance: both ends are characteristically terminated. Therefore, the relation between the 'resonance' frequencies and the geometrical dimensions is not simple. An attempt to explain the phenomenon will be made in section 2.4.

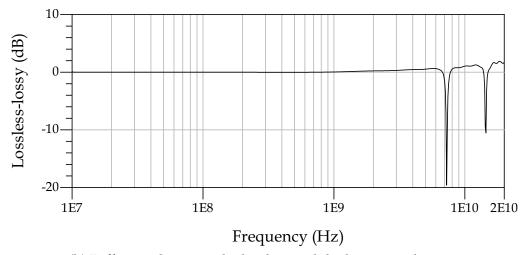

As can be seen from Figure 2.8b, the lossless model slightly overestimates the coupling when the coupling is high, as could be expected. The lossless model underestimates the coupling, however, when it's low. Because EMC problems are most likely to occur when the coupling is high, the lossless model could here safely have been used for design purposes. Therefore and unless otherwise noted, lossless models will be studied in the sequel of this thesis.

It be noted that either-end loads are matched to the trace in this case study, which never occurs in industrial practice. Intuitively, it may be expected that a lossless model also overestimates the field-to-trace coupling in a mismatched case. If that is the case, this lossless model may safely be used in an industrial case. It can also be expected that the bigger the mismatch, the larger the error induced by using a lossless model.<sup>2</sup> A large, pessimistic error will result in expensive over-designing. At any rate, as can be seen above, a lossless model sometimes underestimates coupling, so the lossless model

<sup>&</sup>lt;sup>2</sup>Consider the case of a lossless trace either-end terminated in an open circuit. A lossless model will then predict infinite terminal voltages, although in reality they will be finite because of the trace's losses.

(a) The  $\omega c \tan \delta$  dielectric conductance (notice the unitary slope).

(b) The copper resistance, dominated by the  $\propto \sqrt{f}$  skin loss above 55 MHz.

(c) Comparison of the rg loss model (curve with  $\circ$  markers) with ADS' MSUB model (plain curve) for the 5-cm case study microstrip.

Figure 2.7: Modeling of the frequency dependent transmission line losses by g and r.

(a) Voltage transfer of GTEM input to the microstrip's far end, simulated with (dashed) and without (solid) the rg loss elements.

(b) Difference between the lossless and the lossy simulation.

Figure 2.8: Relevance of taking into account the losses for field-to-trace coupling.

must be used with care and intuition must be checked in general.

Using the lossless model, the near-end and far-end induced voltages of Figure 2.9 were predicted. These values will serve as a reference to compare other models to. It is interesting to note that either terminal voltage has a high-pass envelope.

However, it is a rather laborious task to manually mesh a trace. For the straight trace defined as case study, it was rather straightforward, but for a more realistically-shaped trace, it is more difficult and error-prone. Moreover, it is not easy to change the meshing resolution, which causes over-meshing and wasted time or under-meshing and the risk to miss important details in industrial practice. Therefore, manually meshing a trace

Figure 2.9: ADS simulation result for voltage transfer of the GTEM input to the near-end (dashed trace) and far-end (solid trace) of a 5-cm lossless microstrip trace.

and entering the meshes as discrete elements in a standard circuit simulator does not seem a promising direction for practical use.

## Meshing under Kron's formalism

To facilitate meshing of realistically-shaped traces and to promote experimentation with the meshing resolution, the meshing will be automated. As it is not straightforward to implement this inside existing circuit simulators with a Graphical User Interface (GUI), like ADS or OrCAD, it will be done in a custom circuit simulator.

First, this problem will be analyzed in terms of Gabriel Kron's formalism [29], because of its promise to handle complex electromagnetic systems [30]. Next, the analysis will be translated into a computer programme. Finally, the result will be compared to the result from manual meshing under ADS.

Generally, solving a problem in Kron's formalism consists of eight steps: stating the problem, drawing the associated graph, defining the topological base, entering the sources, transforming, solving in mesh space, deducing the differences of potentials and deducing other required quantities [31].

The problem was already stated in Figure 2.5 and now need to be converted to a graph. In this graph, *nodes* (or junctions) and *meshes* (or loops) need to be identified. Meshes consist of at least two *branches* (or vertices) that each connect two nodes. Simplified Kirchhoff branches will now be used, which generally consist of an impedance *Z* and a voltage source *e* as defined in Figure 2.10. One possible graph is depicted in Figure 2.11.

Figure 2.10: Simplified Kirchhoff branch. The difference of potential v across the branch and the current i through the branch are defined such, that when iv is positive, net power is dissipated in the branch (passive sign convention).

Figure 2.11: Graph representation of a three-cell transmission line model. Please verify that there are 4 meshes (dashed loops, numbered), 8 branches (with arrows, numbered) and 5 nodes (dots, not numbered).

Let i, v and e be column vectors in the *branch space*, that is: containing the currents and voltages of every branch. The (arbitrary) branch numbers of Figure 2.11 define which vector component represents which voltage and current: it is the definition of a *topological base*. Kirchoff's mesh rule and Ohm's law then hold as in e + v = Zi. In this case, the impedance matrix Z only has entries on its main diagonal:

$$Z = \begin{bmatrix} R_{\text{ne}} & & & & & & & \\ & j\omega l\Delta p & & & & & \\ & & \frac{1}{j\omega c\Delta p} & & & & & \\ & & & \frac{1}{j\omega c\Delta p} & & & & \\ & & & & \frac{1}{j\omega c\Delta p} & & & \\ & & & & & \frac{1}{j\omega c\Delta p} & & \\ & & & & & R_{\text{fe}} \end{bmatrix}$$

(2.11)

To incorporate the current sources in the simplified Kirchhoff branch, their Thévenin equivalents  $E_th$  are used. The source vector e stemming from the illumination electro-

magnetic field thus becomes:

$$e = \begin{bmatrix} 0 & 0 \\ H_n(0) & 0 \\ 0 & E_t(0) \\ H_n(\Delta p) & 0 \\ 0 & E_t(\Delta p) \\ H_n(2\Delta p) & 0 \\ 0 & E_t(2\Delta p) \\ 0 & 0 \end{bmatrix} \begin{bmatrix} j\omega\mu_0 h\Delta p \\ h \end{bmatrix}.$$

(2.12)

To solve for the mesh currents, the equations need to be transformed to another topological base: that of the *mesh space*. Simultaneously and inevitably, the branches are connected together. This is done by means of the *connectivity* matrix *L*, which links the branches (rows) with the meshes (columns). In this case,

$$L = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 1 & -1 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 1 & -1 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & -1 \\ 0 & 0 & 0 & 1 \end{bmatrix}. \tag{2.13}$$

Note that a minus sign signifies a branch going against the mesh direction. Tensors in mesh space will be denoted with a hat, e.g.:

$$\hat{e} = L^{-1}e$$

$i = L\hat{i}$   $\hat{Z} = L^{-1}ZL$   $\hat{v} = L^{-1}v \equiv 0$ ,

where the last vector (voltage around every mesh) is zero according to Kirchhoff's mesh law. The connectivity matrix L is Hadamard-like, of which the inverse can be found by its transpose [31]. Kirchoff's mesh rule and Ohm's law can be transformed to mesh space as follows:

$$L^{-1}v + L^{-1}e = L^{-1}Zi = L^{-1}ZL \hat{\imath}$$

(2.14)

$$\hat{e} = \hat{Z} \hat{\imath}. \tag{2.15}$$

Notice that by transforming to the lower-dimensional mesh space, the branches were connected together.

To solve the system, the pseudoinverse (denoted <sup>+</sup>) can be used:

$$\hat{\imath} = \hat{Z}^{+}\hat{e},\tag{2.16}$$

because the sources e and impedances Z are given, and the mesh currents  $\hat{i}$  are sought.

The quantities of interest are the near-end and far-end voltages, which can now be found by means of the terminal impedances:

$$V_{\rm ne} = -\hat{\imath}_1 R_{\rm ne} \tag{2.17}$$

$$V_{\rm fe} = \hat{\imath}_8 R_{\rm fe}. \tag{2.18}$$

As the frequency-domain response is sought, these expressions need to be evaluated as function of the frequency  $\omega$ .

In order to automatically mesh a microstrip and solve for its terminal voltages, the above analysis need to be generalised for an arbitrary number of cells and implemented as a computer programme.

To promote reproducible computational research [32], a free-to-use programming language is preferred. Python was selected, because it is, like its predecessor ABC, a programming language for intelligent computer users, which need not be computer programmers [33]. The numpy and matplotlib packages provide sufficient means for matrix algebra and visualisation of results, respectively.

It is rather straightforward to generalize (2.11) and (2.12), and functions were written that generate these for an arbitrary number of cells. To generalise (2.13), the cases of 2 and 3 cells were manually elaborated and first formulated as a unit test [34]. Next, an implementation satisfying both unit tests was written.

To evaluate (2.16), numpy's Moore-Penrose pseudoinverse was called upon, which uses Singular Value Decomposition (SVD). All code was then incorporated in the field2line framework, written for this thesis and allowing for easy comparison of different field-to-trace coupling models and measurements [35].

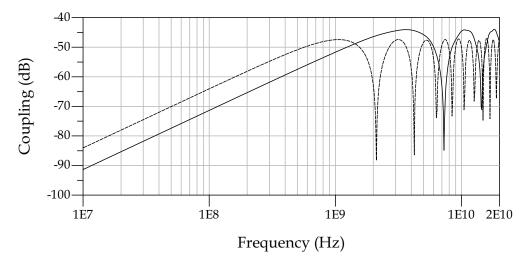

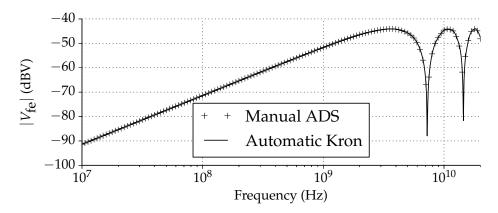

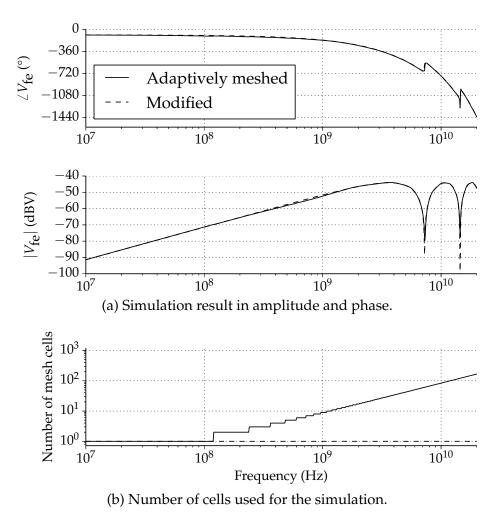

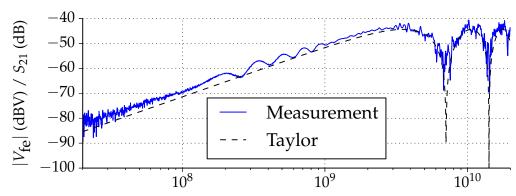

To be sure to over-mesh the structure, a meshing resolution of 50 cells per free-space-wavelength for the highest frequency of interest was chosen: 167 cells in total for the 5-cm case-study. With 661 logarithmically-spaced frequency points from 10 MHz to  $20\,\mathrm{GHz}$ , the calculation took  $54\,\mathrm{s}$  on an Intel  $2.53\,\mathrm{GHz}$  Core  $2\,\mathrm{Duo}$  processor. The far-end result is plotted and compared with the formerly obtained ADS result in Figure 2.12. The log frequency-weighted average difference between manual ADS meshing and automatic Kron meshing is  $-0.03\,\mathrm{dB}$ , the average absolute difference being  $0.1\,\mathrm{dB}$ .

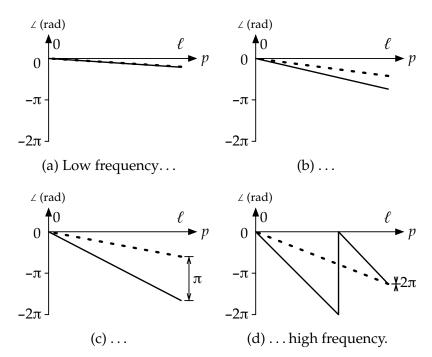

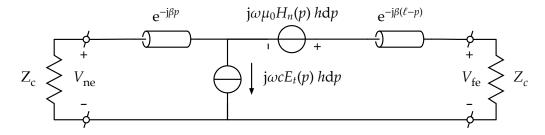

# Frequency-adaptive Meshing

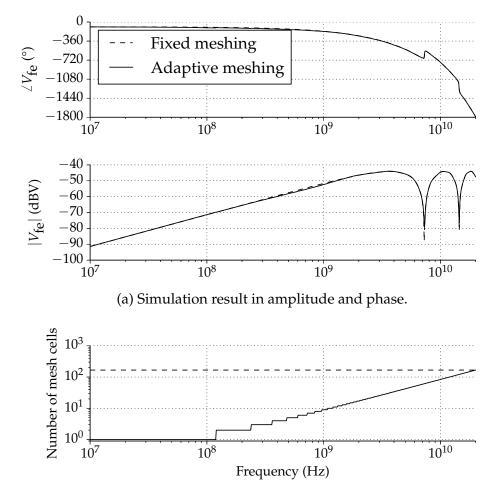

In order to accelerate the calculation, the Kron-based simulation was profiled. About half of the total execution time was found to be spent on the pseudoinverse of (2.16). This and other matrix manipulations depend heavily on the size of the matrix, which is drawn up for every frequency point. As the required number of cells is much lower for low frequencies, it makes sense to mesh the line for each frequency in the required number of cells. Note that the speedup will be most pronounced for a logarithmic frequency sampling. This was done with 50 cells per free-space-wavelength for each

Figure 2.12: Comparison between manually meshed (ADS) and automatically meshed (Kron) simulation of the far-end induced voltage.

frequency, reducing the execution time to  $4 \, \mathrm{s}$  on the same platform. Fixed and frequency-adaptive meshing are compared in Figure 2.13. An average difference between fixed and adaptive meshing of  $-0.1 \, \mathrm{dB}$  and an average absolute difference of  $0.2 \, \mathrm{dB}$  were obtained.

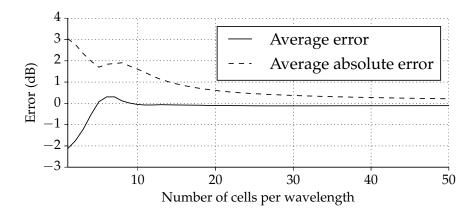

Now that the simulation runs rather quickly, the sensitivity to the meshing resolution can be easily studied. The number of cells per wavelength of the frequency adaptive simulation was swept from 1 to 50, and the error was calculated with respect to the simulation result for a fixed meshing of 50 cells per wavelength. The result is plotted in Figure 2.14. As can be seen, both error metrics become very reasonable (below  $\pm 1\,\mathrm{dB}$ ) from 20 cells per wavelength upward, at least in this case study.

### Conclusion

The simple case study of the far-end induced voltage on a 5-cm, characteristically terminated microstrip, illuminated by a vertically polarised plane wave, was studied by meshing the trace into many Taylor cells. This was first done manually, using ADS, carefully taking into account dielectric and copper losses. This led to the conclusion that the trace losses could be neglected to obtain only slightly pessimistic results. Then, the meshing was automated under Kron's formalism, yielding the same results as under ADS. The latter implementation also allowed for frequency-adaptive meshing, which achieved a speedup of an order of magnitude. In this case study, 20 cells per wavelength sufficed to obtain precise results.

Note that the automatic meshing could easily have been applied to multi-segment, arbitrarily-shaped traces with arbitrary loads. In spite of that and for simplicity, it was not done.

(b) Number of cells used for the simulation.

Figure 2.13: Comparison of fixed and frequency-adaptive automatic meshing in Kronbased simulation.

Figure 2.14: Sensitivity of adaptively-meshed simulation to the meshing resolution. A non-adaptively-meshed simulation with 50 cells per wavelength served as reference to calculate the error metrics.

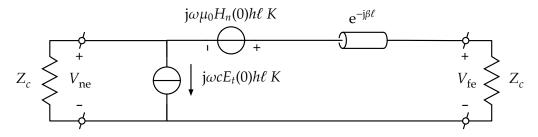

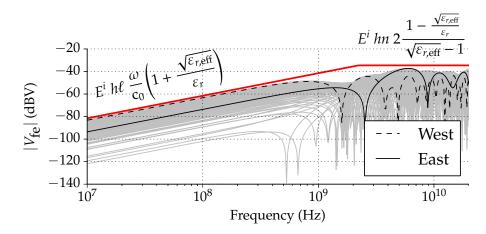

# 2.4 Modified Taylor Model

As shown in the previous section, the coupling of an incident wave to a PCB trace can be predicted by meshing the trace in electrically short Taylor cells, and solving the resulting circuit. Although the solution is found relatively quickly (4 s for a 5-cm microstrip), it does not yield insight. Indeed, the underlying model is completely opaque: imagine the system of equations of a two-cell mesh. Little understanding is obtained, and important engineering questions remain unanswered, like "What design parameters have significant impact on the field-to-trace coupling?" or "What is the worst-case illumination (to test devices)?"

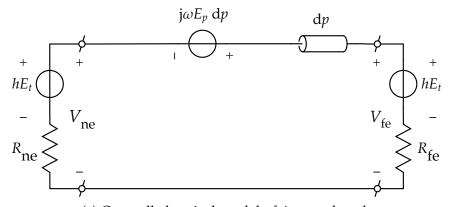

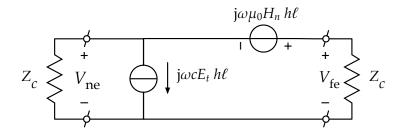

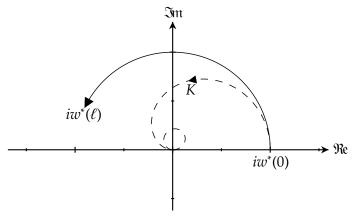

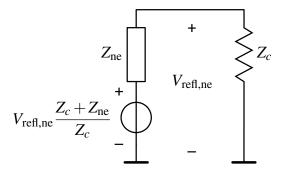

To answer these important questions, a transparent model will be constructed bottom-up. In each step, the model will be generalised, while keeping transparency by determining the worst case. The starting point is a single Taylor cell, valid for grazing-incident, vertically polarised plane wave incident on a single electrically short trace segment with matched loads. Then, the model will be generalised to an electrically long trace segment. Next, the model will be extended to multiple segments. Finally, the model will be generalised to comprise arbitrary loads. To conclude, this modified Taylor cell will be compared to above meshed Taylor simulations in terms of speed and insight.

### **Short Trace**

The starting point for the generalisation is one electrically short microstrip segment, illuminated by a vertically polarised, grazing-incident plane wave.

Electrically short means very small with respect to the exciting wavelength. Conversely, the exciting wavelength is very large with respect to the trace length, so the phase shift of the incident field along the line tends to zero and the field can be con-

Figure 2.15: An electrically short bifilar transmission line with characteristic loads modeled as a single Taylor cell.

sidered spatially uniform. Consequently, the line can be lumped as a single Taylor cell  $\Delta p = \ell$ . Because the line is electrically short, the phase lag  $\beta \ell$  is negligible so the passive line segment  $\ell$  can be neglected. The resulting model of a short line with characteristic loads ( $R_{\rm ne} = R_{\rm fe} = Z_c$ ) is shown in Figure 2.15. The low-frequency either-end terminal voltages can be found by inspection [10]:

$$V_{\rm LF} = -\frac{1}{2} j\omega \ c E_t Z_c \ h\ell \mp \frac{1}{2} j\omega \ \mu_0 H_n \ h\ell, \tag{2.19}$$

where c is the pul capacitance of the line. Unless otherwise noted, the near-end and far-end results are presented simultaneously throughout this thesis;  $\mp$  means minus for the near end and plus for the far end.

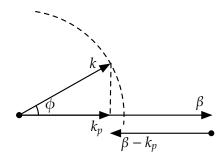

To evaluate this expression for grazing incidence, the substrate fields  $E_t$  and  $H_n$  first need to be determined. Let the incidence azimuth  $\phi$  be defined as in Figure 2.16a. Similarly to the end-fire case developed on p. 19, the incident field doubles in the substrate, the electric field is diminished by the permittivity and the phase speed remains unchanged, as shown in Figure 2.16b.

Using the constitutive relations

$$Z_c = \frac{1}{cv_{ ext{line}}} = \frac{\sqrt{\varepsilon_{r, ext{eff}}}}{c c_0}; \quad E^i = H^i \sqrt{\frac{\mu_0}{\varepsilon_0}}; \quad c_0 = \frac{1}{\sqrt{\mu_0 \varepsilon_0}},$$

the low-frequency terminal voltage under grazing incidence can now be expressed in terms of  $E^i$  and  $\phi$ :

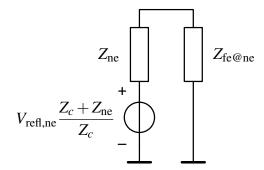

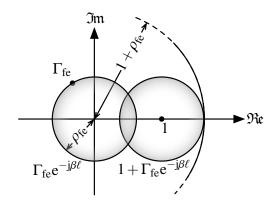

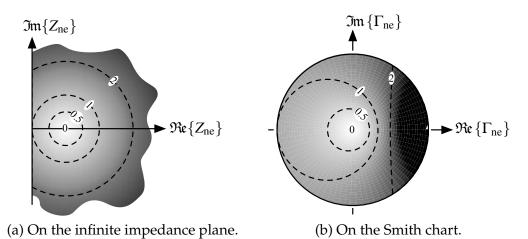

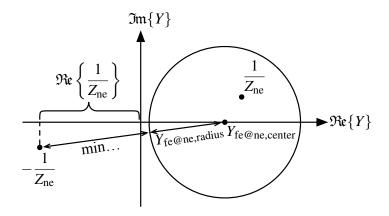

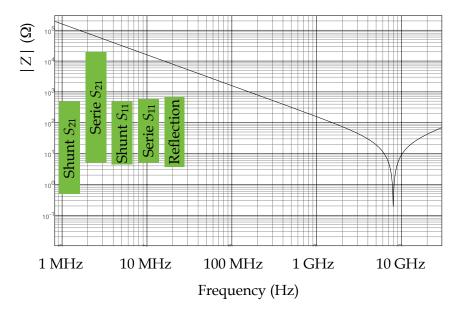

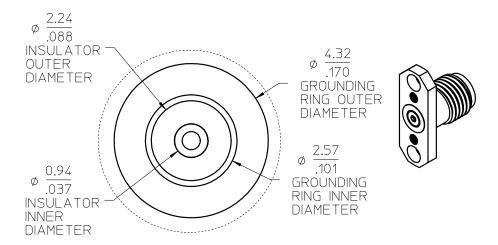

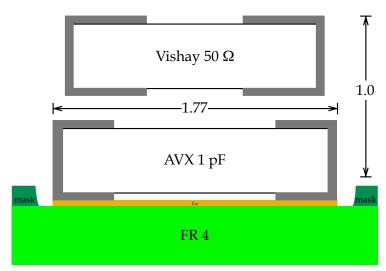

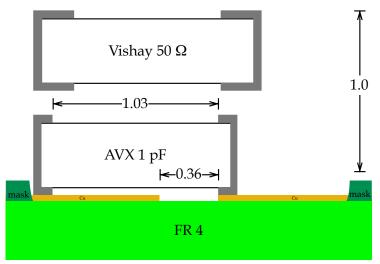

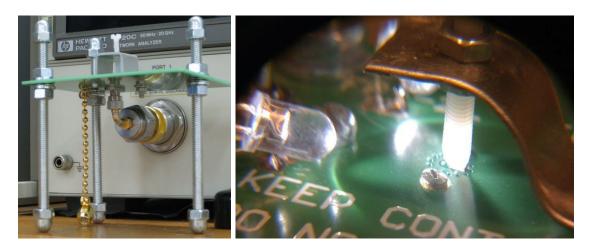

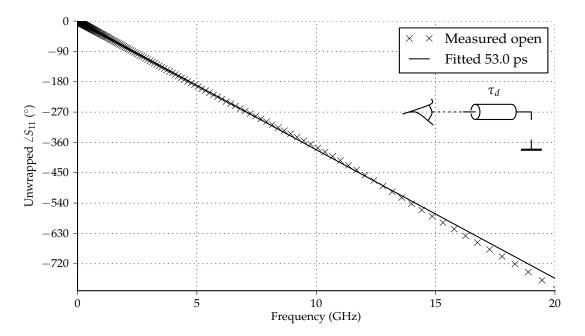

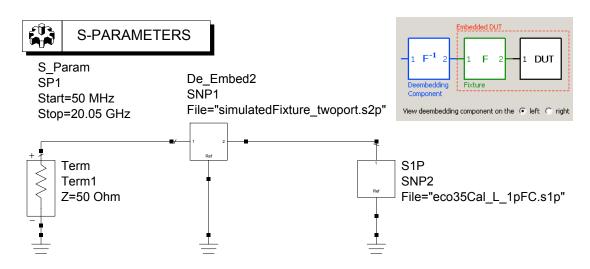

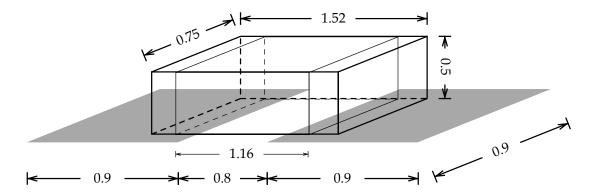

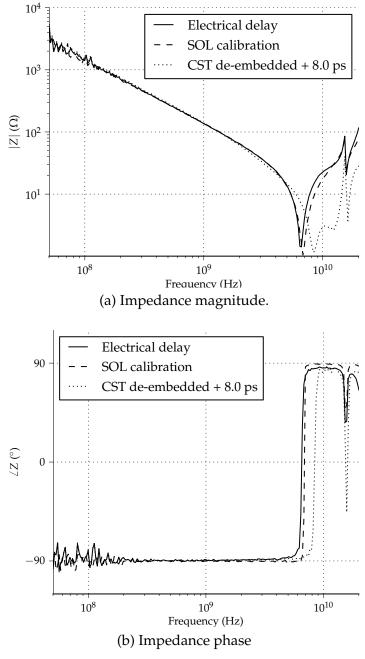

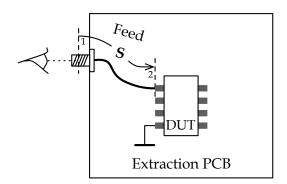

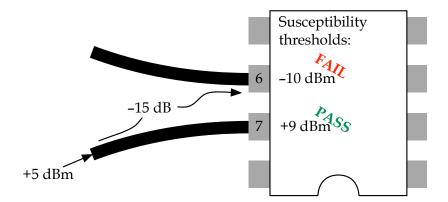

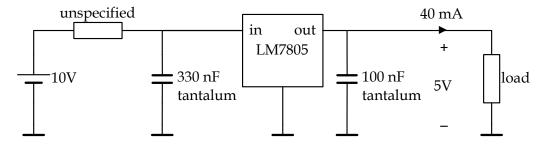

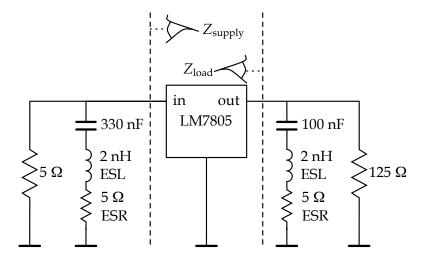

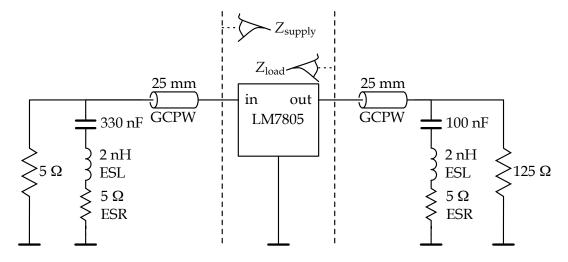

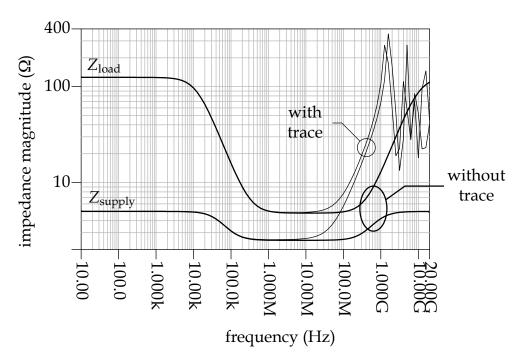

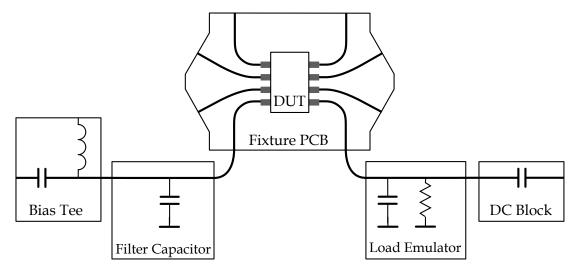

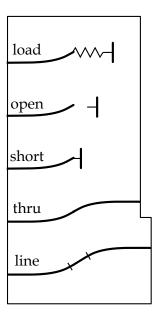

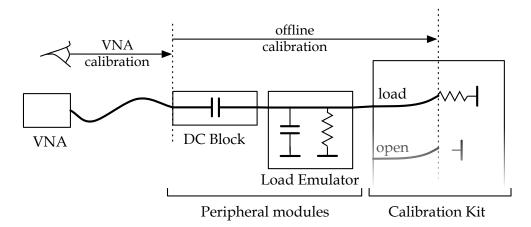

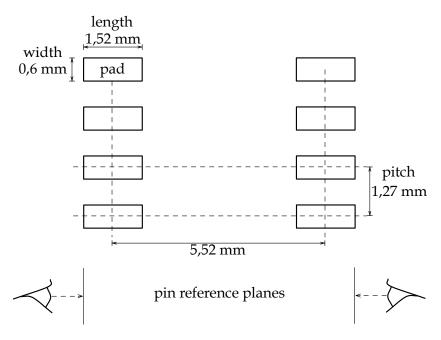

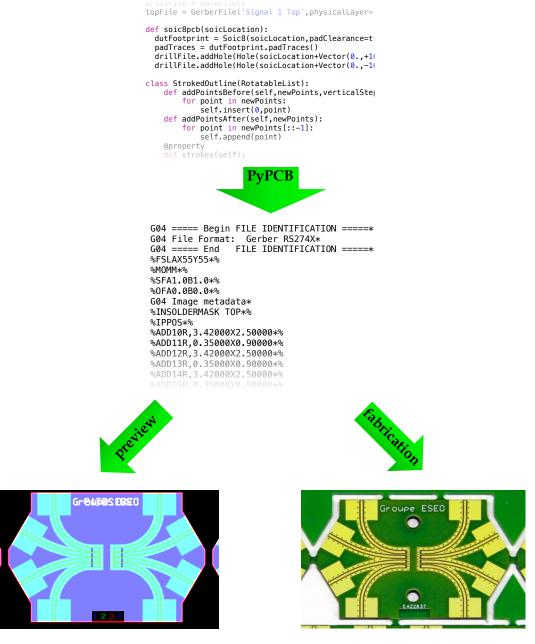

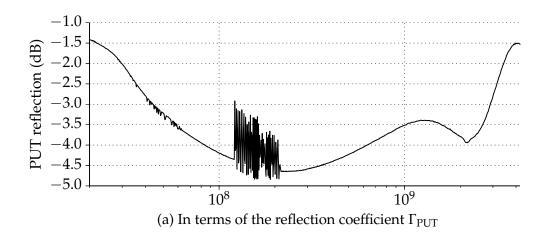

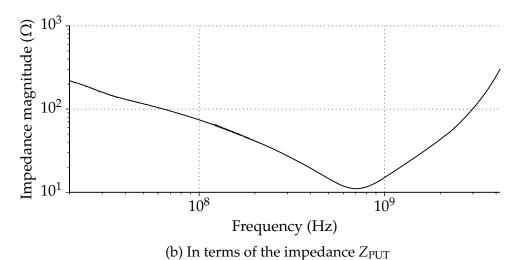

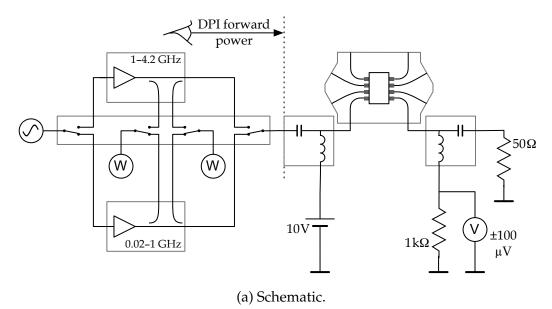

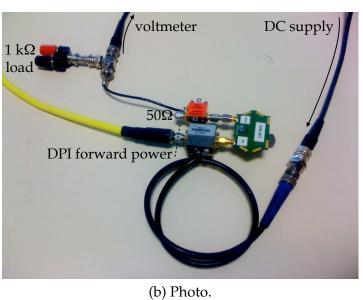

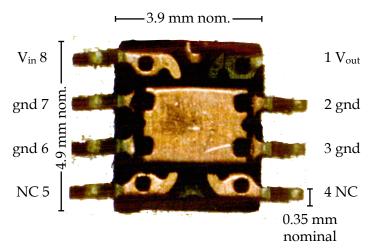

$$V_{\rm LF} = \frac{1}{2} j\omega \left( -Z_c c \frac{2E^i}{\varepsilon_r} \mp \mu_0 2H^i \cos(\phi) \right) h\ell$$