# Caractérisation et modélisation électro-thermique distribuée d'une puce IGBT: Application aux effets du vieillissement de la métallisation d'émetteur

Jeff Moussodji Moussodji

#### ▶ To cite this version:

Jeff Moussodji Moussodji. Caractérisation et modélisation électro-thermique distribuée d'une puce IGBT: Application aux effets du vieillissement de la métallisation d'émetteur. Autre [cond-mat.other]. École normale supérieure de Cachan - ENS Cachan, 2014. Français. NNT: 2014DENS0013. tel-01207802v2

### HAL Id: tel-01207802 https://theses.hal.science/tel-01207802v2

Submitted on 15 Oct 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

ENSC-2014-N°511

## THESE DE DOCTORAT DE L'ECOLE NORMALE SUPERIEURE DE CACHAN

Présentée par

Monsieur Moussodji Moussodji Jeff

#### pour obtenir le grade de

#### DOCTEUR DE L'ECOLE NORMALE SUPERIEURE DE CACHAN

#### Domaine:

ELECTRONIQUE-ELECTROTECHNIQUE-AUTOMATIQUE

#### Sujet de la thèse

Caractérisation et modélisation électro-thermique distribuée d'une puce IGBT - application aux effets du vieillissement de la métallisation d'émetteur

Thèse présentée et soutenue à Cachan le 02/04/2014 devant le jury composé de

| François FOREST     | Professeur des Universités     | Président               |

|---------------------|--------------------------------|-------------------------|

| Dominique PLANSON   | Professeur des Universités     | Rapporteur              |

| Frédéric RICHARDEAU | Directeur de Recherche CNRS    | Rapporteur              |

| Stéphane AZZOPARDI  | Maitre de Conférences HDR      | Examinateur             |

| Thierry KOCINIEWSKI | Maitre de Conférences UVSQ     | Examinateur (Encadrant) |

| Zoubir KHATIR       | Directeur de Recherche IFSTTAR | Directeur de thèse      |

|                     |                                |                         |

Thèse préparée à :

Laboratoire des Technologies Nouvelles

#### Remerciements

Mon travail de thèse a été mené au Laboratoire de Technologies Nouvelles (LTN) de l'Institut Français des Sciences et Technologies des Transports, de l'Aménagement et des Réseaux (IFSTTAR).

Mes premiers remerciements sont adressés à mes encadrants Zoubir KHATIR et Thierry KOCINIEWSKI qui m'ont accueilli au sein de leur équipe de recherche. Ils ont su me faire bénéficier de leurs expériences et de leurs compétences.

Je remercie également les membres du jury M. Dominique PLANSON, M. Frédéric RICHARDEAU, M. François FORES et M. Stéphane AZZOPARDI pour m'avoir fait l'honneur d'examiner mon travail de thèse.

Je remercie toute l'équipe du SATIE et du CNAM pour leur accueil chaleureux lors de mes nombreux passages dans le cadre de travaux de ma thèse. Une pensée particulière à M Stéphane LEFEBVRE et à Mme Mounira BOUARROUDJ-BERKANI pour leur aide dans la caractérisation de mes échantillons.

Mes remerciements vont également aux membres du Groupe d'Etude de la Matière Condensée (GEMAc) de l'Université de Versailles Saint-Quentin-en-Yvelines, pour la mise à disposition des outils et techniques qui ont été d'un apport considérable dans cette thèse.

J'exprime ma profonde gratitude à toute l'équipe du LTN, particulièrement à Jean Pièrre OUSTEN toujours là pour moi, à Ali IBRAHIM, à Alexandre DE BERNARDINIS , à Laurent DUPONT, à Damien INGROSSO, à Juliette KAUV, à Richard LALLEMAND, à Nandhini RAJARAVISHANKAR, à Bogdan VULTURESCU, à Gérard COQUERY et à Denis CANDUSSO, pour leur accueil et leur sympathie. Je n'oublie pas tous mes collègues thésards, en particulier Abdelfatah KOLLI, Yoshua CELNIKIER, Souad BACHTI, Emmanuel FRAPPÉ, Benoît THOLLIN, Stéphane BUTTERBACH et Son Ha TRAN à qui je souhaite bonne continuation. Je tiens à remercier toute cette équipe pour leur aide précieuse, les conseils avisés et les conversations autour de la machine à café et à la cantine. Je garde un grand souvenir.

Bien entendu, je n'oublie pas les différentes personnes qui ont assisté à la soutenance de thèse.

Enfin, je souhaite remercier mon père, qui nous a quitté trop tôt, et sans qui, tout ceci n'aurait pu avoir lieu. Je lui dédie aujourd'hui ce travail....

Je vais terminer mes propos par des extraits de « La Vie en Fleur » de Anatole FRANCE.

Je remercie la destinée de m'avoir fait naitre pauvre. La pauvreté me fut une amie bienfaisante ; elle m'enseigna le véritable prix des biens utiles à la vie, que je n'aurais pas connu sans elle ; en m'évitant le poids du luxe, elle me voua à l'art et à la beauté. Elle me garda sage et courageux.... La Pauvreté oblige ceux qu'elle aime à lutter dans l'ombre avec elle et ils sortent au jour de son étreinte, les tendons froissés, mais le sang plus vif, les reins plus souples, les bras plus forts.

Ayant eu peu de part aux biens de ce monde, j'ai aimé la vie pour elle-même, je l'ai aimée sans voiles, dans sa nudité tour à tour terrible et charmante.

La pauvreté garde à ceux qu'elle aime le seul bien véritable qu'il y'ait au monde, le don qui fait la beauté des êtres et des choses, qui repend son charme et ses parfums sur la nature, le Désir.

« Elle est tout entière douloureuse la vie des hommes, et il n'est pas de trêve à nos souffrances». Ainsi parle la nourrice de Phèdre et les soupirs de sa poitrine n'ont point été démentis. « Et pourtant, ajoute la

vieille Crétoise, nous aimons cette vie, parce que ce qui la suit n'est que ténèbres sur lesquelles on a semé des fables». On aime aussi la vie, la douloureuse vie, parce qu'on aime la douleur. Et comment ne l'aimerait-on pas? Elle ressemble à la joie, et parfois se confond avec elle.

Anatole FRANCE « La Vie en Fleur »

#### Résumé

Les convertisseurs de puissance structurés autour de puces de puissance (IGBT, MOSFET, Diodes, ...,) sont de plus en plus sollicités dans les systèmes de transport, du ferroviaire à l'aéronautique, en passant par l'automobile. Dans toutes ces applications, la fiabilité de ces composants constitue encore un point critique. C'est notamment le cas dans la chaine de traction de véhicules électriques (VE) et hybrides (VH), où les puces sont souvent exposées à de fortes contraintes électriques, thermiques et mécaniques pouvant conduire à leur défaillance. Dans ce contexte, l'amélioration des connaissances sur les effets des dégradations des composants semi-conducteurs de puissance et leurs assemblages dus aux stress électrothermiques et thermomécaniques est incontournable. En particulier sur la puce semi-conductrice elle-même, siège d'interactions physiques importantes, et en son voisinage immédiat.

Les objectifs de la thèse sont de mettre en lumière les stress électro-thermiques et mécaniques dans les puces et leurs effets sur la puce et son voisinage immédiat et à évaluer les effets de dégradations à l'aide de modèles distribués. Les travaux comportent ainsi deux volets.

Un volet expérimental original visant la caractérisation électrothermique de puce de puissance (IGBT et diode) sur la base de micro-sections. La piste suivie par cette approche devrait permettre de rendre possible la caractérisation d'un certain nombre de grandeurs physiques (thermiques, électriques et mécaniques) sur les tranches sectionnées des puces sous polarisation (en statique, voire en dynamique) et ainsi contribuer à l'amélioration des connaissances de leur comportement. Ainsi, des cartographies de distributions verticales de température de puce IGBT et diode et de contraintes mécaniques sont présentées. C'est, à notre connaissance une voie originale qui devrait permettre d'ouvrir un large champ d'investigation dans le domaine de la puissance.

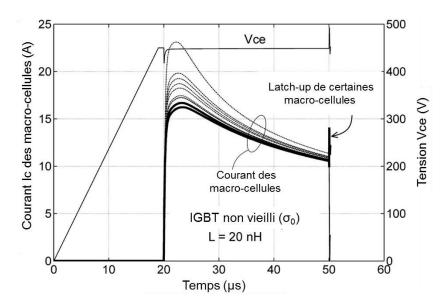

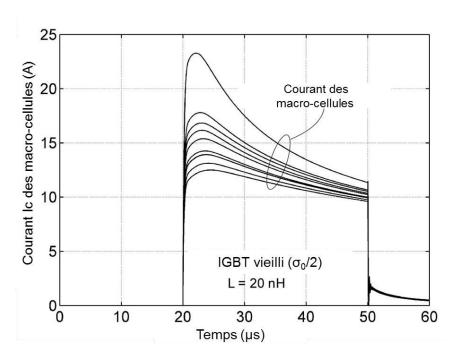

Le second volet est théorique et consiste à mettre en place un modèle électrothermique distribué de puce IGBT. Cette modélisation comme nous l'envisageons, implique de coupler dans un unique environnement (Simplorer), une composante thermique et une composante électrique. Le développement choisi passe par l'utilisation de modèle physique d'IGBT tels que celui de Hefner. Ce modèle est ensuite appliqué pour étudier le rôle et les effets du vieillissement de la métallisation de puce lors de régimes électriques extrêmes répétitifs tels que les courts-circuits. Un aspect original du travail est la démonstration par analyse numérique du mode de défaillance par latch-up dynamique à l'instant de la commande d'ouverture du courant de court-circuit. Ce phénomène bien qu'ayant été observé lors de vieillissement d'IGBT par répétition de courts-circuits n'avait à notre connaissance pas encore été simulé. La modélisation distribuée de la puce et la simulation du phénomène nous a ainsi permis de vérifier certaines hypothèses.

#### Mots clés

IGBT, diodes, Modélisation électrothermique, Caractérisations électrothermiques, Court-circuit, Microsection, Latch-up dynamique.

#### **Abstract**

Power modules, organized around power chips (IGBT, MOSFET, Diodes ...), are increasingly needed for transportation systems such as rail, aeronautics and automobile. In all these applications, power devices reliability is still a critical point. This is particularly the case in the powertrain of hybrid or electric vehicle in which power chips are often subjected to very high electrical and thermal stress levels such as hybrid or electric vehicle, power devices are subjected to very high electrical, thermal and mechanical stress levels which may affect their reliability.

Thus, the ability to analyze the coupled phenomena and to accurately predict degradation mechanisms in power semiconductors and their effects due to electro-thermal and thermo-mechanical stress is essential. Especially on the semiconductor chip where significant physical interactions occur and its immediate vicinity.

The aim of this work is to highlight the electro-mechanical and thermal stress and their effects on the semiconductor chip and its immediate vicinity, by evaluating the effects of damage using distributed models. This work consists of two parts:

An original experimental approach concerning the electro-thermal characterization of cross section power chips (IGBT and diodes). In this approach, it is exposed for the first time, an original way to characterize vertical thermal distributions inside high power silicon devices under forward bias. Thus, the vertical mapping of temperature and mechanical stress of IGBT and diode chip are presented. The impact of this work is that it opens a wide field of investigations in high-power semiconductor devices. The second part is theoretical and aims to implementing a distributed electro-thermal model of IGBT chip. The modeling strategy consists on a discretization of the power semiconductor chip in macro-cells with a distributed electro-thermal behavior over the chip area. In case of the IGBT devices, each macrocell is governed by the Hefner model and electrically linked by their terminals. Temperature variable used in these macro-cells are obtained by a nodal 3D-RC thermal model. This allows the distributed electro-thermal problem to be solved homogeneously and simultaneously by a circuit solver such as Simplorer. The aim of this model is to allow the accurate analysis of some effects in the electrical and thermal coupling over the chip. Especially, this model should allow explaining some effects such as the contacts position over the die metallization and the ageing of the emitter metallization of the chip. In a first step, the model is used to clarify how the current and the temperature map are distributed over the chip according to the relative positions between cells and wire bond contacts on the top-metal during short-circuit operation. In a second step, we will show how dynamic latch-up failures may occur when trying to turn-off a short-circuit process.

## Table des matières

| Rés  | umé     |                                                                            | 4  |

|------|---------|----------------------------------------------------------------------------|----|

| Abs  | tract.  |                                                                            | 5  |

| Tab  | le des  | matières                                                                   | 6  |

| List | e des   | figures                                                                    | 10 |

| Intr | oducti  | on Générale                                                                | 1  |

| Cha  | pitre l | . Mécanismes de défaillance, Caractérisations et Modélisations des IGBT    | 5  |

| I.   | Disp    | ositifs de puissance à IGBT                                                | 5  |

| 1    | . Le    | composant IGBT                                                             | 6  |

| 2    | . St    | ructure interne de l'IGBT                                                  | 7  |

| 3    | . Le    | s technologies de l'IGBT.                                                  | 8  |

|      | 3.1.    | Technologie IGBT PT                                                        | 8  |

|      | 3.2.    | Technologie IGBT NPT                                                       | 9  |

|      | 3.3.    | Les technologies IGBT FS, LPT, SPT, IEGT, CSTBT et HIGT                    | 9  |

|      | 3.4.    | Les technologies à grille en tranchée (Trench Gate)                        | 10 |

| II.  | Méca    | nnismes de dégradation : puce IGBT et voisinage immédiat                   | 11 |

| 1    | . Pu    | ce                                                                         | 11 |

|      | 1.1.    | Phénomène de latch-up dans un IGBT                                         | 12 |

|      | 1.2.    | L'emballement thermique                                                    | 16 |

| 2    | . L'    | oxyde de grille                                                            | 16 |

|      | 2.1.    | Les charges dans l'oxyde                                                   | 17 |

|      | 2.2.    | Les claquages de l'IGBT                                                    | 18 |

|      | 2.3.    | Modélisation de mécanismes de dégradation de l'oxyde de grille             | 19 |

|      | 2.4.    | Modes de défaillance de l'IGBT en condition de court-circuit               | 20 |

| 3    | . M     | étallisation d'émetteur                                                    | 20 |

|      | 3.1.    | Plasticité par mouvement de dislocation                                    | 22 |

|      | 3.2.    | Plasticité par diffusion                                                   | 23 |

| III. | Ca      | ractérisations électrothermiques de l'IGBT à l'aide de micro-sections      | 26 |

| 1    | . Ap    | pproche par micro section des composants de puissance                      | 26 |

| 2    | . Ca    | ractérisation de distributions de courant dans les composants de puissance | 27 |

| 3    | . Te    | chniques de caractérisations thermiques                                    | 30 |

|      | 3.1.    | La thermographie infrarouge                                                | 30 |

|      | 3.2.    | Spectrocopie Raman                                                         | 31 |

| IV.  | M       | odélisation électrothermique de composants de puissance                    | 33 |

| 1    | . Pr    | incipe de la simulation électrothermique                                   | 34 |

|             | 1.1.      | Méthodes de relaxation                                                             | . 34 |

|-------------|-----------|------------------------------------------------------------------------------------|------|

|             | 1.2.      | Méthodes directes                                                                  | . 37 |

| 2.          | Stra      | tégie de modélisation                                                              | . 40 |

|             | 2.1.      | Aspect thermique                                                                   | . 40 |

|             | 2.2.      | Aspects électriques                                                                | . 48 |

|             | 2.3.      | Couplage électro-thermique                                                         | . 52 |

| V.          | Concl     | usion                                                                              | . 57 |

| Cha         | pitre II. | Caractérisations sur micro-sections de composants de puissance                     | . 59 |

| I.          | Introd    | uction                                                                             | . 59 |

| II.<br>élec |           | -section de composants électroniques (IGBT et diode de puissance) et caractéristic | _    |

| 1.          | Préj      | paration des échantillons                                                          | . 60 |

| 2.          | Ana       | llyses optiques, électroniques et chimiques                                        | . 62 |

| 3.          | Car       | actérisations électriques statiques                                                | . 62 |

| III.        | Car       | actérisation thermique de microsection                                             | . 65 |

| 2.          | Car       | actérisation par thermographie infrarouge                                          | . 65 |

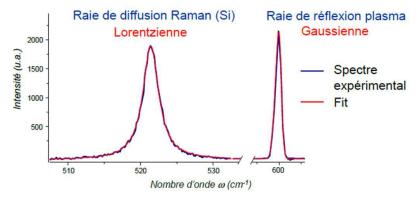

| 3.          | Car       | actérisation par spectroscopie micro Raman                                         | . 66 |

|             | 2.1.      | Dispositif expérimental                                                            | . 67 |

|             | 2.2.      | Cartographies thermiques des micro-sections par µ-Raman                            | . 69 |

|             | 2.3.      | Mesures de la distribution de température                                          | . 73 |

| IV.         | Con       | clusion                                                                            | . 78 |

| Cha         | pitre II  | I. Modèle électrothermique de l'IGBT                                               | . 79 |

| I.          | Introd    | uction                                                                             | . 79 |

| II.         | Outil     | le modélisation et simulation                                                      | . 80 |

| 1.          | Sim       | plorer                                                                             | . 80 |

| 2.          | Lan       | gage de modélisation : VHDL-AMS                                                    | . 80 |

| III.        | Cor       | nposante thermique                                                                 | . 81 |

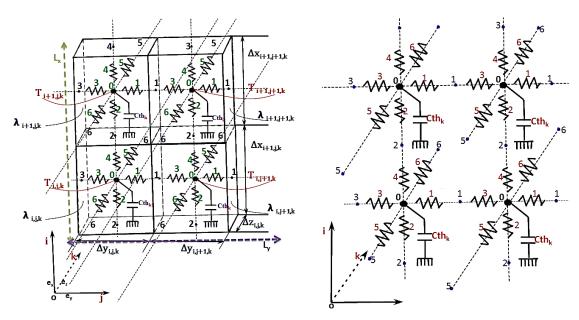

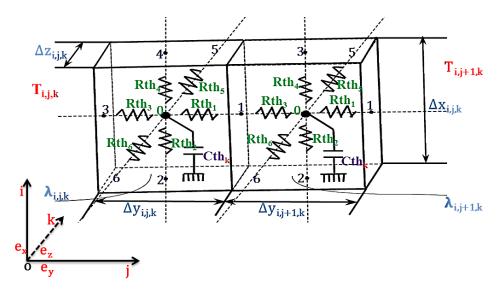

| 1.          | Des       | cription du modèle thermique proposé                                               | . 82 |

| 2.          | Eléı      | ments de volume                                                                    | . 83 |

| 3.          | Exp       | ressions des résistances et capacités thermiques                                   | . 85 |

| 4.          | Gér       | ération du modèle thermique                                                        | . 86 |

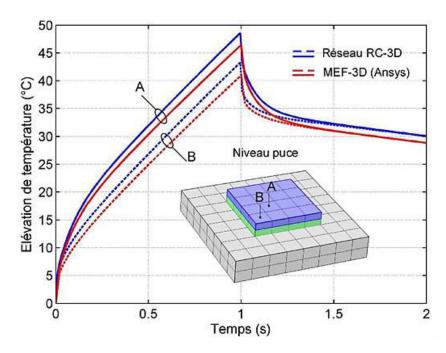

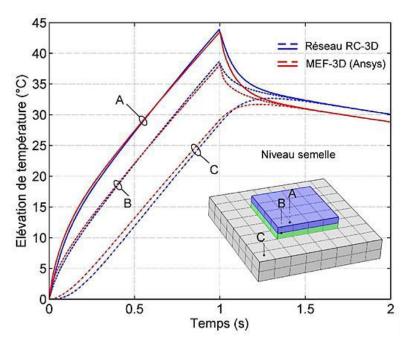

| 5.          | Val       | idation du modèle thermique                                                        | . 87 |

| IV.         | Cor       | nposante électrique                                                                | . 90 |

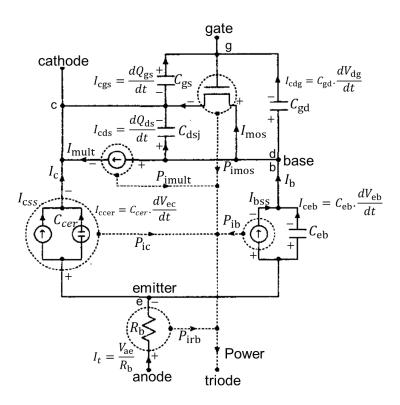

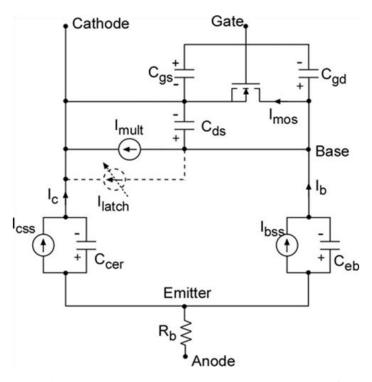

| 1.          | Des       | cription du modèle électrique d'Hefner du transistor IGBT                          | . 91 |

|             | 1.1.      | Le transistor bipolaire PNP de l'IGBT                                              | . 92 |

|             | 1.2.      | Le modèle de transistor MOS de l'IGBT                                              | . 93 |

|               | 1.3.             | Modèle capacitif de l'IGBT                                                           | 93     |

|---------------|------------------|--------------------------------------------------------------------------------------|--------|

|               | 1.4.             | Phénomènes d'Avalanche et secondaires                                                | 94     |

| 2.            | Para             | mètres du modèle d'Hefner dépendant de la température                                | 95     |

| 3.            | Diss             | ipation de puissance instantanée                                                     | 96     |

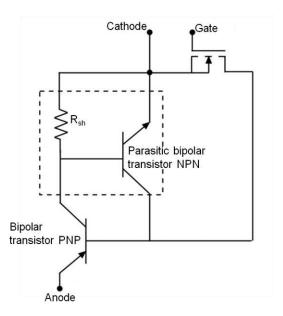

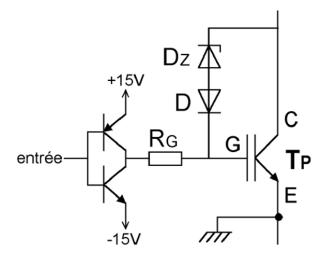

| 4.            | Prise            | e en compte du phénomène latch-up dans le modèle d'Hefner                            | 97     |

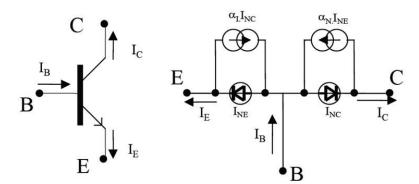

|               | 4.1.             | Modèle du transistor bipolaire d'Ebers-Moll.                                         | 98     |

|               | 4.2.             | Inclusion du courant de latch-up                                                     | 99     |

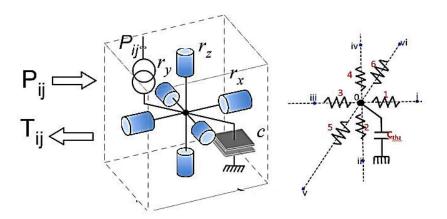

| 5.            | Mod              | lèle électrique de l'IGBT macro-cellulaire                                           | 101    |

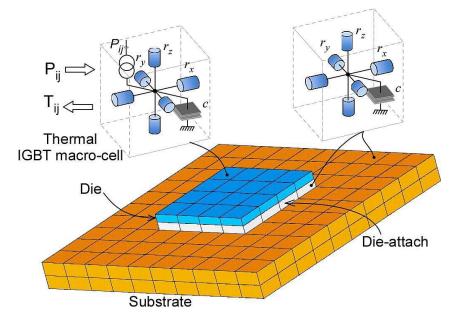

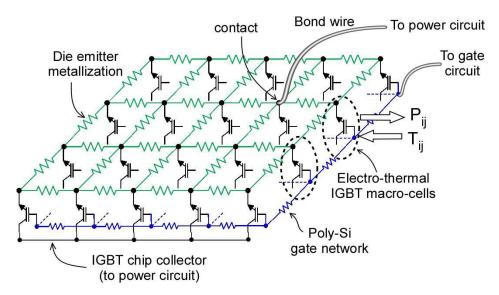

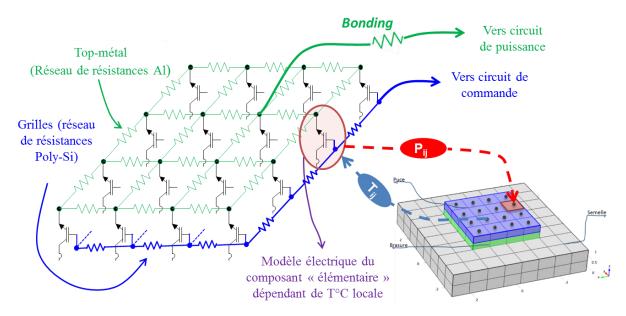

|               | 5.1.             | Discrétisation de l'IGBT en macro-cellules                                           | 101    |

|               | 5.2.             | Réseau de macro-cellules de type IGBT                                                | 101    |

|               | 5.3.             | Modelisation de la metallisation d'une puce                                          | 101    |

|               | 5.4.             | Discrétisation de la couche de polysilicium de grille                                | 103    |

| 6.            | Mod              | lèle électrique distribué 1D et multicellulaire de l'IGBT                            | 103    |

| V.            | Coupla           | ge électrothermique                                                                  | 104    |

| VI.           | Con              | clusion                                                                              | 105    |

| Chap<br>circu | oitre IV<br>iit. | . Simulation des effets du vieillissement de la métallisation sur les régimes de 107 | court- |

| I.            | Introdu          | action                                                                               | 107    |

| II.           | Les dif          | férents régimes extrêmes                                                             | 108    |

| 1.            | Régi             | ime d'avalanche.                                                                     | 109    |

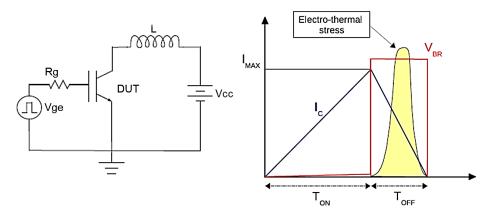

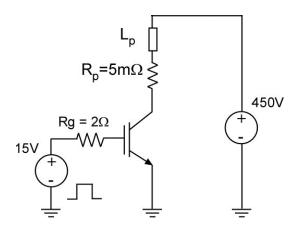

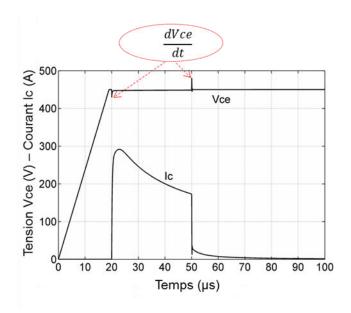

| 2.            | Les              | Régimes de court-circuit                                                             | 111    |

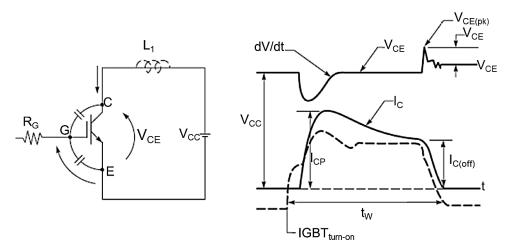

|               | 2.1.             | Court-circuit de type I                                                              | 111    |

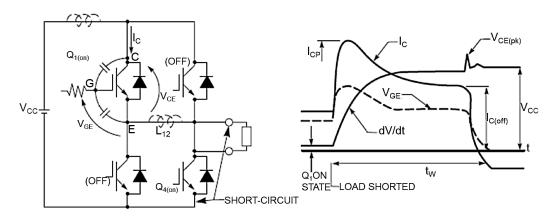

|               | 2.2.             | Court-circuit de type II                                                             | 112    |

|               | 2.3.             | Les modes de défaillance en régime de court-circuit type I                           | 113    |

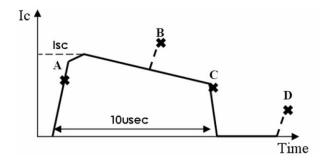

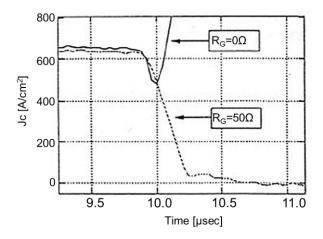

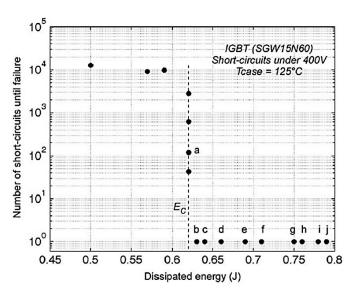

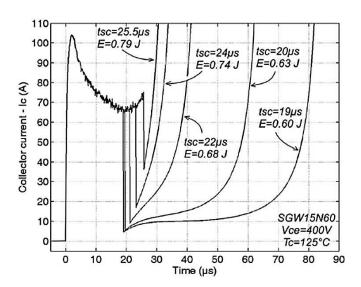

|               | 2.4.             | Défaillance survenant après la répétition de régimes de court-circuit                | 115    |

| III.          | Sim              | ulation et résultats                                                                 | 118    |

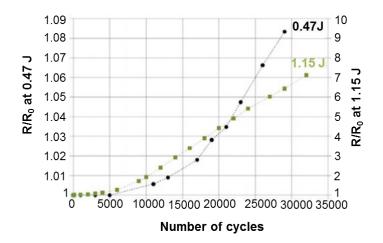

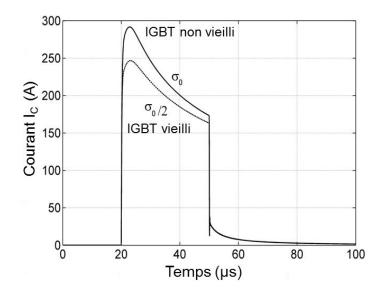

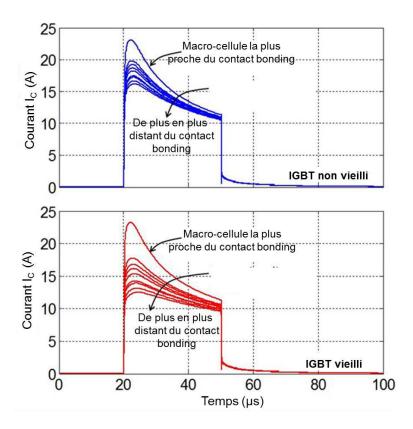

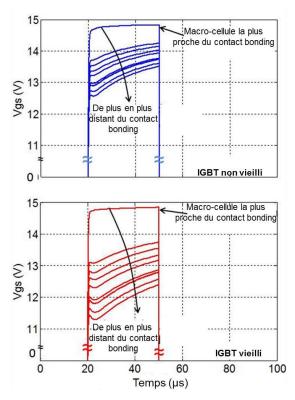

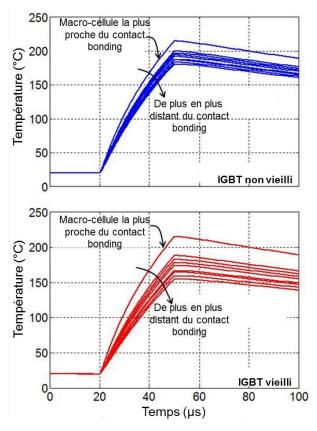

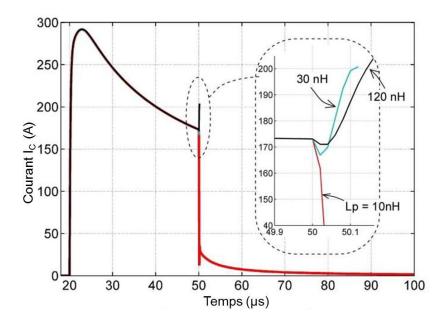

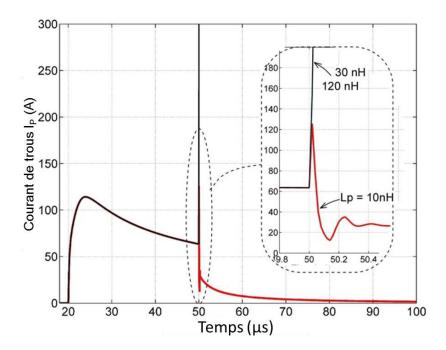

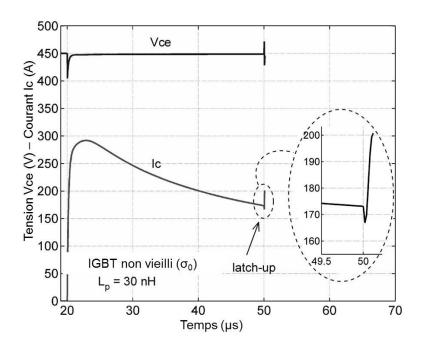

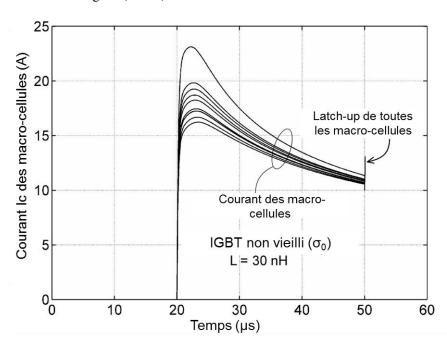

| 1.            | Effe             | t du vieillissement de la métallisation sur un court-circuit                         | 120    |

|               | 1.1.             | Effets sur le courant total de court-circuit (IC)                                    | 120    |

|               | 1.2.             | Effet sur les distributions de courant                                               | 121    |

|               | 1.3.             | Effet sur les distributions de température                                           | 123    |

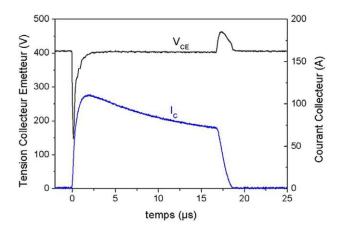

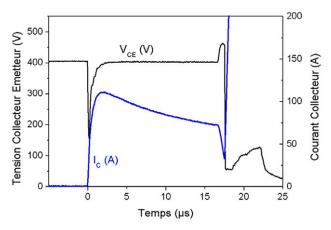

| 2.            | App              | lication au phénomène de latch-up dynamique                                          | 124    |

| IV.           | Con              | clusion                                                                              | 129    |

| Cond          | clusion          | Générale et Perspectives                                                             | 131    |

| Réfé          | rences.          |                                                                                      | 133    |

| Anno          | exes             |                                                                                      | 153    |

| Anno          | exe 1: C         | Caractérisation des matériaux par spéctroscopie Raman                                | 153    |

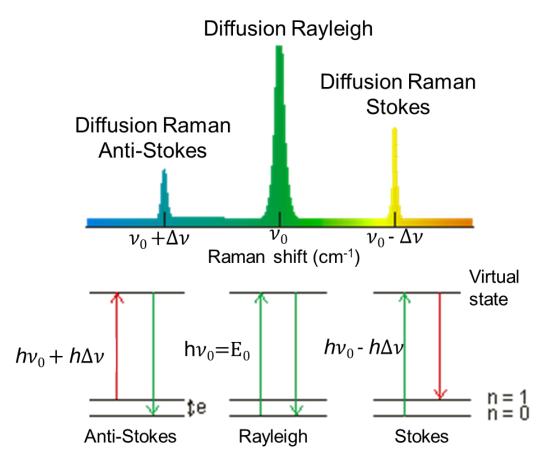

| 1.  | Effe     | et Raman                                                        | . 153 |

|-----|----------|-----------------------------------------------------------------|-------|

|     | 1.1.     | Diffusion Raman                                                 | . 154 |

|     | 1.2.     | Point de vue classique                                          | . 154 |

|     | 1.3.     | Point de vue quantique                                          | . 155 |

| 2.  | Spe      | ctre Raman du silicium monocristallin                           | . 155 |

| Ann | exe 2 :  | Modèle d'Hefner de l'IGBT                                       | . 157 |

| 1.  | Des      | cription du modèle électrique d'Hefner du transistor IGBT       | . 157 |

|     | 1.1.     | Modèle statique                                                 | . 157 |

|     | 1.2.     | Modèle dynamique                                                | . 161 |

| 2.  | Para     | amètres d'entrée du modèle d'Hefner dépendant de la température | . 165 |

| Ann | exe 3: 1 | Extraction de paramètres du Modèle                              | . 168 |

| 1.  | Rev      | erse engineering                                                | . 168 |

| 2.  | Les      | paramètres issus des caractéristiques statiques                 | . 168 |

| 3.  | Les      | paramètres issus des caractéristiques dynamiques                | . 171 |

## Liste des figures

## Chapitre I

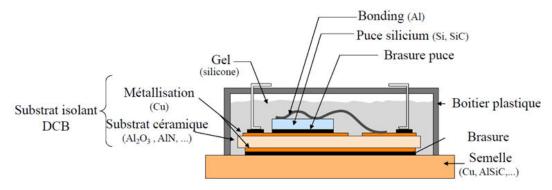

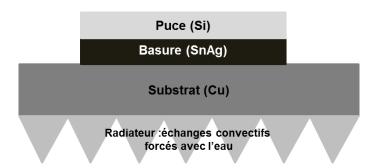

| Fig I. 1 Structure d'un module de puissance standard [Bou13]                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

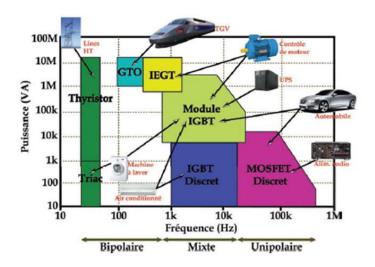

| Fig I.2 Champs d'application des composants de puissance [Nak08]                                                                                    |

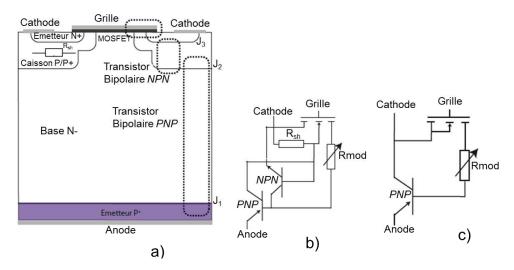

| Fig I.3 (a) Structure interne d'un IGBT; (b) schéma électrique équivalent; (c) schéma électrique                                                    |

| équivalent réduit [Gal10]                                                                                                                           |

| Fig I.4 Motif des cellules élémentaires d'un IGBT [Bou13]                                                                                           |

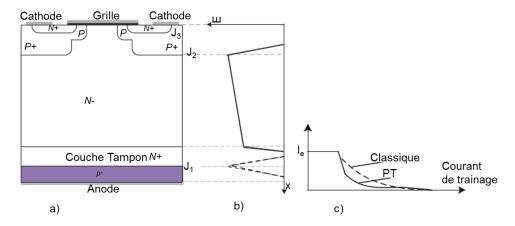

| Fig I.5 (a) Structure PT de l'IGBT, (b) la répartition du champ électrique en polarisation directe (trait                                           |

| plein) et inverse (en pointillé), (c) Courant de trainage [Gal10]9                                                                                  |

| Fig I.6 (a) Structure NPT (à couche homogène); (b) la répartition du champ électrique; (c) courant de                                               |

| trainage [Gal10]9                                                                                                                                   |

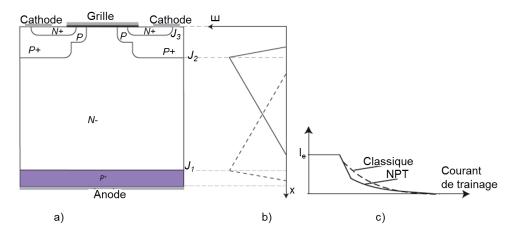

| Fig I.7 Structure de l'IGBT à grille en tranchée[Ibra09]                                                                                            |

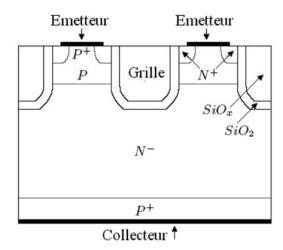

| Fig I. 8 Encoche dans la puce de silicium (à gauche); Fissuration dans la puce de silicium causée par                                               |

| le stress de flexion (micro-section optical image300x) (à droite) [Cia00]                                                                           |

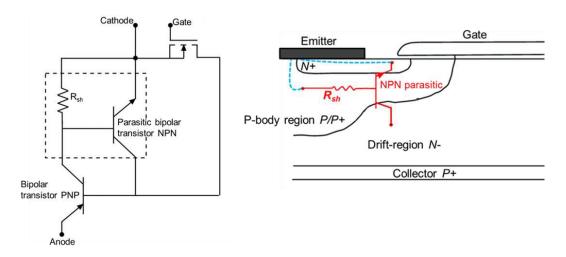

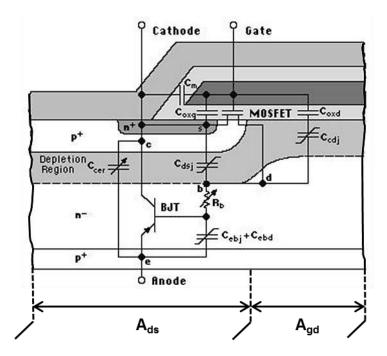

| Fig I. 9 Schéma de structure IGBT mettant en évidence les deux transistors bipolaires imbriqués                                                     |

| [Mou13a]                                                                                                                                            |

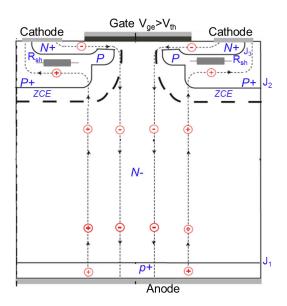

| Fig I.10 Trajectoires des porteurs des charges dans une structure IGBT en polarisation directe 13                                                   |

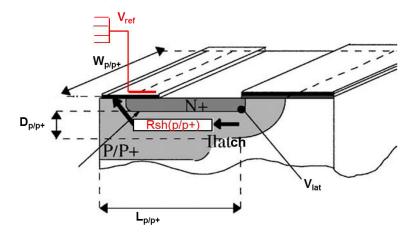

| Fig I.11 Localisation du caisson P/P+ de la cellule élémentaire IGBT [Bon04]                                                                        |

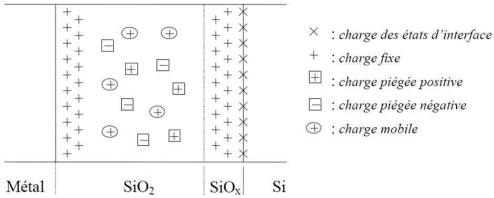

| Fig I.12 Les types de charges de l'oxyde et leur site [Man92]                                                                                       |

| Fig I.13 Modèle de percolation pour le claquage de l'oxyde [Deg99]                                                                                  |

| Fig I.14 Modes de défaillance en court-circuit de l'IGBT [Ben08]                                                                                    |

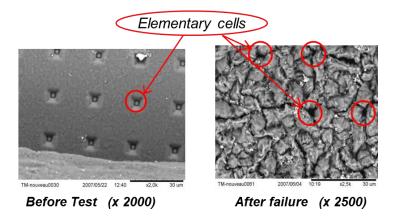

| Fig I.15 Déformation de la surface d'une métallisation [Cia02]                                                                                      |

| Fig I.16 (a) Film d'aluminium déposé sur un substrat Si oxydé, (b) même film après un cycle thermique                                               |

| entre 20 et 450°C dans un TEM [Leg09]                                                                                                               |

| Fig I.17 Modèle de Gao de relaxation des films polycristallins sur substrat rigide [Bue03]                                                          |

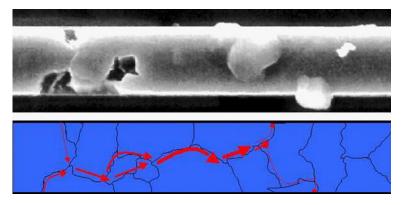

| Fig I.18 Résultat d'expériences d'électromigration dans une ligne d'aluminium (les chemins de                                                       |

| diffusion sont indiqués sur le schéma [Wed98, Foll04]                                                                                               |

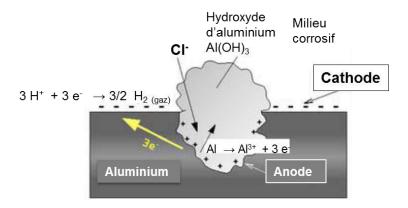

| Fig I.19 Schéma de la corrosion par piqure d'un alliage d'aluminium [Var79]                                                                         |

|                                                                                                                                                     |

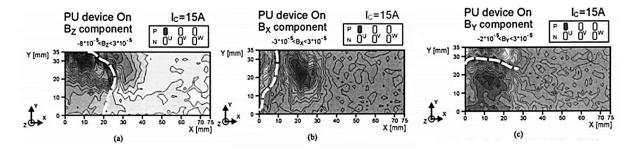

| Fig I.20 Distribution des composantes en x(a), y(b) et z(c) de l'induction magnétique [Bus03]                                                       |

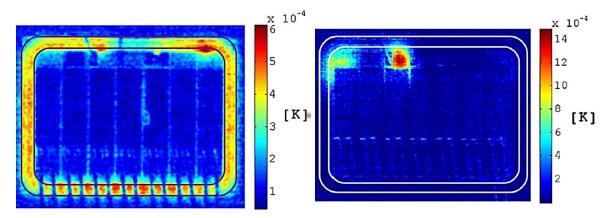

| Fig I. 21 Distribution de température par imagerie LIT pour un dispositif ( $t = \Delta t1$ à gauche), ( $t = \Delta t2 = 12$ us à draite) [Rio10a] |

| 12 μs à droite) [Ric10a]                                                                                                                            |

| Fig I.22 Distribution de champ magnétique à la surface de la métallisation avec des courants de fil de                                              |

| bonding de l'IGBT [Shi13] 30                                                                                                                        |

| Fig I. 23 Illustration des principales informations d'un spectre Raman                                                                              |

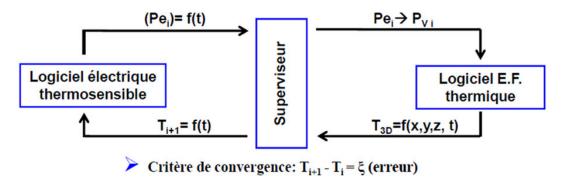

| Fig I.24 Schématisation de la méthode de relaxation [Hab07b]                                                                                        |

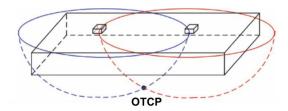

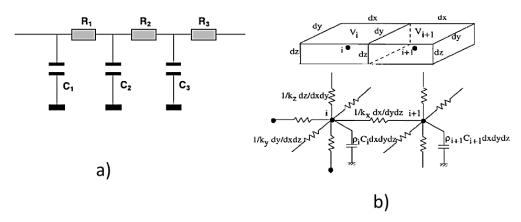

| Fig I.25 (a) Illustration de l'approche de modélisation par réseau distribué (b) Maillage volumique pour                                            |

| le calcul de l'effet thermique [Cas08]                                                                                                              |

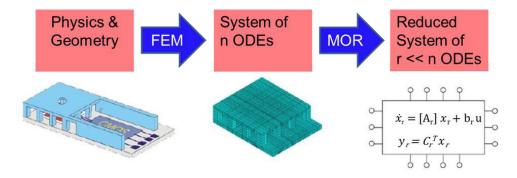

| Fig I.26 Schématisation de principe illustrant la réduction de modèle [Deh08]                                                                       |

| Fig I.27 Schéma de principe de la modélisation électrothermique couplée [Sau09]                                                                     |

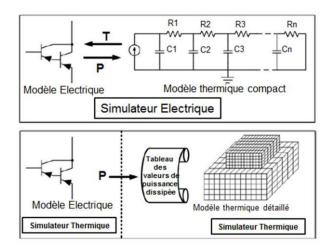

| Fig I.28 Schématisation de la méthode directe [Hab07b]                                                                                              |

| Fig I.29 Principe de la simulation électrothermique directe [Hec99]                                                                                 |

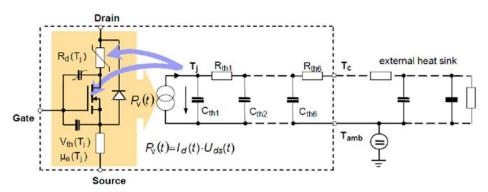

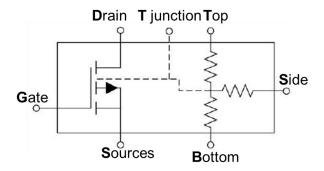

| Fig I.30 Exemple de modélisation électrothermique d'un transistor MOSFET et de son refroidisseur                                                    |

| [Mär00]                                                                                                                                             |

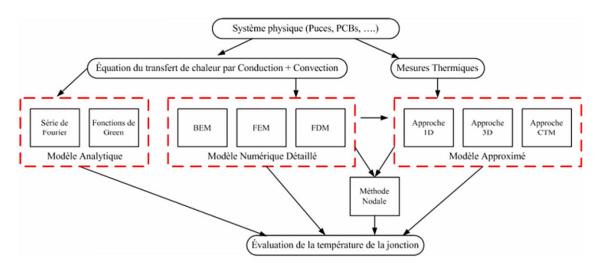

| Fig I. 31 Classification des différentes méthodes de modélisation thermique [Hab07b]41                                                              |

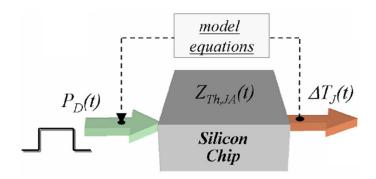

| Fig I.32 Modèle de fonction de transfert pour la réponse thermique d'une puce en fonction de la                                                     |

| puissance dissipée [Cas07]                                                                                                                          |

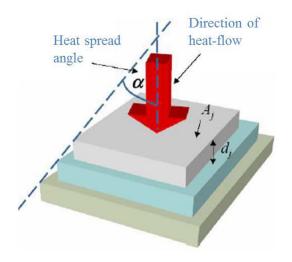

| Fig I.33 Propagation de la chaleur dans une puce de silicium [Cas07]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

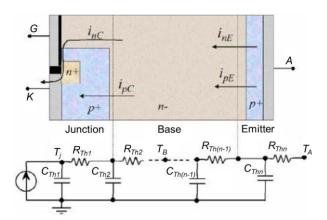

| Fig I.34 Correspondance thermique du réseau RC pour différentes régions de l'IGBT [Cas07]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44                                                                                                        |

| Fig I.35 Illustration du transfert thermique 3D [Mas01]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44                                                                                                        |

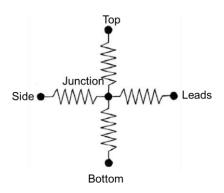

| Fig I.36 Modèle compact en étoile [Ros97a]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46                                                                                                        |

| Fig I.37 Bloc VHDL-AMS représentant un CTM [Hab05b]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47                                                                                                        |

| Fig I.38 Prise en compte du couplage thermique entre deux sources de chaleur [Hab05c]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                           |

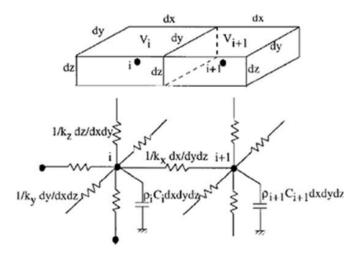

| Fig I. 39 Méthode Nodale : Discrétisation et réseau RC [Hab07b]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                           |

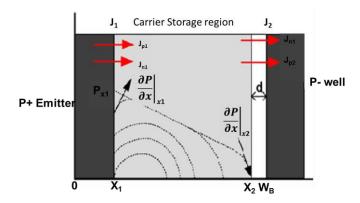

| Fig I.40 Distribution D des porteurs dans un IGBT [Cas07]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51                                                                                                        |

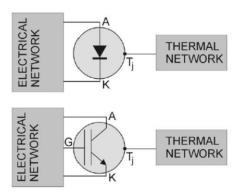

| Fig I.41 Modèles compacts électrothermique de la diode Pin et de l'IGBT [Igi01a, Igi01b]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                           |

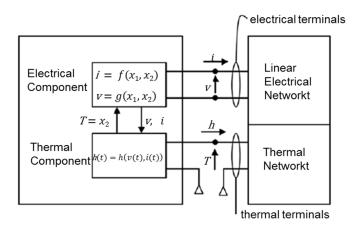

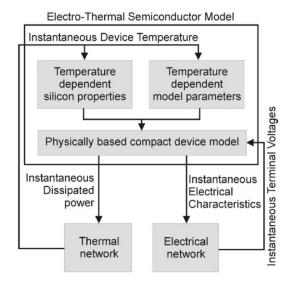

| Fig I. 42 Diagramme représentant le schéma du modèle électrothermique des semi-conducte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                           |

| puissance [Maw01]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                           |

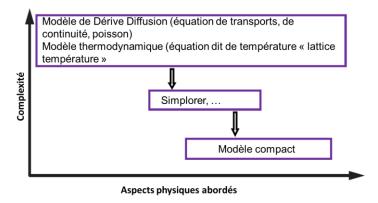

| Fig I.43 Approche multi-physique/ multi-échelle pour la modélisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                           |

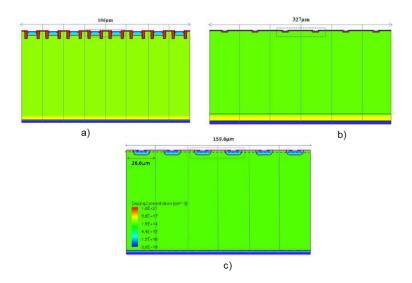

| Fig I.44 Structure d'IGBT : (a) NPT trench; (b) SPT planar; (c) NPT planar [Bou13]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |

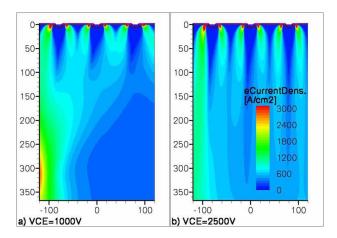

| Fig I.45 Densité de courant d'électron d'une structure d'IGBT 3-cellules présentant des inhomoge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                           |

| de profil de dopage [Kop09]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                           |

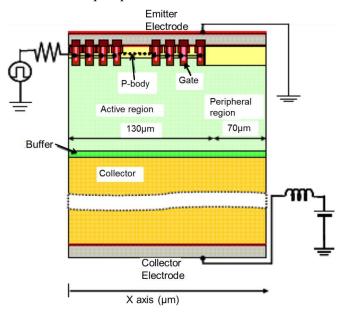

| Fig I.46 Schéma de la structure IGBT trench simulée                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                           |

| Fig I. 47 Résultats de la simulation en phase d'ouverture, b) profil de la densité de courant d'éle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                           |

| à un temps t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                           |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                           |

| Chapitre II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                           |

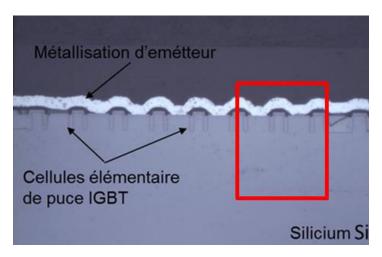

| Fig II.1 Module de puissance Semikron IGBT NPT à grille tranchée (600 V/ 200 A) ouvert (à ga<br>Puces extraites et résinées (à droite)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | T 62                                                                                                      |

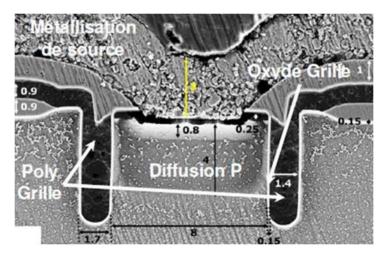

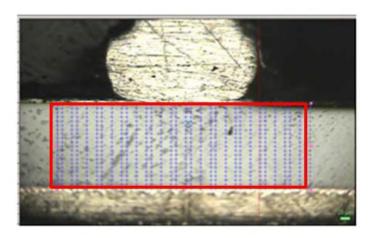

| Fig II.2 (a, b) Image optique de microsection, (c) visualisation de cellules élémentaires de l'IGB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 02                                                                                                        |

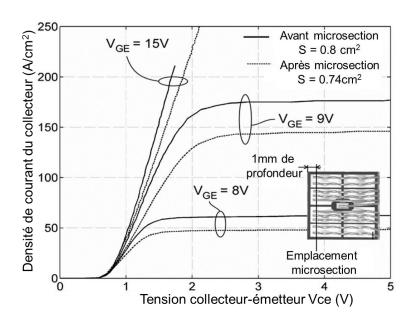

| Fig II.2 (a, b) Image optique de microsection, (c) visualisation de cellules élémentaires de l'IGB Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ssance                                                                                                    |

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ssance 63                                                                                                 |

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui (S=Surface active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ssance<br>63<br>IGBT                                                                                      |

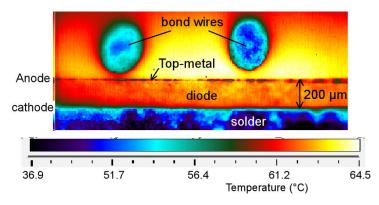

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui (S=Surface active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ssance<br>63<br>IGBT<br>64                                                                                |

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui (S=Surface active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63<br>IGBT<br>64<br>nement                                                                                |

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui (S=Surface active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ssance<br>63<br>IGBT<br>64<br>nement<br>65                                                                |

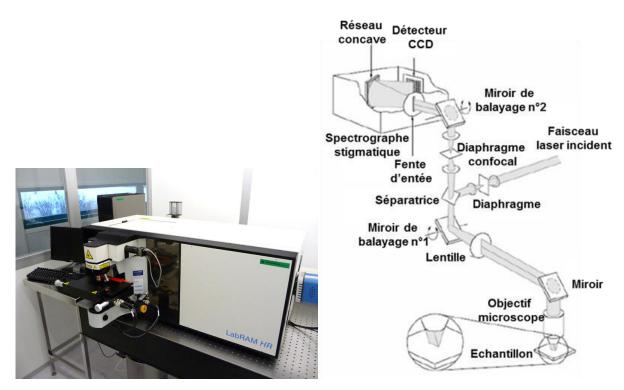

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui (S=Surface active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63 IGBT 64 nement 65 spositif 67                                                                          |

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui (S=Surface active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63 IGBT 64 nement 65 spositif 67                                                                          |

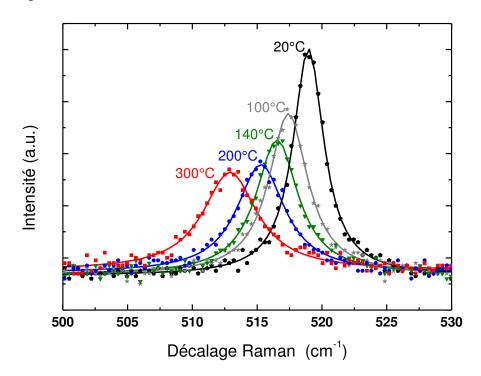

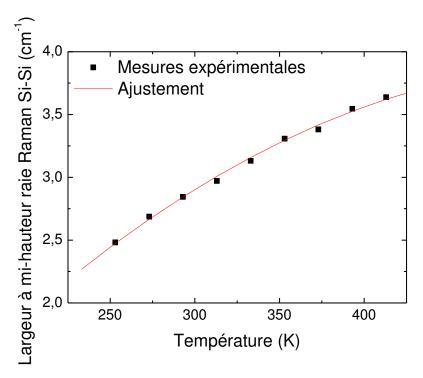

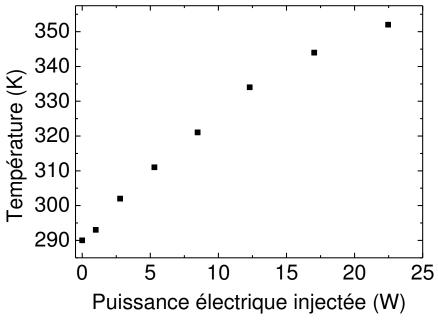

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui (S=Surface active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ssance 63 IGBT 64 nement 65 spositif 67                                                                   |

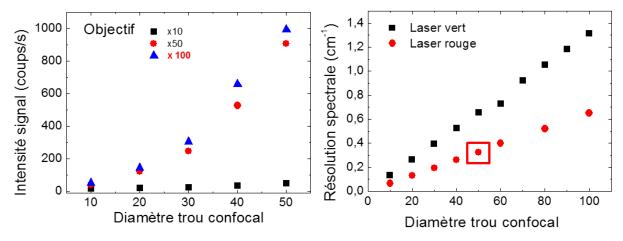

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui (S=Surface active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ssance 63 IGBT 64 nement 65 spositif 67 68                                                                |

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui (S=Surface active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ssance 63 IGBT 64 nement 65 spositif 67 68 69                                                             |

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui (S=Surface active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ssance 63 IGBT 64 nement 65 spositif 67 68 69 71                                                          |

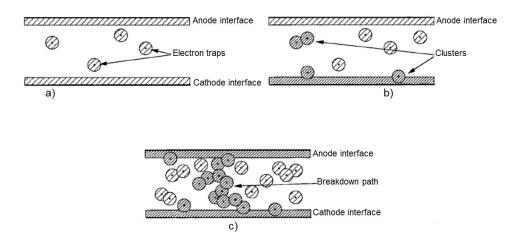

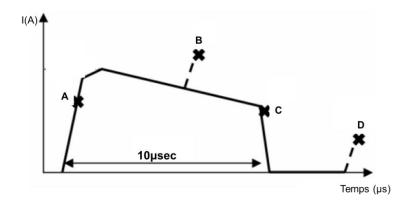

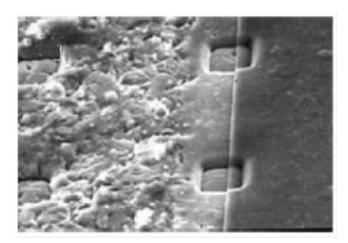

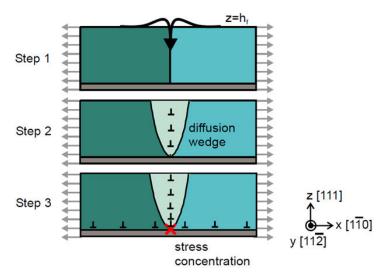

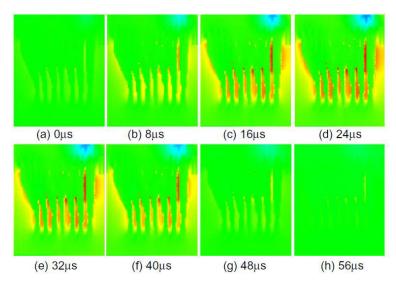

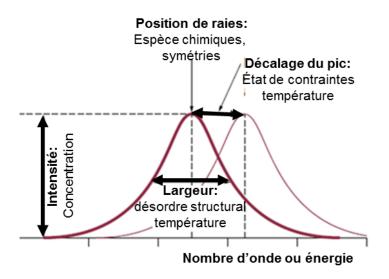

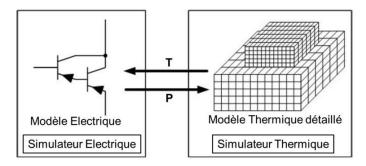

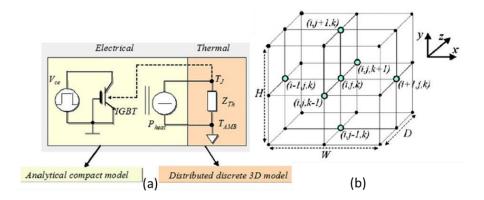

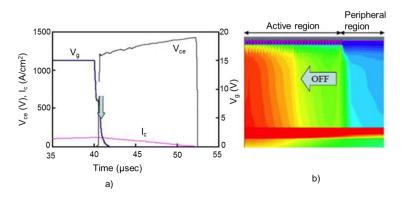

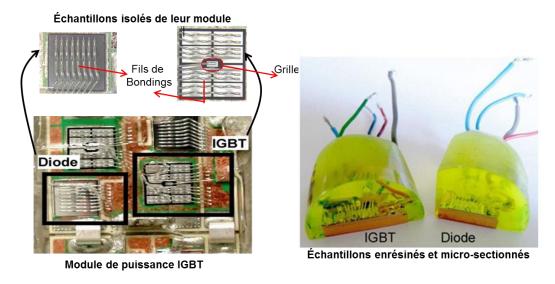

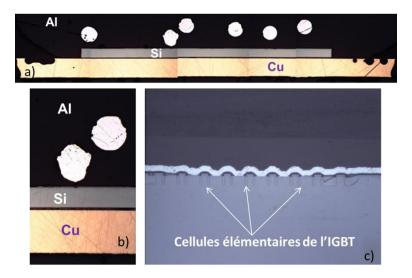

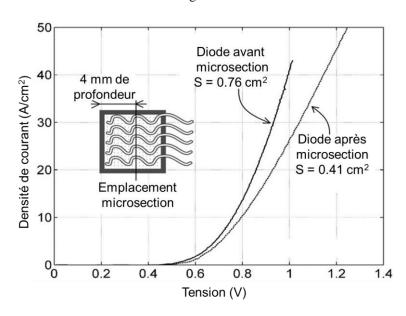

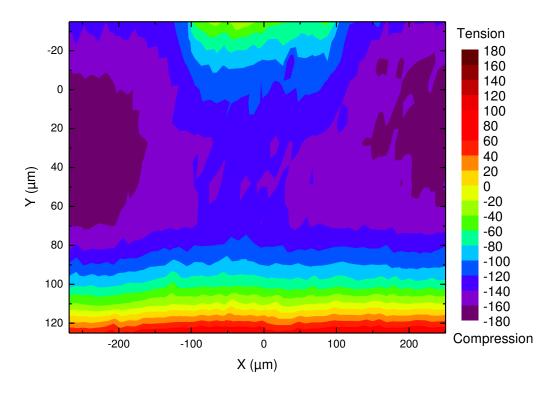

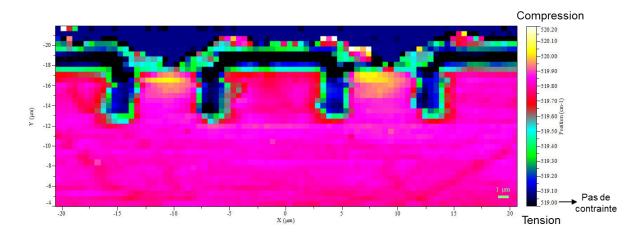

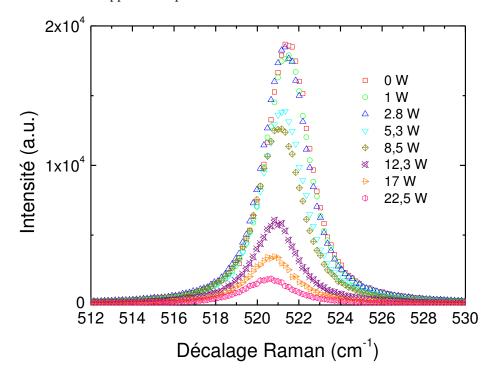

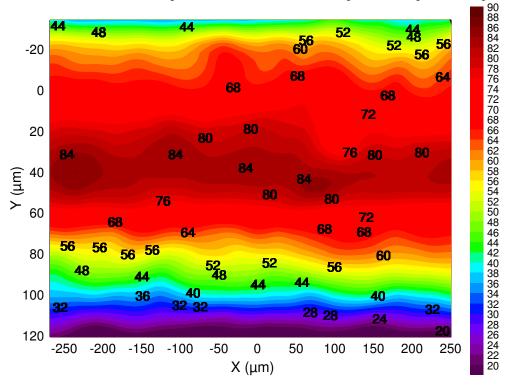

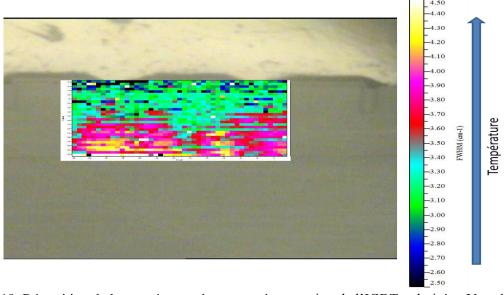

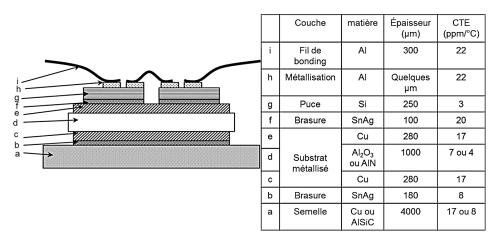

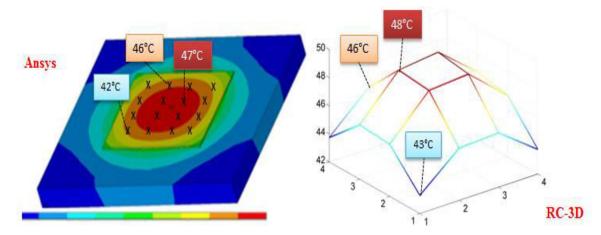

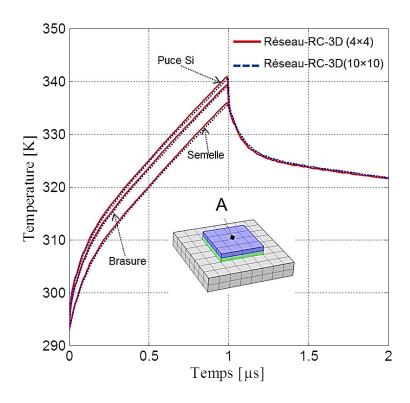

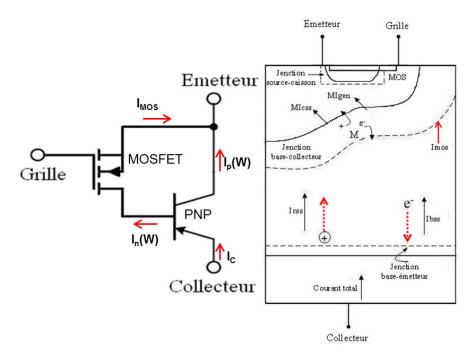

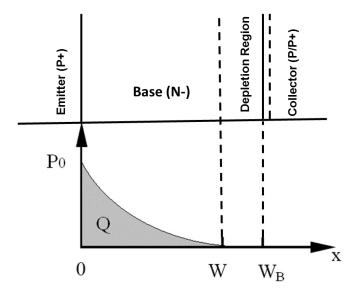

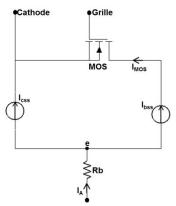

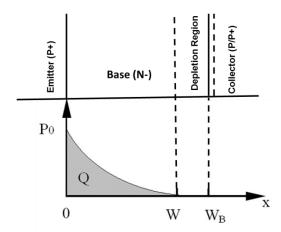

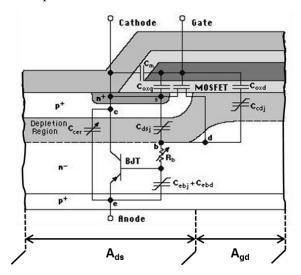

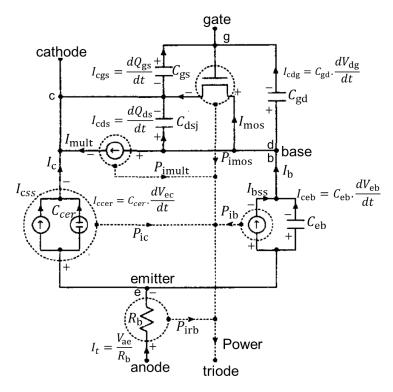

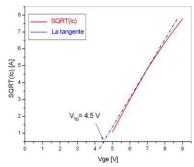

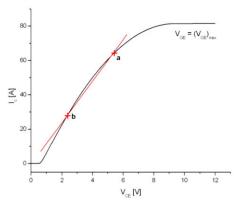

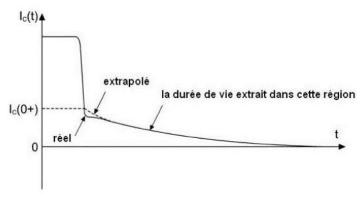

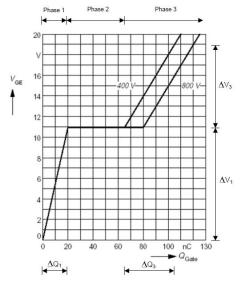

| Fig II.3 Caractéristiques statiques à l'état passant avant et après micro-section d'une diode de pui (S=Surface active)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ssance 63 IGBT 64 nement 65 spositif 67 68 69 71 72                                                       |